半導体装置およびその製造方法

【課題】 ゲート絶縁膜として酸化シリコン膜より誘電率の高い高誘電体膜を使用する場合にMISFETのしきい値電圧を低下するとともにしきい値電圧の微調整を可能にする技術を提供する。

【解決手段】 図2(b)に示すように、半導体基板上にゲート絶縁膜を介してゲート電極を形成する。ゲート絶縁膜には、酸化シリコン膜より誘電率の高い高誘電体膜が使用され、ゲート電極には、プラチナリッチシリサイド膜が使用される。プラチナリッチシリサイド膜は、プラチナ原子に対するシリコン原子の比が1未満である膜をいう(PtSix:x<1)。このプラチナリッチシリサイド膜からなるゲート電極には、導電型不純物としてホウ素が導入されている。このホウ素は、ゲート絶縁膜とゲート電極との界面に偏析している。

【解決手段】 図2(b)に示すように、半導体基板上にゲート絶縁膜を介してゲート電極を形成する。ゲート絶縁膜には、酸化シリコン膜より誘電率の高い高誘電体膜が使用され、ゲート電極には、プラチナリッチシリサイド膜が使用される。プラチナリッチシリサイド膜は、プラチナ原子に対するシリコン原子の比が1未満である膜をいう(PtSix:x<1)。このプラチナリッチシリサイド膜からなるゲート電極には、導電型不純物としてホウ素が導入されている。このホウ素は、ゲート絶縁膜とゲート電極との界面に偏析している。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置およびその製造技術に関し、特に、ハフニウム(Hf)系ゲート絶縁膜上にゲート電極を形成したMISFET(Metal Insulator Semiconductor Field Effect Transistor)を含む半導体装置に適用して有効な技術に関するものである。

【背景技術】

【0002】

米国特許第6,599,831 B1号公報(特許文献1)には、酸化シリコン膜よりなるゲート絶縁膜上にゲート電極を形成したMISFETについて記載されている。具体的には、ゲート電極としてフルシリサイド電極を用い、ドーパントによってMISFETのしきい値電圧を制御する技術が開示されている。

【0003】

近年、ゲート絶縁膜として酸化シリコン膜ではなく、酸化シリコン膜より誘電率の高い高誘電体膜を用いることが検討されている。この場合、ポリシリコン膜よりなるゲート電極のフェルミレベル(仕事関数)が酸化シリコン膜上でとりうるフェルミレベルからMISFETのしきい値が上昇する方向にシフトする現象が報告されている。この現象は、フェルミレベルピニングとして解釈されている(非特許文献1)。

【特許文献1】米国特許第6,599,831 B1号公報

【非特許文献1】IEEE TRANSACTIONS ON ELECTORON DEVICES、VOL.51、No6、JUNE 2004、pp.971-984

【発明の開示】

【発明が解決しようとする課題】

【0004】

従来、CMIS(Complementary Metal Insulator Semiconductor)回路を構成するnチャネル型MISFETおよびpチャネル型MISFETにおいて、ゲート絶縁膜は、酸化シリコン膜が使用されている。

【0005】

ところが、近年、半導体装置を構成するMISFETの微細化に伴って、ゲート絶縁膜の薄膜化が急速に進んでいる。ゲート絶縁膜の膜厚が薄くなると、トンネル効果により、電子がゲート絶縁膜中を通り抜ける現象が生じる。この現象によってゲート絶縁膜中にトンネル電流が流れる。このため、MISFETのリーク電流が増大することになる。

【0006】

そこで、ゲート絶縁膜として、酸化シリコン膜に代えて、酸化シリコン膜よりも誘電率の高い高誘電体膜に置き換える検討が進められている。これは、ゲート絶縁膜を高誘電体膜で構成した場合、酸化シリコン膜で構成した場合と同じ容量であっても、実際の物理膜厚を(高誘電体膜の誘電率/酸化シリコン膜の誘電率)倍だけ厚くできるので、結果としてリーク電流を低減することができるからである。高誘電体膜の材料としては、ハフニウム(Hf)酸化物やジルコニウム(Zr)酸化物といった金属酸化物が検討されている。

【0007】

このように、MISFETのゲート絶縁膜として高誘電体膜を使用することにより、ゲート絶縁膜を通過するリーク電流を低減することができるが、新たな問題が発生する。

【0008】

従来、nチャネル型MISFETおよびpチャネル型MISFETでは、ゲート電極としてポリシリコン膜が使用されている。そして、nチャネル型MISFETでは、ゲート電極を構成するポリシリコン膜にn型不純物(リンや砒素など)を導入している。これにより、ゲート電極の仕事関数(フェルミレベル)をシリコンの伝導帯近傍(4.05eV近傍)に設定することで、nチャネル型MISFETのしきい値電圧の低下を図っている。一方、pチャネル型MISFETでは、ゲート電極を構成するポリシリコン膜にp型不純物(ホウ素など)を導入している。これにより、ゲート電極の仕事関数をシリコンの価電子帯近傍(5.17eV近傍)に設定することで、pチャネル型MISFETのしきい値電圧の低下を図っている。これは、ゲート絶縁膜として酸化シリコン膜を使用した場合の例である。すなわち、ゲート絶縁膜として酸化シリコン膜を使用している場合では、ゲート電極にn型不純物あるいはp型不純物を導入することにより、ゲート電極の仕事関数を伝導帯近傍あるいは価電子帯近傍にすることができる。

【0009】

ところが、ゲート絶縁膜として、高誘電体膜を使用すると、ポリシリコン膜よりなるゲート電極にn型不純物あるいはp型不純物を導入しても、ゲート電極の仕事関数が、伝導帯近傍あるいは価電子帯近傍にならない現象が生じる。すなわち、ゲート絶縁膜として高誘電体膜を使用した場合、nチャネル型MISFETでは、ゲート電極の仕事関数が大きくなって伝導帯近傍から離れる。このため、nチャネル型MISFETのしきい値電圧が上昇する。一方、pチャネル型MISFETでは、ゲート電極の仕事関数が小さくなって価電子帯から離れるので、nチャネル型MISFETと同様にしきい値電圧が上昇する。このように、ゲート電極の仕事関数がしきい値電圧の上昇する方向にシフトする現象はフェルミレベルピニングとして解釈されている。このフェルミレベルピニングは、pチャネル型MISFETで顕著に現われる。すなわち、ゲート絶縁膜に高誘電体膜を使用した場合のしきい値電圧の上昇は、pチャネル型MISFETで顕著に現われる。また、ゲート絶縁膜として酸化シリコン膜を用いた場合は、ゲート電極(ポリシリコン膜)とゲート絶縁膜の界面に導電型不純物を偏析させることにより、MISFETのしきい値電圧の調整をすることが可能であった。これに対し、ゲート絶縁膜に高誘電体膜を用いた場合は、フェルミレベルピニングにより、導電型不純物をゲート電極(ポリシリコン膜)とゲート絶縁膜の界面に偏析させることによるしきい値電圧の制御効果は、ほとんど消失する。

【0010】

このことから、MISFETでしきい値電圧の上昇が生じ、MISFETの低消費電力設計が困難になる。特に、nチャネル型MISFETとpチャネル型MISFETを形成するCMIS回路では、低消費電力設計が困難となる。

【0011】

フェルミレベルピニングは、高誘電体膜よりなるゲート絶縁膜上に形成されたゲート電極に含まれるシリコンの量に左右されると考えられている。そこで、pチャネル型MISFETでは、ゲート電極に含まれるシリコンの量を低減することにより、フェルミレベルピニングを緩和することが検討されている。例えば、特願2004−292420号には、ゲート電極をプラチナリッチシリサイド膜で形成することにより、フェルミレベルピニングを緩和する技術が記載されている。すなわち、シリコン原子に対するプラチナ原子の比を大きくしたプラチナリッチシリサイド膜をゲート電極として用いることにより、しきい値電圧を低下させている。

【0012】

ここで、種々の半導体装置に使用されるMISFETは、それぞれの用途によって要求されるしきい値電圧が異なる。このため、ゲート電極をメタルリッチシリサイド膜で形成することだけでは、それぞれの用途に使用されるMISFETのしきい値電圧を調整するには不充分であるという問題点がある。

【0013】

本発明の目的は、ゲート絶縁膜として酸化シリコン膜より誘電率の高い高誘電体膜を使用する場合にMISFETのしきい値電圧を低下するとともにしきい値電圧の微調整を可能にする技術を提供することにある。

【0014】

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

【課題を解決するための手段】

【0015】

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、次のとおりである。

【0016】

本発明による半導体装置は、(a)半導体基板と、(b)前記半導体基板上に形成され、ハフニウム酸化物を主体として含むゲート絶縁膜と、(c)前記ゲート絶縁膜上に形成され、シリコン膜とメタル膜を反応させて形成したメタルシリサイド膜よりなるゲート電極とを有するMISFETを含む半導体装置に関するものである。そして、前記メタルシリサイド膜のメタル原子に対するシリコン原子の比が1未満であり、かつ、前記メタルシリサイド膜中に導電型不純物が導入されていることを特徴とするものである。

【0017】

本発明による半導体装置の製造方法は、(a)半導体基板上に、ハフニウム酸化物を主体として含むゲート絶縁膜を形成する工程と、(b)前記ゲート絶縁膜上にMISFETのシリコンゲート電極を形成する工程と、(c)前記シリコンゲート電極内に導電型不純物を導入する工程とを備える。さらに、(d)前記半導体基板上に、前記シリコンゲート電極よりも厚い膜厚の絶縁膜を形成した後、前記絶縁膜の表面を平坦化することにより、前記シリコンゲート電極の表面を露出する工程と、(e)前記シリコンゲート電極の上部にメタル膜を形成する工程とを備える。そして、(f)前記半導体基板を加熱し、前記シリコンゲート電極と前記メタル膜を反応させることにより、メタル原子に対するシリコン原子の比が1未満のメタルシリサイド膜からなるゲート電極を形成し、前記ゲート絶縁膜と前記ゲート電極の界面近傍に前記導電型不純物を偏析させる工程とを備えることを特徴とするものである。

【発明の効果】

【0018】

本願において開示される発明のうち、代表的なものによって得られる効果を簡単に説明すれば以下のとおりである。

【0019】

ゲート電極をメタルリッチシリサイド膜で形成するとともに導電型不純物を導入したので、ゲート絶縁膜として酸化シリコン膜より誘電率の高い高誘電体膜を使用する場合に、MISFETのしきい値電圧を低下することができるとともにしきい値電圧の微調整をすることができる。

【発明を実施するための最良の形態】

【0020】

以下、本発明の実施の形態を図面に基づいて詳細に説明する。なお、実施の形態を説明するための全図において、同一の部材には原則として同一の符号を付し、その繰り返しの説明は省略する。

【0021】

図1は、本実施の形態1におけるCMISFETの構成を示した断面図である。左側に形成されているMISFETQnがnチャネル型MISFETであり、右側に形成されているMISFETQpがpチャネル型MISFETである。

【0022】

図1において、半導体基板1には、素子分離領域2が形成されており、素子分離領域2で分離された活性領域には、p型ウェル3あるいはn型ウェル4が形成されている。p型ウェル3上には、MISFETQnが形成されており、n型ウェル4上には、MISFETQpが形成されている。

【0023】

MISFETQnは、p型ウェル3上にゲート絶縁膜5を有しており、このゲート絶縁膜5上にゲート電極6aが形成されている。ゲート絶縁膜5は、酸化シリコン膜より誘電率の高い高誘電体膜から構成される。

【0024】

従来、絶縁耐性が高い、シリコン−酸化シリコン界面の電気的・物性的安定性などが優れているとの観点から、ゲート絶縁膜として酸化シリコン膜が使用されている。

【0025】

しかし、素子の微細化に伴い、ゲート絶縁膜の膜厚について、極薄化が要求されるようになってきている。このように薄い酸化シリコン膜をゲート絶縁膜として使用すると、MISFETのチャネルを流れる電子が酸化シリコン膜によって形成される障壁をトンネルしてゲート電極に流れる、いわゆるトンネル電流が発生してしまう。

【0026】

そこで、酸化シリコン膜より誘電率の高い材料を使用することにより、容量が同じでも物理的膜厚を増加させることができる高誘電体膜が使用されるようになってきている。高誘電体膜によれば、容量を同じにしても物理的膜厚を増加させることができるので、リーク電流を低減することができる。

【0027】

例えば、高誘電体膜として、ハフニウム酸化物の一つであるハフニウムアルミネート膜(HfAlON膜)が使用されるが、ハフニウムアルミネート膜に代えて、酸化ハフニウム膜、HfON膜、HfSiO膜、HfSiON膜、HfAlO膜のような他のハフニウム系絶縁膜を使用することもできる。さらに、これらのハフニウム系絶縁膜に酸化タンタル、酸化ニオブ、酸化チタン、酸化ジルコニウム、酸化ランタン、酸化イットリウムなどの酸化物を導入したハフニウム系絶縁膜を使用することもできる。ハフニウム系絶縁膜は、ハフニウムアルミネート膜と同様、酸化シリコン膜や酸窒化シリコン膜より誘電率が高いので、ハフニウムアルミネート膜を用いた場合と同様の効果が得られる。

【0028】

ゲート絶縁膜5上に形成されるゲート電極6aは、ニッケルシリサイド膜から形成されている。ゲート電極の材料として、一般にポリシリコン膜が使用されているが、本実施の形態では、メタルシリサイド膜の一種であるニッケルシリサイド膜を使用している。MISFETQnのゲート電極として、一般的なポリシリコン膜を用いても良い。ゲート電極内のキャリアの空乏化によるMISFETQnの駆動電流の飽和を改善するには、キャリアの空乏化の影響がないメタルシリサイド膜を使用するのが好ましく、たとえばニッケルシリサイド膜がふさわしい。ニッケルシリサイド膜のみでなく、プラチナシリサイド膜、イリジウムシリサイド膜及びルテニウムシリサイド膜のようなシリサイド膜にしても良い。高誘電体膜をゲート絶縁膜5として使用しているMISFETQnにおいて、ゲート電極6aにポリシリコン膜あるいはニッケルシリサイド膜を使用すると、フェルミレベルピニングによるしきい値の上昇が生じるが、後述するMISFETQpのしきい値上昇と比較して、顕著ではない。

【0029】

ここで、このニッケルシリサイド膜において、ニッケル原子に対するシリコン原子の比はほぼ1とするのが良い。シリコン原子の比を1未満にしても良いが、nチャネル型MISFETであるMISFETQnでは、相対的なNi原子比の増加に伴ってゲート電極6aの仕事関数は増加する方向に変化する。このため、MISFETQnのしきい値電圧は上昇する。しきい値の増加を抑制するには、ニッケル原子に対するシリコン原子の比をほぼ1にするのが好ましい。この金属原子に対するシリコン原子の比は、他のメタルシリサイド膜を用いる場合も同様である。

【0030】

次に、ゲート電極6aの両側の側壁には、サイドウォール11が形成されており、サイドウォール11下のp型ウェル3内には、低濃度n型不純物拡散領域7、8が形成されている。低濃度n型不純物拡散領域7、8の外側には、高濃度n型不純物拡散領域12、13が形成されている。低濃度n型不純物拡散領域7、8および高濃度n型不純物拡散領域12、13には、リンや砒素などのn型不純物(導電型不純物)が導入されているが、低濃度n型不純物拡散領域7、8に比べて高濃度n型不純物拡散領域12、13の方が高濃度にn型不純物が導入されている。低濃度n型不純物拡散領域7、8と高濃度n型不純物拡散領域12、13により、MISFETQnのソース領域とドレイン領域が形成されている。ソース領域およびドレイン領域を低濃度n型不純物拡散領域7、8と高濃度n型不純物拡散領域12、13で形成しているのは、ソース領域およびドレイン領域をLDD(Lightly Doped Drain)構造とするためである。

【0031】

次に、pチャネル型MISFETであるMISFETQpの構成について説明する。MISFETQpは、n型ウェル4上にゲート絶縁膜5が形成されている。このゲート絶縁膜5は、上述したMISFETQnのゲート絶縁膜5と同様に、酸化シリコン膜より誘電率の高い高誘電体膜から形成されている。

【0032】

ゲート絶縁膜5上にはゲート電極6bが形成されており、このゲート電極6bは、プラチナリッチシリサイド膜から形成されている。上述したように、ゲート絶縁膜5として、高誘電体膜を使用し、ゲート電極6bとしてポリシリコン膜を使用すると、フェルミレベルピニングにより、しきい値電圧の上昇が生じる。このしきい値電圧の上昇は、nチャネル型MISFETであるMISFETQnよりも、pチャネル型MISFETであるMISFETQpのほうが顕著に現われる。すなわち、MISFETQnとMISFETQpとも、フェルミレベルピニングによりゲート電極の仕事関数(フェルミレベル)が概ねS

iの禁制帯の中央より伝導帯側によった位置に固定される。MISFETQnでは、伝導帯近傍にゲート電極の仕事関数がある場合、しきい値電圧を低くすることができるが、フェルミレベルピニングにより、伝導帯近傍から上述した位置にゲート電極の仕事関数が移動したとしてもそれほど移動量は大きくないので、しきい値電圧の上昇はあるにしてもそれほど問題は生じない。これに対し、MISFETQpでは、価電子帯近傍にゲート電極の仕事関数がある場合に、しきい値電圧を低くできる。ところが、フェルミレベルピニングにより、仕事関数が価電子帯近傍から上述した位置に移動すると、その移動量は、MISFETQnに比べて大きくなる。したがって、MISFETQpでは、しきい値電圧の上昇も大きくなり問題となる。

【0033】

そこで、pチャネル型MISFETであるMISFETQpでは、フェルミレベルピニングが、ゲート電極6bに含まれるシリコンの量を低減することにより緩和できる観点から、本実施の形態では、MISFETQpのゲート電極6bとしてプラチナリッチシリサイド膜を使用している。つまり、プラチナリッチシリサイド膜の仕事関数は、MISFETQpのしきい値電圧を低減するのに適している値を有しているので、MISFETQpのゲート電極6bに使用される。そして、さらに、ゲート電極6bのシリコン含有率を下げることで、フェルミレベルピニングが緩和されるので、プラチナリッチシリサイド膜を使用している。ここで、プラチナリッチシリサイド膜とは、プラチナ原子に対するシリコン原子の比が1未満である組成を有する膜である。化学式で表せば、PtSix(x<1)となる。具体的に、プラチナリッチシリサイド膜の組成は、Pt3Si、Pt12Si5、Pt2Siなどが考えられるが、これらの中では、シリコンの含有率を下げてフェルミレベルピニングを緩和する観点から、Pt3Siの組成をもつプラチナリッチシリサイド膜をゲート電極6bに使用することが望ましい。このように、ゲート電極6bの材料としてポリシリコン膜に代えて、プラチナリッチシリサイド膜を使用することにより、フェルミレベルピニングを緩和することができ、しきい値電圧を低下させることができる。しかし、ゲート電極6bをプラチナリッチシリサイド膜にしただけでは、種々の半導体装置を構成するMISFETで所望のしきい値を得るようにしきい値電圧の微調整を行なうことが困難である。

【0034】

ゲート絶縁膜として酸化シリコン膜を用い、ゲート電極としてポリシリコン膜を用いた場合、ゲート絶縁膜とゲート電極との界面に導電型不純物を偏析させることにより、しきい値電圧を調整することは行なわれていた。ところが、ゲート絶縁膜として高誘電体膜を用い、ゲート電極としてポリシリコン膜を用いた場合、フェルミレベルピニングが生じるため、ゲート絶縁膜とゲート電極との界面に導電型不純物を偏析させることによるしきい値電圧の調整効果は消失してしまっていた。すなわち、導電型不純物を偏析させることによるしきい値電圧の調整は効果が得られなかった。しかし、ゲート絶縁膜に高誘電体膜を用い、ゲート電極にメタルリッチシリサイド膜を用いた場合、ゲート絶縁膜とゲート電極との界面に導電型不純物を偏析させることにより、しきい値電圧を調整できることを、本発明者らは見出した。つまり、ゲート絶縁膜として高誘電体膜を使用している場合には、フェルミレベルピニングが生じるため、導電型不純物の偏析による効果が得られないと考えられていたが、ゲート電極にメタルリッチシリサイド膜を用いた場合は、導電型不純物の偏析による効果が得られることが判明した。

【0035】

そこで、本実施の形態では、プラチナリッチシリサイド膜からなるゲート電極6bに、導電型不純物を導入している。具体的には、ゲート電極6bとゲート絶縁膜5の界面近傍にホウ素(B)やアルミニウム(Al)などのp型不純物を偏析させている。これにより、MISFETQpのしきい値電圧がp型不純物を導入させない場合に比べて、さらに低下させることができる。そして、ゲート電極6bとゲート絶縁膜5の界面に偏析させるp型不純物の濃度を変えることにより、しきい値電圧の低下量を変えることができるので、MISFETQpのしきい値電圧の微調整を行なうことができる。このように、本実施の形態における特徴の一つは、プラチナリッチシリサイド膜からなるゲート電極6bに導電型不純物を導入する点にある。本実施の形態では、ゲート電極6bにp型不純物を導入しているが、しきい値電圧を上昇する方向に微調整したい場合には、p型不純物ではなく、リン(P)や砒素(As)、アンチモン(Sb)などのn型不純物を導入すればよい。そして、導入するn型不純物の濃度を変えることにより、しきい値電圧の微調整が可能となる。

【0036】

ここで、偏析とは、ゲート絶縁膜5とゲート電極6bとの界面に存在する導電型不純物の濃度を高めることをいう。具体的には、プラチナリッチシリサイド膜からなるゲート電極6bを形成する際、ゲート電極6bの上部から下部に向かってシリサイド反応が進むが、このシリサイド反応の進行によって、ゲート電極6bに導入された導電型不純物がゲート絶縁膜5とゲート電極6bの界面に集められて界面における不純物濃度が高まるのである。

【0037】

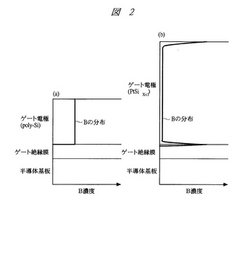

図2は、ゲート電極に導入された導電型不純物のプロファイルを示したものである。図2において、ゲート電極に導入される導電型不純物は、例えばp型不純物であるホウ素(B)である。図2(a)は、シリサイド反応をする前のゲート電極(ポリシリコン膜よりなるゲート電極)に導入されたホウ素の濃度プロファイルを示したものである。図2(a)において、縦軸は、半導体基板からの位置を示している。すなわち、半導体基板上に高誘電体膜からなるゲート絶縁膜が形成されており、このゲート絶縁膜上にポリシリコン膜よりなるゲート電極が形成されている。また、横軸は、ホウ素の濃度を示している。図2(a)に示すように、シリサイド反応をする前のゲート電極には、表面からゲート絶縁膜との界面まで一様にホウ素が導入されていることがわかる。

【0038】

一方、図2(b)は、シリサイド反応後のゲート電極(プラチナリッチシリサイド膜よりなるゲート電極)に導入されたホウ素の濃度プロファイルを示したものである。図2(b)に示すように、シリサイド反応後のゲート電極では、表面からゲート絶縁膜との界面まで、ホウ素の濃度が一様ではなく、ゲート電極とゲート絶縁膜の界面で高まっていることがわかる。言い換えれば、シリサイド反応後のゲート電極では、導電型不純物であるホウ素が、ゲート電極とゲート絶縁膜との界面に偏析していることがわかる。

【0039】

次に、図1のMISFETQpにおいて、ゲート電極6bの両側の側壁には、サイドウォール11が形成されており、このサイドウォール11下のn型ウェル4内には、低濃度p型不純物拡散領域9、10が形成されている。そして、低濃度p型不純物拡散領域9、10の外側には、高濃度p型不純物拡散領域14、15が形成されている。低濃度p型不純物拡散領域9、10および高濃度p型不純物拡散領域14、15には、ホウ素などのp型不純物(導電型不純物)が導入されており、低濃度p型不純物拡散領域9、10に比べて高濃度p型不純物拡散領域14、15の方が高濃度にp型不純物が導入されている。低濃度p型不純物拡散領域9、10と高濃度p型不純物拡散領域14、15により、MISFETQpのソース領域とドレイン領域が形成されている。ソース領域およびドレイン領域を低濃度p型不純物拡散領域9、10と高濃度p型不純物拡散領域14、15で形成しているのは、ソース領域およびドレイン領域をLDD(Lightly Doped Drain)構造とするためである。

【0040】

MISFETQnおよびMISFETQpは上記のように構成されており、このMISFETQnおよびMISFETQpを覆うように、例えば酸化シリコン膜よりなる絶縁膜16、17が形成されている。そして、絶縁膜16、17を貫通するようにコンタクトホール18が形成されている。コンタクトホール18は、高濃度n型不純物拡散領域12、13および高濃度p型不純物拡散領域14、15に達している。このコンタクトホール18内には、チタン/窒化チタン膜19aおよびタングステン膜19bが埋め込まれており、プラグ20が形成されている、そして、プラグ20に接続するように配線22が形成されている。配線22は、例えば、チタン/窒化チタン膜21a、アルミニウム膜21bおよびチタン/窒化チタン膜21cの積層膜から構成されている。

【0041】

次に、本実施の形態におけるCMISFETの製造方法について、図面を参照しながら説明する。

【0042】

まず、図3に示すように、p型の単結晶シリコンからなる半導体基板30の主面に周知のSTI(Shallow Trench Isolation)技術を用いて素子分離領域31を形成する。素子分離領域31は、溝を形成した後、この溝内に酸化シリコン膜を埋め込み、半導体基板30の表面を化学的機械的研磨法(Chemical Mechanical Polishing)を用いて研磨することにより形成することができる。

【0043】

次に、半導体基板30のnチャネル型MISFET形成領域にホウ素をイオン注入し、半導体基板30のpチャネル型MISFET形成領域にリンをイオン注入する。続いて、半導体基板30に対して熱処理を施すことにより、ホウ素およびリンを半導体基板30内に拡散させて、p型ウェル32およびn型ウェル33を形成する。

【0044】

そして、p型ウェル32とn型ウェル33のそれぞれの表面に、MISFETのしきい値電圧を調整するための不純物をイオン注入する。その後、図4に示すように、p型ウェル32とn型ウェル33のそれぞれの表面に、ハフニウムアルミネート膜からなるゲート絶縁膜34を形成する。ハフニウムアルミネート膜は、CVD(Chemical Vapor Deposition)法あるいは原子層制御成膜(ALD:Atomic Layer Deposition)を使用して形成することができる。

【0045】

次に、図5に示すように、ゲート絶縁膜34上にポリシリコン膜35を形成する。ポリシリコン膜35は、例えばCVD法を使用して形成することができ、その膜厚は、例えば50nmである。続いて、図6に示すように、半導体基板30のpチャネル型MISFET形成領域に例えばホウ素(B)などの導電型不純物をイオン注入する。このとき、導電型不純物のドーズ量は、例えば5×1014〜5×1015/cm2である。

【0046】

次に、図7に示すように、フォトリソグラフィ技術およびエッチング技術を使用して、シリコンゲート電極36a、36bを形成する。続いて、図8に示すように、p型ウェル32内にリンまたは砒素をイオン注入することにより、低濃度n型不純物拡散領域37、38を形成する。同様に、n型ウェル33内にホウ素をイオン注入することにより、低濃度p型不純物拡散領域39、40を形成する。その後、シリコンゲート電極36a、36bの側壁にサイドウォール41を形成する。サイドウォール41は、半導体基板30上に例えばCVD法を使用して酸化シリコン膜を形成し、形成した酸化シリコン膜を異方性エッチングすることにより形成する。

【0047】

続いて、図9に示すように、p型ウェル32内にリンまたは砒素をイオン注入し、n型ウェル33内にホウ素をイオン注入する。その後、半導体基板30に熱処理を施して、これらの不純物を拡散させることにより、p型ウェル32内に高濃度n型不純物拡散領域42、43を形成し、n型ウェル33内に高濃度p型不純物拡散領域44、45を形成する。

【0048】

次に、図10に示すように、半導体基板30上にCVD法を使用して酸化シリコン膜46を形成した後、化学的機械的研磨法を用いて酸化シリコン膜46の表面を研磨および平坦化することにより、シリコンゲート電極36a、36bの表面を露出する。

【0049】

そして、酸化シリコン膜46上に絶縁膜47を例えばCVD法を使用して形成した後、フォトリソグラフィ技術およびエッチング技術を使用して絶縁膜47をパターニングする。パターニングは、pチャネル型MISFET形成領域上にだけ、絶縁膜47が残るように行なわれる。続いて、図11に示すように、例えばスパッタリング法を使用して、半導体基板30上にニッケル膜48を形成する。このニッケル膜48の膜厚は、例えば35nmである。このとき、nチャネル型MISFET形成領域に形成されているシリコンゲート電極36aとニッケル膜48とは直接接触しているが、pチャネル型MISFET形成領域に形成されているシリコンゲート電極36b上には、絶縁膜47が形成されているので、シリコンゲート電極36bとニッケル膜48は直接接触していない。

【0050】

次に、半導体基板30に対して、例えば400℃程度の熱処理を施す。これにより、ニッケル膜48と直接接触しているシリコンゲート電極36aでシリサイド反応が進行し、ニッケルシリサイド膜よりなるゲート電極49が形成される。シリコンゲート電極36aに対するニッケル膜48の膜厚を約6割から7割に設定することにより、シリコンゲート電極36aとニッケル膜48との反応によって形成されたニッケルシリサイド膜は、ニッケル原子に対するシリコン原子の比がほぼ1となる(NiSix:x=1)。一方、ニッケル膜48と直接接触していないシリコンゲート電極36bでは、シリサイド反応は生じない。

【0051】

続いて、例えば、硫酸と過酸化水素との混合液を用いて、ニッケル膜48を除去した後、パターニングされている絶縁膜47をエッチングで除去する。その後、半導体基板30上に、例えばCVD法を使用して絶縁膜50を形成する。そして、フォトリソグラフィ技術およびエッチング技術を使用することにより、絶縁膜50をパターニングする。パターニングは、図12に示すように、nチャネル型MISFET形成領域にだけ、絶縁膜50が残るように行なわれる。

【0052】

次に、例えば、スパッタリング法を使用して、半導体基板30上にプラチナ膜51を形成する。このとき、pチャネル型MISFET形成領域に形成されているシリコンゲート電極36bとプラチナ膜51とは直接接触しているが、nチャネル型MISFET形成領域に形成されているゲート電極49上には、絶縁膜50が形成されているので、ゲート電極49とプラチナ膜51は直接接触していない。プラチナ膜51の膜厚は、シリコンゲート電極36bの膜厚(50nm)の2倍以上の膜厚(100nm)、望ましくは3倍以上の膜厚(150nm)を有するように形成されている。

【0053】

続いて、半導体基板30に対して、例えば400℃程度の熱処理を施す。これにより、プラチナ膜51と直接接触しているシリコンゲート電極36bでシリサイド反応が進行し、プラチナリッチシリサイド膜よりなるゲート電極52が形成される。シリコンゲート電極36bの膜厚に比べてプラチナ膜51の膜厚が十分に厚くなっているので、シリコンゲート電極36bとプラチナ膜51との反応によって形成されたプラチナシリサイド膜は、プラチナ原子に対するシリコン原子の比が1未満となる(PtSix:x<1)。したがって、シリコンゲート電極36bとプラチナ膜51との反応によって、プラチナリッチシリサイド膜よりなるゲート電極52が形成される。ここで、シリコンゲート電極36bには、導電型不純物としてホウ素が導入されている。このホウ素は、シリコンゲート電極36b中にほぼ均一に導入されている。しかし、上述したシリコンゲート電極36bとプラチナ膜51とのシリサイド反応によって、ホウ素は、ゲート絶縁膜34の界面に偏析する。すなわち、シリサイド反応は、シリコンゲート電極36bの表面からゲート絶縁膜34との界面に向かって進行する。このとき、シリコンゲート電極36bに導入されているホウ素は、シリサイド反応の進行にともない、シリコンゲート電極36bとゲート絶縁膜34との界面に集められる。このようにして、プラチナリッチシリサイド膜よりなるゲート電極52が形成されるとともに、ゲート電極52とゲート絶縁膜34の界面にホウ素を偏析させることができる。

【0054】

次に、図13に示すように、強酸(王水)を用いたウェットエッチングまたは化学的機械的研磨法を用いて未反応のプラチナ膜51を除去し、続いて、エッチングにより絶縁膜50を除去する。これにより、ニッケルシリサイド膜よりなるゲート電極49およびプラチナリッチシリサイド膜よりなるゲート電極52の表面をそれぞれ露出させる。

【0055】

次に、図14に示すように、例えばCVD法を使用して酸化シリコン膜46上に酸化シリコン膜53を形成する。そして、フォトリソグラフィ技術およびエッチング技術を使用することにより、酸化シリコン膜46および酸化シリコン膜53にコンタクトホール54を形成する。その後、コンタクトホール54の内部を含む酸化シリコン膜53上に、例えば、スパッタリング法を使用してチタン/窒化チタン膜55aを形成する。続いて、チタン/窒化チタン膜55a上に、例えばCVD法を使用してタングステン膜55bを形成する。これにより、コンタクトホール54の内部は、チタン/窒化チタン膜55aおよびタングステン膜55bによって埋め込まれる。そして、酸化シリコン膜53上に形成されたチタン/窒化チタン膜55aおよびタングステン膜55bを、化学的機械的研磨法を使用して除去することで、コンタクトホール54の内部にだけチタン/窒化チタン膜55aおよびタングステン膜55bを残し、プラグ56を形成する。

【0056】

次に、図15に示すように、酸化シリコン膜53上にチタン/窒化チタン膜57a、アルミニウム膜57bおよびチタン/窒化チタン膜57cよりなる積層膜を形成する。そして、フォトリソグラフィ技術およびエッチング技術を使用して積層膜をパターニングすることにより、配線58を形成する。このようにして、本実施の形態におけるCMISFETを形成することができる。

【0057】

次に、本実施の形態におけるpチャネル型MISFETによれば、しきい値電圧を低減できることについて説明する。

【0058】

図16は、ゲート絶縁膜としてハフニウムアルミネート膜を使用した場合におけるpチャネル型MISFETのゲート電圧(V)と容量との関係を示したグラフである。図16において、縦軸は容量を示しており、横軸はゲート電圧を示している。図16は、ゲート電極として、プラチナシリサイド膜(PtSix:x=1)、プラチナリッチシリサイド膜(PtSix:x<1)、プラチナリッチシリサイド膜にホウ素(B)を導入(ドーピング)した場合のそれぞれにおける、ゲート電圧と容量の関係を示している。図16に示すように、ゲート電極としてプラチナシリサイド膜を使用した場合の曲線に比べて、ゲート電極としてプラチナリッチシリサイド膜を使用した場合の曲線は、ゲート電圧の正方向にシフトしていることがわかる。ここで、pチャネル型MISFETのゲート電圧と容量の関係が、ゲート電圧の正方向にシフトしているほど、pチャネル型MISFETのしきい値電圧が低くなる。したがって、ゲート電極としてプラチナシリサイド膜を使用するよりもプラチナリッチシリサイド膜を使用する方が、しきい値電圧を低くすることができる。さらに、ゲート電極にプラチナリッチシリサイド膜を使用し、かつ、ホウ素を導入する場合は、ゲート電極にプラチナリッチシリサイド膜を使用し、かつ、ホウ素を導入しない場合に比べて、曲線がゲート電圧の正方向にシフトしている。このため、ホウ素を導入することにより、pチャネル型MISFETのしきい値電圧をさらに低くすることができることがわかる。

【0059】

図17は、ゲート電極として、プラチナシリサイド膜、プラチナリッチシリサイド膜、プラチナリッチシリサイド膜にホウ素(B)を導入した場合のそれぞれにおける、フラットバンド電圧(V)を示している。図17において、ゲート電極としてプラチナシリサイド膜を使用した場合のフラットバンド電圧は、約0.55V、ゲート電極としてプラチナリッチシリサイド膜を使用した場合のフラットバンド電圧は、約0.9Vとなっている。さらに、ゲート電極としてプラチナリッチシリサイド膜を使用し、かつ、ホウ素を導入した場合のフラットバンド電圧は、約1.0Vとなっている。pチャネル型MISFETの場合、フラットバンド電圧が正方向にシフトするほど、しきい値電圧は低くなる。このため、ゲート電極としてプラチナリッチシリサイド膜を使用し、かつ、ホウ素を導入することにより、しきい値電圧を最も低くすることができることがわかる。つまり、プラチナシリサイド膜からプラチナリッチシリサイド膜にすることで約0.35V、さらにプラチナリッチシリサイド膜にホウ素を導入することにより約0.1Vのシフトが認められる。このように、図16および図17に示す一例から、プラチナリッチシリサイド膜に導電型不純物を導入することにより、しきい値電圧を微調整できることがわかる。

【0060】

図18は、ゲート絶縁膜としてハフニウムオキシナイトライド膜(HfON膜)を使用した場合におけるpチャネル型MISFETのフラットバンド電圧(V)およびしきい値電圧(V)を示したグラフである。ゲート電極として、p型不純物を導入したポリシリコン膜、プラチナシリサイド膜、プラチナリッチシリサイド膜、ホウ素を導入したプラチナリッチシリサイド膜のそれぞれを用いた場合のフラットバンド電圧(V)およびしきい値電圧(V)が示されている。黒丸がフラットバンド電圧を示し、白丸がしきい値電圧を示している。

【0061】

図18に示すように、p型不純物を導入したポリシリコン膜、プラチナシリサイド膜、プラチナリッチシリサイド膜、ホウ素を導入したプラチナリッチシリサイド膜になるにつれて、フラットバンド電圧が上昇していることがわかる。しきい値電圧も同様の変化をして、ホウ素を導入したプラチナリッチシリサイド膜で、最もしきい値電圧の絶対値が低くなることがわかる。言い換えれば、ゲート絶縁膜に高誘電体膜を使用した場合、ゲート電極を構成するプラチナリッチシリサイド膜にホウ素などの導電型不純物を導入することで、しきい値電圧を微調整できることがわかる。

【0062】

本実施の形態によれば、導電型不純物を含有するプラチナリッチシリサイド膜をゲート電極として使用することにより、しきい値電圧を調整することができる。したがって、しきい値電圧を調整することにより、高いON電流を有し、かつ、しきい値電圧の低い半導体装置を製造することができる。また、種々の半導体装置に要求されるしきい値電圧を実現することができる。

【0063】

本実施の形態では、pチャネル型MISFETにおいて、プラチナリッチシリサイド膜よりなるゲート電極52に導電型不純物(例えば、ホウ素)を導入する場合について説明した。ここで、プラチナリッチシリサイド膜に代えて、ニッケルリッチシリサイド膜、ルテニウム(Ru)リッチシリサイド膜またはイリジウム(Ir)リッチシリサイド膜に導電型不純物を導入しても同様の効果が得られる。

【0064】

また、本実施の形態では、図6に示すように、pチャネル型MISFET形成領域のポリシリコン膜35にホウ素を導入する例について説明したが、これに限らず、例えば図9に示すように、n型ウェル33内に高濃度p型不純物拡散領域44、45を形成する際、

シリコンゲート電極36bにホウ素を導入してもよい。

【0065】

また、本実施の形態では、nチャネル型MISFETには、導電型不純物を導入しない例について説明したが、導電型不純物を導入してもよい。

【0066】

以上、本発明者によってなされた発明を実施の形態に基づき具体的に説明したが、本発明は前記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることはいうまでもない。

【産業上の利用可能性】

【0067】

本発明は、半導体装置を製造する製造業に幅広く利用することができる。

【図面の簡単な説明】

【0068】

【図1】本発明の実施の形態におけるCMISFETを示す断面図である。

【図2】(a)は、シリサイド反応する前のゲート電極に導入されているホウ素の濃度プロファイルを示す図であり、(b)は、シリサイド反応後のゲート電極に導入されているホウ素の濃度プロファイルを示す図である。

【図3】実施の形態におけるCMISFETの製造工程を示す断面図である。

【図4】図3に続くCMISFETの製造工程を示す断面図である。

【図5】図4に続くCMISFETの製造工程を示す断面図である。

【図6】図5に続くCMISFETの製造工程を示す断面図である。

【図7】図6に続くCMISFETの製造工程を示す断面図である。

【図8】図7に続くCMISFETの製造工程を示す断面図である。

【図9】図8に続くCMISFETの製造工程を示す断面図である。

【図10】図9に続くCMISFETの製造工程を示す断面図である。

【図11】図10に続くCMISFETの製造工程を示す断面図である。

【図12】図11に続くCMISFETの製造工程を示す断面図である。

【図13】図12に続くCMISFETの製造工程を示す断面図である。

【図14】図13に続くCMISFETの製造工程を示す断面図である。

【図15】図14に続くCMISFETの製造工程を示す断面図である。

【図16】ゲート絶縁膜としてハフニウムアルミネート膜、ゲート電極として、プラチナシリサイド膜、プラチナリッチシリサイド膜、ホウ素を導入したプラチナリッチシリサイド膜をそれぞれ使用した場合におけるゲート電圧と容量との関係を示すグラフである。

【図17】ゲート絶縁膜としてハフニウムアルミネート膜、ゲート電極として、プラチナシリサイド膜、プラチナリッチシリサイド膜、ホウ素を導入したプラチナリッチシリサイド膜をそれぞれ使用した場合におけるフラットバンド電圧を示すグラフである。

【図18】ゲート絶縁膜としてHfON膜、ゲート電極として、p型不純物を導入したポリシリコン膜、プラチナシリサイド膜、プラチナリッチシリサイド膜、ホウ素を導入したプラチナリッチシリサイド膜をそれぞれ使用した場合におけるフラットバンド電圧およびしきい値電圧を示すグラフである。

【符号の説明】

【0069】

1 半導体基板

2 素子分離領域

3 p型ウェル

4 n型ウェル

5 ゲート絶縁膜

6a ゲート電極

6b ゲート電極

7 低濃度n型不純物拡散領域

8 低濃度n型不純物拡散領域

9 低濃度p型不純物拡散領域

10 低濃度p型不純物拡散領域

11 サイドウォール

12 高濃度n型不純物拡散領域

13 高濃度n型不純物拡散領域

14 高濃度p型不純物拡散領域

15 高濃度p型不純物拡散領域

16 絶縁膜

17 絶縁膜

18 コンタクトホール

19a チタン/窒化チタン膜

19b タングステン膜

20 プラグ

21a チタン/窒化チタン膜

21b アルミニウム膜

21c チタン/窒化チタン膜

22 配線

30 半導体基板

31 素子分離領域

32 p型ウェル

33 n型ウェル

34 ゲート絶縁膜

35 ポリシリコン膜

36a シリコンゲート電極

36b シリコンゲート電極

37 低濃度n型不純物拡散領域

38 低濃度n型不純物拡散領域

39 低濃度p型不純物拡散領域

40 低濃度p型不純物拡散領域

41 サイドウォール

42 高濃度n型不純物拡散領域

43 高濃度n型不純物拡散領域

44 高濃度p型不純物拡散領域

45 高濃度p型不純物拡散領域

46 酸化シリコン膜

47 絶縁膜

48 ニッケル膜

49 ゲート電極

50 絶縁膜

51 プラチナ膜

52 ゲート電極

53 酸化シリコン膜

54 コンタクトホール

55a チタン/窒化チタン膜

55b タングステン膜

56 プラグ

57a チタン/窒化チタン膜

57b アルミニウム膜

57c チタン/窒化チタン膜

58 配線

【技術分野】

【0001】

本発明は、半導体装置およびその製造技術に関し、特に、ハフニウム(Hf)系ゲート絶縁膜上にゲート電極を形成したMISFET(Metal Insulator Semiconductor Field Effect Transistor)を含む半導体装置に適用して有効な技術に関するものである。

【背景技術】

【0002】

米国特許第6,599,831 B1号公報(特許文献1)には、酸化シリコン膜よりなるゲート絶縁膜上にゲート電極を形成したMISFETについて記載されている。具体的には、ゲート電極としてフルシリサイド電極を用い、ドーパントによってMISFETのしきい値電圧を制御する技術が開示されている。

【0003】

近年、ゲート絶縁膜として酸化シリコン膜ではなく、酸化シリコン膜より誘電率の高い高誘電体膜を用いることが検討されている。この場合、ポリシリコン膜よりなるゲート電極のフェルミレベル(仕事関数)が酸化シリコン膜上でとりうるフェルミレベルからMISFETのしきい値が上昇する方向にシフトする現象が報告されている。この現象は、フェルミレベルピニングとして解釈されている(非特許文献1)。

【特許文献1】米国特許第6,599,831 B1号公報

【非特許文献1】IEEE TRANSACTIONS ON ELECTORON DEVICES、VOL.51、No6、JUNE 2004、pp.971-984

【発明の開示】

【発明が解決しようとする課題】

【0004】

従来、CMIS(Complementary Metal Insulator Semiconductor)回路を構成するnチャネル型MISFETおよびpチャネル型MISFETにおいて、ゲート絶縁膜は、酸化シリコン膜が使用されている。

【0005】

ところが、近年、半導体装置を構成するMISFETの微細化に伴って、ゲート絶縁膜の薄膜化が急速に進んでいる。ゲート絶縁膜の膜厚が薄くなると、トンネル効果により、電子がゲート絶縁膜中を通り抜ける現象が生じる。この現象によってゲート絶縁膜中にトンネル電流が流れる。このため、MISFETのリーク電流が増大することになる。

【0006】

そこで、ゲート絶縁膜として、酸化シリコン膜に代えて、酸化シリコン膜よりも誘電率の高い高誘電体膜に置き換える検討が進められている。これは、ゲート絶縁膜を高誘電体膜で構成した場合、酸化シリコン膜で構成した場合と同じ容量であっても、実際の物理膜厚を(高誘電体膜の誘電率/酸化シリコン膜の誘電率)倍だけ厚くできるので、結果としてリーク電流を低減することができるからである。高誘電体膜の材料としては、ハフニウム(Hf)酸化物やジルコニウム(Zr)酸化物といった金属酸化物が検討されている。

【0007】

このように、MISFETのゲート絶縁膜として高誘電体膜を使用することにより、ゲート絶縁膜を通過するリーク電流を低減することができるが、新たな問題が発生する。

【0008】

従来、nチャネル型MISFETおよびpチャネル型MISFETでは、ゲート電極としてポリシリコン膜が使用されている。そして、nチャネル型MISFETでは、ゲート電極を構成するポリシリコン膜にn型不純物(リンや砒素など)を導入している。これにより、ゲート電極の仕事関数(フェルミレベル)をシリコンの伝導帯近傍(4.05eV近傍)に設定することで、nチャネル型MISFETのしきい値電圧の低下を図っている。一方、pチャネル型MISFETでは、ゲート電極を構成するポリシリコン膜にp型不純物(ホウ素など)を導入している。これにより、ゲート電極の仕事関数をシリコンの価電子帯近傍(5.17eV近傍)に設定することで、pチャネル型MISFETのしきい値電圧の低下を図っている。これは、ゲート絶縁膜として酸化シリコン膜を使用した場合の例である。すなわち、ゲート絶縁膜として酸化シリコン膜を使用している場合では、ゲート電極にn型不純物あるいはp型不純物を導入することにより、ゲート電極の仕事関数を伝導帯近傍あるいは価電子帯近傍にすることができる。

【0009】

ところが、ゲート絶縁膜として、高誘電体膜を使用すると、ポリシリコン膜よりなるゲート電極にn型不純物あるいはp型不純物を導入しても、ゲート電極の仕事関数が、伝導帯近傍あるいは価電子帯近傍にならない現象が生じる。すなわち、ゲート絶縁膜として高誘電体膜を使用した場合、nチャネル型MISFETでは、ゲート電極の仕事関数が大きくなって伝導帯近傍から離れる。このため、nチャネル型MISFETのしきい値電圧が上昇する。一方、pチャネル型MISFETでは、ゲート電極の仕事関数が小さくなって価電子帯から離れるので、nチャネル型MISFETと同様にしきい値電圧が上昇する。このように、ゲート電極の仕事関数がしきい値電圧の上昇する方向にシフトする現象はフェルミレベルピニングとして解釈されている。このフェルミレベルピニングは、pチャネル型MISFETで顕著に現われる。すなわち、ゲート絶縁膜に高誘電体膜を使用した場合のしきい値電圧の上昇は、pチャネル型MISFETで顕著に現われる。また、ゲート絶縁膜として酸化シリコン膜を用いた場合は、ゲート電極(ポリシリコン膜)とゲート絶縁膜の界面に導電型不純物を偏析させることにより、MISFETのしきい値電圧の調整をすることが可能であった。これに対し、ゲート絶縁膜に高誘電体膜を用いた場合は、フェルミレベルピニングにより、導電型不純物をゲート電極(ポリシリコン膜)とゲート絶縁膜の界面に偏析させることによるしきい値電圧の制御効果は、ほとんど消失する。

【0010】

このことから、MISFETでしきい値電圧の上昇が生じ、MISFETの低消費電力設計が困難になる。特に、nチャネル型MISFETとpチャネル型MISFETを形成するCMIS回路では、低消費電力設計が困難となる。

【0011】

フェルミレベルピニングは、高誘電体膜よりなるゲート絶縁膜上に形成されたゲート電極に含まれるシリコンの量に左右されると考えられている。そこで、pチャネル型MISFETでは、ゲート電極に含まれるシリコンの量を低減することにより、フェルミレベルピニングを緩和することが検討されている。例えば、特願2004−292420号には、ゲート電極をプラチナリッチシリサイド膜で形成することにより、フェルミレベルピニングを緩和する技術が記載されている。すなわち、シリコン原子に対するプラチナ原子の比を大きくしたプラチナリッチシリサイド膜をゲート電極として用いることにより、しきい値電圧を低下させている。

【0012】

ここで、種々の半導体装置に使用されるMISFETは、それぞれの用途によって要求されるしきい値電圧が異なる。このため、ゲート電極をメタルリッチシリサイド膜で形成することだけでは、それぞれの用途に使用されるMISFETのしきい値電圧を調整するには不充分であるという問題点がある。

【0013】

本発明の目的は、ゲート絶縁膜として酸化シリコン膜より誘電率の高い高誘電体膜を使用する場合にMISFETのしきい値電圧を低下するとともにしきい値電圧の微調整を可能にする技術を提供することにある。

【0014】

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

【課題を解決するための手段】

【0015】

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、次のとおりである。

【0016】

本発明による半導体装置は、(a)半導体基板と、(b)前記半導体基板上に形成され、ハフニウム酸化物を主体として含むゲート絶縁膜と、(c)前記ゲート絶縁膜上に形成され、シリコン膜とメタル膜を反応させて形成したメタルシリサイド膜よりなるゲート電極とを有するMISFETを含む半導体装置に関するものである。そして、前記メタルシリサイド膜のメタル原子に対するシリコン原子の比が1未満であり、かつ、前記メタルシリサイド膜中に導電型不純物が導入されていることを特徴とするものである。

【0017】

本発明による半導体装置の製造方法は、(a)半導体基板上に、ハフニウム酸化物を主体として含むゲート絶縁膜を形成する工程と、(b)前記ゲート絶縁膜上にMISFETのシリコンゲート電極を形成する工程と、(c)前記シリコンゲート電極内に導電型不純物を導入する工程とを備える。さらに、(d)前記半導体基板上に、前記シリコンゲート電極よりも厚い膜厚の絶縁膜を形成した後、前記絶縁膜の表面を平坦化することにより、前記シリコンゲート電極の表面を露出する工程と、(e)前記シリコンゲート電極の上部にメタル膜を形成する工程とを備える。そして、(f)前記半導体基板を加熱し、前記シリコンゲート電極と前記メタル膜を反応させることにより、メタル原子に対するシリコン原子の比が1未満のメタルシリサイド膜からなるゲート電極を形成し、前記ゲート絶縁膜と前記ゲート電極の界面近傍に前記導電型不純物を偏析させる工程とを備えることを特徴とするものである。

【発明の効果】

【0018】

本願において開示される発明のうち、代表的なものによって得られる効果を簡単に説明すれば以下のとおりである。

【0019】

ゲート電極をメタルリッチシリサイド膜で形成するとともに導電型不純物を導入したので、ゲート絶縁膜として酸化シリコン膜より誘電率の高い高誘電体膜を使用する場合に、MISFETのしきい値電圧を低下することができるとともにしきい値電圧の微調整をすることができる。

【発明を実施するための最良の形態】

【0020】

以下、本発明の実施の形態を図面に基づいて詳細に説明する。なお、実施の形態を説明するための全図において、同一の部材には原則として同一の符号を付し、その繰り返しの説明は省略する。

【0021】

図1は、本実施の形態1におけるCMISFETの構成を示した断面図である。左側に形成されているMISFETQnがnチャネル型MISFETであり、右側に形成されているMISFETQpがpチャネル型MISFETである。

【0022】

図1において、半導体基板1には、素子分離領域2が形成されており、素子分離領域2で分離された活性領域には、p型ウェル3あるいはn型ウェル4が形成されている。p型ウェル3上には、MISFETQnが形成されており、n型ウェル4上には、MISFETQpが形成されている。

【0023】

MISFETQnは、p型ウェル3上にゲート絶縁膜5を有しており、このゲート絶縁膜5上にゲート電極6aが形成されている。ゲート絶縁膜5は、酸化シリコン膜より誘電率の高い高誘電体膜から構成される。

【0024】

従来、絶縁耐性が高い、シリコン−酸化シリコン界面の電気的・物性的安定性などが優れているとの観点から、ゲート絶縁膜として酸化シリコン膜が使用されている。

【0025】

しかし、素子の微細化に伴い、ゲート絶縁膜の膜厚について、極薄化が要求されるようになってきている。このように薄い酸化シリコン膜をゲート絶縁膜として使用すると、MISFETのチャネルを流れる電子が酸化シリコン膜によって形成される障壁をトンネルしてゲート電極に流れる、いわゆるトンネル電流が発生してしまう。

【0026】

そこで、酸化シリコン膜より誘電率の高い材料を使用することにより、容量が同じでも物理的膜厚を増加させることができる高誘電体膜が使用されるようになってきている。高誘電体膜によれば、容量を同じにしても物理的膜厚を増加させることができるので、リーク電流を低減することができる。

【0027】

例えば、高誘電体膜として、ハフニウム酸化物の一つであるハフニウムアルミネート膜(HfAlON膜)が使用されるが、ハフニウムアルミネート膜に代えて、酸化ハフニウム膜、HfON膜、HfSiO膜、HfSiON膜、HfAlO膜のような他のハフニウム系絶縁膜を使用することもできる。さらに、これらのハフニウム系絶縁膜に酸化タンタル、酸化ニオブ、酸化チタン、酸化ジルコニウム、酸化ランタン、酸化イットリウムなどの酸化物を導入したハフニウム系絶縁膜を使用することもできる。ハフニウム系絶縁膜は、ハフニウムアルミネート膜と同様、酸化シリコン膜や酸窒化シリコン膜より誘電率が高いので、ハフニウムアルミネート膜を用いた場合と同様の効果が得られる。

【0028】

ゲート絶縁膜5上に形成されるゲート電極6aは、ニッケルシリサイド膜から形成されている。ゲート電極の材料として、一般にポリシリコン膜が使用されているが、本実施の形態では、メタルシリサイド膜の一種であるニッケルシリサイド膜を使用している。MISFETQnのゲート電極として、一般的なポリシリコン膜を用いても良い。ゲート電極内のキャリアの空乏化によるMISFETQnの駆動電流の飽和を改善するには、キャリアの空乏化の影響がないメタルシリサイド膜を使用するのが好ましく、たとえばニッケルシリサイド膜がふさわしい。ニッケルシリサイド膜のみでなく、プラチナシリサイド膜、イリジウムシリサイド膜及びルテニウムシリサイド膜のようなシリサイド膜にしても良い。高誘電体膜をゲート絶縁膜5として使用しているMISFETQnにおいて、ゲート電極6aにポリシリコン膜あるいはニッケルシリサイド膜を使用すると、フェルミレベルピニングによるしきい値の上昇が生じるが、後述するMISFETQpのしきい値上昇と比較して、顕著ではない。

【0029】

ここで、このニッケルシリサイド膜において、ニッケル原子に対するシリコン原子の比はほぼ1とするのが良い。シリコン原子の比を1未満にしても良いが、nチャネル型MISFETであるMISFETQnでは、相対的なNi原子比の増加に伴ってゲート電極6aの仕事関数は増加する方向に変化する。このため、MISFETQnのしきい値電圧は上昇する。しきい値の増加を抑制するには、ニッケル原子に対するシリコン原子の比をほぼ1にするのが好ましい。この金属原子に対するシリコン原子の比は、他のメタルシリサイド膜を用いる場合も同様である。

【0030】

次に、ゲート電極6aの両側の側壁には、サイドウォール11が形成されており、サイドウォール11下のp型ウェル3内には、低濃度n型不純物拡散領域7、8が形成されている。低濃度n型不純物拡散領域7、8の外側には、高濃度n型不純物拡散領域12、13が形成されている。低濃度n型不純物拡散領域7、8および高濃度n型不純物拡散領域12、13には、リンや砒素などのn型不純物(導電型不純物)が導入されているが、低濃度n型不純物拡散領域7、8に比べて高濃度n型不純物拡散領域12、13の方が高濃度にn型不純物が導入されている。低濃度n型不純物拡散領域7、8と高濃度n型不純物拡散領域12、13により、MISFETQnのソース領域とドレイン領域が形成されている。ソース領域およびドレイン領域を低濃度n型不純物拡散領域7、8と高濃度n型不純物拡散領域12、13で形成しているのは、ソース領域およびドレイン領域をLDD(Lightly Doped Drain)構造とするためである。

【0031】

次に、pチャネル型MISFETであるMISFETQpの構成について説明する。MISFETQpは、n型ウェル4上にゲート絶縁膜5が形成されている。このゲート絶縁膜5は、上述したMISFETQnのゲート絶縁膜5と同様に、酸化シリコン膜より誘電率の高い高誘電体膜から形成されている。

【0032】

ゲート絶縁膜5上にはゲート電極6bが形成されており、このゲート電極6bは、プラチナリッチシリサイド膜から形成されている。上述したように、ゲート絶縁膜5として、高誘電体膜を使用し、ゲート電極6bとしてポリシリコン膜を使用すると、フェルミレベルピニングにより、しきい値電圧の上昇が生じる。このしきい値電圧の上昇は、nチャネル型MISFETであるMISFETQnよりも、pチャネル型MISFETであるMISFETQpのほうが顕著に現われる。すなわち、MISFETQnとMISFETQpとも、フェルミレベルピニングによりゲート電極の仕事関数(フェルミレベル)が概ねS

iの禁制帯の中央より伝導帯側によった位置に固定される。MISFETQnでは、伝導帯近傍にゲート電極の仕事関数がある場合、しきい値電圧を低くすることができるが、フェルミレベルピニングにより、伝導帯近傍から上述した位置にゲート電極の仕事関数が移動したとしてもそれほど移動量は大きくないので、しきい値電圧の上昇はあるにしてもそれほど問題は生じない。これに対し、MISFETQpでは、価電子帯近傍にゲート電極の仕事関数がある場合に、しきい値電圧を低くできる。ところが、フェルミレベルピニングにより、仕事関数が価電子帯近傍から上述した位置に移動すると、その移動量は、MISFETQnに比べて大きくなる。したがって、MISFETQpでは、しきい値電圧の上昇も大きくなり問題となる。

【0033】

そこで、pチャネル型MISFETであるMISFETQpでは、フェルミレベルピニングが、ゲート電極6bに含まれるシリコンの量を低減することにより緩和できる観点から、本実施の形態では、MISFETQpのゲート電極6bとしてプラチナリッチシリサイド膜を使用している。つまり、プラチナリッチシリサイド膜の仕事関数は、MISFETQpのしきい値電圧を低減するのに適している値を有しているので、MISFETQpのゲート電極6bに使用される。そして、さらに、ゲート電極6bのシリコン含有率を下げることで、フェルミレベルピニングが緩和されるので、プラチナリッチシリサイド膜を使用している。ここで、プラチナリッチシリサイド膜とは、プラチナ原子に対するシリコン原子の比が1未満である組成を有する膜である。化学式で表せば、PtSix(x<1)となる。具体的に、プラチナリッチシリサイド膜の組成は、Pt3Si、Pt12Si5、Pt2Siなどが考えられるが、これらの中では、シリコンの含有率を下げてフェルミレベルピニングを緩和する観点から、Pt3Siの組成をもつプラチナリッチシリサイド膜をゲート電極6bに使用することが望ましい。このように、ゲート電極6bの材料としてポリシリコン膜に代えて、プラチナリッチシリサイド膜を使用することにより、フェルミレベルピニングを緩和することができ、しきい値電圧を低下させることができる。しかし、ゲート電極6bをプラチナリッチシリサイド膜にしただけでは、種々の半導体装置を構成するMISFETで所望のしきい値を得るようにしきい値電圧の微調整を行なうことが困難である。

【0034】

ゲート絶縁膜として酸化シリコン膜を用い、ゲート電極としてポリシリコン膜を用いた場合、ゲート絶縁膜とゲート電極との界面に導電型不純物を偏析させることにより、しきい値電圧を調整することは行なわれていた。ところが、ゲート絶縁膜として高誘電体膜を用い、ゲート電極としてポリシリコン膜を用いた場合、フェルミレベルピニングが生じるため、ゲート絶縁膜とゲート電極との界面に導電型不純物を偏析させることによるしきい値電圧の調整効果は消失してしまっていた。すなわち、導電型不純物を偏析させることによるしきい値電圧の調整は効果が得られなかった。しかし、ゲート絶縁膜に高誘電体膜を用い、ゲート電極にメタルリッチシリサイド膜を用いた場合、ゲート絶縁膜とゲート電極との界面に導電型不純物を偏析させることにより、しきい値電圧を調整できることを、本発明者らは見出した。つまり、ゲート絶縁膜として高誘電体膜を使用している場合には、フェルミレベルピニングが生じるため、導電型不純物の偏析による効果が得られないと考えられていたが、ゲート電極にメタルリッチシリサイド膜を用いた場合は、導電型不純物の偏析による効果が得られることが判明した。

【0035】

そこで、本実施の形態では、プラチナリッチシリサイド膜からなるゲート電極6bに、導電型不純物を導入している。具体的には、ゲート電極6bとゲート絶縁膜5の界面近傍にホウ素(B)やアルミニウム(Al)などのp型不純物を偏析させている。これにより、MISFETQpのしきい値電圧がp型不純物を導入させない場合に比べて、さらに低下させることができる。そして、ゲート電極6bとゲート絶縁膜5の界面に偏析させるp型不純物の濃度を変えることにより、しきい値電圧の低下量を変えることができるので、MISFETQpのしきい値電圧の微調整を行なうことができる。このように、本実施の形態における特徴の一つは、プラチナリッチシリサイド膜からなるゲート電極6bに導電型不純物を導入する点にある。本実施の形態では、ゲート電極6bにp型不純物を導入しているが、しきい値電圧を上昇する方向に微調整したい場合には、p型不純物ではなく、リン(P)や砒素(As)、アンチモン(Sb)などのn型不純物を導入すればよい。そして、導入するn型不純物の濃度を変えることにより、しきい値電圧の微調整が可能となる。

【0036】

ここで、偏析とは、ゲート絶縁膜5とゲート電極6bとの界面に存在する導電型不純物の濃度を高めることをいう。具体的には、プラチナリッチシリサイド膜からなるゲート電極6bを形成する際、ゲート電極6bの上部から下部に向かってシリサイド反応が進むが、このシリサイド反応の進行によって、ゲート電極6bに導入された導電型不純物がゲート絶縁膜5とゲート電極6bの界面に集められて界面における不純物濃度が高まるのである。

【0037】

図2は、ゲート電極に導入された導電型不純物のプロファイルを示したものである。図2において、ゲート電極に導入される導電型不純物は、例えばp型不純物であるホウ素(B)である。図2(a)は、シリサイド反応をする前のゲート電極(ポリシリコン膜よりなるゲート電極)に導入されたホウ素の濃度プロファイルを示したものである。図2(a)において、縦軸は、半導体基板からの位置を示している。すなわち、半導体基板上に高誘電体膜からなるゲート絶縁膜が形成されており、このゲート絶縁膜上にポリシリコン膜よりなるゲート電極が形成されている。また、横軸は、ホウ素の濃度を示している。図2(a)に示すように、シリサイド反応をする前のゲート電極には、表面からゲート絶縁膜との界面まで一様にホウ素が導入されていることがわかる。

【0038】

一方、図2(b)は、シリサイド反応後のゲート電極(プラチナリッチシリサイド膜よりなるゲート電極)に導入されたホウ素の濃度プロファイルを示したものである。図2(b)に示すように、シリサイド反応後のゲート電極では、表面からゲート絶縁膜との界面まで、ホウ素の濃度が一様ではなく、ゲート電極とゲート絶縁膜の界面で高まっていることがわかる。言い換えれば、シリサイド反応後のゲート電極では、導電型不純物であるホウ素が、ゲート電極とゲート絶縁膜との界面に偏析していることがわかる。

【0039】

次に、図1のMISFETQpにおいて、ゲート電極6bの両側の側壁には、サイドウォール11が形成されており、このサイドウォール11下のn型ウェル4内には、低濃度p型不純物拡散領域9、10が形成されている。そして、低濃度p型不純物拡散領域9、10の外側には、高濃度p型不純物拡散領域14、15が形成されている。低濃度p型不純物拡散領域9、10および高濃度p型不純物拡散領域14、15には、ホウ素などのp型不純物(導電型不純物)が導入されており、低濃度p型不純物拡散領域9、10に比べて高濃度p型不純物拡散領域14、15の方が高濃度にp型不純物が導入されている。低濃度p型不純物拡散領域9、10と高濃度p型不純物拡散領域14、15により、MISFETQpのソース領域とドレイン領域が形成されている。ソース領域およびドレイン領域を低濃度p型不純物拡散領域9、10と高濃度p型不純物拡散領域14、15で形成しているのは、ソース領域およびドレイン領域をLDD(Lightly Doped Drain)構造とするためである。

【0040】

MISFETQnおよびMISFETQpは上記のように構成されており、このMISFETQnおよびMISFETQpを覆うように、例えば酸化シリコン膜よりなる絶縁膜16、17が形成されている。そして、絶縁膜16、17を貫通するようにコンタクトホール18が形成されている。コンタクトホール18は、高濃度n型不純物拡散領域12、13および高濃度p型不純物拡散領域14、15に達している。このコンタクトホール18内には、チタン/窒化チタン膜19aおよびタングステン膜19bが埋め込まれており、プラグ20が形成されている、そして、プラグ20に接続するように配線22が形成されている。配線22は、例えば、チタン/窒化チタン膜21a、アルミニウム膜21bおよびチタン/窒化チタン膜21cの積層膜から構成されている。

【0041】

次に、本実施の形態におけるCMISFETの製造方法について、図面を参照しながら説明する。

【0042】

まず、図3に示すように、p型の単結晶シリコンからなる半導体基板30の主面に周知のSTI(Shallow Trench Isolation)技術を用いて素子分離領域31を形成する。素子分離領域31は、溝を形成した後、この溝内に酸化シリコン膜を埋め込み、半導体基板30の表面を化学的機械的研磨法(Chemical Mechanical Polishing)を用いて研磨することにより形成することができる。

【0043】

次に、半導体基板30のnチャネル型MISFET形成領域にホウ素をイオン注入し、半導体基板30のpチャネル型MISFET形成領域にリンをイオン注入する。続いて、半導体基板30に対して熱処理を施すことにより、ホウ素およびリンを半導体基板30内に拡散させて、p型ウェル32およびn型ウェル33を形成する。

【0044】

そして、p型ウェル32とn型ウェル33のそれぞれの表面に、MISFETのしきい値電圧を調整するための不純物をイオン注入する。その後、図4に示すように、p型ウェル32とn型ウェル33のそれぞれの表面に、ハフニウムアルミネート膜からなるゲート絶縁膜34を形成する。ハフニウムアルミネート膜は、CVD(Chemical Vapor Deposition)法あるいは原子層制御成膜(ALD:Atomic Layer Deposition)を使用して形成することができる。

【0045】

次に、図5に示すように、ゲート絶縁膜34上にポリシリコン膜35を形成する。ポリシリコン膜35は、例えばCVD法を使用して形成することができ、その膜厚は、例えば50nmである。続いて、図6に示すように、半導体基板30のpチャネル型MISFET形成領域に例えばホウ素(B)などの導電型不純物をイオン注入する。このとき、導電型不純物のドーズ量は、例えば5×1014〜5×1015/cm2である。

【0046】

次に、図7に示すように、フォトリソグラフィ技術およびエッチング技術を使用して、シリコンゲート電極36a、36bを形成する。続いて、図8に示すように、p型ウェル32内にリンまたは砒素をイオン注入することにより、低濃度n型不純物拡散領域37、38を形成する。同様に、n型ウェル33内にホウ素をイオン注入することにより、低濃度p型不純物拡散領域39、40を形成する。その後、シリコンゲート電極36a、36bの側壁にサイドウォール41を形成する。サイドウォール41は、半導体基板30上に例えばCVD法を使用して酸化シリコン膜を形成し、形成した酸化シリコン膜を異方性エッチングすることにより形成する。

【0047】

続いて、図9に示すように、p型ウェル32内にリンまたは砒素をイオン注入し、n型ウェル33内にホウ素をイオン注入する。その後、半導体基板30に熱処理を施して、これらの不純物を拡散させることにより、p型ウェル32内に高濃度n型不純物拡散領域42、43を形成し、n型ウェル33内に高濃度p型不純物拡散領域44、45を形成する。

【0048】

次に、図10に示すように、半導体基板30上にCVD法を使用して酸化シリコン膜46を形成した後、化学的機械的研磨法を用いて酸化シリコン膜46の表面を研磨および平坦化することにより、シリコンゲート電極36a、36bの表面を露出する。

【0049】

そして、酸化シリコン膜46上に絶縁膜47を例えばCVD法を使用して形成した後、フォトリソグラフィ技術およびエッチング技術を使用して絶縁膜47をパターニングする。パターニングは、pチャネル型MISFET形成領域上にだけ、絶縁膜47が残るように行なわれる。続いて、図11に示すように、例えばスパッタリング法を使用して、半導体基板30上にニッケル膜48を形成する。このニッケル膜48の膜厚は、例えば35nmである。このとき、nチャネル型MISFET形成領域に形成されているシリコンゲート電極36aとニッケル膜48とは直接接触しているが、pチャネル型MISFET形成領域に形成されているシリコンゲート電極36b上には、絶縁膜47が形成されているので、シリコンゲート電極36bとニッケル膜48は直接接触していない。

【0050】

次に、半導体基板30に対して、例えば400℃程度の熱処理を施す。これにより、ニッケル膜48と直接接触しているシリコンゲート電極36aでシリサイド反応が進行し、ニッケルシリサイド膜よりなるゲート電極49が形成される。シリコンゲート電極36aに対するニッケル膜48の膜厚を約6割から7割に設定することにより、シリコンゲート電極36aとニッケル膜48との反応によって形成されたニッケルシリサイド膜は、ニッケル原子に対するシリコン原子の比がほぼ1となる(NiSix:x=1)。一方、ニッケル膜48と直接接触していないシリコンゲート電極36bでは、シリサイド反応は生じない。

【0051】

続いて、例えば、硫酸と過酸化水素との混合液を用いて、ニッケル膜48を除去した後、パターニングされている絶縁膜47をエッチングで除去する。その後、半導体基板30上に、例えばCVD法を使用して絶縁膜50を形成する。そして、フォトリソグラフィ技術およびエッチング技術を使用することにより、絶縁膜50をパターニングする。パターニングは、図12に示すように、nチャネル型MISFET形成領域にだけ、絶縁膜50が残るように行なわれる。

【0052】

次に、例えば、スパッタリング法を使用して、半導体基板30上にプラチナ膜51を形成する。このとき、pチャネル型MISFET形成領域に形成されているシリコンゲート電極36bとプラチナ膜51とは直接接触しているが、nチャネル型MISFET形成領域に形成されているゲート電極49上には、絶縁膜50が形成されているので、ゲート電極49とプラチナ膜51は直接接触していない。プラチナ膜51の膜厚は、シリコンゲート電極36bの膜厚(50nm)の2倍以上の膜厚(100nm)、望ましくは3倍以上の膜厚(150nm)を有するように形成されている。

【0053】

続いて、半導体基板30に対して、例えば400℃程度の熱処理を施す。これにより、プラチナ膜51と直接接触しているシリコンゲート電極36bでシリサイド反応が進行し、プラチナリッチシリサイド膜よりなるゲート電極52が形成される。シリコンゲート電極36bの膜厚に比べてプラチナ膜51の膜厚が十分に厚くなっているので、シリコンゲート電極36bとプラチナ膜51との反応によって形成されたプラチナシリサイド膜は、プラチナ原子に対するシリコン原子の比が1未満となる(PtSix:x<1)。したがって、シリコンゲート電極36bとプラチナ膜51との反応によって、プラチナリッチシリサイド膜よりなるゲート電極52が形成される。ここで、シリコンゲート電極36bには、導電型不純物としてホウ素が導入されている。このホウ素は、シリコンゲート電極36b中にほぼ均一に導入されている。しかし、上述したシリコンゲート電極36bとプラチナ膜51とのシリサイド反応によって、ホウ素は、ゲート絶縁膜34の界面に偏析する。すなわち、シリサイド反応は、シリコンゲート電極36bの表面からゲート絶縁膜34との界面に向かって進行する。このとき、シリコンゲート電極36bに導入されているホウ素は、シリサイド反応の進行にともない、シリコンゲート電極36bとゲート絶縁膜34との界面に集められる。このようにして、プラチナリッチシリサイド膜よりなるゲート電極52が形成されるとともに、ゲート電極52とゲート絶縁膜34の界面にホウ素を偏析させることができる。

【0054】

次に、図13に示すように、強酸(王水)を用いたウェットエッチングまたは化学的機械的研磨法を用いて未反応のプラチナ膜51を除去し、続いて、エッチングにより絶縁膜50を除去する。これにより、ニッケルシリサイド膜よりなるゲート電極49およびプラチナリッチシリサイド膜よりなるゲート電極52の表面をそれぞれ露出させる。

【0055】

次に、図14に示すように、例えばCVD法を使用して酸化シリコン膜46上に酸化シリコン膜53を形成する。そして、フォトリソグラフィ技術およびエッチング技術を使用することにより、酸化シリコン膜46および酸化シリコン膜53にコンタクトホール54を形成する。その後、コンタクトホール54の内部を含む酸化シリコン膜53上に、例えば、スパッタリング法を使用してチタン/窒化チタン膜55aを形成する。続いて、チタン/窒化チタン膜55a上に、例えばCVD法を使用してタングステン膜55bを形成する。これにより、コンタクトホール54の内部は、チタン/窒化チタン膜55aおよびタングステン膜55bによって埋め込まれる。そして、酸化シリコン膜53上に形成されたチタン/窒化チタン膜55aおよびタングステン膜55bを、化学的機械的研磨法を使用して除去することで、コンタクトホール54の内部にだけチタン/窒化チタン膜55aおよびタングステン膜55bを残し、プラグ56を形成する。

【0056】

次に、図15に示すように、酸化シリコン膜53上にチタン/窒化チタン膜57a、アルミニウム膜57bおよびチタン/窒化チタン膜57cよりなる積層膜を形成する。そして、フォトリソグラフィ技術およびエッチング技術を使用して積層膜をパターニングすることにより、配線58を形成する。このようにして、本実施の形態におけるCMISFETを形成することができる。

【0057】

次に、本実施の形態におけるpチャネル型MISFETによれば、しきい値電圧を低減できることについて説明する。

【0058】

図16は、ゲート絶縁膜としてハフニウムアルミネート膜を使用した場合におけるpチャネル型MISFETのゲート電圧(V)と容量との関係を示したグラフである。図16において、縦軸は容量を示しており、横軸はゲート電圧を示している。図16は、ゲート電極として、プラチナシリサイド膜(PtSix:x=1)、プラチナリッチシリサイド膜(PtSix:x<1)、プラチナリッチシリサイド膜にホウ素(B)を導入(ドーピング)した場合のそれぞれにおける、ゲート電圧と容量の関係を示している。図16に示すように、ゲート電極としてプラチナシリサイド膜を使用した場合の曲線に比べて、ゲート電極としてプラチナリッチシリサイド膜を使用した場合の曲線は、ゲート電圧の正方向にシフトしていることがわかる。ここで、pチャネル型MISFETのゲート電圧と容量の関係が、ゲート電圧の正方向にシフトしているほど、pチャネル型MISFETのしきい値電圧が低くなる。したがって、ゲート電極としてプラチナシリサイド膜を使用するよりもプラチナリッチシリサイド膜を使用する方が、しきい値電圧を低くすることができる。さらに、ゲート電極にプラチナリッチシリサイド膜を使用し、かつ、ホウ素を導入する場合は、ゲート電極にプラチナリッチシリサイド膜を使用し、かつ、ホウ素を導入しない場合に比べて、曲線がゲート電圧の正方向にシフトしている。このため、ホウ素を導入することにより、pチャネル型MISFETのしきい値電圧をさらに低くすることができることがわかる。

【0059】

図17は、ゲート電極として、プラチナシリサイド膜、プラチナリッチシリサイド膜、プラチナリッチシリサイド膜にホウ素(B)を導入した場合のそれぞれにおける、フラットバンド電圧(V)を示している。図17において、ゲート電極としてプラチナシリサイド膜を使用した場合のフラットバンド電圧は、約0.55V、ゲート電極としてプラチナリッチシリサイド膜を使用した場合のフラットバンド電圧は、約0.9Vとなっている。さらに、ゲート電極としてプラチナリッチシリサイド膜を使用し、かつ、ホウ素を導入した場合のフラットバンド電圧は、約1.0Vとなっている。pチャネル型MISFETの場合、フラットバンド電圧が正方向にシフトするほど、しきい値電圧は低くなる。このため、ゲート電極としてプラチナリッチシリサイド膜を使用し、かつ、ホウ素を導入することにより、しきい値電圧を最も低くすることができることがわかる。つまり、プラチナシリサイド膜からプラチナリッチシリサイド膜にすることで約0.35V、さらにプラチナリッチシリサイド膜にホウ素を導入することにより約0.1Vのシフトが認められる。このように、図16および図17に示す一例から、プラチナリッチシリサイド膜に導電型不純物を導入することにより、しきい値電圧を微調整できることがわかる。

【0060】

図18は、ゲート絶縁膜としてハフニウムオキシナイトライド膜(HfON膜)を使用した場合におけるpチャネル型MISFETのフラットバンド電圧(V)およびしきい値電圧(V)を示したグラフである。ゲート電極として、p型不純物を導入したポリシリコン膜、プラチナシリサイド膜、プラチナリッチシリサイド膜、ホウ素を導入したプラチナリッチシリサイド膜のそれぞれを用いた場合のフラットバンド電圧(V)およびしきい値電圧(V)が示されている。黒丸がフラットバンド電圧を示し、白丸がしきい値電圧を示している。

【0061】

図18に示すように、p型不純物を導入したポリシリコン膜、プラチナシリサイド膜、プラチナリッチシリサイド膜、ホウ素を導入したプラチナリッチシリサイド膜になるにつれて、フラットバンド電圧が上昇していることがわかる。しきい値電圧も同様の変化をして、ホウ素を導入したプラチナリッチシリサイド膜で、最もしきい値電圧の絶対値が低くなることがわかる。言い換えれば、ゲート絶縁膜に高誘電体膜を使用した場合、ゲート電極を構成するプラチナリッチシリサイド膜にホウ素などの導電型不純物を導入することで、しきい値電圧を微調整できることがわかる。

【0062】

本実施の形態によれば、導電型不純物を含有するプラチナリッチシリサイド膜をゲート電極として使用することにより、しきい値電圧を調整することができる。したがって、しきい値電圧を調整することにより、高いON電流を有し、かつ、しきい値電圧の低い半導体装置を製造することができる。また、種々の半導体装置に要求されるしきい値電圧を実現することができる。

【0063】

本実施の形態では、pチャネル型MISFETにおいて、プラチナリッチシリサイド膜よりなるゲート電極52に導電型不純物(例えば、ホウ素)を導入する場合について説明した。ここで、プラチナリッチシリサイド膜に代えて、ニッケルリッチシリサイド膜、ルテニウム(Ru)リッチシリサイド膜またはイリジウム(Ir)リッチシリサイド膜に導電型不純物を導入しても同様の効果が得られる。

【0064】

また、本実施の形態では、図6に示すように、pチャネル型MISFET形成領域のポリシリコン膜35にホウ素を導入する例について説明したが、これに限らず、例えば図9に示すように、n型ウェル33内に高濃度p型不純物拡散領域44、45を形成する際、

シリコンゲート電極36bにホウ素を導入してもよい。

【0065】

また、本実施の形態では、nチャネル型MISFETには、導電型不純物を導入しない例について説明したが、導電型不純物を導入してもよい。

【0066】

以上、本発明者によってなされた発明を実施の形態に基づき具体的に説明したが、本発明は前記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることはいうまでもない。

【産業上の利用可能性】

【0067】

本発明は、半導体装置を製造する製造業に幅広く利用することができる。

【図面の簡単な説明】

【0068】

【図1】本発明の実施の形態におけるCMISFETを示す断面図である。

【図2】(a)は、シリサイド反応する前のゲート電極に導入されているホウ素の濃度プロファイルを示す図であり、(b)は、シリサイド反応後のゲート電極に導入されているホウ素の濃度プロファイルを示す図である。

【図3】実施の形態におけるCMISFETの製造工程を示す断面図である。

【図4】図3に続くCMISFETの製造工程を示す断面図である。

【図5】図4に続くCMISFETの製造工程を示す断面図である。

【図6】図5に続くCMISFETの製造工程を示す断面図である。

【図7】図6に続くCMISFETの製造工程を示す断面図である。

【図8】図7に続くCMISFETの製造工程を示す断面図である。

【図9】図8に続くCMISFETの製造工程を示す断面図である。

【図10】図9に続くCMISFETの製造工程を示す断面図である。

【図11】図10に続くCMISFETの製造工程を示す断面図である。

【図12】図11に続くCMISFETの製造工程を示す断面図である。

【図13】図12に続くCMISFETの製造工程を示す断面図である。

【図14】図13に続くCMISFETの製造工程を示す断面図である。

【図15】図14に続くCMISFETの製造工程を示す断面図である。

【図16】ゲート絶縁膜としてハフニウムアルミネート膜、ゲート電極として、プラチナシリサイド膜、プラチナリッチシリサイド膜、ホウ素を導入したプラチナリッチシリサイド膜をそれぞれ使用した場合におけるゲート電圧と容量との関係を示すグラフである。

【図17】ゲート絶縁膜としてハフニウムアルミネート膜、ゲート電極として、プラチナシリサイド膜、プラチナリッチシリサイド膜、ホウ素を導入したプラチナリッチシリサイド膜をそれぞれ使用した場合におけるフラットバンド電圧を示すグラフである。

【図18】ゲート絶縁膜としてHfON膜、ゲート電極として、p型不純物を導入したポリシリコン膜、プラチナシリサイド膜、プラチナリッチシリサイド膜、ホウ素を導入したプラチナリッチシリサイド膜をそれぞれ使用した場合におけるフラットバンド電圧およびしきい値電圧を示すグラフである。

【符号の説明】

【0069】

1 半導体基板

2 素子分離領域

3 p型ウェル

4 n型ウェル

5 ゲート絶縁膜

6a ゲート電極

6b ゲート電極

7 低濃度n型不純物拡散領域

8 低濃度n型不純物拡散領域

9 低濃度p型不純物拡散領域

10 低濃度p型不純物拡散領域

11 サイドウォール

12 高濃度n型不純物拡散領域

13 高濃度n型不純物拡散領域

14 高濃度p型不純物拡散領域

15 高濃度p型不純物拡散領域

16 絶縁膜

17 絶縁膜

18 コンタクトホール

19a チタン/窒化チタン膜

19b タングステン膜

20 プラグ

21a チタン/窒化チタン膜

21b アルミニウム膜

21c チタン/窒化チタン膜

22 配線

30 半導体基板

31 素子分離領域

32 p型ウェル

33 n型ウェル

34 ゲート絶縁膜

35 ポリシリコン膜

36a シリコンゲート電極

36b シリコンゲート電極

37 低濃度n型不純物拡散領域

38 低濃度n型不純物拡散領域

39 低濃度p型不純物拡散領域

40 低濃度p型不純物拡散領域

41 サイドウォール

42 高濃度n型不純物拡散領域

43 高濃度n型不純物拡散領域

44 高濃度p型不純物拡散領域

45 高濃度p型不純物拡散領域

46 酸化シリコン膜

47 絶縁膜

48 ニッケル膜

49 ゲート電極

50 絶縁膜

51 プラチナ膜

52 ゲート電極

53 酸化シリコン膜

54 コンタクトホール

55a チタン/窒化チタン膜

55b タングステン膜

56 プラグ

57a チタン/窒化チタン膜

57b アルミニウム膜

57c チタン/窒化チタン膜

58 配線

【特許請求の範囲】

【請求項1】

(a)半導体基板と、

(b)前記半導体基板上に形成され、ハフニウム酸化物を主体として含むゲート絶縁膜と、

(c)前記ゲート絶縁膜上に形成され、シリコン膜とメタル膜を反応させて形成したメタルシリサイド膜よりなるゲート電極とを有するMISFETを含む半導体装置であって、

前記メタルシリサイド膜のメタル原子に対するシリコン原子の比が1未満であり、かつ、前記メタルシリサイド膜中に導電型不純物が導入されていることを特徴とする半導体装置。

【請求項2】

前記メタル膜は、プラチナ膜、ニッケル膜、ルテニウム膜あるいはイリジウム膜であることを特徴とする請求項1記載の半導体装置。

【請求項3】

前記導電型不純物は、p型不純物であることを特徴とする請求項1記載の半導体装置。

【請求項4】

前記導電型不純物は、n型不純物であることを特徴とする請求項1記載の半導体装置。

【請求項5】

前記導電型不純物は、前記ゲート絶縁膜と前記ゲート電極との界面近傍に偏析していることを特徴とする請求項1記載の半導体装置。

【請求項6】

前記MISFETは、pチャネル型MISFETであることを特徴とする請求項1記載の半導体装置。

【請求項7】

半導体基板上にnチャネル型MISFETとpチャネル型MISFETが形成された半導体装置であって、

前記pチャネル型MISFETは、

(a)前記半導体基板上に形成され、ハフニウム酸化物を主体として含むゲート絶縁膜と、

(b)前記ゲート絶縁膜上に形成され、シリコン膜とメタル膜を反応させて形成したメタルシリサイド膜よりなるゲート電極とを備え、

前記メタルシリサイド膜のメタル原子に対するシリコン原子の比が1未満であり、かつ、前記メタルシリサイド膜中に導電型不純物が導入されていることを特徴とする半導体装置。

【請求項8】

(a)半導体基板上に、ハフニウム酸化物を主体として含むゲート絶縁膜を形成する工程と、

(b)前記ゲート絶縁膜上にMISFETのシリコンゲート電極を形成する工程と、

(c)前記シリコンゲート電極内に導電型不純物を導入する工程と、

(d)前記半導体基板上に、前記シリコンゲート電極よりも厚い膜厚の絶縁膜を形成した後、前記絶縁膜の表面を平坦化することにより、前記シリコンゲート電極の表面を露出する工程と、

(e)前記シリコンゲート電極の上部にメタル膜を形成する工程と、

(f)前記半導体基板を加熱し、前記シリコンゲート電極と前記メタル膜を反応させることにより、メタル原子に対するシリコン原子の比が1未満のメタルシリサイド膜からなるゲート電極を形成し、前記ゲート絶縁膜と前記ゲート電極の界面近傍に前記導電型不純物を偏析させる工程とを備えることを特徴とする半導体装置の製造方法。

【請求項9】

前記メタル膜の膜厚は、前記シリコンゲート電極の厚さよりも厚いことを特徴とする請求項8記載の半導体装置の製造方法。

【請求項10】

前記メタル膜の膜厚は、前記シリコンゲート電極の厚さの2倍以上であることを特徴とする請求項9記載の半導体装置の製造方法。

【請求項1】

(a)半導体基板と、

(b)前記半導体基板上に形成され、ハフニウム酸化物を主体として含むゲート絶縁膜と、

(c)前記ゲート絶縁膜上に形成され、シリコン膜とメタル膜を反応させて形成したメタルシリサイド膜よりなるゲート電極とを有するMISFETを含む半導体装置であって、

前記メタルシリサイド膜のメタル原子に対するシリコン原子の比が1未満であり、かつ、前記メタルシリサイド膜中に導電型不純物が導入されていることを特徴とする半導体装置。

【請求項2】

前記メタル膜は、プラチナ膜、ニッケル膜、ルテニウム膜あるいはイリジウム膜であることを特徴とする請求項1記載の半導体装置。

【請求項3】

前記導電型不純物は、p型不純物であることを特徴とする請求項1記載の半導体装置。

【請求項4】

前記導電型不純物は、n型不純物であることを特徴とする請求項1記載の半導体装置。

【請求項5】

前記導電型不純物は、前記ゲート絶縁膜と前記ゲート電極との界面近傍に偏析していることを特徴とする請求項1記載の半導体装置。

【請求項6】

前記MISFETは、pチャネル型MISFETであることを特徴とする請求項1記載の半導体装置。

【請求項7】

半導体基板上にnチャネル型MISFETとpチャネル型MISFETが形成された半導体装置であって、

前記pチャネル型MISFETは、

(a)前記半導体基板上に形成され、ハフニウム酸化物を主体として含むゲート絶縁膜と、

(b)前記ゲート絶縁膜上に形成され、シリコン膜とメタル膜を反応させて形成したメタルシリサイド膜よりなるゲート電極とを備え、

前記メタルシリサイド膜のメタル原子に対するシリコン原子の比が1未満であり、かつ、前記メタルシリサイド膜中に導電型不純物が導入されていることを特徴とする半導体装置。

【請求項8】

(a)半導体基板上に、ハフニウム酸化物を主体として含むゲート絶縁膜を形成する工程と、

(b)前記ゲート絶縁膜上にMISFETのシリコンゲート電極を形成する工程と、

(c)前記シリコンゲート電極内に導電型不純物を導入する工程と、

(d)前記半導体基板上に、前記シリコンゲート電極よりも厚い膜厚の絶縁膜を形成した後、前記絶縁膜の表面を平坦化することにより、前記シリコンゲート電極の表面を露出する工程と、

(e)前記シリコンゲート電極の上部にメタル膜を形成する工程と、

(f)前記半導体基板を加熱し、前記シリコンゲート電極と前記メタル膜を反応させることにより、メタル原子に対するシリコン原子の比が1未満のメタルシリサイド膜からなるゲート電極を形成し、前記ゲート絶縁膜と前記ゲート電極の界面近傍に前記導電型不純物を偏析させる工程とを備えることを特徴とする半導体装置の製造方法。

【請求項9】

前記メタル膜の膜厚は、前記シリコンゲート電極の厚さよりも厚いことを特徴とする請求項8記載の半導体装置の製造方法。

【請求項10】

前記メタル膜の膜厚は、前記シリコンゲート電極の厚さの2倍以上であることを特徴とする請求項9記載の半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【公開番号】特開2006−344713(P2006−344713A)

【公開日】平成18年12月21日(2006.12.21)

【国際特許分類】

【出願番号】特願2005−167903(P2005−167903)

【出願日】平成17年6月8日(2005.6.8)

【国等の委託研究の成果に係る記載事項】(出願人による申告)平成16年度独立行政法人新エネルギー・産業技術総合開発機構「次世代半導体材料・プロセス基盤(MIRAI)」委託研究、産業活力再生特別措置法第30条の適用を受ける特許出願

【出願人】(503121103)株式会社ルネサステクノロジ (4,790)

【出願人】(301021533)独立行政法人産業技術総合研究所 (6,529)

【Fターム(参考)】

【公開日】平成18年12月21日(2006.12.21)

【国際特許分類】

【出願日】平成17年6月8日(2005.6.8)

【国等の委託研究の成果に係る記載事項】(出願人による申告)平成16年度独立行政法人新エネルギー・産業技術総合開発機構「次世代半導体材料・プロセス基盤(MIRAI)」委託研究、産業活力再生特別措置法第30条の適用を受ける特許出願

【出願人】(503121103)株式会社ルネサステクノロジ (4,790)

【出願人】(301021533)独立行政法人産業技術総合研究所 (6,529)

【Fターム(参考)】

[ Back to top ]