半導体装置およびその製造方法

【課題】実装信頼性が向上された半導体装置を提供する。

【解決手段】中央部1aの厚さと周辺部1bの厚さとを比較すると、周辺部1bの厚さの方が小さい。そのため、相対的に厚さの小さい周辺部1bのチップは、肉厚が小さいので撓みやすくなっている。したがって、たとえば温度降下により、実装基板2が収縮し、LSIチップ1と実装基板2とを接続する半田バンプ3において歪が生じても、周辺部1bは実装基板2の収縮に追随して収縮するため、周辺部1bにかかる応力は低減される。

【解決手段】中央部1aの厚さと周辺部1bの厚さとを比較すると、周辺部1bの厚さの方が小さい。そのため、相対的に厚さの小さい周辺部1bのチップは、肉厚が小さいので撓みやすくなっている。したがって、たとえば温度降下により、実装基板2が収縮し、LSIチップ1と実装基板2とを接続する半田バンプ3において歪が生じても、周辺部1bは実装基板2の収縮に追随して収縮するため、周辺部1bにかかる応力は低減される。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置及びその製造方法に関する。

【背景技術】

【0002】

半導体装置の高速化、高密度化の要求に伴い、半導体用LSIにおいても、それに対応した構造や製法が要求され、ハイエンド向けLSIにおいては、フリップチップやベアチップが主流となりつつある。

【0003】

高速化の要求への対策の一つとして、LSIチップ内の配線間容量を低減するため、低誘電率のLow−k材が用いられる。しかし、Low−k材は、周辺膜、特にSiCN膜との密着性が弱いため、実装時や温度サイクル試験などの際、周囲の環境温度変化によって起こる熱応力により、LSIチップ内において界面剥離が発生することがあった。

【0004】

図5を用いて、LSIチップ内における界面剥離の発生を抑制するための従来の半導体装置の構造について説明する。

【0005】

図5(a)は、従来の技術における半導体装置を上方から見た平面図で、図5(b)は、図5(a)のA−A’線における断面図である。

【0006】

LSIチップ51と実装基板52とが半田バンプ53を介して物理的、電気的に接続されている。また、半田バンプ53を覆うように、保護材として樹脂材54が充填されている。LSIチップ51裏面には、溝58が、たとえば格子状に形成されている。

【0007】

上述した半導体装置の製造プロセスとしては、一般的なフリップチップボールグリッドアレイ(以下FCBGA)やベアチップの製造工程と同じように、まず、LSIチップ51に、半田バンプ53を印刷もしくはボール搭載によって取り付け、リフローを行う。次に、実装基板52に半田バンプ53が付いたLSIチップ51を位置合わせしながら搭載し、リフローを行う。ついで、半田バンプ53を完全に覆うように樹脂材54を充填し、ベークを行う。続いて、レーザやカッターを用いて、LSIチップ51の裏面に、溝58を、たとえば格子状に形成する。以上のプロセスにより上述した半導体装置が完成する。

【0008】

また、図6を用いて、従来の半導体装置の他の例を説明する。

【0009】

図6(a)は、従来の技術における半導体装置を上方から見た平面図、図6(b)は、図6(a)のA−A’線における断面図である。

【0010】

一般的なFCBGAやベアチップと同様、LSIチップ101と実装基板102とが半田バンプ103を介して電気的、物理的に接続されている。また、半田バンプ103を覆うように、保護材として樹脂材104が充填されている。

【0011】

また、LSIチップ101は、裏面を全体的に研削することで薄く形成されており、チップの厚さは、一般的には725μm程度のところ、約300μmである。裏面研削は、ダイシング前のウェハ状態において、たとえば、裏面研削工法などにより行われる。

【0012】

【特許文献1】特開2000−260811号公報

【特許文献2】特開平11−345823号公報

【発明の開示】

【発明が解決しようとする課題】

【0013】

しかしながら、上記文献記載の従来技術は、以下の点で改善の余地を有していた。

【0014】

第一に、LSIチップ周辺部における半田バンプの応力低減効果が小さいことがあった。この原因は、LSIチップ周辺部も含めて、チップの厚い領域が多いことに起因する。すなわち、チップの厚い領域がLSIチップの大部分を占めているため、LSIチップ全体としては、基板の変化に追随してLSIチップが変化する量が小さくなるからである。第二に、特に、LSIチップの周辺部近傍において、半田バンプの応力低減効果が更に減少することがあった。第三に、LSIチップを全体的に薄く形成した場合には、LSI全体が反りやすいことがあった。

【課題を解決するための手段】

【0015】

本発明によれば、基板と、複数のバンプと、半導体チップとがこの順に積層された半導体装置であって、前記複数のバンプのそれぞれの上端面と前記半導体チップ素子形成面とが接触し、前記半導体チップの周縁における厚さは、前記半導体チップの中央部における厚さよりも小さいことを特徴とする半導体装置が提供される。

【0016】

この発明によれば、半導体チップの周縁における厚さは、半導体チップの中央部における厚さよりも小さいため、バンプにかかる熱応力を和らげつつ、半導体チップ全体の反りが低減される。また、半導体チップ全体ではなく、その周縁における厚さが小さいため、半導体チップの強度が保たれる。したがって、実装信頼性が向上された半導体装置を提供することができる。

【0017】

本発明によれば、基板と半導体チップとを用意する工程と、前記半導体チップ表面に複数のバンプを設ける工程と、前記基板上面と前記半導体チップの前記複数のバンプが形成された面とが接するように前記基板上に前記半導体チップを設ける工程と、前記半導体チップ裏面の外周縁を選択的に除去し、段差を形成する工程と、を含むことを特徴とする半導体装置の製造方法が提供される。

【0018】

この発明によれば、半導体チップ裏面の外周縁を選択的に除去し、段差を形成することで、実装信頼性の高い半導体装置を安定的に提供することができる。

【発明の効果】

【0019】

本発明によれば、半導体チップの周縁における厚さは、半導体チップの中央部における厚さよりも小さいため、実装信頼性が向上された半導体装置が提供される。

【発明を実施するための最良の形態】

【0020】

以下、本発明の実施の形態について、図面を用いて説明する。尚、すべての図面において、同様な構成要素には同様の符号を付し、適宜説明を省略する。

【0021】

第1の実施の形態

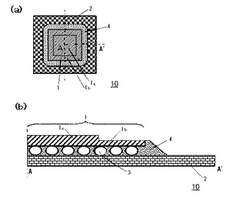

図1は、本実施形態に係る半導体装置10の構造を表わした図で、図1(a)は、半導体装置10を上方から見た平面図であり、図1(b)は、図1(a)のA−A’線における断面図である。

【0022】

半導体装置10は、実装基板2、実装基板2の上面に接して設けられた半田バンプ3、半田バンプ3と接して設けられたLSIチップ1、半田バンプ3を完全に覆うように充填された樹脂材4により構成されており、フリップチップボールグリッドアレイ構造またはベアチップ構造を有する。

【0023】

LSIチップ1は、中央部近傍に設けられた厚さが大きい中央部1aと、LSIチップ1の周縁近傍において、中央部1aよりも前記半導体チップの厚さが小さい領域である厚さが小さい周辺部1bとで構成される。

【0024】

LSIチップ1の厚さは、LSIチップの中央部1aにおいて、700μm程度であり、周辺部1bにおける厚さは、300μm〜400μm程度である。すなわち、LSIチップ1の裏面には、チップの外周縁に沿って段差が設けられており、周辺部1bの厚さの方が、中央部1aの厚さよりも小さい。ここで、周辺部1bの厚さは、研削されることによって、中央部1aの厚さよりも小さくなっている。また、中央部1aの厚さと、周辺部1bの厚さとの差は、200μm〜500μm程度であることが好ましい。厚さの差がこの範囲にあることで、LSIチップ1は、実装基板2の収縮への追随性に比較的優れ、LSI全体の反りが大きくなることを、より効果的に抑制することができる。本実施形態においては、チップ周辺部1bの幅(段差の幅)は、LSIチップ1の端から半田バンプ3の3ピッチ分(約600μm)である。

【0025】

LSIチップ1の周辺部1bは、中央部1aと比較して厚みが小さい。そのため、周辺部1bは撓みやすくなり、実装基板2の伸縮に合わせて、LSIチップ1が追随して伸縮しやすい。そのため、半導体装置10において、周辺部1b直下の半田バンプ3への応力を緩和させることができる。

【0026】

半田バンプ3は、実装基板2の上面およびLSIチップ1の表面(素子形成面)に接するように、グリッドアレイ状に複数個設けられている。半田バンプ3は導電性を有するので、半田バンプ3を介して、LSIチップ1と実装基板2とが電気的および物理的に接続されている。

【0027】

樹脂材4は、半田バンプ3を完全に覆うように充填されており、半田バンプ3の保護材としての機能を有する。

【0028】

図2を用いて、本実施形態に係る半導体装置10の製造プロセスを説明する。

【0029】

まず、図2(a)に示すように、一般的な半導体装置と同様の方法にて、LSIチップ1の電極パッド(不図示)にフラックス3aを印刷し、半田バンプ3をフラックス3aに位置ズレしないように乗せ、リフローを行う。

【0030】

つぎに、図2(b)に示すように、実装基板2の電極パッド(不図示)上にフラックスや予備半田2aを用意し、半田バンプ3を位置ズレしないように予備半田2aに載せて、リフローを行う。これにより、LSIチップ1と実装基板2とは、半田バンプ3を介し、電気的、物理的に接続される。

【0031】

ついで、図2(c)に示すように、樹脂材4を充填し、半田バンプ3を完全に覆うようにする。

【0032】

続いて、図2(d)に示すように、LSIチップ1の裏面の周辺部を選択的に研削する。こうすることにより、図2(e)に示すように、LSIチップ1中央部の研削していない厚い部分である中央部1aと、LSIチップ1周辺部の薄い部分である周辺部1bとを構成することができる。

【0033】

LSIチップ1裏面の研削にはレーザや旋盤などが用いられる。レーザを使用する場合は、LSIチップを300μm〜400μm程度削る。研削の際には、レーザ照射が繰り返し行われたり、レーザのパワー調整がなされる。また、研削幅が所望の幅となるように、レーザの照射領域の調節を行う。旋盤を用いる場合も同様である。

【0034】

以上のプロセスにより、半導体装置10が完成する。

【0035】

以下、本実施形態に係る半導体装置10およびその製造方法の効果について説明する。

【0036】

本実施形態においては、LSIチップ1の周辺部1bの厚さは300〜400μm程度、中央部1aの厚さは700μm程度となっており、中央部1aの厚さと周辺部1bの厚さとを比較すると、周辺部1bの厚さの方が小さい。そのため、相対的に厚さの小さい周辺部1bのチップは、肉厚が小さいので撓みやすくなっている。したがって、たとえば温度降下により、実装基板2が矢印7(図8(b))の方向に収縮し、LSIチップ1と実装基板2とを接続する半田バンプ3において歪が生じても、周辺部1bは実装基板2の収縮に追随して収縮するため、周辺部1bにかかる応力は低減される。

【0037】

ここで、半田バンプ3のうち、中央部1aと接するバンプ3aにおいては、実装基板2の収縮に伴う歪はもともと小さいため、バンプ3aにかかる応力はもともと小さい。そのため、中央部1aにおいては、LSIチップ1を撓ませる必要性が比較的少ない。したがって、本実施形態における半導体装置10においては、LSIチップ1の中央部1aの厚さを相対的に大きくすることで、過度にLSIチップ1を撓ませることなく、半導体装置10が過度に反らないようにできる。

【0038】

特許文献1記載の半導体装置においては、LSIチップのコーナー部近傍において、半田バンプの応力低減効果が減少することがあった。なぜなら、LSIチップ表面に格子状に溝が形成されているが、格子状に形成された溝は、LSIチップの対角線方向にかかる応力の方向に対し最大45度の傾きを有しているからである。そこで、本実施形態においては、半田バンプ3への応力低減が比較的求められる箇所であるLSIチップ1の周辺部1bを薄くすることで、実装基板2の伸縮に対してLSIチップ1を、より効果的に追随させている。そのため、LSIチップ1の強度を損なわずに、半田バンプ3への応力緩和をより効率的に図るという利点が得られる。

【0039】

また、樹脂材4が半田バンプ3を完全に覆うように設けられているため、半田バンプ3が衝撃を受けることを抑制することができる。そのため、半田バンプ3の信頼性を向上させることができる。

【0040】

また、LSIチップ1の周辺部1bをレーザや旋盤を用いて選択的に研削することで、実装基板2の収縮への追随性に優れ、LSIチップ1が過度に反らない半導体装置10を安定的に製造することができる。

【0041】

第2の実施の形態

図3に、本実施形態に係る半導体装置20を示す。半導体装置20は、中央部21aの部分の形状が異なる以外は、第1の実施の形態で説明した半導体装置10と同じ構造を有する。

【0042】

図3(a)は、本実施形態に係る半導体装置20を上方から見た平面図で、図3(b)は、図3(a)のA−A’線における断面図である。LSIチップ21の中央部21aの部分を円形に残す。

【0043】

以下の製造プロセスにより半導体装置20を製造する。

【0044】

まず、第1の実施形態と同様、LSIチップ21と実装基板22とを、一般的な実装技術により半田バンプ23を介して電気的、物理的に接続を行う。次に、半田バンプ23を完全に覆うように樹脂材24を充填する。ついで、半導体チップ21から樹脂材24までにより構成される半導体装置を回転ステージに乗せ、第1の実施形態と同様に、レーザや旋盤を用いてLSIチップ21の周辺部を研削し、中央部の厚い領域である中央部21aと周辺部の薄い領域である周辺部21bとを構成する。LSIチップ21の中央部21aの部分が円形であることによって、LSIチップ21のコーナー部における半田バンプ23への応力低減効果を、より効果的に大きくすることができる。なぜなら、矩形である場合と比較して、中央部21aの角部とLSIチップ21のコーナー部との距離が大きくなるため、コーナー部において、肉厚の薄い領域である周辺部21bが占める領域の面積が、より増大するからである。

【0045】

以上のプロセスにより半導体装置20が完成する。

【0046】

なお、中央部21aの上方から見た平面形状は、たとえば多角形などの円形以外の形状であっても、コーナー部において、肉厚の薄い領域である周辺部が占める領域の面積が増大し、コーナー部における半田バンプへの応力低減効果が、より効果的に大きくなる形状であればよい。

【0047】

第3の実施の形態

図4に、本実施形態に係る半導体装置30の構造を示す。半導体装置30は、周辺部の肉厚が薄い部分である周辺部31bの形状が異なる以外は、第1の実施の形態で説明した半導体装置10と同じ構造を有する。

【0048】

図4(a)は、半導体装置30を上方から見た平面図であり、図4(b)は、図4(a)のA−A’線における断面図である。

【0049】

半導体装置30の周辺部31bの厚さは、中央部31aに近づくにつれて大きくなる。すなわち、周辺部31bの厚さが、LSIチップ31の中央部方向へ向けて漸増する領域を有する。ここで、厚さが大きくなる領域において、周辺部31bの表面は傾斜を有しており、斜面に丸みを含んでいてもよい。

【0050】

以下の製造プロセスにより半導体装置30を製造する。

【0051】

まず、第1の実施の形態および第2の実施の形態と同様、LSIチップ31と実装基板32とを半田バンプ33を介して接続し、樹脂材34を充填する。次に、LSIチップ31の周辺部を研削し、中央部の厚い部分である中央部31aと周辺部の薄い部分である周辺部31bとを構成する。この際、中央部31aと周辺部31bとの間に傾斜を有しており、また、斜面に丸みが設けられている。傾斜や丸みを設ける方法としては、LSIチップ31研削時に側面に丸みや傾斜を帯びた旋盤35などが用いられる。

【0052】

以上のプロセスにより、半導体装置30が完成する。

【0053】

本実施形態に係る半導体装置30の効果を以下に説明する。

【0054】

LSIチップ31は、中央部31aと周辺部31bとの間に、傾斜を有しており、また、斜面に丸みを有している。そのため、LSIチップ31の裏面における応力勾配を和らげることが出来る。したがって、LSIチップ31が、実装基板32の収縮に追随して収縮するため、周辺部31bにかかる応力が低減される。

【実施例】

【0055】

図7および図8に示す半導体装置のそれぞれについて、図9および図10に、温度を100℃から0℃に降下させた場合の、実装基板およびLSIチップの収縮、応力、および反りのシミュレーション結果を示す。図9(a)において、実装基板42上に設けられたLSIチップ41の中央部41aの厚さは700μm、周辺部41bの厚さは400μmである。図9(b)において、溝48の幅は200μmであり、溝とその隣の溝との間隔は1000μmである。図9(c)における、図9(c)の上方向を正の方向とするA’点における反りの数値、図9(c)の左方向を正の方向とするB点およびC点における応力の数値を図10に示した。なお、図7および図8中の矢印6、56、106、206は、それぞれLSIチップ1、LSIチップ51、LSIチップ101、LSIチップ201の収縮方向を表す。また、矢印7、57、107、207は、それぞれ実装基板2、実装基板52、実装基板102、実装基板202の収縮方向を表わす。ここで、矢印の長さはそれぞれの収縮の度合いをイメージしている。また、図7(c)の矢印59は、実装基板52の主な収縮および応力の方向を表わす。

【0056】

実施例1

第1の実施の形態と同様のプロセスで製造された、図8(b)に示すLSIチップ1の周辺部1bの厚さが中央部1aの厚さよりも小さい半導体装置においては、LSI全体を必要以上に反らせることなく、最外周半田バンプ3dにおける応力を低減することができることがわかった。

【0057】

比較例1

図7(a)に示す従来の半導体装置においては、LSIチップ201が実装基板202の収縮に追随しにくいため、最外周半田バンプ203dにおける応力が大きくなることがわかった。

【0058】

比較例2

図7(b)に示す従来の半導体装置(特許文献1記載)においては、LSIチップ51は実装基板52の収縮にある程度追随する。そのため、特に最外周半田バンプ53dにおける応力は、ある程度緩和される。しかし、その効果は比較的大きくないことがわかった。また、LSI全体の反りが、やや大きくなることがわかった。

【0059】

比較例3

図8(a)に示す従来の半導体装置(特許文献2記載)においては、LSIチップ101全体が実装基板102に追随しやすいため、特に最外周半田バンプ103dでの応力は低減されることがわかった。しかし、LSI全体の反りが大きくなることがわかった。

【0060】

以上の実施例および比較例より、LSIチップの周縁部の厚さを中央部の厚さよりも小さくすることで、LSI全体を必要以上に反らせることなく、最外周半田バンプにおける応力を低減できることがわかった。

【0061】

以上、図面を参照して本発明の実施形態について述べたが、これらは本発明の例示であり、上記以外の様々な構成を採用することもできる。

【0062】

たとえば、LSIチップ裏面の外周縁に沿った段差は、実装基板の収縮への追随性に比較的優れ、LSI全体の反りが大きくならない程度の幅を有していればよく、LSIチップの外端から、LSIチップに設けられた半田バンプのうち最外周のバンプの内側を通り、実装基板と略垂直な面と実装基板の裏面との交点までの距離が300μm以上であり、かつ、チップサイズの1/4以下であれば、なおよい。

【0063】

また、上記実施形態において、中央部1aの厚さと周辺部1bの厚さとの差が200μm〜500μmである形態について説明したが、実装基板の収縮への追随性に比較的優れ、LSI全体の反りが大きくならない程度の差であればよい。

【図面の簡単な説明】

【0064】

【図1】実施の形態に係る半導体装置の構造を模式的に示した図である。

【図2】実施の形態に係る半導体装置の製造工程を模式的に示した工程断面図である。

【図3】実施の形態に係る半導体装置の構造を模式的に示した図である。

【図4】実施の形態に係る半導体装置の構造を模式的に示した図である。

【図5】従来の半導体装置の構造を模式的に示した概略図である。

【図6】従来の半導体装置の構造を模式的に示した概略図である。

【図7】従来の技術に係る半導体装置を対比した図である。

【図8】従来の半導体装置と実施の形態に係る半導体装置を対比した図である。

【図9】従来の半導体装置と実施の形態に係る半導体装置のそれぞれにおける応力シミュレーションモデルを説明する図である。

【図10】従来の半導体装置と実施の形態に係る半導体装置のそれぞれにおける応力シミュレーションモデルの結果を説明する図である。

【符号の説明】

【0065】

1 LSIチップ

1a 中央部

1b 周辺部

2 実装基板

3 半田バンプ

4 樹脂材

5 旋盤又はレーザ

6 LSIチップ1の収縮方向

7 実装基板2の収縮方向

21 LSIチップ

21a 中央部

21b 周辺部

31 LSIチップ

31a 中央部

31b 周辺部

41 LSIチップ

41a 中央部

41b 周辺部

42 実装基板

48 溝

51 LSIチップ

52 実装基板

53 半田バンプ

54 樹脂材

56 LSIチップ51の収縮方向

57 実装基板52の収縮方向

58 溝

59 応力(収縮)の方向

101 LSIチップ

102 実装基板

103 半田バンプ

104 樹脂材

106 LSIチップ101の収縮方向

107 実装基板102の収縮方向

201 LSIチップ

202 実装基板

203 半田バンプ

206 LSIチップ201の収縮方向

207 実装基板202の収縮方向

【技術分野】

【0001】

本発明は、半導体装置及びその製造方法に関する。

【背景技術】

【0002】

半導体装置の高速化、高密度化の要求に伴い、半導体用LSIにおいても、それに対応した構造や製法が要求され、ハイエンド向けLSIにおいては、フリップチップやベアチップが主流となりつつある。

【0003】

高速化の要求への対策の一つとして、LSIチップ内の配線間容量を低減するため、低誘電率のLow−k材が用いられる。しかし、Low−k材は、周辺膜、特にSiCN膜との密着性が弱いため、実装時や温度サイクル試験などの際、周囲の環境温度変化によって起こる熱応力により、LSIチップ内において界面剥離が発生することがあった。

【0004】

図5を用いて、LSIチップ内における界面剥離の発生を抑制するための従来の半導体装置の構造について説明する。

【0005】

図5(a)は、従来の技術における半導体装置を上方から見た平面図で、図5(b)は、図5(a)のA−A’線における断面図である。

【0006】

LSIチップ51と実装基板52とが半田バンプ53を介して物理的、電気的に接続されている。また、半田バンプ53を覆うように、保護材として樹脂材54が充填されている。LSIチップ51裏面には、溝58が、たとえば格子状に形成されている。

【0007】

上述した半導体装置の製造プロセスとしては、一般的なフリップチップボールグリッドアレイ(以下FCBGA)やベアチップの製造工程と同じように、まず、LSIチップ51に、半田バンプ53を印刷もしくはボール搭載によって取り付け、リフローを行う。次に、実装基板52に半田バンプ53が付いたLSIチップ51を位置合わせしながら搭載し、リフローを行う。ついで、半田バンプ53を完全に覆うように樹脂材54を充填し、ベークを行う。続いて、レーザやカッターを用いて、LSIチップ51の裏面に、溝58を、たとえば格子状に形成する。以上のプロセスにより上述した半導体装置が完成する。

【0008】

また、図6を用いて、従来の半導体装置の他の例を説明する。

【0009】

図6(a)は、従来の技術における半導体装置を上方から見た平面図、図6(b)は、図6(a)のA−A’線における断面図である。

【0010】

一般的なFCBGAやベアチップと同様、LSIチップ101と実装基板102とが半田バンプ103を介して電気的、物理的に接続されている。また、半田バンプ103を覆うように、保護材として樹脂材104が充填されている。

【0011】

また、LSIチップ101は、裏面を全体的に研削することで薄く形成されており、チップの厚さは、一般的には725μm程度のところ、約300μmである。裏面研削は、ダイシング前のウェハ状態において、たとえば、裏面研削工法などにより行われる。

【0012】

【特許文献1】特開2000−260811号公報

【特許文献2】特開平11−345823号公報

【発明の開示】

【発明が解決しようとする課題】

【0013】

しかしながら、上記文献記載の従来技術は、以下の点で改善の余地を有していた。

【0014】

第一に、LSIチップ周辺部における半田バンプの応力低減効果が小さいことがあった。この原因は、LSIチップ周辺部も含めて、チップの厚い領域が多いことに起因する。すなわち、チップの厚い領域がLSIチップの大部分を占めているため、LSIチップ全体としては、基板の変化に追随してLSIチップが変化する量が小さくなるからである。第二に、特に、LSIチップの周辺部近傍において、半田バンプの応力低減効果が更に減少することがあった。第三に、LSIチップを全体的に薄く形成した場合には、LSI全体が反りやすいことがあった。

【課題を解決するための手段】

【0015】

本発明によれば、基板と、複数のバンプと、半導体チップとがこの順に積層された半導体装置であって、前記複数のバンプのそれぞれの上端面と前記半導体チップ素子形成面とが接触し、前記半導体チップの周縁における厚さは、前記半導体チップの中央部における厚さよりも小さいことを特徴とする半導体装置が提供される。

【0016】

この発明によれば、半導体チップの周縁における厚さは、半導体チップの中央部における厚さよりも小さいため、バンプにかかる熱応力を和らげつつ、半導体チップ全体の反りが低減される。また、半導体チップ全体ではなく、その周縁における厚さが小さいため、半導体チップの強度が保たれる。したがって、実装信頼性が向上された半導体装置を提供することができる。

【0017】

本発明によれば、基板と半導体チップとを用意する工程と、前記半導体チップ表面に複数のバンプを設ける工程と、前記基板上面と前記半導体チップの前記複数のバンプが形成された面とが接するように前記基板上に前記半導体チップを設ける工程と、前記半導体チップ裏面の外周縁を選択的に除去し、段差を形成する工程と、を含むことを特徴とする半導体装置の製造方法が提供される。

【0018】

この発明によれば、半導体チップ裏面の外周縁を選択的に除去し、段差を形成することで、実装信頼性の高い半導体装置を安定的に提供することができる。

【発明の効果】

【0019】

本発明によれば、半導体チップの周縁における厚さは、半導体チップの中央部における厚さよりも小さいため、実装信頼性が向上された半導体装置が提供される。

【発明を実施するための最良の形態】

【0020】

以下、本発明の実施の形態について、図面を用いて説明する。尚、すべての図面において、同様な構成要素には同様の符号を付し、適宜説明を省略する。

【0021】

第1の実施の形態

図1は、本実施形態に係る半導体装置10の構造を表わした図で、図1(a)は、半導体装置10を上方から見た平面図であり、図1(b)は、図1(a)のA−A’線における断面図である。

【0022】

半導体装置10は、実装基板2、実装基板2の上面に接して設けられた半田バンプ3、半田バンプ3と接して設けられたLSIチップ1、半田バンプ3を完全に覆うように充填された樹脂材4により構成されており、フリップチップボールグリッドアレイ構造またはベアチップ構造を有する。

【0023】

LSIチップ1は、中央部近傍に設けられた厚さが大きい中央部1aと、LSIチップ1の周縁近傍において、中央部1aよりも前記半導体チップの厚さが小さい領域である厚さが小さい周辺部1bとで構成される。

【0024】

LSIチップ1の厚さは、LSIチップの中央部1aにおいて、700μm程度であり、周辺部1bにおける厚さは、300μm〜400μm程度である。すなわち、LSIチップ1の裏面には、チップの外周縁に沿って段差が設けられており、周辺部1bの厚さの方が、中央部1aの厚さよりも小さい。ここで、周辺部1bの厚さは、研削されることによって、中央部1aの厚さよりも小さくなっている。また、中央部1aの厚さと、周辺部1bの厚さとの差は、200μm〜500μm程度であることが好ましい。厚さの差がこの範囲にあることで、LSIチップ1は、実装基板2の収縮への追随性に比較的優れ、LSI全体の反りが大きくなることを、より効果的に抑制することができる。本実施形態においては、チップ周辺部1bの幅(段差の幅)は、LSIチップ1の端から半田バンプ3の3ピッチ分(約600μm)である。

【0025】

LSIチップ1の周辺部1bは、中央部1aと比較して厚みが小さい。そのため、周辺部1bは撓みやすくなり、実装基板2の伸縮に合わせて、LSIチップ1が追随して伸縮しやすい。そのため、半導体装置10において、周辺部1b直下の半田バンプ3への応力を緩和させることができる。

【0026】

半田バンプ3は、実装基板2の上面およびLSIチップ1の表面(素子形成面)に接するように、グリッドアレイ状に複数個設けられている。半田バンプ3は導電性を有するので、半田バンプ3を介して、LSIチップ1と実装基板2とが電気的および物理的に接続されている。

【0027】

樹脂材4は、半田バンプ3を完全に覆うように充填されており、半田バンプ3の保護材としての機能を有する。

【0028】

図2を用いて、本実施形態に係る半導体装置10の製造プロセスを説明する。

【0029】

まず、図2(a)に示すように、一般的な半導体装置と同様の方法にて、LSIチップ1の電極パッド(不図示)にフラックス3aを印刷し、半田バンプ3をフラックス3aに位置ズレしないように乗せ、リフローを行う。

【0030】

つぎに、図2(b)に示すように、実装基板2の電極パッド(不図示)上にフラックスや予備半田2aを用意し、半田バンプ3を位置ズレしないように予備半田2aに載せて、リフローを行う。これにより、LSIチップ1と実装基板2とは、半田バンプ3を介し、電気的、物理的に接続される。

【0031】

ついで、図2(c)に示すように、樹脂材4を充填し、半田バンプ3を完全に覆うようにする。

【0032】

続いて、図2(d)に示すように、LSIチップ1の裏面の周辺部を選択的に研削する。こうすることにより、図2(e)に示すように、LSIチップ1中央部の研削していない厚い部分である中央部1aと、LSIチップ1周辺部の薄い部分である周辺部1bとを構成することができる。

【0033】

LSIチップ1裏面の研削にはレーザや旋盤などが用いられる。レーザを使用する場合は、LSIチップを300μm〜400μm程度削る。研削の際には、レーザ照射が繰り返し行われたり、レーザのパワー調整がなされる。また、研削幅が所望の幅となるように、レーザの照射領域の調節を行う。旋盤を用いる場合も同様である。

【0034】

以上のプロセスにより、半導体装置10が完成する。

【0035】

以下、本実施形態に係る半導体装置10およびその製造方法の効果について説明する。

【0036】

本実施形態においては、LSIチップ1の周辺部1bの厚さは300〜400μm程度、中央部1aの厚さは700μm程度となっており、中央部1aの厚さと周辺部1bの厚さとを比較すると、周辺部1bの厚さの方が小さい。そのため、相対的に厚さの小さい周辺部1bのチップは、肉厚が小さいので撓みやすくなっている。したがって、たとえば温度降下により、実装基板2が矢印7(図8(b))の方向に収縮し、LSIチップ1と実装基板2とを接続する半田バンプ3において歪が生じても、周辺部1bは実装基板2の収縮に追随して収縮するため、周辺部1bにかかる応力は低減される。

【0037】

ここで、半田バンプ3のうち、中央部1aと接するバンプ3aにおいては、実装基板2の収縮に伴う歪はもともと小さいため、バンプ3aにかかる応力はもともと小さい。そのため、中央部1aにおいては、LSIチップ1を撓ませる必要性が比較的少ない。したがって、本実施形態における半導体装置10においては、LSIチップ1の中央部1aの厚さを相対的に大きくすることで、過度にLSIチップ1を撓ませることなく、半導体装置10が過度に反らないようにできる。

【0038】

特許文献1記載の半導体装置においては、LSIチップのコーナー部近傍において、半田バンプの応力低減効果が減少することがあった。なぜなら、LSIチップ表面に格子状に溝が形成されているが、格子状に形成された溝は、LSIチップの対角線方向にかかる応力の方向に対し最大45度の傾きを有しているからである。そこで、本実施形態においては、半田バンプ3への応力低減が比較的求められる箇所であるLSIチップ1の周辺部1bを薄くすることで、実装基板2の伸縮に対してLSIチップ1を、より効果的に追随させている。そのため、LSIチップ1の強度を損なわずに、半田バンプ3への応力緩和をより効率的に図るという利点が得られる。

【0039】

また、樹脂材4が半田バンプ3を完全に覆うように設けられているため、半田バンプ3が衝撃を受けることを抑制することができる。そのため、半田バンプ3の信頼性を向上させることができる。

【0040】

また、LSIチップ1の周辺部1bをレーザや旋盤を用いて選択的に研削することで、実装基板2の収縮への追随性に優れ、LSIチップ1が過度に反らない半導体装置10を安定的に製造することができる。

【0041】

第2の実施の形態

図3に、本実施形態に係る半導体装置20を示す。半導体装置20は、中央部21aの部分の形状が異なる以外は、第1の実施の形態で説明した半導体装置10と同じ構造を有する。

【0042】

図3(a)は、本実施形態に係る半導体装置20を上方から見た平面図で、図3(b)は、図3(a)のA−A’線における断面図である。LSIチップ21の中央部21aの部分を円形に残す。

【0043】

以下の製造プロセスにより半導体装置20を製造する。

【0044】

まず、第1の実施形態と同様、LSIチップ21と実装基板22とを、一般的な実装技術により半田バンプ23を介して電気的、物理的に接続を行う。次に、半田バンプ23を完全に覆うように樹脂材24を充填する。ついで、半導体チップ21から樹脂材24までにより構成される半導体装置を回転ステージに乗せ、第1の実施形態と同様に、レーザや旋盤を用いてLSIチップ21の周辺部を研削し、中央部の厚い領域である中央部21aと周辺部の薄い領域である周辺部21bとを構成する。LSIチップ21の中央部21aの部分が円形であることによって、LSIチップ21のコーナー部における半田バンプ23への応力低減効果を、より効果的に大きくすることができる。なぜなら、矩形である場合と比較して、中央部21aの角部とLSIチップ21のコーナー部との距離が大きくなるため、コーナー部において、肉厚の薄い領域である周辺部21bが占める領域の面積が、より増大するからである。

【0045】

以上のプロセスにより半導体装置20が完成する。

【0046】

なお、中央部21aの上方から見た平面形状は、たとえば多角形などの円形以外の形状であっても、コーナー部において、肉厚の薄い領域である周辺部が占める領域の面積が増大し、コーナー部における半田バンプへの応力低減効果が、より効果的に大きくなる形状であればよい。

【0047】

第3の実施の形態

図4に、本実施形態に係る半導体装置30の構造を示す。半導体装置30は、周辺部の肉厚が薄い部分である周辺部31bの形状が異なる以外は、第1の実施の形態で説明した半導体装置10と同じ構造を有する。

【0048】

図4(a)は、半導体装置30を上方から見た平面図であり、図4(b)は、図4(a)のA−A’線における断面図である。

【0049】

半導体装置30の周辺部31bの厚さは、中央部31aに近づくにつれて大きくなる。すなわち、周辺部31bの厚さが、LSIチップ31の中央部方向へ向けて漸増する領域を有する。ここで、厚さが大きくなる領域において、周辺部31bの表面は傾斜を有しており、斜面に丸みを含んでいてもよい。

【0050】

以下の製造プロセスにより半導体装置30を製造する。

【0051】

まず、第1の実施の形態および第2の実施の形態と同様、LSIチップ31と実装基板32とを半田バンプ33を介して接続し、樹脂材34を充填する。次に、LSIチップ31の周辺部を研削し、中央部の厚い部分である中央部31aと周辺部の薄い部分である周辺部31bとを構成する。この際、中央部31aと周辺部31bとの間に傾斜を有しており、また、斜面に丸みが設けられている。傾斜や丸みを設ける方法としては、LSIチップ31研削時に側面に丸みや傾斜を帯びた旋盤35などが用いられる。

【0052】

以上のプロセスにより、半導体装置30が完成する。

【0053】

本実施形態に係る半導体装置30の効果を以下に説明する。

【0054】

LSIチップ31は、中央部31aと周辺部31bとの間に、傾斜を有しており、また、斜面に丸みを有している。そのため、LSIチップ31の裏面における応力勾配を和らげることが出来る。したがって、LSIチップ31が、実装基板32の収縮に追随して収縮するため、周辺部31bにかかる応力が低減される。

【実施例】

【0055】

図7および図8に示す半導体装置のそれぞれについて、図9および図10に、温度を100℃から0℃に降下させた場合の、実装基板およびLSIチップの収縮、応力、および反りのシミュレーション結果を示す。図9(a)において、実装基板42上に設けられたLSIチップ41の中央部41aの厚さは700μm、周辺部41bの厚さは400μmである。図9(b)において、溝48の幅は200μmであり、溝とその隣の溝との間隔は1000μmである。図9(c)における、図9(c)の上方向を正の方向とするA’点における反りの数値、図9(c)の左方向を正の方向とするB点およびC点における応力の数値を図10に示した。なお、図7および図8中の矢印6、56、106、206は、それぞれLSIチップ1、LSIチップ51、LSIチップ101、LSIチップ201の収縮方向を表す。また、矢印7、57、107、207は、それぞれ実装基板2、実装基板52、実装基板102、実装基板202の収縮方向を表わす。ここで、矢印の長さはそれぞれの収縮の度合いをイメージしている。また、図7(c)の矢印59は、実装基板52の主な収縮および応力の方向を表わす。

【0056】

実施例1

第1の実施の形態と同様のプロセスで製造された、図8(b)に示すLSIチップ1の周辺部1bの厚さが中央部1aの厚さよりも小さい半導体装置においては、LSI全体を必要以上に反らせることなく、最外周半田バンプ3dにおける応力を低減することができることがわかった。

【0057】

比較例1

図7(a)に示す従来の半導体装置においては、LSIチップ201が実装基板202の収縮に追随しにくいため、最外周半田バンプ203dにおける応力が大きくなることがわかった。

【0058】

比較例2

図7(b)に示す従来の半導体装置(特許文献1記載)においては、LSIチップ51は実装基板52の収縮にある程度追随する。そのため、特に最外周半田バンプ53dにおける応力は、ある程度緩和される。しかし、その効果は比較的大きくないことがわかった。また、LSI全体の反りが、やや大きくなることがわかった。

【0059】

比較例3

図8(a)に示す従来の半導体装置(特許文献2記載)においては、LSIチップ101全体が実装基板102に追随しやすいため、特に最外周半田バンプ103dでの応力は低減されることがわかった。しかし、LSI全体の反りが大きくなることがわかった。

【0060】

以上の実施例および比較例より、LSIチップの周縁部の厚さを中央部の厚さよりも小さくすることで、LSI全体を必要以上に反らせることなく、最外周半田バンプにおける応力を低減できることがわかった。

【0061】

以上、図面を参照して本発明の実施形態について述べたが、これらは本発明の例示であり、上記以外の様々な構成を採用することもできる。

【0062】

たとえば、LSIチップ裏面の外周縁に沿った段差は、実装基板の収縮への追随性に比較的優れ、LSI全体の反りが大きくならない程度の幅を有していればよく、LSIチップの外端から、LSIチップに設けられた半田バンプのうち最外周のバンプの内側を通り、実装基板と略垂直な面と実装基板の裏面との交点までの距離が300μm以上であり、かつ、チップサイズの1/4以下であれば、なおよい。

【0063】

また、上記実施形態において、中央部1aの厚さと周辺部1bの厚さとの差が200μm〜500μmである形態について説明したが、実装基板の収縮への追随性に比較的優れ、LSI全体の反りが大きくならない程度の差であればよい。

【図面の簡単な説明】

【0064】

【図1】実施の形態に係る半導体装置の構造を模式的に示した図である。

【図2】実施の形態に係る半導体装置の製造工程を模式的に示した工程断面図である。

【図3】実施の形態に係る半導体装置の構造を模式的に示した図である。

【図4】実施の形態に係る半導体装置の構造を模式的に示した図である。

【図5】従来の半導体装置の構造を模式的に示した概略図である。

【図6】従来の半導体装置の構造を模式的に示した概略図である。

【図7】従来の技術に係る半導体装置を対比した図である。

【図8】従来の半導体装置と実施の形態に係る半導体装置を対比した図である。

【図9】従来の半導体装置と実施の形態に係る半導体装置のそれぞれにおける応力シミュレーションモデルを説明する図である。

【図10】従来の半導体装置と実施の形態に係る半導体装置のそれぞれにおける応力シミュレーションモデルの結果を説明する図である。

【符号の説明】

【0065】

1 LSIチップ

1a 中央部

1b 周辺部

2 実装基板

3 半田バンプ

4 樹脂材

5 旋盤又はレーザ

6 LSIチップ1の収縮方向

7 実装基板2の収縮方向

21 LSIチップ

21a 中央部

21b 周辺部

31 LSIチップ

31a 中央部

31b 周辺部

41 LSIチップ

41a 中央部

41b 周辺部

42 実装基板

48 溝

51 LSIチップ

52 実装基板

53 半田バンプ

54 樹脂材

56 LSIチップ51の収縮方向

57 実装基板52の収縮方向

58 溝

59 応力(収縮)の方向

101 LSIチップ

102 実装基板

103 半田バンプ

104 樹脂材

106 LSIチップ101の収縮方向

107 実装基板102の収縮方向

201 LSIチップ

202 実装基板

203 半田バンプ

206 LSIチップ201の収縮方向

207 実装基板202の収縮方向

【特許請求の範囲】

【請求項1】

基板と、複数のバンプと、半導体チップとがこの順に積層された半導体装置であって、

前記複数のバンプのそれぞれの上端面と前記半導体チップ素子形成面とが接触し、

前記半導体チップの周縁における厚さは、前記半導体チップの中央部における厚さよりも小さいことを特徴とする半導体装置。

【請求項2】

請求項1に記載の半導体装置において、

前記周縁近傍において、前記中央部の厚さよりも前記半導体チップの厚さが小さい領域を有することを特徴とする半導体装置。

【請求項3】

請求項2に記載の半導体装置において、

前記領域の幅をc(μm)、前記複数のバンプのうち最も外に設けられたバンプの内端を通り前記基板と略直角に交わる面と前記基板の裏面とが交わる線と前記半導体チップの端部とを結ぶ線の長さをa(μm)、前記半導体チップの一辺の長さをb(μm)としたときに、a≦c≦b/4である関係を満たすことを特徴とする半導体装置。

【請求項4】

請求項2または3に記載の半導体装置において、

前記領域における厚さと前記中央部における厚さとの差は、200μm以上500μm以下であることを特徴とする半導体装置。

【請求項5】

請求項2乃至4いずれかに記載の半導体装置において、

前記領域における厚さが、前記半導体チップの中央部方向へ向けて漸増する領域を有することを特徴とする半導体装置。

【請求項6】

請求項1乃至5いずれかに記載の半導体装置において、

前記複数のバンプを覆うように、前記基板上面と前記半導体チップ素子形成面との間に樹脂が備えられることを特徴とする半導体装置。

【請求項7】

基板と半導体チップとを用意する工程と、

前記半導体チップ表面に複数のバンプを設ける工程と、

前記基板上面と前記半導体チップの前記複数のバンプが形成された面とが接するように前記基板上に前記半導体チップを設ける工程と、

前記半導体チップ裏面の外周縁を選択的に除去し、段差を形成する工程と、

を含むことを特徴とする半導体装置の製造方法。

【請求項1】

基板と、複数のバンプと、半導体チップとがこの順に積層された半導体装置であって、

前記複数のバンプのそれぞれの上端面と前記半導体チップ素子形成面とが接触し、

前記半導体チップの周縁における厚さは、前記半導体チップの中央部における厚さよりも小さいことを特徴とする半導体装置。

【請求項2】

請求項1に記載の半導体装置において、

前記周縁近傍において、前記中央部の厚さよりも前記半導体チップの厚さが小さい領域を有することを特徴とする半導体装置。

【請求項3】

請求項2に記載の半導体装置において、

前記領域の幅をc(μm)、前記複数のバンプのうち最も外に設けられたバンプの内端を通り前記基板と略直角に交わる面と前記基板の裏面とが交わる線と前記半導体チップの端部とを結ぶ線の長さをa(μm)、前記半導体チップの一辺の長さをb(μm)としたときに、a≦c≦b/4である関係を満たすことを特徴とする半導体装置。

【請求項4】

請求項2または3に記載の半導体装置において、

前記領域における厚さと前記中央部における厚さとの差は、200μm以上500μm以下であることを特徴とする半導体装置。

【請求項5】

請求項2乃至4いずれかに記載の半導体装置において、

前記領域における厚さが、前記半導体チップの中央部方向へ向けて漸増する領域を有することを特徴とする半導体装置。

【請求項6】

請求項1乃至5いずれかに記載の半導体装置において、

前記複数のバンプを覆うように、前記基板上面と前記半導体チップ素子形成面との間に樹脂が備えられることを特徴とする半導体装置。

【請求項7】

基板と半導体チップとを用意する工程と、

前記半導体チップ表面に複数のバンプを設ける工程と、

前記基板上面と前記半導体チップの前記複数のバンプが形成された面とが接するように前記基板上に前記半導体チップを設ける工程と、

前記半導体チップ裏面の外周縁を選択的に除去し、段差を形成する工程と、

を含むことを特徴とする半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【公開番号】特開2006−73843(P2006−73843A)

【公開日】平成18年3月16日(2006.3.16)

【国際特許分類】

【出願番号】特願2004−256519(P2004−256519)

【出願日】平成16年9月3日(2004.9.3)

【出願人】(302062931)NECエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

【公開日】平成18年3月16日(2006.3.16)

【国際特許分類】

【出願日】平成16年9月3日(2004.9.3)

【出願人】(302062931)NECエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

[ Back to top ]