半導体装置およびその製造方法

【課題】回路形成領域に電極パッド部を形成したパッドオンエレメント構造を有する半導体素子の被実装基板への実装時に、半導体素子への機械的ダメージの低減化を図り得る半導体装置を提供する。

【解決手段】半導体素子1表面の回路形成領域上に設けられた複数の電極パッド部2と、裏面に複数の接続ランド部3が設けられた半導体キャリア基板4の表面に配置される複数の配線電極部6とが電気的に接続され、且つこれら半導体素子1と半導体キャリア基板4との間に絶縁性樹脂9が充填されてなる半導体装置であって、上記各配線電極部6を凹状に形成するとともに、これら凹状の各配線電極部6と上記各電極パッド部2とを導電性の針状部材7にてそれぞれ接続し、且つこれら各針状部材7と上記各電極パッド部2および各配線電極部6との間に導電性接着剤8を介在させたものである。

【解決手段】半導体素子1表面の回路形成領域上に設けられた複数の電極パッド部2と、裏面に複数の接続ランド部3が設けられた半導体キャリア基板4の表面に配置される複数の配線電極部6とが電気的に接続され、且つこれら半導体素子1と半導体キャリア基板4との間に絶縁性樹脂9が充填されてなる半導体装置であって、上記各配線電極部6を凹状に形成するとともに、これら凹状の各配線電極部6と上記各電極パッド部2とを導電性の針状部材7にてそれぞれ接続し、且つこれら各針状部材7と上記各電極パッド部2および各配線電極部6との間に導電性接着剤8を介在させたものである。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、回路形成領域であるアクティブ領域に電極パッド部を形成したパッドオンエレメント構造(POE構造ともいう)を有する半導体素子を被実装基板に実装させてなる薄型化且つ小型化された半導体装置およびその製造方法に関する。

【背景技術】

【0002】

半導体装置には、回路形成領域に電極パッド部を形成したパッドオンエレメント構造(POE構造ともいう)を有する半導体素子が、フリップチップにより、被実装基板に実装されたものがあり、最近、さらなる薄型化および小型化が望まれている。

【0003】

従来に係るこの種の半導体装置について、図8に基づき説明する。

この半導体装置は、半導体ウエハを切断して個片化された半導体素子51の表面に形成された複数のAlよりなる電極パッド部52にAu等の金属バンプ53を形成し(バンプの平坦化であるレベリングは不要)、そして多層回路実装基板である半導体キャリア基板54の上層面に設けた複数の配線電極部55と、上記半導体素子51上の電極パッド部52に形成したAu等の金属バンプ53とをフリップチップにより接続し、さらにシート形状のエポキシ系樹脂56にて樹脂封止を行うようにしたものである。なお、多層回路実装基板である半導体キャリア基板54の上層面にある複数の配線電極部55と裏面側にある複数の接続ランド部57とは内層ビア58により連結されている。

【0004】

この半導体装置の構成によると、図9に示すように、フリップチップ実装時において、Au等の金属バンプ53が潰れながら半導体素子51と半導体キャリア基板54とが電気的に接続されるフリップチップ実装構造であり、このため、半導体素子51に形成されたTr部51aへの悪影響が懸念され、Tr特性変動や層間膜51bへのクラック61が発生する惧れを有するものであった。

【0005】

ところで、上記問題点を解決し得るものとして、下記に示すような半導体装置がある。

この半導体装置は、図10に示すように、半導体ウエハを切断して個片化された半導体素子51の表面に形成された複数のAlよりなる電極パッド部52にAu等の金属バンプ53を形成し(バンプの平坦化であるレベリングは不要)、次に金属バンプ53をレベリングさせるとともに、導電性接着剤62を介して、この金属バンプ53と、半導体キャリア基板54の上層面に設けた複数の配線電極部55とを電気的に接続した構成にされている。また、半導体素子51と半導体キャリア基板54との隙間には、絶縁性のエポキシ系樹脂56が充填被覆された構造で接続部周辺をサージ破壊等から防止した構造にされている。なお、半導体キャリア基板54の上層面にある複数の配線電極部55と裏面側にある複数の接続ランド部57とは内層ビア58で連結されている。

【0006】

しかしながら、この構成によると、半導体素子51に形成されたTr部51aへの悪影響や層間膜51bへのクラック61等の発生は防止できるが、導電性接着剤62による隣接する電極パッド部間のショートによる不良の発生や接続部のオープンによる不良が発生する。また、組立工程で良品であったが信頼性試験を施すと接続不良が発生する場合もある。

【特許文献1】特開平8−167630号公報

【発明の開示】

【発明が解決しようとする課題】

【0007】

すなわち、従来の半導体装置の構成によると、半導体素子における電極パッド部直下への機械的なダメージの低減化と、電極パッド部の狭ピッチ化の実現およびその接続信頼性向上の両者を満足することができないという問題があり、さらには、多ピン化の要望に対する半導体素子の熱的破壊による不具合を防止するため、高放熱構造の実現化が必要とされている。

【0008】

そこで、本発明は、回路形成領域に電極パッド部を形成したパッドオンエレメント構造を有する半導体素子の被実装基板への実装時に、半導体素子への機械的ダメージの低減化を図り得るとともに、半導体素子における電極パッド部の狭ピッチ化、および実装時における接続部での信頼性の向上を図り得る半導体装置およびその製造方法を提供することを目的とする。

【課題を解決するための手段】

【0009】

上記課題を解決するため、本発明の請求項1に係る半導体装置は、半導体素子の回路形成領域の表面に設けられた複数の電極パッド部と、裏面に接続ランド部が設けられた被実装基板の表面に配置される複数の配線電極部とが電気的に接続され、且つこれら半導体素子と被実装基板との間に絶縁性樹脂が充填されてなる半導体装置であって、

上記各配線電極部を凹状に形成するとともに、これら各凹状の配線電極部と上記各電極パッド部とを導電性の針状部材にてそれぞれ接続し、

且つこれら各針状部材と上記各電極パッド部および各配線電極部との間に、それぞれ導電性接着剤を介在させたものである。

【0010】

また、請求項2に係る半導体装置は、請求項1に記載の半導体装置における凹状の配線電極部を、円筒形状または逆円錐形状に形成したものである。

また、請求項3に係る半導体装置は、半導体素子の回路形成領域の表面に設けられた複数の電極パッド部と、裏面に接続ランド部が設けられた被実装基板の表面に配置される複数の配線電極部とが電気的に接続されてなる半導体装置であって、

上記配線電極部が配置される被実装基板の表面に、周壁部より低くされた凹状空間部を形成するとともに、この凹状空間部内に上記半導体素子が配置された状態の各電極パッド部と当該凹状空間部の表面側に配置された各配線電極部とを導電性の針状部材にてそれぞれ接続し、

且つこれら各針状部材と上記各電極パッド部および各配線電極部との間に、それぞれ導電性接着剤を介在させたものである。

【0011】

また、請求項4に係る半導体装置は、請求項1乃至3のいずれか一項に記載の半導体装置における針状部材の太さを、数ミクロン〜数十ミクロンの範囲にするとともに、当該針状部材をCuまたはAlにて形成したものである。

【0012】

また、請求項5に係る半導体装置は、請求項1乃至4のいずれか一項に記載の半導体装置における針状部材により接続された電極パッド部が、回路形成領域の内、能動素子が形成された能動素子部領域および/または入出力セルが形成された入出力部領域に設けられたものである。

【0013】

また、本発明の請求項6に係る半導体装置の製造方法は、請求項1または2に記載の半導体装置の製造方法であって、

半導体素子表面に設けられた複数の電極パッド部に対応する位置で、保持具によりそれぞれ保持された導電性の各針状部材の一端側に、導電性接着剤を付着させる工程と、

上記各針状部材に付着された導電性接着剤を半導体素子の各電極パッド部に接触させた後、熱により硬化させる工程と、

裏面に複数の接続ランド部が形成されるとともに表面側に当該各接続ランド部にビアを介して接続された複数の凹状の配線電極部が形成されてなる被実装基板の各配線電極部内に導電性接着剤を付着させる工程と、

上記半導体素子に接続された各針状部材の他端部を上記各配線電極部内に挿入して付着された導電性接着剤に接触させた後、熱により硬化させる工程と、

上記針状部材により半導体素子と被実装基板とが接続された後、これら半導体素子と被実装基板との間に絶縁性樹脂を配置して樹脂封止する工程とを具備した方法である。

【0014】

また、請求項7に係る半導体装置の製造方法は、請求項1または2に記載の半導体装置の製造方法であって、

半導体素子表面に設けられた複数の電極パッド部に対応する位置で、保持具によりそれぞれ保持された導電性の各針状部材の一端側に、導電性接着剤を付着させる工程と、

上記各針状部材に付着された導電性接着剤を半導体素子の各電極パッド部に接触させた後、熱により硬化させる工程と、

上記一端側が半導体素子の各電極パッド部に接続された各針状部材の他端側に、導電性接着剤を付着させる工程と、

裏面に複数の接続ランド部が形成されるとともに表面側に上記各接続ランド部にビアを介して接続された複数の凹状の配線電極部が形成されてなる被実装基板の各配線電極部内に、導電性接着剤が付着された各針状部材の他端側を挿入した後、熱により硬化させる工程と、

上記各針状部材により半導体素子と被実装基板とが接続された後、これら半導体素子と被実装基板との間に絶縁性樹脂を配置して樹脂封止する工程とを具備した方法である。

【0015】

さらに、請求項8に係る半導体装置の製造方法は、請求項3に記載の半導体装置の製造方法であって、

半導体素子表面に設けられた複数の電極パッド部に対応する位置で、保持具によりそれぞれ保持された導電性の各針状部材の一端側に、導電性接着剤を付着させる工程と、

裏面に複数の接続ランド部が形成されるとともに表面側に形成された凹状空間部の内側表面に配置され且つ上記各接続ランド部にビアを介して接続された複数の配線電極部を有する被実装基板の上記凹状空間部内に、上記導電性接着剤が付着された各針状部材の一端側を挿入して各配線電極部に接触させて、これら各導電性接着剤を熱により硬化させる工程と、

上記一端側が被実装基板の各配線電極部に接続された各針状部材の他端側に、導電性接着剤を付着させる工程と、

上記導電性接着剤が付着された各針状部材の他端側に半導体素子を、各電極パッド部が各針状部材に接触するように凹状空間部内に配置して仮固定させる工程と、

上記半導体素子が凹状空間部内に仮固定した状態で、当該凹状空間部内の隙間に絶縁性樹脂を充填した後、熱により硬化させて樹脂封止する工程とを具備した方法である。

【発明の効果】

【0016】

上述の半導体装置およびその製造方法によると、半導体素子側の電極パッド部と被実装基板側の配線電極部とを電気的に接続する際に、配線電極部を凹状に形成しまたは凹状空間部に配線電極部を形成するとともに、この配線電極部と電極パッド部とを導電性の針状部材により接続するようにしたので、例えばバンプを用いた加圧方式とは異なり、たとえ接続するために押圧力を付加した場合でも、針状部材が変形して押圧力が吸収されるため、半導体素子側には殆ど力が作用することがなく、したがって実装時に、半導体素子に機械的なダメージが与えられることがないとともに、デバイス特性に悪影響を与える惧れもなくなる。

【0017】

また、半導体素子と被実装基板とを接続する際に、針状部材を凹状の配線電極部に挿入することになるため、やはり、バンプを加圧する場合に比べて、位置ずれが発生するのを防止することができ、延いては、位置ずれによる生産歩留りの低下を防止して製造コストの低減化を図ることができる。なお、半導体素子を凹状空間部内に位置させる場合も、両者の位置ずれの発生を防止することができる。

【0018】

また、被実装基板に設けられる配線電極部を凹状に形成しているため、または配線電極部を凹状空間部内に配置しているため、その凹み量に応じて、半導体装置をさらに薄型化することができる。

【0019】

また、針状部材と凹状の配線電極部とにより、位置決め精度のよい接続を行うことができるので、半導体素子に強く要望されている多ピン化技術の進展に伴うパッドオンエレメント構造における電極パッド部の狭ピッチ化、すなわち半導体素子の小型化を図ることができる。

【0020】

このようなことから、次世代プロセスを用いたパッドオンエリア構造でのフリップチップ実装を、容易に行うことができる。

さらに、導電性の針状部材として放熱性が良好なCuまたはAlを用いることにより、回路形成領域上に設けられた電極パッド部からの発熱を格子状に放熱することができ、したがって放熱性が優れた放熱構造を具備させることができる。これにより、多ピン化した半導体装置における半導体素子の熱的破壊を防止することができる。

【発明を実施するための最良の形態】

【0021】

以下、本発明の実施の形態に係る半導体装置およびその製造方法について説明する。

勿論、以下の実施の形態で説明する半導体装置は、半導体素子における回路形成領域(アクティブ領域)の能動素子部領域および入出力部領域(I/Oセル領域)上に電極パッド部が形成されて(パッドオンエレメント構造)、小型化および薄型化が図られたものである。

[実施の形態1]

以下、本発明の実施の形態1に係る半導体装置およびその製造方法を、図1および図2に基づき説明する。

【0022】

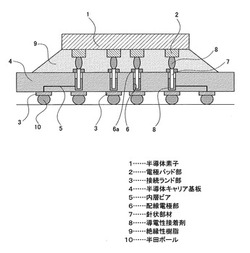

まず、半導体装置の概略構成を図1に基づき説明する。

図1は半導体装置の断面を示す模式図である。

この半導体装置は、半導体素子1の回路形成領域(具体的には、能動素子部領域および入出力部領域)の表面に形成された複数の電極パッド部2と、裏面に複数の接続ランド部3が設けられた被実装基板である半導体キャリア基板4の表面に形成されるとともに上記各接続ランド部3に内層ビア5を介して電気的に接続された複数の凹状の配線電極部6とが導電性の針状部材7を介してそれぞれ接続(所謂、フリップチップ接続である)されたものである。

【0023】

上記各凹状の配線電極部6の本体部分は半導体キャリア基板4に円筒形状(コップ形状)として凹んだ状態で形成されているが、表面側における回路パターンの接続用として、表面部分6aについては、そのまま残されている。勿論、本体部分と表面部分については電気的に接続されており、また表面部分の中央を貫通して形成されている。したがって、以下において配線電極部6と称した場合、凹んだ本体部分を示しているものとして説明する。なお、場合によっては、表面部分と異なる箇所に、本体部分が形成されることもある(この場合、本体部分を形成する際には表面部分が貫通されることはないが、表面部分と本体部分とは電気的に接続されることになる)。

【0024】

また、上記針状部材7としては、Cu(Alでもよい)が用いられるとともに、微細で且つ剛性を有するように形成されており、例えばその太さは、数ミクロン〜数十ミクロンの範囲にされている。

【0025】

また、上記針状部材7と電極パッド部2との接続、および針状部材7と配線電極部6との接続には、熱硬化性の導電性接着剤8が用いられる(言い換えれば、各針状部材7と各電極パッド部2および各配線電極部6との間に、それぞれ導電性接着剤8が介在されている)。

【0026】

さらに、半導体キャリア基板4に半導体素子1が実装された後は、両者の間およびその周辺部に、絶縁性樹脂であるエポキシ系樹脂9が充填されて樹脂封止が行われる。なお、各接続ランド部3には、それぞれ半田ボール10が接続される。

【0027】

次に、上記半導体装置の製造方法を、図2に基づき、工程形式で説明する。

この製造方法は、図2(a)および(b)に示すように、半導体素子1の表面に形成された複数の電極パッド部2に対応する位置で(つまり、同じ座標位置および同じ個数でもって)導電性の針状部材7がそれぞれ鉛直方向で吊持された(収納した)ツールボックス(保持具)21を、導電性接着剤8が塗布された転写台22の表面に降下・接触させて、各針状部材7の一端部に導電性接着剤8を転写塗布させる工程と、図2(c)および(d)に示すように、導電性接着剤8が転写塗布された複数の針状部材7をツールボックス21でもって半導体素子1上に且つ複数の電極パッド部2に対応する位置に移動させ、そして降下し接触させた後、熱風等により硬化させる工程と、図2(d)および(e)に示すように、熱硬化させた後、ツールボックス21で固定していた各針状部材7の一端を開放(解除)させた後、これら針状部材7が接続された半導体素子1を反転させた後、半導体キャリア基板4の表面に形成されるとともに内面に導電性接着剤8が塗布された(別工程で塗布される)複数の凹状の配線電極部6内に、それぞれ針状部材7を挿入する工程と、図2(f)に示すように、各配線電極部6内の導電性接着剤8を熱処理にて仮硬化させた後、両者の間およびその周縁部に絶縁性を有するエポキシ系樹脂9を充填し熱硬化(同時に導電性接着剤の本硬化も行われる)させる工程とを具備したものである。なお、半導体素子1を半導体キャリア基板4に接続する際に、針状部材7に殆ど押圧力が付加されることはない。

【0028】

図2(g)に、半導体素子1表面の電極パッド部2の配置状態を示しておく。この図では、内側の能動素子部領域に2個、外周の入出力部領域に16個配置されている。勿論、これは例示である。

【0029】

なお、配線電極部6内の導電性接着剤8と針状部材7との仮硬化を行わずに、エポキシ系樹脂9の硬化と同時に、硬化させるようにしてもよい。

この半導体装置およびその製造方法によると、半導体素子側の電極パッド部と半導体キャリア基板側の配線電極部とを電気的に接続する際に、配線電極部を凹状に形成するとともに、この凹状の配線電極部と電極パッド部とを導電性の針状部材により接続するようにしたので、例えばバンプを用いた加圧方式とは異なり、たとえ接続するために押圧力を付加した場合でも、針状部材が変形して押圧力が吸収されるため、半導体素子側には殆ど力が作用することがなく、したがって実装時に、半導体素子に機械的なダメージが与えられることがないとともに、デバイス特性に悪影響を与える惧れもなくなる。

【0030】

また、半導体素子と半導体キャリア基板とを接続する際に、針状部材を凹状の配線電極部に挿入することになるため、やはり、バンプを加圧する場合に比べて、位置ずれが発生するのを防止することができ、延いては、位置ずれによる生産歩留りの低下を防止して製造コストの低減化を図ることができる。

【0031】

また、半導体キャリア基板に設けられる配線電極部を凹状に形成しているため、その凹み量に応じて、半導体装置をさらに薄型化することができる。

また、針状部材と凹状の配線電極部とによる位置決め精度がよい接続を行うことができるので、半導体素子に強く要望されている多ピン化技術の進展に伴うパッドオンエレメント構造における電極パッド部の狭ピッチ化、すなわち半導体素子の小型化を図ることができる。

【0032】

このようなことから、次世代プロセスを用いたパッドオンエリア構造でのフリップチップ実装を、容易に行うことができる。

また、針状部材の形状や寸法等については、適宜、変更することが可能であり、例えば針状部材と導電性接着剤との接続抵抗を小さくすることにより、電気的接続性能を向上させて、接続部での信頼性のさらなる向上を図ることができる。

【0033】

また、導電性の針状部材として放熱性が良好なCu(またはAl)を用いることにより、回路形成領域上に設けられた電極パッド部からの熱を格子状に放熱することができ(つまり、針状部材が格子状に配置されているので、半導体素子からの発熱を基板側に逃がしやすくなる)、したがって放熱性が優れた放熱構造を具備させることができる。これにより、多ピン化した半導体装置における半導体素子の熱的破壊を防止することができる。

【0034】

さらに、導電性の針状部材として、Cu(またはAl)を用いるとともに、この針状部材に導電性接着剤を転写させて接続する方式を用いているので、既存設備および既存材料を利用することができ、延いては、製造コストの低減化に繋がることになる。

[実施の形態2]

以下、本発明の実施の形態2に係る半導体装置およびその製造方法を、図3および図4に基づき説明する。

【0035】

なお、上記実施の形態1にて説明したものと異なる箇所は、凹状の配線電極部の形状であり、上記実施の形態1で説明したものと同一の構成部材については、同一の部材番号を付して説明する。

【0036】

まず、半導体装置の概略構成を図3に基づき説明する。

図3は半導体装置の断面を示す模式図である。

この半導体装置は、半導体素子1の表面に配置された複数の電極パッド部2と、裏面に複数の接続ランド部3が設けられた被実装基板である半導体キャリア基板4の表面に形成されるとともに上記各接続ランド部3に内層ビア5を介して電気的に接続された複数の凹状の配線電極部6とが導電性の針状部材7を介してそれぞれ接続(所謂、フリップチップ接続である)されたものである。

【0037】

上記各凹状の配線電極部6の本体部分は半導体キャリア基板4に逆円錐形状(コーン形状)として凹んだ状態で形成されているが、表面側における回路パターンの接続用として、表面部分6aについては、そのまま残されている。勿論、本体部分と表面部分については電気的に接続されており、また表面部分の中央を貫通して形成されている。したがって、以下において配線電極部6と称した場合、凹んだ本体部分を示しているものとして説明する。なお、場合によっては、表面部分と異なる箇所に、本体部分が形成されることもある(この場合、本体部分を形成する際には表面部分が貫通されることはないが、表面部分と本体部分とは電気的に接続されることになる)。

【0038】

また、上記針状部材7としては、Cu(Alでもよい)が用いられるとともに、微細で且つ剛性を有するように形成されており、例えばその太さは、数ミクロン〜数十ミクロンの範囲にされている。

【0039】

また、上記針状部材7と電極パッド部2との接続、および針状部材7と配線電極部6との接続には、熱硬化性の導電性接着剤8が用いられる(言い換えれば、各針状部材7と各電極パッド部2および各配線電極部6との間に、それぞれ導電性接着剤8が介在されている)。

【0040】

さらに、半導体キャリア基板4に半導体素子1が実装された後は、両者の間およびその周辺部に、絶縁性樹脂であるエポキシ系樹脂9が充填されて樹脂封止が行われる。なお、各接続ランド部3には、それぞれ半田ボール10が接続される。

【0041】

次に、上記半導体装置の製造方法を、図4に基づき、工程形式で説明する。

この製造方法は、図4(a)および(b)に示すように、半導体素子1の表面に形成された複数の電極パッド部2に対応する位置で(つまり、同じ座標位置および同じ個数でもって)導電性の針状部材7がそれぞれ鉛直方向で吊持された(収納した)ツールボックス(保持具)21を、導電性接着剤8が塗布された転写台22の表面に降下・接触させて、各針状部材7の一端部に導電性接着剤8を転写塗布させる工程と、図4(c)および(d)に示すように、導電性接着剤8が転写塗布された複数の針状部材7をツールボックス21でもって半導体素子1上に且つ複数の電極パッド部2に対応する位置に移動させ、そして降下し接触させた後、熱風等により硬化させる工程と、図4(d)および(e)に示すように、熱硬化させた後、ツールボックス21で固定していた各針状部材7の一端を開放(解除)させた後、これら針状部材7が接続された半導体素子1を反転させた後、半導体キャリア基板4の表面に形成されるとともに内面に導電性接着剤8が塗布された(別工程で塗布される)複数の凹状の配線電極部6内に、針状部材7を挿入する工程と、図4(f)に示すように、各配線電極部6内の導電性接着剤8を熱処理にて仮硬化させた後、両者の間およびその周縁部に絶縁性を有するエポキシ系樹脂9を充填し熱硬化(同時に導電性接着剤の本硬化も行われる)させる工程とを具備したものである。なお、半導体素子1を半導体キャリア基板4に接続する際に、針状部材7に殆ど押圧力が付加されることはない。

【0042】

図4(g)に、半導体素子1表面の電極パッド部2の配置状態を示しておく。この図では、内側の能動素子部領域に2個、外周の入出力部領域に16個配置されている。勿論、これは例示である。

【0043】

なお、配線電極部6内の導電性接着剤8と針状部材7との仮硬化を行わずに、エポキシ系樹脂9の硬化と同時に、硬化させるようにしてもよい。

この半導体装置およびその製造方法によると、実施の形態1で説明したものと同一の効果を有している。

【0044】

さらに、本実施の形態2に係るものにおいては、凹状の配線電極部6の形状が逆円錐形状にされているため、実施の形態1で示した円筒形状のものよりも、針状部材7の半導体キャリア基板4に対する位置決めを正確に行うことができる。

[実施の形態3]

以下、本発明の実施の形態3に係る半導体装置およびその製造方法を、図5および図6に基づき説明する。

【0045】

なお、上記実施の形態1にて説明したものと異なる箇所は、半導体キャリア基板の表面に形成される配線電極部の部分であり、上記実施の形態1で説明したものと同一の構成部材については、同一の部材番号を付して説明する。

【0046】

まず、半導体装置の概略構成を図5に基づき説明する。

図5は半導体装置の断面を示す模式図である。

この半導体装置は、半導体素子1の表面に形成された複数の電極パッド部2と、裏面に複数の接続ランド部3が設けられた被実装基板である半導体キャリア基板4の表面に形成された凹状空間部[中央部分が薄くされるとともにその全周囲に壁状部(周壁部)が配置された、すなわち当該壁状部の内側に形成された凹状の空間室である]11の内側表面に配置されて上記各接続ランド部3に内層ビア5を介して電気的に接続された複数の配線電極部6とがそれぞれ導電性の針状部材7を介して接続(所謂、フリップチップ接続である)されたものである。

【0047】

また、上記針状部材7としては、Cu(またはAl)が用いられるとともに、微細で且つ剛性を有するように形成されており、例えばその太さは、数ミクロン〜数十ミクロンの範囲にされている。

【0048】

また、上記針状部材7と電極パッド部2との接続、および針状部材7と配線電極部6との接続には、熱硬化性の導電性接着剤8が用いられる(言い換えれば、各針状部材7と各電極パッド部2および各配線電極部6との間に、それぞれ導電性接着剤8が介在されている)。

【0049】

さらに、半導体キャリア基板4に半導体素子1が実装された後は、両者の間、すなわち当該半導体キャリア基板4の凹状空間部11内に、エポキシ系樹脂材9が充填されて樹脂封止が行われる。なお、各接続ランド部3には、それぞれ半田ボール10が接続される。

【0050】

次に、上記半導体装置の製造方法を、図6に基づき、工程形式で説明する。

この製造方法は、図6(a)および(b)に示すように、半導体素子1の表面に形成された複数の電極パッド部2に対応する位置で(つまり、同じ座標位置および同じ個数でもって)導電性の針状部材7がそれぞれ鉛直方向で吊持された(収納した)ツールボックス(保持具)21を、導電性接着剤8が塗布された転写台22の表面に降下・接触させて、各針状部材7の一端部に導電性接着剤8を転写塗布させる工程と、図6(c)および(d)に示すように、導電性接着剤8が転写塗布された複数の針状部材7をツールボックス21でもって凹状空間部11内に且つ複数の配線電極部6に対応する位置に移動させ、そして降下させて接触させた後、熱風等により硬化させる工程と、図6(d)および(e)に示すように、熱硬化させた後、ツールボックス21で固定していた各針状部材7の他端を開放(解除)させた後、これら各他端部に導電性接着剤8を転写塗布させ、さらに半導体素子1を、その電極パッド部2が下方となるように反転させて、半導体キャリア基板4の凹状空間部11内に且つ針状部材7上に載置して仮固定(接着剤による)する工程と、図6(f)に示すように、凹状空間部11内の隙間に絶縁性を有するエポキシ系樹脂9を充填した後、当該樹脂9および導電性接着剤8を熱硬化させる工程とを具備したものである。なお、半導体素子1を半導体キャリア基板4に接続する際に、針状部材7に殆ど押圧力が付加されることはない。

【0051】

図6(g)に、半導体素子1表面の電極パッド部2の配置状態を示しておく。この図では、内側の能動素子部領域に3個、外周の入出力部領域に16個配置されている。勿論、これは例示である。

【0052】

この半導体装置およびその製造方法によると、半導体素子1の電極パッド部2と半導体キャリア基板4の配線電極部6とを針状部材7により接続したので、例えばバンプを用いた加圧方式とは異なり、たとえ接続のために力を付加した場合でも、針状部材7が変形して力が吸収されるため、半導体素子側には殆ど力が加わることがなく、したがって実装時に、半導体素子1に機械的なダメージを与えることがないとともに、デバイス特性に悪影響を与える惧れもなくなる。

【0053】

また、半導体素子1を半導体キャリア基板4側に形成された凹状空間部11内に配置するようにしたので、半導体キャリア基板4に対する半導体素子1の位置決め、すなわちフリップチップ接続する際の位置ずれを完全に防止することができ、したがってこれまで課題であった位置ずれによる生産歩留りの低下を防止して、製造コストの低減化を図ることができる。

【0054】

ところで、上記各実施の形態においては、導電性針状部材7として、Cu(またはAl)を用いたが、例えばAu等のバンプを細長く形成したものを用いてもよい。この場合も、通常のバンプを用いることから、すなわち既存材料および既存設備を用いることができるから、殆ど、コストアップに繋がることはない。

【0055】

また、上記各実施の形態においては、導電性の針状部材7として線状のものを説明したが、例えば図7(a)に示すように、長方形状でもよく、図7(b)に示すように、さらに細い長方形状でもよく、図7(c)に示すように、背が高い台形状でもよく[(a)で示したものを、その根元から先端に徐々に細くしたもの]、図7(d)に示すように、(a)で示した長方形状の先端部の角を斜めに切り落とした(細くした)ものでもよく、図7(e)に示すように、(b)で示した細い長方形状の先端部分の幅を広くしてT字形状にしたものでもよく、また図7(f)に示すように、(a)で示した長方形状の両縁部をギザギザ状(稲妻形状)にして表面積を増加させたものでもよい。

【0056】

さらに、上記各実施の形態においては、半導体素子の回路形成領域における能動素子部領域と入出力部領域とに設けられた電極パッド部に適用したが、例えば能動素子部領域または入出力部領域のいずれかに設けられた電極パッド部に適用してもよい。

【産業上の利用可能性】

【0057】

本発明の半導体装置およびその製造方法は、半導体素子の回路形成領域であるアクティブ領域に電極パッド部を設ける際に、半導体素子に機械的なダメージを与えるのを防止することができるとともに、電極パッド部の狭ピッチ化および薄型化を図ることができるので、次世代プロセスを用いたパッドオンエリア構造でのフリップチップ実装を行うのに最適である。

【図面の簡単な説明】

【0058】

【図1】本発明の実施の形態1に係る半導体装置の断面図である。

【図2】同実施の形態1に係る半導体装置の製造方法を説明する工程図で、(a)〜(f)は断面図、(g)は半導体素子の平面図である。

【図3】本発明の実施の形態2に係る半導体装置の断面図である。

【図4】同実施の形態2に係る半導体装置の製造方法を説明する工程図で、(a)〜(f)は断面図、(g)は半導体素子の平面図である。

【図5】本発明の実施の形態3に係る半導体装置の断面図である。

【図6】同実施の形態3に係る半導体装置の製造方法を説明する工程図で、(a)〜(f)は断面図、(g)は半導体素子の平面図である。

【図7】本発明の半導体装置に用いられる針状部材の変形例を示す側面図である。

【図8】従来の半導体装置の構成を示す断面図である。

【図9】従来の半導体装置における不具合の発生状態を示す模式断面図である。

【図10】従来の他の半導体装置の構成を示す断面図である。

【符号の説明】

【0059】

1 半導体素子

2 電極パッド部

3 接続ランド部

4 半導体キャリア基板

5 内層ビア

6 配線電極部

7 針状部材

8 導電性接着剤

9 絶縁性樹脂

10 半田ボール

11 凹状空間部

【技術分野】

【0001】

本発明は、回路形成領域であるアクティブ領域に電極パッド部を形成したパッドオンエレメント構造(POE構造ともいう)を有する半導体素子を被実装基板に実装させてなる薄型化且つ小型化された半導体装置およびその製造方法に関する。

【背景技術】

【0002】

半導体装置には、回路形成領域に電極パッド部を形成したパッドオンエレメント構造(POE構造ともいう)を有する半導体素子が、フリップチップにより、被実装基板に実装されたものがあり、最近、さらなる薄型化および小型化が望まれている。

【0003】

従来に係るこの種の半導体装置について、図8に基づき説明する。

この半導体装置は、半導体ウエハを切断して個片化された半導体素子51の表面に形成された複数のAlよりなる電極パッド部52にAu等の金属バンプ53を形成し(バンプの平坦化であるレベリングは不要)、そして多層回路実装基板である半導体キャリア基板54の上層面に設けた複数の配線電極部55と、上記半導体素子51上の電極パッド部52に形成したAu等の金属バンプ53とをフリップチップにより接続し、さらにシート形状のエポキシ系樹脂56にて樹脂封止を行うようにしたものである。なお、多層回路実装基板である半導体キャリア基板54の上層面にある複数の配線電極部55と裏面側にある複数の接続ランド部57とは内層ビア58により連結されている。

【0004】

この半導体装置の構成によると、図9に示すように、フリップチップ実装時において、Au等の金属バンプ53が潰れながら半導体素子51と半導体キャリア基板54とが電気的に接続されるフリップチップ実装構造であり、このため、半導体素子51に形成されたTr部51aへの悪影響が懸念され、Tr特性変動や層間膜51bへのクラック61が発生する惧れを有するものであった。

【0005】

ところで、上記問題点を解決し得るものとして、下記に示すような半導体装置がある。

この半導体装置は、図10に示すように、半導体ウエハを切断して個片化された半導体素子51の表面に形成された複数のAlよりなる電極パッド部52にAu等の金属バンプ53を形成し(バンプの平坦化であるレベリングは不要)、次に金属バンプ53をレベリングさせるとともに、導電性接着剤62を介して、この金属バンプ53と、半導体キャリア基板54の上層面に設けた複数の配線電極部55とを電気的に接続した構成にされている。また、半導体素子51と半導体キャリア基板54との隙間には、絶縁性のエポキシ系樹脂56が充填被覆された構造で接続部周辺をサージ破壊等から防止した構造にされている。なお、半導体キャリア基板54の上層面にある複数の配線電極部55と裏面側にある複数の接続ランド部57とは内層ビア58で連結されている。

【0006】

しかしながら、この構成によると、半導体素子51に形成されたTr部51aへの悪影響や層間膜51bへのクラック61等の発生は防止できるが、導電性接着剤62による隣接する電極パッド部間のショートによる不良の発生や接続部のオープンによる不良が発生する。また、組立工程で良品であったが信頼性試験を施すと接続不良が発生する場合もある。

【特許文献1】特開平8−167630号公報

【発明の開示】

【発明が解決しようとする課題】

【0007】

すなわち、従来の半導体装置の構成によると、半導体素子における電極パッド部直下への機械的なダメージの低減化と、電極パッド部の狭ピッチ化の実現およびその接続信頼性向上の両者を満足することができないという問題があり、さらには、多ピン化の要望に対する半導体素子の熱的破壊による不具合を防止するため、高放熱構造の実現化が必要とされている。

【0008】

そこで、本発明は、回路形成領域に電極パッド部を形成したパッドオンエレメント構造を有する半導体素子の被実装基板への実装時に、半導体素子への機械的ダメージの低減化を図り得るとともに、半導体素子における電極パッド部の狭ピッチ化、および実装時における接続部での信頼性の向上を図り得る半導体装置およびその製造方法を提供することを目的とする。

【課題を解決するための手段】

【0009】

上記課題を解決するため、本発明の請求項1に係る半導体装置は、半導体素子の回路形成領域の表面に設けられた複数の電極パッド部と、裏面に接続ランド部が設けられた被実装基板の表面に配置される複数の配線電極部とが電気的に接続され、且つこれら半導体素子と被実装基板との間に絶縁性樹脂が充填されてなる半導体装置であって、

上記各配線電極部を凹状に形成するとともに、これら各凹状の配線電極部と上記各電極パッド部とを導電性の針状部材にてそれぞれ接続し、

且つこれら各針状部材と上記各電極パッド部および各配線電極部との間に、それぞれ導電性接着剤を介在させたものである。

【0010】

また、請求項2に係る半導体装置は、請求項1に記載の半導体装置における凹状の配線電極部を、円筒形状または逆円錐形状に形成したものである。

また、請求項3に係る半導体装置は、半導体素子の回路形成領域の表面に設けられた複数の電極パッド部と、裏面に接続ランド部が設けられた被実装基板の表面に配置される複数の配線電極部とが電気的に接続されてなる半導体装置であって、

上記配線電極部が配置される被実装基板の表面に、周壁部より低くされた凹状空間部を形成するとともに、この凹状空間部内に上記半導体素子が配置された状態の各電極パッド部と当該凹状空間部の表面側に配置された各配線電極部とを導電性の針状部材にてそれぞれ接続し、

且つこれら各針状部材と上記各電極パッド部および各配線電極部との間に、それぞれ導電性接着剤を介在させたものである。

【0011】

また、請求項4に係る半導体装置は、請求項1乃至3のいずれか一項に記載の半導体装置における針状部材の太さを、数ミクロン〜数十ミクロンの範囲にするとともに、当該針状部材をCuまたはAlにて形成したものである。

【0012】

また、請求項5に係る半導体装置は、請求項1乃至4のいずれか一項に記載の半導体装置における針状部材により接続された電極パッド部が、回路形成領域の内、能動素子が形成された能動素子部領域および/または入出力セルが形成された入出力部領域に設けられたものである。

【0013】

また、本発明の請求項6に係る半導体装置の製造方法は、請求項1または2に記載の半導体装置の製造方法であって、

半導体素子表面に設けられた複数の電極パッド部に対応する位置で、保持具によりそれぞれ保持された導電性の各針状部材の一端側に、導電性接着剤を付着させる工程と、

上記各針状部材に付着された導電性接着剤を半導体素子の各電極パッド部に接触させた後、熱により硬化させる工程と、

裏面に複数の接続ランド部が形成されるとともに表面側に当該各接続ランド部にビアを介して接続された複数の凹状の配線電極部が形成されてなる被実装基板の各配線電極部内に導電性接着剤を付着させる工程と、

上記半導体素子に接続された各針状部材の他端部を上記各配線電極部内に挿入して付着された導電性接着剤に接触させた後、熱により硬化させる工程と、

上記針状部材により半導体素子と被実装基板とが接続された後、これら半導体素子と被実装基板との間に絶縁性樹脂を配置して樹脂封止する工程とを具備した方法である。

【0014】

また、請求項7に係る半導体装置の製造方法は、請求項1または2に記載の半導体装置の製造方法であって、

半導体素子表面に設けられた複数の電極パッド部に対応する位置で、保持具によりそれぞれ保持された導電性の各針状部材の一端側に、導電性接着剤を付着させる工程と、

上記各針状部材に付着された導電性接着剤を半導体素子の各電極パッド部に接触させた後、熱により硬化させる工程と、

上記一端側が半導体素子の各電極パッド部に接続された各針状部材の他端側に、導電性接着剤を付着させる工程と、

裏面に複数の接続ランド部が形成されるとともに表面側に上記各接続ランド部にビアを介して接続された複数の凹状の配線電極部が形成されてなる被実装基板の各配線電極部内に、導電性接着剤が付着された各針状部材の他端側を挿入した後、熱により硬化させる工程と、

上記各針状部材により半導体素子と被実装基板とが接続された後、これら半導体素子と被実装基板との間に絶縁性樹脂を配置して樹脂封止する工程とを具備した方法である。

【0015】

さらに、請求項8に係る半導体装置の製造方法は、請求項3に記載の半導体装置の製造方法であって、

半導体素子表面に設けられた複数の電極パッド部に対応する位置で、保持具によりそれぞれ保持された導電性の各針状部材の一端側に、導電性接着剤を付着させる工程と、

裏面に複数の接続ランド部が形成されるとともに表面側に形成された凹状空間部の内側表面に配置され且つ上記各接続ランド部にビアを介して接続された複数の配線電極部を有する被実装基板の上記凹状空間部内に、上記導電性接着剤が付着された各針状部材の一端側を挿入して各配線電極部に接触させて、これら各導電性接着剤を熱により硬化させる工程と、

上記一端側が被実装基板の各配線電極部に接続された各針状部材の他端側に、導電性接着剤を付着させる工程と、

上記導電性接着剤が付着された各針状部材の他端側に半導体素子を、各電極パッド部が各針状部材に接触するように凹状空間部内に配置して仮固定させる工程と、

上記半導体素子が凹状空間部内に仮固定した状態で、当該凹状空間部内の隙間に絶縁性樹脂を充填した後、熱により硬化させて樹脂封止する工程とを具備した方法である。

【発明の効果】

【0016】

上述の半導体装置およびその製造方法によると、半導体素子側の電極パッド部と被実装基板側の配線電極部とを電気的に接続する際に、配線電極部を凹状に形成しまたは凹状空間部に配線電極部を形成するとともに、この配線電極部と電極パッド部とを導電性の針状部材により接続するようにしたので、例えばバンプを用いた加圧方式とは異なり、たとえ接続するために押圧力を付加した場合でも、針状部材が変形して押圧力が吸収されるため、半導体素子側には殆ど力が作用することがなく、したがって実装時に、半導体素子に機械的なダメージが与えられることがないとともに、デバイス特性に悪影響を与える惧れもなくなる。

【0017】

また、半導体素子と被実装基板とを接続する際に、針状部材を凹状の配線電極部に挿入することになるため、やはり、バンプを加圧する場合に比べて、位置ずれが発生するのを防止することができ、延いては、位置ずれによる生産歩留りの低下を防止して製造コストの低減化を図ることができる。なお、半導体素子を凹状空間部内に位置させる場合も、両者の位置ずれの発生を防止することができる。

【0018】

また、被実装基板に設けられる配線電極部を凹状に形成しているため、または配線電極部を凹状空間部内に配置しているため、その凹み量に応じて、半導体装置をさらに薄型化することができる。

【0019】

また、針状部材と凹状の配線電極部とにより、位置決め精度のよい接続を行うことができるので、半導体素子に強く要望されている多ピン化技術の進展に伴うパッドオンエレメント構造における電極パッド部の狭ピッチ化、すなわち半導体素子の小型化を図ることができる。

【0020】

このようなことから、次世代プロセスを用いたパッドオンエリア構造でのフリップチップ実装を、容易に行うことができる。

さらに、導電性の針状部材として放熱性が良好なCuまたはAlを用いることにより、回路形成領域上に設けられた電極パッド部からの発熱を格子状に放熱することができ、したがって放熱性が優れた放熱構造を具備させることができる。これにより、多ピン化した半導体装置における半導体素子の熱的破壊を防止することができる。

【発明を実施するための最良の形態】

【0021】

以下、本発明の実施の形態に係る半導体装置およびその製造方法について説明する。

勿論、以下の実施の形態で説明する半導体装置は、半導体素子における回路形成領域(アクティブ領域)の能動素子部領域および入出力部領域(I/Oセル領域)上に電極パッド部が形成されて(パッドオンエレメント構造)、小型化および薄型化が図られたものである。

[実施の形態1]

以下、本発明の実施の形態1に係る半導体装置およびその製造方法を、図1および図2に基づき説明する。

【0022】

まず、半導体装置の概略構成を図1に基づき説明する。

図1は半導体装置の断面を示す模式図である。

この半導体装置は、半導体素子1の回路形成領域(具体的には、能動素子部領域および入出力部領域)の表面に形成された複数の電極パッド部2と、裏面に複数の接続ランド部3が設けられた被実装基板である半導体キャリア基板4の表面に形成されるとともに上記各接続ランド部3に内層ビア5を介して電気的に接続された複数の凹状の配線電極部6とが導電性の針状部材7を介してそれぞれ接続(所謂、フリップチップ接続である)されたものである。

【0023】

上記各凹状の配線電極部6の本体部分は半導体キャリア基板4に円筒形状(コップ形状)として凹んだ状態で形成されているが、表面側における回路パターンの接続用として、表面部分6aについては、そのまま残されている。勿論、本体部分と表面部分については電気的に接続されており、また表面部分の中央を貫通して形成されている。したがって、以下において配線電極部6と称した場合、凹んだ本体部分を示しているものとして説明する。なお、場合によっては、表面部分と異なる箇所に、本体部分が形成されることもある(この場合、本体部分を形成する際には表面部分が貫通されることはないが、表面部分と本体部分とは電気的に接続されることになる)。

【0024】

また、上記針状部材7としては、Cu(Alでもよい)が用いられるとともに、微細で且つ剛性を有するように形成されており、例えばその太さは、数ミクロン〜数十ミクロンの範囲にされている。

【0025】

また、上記針状部材7と電極パッド部2との接続、および針状部材7と配線電極部6との接続には、熱硬化性の導電性接着剤8が用いられる(言い換えれば、各針状部材7と各電極パッド部2および各配線電極部6との間に、それぞれ導電性接着剤8が介在されている)。

【0026】

さらに、半導体キャリア基板4に半導体素子1が実装された後は、両者の間およびその周辺部に、絶縁性樹脂であるエポキシ系樹脂9が充填されて樹脂封止が行われる。なお、各接続ランド部3には、それぞれ半田ボール10が接続される。

【0027】

次に、上記半導体装置の製造方法を、図2に基づき、工程形式で説明する。

この製造方法は、図2(a)および(b)に示すように、半導体素子1の表面に形成された複数の電極パッド部2に対応する位置で(つまり、同じ座標位置および同じ個数でもって)導電性の針状部材7がそれぞれ鉛直方向で吊持された(収納した)ツールボックス(保持具)21を、導電性接着剤8が塗布された転写台22の表面に降下・接触させて、各針状部材7の一端部に導電性接着剤8を転写塗布させる工程と、図2(c)および(d)に示すように、導電性接着剤8が転写塗布された複数の針状部材7をツールボックス21でもって半導体素子1上に且つ複数の電極パッド部2に対応する位置に移動させ、そして降下し接触させた後、熱風等により硬化させる工程と、図2(d)および(e)に示すように、熱硬化させた後、ツールボックス21で固定していた各針状部材7の一端を開放(解除)させた後、これら針状部材7が接続された半導体素子1を反転させた後、半導体キャリア基板4の表面に形成されるとともに内面に導電性接着剤8が塗布された(別工程で塗布される)複数の凹状の配線電極部6内に、それぞれ針状部材7を挿入する工程と、図2(f)に示すように、各配線電極部6内の導電性接着剤8を熱処理にて仮硬化させた後、両者の間およびその周縁部に絶縁性を有するエポキシ系樹脂9を充填し熱硬化(同時に導電性接着剤の本硬化も行われる)させる工程とを具備したものである。なお、半導体素子1を半導体キャリア基板4に接続する際に、針状部材7に殆ど押圧力が付加されることはない。

【0028】

図2(g)に、半導体素子1表面の電極パッド部2の配置状態を示しておく。この図では、内側の能動素子部領域に2個、外周の入出力部領域に16個配置されている。勿論、これは例示である。

【0029】

なお、配線電極部6内の導電性接着剤8と針状部材7との仮硬化を行わずに、エポキシ系樹脂9の硬化と同時に、硬化させるようにしてもよい。

この半導体装置およびその製造方法によると、半導体素子側の電極パッド部と半導体キャリア基板側の配線電極部とを電気的に接続する際に、配線電極部を凹状に形成するとともに、この凹状の配線電極部と電極パッド部とを導電性の針状部材により接続するようにしたので、例えばバンプを用いた加圧方式とは異なり、たとえ接続するために押圧力を付加した場合でも、針状部材が変形して押圧力が吸収されるため、半導体素子側には殆ど力が作用することがなく、したがって実装時に、半導体素子に機械的なダメージが与えられることがないとともに、デバイス特性に悪影響を与える惧れもなくなる。

【0030】

また、半導体素子と半導体キャリア基板とを接続する際に、針状部材を凹状の配線電極部に挿入することになるため、やはり、バンプを加圧する場合に比べて、位置ずれが発生するのを防止することができ、延いては、位置ずれによる生産歩留りの低下を防止して製造コストの低減化を図ることができる。

【0031】

また、半導体キャリア基板に設けられる配線電極部を凹状に形成しているため、その凹み量に応じて、半導体装置をさらに薄型化することができる。

また、針状部材と凹状の配線電極部とによる位置決め精度がよい接続を行うことができるので、半導体素子に強く要望されている多ピン化技術の進展に伴うパッドオンエレメント構造における電極パッド部の狭ピッチ化、すなわち半導体素子の小型化を図ることができる。

【0032】

このようなことから、次世代プロセスを用いたパッドオンエリア構造でのフリップチップ実装を、容易に行うことができる。

また、針状部材の形状や寸法等については、適宜、変更することが可能であり、例えば針状部材と導電性接着剤との接続抵抗を小さくすることにより、電気的接続性能を向上させて、接続部での信頼性のさらなる向上を図ることができる。

【0033】

また、導電性の針状部材として放熱性が良好なCu(またはAl)を用いることにより、回路形成領域上に設けられた電極パッド部からの熱を格子状に放熱することができ(つまり、針状部材が格子状に配置されているので、半導体素子からの発熱を基板側に逃がしやすくなる)、したがって放熱性が優れた放熱構造を具備させることができる。これにより、多ピン化した半導体装置における半導体素子の熱的破壊を防止することができる。

【0034】

さらに、導電性の針状部材として、Cu(またはAl)を用いるとともに、この針状部材に導電性接着剤を転写させて接続する方式を用いているので、既存設備および既存材料を利用することができ、延いては、製造コストの低減化に繋がることになる。

[実施の形態2]

以下、本発明の実施の形態2に係る半導体装置およびその製造方法を、図3および図4に基づき説明する。

【0035】

なお、上記実施の形態1にて説明したものと異なる箇所は、凹状の配線電極部の形状であり、上記実施の形態1で説明したものと同一の構成部材については、同一の部材番号を付して説明する。

【0036】

まず、半導体装置の概略構成を図3に基づき説明する。

図3は半導体装置の断面を示す模式図である。

この半導体装置は、半導体素子1の表面に配置された複数の電極パッド部2と、裏面に複数の接続ランド部3が設けられた被実装基板である半導体キャリア基板4の表面に形成されるとともに上記各接続ランド部3に内層ビア5を介して電気的に接続された複数の凹状の配線電極部6とが導電性の針状部材7を介してそれぞれ接続(所謂、フリップチップ接続である)されたものである。

【0037】

上記各凹状の配線電極部6の本体部分は半導体キャリア基板4に逆円錐形状(コーン形状)として凹んだ状態で形成されているが、表面側における回路パターンの接続用として、表面部分6aについては、そのまま残されている。勿論、本体部分と表面部分については電気的に接続されており、また表面部分の中央を貫通して形成されている。したがって、以下において配線電極部6と称した場合、凹んだ本体部分を示しているものとして説明する。なお、場合によっては、表面部分と異なる箇所に、本体部分が形成されることもある(この場合、本体部分を形成する際には表面部分が貫通されることはないが、表面部分と本体部分とは電気的に接続されることになる)。

【0038】

また、上記針状部材7としては、Cu(Alでもよい)が用いられるとともに、微細で且つ剛性を有するように形成されており、例えばその太さは、数ミクロン〜数十ミクロンの範囲にされている。

【0039】

また、上記針状部材7と電極パッド部2との接続、および針状部材7と配線電極部6との接続には、熱硬化性の導電性接着剤8が用いられる(言い換えれば、各針状部材7と各電極パッド部2および各配線電極部6との間に、それぞれ導電性接着剤8が介在されている)。

【0040】

さらに、半導体キャリア基板4に半導体素子1が実装された後は、両者の間およびその周辺部に、絶縁性樹脂であるエポキシ系樹脂9が充填されて樹脂封止が行われる。なお、各接続ランド部3には、それぞれ半田ボール10が接続される。

【0041】

次に、上記半導体装置の製造方法を、図4に基づき、工程形式で説明する。

この製造方法は、図4(a)および(b)に示すように、半導体素子1の表面に形成された複数の電極パッド部2に対応する位置で(つまり、同じ座標位置および同じ個数でもって)導電性の針状部材7がそれぞれ鉛直方向で吊持された(収納した)ツールボックス(保持具)21を、導電性接着剤8が塗布された転写台22の表面に降下・接触させて、各針状部材7の一端部に導電性接着剤8を転写塗布させる工程と、図4(c)および(d)に示すように、導電性接着剤8が転写塗布された複数の針状部材7をツールボックス21でもって半導体素子1上に且つ複数の電極パッド部2に対応する位置に移動させ、そして降下し接触させた後、熱風等により硬化させる工程と、図4(d)および(e)に示すように、熱硬化させた後、ツールボックス21で固定していた各針状部材7の一端を開放(解除)させた後、これら針状部材7が接続された半導体素子1を反転させた後、半導体キャリア基板4の表面に形成されるとともに内面に導電性接着剤8が塗布された(別工程で塗布される)複数の凹状の配線電極部6内に、針状部材7を挿入する工程と、図4(f)に示すように、各配線電極部6内の導電性接着剤8を熱処理にて仮硬化させた後、両者の間およびその周縁部に絶縁性を有するエポキシ系樹脂9を充填し熱硬化(同時に導電性接着剤の本硬化も行われる)させる工程とを具備したものである。なお、半導体素子1を半導体キャリア基板4に接続する際に、針状部材7に殆ど押圧力が付加されることはない。

【0042】

図4(g)に、半導体素子1表面の電極パッド部2の配置状態を示しておく。この図では、内側の能動素子部領域に2個、外周の入出力部領域に16個配置されている。勿論、これは例示である。

【0043】

なお、配線電極部6内の導電性接着剤8と針状部材7との仮硬化を行わずに、エポキシ系樹脂9の硬化と同時に、硬化させるようにしてもよい。

この半導体装置およびその製造方法によると、実施の形態1で説明したものと同一の効果を有している。

【0044】

さらに、本実施の形態2に係るものにおいては、凹状の配線電極部6の形状が逆円錐形状にされているため、実施の形態1で示した円筒形状のものよりも、針状部材7の半導体キャリア基板4に対する位置決めを正確に行うことができる。

[実施の形態3]

以下、本発明の実施の形態3に係る半導体装置およびその製造方法を、図5および図6に基づき説明する。

【0045】

なお、上記実施の形態1にて説明したものと異なる箇所は、半導体キャリア基板の表面に形成される配線電極部の部分であり、上記実施の形態1で説明したものと同一の構成部材については、同一の部材番号を付して説明する。

【0046】

まず、半導体装置の概略構成を図5に基づき説明する。

図5は半導体装置の断面を示す模式図である。

この半導体装置は、半導体素子1の表面に形成された複数の電極パッド部2と、裏面に複数の接続ランド部3が設けられた被実装基板である半導体キャリア基板4の表面に形成された凹状空間部[中央部分が薄くされるとともにその全周囲に壁状部(周壁部)が配置された、すなわち当該壁状部の内側に形成された凹状の空間室である]11の内側表面に配置されて上記各接続ランド部3に内層ビア5を介して電気的に接続された複数の配線電極部6とがそれぞれ導電性の針状部材7を介して接続(所謂、フリップチップ接続である)されたものである。

【0047】

また、上記針状部材7としては、Cu(またはAl)が用いられるとともに、微細で且つ剛性を有するように形成されており、例えばその太さは、数ミクロン〜数十ミクロンの範囲にされている。

【0048】

また、上記針状部材7と電極パッド部2との接続、および針状部材7と配線電極部6との接続には、熱硬化性の導電性接着剤8が用いられる(言い換えれば、各針状部材7と各電極パッド部2および各配線電極部6との間に、それぞれ導電性接着剤8が介在されている)。

【0049】

さらに、半導体キャリア基板4に半導体素子1が実装された後は、両者の間、すなわち当該半導体キャリア基板4の凹状空間部11内に、エポキシ系樹脂材9が充填されて樹脂封止が行われる。なお、各接続ランド部3には、それぞれ半田ボール10が接続される。

【0050】

次に、上記半導体装置の製造方法を、図6に基づき、工程形式で説明する。

この製造方法は、図6(a)および(b)に示すように、半導体素子1の表面に形成された複数の電極パッド部2に対応する位置で(つまり、同じ座標位置および同じ個数でもって)導電性の針状部材7がそれぞれ鉛直方向で吊持された(収納した)ツールボックス(保持具)21を、導電性接着剤8が塗布された転写台22の表面に降下・接触させて、各針状部材7の一端部に導電性接着剤8を転写塗布させる工程と、図6(c)および(d)に示すように、導電性接着剤8が転写塗布された複数の針状部材7をツールボックス21でもって凹状空間部11内に且つ複数の配線電極部6に対応する位置に移動させ、そして降下させて接触させた後、熱風等により硬化させる工程と、図6(d)および(e)に示すように、熱硬化させた後、ツールボックス21で固定していた各針状部材7の他端を開放(解除)させた後、これら各他端部に導電性接着剤8を転写塗布させ、さらに半導体素子1を、その電極パッド部2が下方となるように反転させて、半導体キャリア基板4の凹状空間部11内に且つ針状部材7上に載置して仮固定(接着剤による)する工程と、図6(f)に示すように、凹状空間部11内の隙間に絶縁性を有するエポキシ系樹脂9を充填した後、当該樹脂9および導電性接着剤8を熱硬化させる工程とを具備したものである。なお、半導体素子1を半導体キャリア基板4に接続する際に、針状部材7に殆ど押圧力が付加されることはない。

【0051】

図6(g)に、半導体素子1表面の電極パッド部2の配置状態を示しておく。この図では、内側の能動素子部領域に3個、外周の入出力部領域に16個配置されている。勿論、これは例示である。

【0052】

この半導体装置およびその製造方法によると、半導体素子1の電極パッド部2と半導体キャリア基板4の配線電極部6とを針状部材7により接続したので、例えばバンプを用いた加圧方式とは異なり、たとえ接続のために力を付加した場合でも、針状部材7が変形して力が吸収されるため、半導体素子側には殆ど力が加わることがなく、したがって実装時に、半導体素子1に機械的なダメージを与えることがないとともに、デバイス特性に悪影響を与える惧れもなくなる。

【0053】

また、半導体素子1を半導体キャリア基板4側に形成された凹状空間部11内に配置するようにしたので、半導体キャリア基板4に対する半導体素子1の位置決め、すなわちフリップチップ接続する際の位置ずれを完全に防止することができ、したがってこれまで課題であった位置ずれによる生産歩留りの低下を防止して、製造コストの低減化を図ることができる。

【0054】

ところで、上記各実施の形態においては、導電性針状部材7として、Cu(またはAl)を用いたが、例えばAu等のバンプを細長く形成したものを用いてもよい。この場合も、通常のバンプを用いることから、すなわち既存材料および既存設備を用いることができるから、殆ど、コストアップに繋がることはない。

【0055】

また、上記各実施の形態においては、導電性の針状部材7として線状のものを説明したが、例えば図7(a)に示すように、長方形状でもよく、図7(b)に示すように、さらに細い長方形状でもよく、図7(c)に示すように、背が高い台形状でもよく[(a)で示したものを、その根元から先端に徐々に細くしたもの]、図7(d)に示すように、(a)で示した長方形状の先端部の角を斜めに切り落とした(細くした)ものでもよく、図7(e)に示すように、(b)で示した細い長方形状の先端部分の幅を広くしてT字形状にしたものでもよく、また図7(f)に示すように、(a)で示した長方形状の両縁部をギザギザ状(稲妻形状)にして表面積を増加させたものでもよい。

【0056】

さらに、上記各実施の形態においては、半導体素子の回路形成領域における能動素子部領域と入出力部領域とに設けられた電極パッド部に適用したが、例えば能動素子部領域または入出力部領域のいずれかに設けられた電極パッド部に適用してもよい。

【産業上の利用可能性】

【0057】

本発明の半導体装置およびその製造方法は、半導体素子の回路形成領域であるアクティブ領域に電極パッド部を設ける際に、半導体素子に機械的なダメージを与えるのを防止することができるとともに、電極パッド部の狭ピッチ化および薄型化を図ることができるので、次世代プロセスを用いたパッドオンエリア構造でのフリップチップ実装を行うのに最適である。

【図面の簡単な説明】

【0058】

【図1】本発明の実施の形態1に係る半導体装置の断面図である。

【図2】同実施の形態1に係る半導体装置の製造方法を説明する工程図で、(a)〜(f)は断面図、(g)は半導体素子の平面図である。

【図3】本発明の実施の形態2に係る半導体装置の断面図である。

【図4】同実施の形態2に係る半導体装置の製造方法を説明する工程図で、(a)〜(f)は断面図、(g)は半導体素子の平面図である。

【図5】本発明の実施の形態3に係る半導体装置の断面図である。

【図6】同実施の形態3に係る半導体装置の製造方法を説明する工程図で、(a)〜(f)は断面図、(g)は半導体素子の平面図である。

【図7】本発明の半導体装置に用いられる針状部材の変形例を示す側面図である。

【図8】従来の半導体装置の構成を示す断面図である。

【図9】従来の半導体装置における不具合の発生状態を示す模式断面図である。

【図10】従来の他の半導体装置の構成を示す断面図である。

【符号の説明】

【0059】

1 半導体素子

2 電極パッド部

3 接続ランド部

4 半導体キャリア基板

5 内層ビア

6 配線電極部

7 針状部材

8 導電性接着剤

9 絶縁性樹脂

10 半田ボール

11 凹状空間部

【特許請求の範囲】

【請求項1】

半導体素子の回路形成領域の表面に設けられた複数の電極パッド部と、裏面に接続ランド部が設けられた被実装基板の表面に配置される複数の配線電極部とが電気的に接続され、且つこれら半導体素子と被実装基板との間に絶縁性樹脂が充填されてなる半導体装置であって、

上記各配線電極部を凹状に形成するとともに、これら各凹状の配線電極部と上記各電極パッド部とを導電性の針状部材にてそれぞれ接続し、

且つこれら各針状部材と上記各電極パッド部および各配線電極部との間に、それぞれ導電性接着剤を介在させたことを特徴とする半導体装置。

【請求項2】

凹状の配線電極部を、円筒形状または逆円錐形状に形成したことを特徴とする請求項1に記載の半導体装置。

【請求項3】

半導体素子の回路形成領域の表面に設けられた複数の電極パッド部と、裏面に接続ランド部が設けられた被実装基板の表面に配置される複数の配線電極部とが電気的に接続されてなる半導体装置であって、

上記配線電極部が配置される被実装基板の表面に、周壁部より低くされた凹状空間部を形成するとともに、この凹状空間部内に上記半導体素子が配置された状態の各電極パッド部と当該凹状空間部の表面側に配置された各配線電極部とを導電性の針状部材にてそれぞれ接続し、

且つこれら各針状部材と上記各電極パッド部および各配線電極部との間に、それぞれ導電性接着剤を介在させたことを特徴とする半導体装置。

【請求項4】

針状部材の太さを、数ミクロン〜数十ミクロンの範囲にするとともに、当該針状部材をCuまたはAlにて形成したことを特徴とする請求項1乃至3のいずれか一項に記載の半導体装置。

【請求項5】

針状部材により接続された電極パッド部が、回路形成領域の内、能動素子が形成された能動素子部領域および/または入出力セルが形成された入出力部領域に設けられていることを特徴とする請求項1乃至4のいずれか一項に記載の半導体装置。

【請求項6】

請求項1または2に記載の半導体装置の製造方法であって、

半導体素子表面に設けられた複数の電極パッド部に対応する位置で、保持具によりそれぞれ保持された導電性の各針状部材の一端側に、導電性接着剤を付着させる工程と、

上記各針状部材に付着された導電性接着剤を半導体素子の各電極パッド部に接触させた後、熱により硬化させる工程と、

裏面に複数の接続ランド部が形成されるとともに表面側に当該各接続ランド部にビアを介して接続された複数の凹状の配線電極部が形成されてなる被実装基板の各配線電極部内に導電性接着剤を付着させる工程と、

上記半導体素子に接続された各針状部材の他端部を上記各配線電極部内に挿入して付着された導電性接着剤に接触させた後、熱により硬化させる工程と、

上記針状部材により半導体素子と被実装基板とが接続された後、これら半導体素子と被実装基板との間に絶縁性樹脂を配置して樹脂封止する工程と

を具備したことを特徴とする半導体装置の製造方法。

【請求項7】

請求項1または2に記載の半導体装置の製造方法であって、

半導体素子表面に設けられた複数の電極パッド部に対応する位置で、保持具によりそれぞれ保持された導電性の各針状部材の一端側に、導電性接着剤を付着させる工程と、

上記各針状部材に付着された導電性接着剤を半導体素子の各電極パッド部に接触させた後、熱により硬化させる工程と、

上記一端側が半導体素子の各電極パッド部に接続された各針状部材の他端側に、導電性接着剤を付着させる工程と、

裏面に複数の接続ランド部が形成されるとともに表面側に上記各接続ランド部にビアを介して接続された複数の凹状の配線電極部が形成されてなる被実装基板の各配線電極部内に、導電性接着剤が付着された各針状部材の他端側を挿入した後、熱により硬化させる工程と、

上記各針状部材により半導体素子と被実装基板とが接続された後、これら半導体素子と被実装基板との間に絶縁性樹脂を配置して樹脂封止する工程と

を具備したことを特徴とする半導体装置の製造方法。

【請求項8】

請求項3に記載の半導体装置の製造方法であって、

半導体素子表面に設けられた複数の電極パッド部に対応する位置で、保持具によりそれぞれ保持された導電性の各針状部材の一端側に、導電性接着剤を付着させる工程と、

裏面に複数の接続ランド部が形成されるとともに表面側に形成された凹状空間部の内側表面に配置され且つ上記各接続ランド部にビアを介して接続された複数の配線電極部を有する被実装基板の上記凹状空間部内に、上記導電性接着剤が付着された各針状部材の一端側を挿入して各配線電極部に接触させて、これら各導電性接着剤を熱により硬化させる工程と、

上記一端側が被実装基板の各配線電極部に接続された各針状部材の他端側に、導電性接着剤を付着させる工程と、

上記導電性接着剤が付着された各針状部材の他端側に半導体素子を、各電極パッド部が各針状部材に接触するように凹状空間部内に配置して仮固定させる工程と、

上記半導体素子が凹状空間部内に仮固定した状態で、当該凹状空間部内の隙間に絶縁性樹脂を充填した後、熱により硬化させて樹脂封止する工程と

を具備したことを特徴とする半導体装置の製造方法。

【請求項1】

半導体素子の回路形成領域の表面に設けられた複数の電極パッド部と、裏面に接続ランド部が設けられた被実装基板の表面に配置される複数の配線電極部とが電気的に接続され、且つこれら半導体素子と被実装基板との間に絶縁性樹脂が充填されてなる半導体装置であって、

上記各配線電極部を凹状に形成するとともに、これら各凹状の配線電極部と上記各電極パッド部とを導電性の針状部材にてそれぞれ接続し、

且つこれら各針状部材と上記各電極パッド部および各配線電極部との間に、それぞれ導電性接着剤を介在させたことを特徴とする半導体装置。

【請求項2】

凹状の配線電極部を、円筒形状または逆円錐形状に形成したことを特徴とする請求項1に記載の半導体装置。

【請求項3】

半導体素子の回路形成領域の表面に設けられた複数の電極パッド部と、裏面に接続ランド部が設けられた被実装基板の表面に配置される複数の配線電極部とが電気的に接続されてなる半導体装置であって、

上記配線電極部が配置される被実装基板の表面に、周壁部より低くされた凹状空間部を形成するとともに、この凹状空間部内に上記半導体素子が配置された状態の各電極パッド部と当該凹状空間部の表面側に配置された各配線電極部とを導電性の針状部材にてそれぞれ接続し、

且つこれら各針状部材と上記各電極パッド部および各配線電極部との間に、それぞれ導電性接着剤を介在させたことを特徴とする半導体装置。

【請求項4】

針状部材の太さを、数ミクロン〜数十ミクロンの範囲にするとともに、当該針状部材をCuまたはAlにて形成したことを特徴とする請求項1乃至3のいずれか一項に記載の半導体装置。

【請求項5】

針状部材により接続された電極パッド部が、回路形成領域の内、能動素子が形成された能動素子部領域および/または入出力セルが形成された入出力部領域に設けられていることを特徴とする請求項1乃至4のいずれか一項に記載の半導体装置。

【請求項6】

請求項1または2に記載の半導体装置の製造方法であって、

半導体素子表面に設けられた複数の電極パッド部に対応する位置で、保持具によりそれぞれ保持された導電性の各針状部材の一端側に、導電性接着剤を付着させる工程と、

上記各針状部材に付着された導電性接着剤を半導体素子の各電極パッド部に接触させた後、熱により硬化させる工程と、

裏面に複数の接続ランド部が形成されるとともに表面側に当該各接続ランド部にビアを介して接続された複数の凹状の配線電極部が形成されてなる被実装基板の各配線電極部内に導電性接着剤を付着させる工程と、

上記半導体素子に接続された各針状部材の他端部を上記各配線電極部内に挿入して付着された導電性接着剤に接触させた後、熱により硬化させる工程と、

上記針状部材により半導体素子と被実装基板とが接続された後、これら半導体素子と被実装基板との間に絶縁性樹脂を配置して樹脂封止する工程と

を具備したことを特徴とする半導体装置の製造方法。

【請求項7】

請求項1または2に記載の半導体装置の製造方法であって、

半導体素子表面に設けられた複数の電極パッド部に対応する位置で、保持具によりそれぞれ保持された導電性の各針状部材の一端側に、導電性接着剤を付着させる工程と、

上記各針状部材に付着された導電性接着剤を半導体素子の各電極パッド部に接触させた後、熱により硬化させる工程と、

上記一端側が半導体素子の各電極パッド部に接続された各針状部材の他端側に、導電性接着剤を付着させる工程と、

裏面に複数の接続ランド部が形成されるとともに表面側に上記各接続ランド部にビアを介して接続された複数の凹状の配線電極部が形成されてなる被実装基板の各配線電極部内に、導電性接着剤が付着された各針状部材の他端側を挿入した後、熱により硬化させる工程と、

上記各針状部材により半導体素子と被実装基板とが接続された後、これら半導体素子と被実装基板との間に絶縁性樹脂を配置して樹脂封止する工程と

を具備したことを特徴とする半導体装置の製造方法。

【請求項8】

請求項3に記載の半導体装置の製造方法であって、

半導体素子表面に設けられた複数の電極パッド部に対応する位置で、保持具によりそれぞれ保持された導電性の各針状部材の一端側に、導電性接着剤を付着させる工程と、

裏面に複数の接続ランド部が形成されるとともに表面側に形成された凹状空間部の内側表面に配置され且つ上記各接続ランド部にビアを介して接続された複数の配線電極部を有する被実装基板の上記凹状空間部内に、上記導電性接着剤が付着された各針状部材の一端側を挿入して各配線電極部に接触させて、これら各導電性接着剤を熱により硬化させる工程と、

上記一端側が被実装基板の各配線電極部に接続された各針状部材の他端側に、導電性接着剤を付着させる工程と、

上記導電性接着剤が付着された各針状部材の他端側に半導体素子を、各電極パッド部が各針状部材に接触するように凹状空間部内に配置して仮固定させる工程と、

上記半導体素子が凹状空間部内に仮固定した状態で、当該凹状空間部内の隙間に絶縁性樹脂を充填した後、熱により硬化させて樹脂封止する工程と

を具備したことを特徴とする半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【公開番号】特開2007−335480(P2007−335480A)

【公開日】平成19年12月27日(2007.12.27)

【国際特許分類】

【出願番号】特願2006−162944(P2006−162944)

【出願日】平成18年6月13日(2006.6.13)

【出願人】(000005821)松下電器産業株式会社 (73,050)

【Fターム(参考)】

【公開日】平成19年12月27日(2007.12.27)

【国際特許分類】

【出願日】平成18年6月13日(2006.6.13)

【出願人】(000005821)松下電器産業株式会社 (73,050)

【Fターム(参考)】

[ Back to top ]