半導体装置およびその製造方法

【課題】FinFETにおいて、従来のFinFETの構造に比してさらにチャネルに応力を印加することができる半導体装置を提供すること。

【解決手段】Si基板1と、フィン11、フィン11の延在方向に平行な面上にゲート絶縁膜13を介して形成される所定の幅のゲート電極14、およびフィン11の延在方向に平行な面上のゲート電極14の両側に形成されるソース/ドレイン領域を含むFinFET10n,10pと、を備え、ゲート電極14上に形成され、応力印加層31,32の形成温度と室温での線膨張係数の差が、フィン11の形成温度と室温での線膨張係数の差と異なる導電性材料によって形成される応力印加層31,32と、応力印加層31,32上に形成され、フィン11よりもヤング率の大きい導電性材料からなるプラグ層33,34と、を備える。

【解決手段】Si基板1と、フィン11、フィン11の延在方向に平行な面上にゲート絶縁膜13を介して形成される所定の幅のゲート電極14、およびフィン11の延在方向に平行な面上のゲート電極14の両側に形成されるソース/ドレイン領域を含むFinFET10n,10pと、を備え、ゲート電極14上に形成され、応力印加層31,32の形成温度と室温での線膨張係数の差が、フィン11の形成温度と室温での線膨張係数の差と異なる導電性材料によって形成される応力印加層31,32と、応力印加層31,32上に形成され、フィン11よりもヤング率の大きい導電性材料からなるプラグ層33,34と、を備える。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置およびその製造方法に関するものである。

【背景技術】

【0002】

チャネルにフィン構造を用いた電界効果型トランジスタ(以下、FinFETという)において、チャネルでのキャリア移動度を向上させる手法として、チャネルに応力を印加する技術が知られている。たとえば、第1の従来技術では、絶縁膜は収縮する方向に力が働くことを利用して、複数並列して配置されたフィンの間とその上部を絶縁膜で覆うことによって、フィンの高さ方向に垂直な方向に圧縮応力を印加して、電流駆動力を向上させている(たとえば、特許文献1参照)。また、第2の従来技術では、シリコンよりなるフィンの上面と側面にゲート電極を形成し、このゲート電極上にシリコンよりも線膨張係数が小さい層間膜を形成することによって、フィンの高さ方向に垂直な方向に引張り歪を加えて、移動度を向上させている(たとえば、特許文献2参照)。このように、これらの第1と第2の従来技術では、ゲート電極が配置されたフィンの側面と上面に絶縁膜を形成し、主にフィンの高さ方向に垂直な方向に応力を印加することを目的としていた。

【0003】

ところで、FinFETでは、フィンのチャネル領域に応力を加えれば加えるほどチャネルでのキャリア移動度が向上するので、上述した第1と第2の従来技術に示される構造のFinFETのフィンにさらに応力を印加することができる技術が望まれている。また、FinFETにおいては、フィンの高さ方向に応力を印加した場合に、最も効果的にチャネルでのキャリア移動度を向上可能なことが従来から知られている(たとえば、非特許文献1参照)。しかしながら、上述したように第1と第2の従来技術では、フィンの高さ方向に垂直な方向に応力を印加しているので、FinFETにおけるチャネルでのキャリア移動度の向上には効果的でなかった。

【0004】

【特許文献1】特開2006−351975号公報

【特許文献2】国際公開第2004/090992号パンフレット

【非特許文献1】Kyoungsub Shin, et al., “Dual Stress Capping Layer Enhancement Study for Hybrid Orientation FinFET CMOS Technology”, 2005 IEEE

【発明の開示】

【発明が解決しようとする課題】

【0005】

本発明は、FinFETにおいて、従来のFinFETの構造に比してさらにチャネルでのキャリア移動度を向上させることができる半導体装置およびその製造方法を提供することを目的とする。

【課題を解決するための手段】

【0006】

本発明の一態様によれば、半導体基板と、前記半導体基板上に形成され、延在方向にチャネル領域を介してソース/ドレイン領域を有する半導体層からなるフィン、および前記チャネル領域上に絶縁膜を介して形成されるゲート電極を含む電界効果型トランジスタと、を備える半導体装置において、前記ゲート電極上に形成され、該応力印加層の形成温度と室温での線膨張係数の差が、前記フィンの前記形成温度と室温での線膨張係数の差と異なる導電性材料によって形成される応力印加層と、前記応力印加層上に形成され、前記フィンよりもヤング率の大きい導電性材料からなるプラグ層と、を備えることを特徴とする半導体装置が提供される。

【0007】

また、本発明の一態様によれば、半導体基板と、前記半導体基板上に形成され、延在方向にチャネル領域を介してソース/ドレイン領域を有する半導体層からなるフィン、および前記チャネル領域上に絶縁膜を介して形成されるゲート電極を含む電界効果型トランジスタと、を備える半導体装置において、前記ゲート電極上に、前記フィンの高さ方向に応力を印加するシリサイド膜からなる応力印加層と、前記応力印加層上に形成される、前記フィンよりもヤング率の大きい導電性材料からなるプラグ層と、を備えることを特徴とする半導体装置が提供される。

【0008】

さらに、本発明の一態様によれば、フィンを形成した半導体基板上に、ゲート絶縁膜、ゲート電極およびシリコン膜を順に形成する工程と、前記ゲート絶縁膜、前記ゲート電極および前記シリコン膜の積層膜を、チャネルを形成する領域に対応する前記フィン上の領域のみを残すようにパターニングする工程と、前記積層膜をマスクとして、前記積層膜の前記フィンの延在方向に沿った両側の前記フィンに所定の導電型のソース/ドレイン領域を形成する工程と、前記フィンを形成した前記半導体基板上に層間絶縁膜を形成する工程と、前記フィンの上部に形成された前記ゲート電極の形成位置にゲートプラグを形成するための開口部を形成する工程と、前記開口部内にシリコンと合金を形成する金属材料膜を含むプラグ層を形成する工程と、熱処理を行って前記金属材料膜と接する領域の前記シリコン膜を前記金属材料膜と反応させて、シリサイド膜を形成する工程と、を含むことを特徴とする半導体装置の製造方法が提供される。

【発明の効果】

【0009】

本発明によれば、従来のFin構造を有する半導体装置に比してチャネルでのキャリアの移動度をさらに向上させることができるという効果を奏する。また、本発明によれば、従来のFin構造を有する半導体装置に比してチャネルでのキャリアの移動度をさらに向上させた半導体装置を製造することができる。

【発明を実施するための最良の形態】

【0010】

以下に図面を参照して、本発明にかかる半導体装置の最良な実施の形態を詳細に説明する。なお、これらの実施の形態により本発明が限定されるものではない。また、半導体装置の各図は模式的なものであり、層の厚みと幅との関係や各層の厚みの比率などは現実のものとは異なる。

【0011】

(第1の実施の形態)

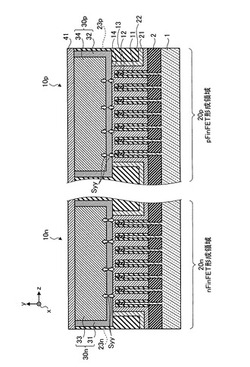

図1は、本発明の第1の実施の形態にかかる半導体装置の一例を模式的に示す平面図であり、図2−1は、図1のA−A断面図であり、図2−2(a)は、図1のB−B断面図であり、図2−2(b)は、図1のC−C断面図である。この第1の実施の形態では、1つのSi基板1上にnチャネル型FinFET(以下、nFinFETという)10nとpチャネル型FinFET(以下、pFinFETという)10pが作り込まれたCMOS(Complementary Metal Oxide Semiconductor)デバイスを例に挙げている。また、各FinFET10n,10pは、複数のフィン11のゲート電極、ソース領域およびドレイン領域を共通の配線(プラグ)で接続したマルチFinFET構造を有している。つまり、図1と図2−1において、nFinFET10nで示される部分が1つのFETの役割を有し、pFinFET10pで示される部分が1つのFETの役割を有している。

【0012】

このFinFETは、半導体基板としてのSi基板1上のnFinFET形成領域20nとpFinFET形成領域20pのそれぞれにnFinFET10nとpFinFET10pが形成される。Si基板1上には、チャネルを構成するフィン11が所定の本数で所定の間隔を置いて形成され、フィン11の上面には絶縁膜からなるキャップ膜12が形成されている。また、隣接するフィン11間の下部には、隣接するフィン11間を電気的に絶縁する素子分離絶縁膜2が形成されている。ここで、フィン11の高さ方向をy軸とし、フィン11内の電流の流れる方向(延在方向)をx軸とし、y軸とx軸の両方に垂直な方向(フィン11の幅方向)をz軸とする。

【0013】

また、フィン11とキャップ膜12の積層体の上面および側面を覆うように、厚さ約5nmのゲート絶縁膜13が形成され、このゲート絶縁膜13を覆うようにゲート電極14が形成される。また、並列して配置されるフィン11の最も外側に位置するゲート電極14の一方の側面とフィン11が形成されない位置のゲート電極14の上面にはライナ膜21が形成されている。ゲート電極14のフィン11のx軸方向に沿った両側のフィン11には、nFinFET10nではn型不純物を拡散して形成されたソース領域16n/ドレイン領域17nが形成され、pFinFET10pではp型不純物を拡散して形成されたソース領域16p/ドレイン領域17pが形成される。さらに、ゲート電極14が形成されたSi基板1上には、シリコン酸化物などからなる層間絶縁膜22が形成される。nFinFET形成領域20nの各フィン11のソース領域16nの上には、各フィン11のソース領域16n同士を結ぶようにソースプラグ35が形成され、各フィン11のドレイン領域17nの上には、各フィン11のドレイン領域17n同士を結ぶように、ドレインプラグ36が形成される。同様に、pFinFET形成領域20pの各フィン11のソース領域16pの上には、各フィン11のソース領域16p同士を結ぶようにソースプラグ35が形成され、各フィン11のドレイン領域17pの上には、各フィン11のドレイン領域17p同士を結ぶように、ドレインプラグ36が形成される。なお、ここではフィン11をSi基板1に形成しているが、SOI基板上にフィンを形成するものであってもよい。

【0014】

ゲート電極14の上部には、ゲート電極14への電気的な接点となるとともに、フィン11に対して圧縮または伸張の応力を印加する機能を有するゲートプラグ30n,30pが形成され、そのゲートプラグ30n,30pの上部には上層配線41が形成される。なお、このゲートプラグ30n,30pは、フィン11のy軸方向に対して圧縮または伸張の応力Syyを印加するものである。これは、フィン11のy軸方向に印加する応力Syyにより、チャネルでのキャリア移動度を向上させるためである。

【0015】

nFinFET10nのゲートプラグ30nは、ゲート電極14上に形成された開口部(コンタクトホール)23n内の側面と底面に形成され、フィン11に対してy軸方向に圧縮応力を印加する導電性材料からなる圧縮応力印加層31と、圧縮応力印加層31が形成された開口部23nを埋めるようにフィン11を構成する材料よりもヤング率の大きい導電性材料からなるプラグ層33と、によって構成される。ここで、圧縮応力印加層31は、圧縮応力印加層31を形成する温度での線膨張係数と室温での線膨張係数の差が、フィン11を構成する材料の圧縮応力印加層31を形成する温度での線膨張係数と室温での線膨張係数の差よりも小さい材料によって構成される。より簡単には、圧縮応力印加層31を形成する温度と室温での体積の差が、フィン11を構成する材料の圧縮応力印加層31を形成する温度と室温での体積の差よりも小さい材料を用いることで、圧縮応力印加層31を形成する温度から室温に温度を下げたときに、圧縮応力印加層31の方が体積の収縮度合いが小さくなるので、フィン11に対して圧縮応力を印加することができる。

【0016】

また、pFinFET10pのゲートプラグ30pは、ゲート電極14上に形成された開口部23p内の側面と底面に形成され、フィン11に対してy軸方向に伸張応力を印加する導電性材料からなる伸張応力印加層32と、伸張応力印加層32が形成された開口部23pを埋めるようにフィン11を構成する材料よりもヤング率の大きい導電性材料からなるプラグ層34と、によって構成される。ここで、伸張応力印加層32は、伸張応力印加層32を形成する温度と室温での線膨張係数の差が、フィン11を構成する材料の伸張応力印加層32を形成する温度と室温での線膨張係数の差よりも大きい材料によって構成される。より簡単には、伸張応力印加層32を形成する温度と室温での体積の差が、フィン11を構成する材料の伸張応力印加層32を形成する温度と室温での体積の差よりも大きい材料を用いることで、伸張応力印加層32を形成する温度から室温に温度を下げたときに、伸張応力印加層32の方が体積の収縮度合いが大きくなるので、フィン11に対して伸張応力を印加することができる。

【0017】

このように、本第1の実施の形態では、応力印加層31,32とプラグ層33,34の積層構造からなるゲートプラグ30n,30pがゲート電極14上に設けられているので、応力印加層31,32とフィン11を構成する材料の応力印加層31,32を形成する温度と室温での線膨張係数の差に応じた圧縮応力(nFinFET10nの場合)または伸張応力(pFinFET10pの場合)を、フィン11の高さ方向(y軸方向)から印加することができる。また、これに加えて、フィン11を構成する材料よりも大きいヤング率を有するプラグ層33,34が応力印加層31,32に対してふたの役割をし、応力印加層31,32がフィン11に対して応力を無効化させずに、効果的に与えることができる。なお、上述した圧縮応力印加層31と伸張応力印加層32の厚さは、フィン11に印加する応力の大きさや使用する材料によって適宜選択することが好ましい。

【0018】

図3は、金属材料とSiの線膨張係数と抵抗率の値を示す図である。ここでは、線膨張係数αとして、応力印加層31,32を形成する温度を500Kであるとして、500Kと293K(室温)のときの線膨張係数を示している。そして、500Kのときの線膨張係数と293Kのときの線膨張係数の差が小さいものから順に並べている。フィン11を構成する材料をSiとした場合、Siの500Kのときと293Kのときの線膨張係数の差が0.9なので、0.9より小さい材料が、圧縮応力印加層31として利用でき、また0.9より大きい材料が伸張応力印加層32として利用できる。しかし、実際には、500Kのときと293Kのときの線膨張係数の差がシリコンの0.9よりも乖離していて、抵抗率ρは273Kで7[Ω/m]よりも小さく、373Kで11[Ω/m]よりも小さい材料であることが望ましい。その結果、圧縮応力印加層31としては、Wなどが望ましく、伸張応力印加層32としては、Mg,Al,Cu,Agなどが望ましい。なお、圧縮応力印加層31として、500Kのときと293Kのときの線膨張係数の差が0.8であるが、抵抗率の低いIrを用いることも可能である。

【0019】

また、プラグ層33,34としては、フィン11を構成する材料のヤング率(Siのヤング率〜107GPa)よりもヤング率の大きい材料が好ましく、炭化タングステンWCx(ヤング率:WC〜550−650GPa)や炭化タンタルTaC(ヤング率:WC〜360−375GPa)などの材料が適当である。

【0020】

つぎに、このような構造を有する半導体装置の製造方法について説明する。図4−1〜図4−3は、第1の実施の形態にかかる半導体装置の製造方法の手順の一例を模式的に示す断面図である。まず、半導体基板としてのSi基板1上に、SiN膜を形成する。ついで、フォトリソグラフィ技術でフィン11を形成する領域にマスクを形成し、RIE(Reactive Ion Etching)によってSiN膜を加工する。これにより、フィン11の形成領域にのみキャップ膜12が形成される。その後、図4−1(a)に示されるように、キャップ膜12をマスクとしてSi基板1をエッチングして、フィン11とキャップ膜12との積層体からなるフィン構造が形成される。

【0021】

ついで、図4−1(b)に示されるように、フィン構造が形成されたSi基板1上にシリコン酸化膜などのSTI(Shallow Trench Isolation)材を埋め込んだ後にエッチバックすることによって素子分離絶縁膜2を形成する。その後、nFinFET形成領域20nのフィン11のチャネル領域18n(図2−2(a)参照)にBなどのp型不純物をイオン注入し、pFinFET形成領域20pのフィン11のチャネル領域18p(図2−2(b)参照)にPなどのn型不純物をイオン注入し、熱処理によって拡散させる。

【0022】

ついで、図4−1(c)に示されるように、フィン構造を形成したSi基板1上に、ゲート絶縁膜13、ゲート電極14を順に形成する。このとき、ゲート電極14は、隣接するフィン構造間を埋めるように形成される。その後、フォトリソグラフィ技術とRIEによって、ゲート絶縁膜13とゲート電極14の積層膜を、所定の形状にパターニングする。そして、nFinFET形成領域20nのゲート電極14のフィン11のx軸方向に沿った両側のフィン11には、上記積層体をマスクとしてAsなどのn型不純物をイオン注入し、pFinFET形成領域20pのゲート電極14のフィン11のx軸方向に沿った両側のフィン11には、上記積層体をマスクとしてBなどのp型不純物をイオン注入し、熱処理によって拡散させてソース領域16n,16p(図2−2参照)とドレイン領域17n,17p(図2−2参照)を形成する。その後、Si基板1上にライナ膜21と層間絶縁膜22を順に形成する。

【0023】

ついで、図4−2(a)に示されるように、層間絶縁膜22上の全面にフォトレジスト51を塗布した後、フォトリソグラフィ技術とRIEを用いて、nFinFET形成領域20nのゲート電極14、ソース領域16n(図2−2(a)参照)、およびドレイン領域17n(図2−2(a)参照)上に、それぞれプラグ30n,35,36を形成するための開口部を形成する。ここでは、ゲート電極14の延在方向に平行なゲート電極14を通る断面を示しているので、ゲートプラグ30nを形成するための開口部23nが形成される状態が示されている。このとき、ライナ膜21をエッチングストッパ膜として使用し、層間絶縁膜22をエッチングするとともに、ライナ膜21も除去して、ゲート電極14を露出させる。

【0024】

フォトレジスト51を除去した後、図4−2(b)に示されるように、スパッタ法などを用いて基板温度を圧縮応力印加層31を形成するために必要な所定の温度(数百℃程度)にして、フィン11を構成する材料(この場合にはSi)よりも圧縮応力印加層31の形成温度と室温での線膨張係数の差が小さい材料からなる圧縮応力印加層31と、フィン11を構成する材料よりもヤング率の大きなプラグ層33と、を続けて形成する。なお、圧縮応力印加層31は、少なくとも開口部23nの底面が覆われるように形成される。その後、Si基板1を室温近くまで冷却する。

【0025】

このとき、圧縮応力印加層31とプラグ層33を形成した直後は、上記したように基板温度が数百℃の温度であるが、時間の経過とともに基板温度は低下する。温度の低下に伴って、各材料の収縮が生じるが、圧縮応力印加層31はフィン11を構成する材料よりも圧縮応力印加層31の形成温度と室温での線膨張係数の差が小さいために、圧縮応力印加層31の方がフィン11を構成する材料よりも収縮の度合いが小さい。このため、フィン11を構成する材料は、ゲートプラグ30n(圧縮応力印加層31)に圧縮されるようなy軸方向の応力Syyを受け、チャネル領域に圧縮歪みが発生する。また、このときプラグ層33はフィン11を構成する材料よりもヤング率が大きいために、フィン11を構成する材料よりも変形し難く、ふたの役割を有する。その結果、フィン11の高さ方向の応力が逃げることを防ぎ、圧縮応力印加層31の体積変化による圧縮応力を効果的にフィン11へと伝えることができる。

【0026】

ついで、図4−2(c)に示されるように、CMP(Chemical Mechanical Polishing)などを用いて層間絶縁膜22などの上に形成された不要な圧縮応力印加層31とプラグ層33を除去する。これによって、nFinFET10nの開口部23nにゲートプラグ30nが形成される。その後、図4−3(a)に示されるように、層間絶縁膜22などの上面の全面にフォトレジスト52を塗布した後、フォトリソグラフィ技術とRIEを用いて、pFinFET形成領域20pのゲート電極14、ソース領域16p(図2−2(b)参照)、およびドレイン領域17p(図2−2(b)参照)上に、プラグ30p,35,36を形成するための開口部を形成する。ここでは、ゲート電極14を通る断面を示しているので、ゲートプラグ30pを形成するための開口部23pが形成される状態が示されている。このとき、ライナ膜21をエッチングストッパ膜として使用し、層間絶縁膜22をエッチングするとともに、ライナ膜21も除去して、ゲート電極14を露出させる。

【0027】

フォトレジスト52を除去した後、図4−3(b)に示されるように、スパッタ法などを用いて基板温度を伸張応力印加層32を形成するために必要な所定の温度(数百℃程度)にして、フィン11を構成する材料(この場合にはSi)よりも伸張応力印加層32の形成温度と室温での線膨張係数の差が大きい材料である伸張応力印加層32と、フィン11を構成する材料よりもヤング率の大きなプラグ層34と、を続けて形成する。なお、伸張応力印加層32は、少なくとも開口部23pの底面が覆われるように形成される。その後、Si基板1を室温近くまで冷却する。

【0028】

このとき、伸張応力印加層32とプラグ層34を形成した直後は、上記したように基板温度が数百℃の温度であるが、時間の経過とともに基板温度は低下する。温度の低下に伴って、各材料の収縮が生じるが、伸張応力印加層32はフィン11を構成する材料よりも伸張応力印加層32の形成温度と室温での線膨張係数の差が大きいために、伸張応力印加層32の方がフィン11を構成する材料よりも収縮の度合いが大きい。このため、フィン11を構成する材料は、ゲートプラグ30p(伸張応力印加層32)に引っ張られるようなy軸方向の応力Syyを受け、チャネル領域に伸張歪みが発生する。また、このときプラグ層34はフィン11を構成する材料よりもヤング率が大きいために、フィン11を構成する材料よりも変形し難く、ふたの役割を有する。その結果、フィン11の高さ方向の応力が逃げることを防ぎ、伸張応力印加層32による伸張応力を効果的にフィン11へと伝えることができる。

【0029】

その後、図4−3(c)に示されるように、CMPなどを用いて層間絶縁膜22などの上に形成された不要な伸張応力印加層32とプラグ層34を除去することによって、pFinFET形成領域20pの開口部23pにゲートプラグ30pが形成される。以上によって、nFinFET形成領域20nにはnFinFET10nが形成され、pFinFET形成領域20pにはnFinFET10pが形成される。そして、ゲートプラグ30p上に上層配線41を形成することによって図2−1に示される本第1の実施の形態のFinFETが形成される。

【0030】

なお、上述した説明では、nFinFET10nを形成した後にpFinFET10pを形成する場合を例に挙げたが、順番はこれに限られるものではなく、pFinFET10pを先に形成し、nFinFET10nを後に形成してもよい。また、上述した説明では、CMOSデバイスを例に挙げたが、これに限定されるものではなく、nFinFET10nからなる半導体装置やpFinFET10pからなる半導体装置に対しても同様に適用することができる。さらに、上述した説明では、プラグ層33,34は、1層の導電性材料から構成される場合について説明したが、複数層の導電性材料から構成されるものであってもよい。

【0031】

本第1の実施の形態によれば、FinFETのゲート電極14の上に、応力印加層形成時の温度と室温での線膨張係数の差が、フィン構成材料の応力印加層形成時の温度と室温での線膨張係数の差と異なる応力印加層31,32と、フィン構成材料よりも大きいヤング率を有するプラグ層33,34を設けたので、フィン11のy軸方向に応力を印加することができ、その結果、従来のFinFET構造に比べてチャネルでのキャリア移動度を向上させることができるという効果を有する。

【0032】

(第2の実施の形態)

図5は、本発明の第2の実施の形態にかかる半導体装置の製造方法の手順の一例を模式的に示す断面図である。第1の実施の形態では、応力印加層31,32をそれぞれゲートプラグ30n,30pの一部として構成していたが、図5(e)に示されるように、この第2の実施の形態のFinFETでは、応力印加層61をSi基板1上に形成されるゲート電極14上の全面に積層して形成し、見掛け上ゲート電極が2層構成となるように形成している。つまり、第1の実施の形態のゲートプラグ30n,30pの応力印加層31,32を除去し、Si基板1上に形成されるゲート電極14上の全面に応力印加層61が形成される構造を有する。そして、ゲートプラグ30n,30pは、フィン11の構成材料よりもヤング率の大きな導電性材料からなるプラグ層62のみによって形成される。なお、第1の実施の形態のFinFETと同一の構成要素には同一の符号を付してその説明を省略している。

【0033】

この第2の実施の形態でもnFinFETの場合には、応力印加層61は、応力印加層61を形成する温度と室温での線膨張係数の差が、フィン11を構成する材料の応力印加層61を形成する温度と室温での線膨張係数の差よりも小さい材料によって構成される。

【0034】

また、pFinFETの場合には、応力印加層61は、応力印加層61を形成する温度と室温での線膨張係数の差が、フィン11を構成する材料の応力印加層61を形成する温度と室温での線膨張係数の差よりも大きい材料によって構成される。

【0035】

さらに、ゲートプラグ30n,30pを構成するプラグ層62としては、フィン11の構成材料よりもヤング率の大きな材料によって形成されることが好ましい。

【0036】

つぎに、この第2の実施の形態の半導体装置の製造方法について説明する。第1の実施の形態の図4−1(a)〜図4−1(b)で説明したように、Si基板1にフィン構造を形成した後、素子分離絶縁膜2をフィン構造間に埋め込み、さらにフィン11のチャネル領域を形成する領域に所定の導電型のイオン注入を行う。

【0037】

ついで、図5(a)に示されるように、フィン構造を形成したSi基板1上に、ゲート絶縁膜13、ゲート電極14、および応力印加層61を形成する。このとき、ゲート電極14は、隣接するフィン構造間を埋めるように形成され、応力印加層61は、形成したゲート電極14上の全面を覆うように形成される。その後、フォトリソグラフィ技術とRIEによって、ゲート絶縁膜13とゲート電極14と応力印加層61の積層膜を、所定の形状にパターニングする。そして、FinFET形成領域のゲート電極14のフィン11のx軸方向に沿った両側のフィン11には、上記積層膜をマスクとして所定の導電型の不純物をイオン注入し、熱処理によって拡散させてソース/ドレイン領域を形成する。その後、図5(b)に示されるように、Si基板1上にライナ膜21と層間絶縁膜22を順に形成する。

【0038】

ついで、図5(c)に示されるように、層間絶縁膜22上の全面にフォトレジスト53を塗布した後、フォトリソグラフィ技術とRIEを用いて、FinFET形成領域のゲート電極14、ソース領域、およびドレイン領域上に、プラグを形成するための開口部を形成する。ここでは、ゲート電極14の延在方向に平行なゲート電極14を通る断面を示しているので、ゲートプラグ30n,30pを形成するための開口部23が形成される状態が示されている。このとき、ライナ膜21をエッチングストッパ膜として使用し、層間絶縁膜22をエッチングするとともに、ライナ膜21も除去する。これによって、応力印加層61の上面が露出する。

【0039】

フォトレジスト53を除去した後、図5(d)に示されるように、スパッタ法などを用いてフィン11を構成する材料よりもヤング率の大きなプラグ層62を開口部23が埋まるように形成する。そして、CMPなどを用いて層間絶縁膜22などの上に形成された不要なプラグ層62を除去することによって、図5(e)に示されるFinFETが形成される。

【0040】

このとき、第1の実施の形態のようにCMOSデバイスを作成する場合には、応力印加層61を形成する際に、nFinFETとpFinFETとで作り分ける必要があるが、ゲートプラグ30n,30p(プラグ層62)の形成時には、nFinFETとpFinFETを同時に形成することができるという利点がある。また、ゲートプラグ30n,30p(プラグ層62)は、1層の導電性材料から構成されるものであってもよいし、複数層の導電性材料から構成されるものであってもよい。

【0041】

本第2の実施の形態によっても、応力印加層61によってフィン11のy軸方向に応力を印加することができるとともに、プラグ層62によって応力印加層61による応力がフィン11に効果的に印加されるようになるので、従来のFinFET構造に比べてチャネルでのキャリア移動度を向上させることができるという効果を有する。

【0042】

(第3の実施の形態)

図6は、本発明の第3の実施の形態にかかる半導体装置の製造方法の手順の一例を模式的に示す断面図である。図6(f)に示されるように、このFinFETは、第2の実施の形態の応力印加層61が多結晶シリコン膜63で形成され、ゲートプラグ30nがSiと合金を形成する金属材料からなるプラグ層64で形成され、ゲート電極14の上部の多結晶シリコン膜63が、プラグ層64を構成する金属と合金化したシリサイド膜65で構成される構造を有している。ここで、ゲートプラグ30nを構成するプラグ層64は、第1および第2の実施の形態と同様に、フィン11の構成材料よりも大きいヤング率を有する導電性材料であるとともに、Siと反応してシリサイドを形成することが可能な金属材料であればよい。また、この第3の実施の形態では、ゲート電極14上部のシリサイド膜65がフィン11に対して圧縮応力を与える圧縮応力印加層として機能している。なお、第1および第2の実施の形態のFinFETと同一の構成要素には同一の符号を付してその説明を省略している。

【0043】

つぎに、この第3の実施の形態の半導体装置の製造方法について説明する。第1の実施の形態の図4−1(a)〜図4−1(b)で説明したように、Si基板1にフィン構造を形成した後、素子分離絶縁膜2をフィン構造間に埋め込み、さらにフィン11のチャネル領域を形成する領域に所定の導電型のイオン注入を行う。

【0044】

ついで、図6(a)に示されるように、フィン構造を形成したSi基板1上に、ゲート絶縁膜13、ゲート電極14、および多結晶シリコン膜63を形成する。このとき、ゲート電極14は、隣接するフィン構造間を埋めるように形成され、多結晶シリコン膜63は、形成したゲート電極14上の全面を覆うように形成される。その後、フォトリソグラフィ技術とRIEによって、ゲート絶縁膜13とゲート電極14と多結晶シリコン膜63の積層膜を、所定の形状にパターニングする。そして、FinFET形成領域のゲート電極14のフィン11のx軸方向に沿った両側のフィン11には、上記積層膜をマスクとして所定の導電型の不純物をイオン注入し、熱処理によって拡散させてソース/ドレイン領域を形成する。その後、図6(b)に示されるように、Si基板1上にライナ膜21と層間絶縁膜22を順に形成する。

【0045】

ついで、図6(c)に示されるように、層間絶縁膜22上の全面にフォトレジスト54を塗布した後、フォトリソグラフィ技術とRIEを用いて、FinFET形成領域のゲート電極14、ソース領域、およびドレイン領域上に、プラグを形成するための開口部を形成する。ここでは、ゲート電極14の延在方向に平行なゲート電極14を通る断面を示しているので、ゲートプラグ30nを形成するための開口部23が形成される状態が示されている。このとき、ライナ膜21をエッチングストッパ膜として使用し、層間絶縁膜22をエッチングするとともに、ライナ膜21も除去する。これによって、多結晶シリコン膜63の上面が露出する。

【0046】

フォトレジスト54を除去した後、図6(d)に示されるように、スパッタ法などを用いて開口部23にSiと反応して合金を形成する金属材料膜をプラグ層64として開口部23が埋まるように形成する。その後、図6(e)に示されるように、熱処理を行って、ゲート電極14上の開口部23内で、多結晶シリコン膜63とプラグ層64とを反応させて、ゲート電極14上にシリサイド膜65を形成する。そして、CMPなどを用いて層間絶縁膜22などの上に形成された不要なプラグ層64を除去することによって、図6(f)に示されるFinFETが形成される。

【0047】

この最後の熱処理で多結晶シリコン膜63とゲートプラグ30nを構成するプラグ層64とが反応して形成されるシリサイド膜65は、多結晶シリコン膜63に比して体積が膨張する。その結果、フィン11に対してy軸方向に圧縮応力を印加する圧縮応力印加層として機能する。ここで、プラグ層64に用いられるSiと合金を形成する金属材料として、Ni,Co,Wなどを用いることができる。この中でも、プラグ層64にWなどの熱処理時の温度と室温での線膨張係数の差がフィン11を構成する材料の線膨張係数よりも小さく、シリコンと合金を形成する金属材料を用いる場合には、シリサイド化による体積膨張で生じる圧縮応力のほかに、実施の形態1,2で説明したように熱処理時の温度と室温での線膨張係数の差に応じた圧縮応力もフィン11の高さ方向(y軸方向)に印加することができるので、フィン11に効果的に圧縮応力を印加することができる。なお、この方法は、フィン11に圧縮応力を印加するものであるので、nFinFET10nに対してのみ適用することができる。また、シリサイド膜65の厚さは、多結晶シリコン膜63の厚さによって決定されるが、この厚さは、フィン11に印加する圧縮応力の大きさによって適宜選択することができる。さらに、ゲートプラグ30n(プラグ層64)は、1層の導電性材料から構成されるものであってもよいし、複数層の導電性材料から構成されるものであってもよい。たとえば、プラグ層64にWを用いる場合には、プラグ層64の下層をWで構成し、上層をフィン11を構成する材料よりもヤング率の大きい導電性材料で構成することで、さらに効果的にフィン11に圧縮応力を印加することができる。

【0048】

本第3の実施の形態によっても、ゲート電極14上部に多結晶シリコン膜63を形成し、さらにその上部に金属材料でゲートプラグ30n(プラグ層64)を形成し、熱処理を行って多結晶シリコン膜63のゲート電極14上部のみをシリサイド化して体積を膨張させたシリサイド膜65を形成することによって、フィン11にy軸方向の圧縮応力を印加するようにしたので、従来のFinFET構造に比べてチャネルでのキャリア移動度を向上させることができるという効果を有する。

【0049】

上述した説明では、複数のフィン11で得られるソース/ドレイン間に流れる電流をまとめて取り出すマルチフィン構造を例に挙げたが、これに限られず1つのフィン11が1つのFETの動作をするシングルフィン構造のFinFETに対しても、同様に本発明を適用することができる。また、上記したFinFETはダブルゲート構造を有するFinFETであったが、トリプルゲート構造を有するFinFETに対しても同様に適用することができる。

【図面の簡単な説明】

【0050】

【図1】第1の実施の形態にかかる半導体装置の一例を模式的に示す平面図。

【図2−1】図1のA−A断面図。

【図2−2】図1のB−B断面図および図1のC−C断面図。

【図3】金属材料とSiの線膨張係数と抵抗率の値を示す図。

【図4−1】第1の実施の形態にかかる半導体装置の製造方法の手順の一例を示す断面図(その1)。

【図4−2】第1の実施の形態にかかる半導体装置の製造方法の手順の一例を示す断面図(その2)。

【図4−3】第1の実施の形態にかかる半導体装置の製造方法の手順の一例を示す断面図(その3)。

【図5】第2の実施の形態にかかる半導体装置の製造方法の手順の一例を模式的に示す断面図。

【図6】第3の実施の形態にかかる半導体装置の製造方法の手順の一例を模式的に示す断面図。

【符号の説明】

【0051】

1…Si基板、11…フィン、12…キャップ膜、13…ゲート絶縁膜、14…ゲート電極、16n,16p…ソース領域、17n,17p…ドレイン領域、22…層間絶縁膜、30n,30p…ゲートプラグ、31…圧縮応力印加層(応力印加層)、32…伸張応力印加層(応力印加層)、33,34,62,64…プラグ層、61…応力印加層、63…多結晶シリコン膜、65…シリサイド膜。

【技術分野】

【0001】

本発明は、半導体装置およびその製造方法に関するものである。

【背景技術】

【0002】

チャネルにフィン構造を用いた電界効果型トランジスタ(以下、FinFETという)において、チャネルでのキャリア移動度を向上させる手法として、チャネルに応力を印加する技術が知られている。たとえば、第1の従来技術では、絶縁膜は収縮する方向に力が働くことを利用して、複数並列して配置されたフィンの間とその上部を絶縁膜で覆うことによって、フィンの高さ方向に垂直な方向に圧縮応力を印加して、電流駆動力を向上させている(たとえば、特許文献1参照)。また、第2の従来技術では、シリコンよりなるフィンの上面と側面にゲート電極を形成し、このゲート電極上にシリコンよりも線膨張係数が小さい層間膜を形成することによって、フィンの高さ方向に垂直な方向に引張り歪を加えて、移動度を向上させている(たとえば、特許文献2参照)。このように、これらの第1と第2の従来技術では、ゲート電極が配置されたフィンの側面と上面に絶縁膜を形成し、主にフィンの高さ方向に垂直な方向に応力を印加することを目的としていた。

【0003】

ところで、FinFETでは、フィンのチャネル領域に応力を加えれば加えるほどチャネルでのキャリア移動度が向上するので、上述した第1と第2の従来技術に示される構造のFinFETのフィンにさらに応力を印加することができる技術が望まれている。また、FinFETにおいては、フィンの高さ方向に応力を印加した場合に、最も効果的にチャネルでのキャリア移動度を向上可能なことが従来から知られている(たとえば、非特許文献1参照)。しかしながら、上述したように第1と第2の従来技術では、フィンの高さ方向に垂直な方向に応力を印加しているので、FinFETにおけるチャネルでのキャリア移動度の向上には効果的でなかった。

【0004】

【特許文献1】特開2006−351975号公報

【特許文献2】国際公開第2004/090992号パンフレット

【非特許文献1】Kyoungsub Shin, et al., “Dual Stress Capping Layer Enhancement Study for Hybrid Orientation FinFET CMOS Technology”, 2005 IEEE

【発明の開示】

【発明が解決しようとする課題】

【0005】

本発明は、FinFETにおいて、従来のFinFETの構造に比してさらにチャネルでのキャリア移動度を向上させることができる半導体装置およびその製造方法を提供することを目的とする。

【課題を解決するための手段】

【0006】

本発明の一態様によれば、半導体基板と、前記半導体基板上に形成され、延在方向にチャネル領域を介してソース/ドレイン領域を有する半導体層からなるフィン、および前記チャネル領域上に絶縁膜を介して形成されるゲート電極を含む電界効果型トランジスタと、を備える半導体装置において、前記ゲート電極上に形成され、該応力印加層の形成温度と室温での線膨張係数の差が、前記フィンの前記形成温度と室温での線膨張係数の差と異なる導電性材料によって形成される応力印加層と、前記応力印加層上に形成され、前記フィンよりもヤング率の大きい導電性材料からなるプラグ層と、を備えることを特徴とする半導体装置が提供される。

【0007】

また、本発明の一態様によれば、半導体基板と、前記半導体基板上に形成され、延在方向にチャネル領域を介してソース/ドレイン領域を有する半導体層からなるフィン、および前記チャネル領域上に絶縁膜を介して形成されるゲート電極を含む電界効果型トランジスタと、を備える半導体装置において、前記ゲート電極上に、前記フィンの高さ方向に応力を印加するシリサイド膜からなる応力印加層と、前記応力印加層上に形成される、前記フィンよりもヤング率の大きい導電性材料からなるプラグ層と、を備えることを特徴とする半導体装置が提供される。

【0008】

さらに、本発明の一態様によれば、フィンを形成した半導体基板上に、ゲート絶縁膜、ゲート電極およびシリコン膜を順に形成する工程と、前記ゲート絶縁膜、前記ゲート電極および前記シリコン膜の積層膜を、チャネルを形成する領域に対応する前記フィン上の領域のみを残すようにパターニングする工程と、前記積層膜をマスクとして、前記積層膜の前記フィンの延在方向に沿った両側の前記フィンに所定の導電型のソース/ドレイン領域を形成する工程と、前記フィンを形成した前記半導体基板上に層間絶縁膜を形成する工程と、前記フィンの上部に形成された前記ゲート電極の形成位置にゲートプラグを形成するための開口部を形成する工程と、前記開口部内にシリコンと合金を形成する金属材料膜を含むプラグ層を形成する工程と、熱処理を行って前記金属材料膜と接する領域の前記シリコン膜を前記金属材料膜と反応させて、シリサイド膜を形成する工程と、を含むことを特徴とする半導体装置の製造方法が提供される。

【発明の効果】

【0009】

本発明によれば、従来のFin構造を有する半導体装置に比してチャネルでのキャリアの移動度をさらに向上させることができるという効果を奏する。また、本発明によれば、従来のFin構造を有する半導体装置に比してチャネルでのキャリアの移動度をさらに向上させた半導体装置を製造することができる。

【発明を実施するための最良の形態】

【0010】

以下に図面を参照して、本発明にかかる半導体装置の最良な実施の形態を詳細に説明する。なお、これらの実施の形態により本発明が限定されるものではない。また、半導体装置の各図は模式的なものであり、層の厚みと幅との関係や各層の厚みの比率などは現実のものとは異なる。

【0011】

(第1の実施の形態)

図1は、本発明の第1の実施の形態にかかる半導体装置の一例を模式的に示す平面図であり、図2−1は、図1のA−A断面図であり、図2−2(a)は、図1のB−B断面図であり、図2−2(b)は、図1のC−C断面図である。この第1の実施の形態では、1つのSi基板1上にnチャネル型FinFET(以下、nFinFETという)10nとpチャネル型FinFET(以下、pFinFETという)10pが作り込まれたCMOS(Complementary Metal Oxide Semiconductor)デバイスを例に挙げている。また、各FinFET10n,10pは、複数のフィン11のゲート電極、ソース領域およびドレイン領域を共通の配線(プラグ)で接続したマルチFinFET構造を有している。つまり、図1と図2−1において、nFinFET10nで示される部分が1つのFETの役割を有し、pFinFET10pで示される部分が1つのFETの役割を有している。

【0012】

このFinFETは、半導体基板としてのSi基板1上のnFinFET形成領域20nとpFinFET形成領域20pのそれぞれにnFinFET10nとpFinFET10pが形成される。Si基板1上には、チャネルを構成するフィン11が所定の本数で所定の間隔を置いて形成され、フィン11の上面には絶縁膜からなるキャップ膜12が形成されている。また、隣接するフィン11間の下部には、隣接するフィン11間を電気的に絶縁する素子分離絶縁膜2が形成されている。ここで、フィン11の高さ方向をy軸とし、フィン11内の電流の流れる方向(延在方向)をx軸とし、y軸とx軸の両方に垂直な方向(フィン11の幅方向)をz軸とする。

【0013】

また、フィン11とキャップ膜12の積層体の上面および側面を覆うように、厚さ約5nmのゲート絶縁膜13が形成され、このゲート絶縁膜13を覆うようにゲート電極14が形成される。また、並列して配置されるフィン11の最も外側に位置するゲート電極14の一方の側面とフィン11が形成されない位置のゲート電極14の上面にはライナ膜21が形成されている。ゲート電極14のフィン11のx軸方向に沿った両側のフィン11には、nFinFET10nではn型不純物を拡散して形成されたソース領域16n/ドレイン領域17nが形成され、pFinFET10pではp型不純物を拡散して形成されたソース領域16p/ドレイン領域17pが形成される。さらに、ゲート電極14が形成されたSi基板1上には、シリコン酸化物などからなる層間絶縁膜22が形成される。nFinFET形成領域20nの各フィン11のソース領域16nの上には、各フィン11のソース領域16n同士を結ぶようにソースプラグ35が形成され、各フィン11のドレイン領域17nの上には、各フィン11のドレイン領域17n同士を結ぶように、ドレインプラグ36が形成される。同様に、pFinFET形成領域20pの各フィン11のソース領域16pの上には、各フィン11のソース領域16p同士を結ぶようにソースプラグ35が形成され、各フィン11のドレイン領域17pの上には、各フィン11のドレイン領域17p同士を結ぶように、ドレインプラグ36が形成される。なお、ここではフィン11をSi基板1に形成しているが、SOI基板上にフィンを形成するものであってもよい。

【0014】

ゲート電極14の上部には、ゲート電極14への電気的な接点となるとともに、フィン11に対して圧縮または伸張の応力を印加する機能を有するゲートプラグ30n,30pが形成され、そのゲートプラグ30n,30pの上部には上層配線41が形成される。なお、このゲートプラグ30n,30pは、フィン11のy軸方向に対して圧縮または伸張の応力Syyを印加するものである。これは、フィン11のy軸方向に印加する応力Syyにより、チャネルでのキャリア移動度を向上させるためである。

【0015】

nFinFET10nのゲートプラグ30nは、ゲート電極14上に形成された開口部(コンタクトホール)23n内の側面と底面に形成され、フィン11に対してy軸方向に圧縮応力を印加する導電性材料からなる圧縮応力印加層31と、圧縮応力印加層31が形成された開口部23nを埋めるようにフィン11を構成する材料よりもヤング率の大きい導電性材料からなるプラグ層33と、によって構成される。ここで、圧縮応力印加層31は、圧縮応力印加層31を形成する温度での線膨張係数と室温での線膨張係数の差が、フィン11を構成する材料の圧縮応力印加層31を形成する温度での線膨張係数と室温での線膨張係数の差よりも小さい材料によって構成される。より簡単には、圧縮応力印加層31を形成する温度と室温での体積の差が、フィン11を構成する材料の圧縮応力印加層31を形成する温度と室温での体積の差よりも小さい材料を用いることで、圧縮応力印加層31を形成する温度から室温に温度を下げたときに、圧縮応力印加層31の方が体積の収縮度合いが小さくなるので、フィン11に対して圧縮応力を印加することができる。

【0016】

また、pFinFET10pのゲートプラグ30pは、ゲート電極14上に形成された開口部23p内の側面と底面に形成され、フィン11に対してy軸方向に伸張応力を印加する導電性材料からなる伸張応力印加層32と、伸張応力印加層32が形成された開口部23pを埋めるようにフィン11を構成する材料よりもヤング率の大きい導電性材料からなるプラグ層34と、によって構成される。ここで、伸張応力印加層32は、伸張応力印加層32を形成する温度と室温での線膨張係数の差が、フィン11を構成する材料の伸張応力印加層32を形成する温度と室温での線膨張係数の差よりも大きい材料によって構成される。より簡単には、伸張応力印加層32を形成する温度と室温での体積の差が、フィン11を構成する材料の伸張応力印加層32を形成する温度と室温での体積の差よりも大きい材料を用いることで、伸張応力印加層32を形成する温度から室温に温度を下げたときに、伸張応力印加層32の方が体積の収縮度合いが大きくなるので、フィン11に対して伸張応力を印加することができる。

【0017】

このように、本第1の実施の形態では、応力印加層31,32とプラグ層33,34の積層構造からなるゲートプラグ30n,30pがゲート電極14上に設けられているので、応力印加層31,32とフィン11を構成する材料の応力印加層31,32を形成する温度と室温での線膨張係数の差に応じた圧縮応力(nFinFET10nの場合)または伸張応力(pFinFET10pの場合)を、フィン11の高さ方向(y軸方向)から印加することができる。また、これに加えて、フィン11を構成する材料よりも大きいヤング率を有するプラグ層33,34が応力印加層31,32に対してふたの役割をし、応力印加層31,32がフィン11に対して応力を無効化させずに、効果的に与えることができる。なお、上述した圧縮応力印加層31と伸張応力印加層32の厚さは、フィン11に印加する応力の大きさや使用する材料によって適宜選択することが好ましい。

【0018】

図3は、金属材料とSiの線膨張係数と抵抗率の値を示す図である。ここでは、線膨張係数αとして、応力印加層31,32を形成する温度を500Kであるとして、500Kと293K(室温)のときの線膨張係数を示している。そして、500Kのときの線膨張係数と293Kのときの線膨張係数の差が小さいものから順に並べている。フィン11を構成する材料をSiとした場合、Siの500Kのときと293Kのときの線膨張係数の差が0.9なので、0.9より小さい材料が、圧縮応力印加層31として利用でき、また0.9より大きい材料が伸張応力印加層32として利用できる。しかし、実際には、500Kのときと293Kのときの線膨張係数の差がシリコンの0.9よりも乖離していて、抵抗率ρは273Kで7[Ω/m]よりも小さく、373Kで11[Ω/m]よりも小さい材料であることが望ましい。その結果、圧縮応力印加層31としては、Wなどが望ましく、伸張応力印加層32としては、Mg,Al,Cu,Agなどが望ましい。なお、圧縮応力印加層31として、500Kのときと293Kのときの線膨張係数の差が0.8であるが、抵抗率の低いIrを用いることも可能である。

【0019】

また、プラグ層33,34としては、フィン11を構成する材料のヤング率(Siのヤング率〜107GPa)よりもヤング率の大きい材料が好ましく、炭化タングステンWCx(ヤング率:WC〜550−650GPa)や炭化タンタルTaC(ヤング率:WC〜360−375GPa)などの材料が適当である。

【0020】

つぎに、このような構造を有する半導体装置の製造方法について説明する。図4−1〜図4−3は、第1の実施の形態にかかる半導体装置の製造方法の手順の一例を模式的に示す断面図である。まず、半導体基板としてのSi基板1上に、SiN膜を形成する。ついで、フォトリソグラフィ技術でフィン11を形成する領域にマスクを形成し、RIE(Reactive Ion Etching)によってSiN膜を加工する。これにより、フィン11の形成領域にのみキャップ膜12が形成される。その後、図4−1(a)に示されるように、キャップ膜12をマスクとしてSi基板1をエッチングして、フィン11とキャップ膜12との積層体からなるフィン構造が形成される。

【0021】

ついで、図4−1(b)に示されるように、フィン構造が形成されたSi基板1上にシリコン酸化膜などのSTI(Shallow Trench Isolation)材を埋め込んだ後にエッチバックすることによって素子分離絶縁膜2を形成する。その後、nFinFET形成領域20nのフィン11のチャネル領域18n(図2−2(a)参照)にBなどのp型不純物をイオン注入し、pFinFET形成領域20pのフィン11のチャネル領域18p(図2−2(b)参照)にPなどのn型不純物をイオン注入し、熱処理によって拡散させる。

【0022】

ついで、図4−1(c)に示されるように、フィン構造を形成したSi基板1上に、ゲート絶縁膜13、ゲート電極14を順に形成する。このとき、ゲート電極14は、隣接するフィン構造間を埋めるように形成される。その後、フォトリソグラフィ技術とRIEによって、ゲート絶縁膜13とゲート電極14の積層膜を、所定の形状にパターニングする。そして、nFinFET形成領域20nのゲート電極14のフィン11のx軸方向に沿った両側のフィン11には、上記積層体をマスクとしてAsなどのn型不純物をイオン注入し、pFinFET形成領域20pのゲート電極14のフィン11のx軸方向に沿った両側のフィン11には、上記積層体をマスクとしてBなどのp型不純物をイオン注入し、熱処理によって拡散させてソース領域16n,16p(図2−2参照)とドレイン領域17n,17p(図2−2参照)を形成する。その後、Si基板1上にライナ膜21と層間絶縁膜22を順に形成する。

【0023】

ついで、図4−2(a)に示されるように、層間絶縁膜22上の全面にフォトレジスト51を塗布した後、フォトリソグラフィ技術とRIEを用いて、nFinFET形成領域20nのゲート電極14、ソース領域16n(図2−2(a)参照)、およびドレイン領域17n(図2−2(a)参照)上に、それぞれプラグ30n,35,36を形成するための開口部を形成する。ここでは、ゲート電極14の延在方向に平行なゲート電極14を通る断面を示しているので、ゲートプラグ30nを形成するための開口部23nが形成される状態が示されている。このとき、ライナ膜21をエッチングストッパ膜として使用し、層間絶縁膜22をエッチングするとともに、ライナ膜21も除去して、ゲート電極14を露出させる。

【0024】

フォトレジスト51を除去した後、図4−2(b)に示されるように、スパッタ法などを用いて基板温度を圧縮応力印加層31を形成するために必要な所定の温度(数百℃程度)にして、フィン11を構成する材料(この場合にはSi)よりも圧縮応力印加層31の形成温度と室温での線膨張係数の差が小さい材料からなる圧縮応力印加層31と、フィン11を構成する材料よりもヤング率の大きなプラグ層33と、を続けて形成する。なお、圧縮応力印加層31は、少なくとも開口部23nの底面が覆われるように形成される。その後、Si基板1を室温近くまで冷却する。

【0025】

このとき、圧縮応力印加層31とプラグ層33を形成した直後は、上記したように基板温度が数百℃の温度であるが、時間の経過とともに基板温度は低下する。温度の低下に伴って、各材料の収縮が生じるが、圧縮応力印加層31はフィン11を構成する材料よりも圧縮応力印加層31の形成温度と室温での線膨張係数の差が小さいために、圧縮応力印加層31の方がフィン11を構成する材料よりも収縮の度合いが小さい。このため、フィン11を構成する材料は、ゲートプラグ30n(圧縮応力印加層31)に圧縮されるようなy軸方向の応力Syyを受け、チャネル領域に圧縮歪みが発生する。また、このときプラグ層33はフィン11を構成する材料よりもヤング率が大きいために、フィン11を構成する材料よりも変形し難く、ふたの役割を有する。その結果、フィン11の高さ方向の応力が逃げることを防ぎ、圧縮応力印加層31の体積変化による圧縮応力を効果的にフィン11へと伝えることができる。

【0026】

ついで、図4−2(c)に示されるように、CMP(Chemical Mechanical Polishing)などを用いて層間絶縁膜22などの上に形成された不要な圧縮応力印加層31とプラグ層33を除去する。これによって、nFinFET10nの開口部23nにゲートプラグ30nが形成される。その後、図4−3(a)に示されるように、層間絶縁膜22などの上面の全面にフォトレジスト52を塗布した後、フォトリソグラフィ技術とRIEを用いて、pFinFET形成領域20pのゲート電極14、ソース領域16p(図2−2(b)参照)、およびドレイン領域17p(図2−2(b)参照)上に、プラグ30p,35,36を形成するための開口部を形成する。ここでは、ゲート電極14を通る断面を示しているので、ゲートプラグ30pを形成するための開口部23pが形成される状態が示されている。このとき、ライナ膜21をエッチングストッパ膜として使用し、層間絶縁膜22をエッチングするとともに、ライナ膜21も除去して、ゲート電極14を露出させる。

【0027】

フォトレジスト52を除去した後、図4−3(b)に示されるように、スパッタ法などを用いて基板温度を伸張応力印加層32を形成するために必要な所定の温度(数百℃程度)にして、フィン11を構成する材料(この場合にはSi)よりも伸張応力印加層32の形成温度と室温での線膨張係数の差が大きい材料である伸張応力印加層32と、フィン11を構成する材料よりもヤング率の大きなプラグ層34と、を続けて形成する。なお、伸張応力印加層32は、少なくとも開口部23pの底面が覆われるように形成される。その後、Si基板1を室温近くまで冷却する。

【0028】

このとき、伸張応力印加層32とプラグ層34を形成した直後は、上記したように基板温度が数百℃の温度であるが、時間の経過とともに基板温度は低下する。温度の低下に伴って、各材料の収縮が生じるが、伸張応力印加層32はフィン11を構成する材料よりも伸張応力印加層32の形成温度と室温での線膨張係数の差が大きいために、伸張応力印加層32の方がフィン11を構成する材料よりも収縮の度合いが大きい。このため、フィン11を構成する材料は、ゲートプラグ30p(伸張応力印加層32)に引っ張られるようなy軸方向の応力Syyを受け、チャネル領域に伸張歪みが発生する。また、このときプラグ層34はフィン11を構成する材料よりもヤング率が大きいために、フィン11を構成する材料よりも変形し難く、ふたの役割を有する。その結果、フィン11の高さ方向の応力が逃げることを防ぎ、伸張応力印加層32による伸張応力を効果的にフィン11へと伝えることができる。

【0029】

その後、図4−3(c)に示されるように、CMPなどを用いて層間絶縁膜22などの上に形成された不要な伸張応力印加層32とプラグ層34を除去することによって、pFinFET形成領域20pの開口部23pにゲートプラグ30pが形成される。以上によって、nFinFET形成領域20nにはnFinFET10nが形成され、pFinFET形成領域20pにはnFinFET10pが形成される。そして、ゲートプラグ30p上に上層配線41を形成することによって図2−1に示される本第1の実施の形態のFinFETが形成される。

【0030】

なお、上述した説明では、nFinFET10nを形成した後にpFinFET10pを形成する場合を例に挙げたが、順番はこれに限られるものではなく、pFinFET10pを先に形成し、nFinFET10nを後に形成してもよい。また、上述した説明では、CMOSデバイスを例に挙げたが、これに限定されるものではなく、nFinFET10nからなる半導体装置やpFinFET10pからなる半導体装置に対しても同様に適用することができる。さらに、上述した説明では、プラグ層33,34は、1層の導電性材料から構成される場合について説明したが、複数層の導電性材料から構成されるものであってもよい。

【0031】

本第1の実施の形態によれば、FinFETのゲート電極14の上に、応力印加層形成時の温度と室温での線膨張係数の差が、フィン構成材料の応力印加層形成時の温度と室温での線膨張係数の差と異なる応力印加層31,32と、フィン構成材料よりも大きいヤング率を有するプラグ層33,34を設けたので、フィン11のy軸方向に応力を印加することができ、その結果、従来のFinFET構造に比べてチャネルでのキャリア移動度を向上させることができるという効果を有する。

【0032】

(第2の実施の形態)

図5は、本発明の第2の実施の形態にかかる半導体装置の製造方法の手順の一例を模式的に示す断面図である。第1の実施の形態では、応力印加層31,32をそれぞれゲートプラグ30n,30pの一部として構成していたが、図5(e)に示されるように、この第2の実施の形態のFinFETでは、応力印加層61をSi基板1上に形成されるゲート電極14上の全面に積層して形成し、見掛け上ゲート電極が2層構成となるように形成している。つまり、第1の実施の形態のゲートプラグ30n,30pの応力印加層31,32を除去し、Si基板1上に形成されるゲート電極14上の全面に応力印加層61が形成される構造を有する。そして、ゲートプラグ30n,30pは、フィン11の構成材料よりもヤング率の大きな導電性材料からなるプラグ層62のみによって形成される。なお、第1の実施の形態のFinFETと同一の構成要素には同一の符号を付してその説明を省略している。

【0033】

この第2の実施の形態でもnFinFETの場合には、応力印加層61は、応力印加層61を形成する温度と室温での線膨張係数の差が、フィン11を構成する材料の応力印加層61を形成する温度と室温での線膨張係数の差よりも小さい材料によって構成される。

【0034】

また、pFinFETの場合には、応力印加層61は、応力印加層61を形成する温度と室温での線膨張係数の差が、フィン11を構成する材料の応力印加層61を形成する温度と室温での線膨張係数の差よりも大きい材料によって構成される。

【0035】

さらに、ゲートプラグ30n,30pを構成するプラグ層62としては、フィン11の構成材料よりもヤング率の大きな材料によって形成されることが好ましい。

【0036】

つぎに、この第2の実施の形態の半導体装置の製造方法について説明する。第1の実施の形態の図4−1(a)〜図4−1(b)で説明したように、Si基板1にフィン構造を形成した後、素子分離絶縁膜2をフィン構造間に埋め込み、さらにフィン11のチャネル領域を形成する領域に所定の導電型のイオン注入を行う。

【0037】

ついで、図5(a)に示されるように、フィン構造を形成したSi基板1上に、ゲート絶縁膜13、ゲート電極14、および応力印加層61を形成する。このとき、ゲート電極14は、隣接するフィン構造間を埋めるように形成され、応力印加層61は、形成したゲート電極14上の全面を覆うように形成される。その後、フォトリソグラフィ技術とRIEによって、ゲート絶縁膜13とゲート電極14と応力印加層61の積層膜を、所定の形状にパターニングする。そして、FinFET形成領域のゲート電極14のフィン11のx軸方向に沿った両側のフィン11には、上記積層膜をマスクとして所定の導電型の不純物をイオン注入し、熱処理によって拡散させてソース/ドレイン領域を形成する。その後、図5(b)に示されるように、Si基板1上にライナ膜21と層間絶縁膜22を順に形成する。

【0038】

ついで、図5(c)に示されるように、層間絶縁膜22上の全面にフォトレジスト53を塗布した後、フォトリソグラフィ技術とRIEを用いて、FinFET形成領域のゲート電極14、ソース領域、およびドレイン領域上に、プラグを形成するための開口部を形成する。ここでは、ゲート電極14の延在方向に平行なゲート電極14を通る断面を示しているので、ゲートプラグ30n,30pを形成するための開口部23が形成される状態が示されている。このとき、ライナ膜21をエッチングストッパ膜として使用し、層間絶縁膜22をエッチングするとともに、ライナ膜21も除去する。これによって、応力印加層61の上面が露出する。

【0039】

フォトレジスト53を除去した後、図5(d)に示されるように、スパッタ法などを用いてフィン11を構成する材料よりもヤング率の大きなプラグ層62を開口部23が埋まるように形成する。そして、CMPなどを用いて層間絶縁膜22などの上に形成された不要なプラグ層62を除去することによって、図5(e)に示されるFinFETが形成される。

【0040】

このとき、第1の実施の形態のようにCMOSデバイスを作成する場合には、応力印加層61を形成する際に、nFinFETとpFinFETとで作り分ける必要があるが、ゲートプラグ30n,30p(プラグ層62)の形成時には、nFinFETとpFinFETを同時に形成することができるという利点がある。また、ゲートプラグ30n,30p(プラグ層62)は、1層の導電性材料から構成されるものであってもよいし、複数層の導電性材料から構成されるものであってもよい。

【0041】

本第2の実施の形態によっても、応力印加層61によってフィン11のy軸方向に応力を印加することができるとともに、プラグ層62によって応力印加層61による応力がフィン11に効果的に印加されるようになるので、従来のFinFET構造に比べてチャネルでのキャリア移動度を向上させることができるという効果を有する。

【0042】

(第3の実施の形態)

図6は、本発明の第3の実施の形態にかかる半導体装置の製造方法の手順の一例を模式的に示す断面図である。図6(f)に示されるように、このFinFETは、第2の実施の形態の応力印加層61が多結晶シリコン膜63で形成され、ゲートプラグ30nがSiと合金を形成する金属材料からなるプラグ層64で形成され、ゲート電極14の上部の多結晶シリコン膜63が、プラグ層64を構成する金属と合金化したシリサイド膜65で構成される構造を有している。ここで、ゲートプラグ30nを構成するプラグ層64は、第1および第2の実施の形態と同様に、フィン11の構成材料よりも大きいヤング率を有する導電性材料であるとともに、Siと反応してシリサイドを形成することが可能な金属材料であればよい。また、この第3の実施の形態では、ゲート電極14上部のシリサイド膜65がフィン11に対して圧縮応力を与える圧縮応力印加層として機能している。なお、第1および第2の実施の形態のFinFETと同一の構成要素には同一の符号を付してその説明を省略している。

【0043】

つぎに、この第3の実施の形態の半導体装置の製造方法について説明する。第1の実施の形態の図4−1(a)〜図4−1(b)で説明したように、Si基板1にフィン構造を形成した後、素子分離絶縁膜2をフィン構造間に埋め込み、さらにフィン11のチャネル領域を形成する領域に所定の導電型のイオン注入を行う。

【0044】

ついで、図6(a)に示されるように、フィン構造を形成したSi基板1上に、ゲート絶縁膜13、ゲート電極14、および多結晶シリコン膜63を形成する。このとき、ゲート電極14は、隣接するフィン構造間を埋めるように形成され、多結晶シリコン膜63は、形成したゲート電極14上の全面を覆うように形成される。その後、フォトリソグラフィ技術とRIEによって、ゲート絶縁膜13とゲート電極14と多結晶シリコン膜63の積層膜を、所定の形状にパターニングする。そして、FinFET形成領域のゲート電極14のフィン11のx軸方向に沿った両側のフィン11には、上記積層膜をマスクとして所定の導電型の不純物をイオン注入し、熱処理によって拡散させてソース/ドレイン領域を形成する。その後、図6(b)に示されるように、Si基板1上にライナ膜21と層間絶縁膜22を順に形成する。

【0045】

ついで、図6(c)に示されるように、層間絶縁膜22上の全面にフォトレジスト54を塗布した後、フォトリソグラフィ技術とRIEを用いて、FinFET形成領域のゲート電極14、ソース領域、およびドレイン領域上に、プラグを形成するための開口部を形成する。ここでは、ゲート電極14の延在方向に平行なゲート電極14を通る断面を示しているので、ゲートプラグ30nを形成するための開口部23が形成される状態が示されている。このとき、ライナ膜21をエッチングストッパ膜として使用し、層間絶縁膜22をエッチングするとともに、ライナ膜21も除去する。これによって、多結晶シリコン膜63の上面が露出する。

【0046】

フォトレジスト54を除去した後、図6(d)に示されるように、スパッタ法などを用いて開口部23にSiと反応して合金を形成する金属材料膜をプラグ層64として開口部23が埋まるように形成する。その後、図6(e)に示されるように、熱処理を行って、ゲート電極14上の開口部23内で、多結晶シリコン膜63とプラグ層64とを反応させて、ゲート電極14上にシリサイド膜65を形成する。そして、CMPなどを用いて層間絶縁膜22などの上に形成された不要なプラグ層64を除去することによって、図6(f)に示されるFinFETが形成される。

【0047】

この最後の熱処理で多結晶シリコン膜63とゲートプラグ30nを構成するプラグ層64とが反応して形成されるシリサイド膜65は、多結晶シリコン膜63に比して体積が膨張する。その結果、フィン11に対してy軸方向に圧縮応力を印加する圧縮応力印加層として機能する。ここで、プラグ層64に用いられるSiと合金を形成する金属材料として、Ni,Co,Wなどを用いることができる。この中でも、プラグ層64にWなどの熱処理時の温度と室温での線膨張係数の差がフィン11を構成する材料の線膨張係数よりも小さく、シリコンと合金を形成する金属材料を用いる場合には、シリサイド化による体積膨張で生じる圧縮応力のほかに、実施の形態1,2で説明したように熱処理時の温度と室温での線膨張係数の差に応じた圧縮応力もフィン11の高さ方向(y軸方向)に印加することができるので、フィン11に効果的に圧縮応力を印加することができる。なお、この方法は、フィン11に圧縮応力を印加するものであるので、nFinFET10nに対してのみ適用することができる。また、シリサイド膜65の厚さは、多結晶シリコン膜63の厚さによって決定されるが、この厚さは、フィン11に印加する圧縮応力の大きさによって適宜選択することができる。さらに、ゲートプラグ30n(プラグ層64)は、1層の導電性材料から構成されるものであってもよいし、複数層の導電性材料から構成されるものであってもよい。たとえば、プラグ層64にWを用いる場合には、プラグ層64の下層をWで構成し、上層をフィン11を構成する材料よりもヤング率の大きい導電性材料で構成することで、さらに効果的にフィン11に圧縮応力を印加することができる。

【0048】

本第3の実施の形態によっても、ゲート電極14上部に多結晶シリコン膜63を形成し、さらにその上部に金属材料でゲートプラグ30n(プラグ層64)を形成し、熱処理を行って多結晶シリコン膜63のゲート電極14上部のみをシリサイド化して体積を膨張させたシリサイド膜65を形成することによって、フィン11にy軸方向の圧縮応力を印加するようにしたので、従来のFinFET構造に比べてチャネルでのキャリア移動度を向上させることができるという効果を有する。

【0049】

上述した説明では、複数のフィン11で得られるソース/ドレイン間に流れる電流をまとめて取り出すマルチフィン構造を例に挙げたが、これに限られず1つのフィン11が1つのFETの動作をするシングルフィン構造のFinFETに対しても、同様に本発明を適用することができる。また、上記したFinFETはダブルゲート構造を有するFinFETであったが、トリプルゲート構造を有するFinFETに対しても同様に適用することができる。

【図面の簡単な説明】

【0050】

【図1】第1の実施の形態にかかる半導体装置の一例を模式的に示す平面図。

【図2−1】図1のA−A断面図。

【図2−2】図1のB−B断面図および図1のC−C断面図。

【図3】金属材料とSiの線膨張係数と抵抗率の値を示す図。

【図4−1】第1の実施の形態にかかる半導体装置の製造方法の手順の一例を示す断面図(その1)。

【図4−2】第1の実施の形態にかかる半導体装置の製造方法の手順の一例を示す断面図(その2)。

【図4−3】第1の実施の形態にかかる半導体装置の製造方法の手順の一例を示す断面図(その3)。

【図5】第2の実施の形態にかかる半導体装置の製造方法の手順の一例を模式的に示す断面図。

【図6】第3の実施の形態にかかる半導体装置の製造方法の手順の一例を模式的に示す断面図。

【符号の説明】

【0051】

1…Si基板、11…フィン、12…キャップ膜、13…ゲート絶縁膜、14…ゲート電極、16n,16p…ソース領域、17n,17p…ドレイン領域、22…層間絶縁膜、30n,30p…ゲートプラグ、31…圧縮応力印加層(応力印加層)、32…伸張応力印加層(応力印加層)、33,34,62,64…プラグ層、61…応力印加層、63…多結晶シリコン膜、65…シリサイド膜。

【特許請求の範囲】

【請求項1】

半導体基板と、

前記半導体基板上に形成され、延在方向にチャネル領域を介してソース/ドレイン領域を有する半導体層からなるフィン、および前記チャネル領域上に絶縁膜を介して形成されるゲート電極を含む電界効果型トランジスタと、

を備える半導体装置において、

前記ゲート電極上に形成され、該応力印加層の形成温度と室温での線膨張係数の差が、前記フィンの前記形成温度と室温での線膨張係数の差と異なる導電性材料によって形成される応力印加層と、

前記応力印加層上に形成され、前記フィンよりもヤング率の大きい導電性材料からなるプラグ層と、

を備えることを特徴とする半導体装置。

【請求項2】

前記フィンは、n型のチャネルを形成し、

前記応力印加層は、該応力印加層の形成温度と室温での線膨張係数の差が、前記フィンの前記形成温度と室温での線膨張係数の差よりも小さい材料によって構成されることを特徴とする請求項1に記載の半導体装置。

【請求項3】

前記フィンは、p型のチャネルを形成し、

前記応力印加層は、該応力印加層の形成温度と室温での線膨張係数の差が、前記フィンの前記形成温度と室温での線膨張係数の差よりも大きい材料によって構成されることを特徴とする請求項1に記載の半導体装置。

【請求項4】

半導体基板と、

前記半導体基板上に形成され、延在方向にチャネル領域を介してソース/ドレイン領域を有する半導体層からなるフィン、および前記チャネル領域上に絶縁膜を介して形成されるゲート電極を含む電界効果型トランジスタと、

を備える半導体装置において、

前記ゲート電極上に、前記フィンの高さ方向に応力を印加するシリサイド膜からなる応力印加層と、

前記応力印加層上に形成される、前記フィンよりもヤング率の大きい導電性材料からなるプラグ層と、

を備えることを特徴とする半導体装置。

【請求項5】

フィンを形成した半導体基板上に、ゲート絶縁膜、ゲート電極およびシリコン膜を順に形成する工程と、

前記ゲート絶縁膜、前記ゲート電極および前記シリコン膜の積層膜を、チャネルを形成する領域に対応する前記フィン上の領域のみを残すようにパターニングする工程と、

前記積層膜をマスクとして、前記積層膜の前記フィンの延在方向に沿った両側の前記フィンに所定の導電型のソース/ドレイン領域を形成する工程と、

前記フィンを形成した前記半導体基板上に層間絶縁膜を形成する工程と、

前記フィンの上部に形成された前記ゲート電極の形成位置にゲートプラグを形成するための開口部を形成する工程と、

前記開口部内にシリコンと合金を形成する金属材料膜を含むプラグ層を形成する工程と、

熱処理を行って前記金属材料膜と接する領域の前記シリコン膜を前記金属材料膜と反応させて、シリサイド膜を形成する工程と、

を含むことを特徴とする半導体装置の製造方法。

【請求項1】

半導体基板と、

前記半導体基板上に形成され、延在方向にチャネル領域を介してソース/ドレイン領域を有する半導体層からなるフィン、および前記チャネル領域上に絶縁膜を介して形成されるゲート電極を含む電界効果型トランジスタと、

を備える半導体装置において、

前記ゲート電極上に形成され、該応力印加層の形成温度と室温での線膨張係数の差が、前記フィンの前記形成温度と室温での線膨張係数の差と異なる導電性材料によって形成される応力印加層と、

前記応力印加層上に形成され、前記フィンよりもヤング率の大きい導電性材料からなるプラグ層と、

を備えることを特徴とする半導体装置。

【請求項2】

前記フィンは、n型のチャネルを形成し、

前記応力印加層は、該応力印加層の形成温度と室温での線膨張係数の差が、前記フィンの前記形成温度と室温での線膨張係数の差よりも小さい材料によって構成されることを特徴とする請求項1に記載の半導体装置。

【請求項3】

前記フィンは、p型のチャネルを形成し、

前記応力印加層は、該応力印加層の形成温度と室温での線膨張係数の差が、前記フィンの前記形成温度と室温での線膨張係数の差よりも大きい材料によって構成されることを特徴とする請求項1に記載の半導体装置。

【請求項4】

半導体基板と、

前記半導体基板上に形成され、延在方向にチャネル領域を介してソース/ドレイン領域を有する半導体層からなるフィン、および前記チャネル領域上に絶縁膜を介して形成されるゲート電極を含む電界効果型トランジスタと、

を備える半導体装置において、

前記ゲート電極上に、前記フィンの高さ方向に応力を印加するシリサイド膜からなる応力印加層と、

前記応力印加層上に形成される、前記フィンよりもヤング率の大きい導電性材料からなるプラグ層と、

を備えることを特徴とする半導体装置。

【請求項5】

フィンを形成した半導体基板上に、ゲート絶縁膜、ゲート電極およびシリコン膜を順に形成する工程と、

前記ゲート絶縁膜、前記ゲート電極および前記シリコン膜の積層膜を、チャネルを形成する領域に対応する前記フィン上の領域のみを残すようにパターニングする工程と、

前記積層膜をマスクとして、前記積層膜の前記フィンの延在方向に沿った両側の前記フィンに所定の導電型のソース/ドレイン領域を形成する工程と、

前記フィンを形成した前記半導体基板上に層間絶縁膜を形成する工程と、

前記フィンの上部に形成された前記ゲート電極の形成位置にゲートプラグを形成するための開口部を形成する工程と、

前記開口部内にシリコンと合金を形成する金属材料膜を含むプラグ層を形成する工程と、

熱処理を行って前記金属材料膜と接する領域の前記シリコン膜を前記金属材料膜と反応させて、シリサイド膜を形成する工程と、

を含むことを特徴とする半導体装置の製造方法。

【図1】

【図2−1】

【図2−2】

【図3】

【図4−1】

【図4−2】

【図4−3】

【図5】

【図6】

【図2−1】

【図2−2】

【図3】

【図4−1】

【図4−2】

【図4−3】

【図5】

【図6】

【公開番号】特開2009−105155(P2009−105155A)

【公開日】平成21年5月14日(2009.5.14)

【国際特許分類】

【出願番号】特願2007−274118(P2007−274118)

【出願日】平成19年10月22日(2007.10.22)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

【公開日】平成21年5月14日(2009.5.14)

【国際特許分類】

【出願日】平成19年10月22日(2007.10.22)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

[ Back to top ]