半導体装置およびその製造方法

【課題】抵抗素子として機能する配線を有し、かつ面積の小さな半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、半導体基板SBと、半導体基板SB上に設けられた第2の配線層L2とを備えている。第2の配線層L2は、通常の配線WRと、高抵抗配線REと、通常の配線WRおよび高抵抗配線REを埋め込む絶縁膜8とを含んでいる。通常の配線WRは、第1の銅部10Wと、第1の銅部10Wの底面側および側面側を覆う第1のバリアメタル膜9Wとを有している。高抵抗配線REは、空洞部CVと、空洞部CVの底面側および側面側を覆う第2のバリアメタル膜19Rとを有している。

【解決手段】半導体装置は、半導体基板SBと、半導体基板SB上に設けられた第2の配線層L2とを備えている。第2の配線層L2は、通常の配線WRと、高抵抗配線REと、通常の配線WRおよび高抵抗配線REを埋め込む絶縁膜8とを含んでいる。通常の配線WRは、第1の銅部10Wと、第1の銅部10Wの底面側および側面側を覆う第1のバリアメタル膜9Wとを有している。高抵抗配線REは、空洞部CVと、空洞部CVの底面側および側面側を覆う第2のバリアメタル膜19Rとを有している。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置およびその製造方法に関し、特に、金属配線を有する半導体装置およびその製造方法に関するものである。

【背景技術】

【0002】

システムLSIなどの半導体装置に抵抗素子や容量素子を含むアナログ回路を搭載することが一般的になっている。従来、このような抵抗素子や容量素子は、ゲート金属層や拡散層などの元来は半導体素子を構成するための層の一部が用いられて形成されることが主であった。このため抵抗素子や容量素子の設計変更がなされる場合、ゲート金属層や拡散層などの構成を変更する必要が生じる。よって、ゲート金属層や拡散層の形成工程を変更する必要が生じる。すなわち半導体素子自体に設計変更がなくても半導体素子の形成工程の変更が必要となる。このため設計変更後の半導体装置の出荷までに時間を要していた。

【0003】

そこで半導体素子の形成工程後に行なわれるダマシン法などによる配線層の形成工程(たとえば、非特許文献1参照)において抵抗素子や容量素子を形成することができれば、抵抗素子や容量素子の設計変更の影響が半導体素子の形成工程よりも下流の工程に限られるため、設計変更後の半導体装置の出荷までの時間を短縮することができる。

【0004】

近年配線層の配線の微細化が進んでおり、配線間隔が100nm〜40nm程度にまで狭くなってきている。また配線層の多層化も進んでおり、4層以上の配線層を有する製品が標準となりつつある。この結果、層内で互いに隣り合う配線間や、積層された配線間の容量を利用して十分な容量を有する容量素子を作ることが可能となってきている。たとえば容量密度が3fF/μm2程度の容量素子を65nmルールのプロセス技術による配線で形成することが可能となってきている。

【非特許文献1】王新明、他2名、「無電解キャップめっきプロセス」、エバラ時報、株式会社荏原製作所、平成17年4月、第207号、p.10−14

【発明の開示】

【発明が解決しようとする課題】

【0005】

半導体装置における配線層の配線は、元来、半導体素子間あるいは半導体素子と外部との間を低抵抗で電気的に接続することを目的とするものである。このため配線は低い抵抗率を有する材質により形成されている。よって配線が十分大きな抵抗値を有する抵抗素子として機能するためには非常に長い配線長が必要となる。たとえば65nmルールのプロセス技術による配線で100kΩの抵抗値を得るには配線長は50mm程度必要となる。このように配線長が長くなると半導体基板上での配線の面積が大きくなるので半導体装置の面積が大きくなってしまうという問題があった。

【0006】

本発明は、上記の問題に鑑みてなされたものであり、その目的は、抵抗素子として機能する配線を有し、かつ面積の小さな半導体装置およびその製造方法を提供することである。

【課題を解決するための手段】

【0007】

本発明の一実施の形態によれば、半導体装置は、半導体基板と、半導体基板上に設けられた配線層とを備えている。配線層は、第1の金属配線と、第2の金属配線と、第1および第2の金属配線を埋め込む絶縁膜とを含んでいる。第1の金属配線は、第1の金属部と、第1の金属部の底面側および側面側を覆う第1の金属膜とを有している。第2の金属配線は、絶縁部と、絶縁部の底面側および側面側を覆う第2の金属膜とを有している。

【0008】

本発明の一実施の形態によれば、半導体装置の製造方法は、第1の金属部および第1の金属膜を有する第1の金属配線と、絶縁部および第2の金属膜を有する第2の金属配線とを含む半導体装置の製造方法であって、以下の工程を備えている。

【0009】

まず半導体基板上に絶縁膜が堆積される。この絶縁膜の第1の金属配線が形成される領域に、第1の溝部が形成される。この第1の溝部の底面側および側面側を覆うように、第1の金属膜となる膜が堆積される。この第1の金属膜となる膜上に、第1の溝部を充填するように第1の金属部となる層が堆積される。第1の金属膜となる膜および第1の金属部となる層のうち第1の溝部の外側の部分が除去されることにより、第1の金属配線が形成される。絶縁膜の第2の金属配線が形成される領域に第2の溝部が形成される。この第2の溝部の底面側および側面側を覆うように、第2の金属膜となる膜が堆積される。この第2の金属膜となる膜上に、第2の溝部を充填するように金属層が堆積される。第2の金属膜となる膜および金属層のうち第2の溝部の外側の部分が除去されることにより、第2の金属膜と、絶縁部となる領域に形成された第2の金属部とが形成される。この第2の金属部が加熱されることで第2の金属部をなす金属が第2の溝部の側面側を覆う第2の金属膜を介して絶縁膜中に拡散することにより、第2の金属部の領域が空洞部にされる。

【発明の効果】

【0010】

本発明の一実施の形態によれば、半導体装置の第2の金属配線は底面側および側面側が第2の金属膜に覆われた絶縁部を有するため、第2の金属膜により底面側および側面側が覆われた部分が導体部である場合に比して、第2の金属配線の単位長さ当たりの抵抗値を大きくすることができる。よって短い配線長で大きな抵抗値を得ることができるので、半導体装置の面積を小さくすることができる。

【発明を実施するための最良の形態】

【0011】

以下、本発明の一実施の形態について図に基づいて説明する。

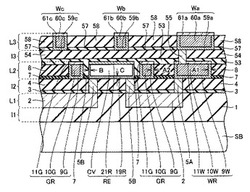

図1は、本発明の一実施の形態における半導体装置の構成を概略的に示す断面図である。

【0012】

図1を参照して、本実施の形態の半導体装置は、半導体基板SBと、第1〜第3の配線層L1〜L3と、第1〜第3の絶縁層I1〜I3とを有している。第1〜第3の配線層L1〜L3は、半導体基板SB上に順に積層された多層配線である。第1〜第3の配線層L1〜L3のそれぞれは、第1〜第3の絶縁層I1〜I3の各々により、半導体基板SBあるいは半導体基板SB側(図中下側)の他の配線層と絶縁されている。第1〜第3の絶縁層I1〜I3のそれぞれは、必要に応じてビア配線を有している。このビア配線により、第1〜第3の配線層L1〜L3の異なる層間の電気的接続が行なわれている。

【0013】

第2の配線層L2(配線層)は、第1の金属配線と、第2の金属配線と、第1および第2の金属配線を埋込む絶縁膜7および8とを有している。第1の金属配線は、通常の配線WRと、ガードリングGRとを有している。第2の金属配線は、通常の配線WRよりも単位長さ当たりの抵抗値が大きい高抵抗配線REを有している。ガードリングGRは、第2の配線層L2において高抵抗配線REを取囲むように設けられている。すなわち、半導体基板SB上において、ガードリングGRの平面パターンが高抵抗配線REの平面パターンを取囲んでいる。

【0014】

通常の配線WRは、銅(Cu)からなる第1の銅部(第1の金属部)10Wと、第1のバリアメタル膜(第1の金属膜)9Wと、高融点金属膜11Wとを有している。またガードリングGRは、銅(Cu)からなる第1の銅部(第1の金属部)10Gと、第1のバリアメタル膜(第1の金属膜)9Gと、高融点金属膜11Gとを有している。第1のバリアメタル膜9Wおよび9Gのそれぞれは、第1の銅部10Wおよび10Gの各々の底面側(半導体基板SB側)および側面側(図中横側)を覆っている。高融点金属膜11Wおよび11Gのそれぞれは、第1の銅部10Wおよび10Gの各々の上面側を覆っている。

【0015】

高抵抗配線REは、絶縁部である空洞部CVと、第2のバリアメタル膜19R(第2の金属膜)と、高融点金属膜21Rとを有している。第2のバリアメタル膜19Rは、空洞部CVの底面側(半導体基板SB側)および側面側(図中横側)を覆っている。高融点金属膜21Rは空洞部CVの上面側を覆っている。

【0016】

第2のバリアメタル膜19Rの空洞部CVの底面側を覆う部分の膜厚Cは、側面側を覆う部分の膜厚Bよりも大きい。膜厚BおよびCのそれぞれは、たとえば1〜5nm程度である。

【0017】

膜厚Bは、第1のバリアメタル膜9Wの第1の銅部10Wの側面側を覆う部分の膜厚A1よりも小さい。また膜厚Bは、第1のバリアメタル膜9Gの第1の銅部10Gの側面側を覆う部分の膜厚A2よりも小さい。膜厚A1およびA2のそれぞれは、たとえば1〜20nm程度である。

【0018】

第1のバリアメタル膜9Wおよび9Gは、第1の金属部10Wおよび10Gをなす材質である銅(Cu)の熱的な拡散を阻止する能力が高い材質からなる。第2のバリアメタル膜19Rは、第1のバリアメタル膜9Wおよび9Gのそれぞれの材質よりも、上記の熱的な拡散を阻止する能力が低い材質からなる。第1および第2のバリアメタル膜9W、9Gおよび19Rの材質は、たとえばTa(タンタル)、TaN(窒化タンタル)、WN(窒化タングステン)、CuSiO(酸化銅シリサイド)、RuO(酸化ルテニウム)、CuMo(銅−モリブデン)などである。

【0019】

絶縁膜8は、低誘電率膜、すなわち二酸化シリコンよりも低い誘電率を有する材質からなる膜である。この材質としては、たとえばSiOC(炭素含有酸化シリコン)がある。

【0020】

絶縁膜7は、絶縁膜8よりも小さい膜厚を有している。また絶縁膜7の材質は、絶縁膜8よりもエッチングレートを低くすることができる材質からなる。絶縁膜7の材質は、たとえばSiCN(炭窒化シリコン)やSiCO(炭化酸化シリコン)、あるいはこれらの積層材料である。絶縁膜7の膜厚は、たとえば20〜60nmである。

【0021】

第2の絶縁層I2は、半導体基板SBと第2の配線層L2との間に位置している。第2の絶縁層I2は、ビア配線5Aおよび5Bと、ビア配線5Aおよび5Bを埋込む絶縁膜3および4とを有している。ビア配線5Aは、通常の配線WRの半導体基板SB側に接する面を有している。ビア配線5Bは、高抵抗配線REの半導体基板SB側に接する面を有している。

【0022】

絶縁膜3および4のそれぞれは、たとえば絶縁膜7および8の各々と同様の膜厚を有し、同様の材質からなる。

【0023】

第1の配線層L1は、配線2と絶縁膜1の一部とを有している。配線2は、ビア配線5Aまたは5Bを介して、第2の配線層L2と電気的に接続されている。

【0024】

第1の絶縁層I1は、絶縁膜1の一部を有している。また第1の絶縁層I1は、ビア配線(図示せず)を有している。このビア配線を介して半導体基板SBに形成された半導体素子(図示せず)と第1の配線層L1とが電気的に接続されている。

【0025】

第3の絶縁層I3は、ビア配線55と、このビア配線55を埋込む絶縁膜53および54とを有している。なお絶縁膜53の一部は高抵抗配線REおよびガードリングGRの間の部分も埋込んでいる。絶縁膜53および54のそれぞれは、たとえば絶縁膜7および8の各々と同様の材料からなる。

【0026】

配線層L3は、配線Wa、WbおよびWcと、これら配線Wa、WbおよびWcを埋込む絶縁膜57および58とを有している。配線Waは、銅(Cu)からなる銅部60aと、バリアメタル膜59aと、高融点金属膜61aとを有している。バリアメタル膜59aは、銅部60aの底面側(半導体基板SB側)および側面側(図中横側)を覆っている。高融点金属膜61aは、銅部60aの上面側を覆っている。

【0027】

配線WbおよびWcのそれぞれも、配線Waとほぼ同様の構成を有しており、銅部60b、60c、バリアメタル膜59b、59c、高融点金属膜61bおよび61cが設けられている。絶縁膜57および58のそれぞれは、たとえば絶縁膜7および8と同様の膜厚を有し、同様の材質からなる。

【0028】

高融点金属膜11W、11G、21R、61a、61bおよび61cの材料は、たとえばCoWP(コバルト−タングステン−リン)、CoWBP(コバルト−タングステン−ボロン−リン)、CoW(コバルト−タングステン)、NiP(ニッケル−リン)またはPb(鉛)などのめっき材料である。あるいはW(タングステン)またはAl(アルミニウム)など、選択CVD法が適用可能な材料が用いられてもよい。

【0029】

次に、本実施の形態における半導体装置の製造方法について説明する。

図2〜図23は、本発明の一実施の形態における半導体装置の製造方法を工程順に示す概略断面図である。

【0030】

図2を参照して、通常の方法により、半導体基板SB上に、絶縁膜1と、この絶縁膜1の上面側に埋込まれた配線2とが形成される。これにより、第1の絶縁層I1および第1の配線層L1が形成される。

【0031】

図3〜図5を参照して、シングルダマシン法によりビア配線5Aおよび5Bの形成が以下のように行なわれる。

【0032】

図3を参照して、第1の配線層L1上に絶縁膜3および4が順に堆積される。絶縁膜3の膜厚は絶縁膜4の膜厚よりも小さくされる。また後に図4を用いて説明するエッチングにおいて絶縁膜3の材質のエッチングレートが絶縁膜4のエッチングレートよりも小さくすることができるように絶縁膜3および4の材質が選択される。

【0033】

絶縁膜3は、たとえばプラズマCVD法により形成される。絶縁膜3の材質は、たとえばSiCN(炭窒化シリコン)やSiCO(炭化酸化シリコン)の単層材料、あるいはこれらの積層材料が選択される。絶縁膜3の膜厚は、たとえば20〜60nmとされる。絶縁膜4の材質はSiOC(炭素含有酸化シリコン)などの低誘電率材料(low−K材)が用いられる。

【0034】

絶縁膜4上に写真製版法によりレジストマスク41が形成される。このレジストマスク41を用いて、絶縁膜3および4のエッチングが行なわれる。この後、レジストマスク41が除去される。

【0035】

図4および図5を参照して、上記エッチングにより絶縁膜3および4にビアホールVHが形成される。ビアホールVHは配線2の一部が露出するように設けられる。次にこのビアホールVHに金属の充填が行なわれることにより、ビア配線5Aおよび5Bが形成される。以下にこの金属の充填の方法について詳しく説明する。

【0036】

まずビアホールVHの底面および側面を被覆するようにバリアメタル膜がたとえばスパッタ法により形成される。このバリアメタル膜の膜厚は、たとえば5〜20nmである。またバリアメタル膜の材質としては、Ta(タンタル)、TaN(窒化タンタル)、WN(窒化タングステン)、CuSiO(酸化銅シリサイド)、RuO(酸化ルテニウム)またはCuMo(銅−モリブデン)などのCu(銅)の熱的な拡散を抑制する能力が高い材質が選択される。バリアメタル膜は、上記材質からなる単層膜、あるいは上記材料の複数が組合された積層膜とされることができる。

【0037】

上記のバリアメタル膜の形成後、連続してCu(銅)電解めっき法のための電極膜が形成される。電極膜の膜厚は、たとえば5〜20nmである。また電極膜の材料としては、電気固有抵抗が50μΩ・cm程度の材料が選択される。具体的には、Cu(銅)を用いることができる。あるいはCu(銅)、Al(アルミニウム)、Ti(チタン)、Mg(マグネシウム)、Zn(亜鉛)、B(ボロン)などを含む合金を用いることができる。なお上記のバリアメタル膜を電極膜として用いることにより、別途電極膜を形成することを省略することができる。

【0038】

次に上記電極膜上の全面に電解めっき法によりCu(銅)からなるめっき膜が形成される。これによりビアホールVHが完全に充填される。次に100〜400℃の熱処理が行なわれ、上記めっき膜の結晶性が改善される。次にCMP(Chemical Mechanical Polishing)によりビアホールVHの外側の膜が除去されることにより、第2の絶縁層I2が形成される。

【0039】

図6〜図10を参照して、主にシングルダマシン法を用いて通常の配線WRおよびガードリングGRの形成が以下のように行なわれる。

【0040】

主に図6を参照して、第2の絶縁層I2上に絶縁膜7および8が順に堆積される。絶縁膜7および8のそれぞれの形成方法、膜厚および材質は、絶縁膜3および4(図3)と同様とすることができる。

【0041】

絶縁膜8上のレジストマスク42が形成される。このレジストマスク42を用いて絶縁膜7および8のエッチングが行なわれる。その後、レジストマスク42の除去が行なわれる。

【0042】

主に図7を参照して、上記のエッチングにより絶縁膜7および8に第1の溝部TWおよびTGが形成される。第1の溝部TWはビア配線5Aが露出するように設けられる。第1の溝部TGは、絶縁膜4のビア配線5Bを取囲む部分が露出するようにもうけられる。なお第1の溝部TWおよびTGのそれぞれが形成される領域は、第1の金属配線WRおよびGR(図1)の各々が形成される領域に対応している。

【0043】

主に図7および図8を参照して、第1の溝部TWおよびTGの底面側および側面側が覆われるように、金属膜9が堆積される。この金属膜9は、第1のバリアメタル膜9Wおよび9G(図1)となる膜である。金属膜9が第1の溝部TWおよびTGのそれぞれの側面側を覆う部分の膜厚は、膜厚A1およびA2の各々である。金属膜9の形成方法および材料は、図5の工程で説明したバリアメタル膜と同様とすることができる。膜厚A1およびA2のそれぞれは、たとえば1〜20nm程度である。

【0044】

次に金属膜9上に、第1の溝部TWおよびTGが充填されるように銅(Cu)層10が堆積される。銅層10の堆積方法は、図5の工程で説明した銅(Cu)からなるめっき膜のめっき方法と同様である。次に図5の工程と同様の熱処理により、銅層10の結晶性が改善される。

【0045】

主に図8および図9を参照して、CMPにより第1の溝部TWおよびTGの外側の金属膜9および銅層10が除去される。これにより第1のバリアメタル膜9Wおよび9Gと、第1の銅部10Wおよび10Gとが形成される。

【0046】

図10を参照して、第1のバリアメタル膜9Wおよび第1の銅部10Wの上に選択的に高融点金属膜11Wが形成される。また第1のバリアメタル膜9Gおよび第1の銅部10Gの上に選択的に高融点金属膜11Gが形成される。

【0047】

高融点金属膜11Wおよび11Gの形成方法としては、無電解めっき法を用いることができる。この場合、高融点金属膜11Wおよび11Gの材質としては、たとえばCoWP(コバルト−タングステン−リン)やCoWBP(コバルト−タングステン−ボロン−リン)、CoW(コバルト−タングステン)、NiP(ニッケル−リン)、Pb(鉛)などを用いることができる。あるいは無電解めっき法の代わりに選択CVD法を用いて、高融点金属膜11Wおよび11Gとして、W(タングステン)やAl(アルミニウム)からなる膜を形成してもよい。

【0048】

以上により、通常の配線WRおよびガードリングGRが形成される。

次に、図11〜図17を参照して、高抵抗配線REの形成が以下のように行なわれる。

【0049】

図11を参照して、通常の配線WR、ガードリングGRおよび絶縁膜8を覆うようにレジストマスク43が形成される。レジストマスク43は、平面パターンとして、ガードリングGRに囲まれた領域内であって、かつビア配線5Bを含む領域に開口部を有している。このレジストマスク43を用いて絶縁膜7および8のエッチングが行なわれる。その後、レジストマスク43が除去される。

【0050】

主に図12を参照して、上記エッチングにより絶縁膜7および8に第2の溝部TRが形成される。第2の溝部TRが形成される領域は、高抵抗配線RE(図1)が形成される領域に対応している。

【0051】

主に図12および図13を参照して、第2の溝部TRの底面側および側面側が覆われるように、金属膜19が堆積される。この金属膜19は第2のバリアメタル膜19Rとなる膜である。

【0052】

金属膜19は、金属膜19の第2の溝部TRの底面側を覆う部分の膜厚Cが、金属膜19の第2の溝部TRの側面側を覆う部分の膜厚Bよりも大きくなるように堆積される。すなわちステップカバレッジの悪い方法による堆積が行なわれる。

【0053】

また金属膜19の堆積は、金属膜19の第2の溝部TRの側面側を覆う部分が金属膜9の第1の溝部TWおよびTGの側面側を覆う部分よりも第1の金属部10Wおよび10Gの材質である銅(Cu)の熱的拡散を阻止する能力が低くなるように行なわれる。上記能力を低くするため、最適な膜厚の選択と、最適な材質の選択との少なくともいずれかが行なわれる。

【0054】

最適な膜厚の選択としては、金属膜19の膜厚Bが金属膜9の膜厚A1およびA2(図8)のそれぞれよりも小さくされる。最適な材質の選択としては、金属膜19の材質が、金属膜9(図8)の材質よりも、第1の金属部10Wおよび10Gの材質である銅(Cu)の熱的拡散を阻止する能力が低い材質とされる。金属膜19の材質は、たとえばTa(タンタル)やTaN(窒化タンタル)、WN(窒化タングステン)、CuSiO(酸化銅シリサイド)、RuO(酸化ルテニウム)、CuMo(銅−モリブデン)とされる。

【0055】

次に金属膜19上に、第2の溝部TR(図12)が充填されるように銅(Cu)層20が堆積される。銅層20の堆積方法は、図5の工程で説明した銅(Cu)からなるめっき膜の形成方法と同様である。ただし、銅層20に対しては熱処理は行なわれない。次に、銅層20のうち第2の溝部TRの外側の部分を除去するCMPが行なわれる。CMPの条件としては、銅層20が高速で除去される条件が用いられる。

【0056】

図14を参照して、上記CMPにより銅(Cu)からなる第2の銅部20R(第2の金属部)が形成される。次に第2の銅部20Rが削られにくい条件で、露出した金属膜19を除去するためのCMPが行なわれる。

【0057】

主に図15を参照して、上記CMPにより金属膜19のうち第2の溝部TR(図12)の外側の部分が除去されて、第2のバリアメタル膜19Rが形成される。

【0058】

主に図16を参照して、第2のバリアメタル膜19Rおよび第2の銅部20Rの上に選択的に高融点金属膜21Rが形成される。高融点金属膜21Rの材質および形成方法は、図10の工程で説明した高融点金属膜11Wおよび11Gと同様である。

【0059】

次に、第2の銅部20Rが加熱される。たとえば、加熱する温度は400℃から500℃で、絶縁膜の酸化を防止するため水素や不活性ガス雰囲気が望ましい。その時間は、バリアメタルの結晶性、膜厚によって3〜5時間程度となる。第2の銅部20Rは第1の銅部10Wおよび10Gと比して結晶性が悪いため、銅(Cu)の拡散が生じやすい。また図13に示すように膜厚Bが膜厚Cよりも小さいことから、第2の銅部20Rをなす金属である銅(Cu)は、第2の溝部TR(図12)の底面側ではなく側面側を覆う第2のバリアメタル膜19Rを介して図中矢印のように絶縁膜8中へと拡散する。

【0060】

なお、膜厚C(図13)が膜厚Bよりも大きいことから、第2の溝部TR(図12)の底面側を覆う第2のバリアメタル膜19Rを介しての半導体基板SB側への拡散は抑制される。またガードリングGRの存在によりガードリングGRよりも外側の絶縁膜8にまで上記の拡散が生じることは抑制される。また高融点金属膜21Rにより半導体基板SBと反対の側への拡散は抑制される。

【0061】

また図13の工程で説明したように、金属膜9の第1の溝部TWおよびTGの側面側を覆う部分は、金属膜19の第2の溝部TRの側面側を覆う部分よりも第1の金属部10Wおよび10Gの材質である銅(Cu)の熱的拡散を阻止する能力が高い。すなわち、第1のバリアメタル膜9Wおよび9Gの第1の溝部TWおよびTGの側面側を覆う部分は、第2のバリアメタル膜19Rの第2の溝部TRの側面側を覆う部分よりも第1の金属部10Wおよび10Gの材質である銅(Cu)の熱的拡散を阻止する能力が高い。これにより第1の銅部10Wおよび10Gのそれぞれをなす金属である銅(Cu)が第1のバリアメタル膜9Wおよび9Gの各々を介して絶縁膜8中へと拡散することは抑制される。

【0062】

図16および図17を参照して、上記の拡散により第2の銅部20Rの領域が、空洞部CVとなる。以上により高抵抗配線REが形成される。なお、図16の矢印に示す拡散により絶縁膜8(図16)が銅(Cu)を含有する変質膜23(図17)に変質する。

【0063】

図18および図19を参照して、変質膜23を露出し、かつ変質しなかった絶縁膜8を覆うようにレジストマスク44が形成される。次にこのレジストマスク44を用いて変質膜23のエッチングが行なわれる。このエッチングの際、変質膜23のエッチングレートが高融点金属膜21Rおよび11Gのエッチングレートよりも大きくなるような選択比が得られるようなエッチング条件が用いられる。この後、レジストマスク44が除去される。上記のエッチングにより変質膜23が除去される。

【0064】

図20を参照して、上記のように変質膜23が除去された部分を充填するように絶縁膜53が堆積される。次に絶縁膜53の上に絶縁膜54が堆積される。絶縁膜53および54のそれぞれの堆積方法および材質は、絶縁膜3および4(図3)と同様とすることができる。

【0065】

図21を参照して、シングルダマシン法により、通常の配線WR上に、絶縁膜53および54を貫通するビア配線55が形成される。

【0066】

図22を参照して、絶縁膜54およびビア配線55上に絶縁膜57および58が順に堆積される。絶縁膜57および58のそれぞれの堆積方法および材質は、絶縁膜3および4(図3)と同様とすることができる。

【0067】

主に図23を参照して、シングルダマシン法により、バリアメタル膜59a、59b、59c、銅(Cu)部60a、60bおよび60cが絶縁膜57および58に埋込まれる。次にバリアメタル膜59a、59b、59c、銅部60a、60bおよび60cの上に選択的に高融点金属膜61a、61bおよび61cが形成される。これにより配線Wa、WbおよびWc(図1)が形成される。以上により、図1に示す半導体装置が製造される。

【0068】

なお上記の製造方法においてシングルダマシン法を用いた工程についてはデュアルダマシン法を用いた工程に置換することもできる。

【0069】

本実施の形態の半導体装置およびその製造方法によれば、図1に示すように、高抵抗配線REは底面側および側面側を第2のバリアメタル膜19Rに覆われた絶縁部である空洞部CVを有している。このため第2のバリアメタル膜19Rにより底面側および側面側が覆われた部分が導体部である場合に比して、高抵抗配線REの単位長さ当たりの抵抗値を大きくすることができる。よって短い長さで抵抗素子として機能する高抵抗配線REを形成することができるので、半導体装置の面積を小さくすることができる。

【0070】

また、通常の配線WRは、上記の空洞部CVに対応する位置において、底面側および側面側を第1のバリアメタル膜9Wに覆われた導体部である第1の銅部10Wを有している。このため、通常の配線WRの単位長さ当たりの抵抗値を小さくすることができる。よって通常の配線WRを用いて半導体素子間や半導体素子と外部との間を少ない電気的損失で接続することができる。

【0071】

また高抵抗配線REは上記の様に空洞部CVを有することにより単位長さ当たりの抵抗を大きくすることができる。このため加工精度の十分な安定性が得られなくなるほどに高抵抗配線REの線幅を小さくしなくても、高抵抗配線REの単位長さ当たりの抵抗を十分に確保することができる。このため高抵抗配線REの線幅の加工ばらつきに起因する抵抗値のばらつきを、たとえばアナログ回路において一般に要求される5%程度の範囲に収めることができる。

【0072】

また単位長さ当たりの抵抗値が大きい抵抗配線REにより抵抗素子として機能する部分が形成されるので、抵抗配線REに比して単位長さ当たりの抵抗値が小さい通常の配線WRにより抵抗素子として機能する部分を形成する必要がない。このため、通常の配線WRに極端に長さの長い部分を設ける必要がない。これにより、たとえば通常の配線WRの99%を1mm以下程度の長さとすることができる。このように極端に長さの長い部分が設けられなくてもよいので、配線の長さが長い部分で生じやすいパターン欠陥や異物の付着の可能性が低減され、半導体装置の信頼性が向上する。

【0073】

また第2のバリアメタル膜19R(図1)の膜厚Cは膜厚Bよりも大きい。これにより、図16に示すように第2の銅部20Rをなす金属である銅(Cu)は、第2の溝部TR(図12)の底面側ではなく側面側を覆う第2のバリアメタル膜19Rを介して図中矢印のように絶縁膜8中へと拡散する。よって絶縁膜4の高抵抗配線REの下部の部分が銅(Cu)の拡散により変質することを防ぐことができる。

【0074】

また、図1に示すように第2のバリアメタル膜19Rの膜厚Bが、第1のバリアメタル膜9Wおよび9Gのそれぞれの膜厚A1およびA2のそれぞれよりも小さくされる。すなわち金属膜19(図13)の膜厚Bが金属膜9(図8)の膜厚A1およびA2のそれぞれよりも小さくされる。言い換えれば、金属膜19(図13)の第2の溝部TR(図12)の側面側を覆う部分が、金属膜9(図8)の第1の溝部TWおよびTG(図7)の側面側を覆う部分よりも、第1の金属部10Wおよび10Gの材質である銅(Cu)の熱的拡散を阻止する能力を低くすることができる。これにより、図16に示す銅(Cu)の拡散工程において、第1の銅部10Wおよび10Gから絶縁膜8への拡散を抑制しつつ、かつ第2の銅部20Rを絶縁膜8中に拡散させることができる。

【0075】

また、図1に示すように第2のバリアメタル膜19Rの材質が第1のバリアメタル膜9Wおよび9Gのそれぞれの材質よりも、第1の金属部10Wおよび10Gの材質である銅(Cu)の熱的拡散を阻止する能力が低い材質とされる。すなわち、金属膜19(図13)の材質が、金属膜9(図8)の材質よりも、第1の金属部10Wおよび10Gの材質である銅(Cu)の熱的拡散を阻止する能力が低い材質とされる。これにより、図16に示す銅(Cu)の拡散工程において、第1の銅部10Wおよび10Gから絶縁膜8への拡散を抑制しつつ、かつ第2の銅部を絶縁膜8中に拡散させることができる。

【0076】

また第1の金属配線WRおよびGRは、第2の配線層L2において高抵抗配線REを取り囲む部分であるガードリングGRを含んでいる。これにより、図16に示す第2の銅部20Rの拡散工程においてガードリングGRよりも外側の絶縁膜8にまで拡散が生じることが抑制される。

【0077】

また高抵抗配線REおよび通常の配線WRを埋め込む絶縁膜8(図1)は二酸化シリコンよりも低い誘電率を有する材質からなる膜(低誘電率膜)であるため、配線間の容量を抑制することができる。また一般に低誘電率膜は半導体装置の製造工程におけるRIE(Reactive Ion Etching)などのプラズマに曝されると特性が劣化し易いが、本実施の形態では絶縁膜8の表面が直接プラズマに曝されないため、低誘電率膜の本来の特性を発揮することができる。

【0078】

また、図1に示すように、ビア配線5Bは、高抵抗配線REの半導体基板SB側に接する面を有している。これにより高抵抗配線REに対して半導体基板SB側から電気的接続をとることができる。なお仮に高抵抗配線REに対して半導体基板SBと反対側から電気的接続をとる場合、高抵抗配線REの半導体基板SBと反対側にビア配線が形成される必要がある。この形成の前段階として高抵抗配線REの上層である第3の絶縁層にビアホールが形成される。このビアホールの形成時のエッチングは高融点金属膜21Rの領域内で停止させなければならない。なぜならばエッチングが過剰に進めばビアホールが空洞部CVとつながり空洞部CVに穴が空いてしまい、逆にエッチングが過小であれば高抵抗配線REとの電気的接続がとれなくなるからである。なお半導体装置の製造工程途中で空洞部CVに穴が空いてしまうと、その後に導電体の成膜が行なわれた際に空洞部CVだったところが導電体部となってしまい、高抵抗配線REにより諸名の抵抗が得られなくなる。

【0079】

また本実施の形態の半導体装置の製造方法によれば、図16に示すように第2の銅部20Rを加熱することで、第2の銅部20Rをなす銅(Cu)を第2の溝部TR(図12)の側面側を覆う第2のバリアメタル19Rを介して絶縁膜8に拡散させる工程を有している。これにより底面側および側面側を第2のバリアメタル膜19Rに覆われた空洞部CVを形成することができる。

【0080】

今回開示された実施の形態はすべての点で例示であって制限的なものではないと考えられるべきである。本発明の範囲は上記した説明ではなくて特許請求の範囲によって示され、特許請求の範囲と均等の意味および範囲内でのすべての変更が含まれることが意図される。

【産業上の利用可能性】

【0081】

本発明は、金属配線を有する半導体装置およびその製造方法に特に有利に適用され得る。

【図面の簡単な説明】

【0082】

【図1】本発明の一実施の形態における半導体装置の構成を概略的に示す断面図である。

【図2】本発明の一実施の形態における半導体装置の製造方法の第1工程を示す概略断面図である。

【図3】本発明の一実施の形態における半導体装置の製造方法の第2工程を示す概略断面図である。

【図4】本発明の一実施の形態における半導体装置の製造方法の第3工程を示す概略断面図である。

【図5】本発明の一実施の形態における半導体装置の製造方法の第4工程を示す概略断面図である。

【図6】本発明の一実施の形態における半導体装置の製造方法の第5工程を示す概略断面図である。

【図7】本発明の一実施の形態における半導体装置の製造方法の第6工程を示す概略断面図である。

【図8】本発明の一実施の形態における半導体装置の製造方法の第7工程を示す概略断面図である。

【図9】本発明の一実施の形態における半導体装置の製造方法の第8工程を示す概略断面図である。

【図10】本発明の一実施の形態における半導体装置の製造方法の第9工程を示す概略断面図である。

【図11】本発明の一実施の形態における半導体装置の製造方法の第10工程を示す概略断面図である。

【図12】本発明の一実施の形態における半導体装置の製造方法の第11工程を示す概略断面図である。

【図13】本発明の一実施の形態における半導体装置の製造方法の第12工程を示す概略断面図である。

【図14】本発明の一実施の形態における半導体装置の製造方法の第13工程を示す概略断面図である。

【図15】本発明の一実施の形態における半導体装置の製造方法の第14工程を示す概略断面図である。

【図16】本発明の一実施の形態における半導体装置の製造方法の第15工程を示す概略断面図である。

【図17】本発明の一実施の形態における半導体装置の製造方法の第16工程を示す概略断面図である。

【図18】本発明の一実施の形態における半導体装置の製造方法の第17工程を示す概略断面図である。

【図19】本発明の一実施の形態における半導体装置の製造方法の第18工程を示す概略断面図である。

【図20】本発明の一実施の形態における半導体装置の製造方法の第19工程を示す概略断面図である。

【図21】本発明の一実施の形態における半導体装置の製造方法の第20工程を示す概略断面図である。

【図22】本発明の一実施の形態における半導体装置の製造方法の第21工程を示す概略断面図である。

【図23】本発明の一実施の形態における半導体装置の製造方法の第22工程を示す概略断面図である。

【符号の説明】

【0083】

CV 空洞部、GR ガードリング、I1〜I3 第1〜第3の絶縁層、L1〜L3 第1〜第3の配線層、RE 高抵抗配線、SB 半導体基板、WR 通常の配線、1,3,4,7,8,53,54,57,58 絶縁膜、2 配線、5A,5B ビア配線、9,19 金属膜、9W,9G 第1のバリアメタル膜、10W,10G 第1の銅部、11G,11W,21R 高融点金属膜、19R 第2のバリアメタル膜、20R 第2の銅部、23 変質膜。

【技術分野】

【0001】

本発明は、半導体装置およびその製造方法に関し、特に、金属配線を有する半導体装置およびその製造方法に関するものである。

【背景技術】

【0002】

システムLSIなどの半導体装置に抵抗素子や容量素子を含むアナログ回路を搭載することが一般的になっている。従来、このような抵抗素子や容量素子は、ゲート金属層や拡散層などの元来は半導体素子を構成するための層の一部が用いられて形成されることが主であった。このため抵抗素子や容量素子の設計変更がなされる場合、ゲート金属層や拡散層などの構成を変更する必要が生じる。よって、ゲート金属層や拡散層の形成工程を変更する必要が生じる。すなわち半導体素子自体に設計変更がなくても半導体素子の形成工程の変更が必要となる。このため設計変更後の半導体装置の出荷までに時間を要していた。

【0003】

そこで半導体素子の形成工程後に行なわれるダマシン法などによる配線層の形成工程(たとえば、非特許文献1参照)において抵抗素子や容量素子を形成することができれば、抵抗素子や容量素子の設計変更の影響が半導体素子の形成工程よりも下流の工程に限られるため、設計変更後の半導体装置の出荷までの時間を短縮することができる。

【0004】

近年配線層の配線の微細化が進んでおり、配線間隔が100nm〜40nm程度にまで狭くなってきている。また配線層の多層化も進んでおり、4層以上の配線層を有する製品が標準となりつつある。この結果、層内で互いに隣り合う配線間や、積層された配線間の容量を利用して十分な容量を有する容量素子を作ることが可能となってきている。たとえば容量密度が3fF/μm2程度の容量素子を65nmルールのプロセス技術による配線で形成することが可能となってきている。

【非特許文献1】王新明、他2名、「無電解キャップめっきプロセス」、エバラ時報、株式会社荏原製作所、平成17年4月、第207号、p.10−14

【発明の開示】

【発明が解決しようとする課題】

【0005】

半導体装置における配線層の配線は、元来、半導体素子間あるいは半導体素子と外部との間を低抵抗で電気的に接続することを目的とするものである。このため配線は低い抵抗率を有する材質により形成されている。よって配線が十分大きな抵抗値を有する抵抗素子として機能するためには非常に長い配線長が必要となる。たとえば65nmルールのプロセス技術による配線で100kΩの抵抗値を得るには配線長は50mm程度必要となる。このように配線長が長くなると半導体基板上での配線の面積が大きくなるので半導体装置の面積が大きくなってしまうという問題があった。

【0006】

本発明は、上記の問題に鑑みてなされたものであり、その目的は、抵抗素子として機能する配線を有し、かつ面積の小さな半導体装置およびその製造方法を提供することである。

【課題を解決するための手段】

【0007】

本発明の一実施の形態によれば、半導体装置は、半導体基板と、半導体基板上に設けられた配線層とを備えている。配線層は、第1の金属配線と、第2の金属配線と、第1および第2の金属配線を埋め込む絶縁膜とを含んでいる。第1の金属配線は、第1の金属部と、第1の金属部の底面側および側面側を覆う第1の金属膜とを有している。第2の金属配線は、絶縁部と、絶縁部の底面側および側面側を覆う第2の金属膜とを有している。

【0008】

本発明の一実施の形態によれば、半導体装置の製造方法は、第1の金属部および第1の金属膜を有する第1の金属配線と、絶縁部および第2の金属膜を有する第2の金属配線とを含む半導体装置の製造方法であって、以下の工程を備えている。

【0009】

まず半導体基板上に絶縁膜が堆積される。この絶縁膜の第1の金属配線が形成される領域に、第1の溝部が形成される。この第1の溝部の底面側および側面側を覆うように、第1の金属膜となる膜が堆積される。この第1の金属膜となる膜上に、第1の溝部を充填するように第1の金属部となる層が堆積される。第1の金属膜となる膜および第1の金属部となる層のうち第1の溝部の外側の部分が除去されることにより、第1の金属配線が形成される。絶縁膜の第2の金属配線が形成される領域に第2の溝部が形成される。この第2の溝部の底面側および側面側を覆うように、第2の金属膜となる膜が堆積される。この第2の金属膜となる膜上に、第2の溝部を充填するように金属層が堆積される。第2の金属膜となる膜および金属層のうち第2の溝部の外側の部分が除去されることにより、第2の金属膜と、絶縁部となる領域に形成された第2の金属部とが形成される。この第2の金属部が加熱されることで第2の金属部をなす金属が第2の溝部の側面側を覆う第2の金属膜を介して絶縁膜中に拡散することにより、第2の金属部の領域が空洞部にされる。

【発明の効果】

【0010】

本発明の一実施の形態によれば、半導体装置の第2の金属配線は底面側および側面側が第2の金属膜に覆われた絶縁部を有するため、第2の金属膜により底面側および側面側が覆われた部分が導体部である場合に比して、第2の金属配線の単位長さ当たりの抵抗値を大きくすることができる。よって短い配線長で大きな抵抗値を得ることができるので、半導体装置の面積を小さくすることができる。

【発明を実施するための最良の形態】

【0011】

以下、本発明の一実施の形態について図に基づいて説明する。

図1は、本発明の一実施の形態における半導体装置の構成を概略的に示す断面図である。

【0012】

図1を参照して、本実施の形態の半導体装置は、半導体基板SBと、第1〜第3の配線層L1〜L3と、第1〜第3の絶縁層I1〜I3とを有している。第1〜第3の配線層L1〜L3は、半導体基板SB上に順に積層された多層配線である。第1〜第3の配線層L1〜L3のそれぞれは、第1〜第3の絶縁層I1〜I3の各々により、半導体基板SBあるいは半導体基板SB側(図中下側)の他の配線層と絶縁されている。第1〜第3の絶縁層I1〜I3のそれぞれは、必要に応じてビア配線を有している。このビア配線により、第1〜第3の配線層L1〜L3の異なる層間の電気的接続が行なわれている。

【0013】

第2の配線層L2(配線層)は、第1の金属配線と、第2の金属配線と、第1および第2の金属配線を埋込む絶縁膜7および8とを有している。第1の金属配線は、通常の配線WRと、ガードリングGRとを有している。第2の金属配線は、通常の配線WRよりも単位長さ当たりの抵抗値が大きい高抵抗配線REを有している。ガードリングGRは、第2の配線層L2において高抵抗配線REを取囲むように設けられている。すなわち、半導体基板SB上において、ガードリングGRの平面パターンが高抵抗配線REの平面パターンを取囲んでいる。

【0014】

通常の配線WRは、銅(Cu)からなる第1の銅部(第1の金属部)10Wと、第1のバリアメタル膜(第1の金属膜)9Wと、高融点金属膜11Wとを有している。またガードリングGRは、銅(Cu)からなる第1の銅部(第1の金属部)10Gと、第1のバリアメタル膜(第1の金属膜)9Gと、高融点金属膜11Gとを有している。第1のバリアメタル膜9Wおよび9Gのそれぞれは、第1の銅部10Wおよび10Gの各々の底面側(半導体基板SB側)および側面側(図中横側)を覆っている。高融点金属膜11Wおよび11Gのそれぞれは、第1の銅部10Wおよび10Gの各々の上面側を覆っている。

【0015】

高抵抗配線REは、絶縁部である空洞部CVと、第2のバリアメタル膜19R(第2の金属膜)と、高融点金属膜21Rとを有している。第2のバリアメタル膜19Rは、空洞部CVの底面側(半導体基板SB側)および側面側(図中横側)を覆っている。高融点金属膜21Rは空洞部CVの上面側を覆っている。

【0016】

第2のバリアメタル膜19Rの空洞部CVの底面側を覆う部分の膜厚Cは、側面側を覆う部分の膜厚Bよりも大きい。膜厚BおよびCのそれぞれは、たとえば1〜5nm程度である。

【0017】

膜厚Bは、第1のバリアメタル膜9Wの第1の銅部10Wの側面側を覆う部分の膜厚A1よりも小さい。また膜厚Bは、第1のバリアメタル膜9Gの第1の銅部10Gの側面側を覆う部分の膜厚A2よりも小さい。膜厚A1およびA2のそれぞれは、たとえば1〜20nm程度である。

【0018】

第1のバリアメタル膜9Wおよび9Gは、第1の金属部10Wおよび10Gをなす材質である銅(Cu)の熱的な拡散を阻止する能力が高い材質からなる。第2のバリアメタル膜19Rは、第1のバリアメタル膜9Wおよび9Gのそれぞれの材質よりも、上記の熱的な拡散を阻止する能力が低い材質からなる。第1および第2のバリアメタル膜9W、9Gおよび19Rの材質は、たとえばTa(タンタル)、TaN(窒化タンタル)、WN(窒化タングステン)、CuSiO(酸化銅シリサイド)、RuO(酸化ルテニウム)、CuMo(銅−モリブデン)などである。

【0019】

絶縁膜8は、低誘電率膜、すなわち二酸化シリコンよりも低い誘電率を有する材質からなる膜である。この材質としては、たとえばSiOC(炭素含有酸化シリコン)がある。

【0020】

絶縁膜7は、絶縁膜8よりも小さい膜厚を有している。また絶縁膜7の材質は、絶縁膜8よりもエッチングレートを低くすることができる材質からなる。絶縁膜7の材質は、たとえばSiCN(炭窒化シリコン)やSiCO(炭化酸化シリコン)、あるいはこれらの積層材料である。絶縁膜7の膜厚は、たとえば20〜60nmである。

【0021】

第2の絶縁層I2は、半導体基板SBと第2の配線層L2との間に位置している。第2の絶縁層I2は、ビア配線5Aおよび5Bと、ビア配線5Aおよび5Bを埋込む絶縁膜3および4とを有している。ビア配線5Aは、通常の配線WRの半導体基板SB側に接する面を有している。ビア配線5Bは、高抵抗配線REの半導体基板SB側に接する面を有している。

【0022】

絶縁膜3および4のそれぞれは、たとえば絶縁膜7および8の各々と同様の膜厚を有し、同様の材質からなる。

【0023】

第1の配線層L1は、配線2と絶縁膜1の一部とを有している。配線2は、ビア配線5Aまたは5Bを介して、第2の配線層L2と電気的に接続されている。

【0024】

第1の絶縁層I1は、絶縁膜1の一部を有している。また第1の絶縁層I1は、ビア配線(図示せず)を有している。このビア配線を介して半導体基板SBに形成された半導体素子(図示せず)と第1の配線層L1とが電気的に接続されている。

【0025】

第3の絶縁層I3は、ビア配線55と、このビア配線55を埋込む絶縁膜53および54とを有している。なお絶縁膜53の一部は高抵抗配線REおよびガードリングGRの間の部分も埋込んでいる。絶縁膜53および54のそれぞれは、たとえば絶縁膜7および8の各々と同様の材料からなる。

【0026】

配線層L3は、配線Wa、WbおよびWcと、これら配線Wa、WbおよびWcを埋込む絶縁膜57および58とを有している。配線Waは、銅(Cu)からなる銅部60aと、バリアメタル膜59aと、高融点金属膜61aとを有している。バリアメタル膜59aは、銅部60aの底面側(半導体基板SB側)および側面側(図中横側)を覆っている。高融点金属膜61aは、銅部60aの上面側を覆っている。

【0027】

配線WbおよびWcのそれぞれも、配線Waとほぼ同様の構成を有しており、銅部60b、60c、バリアメタル膜59b、59c、高融点金属膜61bおよび61cが設けられている。絶縁膜57および58のそれぞれは、たとえば絶縁膜7および8と同様の膜厚を有し、同様の材質からなる。

【0028】

高融点金属膜11W、11G、21R、61a、61bおよび61cの材料は、たとえばCoWP(コバルト−タングステン−リン)、CoWBP(コバルト−タングステン−ボロン−リン)、CoW(コバルト−タングステン)、NiP(ニッケル−リン)またはPb(鉛)などのめっき材料である。あるいはW(タングステン)またはAl(アルミニウム)など、選択CVD法が適用可能な材料が用いられてもよい。

【0029】

次に、本実施の形態における半導体装置の製造方法について説明する。

図2〜図23は、本発明の一実施の形態における半導体装置の製造方法を工程順に示す概略断面図である。

【0030】

図2を参照して、通常の方法により、半導体基板SB上に、絶縁膜1と、この絶縁膜1の上面側に埋込まれた配線2とが形成される。これにより、第1の絶縁層I1および第1の配線層L1が形成される。

【0031】

図3〜図5を参照して、シングルダマシン法によりビア配線5Aおよび5Bの形成が以下のように行なわれる。

【0032】

図3を参照して、第1の配線層L1上に絶縁膜3および4が順に堆積される。絶縁膜3の膜厚は絶縁膜4の膜厚よりも小さくされる。また後に図4を用いて説明するエッチングにおいて絶縁膜3の材質のエッチングレートが絶縁膜4のエッチングレートよりも小さくすることができるように絶縁膜3および4の材質が選択される。

【0033】

絶縁膜3は、たとえばプラズマCVD法により形成される。絶縁膜3の材質は、たとえばSiCN(炭窒化シリコン)やSiCO(炭化酸化シリコン)の単層材料、あるいはこれらの積層材料が選択される。絶縁膜3の膜厚は、たとえば20〜60nmとされる。絶縁膜4の材質はSiOC(炭素含有酸化シリコン)などの低誘電率材料(low−K材)が用いられる。

【0034】

絶縁膜4上に写真製版法によりレジストマスク41が形成される。このレジストマスク41を用いて、絶縁膜3および4のエッチングが行なわれる。この後、レジストマスク41が除去される。

【0035】

図4および図5を参照して、上記エッチングにより絶縁膜3および4にビアホールVHが形成される。ビアホールVHは配線2の一部が露出するように設けられる。次にこのビアホールVHに金属の充填が行なわれることにより、ビア配線5Aおよび5Bが形成される。以下にこの金属の充填の方法について詳しく説明する。

【0036】

まずビアホールVHの底面および側面を被覆するようにバリアメタル膜がたとえばスパッタ法により形成される。このバリアメタル膜の膜厚は、たとえば5〜20nmである。またバリアメタル膜の材質としては、Ta(タンタル)、TaN(窒化タンタル)、WN(窒化タングステン)、CuSiO(酸化銅シリサイド)、RuO(酸化ルテニウム)またはCuMo(銅−モリブデン)などのCu(銅)の熱的な拡散を抑制する能力が高い材質が選択される。バリアメタル膜は、上記材質からなる単層膜、あるいは上記材料の複数が組合された積層膜とされることができる。

【0037】

上記のバリアメタル膜の形成後、連続してCu(銅)電解めっき法のための電極膜が形成される。電極膜の膜厚は、たとえば5〜20nmである。また電極膜の材料としては、電気固有抵抗が50μΩ・cm程度の材料が選択される。具体的には、Cu(銅)を用いることができる。あるいはCu(銅)、Al(アルミニウム)、Ti(チタン)、Mg(マグネシウム)、Zn(亜鉛)、B(ボロン)などを含む合金を用いることができる。なお上記のバリアメタル膜を電極膜として用いることにより、別途電極膜を形成することを省略することができる。

【0038】

次に上記電極膜上の全面に電解めっき法によりCu(銅)からなるめっき膜が形成される。これによりビアホールVHが完全に充填される。次に100〜400℃の熱処理が行なわれ、上記めっき膜の結晶性が改善される。次にCMP(Chemical Mechanical Polishing)によりビアホールVHの外側の膜が除去されることにより、第2の絶縁層I2が形成される。

【0039】

図6〜図10を参照して、主にシングルダマシン法を用いて通常の配線WRおよびガードリングGRの形成が以下のように行なわれる。

【0040】

主に図6を参照して、第2の絶縁層I2上に絶縁膜7および8が順に堆積される。絶縁膜7および8のそれぞれの形成方法、膜厚および材質は、絶縁膜3および4(図3)と同様とすることができる。

【0041】

絶縁膜8上のレジストマスク42が形成される。このレジストマスク42を用いて絶縁膜7および8のエッチングが行なわれる。その後、レジストマスク42の除去が行なわれる。

【0042】

主に図7を参照して、上記のエッチングにより絶縁膜7および8に第1の溝部TWおよびTGが形成される。第1の溝部TWはビア配線5Aが露出するように設けられる。第1の溝部TGは、絶縁膜4のビア配線5Bを取囲む部分が露出するようにもうけられる。なお第1の溝部TWおよびTGのそれぞれが形成される領域は、第1の金属配線WRおよびGR(図1)の各々が形成される領域に対応している。

【0043】

主に図7および図8を参照して、第1の溝部TWおよびTGの底面側および側面側が覆われるように、金属膜9が堆積される。この金属膜9は、第1のバリアメタル膜9Wおよび9G(図1)となる膜である。金属膜9が第1の溝部TWおよびTGのそれぞれの側面側を覆う部分の膜厚は、膜厚A1およびA2の各々である。金属膜9の形成方法および材料は、図5の工程で説明したバリアメタル膜と同様とすることができる。膜厚A1およびA2のそれぞれは、たとえば1〜20nm程度である。

【0044】

次に金属膜9上に、第1の溝部TWおよびTGが充填されるように銅(Cu)層10が堆積される。銅層10の堆積方法は、図5の工程で説明した銅(Cu)からなるめっき膜のめっき方法と同様である。次に図5の工程と同様の熱処理により、銅層10の結晶性が改善される。

【0045】

主に図8および図9を参照して、CMPにより第1の溝部TWおよびTGの外側の金属膜9および銅層10が除去される。これにより第1のバリアメタル膜9Wおよび9Gと、第1の銅部10Wおよび10Gとが形成される。

【0046】

図10を参照して、第1のバリアメタル膜9Wおよび第1の銅部10Wの上に選択的に高融点金属膜11Wが形成される。また第1のバリアメタル膜9Gおよび第1の銅部10Gの上に選択的に高融点金属膜11Gが形成される。

【0047】

高融点金属膜11Wおよび11Gの形成方法としては、無電解めっき法を用いることができる。この場合、高融点金属膜11Wおよび11Gの材質としては、たとえばCoWP(コバルト−タングステン−リン)やCoWBP(コバルト−タングステン−ボロン−リン)、CoW(コバルト−タングステン)、NiP(ニッケル−リン)、Pb(鉛)などを用いることができる。あるいは無電解めっき法の代わりに選択CVD法を用いて、高融点金属膜11Wおよび11Gとして、W(タングステン)やAl(アルミニウム)からなる膜を形成してもよい。

【0048】

以上により、通常の配線WRおよびガードリングGRが形成される。

次に、図11〜図17を参照して、高抵抗配線REの形成が以下のように行なわれる。

【0049】

図11を参照して、通常の配線WR、ガードリングGRおよび絶縁膜8を覆うようにレジストマスク43が形成される。レジストマスク43は、平面パターンとして、ガードリングGRに囲まれた領域内であって、かつビア配線5Bを含む領域に開口部を有している。このレジストマスク43を用いて絶縁膜7および8のエッチングが行なわれる。その後、レジストマスク43が除去される。

【0050】

主に図12を参照して、上記エッチングにより絶縁膜7および8に第2の溝部TRが形成される。第2の溝部TRが形成される領域は、高抵抗配線RE(図1)が形成される領域に対応している。

【0051】

主に図12および図13を参照して、第2の溝部TRの底面側および側面側が覆われるように、金属膜19が堆積される。この金属膜19は第2のバリアメタル膜19Rとなる膜である。

【0052】

金属膜19は、金属膜19の第2の溝部TRの底面側を覆う部分の膜厚Cが、金属膜19の第2の溝部TRの側面側を覆う部分の膜厚Bよりも大きくなるように堆積される。すなわちステップカバレッジの悪い方法による堆積が行なわれる。

【0053】

また金属膜19の堆積は、金属膜19の第2の溝部TRの側面側を覆う部分が金属膜9の第1の溝部TWおよびTGの側面側を覆う部分よりも第1の金属部10Wおよび10Gの材質である銅(Cu)の熱的拡散を阻止する能力が低くなるように行なわれる。上記能力を低くするため、最適な膜厚の選択と、最適な材質の選択との少なくともいずれかが行なわれる。

【0054】

最適な膜厚の選択としては、金属膜19の膜厚Bが金属膜9の膜厚A1およびA2(図8)のそれぞれよりも小さくされる。最適な材質の選択としては、金属膜19の材質が、金属膜9(図8)の材質よりも、第1の金属部10Wおよび10Gの材質である銅(Cu)の熱的拡散を阻止する能力が低い材質とされる。金属膜19の材質は、たとえばTa(タンタル)やTaN(窒化タンタル)、WN(窒化タングステン)、CuSiO(酸化銅シリサイド)、RuO(酸化ルテニウム)、CuMo(銅−モリブデン)とされる。

【0055】

次に金属膜19上に、第2の溝部TR(図12)が充填されるように銅(Cu)層20が堆積される。銅層20の堆積方法は、図5の工程で説明した銅(Cu)からなるめっき膜の形成方法と同様である。ただし、銅層20に対しては熱処理は行なわれない。次に、銅層20のうち第2の溝部TRの外側の部分を除去するCMPが行なわれる。CMPの条件としては、銅層20が高速で除去される条件が用いられる。

【0056】

図14を参照して、上記CMPにより銅(Cu)からなる第2の銅部20R(第2の金属部)が形成される。次に第2の銅部20Rが削られにくい条件で、露出した金属膜19を除去するためのCMPが行なわれる。

【0057】

主に図15を参照して、上記CMPにより金属膜19のうち第2の溝部TR(図12)の外側の部分が除去されて、第2のバリアメタル膜19Rが形成される。

【0058】

主に図16を参照して、第2のバリアメタル膜19Rおよび第2の銅部20Rの上に選択的に高融点金属膜21Rが形成される。高融点金属膜21Rの材質および形成方法は、図10の工程で説明した高融点金属膜11Wおよび11Gと同様である。

【0059】

次に、第2の銅部20Rが加熱される。たとえば、加熱する温度は400℃から500℃で、絶縁膜の酸化を防止するため水素や不活性ガス雰囲気が望ましい。その時間は、バリアメタルの結晶性、膜厚によって3〜5時間程度となる。第2の銅部20Rは第1の銅部10Wおよび10Gと比して結晶性が悪いため、銅(Cu)の拡散が生じやすい。また図13に示すように膜厚Bが膜厚Cよりも小さいことから、第2の銅部20Rをなす金属である銅(Cu)は、第2の溝部TR(図12)の底面側ではなく側面側を覆う第2のバリアメタル膜19Rを介して図中矢印のように絶縁膜8中へと拡散する。

【0060】

なお、膜厚C(図13)が膜厚Bよりも大きいことから、第2の溝部TR(図12)の底面側を覆う第2のバリアメタル膜19Rを介しての半導体基板SB側への拡散は抑制される。またガードリングGRの存在によりガードリングGRよりも外側の絶縁膜8にまで上記の拡散が生じることは抑制される。また高融点金属膜21Rにより半導体基板SBと反対の側への拡散は抑制される。

【0061】

また図13の工程で説明したように、金属膜9の第1の溝部TWおよびTGの側面側を覆う部分は、金属膜19の第2の溝部TRの側面側を覆う部分よりも第1の金属部10Wおよび10Gの材質である銅(Cu)の熱的拡散を阻止する能力が高い。すなわち、第1のバリアメタル膜9Wおよび9Gの第1の溝部TWおよびTGの側面側を覆う部分は、第2のバリアメタル膜19Rの第2の溝部TRの側面側を覆う部分よりも第1の金属部10Wおよび10Gの材質である銅(Cu)の熱的拡散を阻止する能力が高い。これにより第1の銅部10Wおよび10Gのそれぞれをなす金属である銅(Cu)が第1のバリアメタル膜9Wおよび9Gの各々を介して絶縁膜8中へと拡散することは抑制される。

【0062】

図16および図17を参照して、上記の拡散により第2の銅部20Rの領域が、空洞部CVとなる。以上により高抵抗配線REが形成される。なお、図16の矢印に示す拡散により絶縁膜8(図16)が銅(Cu)を含有する変質膜23(図17)に変質する。

【0063】

図18および図19を参照して、変質膜23を露出し、かつ変質しなかった絶縁膜8を覆うようにレジストマスク44が形成される。次にこのレジストマスク44を用いて変質膜23のエッチングが行なわれる。このエッチングの際、変質膜23のエッチングレートが高融点金属膜21Rおよび11Gのエッチングレートよりも大きくなるような選択比が得られるようなエッチング条件が用いられる。この後、レジストマスク44が除去される。上記のエッチングにより変質膜23が除去される。

【0064】

図20を参照して、上記のように変質膜23が除去された部分を充填するように絶縁膜53が堆積される。次に絶縁膜53の上に絶縁膜54が堆積される。絶縁膜53および54のそれぞれの堆積方法および材質は、絶縁膜3および4(図3)と同様とすることができる。

【0065】

図21を参照して、シングルダマシン法により、通常の配線WR上に、絶縁膜53および54を貫通するビア配線55が形成される。

【0066】

図22を参照して、絶縁膜54およびビア配線55上に絶縁膜57および58が順に堆積される。絶縁膜57および58のそれぞれの堆積方法および材質は、絶縁膜3および4(図3)と同様とすることができる。

【0067】

主に図23を参照して、シングルダマシン法により、バリアメタル膜59a、59b、59c、銅(Cu)部60a、60bおよび60cが絶縁膜57および58に埋込まれる。次にバリアメタル膜59a、59b、59c、銅部60a、60bおよび60cの上に選択的に高融点金属膜61a、61bおよび61cが形成される。これにより配線Wa、WbおよびWc(図1)が形成される。以上により、図1に示す半導体装置が製造される。

【0068】

なお上記の製造方法においてシングルダマシン法を用いた工程についてはデュアルダマシン法を用いた工程に置換することもできる。

【0069】

本実施の形態の半導体装置およびその製造方法によれば、図1に示すように、高抵抗配線REは底面側および側面側を第2のバリアメタル膜19Rに覆われた絶縁部である空洞部CVを有している。このため第2のバリアメタル膜19Rにより底面側および側面側が覆われた部分が導体部である場合に比して、高抵抗配線REの単位長さ当たりの抵抗値を大きくすることができる。よって短い長さで抵抗素子として機能する高抵抗配線REを形成することができるので、半導体装置の面積を小さくすることができる。

【0070】

また、通常の配線WRは、上記の空洞部CVに対応する位置において、底面側および側面側を第1のバリアメタル膜9Wに覆われた導体部である第1の銅部10Wを有している。このため、通常の配線WRの単位長さ当たりの抵抗値を小さくすることができる。よって通常の配線WRを用いて半導体素子間や半導体素子と外部との間を少ない電気的損失で接続することができる。

【0071】

また高抵抗配線REは上記の様に空洞部CVを有することにより単位長さ当たりの抵抗を大きくすることができる。このため加工精度の十分な安定性が得られなくなるほどに高抵抗配線REの線幅を小さくしなくても、高抵抗配線REの単位長さ当たりの抵抗を十分に確保することができる。このため高抵抗配線REの線幅の加工ばらつきに起因する抵抗値のばらつきを、たとえばアナログ回路において一般に要求される5%程度の範囲に収めることができる。

【0072】

また単位長さ当たりの抵抗値が大きい抵抗配線REにより抵抗素子として機能する部分が形成されるので、抵抗配線REに比して単位長さ当たりの抵抗値が小さい通常の配線WRにより抵抗素子として機能する部分を形成する必要がない。このため、通常の配線WRに極端に長さの長い部分を設ける必要がない。これにより、たとえば通常の配線WRの99%を1mm以下程度の長さとすることができる。このように極端に長さの長い部分が設けられなくてもよいので、配線の長さが長い部分で生じやすいパターン欠陥や異物の付着の可能性が低減され、半導体装置の信頼性が向上する。

【0073】

また第2のバリアメタル膜19R(図1)の膜厚Cは膜厚Bよりも大きい。これにより、図16に示すように第2の銅部20Rをなす金属である銅(Cu)は、第2の溝部TR(図12)の底面側ではなく側面側を覆う第2のバリアメタル膜19Rを介して図中矢印のように絶縁膜8中へと拡散する。よって絶縁膜4の高抵抗配線REの下部の部分が銅(Cu)の拡散により変質することを防ぐことができる。

【0074】

また、図1に示すように第2のバリアメタル膜19Rの膜厚Bが、第1のバリアメタル膜9Wおよび9Gのそれぞれの膜厚A1およびA2のそれぞれよりも小さくされる。すなわち金属膜19(図13)の膜厚Bが金属膜9(図8)の膜厚A1およびA2のそれぞれよりも小さくされる。言い換えれば、金属膜19(図13)の第2の溝部TR(図12)の側面側を覆う部分が、金属膜9(図8)の第1の溝部TWおよびTG(図7)の側面側を覆う部分よりも、第1の金属部10Wおよび10Gの材質である銅(Cu)の熱的拡散を阻止する能力を低くすることができる。これにより、図16に示す銅(Cu)の拡散工程において、第1の銅部10Wおよび10Gから絶縁膜8への拡散を抑制しつつ、かつ第2の銅部20Rを絶縁膜8中に拡散させることができる。

【0075】

また、図1に示すように第2のバリアメタル膜19Rの材質が第1のバリアメタル膜9Wおよび9Gのそれぞれの材質よりも、第1の金属部10Wおよび10Gの材質である銅(Cu)の熱的拡散を阻止する能力が低い材質とされる。すなわち、金属膜19(図13)の材質が、金属膜9(図8)の材質よりも、第1の金属部10Wおよび10Gの材質である銅(Cu)の熱的拡散を阻止する能力が低い材質とされる。これにより、図16に示す銅(Cu)の拡散工程において、第1の銅部10Wおよび10Gから絶縁膜8への拡散を抑制しつつ、かつ第2の銅部を絶縁膜8中に拡散させることができる。

【0076】

また第1の金属配線WRおよびGRは、第2の配線層L2において高抵抗配線REを取り囲む部分であるガードリングGRを含んでいる。これにより、図16に示す第2の銅部20Rの拡散工程においてガードリングGRよりも外側の絶縁膜8にまで拡散が生じることが抑制される。

【0077】

また高抵抗配線REおよび通常の配線WRを埋め込む絶縁膜8(図1)は二酸化シリコンよりも低い誘電率を有する材質からなる膜(低誘電率膜)であるため、配線間の容量を抑制することができる。また一般に低誘電率膜は半導体装置の製造工程におけるRIE(Reactive Ion Etching)などのプラズマに曝されると特性が劣化し易いが、本実施の形態では絶縁膜8の表面が直接プラズマに曝されないため、低誘電率膜の本来の特性を発揮することができる。

【0078】

また、図1に示すように、ビア配線5Bは、高抵抗配線REの半導体基板SB側に接する面を有している。これにより高抵抗配線REに対して半導体基板SB側から電気的接続をとることができる。なお仮に高抵抗配線REに対して半導体基板SBと反対側から電気的接続をとる場合、高抵抗配線REの半導体基板SBと反対側にビア配線が形成される必要がある。この形成の前段階として高抵抗配線REの上層である第3の絶縁層にビアホールが形成される。このビアホールの形成時のエッチングは高融点金属膜21Rの領域内で停止させなければならない。なぜならばエッチングが過剰に進めばビアホールが空洞部CVとつながり空洞部CVに穴が空いてしまい、逆にエッチングが過小であれば高抵抗配線REとの電気的接続がとれなくなるからである。なお半導体装置の製造工程途中で空洞部CVに穴が空いてしまうと、その後に導電体の成膜が行なわれた際に空洞部CVだったところが導電体部となってしまい、高抵抗配線REにより諸名の抵抗が得られなくなる。

【0079】

また本実施の形態の半導体装置の製造方法によれば、図16に示すように第2の銅部20Rを加熱することで、第2の銅部20Rをなす銅(Cu)を第2の溝部TR(図12)の側面側を覆う第2のバリアメタル19Rを介して絶縁膜8に拡散させる工程を有している。これにより底面側および側面側を第2のバリアメタル膜19Rに覆われた空洞部CVを形成することができる。

【0080】

今回開示された実施の形態はすべての点で例示であって制限的なものではないと考えられるべきである。本発明の範囲は上記した説明ではなくて特許請求の範囲によって示され、特許請求の範囲と均等の意味および範囲内でのすべての変更が含まれることが意図される。

【産業上の利用可能性】

【0081】

本発明は、金属配線を有する半導体装置およびその製造方法に特に有利に適用され得る。

【図面の簡単な説明】

【0082】

【図1】本発明の一実施の形態における半導体装置の構成を概略的に示す断面図である。

【図2】本発明の一実施の形態における半導体装置の製造方法の第1工程を示す概略断面図である。

【図3】本発明の一実施の形態における半導体装置の製造方法の第2工程を示す概略断面図である。

【図4】本発明の一実施の形態における半導体装置の製造方法の第3工程を示す概略断面図である。

【図5】本発明の一実施の形態における半導体装置の製造方法の第4工程を示す概略断面図である。

【図6】本発明の一実施の形態における半導体装置の製造方法の第5工程を示す概略断面図である。

【図7】本発明の一実施の形態における半導体装置の製造方法の第6工程を示す概略断面図である。

【図8】本発明の一実施の形態における半導体装置の製造方法の第7工程を示す概略断面図である。

【図9】本発明の一実施の形態における半導体装置の製造方法の第8工程を示す概略断面図である。

【図10】本発明の一実施の形態における半導体装置の製造方法の第9工程を示す概略断面図である。

【図11】本発明の一実施の形態における半導体装置の製造方法の第10工程を示す概略断面図である。

【図12】本発明の一実施の形態における半導体装置の製造方法の第11工程を示す概略断面図である。

【図13】本発明の一実施の形態における半導体装置の製造方法の第12工程を示す概略断面図である。

【図14】本発明の一実施の形態における半導体装置の製造方法の第13工程を示す概略断面図である。

【図15】本発明の一実施の形態における半導体装置の製造方法の第14工程を示す概略断面図である。

【図16】本発明の一実施の形態における半導体装置の製造方法の第15工程を示す概略断面図である。

【図17】本発明の一実施の形態における半導体装置の製造方法の第16工程を示す概略断面図である。

【図18】本発明の一実施の形態における半導体装置の製造方法の第17工程を示す概略断面図である。

【図19】本発明の一実施の形態における半導体装置の製造方法の第18工程を示す概略断面図である。

【図20】本発明の一実施の形態における半導体装置の製造方法の第19工程を示す概略断面図である。

【図21】本発明の一実施の形態における半導体装置の製造方法の第20工程を示す概略断面図である。

【図22】本発明の一実施の形態における半導体装置の製造方法の第21工程を示す概略断面図である。

【図23】本発明の一実施の形態における半導体装置の製造方法の第22工程を示す概略断面図である。

【符号の説明】

【0083】

CV 空洞部、GR ガードリング、I1〜I3 第1〜第3の絶縁層、L1〜L3 第1〜第3の配線層、RE 高抵抗配線、SB 半導体基板、WR 通常の配線、1,3,4,7,8,53,54,57,58 絶縁膜、2 配線、5A,5B ビア配線、9,19 金属膜、9W,9G 第1のバリアメタル膜、10W,10G 第1の銅部、11G,11W,21R 高融点金属膜、19R 第2のバリアメタル膜、20R 第2の銅部、23 変質膜。

【特許請求の範囲】

【請求項1】

半導体基板と、前記半導体基板上に設けられた配線層とを備えた半導体装置であって、

前記配線層は、第1の金属配線と、第2の金属配線と、前記第1および第2の金属配線を埋め込む絶縁膜とを含み、

前記第1の金属配線は、第1の金属部と、前記第1の金属部の底面側および側面側を覆う第1の金属膜とを有し、

前記第2の金属配線は、絶縁部と、前記絶縁部の底面側および側面側を覆う第2の金属膜とを有する、半導体装置。

【請求項2】

前記絶縁部は空洞部である、請求項1に記載の半導体装置。

【請求項3】

前記第2の金属膜の前記絶縁部の底面側を覆う部分の膜厚は、前記第2の金属膜の前記絶縁部の側面側を覆う部分の膜厚よりも大きい、請求項1または2に記載の半導体装置。

【請求項4】

前記第2の金属膜の前記絶縁部の側面側を覆う部分の膜厚は、前記第1の金属膜の前記第1の金属部の側面側を覆う部分の膜厚よりも小さい、請求項1〜3のいずれかに記載の半導体装置。

【請求項5】

前記第2の金属膜は、前記第1の金属膜の材質よりも前記第1の金属部の材質の熱的拡散を阻止する能力が低い材質からなる、請求項1〜4のいずれかに記載の半導体装置。

【請求項6】

前記第1の金属配線は、前記配線層において前記第2の金属配線を取り囲む部分を含む、請求項1〜5のいずれかに記載の半導体装置。

【請求項7】

前記絶縁膜は、二酸化シリコンよりも低い誘電率を有する材料からなる部分を含む、請求項1〜6のいずれかに記載の半導体装置。

【請求項8】

前記半導体基板と前記配線層との間に位置する絶縁層をさらに備え、

前記絶縁層は、ビア配線と、前記ビア配線を埋め込む絶縁膜とを含み、

前記ビア配線は、前記第2の金属配線の前記半導体基板側に接する面を有する、請求項1〜7のいずれかに記載の半導体装置。

【請求項9】

第1の金属部および第1の金属膜を有する第1の金属配線と、絶縁部および第2の金属膜を有する第2の金属配線とを含む半導体装置の製造方法であって、

半導体基板上に絶縁膜を堆積する工程と、

前記絶縁膜の前記第1の金属配線が形成される領域に第1の溝部を形成する工程と、

前記第1の溝部の底面側および側面側を覆うように前記第1の金属膜となる膜を堆積する工程と、

前記第1の金属膜となる膜上に、前記第1の溝部を充填するように前記第1の金属部となる層を堆積する工程と、

前記第1の金属膜となる膜および前記第1の金属部となる層のうち前記第1の溝部の外側の部分を除去することにより、前記第1の金属配線を形成する工程と、

前記絶縁膜の前記第2の金属配線が形成される領域に第2の溝部を形成する工程と、

前記第2の溝部の底面側および側面側を覆うように前記第2の金属膜となる膜を堆積する工程と、

前記第2の金属膜となる膜上に、前記第2の溝部を充填するように金属層を堆積する工程と、

前記第2の金属膜となる膜および前記金属層のうち前記第2の溝部の外側の部分を除去することにより、前記第2の金属膜と、前記絶縁部となる領域に形成された第2の金属部とを形成する工程と、

前記第2の金属部を加熱することで前記第2の金属部をなす金属を前記第2の溝部の側面側を覆う前記第2の金属膜を介して前記絶縁膜中に拡散させることにより、前記第2の金属部の領域を空洞部にする工程とを備えた、半導体装置の製造方法。

【請求項10】

前記第2の金属膜となる膜を堆積する工程は、前記第2の金属膜となる膜の前記第2の溝部の底面側を覆う部分の膜厚が前記第2の金属膜となる膜の前記第2の溝部の側面側を覆う部分の膜厚よりも大きくなるように行なわれる、請求項9に記載の半導体装置の製造方法。

【請求項11】

前記第1の金属膜となる膜を堆積する工程と、前記第2の金属膜となる膜を堆積する工程とは、前記第2の金属膜となる膜の前記第2の溝部の側面側を覆う部分の膜厚が、前記第1の金属膜となる膜の前記第1の溝部の側面側を覆う部分の膜厚よりも小さくなるように行なわれる、請求項9または10に記載の半導体装置の製造方法。

【請求項1】

半導体基板と、前記半導体基板上に設けられた配線層とを備えた半導体装置であって、

前記配線層は、第1の金属配線と、第2の金属配線と、前記第1および第2の金属配線を埋め込む絶縁膜とを含み、

前記第1の金属配線は、第1の金属部と、前記第1の金属部の底面側および側面側を覆う第1の金属膜とを有し、

前記第2の金属配線は、絶縁部と、前記絶縁部の底面側および側面側を覆う第2の金属膜とを有する、半導体装置。

【請求項2】

前記絶縁部は空洞部である、請求項1に記載の半導体装置。

【請求項3】

前記第2の金属膜の前記絶縁部の底面側を覆う部分の膜厚は、前記第2の金属膜の前記絶縁部の側面側を覆う部分の膜厚よりも大きい、請求項1または2に記載の半導体装置。

【請求項4】

前記第2の金属膜の前記絶縁部の側面側を覆う部分の膜厚は、前記第1の金属膜の前記第1の金属部の側面側を覆う部分の膜厚よりも小さい、請求項1〜3のいずれかに記載の半導体装置。

【請求項5】

前記第2の金属膜は、前記第1の金属膜の材質よりも前記第1の金属部の材質の熱的拡散を阻止する能力が低い材質からなる、請求項1〜4のいずれかに記載の半導体装置。

【請求項6】

前記第1の金属配線は、前記配線層において前記第2の金属配線を取り囲む部分を含む、請求項1〜5のいずれかに記載の半導体装置。

【請求項7】

前記絶縁膜は、二酸化シリコンよりも低い誘電率を有する材料からなる部分を含む、請求項1〜6のいずれかに記載の半導体装置。

【請求項8】

前記半導体基板と前記配線層との間に位置する絶縁層をさらに備え、

前記絶縁層は、ビア配線と、前記ビア配線を埋め込む絶縁膜とを含み、

前記ビア配線は、前記第2の金属配線の前記半導体基板側に接する面を有する、請求項1〜7のいずれかに記載の半導体装置。

【請求項9】

第1の金属部および第1の金属膜を有する第1の金属配線と、絶縁部および第2の金属膜を有する第2の金属配線とを含む半導体装置の製造方法であって、

半導体基板上に絶縁膜を堆積する工程と、

前記絶縁膜の前記第1の金属配線が形成される領域に第1の溝部を形成する工程と、

前記第1の溝部の底面側および側面側を覆うように前記第1の金属膜となる膜を堆積する工程と、

前記第1の金属膜となる膜上に、前記第1の溝部を充填するように前記第1の金属部となる層を堆積する工程と、

前記第1の金属膜となる膜および前記第1の金属部となる層のうち前記第1の溝部の外側の部分を除去することにより、前記第1の金属配線を形成する工程と、

前記絶縁膜の前記第2の金属配線が形成される領域に第2の溝部を形成する工程と、

前記第2の溝部の底面側および側面側を覆うように前記第2の金属膜となる膜を堆積する工程と、

前記第2の金属膜となる膜上に、前記第2の溝部を充填するように金属層を堆積する工程と、

前記第2の金属膜となる膜および前記金属層のうち前記第2の溝部の外側の部分を除去することにより、前記第2の金属膜と、前記絶縁部となる領域に形成された第2の金属部とを形成する工程と、

前記第2の金属部を加熱することで前記第2の金属部をなす金属を前記第2の溝部の側面側を覆う前記第2の金属膜を介して前記絶縁膜中に拡散させることにより、前記第2の金属部の領域を空洞部にする工程とを備えた、半導体装置の製造方法。

【請求項10】

前記第2の金属膜となる膜を堆積する工程は、前記第2の金属膜となる膜の前記第2の溝部の底面側を覆う部分の膜厚が前記第2の金属膜となる膜の前記第2の溝部の側面側を覆う部分の膜厚よりも大きくなるように行なわれる、請求項9に記載の半導体装置の製造方法。

【請求項11】

前記第1の金属膜となる膜を堆積する工程と、前記第2の金属膜となる膜を堆積する工程とは、前記第2の金属膜となる膜の前記第2の溝部の側面側を覆う部分の膜厚が、前記第1の金属膜となる膜の前記第1の溝部の側面側を覆う部分の膜厚よりも小さくなるように行なわれる、請求項9または10に記載の半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【公開番号】特開2009−111258(P2009−111258A)

【公開日】平成21年5月21日(2009.5.21)

【国際特許分類】

【出願番号】特願2007−283815(P2007−283815)

【出願日】平成19年10月31日(2007.10.31)

【出願人】(503121103)株式会社ルネサステクノロジ (4,790)

【Fターム(参考)】

【公開日】平成21年5月21日(2009.5.21)

【国際特許分類】

【出願日】平成19年10月31日(2007.10.31)

【出願人】(503121103)株式会社ルネサステクノロジ (4,790)

【Fターム(参考)】

[ Back to top ]