半導体装置およびその製造方法

【課題】同一導電型のチャネル領域を有し、かつ閾値電圧の異なる複数の半導体素子を有する半導体装置を提供する。

【解決手段】閾値電圧が互いに異なる2つのトランジスタが同一半導体基板上に形成された半導体装置において、トランジスタのゲート電極は、半導体基板上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成された、第2金属を含み第1金属を主成分とする金属層とを含み、更に、一方のトランジスタが、ゲート絶縁膜と金属層との間に、第2金属の酸化膜を含む。

【解決手段】閾値電圧が互いに異なる2つのトランジスタが同一半導体基板上に形成された半導体装置において、トランジスタのゲート電極は、半導体基板上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成された、第2金属を含み第1金属を主成分とする金属層とを含み、更に、一方のトランジスタが、ゲート絶縁膜と金属層との間に、第2金属の酸化膜を含む。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、閾値電圧の異なる複数の半導体素子を含む半導体装置およびその製造方法に関し、特に、同一半導体基板上に閾値電圧の異なる複数のMOSFETを含む半導体装置およびその製造方法に関する。

【背景技術】

【0002】

閾値電圧(Vt)の異なる複数のMOSFETを同一基板上に作製する場合、従来は、チャネル領域に選択的にイオンを注入することにより、MOSFETの閾値電圧を変える方法が用いられていた。また、それぞれのゲート電極を、仕事関数の異なる金属材料から作製する方法も用いられていた(例えば、非特許文献1参照)。

【非特許文献1】F. Ootsuka, et. al., "Full Metal-Gate Integration of Dual-Metal-Gate HfSON CMOS Transistors by Using Oxidation-Free Dummy-Mask Process", SSDM2006. pp.1116

【発明の開示】

【発明が解決しようとする課題】

【0003】

しかしながら、チャネル領域にイオンを注入する方法では、MOSFETの微細化にともない、注入されるイオン量のばらつきが閾値電圧の値に影響し、閾値電圧がばらつくという問題があった。

一方、仕事関数の異なる金属材料からゲート電極を作製する方法では、導電型の異なるMOSFETには適用できるが、同一導電型のMOSFETで異なる閾値電圧をもたせることが困難であるという問題があった。あえて、同一導電型のMOSFETのゲート電極を、異なる金属材料から形成した場合、製造工程が複雑化するとともに、製造コストが高くなり、現実的ではなかった。

【0004】

そこで、本発明は、同一導電型のチャネル領域を有し、かつ閾値電圧の異なる複数の半導体素子を有する半導体装置の提供を目的とする。

【課題を解決するための手段】

【0005】

本発明の一実施例によれば、閾値電圧が互いに異なる2つのトランジスタが同一半導体基板上に形成された半導体装置であって、トランジスタのゲート電極は、半導体基板上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成された、第2金属を含み第1金属を主成分とする金属層とを含み、更に、一方のトランジスタが、ゲート絶縁膜と金属層との間に、第2金属の酸化膜を含む半導体装置が提供される。

【0006】

本発明の他の実施例によれば、閾値電圧が互いに異なる2つのトランジスタを同一半導体基板上に形成する半導体装置の製造方法であって、半導体基板を準備する工程と、半導体基板上に、ゲート絶縁膜を形成する工程と、ゲート絶縁膜上に、第2金属を含み第1金属を主成分とする金属層を形成する工程と、ゲート絶縁膜と金属層をエッチングして、ゲート絶縁膜と金属層とを含む第1および第2のゲート電極を形成する工程と、それぞれのゲート電極の両側にソース/ドレイン領域を形成する工程と、第1のゲート電極の温度が第2のゲート電極の温度より高くなるように加熱し、第1のゲート電極の金属層中の第2金属の酸化物を、金属層とゲート絶縁膜との間に形成する加熱工程とを含む製造方法が提供される。

【発明の効果】

【0007】

本発明では、同一半導体基板上に閾値電圧の異なる複数の半導体素子を含む半導体装置の提供が可能となる。特に、同一導電型のチャネル領域を有し、閾値電圧の異なる複数の半導体素子を含む半導体装置の提供が可能となる。

【発明を実施するための最良の形態】

【0008】

実施の形態1.

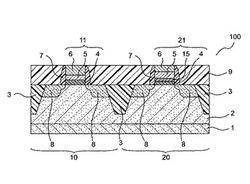

図1は、全体が100で表される、本発明の実施の形態1にかかる半導体装置の断面図である。半導体装置100は、同一半導体基板1の上に、閾値電圧(Vt)の異なる、同一導電型のチャネル領域を有する第1半導体素子10、第2半導体素子20が、それぞれ形成されている。

【0009】

シリコン等の半導体基板1の上には、シリコン層等の半導体層2が形成される。半導体層2は、例えばウエル構造であっても構わない。半導体層2には、例えば、酸化シリコンが埋め込まれた素子分離領域3が形成されている。第1半導体素子10と第2半導体素子20とは、素子分離領域3により電気的に分離されている。

【0010】

第1半導体素子10は、ゲート絶縁膜4、金属層5、低抵抗金属層6からなるゲート電極11を含み、ゲート電極11を挟むように、ソース/ドレイン領域3が設けられている。

また、第2半導体素子20は、ゲート絶縁膜4、金属層5、低抵抗金属層6、およびゲート絶縁膜4と金属層5との間に設けられた金属酸化膜15を含む。また、ゲート電極11を挟むように、ソース/ドレイン領域8が設けられている。

【0011】

ゲート絶縁膜は、HfO2、HfSiO、HfSiON等のHf系のhigh−k(高誘電体)材料から形成されるが、SiO2、SiON等を用いることも可能である。

【0012】

また、Hf系のhigh−k(高誘電体)材料を用いる場合は、半導体表面2との界面にSiO2、SiONを有する場合もある。

【0013】

金属層5は、主に第1金属あるいはその窒化物もしくは炭化物からなり、第1金属とは異なる第2金属を含む。第2金属の含有量は、組成比で30%以下であることが好ましい。

半導体素子のチャネル領域がp型チャネル領域を有する場合、第1金属は、例えばRu、Ir、Pt、Pd、Re、W、Mo、Ni、TiおよびCoから選択される金属からなる。また、第2金属は、例えばAlからなる。Al以外にTi、Ta、もしくはランタノイド系(La、Ce、Pr、Nd、Pm、Sm、En、Gd、Tb、Dy、Ho、Er、Tm、Yb、Lu)等の希土類金属を用いても構わない。

一方、半導体素子のチャネル領域がn型の場合、第1金属は、例えば、Al、Ga、In、Tl、Rb、Bi、Ti、Zr、Hf、V、Nb、TaおよびMn等からなり、第2金属は、例えばMg、Li、Be、Ca、Srまたは上記ランタノイド系の希土類金属からなる。

【0014】

低抵抗金属層6は、例えばW、シリサイド金属もしくはシリサイド金属とポリシリコンの積層膜からなる。

【0015】

金属酸化膜15は、金属層5に含まれる第2金属の酸化物からなり、例えば第2金属がアルミニウム(Al)の場合は酸化アルミニウム(AlOx等)からなり、第2金属がマグネシウム(Mg)の場合は酸化マグネシウム(MgOx等)からなる。

【0016】

金属酸化膜15が形成されることにより、第2半導体素子20の閾値電圧は、金属酸化膜15を含まない第1半導体素子10の閾値電圧より高くなる。これにより、同一導電型のチャネル領域を有し、かつ閾値電圧の異なる2つの半導体素子10、20を、同一半導体基板1の上に形成できる。

【0017】

ゲート電極11、21の両側面は、例えば酸化シリコンからなるサイドウォール7で覆われている。更に、半導体基板1の上には、例えば酸化シリコンからなる層間絶縁層9が形成されている。

【0018】

次に、図2を用いて、本実施の形態1にかかる半導体装置100の製造方法について説明する。図2は、半導体装置100の製造工程の断面図であり、図2中、図1と同一符号は、同一または相当箇所を示す。かかる製造工程は、以下の工程1〜5を含む。

【0019】

工程1:図2(a)に示すように、シリコン等の半導体基板1を準備する。続いて、半導体基板1の上に、例えばシリコンからなる半導体層2を形成する。更に、半導体層2中に、例えば酸化シリコンからなる素子分離領域3を形成する。素子分離領域3で分離された領域に、第1半導体素子10、第2半導体素子20が形成される。

【0020】

工程2:図2(b)に示すように、ゲート絶縁膜4、金属層5、および低抵抗金属層6を、例えばスパッタ法やCVD法で作製する。ゲート絶縁膜4は、HfSiON等のhigh−k(高誘電体)材料から形成される。

【0021】

金属層5は、第1金属を主成分とし、第1金属とは異なる第2金属を含む。半導体素子のp型チャネル領域を有する場合、第1金属は、例えばRuからなり、第2金素は、例えばAlからなる。一方、半導体素子のチャネル領域がn型の場合、第1金属は、例えば、TaSiNからなり、第2金属はMgからなる。また、低抵抗金属層6は、例えばWからなる。

【0022】

工程3:図2(c)に示すように、例えばハードマスク(図示せず)を用いてゲート絶縁膜4、金属層5、および低抵抗金属層6をエッチングし、ゲート電極11、21を形成する。続いて、ゲート電極11、21の側壁に、例えば酸化シリコンからなるサイドウォール7を形成する。続いて、ゲート電極11、21を注入マスクに用いたイオン注入および活性化アニールにより、ソース/ドレイン領域8を形成する。活性化アニールの温度は、例えば800℃である。ソース/ドレイン領域8は、エクステンション領域を含んでも構わない。

【0023】

工程4:図2(d)に示すように、例えば酸化シリコンからなる層間絶縁層9を形成し、更に、ゲート電極21を覆うように光吸収膜30を形成する。光吸収膜30は、例えばアモルファスカーボン(a−C)からなる。光吸収膜は、例えば破線31で示すように、第2半導体素子20の上方を覆うように形成しても構わない。

【0024】

かかる状態でレーザアニールやランプアニールを行う。具体的には、半導体基板1の上面(図2(d)では上方向)からレーザ光やランプ光のような光を照射する。このアニールは、ソース/ドレイン領域8の活性化アニール温度より高い温度で行われ、例えばソース/ドレイン領域活性化アニールが800℃の時は850℃以上、好適には900℃で行われる。アニール時間は、数ミリ秒以下である。かかるアニールでは、光吸収膜30を形成したゲート電極21の温度が、光吸収膜30を形成しないゲート電極11の温度より高くなる。これにより、金属層5中の第2金属(Al)が、金属層5とゲート絶縁膜4との間に析出して酸化され、酸化アルミニウム(AlOx)となる。

【0025】

工程5:図2(e)に示すように、光吸収膜30を除去する。この結果、第2半導体素子20は、ゲート絶縁膜4と金属層5との間に金属酸化膜15が形成されたゲート電極21を有するようになる。

【0026】

以上の工程で、本発明の実施の形態1にかかる半導体装置100が完成する。なお、配線層等は、必要に応じて適宜形成しても構わない。

【0027】

図3は、閾値電圧、仕事関数の、アニール温度依存性を示す。横軸はアニール温度(ゲート電極の温度)であり、縦軸はゲート電極の仕事関数と、そのゲート電極を有する半導体素子の閾値電圧である。ゲート電極は、HfSiONからなるゲート絶縁膜、Al(Alの組成比が10%)を第2金属として含むRuの金属層、およびWの低抵抗金属層が積層された構造である。

【0028】

図3から分かるように、アニール温度が800℃程度では金属酸化膜(AlOx)が形成されず、アニール温度が900℃程度では金属酸化膜(AlOx)が形成されている。これに伴い、仕事関数は、約4.5eVから約4.7eVと大きくなり、閾値電圧も、Vt1からVt2まで大きくなる。アニール温度が850℃を超えると、金属酸化膜が析出することが確認されている。

【0029】

このように、本実施の形態1にかかる製造方法では、ゲート電極を形成した後に熱処理を行うことにより、特定のゲート電極中に金属酸化膜を形成して閾値電圧を変えることができる。これにより、同一半導体基板上に、閾値電圧の異なる複数の半導体素子を、容易に形成することができる。

【0030】

なお、本実施の形態1では、図2(d)に示すように、高い温度で熱処理するゲート電極の上に光吸収膜30を形成したが、逆に、低い温度で熱処理するゲート電極の上に光反射膜を形成しても良い。

例えば、図2(d)において、ゲート電極11の上、または第1半導体素子10の上を覆うように、光反射膜を形成しても構わない。光反射膜は、例えばSiON等からなる。

【0031】

実施の形態2.

実施の形態1では、第2半導体素子20の、ゲート絶縁膜4と金属層5との間に金属酸化膜15が形成されたが、半導体層2とゲート絶縁膜4との間に金属酸化膜15が形成される場合もある。例えば、ゲート絶縁膜4にHfSiOを用いた場合、金属層5中の第2金属Alは、熱処理工程でゲート絶縁膜4中を移動し、ゲート絶縁膜4の下面に金属酸化膜(AlOx)を形成する。このような金属酸化膜の形成によっても、閾値電圧を変えることが可能となる。

なお、半導体層2の表面にシリコン酸化膜がある場合、シリコン酸化膜とゲート絶縁膜4との間に金属酸化膜15が形成されることとなる。

【0032】

実施の形態3.

実施の形態1、2では、第1金属を主成分とする金属層5中に含まれるAl等の第2金属から金属酸化膜15が形成されたが、第2金属は、ゲート絶縁膜4中に拡散した状態で、ゲート絶縁膜4中に含まれても良い。例えば、ゲート絶縁膜4にHfSiONを用いた場合、金属層5中の第2金属Mgは、熱処理工程でゲート絶縁膜4中に拡散した状態でゲート絶縁膜4中に含まれる。このようなゲート絶縁膜4の形成によっても、閾値電圧を変えることが可能となる。

【0033】

なお、熱処理等の条件によっては、実施の形態1〜3の3種類の態様が混在する場合もある。即ち、ゲート絶縁膜4の上部および/または下部に金属酸化膜が存在し、更には第2金属がゲート絶縁膜4中に含まれる場合もある。

【0034】

また、本実施の形態1〜3では、p型同士またはn型同士のような同一導電型のチャネル領域を有する複数の半導体素子が、互いに異なる閾値電圧を有する構造について説明したが、p型とn型のように導電型の異なるチャネル領域を有する半導体素子についても適用可能である。更に、MOSFETの他に、MISFET等の半導体素子にも適用できる。更には、半導体基板1や半導体層2が、シリコン以外の砒化ガリウム等の場合にも適用可能である。

【図面の簡単な説明】

【0035】

【図1】本発明の実施の形態1にかかる半導体装置の断面図である。

【図2】本発明の実施の形態1にかかる半導体装置の製造工程の断面図である。

【図3】本発明の実施の形態1にかかる半導体装置に対する熱処理の効果を示す。

【符号の説明】

【0036】

1 半導体基板、2 半導体層、3 素子分離領域、4 ゲート絶縁膜、5 金属層、

6 低抵抗金属層、7 サイドウォール、8 ソース/ドレイン領域、9 層間絶縁層、11 ゲート電極、15 金属酸化膜、21 ゲート電極、100 半導体装置。

【技術分野】

【0001】

本発明は、閾値電圧の異なる複数の半導体素子を含む半導体装置およびその製造方法に関し、特に、同一半導体基板上に閾値電圧の異なる複数のMOSFETを含む半導体装置およびその製造方法に関する。

【背景技術】

【0002】

閾値電圧(Vt)の異なる複数のMOSFETを同一基板上に作製する場合、従来は、チャネル領域に選択的にイオンを注入することにより、MOSFETの閾値電圧を変える方法が用いられていた。また、それぞれのゲート電極を、仕事関数の異なる金属材料から作製する方法も用いられていた(例えば、非特許文献1参照)。

【非特許文献1】F. Ootsuka, et. al., "Full Metal-Gate Integration of Dual-Metal-Gate HfSON CMOS Transistors by Using Oxidation-Free Dummy-Mask Process", SSDM2006. pp.1116

【発明の開示】

【発明が解決しようとする課題】

【0003】

しかしながら、チャネル領域にイオンを注入する方法では、MOSFETの微細化にともない、注入されるイオン量のばらつきが閾値電圧の値に影響し、閾値電圧がばらつくという問題があった。

一方、仕事関数の異なる金属材料からゲート電極を作製する方法では、導電型の異なるMOSFETには適用できるが、同一導電型のMOSFETで異なる閾値電圧をもたせることが困難であるという問題があった。あえて、同一導電型のMOSFETのゲート電極を、異なる金属材料から形成した場合、製造工程が複雑化するとともに、製造コストが高くなり、現実的ではなかった。

【0004】

そこで、本発明は、同一導電型のチャネル領域を有し、かつ閾値電圧の異なる複数の半導体素子を有する半導体装置の提供を目的とする。

【課題を解決するための手段】

【0005】

本発明の一実施例によれば、閾値電圧が互いに異なる2つのトランジスタが同一半導体基板上に形成された半導体装置であって、トランジスタのゲート電極は、半導体基板上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成された、第2金属を含み第1金属を主成分とする金属層とを含み、更に、一方のトランジスタが、ゲート絶縁膜と金属層との間に、第2金属の酸化膜を含む半導体装置が提供される。

【0006】

本発明の他の実施例によれば、閾値電圧が互いに異なる2つのトランジスタを同一半導体基板上に形成する半導体装置の製造方法であって、半導体基板を準備する工程と、半導体基板上に、ゲート絶縁膜を形成する工程と、ゲート絶縁膜上に、第2金属を含み第1金属を主成分とする金属層を形成する工程と、ゲート絶縁膜と金属層をエッチングして、ゲート絶縁膜と金属層とを含む第1および第2のゲート電極を形成する工程と、それぞれのゲート電極の両側にソース/ドレイン領域を形成する工程と、第1のゲート電極の温度が第2のゲート電極の温度より高くなるように加熱し、第1のゲート電極の金属層中の第2金属の酸化物を、金属層とゲート絶縁膜との間に形成する加熱工程とを含む製造方法が提供される。

【発明の効果】

【0007】

本発明では、同一半導体基板上に閾値電圧の異なる複数の半導体素子を含む半導体装置の提供が可能となる。特に、同一導電型のチャネル領域を有し、閾値電圧の異なる複数の半導体素子を含む半導体装置の提供が可能となる。

【発明を実施するための最良の形態】

【0008】

実施の形態1.

図1は、全体が100で表される、本発明の実施の形態1にかかる半導体装置の断面図である。半導体装置100は、同一半導体基板1の上に、閾値電圧(Vt)の異なる、同一導電型のチャネル領域を有する第1半導体素子10、第2半導体素子20が、それぞれ形成されている。

【0009】

シリコン等の半導体基板1の上には、シリコン層等の半導体層2が形成される。半導体層2は、例えばウエル構造であっても構わない。半導体層2には、例えば、酸化シリコンが埋め込まれた素子分離領域3が形成されている。第1半導体素子10と第2半導体素子20とは、素子分離領域3により電気的に分離されている。

【0010】

第1半導体素子10は、ゲート絶縁膜4、金属層5、低抵抗金属層6からなるゲート電極11を含み、ゲート電極11を挟むように、ソース/ドレイン領域3が設けられている。

また、第2半導体素子20は、ゲート絶縁膜4、金属層5、低抵抗金属層6、およびゲート絶縁膜4と金属層5との間に設けられた金属酸化膜15を含む。また、ゲート電極11を挟むように、ソース/ドレイン領域8が設けられている。

【0011】

ゲート絶縁膜は、HfO2、HfSiO、HfSiON等のHf系のhigh−k(高誘電体)材料から形成されるが、SiO2、SiON等を用いることも可能である。

【0012】

また、Hf系のhigh−k(高誘電体)材料を用いる場合は、半導体表面2との界面にSiO2、SiONを有する場合もある。

【0013】

金属層5は、主に第1金属あるいはその窒化物もしくは炭化物からなり、第1金属とは異なる第2金属を含む。第2金属の含有量は、組成比で30%以下であることが好ましい。

半導体素子のチャネル領域がp型チャネル領域を有する場合、第1金属は、例えばRu、Ir、Pt、Pd、Re、W、Mo、Ni、TiおよびCoから選択される金属からなる。また、第2金属は、例えばAlからなる。Al以外にTi、Ta、もしくはランタノイド系(La、Ce、Pr、Nd、Pm、Sm、En、Gd、Tb、Dy、Ho、Er、Tm、Yb、Lu)等の希土類金属を用いても構わない。

一方、半導体素子のチャネル領域がn型の場合、第1金属は、例えば、Al、Ga、In、Tl、Rb、Bi、Ti、Zr、Hf、V、Nb、TaおよびMn等からなり、第2金属は、例えばMg、Li、Be、Ca、Srまたは上記ランタノイド系の希土類金属からなる。

【0014】

低抵抗金属層6は、例えばW、シリサイド金属もしくはシリサイド金属とポリシリコンの積層膜からなる。

【0015】

金属酸化膜15は、金属層5に含まれる第2金属の酸化物からなり、例えば第2金属がアルミニウム(Al)の場合は酸化アルミニウム(AlOx等)からなり、第2金属がマグネシウム(Mg)の場合は酸化マグネシウム(MgOx等)からなる。

【0016】

金属酸化膜15が形成されることにより、第2半導体素子20の閾値電圧は、金属酸化膜15を含まない第1半導体素子10の閾値電圧より高くなる。これにより、同一導電型のチャネル領域を有し、かつ閾値電圧の異なる2つの半導体素子10、20を、同一半導体基板1の上に形成できる。

【0017】

ゲート電極11、21の両側面は、例えば酸化シリコンからなるサイドウォール7で覆われている。更に、半導体基板1の上には、例えば酸化シリコンからなる層間絶縁層9が形成されている。

【0018】

次に、図2を用いて、本実施の形態1にかかる半導体装置100の製造方法について説明する。図2は、半導体装置100の製造工程の断面図であり、図2中、図1と同一符号は、同一または相当箇所を示す。かかる製造工程は、以下の工程1〜5を含む。

【0019】

工程1:図2(a)に示すように、シリコン等の半導体基板1を準備する。続いて、半導体基板1の上に、例えばシリコンからなる半導体層2を形成する。更に、半導体層2中に、例えば酸化シリコンからなる素子分離領域3を形成する。素子分離領域3で分離された領域に、第1半導体素子10、第2半導体素子20が形成される。

【0020】

工程2:図2(b)に示すように、ゲート絶縁膜4、金属層5、および低抵抗金属層6を、例えばスパッタ法やCVD法で作製する。ゲート絶縁膜4は、HfSiON等のhigh−k(高誘電体)材料から形成される。

【0021】

金属層5は、第1金属を主成分とし、第1金属とは異なる第2金属を含む。半導体素子のp型チャネル領域を有する場合、第1金属は、例えばRuからなり、第2金素は、例えばAlからなる。一方、半導体素子のチャネル領域がn型の場合、第1金属は、例えば、TaSiNからなり、第2金属はMgからなる。また、低抵抗金属層6は、例えばWからなる。

【0022】

工程3:図2(c)に示すように、例えばハードマスク(図示せず)を用いてゲート絶縁膜4、金属層5、および低抵抗金属層6をエッチングし、ゲート電極11、21を形成する。続いて、ゲート電極11、21の側壁に、例えば酸化シリコンからなるサイドウォール7を形成する。続いて、ゲート電極11、21を注入マスクに用いたイオン注入および活性化アニールにより、ソース/ドレイン領域8を形成する。活性化アニールの温度は、例えば800℃である。ソース/ドレイン領域8は、エクステンション領域を含んでも構わない。

【0023】

工程4:図2(d)に示すように、例えば酸化シリコンからなる層間絶縁層9を形成し、更に、ゲート電極21を覆うように光吸収膜30を形成する。光吸収膜30は、例えばアモルファスカーボン(a−C)からなる。光吸収膜は、例えば破線31で示すように、第2半導体素子20の上方を覆うように形成しても構わない。

【0024】

かかる状態でレーザアニールやランプアニールを行う。具体的には、半導体基板1の上面(図2(d)では上方向)からレーザ光やランプ光のような光を照射する。このアニールは、ソース/ドレイン領域8の活性化アニール温度より高い温度で行われ、例えばソース/ドレイン領域活性化アニールが800℃の時は850℃以上、好適には900℃で行われる。アニール時間は、数ミリ秒以下である。かかるアニールでは、光吸収膜30を形成したゲート電極21の温度が、光吸収膜30を形成しないゲート電極11の温度より高くなる。これにより、金属層5中の第2金属(Al)が、金属層5とゲート絶縁膜4との間に析出して酸化され、酸化アルミニウム(AlOx)となる。

【0025】

工程5:図2(e)に示すように、光吸収膜30を除去する。この結果、第2半導体素子20は、ゲート絶縁膜4と金属層5との間に金属酸化膜15が形成されたゲート電極21を有するようになる。

【0026】

以上の工程で、本発明の実施の形態1にかかる半導体装置100が完成する。なお、配線層等は、必要に応じて適宜形成しても構わない。

【0027】

図3は、閾値電圧、仕事関数の、アニール温度依存性を示す。横軸はアニール温度(ゲート電極の温度)であり、縦軸はゲート電極の仕事関数と、そのゲート電極を有する半導体素子の閾値電圧である。ゲート電極は、HfSiONからなるゲート絶縁膜、Al(Alの組成比が10%)を第2金属として含むRuの金属層、およびWの低抵抗金属層が積層された構造である。

【0028】

図3から分かるように、アニール温度が800℃程度では金属酸化膜(AlOx)が形成されず、アニール温度が900℃程度では金属酸化膜(AlOx)が形成されている。これに伴い、仕事関数は、約4.5eVから約4.7eVと大きくなり、閾値電圧も、Vt1からVt2まで大きくなる。アニール温度が850℃を超えると、金属酸化膜が析出することが確認されている。

【0029】

このように、本実施の形態1にかかる製造方法では、ゲート電極を形成した後に熱処理を行うことにより、特定のゲート電極中に金属酸化膜を形成して閾値電圧を変えることができる。これにより、同一半導体基板上に、閾値電圧の異なる複数の半導体素子を、容易に形成することができる。

【0030】

なお、本実施の形態1では、図2(d)に示すように、高い温度で熱処理するゲート電極の上に光吸収膜30を形成したが、逆に、低い温度で熱処理するゲート電極の上に光反射膜を形成しても良い。

例えば、図2(d)において、ゲート電極11の上、または第1半導体素子10の上を覆うように、光反射膜を形成しても構わない。光反射膜は、例えばSiON等からなる。

【0031】

実施の形態2.

実施の形態1では、第2半導体素子20の、ゲート絶縁膜4と金属層5との間に金属酸化膜15が形成されたが、半導体層2とゲート絶縁膜4との間に金属酸化膜15が形成される場合もある。例えば、ゲート絶縁膜4にHfSiOを用いた場合、金属層5中の第2金属Alは、熱処理工程でゲート絶縁膜4中を移動し、ゲート絶縁膜4の下面に金属酸化膜(AlOx)を形成する。このような金属酸化膜の形成によっても、閾値電圧を変えることが可能となる。

なお、半導体層2の表面にシリコン酸化膜がある場合、シリコン酸化膜とゲート絶縁膜4との間に金属酸化膜15が形成されることとなる。

【0032】

実施の形態3.

実施の形態1、2では、第1金属を主成分とする金属層5中に含まれるAl等の第2金属から金属酸化膜15が形成されたが、第2金属は、ゲート絶縁膜4中に拡散した状態で、ゲート絶縁膜4中に含まれても良い。例えば、ゲート絶縁膜4にHfSiONを用いた場合、金属層5中の第2金属Mgは、熱処理工程でゲート絶縁膜4中に拡散した状態でゲート絶縁膜4中に含まれる。このようなゲート絶縁膜4の形成によっても、閾値電圧を変えることが可能となる。

【0033】

なお、熱処理等の条件によっては、実施の形態1〜3の3種類の態様が混在する場合もある。即ち、ゲート絶縁膜4の上部および/または下部に金属酸化膜が存在し、更には第2金属がゲート絶縁膜4中に含まれる場合もある。

【0034】

また、本実施の形態1〜3では、p型同士またはn型同士のような同一導電型のチャネル領域を有する複数の半導体素子が、互いに異なる閾値電圧を有する構造について説明したが、p型とn型のように導電型の異なるチャネル領域を有する半導体素子についても適用可能である。更に、MOSFETの他に、MISFET等の半導体素子にも適用できる。更には、半導体基板1や半導体層2が、シリコン以外の砒化ガリウム等の場合にも適用可能である。

【図面の簡単な説明】

【0035】

【図1】本発明の実施の形態1にかかる半導体装置の断面図である。

【図2】本発明の実施の形態1にかかる半導体装置の製造工程の断面図である。

【図3】本発明の実施の形態1にかかる半導体装置に対する熱処理の効果を示す。

【符号の説明】

【0036】

1 半導体基板、2 半導体層、3 素子分離領域、4 ゲート絶縁膜、5 金属層、

6 低抵抗金属層、7 サイドウォール、8 ソース/ドレイン領域、9 層間絶縁層、11 ゲート電極、15 金属酸化膜、21 ゲート電極、100 半導体装置。

【特許請求の範囲】

【請求項1】

閾値電圧が互いに異なる2つのトランジスタが同一半導体基板上に形成された半導体装置であって、

該トランジスタのゲート電極は、該半導体基板上に形成されたゲート絶縁膜と、該ゲート絶縁膜上に形成された、第2金属を含み第1金属を主成分とする金属層とを含み、

更に、一方のトランジスタが、該ゲート絶縁膜と該金属層との間に、該第2金属の酸化膜を含むことを特徴とする半導体装置。

【請求項2】

閾値電圧が互いに異なる2つのトランジスタが同一半導体基板上に形成された半導体装置であって、

該トランジスタのゲート電極は、該半導体基板上に形成されたゲート絶縁膜と、該ゲート絶縁膜上に形成された、第2金属を含み第1金属を主成分とする金属層とを含み、

更に、一方のトランジスタが、該半導体基板と該ゲート絶縁膜との間に、該第2金属の酸化膜を含むことを特徴とする半導体装置。

【請求項3】

閾値電圧が互いに異なる2つのトランジスタが同一半導体基板上に形成された半導体装置であって、

該トランジスタのゲート電極は、該半導体基板上に形成されたゲート絶縁膜と、該ゲート絶縁膜上に形成された、第2金属を含み第1金属を主成分とする金属層とを含み、

更に、一方のトランジスタが、該ゲート絶縁膜中に該第2金属を含むことを特徴とする半導体装置。

【請求項4】

上記トランジスタがpチャネル型トランジスタの場合に、上記金属層は、Ru、Ir、Pt、Pd、Re、W、Mo、Ni、TiおよびCoからなる群から選択される第1金属あるいはその窒化物もしくは炭化物からなることを特徴とする請求項1〜3のいずれかに記載の半導体装置。

【請求項5】

上記トランジスタがpチャネル型トランジスタの場合に、上記第2金属は、Al、Ti、Taまたは希土類金属からなることを特徴とする請求項1〜3のいずれかに記載の半導体装置。

【請求項6】

上記トランジスタがnチャネル型トランジスタの場合に、上記金属層は、Al、Ga、In、Tl、Rb、Bi、Ti、Zr、Hf、V、Nb、TaおよびMnからなる群から選択される第1金属あるいはその窒化物もしくは炭化物からなることを特徴とする請求項1〜3のいずれかに記載の半導体装置。

【請求項7】

上記トランジスタがnチャネル型トランジスタの場合に、上記第2金属は、Mg、Li、Be、Ca、Srまたは希土類金属からなることを特徴とする請求項1〜3のいずれかに記載の半導体装置。

【請求項8】

上記第1金属が、組成比で30%以下の上記第2金属を含むことを特徴とする請求項1〜7のいずれかに記載の半導体装置。

【請求項9】

上記ゲート絶縁膜が、high−k材料からなる膜、もしくはシリコン酸化膜あるいはシリコン酸窒化膜とhigh−k材料の積層膜からなることを特徴とする請求項1〜8のいずれかに記載の半導体装置。

【請求項10】

閾値電圧が互いに異なる2つのトランジスタを同一半導体基板上に形成する半導体装置の製造方法であって、

半導体基板を準備する工程と、

該半導体基板上に、ゲート絶縁膜を形成する工程と、

該ゲート絶縁膜上に、第2金属を含み第1金属を主成分とする金属層を形成する工程と、

該ゲート絶縁膜と該金属層をエッチングして、該ゲート絶縁膜と該金属層とを含む第1および第2のゲート電極を形成する工程と、

それぞれの該ゲート電極の両側にソース/ドレイン領域を形成する工程と、

第1のゲート電極の温度が第2のゲート電極の温度より高くなるように加熱し、第1のゲート電極の金属層中の第2金属の酸化物を、該金属層と該ゲート絶縁膜との間に形成する加熱工程と、を含むことを特徴とする半導体装置の製造方法。

【請求項11】

閾値電圧が互いに異なる2つのトランジスタを同一半導体基板上に形成する半導体装置の製造方法であって、

半導体基板を準備する工程と、

該半導体基板上に、ゲート絶縁膜を形成する工程と、

該ゲート絶縁膜上に、第2金属を含み第1金属を主成分とする金属層を形成する工程と、

該ゲート絶縁膜と該金属層をエッチングして、該ゲート絶縁膜と該金属層とを含む第1および第2のゲート電極を形成する工程と、

それぞれの該ゲート電極の両側にソース/ドレイン領域を形成する工程と、

第1のゲート電極の温度が第2のゲート電極の温度より高くなるように加熱し、第1のゲート電極の金属層中の第2金属の酸化物を、該ゲート絶縁膜と該半導体基板との間に形成する加熱工程と、を含むことを特徴とする半導体装置の製造方法。

【請求項12】

閾値電圧が互いに異なる2つのトランジスタを同一半導体基板上に形成する半導体装置の製造方法であって、

半導体基板を準備する工程と、

該半導体基板上に、ゲート絶縁膜を形成する工程と、

該ゲート絶縁膜上に、第2金属を含み第1金属を主成分とする金属層を形成する工程と、

該ゲート絶縁膜と該金属層をエッチングして、該ゲート絶縁膜と該金属層とを含む、第1および第2のゲート電極を形成する工程と、

それぞれの該ゲート電極の両側にソース/ドレイン領域を形成する工程と、

第1のゲート電極の温度が第2のゲート電極の温度より高くなるように加熱し、第1のゲート電極の金属層中の第2金属を、該ゲート絶縁膜中に拡散させる加熱工程と、を含むことを特徴とする半導体装置の製造方法。

【請求項13】

上記加熱工程が、上記第1のゲート電極を覆い、上記第2ゲート電極を覆わないように光吸収膜を形成し、上記半導体基板に光を照射して加熱する工程であることを特徴とする

請求項10〜12のいずれかに記載の製造方法。

【請求項14】

上記光吸収膜が、アモルファスカーボン膜であることを特徴とする請求項13に記載の製造方法。

【請求項15】

上記加熱工程が、上記第2のゲート電極を覆い、上記第1ゲート電極を覆わないように光反射膜を形成し、上記半導体基板に光を照射して加熱する工程であることを特徴とする

請求項10〜12のいずれかに記載の製造方法。

【請求項16】

上記光反射膜が、SiON膜であることを特徴とする請求項15に記載の製造方法。

【請求項17】

上記ソース/ドレイン領域を形成する工程の熱処理温度より、上記加熱工程の加熱温度の方が高温であることを特徴とする請求項10〜16のいずれかに記載の製造方法。

【請求項1】

閾値電圧が互いに異なる2つのトランジスタが同一半導体基板上に形成された半導体装置であって、

該トランジスタのゲート電極は、該半導体基板上に形成されたゲート絶縁膜と、該ゲート絶縁膜上に形成された、第2金属を含み第1金属を主成分とする金属層とを含み、

更に、一方のトランジスタが、該ゲート絶縁膜と該金属層との間に、該第2金属の酸化膜を含むことを特徴とする半導体装置。

【請求項2】

閾値電圧が互いに異なる2つのトランジスタが同一半導体基板上に形成された半導体装置であって、

該トランジスタのゲート電極は、該半導体基板上に形成されたゲート絶縁膜と、該ゲート絶縁膜上に形成された、第2金属を含み第1金属を主成分とする金属層とを含み、

更に、一方のトランジスタが、該半導体基板と該ゲート絶縁膜との間に、該第2金属の酸化膜を含むことを特徴とする半導体装置。

【請求項3】

閾値電圧が互いに異なる2つのトランジスタが同一半導体基板上に形成された半導体装置であって、

該トランジスタのゲート電極は、該半導体基板上に形成されたゲート絶縁膜と、該ゲート絶縁膜上に形成された、第2金属を含み第1金属を主成分とする金属層とを含み、

更に、一方のトランジスタが、該ゲート絶縁膜中に該第2金属を含むことを特徴とする半導体装置。

【請求項4】

上記トランジスタがpチャネル型トランジスタの場合に、上記金属層は、Ru、Ir、Pt、Pd、Re、W、Mo、Ni、TiおよびCoからなる群から選択される第1金属あるいはその窒化物もしくは炭化物からなることを特徴とする請求項1〜3のいずれかに記載の半導体装置。

【請求項5】

上記トランジスタがpチャネル型トランジスタの場合に、上記第2金属は、Al、Ti、Taまたは希土類金属からなることを特徴とする請求項1〜3のいずれかに記載の半導体装置。

【請求項6】

上記トランジスタがnチャネル型トランジスタの場合に、上記金属層は、Al、Ga、In、Tl、Rb、Bi、Ti、Zr、Hf、V、Nb、TaおよびMnからなる群から選択される第1金属あるいはその窒化物もしくは炭化物からなることを特徴とする請求項1〜3のいずれかに記載の半導体装置。

【請求項7】

上記トランジスタがnチャネル型トランジスタの場合に、上記第2金属は、Mg、Li、Be、Ca、Srまたは希土類金属からなることを特徴とする請求項1〜3のいずれかに記載の半導体装置。

【請求項8】

上記第1金属が、組成比で30%以下の上記第2金属を含むことを特徴とする請求項1〜7のいずれかに記載の半導体装置。

【請求項9】

上記ゲート絶縁膜が、high−k材料からなる膜、もしくはシリコン酸化膜あるいはシリコン酸窒化膜とhigh−k材料の積層膜からなることを特徴とする請求項1〜8のいずれかに記載の半導体装置。

【請求項10】

閾値電圧が互いに異なる2つのトランジスタを同一半導体基板上に形成する半導体装置の製造方法であって、

半導体基板を準備する工程と、

該半導体基板上に、ゲート絶縁膜を形成する工程と、

該ゲート絶縁膜上に、第2金属を含み第1金属を主成分とする金属層を形成する工程と、

該ゲート絶縁膜と該金属層をエッチングして、該ゲート絶縁膜と該金属層とを含む第1および第2のゲート電極を形成する工程と、

それぞれの該ゲート電極の両側にソース/ドレイン領域を形成する工程と、

第1のゲート電極の温度が第2のゲート電極の温度より高くなるように加熱し、第1のゲート電極の金属層中の第2金属の酸化物を、該金属層と該ゲート絶縁膜との間に形成する加熱工程と、を含むことを特徴とする半導体装置の製造方法。

【請求項11】

閾値電圧が互いに異なる2つのトランジスタを同一半導体基板上に形成する半導体装置の製造方法であって、

半導体基板を準備する工程と、

該半導体基板上に、ゲート絶縁膜を形成する工程と、

該ゲート絶縁膜上に、第2金属を含み第1金属を主成分とする金属層を形成する工程と、

該ゲート絶縁膜と該金属層をエッチングして、該ゲート絶縁膜と該金属層とを含む第1および第2のゲート電極を形成する工程と、

それぞれの該ゲート電極の両側にソース/ドレイン領域を形成する工程と、

第1のゲート電極の温度が第2のゲート電極の温度より高くなるように加熱し、第1のゲート電極の金属層中の第2金属の酸化物を、該ゲート絶縁膜と該半導体基板との間に形成する加熱工程と、を含むことを特徴とする半導体装置の製造方法。

【請求項12】

閾値電圧が互いに異なる2つのトランジスタを同一半導体基板上に形成する半導体装置の製造方法であって、

半導体基板を準備する工程と、

該半導体基板上に、ゲート絶縁膜を形成する工程と、

該ゲート絶縁膜上に、第2金属を含み第1金属を主成分とする金属層を形成する工程と、

該ゲート絶縁膜と該金属層をエッチングして、該ゲート絶縁膜と該金属層とを含む、第1および第2のゲート電極を形成する工程と、

それぞれの該ゲート電極の両側にソース/ドレイン領域を形成する工程と、

第1のゲート電極の温度が第2のゲート電極の温度より高くなるように加熱し、第1のゲート電極の金属層中の第2金属を、該ゲート絶縁膜中に拡散させる加熱工程と、を含むことを特徴とする半導体装置の製造方法。

【請求項13】

上記加熱工程が、上記第1のゲート電極を覆い、上記第2ゲート電極を覆わないように光吸収膜を形成し、上記半導体基板に光を照射して加熱する工程であることを特徴とする

請求項10〜12のいずれかに記載の製造方法。

【請求項14】

上記光吸収膜が、アモルファスカーボン膜であることを特徴とする請求項13に記載の製造方法。

【請求項15】

上記加熱工程が、上記第2のゲート電極を覆い、上記第1ゲート電極を覆わないように光反射膜を形成し、上記半導体基板に光を照射して加熱する工程であることを特徴とする

請求項10〜12のいずれかに記載の製造方法。

【請求項16】

上記光反射膜が、SiON膜であることを特徴とする請求項15に記載の製造方法。

【請求項17】

上記ソース/ドレイン領域を形成する工程の熱処理温度より、上記加熱工程の加熱温度の方が高温であることを特徴とする請求項10〜16のいずれかに記載の製造方法。

【図1】

【図2】

【図3】

【図2】

【図3】

【公開番号】特開2009−200211(P2009−200211A)

【公開日】平成21年9月3日(2009.9.3)

【国際特許分類】

【出願番号】特願2008−39725(P2008−39725)

【出願日】平成20年2月21日(2008.2.21)

【出願人】(503121103)株式会社ルネサステクノロジ (4,790)

【Fターム(参考)】

【公開日】平成21年9月3日(2009.9.3)

【国際特許分類】

【出願日】平成20年2月21日(2008.2.21)

【出願人】(503121103)株式会社ルネサステクノロジ (4,790)

【Fターム(参考)】

[ Back to top ]