半導体装置およびその製造方法

【課題】エレクトロマイグレイション耐性の高いエアブリッジ配線を具備した半導体装置及びその製造方法を提供すること。

【解決手段】第1の配線と、第1の配線から空間によって隔てられた状態で、前記第1の配線の上を横切る第2の配線と、前記第1及び第2の配線に接続された半導体素子を具備し、前記第2の配線は、下から順に、タンタル層、タンタルナイトライド層、及び金層が積層されて形成されていること。

【解決手段】第1の配線と、第1の配線から空間によって隔てられた状態で、前記第1の配線の上を横切る第2の配線と、前記第1及び第2の配線に接続された半導体素子を具備し、前記第2の配線は、下から順に、タンタル層、タンタルナイトライド層、及び金層が積層されて形成されていること。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置及びその製造方法に関する。

【背景技術】

【0002】

半導体装置、例えば電力増幅用電界効果トランジスタを低コストで大量に生産するためには、半導体装置を微細化する必要がある。

【0003】

しかし、半導体装置を微細化すると、配線間の距離、特に絶縁膜を介して交差する配線間の距離が狭くなる。このような配線間隔の狭窄化は、配線間の寄生容量を大きくして、半導体装置の高周波動作を困難にする。

【0004】

絶縁膜を介して交差する配線間の寄生容量を小さくするためには、エアブリッジ配線が有効である。特に、マルチゲートトランジスタと呼ばれる、複数の電界効果トランジスタ(field effect transistor;以下、FETと呼ぶ)を同一基板上に配置した電力増幅用電界効果トランジスタの高速化には、エアブリッジ配線が有効である。

【0005】

マルチゲートトランジスタでは、複数のFETが一列に整列させられて、対応する端子(ソース、ドレイン、ゲート)同士が櫛の歯状の電極によって接続されている。この時、複数のソースを接続するソース電極と、複数のゲートを接続するゲート電極とに交差部位が生じてしまう。

【0006】

この交差部位には、ソース電極とゲート電極の接触を回避するため、両者を絶縁膜を介して立体交差させるブリッジ(橋渡し)配線構造が形成される(特許文献1)。

【0007】

ブリッジ配線構造では、交差する配線間に介在する絶縁膜の高い誘電率によって、寄生容量が大きくなってしまう。従って、マルチゲートトランジスタを高速化しようとする場合には、交差する配線間が空間によって隔てられているエアブリッジ配線が用いられる。

【0008】

エアブリッジ配線を形成する金属層としては、導電率が高い金が広く用いられている。しかし、金(Au)は柔らかく単独ではエアブリッジ構造を維持することができない。そこで、チタン(Ti)と白金(Pt)の積層構造を支持体とするTi/Pt/Au積層構造によって、エアブリッジ配線が形成される。ここで、Tiは基板とエアブリッジ層の密着を良くするためのものであり、Au層は、Pt層によって支持されている(特許文献2)。

【0009】

ところで、近年、窒化ガリウム(GaN)によってチャネル層が形成された高電子移動トランジスタ(high electron mobility transistor;HEMT)が、高周波高出力トランジスタとして注目されている(GaNによってチャネル層が形成されたHEMTは、以後GaN−HEMTと表される。)。

【0010】

GaNは、SiやGaAsに比べ、バンドギャップが広い。このため、GaN−HEMTは、高温動作に適し、しかも破壊電界が高いため高電圧動作に適している。故に、GaN−HEMTは、小型化され大電流で動作させられても、動作温度の上昇やチャネルへ印加される電界の増大によって動作不良を起こすことはない。

【0011】

このため、GaN−HEMTによってマルチゲートトランジスタが形成され、高周波高出力電力増幅器として使用されている。

【特許文献1】特開2003−197740号公報

【特許文献2】特開2007−150282号公報

【発明の開示】

【発明が解決しようとする課題】

【0012】

上述したように、高周波動作に適したFETによってマルチゲートトランジスタを形成する場合、寄生容量が小さくなるエアブリッジ配線が採用される。ここで、GaN−HEMTのように大電流で動作するFETによってマルチゲートトランジスタを形成した場合、エアブリッジ配線にも大電流が流れることになる。

【0013】

本発明者は、この点に着目して、複数のGaN−HEMTを含むマルチゲートトランジスタ(以後、GaN−HEMTマルチゲートトランジスタと呼ばれる)を今後更に高出力化した場合、どのような影響が現れるのか検討した。

【0014】

その結果、エアブリッジに大電流を流すと、エアブリッジ配線を形成するAuがエレクトロマイグレーションして、Pt支持層の結晶粒界に入り込む虞のあることが明らかになった。この場合、Pt支持層が崩壊して、エアブリッジ配線が支持体を失い断線することが懸念される。

【0015】

そこで、本発明の目的は、大電流を流しても断線し難いエアブリッジ配線、すなわちエレクトロマイグレーション耐性の高いエアブリッジ配線を具備した半導体装置及びその製造方法を提供することである。

【課題を解決するための手段】

【0016】

本半導体装置は、第1の配線と、前記第1の配線と交差する方向に延在し、前記第1の配線と空間を介して配置され、タンタル層、該タンタル層上に形成されたタンタルナイトライド層、該タンタルナイトライド層上に形成された金属層を含む第2の配線とを有する。

【発明の効果】

【0017】

本半導体装置によれば、大電流を流しても断線し難いエアブリッジ配線を具備した半導体装置を提供することができる。

【発明を実施するための最良の形態】

【0018】

以下、図面にしたがって本発明の実施の形態が説明される。但し、本発明の技術的範囲はこれらの実施の形態に限定されず、特許請求の範囲に記載された事項とその均等物まで及ぶものである。

【0019】

特許文献2に開示されたようなTi/Pt/Au積層構造によって形成されたエアブリッジ配線では、エアブリッジ配線の本体は、厚いAu層である。しかし、Auは柔らかいので、Au層単独でエアブリッジ構造を保持することはできない。従って、Au層の下方に形成されたPt層によってAu層が支えられている。

【0020】

ところで、Auは、エレクトロマイグレーションしやすいことが知られている。このため、マルチゲートトランジスタを大電流(例えば、1×105A/cm2以上)で動作させた場合、電子流に押し流されたAu原子がAu層からPt膜中に移動して、Pt膜を破壊するのではと懸念される。

【0021】

図1は、エレクトロマイグレーションを説明する図である。図2は、図1中の円で囲った領域Aを拡大した図である。

【0022】

図1には、エアブリッジ配線12の左端が図示されている。ここで、エアブリッジ配線12は、空間38を介してマルチゲートトランジスタのゲートに接続される共通電極14の上方に形成されている。そして、エアブリッジ配線12は、Ti層40、Pt層42、第1のAu層44、第2のAu層46、及び第3のAu層48が積層されて形成されている。

【0023】

図1に示すように、エアブリッジ配線中の電子の流れ60は、エアブリッジ配線の内壁62近くまでは直進しその後向きを変える(尚、図1には、エアブリッジ配線12の底の部分を流れる電子流のみが描かれている。)。従って、図2に示すように、Au層44,46,48中のAu原子64は、電子流60によって衝突・散乱されて、Pt層42に向かって移動して行く(すなわち、エレクトロマイグレーションする。)。

【0024】

一方、Pt層42中には、成長方向に延びた多数の結晶粒界66(grain boundary)が存在している。Pt層42に向かって移動してきたAu原子64は、この結晶粒界66に入り込みPt微結晶同士の結合を断ち切ろうとする。

【0025】

その結果、Pt層42は崩壊し、エアブリッジ配線12を支持することができなくなる。そして、支持体を失ったエアブリッジ配線12は、ついには断線すると考えられる。

【0026】

尚、図1及び図2に示されたエアブリッジ配線は直角に折れ曲がっているが、エアブリッジ配線がなだらかに折れ曲がっている場合にも同様の現象が起きて、エアブリッジ配線は断線すると考えられる。

【0027】

電子流に曝された金属原子は、電子と衝突を繰り返して激しく振動し、やがて束縛されていた格子点から移動する。この時、個々の金属原子の移動方向は一定しないが、金属原子集団全体としては電子流の下流側に移動する。このような金属原子の移動現象が、エレクトロマイグレーションである。

【0028】

エレクトロマイグレーションの起因となる金属原子の振動は、高温に加熱された金属原子の振動に類似している。従って、高温でも安定な金属、すなわち高融点金属は、エレクトロマイグレーションに対しても強い耐性を有していると考えられる。

【0029】

そこで、本発明者は、配線として使用可能な高融点金属であるTa1-xNx(0≦X<1)のエレクトロマイグレーション耐性を検討した。

【0030】

エレクトロマイグレーション耐性は、被試験金属膜を加熱してその劣化速度を調べる熱劣化加速試験によって調べられた。被試験金属膜を高温に曝すことによって、金属原子が電子流に曝され激しく振動している状態を擬似的に作り出すことができる。

【0031】

具体的には、次のような試験が実施された。まず、Ti層の上にAl層が積層されたTi/Al積層膜を形成し、その上に、Ti層、Ta1-xNx層(0≦X<1)、及びAu層が順次積層された試料(Ti/Ta1-xNx/Au積層膜)(0≦X<1)を形成した。また、比較試料として、Ti/Al積層膜の上に、Ti層、Pt層及びAu層が、順次積層された試料(Ti/Pt/Au積層膜)を形成した。

【0032】

ここで、Ta1-xNx層は、Taをターゲットとして、反応性スパッタ法によって形成される。スパッタガス及び反応ガスは、夫々、Ar及びN2である。Au層及びPt層は、夫々、Au及びTaをターゲットとして、スパッタ法によって形成される。この時のスパッタガスは、Arである。

【0033】

ここで、Ti層、Ta1-xNx層、及びAu層の厚さは、夫々、数10nm、200nm、及び50nm〜300nmである。また、比較用試料のPt層の厚さは、Ta1-xNx層と同じ200nmである。尚、Al層及びTi層の厚さは、全ての試料で同じである。

【0034】

以上のようにして形成された試料が450℃に加熱されて、Au層の表面に変化が現れるまでの時間が計測される。ここでAu層の厚さは、この変化が現れやいように、実際のエアブリッジ配線のAu層より薄く形成されている。

【0035】

加熱前の試料の表面は、均一で何の特徴もない。しかし、加熱を続けるとやがて試料の表面に染みが現れる。この染みの現れるまでの加熱時間(以後、反応時間と呼ぶ)が計測され比較される。

【0036】

この染みは、Au原子が、Ta1-xNx層(又は、Pt層)を破壊して、Ta1-xNx層(又は、Pt層)の下に配置されたAl膜と反応してできたAlAu合金である。すなわち、熱劣化加速試験によって計測される反応時間は、激しく振動するAu原子によってTa1-xNx層(又は、Pt層)が破壊されるまでの時間を表している。従って、この反応時間が長い金属膜ほど、エレクトロマイグレーション耐性が高いと考えられる。

【0037】

図3は、Ta1-xNx層の組成を変えて反応時間を測定した結果である。横軸は、Ta1-xNx層の窒素含有率である。縦軸は反応時間である。「TaN」と表示された曲線は、Ti/Al積層膜とAu層の間にTi/Ta1-xNx積層膜が形成された試料の反応時間を表している。一方、「Pt」と表示された破線は、Ti/Al積層膜とAu層の間にTi/Pt積層膜が形成された試料の反応時間(2分)を表している。ここで、Ti層は、Ti/Ta1-xNx積層膜及びTi/Pt積層膜の双方に形成されているので、両者の反応時間に違いを起させるものではない。

【0038】

図3に示すように、窒素含有率が0%の試料すなわちTa層が形成された試料の反応時間(3分)は、Pt層が形成された試料の反応時間(2分)より長い。しかし、窒素含有率が増加すると、Ta1-xNx層の反応時間は一旦短くなり、比較試料より反応時間が短くなる。そして、反応時間は、窒素含有率40%近傍で最低になる。

【0039】

その後、Ta1-xNx層の反応時間は、窒素含有率の増加と共に急激に増加し、窒素含有率が48%で比較試料と同じになり、窒素含有率が50%で比較試料の2倍になる。その後も、反応時間は増加し続ける。しかし、窒素含有率が52%を超える試料の作製は困難であった。

【0040】

以上の結果は、窒素含有率が48%より高いTaNによって支持されたTi/TaN/Au積層膜によってエアブリッジ配線を形成すると、エレクトロマイグレーション耐性の高いエアブリッジ配線の形成が可能になることを教示している。

【0041】

そこで、本発明者は、Ti/TaN/Au積層膜によって形成されたエアブリッジ配線を具備するマルチゲートトランジスタの製造を試みた。以下、図4、図5、及び図6を用いてエアブリッジ配線の製造工程について説明をする。

【0042】

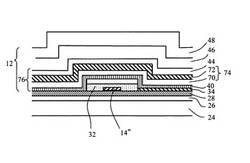

図4は、試作したマルチゲートトランジスタのゲート電極とソース電極が立体交差するエアブリッジ配線構造の断面図である。

【0043】

ゲート電極を形成する共通電極14´´は、n型AlGaNキャリア供給層28がイオン注入によって高抵抗化されたAlGaN不活性領域36の上に形成されている。そして、保護膜32によって覆われた共通電極14´´(ゲート電極)上を、空間38を介して、エアブリッジ配線12(ソース電極)が横切っている。

【0044】

ここで、エアブリッジ配線12は、Ti層40、TaN層42、第1のAu層44、第2のAu層46、及び第3のAu層48が積層されて形成されている。

【0045】

次に、試作したマルチゲートトランジスタに於けるエアブリッジ配線構造の製造手順を説明する。

【0046】

図5及び図6は、エアブリッジ配線構造の製造工程を説明する断面図である。

【0047】

まず、SiC基板24の上に、Unitentionally Doped(UID)−GaNチャネル層26、n型AlGaNキャリア供給層28、UID−GaNキャップ層(図示せず)が順次積層され、更にオーミック電極34が形成された基板50が準備される(図5(a)参照)。

【0048】

ここで、オーミック電極34は、ソース及びドレインとなる半導体領域の上に設けられる。また、UID−GaNキャップ層は、チャネルとなる半導体領域以外では除去されている(従って、図5(a)には図示されていない。)。そして、共通電極14´´の形成予定領域に露出したn型AlGaNキャリア供給層28は、イオン注入によって高抵抗化され、AlGaN不活性領域36となっている。

【0049】

次に、この基板50の上に、リフトオフ用のフォトレジスト膜52が形成される。その後、ゲート電極となるNi/Au積層膜54が蒸着される(図5(b)参照)。最後に、リフトオフ用フォトレジスト膜52が除去されて、ゲート電極22が完成する。このNi/Au積層膜54は、UID−GaNキャップ層にショットキー障壁を形成する。

【0050】

次に、基板50の全面に、保護膜となる厚さ500nmのSiN膜56が堆積される(図5(c)参照)。

【0051】

その後、保護膜32の形成予定領域にフォトレジスト膜52´が形成される(図5(d)参照)。このフォトレジスト膜52´をエッチングマスクとして、SiN膜56がドライエッチングによって除去されて、保護膜32が形成される(図6(a)参照)。

【0052】

次に、ゲート電極とソース電極の交差予定位置で、保護膜32の上にエアブリッジ形成用フォトレジスト膜(マスク)58が形成される(図6(b)参照)。

【0053】

次に、スパッタ法により、基板50の上に、Ti層40(厚さ数10nm)、TaN層42(厚さ200nm)、及び第1のAu層44(厚さ数50nm)を順次堆積する(図6(c)参照)。ここで、Ti層40及び第1のAu層44は、Ti及びAuをターゲットとしてスパッタ法によって堆積する。スパッタガスはArである。また、TaNは、Taをターゲットとして反応性スパッタ法により堆積される。ここで、反応ガスはN2である。

【0054】

次に、第1のAu層44をシード膜とし、ソース電極及びドレイン電極の形成予定領域が開口したフォトレジスト膜(図示せず)をメッキマスクとして、Au層が電解メッキによって、第2及び第3のAu層46,48が厚く形成される。第2及び第3のAu層46,48の厚さは、合計で1〜2μmである。

【0055】

その後、メッキマスクが除去され、各電極間に露出したスパッタ膜がミリングで除去される。

【0056】

最後に、エアブリッジ形成用フォトレジスト膜58が酸素を反応ガスとするマイクロ波アッシャーにより除去され、マルチゲートトランジスタ2が完成する(図6(d)参照)。

【0057】

以上のようにしてマルチゲートトランジスタを試作した結果、Ti/TaN/Auスパッタ膜68を堆積する過程で、エアブリッジ形成用フォトレジスト膜58が融解して、Ti/TaN/Auスパッタ膜68とゲート電極22を隔てる空間38が形成されないことが判明した。

【0058】

そこで、本発明者は、TaN層の堆積中に基板温度が何度まで上昇するか測定した。その結果、基板温度は、フォトレジストが融解する150℃を超えて上昇することが明らかになった。

【0059】

このような温度の上昇は、TaターゲットからスパッタされたTaと窒素ガスの生成熱に起因するものである。

【0060】

すなわち、Ti/TaN/Au積層膜を用いることによってエレクトロマイグレーション耐性の高いエアブリッジ配線の形成が可能になると期待されたが、実際にはTaN堆積時の基板温度上昇によってエアブリッジ配線自体の形成が困難になることが本発明者らによって見い出された。

【0061】

(実施の形態1)

TaN層の堆積に伴う基板温度の上昇は、成膜するTaN層を薄くすれば抑制できる。これは、基板50がTaNの生成熱に曝される時間が短くなるからである。しかしながら、Au層(第1〜第3のAu層44,46,48)を強固に支持するためには、ある程度の膜厚(例えば、100nm〜200nm)を持った金属層が必要である。従って、単にTaN層を薄くすることは、エアブリッジ配線の強度を劣化させる。

【0062】

そこで、本発明者は種々検討した結果、Ta層の上にTaN層を積層したTa/TaN積層膜を形成した場合、基板温度の上昇が、同じ膜厚のTaN膜を形成した場合より低くなることを見出した。

【0063】

これは、Ta/TaN積層膜では、最初に成膜するTa層の分だけTaN層が薄くなるからである。この場合、TaNの生成熱に基板が曝される時間が短くなるため、基板温度の上昇が抑制される。更に、本発明者は、後述するように、Ta/TaN積層膜のエレクトロマイグレーション耐性が、TaN膜より高いことも見出した。

【0064】

そこで、本発明者は、Ti/Ta/TaN/Au積層膜で形成されたエアブリッジ配線によって、マルチゲートトランジスタを製造することとした。

【0065】

(1)構 成

図7は、本実施の形態によるマルチゲートトランジスタを示す斜視図である。図8は、図7のA−A線に於ける断面を矢印の方向から見た図である。

【0066】

図9は、図7のB−B線に於ける断面を矢印の方向から見た図である。

【0067】

本実施の形態に従うマルチゲートトランジスタ2では、4つのGaN−HEMT4が一列に整列している。そして、隣接するGaN−HEMT4は、一つの半導体領域をソース6又はドレイン8として共有している(図8参照)。各半導体領域の上には、一つの電極10,10´が形成されている。

【0068】

更に、ソース6の上に形成された2つの電極10は、2つのエアブリッジ配線12によって1つの共通電極14に接続されて、櫛の歯状のソース電極16が形成される。

【0069】

一方、ドレイン8の上に形成された3つの電極10´は1つの共通電極14´に接続されて、櫛の歯状のドレイン電極18が形成される。

【0070】

また、チャネルの上に形成されゲート20となる4つの電極10´´も1つの共通電極14´´に接続されて、櫛の歯状のゲート電極22が形成される。

【0071】

このように3つの櫛の歯状の電極を一箇所に形成した場合、2つの電極、例えばゲート電極22とソース電極16の交差は避けられない(図7参照)。

【0072】

そこで、このような交差部位には、電極間の接触を回避するために、空間を介して両者が立体交差するエアブリッジ配線構造が形成されている。

【0073】

なお、ソース電極16、ドレイン電極18、及びゲート電極22は、夫々の共通電極14,14´,14´´を外部回路との接続用パッドとして使用することができるので、所謂「電極」としての機能を有している。一方、ソース電極16、ドレイン電極18、及びゲート電極22は、GaN−HEMTの各端子(ソース、ドレイン、ゲート)へ入出力される電気信号の経路を確保するものなので、「配線」としての機能も有している。すなわち、ソース電極16、ドレイン電極18、及びゲート電極22は、その名称に拘わらず、配線でもある。

【0074】

ここで、GaN―HEMTの構成を、もう少し詳しく説明する。

【0075】

図8に示すように、本実施の形態に従うGaN―HEMT2では、SiC基板24の上に、まず不純物の添加されていないUnitentionally Doped(UID)−GaNチャネル層26が積層されている。更に、本実施の形態では、このUID−GaNチャネル層26の上に、n型AlGaNキャリア供給層28とUID−GaNキャップ層30が順次積層されている。

【0076】

そして、ソース6及びドレイン8の一部を形成するn型AlGaNキャリア供給層28の上には、Tiの上にアルミニウム(Al)が積層されたTi/Alオーミック電極34が形成されている。更に、オーミック電極34の上には、ソース電極16を形成する電極10及びドレイン電極18を形成する電極10´の何れか一方が形成されている。また、チャネル20となるUID−GaNチャネル層26の上に積層された、UID−GaNキャップ層30の上には、ゲート電極22を形成する電極10´´が形成されている。

【0077】

また、ゲート電極22(電極10´´)は、例えば窒化珪素(SiN)製の保護膜32によって覆われている。この保護膜32はゲート電極22を不純物の汚染から保護して、出力信号(ドレイン電流波形)の劣化を防止するためのものである。

【0078】

図9は、図7のB−B線に於ける断面を矢印の方向から見た図である。すなわち、図9は、ゲート電極22とソース電極16が立体交差するエアブリッジ配線構造の断面図である。

【0079】

ゲート電極22を形成する共通電極14´´は、n型AlGaNキャリア供給層28がイオン注入によって高抵抗化されたAlGaN不活性領域の上に形成されている。そして、保護膜32によって覆われた共通電極14´´(すなわちゲート電極22)上を、空間を介して、エアブリッジ配線12(すなわちソース電極16)が横切っている。

【0080】

ここで、エアブリッジ配線12は、Ti層40、Ta層70、TaN層72、第1のAu層44、第2のAu層46、及び第3のAu層48が積層されて形成されている。TaNの窒素含有率は50%である。また、Ta層及びTaN層の厚さは、夫々100nmである。

【0081】

尚、ソース電極16及びドレイン電極18を形成する共通電極14,14´も、AlGaN不活性領域の上に形成されている。

【0082】

(2)製造手順

図10乃至図12は、

本実施の形態のエアブリッジを形成する工程を説明する工程断面図である。

【0083】

次に、試作したマルチゲートトランジスタに於けるエアブリッジ配線構造の製造手順を説明する。

【0084】

図10、図11、及び図12は、エアブリッジ配線構造の製造工程を説明する断面図である。

【0085】

まず、SiC基板24の上に、UID−GaNチャネル層26、n型AlGaNキャリア供給層28、UID−GaNキャップ層(図示せず)が順次積層され、更にオーミック電極34が形成された基板50が準備される(図10(a)参照)。

【0086】

ここで、オーミック電極34は、ソース及びドレインとなる半導体領域の上に設けられる。また、UID−GaNキャップ層は、チャネルとなる半導体領域以外では除去されている(従って、図10(a)には図示されていない。)。そして、共通電極14´´の形成予定領域に露出したn型AlGaNキャリア供給層28は、イオン注入によって高抵抗化され、AlGaN不活性領域36となっている。

【0087】

次に、この基板50の上に、リフトオフ用のフォトレジスト膜52が形成される。その後、ゲート電極となるNi/Au積層膜54が蒸着される(図10(b)参照)。最後に、リフトオフ用フォトレジスト膜52が除去されて、ゲート電極22が完成する。このNi/Au積層膜54は、UID−GaNキャップ層にショットキー障壁を形成する。

【0088】

次に、基板50の全面に、保護膜となる厚さ500nmのSiN膜56が堆積される(図10(c)参照)。ここで、保護膜32の厚さとしては、5nm乃至500nmが好ましい。

【0089】

その後、保護膜32の形成予定領域にフォトレジスト膜52´が形成される(図10(d)参照)。このフォトレジスト膜52´をエッチングマスクとして、SiN膜56がドライエッチングによって除去されて、保護膜32が形成される(図11(a)参照)。

【0090】

次に、ゲート電極とソース電極の交差予定位置で、保護膜32の上にエアブリッジ形成用フォトレジスト膜(マスク)58が形成される(図11(b)参照)。

【0091】

次に、基板50の上に、Ti層40、Ta層70、TaN層72(窒素含有率50%)、及び第1のAu層44が順次堆積される(図12(a)参照)。ここで、Ti層40、Ta層70、TaN層72、及び第1のAu層44の厚さは、夫々、数10nm、100nm、100nm、及び50nmである。

【0092】

尚、Ti層は、Ta/TaN積層膜の密着性をよくするためのものであり、他の金属層、例えばCr層と代替可能である。

【0093】

Ti層40、Ta層70、及び第1のAu層44は、夫々Ti、Ta、及びAuをターゲットとしてスパッタ法によって堆積される。スパッタガスはArである。一方、TaN72は、Taをターゲットとして反応性スパッタ法により堆積される。反応ガスはN2である。この時、堆積されるTaN層が100nmと薄いので、基板50の温度は150℃以上には上昇しない。従って、エアブリッジ形成用フォトレジスト膜58が融解することはない。

【0094】

尚、Ti層40を形成する前に、エアブリッジ形成用フォトレジスト膜58にUVキャアを施し、その断面を丸めてもよい。

【0095】

エアブリッジ形成用フォトレジスト膜58の断面が矩形に近いほど、Ti/Ta/TaN/Auスパッタ膜76のカバレッジ(レジストの頂上に堆積した金属膜の厚さに対する、レジストの側面に堆積した金属膜の厚さの比)が小さくなる。このようなレジスト膜は、エアブリッジの形成を困難にする。しかし、エアブリッジ形成用フォトレジスト膜58の断面を丸めておけば、エアブリッジの形成が阻害されることはない。

【0096】

次に、第1のAu層44をシード膜とし、ソース電極及びドレイン電極の形成予定領域が開口したフォトレジスト膜(図示せず)をメッキマスクとして、Au層が電解メッキによって、第2及び第3のAu層46,48が形成される。第2及び第3のAu層46,48の厚さは、合計で1〜2μmである。

【0097】

その後、メッキマスクが除去され、各電極間に露出したスパッタ膜がミリングで除去される(図12(b))。

【0098】

最後に、エアブリッジ形成用フォトレジスト膜58が酸素を反応ガスとするマイクロ波アッシャーにより除去され、マルチゲートトランジスタ2が完成する(図12(c)参照)。

【0099】

ここで、Ta/TaN積層は200nmと十分に厚いので、エアブリッジ形成用フォトレジスト膜58を除去しても、エアブリッジ配線が崩れることはない。

【0100】

以上の手順によって、図7、図8、及び図9を参照して説明した本実施の形態に従うマルチゲートトランジスタ2が完成する。

【0101】

ここで、本実施の形態に従うマルチゲートトランジスタ2の製造方法の要部は、以下のように纏められることができる。

【0102】

本製造方法は、半導体素子(GaN−HEMT4)が形成された基板50上に、上記半導体素子に接続され他の配線と交差する第1の配線(ゲート電極22)の上部を、交差予定位置で覆って線状に延在するエアブリッジ形成用フォトレジスト膜58を形成する。

【0103】

また、本製造方法は、上記半導体基板50上に、チタン層40、タンタル層70、タンタルナイトライド層72、第1の金層44を順次積層して、上記フォトレジスト膜58の上を乗り越えて上記フォトレジスト膜58の一方の脇から他方の脇に延在し且つ上記半導体素子に電気的に接続される第2の配線(ソース電極16)を上記他の配線として形成する。

【0104】

更に、本製造方法は、上記第2の配線の形成後に上記フォトレジスト膜58を除去する。

【0105】

ここで、上記タンタルナイトライド層72の成膜は、上記フォトレジスト膜58が融解する前に終了する。

【0106】

(3)エレクトロマイグレーション耐性

次に、本実施の形態に従うエアブリッジ配線のエレクトロマイグレーション耐性を評価した結果を説明する。

【0107】

上述の熱劣化加速試験と同様の方法によってエレクトロマイグレーション耐性を評価した。

【0108】

評価に用いた評価試料は、Ti/Al積層膜の上に、Ti層(厚さ数10nm)、Ta層(厚さ100nm)、TaN層(厚さ100nm、窒素含有率50%)、及びAu層(厚さ50nm〜300nm)を順次積層したものである。Ti層、Ta層、TaN層、及びAu層の成膜方法は、上述の成膜方法と同じである。一方、加熱温度は、450℃である。

【0109】

図13は、本実施の形態に従う熱劣化加速試験の結果を説明する図である。比較のため、図13には、Ti/TaN/Au及びTi/Pt/Auの結果(図3参照)と、本実施の形態に従う熱劣化加速試験の結果の双方が記載されている。

【0110】

「Ta/TaN」と表示された破線は、Ti/Al積層膜とAu層の間にTi/Ta/TaN積層膜が形成された上記評価試料の反応時間(6分)を表している(Ta層及びTaN層の厚さは、夫々100nm)。

【0111】

一方、「TaN」と表示された曲線は、Ti/Al積層膜とAu層の間に、Ti/TaxN1-x積層膜(0≦X<1)が形成された試料の反応時間を表している(但し、TaxN1-x層の厚さは200nm)。

【0112】

また、「TaN(t=200nm)」と表示された破線は、Ti/Al積層膜とAu層の間に、Ti層(厚さ数10nm)の上に厚さが200nmで窒素含有率が50%のTaN層が積層されたTi/TaN積層膜によって形成された試料の反応時間(4分)を表している。

【0113】

一方、「Pt」と表示された破線は、Al層とAu層の間にTi/Pt積層膜が形成された試料の反応時間(2分)を表している(Pt層の厚さは、200nm)。

【0114】

ここで、Ti層は、Ti/Ta/TaN積層膜、Ti/TaN積層膜、及びTi/Pt積層膜の何れにも形成されているので、反応時間の違いを生じさせるものではない。従って、各積層膜のエレクトロマイグレーション耐性の違いに寄与する金属層は、Ta/TaN積層膜、TaN層、及びTi/Pt層である。

【0115】

図13から明らかなように、Ti/Ta/TaN積層膜が形成された試料の反応時間は、Ti/Pt積層膜が形成された試料の3倍に達し、しかもTi/TaN(厚さ200nm)が形成された試料の1.5倍である。

【0116】

この事実は、Ta/TaN積層膜のエレクトロマイグレーション耐性が、TaN層(厚さ200nm)を超え、従来のPt層より格段に高いことを示している。

【0117】

尚、図13には、Ti層に厚さ100nmのTaN層を積層したTi/TaN積層膜に対して熱劣化加速試験を実施した結果も、「TaN(t=100nm)」と付した破線で示されている。図13に示されているように、100nmのTaNの形成された試料の反応時間は1分であり、Pt層(厚さ200nm)の形成された試料の半分でしかない。

【0118】

上述したように、Ta/TaN積層膜のエレクトロマイグレーション耐性は、同じ膜厚のTaN層のエレクトロマイグレーション耐性を超えている。その理由は、TaN層をTa層の上に成長するとTaN層の層構造(組織)が変化し、TaN層が緻密化するためと推定される。例えば、Ta層の上にTaN層を成長すると大小の結晶粒が混在して成長し、大きなTaNの結晶粒の間を小さな結晶粒が埋めて、TaN層が緻密化されると考えられる。

【0119】

(4)動 作

最後に、本実施の形態に従うマルチゲートトランジスタ2の動作について以下説明する。

【0120】

動作の前提として、各電極は次のように接続される。まず、マルチゲートトランジスタ2のソース電極16は、接地面に電気的に接続される。一方、ドレイン電極18は、負荷抵抗を介して電源に電気的に接続される。この状態で、ゲート電極22に信号が入力される。

【0121】

ゲート電極22に入力された信号電圧は、各GaN−HEMT4のゲート20に供給され、相互コンダクタンスに従って、各GaN−HEMT4のドレイン電流を変化させる。ドレイン電流は、(ドレイン電極18を形成する)共通電極14´によって合流された後、負荷に供給される(本実施の形態のGaN―HEMTは、nチャネル電界効果トランジスタである。従って、電流は負荷からドレインに向かって流れる。従って、正確には、「ドレイン電流」ではなく、ドレインから流出した電子流が合流され負荷に供給される。)。

【0122】

ここで、ドレイン電流は共通電極14´によって束ねられるので、負荷に流れる電流は、マルチゲートトランジスタ2を形成するGaN−HEMT4の個数分だけ大きくなる。

【0123】

この時、各GaN−HEMT4のソース電流は、エアブリッジ配線12を経由して共通電極14で束ねられた後、接地面に放出される。従って、エアブリッジ配線12に流れる電流も、ゲートに印加される信号電圧に従って変化する。そして、エアブリッジ配線12に流れる電流の平均値は1×105A/cm2を超える。

【0124】

しかし、本実施の形態に従うマルチゲートトランジスタ2では、エアブリッジ配線12は、エレクトロマイグレーション耐性の高いTa/TaN積層膜74によって支持されている。このため、エアブリッジ配線12が断線する虞はない。

【0125】

ところで、各GaN−HEMTのソース6にも大電流が流れる。この際、ソース電極16の電極10´を形成するAu層がエレクトロマイグレーションして、ソース6に設けられたTi/Alオーミック電極34と反応する虞がある。しかし、上記製造手順から明らかなように、電極10´を形成するAu層(第1〜第3のAu層44,46,48)は、エレクトロマイグレーション耐性の高いTa/TaN積層膜74によって、Ti/Alオーミック電極34と分離されている。従って、両者が反応する虞はない。

【0126】

また、Ta/TaN積層膜42の抵抗値は、同じ厚さのTaN層の抵抗値の約6割しかない。

【0127】

ところで、ゲート電極22に入力された信号電圧は、ゲート電極22(第1の配線)を伝播する。このゲート電極22は、エアブリッジ配線12と交差している。しかし、両者は空間38によって分離されているので、寄生容量による両者の間のクロストークは小さい。この点は、後述する他の実施の形態にも共通する。

【0128】

このように寄生容量が小さいので、本実施の形態に従うマルチゲートトランジスタは、例えば、数GHzで動作する。

【0129】

(実施の形態2)

本実施の形態は、実施の形態1の半導体装置において、エアブリッジ配線12を形成するTa/TaN層をTa/Ti/TaN(窒素含有率50%)積層膜で代替した半導体装置およびその製造方法に関する。

【0130】

(1)構 成

本実施の形態に従う半導体装置の構成は、(エアブリッジ配線12を含む)ソース電極16及びドレイン電極18の構造を除き、実施の形態1の半導体装置と同じである。

【0131】

ソース電極16およびドレイン電極18は、実施の形態1と同様に、同時に形成される。従って、ソース電極16とドレイン電極18は同一の積層構造を有している。そこで、ソース電極16の一部を形成するエアブリッジ配線12に着目して、本実施の形態に従う半導体装置(マルチゲートトランジスタ)の構成を以下に説明する。

【0132】

図14は、本実施の形態に従うマルチゲートトランジスタを形成するエアブリッジ配線12の断面を説明する図である。

【0133】

本実施の形態のエアブリッジ配線では、実施の形態1に於いてエアブリッジ配線12を形成しているTa/TaN層74が、Ta/Ti/TaN積層膜80によって代替されている(図9及び図14参照)。ここで、Ta/Ti/TaN積層膜80は、Ta層70、Ti層78と、TaN層72が順次積層されて形成されている。

【0134】

また、Ta層70、Ti層78、及びTaN層72の厚さは、夫々、100nm、10nm、及び100nmである。その他の金属層の厚さは、実施の形態1に従うマルチゲートトランジスタの対応する金属層と同じである。尚、TaN層の窒素含有率は、50%としている。

【0135】

すなわち、本実施の形態に従うマルチゲートトランジスタでは、実施の形態1に従うマルチゲートトランジスタにおいて、エアブリッジ配線を形成するTa(タンタル)層70とTaN(タンタルナイトライド)層72の間に、他のTi(チタン)層78が介在している。

【0136】

(2)製造手順

本実施の形態に従うマルチゲートトランジスタの製造手順は、実施の形態1に於けるマルチゲートトランジスタの製造手順と略同じである。以下異なる製造手順について説明する。

【0137】

本実施の形態では、Ti/Ta/TaN/Auスパッタ膜ではなくTi/Ta/Ti/TaN/Auスパッタ膜82が形成される点を除き、実施の形態1と同じである。ここで、Ta層とTaN層の間に介在するTi層78は、Tiをターゲットするスパッタ法によって形成される。スパッタガスはArである。

【0138】

すなわち、本実施の形態に従う半導体装置の製造方法では、実施の形態1で説明した製造方法おいて、Ta(タンタル)層の上に他のTi(チタン)層を積層してから、TaN(タンタルナイトライド)層が積層される。

【0139】

(3)エレクトロマイグレーション耐性

次に、Ta/Ti/TaN積層膜80のエレクトロマイグレーション耐性が熱劣化加速試験によって評価された結果が説明される。評価に用いた試料は、Ti/Al積層膜の上に、上記Ti/Ta/Ti/TaN/Auスパッタ膜80が積層されたものである。但し、Au層の厚さは50〜300nmである。

【0140】

図15は、本実施の形態に従うTa/Ti/TaN積層膜80に対して実施された熱劣化加速試験の結果を説明する図である。比較のため、図15には、図3及び図13で説明した熱劣化加速試験の結果も記載する。

【0141】

「Ta/Ti/TaN」と表示された破線は、本実施の形態に従うTa/Ti/TaN積層膜80が形成された試料の反応時間(8分)を表している。図15から明らかなように、Ta/Ti/TaN積層膜80が形成された試料の反応時間は、Pt層が形成された試料の4倍、実施の形態1に従うTa/TaN積層膜74が形成された試料の1.3倍である。

【0142】

この事実は、Ta/Ti/TaN積層膜80のエレクトロマイグレーション耐性は、実施の形態1に従うTa/TaN積層膜74を超え、従来のPt層より格段に高いことを示している。

【0143】

このように、Ta/Ti/TaN積層膜80のエレクトロマイグレーション耐性が、実施の形態1に従うTa/TaN積層膜より更に高くなった理由は、Ta層とTaN層の間にTi層を介在させることによって、TaN層の緻密化が促進されたためと考えられる。

【0144】

尚、本実施の形態に従うマルチゲートトランジスタの動作は、エアブリッジ配線のエレクトロマイグレーション耐性がより高くなっている点を除けば、実施の形態1に従うマルチゲートトランジスタと同じである。

【0145】

(実施の形態3)

本実施の形態は、実施の形態1の半導体装置において、ソース電極を覆う保護膜がエアブリッジ配線の下側で除去された半導体装置およびその製造方法に関する。

【0146】

(1)構 成

図16は、本実施の形態に従うマルチゲートトランジスタ84の斜視図である。図17は、図16のB−B線に於ける断面を矢印の方向から見た図である。

【0147】

図16に示すように、本実施の形態に従うマルチゲートトランジスタ84は、ゲート電極22を形成する共通電極14´´が保護膜32で覆われていない点で、実施の形態1に従うマルチゲートトランジスタ2と相違する。尚、共通電極14´´は、ゲート電極22のうち、エアブリッジ配線12の下側に配置された部分である。

【0148】

共通電極14´´以外の構成は、実施の形態1のマルチゲートトランジスタ2と同じである。従って、共通電極14´´に関する構成以外の説明は省略される。

【0149】

実施の形態1に従うマルチゲートトランジスタ2では、図9に示すように、エアブリッジ配線12の下側でも、共通電極14´´は保護膜32によって覆われている。従って、エアブリッジ配線12と共通電極14´´の間に、SiN等の誘電体膜が存在する領域が発生することになる。この誘電体膜の存在によって、エアブリッジ配線12を含むソース電極16と、共通電極14´´を含むゲート電極22間の寄生容量が大きくなる。

【0150】

そこで、本実施の形態に従うマルチゲートトランジスタ84では、図16に示すように、エアブリッジ配線12の下側でソース電極16を覆う保護膜32が除去されて、寄生容量の最小化が図られている。すなわち、図17のように、第1の配線(共通電極14´´を含むゲート電極22)が第2の配線(エアブリッジ配線12を含むソース電極16)によって横切られる領域で、保護膜(SiN膜)が取り除かれている。

【0151】

このため、本実施の形態に従うマルチゲートトランジスタ84は、ゲート電極22とソース電極16間の信号干渉が小さくなる。故に、本実施の形態に従うマルチゲートトランジスタ84は、実施の形態1のマルチゲートトランジスタ2より高速で動作することができる。

【0152】

保護膜32は、ゲート電極22を不純物の汚染から保護して、出力信号(ドレイン電流波形)の劣化を防止するためのものである。

【0153】

しかし、出力信号の劣化を防止するためには、ゲート20を形成するNi/Au電極10´´が保護膜32で覆われていれば十分である。従って、本実施の形態のように共通電極14´´を覆う保護膜32が除去されても、出力信号が劣化することはない。

【0154】

尚、実施の形態1に従うマルチゲートトランジスタ84では、保護膜32はNi/Au共通電極14´´を覆い、共通電極14´´を形成するNi層の酸化防止に役立っている。

【0155】

尚、エアブリッジ配線12を形成するTa/TaN層を、実施の形態2で説明したように、Ta/Ti/TaN積層膜で代替しても良い。

【0156】

(2)製造手順

図18は、本実施の形態の保護膜32乃至エアブリッジ配線12を形成する製造手順を説明する工程断面図である。ここで、図18は、製造手順の進行に合わせて、図16のB−B線に於ける断面を矢印の方向から見た図である。

【0157】

以下に説明する通り、本実施の形態の製造手順は、保護膜の形成及びエアブリッジ用フォトレジスト膜(マスク)の形成を除き、実施の形態1の製造手順と同じである。

【0158】

まず、マルチゲートトランジスタ2を形成する複数のGaN−HEMT4(オーミック電極を含む)が形成された基板50を準備する。

【0159】

次に、Ni/Auゲート電極22を形成する。

【0160】

これらのステップは、対応する実施の形態1と同じである。従って、詳しい説明は省略する。

【0161】

まず、ゲート電極22の形成されたSiC基板24の全面に、保護膜32となる厚さ500nmのSiN膜を堆積する。ここで、SiN膜の厚さとしては、5nm乃至500nmが好ましい。

【0162】

その後、保護膜の形成予定領域にフォトレジスト膜を形成する。ここで、本実施の形態では、実施の形態1とは異なり、共通電極14´´はフォトレジスト膜によって覆われない。

【0163】

このフォトレジスト膜をエッチングマスクとして、SiN膜がドライエッチングによって除去されて、保護膜32が形成される(図16参照)。

【0164】

従って、ゲート電極22(第1の配線)がソース電極16(第2の配線)によって横切られる領域(交差予定位置)、すなわちエアブリッジ配線12の形成予定領域の下側では、保護膜(SiN膜)が取り除かれる(図18(a)参照)。

【0165】

次に、基板24の上に、共通電極14´´の上部及び側面を覆って線状に延在するエアブリッジ形成用フォトレジスト膜58を形成する(図18(b)参照)。

【0166】

次に、図18(c)に示すように、エアブリッジ形成用フォトレジスト膜58が形成された基板24の上に、Ti/Ta/TaN(窒素含有率50%)/Auスパッタ膜76を形成する。

【0167】

次に、Ti/Ta/TaN/Auスパッタ膜76の上に、メッキ法によって第2及び第3のAu層46,48を形成する。

【0168】

次いで、図18(d)に示すように、エアブリッジ形成用フォトレジスト膜58を除去し、マルチゲートトランジスタ84が完成する。

【0169】

(3)動作

本実施の形態に従うマルチゲートトランジスタ84の動作は、実施の形態1のマルチゲートトランジスタ2と略同じである。但し、本実施の形態に従うマルチゲートトランジスタ84は、ソース電極16とゲート電極22間の寄生容量が小さいので、実施の形態1に従うマルチゲートトランジスタより高周波で動作する。

【0170】

(実施の形態4)

本実施の形態は、実施の形態1〜3に従うマルチゲートトランジスタを具備する高周波増幅器に関する。

【0171】

図19(は、本実施の形態に従う高周波増幅器の回路図である。

【0172】

本実施の形態に従う高周波増幅器86は、実施の形態1〜3の何れかに従うマルチゲートトランジスタ2´を有している。

【0173】

また、本実施の形態に従う高周波増幅器86は、電気信号が入力される第1の端子(入力端子88)と、増幅された電気信号が出力される第2の端子(出力端子90)を有している。

【0174】

また、本実施の形態に従う高周波増幅器86は、第1の端子(入力端子88)から前記第1の配線(ゲート電極22)に至る、電気信号が伝播する第1の経路92を具備している。

【0175】

更に、本実施の形態に従う高周波増幅器86は、ドレイン8に電気的に接続された第3の配線(ドレイン電極18)から第2の端子(出力端子90)に至る、電気信号が伝播する第2の経路94を具備する。

【0176】

ここで、第1及び第2の経路92には、第1及び第2のコンデンサ97,99が配置されている。従って、第1及び第2の経路92,94には、高周波信号のみが伝播する。

【0177】

また、本実施の形態に従う高周波増幅器86は、電源電圧に接続される第3の端子(電源端子96)を有している。そして、電源端子96は、第1の抵抗98を介して、第2の配線(ドレイン電極18)に接続されている。

【0178】

また、電源端子96は、第2の抵抗100を介して、第1のコンデンサ97と第1の配線(ゲート電極22)の間に設けられた接続点に接続されている。更に、この接続点は、第3の抵抗102を介して接地面に接続されている。ここで、第2及び第3の抵抗100,102は、マルチゲートトランジスタ2´のバイアス点を設定する。

【0179】

一方、ソース電極16は、第4の抵抗104と第3のコンデンサ106が並列に接続された回路を介して、接地面に接続されている。

【0180】

ここで、マルチゲートトランジスタ2´は所定のパッケージに搭載され、第1〜第4の抵抗及び第1〜第3のコンデンサと共に、プリント基板上に配置される。

【0181】

以上のように形成された高周波増幅86は、以下のように動作する。電気信号が第1の端子88に入力されると、第1の経路92を伝播し、マルチゲートトランジスタ2´のゲート電極に到達する。マルチゲートトランジスタ2´は、上記各実施の形態で説明したように動作して、入力した電気信号を増幅する。増幅された電気信号は、第2の経路94を伝播して、第2の端子90から出力される。

【0182】

本実施の形態に従う高周波増幅器86は、実施の形態1〜3に従うマルチゲートトランジスタ2´を備えているので、大電流動作で動作させてもエアブリッジ配線が断線することはない。

【0183】

尚、図19を参照して説明した回路は、実施の形態1〜3に従うマルチゲートトランジスタを利用した高周波増幅器の一例に過ぎない。

【0184】

(実施の形態5)

本実施の形態は、実施の形態4に従う高周波増幅器を備えた送信機に関する。

【0185】

図20(は、本実施の形態に従う送信機108のブロック図である。

【0186】

本実施の形態に従う無線送信機108は、図20に示すように、電気信号が入力される入力端子116と、アンテナ112が接続される出力端子114と、実施の形態5に従う高周波増幅器86を備えている。更に、本実施の形態に従う無線送信機108は、入力信号に従って変調された高周波信号を生成し出力する高周波信号発生ユニット110(例えば、電圧制御発信器(voltage controlled oscillator; VCO))を具備している。

【0187】

そして、本実施の形態に従う無線送信機108は、入力端子116が、高周波信号発生ユニット110の入力端子に接続されている。また、高周波信号発生ユニット110の出力端子が、高周波増幅器86の第1の端子(入力端子88)に接続され、出力端子114が、高周波増幅器86の第2の端子(出力端子90)に接続されている。

【0188】

この送信機108は、以下のように動作する。入力端子116から入力された電気信号は、高周波信号発生ユニット110に供給される。高周波発生ユニット110は、入力された電気信号によって変調された高周波信号を発生し、高周波増幅器86に供給する。高周波増幅器86は供給された高周波信号を増幅して、出力端子114に接続されたアンテナ112に供給する。

【0189】

ここで、送信機108は、実施の形態5に従う高周波増幅器86を備えているので、大電力信号をアンテナに供給することができる。

【0190】

本実施の形態に従う送信機は、例えば携帯電話システムの基地局に使用される。

【0191】

(変形例)

上記各実施の形態では、TaN層の窒素含有率は50%を例に説明した。しかし、TaN層の窒素含有率は、この値に限られない。TaN層の窒素含有率は、好ましくは、48%より大きく52%以下であればよく、更に好ましくは49%以上51%以下であればよい。

【0192】

図15から明らかなように、窒素含有率が48%より大きければ、Ta/TaxN1-x積層膜(又は、Ta/Ti/TaxN1-x積層膜)のエレクトロマイグレーション耐性が従来のPt層より高くなる。従って、TaNの窒素含有率は、48%より大きいことが好ましい。一方、窒素含有率が高くなるに従いTaNの成膜が困難になり、窒素含有率52%以上のTaN膜の成膜は極めて困難になる。従って、TaNの窒素含有率は、52%以下が好ましい。

【0193】

上記各実施の形態では、保護膜は窒化珪素で形成されている。しかし、保護膜として使用可能な絶縁膜は窒化珪素(SiN)膜に限られない。例えば、保護膜は二酸化珪素(SiO2)膜によって形成されてもよい。

【0194】

上記各実施の形態では、エアブリッジ配線はソース電極に設けられている。しかし、ドレイン電極がゲート電極と交差する場合には、エアブリッジ配線はドレイン電極に設けることが好ましい。すなわち、上記第2の配線は、電界効果トランジスタのソースでなく、ドレインに接続されていてもよい。また、本実施の形態のエアブリッジ配線は、ソース電極及びドレイン電極以外の配線に形成されてもよい。

【0195】

上記各実施の形態では、GaN−HEMTによってマルチゲートトランジスタが形成されている。しかし、他の電界効果トランジスタ(例えば、半絶縁性InPを基板とし、InGaAs製のチャネル層と、SiがドーピングされたInAlAs製のバリア層を具備するInP−HEMT)によって、マルチゲートトランジスタが形成されてもよい。

【0196】

更に、上記各実施の形態で説明されたエアブリッジ配線は、マルチゲートトランジスタ以外の半導体装置、例えば、複数のゲートを備えた電界効果トランジスタ(特許文献1)にも適用できる。

【0197】

また、上記各実施の形態に従う半導体装置を形成する半導体素子は、電界効果トランジスタである。しかし、上記半導体素子は、電界効果トランジスタ以外の他の半導体素子、例えばバイポーラトランジスタであってもよい。上記半導体素子としてバイポーラトランジスタが使用される場合には、例えば、第1の配線はベースに接続され、第2の配線はエミッタ又はコレクタに接続される。

【0198】

更に、上記各実施の形態では、ゲート電極はNi/Au積層膜によって形成されたが、他の積層膜によって形成されてもよい。また、上記各実施の形態では、絶縁膜がドライエッチングによってエッチングされて保護膜に加工されるが、ウエットエッチングやイオンミリング等他のエッチング法でエッチングされてもよい。

【0199】

以上の実施の形態をまとめると、次の付記のとおりである。

【0200】

(付記1)

第1の配線と、

前記第1の配線と交差する方向に延在し、前記第1の配線と空間を介して配置され、タンタル層、該タンタル層上に形成されたタンタルナイトライド層、該タンタルナイトライド層上に形成された金属層を含む第2の配線と、

を有することを特徴とする半導体装置。

【0201】

(付記2)

付記1に記載の半導体装置において、

前記タンタルナイトライド層の窒素含有率は、48%より大きく52%以下であることを、

特徴とする半導体装置。

【0202】

(付記3)

付記1又は付記2に記載の半導体装置において、

前記タンタル層とタンタルナイトライド層の間に、チタン層が形成されていることを、

特徴とする半導体装置。

【0203】

(付記4)

付記1〜付記3の何れか1項に記載の半導体装置において、

更に半導体素子を有し、前記第1の配線及び前記第2の配線は、半導体素子に接続され、

前記半導体素子へ入力される信号は、前記第1の配線を伝播することを、

特徴とする半導体装置。

【0204】

(付記5)

付記4に記載の半導体装置において、

更に、前記第1の配線を覆う保護膜を有することを

特徴とする半導体装置。

【0205】

(付記6)

付記5に記載の半導体装置において、

前記第1の配線が前記第2の配線と交差する領域では、前記保護膜が取り除かれていることを、

特徴とする半導体装置。

【0206】

(付記7)

付記5又は6に記載の半導体装置において、

前記保護膜が、窒化珪素膜又は二酸化珪素膜であることを、

特徴とする半導体装置。

【0207】

(付記8)

付記4乃至7の何れか1項に記載の半導体装置において、

前記半導体素子が、複数の電界効果トランジスタであって、

前記複数の電界効果トランジスタ夫々のソース、ゲート、及びドレインの夫々は、同じ方向に延在し、、

前記複数の電界効果トランジスタの各々は、隣接する前記複数の電界効果トランジスタと、前記ソース及び前記ドレインの少なくても一方を共有し、

前記第1の配線が、前記ゲートに電気的に接続され、

前記第2の配線が、前記ソース及び前記ドレインの何れか一方に電気的に接続されていることを、

特徴とする半導体装置。

【0208】

(付記9)

付記8に記載の半導体装置において、

前記電界効果トランジスタが、

窒化ガリウムをチャネル層とすることを特徴とする半導体装置。

【0209】

(付記10)

第1の配線と、

前記第1の配線と交差する方向に延在し、前記第1の配線と空間を介して配置され、タンタル層、該タンタル層上に形成されたタンタルナイトライド層、該タンタルナイトライド層上に形成された金属層を含む第2の配線と、

前記第1及び第2の配線が接続された複数の電界効果トランジスタを有し、

前記複数の電界効果トランジスタ夫々のソース、ゲート、及びドレインの夫々は、同じ方向に延在し、

前記複数の電界効果トランジスタの各々は、隣接する前記複数の電界効果トランジスタと、前記ソース及び前記ドレインの少なくても一方を共有し、

前記第1の配線が、前記ゲートに電気的に接続され、

前記第2の配線が、前記ソースに電気的に接続され、

第3の配線が、前記ドレインに電気的に接続されている半導体装置を具備し、

更に、前記第1の配線に電気的に接続され、電気信号が入力される第1の端子と、

前記第3の配線に電気的に接続され、増幅された前記電気信号が出力される第2の端子とを具備する高周波増幅器。

【0210】

(付記11)

第1の配線と、

前記第1の配線と交差する方向に延在し、前記第1の配線と空間を介して配置され、タンタル層、該タンタル層上に形成されたタンタルナイトライド層、該タンタルナイトライド層上に形成された金属層を含む第2の配線と、

前記第1及び第2の配線が接続された複数の電界効果トランジスタを有し、

前記複数の電界効果トランジスタ夫々のソース、ゲート、及びドレインの夫々は、同じ方向に延在し、

前記複数の電界効果トランジスタの各々は、隣接する前記複数の電界効果トランジスタと、前記ソース及び前記ドレインの少なくても一方を共有し、

前記第1の配線が、前記ゲートに電気的に接続され、

前記第2の配線が、前記ソースに電気的に接続され、

第3の配線が、前記ドレインに電気的に接続されている半導体装置を具備し、

更に、前記第1の配線に電気的に接続され、電気信号が入力される第1の端子と、

前記第3の配線に電気的に接続された、増幅された前記電気信号が出力される第2の端子とを具備する高周波増幅器を備えた無線送信機であって、

電気信号が入力される入力端子と、

アンテナが接続される出力端子と、

入力信号に従って変調された高周波信号を生成し出力する高周波信号発生ユニットとを具備し、

前記入力端子が、前記高周波信号発生ユニットの入力端子に接続され、

前記高周波信号発生ユニットの出力端子が、前記第1の端子に接続され、

前記出力端子が前記第2の端子に接続されている、

無線送信機。

【0211】

(付記12)

半導体基板上方に第1の配線を形成する工程と、

前記第1の配線上方にマスクを形成する工程と、

前記マスク上に、タンタル層、タンタルナイトライド層、及び金属層を順次積層して、前記第1の配線に交差する方向に延在する第2の配線を形成する工程と、

前記第2の配線の形成後に前記マスクを除去する工程を具備し、

前記タンタルナイトライド層は、前記マスクが融解する前に成膜が終了することを特徴とする

半導体装置の製造方法。

【0212】

(付記13)

付記12に記載の半導体装置の製造方法において、

前記タンタルナイトライド層の窒素含有率が、48%より大きく52%以下であることを、

特徴とする半導体装置の製造方法。

【0213】

(付記14)

付記12又は付記13に記載の半導体装置の製造方法において、

前記タンタル層の上にチタン層を積層してから、前記タンタルナイトライド層を積層することを、

特徴とする半導体装置の製造方法。

【0214】

(付記15)

付記12乃至付記14の何れか1項に記載の半導体装置の製造方法において、

前記タンタル層が、タンタルをターゲットとするスパッタ法で形成され、

前記タンタルナイトライド層が、タンタルをターゲットとする反応性スパッタ法で形成されることを、

特徴とする半導体装置の製造方法。

【0215】

(付記16)

付記12乃至付記15の何れか1項に記載の半導体装置の製造方法において、

前記タンタル層が、タンタルをターゲットとするスパッタ法で形成され、

前記タンタルナイトライド層が、タンタルをターゲットとし窒素を反応性ガスとする反応性スパッタ法で形成され、

前記金属層が、

金をターゲットとするスパッタ法で、第1の金層が形成され、

その後、メッキ法によって第2の金層が積層されて形成されることを、

特徴とする半導体装置の製造方法。

【0216】

(付記17)

付記12乃至16の何れか1項に記載の半導体装置の製造方法において、

前記半導体装置が、前記第1の配線及び前記第2の配線に接続された半導体素子を有し、

前記第1の配線は、前記半導体素子へ入力される信号が伝播する配線であることを、

特徴とする半導体装置の製造方法。

【0217】

(付記18)

付記12乃至17の何れか1項に記載の半導体装置の製造方法において、

前記マスクを形成する前に、

前記第1の配線を、保護膜で覆うことを、

特徴とする半導体装置の製造方法。

【0218】

(付記19)

付記18に記載の半導体装置の製造方法において、

前記マスクを形成する前に、

前記第2の配線下方の前記保護膜を取り除くことを、

特徴とする半導体装置の製造方法。

【0219】

(付記20)

付記18又は19に記載の半導体装置の製造方法において、

前記保護膜が、窒化珪素膜又は二酸化珪素であることを、

特徴とする半導体装置の製造方法。

【図面の簡単な説明】

【0220】

【図1】Ti/TaN/Auエアブリッジ配線の左端を拡大した図である。

【図2】図1中の円で囲った領域Aを拡大した図である。

【図3】TaNの窒素含有率と反応時間の関係を説明する図である。

【図4】TiTaN/Auエアブリッジ配線の製造工程を説明する断面図である(その1)。

【図5】Ti/TaN/Auエアブリッジ配線の製造工程を説明する断面図である(その2)。

【図6】Ti/TaN/Auエアブリッジ配線の製造工程を説明する断面図である(その3)。

【図7】実施の形態1によるマルチゲートトランジスタの構成を説明する斜視図である。

【図8】図7のA−A線に於ける断面を説明する図である。

【図9】図7のB−B線に於ける断面を説明する図である。

【図10】実施の形態1によるエアブリッジ配線構造の製造工程を説明する断面図である(その1)。

【図11】実施の形態1によるエアブリッジ配線構造の製造工程を説明する断面図である(その2)。

【図12】実施の形態1によるエアブリッジ配線構造の製造工程を説明する断面図である(その3)。

【図13】実施の形態1に従うTa/TaN積層膜に対して実施された熱劣化加速試験の結果を説明する図である。

【図14】実施の形態2に従うマルチゲートトランジスタを形成するエアブリッジ配線の断面を説明する図である。

【図15】実施の形態2に従うTa/Ti/TaN積層膜に対して実施された熱劣化加速試験の結果を説明する図である.

【図16】実施の形態3に従うマルチゲートトランジスタの斜視図である。

【図17】図16のB−B線に於ける断面を矢印の方向から見た図である。

【図18】実施の形態3に従うマルチゲートトランジスタの製造手順を説明する工程断面図である。

【図19】実施の形態4に従う高周波増幅器の回路図である。

【図20】実施の形態5に従う送信機のブロック図である。

【符号の説明】

【0221】

2・・・マルチゲートトランジスタ 4・・・GaN−HEMT

6・・・ソース 8・・・ドレイン

10,10´,10´´・・・電極 12・・・エアブリッジ配線

14,14´,14´´・・・共通電極

16・・・ソース電極 18・・・ドレイン電極

20・・・ゲート 22・・・ゲート電極

24・・・SiC基板 26・・・UID−GaNチャネル層

28・・・n型AlGaNキャリア供給層 30・・・UID−GaNキャップ層

32・・・保護膜 34・・・オーミック電極

36・・・AlGaN不活性領域 38・・・空間

40・・・Ti層 42・・・TaN層

44・・・第1のAu層 46・・・第2のAu層

48・・・第3のAu層 50・・・基板

52・・・リフトオフ用フォトレジスト膜 54・・・Ni/Au積層膜

56・・・SiN膜 58・・・エアブリッジ形成用フォトレジスト膜

60・・・電子流れ 62・・・内壁 64・・・Au原子

66・・・結晶粒界

68・・・Ti/Pt/Auスパッタ膜(又は、Ti/TaN/Auスパッタ膜)

70・・・Ta層 72・・・TaN層 74・・・Ta/TaN積層膜

76・・・Ti/Ta/TaN/Auスパッタ膜 78・・・他のTi層

80・・・Ta/Ti/TaN積層膜

82・・・Ti/Ta/Ti/TaN/Auスパッタ膜

84・・・マルチゲートトランジスタ(実施の形態3)

86・・・高周波増幅器 88・・・入力端子

90・・・出力端子 92・・・第1の経路

94・・・ドレイン電極 96・・・電源端子

97・・・第1のコンデンサ 98・・・第1の抵抗

99・・・第2のコンデンサ 100・・・第2の抵抗

102・・第3の抵抗 104・・・第4の抵抗

106・・・第3のコンデンサ 108・・・無線送信機

110・・・高周波信号発生ユニット 112・・・アンテナ

114・・・出力端子 116・・・入力端子

【技術分野】

【0001】

本発明は、半導体装置及びその製造方法に関する。

【背景技術】

【0002】

半導体装置、例えば電力増幅用電界効果トランジスタを低コストで大量に生産するためには、半導体装置を微細化する必要がある。

【0003】

しかし、半導体装置を微細化すると、配線間の距離、特に絶縁膜を介して交差する配線間の距離が狭くなる。このような配線間隔の狭窄化は、配線間の寄生容量を大きくして、半導体装置の高周波動作を困難にする。

【0004】

絶縁膜を介して交差する配線間の寄生容量を小さくするためには、エアブリッジ配線が有効である。特に、マルチゲートトランジスタと呼ばれる、複数の電界効果トランジスタ(field effect transistor;以下、FETと呼ぶ)を同一基板上に配置した電力増幅用電界効果トランジスタの高速化には、エアブリッジ配線が有効である。

【0005】

マルチゲートトランジスタでは、複数のFETが一列に整列させられて、対応する端子(ソース、ドレイン、ゲート)同士が櫛の歯状の電極によって接続されている。この時、複数のソースを接続するソース電極と、複数のゲートを接続するゲート電極とに交差部位が生じてしまう。

【0006】

この交差部位には、ソース電極とゲート電極の接触を回避するため、両者を絶縁膜を介して立体交差させるブリッジ(橋渡し)配線構造が形成される(特許文献1)。

【0007】

ブリッジ配線構造では、交差する配線間に介在する絶縁膜の高い誘電率によって、寄生容量が大きくなってしまう。従って、マルチゲートトランジスタを高速化しようとする場合には、交差する配線間が空間によって隔てられているエアブリッジ配線が用いられる。

【0008】

エアブリッジ配線を形成する金属層としては、導電率が高い金が広く用いられている。しかし、金(Au)は柔らかく単独ではエアブリッジ構造を維持することができない。そこで、チタン(Ti)と白金(Pt)の積層構造を支持体とするTi/Pt/Au積層構造によって、エアブリッジ配線が形成される。ここで、Tiは基板とエアブリッジ層の密着を良くするためのものであり、Au層は、Pt層によって支持されている(特許文献2)。

【0009】

ところで、近年、窒化ガリウム(GaN)によってチャネル層が形成された高電子移動トランジスタ(high electron mobility transistor;HEMT)が、高周波高出力トランジスタとして注目されている(GaNによってチャネル層が形成されたHEMTは、以後GaN−HEMTと表される。)。

【0010】

GaNは、SiやGaAsに比べ、バンドギャップが広い。このため、GaN−HEMTは、高温動作に適し、しかも破壊電界が高いため高電圧動作に適している。故に、GaN−HEMTは、小型化され大電流で動作させられても、動作温度の上昇やチャネルへ印加される電界の増大によって動作不良を起こすことはない。

【0011】

このため、GaN−HEMTによってマルチゲートトランジスタが形成され、高周波高出力電力増幅器として使用されている。

【特許文献1】特開2003−197740号公報

【特許文献2】特開2007−150282号公報

【発明の開示】

【発明が解決しようとする課題】

【0012】

上述したように、高周波動作に適したFETによってマルチゲートトランジスタを形成する場合、寄生容量が小さくなるエアブリッジ配線が採用される。ここで、GaN−HEMTのように大電流で動作するFETによってマルチゲートトランジスタを形成した場合、エアブリッジ配線にも大電流が流れることになる。

【0013】

本発明者は、この点に着目して、複数のGaN−HEMTを含むマルチゲートトランジスタ(以後、GaN−HEMTマルチゲートトランジスタと呼ばれる)を今後更に高出力化した場合、どのような影響が現れるのか検討した。

【0014】

その結果、エアブリッジに大電流を流すと、エアブリッジ配線を形成するAuがエレクトロマイグレーションして、Pt支持層の結晶粒界に入り込む虞のあることが明らかになった。この場合、Pt支持層が崩壊して、エアブリッジ配線が支持体を失い断線することが懸念される。

【0015】

そこで、本発明の目的は、大電流を流しても断線し難いエアブリッジ配線、すなわちエレクトロマイグレーション耐性の高いエアブリッジ配線を具備した半導体装置及びその製造方法を提供することである。

【課題を解決するための手段】

【0016】

本半導体装置は、第1の配線と、前記第1の配線と交差する方向に延在し、前記第1の配線と空間を介して配置され、タンタル層、該タンタル層上に形成されたタンタルナイトライド層、該タンタルナイトライド層上に形成された金属層を含む第2の配線とを有する。

【発明の効果】

【0017】

本半導体装置によれば、大電流を流しても断線し難いエアブリッジ配線を具備した半導体装置を提供することができる。

【発明を実施するための最良の形態】

【0018】

以下、図面にしたがって本発明の実施の形態が説明される。但し、本発明の技術的範囲はこれらの実施の形態に限定されず、特許請求の範囲に記載された事項とその均等物まで及ぶものである。

【0019】

特許文献2に開示されたようなTi/Pt/Au積層構造によって形成されたエアブリッジ配線では、エアブリッジ配線の本体は、厚いAu層である。しかし、Auは柔らかいので、Au層単独でエアブリッジ構造を保持することはできない。従って、Au層の下方に形成されたPt層によってAu層が支えられている。

【0020】

ところで、Auは、エレクトロマイグレーションしやすいことが知られている。このため、マルチゲートトランジスタを大電流(例えば、1×105A/cm2以上)で動作させた場合、電子流に押し流されたAu原子がAu層からPt膜中に移動して、Pt膜を破壊するのではと懸念される。

【0021】

図1は、エレクトロマイグレーションを説明する図である。図2は、図1中の円で囲った領域Aを拡大した図である。

【0022】

図1には、エアブリッジ配線12の左端が図示されている。ここで、エアブリッジ配線12は、空間38を介してマルチゲートトランジスタのゲートに接続される共通電極14の上方に形成されている。そして、エアブリッジ配線12は、Ti層40、Pt層42、第1のAu層44、第2のAu層46、及び第3のAu層48が積層されて形成されている。

【0023】

図1に示すように、エアブリッジ配線中の電子の流れ60は、エアブリッジ配線の内壁62近くまでは直進しその後向きを変える(尚、図1には、エアブリッジ配線12の底の部分を流れる電子流のみが描かれている。)。従って、図2に示すように、Au層44,46,48中のAu原子64は、電子流60によって衝突・散乱されて、Pt層42に向かって移動して行く(すなわち、エレクトロマイグレーションする。)。

【0024】

一方、Pt層42中には、成長方向に延びた多数の結晶粒界66(grain boundary)が存在している。Pt層42に向かって移動してきたAu原子64は、この結晶粒界66に入り込みPt微結晶同士の結合を断ち切ろうとする。

【0025】

その結果、Pt層42は崩壊し、エアブリッジ配線12を支持することができなくなる。そして、支持体を失ったエアブリッジ配線12は、ついには断線すると考えられる。

【0026】

尚、図1及び図2に示されたエアブリッジ配線は直角に折れ曲がっているが、エアブリッジ配線がなだらかに折れ曲がっている場合にも同様の現象が起きて、エアブリッジ配線は断線すると考えられる。

【0027】

電子流に曝された金属原子は、電子と衝突を繰り返して激しく振動し、やがて束縛されていた格子点から移動する。この時、個々の金属原子の移動方向は一定しないが、金属原子集団全体としては電子流の下流側に移動する。このような金属原子の移動現象が、エレクトロマイグレーションである。

【0028】

エレクトロマイグレーションの起因となる金属原子の振動は、高温に加熱された金属原子の振動に類似している。従って、高温でも安定な金属、すなわち高融点金属は、エレクトロマイグレーションに対しても強い耐性を有していると考えられる。

【0029】

そこで、本発明者は、配線として使用可能な高融点金属であるTa1-xNx(0≦X<1)のエレクトロマイグレーション耐性を検討した。

【0030】

エレクトロマイグレーション耐性は、被試験金属膜を加熱してその劣化速度を調べる熱劣化加速試験によって調べられた。被試験金属膜を高温に曝すことによって、金属原子が電子流に曝され激しく振動している状態を擬似的に作り出すことができる。

【0031】

具体的には、次のような試験が実施された。まず、Ti層の上にAl層が積層されたTi/Al積層膜を形成し、その上に、Ti層、Ta1-xNx層(0≦X<1)、及びAu層が順次積層された試料(Ti/Ta1-xNx/Au積層膜)(0≦X<1)を形成した。また、比較試料として、Ti/Al積層膜の上に、Ti層、Pt層及びAu層が、順次積層された試料(Ti/Pt/Au積層膜)を形成した。

【0032】

ここで、Ta1-xNx層は、Taをターゲットとして、反応性スパッタ法によって形成される。スパッタガス及び反応ガスは、夫々、Ar及びN2である。Au層及びPt層は、夫々、Au及びTaをターゲットとして、スパッタ法によって形成される。この時のスパッタガスは、Arである。

【0033】

ここで、Ti層、Ta1-xNx層、及びAu層の厚さは、夫々、数10nm、200nm、及び50nm〜300nmである。また、比較用試料のPt層の厚さは、Ta1-xNx層と同じ200nmである。尚、Al層及びTi層の厚さは、全ての試料で同じである。

【0034】

以上のようにして形成された試料が450℃に加熱されて、Au層の表面に変化が現れるまでの時間が計測される。ここでAu層の厚さは、この変化が現れやいように、実際のエアブリッジ配線のAu層より薄く形成されている。

【0035】

加熱前の試料の表面は、均一で何の特徴もない。しかし、加熱を続けるとやがて試料の表面に染みが現れる。この染みの現れるまでの加熱時間(以後、反応時間と呼ぶ)が計測され比較される。

【0036】

この染みは、Au原子が、Ta1-xNx層(又は、Pt層)を破壊して、Ta1-xNx層(又は、Pt層)の下に配置されたAl膜と反応してできたAlAu合金である。すなわち、熱劣化加速試験によって計測される反応時間は、激しく振動するAu原子によってTa1-xNx層(又は、Pt層)が破壊されるまでの時間を表している。従って、この反応時間が長い金属膜ほど、エレクトロマイグレーション耐性が高いと考えられる。

【0037】

図3は、Ta1-xNx層の組成を変えて反応時間を測定した結果である。横軸は、Ta1-xNx層の窒素含有率である。縦軸は反応時間である。「TaN」と表示された曲線は、Ti/Al積層膜とAu層の間にTi/Ta1-xNx積層膜が形成された試料の反応時間を表している。一方、「Pt」と表示された破線は、Ti/Al積層膜とAu層の間にTi/Pt積層膜が形成された試料の反応時間(2分)を表している。ここで、Ti層は、Ti/Ta1-xNx積層膜及びTi/Pt積層膜の双方に形成されているので、両者の反応時間に違いを起させるものではない。

【0038】

図3に示すように、窒素含有率が0%の試料すなわちTa層が形成された試料の反応時間(3分)は、Pt層が形成された試料の反応時間(2分)より長い。しかし、窒素含有率が増加すると、Ta1-xNx層の反応時間は一旦短くなり、比較試料より反応時間が短くなる。そして、反応時間は、窒素含有率40%近傍で最低になる。

【0039】

その後、Ta1-xNx層の反応時間は、窒素含有率の増加と共に急激に増加し、窒素含有率が48%で比較試料と同じになり、窒素含有率が50%で比較試料の2倍になる。その後も、反応時間は増加し続ける。しかし、窒素含有率が52%を超える試料の作製は困難であった。

【0040】

以上の結果は、窒素含有率が48%より高いTaNによって支持されたTi/TaN/Au積層膜によってエアブリッジ配線を形成すると、エレクトロマイグレーション耐性の高いエアブリッジ配線の形成が可能になることを教示している。

【0041】

そこで、本発明者は、Ti/TaN/Au積層膜によって形成されたエアブリッジ配線を具備するマルチゲートトランジスタの製造を試みた。以下、図4、図5、及び図6を用いてエアブリッジ配線の製造工程について説明をする。

【0042】

図4は、試作したマルチゲートトランジスタのゲート電極とソース電極が立体交差するエアブリッジ配線構造の断面図である。

【0043】

ゲート電極を形成する共通電極14´´は、n型AlGaNキャリア供給層28がイオン注入によって高抵抗化されたAlGaN不活性領域36の上に形成されている。そして、保護膜32によって覆われた共通電極14´´(ゲート電極)上を、空間38を介して、エアブリッジ配線12(ソース電極)が横切っている。

【0044】

ここで、エアブリッジ配線12は、Ti層40、TaN層42、第1のAu層44、第2のAu層46、及び第3のAu層48が積層されて形成されている。

【0045】

次に、試作したマルチゲートトランジスタに於けるエアブリッジ配線構造の製造手順を説明する。

【0046】

図5及び図6は、エアブリッジ配線構造の製造工程を説明する断面図である。

【0047】

まず、SiC基板24の上に、Unitentionally Doped(UID)−GaNチャネル層26、n型AlGaNキャリア供給層28、UID−GaNキャップ層(図示せず)が順次積層され、更にオーミック電極34が形成された基板50が準備される(図5(a)参照)。

【0048】

ここで、オーミック電極34は、ソース及びドレインとなる半導体領域の上に設けられる。また、UID−GaNキャップ層は、チャネルとなる半導体領域以外では除去されている(従って、図5(a)には図示されていない。)。そして、共通電極14´´の形成予定領域に露出したn型AlGaNキャリア供給層28は、イオン注入によって高抵抗化され、AlGaN不活性領域36となっている。

【0049】

次に、この基板50の上に、リフトオフ用のフォトレジスト膜52が形成される。その後、ゲート電極となるNi/Au積層膜54が蒸着される(図5(b)参照)。最後に、リフトオフ用フォトレジスト膜52が除去されて、ゲート電極22が完成する。このNi/Au積層膜54は、UID−GaNキャップ層にショットキー障壁を形成する。

【0050】

次に、基板50の全面に、保護膜となる厚さ500nmのSiN膜56が堆積される(図5(c)参照)。

【0051】

その後、保護膜32の形成予定領域にフォトレジスト膜52´が形成される(図5(d)参照)。このフォトレジスト膜52´をエッチングマスクとして、SiN膜56がドライエッチングによって除去されて、保護膜32が形成される(図6(a)参照)。

【0052】

次に、ゲート電極とソース電極の交差予定位置で、保護膜32の上にエアブリッジ形成用フォトレジスト膜(マスク)58が形成される(図6(b)参照)。

【0053】

次に、スパッタ法により、基板50の上に、Ti層40(厚さ数10nm)、TaN層42(厚さ200nm)、及び第1のAu層44(厚さ数50nm)を順次堆積する(図6(c)参照)。ここで、Ti層40及び第1のAu層44は、Ti及びAuをターゲットとしてスパッタ法によって堆積する。スパッタガスはArである。また、TaNは、Taをターゲットとして反応性スパッタ法により堆積される。ここで、反応ガスはN2である。

【0054】

次に、第1のAu層44をシード膜とし、ソース電極及びドレイン電極の形成予定領域が開口したフォトレジスト膜(図示せず)をメッキマスクとして、Au層が電解メッキによって、第2及び第3のAu層46,48が厚く形成される。第2及び第3のAu層46,48の厚さは、合計で1〜2μmである。

【0055】

その後、メッキマスクが除去され、各電極間に露出したスパッタ膜がミリングで除去される。

【0056】

最後に、エアブリッジ形成用フォトレジスト膜58が酸素を反応ガスとするマイクロ波アッシャーにより除去され、マルチゲートトランジスタ2が完成する(図6(d)参照)。

【0057】

以上のようにしてマルチゲートトランジスタを試作した結果、Ti/TaN/Auスパッタ膜68を堆積する過程で、エアブリッジ形成用フォトレジスト膜58が融解して、Ti/TaN/Auスパッタ膜68とゲート電極22を隔てる空間38が形成されないことが判明した。

【0058】

そこで、本発明者は、TaN層の堆積中に基板温度が何度まで上昇するか測定した。その結果、基板温度は、フォトレジストが融解する150℃を超えて上昇することが明らかになった。

【0059】

このような温度の上昇は、TaターゲットからスパッタされたTaと窒素ガスの生成熱に起因するものである。

【0060】

すなわち、Ti/TaN/Au積層膜を用いることによってエレクトロマイグレーション耐性の高いエアブリッジ配線の形成が可能になると期待されたが、実際にはTaN堆積時の基板温度上昇によってエアブリッジ配線自体の形成が困難になることが本発明者らによって見い出された。

【0061】

(実施の形態1)

TaN層の堆積に伴う基板温度の上昇は、成膜するTaN層を薄くすれば抑制できる。これは、基板50がTaNの生成熱に曝される時間が短くなるからである。しかしながら、Au層(第1〜第3のAu層44,46,48)を強固に支持するためには、ある程度の膜厚(例えば、100nm〜200nm)を持った金属層が必要である。従って、単にTaN層を薄くすることは、エアブリッジ配線の強度を劣化させる。

【0062】

そこで、本発明者は種々検討した結果、Ta層の上にTaN層を積層したTa/TaN積層膜を形成した場合、基板温度の上昇が、同じ膜厚のTaN膜を形成した場合より低くなることを見出した。

【0063】

これは、Ta/TaN積層膜では、最初に成膜するTa層の分だけTaN層が薄くなるからである。この場合、TaNの生成熱に基板が曝される時間が短くなるため、基板温度の上昇が抑制される。更に、本発明者は、後述するように、Ta/TaN積層膜のエレクトロマイグレーション耐性が、TaN膜より高いことも見出した。

【0064】

そこで、本発明者は、Ti/Ta/TaN/Au積層膜で形成されたエアブリッジ配線によって、マルチゲートトランジスタを製造することとした。

【0065】

(1)構 成

図7は、本実施の形態によるマルチゲートトランジスタを示す斜視図である。図8は、図7のA−A線に於ける断面を矢印の方向から見た図である。

【0066】

図9は、図7のB−B線に於ける断面を矢印の方向から見た図である。

【0067】

本実施の形態に従うマルチゲートトランジスタ2では、4つのGaN−HEMT4が一列に整列している。そして、隣接するGaN−HEMT4は、一つの半導体領域をソース6又はドレイン8として共有している(図8参照)。各半導体領域の上には、一つの電極10,10´が形成されている。

【0068】

更に、ソース6の上に形成された2つの電極10は、2つのエアブリッジ配線12によって1つの共通電極14に接続されて、櫛の歯状のソース電極16が形成される。

【0069】

一方、ドレイン8の上に形成された3つの電極10´は1つの共通電極14´に接続されて、櫛の歯状のドレイン電極18が形成される。

【0070】

また、チャネルの上に形成されゲート20となる4つの電極10´´も1つの共通電極14´´に接続されて、櫛の歯状のゲート電極22が形成される。

【0071】

このように3つの櫛の歯状の電極を一箇所に形成した場合、2つの電極、例えばゲート電極22とソース電極16の交差は避けられない(図7参照)。

【0072】

そこで、このような交差部位には、電極間の接触を回避するために、空間を介して両者が立体交差するエアブリッジ配線構造が形成されている。

【0073】

なお、ソース電極16、ドレイン電極18、及びゲート電極22は、夫々の共通電極14,14´,14´´を外部回路との接続用パッドとして使用することができるので、所謂「電極」としての機能を有している。一方、ソース電極16、ドレイン電極18、及びゲート電極22は、GaN−HEMTの各端子(ソース、ドレイン、ゲート)へ入出力される電気信号の経路を確保するものなので、「配線」としての機能も有している。すなわち、ソース電極16、ドレイン電極18、及びゲート電極22は、その名称に拘わらず、配線でもある。

【0074】

ここで、GaN―HEMTの構成を、もう少し詳しく説明する。

【0075】

図8に示すように、本実施の形態に従うGaN―HEMT2では、SiC基板24の上に、まず不純物の添加されていないUnitentionally Doped(UID)−GaNチャネル層26が積層されている。更に、本実施の形態では、このUID−GaNチャネル層26の上に、n型AlGaNキャリア供給層28とUID−GaNキャップ層30が順次積層されている。

【0076】

そして、ソース6及びドレイン8の一部を形成するn型AlGaNキャリア供給層28の上には、Tiの上にアルミニウム(Al)が積層されたTi/Alオーミック電極34が形成されている。更に、オーミック電極34の上には、ソース電極16を形成する電極10及びドレイン電極18を形成する電極10´の何れか一方が形成されている。また、チャネル20となるUID−GaNチャネル層26の上に積層された、UID−GaNキャップ層30の上には、ゲート電極22を形成する電極10´´が形成されている。

【0077】

また、ゲート電極22(電極10´´)は、例えば窒化珪素(SiN)製の保護膜32によって覆われている。この保護膜32はゲート電極22を不純物の汚染から保護して、出力信号(ドレイン電流波形)の劣化を防止するためのものである。

【0078】

図9は、図7のB−B線に於ける断面を矢印の方向から見た図である。すなわち、図9は、ゲート電極22とソース電極16が立体交差するエアブリッジ配線構造の断面図である。

【0079】

ゲート電極22を形成する共通電極14´´は、n型AlGaNキャリア供給層28がイオン注入によって高抵抗化されたAlGaN不活性領域の上に形成されている。そして、保護膜32によって覆われた共通電極14´´(すなわちゲート電極22)上を、空間を介して、エアブリッジ配線12(すなわちソース電極16)が横切っている。

【0080】

ここで、エアブリッジ配線12は、Ti層40、Ta層70、TaN層72、第1のAu層44、第2のAu層46、及び第3のAu層48が積層されて形成されている。TaNの窒素含有率は50%である。また、Ta層及びTaN層の厚さは、夫々100nmである。

【0081】

尚、ソース電極16及びドレイン電極18を形成する共通電極14,14´も、AlGaN不活性領域の上に形成されている。

【0082】

(2)製造手順

図10乃至図12は、

本実施の形態のエアブリッジを形成する工程を説明する工程断面図である。

【0083】

次に、試作したマルチゲートトランジスタに於けるエアブリッジ配線構造の製造手順を説明する。

【0084】

図10、図11、及び図12は、エアブリッジ配線構造の製造工程を説明する断面図である。

【0085】

まず、SiC基板24の上に、UID−GaNチャネル層26、n型AlGaNキャリア供給層28、UID−GaNキャップ層(図示せず)が順次積層され、更にオーミック電極34が形成された基板50が準備される(図10(a)参照)。

【0086】

ここで、オーミック電極34は、ソース及びドレインとなる半導体領域の上に設けられる。また、UID−GaNキャップ層は、チャネルとなる半導体領域以外では除去されている(従って、図10(a)には図示されていない。)。そして、共通電極14´´の形成予定領域に露出したn型AlGaNキャリア供給層28は、イオン注入によって高抵抗化され、AlGaN不活性領域36となっている。

【0087】

次に、この基板50の上に、リフトオフ用のフォトレジスト膜52が形成される。その後、ゲート電極となるNi/Au積層膜54が蒸着される(図10(b)参照)。最後に、リフトオフ用フォトレジスト膜52が除去されて、ゲート電極22が完成する。このNi/Au積層膜54は、UID−GaNキャップ層にショットキー障壁を形成する。

【0088】

次に、基板50の全面に、保護膜となる厚さ500nmのSiN膜56が堆積される(図10(c)参照)。ここで、保護膜32の厚さとしては、5nm乃至500nmが好ましい。

【0089】

その後、保護膜32の形成予定領域にフォトレジスト膜52´が形成される(図10(d)参照)。このフォトレジスト膜52´をエッチングマスクとして、SiN膜56がドライエッチングによって除去されて、保護膜32が形成される(図11(a)参照)。

【0090】

次に、ゲート電極とソース電極の交差予定位置で、保護膜32の上にエアブリッジ形成用フォトレジスト膜(マスク)58が形成される(図11(b)参照)。

【0091】

次に、基板50の上に、Ti層40、Ta層70、TaN層72(窒素含有率50%)、及び第1のAu層44が順次堆積される(図12(a)参照)。ここで、Ti層40、Ta層70、TaN層72、及び第1のAu層44の厚さは、夫々、数10nm、100nm、100nm、及び50nmである。

【0092】

尚、Ti層は、Ta/TaN積層膜の密着性をよくするためのものであり、他の金属層、例えばCr層と代替可能である。

【0093】

Ti層40、Ta層70、及び第1のAu層44は、夫々Ti、Ta、及びAuをターゲットとしてスパッタ法によって堆積される。スパッタガスはArである。一方、TaN72は、Taをターゲットとして反応性スパッタ法により堆積される。反応ガスはN2である。この時、堆積されるTaN層が100nmと薄いので、基板50の温度は150℃以上には上昇しない。従って、エアブリッジ形成用フォトレジスト膜58が融解することはない。

【0094】

尚、Ti層40を形成する前に、エアブリッジ形成用フォトレジスト膜58にUVキャアを施し、その断面を丸めてもよい。

【0095】

エアブリッジ形成用フォトレジスト膜58の断面が矩形に近いほど、Ti/Ta/TaN/Auスパッタ膜76のカバレッジ(レジストの頂上に堆積した金属膜の厚さに対する、レジストの側面に堆積した金属膜の厚さの比)が小さくなる。このようなレジスト膜は、エアブリッジの形成を困難にする。しかし、エアブリッジ形成用フォトレジスト膜58の断面を丸めておけば、エアブリッジの形成が阻害されることはない。

【0096】

次に、第1のAu層44をシード膜とし、ソース電極及びドレイン電極の形成予定領域が開口したフォトレジスト膜(図示せず)をメッキマスクとして、Au層が電解メッキによって、第2及び第3のAu層46,48が形成される。第2及び第3のAu層46,48の厚さは、合計で1〜2μmである。

【0097】

その後、メッキマスクが除去され、各電極間に露出したスパッタ膜がミリングで除去される(図12(b))。

【0098】

最後に、エアブリッジ形成用フォトレジスト膜58が酸素を反応ガスとするマイクロ波アッシャーにより除去され、マルチゲートトランジスタ2が完成する(図12(c)参照)。

【0099】

ここで、Ta/TaN積層は200nmと十分に厚いので、エアブリッジ形成用フォトレジスト膜58を除去しても、エアブリッジ配線が崩れることはない。

【0100】

以上の手順によって、図7、図8、及び図9を参照して説明した本実施の形態に従うマルチゲートトランジスタ2が完成する。

【0101】

ここで、本実施の形態に従うマルチゲートトランジスタ2の製造方法の要部は、以下のように纏められることができる。

【0102】

本製造方法は、半導体素子(GaN−HEMT4)が形成された基板50上に、上記半導体素子に接続され他の配線と交差する第1の配線(ゲート電極22)の上部を、交差予定位置で覆って線状に延在するエアブリッジ形成用フォトレジスト膜58を形成する。

【0103】

また、本製造方法は、上記半導体基板50上に、チタン層40、タンタル層70、タンタルナイトライド層72、第1の金層44を順次積層して、上記フォトレジスト膜58の上を乗り越えて上記フォトレジスト膜58の一方の脇から他方の脇に延在し且つ上記半導体素子に電気的に接続される第2の配線(ソース電極16)を上記他の配線として形成する。

【0104】

更に、本製造方法は、上記第2の配線の形成後に上記フォトレジスト膜58を除去する。

【0105】

ここで、上記タンタルナイトライド層72の成膜は、上記フォトレジスト膜58が融解する前に終了する。

【0106】

(3)エレクトロマイグレーション耐性

次に、本実施の形態に従うエアブリッジ配線のエレクトロマイグレーション耐性を評価した結果を説明する。

【0107】

上述の熱劣化加速試験と同様の方法によってエレクトロマイグレーション耐性を評価した。

【0108】

評価に用いた評価試料は、Ti/Al積層膜の上に、Ti層(厚さ数10nm)、Ta層(厚さ100nm)、TaN層(厚さ100nm、窒素含有率50%)、及びAu層(厚さ50nm〜300nm)を順次積層したものである。Ti層、Ta層、TaN層、及びAu層の成膜方法は、上述の成膜方法と同じである。一方、加熱温度は、450℃である。

【0109】

図13は、本実施の形態に従う熱劣化加速試験の結果を説明する図である。比較のため、図13には、Ti/TaN/Au及びTi/Pt/Auの結果(図3参照)と、本実施の形態に従う熱劣化加速試験の結果の双方が記載されている。

【0110】

「Ta/TaN」と表示された破線は、Ti/Al積層膜とAu層の間にTi/Ta/TaN積層膜が形成された上記評価試料の反応時間(6分)を表している(Ta層及びTaN層の厚さは、夫々100nm)。

【0111】

一方、「TaN」と表示された曲線は、Ti/Al積層膜とAu層の間に、Ti/TaxN1-x積層膜(0≦X<1)が形成された試料の反応時間を表している(但し、TaxN1-x層の厚さは200nm)。

【0112】

また、「TaN(t=200nm)」と表示された破線は、Ti/Al積層膜とAu層の間に、Ti層(厚さ数10nm)の上に厚さが200nmで窒素含有率が50%のTaN層が積層されたTi/TaN積層膜によって形成された試料の反応時間(4分)を表している。

【0113】

一方、「Pt」と表示された破線は、Al層とAu層の間にTi/Pt積層膜が形成された試料の反応時間(2分)を表している(Pt層の厚さは、200nm)。

【0114】

ここで、Ti層は、Ti/Ta/TaN積層膜、Ti/TaN積層膜、及びTi/Pt積層膜の何れにも形成されているので、反応時間の違いを生じさせるものではない。従って、各積層膜のエレクトロマイグレーション耐性の違いに寄与する金属層は、Ta/TaN積層膜、TaN層、及びTi/Pt層である。

【0115】

図13から明らかなように、Ti/Ta/TaN積層膜が形成された試料の反応時間は、Ti/Pt積層膜が形成された試料の3倍に達し、しかもTi/TaN(厚さ200nm)が形成された試料の1.5倍である。

【0116】

この事実は、Ta/TaN積層膜のエレクトロマイグレーション耐性が、TaN層(厚さ200nm)を超え、従来のPt層より格段に高いことを示している。

【0117】

尚、図13には、Ti層に厚さ100nmのTaN層を積層したTi/TaN積層膜に対して熱劣化加速試験を実施した結果も、「TaN(t=100nm)」と付した破線で示されている。図13に示されているように、100nmのTaNの形成された試料の反応時間は1分であり、Pt層(厚さ200nm)の形成された試料の半分でしかない。

【0118】

上述したように、Ta/TaN積層膜のエレクトロマイグレーション耐性は、同じ膜厚のTaN層のエレクトロマイグレーション耐性を超えている。その理由は、TaN層をTa層の上に成長するとTaN層の層構造(組織)が変化し、TaN層が緻密化するためと推定される。例えば、Ta層の上にTaN層を成長すると大小の結晶粒が混在して成長し、大きなTaNの結晶粒の間を小さな結晶粒が埋めて、TaN層が緻密化されると考えられる。

【0119】

(4)動 作

最後に、本実施の形態に従うマルチゲートトランジスタ2の動作について以下説明する。

【0120】

動作の前提として、各電極は次のように接続される。まず、マルチゲートトランジスタ2のソース電極16は、接地面に電気的に接続される。一方、ドレイン電極18は、負荷抵抗を介して電源に電気的に接続される。この状態で、ゲート電極22に信号が入力される。

【0121】

ゲート電極22に入力された信号電圧は、各GaN−HEMT4のゲート20に供給され、相互コンダクタンスに従って、各GaN−HEMT4のドレイン電流を変化させる。ドレイン電流は、(ドレイン電極18を形成する)共通電極14´によって合流された後、負荷に供給される(本実施の形態のGaN―HEMTは、nチャネル電界効果トランジスタである。従って、電流は負荷からドレインに向かって流れる。従って、正確には、「ドレイン電流」ではなく、ドレインから流出した電子流が合流され負荷に供給される。)。

【0122】

ここで、ドレイン電流は共通電極14´によって束ねられるので、負荷に流れる電流は、マルチゲートトランジスタ2を形成するGaN−HEMT4の個数分だけ大きくなる。

【0123】

この時、各GaN−HEMT4のソース電流は、エアブリッジ配線12を経由して共通電極14で束ねられた後、接地面に放出される。従って、エアブリッジ配線12に流れる電流も、ゲートに印加される信号電圧に従って変化する。そして、エアブリッジ配線12に流れる電流の平均値は1×105A/cm2を超える。

【0124】

しかし、本実施の形態に従うマルチゲートトランジスタ2では、エアブリッジ配線12は、エレクトロマイグレーション耐性の高いTa/TaN積層膜74によって支持されている。このため、エアブリッジ配線12が断線する虞はない。

【0125】

ところで、各GaN−HEMTのソース6にも大電流が流れる。この際、ソース電極16の電極10´を形成するAu層がエレクトロマイグレーションして、ソース6に設けられたTi/Alオーミック電極34と反応する虞がある。しかし、上記製造手順から明らかなように、電極10´を形成するAu層(第1〜第3のAu層44,46,48)は、エレクトロマイグレーション耐性の高いTa/TaN積層膜74によって、Ti/Alオーミック電極34と分離されている。従って、両者が反応する虞はない。

【0126】

また、Ta/TaN積層膜42の抵抗値は、同じ厚さのTaN層の抵抗値の約6割しかない。

【0127】

ところで、ゲート電極22に入力された信号電圧は、ゲート電極22(第1の配線)を伝播する。このゲート電極22は、エアブリッジ配線12と交差している。しかし、両者は空間38によって分離されているので、寄生容量による両者の間のクロストークは小さい。この点は、後述する他の実施の形態にも共通する。

【0128】

このように寄生容量が小さいので、本実施の形態に従うマルチゲートトランジスタは、例えば、数GHzで動作する。

【0129】

(実施の形態2)

本実施の形態は、実施の形態1の半導体装置において、エアブリッジ配線12を形成するTa/TaN層をTa/Ti/TaN(窒素含有率50%)積層膜で代替した半導体装置およびその製造方法に関する。

【0130】

(1)構 成

本実施の形態に従う半導体装置の構成は、(エアブリッジ配線12を含む)ソース電極16及びドレイン電極18の構造を除き、実施の形態1の半導体装置と同じである。

【0131】

ソース電極16およびドレイン電極18は、実施の形態1と同様に、同時に形成される。従って、ソース電極16とドレイン電極18は同一の積層構造を有している。そこで、ソース電極16の一部を形成するエアブリッジ配線12に着目して、本実施の形態に従う半導体装置(マルチゲートトランジスタ)の構成を以下に説明する。

【0132】

図14は、本実施の形態に従うマルチゲートトランジスタを形成するエアブリッジ配線12の断面を説明する図である。

【0133】

本実施の形態のエアブリッジ配線では、実施の形態1に於いてエアブリッジ配線12を形成しているTa/TaN層74が、Ta/Ti/TaN積層膜80によって代替されている(図9及び図14参照)。ここで、Ta/Ti/TaN積層膜80は、Ta層70、Ti層78と、TaN層72が順次積層されて形成されている。

【0134】

また、Ta層70、Ti層78、及びTaN層72の厚さは、夫々、100nm、10nm、及び100nmである。その他の金属層の厚さは、実施の形態1に従うマルチゲートトランジスタの対応する金属層と同じである。尚、TaN層の窒素含有率は、50%としている。

【0135】

すなわち、本実施の形態に従うマルチゲートトランジスタでは、実施の形態1に従うマルチゲートトランジスタにおいて、エアブリッジ配線を形成するTa(タンタル)層70とTaN(タンタルナイトライド)層72の間に、他のTi(チタン)層78が介在している。

【0136】

(2)製造手順

本実施の形態に従うマルチゲートトランジスタの製造手順は、実施の形態1に於けるマルチゲートトランジスタの製造手順と略同じである。以下異なる製造手順について説明する。

【0137】

本実施の形態では、Ti/Ta/TaN/Auスパッタ膜ではなくTi/Ta/Ti/TaN/Auスパッタ膜82が形成される点を除き、実施の形態1と同じである。ここで、Ta層とTaN層の間に介在するTi層78は、Tiをターゲットするスパッタ法によって形成される。スパッタガスはArである。

【0138】

すなわち、本実施の形態に従う半導体装置の製造方法では、実施の形態1で説明した製造方法おいて、Ta(タンタル)層の上に他のTi(チタン)層を積層してから、TaN(タンタルナイトライド)層が積層される。

【0139】

(3)エレクトロマイグレーション耐性

次に、Ta/Ti/TaN積層膜80のエレクトロマイグレーション耐性が熱劣化加速試験によって評価された結果が説明される。評価に用いた試料は、Ti/Al積層膜の上に、上記Ti/Ta/Ti/TaN/Auスパッタ膜80が積層されたものである。但し、Au層の厚さは50〜300nmである。

【0140】

図15は、本実施の形態に従うTa/Ti/TaN積層膜80に対して実施された熱劣化加速試験の結果を説明する図である。比較のため、図15には、図3及び図13で説明した熱劣化加速試験の結果も記載する。

【0141】

「Ta/Ti/TaN」と表示された破線は、本実施の形態に従うTa/Ti/TaN積層膜80が形成された試料の反応時間(8分)を表している。図15から明らかなように、Ta/Ti/TaN積層膜80が形成された試料の反応時間は、Pt層が形成された試料の4倍、実施の形態1に従うTa/TaN積層膜74が形成された試料の1.3倍である。

【0142】

この事実は、Ta/Ti/TaN積層膜80のエレクトロマイグレーション耐性は、実施の形態1に従うTa/TaN積層膜74を超え、従来のPt層より格段に高いことを示している。

【0143】

このように、Ta/Ti/TaN積層膜80のエレクトロマイグレーション耐性が、実施の形態1に従うTa/TaN積層膜より更に高くなった理由は、Ta層とTaN層の間にTi層を介在させることによって、TaN層の緻密化が促進されたためと考えられる。

【0144】

尚、本実施の形態に従うマルチゲートトランジスタの動作は、エアブリッジ配線のエレクトロマイグレーション耐性がより高くなっている点を除けば、実施の形態1に従うマルチゲートトランジスタと同じである。

【0145】

(実施の形態3)

本実施の形態は、実施の形態1の半導体装置において、ソース電極を覆う保護膜がエアブリッジ配線の下側で除去された半導体装置およびその製造方法に関する。

【0146】

(1)構 成

図16は、本実施の形態に従うマルチゲートトランジスタ84の斜視図である。図17は、図16のB−B線に於ける断面を矢印の方向から見た図である。

【0147】

図16に示すように、本実施の形態に従うマルチゲートトランジスタ84は、ゲート電極22を形成する共通電極14´´が保護膜32で覆われていない点で、実施の形態1に従うマルチゲートトランジスタ2と相違する。尚、共通電極14´´は、ゲート電極22のうち、エアブリッジ配線12の下側に配置された部分である。

【0148】

共通電極14´´以外の構成は、実施の形態1のマルチゲートトランジスタ2と同じである。従って、共通電極14´´に関する構成以外の説明は省略される。

【0149】

実施の形態1に従うマルチゲートトランジスタ2では、図9に示すように、エアブリッジ配線12の下側でも、共通電極14´´は保護膜32によって覆われている。従って、エアブリッジ配線12と共通電極14´´の間に、SiN等の誘電体膜が存在する領域が発生することになる。この誘電体膜の存在によって、エアブリッジ配線12を含むソース電極16と、共通電極14´´を含むゲート電極22間の寄生容量が大きくなる。

【0150】

そこで、本実施の形態に従うマルチゲートトランジスタ84では、図16に示すように、エアブリッジ配線12の下側でソース電極16を覆う保護膜32が除去されて、寄生容量の最小化が図られている。すなわち、図17のように、第1の配線(共通電極14´´を含むゲート電極22)が第2の配線(エアブリッジ配線12を含むソース電極16)によって横切られる領域で、保護膜(SiN膜)が取り除かれている。

【0151】

このため、本実施の形態に従うマルチゲートトランジスタ84は、ゲート電極22とソース電極16間の信号干渉が小さくなる。故に、本実施の形態に従うマルチゲートトランジスタ84は、実施の形態1のマルチゲートトランジスタ2より高速で動作することができる。

【0152】

保護膜32は、ゲート電極22を不純物の汚染から保護して、出力信号(ドレイン電流波形)の劣化を防止するためのものである。

【0153】

しかし、出力信号の劣化を防止するためには、ゲート20を形成するNi/Au電極10´´が保護膜32で覆われていれば十分である。従って、本実施の形態のように共通電極14´´を覆う保護膜32が除去されても、出力信号が劣化することはない。

【0154】

尚、実施の形態1に従うマルチゲートトランジスタ84では、保護膜32はNi/Au共通電極14´´を覆い、共通電極14´´を形成するNi層の酸化防止に役立っている。

【0155】

尚、エアブリッジ配線12を形成するTa/TaN層を、実施の形態2で説明したように、Ta/Ti/TaN積層膜で代替しても良い。

【0156】

(2)製造手順

図18は、本実施の形態の保護膜32乃至エアブリッジ配線12を形成する製造手順を説明する工程断面図である。ここで、図18は、製造手順の進行に合わせて、図16のB−B線に於ける断面を矢印の方向から見た図である。

【0157】

以下に説明する通り、本実施の形態の製造手順は、保護膜の形成及びエアブリッジ用フォトレジスト膜(マスク)の形成を除き、実施の形態1の製造手順と同じである。

【0158】

まず、マルチゲートトランジスタ2を形成する複数のGaN−HEMT4(オーミック電極を含む)が形成された基板50を準備する。

【0159】

次に、Ni/Auゲート電極22を形成する。

【0160】

これらのステップは、対応する実施の形態1と同じである。従って、詳しい説明は省略する。

【0161】

まず、ゲート電極22の形成されたSiC基板24の全面に、保護膜32となる厚さ500nmのSiN膜を堆積する。ここで、SiN膜の厚さとしては、5nm乃至500nmが好ましい。

【0162】

その後、保護膜の形成予定領域にフォトレジスト膜を形成する。ここで、本実施の形態では、実施の形態1とは異なり、共通電極14´´はフォトレジスト膜によって覆われない。

【0163】

このフォトレジスト膜をエッチングマスクとして、SiN膜がドライエッチングによって除去されて、保護膜32が形成される(図16参照)。

【0164】

従って、ゲート電極22(第1の配線)がソース電極16(第2の配線)によって横切られる領域(交差予定位置)、すなわちエアブリッジ配線12の形成予定領域の下側では、保護膜(SiN膜)が取り除かれる(図18(a)参照)。

【0165】

次に、基板24の上に、共通電極14´´の上部及び側面を覆って線状に延在するエアブリッジ形成用フォトレジスト膜58を形成する(図18(b)参照)。

【0166】

次に、図18(c)に示すように、エアブリッジ形成用フォトレジスト膜58が形成された基板24の上に、Ti/Ta/TaN(窒素含有率50%)/Auスパッタ膜76を形成する。

【0167】

次に、Ti/Ta/TaN/Auスパッタ膜76の上に、メッキ法によって第2及び第3のAu層46,48を形成する。

【0168】

次いで、図18(d)に示すように、エアブリッジ形成用フォトレジスト膜58を除去し、マルチゲートトランジスタ84が完成する。

【0169】

(3)動作

本実施の形態に従うマルチゲートトランジスタ84の動作は、実施の形態1のマルチゲートトランジスタ2と略同じである。但し、本実施の形態に従うマルチゲートトランジスタ84は、ソース電極16とゲート電極22間の寄生容量が小さいので、実施の形態1に従うマルチゲートトランジスタより高周波で動作する。

【0170】

(実施の形態4)

本実施の形態は、実施の形態1〜3に従うマルチゲートトランジスタを具備する高周波増幅器に関する。

【0171】

図19(は、本実施の形態に従う高周波増幅器の回路図である。

【0172】

本実施の形態に従う高周波増幅器86は、実施の形態1〜3の何れかに従うマルチゲートトランジスタ2´を有している。

【0173】

また、本実施の形態に従う高周波増幅器86は、電気信号が入力される第1の端子(入力端子88)と、増幅された電気信号が出力される第2の端子(出力端子90)を有している。

【0174】

また、本実施の形態に従う高周波増幅器86は、第1の端子(入力端子88)から前記第1の配線(ゲート電極22)に至る、電気信号が伝播する第1の経路92を具備している。

【0175】

更に、本実施の形態に従う高周波増幅器86は、ドレイン8に電気的に接続された第3の配線(ドレイン電極18)から第2の端子(出力端子90)に至る、電気信号が伝播する第2の経路94を具備する。

【0176】

ここで、第1及び第2の経路92には、第1及び第2のコンデンサ97,99が配置されている。従って、第1及び第2の経路92,94には、高周波信号のみが伝播する。

【0177】

また、本実施の形態に従う高周波増幅器86は、電源電圧に接続される第3の端子(電源端子96)を有している。そして、電源端子96は、第1の抵抗98を介して、第2の配線(ドレイン電極18)に接続されている。

【0178】

また、電源端子96は、第2の抵抗100を介して、第1のコンデンサ97と第1の配線(ゲート電極22)の間に設けられた接続点に接続されている。更に、この接続点は、第3の抵抗102を介して接地面に接続されている。ここで、第2及び第3の抵抗100,102は、マルチゲートトランジスタ2´のバイアス点を設定する。

【0179】

一方、ソース電極16は、第4の抵抗104と第3のコンデンサ106が並列に接続された回路を介して、接地面に接続されている。

【0180】

ここで、マルチゲートトランジスタ2´は所定のパッケージに搭載され、第1〜第4の抵抗及び第1〜第3のコンデンサと共に、プリント基板上に配置される。

【0181】

以上のように形成された高周波増幅86は、以下のように動作する。電気信号が第1の端子88に入力されると、第1の経路92を伝播し、マルチゲートトランジスタ2´のゲート電極に到達する。マルチゲートトランジスタ2´は、上記各実施の形態で説明したように動作して、入力した電気信号を増幅する。増幅された電気信号は、第2の経路94を伝播して、第2の端子90から出力される。

【0182】

本実施の形態に従う高周波増幅器86は、実施の形態1〜3に従うマルチゲートトランジスタ2´を備えているので、大電流動作で動作させてもエアブリッジ配線が断線することはない。

【0183】

尚、図19を参照して説明した回路は、実施の形態1〜3に従うマルチゲートトランジスタを利用した高周波増幅器の一例に過ぎない。

【0184】

(実施の形態5)

本実施の形態は、実施の形態4に従う高周波増幅器を備えた送信機に関する。

【0185】

図20(は、本実施の形態に従う送信機108のブロック図である。

【0186】

本実施の形態に従う無線送信機108は、図20に示すように、電気信号が入力される入力端子116と、アンテナ112が接続される出力端子114と、実施の形態5に従う高周波増幅器86を備えている。更に、本実施の形態に従う無線送信機108は、入力信号に従って変調された高周波信号を生成し出力する高周波信号発生ユニット110(例えば、電圧制御発信器(voltage controlled oscillator; VCO))を具備している。

【0187】

そして、本実施の形態に従う無線送信機108は、入力端子116が、高周波信号発生ユニット110の入力端子に接続されている。また、高周波信号発生ユニット110の出力端子が、高周波増幅器86の第1の端子(入力端子88)に接続され、出力端子114が、高周波増幅器86の第2の端子(出力端子90)に接続されている。

【0188】

この送信機108は、以下のように動作する。入力端子116から入力された電気信号は、高周波信号発生ユニット110に供給される。高周波発生ユニット110は、入力された電気信号によって変調された高周波信号を発生し、高周波増幅器86に供給する。高周波増幅器86は供給された高周波信号を増幅して、出力端子114に接続されたアンテナ112に供給する。

【0189】

ここで、送信機108は、実施の形態5に従う高周波増幅器86を備えているので、大電力信号をアンテナに供給することができる。

【0190】

本実施の形態に従う送信機は、例えば携帯電話システムの基地局に使用される。

【0191】

(変形例)

上記各実施の形態では、TaN層の窒素含有率は50%を例に説明した。しかし、TaN層の窒素含有率は、この値に限られない。TaN層の窒素含有率は、好ましくは、48%より大きく52%以下であればよく、更に好ましくは49%以上51%以下であればよい。

【0192】

図15から明らかなように、窒素含有率が48%より大きければ、Ta/TaxN1-x積層膜(又は、Ta/Ti/TaxN1-x積層膜)のエレクトロマイグレーション耐性が従来のPt層より高くなる。従って、TaNの窒素含有率は、48%より大きいことが好ましい。一方、窒素含有率が高くなるに従いTaNの成膜が困難になり、窒素含有率52%以上のTaN膜の成膜は極めて困難になる。従って、TaNの窒素含有率は、52%以下が好ましい。

【0193】

上記各実施の形態では、保護膜は窒化珪素で形成されている。しかし、保護膜として使用可能な絶縁膜は窒化珪素(SiN)膜に限られない。例えば、保護膜は二酸化珪素(SiO2)膜によって形成されてもよい。

【0194】

上記各実施の形態では、エアブリッジ配線はソース電極に設けられている。しかし、ドレイン電極がゲート電極と交差する場合には、エアブリッジ配線はドレイン電極に設けることが好ましい。すなわち、上記第2の配線は、電界効果トランジスタのソースでなく、ドレインに接続されていてもよい。また、本実施の形態のエアブリッジ配線は、ソース電極及びドレイン電極以外の配線に形成されてもよい。

【0195】

上記各実施の形態では、GaN−HEMTによってマルチゲートトランジスタが形成されている。しかし、他の電界効果トランジスタ(例えば、半絶縁性InPを基板とし、InGaAs製のチャネル層と、SiがドーピングされたInAlAs製のバリア層を具備するInP−HEMT)によって、マルチゲートトランジスタが形成されてもよい。

【0196】

更に、上記各実施の形態で説明されたエアブリッジ配線は、マルチゲートトランジスタ以外の半導体装置、例えば、複数のゲートを備えた電界効果トランジスタ(特許文献1)にも適用できる。

【0197】

また、上記各実施の形態に従う半導体装置を形成する半導体素子は、電界効果トランジスタである。しかし、上記半導体素子は、電界効果トランジスタ以外の他の半導体素子、例えばバイポーラトランジスタであってもよい。上記半導体素子としてバイポーラトランジスタが使用される場合には、例えば、第1の配線はベースに接続され、第2の配線はエミッタ又はコレクタに接続される。

【0198】

更に、上記各実施の形態では、ゲート電極はNi/Au積層膜によって形成されたが、他の積層膜によって形成されてもよい。また、上記各実施の形態では、絶縁膜がドライエッチングによってエッチングされて保護膜に加工されるが、ウエットエッチングやイオンミリング等他のエッチング法でエッチングされてもよい。

【0199】

以上の実施の形態をまとめると、次の付記のとおりである。

【0200】

(付記1)

第1の配線と、

前記第1の配線と交差する方向に延在し、前記第1の配線と空間を介して配置され、タンタル層、該タンタル層上に形成されたタンタルナイトライド層、該タンタルナイトライド層上に形成された金属層を含む第2の配線と、

を有することを特徴とする半導体装置。

【0201】

(付記2)

付記1に記載の半導体装置において、

前記タンタルナイトライド層の窒素含有率は、48%より大きく52%以下であることを、

特徴とする半導体装置。

【0202】

(付記3)

付記1又は付記2に記載の半導体装置において、

前記タンタル層とタンタルナイトライド層の間に、チタン層が形成されていることを、

特徴とする半導体装置。

【0203】

(付記4)

付記1〜付記3の何れか1項に記載の半導体装置において、

更に半導体素子を有し、前記第1の配線及び前記第2の配線は、半導体素子に接続され、

前記半導体素子へ入力される信号は、前記第1の配線を伝播することを、

特徴とする半導体装置。

【0204】

(付記5)

付記4に記載の半導体装置において、

更に、前記第1の配線を覆う保護膜を有することを

特徴とする半導体装置。

【0205】

(付記6)

付記5に記載の半導体装置において、

前記第1の配線が前記第2の配線と交差する領域では、前記保護膜が取り除かれていることを、

特徴とする半導体装置。

【0206】

(付記7)

付記5又は6に記載の半導体装置において、

前記保護膜が、窒化珪素膜又は二酸化珪素膜であることを、

特徴とする半導体装置。

【0207】

(付記8)

付記4乃至7の何れか1項に記載の半導体装置において、

前記半導体素子が、複数の電界効果トランジスタであって、

前記複数の電界効果トランジスタ夫々のソース、ゲート、及びドレインの夫々は、同じ方向に延在し、、

前記複数の電界効果トランジスタの各々は、隣接する前記複数の電界効果トランジスタと、前記ソース及び前記ドレインの少なくても一方を共有し、

前記第1の配線が、前記ゲートに電気的に接続され、

前記第2の配線が、前記ソース及び前記ドレインの何れか一方に電気的に接続されていることを、

特徴とする半導体装置。

【0208】

(付記9)

付記8に記載の半導体装置において、

前記電界効果トランジスタが、

窒化ガリウムをチャネル層とすることを特徴とする半導体装置。

【0209】

(付記10)

第1の配線と、

前記第1の配線と交差する方向に延在し、前記第1の配線と空間を介して配置され、タンタル層、該タンタル層上に形成されたタンタルナイトライド層、該タンタルナイトライド層上に形成された金属層を含む第2の配線と、

前記第1及び第2の配線が接続された複数の電界効果トランジスタを有し、

前記複数の電界効果トランジスタ夫々のソース、ゲート、及びドレインの夫々は、同じ方向に延在し、

前記複数の電界効果トランジスタの各々は、隣接する前記複数の電界効果トランジスタと、前記ソース及び前記ドレインの少なくても一方を共有し、

前記第1の配線が、前記ゲートに電気的に接続され、

前記第2の配線が、前記ソースに電気的に接続され、

第3の配線が、前記ドレインに電気的に接続されている半導体装置を具備し、

更に、前記第1の配線に電気的に接続され、電気信号が入力される第1の端子と、

前記第3の配線に電気的に接続され、増幅された前記電気信号が出力される第2の端子とを具備する高周波増幅器。

【0210】

(付記11)

第1の配線と、

前記第1の配線と交差する方向に延在し、前記第1の配線と空間を介して配置され、タンタル層、該タンタル層上に形成されたタンタルナイトライド層、該タンタルナイトライド層上に形成された金属層を含む第2の配線と、

前記第1及び第2の配線が接続された複数の電界効果トランジスタを有し、

前記複数の電界効果トランジスタ夫々のソース、ゲート、及びドレインの夫々は、同じ方向に延在し、

前記複数の電界効果トランジスタの各々は、隣接する前記複数の電界効果トランジスタと、前記ソース及び前記ドレインの少なくても一方を共有し、

前記第1の配線が、前記ゲートに電気的に接続され、

前記第2の配線が、前記ソースに電気的に接続され、

第3の配線が、前記ドレインに電気的に接続されている半導体装置を具備し、

更に、前記第1の配線に電気的に接続され、電気信号が入力される第1の端子と、

前記第3の配線に電気的に接続された、増幅された前記電気信号が出力される第2の端子とを具備する高周波増幅器を備えた無線送信機であって、

電気信号が入力される入力端子と、

アンテナが接続される出力端子と、

入力信号に従って変調された高周波信号を生成し出力する高周波信号発生ユニットとを具備し、

前記入力端子が、前記高周波信号発生ユニットの入力端子に接続され、

前記高周波信号発生ユニットの出力端子が、前記第1の端子に接続され、

前記出力端子が前記第2の端子に接続されている、

無線送信機。

【0211】

(付記12)

半導体基板上方に第1の配線を形成する工程と、

前記第1の配線上方にマスクを形成する工程と、

前記マスク上に、タンタル層、タンタルナイトライド層、及び金属層を順次積層して、前記第1の配線に交差する方向に延在する第2の配線を形成する工程と、

前記第2の配線の形成後に前記マスクを除去する工程を具備し、

前記タンタルナイトライド層は、前記マスクが融解する前に成膜が終了することを特徴とする

半導体装置の製造方法。

【0212】

(付記13)

付記12に記載の半導体装置の製造方法において、

前記タンタルナイトライド層の窒素含有率が、48%より大きく52%以下であることを、

特徴とする半導体装置の製造方法。

【0213】

(付記14)

付記12又は付記13に記載の半導体装置の製造方法において、

前記タンタル層の上にチタン層を積層してから、前記タンタルナイトライド層を積層することを、

特徴とする半導体装置の製造方法。

【0214】

(付記15)

付記12乃至付記14の何れか1項に記載の半導体装置の製造方法において、

前記タンタル層が、タンタルをターゲットとするスパッタ法で形成され、

前記タンタルナイトライド層が、タンタルをターゲットとする反応性スパッタ法で形成されることを、

特徴とする半導体装置の製造方法。

【0215】

(付記16)

付記12乃至付記15の何れか1項に記載の半導体装置の製造方法において、

前記タンタル層が、タンタルをターゲットとするスパッタ法で形成され、

前記タンタルナイトライド層が、タンタルをターゲットとし窒素を反応性ガスとする反応性スパッタ法で形成され、

前記金属層が、

金をターゲットとするスパッタ法で、第1の金層が形成され、

その後、メッキ法によって第2の金層が積層されて形成されることを、

特徴とする半導体装置の製造方法。

【0216】

(付記17)

付記12乃至16の何れか1項に記載の半導体装置の製造方法において、

前記半導体装置が、前記第1の配線及び前記第2の配線に接続された半導体素子を有し、

前記第1の配線は、前記半導体素子へ入力される信号が伝播する配線であることを、

特徴とする半導体装置の製造方法。

【0217】

(付記18)

付記12乃至17の何れか1項に記載の半導体装置の製造方法において、

前記マスクを形成する前に、

前記第1の配線を、保護膜で覆うことを、

特徴とする半導体装置の製造方法。

【0218】

(付記19)

付記18に記載の半導体装置の製造方法において、

前記マスクを形成する前に、

前記第2の配線下方の前記保護膜を取り除くことを、

特徴とする半導体装置の製造方法。

【0219】

(付記20)

付記18又は19に記載の半導体装置の製造方法において、

前記保護膜が、窒化珪素膜又は二酸化珪素であることを、

特徴とする半導体装置の製造方法。

【図面の簡単な説明】

【0220】

【図1】Ti/TaN/Auエアブリッジ配線の左端を拡大した図である。

【図2】図1中の円で囲った領域Aを拡大した図である。

【図3】TaNの窒素含有率と反応時間の関係を説明する図である。

【図4】TiTaN/Auエアブリッジ配線の製造工程を説明する断面図である(その1)。

【図5】Ti/TaN/Auエアブリッジ配線の製造工程を説明する断面図である(その2)。

【図6】Ti/TaN/Auエアブリッジ配線の製造工程を説明する断面図である(その3)。

【図7】実施の形態1によるマルチゲートトランジスタの構成を説明する斜視図である。

【図8】図7のA−A線に於ける断面を説明する図である。

【図9】図7のB−B線に於ける断面を説明する図である。

【図10】実施の形態1によるエアブリッジ配線構造の製造工程を説明する断面図である(その1)。

【図11】実施の形態1によるエアブリッジ配線構造の製造工程を説明する断面図である(その2)。

【図12】実施の形態1によるエアブリッジ配線構造の製造工程を説明する断面図である(その3)。

【図13】実施の形態1に従うTa/TaN積層膜に対して実施された熱劣化加速試験の結果を説明する図である。

【図14】実施の形態2に従うマルチゲートトランジスタを形成するエアブリッジ配線の断面を説明する図である。

【図15】実施の形態2に従うTa/Ti/TaN積層膜に対して実施された熱劣化加速試験の結果を説明する図である.

【図16】実施の形態3に従うマルチゲートトランジスタの斜視図である。

【図17】図16のB−B線に於ける断面を矢印の方向から見た図である。

【図18】実施の形態3に従うマルチゲートトランジスタの製造手順を説明する工程断面図である。

【図19】実施の形態4に従う高周波増幅器の回路図である。

【図20】実施の形態5に従う送信機のブロック図である。

【符号の説明】

【0221】

2・・・マルチゲートトランジスタ 4・・・GaN−HEMT

6・・・ソース 8・・・ドレイン

10,10´,10´´・・・電極 12・・・エアブリッジ配線

14,14´,14´´・・・共通電極

16・・・ソース電極 18・・・ドレイン電極

20・・・ゲート 22・・・ゲート電極

24・・・SiC基板 26・・・UID−GaNチャネル層

28・・・n型AlGaNキャリア供給層 30・・・UID−GaNキャップ層

32・・・保護膜 34・・・オーミック電極

36・・・AlGaN不活性領域 38・・・空間

40・・・Ti層 42・・・TaN層

44・・・第1のAu層 46・・・第2のAu層

48・・・第3のAu層 50・・・基板

52・・・リフトオフ用フォトレジスト膜 54・・・Ni/Au積層膜

56・・・SiN膜 58・・・エアブリッジ形成用フォトレジスト膜

60・・・電子流れ 62・・・内壁 64・・・Au原子

66・・・結晶粒界

68・・・Ti/Pt/Auスパッタ膜(又は、Ti/TaN/Auスパッタ膜)

70・・・Ta層 72・・・TaN層 74・・・Ta/TaN積層膜

76・・・Ti/Ta/TaN/Auスパッタ膜 78・・・他のTi層

80・・・Ta/Ti/TaN積層膜

82・・・Ti/Ta/Ti/TaN/Auスパッタ膜

84・・・マルチゲートトランジスタ(実施の形態3)

86・・・高周波増幅器 88・・・入力端子

90・・・出力端子 92・・・第1の経路

94・・・ドレイン電極 96・・・電源端子

97・・・第1のコンデンサ 98・・・第1の抵抗

99・・・第2のコンデンサ 100・・・第2の抵抗

102・・第3の抵抗 104・・・第4の抵抗

106・・・第3のコンデンサ 108・・・無線送信機

110・・・高周波信号発生ユニット 112・・・アンテナ

114・・・出力端子 116・・・入力端子

【特許請求の範囲】

【請求項1】

第1の配線と、

前記第1の配線と交差する方向に延在し、前記第1の配線と空間を介して配置され、タンタル層、該タンタル層上に形成されたタンタルナイトライド層、該タンタルナイトライド層上に形成された金属層を含む第2の配線と、

を有することを特徴とする半導体装置。

【請求項2】

請求項1に記載の半導体装置において、

前記タンタルナイトライド層の窒素含有率は、48%より大きく52%以下であることを、

特徴とする半導体装置。

【請求項3】

請求項1又は2に記載の半導体装置において、

前記タンタル層とタンタルナイトライド層の間に、チタン層が形成されていることを、

特徴とする半導体装置。

【請求項4】

請求項1乃至3の何れか1項に記載の半導体装置において、

半導体素子と前記第1の配線を覆う保護膜を有し、

前記第1の配線及び前記第2の配線は、半導体素子に接続され、

前記半導体素子へ入力される信号は、前記第1の配線を伝播し、

前記第1の配線が前記第2の配線と交差する領域では、前記保護膜が取り除かれていることを、

特徴とする半導体装置。

【請求項5】

第1の配線と、

前記第1の配線と交差する方向に延在し、前記第1の配線と空間を介して配置され、タンタル層、該タンタル層上に形成されたタンタルナイトライド層、該タンタルナイトライド層上に形成された金属層を含む第2の配線と、

前記第1及び第2の配線が接続された複数の電界効果トランジスタを有し、

前記複数の電界効果トランジスタ夫々のソース、ゲート、及びドレインの夫々は、同じ方向に延在し、

前記複数の電界効果トランジスタの各々は、隣接する前記複数の電界効果トランジスタと、前記ソース及び前記ドレインの少なくても一方を共有し、

前記第1の配線が、前記ゲートに電気的に接続され、

前記第2の配線が、前記ソースに電気的に接続され、

第3の配線が、前記ドレインに電気的に接続されている半導体装置を具備し、

更に、前記第1の配線に電気的に接続され、電気信号が入力される第1の端子と、

前記第3の配線に電気的に接続された、増幅された前記電気信号が出力される第2の端子とを具備する高周波増幅器。

【請求項6】

半導体基板上方に第1の配線を形成する工程と、

前記第1の配線上方にマスクを形成する工程と、

前記マスク上に、タンタル層、タンタルナイトライド層、及び金属層を順次積層して、前記第1の配線に交差する方向に延在する第2の配線を形成する工程と、

前記第2の配線の形成後に前記マスクを除去する工程を具備し、

前記タンタルナイトライド層は、前記マスクが融解する前に成膜が終了することを特徴とする

半導体装置の製造方法。

【請求項7】

請求項6に記載の半導体装置の製造方法において、

前記タンタルナイトライド層の窒素含有率が、48%より大きく52%以下であることを、

特徴とする半導体装置の製造方法。

【請求項8】

請求項6又は請求項7に記載の半導体装置の製造方法において、

前記タンタル層の上にチタン層を積層してから、前記タンタルナイトライド層を積層することを、

特徴とする半導体装置の製造方法。

【請求項9】

請求項6乃至8の何れか1項に記載の半導体装置の製造方法において、

前記マスクを形成する前に、

前記第1の配線を保護膜で覆い、且つ、前記第2の配線下方の前記保護膜を取り除くことを、

特徴とする半導体装置の製造方法。

【請求項1】

第1の配線と、

前記第1の配線と交差する方向に延在し、前記第1の配線と空間を介して配置され、タンタル層、該タンタル層上に形成されたタンタルナイトライド層、該タンタルナイトライド層上に形成された金属層を含む第2の配線と、

を有することを特徴とする半導体装置。

【請求項2】

請求項1に記載の半導体装置において、

前記タンタルナイトライド層の窒素含有率は、48%より大きく52%以下であることを、

特徴とする半導体装置。

【請求項3】

請求項1又は2に記載の半導体装置において、

前記タンタル層とタンタルナイトライド層の間に、チタン層が形成されていることを、

特徴とする半導体装置。

【請求項4】

請求項1乃至3の何れか1項に記載の半導体装置において、

半導体素子と前記第1の配線を覆う保護膜を有し、

前記第1の配線及び前記第2の配線は、半導体素子に接続され、

前記半導体素子へ入力される信号は、前記第1の配線を伝播し、

前記第1の配線が前記第2の配線と交差する領域では、前記保護膜が取り除かれていることを、

特徴とする半導体装置。

【請求項5】

第1の配線と、

前記第1の配線と交差する方向に延在し、前記第1の配線と空間を介して配置され、タンタル層、該タンタル層上に形成されたタンタルナイトライド層、該タンタルナイトライド層上に形成された金属層を含む第2の配線と、

前記第1及び第2の配線が接続された複数の電界効果トランジスタを有し、

前記複数の電界効果トランジスタ夫々のソース、ゲート、及びドレインの夫々は、同じ方向に延在し、

前記複数の電界効果トランジスタの各々は、隣接する前記複数の電界効果トランジスタと、前記ソース及び前記ドレインの少なくても一方を共有し、

前記第1の配線が、前記ゲートに電気的に接続され、

前記第2の配線が、前記ソースに電気的に接続され、

第3の配線が、前記ドレインに電気的に接続されている半導体装置を具備し、

更に、前記第1の配線に電気的に接続され、電気信号が入力される第1の端子と、

前記第3の配線に電気的に接続された、増幅された前記電気信号が出力される第2の端子とを具備する高周波増幅器。

【請求項6】

半導体基板上方に第1の配線を形成する工程と、

前記第1の配線上方にマスクを形成する工程と、

前記マスク上に、タンタル層、タンタルナイトライド層、及び金属層を順次積層して、前記第1の配線に交差する方向に延在する第2の配線を形成する工程と、

前記第2の配線の形成後に前記マスクを除去する工程を具備し、

前記タンタルナイトライド層は、前記マスクが融解する前に成膜が終了することを特徴とする

半導体装置の製造方法。

【請求項7】

請求項6に記載の半導体装置の製造方法において、

前記タンタルナイトライド層の窒素含有率が、48%より大きく52%以下であることを、

特徴とする半導体装置の製造方法。

【請求項8】

請求項6又は請求項7に記載の半導体装置の製造方法において、

前記タンタル層の上にチタン層を積層してから、前記タンタルナイトライド層を積層することを、

特徴とする半導体装置の製造方法。

【請求項9】

請求項6乃至8の何れか1項に記載の半導体装置の製造方法において、

前記マスクを形成する前に、

前記第1の配線を保護膜で覆い、且つ、前記第2の配線下方の前記保護膜を取り除くことを、

特徴とする半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【公開番号】特開2010−56388(P2010−56388A)

【公開日】平成22年3月11日(2010.3.11)

【国際特許分類】

【出願番号】特願2008−221412(P2008−221412)

【出願日】平成20年8月29日(2008.8.29)

【出願人】(000005223)富士通株式会社 (25,993)

【Fターム(参考)】

【公開日】平成22年3月11日(2010.3.11)

【国際特許分類】

【出願日】平成20年8月29日(2008.8.29)

【出願人】(000005223)富士通株式会社 (25,993)

【Fターム(参考)】

[ Back to top ]