半導体装置およびその製造方法

【課題】バンプ電極によって半導体チップ間あるいは半導体チップと配線基板とを電気的に接続する半導体装置において、特に、接続部の高密度化や狭ピッチ化が進んでも、接続不良の発生を低減できる技術を提供する。

【解決手段】接続部CNTにバンプ電極BMP1を押し付けることにより、接続部CNTを構成する梁BMが曲がる(たわむ)。そして、さらに、バンプ電極BMP1を接続部CNTに押し付けると、バンプ電極BMP1の先端部が空洞部CAの底面に到達する。このとき、押し曲げられた梁BMには復元力が働き、空洞部CAの底面にまで挿入されたバンプ電極BMP1を左右から挟む。このため、空洞部CAに挿入されたバンプ電極BMP1は、左右から梁BMの復元力により固定される。

【解決手段】接続部CNTにバンプ電極BMP1を押し付けることにより、接続部CNTを構成する梁BMが曲がる(たわむ)。そして、さらに、バンプ電極BMP1を接続部CNTに押し付けると、バンプ電極BMP1の先端部が空洞部CAの底面に到達する。このとき、押し曲げられた梁BMには復元力が働き、空洞部CAの底面にまで挿入されたバンプ電極BMP1を左右から挟む。このため、空洞部CAに挿入されたバンプ電極BMP1は、左右から梁BMの復元力により固定される。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置およびその製造方法に関し、特に、バンプ電極によって半導体チップ間あるいは半導体チップと配線基板とを電気的に接続する半導体装置およびその製造に適用して有効な技術に関する。

【背景技術】

【0002】

特開平10−163267号公報(特許文献1)には、加熱工程を不要にして、バンプ付きワークのバンプを基板のパッド上に簡単に固着でき、さらにはパッドやバンプの高密度・ファイン化にも対応できるバンプ付きワークの実装方法および実装基板を提供することを目的とする技術が記載されている。具体的には、基材のパッド上に第1メッキ層と第2メッキ層から成る導電部を形成する。バンプ付きワークのバンプの膨大部を導電部の孔部に強制的に嵌合し、導電部の突出部を膨大部のエッジに係止させる。これにより、バンプが孔部から抜け出さないようにするとともに、導電部にしっかり接触させることができるとしている。

【0003】

特開2004−12357号公報(特許文献2)には、挟ピッチ化が進行する半導体デバイスや超小型のペアチップに対応可能な技術が記載されている。具体的には、半導体デバイスの接続端子と電気的に接続し、平面視してスパイラル形状を有するスパイラル状接触子を絶縁基板上に備えている。そして、スパイラル状接触子は、絶縁基板上に球状接続端子との接触の際に、球状接続端子の形状に対応して変形可能となっており、半導体デバイスとの電気的な接続を行うように構成されている。このとき、スパイラル状接触子の渦巻き部、幅が一定で、先端から根元に近づくに従って厚みが厚くなるとしている。

【0004】

特開2004−354179号公報(特許文献3)には、電子部品を装着してテストを行なうテスト用ソケットに関し、低コスト化および信頼性の向上を図ることを目的とする技術が記載されている。具体的には、半導体装置が装着され、この半導体装置に対してテストを行なうテスト用ソケットにおいて、層間接続を行なうためのビアが形成されると共に半導体装置の半田ボールが接続される位置に貫通孔が形成されてなる基材層を複数積層してなる基板部と、この基板部に配設されると共にビアと電気的に接続され、かつ、半導体装置と電気的に接続される電極部が形成されたコンタクト部とを具備するとしている。そして、このコンタクト部にはスリットが形成されている。これにより、半田ボールの接続時に、この接続に伴いコンタクト部が変位する。このため、半田ボールとコンタクト部との接触面積を増大させることができ、コンタクト部と半田ボールとを確実に電気的に接続することができるとしている。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開平10−163267号公報

【特許文献2】特開2004−12357号公報

【特許文献3】特開2004−354179号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

携帯電話機やデジタルカメラなどのモバイル機器には、1つの半導体パッケージの内部に複数の半導体チップを積層して搭載する、いわゆるSIP(System In Package)が広く使用されている。これは、半導体チップを積層して配置することにより、半導体チップを平面上に並べて配置する(平置きする)場合に比べて、実装面積を小さくすることができ、同一の実装面積で多数の半導体チップを搭載できるからである。すなわち、モバイル機器には持ち運びの利便性の観点から小型化が要求されており、この小型化を実現するために、実装面積を小さくすることができるSIPが使用されるのである。

【0007】

SIPでは、半導体チップを積層するが、積層された半導体チップ間の電気的な接続は、例えば、下層に配置される半導体チップに形成された端子と、上層に配置される半導体チップに形成されたバンプ電極とを半田で電気的に接続する。

【0008】

近年では、半導体装置の小型化のために、半導体チップ間を接続する接続部の高密度・狭ピッチ化が要求されており、高密度・狭ピッチに配置された端子とバンプ電極とを半田で接続する必要がある。しかし、半田を使用した接続では、半田を加熱して溶融(リフロー)させる工程が必要である。このとき、端子やバンプ電極から構成される接続部の高密度化や狭ピッチ化が進むと、半田の加熱溶融時に半田が流動化するため、隣り合う位置に配置されている端子上に形成されている半田同士が接合してショート不良が発生するという問題点がある。

【0009】

以上では、SIPを例に挙げて、積層された半導体チップ間の接続に半田を使用する場合を説明したが、半導体チップを積層するSIPに限らず、例えば、半導体チップと配線基板とをフリップチップ接続する場合も同様の問題が発生する。すなわち、半導体チップに形成されているバンプ電極を、配線基板に形成されている端子に半田を使用して接続する場合も、バンプ電極および端子の高密度化や狭ピッチ化に伴って、半田を介した端子間のショート不良が問題となる。

【0010】

本発明の目的は、バンプ電極によって半導体チップ間あるいは半導体チップと配線基板とを電気的に接続する半導体装置において、特に、接続部の高密度化や狭ピッチ化が進んでも、接続不良の発生を低減できる技術を提供することにある。

【0011】

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

【課題を解決するための手段】

【0012】

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、次のとおりである。

【0013】

代表的な実施の形態による半導体装置は、(a)第1基板と、(b)前記第1基板上に形成され、かつ、パターニングされた第1導体膜と、(c)前記第1導体膜に形成された空洞部と、(d)前記第1導体膜上に形成され、かつ、一部が前記空洞部に突き出るようにパターニングされた第2導体膜と、(e)前記第2導体膜に形成された開口部とを備える。そして、平面的に前記開口部が前記空洞部に内包され、かつ、前記開口部と前記空洞部が一体化され、かつ、前記第2導体膜のうち前記空洞部に突き出た部分が梁として機能する。このとき、前記開口部の輪郭形状は、前記空洞部に突き出ている前記梁の根元から先端部に至る形状を縁取る形状を有し、前記開口部の平面上の面積は、前記梁の平面上の面積よりも大きいことを特徴とするものである。

【0014】

また、代表的な実施の形態による半導体装置は、(a)第1半導体基板と、(b)前記第1半導体基板の裏面から前記裏面とは反対側の素子形成面に達する孔と、(c)前記孔内を含む前記第1半導体基板の前記裏面に形成され、かつ、パターニングされた第1導体膜とを備える。そして、(d)前記第1半導体基板の前記裏面に形成されている前記第1導体膜に形成された空洞部と、(e)前記第1導体膜上に形成され、かつ、一部が前記空洞部に突き出るようにパターニングされた第2導体膜と、(f)前記第2導体膜に形成された開口部とを備える。このとき、平面的に前記開口部が前記空洞部に内包され、かつ、前記開口部と前記空洞部が一体化され、かつ、前記第2導体膜のうち前記空洞部に突き出た部分が梁として機能する。そして、前記開口部の輪郭形状は、前記空洞部に突き出ている前記梁の根元から先端部に至る形状を縁取る形状を有し、前記開口部の平面上の面積は、前記梁の平面上の面積よりも大きいことを特徴とするものである。

【0015】

さらに、代表的な実施の形態による半導体装置の製造方法は、(a)第1基板の第1面上に第1導体膜を形成する工程と、(b)前記第1導体膜上に第2導体膜を形成する工程と、(c)前記第2導体膜を貫通する開口部を形成する工程と、(d)前記開口部をエッチング孔として前記第1導体膜をウェットエッチングすることにより、前記第1導体膜に空洞部を形成する工程とを備える。そして、平面的に前記開口部が前記空洞部に内包され、かつ、前記開口部と前記空洞部が一体化され、かつ、前記第2導体膜のうち前記空洞部に突き出た部分が梁となる。ここで、前記開口部の輪郭形状は、前記空洞部に突き出ている前記梁の根元から先端部に至る形状を縁取る形状を有し、前記開口部の平面上の面積は、前記梁の平面上の面積よりも大きいことを特徴とするものである。

【0016】

また、代表的な実施の形態による半導体装置の製造方法は、(a)第1半導体基板の裏面から前記裏面とは反対側の素子形成面に形成された電極に達する孔を形成する工程と、(b)前記孔内を含む前記第1半導体基板の前記裏面上に第1導体膜を形成する工程と、(c)前記第1導体膜上に第2導体膜を形成する工程とを備える。そして、(d)前記第2導体膜をパターニングすることにより、前記第1半導体基板の前記裏面に形成されている前記第2導体膜に開口部を形成する工程と、(e)前記開口部をエッチング孔として前記第1導体膜をウェットエッチングすることにより、前記第1導体膜に空洞部を形成する工程とを備える。ここで、平面的に前記開口部が前記空洞部に内包され、かつ、前記開口部と前記空洞部が一体化され、かつ、前記第2導体膜のうち前記空洞部に突き出た部分が梁となる。このとき、前記開口部の輪郭形状は、前記空洞部に突き出ている前記梁の根元から先端部に至る形状を縁取る形状を有し、前記開口部の平面上の面積は、前記梁の平面上の面積よりも大きいことを特徴とするものである。

【発明の効果】

【0017】

本願において開示される発明のうち、代表的なものによって得られる効果を簡単に説明すれば以下のとおりである。

【0018】

バンプ電極によって半導体チップ間あるいは半導体チップと配線基板とを電気的に接続する半導体装置において、接続不良の発生を低減できる。

【図面の簡単な説明】

【0019】

【図1】本発明の実施の形態1における半導体チップに形成されている接続部の構成を示す断面図である。

【図2】接続部を形成した半導体チップと、バンプ電極を形成した半導体チップとを相対させた断面図である。

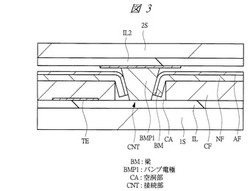

【図3】接続部とバンプ電極との接続状態の一例を示す断面図である。

【図4】接続部を形成した半導体チップと、バンプ電極を形成した半導体チップとを相対させた断面図である。

【図5】接続部とバンプ電極との接続状態の他の一例を示す断面図である。

【図6】接続部を形成した半導体チップと、バンプ電極を形成した半導体チップとを相対させた断面図である。

【図7】接続部とバンプ電極との接続状態のさらに他の一例を示す断面図である。

【図8】接続部の位置と端子の位置とが平面的に重なるように配置される例を示す断面図である。

【図9】接続部を構成する主要な構成要素の寸法と、バンプ電極の先端部の寸法を示す図である。

【図10】接続部の平面構造を示す図である。

【図11】比較例の接続部の構造を示す図である。

【図12】下層の半導体チップと上層の半導体チップとを積層する様子を示す図である。

【図13】下層の半導体チップと上層の半導体チップとを積層する様子を示す断面図である。

【図14】実施の形態1における半導体装置の製造工程を示す断面図である。

【図15】図14に続く半導体装置の製造工程を示す断面図である。

【図16】図15に続く半導体装置の製造工程を示す断面図である。

【図17】図16に続く半導体装置の製造工程を示す断面図である。

【図18】図17に続く半導体装置の製造工程を示す断面図である。

【図19】図18に続く半導体装置の製造工程を示す断面図である。

【図20】図19に続く半導体装置の製造工程を示す断面図である。

【図21】図20に続く半導体装置の製造工程を示す断面図である。

【図22】図21に続く半導体装置の製造工程を示す断面図である。

【図23】実施の形態2における半導体基板に形成された接続部と貫通電極を示す図である。

【図24】接続部と貫通電極を形成した半導体基板の構成を示す断面図である。

【図25】実施の形態2における半導体装置の製造工程を示す断面図である。

【図26】図25に続く半導体装置の製造工程を示す断面図である。

【図27】図26に続く半導体装置の製造工程を示す断面図である。

【図28】図27に続く半導体装置の製造工程を示す断面図である。

【図29】図28に続く半導体装置の製造工程を示す断面図である。

【図30】図29に続く半導体装置の製造工程を示す断面図である。

【図31】図30に続く半導体装置の製造工程を示す断面図である。

【図32】図31に続く半導体装置の製造工程を示す断面図である。

【図33】図32に続く半導体装置の製造工程を示す断面図である。

【図34】図33に続く半導体装置の製造工程を示す断面図である。

【図35】図34に続く半導体装置の製造工程を示す断面図である。

【図36】図35に続く半導体装置の製造工程を示す断面図である。

【図37】図36に続く半導体装置の製造工程を示す断面図である。

【図38】図37に続く半導体装置の製造工程を示す断面図である。

【図39】図38に続く半導体装置の製造工程を示す断面図である。

【図40】図39に続く半導体装置の製造工程を示す断面図である。

【図41】図40に続く半導体装置の製造工程を示す断面図である。

【図42】図41に続く半導体装置の製造工程を示す断面図である。

【図43】図42に続く半導体装置の製造工程を示す断面図である。

【図44】図43に続く半導体装置の製造工程を示す断面図である。

【図45】複数の半導体チップを積層する様子を示す図である。

【図46】複数の半導体チップを積層する様子を示す断面図である。

【発明を実施するための形態】

【0020】

以下の実施の形態においては便宜上その必要があるときは、複数のセクションまたは実施の形態に分割して説明するが、特に明示した場合を除き、それらはお互いに無関係なものではなく、一方は他方の一部または全部の変形例、詳細、補足説明等の関係にある。

【0021】

また、以下の実施の形態において、要素の数等(個数、数値、量、範囲等を含む)に言及する場合、特に明示した場合および原理的に明らかに特定の数に限定される場合等を除き、その特定の数に限定されるものではなく、特定の数以上でも以下でもよい。

【0022】

さらに、以下の実施の形態において、その構成要素(要素ステップ等も含む)は、特に明示した場合および原理的に明らかに必須であると考えられる場合等を除き、必ずしも必須のものではないことは言うまでもない。

【0023】

同様に、以下の実施の形態において、構成要素等の形状、位置関係等に言及するときは、特に明示した場合および原理的に明らかにそうではないと考えられる場合等を除き、実質的にその形状等に近似または類似するもの等を含むものとする。このことは、上記数値および範囲についても同様である。

【0024】

また、実施の形態を説明するための全図において、同一の部材には原則として同一の符号を付し、その繰り返しの説明は省略する。なお、図面をわかりやすくするために平面図であってもハッチングを付す場合がある。

【0025】

(実施の形態1)

本実施の形態1では、主に複数の半導体チップを積層する例について説明する。積層された複数の半導体チップを電気的に接続する方法としては、上層の半導体チップにバンプ電極を形成し、かつ、下層の半導体チップに端子を形成し、上層の半導体チップに形成されているバンプ電極を、下層に形成されている端子に半田を使用して接続する方法が考えられる。

【0026】

近年、半導体装置の小型化のために、半導体チップ間を接続する接続部の高密度・狭ピッチ化が要求されており、高密度・狭ピッチに配置された端子とバンプ電極とを半田で接続する必要がある。このとき、半田を使用した接続では、半田を加熱して溶融(リフロー)させる工程が必要である。ところが、端子やバンプ電極から構成される接続部の高密度化や狭ピッチ化が進むと、半田の加熱溶融時に半田が流動化するため、隣り合う位置に配置されている端子上に形成されている半田同士が接合してショート不良が発生するおそれがある。つまり、半田を使用して上層の半導体チップと下層の半導体チップを接続する方法は、半導体チップ間を接続する端子およびバンプ電極の高密度・狭ピッチ化が進むにつれて、隣接する端子間をショートさせることなく端子とバンプ電極とを接続することが困難になってきている。

【0027】

そこで、本実施の形態1では、半田を使用することなく、上層の半導体チップと下層の半導体チップとを電気的に接続する工夫を施している。以下では、上層の半導体チップと下層の半導体チップとを電気的に接続する工夫について説明する。本実施の形態1では、上層の半導体チップにバンプ電極を形成し、このバンプ電極と電気的に接続する下層の半導体チップの接続部に工夫を施している。

【0028】

図1は、下層の半導体チップに形成されている接続部CNTの構成を示す断面図である。図1において、半導体基板1Sの上面(主面、素子形成面)には、MISFET(Metal Insulator Semiconductor Field Effect Transistor)などの半導体素子(図示せず)が形成されている。そして、半導体素子を形成した半導体基板1S上には、層間絶縁膜ILが形成されている。この層間絶縁膜ILには、多層配線(図示せず)が形成されており、多層配線は、半導体基板1Sに形成されている半導体素子と電気的に接続されている。さらに、この層間絶縁膜ILの最上層には端子(基板電極)TEが形成されている。

【0029】

端子TEが形成された層間絶縁膜IL上には銅膜CFが形成され、この銅膜CF上にニッケル膜NFが形成されている。そして、ニッケル膜NFの表面に金膜AFが形成されている。このとき、接続部CNTは、層間絶縁膜IL上に形成されている銅膜CF、ニッケル膜NFおよび金膜AFを加工することにより形成されている。具体的に、接続部CNTは、金膜AFおよびニッケル膜NFを貫通するように形成された開口部OPを有している。そして、この開口部OPから露出する銅膜CFが除去されて、銅膜CFに空洞部CAが形成されている。このとき、銅膜CFに形成されている空洞部CAの大きさは、ニッケル膜NFおよび金膜AFに形成されている開口部OPの大きさよりも大きくなっている。したがって、空洞部CA上には、ニッケル膜NFおよび金膜AFからなる梁BMが突き出た構造となっている。つまり、本実施の形態1における接続部CNTは、銅膜CF、ニッケル膜NFおよび金膜AFを構成要素とし、銅膜CFに空洞部CAが形成され、かつ、ニッケル膜NFおよび金膜AFに開口部OPが形成された構造をしている。そして、空洞部CAが開口部OPを内包し、かつ、空洞部CAの大きさが開口部OPの大きさよりも大きくなっているので、空洞部CAの上部にニッケル膜NFおよび金膜AFよりなる梁BMが形成されていることになる。なお、銅膜CF、ニッケル膜NFおよび金膜AFは接続部CNTに接続される配線としても機能する。

【0030】

接続部CNTを構成する空洞部CAと開口部OPは接続されており一体化している。接続部CNTを構成する銅膜CFは、空洞部CAを形成し、かつ、端子TEと接続部CNTを電気的に接続する機能を有している。接続部CNTを構成するニッケル膜NFは、梁BMを構成するための膜であり、このニッケル膜NFの膜厚によって梁BMの剛性が決まる。つまり、ニッケル膜NFは梁BMとして機能する膜であり、ニッケル膜NFは高い剛性を有していることから、梁BMとして使用されている。ニッケル膜NF上に形成されている金膜AFは、接続部CNTとバンプ電極とを低抵抗で接続するために形成される膜である。

【0031】

本実施の形態1における接続部CNTは上記のように構成されており、以下に、この接続部CNTとバンプ電極との接続形態について説明する。つまり、接続部CNTを形成した下層の半導体チップと、バンプ電極を形成した上層の半導体チップとの接続構造について説明する。

【0032】

図2は、接続部CNTを形成した半導体基板1S(下層の半導体チップ)と、バンプ電極BMP1を形成した半導体基板2S(上層の半導体チップ)とを相対させた図である。図2において、半導体基板1Sに形成された接続部CNTの構成は図1で説明したものと同様である。一方、半導体基板2Sには、図2の下面(主面、素子形成面)にMISFETなどの半導体素子が形成されており、この半導体素子を形成した半導体基板2S上に層間絶縁膜IL2が形成されている。この層間絶縁膜IL2には多層配線が形成されており、多層配線は半導体基板2Sに形成された半導体素子と電気的に接続されている。そして、層間絶縁膜IL2の最上層にパッドが形成されており、このパッド上にバンプ電極BMP1が形成されている。

【0033】

バンプ電極BMP1は、例えば、めっき法で形成された金膜から形成されている。このようにめっき法で形成されたバンプ電極BMP1は、バンプ電極BMP1の材料(金膜)を溶融させていないので、変形しにくいという特性がある。

【0034】

上述したバンプ電極BMP1を形成した半導体基板2Sと、接続部CNTを形成した半導体基板1Sとを接続する。具体的に、図2に示すように、半導体基板1Sに形成されている接続部CNTと、半導体基板2Sに形成されているバンプ電極BMP1との位置合わせを実施する。その後、上層の半導体基板2Sに荷重を加えることにより、下層の半導体基板1Sに形成されている接続部CNTに、上層の半導体基板2Sに形成されているバンプ電極BMP1を押し付ける。これにより、図3に示すように、上層のバンプ電極BMP1と下層の接続部CNTが接続される。具体的に、図3は、バンプ電極BMP1と接続部CNTとの接続状態を示す図である。図3において、接続部CNTにバンプ電極BMP1を押し付けることにより、接続部CNTを構成する梁BMが曲がる(たわむ)。そして、さらに、バンプ電極BMP1を接続部CNTに押し付けると、バンプ電極BMP1の先端部が空洞部CAの底面に到達する。このとき、押し曲げられた梁BMには復元力が働き、空洞部CAの底面にまで挿入されたバンプ電極BMP1を左右から挟む。このため、空洞部CAに挿入されたバンプ電極BMP1は、左右から梁BMの復元力により固定される。このようにして、バンプ電極BMP1を接続部CNTに接続することができる。

【0035】

このとき、半導体基板2Sに形成されている半導体素子は、層間絶縁膜IL2に形成されている多層配線と多層配線上に形成されているバンプ電極BMP1と電気的に接続されている。そして、バンプ電極BMP1は、接続部CNTと接続されている。具体的に、バンプ電極BMP1は梁BMで固定されていることから、バンプ電極BMP1は、梁BMを構成するニッケル膜NFおよび金膜AFと接続される。そして、ニッケル膜NFは銅膜CFと接続され、かつ、銅膜CFは層間絶縁膜IL1上に形成されている端子TEと接続されていることから、バンプ電極BMP1は、接続部CNTを介して端子TEと接続される。さらに、端子TEは、層間絶縁膜IL1に形成された多層配線および多層配線の下層に形成された半導体素子と接続されている。したがって、半導体基板2Sに形成されているバンプ電極BMP1と、半導体基板1Sに形成されている接続部CNTとを接続することにより、半導体基板2Sに形成されている半導体素子と、半導体基板1Sに形成されている半導体素子とを電気的に接続することができる。ここで、バンプ電極BMP1には接続部CNTを構成する梁BMが接続されているが、梁BMの表面には金膜AFが形成されているので、バンプ電極BMP1と接続部CNTとの接触抵抗を小さくすることができる。

【0036】

以上のように、本実施の形態1の第1特徴点は、図3に示すように、半導体基板1Sに形成した接続部CNTに、半導体基板2Sに形成したバンプ電極BMP2を挿入することにより、接続部CNTとバンプ電極BMP1とを接続することにある。詳細には、接続部CNTを、銅膜CFに形成された空洞部CAと、空洞部CA上に形成されたニッケル膜NFおよび金膜AFからなる梁BMと、梁BMの間に形成された開口部OPから構成することにより、バンプ電極BMP1を開口部OPから空洞部CA内に挿入し、バンプ電極BMP1を挿入することにより変形した梁BMの復元力でバンプ電極BMP1を固定することができる。この結果、本実施の形態1によれば、バンプ電極BMP1と接続部CNTとを半田を使用せずに接続することができる。つまり、本実施の形態1では、空洞部CAにバンプ電極BMP1を挿入し、かつ、空洞部CAに突き出るように配置された梁BMの変形による復元力でバンプ電極BMP1を固定するように構成している。このため、本実施の形態1では、半田を使用せずに、バンプ電極BMP1を接続部CNTへ機械的に固定することができる。このことは、バンプ電極BMP1と接続部CNTの接続に半田を使用しないので、接続部CNTおよびバンプ電極BMP1の高密度化や狭ピッチ化が行なわれても、隣接する接続部CNT間や隣接するバンプ電極BMP1間でのショート不良を抑制できることを意味している。言い換えれば、本実施の形態1では、バンプ電極BMP1と接続部CNTとの接続に溶融した半田を使用しないために、半田ブリッジによるショート不良を抑制することができ、半導体装置の信頼性を向上することができるのである。

【0037】

図2および図3では、例えば、めっき法で形成された変形しにくいバンプ電極BMP1を接続部CNTに挿入して接続する例を説明したが、次に、変形しやすいバンプ電極BMP2を接続部CNTに挿入して接続する例について説明する。

【0038】

図4は、接続部CNTを形成した半導体基板1S(下層の半導体チップ)と、バンプ電極BMP2を形成した半導体基板2S(上層の半導体チップ)とを相対させた図である。図4において、半導体基板1Sに形成された接続部CNTの構成は図1で説明したものと同様である。一方、半導体基板2Sに形成されたバンプ電極BMP2は、図2で説明したバンプ電極BMP1とは形成方法が異なっている。つまり、図4におけるバンプ電極BMP2は、例えば、スタッドバンプ電極のように変形しやすいバンプ電極から構成されている。スタッドバンプ電極とは、金線を溶融させてキャピラリと呼ばれる型に押し付けることにより成形したバンプ電極であり、一度溶融させているため、変形しやすいという特性を有している。

【0039】

上述したバンプ電極BMP2を形成した半導体基板2Sと、接続部CNTを形成した半導体基板1Sとを接続する。具体的に、図4に示すように、半導体基板1Sに形成されている接続部CNTと、半導体基板2Sに形成されているバンプ電極BMP2との位置合わせを実施する。その後、上層の半導体基板2Sに荷重を加えることにより、下層の半導体基板1Sに形成されている接続部CNTに、上層の半導体基板2Sに形成されているバンプ電極BMP2を押し付ける。これにより、図5に示すように、上層のバンプ電極BMP2と下層の接続部CNTが接続される。具体的に、図5は、バンプ電極BMP2と接続部CNTとの接続状態を示す図である。図5において、接続部CNTにバンプ電極BMP2を押し付けることにより、接続部CNTを構成する梁BMが曲がる(たわむ)。そして、さらに、バンプ電極BMP2を接続部CNTに押し付けると、バンプ電極BMP2の先端部が空洞部CAの底面に到達する。このとき、押し曲げられた梁BMには復元力が働き、空洞部CAの底面にまで挿入されたバンプ電極BMP2を左右から挟む。このため、空洞部CAに挿入されたバンプ電極BMP2は、左右から梁BMの復元力により固定される。さらに、この状態で、バンプ電極BMP2に荷重を加えると、バンプ電極BMP2が塑性変形し、バンプ電極BMP2の先端部が横方向に広がる。この結果、梁BMの復元力に加えて、梁BMとバンプ電極BMP2がかしめられるので、バンプ電極BMP2と接続部CNTの接合力が向上する。このようにして、バンプ電極BMP2を接続部CNTに接続することができる。

【0040】

続いて、半球状で比較的柔らかいバンプ電極BMP3を接続部CNTに挿入して接続する例について説明する。図6は、接続部CNTを形成した半導体基板1S(下層の半導体チップ)と、バンプ電極BMP3を形成した半導体基板2S(上層の半導体チップ)とを相対させた図である。図6において、半導体基板1Sに形成された接続部CNTの構成は図1で説明したものと同様である。一方、半導体基板2Sに形成されたバンプ電極BMP3は、図2で説明したバンプ電極BMP1や図4で説明したバンプ電極BMP2とは材質が異なり、例えば、半田から構成されている。この半田から構成されているバンプ電極BMP3は、半球状で比較的柔らかな構造をしている。

【0041】

上述したバンプ電極BMP3を形成した半導体基板2Sと、接続部CNTを形成した半導体基板1Sとを接続する。具体的に、図6に示すように、半導体基板1Sに形成されている接続部CNTと、半導体基板2Sに形成されているバンプ電極BMP3との位置合わせを実施する。その後、上層の半導体基板2Sに荷重を加えることにより、下層の半導体基板1Sに形成されている接続部CNTに、上層の半導体基板2Sに形成されているバンプ電極BMP3を押し付ける。これにより、図7に示すように、上層のバンプ電極BMP3と下層の接続部CNTが接続される。具体的に、図7は、バンプ電極BMP3と接続部CNTとの接続状態を示す図である。図7において、接続部CNTにバンプ電極BMP3を押し付けると、接続部CNTを構成する梁BMが曲がり始めるとともに、柔らかいバンプ電極BMP3も梁BMのたわみに沿って変形する。そして、さらに、バンプ電極BMP3を接続部CNTに押し付けると、バンプ電極BMP3の先端部が空洞部CAの底面に到達する。このとき、押し曲げられた梁BMには復元力が働き、空洞部CAの底面にまで挿入されたバンプ電極BMP3を左右から挟む。このため、空洞部CAに挿入されたバンプ電極BMP3は、左右から梁BMの復元力により固定される。このようにして、バンプ電極BMP3を接続部CNTに接続することができる。

【0042】

以上のことから、本実施の形態1における接続部CNTは、様々な材質や形状のバンプ電極BMP1〜BMP3と接続することができることがわかる。すなわち、本実施の形態1による接続部CNTは、バンプ電極BMP1〜BMP3の種類を問わず、半導体基板1S(下層の半導体チップ)と半導体基板2S(上層の半導体チップ)とを接続することができる。

【0043】

次に、本実施の形態1における接続部CNTと端子TEとの位置関係について説明する。例えば、図1〜図7では、接続部CNTの位置と端子TEの位置とは、平面的に離れた位置に形成されている。この場合、接続部CNTと端子TEとの電気的な接続は、接続部CNTを構成する銅膜CFによって行なわれる。すなわち、接続部CNTにバンプ電極BMP1〜BMP3が接続されると、バンプ電極BMP1〜BMP3は梁BMと接触する。この梁BMは、ニッケル膜NFと金膜AFとの積層膜から形成され、銅膜CFと電気的に接続される。さらに、銅膜CFは端子TEと接続されている。したがって、バンプ電極BMP1〜BMP3は、接続部CNTを介して銅膜CFにより端子TEと接続される。このとき、バンプ電極BMP1〜BMP3が梁BMと接触すれば、必然的に、梁BMと接続されている銅膜CFを介して端子TEと接続することができるので、バンプ電極BMP1〜BMP3と端子TEとを安定して接続することができる。

【0044】

これに対し、例えば、図8では、接続部CNTの位置と端子TEの位置とが平面的に重なるように配置されている。言い換えれば、接続部CNTを構成する空洞部CAの底部に端子TEが形成されている。この場合、空洞部CAの底部に形成されている端子TEと、バンプ電極BMPとを直接接続することができる。したがって、接続部CNTの周辺部に端子TEを配置する必要がなくなるため、接続部CNTと端子TEとを含む接続構造を形成するスペースを小さくすることができる。この結果、図8に示す接続構造によれば、半導体装置の小型化を推進できる利点がある。

【0045】

本実施の形態1における第1特徴点は、図9に示すように、接続部CNTを、銅膜CFに形成された空洞部CAと、空洞部CA上に形成されたニッケル膜NFおよび金膜AFからなる梁BMと、梁BMの間に形成された開口部OPから構成することにより、バンプ電極BMPを開口部OPから空洞部CA内に挿入し、バンプ電極BMPを挿入することにより変形した梁BMの復元力でバンプ電極BMPを固定する点にある。この第1特徴点により、バンプ電極BMPを接続部CNTに接続することができるが、バンプ電極BMPと接続部CNTの接続を良好にする観点からは、以下に示す関係を満たしていることが望ましい。この関係について図9を参照しながら説明する。

【0046】

まず、図9は、接続部CNTを構成する主要な構成要素の寸法と、バンプ電極BMPの先端部の寸法を示す図である。図9において、開口部OPの径をaとしている。すなわち、開口部OPの径を言い換えると、複数の梁BMの先端部間の距離をaとしている。そして、バンプ電極BMPの先端部の径をbとしている。このとき、条件a<bが成立していることが望ましい。なぜなら、開口部OPの径(a)がバンプ電極BMPの先端部の径(b)よりも小さければ、バンプ電極BMPを開口部OPに挿入した場合、梁BMにバンプ電極BMPが接触し、バンプ電極BMPを挿入するにしたがって梁BMが変形し、変形した梁BMによる復元力で挿入されたバンプ電極BMPを固定することができるからである。

【0047】

また、梁BMの長さをcとしており、空洞部CAの深さをdとしている。空洞部CAの深さは、言い換えれば、銅膜CFの厚さということもできる。このとき、条件c<dが成立していることが望ましい。なぜなら、梁BMの長さ(c)が空洞部CAの深さ(d)よりも小さければ、バンプ電極BMPが空洞部CA内に挿入されたとき、梁BMが空洞部CAの底部に接触してバンプ電極BMPの空洞部CAへの挿入が妨げられることや、梁BMが空洞部CAの底部に接触して折れ曲がって折れてしまうことを抑制できるからである。これらの条件(a<b、c<d)を満たすことにより、バンプ電極BMPと接続部CNTの接続を良好にすることができる。

【0048】

上述した記載では、本実施の形態1における接続部CNTの特徴(第1特徴点)を断面構造の観点から説明したが、次に、本実施の形態1における接続部CNTのさらなる特徴を平面構造の観点から説明する。

【0049】

図10は、本実施の形態1における接続部CNTの平面構造を示す図である。図10において、半導体基板1S上に接続部CNTが形成されている。この接続部CNTは、半導体基板1S上に形成された導体膜CON(ニッケル膜NF+金膜AF)を有し、この導体膜CONには、導体膜CONを貫通する開口部OPが形成されている。この開口部OPの下層には、開口部OPと一体化された空洞部CAが形成されている。この空洞部CAは、開口部OPを平面的に内包し、かつ、空洞部CAの大きさが開口部OPの大きさよりも大きくなるように形成されている。そして、開口部OP上には導体膜CONからなる複数の梁BMが形成されており、この複数の梁BMは開口部OPに突き出すように形成されている。このように構成されている接続部CNTにおいて、図10のA−A線で切断した断面が、例えば、図1などに該当する。

【0050】

本実施の形態1の第2特徴点は、平面的に開口部OPが空洞部CAに内包され、かつ、開口部OPと空洞部CAが一体化され、かつ、導体膜CONのうち空洞部CAに突き出た部分が梁BMとなる接続部CNTにおいて、開口部OPの輪郭形状が、空洞部CAに突き出ている梁BMの根元から先端部に至る形状を縁取る形状を有している点にある。すなわち、本実施の形態1における開口部OPは、隣接する梁BMの間において、梁BMの根元から先端部に至るまで大きく開口されている。特に、開口部OPの平面上の面積は、梁BMの平面上の面積よりも大きくなっている。これにより、開口部OPの下層に形成される空洞部CAを容易に作ることができるのである。

【0051】

具体的に、本実施の形態1では、開口部OPから露出する下地膜(銅膜)をウェットエッチングすることにより空洞部CAを形成している。このとき、開口部OPの輪郭形状が、空洞部CAに突き出ている梁BMの根元から先端部に至る形状を縁取る形状を有しており、隣接する梁BMの間において、梁BMの根元から先端部に至るまで大きく開口されていると、開口部OPから露出する下地膜の表面積が大きくなる。この場合、エッチング液の循環もよくなり、エッチング速度が速くなる利点がある。さらに、開口部OPの下層に空洞部CAを形成するためのエッチング面積も少なくすることができる。つまり、空洞部CAは、梁BMの下層に空洞を形成するためのものであるが、隣接する梁BMの間において、開口部OPの形状が梁BMの根元から先端部に至るまで大きく開口されていると、開口部OPから露出する下地膜の表面積が大きくなるため、大きな露出領域の各領域からエッチングが進行する。このため、梁BMの下層に形成される空洞部CAをより少ないエッチング量で形成することができるのである。このように本実施の形態1によれば、開口部OPの輪郭形状が、空洞部CAに突き出ている梁BMの根元から先端部に至る形状を縁取る形状を有し、隣接する梁BMの間において、梁BMの根元から先端部に至るまで大きく開口されている形状をしていることから(第2特徴点)、空洞部CAを形成するエッチング量を低減することができるとともに、エッチング速度を速くすることができる。このことは、空洞部CAを形成するための処理時間が短くなることを意味し、これにより、コストの削減を図ることができることを意味している。特に、開口部OPの平面上の面積が、梁BMの平面上の面積よりも大きくなっていると上述した効果は大きくなる。

【0052】

ここで、例えば、図11に示すような接続部CNT2の構造を考える。この接続部CNT2は、中央部に円形の開口部OPTが形成されており、この開口部OPTの外側に梁BM2が形成されている。このとき、梁BM2は、開口部OPTから放射状に形成されたスリットSLによって分割されて梁BM2となっている。このような接続部CNT2において、開口部OPTの下層に空洞部を形成することを考える。この場合、開口部OPTから露出する下地膜をウェットエッチングすることにより、梁BMの下層に空洞部CAを形成する。

【0053】

しかし、接続部CNT2の構成では、本実施の形態1の接続部CNTと異なり、開口部OPTの輪郭形状が、空洞部に突き出ている梁BM2の根元から先端部に至る形状を縁取る形状をしておらず、隣接する梁BM2の間において、梁BM2の根元から先端部に至るまで大きく開口されていない。つまり、接続部CNT2では、隣接する梁BM2の間には線状のスリットSLが形成されているだけである。このため、エッチング液は、開口部OPTからしか内部に浸入しないことなり、空洞部を形成するエッチングは図11に示すように、開口部OPTから同心円状に進むことになる。この場合、開口部OPTから露出する露出領域が小さいことからエッチング液の循環が悪くなるとともに、露出領域の表面積が小さいことから、同時にエッチングされる領域も狭くなる。さらに、エッチングが同心円状に進むことから、梁BM2の下層全体に空洞部を形成するエッチング量も大きくなる。このことは、空洞部を形成するための処理時間が長くなることを意味し、これにより、コストの上昇を招くことになる。

【0054】

これに対し、本実施の形態1では、開口部OPの輪郭形状が、空洞部CAに突き出ている梁BMの根元から先端部に至る形状を縁取る形状を有し、隣接する梁BMの間において、梁BMの根元から先端部に至るまで大きく開口されている形状をしていることから(第2特徴点)、空洞部CAを形成するエッチング量を低減することができるとともに、エッチング速度を速くすることができる利点を有するのである。

【0055】

さらに、本実施の形態1では、上述した第2特徴点により別の効果も奏する。例えば、接続部CNTにバンプ電極を挿入して複数の半導体チップを積層した構造では、複数の半導体チップ間にアンダーフィルと呼ばれる樹脂を注入することが行なわれる。このアンダーフィルは、半導体装置に熱負荷が加わった場合に、材質間の熱膨張率の相違による剥がれを抑制して接着効果を高める機能を有している。このとき、本実施の形態1の接続部CNTのように、隣接する梁BMの間において、梁BMの根元から先端部に至るまで大きく開口されている形状をしていると、この接続部CNTにバンプ電極BMPを挿入した後も、各梁BMの根元に隙間が生じている。したがって、アンダーフィルを半導体チップ間に注入すると、梁BMの根元に生じている隙間を介してアンダーフィルが接続部CNTの内部にまで充填される。このため、接続部CNTとこの接続部CNTに挿入されているバンプ電極BMPとの接続強度が隙間をアンダーフィルで充填することにより向上するのである。すなわち、本実施の形態1によれば、開口部OPの輪郭形状が、空洞部CAに突き出ている梁BMの根元から先端部に至る形状を縁取る形状を有し、隣接する梁BMの間において、梁BMの根元から先端部に至るまで大きく開口されている形状をするように構成することにより、エッチング処理時間の短縮だけでなく、接続部CNTとバンプ電極BMP間の接続強度の向上も図ることができるのである。

【0056】

次に、本実施の形態1における第3特徴点について説明する。本実施の形態1における第3特徴点は、梁BMの構造に対する工夫にある。具体的に、図10に示すように、梁BMの幅は、梁BMの先端部から梁BMの根元に向って大きくなっている点に特徴がある。つまり、梁BMを、いわゆる平等強さの梁から構成する。これにより、梁BMを介して接続部CNTにバンプ電極BMPを挿入したとき、梁BMにかかる応力を均一にすることができ、梁BMの応力に対する耐性を向上させることができる。

【0057】

例えば、梁BMの幅を先端部から根元まで同じ大きさにすると、梁BMにかかる応力が根元に集中する。すると、梁BMが根元から折れてしまうおそれがある。そこで、梁BMの幅を先端部から根元に向って大きくするように梁BMを構成することにより、梁BMの根元の応力に対する耐性を向上することができる。つまり、梁BMの幅を先端部から根元に向って大きくするように構成することにより、梁BMの全体にかかる応力を均一にすることができる。この結果、梁BMの根元に過大な応力が印加されることを抑制することができ、梁BMの曲げ応力に対する耐性を向上することができる。したがって、本実施の形態1によれば、梁BMの構成をいわゆる平等強さの梁構造とする第3特徴点により、梁BMの強度を確保することができ、接続部CNTの信頼性を向上することができる。

【0058】

さらに、本実施の形態1では、梁BMの先端部や根元の形状に丸みをもたせている。これにより、梁BMに荷重が加わった場合、先端部や根元に荷重が集中することを抑制できる。なお、図10では、接続部CNTに4つの梁BMを形成している例を示しているが、これに限らず、5本や6本のように4本よりも多くてもよいし、3本や2本のように4本よりも少なくてもよい。さらには、1本の梁BMだけを形成する場合であってもよい。

【0059】

本実施の形態1における接続部CNTは上記のように構成されており、以下に、この接続部CNTとバンプ電極BMPによって、複数の半導体チップを電気的に接続しながら、3次元的に積層する接続例について説明する。

【0060】

図12は、半導体基板(下層の半導体チップ)1Sと半導体基板(上層の半導体チップ)2Sとを積層する様子を示す図である。図12において、下層の半導体基板1Sに複数の接続部CNTが形成され、上層の半導体基板2Sに複数のバンプ電極が形成されている。半導体基板1Sは矩形形状(四角形状)をしており、半導体基板1Sの周辺部(辺)に沿って、複数の接続部CNTが配列している。例えば、半導体基板1Sに形成されている複数の接続部CNTは、ペリフェラル配置で配置されているが、接続部CNTの配置は、ペリフェラル配置に限定されない。一方、半導体基板2Sも矩形形状(四角形状)をしており、半導体基板2Sの周辺部(辺)に沿って複数のバンプ電極BMPが形成されている。このバンプ電極BMPは、接続部CNTに対応するように配置されている。

【0061】

図13は、半導体基板1Sに形成した接続部CNTと、半導体基板2Sに形成したバンプ電極BMPとを接続した様子を示す断面図である。図13に示すように、半導体基板1Sに形成された接続部CNTのそれぞれに、半導体基板2Sに形成されたバンプ電極BMPのそれぞれは挿入されている。これにより、半導体基板1Sと半導体基板2Sとを電気的に接続しながら、3次元的に積層することができる。つまり、本実施の形態1では、図13に示すように、空洞部CAにバンプ電極BMPを挿入し、かつ、空洞部CAに突き出るように配置された梁BMの変形による復元力でバンプ電極BMPを固定するように構成している。このため、本実施の形態1では、半田を使用せずに、バンプ電極BMPを接続部CNTへ機械的に固定することができる。したがって、バンプ電極BMPと接続部CNTの接続に半田を使用しないので、接続部CNTおよびバンプ電極BMPの高密度化や狭ピッチ化が行なわれても、隣接する接続部CNT間や隣接するバンプ電極BMP間でのショート不良を抑制できる。言い換えれば、本実施の形態1では、バンプ電極BMPと接続部CNTとの接続に溶融した半田を使用しないために、半田ブリッジによるショート不良を抑制することができ、半導体装置の信頼性を向上することができる。

【0062】

このとき、本実施の形態1では、図10に示すように、梁BMの構成をいわゆる平等強さの梁構造とすることにより(第3特徴点)、梁BMの強度を確保することができ、接続部CNTの信頼性を向上することができる。

【0063】

さらに、半導体基板1Sと半導体基板2Sの間にはアンダーフィルUFが注入されている。本実施の形態1では、図10に示すように、開口部OPの輪郭形状が、空洞部CAに突き出ている梁BMの根元から先端部に至る形状を縁取る形状を有し、隣接する梁BMの間において、梁BMの根元から先端部に至るまで大きく開口されている形状をしていることから(第2特徴点)、接続部CNTにバンプ電極BMPを挿入した後も、各梁BMの根元に隙間が生じている。したがって、アンダーフィルUFを半導体基板1Sと半導体基板2Sとの間に注入すると、梁BMの根元に生じている隙間を介してアンダーフィルUFが接続部CNTの内部にまで充填される。このため、接続部CNTとこの接続部CNTに挿入されているバンプ電極BMPとの接続強度が向上している。

【0064】

なお、図12および図13では、半導体基板(半導体チップ)1Sと、半導体基板(半導体チップ)2Sを3次元的に積層する例について説明したが、本実施の形態1における接続部CNTとバンプ電極BMPによる接続は、半導体基板(半導体チップ)と配線基板との接続にも応用することができる。例えば、配線基板に接続部を形成し、半導体基板にバンプ電極を形成する。そして、半導体基板に形成されたバンプ電極を配線基板に形成された接続部に挿入することにより、配線基板と半導体基板とを接続することができる(フリップチップ接続)。

【0065】

次に、本実施の形態1における半導体装置の製造方法について図面を参照しながら説明する。以下に示す半導体装置の製造方法では、本実施の形態1の特徴である接続部CNTを形成する工程について説明する。

【0066】

まず、図14に示すように、半導体基板1Sの上面(主面、素子形成面)に通常の技術を使用することにより、MISFETなどの半導体素子(図示せず)を形成する。そして、半導体素子を形成した半導体素子上に層間絶縁膜ILを形成する。その後、層間絶縁膜ILの層間に多層配線(図示せず)を形成し、層間絶縁膜ILの最上層に端子TEを形成する。このとき、層間絶縁膜ILの最上層に形成されている端子TEは、層間絶縁膜ILの内部に形成されている多層配線を介して、半導体基板1Sに形成されている半導体素子と電気的に接続されている。

【0067】

次に、図15に示すように、端子TEを形成した層間絶縁膜IL上に銅膜CFを形成する。銅膜CFは、例えば、スパッタリング法を使用することにより形成することができる。この銅膜CFには、後述する工程でウェットエッチングすることにより梁の下層に空洞部を形成して接続部CNTを形成するため、梁の可動範囲は充分に得られるように銅膜CFの膜厚が設定される。例えば、銅膜CFの膜厚は、約10μmである。銅膜CFの形成方法は、スパッタリング法のほか、スパッタリング法で0.3μm〜1μmの銅膜CFを形成した後、電解めっき法で10μmの厚さの銅膜CFを形成することもできる。

【0068】

続いて、図16に示すように、銅膜CF上にニッケル膜NFを形成する。ニッケル膜NFは、例えば、スパッタリング法を使用することにより形成することができる。このニッケル膜NFは、後述する梁を構成する部材であり、ニッケル膜NFの厚さによって梁の剛性、つまり、梁のばね定数が決定される。梁はバンプ電極を挿入した際、梁の復元力によって充分な接合力を得る必要があり、この梁の復元力は、ニッケル膜NFの膜厚によって決定される。したがって、ニッケル膜NFの膜厚は、例えば、5μmである。

【0069】

その後、図17に示すように、ニッケル膜NF上に金膜AFを形成する。金膜AFは、例えば、スパッタリング法を使用することにより形成することができる。金膜AFは、梁とバンプ電極との接触抵抗を低抵抗とするために設けられる膜であるため、金膜AFの膜厚は薄くてよい。例えば、金膜AFの膜厚は、約0.2μmとする。

【0070】

次に、図18に示すように、金膜AF上にレジスト膜FR1を塗布した後、このレジスト膜FR1に対して露光・現像処理を施すことにより、レジスト膜FR1に開口部OPを形成する。そして、図19に示すように、開口部OPから露出する金膜AFを除去する。金膜AFを除去するには、例えば、ミリング法を使用することもできるし、その他、ドライエッチング法やAuエッチング溶液を使用したウェットエッチングを使用することもできる。

【0071】

続いて、図20に示すように、開口部OPから露出するニッケル膜NFを除去する。ニッケル膜NFの除去は、例えば、ミリング法を使用することにより実施できる。なお、レジスト膜FR1に形成された開口部OPから露出する金膜AFとニッケル膜NFを除去する工程は、一括して行なうことができる。

【0072】

次に、図21に示すように、銅のエッチャントによるウェットエッチングを実施することにより、開口部OPから露出する銅膜CFを除去する。銅膜CFをウェットエッチングすることにより、銅膜CFに空洞部CAが形成される。ウェットエッチングは、等方性エッチングであるため、開口部OPの直下にある銅膜CFだけでなく、横方向に回り込むようにエッチングが進行し、空洞部CAが形成される。

【0073】

このとき、開口部OPの輪郭形状が図10に示すような形状となっており、開口部OPから露出する下地膜(銅膜CF)の表面積が大きくなる。この場合、エッチング液の循環もよくなり、エッチング速度が速くなる利点がある。さらに、大きな露出領域の各領域からエッチングが進行する。このため、空洞部CAをより少ないエッチング量で形成することができる。このように本実施の形態1によれば、開口部OPの輪郭形状が、図10に示す形状をしていることから(第2特徴点)、空洞部CAを形成するエッチング量を低減することができるとともに、エッチング速度を速くすることができる。

【0074】

空洞部CAは開口部OPを内包し、かつ、空洞部CAの大きさが開口部OPの大きさよりも大きくなる。このことから、空洞部CAの上部にニッケル膜NFおよび金膜AFよりなる梁BMが形成される。

【0075】

その後、図22に示すように、アセトン洗浄や酸素を使用したアッシングにより、レジスト膜FR1を除去する。このようにして、半導体基板1Sに梁構造を有する接続部CNTを形成することができる。

【0076】

本実施の形態1による説明の最後に先行技術文献との差異について説明する。まず、先行技術文献1(特開平10−163267号公報)との差異について説明する。先行技術文献1には、基材のパッド上に第1メッキ層と第2メッキ層からなる導電部を形成し、導電部を構成する第2メッキ層の先端部が突出して突出部となっている構造が記載されている。そして、この導電部にバンプ電極を強制的に挿入し、導電部の突出部をバンプ電極のエッジに係止させることにより導電部とバンプ電極とを接続するとしている。

【0077】

ここで、本実施の形態1における第1特徴点は、例えば、図3に示すように、空洞部CAにバンプ電極BMP1を挿入し、かつ、空洞部CAに突き出るように配置された梁BMの変形による復元力でバンプ電極BMP1を固定するように構成する点にある。つまり、本実施の形態1では、梁BMの復元力によってバンプ電極BMP1を固定する構造であるのに対し、先行技術文献1に記載された技術は、導電部の突出部にバンプ電極のエッジを係止させることにより固定する点で相違する。そして、この固定方法の相違から、本実施の形態1では、接合するバンプの形状にあまり制限なく適用可能であるのに対し、先行技術文献1では、接合するバンプの形状が2段形状となってエッジが突出した形状である必要がある。さらに、本実施の形態1では、接続部の断面構造だけでなく平面構造にも特徴がある。具体的に本実施の形態1の第2特徴点は、図10に示すように、開口部OPの輪郭形状が、空洞部CAに突き出ている梁BMの根元から先端部に至る形状を縁取る形状を有し、隣接する梁BMの間において、梁BMの根元から先端部に至るまで大きく開口されている形状をしている点にある。そして、特に、開口部OPの平面上の面積は、梁BMの平面上の面積よりも大きくなっている。また、本実施の形態1の第3特徴点は、図10に示すように、梁BMの幅を、梁BMの先端部から梁BMの根元に向って大きくする点にある。このような本実施の形態1の平面構造における特徴点(第2特徴点や第3特徴点)について、先行技術文献1には記載も示唆もされていない。したがって、先行技術文献1から本実施の形態1における技術的思想を想到するのは当業者といえども困難である。

【0078】

続いて、先行技術文献2(特開2004−12357号公報)において、スパイラル状接触子は、絶縁基板上に球状接続端子との接触の際に、球状接続端子の形状に対応して変形可能となっており、半導体デバイスとの電気的な接続を行うように構成されている。このとき、スパイラル状接触子の渦巻き部、幅が一定で、先端から根元に近づくに従って厚みが厚くなるとしている。

【0079】

ここで、本実施の形態1における第1特徴点は、例えば、図3に示すように、空洞部CAにバンプ電極BMP1を挿入し、かつ、空洞部CAに突き出るように配置された梁BMの変形による復元力でバンプ電極BMP1を固定するように構成する点にある。したがって、本実施の形態1では、梁BMの復元力によってバンプ電極BMP1を固定する構造であるのに対し、先行技術文献2に記載された技術は、スパイラル状接触子の変形により固定する点で相違する。さらに、先行技術文献2には、本実施の形態1の平面構造における特徴点(第2特徴点)について、記載も示唆もされていない。したがって、先行技術文献2から本実施の形態1における技術的思想を想到するのは当業者といえども困難である。

【0080】

次に、先行技術文献3(特開2004−354179号公報)には、スリットが形成されたコンタクト部が記載されている。これにより、半田ボールの接続時に、この接続に伴いコンタクト部が変位する。このため、半田ボールとコンタクト部との接触面積を増大させることができ、コンタクト部と半田ボールとを確実に電気的に接続することができるとしている。

【0081】

しかし、先行技術文献3に記載されたスリットを有するコンタクト部は、本実施の形態1の接続部CNTと異なり、開口部OPの輪郭形状が、空洞部CAに突き出ている梁BMの根元から先端部に至る形状を縁取る形状をしておらず、隣接する梁BMの間において、梁BMの根元から先端部に至るまで大きく開口されていない。つまり、先行技術文献3のコンタクト部では、スリットが形成されているだけである。これに対し、本実施の形態1では、開口部OPの輪郭形状が、空洞部CAに突き出ている梁BMの根元から先端部に至る形状を縁取る形状を有し、隣接する梁BMの間において、梁BMの根元から先端部に至るまで大きく開口されている形状をしていることから(第2特徴点)、空洞部CAを形成するエッチング量を低減することができるとともに、エッチング速度を速くすることができる利点を有するのである。特に、開口部OPの平面上の面積は、梁BMの平面上の面積よりも大きくなっていることにより顕著な効果が得られるのである。さらに、本実施の形態1の接続部CNTのように、隣接する梁BMの間において、梁BMの根元から先端部に至るまで大きく開口されている形状をしていると、この接続部CNTにバンプ電極BMPを挿入した後も、各梁BMの根元に隙間が生じている。したがって、アンダーフィルを半導体チップ間に注入すると、梁BMの根元に生じている隙間を介してアンダーフィルが接続部CNTの内部にまで充填される。このため、接続部CNTとこの接続部CNTに挿入されているバンプ電極BMPとの接続強度が向上する。

【0082】

このような本実施の形態1の平面構造における特徴点(第2特徴点)について、先行技術文献3には記載も示唆もされていない。したがって、先行技術文献3から本実施の形態1における技術的思想を想到するのは当業者といえども困難である。以上のことから、本実施の形態1の平面構造における第2特徴点については、先行技術文献1〜3のいずれにも記載も示唆もされていないことから、先行技術文献1〜3を組み合わせても、本実施の形態1における技術的思想を想到することは困難である。

【0083】

(実施の形態2)

本実施の形態2では、半導体チップを貫通する貫通電極と本発明による接続部をともに形成する例について説明する。例えば、携帯電話機などのモバイル機器に搭載されるマイコンチップに貫通電極と本発明の接続部を形成する例について説明する。

【0084】

図23は、本実施の形態2における半導体基板(半導体チップ)1Sに形成された接続部CNTと貫通電極TREを示す図である。図23に示すように、半導体基板1Sに形成されている接続部CNTと貫通電極TREは、例えば、並ぶように配置されている。

【0085】

図24は、図23の貫通電極TREと接続部CNTを含む一断面で切断した断面図である。図24において、半導体基板1Sの下面(主面、素子形成面)には、MISFETなどの半導体素子(図示せず)が形成されており、この半導体素子を形成した半導体基板1S上に層間絶縁膜ILが形成されている。この層間絶縁膜ILの内部には多層配線が形成されている。

【0086】

以下に、貫通電極TREの構成について説明する。まず、層間絶縁膜IL上にはパッドPDが形成されており、このパッドPD上にバンプ電極BMPが形成されている。半導体基板1Sの裏面(上面)から層間絶縁膜の内部まで達するように孔H1が形成されており、孔H1の底面の層間絶縁膜ILには、孔H1よりも小径の孔H2がパッドPDに達するまで形成されている。孔H1と孔H2の内壁(側面および底面)と半導体基板1Sの裏面の一部には、順次、銅膜CF、ニッケル膜NF、金膜AFが形成されている。これにより、銅膜CF,ニッケル膜NFおよび金膜AFはパッドPDと電気的に接続されている。

【0087】

次に、接続部CNTの構成について説明する。接続部CNTは、半導体基板1Sの裏面に形成された金膜AFおよびニッケル膜NFを貫通するように形成された開口部OPを有している。そして、この開口部OPから露出する銅膜CFが除去されて、銅膜CFに空洞部CAが形成されている。このとき、銅膜CFに形成されている空洞部CAの大きさは、ニッケル膜NFおよび金膜AFに形成されている開口部OPの大きさよりも大きくなっている。したがって、空洞部CA上には、ニッケル膜NFおよび金膜AFからなる梁BMが突き出た構造となっている。つまり、本実施の形態2における接続部CNTは、銅膜CF、ニッケル膜NFおよび金膜AFを構成要素とし、銅膜CFに空洞部CAが形成され、かつ、ニッケル膜NFおよび金膜AFに開口部OPが形成された構造をしている。そして、空洞部CAが開口部OPを内包し、かつ、空洞部CAの大きさが開口部OPの大きさよりも大きくなっているので、空洞部CAの上部にニッケル膜NFおよび金膜AFよりなる梁BMが形成されていることになる。このように構成された接続部CNTと貫通電極TREは電気的に接続されている。

【0088】

本実施の形態2における半導体装置は上記のように構成されており、以下にその製造方法について図面を参照しながら説明する。まず、図25に示すように、半導体基板1Sの下面(主面、素子形成面)に通常の技術を使用することにより、MISFETなどの半導体素子(図示せず)を形成する。そして、半導体素子を形成した半導体素子上に層間絶縁膜ILを形成する。その後、層間絶縁膜ILの層間に多層配線(図示せず)を形成し、層間絶縁膜ILの最上層にパッドPDを形成する。このとき、層間絶縁膜ILの最上層に形成されているパッドPDは、層間絶縁膜ILの内部に形成されている多層配線を介して、半導体基板1Sに形成されている半導体素子と電気的に接続されている。

【0089】

この半導体基板(半導体ウェハ)1Sに貫通電極を形成するため、例えば、10μm〜50μm程度まで半導体基板1Sを薄型化し、貫通電極の形成難易度を低減する。ただし、半導体基板1Sの薄型化によって、半導体基板1Sの強度低下および半導体基板1Sの反りによる歩留まり低下が生じるおそれがある。

【0090】

そこで、本実施の形態2では、図26に示すように、半導体基板1Sの下面(主面、素子形成面)に接着材BAを塗布し、この接着材BAにより、例えば、ガラスや石英やシリコンからなる支持基板SBを貼り合せる。このように支持基板SBを半導体基板1Sに貼り付けることで、薄型化後の半導体基板1Sの強度低下および反りを抑制することができる。また、接着材BAは、半導体基板1Sに形成された半導体素子を保護する機能を有する。

【0091】

次に、図27に示すように、半導体基板1Sの裏面(上面)に対してバックグラインド処理を実施することにより、半導体基板1Sの厚さを薄くする。半導体基板1Sの裏面をバックグラインドする方法としては、研削や研磨する方法がある。なお、バックグラインドした後の平坦性が半導体基板1Sの裏面に形成する接続部の精度に影響するため、半導体基板1Sの裏面をバックグラインドした後、ドライポリッシュやエッチング、あるいは、化学的機械的研磨(CMP:Chemical Mechanical Polishing)を実施することが望ましい。

【0092】

続いて、図28に示すように、半導体基板1Sの裏面(上面)上にレジスト膜FR2を塗布する。そして、塗布したレジスト膜FR2に対して露光・現像処理を施すことにより、レジスト膜FRに開口部OP2を形成する。レジスト膜FR2を塗布する方法としては、例えば、スピナー塗布法がある。なお、開口部OPの形成位置は、赤外分光法により半導体基板1Sの素子形成面に形成されているデバイスパターンを確認して行なう方法や、両面マスクアライナを用いて行なう方法がある。

【0093】

次に、図29に示すように、開口部OP2を形成したレジスト膜FR2をマスクにしたエッチングにより孔H1を形成する。具体的には、ICP−RIE(Inductively coupled plasma Reactive ion etching)を使用することにより異方性エッチングを行ない、孔H1を形成する。ここで、例えば、プロセスガスとしてSF6とC4H8を使用している。通常、シリコンのドライエッチングでは、酸化シリコン膜をマスクとしてシリコンをエッチングする。このため、SF6とC4H8によるエッチングでは、酸化シリコン膜を主成分とする層間絶縁膜ILでエッチングがストップする。このときの孔H1の深さは、シリコンよりなる半導体基板1Sの膜厚によって決定される。

【0094】

その後、プロセスガスをSF6とC4H8からC3H8、Ar、CHF4の混合ガスに代えて、層間絶縁膜ILの加工(エッチング)を進める。この際、新たなマスクの形成は行なわない。この結果、レジスト膜FR2と半導体基板1Sをマスクとして孔H1の底部の層間絶縁膜ILの薄膜化が進む。このとき、層間絶縁膜ILをエッチングし続けることにより、パッドPDに達する孔H1を形成してもよいが、パッドPDに接する層間絶縁膜ILがなくなりパッドPDの強度が低下する。そこで、本実施の形態2では、層間絶縁膜ILの表面下部からパッドPDに達するまでの範囲で半導体基板1Sに形成した孔H1よりも小径の孔を形成する方法を採用する。

【0095】

次に、孔H1を形成した後、図30に示すように、有機溶剤や酸素アッシングによってレジスト膜FR2を除去する。そして、図31に示すように、孔H1の内部を含む半導体基板1Sの裏面の全面に絶縁膜IF1を形成する。この絶縁膜IF1は、例えば、酸化シリコン膜、窒化シリコン膜、ポリイミド樹脂膜などからなり、例えば、CVD(Chemical Vapor Deposition)法により形成することができる。絶縁膜IF1は、孔H1の内部において、孔H1の内壁および底面に沿ってこれらの面を覆うように形成される。

【0096】

続いて、図32に示すように、孔H1の内部を含む半導体基板1Sの裏面にレジスト膜FR3を塗布する。レジスト膜FR3は、例えば、スピナーによる塗布やスプレーによる塗布などによって形成される。スピナーで塗布する場合は、孔H1を埋め込むため、5μm〜30μmの膜厚で塗布できるレジスト膜FR3を使用することが望ましい。さらに、レジスト膜FR3の中に気泡が残存していると、フォトリソグラフィ工程での露光が難しくなりパターン不良が発生する。このため、真空脱泡により気泡を除去することが望ましい。スプレーで塗布する場合は、スピナーで塗布する場合と異なり、孔H1に沿ってレジスト膜FR3を塗布する。このため、孔H1内部で偏ったレジスト形状となりやすい。その後、孔H1の内面に塗布したレジスト膜FR3のパターニングを行ない、孔H1の底面に開口部OP3を形成する。このとき、孔H1の内壁を保護するレジスト膜FR3がパターニングされないように、開口部OP3の開口径を小さく形成する。

【0097】

その後、図33に示すように、開口部OP3から露出する絶縁膜IF1と層間絶縁膜ILの残りをすべてエッチングすることにより、孔H2を形成する。これにより、孔H2の底部にパッドPDが露出する。絶縁膜IF1および層間絶縁膜ILのエッチングには、例えば、CHF3やC4H8を主成分とする混合ガスを使用する。そして、図34に示すように、有機溶剤や酸素アッシングにより、パターニングされたレジスト膜FR3を除去する。

【0098】

次に、図35に示すように、孔H1および孔H2内を含む半導体基板1Sの裏面上に銅膜CFを形成する。銅膜CFは、例えば、スパッタリング法を使用することにより形成することができる。この銅膜CFには、後述する工程でウェットエッチングすることにより梁の下層に空洞部を形成して接続部CNTを形成するため、梁の可動範囲は充分に得られるように銅膜CFの膜厚が設定される。例えば、銅膜CFの膜厚は、約10μmである。銅膜CFの形成方法は、スパッタリング法のほか、スパッタリング法で0.3μm〜1μmの銅膜CFを形成した後、電解めっき法で10μmの厚さの銅膜CFを形成することもできる。

【0099】

続いて、図36に示すように、銅膜CF上にニッケル膜NFを形成する。ニッケル膜NFは、例えば、スパッタリング法を使用することにより形成することができる。このニッケル膜NFは、後述する梁を構成する部材であり、ニッケル膜NFの厚さによって梁の剛性、つまり、梁のばね定数が決定される。梁はバンプ電極を挿入した際、梁の復元力によって充分な接合力を得る必要があり、この梁の復元力は、ニッケル膜NFの膜厚によって決定される。したがって、ニッケル膜NFの膜厚は、例えば、5μmである。

【0100】

その後、図37に示すように、ニッケル膜NF上に金膜AFを形成する。金膜AFは、例えば、スパッタリング法を使用することにより形成することができる。金膜AFは、梁とバンプ電極との接触抵抗を低抵抗とするために設けられる膜であるため、金膜AFの膜厚は薄くてよい。例えば、金膜AFの膜厚は、約0.2μmとする。

【0101】

次に、図38に示すように、金膜AF上にレジスト膜FR4を塗布する。レジスト膜FR4は、例えば、スピナーによる塗布やスプレーによる塗布によって、半導体基板1Sの裏面を覆うように形成することができる。このレジスト膜FR4に対して露光・現像処理を施すことにより、レジスト膜FR4に電極パターンおよび開口部OPを形成する。そして、図39に示すように、開口部OPから露出する金膜AFを除去する。金膜AFを除去するには、例えば、ミリング法を使用することもできるし、その他、ドライエッチング法やAuエッチング溶液を使用したウェットエッチングを使用することもできる。Auエッチング溶液としては、ヨウ素とヨウ化アンモニウムの混合液が考えられる。

【0102】

続いて、図40に示すように、開口部OPから露出するニッケル膜NFを除去する。ニッケル膜NFの除去は、例えば、ミリング法を使用することにより実施できる。なお、レジスト膜FR4に形成された開口部OPから露出する金膜AFとニッケル膜NFを除去する工程は、一括して行なうことができる。

【0103】

次に、図41に示すように、銅のエッチャントによるウェットエッチングを実施することにより、開口部OPから露出する銅膜CFを除去する。銅膜CFをウェットエッチングすることにより、銅膜CFに空洞部CAが形成される。ウェットエッチングは、等方性エッチングであるため、開口部OPの直下にある銅膜CFだけでなく、横方向に回り込むようにエッチングが進行し、空洞部CAが形成される。

【0104】

このとき、開口部OPの輪郭形状が図23に示すような形状となっており、開口部OPから露出する下地膜(銅膜CF)の表面積が大きくなる。この場合、エッチング液の循環もよくなり、エッチング速度が速くなる利点がある。さらに、大きな露出領域の各領域からエッチングが進行する。このため、空洞部CAをより少ないエッチング量で形成することができる。このように本実施の形態1によれば、開口部OPの輪郭形状が、図23に示す形状をしていることから(第2特徴点)、空洞部CAを形成するエッチング量を低減することができるとともに、エッチング速度を速くすることができる。

【0105】

空洞部CAは開口部OPを内包し、かつ、空洞部CAの大きさが開口部OPの大きさよりも大きくなる。このことから、空洞部CAの上部にニッケル膜NFおよび金膜AFよりなる梁BMが形成される。

【0106】

その後、図42に示すように、アセトン洗浄や酸素を使用したアッシングにより、レジスト膜FR4を除去する。これにより、半導体基板1Sni貫通電極TREと接続部CNTを形成することができる。

【0107】

次に、図43に示すように、半導体基板1Sから支持基板SBを引き剥がす。例えば、熱可塑性の接着材BAであれば、半導体基板1Sと支持基板SBを加熱することにより、半導体基板1Sから支持基板SBを引き剥がす。

【0108】

続いて、半導体基板1Sをブレードダイシングによって半導体チップへ個片化する。半導体チップへの個片化は、支持基板SBに半導体基板1Swo貼り付けた状態でも実施できるが、支持基板SBごと切断してしまう。ハンドリングは難しくなるが、支持基板SBを半導体基板1Sから剥がしてダイシングすることにより、支持基板SBの再利用が可能となる。

【0109】

最後に、図44に示すように、半導体基板1Sの主面(素子形成面、下面)に形成されているパッド上にバンプ電極BMPを形成する。バンプ電極BMPを形成する方法としては、例えば、スタッドバンプ法がある。その他の形成方法としては、ソルダペーストバンプ法、めっき法、あるいは、蒸着法などがある。以上のようにして、貫通電極TREと接続部CNTを形成した半導体装置を製造することができる。

【0110】

次に、貫通電極TREと接続部CNTを形成した複数の半導体チップを電気的に接続しながら、3次元的に積層する接続例について説明する。

【0111】

図45は、例えば、マイコンチップから構成される半導体チップCHP1と、SDRAMを形成した半導体チップCHP2とを積層する前の様子を示す図である。図45において、配線基板WB上に半導体チップCHP1が搭載され、この半導体チップCHP1上に再配線を行なうインターポーザIPを介して半導体チップCHP2が搭載される。半導体チップCHP1は矩形形状(四角形状)をしており、半導体チップCHP1の周辺部(辺)に沿って貫通電極と接続部CNT(CHP1)が形成されている。同様に、インターポーザIPも矩形形状(四角形状)をしており、インターポーザIPの周辺部(辺)に沿って貫通電極(バンプ電極BMP(IP))と接続部CNT(IP)が形成されている。そして、半導体チップCHP2も矩形形状(四角形状)をしており、半導体チップCHP2の周辺部(辺)に沿って貫通電極(バンプ電極BMP(CHP2))と接続部が形成されている。例えば、半導体チップCHP1、インターポーザIPおよび半導体チップCHP2に形成されている複数の貫通電極(バンプ電極BMP(IP)、バンプ電極BMP(CHP2))と接続部CNT(CHP1)や接続部CNT(IP)は、ペリフェラル配置で配置されているが、これらの配置はペリフェラル配置に限定されない。このように構成された半導体チップCHP1、インターポーザIPおよび半導体チップCHP2は、例えば、半導体チップCHP1に形成された接続部CNT(CHP1)へインターポーザIPに形成されたバンプ電極BMP(IP)を挿入し、かつ、インターポーザIPに形成された接続部CNT(IP)へ半導体チップCHP2に形成されたバンプ電極BMP(CHP2)を挿入することで、半導体チップCHP1、インターポーザIPおよび半導体チップCHP2を電気的に接続しながら、3次元的に積層することができる。

【0112】

図46は、配線基板WB上に半導体チップCHP1を搭載し、半導体チップCHP1上にインターポーザIPを介して半導体チップCHP2を搭載した積層構造を示す断面図である。図46に示すように、配線基板WBに形成された端子TEに、半導体チップCHP1のバンプ電極BMP(CHP1)が接続されている。そして、半導体チップCHP1に形成された接続部CNT(CHP1)に、インターポーザIPに形成されたバンプ電極BMP(IP)が挿入されている。さらに、インターポーザIPに形成された接続部CNT(IP)に半導体チップCHP2のバンプ電極BMP(CHP2)が挿入されている。これにより、配線基板WB,半導体チップCHP1、インターポーザIPおよび半導体チップCHP2を電気的に接続しながら、3次元的に積層することができる。

【0113】

本実施の形態2では、接続部にバンプ電極を挿入し、かつ、接続部を構成する空洞部に突き出るように配置された梁の変形による復元力でバンプ電極を固定するように構成している。このため、本実施の形態2では、半田を使用せずに、バンプ電極を接続部へ機械的に固定することができる。したがって、バンプ電極と接続部の接続に半田を使用しないので、接続部およびバンプ電極の高密度化や狭ピッチ化が行なわれても、隣接する接続部間や隣接するバンプ電極間でのショート不良を抑制できる。言い換えれば、本実施の形態2では、バンプ電極と接続部との接続に溶融した半田を使用しないために、半田ブリッジによるショート不良を抑制することができ、半導体装置の信頼性を向上することができる。

【0114】

このとき、本実施の形態2では、梁の構成をいわゆる平等強さの梁構造とすることにより(第3特徴点)、梁の強度を確保することができ、接続部の信頼性を向上することができる。

【0115】

さらに、配線基板WBと半導体チップCHP1の間、半導体チップCHP1とインターポーザIPの間、および、インターポーザIPと半導体チップCHP2の間には、アンダーフィルUFが注入されている。本実施の形態2では、接続部を構成する開口部の輪郭形状が、空洞部に突き出ている梁の根元から先端部に至る形状を縁取る形状を有し、隣接する梁の間において、梁の根元から先端部に至るまで大きく開口されている形状をしていることから(第2特徴点)、接続部にバンプ電極を挿入した後も、各梁の根元に隙間が生じている。したがって、アンダーフィルUFを注入すると、梁の根元に生じている隙間を介してアンダーフィルUFが接続部の内部にまで充填される。このため、接続部とこの接続部に挿入されているバンプ電極との接続強度を向上することができる。

【0116】

以上、本発明者によってなされた発明をその実施の形態に基づき具体的に説明したが、本発明は前記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることは言うまでもない。

【産業上の利用可能性】

【0117】

本発明は、半導体装置を製造する製造業に幅広く利用することができる。

【符号の説明】

【0118】

1S 半導体基板

2S 半導体基板

AF 金膜

BM 梁

BM2 梁

BMP バンプ電極

BMP1 バンプ電極

BMP2 バンプ電極

BMP3 バンプ電極

BMP(IP) バンプ電極

BMP(CHP1) バンプ電極

BMP(CHP2) バンプ電極

CA 空洞部

CF 銅膜

CHP1 半導体チップ

CHP2 半導体チップ

CNT 接続部

CNT2 接続部

CNT(CHP1) 接続部

CNT(IP) 接続部

CON 導体膜

FR1 レジスト膜

FR2 レジスト膜

FR3 レジスト膜

FR4 レジスト膜

H1 孔

H2 孔

IF1 絶縁膜

IL 層間絶縁膜

IL2 層間絶縁膜

IP インターポーザ

NF ニッケル膜

OP 開口部

OPT 開口部

OP2 開口部

OP3 開口部

PD パッド

SL スリット

TE 端子

TRE 貫通電極

UF アンダーフィル

WB 配線基板

【技術分野】

【0001】

本発明は、半導体装置およびその製造方法に関し、特に、バンプ電極によって半導体チップ間あるいは半導体チップと配線基板とを電気的に接続する半導体装置およびその製造に適用して有効な技術に関する。

【背景技術】

【0002】

特開平10−163267号公報(特許文献1)には、加熱工程を不要にして、バンプ付きワークのバンプを基板のパッド上に簡単に固着でき、さらにはパッドやバンプの高密度・ファイン化にも対応できるバンプ付きワークの実装方法および実装基板を提供することを目的とする技術が記載されている。具体的には、基材のパッド上に第1メッキ層と第2メッキ層から成る導電部を形成する。バンプ付きワークのバンプの膨大部を導電部の孔部に強制的に嵌合し、導電部の突出部を膨大部のエッジに係止させる。これにより、バンプが孔部から抜け出さないようにするとともに、導電部にしっかり接触させることができるとしている。

【0003】

特開2004−12357号公報(特許文献2)には、挟ピッチ化が進行する半導体デバイスや超小型のペアチップに対応可能な技術が記載されている。具体的には、半導体デバイスの接続端子と電気的に接続し、平面視してスパイラル形状を有するスパイラル状接触子を絶縁基板上に備えている。そして、スパイラル状接触子は、絶縁基板上に球状接続端子との接触の際に、球状接続端子の形状に対応して変形可能となっており、半導体デバイスとの電気的な接続を行うように構成されている。このとき、スパイラル状接触子の渦巻き部、幅が一定で、先端から根元に近づくに従って厚みが厚くなるとしている。

【0004】

特開2004−354179号公報(特許文献3)には、電子部品を装着してテストを行なうテスト用ソケットに関し、低コスト化および信頼性の向上を図ることを目的とする技術が記載されている。具体的には、半導体装置が装着され、この半導体装置に対してテストを行なうテスト用ソケットにおいて、層間接続を行なうためのビアが形成されると共に半導体装置の半田ボールが接続される位置に貫通孔が形成されてなる基材層を複数積層してなる基板部と、この基板部に配設されると共にビアと電気的に接続され、かつ、半導体装置と電気的に接続される電極部が形成されたコンタクト部とを具備するとしている。そして、このコンタクト部にはスリットが形成されている。これにより、半田ボールの接続時に、この接続に伴いコンタクト部が変位する。このため、半田ボールとコンタクト部との接触面積を増大させることができ、コンタクト部と半田ボールとを確実に電気的に接続することができるとしている。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開平10−163267号公報

【特許文献2】特開2004−12357号公報

【特許文献3】特開2004−354179号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

携帯電話機やデジタルカメラなどのモバイル機器には、1つの半導体パッケージの内部に複数の半導体チップを積層して搭載する、いわゆるSIP(System In Package)が広く使用されている。これは、半導体チップを積層して配置することにより、半導体チップを平面上に並べて配置する(平置きする)場合に比べて、実装面積を小さくすることができ、同一の実装面積で多数の半導体チップを搭載できるからである。すなわち、モバイル機器には持ち運びの利便性の観点から小型化が要求されており、この小型化を実現するために、実装面積を小さくすることができるSIPが使用されるのである。

【0007】

SIPでは、半導体チップを積層するが、積層された半導体チップ間の電気的な接続は、例えば、下層に配置される半導体チップに形成された端子と、上層に配置される半導体チップに形成されたバンプ電極とを半田で電気的に接続する。

【0008】

近年では、半導体装置の小型化のために、半導体チップ間を接続する接続部の高密度・狭ピッチ化が要求されており、高密度・狭ピッチに配置された端子とバンプ電極とを半田で接続する必要がある。しかし、半田を使用した接続では、半田を加熱して溶融(リフロー)させる工程が必要である。このとき、端子やバンプ電極から構成される接続部の高密度化や狭ピッチ化が進むと、半田の加熱溶融時に半田が流動化するため、隣り合う位置に配置されている端子上に形成されている半田同士が接合してショート不良が発生するという問題点がある。

【0009】

以上では、SIPを例に挙げて、積層された半導体チップ間の接続に半田を使用する場合を説明したが、半導体チップを積層するSIPに限らず、例えば、半導体チップと配線基板とをフリップチップ接続する場合も同様の問題が発生する。すなわち、半導体チップに形成されているバンプ電極を、配線基板に形成されている端子に半田を使用して接続する場合も、バンプ電極および端子の高密度化や狭ピッチ化に伴って、半田を介した端子間のショート不良が問題となる。

【0010】

本発明の目的は、バンプ電極によって半導体チップ間あるいは半導体チップと配線基板とを電気的に接続する半導体装置において、特に、接続部の高密度化や狭ピッチ化が進んでも、接続不良の発生を低減できる技術を提供することにある。

【0011】

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

【課題を解決するための手段】

【0012】

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、次のとおりである。

【0013】

代表的な実施の形態による半導体装置は、(a)第1基板と、(b)前記第1基板上に形成され、かつ、パターニングされた第1導体膜と、(c)前記第1導体膜に形成された空洞部と、(d)前記第1導体膜上に形成され、かつ、一部が前記空洞部に突き出るようにパターニングされた第2導体膜と、(e)前記第2導体膜に形成された開口部とを備える。そして、平面的に前記開口部が前記空洞部に内包され、かつ、前記開口部と前記空洞部が一体化され、かつ、前記第2導体膜のうち前記空洞部に突き出た部分が梁として機能する。このとき、前記開口部の輪郭形状は、前記空洞部に突き出ている前記梁の根元から先端部に至る形状を縁取る形状を有し、前記開口部の平面上の面積は、前記梁の平面上の面積よりも大きいことを特徴とするものである。

【0014】

また、代表的な実施の形態による半導体装置は、(a)第1半導体基板と、(b)前記第1半導体基板の裏面から前記裏面とは反対側の素子形成面に達する孔と、(c)前記孔内を含む前記第1半導体基板の前記裏面に形成され、かつ、パターニングされた第1導体膜とを備える。そして、(d)前記第1半導体基板の前記裏面に形成されている前記第1導体膜に形成された空洞部と、(e)前記第1導体膜上に形成され、かつ、一部が前記空洞部に突き出るようにパターニングされた第2導体膜と、(f)前記第2導体膜に形成された開口部とを備える。このとき、平面的に前記開口部が前記空洞部に内包され、かつ、前記開口部と前記空洞部が一体化され、かつ、前記第2導体膜のうち前記空洞部に突き出た部分が梁として機能する。そして、前記開口部の輪郭形状は、前記空洞部に突き出ている前記梁の根元から先端部に至る形状を縁取る形状を有し、前記開口部の平面上の面積は、前記梁の平面上の面積よりも大きいことを特徴とするものである。

【0015】

さらに、代表的な実施の形態による半導体装置の製造方法は、(a)第1基板の第1面上に第1導体膜を形成する工程と、(b)前記第1導体膜上に第2導体膜を形成する工程と、(c)前記第2導体膜を貫通する開口部を形成する工程と、(d)前記開口部をエッチング孔として前記第1導体膜をウェットエッチングすることにより、前記第1導体膜に空洞部を形成する工程とを備える。そして、平面的に前記開口部が前記空洞部に内包され、かつ、前記開口部と前記空洞部が一体化され、かつ、前記第2導体膜のうち前記空洞部に突き出た部分が梁となる。ここで、前記開口部の輪郭形状は、前記空洞部に突き出ている前記梁の根元から先端部に至る形状を縁取る形状を有し、前記開口部の平面上の面積は、前記梁の平面上の面積よりも大きいことを特徴とするものである。

【0016】

また、代表的な実施の形態による半導体装置の製造方法は、(a)第1半導体基板の裏面から前記裏面とは反対側の素子形成面に形成された電極に達する孔を形成する工程と、(b)前記孔内を含む前記第1半導体基板の前記裏面上に第1導体膜を形成する工程と、(c)前記第1導体膜上に第2導体膜を形成する工程とを備える。そして、(d)前記第2導体膜をパターニングすることにより、前記第1半導体基板の前記裏面に形成されている前記第2導体膜に開口部を形成する工程と、(e)前記開口部をエッチング孔として前記第1導体膜をウェットエッチングすることにより、前記第1導体膜に空洞部を形成する工程とを備える。ここで、平面的に前記開口部が前記空洞部に内包され、かつ、前記開口部と前記空洞部が一体化され、かつ、前記第2導体膜のうち前記空洞部に突き出た部分が梁となる。このとき、前記開口部の輪郭形状は、前記空洞部に突き出ている前記梁の根元から先端部に至る形状を縁取る形状を有し、前記開口部の平面上の面積は、前記梁の平面上の面積よりも大きいことを特徴とするものである。

【発明の効果】

【0017】

本願において開示される発明のうち、代表的なものによって得られる効果を簡単に説明すれば以下のとおりである。

【0018】

バンプ電極によって半導体チップ間あるいは半導体チップと配線基板とを電気的に接続する半導体装置において、接続不良の発生を低減できる。

【図面の簡単な説明】

【0019】

【図1】本発明の実施の形態1における半導体チップに形成されている接続部の構成を示す断面図である。

【図2】接続部を形成した半導体チップと、バンプ電極を形成した半導体チップとを相対させた断面図である。

【図3】接続部とバンプ電極との接続状態の一例を示す断面図である。

【図4】接続部を形成した半導体チップと、バンプ電極を形成した半導体チップとを相対させた断面図である。

【図5】接続部とバンプ電極との接続状態の他の一例を示す断面図である。

【図6】接続部を形成した半導体チップと、バンプ電極を形成した半導体チップとを相対させた断面図である。

【図7】接続部とバンプ電極との接続状態のさらに他の一例を示す断面図である。

【図8】接続部の位置と端子の位置とが平面的に重なるように配置される例を示す断面図である。

【図9】接続部を構成する主要な構成要素の寸法と、バンプ電極の先端部の寸法を示す図である。

【図10】接続部の平面構造を示す図である。

【図11】比較例の接続部の構造を示す図である。

【図12】下層の半導体チップと上層の半導体チップとを積層する様子を示す図である。

【図13】下層の半導体チップと上層の半導体チップとを積層する様子を示す断面図である。

【図14】実施の形態1における半導体装置の製造工程を示す断面図である。

【図15】図14に続く半導体装置の製造工程を示す断面図である。

【図16】図15に続く半導体装置の製造工程を示す断面図である。

【図17】図16に続く半導体装置の製造工程を示す断面図である。

【図18】図17に続く半導体装置の製造工程を示す断面図である。

【図19】図18に続く半導体装置の製造工程を示す断面図である。

【図20】図19に続く半導体装置の製造工程を示す断面図である。

【図21】図20に続く半導体装置の製造工程を示す断面図である。

【図22】図21に続く半導体装置の製造工程を示す断面図である。

【図23】実施の形態2における半導体基板に形成された接続部と貫通電極を示す図である。

【図24】接続部と貫通電極を形成した半導体基板の構成を示す断面図である。

【図25】実施の形態2における半導体装置の製造工程を示す断面図である。

【図26】図25に続く半導体装置の製造工程を示す断面図である。

【図27】図26に続く半導体装置の製造工程を示す断面図である。

【図28】図27に続く半導体装置の製造工程を示す断面図である。

【図29】図28に続く半導体装置の製造工程を示す断面図である。

【図30】図29に続く半導体装置の製造工程を示す断面図である。

【図31】図30に続く半導体装置の製造工程を示す断面図である。

【図32】図31に続く半導体装置の製造工程を示す断面図である。

【図33】図32に続く半導体装置の製造工程を示す断面図である。

【図34】図33に続く半導体装置の製造工程を示す断面図である。

【図35】図34に続く半導体装置の製造工程を示す断面図である。

【図36】図35に続く半導体装置の製造工程を示す断面図である。

【図37】図36に続く半導体装置の製造工程を示す断面図である。

【図38】図37に続く半導体装置の製造工程を示す断面図である。

【図39】図38に続く半導体装置の製造工程を示す断面図である。

【図40】図39に続く半導体装置の製造工程を示す断面図である。

【図41】図40に続く半導体装置の製造工程を示す断面図である。

【図42】図41に続く半導体装置の製造工程を示す断面図である。

【図43】図42に続く半導体装置の製造工程を示す断面図である。

【図44】図43に続く半導体装置の製造工程を示す断面図である。

【図45】複数の半導体チップを積層する様子を示す図である。

【図46】複数の半導体チップを積層する様子を示す断面図である。

【発明を実施するための形態】

【0020】

以下の実施の形態においては便宜上その必要があるときは、複数のセクションまたは実施の形態に分割して説明するが、特に明示した場合を除き、それらはお互いに無関係なものではなく、一方は他方の一部または全部の変形例、詳細、補足説明等の関係にある。

【0021】

また、以下の実施の形態において、要素の数等(個数、数値、量、範囲等を含む)に言及する場合、特に明示した場合および原理的に明らかに特定の数に限定される場合等を除き、その特定の数に限定されるものではなく、特定の数以上でも以下でもよい。

【0022】

さらに、以下の実施の形態において、その構成要素(要素ステップ等も含む)は、特に明示した場合および原理的に明らかに必須であると考えられる場合等を除き、必ずしも必須のものではないことは言うまでもない。

【0023】

同様に、以下の実施の形態において、構成要素等の形状、位置関係等に言及するときは、特に明示した場合および原理的に明らかにそうではないと考えられる場合等を除き、実質的にその形状等に近似または類似するもの等を含むものとする。このことは、上記数値および範囲についても同様である。

【0024】

また、実施の形態を説明するための全図において、同一の部材には原則として同一の符号を付し、その繰り返しの説明は省略する。なお、図面をわかりやすくするために平面図であってもハッチングを付す場合がある。

【0025】

(実施の形態1)

本実施の形態1では、主に複数の半導体チップを積層する例について説明する。積層された複数の半導体チップを電気的に接続する方法としては、上層の半導体チップにバンプ電極を形成し、かつ、下層の半導体チップに端子を形成し、上層の半導体チップに形成されているバンプ電極を、下層に形成されている端子に半田を使用して接続する方法が考えられる。

【0026】

近年、半導体装置の小型化のために、半導体チップ間を接続する接続部の高密度・狭ピッチ化が要求されており、高密度・狭ピッチに配置された端子とバンプ電極とを半田で接続する必要がある。このとき、半田を使用した接続では、半田を加熱して溶融(リフロー)させる工程が必要である。ところが、端子やバンプ電極から構成される接続部の高密度化や狭ピッチ化が進むと、半田の加熱溶融時に半田が流動化するため、隣り合う位置に配置されている端子上に形成されている半田同士が接合してショート不良が発生するおそれがある。つまり、半田を使用して上層の半導体チップと下層の半導体チップを接続する方法は、半導体チップ間を接続する端子およびバンプ電極の高密度・狭ピッチ化が進むにつれて、隣接する端子間をショートさせることなく端子とバンプ電極とを接続することが困難になってきている。

【0027】

そこで、本実施の形態1では、半田を使用することなく、上層の半導体チップと下層の半導体チップとを電気的に接続する工夫を施している。以下では、上層の半導体チップと下層の半導体チップとを電気的に接続する工夫について説明する。本実施の形態1では、上層の半導体チップにバンプ電極を形成し、このバンプ電極と電気的に接続する下層の半導体チップの接続部に工夫を施している。

【0028】

図1は、下層の半導体チップに形成されている接続部CNTの構成を示す断面図である。図1において、半導体基板1Sの上面(主面、素子形成面)には、MISFET(Metal Insulator Semiconductor Field Effect Transistor)などの半導体素子(図示せず)が形成されている。そして、半導体素子を形成した半導体基板1S上には、層間絶縁膜ILが形成されている。この層間絶縁膜ILには、多層配線(図示せず)が形成されており、多層配線は、半導体基板1Sに形成されている半導体素子と電気的に接続されている。さらに、この層間絶縁膜ILの最上層には端子(基板電極)TEが形成されている。

【0029】

端子TEが形成された層間絶縁膜IL上には銅膜CFが形成され、この銅膜CF上にニッケル膜NFが形成されている。そして、ニッケル膜NFの表面に金膜AFが形成されている。このとき、接続部CNTは、層間絶縁膜IL上に形成されている銅膜CF、ニッケル膜NFおよび金膜AFを加工することにより形成されている。具体的に、接続部CNTは、金膜AFおよびニッケル膜NFを貫通するように形成された開口部OPを有している。そして、この開口部OPから露出する銅膜CFが除去されて、銅膜CFに空洞部CAが形成されている。このとき、銅膜CFに形成されている空洞部CAの大きさは、ニッケル膜NFおよび金膜AFに形成されている開口部OPの大きさよりも大きくなっている。したがって、空洞部CA上には、ニッケル膜NFおよび金膜AFからなる梁BMが突き出た構造となっている。つまり、本実施の形態1における接続部CNTは、銅膜CF、ニッケル膜NFおよび金膜AFを構成要素とし、銅膜CFに空洞部CAが形成され、かつ、ニッケル膜NFおよび金膜AFに開口部OPが形成された構造をしている。そして、空洞部CAが開口部OPを内包し、かつ、空洞部CAの大きさが開口部OPの大きさよりも大きくなっているので、空洞部CAの上部にニッケル膜NFおよび金膜AFよりなる梁BMが形成されていることになる。なお、銅膜CF、ニッケル膜NFおよび金膜AFは接続部CNTに接続される配線としても機能する。

【0030】

接続部CNTを構成する空洞部CAと開口部OPは接続されており一体化している。接続部CNTを構成する銅膜CFは、空洞部CAを形成し、かつ、端子TEと接続部CNTを電気的に接続する機能を有している。接続部CNTを構成するニッケル膜NFは、梁BMを構成するための膜であり、このニッケル膜NFの膜厚によって梁BMの剛性が決まる。つまり、ニッケル膜NFは梁BMとして機能する膜であり、ニッケル膜NFは高い剛性を有していることから、梁BMとして使用されている。ニッケル膜NF上に形成されている金膜AFは、接続部CNTとバンプ電極とを低抵抗で接続するために形成される膜である。

【0031】

本実施の形態1における接続部CNTは上記のように構成されており、以下に、この接続部CNTとバンプ電極との接続形態について説明する。つまり、接続部CNTを形成した下層の半導体チップと、バンプ電極を形成した上層の半導体チップとの接続構造について説明する。

【0032】

図2は、接続部CNTを形成した半導体基板1S(下層の半導体チップ)と、バンプ電極BMP1を形成した半導体基板2S(上層の半導体チップ)とを相対させた図である。図2において、半導体基板1Sに形成された接続部CNTの構成は図1で説明したものと同様である。一方、半導体基板2Sには、図2の下面(主面、素子形成面)にMISFETなどの半導体素子が形成されており、この半導体素子を形成した半導体基板2S上に層間絶縁膜IL2が形成されている。この層間絶縁膜IL2には多層配線が形成されており、多層配線は半導体基板2Sに形成された半導体素子と電気的に接続されている。そして、層間絶縁膜IL2の最上層にパッドが形成されており、このパッド上にバンプ電極BMP1が形成されている。

【0033】

バンプ電極BMP1は、例えば、めっき法で形成された金膜から形成されている。このようにめっき法で形成されたバンプ電極BMP1は、バンプ電極BMP1の材料(金膜)を溶融させていないので、変形しにくいという特性がある。

【0034】

上述したバンプ電極BMP1を形成した半導体基板2Sと、接続部CNTを形成した半導体基板1Sとを接続する。具体的に、図2に示すように、半導体基板1Sに形成されている接続部CNTと、半導体基板2Sに形成されているバンプ電極BMP1との位置合わせを実施する。その後、上層の半導体基板2Sに荷重を加えることにより、下層の半導体基板1Sに形成されている接続部CNTに、上層の半導体基板2Sに形成されているバンプ電極BMP1を押し付ける。これにより、図3に示すように、上層のバンプ電極BMP1と下層の接続部CNTが接続される。具体的に、図3は、バンプ電極BMP1と接続部CNTとの接続状態を示す図である。図3において、接続部CNTにバンプ電極BMP1を押し付けることにより、接続部CNTを構成する梁BMが曲がる(たわむ)。そして、さらに、バンプ電極BMP1を接続部CNTに押し付けると、バンプ電極BMP1の先端部が空洞部CAの底面に到達する。このとき、押し曲げられた梁BMには復元力が働き、空洞部CAの底面にまで挿入されたバンプ電極BMP1を左右から挟む。このため、空洞部CAに挿入されたバンプ電極BMP1は、左右から梁BMの復元力により固定される。このようにして、バンプ電極BMP1を接続部CNTに接続することができる。

【0035】

このとき、半導体基板2Sに形成されている半導体素子は、層間絶縁膜IL2に形成されている多層配線と多層配線上に形成されているバンプ電極BMP1と電気的に接続されている。そして、バンプ電極BMP1は、接続部CNTと接続されている。具体的に、バンプ電極BMP1は梁BMで固定されていることから、バンプ電極BMP1は、梁BMを構成するニッケル膜NFおよび金膜AFと接続される。そして、ニッケル膜NFは銅膜CFと接続され、かつ、銅膜CFは層間絶縁膜IL1上に形成されている端子TEと接続されていることから、バンプ電極BMP1は、接続部CNTを介して端子TEと接続される。さらに、端子TEは、層間絶縁膜IL1に形成された多層配線および多層配線の下層に形成された半導体素子と接続されている。したがって、半導体基板2Sに形成されているバンプ電極BMP1と、半導体基板1Sに形成されている接続部CNTとを接続することにより、半導体基板2Sに形成されている半導体素子と、半導体基板1Sに形成されている半導体素子とを電気的に接続することができる。ここで、バンプ電極BMP1には接続部CNTを構成する梁BMが接続されているが、梁BMの表面には金膜AFが形成されているので、バンプ電極BMP1と接続部CNTとの接触抵抗を小さくすることができる。

【0036】

以上のように、本実施の形態1の第1特徴点は、図3に示すように、半導体基板1Sに形成した接続部CNTに、半導体基板2Sに形成したバンプ電極BMP2を挿入することにより、接続部CNTとバンプ電極BMP1とを接続することにある。詳細には、接続部CNTを、銅膜CFに形成された空洞部CAと、空洞部CA上に形成されたニッケル膜NFおよび金膜AFからなる梁BMと、梁BMの間に形成された開口部OPから構成することにより、バンプ電極BMP1を開口部OPから空洞部CA内に挿入し、バンプ電極BMP1を挿入することにより変形した梁BMの復元力でバンプ電極BMP1を固定することができる。この結果、本実施の形態1によれば、バンプ電極BMP1と接続部CNTとを半田を使用せずに接続することができる。つまり、本実施の形態1では、空洞部CAにバンプ電極BMP1を挿入し、かつ、空洞部CAに突き出るように配置された梁BMの変形による復元力でバンプ電極BMP1を固定するように構成している。このため、本実施の形態1では、半田を使用せずに、バンプ電極BMP1を接続部CNTへ機械的に固定することができる。このことは、バンプ電極BMP1と接続部CNTの接続に半田を使用しないので、接続部CNTおよびバンプ電極BMP1の高密度化や狭ピッチ化が行なわれても、隣接する接続部CNT間や隣接するバンプ電極BMP1間でのショート不良を抑制できることを意味している。言い換えれば、本実施の形態1では、バンプ電極BMP1と接続部CNTとの接続に溶融した半田を使用しないために、半田ブリッジによるショート不良を抑制することができ、半導体装置の信頼性を向上することができるのである。

【0037】

図2および図3では、例えば、めっき法で形成された変形しにくいバンプ電極BMP1を接続部CNTに挿入して接続する例を説明したが、次に、変形しやすいバンプ電極BMP2を接続部CNTに挿入して接続する例について説明する。

【0038】

図4は、接続部CNTを形成した半導体基板1S(下層の半導体チップ)と、バンプ電極BMP2を形成した半導体基板2S(上層の半導体チップ)とを相対させた図である。図4において、半導体基板1Sに形成された接続部CNTの構成は図1で説明したものと同様である。一方、半導体基板2Sに形成されたバンプ電極BMP2は、図2で説明したバンプ電極BMP1とは形成方法が異なっている。つまり、図4におけるバンプ電極BMP2は、例えば、スタッドバンプ電極のように変形しやすいバンプ電極から構成されている。スタッドバンプ電極とは、金線を溶融させてキャピラリと呼ばれる型に押し付けることにより成形したバンプ電極であり、一度溶融させているため、変形しやすいという特性を有している。

【0039】

上述したバンプ電極BMP2を形成した半導体基板2Sと、接続部CNTを形成した半導体基板1Sとを接続する。具体的に、図4に示すように、半導体基板1Sに形成されている接続部CNTと、半導体基板2Sに形成されているバンプ電極BMP2との位置合わせを実施する。その後、上層の半導体基板2Sに荷重を加えることにより、下層の半導体基板1Sに形成されている接続部CNTに、上層の半導体基板2Sに形成されているバンプ電極BMP2を押し付ける。これにより、図5に示すように、上層のバンプ電極BMP2と下層の接続部CNTが接続される。具体的に、図5は、バンプ電極BMP2と接続部CNTとの接続状態を示す図である。図5において、接続部CNTにバンプ電極BMP2を押し付けることにより、接続部CNTを構成する梁BMが曲がる(たわむ)。そして、さらに、バンプ電極BMP2を接続部CNTに押し付けると、バンプ電極BMP2の先端部が空洞部CAの底面に到達する。このとき、押し曲げられた梁BMには復元力が働き、空洞部CAの底面にまで挿入されたバンプ電極BMP2を左右から挟む。このため、空洞部CAに挿入されたバンプ電極BMP2は、左右から梁BMの復元力により固定される。さらに、この状態で、バンプ電極BMP2に荷重を加えると、バンプ電極BMP2が塑性変形し、バンプ電極BMP2の先端部が横方向に広がる。この結果、梁BMの復元力に加えて、梁BMとバンプ電極BMP2がかしめられるので、バンプ電極BMP2と接続部CNTの接合力が向上する。このようにして、バンプ電極BMP2を接続部CNTに接続することができる。

【0040】

続いて、半球状で比較的柔らかいバンプ電極BMP3を接続部CNTに挿入して接続する例について説明する。図6は、接続部CNTを形成した半導体基板1S(下層の半導体チップ)と、バンプ電極BMP3を形成した半導体基板2S(上層の半導体チップ)とを相対させた図である。図6において、半導体基板1Sに形成された接続部CNTの構成は図1で説明したものと同様である。一方、半導体基板2Sに形成されたバンプ電極BMP3は、図2で説明したバンプ電極BMP1や図4で説明したバンプ電極BMP2とは材質が異なり、例えば、半田から構成されている。この半田から構成されているバンプ電極BMP3は、半球状で比較的柔らかな構造をしている。

【0041】

上述したバンプ電極BMP3を形成した半導体基板2Sと、接続部CNTを形成した半導体基板1Sとを接続する。具体的に、図6に示すように、半導体基板1Sに形成されている接続部CNTと、半導体基板2Sに形成されているバンプ電極BMP3との位置合わせを実施する。その後、上層の半導体基板2Sに荷重を加えることにより、下層の半導体基板1Sに形成されている接続部CNTに、上層の半導体基板2Sに形成されているバンプ電極BMP3を押し付ける。これにより、図7に示すように、上層のバンプ電極BMP3と下層の接続部CNTが接続される。具体的に、図7は、バンプ電極BMP3と接続部CNTとの接続状態を示す図である。図7において、接続部CNTにバンプ電極BMP3を押し付けると、接続部CNTを構成する梁BMが曲がり始めるとともに、柔らかいバンプ電極BMP3も梁BMのたわみに沿って変形する。そして、さらに、バンプ電極BMP3を接続部CNTに押し付けると、バンプ電極BMP3の先端部が空洞部CAの底面に到達する。このとき、押し曲げられた梁BMには復元力が働き、空洞部CAの底面にまで挿入されたバンプ電極BMP3を左右から挟む。このため、空洞部CAに挿入されたバンプ電極BMP3は、左右から梁BMの復元力により固定される。このようにして、バンプ電極BMP3を接続部CNTに接続することができる。

【0042】

以上のことから、本実施の形態1における接続部CNTは、様々な材質や形状のバンプ電極BMP1〜BMP3と接続することができることがわかる。すなわち、本実施の形態1による接続部CNTは、バンプ電極BMP1〜BMP3の種類を問わず、半導体基板1S(下層の半導体チップ)と半導体基板2S(上層の半導体チップ)とを接続することができる。

【0043】

次に、本実施の形態1における接続部CNTと端子TEとの位置関係について説明する。例えば、図1〜図7では、接続部CNTの位置と端子TEの位置とは、平面的に離れた位置に形成されている。この場合、接続部CNTと端子TEとの電気的な接続は、接続部CNTを構成する銅膜CFによって行なわれる。すなわち、接続部CNTにバンプ電極BMP1〜BMP3が接続されると、バンプ電極BMP1〜BMP3は梁BMと接触する。この梁BMは、ニッケル膜NFと金膜AFとの積層膜から形成され、銅膜CFと電気的に接続される。さらに、銅膜CFは端子TEと接続されている。したがって、バンプ電極BMP1〜BMP3は、接続部CNTを介して銅膜CFにより端子TEと接続される。このとき、バンプ電極BMP1〜BMP3が梁BMと接触すれば、必然的に、梁BMと接続されている銅膜CFを介して端子TEと接続することができるので、バンプ電極BMP1〜BMP3と端子TEとを安定して接続することができる。

【0044】

これに対し、例えば、図8では、接続部CNTの位置と端子TEの位置とが平面的に重なるように配置されている。言い換えれば、接続部CNTを構成する空洞部CAの底部に端子TEが形成されている。この場合、空洞部CAの底部に形成されている端子TEと、バンプ電極BMPとを直接接続することができる。したがって、接続部CNTの周辺部に端子TEを配置する必要がなくなるため、接続部CNTと端子TEとを含む接続構造を形成するスペースを小さくすることができる。この結果、図8に示す接続構造によれば、半導体装置の小型化を推進できる利点がある。

【0045】

本実施の形態1における第1特徴点は、図9に示すように、接続部CNTを、銅膜CFに形成された空洞部CAと、空洞部CA上に形成されたニッケル膜NFおよび金膜AFからなる梁BMと、梁BMの間に形成された開口部OPから構成することにより、バンプ電極BMPを開口部OPから空洞部CA内に挿入し、バンプ電極BMPを挿入することにより変形した梁BMの復元力でバンプ電極BMPを固定する点にある。この第1特徴点により、バンプ電極BMPを接続部CNTに接続することができるが、バンプ電極BMPと接続部CNTの接続を良好にする観点からは、以下に示す関係を満たしていることが望ましい。この関係について図9を参照しながら説明する。

【0046】

まず、図9は、接続部CNTを構成する主要な構成要素の寸法と、バンプ電極BMPの先端部の寸法を示す図である。図9において、開口部OPの径をaとしている。すなわち、開口部OPの径を言い換えると、複数の梁BMの先端部間の距離をaとしている。そして、バンプ電極BMPの先端部の径をbとしている。このとき、条件a<bが成立していることが望ましい。なぜなら、開口部OPの径(a)がバンプ電極BMPの先端部の径(b)よりも小さければ、バンプ電極BMPを開口部OPに挿入した場合、梁BMにバンプ電極BMPが接触し、バンプ電極BMPを挿入するにしたがって梁BMが変形し、変形した梁BMによる復元力で挿入されたバンプ電極BMPを固定することができるからである。

【0047】

また、梁BMの長さをcとしており、空洞部CAの深さをdとしている。空洞部CAの深さは、言い換えれば、銅膜CFの厚さということもできる。このとき、条件c<dが成立していることが望ましい。なぜなら、梁BMの長さ(c)が空洞部CAの深さ(d)よりも小さければ、バンプ電極BMPが空洞部CA内に挿入されたとき、梁BMが空洞部CAの底部に接触してバンプ電極BMPの空洞部CAへの挿入が妨げられることや、梁BMが空洞部CAの底部に接触して折れ曲がって折れてしまうことを抑制できるからである。これらの条件(a<b、c<d)を満たすことにより、バンプ電極BMPと接続部CNTの接続を良好にすることができる。

【0048】

上述した記載では、本実施の形態1における接続部CNTの特徴(第1特徴点)を断面構造の観点から説明したが、次に、本実施の形態1における接続部CNTのさらなる特徴を平面構造の観点から説明する。

【0049】

図10は、本実施の形態1における接続部CNTの平面構造を示す図である。図10において、半導体基板1S上に接続部CNTが形成されている。この接続部CNTは、半導体基板1S上に形成された導体膜CON(ニッケル膜NF+金膜AF)を有し、この導体膜CONには、導体膜CONを貫通する開口部OPが形成されている。この開口部OPの下層には、開口部OPと一体化された空洞部CAが形成されている。この空洞部CAは、開口部OPを平面的に内包し、かつ、空洞部CAの大きさが開口部OPの大きさよりも大きくなるように形成されている。そして、開口部OP上には導体膜CONからなる複数の梁BMが形成されており、この複数の梁BMは開口部OPに突き出すように形成されている。このように構成されている接続部CNTにおいて、図10のA−A線で切断した断面が、例えば、図1などに該当する。

【0050】

本実施の形態1の第2特徴点は、平面的に開口部OPが空洞部CAに内包され、かつ、開口部OPと空洞部CAが一体化され、かつ、導体膜CONのうち空洞部CAに突き出た部分が梁BMとなる接続部CNTにおいて、開口部OPの輪郭形状が、空洞部CAに突き出ている梁BMの根元から先端部に至る形状を縁取る形状を有している点にある。すなわち、本実施の形態1における開口部OPは、隣接する梁BMの間において、梁BMの根元から先端部に至るまで大きく開口されている。特に、開口部OPの平面上の面積は、梁BMの平面上の面積よりも大きくなっている。これにより、開口部OPの下層に形成される空洞部CAを容易に作ることができるのである。

【0051】

具体的に、本実施の形態1では、開口部OPから露出する下地膜(銅膜)をウェットエッチングすることにより空洞部CAを形成している。このとき、開口部OPの輪郭形状が、空洞部CAに突き出ている梁BMの根元から先端部に至る形状を縁取る形状を有しており、隣接する梁BMの間において、梁BMの根元から先端部に至るまで大きく開口されていると、開口部OPから露出する下地膜の表面積が大きくなる。この場合、エッチング液の循環もよくなり、エッチング速度が速くなる利点がある。さらに、開口部OPの下層に空洞部CAを形成するためのエッチング面積も少なくすることができる。つまり、空洞部CAは、梁BMの下層に空洞を形成するためのものであるが、隣接する梁BMの間において、開口部OPの形状が梁BMの根元から先端部に至るまで大きく開口されていると、開口部OPから露出する下地膜の表面積が大きくなるため、大きな露出領域の各領域からエッチングが進行する。このため、梁BMの下層に形成される空洞部CAをより少ないエッチング量で形成することができるのである。このように本実施の形態1によれば、開口部OPの輪郭形状が、空洞部CAに突き出ている梁BMの根元から先端部に至る形状を縁取る形状を有し、隣接する梁BMの間において、梁BMの根元から先端部に至るまで大きく開口されている形状をしていることから(第2特徴点)、空洞部CAを形成するエッチング量を低減することができるとともに、エッチング速度を速くすることができる。このことは、空洞部CAを形成するための処理時間が短くなることを意味し、これにより、コストの削減を図ることができることを意味している。特に、開口部OPの平面上の面積が、梁BMの平面上の面積よりも大きくなっていると上述した効果は大きくなる。

【0052】

ここで、例えば、図11に示すような接続部CNT2の構造を考える。この接続部CNT2は、中央部に円形の開口部OPTが形成されており、この開口部OPTの外側に梁BM2が形成されている。このとき、梁BM2は、開口部OPTから放射状に形成されたスリットSLによって分割されて梁BM2となっている。このような接続部CNT2において、開口部OPTの下層に空洞部を形成することを考える。この場合、開口部OPTから露出する下地膜をウェットエッチングすることにより、梁BMの下層に空洞部CAを形成する。

【0053】

しかし、接続部CNT2の構成では、本実施の形態1の接続部CNTと異なり、開口部OPTの輪郭形状が、空洞部に突き出ている梁BM2の根元から先端部に至る形状を縁取る形状をしておらず、隣接する梁BM2の間において、梁BM2の根元から先端部に至るまで大きく開口されていない。つまり、接続部CNT2では、隣接する梁BM2の間には線状のスリットSLが形成されているだけである。このため、エッチング液は、開口部OPTからしか内部に浸入しないことなり、空洞部を形成するエッチングは図11に示すように、開口部OPTから同心円状に進むことになる。この場合、開口部OPTから露出する露出領域が小さいことからエッチング液の循環が悪くなるとともに、露出領域の表面積が小さいことから、同時にエッチングされる領域も狭くなる。さらに、エッチングが同心円状に進むことから、梁BM2の下層全体に空洞部を形成するエッチング量も大きくなる。このことは、空洞部を形成するための処理時間が長くなることを意味し、これにより、コストの上昇を招くことになる。

【0054】

これに対し、本実施の形態1では、開口部OPの輪郭形状が、空洞部CAに突き出ている梁BMの根元から先端部に至る形状を縁取る形状を有し、隣接する梁BMの間において、梁BMの根元から先端部に至るまで大きく開口されている形状をしていることから(第2特徴点)、空洞部CAを形成するエッチング量を低減することができるとともに、エッチング速度を速くすることができる利点を有するのである。

【0055】

さらに、本実施の形態1では、上述した第2特徴点により別の効果も奏する。例えば、接続部CNTにバンプ電極を挿入して複数の半導体チップを積層した構造では、複数の半導体チップ間にアンダーフィルと呼ばれる樹脂を注入することが行なわれる。このアンダーフィルは、半導体装置に熱負荷が加わった場合に、材質間の熱膨張率の相違による剥がれを抑制して接着効果を高める機能を有している。このとき、本実施の形態1の接続部CNTのように、隣接する梁BMの間において、梁BMの根元から先端部に至るまで大きく開口されている形状をしていると、この接続部CNTにバンプ電極BMPを挿入した後も、各梁BMの根元に隙間が生じている。したがって、アンダーフィルを半導体チップ間に注入すると、梁BMの根元に生じている隙間を介してアンダーフィルが接続部CNTの内部にまで充填される。このため、接続部CNTとこの接続部CNTに挿入されているバンプ電極BMPとの接続強度が隙間をアンダーフィルで充填することにより向上するのである。すなわち、本実施の形態1によれば、開口部OPの輪郭形状が、空洞部CAに突き出ている梁BMの根元から先端部に至る形状を縁取る形状を有し、隣接する梁BMの間において、梁BMの根元から先端部に至るまで大きく開口されている形状をするように構成することにより、エッチング処理時間の短縮だけでなく、接続部CNTとバンプ電極BMP間の接続強度の向上も図ることができるのである。

【0056】

次に、本実施の形態1における第3特徴点について説明する。本実施の形態1における第3特徴点は、梁BMの構造に対する工夫にある。具体的に、図10に示すように、梁BMの幅は、梁BMの先端部から梁BMの根元に向って大きくなっている点に特徴がある。つまり、梁BMを、いわゆる平等強さの梁から構成する。これにより、梁BMを介して接続部CNTにバンプ電極BMPを挿入したとき、梁BMにかかる応力を均一にすることができ、梁BMの応力に対する耐性を向上させることができる。

【0057】

例えば、梁BMの幅を先端部から根元まで同じ大きさにすると、梁BMにかかる応力が根元に集中する。すると、梁BMが根元から折れてしまうおそれがある。そこで、梁BMの幅を先端部から根元に向って大きくするように梁BMを構成することにより、梁BMの根元の応力に対する耐性を向上することができる。つまり、梁BMの幅を先端部から根元に向って大きくするように構成することにより、梁BMの全体にかかる応力を均一にすることができる。この結果、梁BMの根元に過大な応力が印加されることを抑制することができ、梁BMの曲げ応力に対する耐性を向上することができる。したがって、本実施の形態1によれば、梁BMの構成をいわゆる平等強さの梁構造とする第3特徴点により、梁BMの強度を確保することができ、接続部CNTの信頼性を向上することができる。

【0058】

さらに、本実施の形態1では、梁BMの先端部や根元の形状に丸みをもたせている。これにより、梁BMに荷重が加わった場合、先端部や根元に荷重が集中することを抑制できる。なお、図10では、接続部CNTに4つの梁BMを形成している例を示しているが、これに限らず、5本や6本のように4本よりも多くてもよいし、3本や2本のように4本よりも少なくてもよい。さらには、1本の梁BMだけを形成する場合であってもよい。

【0059】

本実施の形態1における接続部CNTは上記のように構成されており、以下に、この接続部CNTとバンプ電極BMPによって、複数の半導体チップを電気的に接続しながら、3次元的に積層する接続例について説明する。

【0060】

図12は、半導体基板(下層の半導体チップ)1Sと半導体基板(上層の半導体チップ)2Sとを積層する様子を示す図である。図12において、下層の半導体基板1Sに複数の接続部CNTが形成され、上層の半導体基板2Sに複数のバンプ電極が形成されている。半導体基板1Sは矩形形状(四角形状)をしており、半導体基板1Sの周辺部(辺)に沿って、複数の接続部CNTが配列している。例えば、半導体基板1Sに形成されている複数の接続部CNTは、ペリフェラル配置で配置されているが、接続部CNTの配置は、ペリフェラル配置に限定されない。一方、半導体基板2Sも矩形形状(四角形状)をしており、半導体基板2Sの周辺部(辺)に沿って複数のバンプ電極BMPが形成されている。このバンプ電極BMPは、接続部CNTに対応するように配置されている。

【0061】

図13は、半導体基板1Sに形成した接続部CNTと、半導体基板2Sに形成したバンプ電極BMPとを接続した様子を示す断面図である。図13に示すように、半導体基板1Sに形成された接続部CNTのそれぞれに、半導体基板2Sに形成されたバンプ電極BMPのそれぞれは挿入されている。これにより、半導体基板1Sと半導体基板2Sとを電気的に接続しながら、3次元的に積層することができる。つまり、本実施の形態1では、図13に示すように、空洞部CAにバンプ電極BMPを挿入し、かつ、空洞部CAに突き出るように配置された梁BMの変形による復元力でバンプ電極BMPを固定するように構成している。このため、本実施の形態1では、半田を使用せずに、バンプ電極BMPを接続部CNTへ機械的に固定することができる。したがって、バンプ電極BMPと接続部CNTの接続に半田を使用しないので、接続部CNTおよびバンプ電極BMPの高密度化や狭ピッチ化が行なわれても、隣接する接続部CNT間や隣接するバンプ電極BMP間でのショート不良を抑制できる。言い換えれば、本実施の形態1では、バンプ電極BMPと接続部CNTとの接続に溶融した半田を使用しないために、半田ブリッジによるショート不良を抑制することができ、半導体装置の信頼性を向上することができる。

【0062】

このとき、本実施の形態1では、図10に示すように、梁BMの構成をいわゆる平等強さの梁構造とすることにより(第3特徴点)、梁BMの強度を確保することができ、接続部CNTの信頼性を向上することができる。

【0063】

さらに、半導体基板1Sと半導体基板2Sの間にはアンダーフィルUFが注入されている。本実施の形態1では、図10に示すように、開口部OPの輪郭形状が、空洞部CAに突き出ている梁BMの根元から先端部に至る形状を縁取る形状を有し、隣接する梁BMの間において、梁BMの根元から先端部に至るまで大きく開口されている形状をしていることから(第2特徴点)、接続部CNTにバンプ電極BMPを挿入した後も、各梁BMの根元に隙間が生じている。したがって、アンダーフィルUFを半導体基板1Sと半導体基板2Sとの間に注入すると、梁BMの根元に生じている隙間を介してアンダーフィルUFが接続部CNTの内部にまで充填される。このため、接続部CNTとこの接続部CNTに挿入されているバンプ電極BMPとの接続強度が向上している。

【0064】

なお、図12および図13では、半導体基板(半導体チップ)1Sと、半導体基板(半導体チップ)2Sを3次元的に積層する例について説明したが、本実施の形態1における接続部CNTとバンプ電極BMPによる接続は、半導体基板(半導体チップ)と配線基板との接続にも応用することができる。例えば、配線基板に接続部を形成し、半導体基板にバンプ電極を形成する。そして、半導体基板に形成されたバンプ電極を配線基板に形成された接続部に挿入することにより、配線基板と半導体基板とを接続することができる(フリップチップ接続)。

【0065】

次に、本実施の形態1における半導体装置の製造方法について図面を参照しながら説明する。以下に示す半導体装置の製造方法では、本実施の形態1の特徴である接続部CNTを形成する工程について説明する。

【0066】

まず、図14に示すように、半導体基板1Sの上面(主面、素子形成面)に通常の技術を使用することにより、MISFETなどの半導体素子(図示せず)を形成する。そして、半導体素子を形成した半導体素子上に層間絶縁膜ILを形成する。その後、層間絶縁膜ILの層間に多層配線(図示せず)を形成し、層間絶縁膜ILの最上層に端子TEを形成する。このとき、層間絶縁膜ILの最上層に形成されている端子TEは、層間絶縁膜ILの内部に形成されている多層配線を介して、半導体基板1Sに形成されている半導体素子と電気的に接続されている。

【0067】

次に、図15に示すように、端子TEを形成した層間絶縁膜IL上に銅膜CFを形成する。銅膜CFは、例えば、スパッタリング法を使用することにより形成することができる。この銅膜CFには、後述する工程でウェットエッチングすることにより梁の下層に空洞部を形成して接続部CNTを形成するため、梁の可動範囲は充分に得られるように銅膜CFの膜厚が設定される。例えば、銅膜CFの膜厚は、約10μmである。銅膜CFの形成方法は、スパッタリング法のほか、スパッタリング法で0.3μm〜1μmの銅膜CFを形成した後、電解めっき法で10μmの厚さの銅膜CFを形成することもできる。

【0068】

続いて、図16に示すように、銅膜CF上にニッケル膜NFを形成する。ニッケル膜NFは、例えば、スパッタリング法を使用することにより形成することができる。このニッケル膜NFは、後述する梁を構成する部材であり、ニッケル膜NFの厚さによって梁の剛性、つまり、梁のばね定数が決定される。梁はバンプ電極を挿入した際、梁の復元力によって充分な接合力を得る必要があり、この梁の復元力は、ニッケル膜NFの膜厚によって決定される。したがって、ニッケル膜NFの膜厚は、例えば、5μmである。

【0069】

その後、図17に示すように、ニッケル膜NF上に金膜AFを形成する。金膜AFは、例えば、スパッタリング法を使用することにより形成することができる。金膜AFは、梁とバンプ電極との接触抵抗を低抵抗とするために設けられる膜であるため、金膜AFの膜厚は薄くてよい。例えば、金膜AFの膜厚は、約0.2μmとする。

【0070】

次に、図18に示すように、金膜AF上にレジスト膜FR1を塗布した後、このレジスト膜FR1に対して露光・現像処理を施すことにより、レジスト膜FR1に開口部OPを形成する。そして、図19に示すように、開口部OPから露出する金膜AFを除去する。金膜AFを除去するには、例えば、ミリング法を使用することもできるし、その他、ドライエッチング法やAuエッチング溶液を使用したウェットエッチングを使用することもできる。

【0071】

続いて、図20に示すように、開口部OPから露出するニッケル膜NFを除去する。ニッケル膜NFの除去は、例えば、ミリング法を使用することにより実施できる。なお、レジスト膜FR1に形成された開口部OPから露出する金膜AFとニッケル膜NFを除去する工程は、一括して行なうことができる。

【0072】

次に、図21に示すように、銅のエッチャントによるウェットエッチングを実施することにより、開口部OPから露出する銅膜CFを除去する。銅膜CFをウェットエッチングすることにより、銅膜CFに空洞部CAが形成される。ウェットエッチングは、等方性エッチングであるため、開口部OPの直下にある銅膜CFだけでなく、横方向に回り込むようにエッチングが進行し、空洞部CAが形成される。

【0073】

このとき、開口部OPの輪郭形状が図10に示すような形状となっており、開口部OPから露出する下地膜(銅膜CF)の表面積が大きくなる。この場合、エッチング液の循環もよくなり、エッチング速度が速くなる利点がある。さらに、大きな露出領域の各領域からエッチングが進行する。このため、空洞部CAをより少ないエッチング量で形成することができる。このように本実施の形態1によれば、開口部OPの輪郭形状が、図10に示す形状をしていることから(第2特徴点)、空洞部CAを形成するエッチング量を低減することができるとともに、エッチング速度を速くすることができる。

【0074】

空洞部CAは開口部OPを内包し、かつ、空洞部CAの大きさが開口部OPの大きさよりも大きくなる。このことから、空洞部CAの上部にニッケル膜NFおよび金膜AFよりなる梁BMが形成される。

【0075】

その後、図22に示すように、アセトン洗浄や酸素を使用したアッシングにより、レジスト膜FR1を除去する。このようにして、半導体基板1Sに梁構造を有する接続部CNTを形成することができる。

【0076】

本実施の形態1による説明の最後に先行技術文献との差異について説明する。まず、先行技術文献1(特開平10−163267号公報)との差異について説明する。先行技術文献1には、基材のパッド上に第1メッキ層と第2メッキ層からなる導電部を形成し、導電部を構成する第2メッキ層の先端部が突出して突出部となっている構造が記載されている。そして、この導電部にバンプ電極を強制的に挿入し、導電部の突出部をバンプ電極のエッジに係止させることにより導電部とバンプ電極とを接続するとしている。

【0077】

ここで、本実施の形態1における第1特徴点は、例えば、図3に示すように、空洞部CAにバンプ電極BMP1を挿入し、かつ、空洞部CAに突き出るように配置された梁BMの変形による復元力でバンプ電極BMP1を固定するように構成する点にある。つまり、本実施の形態1では、梁BMの復元力によってバンプ電極BMP1を固定する構造であるのに対し、先行技術文献1に記載された技術は、導電部の突出部にバンプ電極のエッジを係止させることにより固定する点で相違する。そして、この固定方法の相違から、本実施の形態1では、接合するバンプの形状にあまり制限なく適用可能であるのに対し、先行技術文献1では、接合するバンプの形状が2段形状となってエッジが突出した形状である必要がある。さらに、本実施の形態1では、接続部の断面構造だけでなく平面構造にも特徴がある。具体的に本実施の形態1の第2特徴点は、図10に示すように、開口部OPの輪郭形状が、空洞部CAに突き出ている梁BMの根元から先端部に至る形状を縁取る形状を有し、隣接する梁BMの間において、梁BMの根元から先端部に至るまで大きく開口されている形状をしている点にある。そして、特に、開口部OPの平面上の面積は、梁BMの平面上の面積よりも大きくなっている。また、本実施の形態1の第3特徴点は、図10に示すように、梁BMの幅を、梁BMの先端部から梁BMの根元に向って大きくする点にある。このような本実施の形態1の平面構造における特徴点(第2特徴点や第3特徴点)について、先行技術文献1には記載も示唆もされていない。したがって、先行技術文献1から本実施の形態1における技術的思想を想到するのは当業者といえども困難である。

【0078】

続いて、先行技術文献2(特開2004−12357号公報)において、スパイラル状接触子は、絶縁基板上に球状接続端子との接触の際に、球状接続端子の形状に対応して変形可能となっており、半導体デバイスとの電気的な接続を行うように構成されている。このとき、スパイラル状接触子の渦巻き部、幅が一定で、先端から根元に近づくに従って厚みが厚くなるとしている。

【0079】

ここで、本実施の形態1における第1特徴点は、例えば、図3に示すように、空洞部CAにバンプ電極BMP1を挿入し、かつ、空洞部CAに突き出るように配置された梁BMの変形による復元力でバンプ電極BMP1を固定するように構成する点にある。したがって、本実施の形態1では、梁BMの復元力によってバンプ電極BMP1を固定する構造であるのに対し、先行技術文献2に記載された技術は、スパイラル状接触子の変形により固定する点で相違する。さらに、先行技術文献2には、本実施の形態1の平面構造における特徴点(第2特徴点)について、記載も示唆もされていない。したがって、先行技術文献2から本実施の形態1における技術的思想を想到するのは当業者といえども困難である。

【0080】

次に、先行技術文献3(特開2004−354179号公報)には、スリットが形成されたコンタクト部が記載されている。これにより、半田ボールの接続時に、この接続に伴いコンタクト部が変位する。このため、半田ボールとコンタクト部との接触面積を増大させることができ、コンタクト部と半田ボールとを確実に電気的に接続することができるとしている。

【0081】

しかし、先行技術文献3に記載されたスリットを有するコンタクト部は、本実施の形態1の接続部CNTと異なり、開口部OPの輪郭形状が、空洞部CAに突き出ている梁BMの根元から先端部に至る形状を縁取る形状をしておらず、隣接する梁BMの間において、梁BMの根元から先端部に至るまで大きく開口されていない。つまり、先行技術文献3のコンタクト部では、スリットが形成されているだけである。これに対し、本実施の形態1では、開口部OPの輪郭形状が、空洞部CAに突き出ている梁BMの根元から先端部に至る形状を縁取る形状を有し、隣接する梁BMの間において、梁BMの根元から先端部に至るまで大きく開口されている形状をしていることから(第2特徴点)、空洞部CAを形成するエッチング量を低減することができるとともに、エッチング速度を速くすることができる利点を有するのである。特に、開口部OPの平面上の面積は、梁BMの平面上の面積よりも大きくなっていることにより顕著な効果が得られるのである。さらに、本実施の形態1の接続部CNTのように、隣接する梁BMの間において、梁BMの根元から先端部に至るまで大きく開口されている形状をしていると、この接続部CNTにバンプ電極BMPを挿入した後も、各梁BMの根元に隙間が生じている。したがって、アンダーフィルを半導体チップ間に注入すると、梁BMの根元に生じている隙間を介してアンダーフィルが接続部CNTの内部にまで充填される。このため、接続部CNTとこの接続部CNTに挿入されているバンプ電極BMPとの接続強度が向上する。

【0082】

このような本実施の形態1の平面構造における特徴点(第2特徴点)について、先行技術文献3には記載も示唆もされていない。したがって、先行技術文献3から本実施の形態1における技術的思想を想到するのは当業者といえども困難である。以上のことから、本実施の形態1の平面構造における第2特徴点については、先行技術文献1〜3のいずれにも記載も示唆もされていないことから、先行技術文献1〜3を組み合わせても、本実施の形態1における技術的思想を想到することは困難である。

【0083】

(実施の形態2)

本実施の形態2では、半導体チップを貫通する貫通電極と本発明による接続部をともに形成する例について説明する。例えば、携帯電話機などのモバイル機器に搭載されるマイコンチップに貫通電極と本発明の接続部を形成する例について説明する。

【0084】

図23は、本実施の形態2における半導体基板(半導体チップ)1Sに形成された接続部CNTと貫通電極TREを示す図である。図23に示すように、半導体基板1Sに形成されている接続部CNTと貫通電極TREは、例えば、並ぶように配置されている。

【0085】

図24は、図23の貫通電極TREと接続部CNTを含む一断面で切断した断面図である。図24において、半導体基板1Sの下面(主面、素子形成面)には、MISFETなどの半導体素子(図示せず)が形成されており、この半導体素子を形成した半導体基板1S上に層間絶縁膜ILが形成されている。この層間絶縁膜ILの内部には多層配線が形成されている。

【0086】

以下に、貫通電極TREの構成について説明する。まず、層間絶縁膜IL上にはパッドPDが形成されており、このパッドPD上にバンプ電極BMPが形成されている。半導体基板1Sの裏面(上面)から層間絶縁膜の内部まで達するように孔H1が形成されており、孔H1の底面の層間絶縁膜ILには、孔H1よりも小径の孔H2がパッドPDに達するまで形成されている。孔H1と孔H2の内壁(側面および底面)と半導体基板1Sの裏面の一部には、順次、銅膜CF、ニッケル膜NF、金膜AFが形成されている。これにより、銅膜CF,ニッケル膜NFおよび金膜AFはパッドPDと電気的に接続されている。

【0087】

次に、接続部CNTの構成について説明する。接続部CNTは、半導体基板1Sの裏面に形成された金膜AFおよびニッケル膜NFを貫通するように形成された開口部OPを有している。そして、この開口部OPから露出する銅膜CFが除去されて、銅膜CFに空洞部CAが形成されている。このとき、銅膜CFに形成されている空洞部CAの大きさは、ニッケル膜NFおよび金膜AFに形成されている開口部OPの大きさよりも大きくなっている。したがって、空洞部CA上には、ニッケル膜NFおよび金膜AFからなる梁BMが突き出た構造となっている。つまり、本実施の形態2における接続部CNTは、銅膜CF、ニッケル膜NFおよび金膜AFを構成要素とし、銅膜CFに空洞部CAが形成され、かつ、ニッケル膜NFおよび金膜AFに開口部OPが形成された構造をしている。そして、空洞部CAが開口部OPを内包し、かつ、空洞部CAの大きさが開口部OPの大きさよりも大きくなっているので、空洞部CAの上部にニッケル膜NFおよび金膜AFよりなる梁BMが形成されていることになる。このように構成された接続部CNTと貫通電極TREは電気的に接続されている。

【0088】

本実施の形態2における半導体装置は上記のように構成されており、以下にその製造方法について図面を参照しながら説明する。まず、図25に示すように、半導体基板1Sの下面(主面、素子形成面)に通常の技術を使用することにより、MISFETなどの半導体素子(図示せず)を形成する。そして、半導体素子を形成した半導体素子上に層間絶縁膜ILを形成する。その後、層間絶縁膜ILの層間に多層配線(図示せず)を形成し、層間絶縁膜ILの最上層にパッドPDを形成する。このとき、層間絶縁膜ILの最上層に形成されているパッドPDは、層間絶縁膜ILの内部に形成されている多層配線を介して、半導体基板1Sに形成されている半導体素子と電気的に接続されている。

【0089】

この半導体基板(半導体ウェハ)1Sに貫通電極を形成するため、例えば、10μm〜50μm程度まで半導体基板1Sを薄型化し、貫通電極の形成難易度を低減する。ただし、半導体基板1Sの薄型化によって、半導体基板1Sの強度低下および半導体基板1Sの反りによる歩留まり低下が生じるおそれがある。

【0090】

そこで、本実施の形態2では、図26に示すように、半導体基板1Sの下面(主面、素子形成面)に接着材BAを塗布し、この接着材BAにより、例えば、ガラスや石英やシリコンからなる支持基板SBを貼り合せる。このように支持基板SBを半導体基板1Sに貼り付けることで、薄型化後の半導体基板1Sの強度低下および反りを抑制することができる。また、接着材BAは、半導体基板1Sに形成された半導体素子を保護する機能を有する。

【0091】

次に、図27に示すように、半導体基板1Sの裏面(上面)に対してバックグラインド処理を実施することにより、半導体基板1Sの厚さを薄くする。半導体基板1Sの裏面をバックグラインドする方法としては、研削や研磨する方法がある。なお、バックグラインドした後の平坦性が半導体基板1Sの裏面に形成する接続部の精度に影響するため、半導体基板1Sの裏面をバックグラインドした後、ドライポリッシュやエッチング、あるいは、化学的機械的研磨(CMP:Chemical Mechanical Polishing)を実施することが望ましい。

【0092】

続いて、図28に示すように、半導体基板1Sの裏面(上面)上にレジスト膜FR2を塗布する。そして、塗布したレジスト膜FR2に対して露光・現像処理を施すことにより、レジスト膜FRに開口部OP2を形成する。レジスト膜FR2を塗布する方法としては、例えば、スピナー塗布法がある。なお、開口部OPの形成位置は、赤外分光法により半導体基板1Sの素子形成面に形成されているデバイスパターンを確認して行なう方法や、両面マスクアライナを用いて行なう方法がある。

【0093】

次に、図29に示すように、開口部OP2を形成したレジスト膜FR2をマスクにしたエッチングにより孔H1を形成する。具体的には、ICP−RIE(Inductively coupled plasma Reactive ion etching)を使用することにより異方性エッチングを行ない、孔H1を形成する。ここで、例えば、プロセスガスとしてSF6とC4H8を使用している。通常、シリコンのドライエッチングでは、酸化シリコン膜をマスクとしてシリコンをエッチングする。このため、SF6とC4H8によるエッチングでは、酸化シリコン膜を主成分とする層間絶縁膜ILでエッチングがストップする。このときの孔H1の深さは、シリコンよりなる半導体基板1Sの膜厚によって決定される。

【0094】

その後、プロセスガスをSF6とC4H8からC3H8、Ar、CHF4の混合ガスに代えて、層間絶縁膜ILの加工(エッチング)を進める。この際、新たなマスクの形成は行なわない。この結果、レジスト膜FR2と半導体基板1Sをマスクとして孔H1の底部の層間絶縁膜ILの薄膜化が進む。このとき、層間絶縁膜ILをエッチングし続けることにより、パッドPDに達する孔H1を形成してもよいが、パッドPDに接する層間絶縁膜ILがなくなりパッドPDの強度が低下する。そこで、本実施の形態2では、層間絶縁膜ILの表面下部からパッドPDに達するまでの範囲で半導体基板1Sに形成した孔H1よりも小径の孔を形成する方法を採用する。

【0095】

次に、孔H1を形成した後、図30に示すように、有機溶剤や酸素アッシングによってレジスト膜FR2を除去する。そして、図31に示すように、孔H1の内部を含む半導体基板1Sの裏面の全面に絶縁膜IF1を形成する。この絶縁膜IF1は、例えば、酸化シリコン膜、窒化シリコン膜、ポリイミド樹脂膜などからなり、例えば、CVD(Chemical Vapor Deposition)法により形成することができる。絶縁膜IF1は、孔H1の内部において、孔H1の内壁および底面に沿ってこれらの面を覆うように形成される。

【0096】

続いて、図32に示すように、孔H1の内部を含む半導体基板1Sの裏面にレジスト膜FR3を塗布する。レジスト膜FR3は、例えば、スピナーによる塗布やスプレーによる塗布などによって形成される。スピナーで塗布する場合は、孔H1を埋め込むため、5μm〜30μmの膜厚で塗布できるレジスト膜FR3を使用することが望ましい。さらに、レジスト膜FR3の中に気泡が残存していると、フォトリソグラフィ工程での露光が難しくなりパターン不良が発生する。このため、真空脱泡により気泡を除去することが望ましい。スプレーで塗布する場合は、スピナーで塗布する場合と異なり、孔H1に沿ってレジスト膜FR3を塗布する。このため、孔H1内部で偏ったレジスト形状となりやすい。その後、孔H1の内面に塗布したレジスト膜FR3のパターニングを行ない、孔H1の底面に開口部OP3を形成する。このとき、孔H1の内壁を保護するレジスト膜FR3がパターニングされないように、開口部OP3の開口径を小さく形成する。

【0097】

その後、図33に示すように、開口部OP3から露出する絶縁膜IF1と層間絶縁膜ILの残りをすべてエッチングすることにより、孔H2を形成する。これにより、孔H2の底部にパッドPDが露出する。絶縁膜IF1および層間絶縁膜ILのエッチングには、例えば、CHF3やC4H8を主成分とする混合ガスを使用する。そして、図34に示すように、有機溶剤や酸素アッシングにより、パターニングされたレジスト膜FR3を除去する。

【0098】

次に、図35に示すように、孔H1および孔H2内を含む半導体基板1Sの裏面上に銅膜CFを形成する。銅膜CFは、例えば、スパッタリング法を使用することにより形成することができる。この銅膜CFには、後述する工程でウェットエッチングすることにより梁の下層に空洞部を形成して接続部CNTを形成するため、梁の可動範囲は充分に得られるように銅膜CFの膜厚が設定される。例えば、銅膜CFの膜厚は、約10μmである。銅膜CFの形成方法は、スパッタリング法のほか、スパッタリング法で0.3μm〜1μmの銅膜CFを形成した後、電解めっき法で10μmの厚さの銅膜CFを形成することもできる。

【0099】

続いて、図36に示すように、銅膜CF上にニッケル膜NFを形成する。ニッケル膜NFは、例えば、スパッタリング法を使用することにより形成することができる。このニッケル膜NFは、後述する梁を構成する部材であり、ニッケル膜NFの厚さによって梁の剛性、つまり、梁のばね定数が決定される。梁はバンプ電極を挿入した際、梁の復元力によって充分な接合力を得る必要があり、この梁の復元力は、ニッケル膜NFの膜厚によって決定される。したがって、ニッケル膜NFの膜厚は、例えば、5μmである。

【0100】

その後、図37に示すように、ニッケル膜NF上に金膜AFを形成する。金膜AFは、例えば、スパッタリング法を使用することにより形成することができる。金膜AFは、梁とバンプ電極との接触抵抗を低抵抗とするために設けられる膜であるため、金膜AFの膜厚は薄くてよい。例えば、金膜AFの膜厚は、約0.2μmとする。

【0101】

次に、図38に示すように、金膜AF上にレジスト膜FR4を塗布する。レジスト膜FR4は、例えば、スピナーによる塗布やスプレーによる塗布によって、半導体基板1Sの裏面を覆うように形成することができる。このレジスト膜FR4に対して露光・現像処理を施すことにより、レジスト膜FR4に電極パターンおよび開口部OPを形成する。そして、図39に示すように、開口部OPから露出する金膜AFを除去する。金膜AFを除去するには、例えば、ミリング法を使用することもできるし、その他、ドライエッチング法やAuエッチング溶液を使用したウェットエッチングを使用することもできる。Auエッチング溶液としては、ヨウ素とヨウ化アンモニウムの混合液が考えられる。

【0102】

続いて、図40に示すように、開口部OPから露出するニッケル膜NFを除去する。ニッケル膜NFの除去は、例えば、ミリング法を使用することにより実施できる。なお、レジスト膜FR4に形成された開口部OPから露出する金膜AFとニッケル膜NFを除去する工程は、一括して行なうことができる。

【0103】

次に、図41に示すように、銅のエッチャントによるウェットエッチングを実施することにより、開口部OPから露出する銅膜CFを除去する。銅膜CFをウェットエッチングすることにより、銅膜CFに空洞部CAが形成される。ウェットエッチングは、等方性エッチングであるため、開口部OPの直下にある銅膜CFだけでなく、横方向に回り込むようにエッチングが進行し、空洞部CAが形成される。

【0104】

このとき、開口部OPの輪郭形状が図23に示すような形状となっており、開口部OPから露出する下地膜(銅膜CF)の表面積が大きくなる。この場合、エッチング液の循環もよくなり、エッチング速度が速くなる利点がある。さらに、大きな露出領域の各領域からエッチングが進行する。このため、空洞部CAをより少ないエッチング量で形成することができる。このように本実施の形態1によれば、開口部OPの輪郭形状が、図23に示す形状をしていることから(第2特徴点)、空洞部CAを形成するエッチング量を低減することができるとともに、エッチング速度を速くすることができる。

【0105】

空洞部CAは開口部OPを内包し、かつ、空洞部CAの大きさが開口部OPの大きさよりも大きくなる。このことから、空洞部CAの上部にニッケル膜NFおよび金膜AFよりなる梁BMが形成される。

【0106】

その後、図42に示すように、アセトン洗浄や酸素を使用したアッシングにより、レジスト膜FR4を除去する。これにより、半導体基板1Sni貫通電極TREと接続部CNTを形成することができる。

【0107】

次に、図43に示すように、半導体基板1Sから支持基板SBを引き剥がす。例えば、熱可塑性の接着材BAであれば、半導体基板1Sと支持基板SBを加熱することにより、半導体基板1Sから支持基板SBを引き剥がす。

【0108】

続いて、半導体基板1Sをブレードダイシングによって半導体チップへ個片化する。半導体チップへの個片化は、支持基板SBに半導体基板1Swo貼り付けた状態でも実施できるが、支持基板SBごと切断してしまう。ハンドリングは難しくなるが、支持基板SBを半導体基板1Sから剥がしてダイシングすることにより、支持基板SBの再利用が可能となる。

【0109】

最後に、図44に示すように、半導体基板1Sの主面(素子形成面、下面)に形成されているパッド上にバンプ電極BMPを形成する。バンプ電極BMPを形成する方法としては、例えば、スタッドバンプ法がある。その他の形成方法としては、ソルダペーストバンプ法、めっき法、あるいは、蒸着法などがある。以上のようにして、貫通電極TREと接続部CNTを形成した半導体装置を製造することができる。

【0110】

次に、貫通電極TREと接続部CNTを形成した複数の半導体チップを電気的に接続しながら、3次元的に積層する接続例について説明する。

【0111】

図45は、例えば、マイコンチップから構成される半導体チップCHP1と、SDRAMを形成した半導体チップCHP2とを積層する前の様子を示す図である。図45において、配線基板WB上に半導体チップCHP1が搭載され、この半導体チップCHP1上に再配線を行なうインターポーザIPを介して半導体チップCHP2が搭載される。半導体チップCHP1は矩形形状(四角形状)をしており、半導体チップCHP1の周辺部(辺)に沿って貫通電極と接続部CNT(CHP1)が形成されている。同様に、インターポーザIPも矩形形状(四角形状)をしており、インターポーザIPの周辺部(辺)に沿って貫通電極(バンプ電極BMP(IP))と接続部CNT(IP)が形成されている。そして、半導体チップCHP2も矩形形状(四角形状)をしており、半導体チップCHP2の周辺部(辺)に沿って貫通電極(バンプ電極BMP(CHP2))と接続部が形成されている。例えば、半導体チップCHP1、インターポーザIPおよび半導体チップCHP2に形成されている複数の貫通電極(バンプ電極BMP(IP)、バンプ電極BMP(CHP2))と接続部CNT(CHP1)や接続部CNT(IP)は、ペリフェラル配置で配置されているが、これらの配置はペリフェラル配置に限定されない。このように構成された半導体チップCHP1、インターポーザIPおよび半導体チップCHP2は、例えば、半導体チップCHP1に形成された接続部CNT(CHP1)へインターポーザIPに形成されたバンプ電極BMP(IP)を挿入し、かつ、インターポーザIPに形成された接続部CNT(IP)へ半導体チップCHP2に形成されたバンプ電極BMP(CHP2)を挿入することで、半導体チップCHP1、インターポーザIPおよび半導体チップCHP2を電気的に接続しながら、3次元的に積層することができる。

【0112】

図46は、配線基板WB上に半導体チップCHP1を搭載し、半導体チップCHP1上にインターポーザIPを介して半導体チップCHP2を搭載した積層構造を示す断面図である。図46に示すように、配線基板WBに形成された端子TEに、半導体チップCHP1のバンプ電極BMP(CHP1)が接続されている。そして、半導体チップCHP1に形成された接続部CNT(CHP1)に、インターポーザIPに形成されたバンプ電極BMP(IP)が挿入されている。さらに、インターポーザIPに形成された接続部CNT(IP)に半導体チップCHP2のバンプ電極BMP(CHP2)が挿入されている。これにより、配線基板WB,半導体チップCHP1、インターポーザIPおよび半導体チップCHP2を電気的に接続しながら、3次元的に積層することができる。

【0113】

本実施の形態2では、接続部にバンプ電極を挿入し、かつ、接続部を構成する空洞部に突き出るように配置された梁の変形による復元力でバンプ電極を固定するように構成している。このため、本実施の形態2では、半田を使用せずに、バンプ電極を接続部へ機械的に固定することができる。したがって、バンプ電極と接続部の接続に半田を使用しないので、接続部およびバンプ電極の高密度化や狭ピッチ化が行なわれても、隣接する接続部間や隣接するバンプ電極間でのショート不良を抑制できる。言い換えれば、本実施の形態2では、バンプ電極と接続部との接続に溶融した半田を使用しないために、半田ブリッジによるショート不良を抑制することができ、半導体装置の信頼性を向上することができる。

【0114】

このとき、本実施の形態2では、梁の構成をいわゆる平等強さの梁構造とすることにより(第3特徴点)、梁の強度を確保することができ、接続部の信頼性を向上することができる。

【0115】

さらに、配線基板WBと半導体チップCHP1の間、半導体チップCHP1とインターポーザIPの間、および、インターポーザIPと半導体チップCHP2の間には、アンダーフィルUFが注入されている。本実施の形態2では、接続部を構成する開口部の輪郭形状が、空洞部に突き出ている梁の根元から先端部に至る形状を縁取る形状を有し、隣接する梁の間において、梁の根元から先端部に至るまで大きく開口されている形状をしていることから(第2特徴点)、接続部にバンプ電極を挿入した後も、各梁の根元に隙間が生じている。したがって、アンダーフィルUFを注入すると、梁の根元に生じている隙間を介してアンダーフィルUFが接続部の内部にまで充填される。このため、接続部とこの接続部に挿入されているバンプ電極との接続強度を向上することができる。

【0116】

以上、本発明者によってなされた発明をその実施の形態に基づき具体的に説明したが、本発明は前記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることは言うまでもない。

【産業上の利用可能性】

【0117】

本発明は、半導体装置を製造する製造業に幅広く利用することができる。

【符号の説明】

【0118】

1S 半導体基板

2S 半導体基板

AF 金膜

BM 梁

BM2 梁

BMP バンプ電極

BMP1 バンプ電極

BMP2 バンプ電極

BMP3 バンプ電極

BMP(IP) バンプ電極

BMP(CHP1) バンプ電極

BMP(CHP2) バンプ電極

CA 空洞部

CF 銅膜

CHP1 半導体チップ

CHP2 半導体チップ

CNT 接続部

CNT2 接続部

CNT(CHP1) 接続部

CNT(IP) 接続部

CON 導体膜

FR1 レジスト膜

FR2 レジスト膜

FR3 レジスト膜

FR4 レジスト膜

H1 孔

H2 孔

IF1 絶縁膜

IL 層間絶縁膜

IL2 層間絶縁膜

IP インターポーザ

NF ニッケル膜

OP 開口部

OPT 開口部

OP2 開口部

OP3 開口部

PD パッド

SL スリット

TE 端子

TRE 貫通電極

UF アンダーフィル

WB 配線基板

【特許請求の範囲】

【請求項1】

(a)第1基板と、

(b)前記第1基板上に形成され、かつ、パターニングされた第1導体膜と、

(c)前記第1導体膜に形成された空洞部と、

(d)前記第1導体膜上に形成され、かつ、一部が前記空洞部に突き出るようにパターニングされた第2導体膜と、

(e)前記第2導体膜に形成された開口部とを備え、

平面的に前記開口部が前記空洞部に内包され、かつ、前記開口部と前記空洞部が一体化され、かつ、前記第2導体膜のうち前記空洞部に突き出た部分が梁として機能する半導体装置であって、

前記開口部の輪郭形状は、前記空洞部に突き出ている前記梁の根元から先端部に至る形状を縁取る形状を有し、前記開口部の平面上の面積は、前記梁の平面上の面積よりも大きいことを特徴とする半導体装置。

【請求項2】

請求項1記載の半導体装置であって、

前記開口部は、前記空洞部を形成する際のエッチング孔として機能することを特徴とする半導体装置。

【請求項3】

請求項1記載の半導体装置であって、

前記梁の幅は、前記梁の先端部から前記梁の根元に向って大きくなっていることを特徴とする半導体装置。

【請求項4】

請求項1記載の半導体装置であって、

パターニングされた前記第1導体膜と、一部が前記空洞部に突き出るようにパターニングされた前記第2導体膜とは、配線を構成していることを特徴とする半導体装置。

【請求項5】

請求項4記載の半導体装置であって、

前記第1導体膜は、銅膜から形成され、前記第2導体膜は、ニッケル膜から形成されていることを特徴とする半導体装置。

【請求項6】

請求項4記載の半導体装置であって、

前記第2導体膜上に第3導体膜が形成されていることを特徴とする半導体装置。

【請求項7】

請求項6記載の半導体装置であって、

前記第3導体膜は、金膜から形成されていることを特徴とする半導体装置。

【請求項8】

請求項1記載の半導体装置であって、

前記第1基板は、半導体チップと接続する配線基板であることを特徴とする半導体装置。

【請求項9】

請求項1記載の半導体装置であって、

前記第1基板は、半導体基板であることを特徴とする半導体装置。

【請求項10】

請求項1記載の半導体装置であって、

さらに、バンプ電極が形成された第2基板を有し、

前記第2基板に形成されている前記バンプ電極を、前記第1基板に形成されている前記梁を介して、前記第1基板に形成されている前記空洞部に挿入することにより、前記梁の復元力で前記梁と前記バンプ電極とを接続して、前記第1基板と前記第2基板を電気的に接続し、かつ、前記第1基板と前記第2基板とを積層することを特徴とする半導体装置。

【請求項11】

請求項10記載の半導体装置であって、

前記空洞部には、アンダーフィルが充填されていることを特徴とする半導体装置。

【請求項12】

請求項10記載の半導体装置であって、

前記空洞部に突き出ている前記梁は複数存在し、

1つの前記梁の先端部と他の1つの前記梁の先端部との間の距離をa、

前記バンプ電極の先端部の径をb、

前記空洞部に突き出ている前記梁の長さをc、

前記空洞部の深さをdとする場合、

条件a<b、かつ、条件c<dを満たすことを特徴とする半導体装置。

【請求項13】

(a)第1半導体基板と、

(b)前記第1半導体基板の裏面から前記裏面とは反対側の素子形成面に達する孔と、

(c)前記孔内を含む前記第1半導体基板の前記裏面に形成され、かつ、パターニングされた第1導体膜と、

(d)前記第1半導体基板の前記裏面に形成されている前記第1導体膜に形成された空洞部と、

(e)前記第1導体膜上に形成され、かつ、一部が前記空洞部に突き出るようにパターニングされた第2導体膜と、

(f)前記第2導体膜に形成された開口部とを備え、

平面的に前記開口部が前記空洞部に内包され、かつ、前記開口部と前記空洞部が一体化され、かつ、前記第2導体膜のうち前記空洞部に突き出た部分が梁として機能する半導体装置であって、

前記開口部の輪郭形状は、前記空洞部に突き出ている前記梁の根元から先端部に至る形状を縁取る形状を有し、前記開口部の平面上の面積は、前記梁の平面上の面積よりも大きいことを特徴とする半導体装置。

【請求項14】

請求項13記載の半導体装置であって、

前記開口部は、前記空洞部を形成する際のエッチング孔として機能することを特徴とする半導体装置。

【請求項15】

請求項13記載の半導体装置であって、

前記梁の幅は、前記梁の先端部から前記梁の根元に向かって大きくなっていることを特徴とする半導体装置。

【請求項16】

請求項13記載の半導体装置であって、

さらに、バンプ電極が形成された第2半導体基板を有し、

前記第2半導体基板に形成されている前記バンプ電極を、前記第1半導体基板に形成されている前記梁を介して、前記第1半導体基板に形成されている前記空洞部に挿入することにより、前記梁の復元力で前記梁と前記バンプ電極とを接続して、前記第1半導体基板と前記第2半導体基板を電気的に接続し、かつ、前記第1半導体基板と前記第2半導体基板とを積層することを特徴とする半導体装置。

【請求項17】

請求項16記載の半導体装置であって、

前記空洞部には、アンダーフィルが充填されていることを特徴とする半導体装置。

【請求項18】

(a)第1基板の第1面上に第1導体膜を形成する工程と、

(b)前記第1導体膜上に第2導体膜を形成する工程と、

(c)前記第2導体膜を貫通する開口部を形成する工程と、

(d)前記開口部をエッチング孔として前記第1導体膜をウェットエッチングすることにより、前記第1導体膜に空洞部を形成する工程とを備え、

平面的に前記開口部が前記空洞部に内包され、かつ、前記開口部と前記空洞部が一体化され、かつ、前記第2導体膜のうち前記空洞部に突き出た部分が梁となる半導体装置の製造方法であって、

前記開口部の輪郭形状は、前記空洞部に突き出ている前記梁の根元から先端部に至る形状を縁取る形状を有し、前記開口部の平面上の面積は、前記梁の平面上の面積よりも大きいことを特徴とする半導体装置の製造方法。

【請求項19】

請求項18記載の半導体装置の製造方法であって、

前記(b)工程後、前記(c)工程前に、

(e)前記第2導体膜上に第3導体膜を形成する工程と、

(f)前記第3導体膜に前記開口部を形成する工程とを有し、

前記(c)工程は、前記第3導体膜に形成された前記開口部から露出する前記第2導体膜を除去することにより、前記第2導体膜を貫通する前記開口部を形成することを特徴とする半導体装置の製造方法。

【請求項20】

請求項19記載の半導体装置の製造方法であって、

前記(a)工程で形成される前記第1導体膜を銅膜から形成し、

前記(b)工程で形成される前記第2導体膜をニッケル膜から形成し、

前記(e)工程で形成される前記第3導体膜を金膜から形成することを特徴とする半導体装置の製造方法。

【請求項21】

請求項18記載の半導体装置の製造方法であって、さらに、

(g)バンプ電極を形成した第2基板を用意する工程と、

(h)前記(d)工程後、前記第2基板に形成されている前記バンプ電極を、前記第1基板に形成されている前記梁を介して、前記第1基板に形成されている前記空洞部に挿入することにより、前記梁の復元力で前記梁と前記バンプ電極とを接続して、前記第1基板と前記第2基板を電気的に接続し、かつ、前記第1基板と前記第2基板とを積層する工程とを有することを特徴とする半導体装置の製造方法。

【請求項22】

請求項21記載の半導体装置の製造方法であって、

さらに、前記(h)工程後、

(i)前記空洞部にアンダーフィルを充填する工程を有することを特徴とする半導体装置の製造方法。

【請求項23】

(a)第1半導体基板の裏面から前記裏面とは反対側の素子形成面に形成された電極に達する孔を形成する工程と、

(b)前記孔内を含む前記第1半導体基板の前記裏面上に第1導体膜を形成する工程と、

(c)前記第1導体膜上に第2導体膜を形成する工程と、

(d)前記第2導体膜をパターニングすることにより、前記第1半導体基板の前記裏面に形成されている前記第2導体膜に開口部を形成する工程と、

(e)前記開口部をエッチング孔として前記第1導体膜をウェットエッチングすることにより、前記第1導体膜に空洞部を形成する工程とを備え、

平面的に前記開口部が前記空洞部に内包され、かつ、前記開口部と前記空洞部が一体化され、かつ、前記第2導体膜のうち前記空洞部に突き出た部分が梁となる半導体装置の製造方法であって、

前記開口部の輪郭形状は、前記空洞部に突き出ている前記梁の根元から先端部に至る形状を縁取る形状を有し、前記開口部の平面上の面積は、前記梁の平面上の面積よりも大きいことを特徴とする半導体装置の製造方法。

【請求項24】

請求項23記載の半導体装置の製造方法であって、

前記(c)工程後、前記(d)工程前に、

(f)前記第2導体膜上に第3導体膜を形成する工程と、

(g)前記第3導体膜に前記開口部を形成する工程とを有し、

前記(d)工程は、前記第3導体膜に形成された前記開口部から露出する前記第2導体膜を除去することにより、前記第2導体膜を貫通する前記開口部を形成することを特徴とする半導体装置の製造方法。

【請求項25】

請求項24記載の半導体装置の製造方法であって、

前記(b)工程で形成される前記第1導体膜を銅膜から形成し、

前記(c)工程で形成される前記第2導体膜をニッケル膜から形成し、

前記(f)工程で形成される前記第3導体膜を金膜から形成することを特徴とする半導体装置の製造方法。

【請求項26】

請求項23記載の半導体装置の製造方法であって、さらに、

(h)バンプ電極を形成した第2半導体基板を用意する工程と、

(i)前記(e)工程後、前記第2半導体基板に形成されている前記バンプ電極を、前記第1半導体基板に形成されている前記梁を介して、前記第1半導体基板に形成されている前記空洞部に挿入することにより、前記梁の復元力で前記梁と前記バンプ電極とを接続して、前記第1半導体基板と前記第2半導体基板を電気的に接続し、かつ、前記第1半導体基板と前記第2半導体基板とを積層する工程とを有することを特徴とする半導体装置の製造方法。

【請求項27】

請求項26記載の半導体装置の製造方法であって、

さらに、前記(i)工程後、

(j)前記空洞部にアンダーフィルを充填する工程を有することを特徴とする半導体装置の製造方法。

【請求項1】

(a)第1基板と、

(b)前記第1基板上に形成され、かつ、パターニングされた第1導体膜と、

(c)前記第1導体膜に形成された空洞部と、

(d)前記第1導体膜上に形成され、かつ、一部が前記空洞部に突き出るようにパターニングされた第2導体膜と、

(e)前記第2導体膜に形成された開口部とを備え、

平面的に前記開口部が前記空洞部に内包され、かつ、前記開口部と前記空洞部が一体化され、かつ、前記第2導体膜のうち前記空洞部に突き出た部分が梁として機能する半導体装置であって、

前記開口部の輪郭形状は、前記空洞部に突き出ている前記梁の根元から先端部に至る形状を縁取る形状を有し、前記開口部の平面上の面積は、前記梁の平面上の面積よりも大きいことを特徴とする半導体装置。

【請求項2】

請求項1記載の半導体装置であって、

前記開口部は、前記空洞部を形成する際のエッチング孔として機能することを特徴とする半導体装置。

【請求項3】

請求項1記載の半導体装置であって、

前記梁の幅は、前記梁の先端部から前記梁の根元に向って大きくなっていることを特徴とする半導体装置。

【請求項4】

請求項1記載の半導体装置であって、

パターニングされた前記第1導体膜と、一部が前記空洞部に突き出るようにパターニングされた前記第2導体膜とは、配線を構成していることを特徴とする半導体装置。

【請求項5】

請求項4記載の半導体装置であって、

前記第1導体膜は、銅膜から形成され、前記第2導体膜は、ニッケル膜から形成されていることを特徴とする半導体装置。

【請求項6】

請求項4記載の半導体装置であって、

前記第2導体膜上に第3導体膜が形成されていることを特徴とする半導体装置。

【請求項7】

請求項6記載の半導体装置であって、

前記第3導体膜は、金膜から形成されていることを特徴とする半導体装置。

【請求項8】

請求項1記載の半導体装置であって、

前記第1基板は、半導体チップと接続する配線基板であることを特徴とする半導体装置。

【請求項9】

請求項1記載の半導体装置であって、

前記第1基板は、半導体基板であることを特徴とする半導体装置。

【請求項10】

請求項1記載の半導体装置であって、

さらに、バンプ電極が形成された第2基板を有し、

前記第2基板に形成されている前記バンプ電極を、前記第1基板に形成されている前記梁を介して、前記第1基板に形成されている前記空洞部に挿入することにより、前記梁の復元力で前記梁と前記バンプ電極とを接続して、前記第1基板と前記第2基板を電気的に接続し、かつ、前記第1基板と前記第2基板とを積層することを特徴とする半導体装置。

【請求項11】

請求項10記載の半導体装置であって、

前記空洞部には、アンダーフィルが充填されていることを特徴とする半導体装置。

【請求項12】

請求項10記載の半導体装置であって、

前記空洞部に突き出ている前記梁は複数存在し、

1つの前記梁の先端部と他の1つの前記梁の先端部との間の距離をa、

前記バンプ電極の先端部の径をb、

前記空洞部に突き出ている前記梁の長さをc、

前記空洞部の深さをdとする場合、

条件a<b、かつ、条件c<dを満たすことを特徴とする半導体装置。

【請求項13】

(a)第1半導体基板と、

(b)前記第1半導体基板の裏面から前記裏面とは反対側の素子形成面に達する孔と、

(c)前記孔内を含む前記第1半導体基板の前記裏面に形成され、かつ、パターニングされた第1導体膜と、

(d)前記第1半導体基板の前記裏面に形成されている前記第1導体膜に形成された空洞部と、

(e)前記第1導体膜上に形成され、かつ、一部が前記空洞部に突き出るようにパターニングされた第2導体膜と、

(f)前記第2導体膜に形成された開口部とを備え、

平面的に前記開口部が前記空洞部に内包され、かつ、前記開口部と前記空洞部が一体化され、かつ、前記第2導体膜のうち前記空洞部に突き出た部分が梁として機能する半導体装置であって、

前記開口部の輪郭形状は、前記空洞部に突き出ている前記梁の根元から先端部に至る形状を縁取る形状を有し、前記開口部の平面上の面積は、前記梁の平面上の面積よりも大きいことを特徴とする半導体装置。

【請求項14】

請求項13記載の半導体装置であって、

前記開口部は、前記空洞部を形成する際のエッチング孔として機能することを特徴とする半導体装置。

【請求項15】

請求項13記載の半導体装置であって、

前記梁の幅は、前記梁の先端部から前記梁の根元に向かって大きくなっていることを特徴とする半導体装置。

【請求項16】

請求項13記載の半導体装置であって、

さらに、バンプ電極が形成された第2半導体基板を有し、

前記第2半導体基板に形成されている前記バンプ電極を、前記第1半導体基板に形成されている前記梁を介して、前記第1半導体基板に形成されている前記空洞部に挿入することにより、前記梁の復元力で前記梁と前記バンプ電極とを接続して、前記第1半導体基板と前記第2半導体基板を電気的に接続し、かつ、前記第1半導体基板と前記第2半導体基板とを積層することを特徴とする半導体装置。

【請求項17】

請求項16記載の半導体装置であって、

前記空洞部には、アンダーフィルが充填されていることを特徴とする半導体装置。

【請求項18】

(a)第1基板の第1面上に第1導体膜を形成する工程と、

(b)前記第1導体膜上に第2導体膜を形成する工程と、

(c)前記第2導体膜を貫通する開口部を形成する工程と、

(d)前記開口部をエッチング孔として前記第1導体膜をウェットエッチングすることにより、前記第1導体膜に空洞部を形成する工程とを備え、

平面的に前記開口部が前記空洞部に内包され、かつ、前記開口部と前記空洞部が一体化され、かつ、前記第2導体膜のうち前記空洞部に突き出た部分が梁となる半導体装置の製造方法であって、