半導体装置およびその製造方法

【課題】誘電率が低くかつ金属との密着性に優れた絶縁層を有する半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、基板(シリコン基板)と、基板上に設けられており、炭素−炭素結合を有し、かつ炭素原子数とシリコン原子数との比(C/Si)が2以上である、多孔質SiOCH膜12bと、多孔質SiOCH膜12bに設けられた凹部と、凹部を埋め込むように設けられた金属膜(Cu膜22b)と、Cu膜22bと接しており、凹部内の多孔質SiOCH膜12bの表面に設けられた、改質層31bと、を備え、改質層31bは、多孔質SiOCH膜12bの内部と比較して、C/Si比が小さく、かつO/Si比が同等である。

【解決手段】半導体装置は、基板(シリコン基板)と、基板上に設けられており、炭素−炭素結合を有し、かつ炭素原子数とシリコン原子数との比(C/Si)が2以上である、多孔質SiOCH膜12bと、多孔質SiOCH膜12bに設けられた凹部と、凹部を埋め込むように設けられた金属膜(Cu膜22b)と、Cu膜22bと接しており、凹部内の多孔質SiOCH膜12bの表面に設けられた、改質層31bと、を備え、改質層31bは、多孔質SiOCH膜12bの内部と比較して、C/Si比が小さく、かつO/Si比が同等である。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置およびその製造方法に関する。

【背景技術】

【0002】

微細化と高速化が進む昨今の半導体装置においては、配線の寄生抵抗や寄生容量による信号遅延が深刻になっている。このため、層間絶縁膜中に金属配線を有する多層配線構造の半導体装置においては、金属配線として低抵抗な銅(Cu)を用い、層間絶縁膜として低誘電率の材料を用いることが一般的になっている。この中で、層間絶縁膜については、様々な低誘電率の材料が検討されている。

【0003】

元来、層間絶縁膜は、シリコン酸化膜で構成されていた。この層間絶縁膜の誘電率を低減するには、分極率の高いシリコンと酸素の結合(Si−O)を減少させることが有効である。これを実現するために、フッ素(F)や炭素(C)を膜中に導入することが検討された。

【0004】

もう一つの層間絶縁膜の低誘電率化の手法としては、膜中に空孔を導入する手法が用いられる。空孔は、ほぼ空気の誘電率である1を示す。このため、層間絶縁膜の誘電率を大きく下げることができる。膜中に空孔を導入するには、まず、ポロジェン(発泡剤)を膜中に含有させ、この膜に熱、紫外線(UV)照射、電子線(EB)照射等を処理する。これにより、膜中のポロジェンを脱離させる。そして、ポロジェンの脱離によって、膜中に空孔が残されることになる。

【0005】

このように層間絶縁膜は、低誘電率という特性が求められる一方で、金属配線との密着性も求められている。密着性が低いと、金属配線の剥離が生じることがあり、半導体装置の信頼性が低下することがあった。

【0006】

特許文献1には、SiO2―CH3で構成されるMSQについて、炭素を引き抜くように改質する技術が記載されている。炭素を引き抜くことにより、Si―CH3結合を、Si−H結合に置換する。そして、改質層表面を親水性にすることにより、金属膜との密着性を向上できると記載されている。同文献には、改質層の膜厚が14nm(C濃度が7%以下)のとき、スクラッチが低減され、すなわち、密着性が向上すると記載されている。

【0007】

特許文献2には、多孔質MSQ膜を用いた配線構造において、配線溝やビア等の開口部の側壁に保護膜を形成する技術が記載されている。開口部の底部をプラズマでたたき、その成分を、開口部の側壁に成膜させる。これにより、開口部の側壁上に緻密な保護膜を形成できると記載されている。

【0008】

特許文献3には、シリコン、酸素、炭素を含む絶縁膜の表層に酸素を導入して、酸素と炭素とを置換し、高密度な低炭素濃度の改質層を形成することが記載されている。改質層は、酸素原子数が多いので、金属との密着力が向上すると記載されている。

【先行技術文献】

【特許文献】

【0009】

【特許文献1】特開2003−309170号公報

【特許文献2】特開2005−217162号公報

【特許文献3】国際公開第2007/132879号パンフレット

【発明の概要】

【発明が解決しようとする課題】

【0010】

層間絶縁膜の誘電率を下げるには、(i)誘電率が低い材料を用いること、(ii)誘電率の高い部分の膜厚を薄くすることの両方を満たすことが必要である。そして、本発明者が検討した結果、この(i)且つ(ii)の低誘電率化を満たすとともに、金属膜との密着性とを満たすというトレードオフの関係を改善することが困難であることが見出された。

【0011】

特許文献1に記載の技術では、低炭素濃度の改質MSQにおいては、膜厚が10nm以下となるような条件では、バリアメタルの剥離を完全に抑制できていないことが記載されている。一方、バリアメタルの剥離を抑制するためには、改質MSQの膜厚を厚くする必要があることが記載されている。このように、特許文献1に記載の技術では、(ii)誘電率の高い改質層の膜厚を薄くすることと、金属膜との密着性とのトレードオフを改善するのが困難であった。

【0012】

これに対して、特許文献3には、表層に酸素を導入して、酸素と炭素とを置換し、高密度な低炭素濃度の改質層を形成する。これにより、改質層の膜厚を薄くしたまま、改質層の密着性を向上させることができると記載されている。

しかしながら、積極的に酸素を導入することで、表面がシリコン酸化膜(SiO2)に類似の膜構造となる。このため、誘電率の極端な増大をもたらすことになる。

このように、特許文献3に記載の技術では、(i)誘電率が低い改質層を用いることと、金属膜との密着性とのトレードオフを改善するのが困難であった。

【0013】

なお、特許文献2に記載の技術においては、配線を形成する溝底が激しくエッチングされるため、深刻な損傷が発生する。これにより、底荒れ、誘電率増大等が発生する。また、この技術は配線溝底に対する強化策とはなっていない。このため、配線溝底での金属配線との密着強度が課題として残る。

【課題を解決するための手段】

【0014】

C―C結合は、C―Si結合に対して優先して切断される。このため、C−C結合を有する多孔質SiOCH膜を改質する際、C―Si結合を残しつつ、C―C結合の結合を切断して炭素を引き抜くことができる。そして、深さ方向(膜厚方向)に、切断対象が、C―C結合の分だけ増加するので、C―Si結合を残しつつも、改質層の膜厚を薄くすることができる。また、C―Si結合を残すことにより、分極率の高いSi−OH結合への変化を抑制できるので、誘電率を低く抑えることができる。

以上を背景に本発明者は以下に示す本発明を想到するに至った。

【0015】

すなわち、本発明によれば、

基板上に、炭素−炭素結合を有し、かつ炭素原子数とシリコン原子数との比(C/Si)が2以上である、多孔質SiOCH膜を形成する工程と、

前記多孔質SiOCH膜に凹部を形成する工程と、

前記凹部内の前記多孔質SiOCH膜の表面に、前記多孔質SiOCH膜の内部と比較して、C/Si比が小さく、かつO/Si比が同等な改質層を形成する工程と、

前記凹部に金属膜を埋め込む工程と、を含む、半導体装置の製造方法が提供される。

【0016】

多孔質SiOCH膜は、炭素−炭素結合を有する。改質層形成工程においては、多孔質SiOCH膜においては、炭素原子は、C―C結合から引き抜かれ、C―Si結合が残る。このため、改質層は、多孔質SiOCH膜と比較して炭素濃度が低くなる(C/Si比が小さくなる)ものの、C―Si結合が残るので誘電率の上昇を抑制できる。また、切断対象が、C―C結合の分だけ増加するので、改質層の膜厚を薄くすることができる。さらに、改質層では、酸素が導入されないので、多孔質SiOCH膜と同程度のO/Si比となっており、誘電率の上昇が抑制されている。

このように、改質層は、改質層の低誘電率が低くかつその膜厚が薄い。このため、多孔質SiOCH膜全体の誘電率を低く抑えることができる。

一方、改質層においては、炭素濃度が低くなり、疎水性が低下するので、金属膜との密着性が向上する。

【0017】

また、本発明によれば、

基板と、

前記基板上に設けられており、炭素−炭素結合を有し、かつ炭素原子数とシリコン原子数との比(C/Si)が2以上である、多孔質SiOCH膜と、

前記多孔質SiOCH膜に設けられた凹部と、

前記凹部を埋め込むように設けられた金属膜と、

前記金属膜と接しており、前記凹部内の前記多孔質SiOCH膜の表面に設けられた、改質層と、を備え、

前記改質層は、前記多孔質SiOCH膜の内部と比較して、C/Si比が小さく、かつO/Si比が同等である、半導体装置が提供される。

【0018】

改質層は、多孔質SiOCH膜と比較して炭素濃度が低く(C/Si比が小さい)。多孔質SiOCH膜は、炭素−炭素結合を有する。このため、改質層では、炭素原子は、C―C結合から引き抜かれ、C―Si結合が残っている。このため、切断対象が、C―C結合の分だけ増加しているので、改質層の膜厚は薄くなっている。また、C―Si結合が残るので、改質層の誘電率の上昇が抑制されている。さらに、改質層では、多孔質SiOCH膜と同程度のO/Si比となっており、酸素が導入されないので、誘電率の上昇が抑制されている。

このように、改質層は、改質層の低誘電率が低くかつその膜厚が薄い。このため、多孔質SiOCH膜全体の誘電率を低く抑えることができる。

一方、改質層は、炭素濃度が低い。このため、改質層においては、疎水性が低下するので、金属膜との密着性が向上する。

【発明の効果】

【0019】

本発明によれば、誘電率が低くかつ金属との密着性に優れた絶縁層を有する半導体装置およびその製造方法が提供される。

【図面の簡単な説明】

【0020】

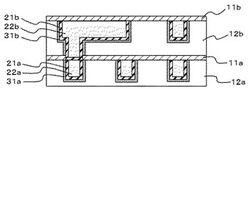

【図1】本実施の形態の半導体装置を模式的に示す断面構造図。

【図2】配線溝底を示す断面写真。

【図3】C/Si組成比と比誘電率上昇率との関係を示す図。

【図4】C/Si組成比の深さ方向分布を示す図。

【図5】半導体パッケージの超音波顕微鏡写真。

【図6】半導体パッケージの異常部の断面解析写真。

【図7】バリア金属膜と多孔質SiOCH膜の密着強度を示す図。

【図8】本実施の形態の半導体装置の製造方法を示す工程断面図。

【図9】本実施の形態の半導体装置の製造方法を示す工程断面図。

【図10】本実施の形態の半導体装置の製造方法を示す工程断面図。

【図11】本実施の形態の半導体装置の製造方法を示す工程断面図。

【図12】本実施の形態の半導体装置の製造方法を示す工程断面図。

【図13】本実施の形態の半導体パッケージの実装方法を示す図。

【図14】本実施の形態の半導体パッケージの実装方法を示す図。

【発明を実施するための形態】

【0021】

以下、本発明の実施の形態について、図面を用いて説明する。尚、すべての図面において、同様な構成要素には同様の符号を付し、適宜説明を省略する。

【0022】

(半導体装置)

図1は、本実施の形態の半導体装置の模式的な断面図を示す。

本実施の形態の半導体装置は、基板(シリコン基板)と、基板上に設けられており、炭素−炭素結合を有し、かつ炭素原子数とシリコン原子数との比(C/Si)が2以上である、多孔質SiOCH膜12bと、多孔質SiOCH膜12bに設けられた凹部と、凹部を埋め込むように設けられた金属膜(Cu膜22b)と、Cu膜22bと接しており、凹部内の多孔質SiOCH膜12bの表面に設けられた、改質層31bと、を備え、改質層31bは、多孔質SiOCH膜12bの内部と比較して、C/Si比が小さく、かつO/Si比が同等である。

【0023】

図1に示すように、本実施の形態の半導体装置は、不図示の半導体基板(シリコン基板)上に形成され、配線(銅配線)および絶縁層(層間絶縁膜)により構成された配線層が複数積層された多層配線層を有する。多孔質SiOCH膜12a、12b(第1の層間絶縁膜および第2の層間絶縁膜)には、それぞれ複数の配線溝が形成されている。各配線溝にCu膜22a、22b(第1の金属配線および第2の金属配線)が埋め込まれている。第1の金属配線(Cu膜22a)と第2の金属配線(Cu膜22b)は電気的に接続されている。Cu膜22bはデュアルダマシン構造を有してもよいが、シングルダマシン構造を有してもよい。各配線溝内には、Cu膜22a、Cu膜22bを覆うようにバリア金属膜21a、21bが形成されている。このバリア金属膜21a、21bと接する部分に、改質層31a、31bが形成されている。すなわち、改質層31aは、配線溝の底部および側壁部を覆うように形成されている。この改質層31aの断面形状は、コの字やU字状等とすることができる。一方、改質層31bは、例えば、配線溝の側壁部を覆うように形成されている。この改質層31bの断面形状は、ハの字状等とすることができる。改質層31a、31bは、それぞれ多孔質SiOCH膜12a、12bを改質することにより得られる。多孔質SiOCH膜12aと多孔質SiOCH膜12bとの間には、キャップ絶縁膜11aが形成されている。一方、多孔質SiOCH膜12b上およびCu膜22b上には、キャップ絶縁膜11bが形成されている。

【0024】

本実施の形態の半導体装置においては、多孔質SiOCH膜の改質層において、改質層の低誘電率が低くかつその膜厚が薄い。このため、多孔質SiOCH膜全体の実効的な誘電率を低く抑えることができる。多孔質SiOCH膜の表層において、改質層の炭素濃度が低いため、疎水性が低下する。このため、改質と金属膜との密着性が向上する。これにより、銅配線と多孔質SiOCH膜との密着強度を改善し、半導体チップをパッケージに実装する際の配線層の剥離や破壊を抑制することができる。

【0025】

(多孔質SiOCH膜)

本実施の形態に係る多孔質SiOCH膜は、半導体素子を接続する多層配線間を絶縁しながら寄生容量を低減する膜として機能する。この多孔質SiOCH膜は、環状有機シロキサンを含む。

環状有機シロキサンは、環状シロキサン構造と、その側鎖に炭化水素基を有する。

環状シロキサンは、Si−O(シロキサン結合)を1ユニットとして数えた場合に、複数のユニットからなる環状構造を有する。この環状シロキサンは、同数のシリコン(Si)原子と酸素(O)原子が交互に連なった環状構造を有する。環状構造としては、例えば、3員環、4員環、5員環が挙げられる。環状構造としては、密着性の観点から、空孔径が小さい3員環が好ましい。

一方、炭化水素基としては、炭素−炭素結合を有する限り、特に限定されない。すなわち、炭化水素基としては、環状シロキサンは、シリコン原子に対して、炭素(C)原子を2個以上含む側鎖(炭化水素基)を、少なくとも1個以上有する。

このように本実施の形態に係る多孔質SiOCH膜においては、C/Si組成比は2以上である。

【0026】

一方、本実施の形態に係る多孔質SiOCH膜は、個々の空孔が接続されていない独立空孔で構成されている。ここで、多孔質SiOCH膜の空孔の形成メカニズムを説明する。多孔質SiOCH膜の膜中の空孔の起源は、環状シロキサン骨格にある。このため、多孔質SiOCH膜は、個々の空孔が接続されていない独立空孔によって多孔質化されている。言い換えると、本実施の形態では、ポロジェンを脱離させて多孔質化するプロセスが不要となる。したがって、本実施の形態に係る多孔質SiOCH膜には、脱離に起因する連続空孔が形成されない。

【0027】

多孔質SiOCH膜は、下記式(1)で表される構造を有する環状有機シロキサン化合物を用いて得られる。例えば、多孔質SiOCH膜は、プラズマ重合法により得られる。これにより、空孔径が小さい多孔質SiOCH膜が形成される。

【0028】

【化1】

【0029】

式(1)中、R1およびR2は、それぞれ同一または異なってよく、少なくとも一方が、置換又は無置換の炭素−炭素結合を有する炭化水素基(メチル基以外であり、炭素原子を少なくとも2個以上含有する)を示す。炭化水素基としては、直鎖もしくは分枝のアルキル基、環状のアルキル基、アルケニル基等が挙げられる。

アルキル基としては、例えば、1〜8の炭素数を有するアルキル基である。アルキル基の一例としては、メチル基、エチル基、プロピル基、イソプロピル基、ブチル基等が挙げられる。

アルケニル基としては、例えば、1〜8の炭素数を有するアルケニル基である。アルケニル基の一例としては、ビニル基、アリル基等である。

【0030】

前記環状有機シロキサン構造を有する化合物が、R1が不飽和炭化水素基であり、R2が飽和炭化水素基であってもよい。この場合、R1の不飽和炭化水素基のプラズマ重合反応により環状シロキサンを結合させた低誘電率絶縁膜を成長できる。具体的には、R1がビニル基であり、R2が立体障害の大きな分岐構造を有する飽和炭化水素基であり、例えばイソプロピル基(下記式(2)で表される環状有機シロキサン構造)を有する化合物であってもよい。側鎖R2の立体障害が大きいことにより膜密度を減らし、比誘電率を低減させることができるので望ましい。なお、立体障害の大きな分岐構造を有する飽和炭化水素(R2)としては、イソブチル、ターシャリーブチル等でもよいことは自明である。

【0031】

【化2】

【0032】

また、多孔質SiOCH膜は、上記式(2)に示す環状有機シロキサン構造を有する化合物を材料に用いて、プラズマCVD法により形成することができる。このとき、多孔質SiOCH膜は、平均空孔径が1nm以下、例えば、0.3〜0.7nmである小さい空孔構造を有することができる。

平均空孔径は、小角エックス線散乱法や陽電子消滅法、高分解能の電子顕微鏡観察等により測定することができる。

【0033】

多孔質SiOCH膜の誘電率は、特に限定されないが、例えば2.7以下であり、より好ましくは2.6以下とすることができ、一方、2.0以上であり、2.2以上とすることができる。

また、多孔質SiOCH膜におけるC/Si比率は、例えば、2以上であり、よりこのましくは3以上とすることができ、一方、20以下、5以下とすることができる。このC/Si比率を上記範囲内とすることにより、改質層の膜厚を薄くできる、また改質層の誘電率を低減できる。

【0034】

(改質層)

本実施の形態に係る改質層は、多孔質SiOCH膜の表層を改質処理することにより形成される。改質処理には、例えば、プラズマ処理を用いることができる。これにより、多孔質SiOCH膜の表層の炭素を引き抜くことができる。そして、炭素濃度が低い改質層が形成される。

本実施の形態に係るプラズマ処理では、Cを脱離させることが目的であり、OやSiの含有量の変動を抑制するものである。このプラズマ処理においては、He、Ar、Ne、Xe等の希ガス、あるいはN2等の不活性ガスを用いたプラズマを用いることが望ましい。そして、プラズマ処理においては、OやSiを含むプラズマガスを用いない。このようにして得られた改質層は、多孔質SiOCH膜よりもC/Si比が低く、かつO/Si比が同等となる。

【0035】

ここで、本実施の形態に係る改質層においては、(i)改質層の誘電率が低いこと、かつ(ii)改質層の膜厚を薄くすることの両方を満たすとともに、金属膜との密着性が向上することを説明する。

【0036】

まず、本発明者の知見によれば、プラズマ処理において、C―C結合が、C―Si結合に対して優先して切断されることが見出された。すなわち、プラズマのエネルギーが、主にC−C結合の切断に使用され、Si−CH3結合は切断されずに維持される。このため、深さ方向(膜厚方向)に、切断対象としてC―C結合の分だけ増加する(Siに複数の炭素を含有する高次のハイドロカーボン(CHx)が存在する)。これにより、炭素を引き抜く際、C―Si結合を残しつつも、改質層の膜厚を薄くすることができる。また、C―Si結合を残すことにより、分極率の高いSi−OH結合への変化を抑制できるので、誘電率を低く抑えることができる。このように、改質層の誘電率を低く保ったまま、その膜厚を薄くできる。

【0037】

さらに、本実施の形態に係る多孔質SiOCH膜は、独立空孔を有する。これにより、空孔を介したプラズマ粒子の打ち込みが発生しにくい。言い換えると、本実施の形態では、連続空孔の場合のように、プラズマ中の高エネルギー粒子が、空孔を介して膜の奥深くまで打ち込まれてしまうという現象を抑制できる。このため、改質層の膜厚を薄くすることができる。そのため、実効誘電率の上昇を抑制できる。

【0038】

一方、改質層においては、炭素濃度が低くなり、疎水性が低下するので、金属膜との密着性が向上する。また、改質層は、多孔質SiOCH膜由来の微細な独立空孔を有する。多孔質SiOCH膜に配線溝を形成する際、配線溝の底部または側壁部には独立空孔が現れる。この独立空孔は、ポロジェンで形成された空孔と比較して、非常に微細である。このため、配線溝の底部または側壁部は、ポロジェンによる連結空孔に起因した凹凸面と比較して、平坦になる。このため、改質層においては、その表面が平坦になるので、金属膜との密着性が向上する。

【0039】

改質層の膜厚は、誘電率の値が問題にならない限りにおいては限定されないが、例えば、10nm未満、より好ましくは5nm未満である。とくに、バリアメタル膜と多孔質SiOCH膜の密着強度を高める改質層を5nm未満に抑えることができる。

【0040】

以上の働きにより、膜の低誘電率を維持しながら、配線溝底での金属材料と低誘電率膜の密着強度を高め、チップを実装する際の応力による配線層の剥離や破壊を抑制することができる。

【0041】

ここで、多孔質SiOCH膜にプラズマ処理を施した際の影響について説明する。

【0042】

図2(a)は、ポロジェンを用いた多孔質SiOCH膜の配線構造の断面電子顕微鏡写真を示す。図2(b)は、本実施の形態に係る独立空孔型多孔質SiOCH膜の配線構造の断面電子顕微鏡写真を示す。

図2(a)に示すように、配線溝の底部に、ポロジェンの脱離により形成された連続空孔に由来する底荒れが観察される。このような配線溝底の荒れは、信頼性を大幅に劣化させることが知られている。また、プラズマ中の高エネルギー粒子が、連続空孔を介して膜の奥深くまで打ち込まれてしまうことにより、奥深くまでダメージが導入されていることも示唆されている。このため、ポロジェンを用いた場合では、実効的な誘電率の著しい上昇を招くことが分かった。

これに対して、本実施の形態に係る独立空孔型多孔質SiOCH膜では、図2(b)に示すように、配線溝底が極めて平坦であることが分かった。これにより、信頼性の劣化や誘電率の上昇を抑制することができる。

【0043】

図3は、本実施の形態に係る独立空孔型多孔質SiOCH膜(C/Si=2.5、比誘電率2.5)に対して、意図的にC/Si比を変化させた場合の比誘電率の上昇率を示す。

C/Si比が1.0から2.5の範囲で、比誘電率上昇率はC/Si比に対して線形に変化することがわかる。C/Si比が2.0以上であれば、C/Si=2.5の膜に対して5%未満の比誘電率上昇に抑えられる。このときの膜の誘電率は2.6未満である。

本実施の形態において、誘電率は、水銀プローブを用いた容量測定結果と、光学測定に基づくSiOCH膜厚から算出した。容量値およびSiOCH膜厚の測定には、ともにシリコン基板上にSiOCH膜を成膜したサンプルを用いた。容量測定は、絶縁膜に印加される電界が0.1乃至10MV/cm、好ましくは1MV/cmとなるようにバイアスを印加し、周波数を1kHz乃至10MHz、好ましくは10kHz乃至1MHzの条件下で実施した。

【0044】

図4は、Heプラズマ処理の有無による、独立空孔型多孔質SiOCH膜表面付近のC/Si比分布を測定した結果を示す。ここで、He処理条件としては、室温、Heガス流量を200sccm、圧力を0.1Torr、プラズマ生成用高周波電源(2MHz)の電力を800W、30秒間という条件を用いた。また、炭素原子やシリコン原子等の組成分析については、光電子分光法(XPS)もしくはラザフォード後方散乱法(RBS)等を用いた。He処理の有無によらず、TaN/Ta積層膜に続いて、Cuを成膜して界面部分の組成を分析している。

Heプラズマ処理を行う場合について説明する。界面付近の25nm程度までの間で、C組成のプロファイルが減少していることが分かる(炭素が抜けている)。すなわち、金属膜と改質層との界面から、5nm以上離れた領域では、例えば、界面から5nm以上25nm以下の範囲では、C/Si組成比は2.0以上である。このため、前述のように、比誘電率の上昇は抑制できることがわかる。また、界面付近5nm未満の組成は、界面の揺らぎにより正確に測定できていない。しかしながら、C/Si比が2未満となるまでCが減少している領域があるとしても、その厚さは5nm未満であることがわかる。すなわち、多孔質SiOCH膜の内部の誘電率と比較して、高い誘電率を有する改質層の膜厚を非常に薄くすることができる。例えば、改質層の膜厚を5nm未満に抑えることができる。

【0045】

ここで、前述のように、膜の比誘電率は、Si−C結合が切断される量と、その深さに関係して上昇する。本実施の形態に係る独立空孔型多孔質SiOCH膜では、側鎖に複数の炭素原子を有する環状シロキサン構造を有している。このため、側鎖の複数のC原子間の結合が優先的に切断される。これにより、ハイドロカーボンが減少するが、側鎖の炭素原子が減少した結果、炭素原子1個の側鎖であるSi−C結合は保存される。そのため、比誘電率上昇が抑えられる。かつ、独立空孔の効果も合わせて、C/Si比が2未満になるまでCが減少する領域は、少なくとも5nm未満に抑えられる。

【0046】

このように、本実施の形態では、C/Si比が2.0未満となる改質層の厚さは5nm未満に抑えることができる。現在、検討されているCu配線の配線間スペースは50nmを下回るようになっている。このような微細化において、C/Si比が2.0未満となる改質層をその10%未満(膜厚が5nm未満)に抑えることは、寄生容量の上昇を抑制する上できわめて重要である。

【0047】

図5に、改質処理を行わない独立空孔型多孔質SiOCH膜を用いた多層配線を有する半導体チップを、フリップチップパッケージに封入した後の超音波顕微鏡写真を示す。図中の黒丸は、はんだバンプ部を示している。図には、一部を拡大した写真も示している。この拡大写真中において、バンプ部中央に白点が見られる異常なバンプ40が見られる。この部分のチップ側の断面を、電子顕微鏡で観察した結果が図6である。この図から、異常バンプの直下では、Cu配線(Cu膜22c)と独立空孔型多孔質SiOCH膜12cの間で剥離が生じていることがわかる。これにより、改質処理を行わない独立空孔型多孔質SiOCH膜においては、金属配線との密着強度が不十分であることが示唆された。

【0048】

図7に、バリア金属膜と独立空孔型SiOCH膜の間の密着強度について、バリア金属膜を形成する前に実施するHeプラズマ処理の有無で比較した結果を示す。ここで、バリア金属は、TaとTaNの積層膜としており、PVD法にて形成している。また、Heプラズマ処理は、PVD成膜チャンバと真空搬送室を介したチャンバを用いる。

図7に示すように、He処理を行うことによって、大幅に密着強度が改善することがわかる。このことは、独立空孔型SiOCH膜の表面の炭素が脱離したことによって、無機膜との密着強度が改善したことを示している。

本実施の形態においては、密着強度は、特に限定されないが、例えば0.13MPa/m2以上0.3MPa/m2以下とすることができる。

ここでは、密着強度の測定を、mELT(Modified Edge−Lift Test)法により行うが、この他にも、4−Point Bebding法などの手法を用いることも可能である。ただし、測定方法によって、得られる物理量が異なる。

このような、改質層を設けることにより、フリップチップ実装時に見られた、バリア金属と多孔質環状シロキサン界面での剥離によるバンプ部の異常を抑制することができる。

【0049】

(半導体装置の製造方法)

次に、本実施の形態の半導体装置の製造方法として、第1例について説明する。

図8および図9は、第1例の半導体装置の製造方法の工程断面図を示す。

本実施の形態の半導体装置の製造方法は、基板(シリコン基板)上に、炭素−炭素結合を有し、かつ炭素原子数とシリコン原子数との比(C/Si)が2以上である、多孔質SiOCH膜12bを形成する工程と、多孔質SiOCH膜12bに凹部(配線溝15や配線孔16)を形成する工程と、凹部内の多孔質SiOCH膜12bの表面に、多孔質SiOCH膜12bの内部と比較して、C/Si比が小さく、かつO/Si比が同等な改質層31bを形成する工程と、凹部に金属膜(Cu膜22b)を埋め込む工程と、を含む。

本例では、下部配線層上に上部配線層を形成する工程について説明する。

【0050】

まず、図8(a)に示すように、不図示の半導体基板(シリコン基板)上に下部配線層を形成する。下層配線層は、第1の層間絶縁膜(多孔質SiOCH膜12a)と、第1の層間絶縁膜中に、埋め込まれた金属配線(Cu膜22a)とから構成される。この多孔質SiOCH膜12aの表面には、改質層31aが形成されている。そして、この改質層31aとCu膜22aとの間に、バリア金属膜21aが形成されている。また、多孔質SiOCH膜12a上およびCu膜22a上には、キャップ絶縁膜11aが形成されている。この下層配線も、後述する上層配線と同様のプロセスおよび材料により形成できる。

【0051】

続いて、図8(b)に示すように、下層配線のキャップ絶縁膜11a上に、多孔質SiOCH膜12b、およびハードマスク13bをこの順で形成する。

【0052】

ここで、多孔質SiOCH膜12bを成膜する方法について説明する。

本実施の形態では、原料モノマーとして、下記式(2)で示す環状有機シロキサン構造を有する化合物を用いる。まず、原料モノマーを、キャリアガスのHeと混合して、気化器に送り込む。この原料モノマーの流量は、液体マスフローコントローラで制御する。続いて、原料モノマーを、気化器で液体から気体へと気化させる。気化した原料モノマーを含む原料ガスを、反応室内に導入する。そして、反応室内に、13.56MHzの高周波電力を印加する。反応室内で、原料ガスのプラズマが生成する。そして、化学気相成長により環状シロキサン膜(多孔質SiOCH膜12b)を、基板上に成膜する。原料モノマーの供給量は、0.1g/min以上10g/min以下であることが好ましく、さらに好ましくは2g/min以下である。キャリアガスであるHe流量は、50sccm以上5000sccm以下であることが好ましく、さらに好ましくは2000sccm以下である。リアクター(気化器)内の圧力は133〜1333Paであることが好ましい。RF電源の出力は2000W以下であることが好ましく、さらに好ましくは1000W以下である。このとき、キャリアガスとして、酸素を含まないガスを用いることができる。

【0053】

【化3】

【0054】

ハードマスク13bには、多孔質SiOCH膜よりもC濃度が少なく、酸素濃度が多い膜を用いる。例えば、ハードマスク膜13bとしては、SiO2、SiN、SiOCH等を用いることができる。ハードマスク膜13bの形成には、例えば、プラズマCVD法を用いる。

【0055】

続いて、図8(c)に示すように、多孔質SiOCH膜12bに、凹部(配線溝15、配線孔16)を形成する。これらの凹部は、ハードマスク13bを貫通する。配線溝15の底部には、キャップ絶縁膜11aが露出している。一方、配線孔16の底部は、多孔質SiOCH膜12bの内部の一部に形成されている。配線溝15と配線孔16との最接近距離(配線間スペース)としては、特に限定されないが、例えば、50nm以下とすることができる。凹部の形成には、例えば、リソグラフィー法と異方性エッチング法を用いる。異方性エッチング法としては、例えば、ウエットエッチングまたはドライエッチングを用いることができる。

【0056】

次いで、図8(d)に示すように、配線溝15の側壁、配線孔16の側壁および底部の多孔質SiOCH膜12bの表面に改質処理を行う。これにより、多孔質SiOCH膜12bの表面に、C濃度が低減した改質層31bを形成する。このとき、配線溝15の底部におけるキャップ絶縁膜11aが除去される。そして、配線溝15の底部に、Cu膜22aの表面が露出する。

【0057】

改質処理には、例えば、プラズマ処理を用いる。プラズマ処理条件としては、例えば、室温、Heガス流量を200sccm、圧力を0.1Torr、プラズマ生成用高周波(2MHz)電源の電力を800W、30秒間とすることができる。ここで、ガスは、Heに限定されるものではなく、Ne、Ar、Xe等の希ガスや、希ガスとHを混合したガス、あるいはN2等の不活性ガスを用いてもよい。特に、プラズマ中にOを含まないようにすることが重要である。プラズマ処理条件については、ガス流量10〜1000sccm、圧力0.01〜0.5Torr、プラズマ発生用高周波電源パワー100〜2000W、時間は5〜90秒に設定すればよい。また、放電開始時に基板側に13.56MHzの100〜1000Wのバイアスを印加することで放電開始を促進すると効果的である。

【0058】

続いて、図9(a)に示すように、配線溝15および配線孔16の内部にバリア金属膜21bを形成する。そして、配線溝15および配線孔16を埋め込むように、金属膜(Cu膜22b)を多孔質SiOCH膜12b上およびバリア金属膜21b上に形成する。

【0059】

バリア金属膜21は、配線金属を構成する金属元素が層間絶縁膜や下層へ拡散することを防止する機能を有する。また、バリア金属膜21bは、バリア性を有する導電性膜である。バリア金属膜21bとしては、例えば、配線金属がCuを主成分とする場合には、タンタル(Ta)、ルネニウム(Ru)、窒化タンタル(TaN)、窒化チタン(TiN)、炭窒化タングステン(WCN)のような高融点金属やその窒化物等が用いられる。また、これらの材料を用いた積層の膜であってもよい。本実施の形態では、バリア金属膜21bとしては、TaNとTaの積層膜を用いる。バリア金属膜21bの形成方法としては、例えばPVD法を用いる。なお、バリア金属の形成方法は、PVD法に限定されるものではなく、有機金属材料を用いたCVD法等で形成してもよい。また、前述のプラズマ処理工程とバリア金属膜の成膜工程の間は、真空中で行う必要がある。これにより、Heプラズマ処理後に、一旦大気中に取り出すと、Heプラズマ処理によって活性となった表面に水分等が付着することを防止できる。その後、成膜するバリア金属膜との密着強度が劣化するだけでなく、実効的な誘電率の上昇をもたらすことを抑制できる。

【0060】

次いで、Cu粒成長のための熱処理を施す。この熱処理の温度は、例えば200〜400℃、時間は30秒〜1時間に設定する。

【0061】

続いて、図9(b)に示すように、凹部(配線溝15および配線孔16)の外部に露出したCu膜22b、バリア膜21b、およびハードマスク13bを除去する。除去には、化学機械研磨(Chemical Mechanical Polishing:CMP)等の研磨技術を用いる。多孔質SiOCH膜12bおよびCu膜22bが露出した状態でCMPを停止する。

【0062】

Cu膜22bは、凹部(配線溝15、配線孔16)の内壁面に形成されたバリア金属膜21bで覆われている。このCu膜22bは、バリア金属膜21bを介して改質層31bと接合している。

Cu膜22bは、Cuを主成分とする銅含有配線である。信頼性を向上させるため、Cu膜22bには、Cu以外の金属元素、例えばAl等が含まれていてもよい。また、Cu以外の金属元素が、Cu膜22bの上面や側面等に形成されていてもよい。

【0063】

続いて、図9(c)に示すように、露出している多孔質SiOCH膜12bおよびCu膜22bの表面に、キャップ絶縁膜11bを成膜する。これにより、上部配線層の配線工程を終了する。キャップ絶縁膜11bの形成方法としては、例えば、プラズマCVD法を用いることができる。

【0064】

キャップ絶縁膜11bは、Cu膜22bに含まれるCuの酸化や絶縁膜中へのCuの拡散を防ぐ機能、および加工時にエッチングストップ層としての役割を有する。キャップ絶縁膜11bの誘電率を低くすることで、配線信号伝達遅延が改善できる。キャップ絶縁膜11bは、バリア絶縁膜としても機能する。キャップ絶縁膜11bとしては、SiN、SiC、SiCNおよびCu拡散バリア性を有する有機シロキサン膜等を用いることができる。また、キャップ絶縁膜11は、不飽和炭化水素とアモルファスカーボンを有する膜、またはSiN膜、SiCN膜、およびSiC膜のうち少なくとも一つを用いた膜と不飽和炭化水素およびアモルファスカーボンを有する膜との積層膜であってもよい。キャップ絶縁膜11bは、これらの膜を2種類以上積層してもよい。

【0065】

本実施の形態では、図8(b)〜図9(c)で示された工程を繰り返すことで、多層配線構造を形成することができる。また、本実施の形態では、配線溝と配線孔を同時に形成するデュアルダマシン法を用いて説明したが、シングルダマシン法を用いた配線形成であってもよい。

以上により、本実施の形態の半導体チップを得ることができる。

【0066】

また、多層配線を有する半導体チップを、電子機器に搭載するためには、外部回路との接続を行うための組立工程あるいは実装工程を経て、パッケージ中に封入されることが多い。パッケージへの封入の仕方には、複数の方法がある。ここでは、代表的な二種類のパッケージ手法を説明する。

【0067】

一つは、ワイヤボンディングと呼ばれる手法であり、図13に示すような接続形態をとる。すなわち、半導体チップ51aの最上層の金属層で形成されたボンディングパッド(図示せず)とパッケージ基板52a上のボンディングパッド(図示せず)をボンディングワイヤ55で接続する方法である。半導体チップ51aは、裏面側でパッケージ基板52aに接着され、封入樹脂53a内に封入される。また、パッケージ基板52aには、外部回路と接続するための外部接続端子54aが設けられている。

【0068】

もう一つの手法は、フリップチップ接続と呼ばれる手法であり、図14に示すような接続形態をとる。半導体チップ51bの最上層の金属層で形成されたパッド(図示せず)上にはんだバンプ56を形成し、はんだバンプ56が下側に向くように裏返し、パッケージ基板52b上に形成されたはんだバンプ57と接合させる手法である。はんだバンプ同士を接触させ、加熱してはんだを溶融させて接合する。この際、接合後の冷却過程で半導体チップとパッケージ基板の熱膨張係数の違いによって、接合部に応力が加わることが知られている。なお、半導体チップ51bは封止樹脂53bで封入されることもあり、半導体基板52bの裏面には、外部回路と接続するための外部接続端子54bが設けられている。

以上により、本実施の形態の半導体装置を得ることができる。

【0069】

次に、本実施の形態の作用効果について説明する。

【0070】

本実施の形態においては、多孔質SiOCH膜は、炭素−炭素結合を有する。改質層形成工程においては、多孔質SiOCH膜においては、炭素原子は、C―C結合から引き抜かれ、C―Si結合が残る。このため、改質層は、多孔質SiOCH膜と比較して炭素濃度が低くなる(C/Si比が小さくなる)ものの、C―Si結合が残るので誘電率を低減できる。また、切断対象が、C―C結合の分だけ増加するので、改質層の膜厚を薄くすることができる。さらに、改質層では、酸素が導入されないので、多孔質SiOCH膜と同程度のO/Si比となっており、誘電率の上昇が抑制されている。

このように、改質層は、改質層の低誘電率が低くかつその膜厚が薄い。このため、C/Siが2以上の多孔質SiOCH膜全体の誘電率を低く抑えることができる。

一方、改質層においては、炭素濃度が低くなり、疎水性が低下するので、金属膜との密着性が向上する。これにより、銅配線と多孔質SiOCH膜との密着強度を改善し、半導体チップをパッケージに実装する際の配線層の剥離や破壊を抑制することができる。

したがって、本実施の形態では、低誘電率化および金属膜との密着性の向上の両立を実現することができる。

【0071】

特許文献1では、低誘電率化に貢献するのはSiとCの結合であるが、C/Si比<1の場合に生成される低C濃度領域では、Si−C結合の量が減少して誘電率が上昇する。このとき、残留するSi−Cの量が、プラズマ処理条件によって不安定になり、誘電率の上昇率を制御することが難しくなる。

これに対して、本実施の形態では、SiにC原子を二個以上含む側鎖が形成されている。このため、C−C結合の切断によるC量の減少によって低C濃度層が形成される。したがって、低誘電率化に寄与するSi−C結合は保存されることになる。これにより、誘電率の上昇率を抑制できる。

【0072】

次に、本実施の形態の半導体装置の製造方法として、第2例について説明する。

図10は、第2例の半導体装置の製造方法の工程断面図を示す。

第2例の半導体装置の製造方法においては、多孔質SiOCH膜12a、12bの上面にも、改質層32a、32bを形成する以外は、第1例と同様にする。

【0073】

第2例では、キャップ絶縁膜11b成膜前に、同一チャンバ内でプラズマ処理を施す。これにより、露出している多孔質SiOCH膜12bの表面に、低炭層濃度の改質層32bを形成しつつ、露出しているCu膜22bの表面の清浄化処理を行うことができる。このため、キャップ絶縁膜11bとの密着強度を強化させつつ、信頼性の向上を図ることができる。また、改質層32bは、配線溝形成や、CMPにより配線材の研磨時等に、多孔質SiOCH膜12bの表面を保護する役割を果たす。このときの、プラズマ処理においては、Cu表面の還元性を高めるため、水素を含有するプラズマで行うことが好ましい。例えば、NH3、H2プラズマを用いることが効果的である。また、第2例においては、第1例と同様の効果が得られる。

【0074】

次に、本実施の形態の半導体装置の製造方法として、第3例について説明する。

図11および図12は、第3例の半導体装置の製造方法の工程断面図を示す。

第3例の半導体装置の製造方法においては、ハードマスク膜13a、13bを、多孔質SiOCH膜12a、12bの上面の一部に残す以外は、第1例と同様にする。

【0075】

図11(a)は、本実施の形態の半導体装置における下層配線層の断面を示している。この下層配層線も、後述する上層配線層と同様のプロセスおよび材料により形成できる。

【0076】

図11(b)に示すように、下層配線のキャップ絶縁膜11a上に多孔質SiOCH膜12b、およびハードマスク13bを形成する。

【0077】

多孔質SiOCH膜は、同数のシリコン(Si)原子と酸素(O)原子が交互に連なった環状構造(環状シロキサン構造)を含み、それぞれのシリコン原子に属する側鎖として、炭素(C)原子を2個以上含む側鎖が少なくとも1個存在しているモノマーを原料として用いる。まず、原料モノマーを、キャリアガスのHeと混合して、気化器に送り込む。この原料モノマーの流量は、液体マスフローコントローラで制御する。続いて、原料モノマーを、気化器で液体から気体へと気化させる。気化した原料モノマーを含む原料ガスを、反応室内に導入する。そして、反応室内に、13.56MHzの高周波電力を印加する。反応室内で、原料ガスのプラズマが生成する。そして、化学気相成長により環状シロキサン膜(多孔質SiOCH膜12b)を、基板上に成膜する。原料モノマーの供給量は、0.1g/min以上10g/min以下であることが好ましく、さらに好ましくは2g/min以下である。キャリアガスであるHe流量は、50sccm以上5000sccm以下であることが好ましく、さらに好ましくは2000sccm以下である。リアクター(気化器)内の圧力は133〜1333Paであることが好ましい。RF電源の出力は2000W以下であることが好ましく、さらに好ましくは1000W以下である。このとき、キャリアガスとして、酸素を含まないガスを用いることができる。

【0078】

このようにして形成された独立空孔型多孔質SiOCH膜12b中に存在するC/Si組成比は2以上である。

【0079】

多孔質SiOCH膜12b上に形成するハードマスク13bには、多孔質SiOCH膜よりもC濃度が少なく、酸素濃度が多い膜を用いる。例えば、SiO2、SiN、SiOCH等が用いられる。また、ハードマスク膜13bは、下層をSiOCH、上層をSiO2といった多層構造を用いてもよい。ハードマスク膜13bは、例えば、プラズマCVD法で形成する。

【0080】

続いて、図11(c)に示すように、リソグラフィーと異方性エッチングによって、ハードマスク13bおよび多孔質SiOCH膜12b(環状シロキサン膜)に、凹部(配線溝15、配線孔16)を形成する。

【0081】

次いで、図11(d)に示すように、プラズマ処理によって、配線溝15の側面や配線孔16の側面、底面の多孔質SiOCH膜12bの表面を改質する。これにより、多孔質SiOCH膜12bの表層に、C濃度が低減した改質層31bを形成する。プラズマ処理条件としては、例えば、室温、Heガス流量を200sccm、圧力を0.1Torr、プラズマ生成用高周波(2MHz)電源の電力を800W、30秒間という条件を用いる。ここで、ガスは、Heに限定されるものではなく、Ne、Ar、Xe等の希ガスや、希ガスとHを混合したガス、あるいはN2等の不活性ガスを用いてもよい。特に、プラズマ中にOを含まないようにすることが重要である。プラズマ処理条件については、周波数200kHz〜100MHz、ガス流量10〜1000sccm、圧力0.01〜0.5Torr、プラズマ発生用高周波電源パワー100〜2000W、時間は5〜90秒に設定すればよい。また、放電開始時に基板側に200kHz〜100MHzの100〜1000Wのバイアスを印加することで放電開始を促進すると効果的である。

【0082】

続いて、図12(a)に示すように、配線溝15および配線孔16内に、バリア金属膜としてTaNとTaの積層膜をPVD法により形成する。引き続き、配線溝や配線孔にCu膜22bを埋設する。次いで、Cu粒成長のための熱処理を施す。この熱処理の温度は、例えば200〜400℃、時間は30秒〜1時間に設定する。

【0083】

続いて、図12(b)に示すように、CMP等の研磨技術を用い、凹部の外部に露出したCu膜22b、バリア膜21b、およびハードマスクの13bの一部を除去する。これにより、Cuが露出していない領域ではハードマスク13bが、多孔質SiOCH膜12bを被覆している。すなわち、多孔質SiOCH膜12bの上面は、Cu膜22bまたはハードマスク膜13bにより覆われている。ここで、ハードマスク膜13bをSiO2とSiOCHの二層構成とした場合には、表面側のSiO2のみを研磨し、SiOCHが露出した段階でCMPを停止する等を行ってもよい。

【0084】

続いて、図12(c)に示すように、露出しているハードマスク膜13b、およびCu膜22bの表面にキャップ絶縁膜11bを成膜する。キャップ絶縁膜としては、プラズマCVD法によって成膜するSiN、SiC、SiCN等を用いる。これらの膜の2種類以上を積層してもよい。

【0085】

図11(b)〜図12(c)で示された工程を繰り返すことで、多層配線構造を形成することができる。また、本実施の形態では、配線溝と配線孔を同時に形成するデュアルダマシン法を用いて説明したが、シングルダマシン法を用いた配線形成であってもよい。

以上により、本実施の形態の半導体チップを得ることができる。

【0086】

キャップ絶縁膜11bと多孔質SiOCH膜12b(多孔質環状シロキサン膜)との間に、多孔質環状シロキサン膜よりも炭素濃度が少なく、かつ空孔を含有しないハードマスク膜13bが設けられている。ハードマスク膜13bは、配線溝形成や、CMPにより配線材の研磨時等に、多孔質SiOCH膜12bの表面を保護する役割を担う。また、第3例においては、第1例と同様の効果が得られる。

【0087】

以上、図面を参照して本発明の実施形態について述べたが、これらは本発明の例示であり、上記以外の様々な構成を採用することもできる。

【符号の説明】

【0088】

11a、11b キャップ絶縁膜

12a、12b、12c 多孔質SiOCH膜

13a、13b ハードマスク膜

15 配線溝

16 配線孔

21a、21b バリア金属膜

22a、22b、22c Cu膜

31a、31b 改質層

32a、32b 改質層

40 異常なバンプ

51a、51b 半導体チップ

52a、52b パッケージ基板

53a、53b 封入樹脂

54a、54b 外部接続端子

55 ボンディングワイヤ

56 はんだバンプ

57 はんだバンプ

【技術分野】

【0001】

本発明は、半導体装置およびその製造方法に関する。

【背景技術】

【0002】

微細化と高速化が進む昨今の半導体装置においては、配線の寄生抵抗や寄生容量による信号遅延が深刻になっている。このため、層間絶縁膜中に金属配線を有する多層配線構造の半導体装置においては、金属配線として低抵抗な銅(Cu)を用い、層間絶縁膜として低誘電率の材料を用いることが一般的になっている。この中で、層間絶縁膜については、様々な低誘電率の材料が検討されている。

【0003】

元来、層間絶縁膜は、シリコン酸化膜で構成されていた。この層間絶縁膜の誘電率を低減するには、分極率の高いシリコンと酸素の結合(Si−O)を減少させることが有効である。これを実現するために、フッ素(F)や炭素(C)を膜中に導入することが検討された。

【0004】

もう一つの層間絶縁膜の低誘電率化の手法としては、膜中に空孔を導入する手法が用いられる。空孔は、ほぼ空気の誘電率である1を示す。このため、層間絶縁膜の誘電率を大きく下げることができる。膜中に空孔を導入するには、まず、ポロジェン(発泡剤)を膜中に含有させ、この膜に熱、紫外線(UV)照射、電子線(EB)照射等を処理する。これにより、膜中のポロジェンを脱離させる。そして、ポロジェンの脱離によって、膜中に空孔が残されることになる。

【0005】

このように層間絶縁膜は、低誘電率という特性が求められる一方で、金属配線との密着性も求められている。密着性が低いと、金属配線の剥離が生じることがあり、半導体装置の信頼性が低下することがあった。

【0006】

特許文献1には、SiO2―CH3で構成されるMSQについて、炭素を引き抜くように改質する技術が記載されている。炭素を引き抜くことにより、Si―CH3結合を、Si−H結合に置換する。そして、改質層表面を親水性にすることにより、金属膜との密着性を向上できると記載されている。同文献には、改質層の膜厚が14nm(C濃度が7%以下)のとき、スクラッチが低減され、すなわち、密着性が向上すると記載されている。

【0007】

特許文献2には、多孔質MSQ膜を用いた配線構造において、配線溝やビア等の開口部の側壁に保護膜を形成する技術が記載されている。開口部の底部をプラズマでたたき、その成分を、開口部の側壁に成膜させる。これにより、開口部の側壁上に緻密な保護膜を形成できると記載されている。

【0008】

特許文献3には、シリコン、酸素、炭素を含む絶縁膜の表層に酸素を導入して、酸素と炭素とを置換し、高密度な低炭素濃度の改質層を形成することが記載されている。改質層は、酸素原子数が多いので、金属との密着力が向上すると記載されている。

【先行技術文献】

【特許文献】

【0009】

【特許文献1】特開2003−309170号公報

【特許文献2】特開2005−217162号公報

【特許文献3】国際公開第2007/132879号パンフレット

【発明の概要】

【発明が解決しようとする課題】

【0010】

層間絶縁膜の誘電率を下げるには、(i)誘電率が低い材料を用いること、(ii)誘電率の高い部分の膜厚を薄くすることの両方を満たすことが必要である。そして、本発明者が検討した結果、この(i)且つ(ii)の低誘電率化を満たすとともに、金属膜との密着性とを満たすというトレードオフの関係を改善することが困難であることが見出された。

【0011】

特許文献1に記載の技術では、低炭素濃度の改質MSQにおいては、膜厚が10nm以下となるような条件では、バリアメタルの剥離を完全に抑制できていないことが記載されている。一方、バリアメタルの剥離を抑制するためには、改質MSQの膜厚を厚くする必要があることが記載されている。このように、特許文献1に記載の技術では、(ii)誘電率の高い改質層の膜厚を薄くすることと、金属膜との密着性とのトレードオフを改善するのが困難であった。

【0012】

これに対して、特許文献3には、表層に酸素を導入して、酸素と炭素とを置換し、高密度な低炭素濃度の改質層を形成する。これにより、改質層の膜厚を薄くしたまま、改質層の密着性を向上させることができると記載されている。

しかしながら、積極的に酸素を導入することで、表面がシリコン酸化膜(SiO2)に類似の膜構造となる。このため、誘電率の極端な増大をもたらすことになる。

このように、特許文献3に記載の技術では、(i)誘電率が低い改質層を用いることと、金属膜との密着性とのトレードオフを改善するのが困難であった。

【0013】

なお、特許文献2に記載の技術においては、配線を形成する溝底が激しくエッチングされるため、深刻な損傷が発生する。これにより、底荒れ、誘電率増大等が発生する。また、この技術は配線溝底に対する強化策とはなっていない。このため、配線溝底での金属配線との密着強度が課題として残る。

【課題を解決するための手段】

【0014】

C―C結合は、C―Si結合に対して優先して切断される。このため、C−C結合を有する多孔質SiOCH膜を改質する際、C―Si結合を残しつつ、C―C結合の結合を切断して炭素を引き抜くことができる。そして、深さ方向(膜厚方向)に、切断対象が、C―C結合の分だけ増加するので、C―Si結合を残しつつも、改質層の膜厚を薄くすることができる。また、C―Si結合を残すことにより、分極率の高いSi−OH結合への変化を抑制できるので、誘電率を低く抑えることができる。

以上を背景に本発明者は以下に示す本発明を想到するに至った。

【0015】

すなわち、本発明によれば、

基板上に、炭素−炭素結合を有し、かつ炭素原子数とシリコン原子数との比(C/Si)が2以上である、多孔質SiOCH膜を形成する工程と、

前記多孔質SiOCH膜に凹部を形成する工程と、

前記凹部内の前記多孔質SiOCH膜の表面に、前記多孔質SiOCH膜の内部と比較して、C/Si比が小さく、かつO/Si比が同等な改質層を形成する工程と、

前記凹部に金属膜を埋め込む工程と、を含む、半導体装置の製造方法が提供される。

【0016】

多孔質SiOCH膜は、炭素−炭素結合を有する。改質層形成工程においては、多孔質SiOCH膜においては、炭素原子は、C―C結合から引き抜かれ、C―Si結合が残る。このため、改質層は、多孔質SiOCH膜と比較して炭素濃度が低くなる(C/Si比が小さくなる)ものの、C―Si結合が残るので誘電率の上昇を抑制できる。また、切断対象が、C―C結合の分だけ増加するので、改質層の膜厚を薄くすることができる。さらに、改質層では、酸素が導入されないので、多孔質SiOCH膜と同程度のO/Si比となっており、誘電率の上昇が抑制されている。

このように、改質層は、改質層の低誘電率が低くかつその膜厚が薄い。このため、多孔質SiOCH膜全体の誘電率を低く抑えることができる。

一方、改質層においては、炭素濃度が低くなり、疎水性が低下するので、金属膜との密着性が向上する。

【0017】

また、本発明によれば、

基板と、

前記基板上に設けられており、炭素−炭素結合を有し、かつ炭素原子数とシリコン原子数との比(C/Si)が2以上である、多孔質SiOCH膜と、

前記多孔質SiOCH膜に設けられた凹部と、

前記凹部を埋め込むように設けられた金属膜と、

前記金属膜と接しており、前記凹部内の前記多孔質SiOCH膜の表面に設けられた、改質層と、を備え、

前記改質層は、前記多孔質SiOCH膜の内部と比較して、C/Si比が小さく、かつO/Si比が同等である、半導体装置が提供される。

【0018】

改質層は、多孔質SiOCH膜と比較して炭素濃度が低く(C/Si比が小さい)。多孔質SiOCH膜は、炭素−炭素結合を有する。このため、改質層では、炭素原子は、C―C結合から引き抜かれ、C―Si結合が残っている。このため、切断対象が、C―C結合の分だけ増加しているので、改質層の膜厚は薄くなっている。また、C―Si結合が残るので、改質層の誘電率の上昇が抑制されている。さらに、改質層では、多孔質SiOCH膜と同程度のO/Si比となっており、酸素が導入されないので、誘電率の上昇が抑制されている。

このように、改質層は、改質層の低誘電率が低くかつその膜厚が薄い。このため、多孔質SiOCH膜全体の誘電率を低く抑えることができる。

一方、改質層は、炭素濃度が低い。このため、改質層においては、疎水性が低下するので、金属膜との密着性が向上する。

【発明の効果】

【0019】

本発明によれば、誘電率が低くかつ金属との密着性に優れた絶縁層を有する半導体装置およびその製造方法が提供される。

【図面の簡単な説明】

【0020】

【図1】本実施の形態の半導体装置を模式的に示す断面構造図。

【図2】配線溝底を示す断面写真。

【図3】C/Si組成比と比誘電率上昇率との関係を示す図。

【図4】C/Si組成比の深さ方向分布を示す図。

【図5】半導体パッケージの超音波顕微鏡写真。

【図6】半導体パッケージの異常部の断面解析写真。

【図7】バリア金属膜と多孔質SiOCH膜の密着強度を示す図。

【図8】本実施の形態の半導体装置の製造方法を示す工程断面図。

【図9】本実施の形態の半導体装置の製造方法を示す工程断面図。

【図10】本実施の形態の半導体装置の製造方法を示す工程断面図。

【図11】本実施の形態の半導体装置の製造方法を示す工程断面図。

【図12】本実施の形態の半導体装置の製造方法を示す工程断面図。

【図13】本実施の形態の半導体パッケージの実装方法を示す図。

【図14】本実施の形態の半導体パッケージの実装方法を示す図。

【発明を実施するための形態】

【0021】

以下、本発明の実施の形態について、図面を用いて説明する。尚、すべての図面において、同様な構成要素には同様の符号を付し、適宜説明を省略する。

【0022】

(半導体装置)

図1は、本実施の形態の半導体装置の模式的な断面図を示す。

本実施の形態の半導体装置は、基板(シリコン基板)と、基板上に設けられており、炭素−炭素結合を有し、かつ炭素原子数とシリコン原子数との比(C/Si)が2以上である、多孔質SiOCH膜12bと、多孔質SiOCH膜12bに設けられた凹部と、凹部を埋め込むように設けられた金属膜(Cu膜22b)と、Cu膜22bと接しており、凹部内の多孔質SiOCH膜12bの表面に設けられた、改質層31bと、を備え、改質層31bは、多孔質SiOCH膜12bの内部と比較して、C/Si比が小さく、かつO/Si比が同等である。

【0023】

図1に示すように、本実施の形態の半導体装置は、不図示の半導体基板(シリコン基板)上に形成され、配線(銅配線)および絶縁層(層間絶縁膜)により構成された配線層が複数積層された多層配線層を有する。多孔質SiOCH膜12a、12b(第1の層間絶縁膜および第2の層間絶縁膜)には、それぞれ複数の配線溝が形成されている。各配線溝にCu膜22a、22b(第1の金属配線および第2の金属配線)が埋め込まれている。第1の金属配線(Cu膜22a)と第2の金属配線(Cu膜22b)は電気的に接続されている。Cu膜22bはデュアルダマシン構造を有してもよいが、シングルダマシン構造を有してもよい。各配線溝内には、Cu膜22a、Cu膜22bを覆うようにバリア金属膜21a、21bが形成されている。このバリア金属膜21a、21bと接する部分に、改質層31a、31bが形成されている。すなわち、改質層31aは、配線溝の底部および側壁部を覆うように形成されている。この改質層31aの断面形状は、コの字やU字状等とすることができる。一方、改質層31bは、例えば、配線溝の側壁部を覆うように形成されている。この改質層31bの断面形状は、ハの字状等とすることができる。改質層31a、31bは、それぞれ多孔質SiOCH膜12a、12bを改質することにより得られる。多孔質SiOCH膜12aと多孔質SiOCH膜12bとの間には、キャップ絶縁膜11aが形成されている。一方、多孔質SiOCH膜12b上およびCu膜22b上には、キャップ絶縁膜11bが形成されている。

【0024】

本実施の形態の半導体装置においては、多孔質SiOCH膜の改質層において、改質層の低誘電率が低くかつその膜厚が薄い。このため、多孔質SiOCH膜全体の実効的な誘電率を低く抑えることができる。多孔質SiOCH膜の表層において、改質層の炭素濃度が低いため、疎水性が低下する。このため、改質と金属膜との密着性が向上する。これにより、銅配線と多孔質SiOCH膜との密着強度を改善し、半導体チップをパッケージに実装する際の配線層の剥離や破壊を抑制することができる。

【0025】

(多孔質SiOCH膜)

本実施の形態に係る多孔質SiOCH膜は、半導体素子を接続する多層配線間を絶縁しながら寄生容量を低減する膜として機能する。この多孔質SiOCH膜は、環状有機シロキサンを含む。

環状有機シロキサンは、環状シロキサン構造と、その側鎖に炭化水素基を有する。

環状シロキサンは、Si−O(シロキサン結合)を1ユニットとして数えた場合に、複数のユニットからなる環状構造を有する。この環状シロキサンは、同数のシリコン(Si)原子と酸素(O)原子が交互に連なった環状構造を有する。環状構造としては、例えば、3員環、4員環、5員環が挙げられる。環状構造としては、密着性の観点から、空孔径が小さい3員環が好ましい。

一方、炭化水素基としては、炭素−炭素結合を有する限り、特に限定されない。すなわち、炭化水素基としては、環状シロキサンは、シリコン原子に対して、炭素(C)原子を2個以上含む側鎖(炭化水素基)を、少なくとも1個以上有する。

このように本実施の形態に係る多孔質SiOCH膜においては、C/Si組成比は2以上である。

【0026】

一方、本実施の形態に係る多孔質SiOCH膜は、個々の空孔が接続されていない独立空孔で構成されている。ここで、多孔質SiOCH膜の空孔の形成メカニズムを説明する。多孔質SiOCH膜の膜中の空孔の起源は、環状シロキサン骨格にある。このため、多孔質SiOCH膜は、個々の空孔が接続されていない独立空孔によって多孔質化されている。言い換えると、本実施の形態では、ポロジェンを脱離させて多孔質化するプロセスが不要となる。したがって、本実施の形態に係る多孔質SiOCH膜には、脱離に起因する連続空孔が形成されない。

【0027】

多孔質SiOCH膜は、下記式(1)で表される構造を有する環状有機シロキサン化合物を用いて得られる。例えば、多孔質SiOCH膜は、プラズマ重合法により得られる。これにより、空孔径が小さい多孔質SiOCH膜が形成される。

【0028】

【化1】

【0029】

式(1)中、R1およびR2は、それぞれ同一または異なってよく、少なくとも一方が、置換又は無置換の炭素−炭素結合を有する炭化水素基(メチル基以外であり、炭素原子を少なくとも2個以上含有する)を示す。炭化水素基としては、直鎖もしくは分枝のアルキル基、環状のアルキル基、アルケニル基等が挙げられる。

アルキル基としては、例えば、1〜8の炭素数を有するアルキル基である。アルキル基の一例としては、メチル基、エチル基、プロピル基、イソプロピル基、ブチル基等が挙げられる。

アルケニル基としては、例えば、1〜8の炭素数を有するアルケニル基である。アルケニル基の一例としては、ビニル基、アリル基等である。

【0030】

前記環状有機シロキサン構造を有する化合物が、R1が不飽和炭化水素基であり、R2が飽和炭化水素基であってもよい。この場合、R1の不飽和炭化水素基のプラズマ重合反応により環状シロキサンを結合させた低誘電率絶縁膜を成長できる。具体的には、R1がビニル基であり、R2が立体障害の大きな分岐構造を有する飽和炭化水素基であり、例えばイソプロピル基(下記式(2)で表される環状有機シロキサン構造)を有する化合物であってもよい。側鎖R2の立体障害が大きいことにより膜密度を減らし、比誘電率を低減させることができるので望ましい。なお、立体障害の大きな分岐構造を有する飽和炭化水素(R2)としては、イソブチル、ターシャリーブチル等でもよいことは自明である。

【0031】

【化2】

【0032】

また、多孔質SiOCH膜は、上記式(2)に示す環状有機シロキサン構造を有する化合物を材料に用いて、プラズマCVD法により形成することができる。このとき、多孔質SiOCH膜は、平均空孔径が1nm以下、例えば、0.3〜0.7nmである小さい空孔構造を有することができる。

平均空孔径は、小角エックス線散乱法や陽電子消滅法、高分解能の電子顕微鏡観察等により測定することができる。

【0033】

多孔質SiOCH膜の誘電率は、特に限定されないが、例えば2.7以下であり、より好ましくは2.6以下とすることができ、一方、2.0以上であり、2.2以上とすることができる。

また、多孔質SiOCH膜におけるC/Si比率は、例えば、2以上であり、よりこのましくは3以上とすることができ、一方、20以下、5以下とすることができる。このC/Si比率を上記範囲内とすることにより、改質層の膜厚を薄くできる、また改質層の誘電率を低減できる。

【0034】

(改質層)

本実施の形態に係る改質層は、多孔質SiOCH膜の表層を改質処理することにより形成される。改質処理には、例えば、プラズマ処理を用いることができる。これにより、多孔質SiOCH膜の表層の炭素を引き抜くことができる。そして、炭素濃度が低い改質層が形成される。

本実施の形態に係るプラズマ処理では、Cを脱離させることが目的であり、OやSiの含有量の変動を抑制するものである。このプラズマ処理においては、He、Ar、Ne、Xe等の希ガス、あるいはN2等の不活性ガスを用いたプラズマを用いることが望ましい。そして、プラズマ処理においては、OやSiを含むプラズマガスを用いない。このようにして得られた改質層は、多孔質SiOCH膜よりもC/Si比が低く、かつO/Si比が同等となる。

【0035】

ここで、本実施の形態に係る改質層においては、(i)改質層の誘電率が低いこと、かつ(ii)改質層の膜厚を薄くすることの両方を満たすとともに、金属膜との密着性が向上することを説明する。

【0036】

まず、本発明者の知見によれば、プラズマ処理において、C―C結合が、C―Si結合に対して優先して切断されることが見出された。すなわち、プラズマのエネルギーが、主にC−C結合の切断に使用され、Si−CH3結合は切断されずに維持される。このため、深さ方向(膜厚方向)に、切断対象としてC―C結合の分だけ増加する(Siに複数の炭素を含有する高次のハイドロカーボン(CHx)が存在する)。これにより、炭素を引き抜く際、C―Si結合を残しつつも、改質層の膜厚を薄くすることができる。また、C―Si結合を残すことにより、分極率の高いSi−OH結合への変化を抑制できるので、誘電率を低く抑えることができる。このように、改質層の誘電率を低く保ったまま、その膜厚を薄くできる。

【0037】

さらに、本実施の形態に係る多孔質SiOCH膜は、独立空孔を有する。これにより、空孔を介したプラズマ粒子の打ち込みが発生しにくい。言い換えると、本実施の形態では、連続空孔の場合のように、プラズマ中の高エネルギー粒子が、空孔を介して膜の奥深くまで打ち込まれてしまうという現象を抑制できる。このため、改質層の膜厚を薄くすることができる。そのため、実効誘電率の上昇を抑制できる。

【0038】

一方、改質層においては、炭素濃度が低くなり、疎水性が低下するので、金属膜との密着性が向上する。また、改質層は、多孔質SiOCH膜由来の微細な独立空孔を有する。多孔質SiOCH膜に配線溝を形成する際、配線溝の底部または側壁部には独立空孔が現れる。この独立空孔は、ポロジェンで形成された空孔と比較して、非常に微細である。このため、配線溝の底部または側壁部は、ポロジェンによる連結空孔に起因した凹凸面と比較して、平坦になる。このため、改質層においては、その表面が平坦になるので、金属膜との密着性が向上する。

【0039】

改質層の膜厚は、誘電率の値が問題にならない限りにおいては限定されないが、例えば、10nm未満、より好ましくは5nm未満である。とくに、バリアメタル膜と多孔質SiOCH膜の密着強度を高める改質層を5nm未満に抑えることができる。

【0040】

以上の働きにより、膜の低誘電率を維持しながら、配線溝底での金属材料と低誘電率膜の密着強度を高め、チップを実装する際の応力による配線層の剥離や破壊を抑制することができる。

【0041】

ここで、多孔質SiOCH膜にプラズマ処理を施した際の影響について説明する。

【0042】

図2(a)は、ポロジェンを用いた多孔質SiOCH膜の配線構造の断面電子顕微鏡写真を示す。図2(b)は、本実施の形態に係る独立空孔型多孔質SiOCH膜の配線構造の断面電子顕微鏡写真を示す。

図2(a)に示すように、配線溝の底部に、ポロジェンの脱離により形成された連続空孔に由来する底荒れが観察される。このような配線溝底の荒れは、信頼性を大幅に劣化させることが知られている。また、プラズマ中の高エネルギー粒子が、連続空孔を介して膜の奥深くまで打ち込まれてしまうことにより、奥深くまでダメージが導入されていることも示唆されている。このため、ポロジェンを用いた場合では、実効的な誘電率の著しい上昇を招くことが分かった。

これに対して、本実施の形態に係る独立空孔型多孔質SiOCH膜では、図2(b)に示すように、配線溝底が極めて平坦であることが分かった。これにより、信頼性の劣化や誘電率の上昇を抑制することができる。

【0043】

図3は、本実施の形態に係る独立空孔型多孔質SiOCH膜(C/Si=2.5、比誘電率2.5)に対して、意図的にC/Si比を変化させた場合の比誘電率の上昇率を示す。

C/Si比が1.0から2.5の範囲で、比誘電率上昇率はC/Si比に対して線形に変化することがわかる。C/Si比が2.0以上であれば、C/Si=2.5の膜に対して5%未満の比誘電率上昇に抑えられる。このときの膜の誘電率は2.6未満である。

本実施の形態において、誘電率は、水銀プローブを用いた容量測定結果と、光学測定に基づくSiOCH膜厚から算出した。容量値およびSiOCH膜厚の測定には、ともにシリコン基板上にSiOCH膜を成膜したサンプルを用いた。容量測定は、絶縁膜に印加される電界が0.1乃至10MV/cm、好ましくは1MV/cmとなるようにバイアスを印加し、周波数を1kHz乃至10MHz、好ましくは10kHz乃至1MHzの条件下で実施した。

【0044】

図4は、Heプラズマ処理の有無による、独立空孔型多孔質SiOCH膜表面付近のC/Si比分布を測定した結果を示す。ここで、He処理条件としては、室温、Heガス流量を200sccm、圧力を0.1Torr、プラズマ生成用高周波電源(2MHz)の電力を800W、30秒間という条件を用いた。また、炭素原子やシリコン原子等の組成分析については、光電子分光法(XPS)もしくはラザフォード後方散乱法(RBS)等を用いた。He処理の有無によらず、TaN/Ta積層膜に続いて、Cuを成膜して界面部分の組成を分析している。

Heプラズマ処理を行う場合について説明する。界面付近の25nm程度までの間で、C組成のプロファイルが減少していることが分かる(炭素が抜けている)。すなわち、金属膜と改質層との界面から、5nm以上離れた領域では、例えば、界面から5nm以上25nm以下の範囲では、C/Si組成比は2.0以上である。このため、前述のように、比誘電率の上昇は抑制できることがわかる。また、界面付近5nm未満の組成は、界面の揺らぎにより正確に測定できていない。しかしながら、C/Si比が2未満となるまでCが減少している領域があるとしても、その厚さは5nm未満であることがわかる。すなわち、多孔質SiOCH膜の内部の誘電率と比較して、高い誘電率を有する改質層の膜厚を非常に薄くすることができる。例えば、改質層の膜厚を5nm未満に抑えることができる。

【0045】

ここで、前述のように、膜の比誘電率は、Si−C結合が切断される量と、その深さに関係して上昇する。本実施の形態に係る独立空孔型多孔質SiOCH膜では、側鎖に複数の炭素原子を有する環状シロキサン構造を有している。このため、側鎖の複数のC原子間の結合が優先的に切断される。これにより、ハイドロカーボンが減少するが、側鎖の炭素原子が減少した結果、炭素原子1個の側鎖であるSi−C結合は保存される。そのため、比誘電率上昇が抑えられる。かつ、独立空孔の効果も合わせて、C/Si比が2未満になるまでCが減少する領域は、少なくとも5nm未満に抑えられる。

【0046】

このように、本実施の形態では、C/Si比が2.0未満となる改質層の厚さは5nm未満に抑えることができる。現在、検討されているCu配線の配線間スペースは50nmを下回るようになっている。このような微細化において、C/Si比が2.0未満となる改質層をその10%未満(膜厚が5nm未満)に抑えることは、寄生容量の上昇を抑制する上できわめて重要である。

【0047】

図5に、改質処理を行わない独立空孔型多孔質SiOCH膜を用いた多層配線を有する半導体チップを、フリップチップパッケージに封入した後の超音波顕微鏡写真を示す。図中の黒丸は、はんだバンプ部を示している。図には、一部を拡大した写真も示している。この拡大写真中において、バンプ部中央に白点が見られる異常なバンプ40が見られる。この部分のチップ側の断面を、電子顕微鏡で観察した結果が図6である。この図から、異常バンプの直下では、Cu配線(Cu膜22c)と独立空孔型多孔質SiOCH膜12cの間で剥離が生じていることがわかる。これにより、改質処理を行わない独立空孔型多孔質SiOCH膜においては、金属配線との密着強度が不十分であることが示唆された。

【0048】

図7に、バリア金属膜と独立空孔型SiOCH膜の間の密着強度について、バリア金属膜を形成する前に実施するHeプラズマ処理の有無で比較した結果を示す。ここで、バリア金属は、TaとTaNの積層膜としており、PVD法にて形成している。また、Heプラズマ処理は、PVD成膜チャンバと真空搬送室を介したチャンバを用いる。

図7に示すように、He処理を行うことによって、大幅に密着強度が改善することがわかる。このことは、独立空孔型SiOCH膜の表面の炭素が脱離したことによって、無機膜との密着強度が改善したことを示している。

本実施の形態においては、密着強度は、特に限定されないが、例えば0.13MPa/m2以上0.3MPa/m2以下とすることができる。

ここでは、密着強度の測定を、mELT(Modified Edge−Lift Test)法により行うが、この他にも、4−Point Bebding法などの手法を用いることも可能である。ただし、測定方法によって、得られる物理量が異なる。

このような、改質層を設けることにより、フリップチップ実装時に見られた、バリア金属と多孔質環状シロキサン界面での剥離によるバンプ部の異常を抑制することができる。

【0049】

(半導体装置の製造方法)

次に、本実施の形態の半導体装置の製造方法として、第1例について説明する。

図8および図9は、第1例の半導体装置の製造方法の工程断面図を示す。

本実施の形態の半導体装置の製造方法は、基板(シリコン基板)上に、炭素−炭素結合を有し、かつ炭素原子数とシリコン原子数との比(C/Si)が2以上である、多孔質SiOCH膜12bを形成する工程と、多孔質SiOCH膜12bに凹部(配線溝15や配線孔16)を形成する工程と、凹部内の多孔質SiOCH膜12bの表面に、多孔質SiOCH膜12bの内部と比較して、C/Si比が小さく、かつO/Si比が同等な改質層31bを形成する工程と、凹部に金属膜(Cu膜22b)を埋め込む工程と、を含む。

本例では、下部配線層上に上部配線層を形成する工程について説明する。

【0050】

まず、図8(a)に示すように、不図示の半導体基板(シリコン基板)上に下部配線層を形成する。下層配線層は、第1の層間絶縁膜(多孔質SiOCH膜12a)と、第1の層間絶縁膜中に、埋め込まれた金属配線(Cu膜22a)とから構成される。この多孔質SiOCH膜12aの表面には、改質層31aが形成されている。そして、この改質層31aとCu膜22aとの間に、バリア金属膜21aが形成されている。また、多孔質SiOCH膜12a上およびCu膜22a上には、キャップ絶縁膜11aが形成されている。この下層配線も、後述する上層配線と同様のプロセスおよび材料により形成できる。

【0051】

続いて、図8(b)に示すように、下層配線のキャップ絶縁膜11a上に、多孔質SiOCH膜12b、およびハードマスク13bをこの順で形成する。

【0052】

ここで、多孔質SiOCH膜12bを成膜する方法について説明する。

本実施の形態では、原料モノマーとして、下記式(2)で示す環状有機シロキサン構造を有する化合物を用いる。まず、原料モノマーを、キャリアガスのHeと混合して、気化器に送り込む。この原料モノマーの流量は、液体マスフローコントローラで制御する。続いて、原料モノマーを、気化器で液体から気体へと気化させる。気化した原料モノマーを含む原料ガスを、反応室内に導入する。そして、反応室内に、13.56MHzの高周波電力を印加する。反応室内で、原料ガスのプラズマが生成する。そして、化学気相成長により環状シロキサン膜(多孔質SiOCH膜12b)を、基板上に成膜する。原料モノマーの供給量は、0.1g/min以上10g/min以下であることが好ましく、さらに好ましくは2g/min以下である。キャリアガスであるHe流量は、50sccm以上5000sccm以下であることが好ましく、さらに好ましくは2000sccm以下である。リアクター(気化器)内の圧力は133〜1333Paであることが好ましい。RF電源の出力は2000W以下であることが好ましく、さらに好ましくは1000W以下である。このとき、キャリアガスとして、酸素を含まないガスを用いることができる。

【0053】

【化3】

【0054】

ハードマスク13bには、多孔質SiOCH膜よりもC濃度が少なく、酸素濃度が多い膜を用いる。例えば、ハードマスク膜13bとしては、SiO2、SiN、SiOCH等を用いることができる。ハードマスク膜13bの形成には、例えば、プラズマCVD法を用いる。

【0055】

続いて、図8(c)に示すように、多孔質SiOCH膜12bに、凹部(配線溝15、配線孔16)を形成する。これらの凹部は、ハードマスク13bを貫通する。配線溝15の底部には、キャップ絶縁膜11aが露出している。一方、配線孔16の底部は、多孔質SiOCH膜12bの内部の一部に形成されている。配線溝15と配線孔16との最接近距離(配線間スペース)としては、特に限定されないが、例えば、50nm以下とすることができる。凹部の形成には、例えば、リソグラフィー法と異方性エッチング法を用いる。異方性エッチング法としては、例えば、ウエットエッチングまたはドライエッチングを用いることができる。

【0056】

次いで、図8(d)に示すように、配線溝15の側壁、配線孔16の側壁および底部の多孔質SiOCH膜12bの表面に改質処理を行う。これにより、多孔質SiOCH膜12bの表面に、C濃度が低減した改質層31bを形成する。このとき、配線溝15の底部におけるキャップ絶縁膜11aが除去される。そして、配線溝15の底部に、Cu膜22aの表面が露出する。

【0057】

改質処理には、例えば、プラズマ処理を用いる。プラズマ処理条件としては、例えば、室温、Heガス流量を200sccm、圧力を0.1Torr、プラズマ生成用高周波(2MHz)電源の電力を800W、30秒間とすることができる。ここで、ガスは、Heに限定されるものではなく、Ne、Ar、Xe等の希ガスや、希ガスとHを混合したガス、あるいはN2等の不活性ガスを用いてもよい。特に、プラズマ中にOを含まないようにすることが重要である。プラズマ処理条件については、ガス流量10〜1000sccm、圧力0.01〜0.5Torr、プラズマ発生用高周波電源パワー100〜2000W、時間は5〜90秒に設定すればよい。また、放電開始時に基板側に13.56MHzの100〜1000Wのバイアスを印加することで放電開始を促進すると効果的である。

【0058】

続いて、図9(a)に示すように、配線溝15および配線孔16の内部にバリア金属膜21bを形成する。そして、配線溝15および配線孔16を埋め込むように、金属膜(Cu膜22b)を多孔質SiOCH膜12b上およびバリア金属膜21b上に形成する。

【0059】

バリア金属膜21は、配線金属を構成する金属元素が層間絶縁膜や下層へ拡散することを防止する機能を有する。また、バリア金属膜21bは、バリア性を有する導電性膜である。バリア金属膜21bとしては、例えば、配線金属がCuを主成分とする場合には、タンタル(Ta)、ルネニウム(Ru)、窒化タンタル(TaN)、窒化チタン(TiN)、炭窒化タングステン(WCN)のような高融点金属やその窒化物等が用いられる。また、これらの材料を用いた積層の膜であってもよい。本実施の形態では、バリア金属膜21bとしては、TaNとTaの積層膜を用いる。バリア金属膜21bの形成方法としては、例えばPVD法を用いる。なお、バリア金属の形成方法は、PVD法に限定されるものではなく、有機金属材料を用いたCVD法等で形成してもよい。また、前述のプラズマ処理工程とバリア金属膜の成膜工程の間は、真空中で行う必要がある。これにより、Heプラズマ処理後に、一旦大気中に取り出すと、Heプラズマ処理によって活性となった表面に水分等が付着することを防止できる。その後、成膜するバリア金属膜との密着強度が劣化するだけでなく、実効的な誘電率の上昇をもたらすことを抑制できる。

【0060】

次いで、Cu粒成長のための熱処理を施す。この熱処理の温度は、例えば200〜400℃、時間は30秒〜1時間に設定する。

【0061】

続いて、図9(b)に示すように、凹部(配線溝15および配線孔16)の外部に露出したCu膜22b、バリア膜21b、およびハードマスク13bを除去する。除去には、化学機械研磨(Chemical Mechanical Polishing:CMP)等の研磨技術を用いる。多孔質SiOCH膜12bおよびCu膜22bが露出した状態でCMPを停止する。

【0062】

Cu膜22bは、凹部(配線溝15、配線孔16)の内壁面に形成されたバリア金属膜21bで覆われている。このCu膜22bは、バリア金属膜21bを介して改質層31bと接合している。

Cu膜22bは、Cuを主成分とする銅含有配線である。信頼性を向上させるため、Cu膜22bには、Cu以外の金属元素、例えばAl等が含まれていてもよい。また、Cu以外の金属元素が、Cu膜22bの上面や側面等に形成されていてもよい。

【0063】

続いて、図9(c)に示すように、露出している多孔質SiOCH膜12bおよびCu膜22bの表面に、キャップ絶縁膜11bを成膜する。これにより、上部配線層の配線工程を終了する。キャップ絶縁膜11bの形成方法としては、例えば、プラズマCVD法を用いることができる。

【0064】

キャップ絶縁膜11bは、Cu膜22bに含まれるCuの酸化や絶縁膜中へのCuの拡散を防ぐ機能、および加工時にエッチングストップ層としての役割を有する。キャップ絶縁膜11bの誘電率を低くすることで、配線信号伝達遅延が改善できる。キャップ絶縁膜11bは、バリア絶縁膜としても機能する。キャップ絶縁膜11bとしては、SiN、SiC、SiCNおよびCu拡散バリア性を有する有機シロキサン膜等を用いることができる。また、キャップ絶縁膜11は、不飽和炭化水素とアモルファスカーボンを有する膜、またはSiN膜、SiCN膜、およびSiC膜のうち少なくとも一つを用いた膜と不飽和炭化水素およびアモルファスカーボンを有する膜との積層膜であってもよい。キャップ絶縁膜11bは、これらの膜を2種類以上積層してもよい。

【0065】

本実施の形態では、図8(b)〜図9(c)で示された工程を繰り返すことで、多層配線構造を形成することができる。また、本実施の形態では、配線溝と配線孔を同時に形成するデュアルダマシン法を用いて説明したが、シングルダマシン法を用いた配線形成であってもよい。

以上により、本実施の形態の半導体チップを得ることができる。

【0066】

また、多層配線を有する半導体チップを、電子機器に搭載するためには、外部回路との接続を行うための組立工程あるいは実装工程を経て、パッケージ中に封入されることが多い。パッケージへの封入の仕方には、複数の方法がある。ここでは、代表的な二種類のパッケージ手法を説明する。

【0067】

一つは、ワイヤボンディングと呼ばれる手法であり、図13に示すような接続形態をとる。すなわち、半導体チップ51aの最上層の金属層で形成されたボンディングパッド(図示せず)とパッケージ基板52a上のボンディングパッド(図示せず)をボンディングワイヤ55で接続する方法である。半導体チップ51aは、裏面側でパッケージ基板52aに接着され、封入樹脂53a内に封入される。また、パッケージ基板52aには、外部回路と接続するための外部接続端子54aが設けられている。

【0068】

もう一つの手法は、フリップチップ接続と呼ばれる手法であり、図14に示すような接続形態をとる。半導体チップ51bの最上層の金属層で形成されたパッド(図示せず)上にはんだバンプ56を形成し、はんだバンプ56が下側に向くように裏返し、パッケージ基板52b上に形成されたはんだバンプ57と接合させる手法である。はんだバンプ同士を接触させ、加熱してはんだを溶融させて接合する。この際、接合後の冷却過程で半導体チップとパッケージ基板の熱膨張係数の違いによって、接合部に応力が加わることが知られている。なお、半導体チップ51bは封止樹脂53bで封入されることもあり、半導体基板52bの裏面には、外部回路と接続するための外部接続端子54bが設けられている。

以上により、本実施の形態の半導体装置を得ることができる。

【0069】

次に、本実施の形態の作用効果について説明する。

【0070】

本実施の形態においては、多孔質SiOCH膜は、炭素−炭素結合を有する。改質層形成工程においては、多孔質SiOCH膜においては、炭素原子は、C―C結合から引き抜かれ、C―Si結合が残る。このため、改質層は、多孔質SiOCH膜と比較して炭素濃度が低くなる(C/Si比が小さくなる)ものの、C―Si結合が残るので誘電率を低減できる。また、切断対象が、C―C結合の分だけ増加するので、改質層の膜厚を薄くすることができる。さらに、改質層では、酸素が導入されないので、多孔質SiOCH膜と同程度のO/Si比となっており、誘電率の上昇が抑制されている。

このように、改質層は、改質層の低誘電率が低くかつその膜厚が薄い。このため、C/Siが2以上の多孔質SiOCH膜全体の誘電率を低く抑えることができる。

一方、改質層においては、炭素濃度が低くなり、疎水性が低下するので、金属膜との密着性が向上する。これにより、銅配線と多孔質SiOCH膜との密着強度を改善し、半導体チップをパッケージに実装する際の配線層の剥離や破壊を抑制することができる。

したがって、本実施の形態では、低誘電率化および金属膜との密着性の向上の両立を実現することができる。

【0071】

特許文献1では、低誘電率化に貢献するのはSiとCの結合であるが、C/Si比<1の場合に生成される低C濃度領域では、Si−C結合の量が減少して誘電率が上昇する。このとき、残留するSi−Cの量が、プラズマ処理条件によって不安定になり、誘電率の上昇率を制御することが難しくなる。

これに対して、本実施の形態では、SiにC原子を二個以上含む側鎖が形成されている。このため、C−C結合の切断によるC量の減少によって低C濃度層が形成される。したがって、低誘電率化に寄与するSi−C結合は保存されることになる。これにより、誘電率の上昇率を抑制できる。

【0072】

次に、本実施の形態の半導体装置の製造方法として、第2例について説明する。

図10は、第2例の半導体装置の製造方法の工程断面図を示す。

第2例の半導体装置の製造方法においては、多孔質SiOCH膜12a、12bの上面にも、改質層32a、32bを形成する以外は、第1例と同様にする。

【0073】

第2例では、キャップ絶縁膜11b成膜前に、同一チャンバ内でプラズマ処理を施す。これにより、露出している多孔質SiOCH膜12bの表面に、低炭層濃度の改質層32bを形成しつつ、露出しているCu膜22bの表面の清浄化処理を行うことができる。このため、キャップ絶縁膜11bとの密着強度を強化させつつ、信頼性の向上を図ることができる。また、改質層32bは、配線溝形成や、CMPにより配線材の研磨時等に、多孔質SiOCH膜12bの表面を保護する役割を果たす。このときの、プラズマ処理においては、Cu表面の還元性を高めるため、水素を含有するプラズマで行うことが好ましい。例えば、NH3、H2プラズマを用いることが効果的である。また、第2例においては、第1例と同様の効果が得られる。

【0074】

次に、本実施の形態の半導体装置の製造方法として、第3例について説明する。

図11および図12は、第3例の半導体装置の製造方法の工程断面図を示す。

第3例の半導体装置の製造方法においては、ハードマスク膜13a、13bを、多孔質SiOCH膜12a、12bの上面の一部に残す以外は、第1例と同様にする。

【0075】

図11(a)は、本実施の形態の半導体装置における下層配線層の断面を示している。この下層配層線も、後述する上層配線層と同様のプロセスおよび材料により形成できる。

【0076】

図11(b)に示すように、下層配線のキャップ絶縁膜11a上に多孔質SiOCH膜12b、およびハードマスク13bを形成する。

【0077】

多孔質SiOCH膜は、同数のシリコン(Si)原子と酸素(O)原子が交互に連なった環状構造(環状シロキサン構造)を含み、それぞれのシリコン原子に属する側鎖として、炭素(C)原子を2個以上含む側鎖が少なくとも1個存在しているモノマーを原料として用いる。まず、原料モノマーを、キャリアガスのHeと混合して、気化器に送り込む。この原料モノマーの流量は、液体マスフローコントローラで制御する。続いて、原料モノマーを、気化器で液体から気体へと気化させる。気化した原料モノマーを含む原料ガスを、反応室内に導入する。そして、反応室内に、13.56MHzの高周波電力を印加する。反応室内で、原料ガスのプラズマが生成する。そして、化学気相成長により環状シロキサン膜(多孔質SiOCH膜12b)を、基板上に成膜する。原料モノマーの供給量は、0.1g/min以上10g/min以下であることが好ましく、さらに好ましくは2g/min以下である。キャリアガスであるHe流量は、50sccm以上5000sccm以下であることが好ましく、さらに好ましくは2000sccm以下である。リアクター(気化器)内の圧力は133〜1333Paであることが好ましい。RF電源の出力は2000W以下であることが好ましく、さらに好ましくは1000W以下である。このとき、キャリアガスとして、酸素を含まないガスを用いることができる。

【0078】

このようにして形成された独立空孔型多孔質SiOCH膜12b中に存在するC/Si組成比は2以上である。

【0079】

多孔質SiOCH膜12b上に形成するハードマスク13bには、多孔質SiOCH膜よりもC濃度が少なく、酸素濃度が多い膜を用いる。例えば、SiO2、SiN、SiOCH等が用いられる。また、ハードマスク膜13bは、下層をSiOCH、上層をSiO2といった多層構造を用いてもよい。ハードマスク膜13bは、例えば、プラズマCVD法で形成する。

【0080】

続いて、図11(c)に示すように、リソグラフィーと異方性エッチングによって、ハードマスク13bおよび多孔質SiOCH膜12b(環状シロキサン膜)に、凹部(配線溝15、配線孔16)を形成する。

【0081】

次いで、図11(d)に示すように、プラズマ処理によって、配線溝15の側面や配線孔16の側面、底面の多孔質SiOCH膜12bの表面を改質する。これにより、多孔質SiOCH膜12bの表層に、C濃度が低減した改質層31bを形成する。プラズマ処理条件としては、例えば、室温、Heガス流量を200sccm、圧力を0.1Torr、プラズマ生成用高周波(2MHz)電源の電力を800W、30秒間という条件を用いる。ここで、ガスは、Heに限定されるものではなく、Ne、Ar、Xe等の希ガスや、希ガスとHを混合したガス、あるいはN2等の不活性ガスを用いてもよい。特に、プラズマ中にOを含まないようにすることが重要である。プラズマ処理条件については、周波数200kHz〜100MHz、ガス流量10〜1000sccm、圧力0.01〜0.5Torr、プラズマ発生用高周波電源パワー100〜2000W、時間は5〜90秒に設定すればよい。また、放電開始時に基板側に200kHz〜100MHzの100〜1000Wのバイアスを印加することで放電開始を促進すると効果的である。

【0082】

続いて、図12(a)に示すように、配線溝15および配線孔16内に、バリア金属膜としてTaNとTaの積層膜をPVD法により形成する。引き続き、配線溝や配線孔にCu膜22bを埋設する。次いで、Cu粒成長のための熱処理を施す。この熱処理の温度は、例えば200〜400℃、時間は30秒〜1時間に設定する。

【0083】

続いて、図12(b)に示すように、CMP等の研磨技術を用い、凹部の外部に露出したCu膜22b、バリア膜21b、およびハードマスクの13bの一部を除去する。これにより、Cuが露出していない領域ではハードマスク13bが、多孔質SiOCH膜12bを被覆している。すなわち、多孔質SiOCH膜12bの上面は、Cu膜22bまたはハードマスク膜13bにより覆われている。ここで、ハードマスク膜13bをSiO2とSiOCHの二層構成とした場合には、表面側のSiO2のみを研磨し、SiOCHが露出した段階でCMPを停止する等を行ってもよい。

【0084】

続いて、図12(c)に示すように、露出しているハードマスク膜13b、およびCu膜22bの表面にキャップ絶縁膜11bを成膜する。キャップ絶縁膜としては、プラズマCVD法によって成膜するSiN、SiC、SiCN等を用いる。これらの膜の2種類以上を積層してもよい。

【0085】

図11(b)〜図12(c)で示された工程を繰り返すことで、多層配線構造を形成することができる。また、本実施の形態では、配線溝と配線孔を同時に形成するデュアルダマシン法を用いて説明したが、シングルダマシン法を用いた配線形成であってもよい。

以上により、本実施の形態の半導体チップを得ることができる。

【0086】

キャップ絶縁膜11bと多孔質SiOCH膜12b(多孔質環状シロキサン膜)との間に、多孔質環状シロキサン膜よりも炭素濃度が少なく、かつ空孔を含有しないハードマスク膜13bが設けられている。ハードマスク膜13bは、配線溝形成や、CMPにより配線材の研磨時等に、多孔質SiOCH膜12bの表面を保護する役割を担う。また、第3例においては、第1例と同様の効果が得られる。

【0087】

以上、図面を参照して本発明の実施形態について述べたが、これらは本発明の例示であり、上記以外の様々な構成を採用することもできる。

【符号の説明】

【0088】

11a、11b キャップ絶縁膜

12a、12b、12c 多孔質SiOCH膜

13a、13b ハードマスク膜

15 配線溝

16 配線孔

21a、21b バリア金属膜

22a、22b、22c Cu膜

31a、31b 改質層

32a、32b 改質層

40 異常なバンプ

51a、51b 半導体チップ

52a、52b パッケージ基板

53a、53b 封入樹脂

54a、54b 外部接続端子

55 ボンディングワイヤ

56 はんだバンプ

57 はんだバンプ

【特許請求の範囲】

【請求項1】

基板上に、炭素−炭素結合を有し、かつ炭素原子数とシリコン原子数との比(C/Si)が2以上である、多孔質SiOCH膜を形成する工程と、

前記多孔質SiOCH膜に凹部を形成する工程と、

前記凹部内の前記多孔質SiOCH膜の表面に、前記多孔質SiOCH膜の内部と比較して、C/Si比が小さく、かつO/Si比が同等な改質層を形成する工程と、

前記凹部に金属膜を埋め込む工程と、を含む、半導体装置の製造方法。

【請求項2】

前記改質層を形成する工程において、不活性ガスを含む雰囲気下で、前記多孔質SiOCH膜にプラズマ処理を行う、請求項1に記載の半導体装置の製造方法。

【請求項3】

前記不活性ガスがヘリウムである、請求項2に記載の半導体装置の製造方法。

【請求項4】

前記雰囲気は酸素を含まない、請求項2または3に記載の半導体装置の製造方法。

【請求項5】

前記多孔質SiOCH膜中に、平均空孔が1nm未満、かつ互いに独立している空孔が形成されている、請求項1から4のいずれか1項に記載の半導体装置の製造方法。

【請求項6】

前記多孔質SiOCH膜は、下記式(1)で表される環状有機シロキサン構造を有する化合物から得られる、請求項1から5のいずれか1項に記載の半導体装置の製造方法。

【化1】

(式(1)中、R1およびR2は、同一または相異なり、それぞれ炭化水素基を表し、かつR1およびR2の少なくとも一方が前記炭素−炭素結合を有する。)

【請求項7】

前記環状有機シロキサン構造を有する化合物は、下記式(2)で表される、請求項6に記載の半導体装置の製造方法。

【化2】

【請求項8】

前記多孔質SiOCH膜の上面に、前記改質層を形成する工程と、

前記多孔質SiOCH膜上および前記金属膜上に、キャップ絶縁膜を形成する工程と、をさらに含む、請求項1から7のいずれか1項に記載の半導体装置の製造方法。

【請求項9】

基板と、

前記基板上に設けられており、炭素−炭素結合を有し、かつ炭素原子数とシリコン原子数との比(C/Si)が2以上である、多孔質SiOCH膜と、

前記多孔質SiOCH膜に設けられた凹部と、

前記凹部を埋め込むように設けられた金属膜と、

前記金属膜と接しており、前記凹部内の前記多孔質SiOCH膜の表面に設けられた、改質層と、を備え、

前記改質層は、前記多孔質SiOCH膜の内部と比較して、C/Si比が小さく、かつO/Si比が同等である、半導体装置。

【請求項10】

前記金属膜と前記改質層との界面から、5nm以上離れた領域ではC/Si比が2以上である、請求項9に記載の半導体装置。

【請求項11】

前記多孔質SiOCH膜に、平均空孔が1nm未満、かつ互いに独立している空孔が設けられている、請求項9または10に記載の半導体装置。

【請求項12】

前記多孔質SiOCH膜の比誘電率が2.7以下である、請求項9から11のいずれか1項に記載の半導体装置。

【請求項13】

前記多孔質SiOCH膜上および前記金属膜上に設けられた、キャップ絶縁膜と、

前記キャップ絶縁膜と接しており、前記多孔質SiOCH膜の表面に設けられた前記改質層と、をさらに備える、請求項9から12のいずれか1項に記載の半導体装置。

【請求項14】

前記多孔質SiOCH膜は、下記式(1)で表される環状有機シロキサン構造を有する化合物を含む、請求項9から13のいずれか1項に記載の半導体装置。

【化3】

(式(1)中、R1およびR2は、同一または相異なり、それぞれ炭化水素基を表し、かつR1およびR2の少なくとも一方が前記炭素−炭素結合を有する。)

【請求項15】

前記環状有機シロキサン構造を有する化合物は、下記式(2)で表される、請求項14に記載の半導体装置。

【化4】

【請求項16】

前記金属膜は銅を含む、請求項9から15のいずれか1項に記載の半導体装置。

【請求項1】

基板上に、炭素−炭素結合を有し、かつ炭素原子数とシリコン原子数との比(C/Si)が2以上である、多孔質SiOCH膜を形成する工程と、

前記多孔質SiOCH膜に凹部を形成する工程と、

前記凹部内の前記多孔質SiOCH膜の表面に、前記多孔質SiOCH膜の内部と比較して、C/Si比が小さく、かつO/Si比が同等な改質層を形成する工程と、

前記凹部に金属膜を埋め込む工程と、を含む、半導体装置の製造方法。

【請求項2】

前記改質層を形成する工程において、不活性ガスを含む雰囲気下で、前記多孔質SiOCH膜にプラズマ処理を行う、請求項1に記載の半導体装置の製造方法。

【請求項3】

前記不活性ガスがヘリウムである、請求項2に記載の半導体装置の製造方法。

【請求項4】

前記雰囲気は酸素を含まない、請求項2または3に記載の半導体装置の製造方法。

【請求項5】

前記多孔質SiOCH膜中に、平均空孔が1nm未満、かつ互いに独立している空孔が形成されている、請求項1から4のいずれか1項に記載の半導体装置の製造方法。

【請求項6】

前記多孔質SiOCH膜は、下記式(1)で表される環状有機シロキサン構造を有する化合物から得られる、請求項1から5のいずれか1項に記載の半導体装置の製造方法。

【化1】

(式(1)中、R1およびR2は、同一または相異なり、それぞれ炭化水素基を表し、かつR1およびR2の少なくとも一方が前記炭素−炭素結合を有する。)

【請求項7】

前記環状有機シロキサン構造を有する化合物は、下記式(2)で表される、請求項6に記載の半導体装置の製造方法。

【化2】

【請求項8】

前記多孔質SiOCH膜の上面に、前記改質層を形成する工程と、

前記多孔質SiOCH膜上および前記金属膜上に、キャップ絶縁膜を形成する工程と、をさらに含む、請求項1から7のいずれか1項に記載の半導体装置の製造方法。

【請求項9】

基板と、

前記基板上に設けられており、炭素−炭素結合を有し、かつ炭素原子数とシリコン原子数との比(C/Si)が2以上である、多孔質SiOCH膜と、

前記多孔質SiOCH膜に設けられた凹部と、

前記凹部を埋め込むように設けられた金属膜と、

前記金属膜と接しており、前記凹部内の前記多孔質SiOCH膜の表面に設けられた、改質層と、を備え、

前記改質層は、前記多孔質SiOCH膜の内部と比較して、C/Si比が小さく、かつO/Si比が同等である、半導体装置。

【請求項10】

前記金属膜と前記改質層との界面から、5nm以上離れた領域ではC/Si比が2以上である、請求項9に記載の半導体装置。

【請求項11】

前記多孔質SiOCH膜に、平均空孔が1nm未満、かつ互いに独立している空孔が設けられている、請求項9または10に記載の半導体装置。

【請求項12】

前記多孔質SiOCH膜の比誘電率が2.7以下である、請求項9から11のいずれか1項に記載の半導体装置。

【請求項13】

前記多孔質SiOCH膜上および前記金属膜上に設けられた、キャップ絶縁膜と、

前記キャップ絶縁膜と接しており、前記多孔質SiOCH膜の表面に設けられた前記改質層と、をさらに備える、請求項9から12のいずれか1項に記載の半導体装置。

【請求項14】

前記多孔質SiOCH膜は、下記式(1)で表される環状有機シロキサン構造を有する化合物を含む、請求項9から13のいずれか1項に記載の半導体装置。

【化3】

(式(1)中、R1およびR2は、同一または相異なり、それぞれ炭化水素基を表し、かつR1およびR2の少なくとも一方が前記炭素−炭素結合を有する。)

【請求項15】

前記環状有機シロキサン構造を有する化合物は、下記式(2)で表される、請求項14に記載の半導体装置。

【化4】

【請求項16】

前記金属膜は銅を含む、請求項9から15のいずれか1項に記載の半導体装置。

【図1】

【図3】

【図4】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図2】

【図5】

【図6】

【図3】

【図4】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図2】

【図5】

【図6】

【公開番号】特開2011−199059(P2011−199059A)

【公開日】平成23年10月6日(2011.10.6)

【国際特許分類】

【出願番号】特願2010−65029(P2010−65029)

【出願日】平成22年3月19日(2010.3.19)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

【公開日】平成23年10月6日(2011.10.6)

【国際特許分類】

【出願日】平成22年3月19日(2010.3.19)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

[ Back to top ]