半導体装置およびその製造方法

【課題】従来の半導体装置では、半導体素子と導電パターンとの隙間が確保され難く、アンダーフィル材にて充填していたため、放熱性が悪く、量産性に適さないという問題があった。

【解決手段】本発明の半導体装置では、半導体素子2と導電パターン9A〜9Cとの間にはスペーサー11A〜11Dが配置され、半導体素子2と導電パターン9A〜9Cとの間隙間の幅W1は、スペーサー11A〜11Dの膜厚となる。この構造により、半導体素子2下面の隙間の幅W1が一定に保たれ、その隙間への樹脂の充填性が向上される。そして、トランスファーモールドを用いることが可能となり、量産性に適した構造となる。

【解決手段】本発明の半導体装置では、半導体素子2と導電パターン9A〜9Cとの間にはスペーサー11A〜11Dが配置され、半導体素子2と導電パターン9A〜9Cとの間隙間の幅W1は、スペーサー11A〜11Dの膜厚となる。この構造により、半導体素子2下面の隙間の幅W1が一定に保たれ、その隙間への樹脂の充填性が向上される。そして、トランスファーモールドを用いることが可能となり、量産性に適した構造となる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、放熱性を向上させる半導体装置およびその製造方法に関する。

【背景技術】

【0002】

従来の半導体装置の実施例として、下記の構造が知られている。

【0003】

図12(A)は、半導体装置51の平面図を示し、樹脂封止体52内には、半導体素子53や導電パターン54が配置される。点線55は、半導体素子53の外形ラインを示し、半導体素子53の外周囲に沿って複数のパッド電極56が配置される。そして、導電パターン54は、主に、放熱用の電極54A、配線54B及び外部接続電極54Cから構成され、半導体素子53の下面に配置される。

【0004】

図12(B)は、図12(A)に示す半導体装置51のF−F線方向の断面図を示す。半導体素子53が導電パターン54上にフェイスダウンにて実装される。半導体素子53のパッド電極56と外部接続電極54Cとは、半田等の導電性接着材58により電気的に接続される。そして、導電パターン54は、分離溝59によりパターニングされ、半導体素子53と導電パターン54との間には、アンダーフィル材60が充填される。導電パターン54同士は分離溝59により分離されるが、アンダーフィル材60により支持され、導電パターン54は樹脂封止体52内に支持される。また、半導体素子53は、アンダーフィル材60により放熱用の電極54A上に固着される。

【0005】

図示したように、半導体装置51の裏面側には絶縁被膜61が形成され、絶縁被膜61に形成された開口領域を利用して、導電パターン54と接続する電極62が形成される(例えば、特許文献1参照。)。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2002−83903号公報(第5−8頁、第1−4図)

【発明の概要】

【発明が解決しようとする課題】

【0007】

図12(B)に示す如く、半導体装置51は、支持基板を有さず、導電パターン54上に半導体素子53が固着される構造となる。そして、半導体素子53は、導電パターン54上にフェイスダウンにて実装され、導電パターン54同士のショートを防止するため、導電パターン54は、分離溝59を用いて分離される必要がある。この構造により、導電パターン54が樹脂封止体52から抜け落ちることを防止するため、半導体素子53下面にはアンダーフィル材60が充填され、導電パターン54同士がアンダーフィル材60により支持される必要がある。

【0008】

このとき、半導体素子53と導電パターン54との間の隙間は、導電性接着材58の厚みとなり、その幅W3は狭くなる。そのため、アンダーフィル材60としては、狭い空間に浸透可能な絶縁材料が用いられ、樹脂封止体52の形成前に半導体素子53下面の隙間が、アンダーフィル材60により充填される。そして、アンダーフィル材60内のフィラーの含有率を高めるとアンダーフィル材の流動性が悪化するため、アンダーフィル材内のフィラーの含有率を高くし難く、放熱性の悪い材料となる。

【0009】

この構造により、半導体素子53の下面には放熱用の電極54Aが配置されるが、両者間にはアンダーフィル材60が介在することで、半導体素子53からの熱の伝導性が悪化し、半導体装置51としての放熱性が悪化するという問題がある。特に、パワー系の半導体素子では、半導体素子の温度上昇が著しく、優れた放熱性が要求される。

【0010】

その一方、半導体装置51の放熱性を向上させるためには、半導体素子53下面にフィラーの含有率の高い樹脂が充填される必要がある。更に、フィラーの粒径を大きくする程熱伝導率も向上する。そのため、半導体素子53下面の隙間に放熱性に優れた樹脂を充填するためには、その隙間の幅W3が一定幅に保たれる必要がある。しかしながら、半導体素子53下面の隙間の幅W3は、導電性接着材58の厚みとなるため、導電性接着材58の塗布量によりばらつき、一定幅として確保し難いという問題がある。更に、フェイスダウン型の半導体素子53では、リフローの際に半導体素子53の自重により導電性接着材58の厚みを所望の厚みとして確保し難いという問題がある。

【0011】

そのため、樹脂封止体52を形成する工程において、例えば、トランスファーモールドにより、半導体素子53下面の隙間にフィラーが含有された樹脂を充填することも難しく、量産性に適さないという問題がある。特に、放熱性を重視し、樹脂内のフィラーの含有率を増大させた場合には、樹脂の流動性が悪化し、より半導体素子54下面の隙間にその樹脂を充填し難くなる。そして、支持基板を有しない半導体装置51では、導電パターン54間に未充填領域が発生し、導電パターン54が半導体装置51内に支持されず、抜け落ちる等の不良品が発生し易くなる。

【0012】

また、半導体素子53下面の隙間の幅W3を広げるために導電性接着材58の塗布量を増大させることも考えられる。しかしながら、導電性接着材58の塗布量を増大させることで、リフローの際に半導体素子53の自重により導電性接着材58が導電パターン54上から流れ出し、隣り合う導電パターン54同士が、導電性接着材58を介してショートするという新たな問題が発生する。

【課題を解決するための手段】

【0013】

前述した各事情に鑑みて成されたものであり、本発明の半導体装置では、少なくともその一主面側に複数のパッド電極が配置された半導体素子と、前記半導体素子の一主面側に配置されたパッド電極と対応して形成され、前記半導体素子の一主面側がフェイスダウンにて電気的に接続された導電パターンと、前記導電パターンの一主面と対向する他の主面側が露出するように前記半導体素子を封止する樹脂封止体とを有し、前記導電パターンの一主面上には、前記半導体素子の一主面側と当接するスペーサーが配置され、前記半導体素子と前記導電パターンの一主面との間の隙間には、前記樹脂封止体を構成する樹脂が充填されることを特徴とする。

【0014】

また、本発明の半導体装置の製造方法では、導電箔を用意し、前記導電箔の一主面側に前記導電箔の膜厚よりも浅い分離溝を形成し、導電パターンを形成する工程と、前記導電パターンの一主面上にスペーサーを形成し、前記スペーサーと当接するように前記導電パターンの一主面上に半導体素子をフェイスダウンにて電気的に接続する工程と、前記導電パターンの一主面と対向する他の主面側が露出するように、前記半導体素子を封止する樹脂封止体を形成する工程と、前記導電箔の一主面側と対向する他の主面側から、前記分離溝を充填する前記樹脂封止体が露出するまで前記導電箔を除去する工程とを有することを特徴とする。

【発明の効果】

【0015】

本発明では、フェイスダウン型の半導体素子と導電パターンとの間にスペーサーが配置され、両者間の隙間の幅が一定に保たれ、その隙間への樹脂の充填性が向上される。

【0016】

また、本発明では、半導体素子のコーナー部の下面にスペーサーが配置されることで、スペーサーが応力緩和部材として機能し、半導体素子のチッピングが防止される。

【0017】

また、本発明では、半導体素子の下面への樹脂の充填性が向上されることで、半導体素子の下面の導電パターンが樹脂により確実に絶縁される。

【0018】

また、本発明では、半導体素子の下面への樹脂の充填性が向上されることで、樹脂内のフィラーの含有率が高められ、放熱性が向上される。

【0019】

また、本発明では、トランスファーモールドにより半導体素子の下面の隙間へ樹脂を充填することで、量産性が向上される。

【0020】

また、本発明では、スペーサーを利用して半導体素子を導電パターン上に固着することで、半導体素子の下面の幅を一定幅に保つことができる。

【図面の簡単な説明】

【0021】

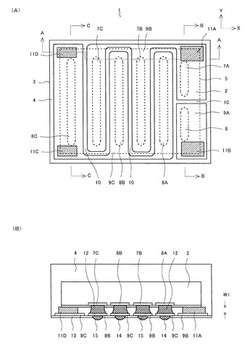

【図1】本発明の実施の形態における半導体装置を説明する(A)平面図、(B)断面図である。

【図2】本発明の実施の形態における半導体装置を説明する(A)断面図、(B)断面図、(C)平面図である。

【図3】本発明の実施の形態における半導体装置を説明する(A)平面図、(B)断面図である。

【図4】本発明の実施の形態における半導体装置を説明する(A)断面図、(B)平面図である。

【図5】本発明の実施の形態における半導体装置の製造方法を説明する(A)断面図、(B)平面図である。

【図6】本発明の実施の形態における半導体装置の製造方法を説明する(A)断面図、(B)平面図、(C)平面図である。

【図7】本発明の実施の形態における半導体装置の製造方法を説明する(A)断面図、(B)平面図である。

【図8】本発明の実施の形態における半導体装置の製造方法を説明する(A)断面図、(B)断面図である。

【図9】本発明の実施の形態における半導体装置の製造方法を説明する(A)断面図、(B)平面図である。

【図10】本発明の実施の形態における半導体装置の製造方法を説明する断面図である。

【図11】本発明の実施の形態における半導体装置の製造方法を説明する断面図である。

【図12】従来の実施の形態における半導体装置を説明する(A)平面図、(B)断面図である。

【発明を実施するための形態】

【0022】

以下に、本発明の第1の実施の形態である半導体装置について説明する。図1(B)は、図1(A)に示す半導体装置のA−A線方向の断面図である。図2(A)は、図1(A)に示す半導体装置のB−B線方向の断面図である。図2(B)は、図1(A)に示すC−C線方向の断面図である。図2(C)は、図1(A)に示す半導体装置の裏面側からの平面図である。尚、図1(A)の説明では、半導体装置1の表面側からは封止樹脂体により見えない部分も実線や点線により示し、説明している。

【0023】

図1(A)に示す如く、半導体装置1は、内蔵される半導体素子2よりも外形寸法が若干大きいサイズの樹脂封止型のCSP(Chip Size Package)である。最外周の実線3による矩形形状は、樹脂封止体4の外形を示し、その内側に示す点線5による矩形形状は、半導体素子2の外形を示す。そして、半導体素子2の表面側には、点線にて示すように、紙面Y軸方向に延在する複数のパッド電極6、7A〜7C、8A〜8Cが配置される。

【0024】

一方、実線3の内側に示す実線は、半導体素子2が固着される導電パターン9A〜9Cを示し、導電パターン9A〜9Cは、分離溝10により区分され、電気的にショートしない構造となる。そして、導電パターン9Aは、半導体素子2のパッド電極6と電気的に接続し、導電パターン9Bは、半導体素子2のパッド電極7A〜7Cと電気的に接続し、導電パターン9Cは、半導体素子2のパッド電極8A〜8Cと電気的に接続する。導電パターン9B、9Cは、それぞれ紙面Y軸方向に延在し、櫛歯状に配置される。

【0025】

図示したように、半導体装置1の4つのコーナー部近傍には、斜線のハッチングで示すスペーサー11A〜11Dが、導電パターン9A〜9C上に配置される。そして、スペーサー11A〜11Dは、半導体素子2の4つのコーナー部下面にそれぞれ配置される。尚、スペーサー11A〜11Dは、その上面に半導体素子2が安定した状態にて配置される領域に配置される場合でも良い。

【0026】

図1(B)に示す如く、導電パターン9B、9Cは、Cuを主材料とした導電箔、Alを主材料とした導電箔、またはFe−Ni等の合金から成る導電箔等を用いて形成される。そして、分離溝10は、前述した導電箔を非異方性のエッチング、例えば、ウエットエッチングすることで形成され、導電パターン9B、9Cの側面は、湾曲構造を有する。尚、導電パターン9B、9Cの材料としては、他の導電材料でも可能であり、特にエッチングできる導電材、レーザで蒸発する導電材が好ましい。また、ハーフエッチング性、メッキの形成性、熱応力等を考慮すると、圧延で形成されたCuを主材料とする導電材料が好ましい。

【0027】

スペーサー11A、11Dは、例えば、PSR(Photo solder resist)を用いて形成される。例えば、導電パターン9B、9C上にPSRを塗布した後、そのPSRを露光処理した後、現像処理することで、スペーサー11A、11Dは所望の領域に形成される。そして、スペーサー11A、11Dの膜厚は、導電パターン9B、9C上に塗布されたPSRの膜厚となり、用途に応じて任意の設計変更が可能である。スペーサー11A、11Dの膜厚は、半導体素子2を導電パターン9B、9C上に実装する際のリフロー工程では、その膜厚は変わらないため、半導体素子2と導電パターン9B、9Cとの隙間の幅W1は、スペーサー11A、11Dの膜厚となる。尚、スペーサー11A、11Dは、前述した隙間の幅W1が一定に保たれる構造であれば、半田バンプや金属バンプから形成される場合でも良い。

【0028】

半導体素子2は、導電パターン9B、9C上に半田クリーム、ロウ材または導電性ペースト等の導電性接着材12を介してフェイスダウンにて実装される。そして、半導体素子2としては、IC、LSI、ディスクリート型のトランジスタ、ダイオード等の能動素子が用いられる。例えば、図1(A)に示す半導体素子2は、窒化ガリウムを用いたパワートランジスタであり、パッド電極6がゲート電極であり、パッド電極7A〜7Cはソース電極であり、パッド電極8A〜8Cはドレイン電極として用いられる。このパワートランジスタは、シリコンを用いたパワートランジスタよりも高耐圧及び高速性を有する素子であり、大電流を流すことが可能となり、素子の放熱性が重要なテーマとなる。

【0029】

樹脂封止体4は、半導体素子2を被覆するように形成され、トランスファーモールドにより形成される場合には熱硬化性樹脂により形成され、または、インジェクションモールドにより形成される場合には熱可塑性樹脂により形成される。図示したように、樹脂封止体4は、半導体素子2と導電パターン9B、9Cとの間の隙間や分離溝10にも配置される。そして、半導体装置1は支持基板を有しないため、半導体素子2下面に位置する導電パターン9B、9Cは、その樹脂封止体4と密着することで、樹脂封止体4内に支持される。

【0030】

被覆層13は、半導体装置1の裏面側を被覆し、外部電極14、15が形成される箇所の被覆層13には開口部が形成される。そして、被覆層13は、エポキシ樹脂等の熱硬化性樹脂、ポリエチレン等の熱可塑性樹脂またはPSRから形成される。

【0031】

外部電極14、15は、半田等の導電性材料から成り、被覆層13の開口部から露出する導電パターン9B、9C上に形成される。そして、外部電極14、15は、半導体装置1に内蔵される半導体素子2と導電パターン9B、9Cを介して電気的に接続される。

【0032】

図2(A)に示すB−B線方向の断面では、導電パターン9A、9B上にスペーサー11A、11Bが配置され、半導体素子2のコーナー部が、スペーサー11A、11B上に配置される。そして、スペーサー11A、11Bにより確保された幅W1の隙間や分離溝10内には、樹脂封止体4が形成され、導電パターン9A、9Bは、樹脂封止体4と密着し、半導体装置1内に支持される。また、被覆層13の開口部から露出する導電パターン9A、9B上には外部電極15、16が形成される。尚、導電パターン9A、スペーサー11Bや外部電極16の構造及び材料は、前述した導電パターン9B、9C、スペーサー11A、11Dや外部電極14、15と同様である。

【0033】

図2(B)に示すC−C線方向の断面では、導電パターン9C上にスペーサー11C、11Dが配置され、半導体素子2のコーナー部が、スペーサー11C、11D上に配置される。そして、スペーサー11C、11Dにより確保された幅W1の隙間内には、樹脂封止体4が形成される。また、被覆層13の開口部から露出する導電パターン9A上には外部電極14が形成される。尚、スペーサー11Cの構造及び材料は、前述したスペーサー11A、11Dと同様である。

【0034】

図2(C)は、半導体装置1の裏面側を示し、被覆層13の開口部から露出する導電パターン9A〜9C上には外部電極14〜16が形成される。そして、導電パターン9A〜9Cは点線にて表示するが、前述したように、半導体素子2が、窒化ガリウムを用いたパワートランジスタである場合には、外部電極16がゲート電極であり、外部電極15はソース電極であり、外部電極14はドレイン電極として用いられる。図示したように、外部電極14〜16は、それぞれ紙面Y軸方向に延在して配置され、ソース電極用の外部電極15とドレイン電極用の外部電極14は、紙面X軸方向に交互に配置される。

【0035】

前述したように、半導体素子2の4つのコーナー部下面には、それぞれスペーサー11A〜11Dが配置され、そのスペーサー11A〜11Dの膜厚により、半導体素子2と導電パターン9A〜9Cとの隙間の幅W1が、一定幅に保たれる。そのため、半導体素子2下面の幅W1は、トランスファーモールドにより樹脂が充填されるのに必要な幅に容易に調整される。また、スペーサー11A〜11Dの膜厚は、半導体素子2を実装する際の作業熱によりその膜厚が変化することもなく、トランスファーモールドを用いた場合でも半導体素子2下面に未充填領域が発生し難く、量産性に適した構造となる。そして、トランスファーモールドを用いることで、樹脂注入時の圧力を強めることが可能となり、フィラーの含有率を高め、樹脂の流動性が低下した場合でも、前述した未充填領域の発生を防止できる。

【0036】

特に、半導体素子2として、パワー系の半導体素子を用いた場合には、半導体素子2と導電パターン9A〜9Cとの間の領域は電流経路となり、高温領域となる。そのため、半導体素子2の下面に配置される樹脂封止体4は、放熱性に優れた材料により構成される必要があり、樹脂封止体4内のフィラーの含有率が増大されることが望ましい。また、樹脂封止体4内に含有されるフィラーの粒径が大きくなるほど、熱伝導率が向上される。そこで、半導体装置1では、スペーサー11A〜11Dの膜厚を50μm程度とすることで、樹脂封止体4内に含有されるフィラーの粒径を最大で25μm程度のものを用いることが可能となる。尚、スペーサー11A〜11Dの膜厚やフィラーの粒径は、使用される半導体素子に対する放熱性やパッケージ寸法等が考慮され、任意の設計変更が可能である。

【0037】

また、半導体装置1を実装基板(図示せず)上に実装し、電気回路として駆動することで、導電性接着材12を含めた半導体装置1全体としての熱膨張、熱収縮を繰り返す。特に、フェイスダウン型の半導体素子2では、半導体素子2と導電パターン9A〜9Cとの間が高温領域となり、熱膨張、熱収縮する量も大きくなる。そして、半導体素子2は、導電性接着材12との接着面積も広く、導電性接着材12による熱膨張や熱収縮の影響を受け易く、半導体装置1の厚み方向や幅方向への伸縮を繰り返す。そのため、熱膨張や熱収縮により応力集中し易い半導体素子2の4つのコーナー部下面には、スペーサー11A〜11Dが配置される。この構造により、半導体素子2の4つのコーナー部は、スペーサー11A〜11Dに食い込む等により集中した応力の一部が分散し、半導体素子2のチッピングが防止される。

【0038】

尚、本実施の形態では、CSP型の半導体装置1として説明するが、複数の受動素子や能動素子が組み込まれ、樹脂封止された回路装置の場合でも、前述したスペーサー構造を用いることで同様な効果が得られる。あるいは、放熱性が必要とされる受動素子や能動素子のみ、前述したスペーサー構造を用いる場合でも良い。

【0039】

また、半導体素子2下面の導電パターン9A〜9Cが櫛歯状に配置される場合について説明したが、この場合に限定するものではない。導電パターン9A〜9Cが、半導体素子2下面でパターニングされ、樹脂封止体にて電気的に絶縁される構造において、前述したスペーサー構造を用いることで同様な効果が得られる。その他、本発明の要旨を逸脱しない範囲で、種々の変更が可能である。

【0040】

次に、本発明の第2の実施の形態である半導体装置について説明する。図3(B)は、図3(A)に示す半導体装置のD−D線方向の断面図である。図4(A)は、図3(A)に示す半導体装置のE−E線方向の断面図である。図4(B)は、図3(A)に示す半導体装置の裏面側からの平面図である。尚、図3(A)の説明では、半導体装置の表面側からは封止樹脂体により見えない部分も実線、点線や一点鎖線により示し、説明している。

【0041】

図3(A)に示す半導体装置21は、半導体素子22及び半導体素子22のパッド電極と接続する導電プレート23を含め樹脂封止するパッケージである。

【0042】

図示したように、最外周の実線24による矩形形状は、樹脂封止体25の外形を示し、その内側に示す点線26による矩形形状は、半導体素子22の外形を示す。そして、一点鎖線27による矩形形状は、導電プレート23を示す。また、実線24の内側に示す実線は、半導体素子22や導電プレート23が固着される導電パターン28A〜28Cを示し、導電パターン28A〜28Cは、分離溝29により区分され、電気的にショートしない構造となる。

【0043】

前述した第1の実施の形態と同様に、斜線のハッチングで示すスペーサー30A〜30Dが、導電パターン28B上に配置される。そして、スペーサー30A〜30Dは、半導体素子22の4つのコーナー部下面に配置される。尚、スペーサー30A〜30Dは、その上面に半導体素子22が安定した状態にて配置される領域に配置される場合でも良い。

【0044】

図3(B)に示すD−D線方向の断面では、半導体素子22が、導電パターン28A、28B上にフェイスダウンにて実装される。半導体素子22は、例えば、MOSトランジスタであり、その表面側にゲート電極用のパッド電極32とソース電極用のパッド電極33が配置される。そして、導電パターン28Aは、導電性接着材31を介してパッド電極32と電気的に接続され、導電パターン28Bは、導電性接着材31を介してパッド電極33と電気的に接続される。

【0045】

一方、半導体素子22の裏面側には、ドレイン電極用のパッド電極34が配置され、導電プレート23とパッド電極34とは導電性接着材31を介して電気的に接続される。導電プレート23は、Cuフレーム等の導電性材料より形成され、パッド電極34及び導電パターン28Cとの接続領域には、半田濡れ性を高めるメッキ処理が施される。そして、導電パターン28Cは、導電性接着材31及び導電プレート23を介してパッド電極34と電気的に接続される。導電プレート23を用いることで、金属細線を用いる場合と比較して、オン抵抗値や寄生抵抗値が低減でき、大電流に対応することが可能となり、また、放熱性にも優れた構造が実現される。

【0046】

図示したように、半導体装置21の裏面側には、被覆層35が形成される。そして、外部電極36、37、38が、被覆層35の開口部から露出する導電パターン28A〜28C上に形成される。

【0047】

尚、樹脂封止体25、導電パターン28A〜28C、導電性接着材31、被覆層35及び外部電極36〜38の材料や構造は、図1及び図2を用いて説明した第1の実施の形態の材料や構造と同様であり、その説明を参酌する。

【0048】

図4(A)に示すE−E線方向の断面では、導電パターン28A、28B上にスペーサー30A、30Bが配置され、半導体素子22のコーナー部が、スペーサー30A、30B上に配置される。そして、スペーサー30A、30Bにより確保された幅W2の隙間や分離溝29内には、樹脂封止体25が形成され、導電パターン28A、28Bは、樹脂封止体25と密着し、半導体装置21内に支持される。尚、図示していないが、半導体素子22のその他のコーナー部下面にもスペーサー30C、30Dが配置され、半導体素子22と導電パターン28A〜28Cとの間の隙間の幅W2は、一定幅に保たれる。

【0049】

図4(B)は、半導体装置21の裏面側を示し、被覆層35の開口部から露出する導電パターン28A〜28C上には外部電極36〜38が形成される。図示したように、外部電極36〜38は、点線にて示す導電パターン28A〜28Cに対応し、それぞれ紙面Y軸方向に延在して配置される。

【0050】

尚、本実施の形態においても、前述した第1の実施の形態と同様に、半導体素子22のコーナー部下面にスペーサー30A〜30Dが配置されることで、同様な効果が得られる。その他、本発明の要旨を逸脱しない範囲で、種々の変更が可能である。

【0051】

次に、本発明の第3の実施の形態である半導体装置の製造方法について、図5〜図11を参照して説明する。尚、本実施の形態では、主に、図1(B)に示す断面構造を用いてその製造方法を説明するため、図1及び図2に示す同一の構成部材には同一の符番を付している。

【0052】

先ず、図5(A)に示す如く、シート状の導電箔41を用意する。導電箔41は、Cuを主材料とした導電箔、Alを主材料とした導電箔またはFe−Ni等の合金から成る導電箔等が採用される。そして、導電箔41の厚さは、後のエッチングを考慮すると10μm〜300μm程度が好ましい。尚、シート状の導電箔41は、所定の幅、例えば45mmでロール状に巻かれて用意され、これが後述する各工程に搬送されても良いし、所定の大きさにカットされた短冊状の導電箔41が用意され、後述する各工程に搬送されても良い。

【0053】

図5(B)に示す如く、短冊状の導電箔41には、多数の搭載部が形成されるブロック42が4〜5個離間して並べられる。各ブロック42間にはスリット43が設けられ、モールド工程等での加熱処理で発生する導電箔41の応力を吸収する。また、導電箔41の上下周端にはインデックス孔44が一定の間隔で設けられ、各工程での位置決めに用いられる。

【0054】

次に、図6(A)に示す如く、導電箔41上に、フォトレジスト(耐エッチングマスク)45を形成し、導電パターン9B、9Cとなる領域を除いた導電箔41が露出するようにフォトレジスト45をパターニングする。そして、フォトレジスト45をマスクとして用い導電箔41を選択的にエッチングすることで、図6(B)に示すように、導電パターン9A〜9Cが形成される。砂状のハッチングにて示す領域が、分離溝10の領域及び搭載部46周囲の領域であり、そのエッチングされる深さは、例えば、50μmである。

【0055】

図6(C)では、導電箔41に形成されたブロック42の1個を示し、例えば、1つのブロック42には、図6(B)に示す搭載部46がマトリックス状に多数配列され、各搭載部46毎に同一の導電パターン9A〜9Cが形成される。そして、各搭載部46間の導電箔41もエッチングされ、後工程での樹脂の注入効率を向上させる。

【0056】

次に、図7(A)に示す如く、導電箔41上のフォトレジスト45(図6(A)参照)を除去した後、導電パターン9A〜9Cが形成された導電箔41上にPSRを、例えば、50μmの膜厚にて形成する。そして、図7(B)に示すように、各搭載部46毎に、点線5にて示す半導体素子2の4つのコーナー部下面にPSRが残存するように、PSRを露光処理した後、現像処理することで、導電パターン9A〜9C上の所望領域にスペーサー11A〜11Dが形成される。

【0057】

次に、図8(A)に示す如く、各搭載部46毎に、導電パターン9A〜9C上に、例えば、半田クリーム等の導電性接着材12をスクリーン印刷により塗布する。そして、半導体素子2をフェイスダウンにてスペーサー11A〜11D上に位置するようにマウントした後、リフローする。このとき、スクリーン印刷される導電性接着材12の膜厚は、スペーサー11A〜11Dの膜厚と同等か、若干、厚い膜厚となる。この製造方法により、図8(B)に示すように、リフローした際に、半導体素子2の自重により、半導体素子2は導電パターン9A〜9C側へと沈むが、スペーサー11A〜11Dにより一定の高さに保たれる。そして、半導体素子2のパッド電極8A、8B、7B、7Cと導電パターン9B、9Cとは、導電性接着材12の表面張力を利用し接着される。尚、導電性接着材12は、導電パターン9A〜9Cの幅よりも狭い領域にスクリーン印刷されることで、導電性接着材12が、導電パターン9A〜9C上から分離溝10へと流れ込むこともなく、導電パターン9A〜9C同士が、導電性接着材12を介してショートすることもない。また、導電パターン9A〜9C上にPSRをパターン配置し、導電性接着材12が広がる範囲を規制し、電パターン9A〜9C同士が、導電性接着材12を介してショートすること防止する場合でも良い。この場合のPSRは、スペーサー11A〜11Dの膜厚よりも薄く形成される。

【0058】

次に、図9(A)に示す如く、トランスファーモールドあるいはインジェクションモールドを用い、各ブロック42毎に1つの共通のモールド金型に導電箔41を収納し、図11に示すように、各ブロック毎に共通の樹脂封止体47を形成する。そして、トランスファーモールドにより共通の樹脂封止体47を形成する際には、エポキシ樹脂等の熱硬化性樹脂が用いられ、インジェクションモールドにより共通の樹脂封止体47を形成する際には、ポリイミド樹脂、ポリフェニレンサルファイド等の熱可塑性樹脂が用いられる。

【0059】

図示したように、共通の樹脂封止体47を形成するまでは、導電パターン9A〜9Cとなる導電箔41が支持基板となる。そして、分離溝10は、導電箔41の厚みよりも浅く形成されるため、この樹脂モールド工程では導電箔41の導電パターン9A〜9Cは個々に分離されていない。そのため、シート状の導電箔41として一体に取り扱え、金型への搬送、金型への実装の作業が容易に行われる。

【0060】

また、この樹脂モールド工程では、半導体素子2下面の隙間及び分離溝10内が、共通の樹脂封止体47を構成する樹脂により充填されなければならない。図1(B)に示すように、半導体装置1は支持基板を有しない構造のため、導電パターン9A〜9Cが、共通の樹脂封止体47を構成する樹脂と密着しなければならないからである。そして、半導体素子2として、パワー系の半導体素子を用いた場合には、この領域の放熱性を向上させる必要もあり、共通の樹脂封止体47を構成する樹脂にはフィラーが含有される。

【0061】

前述したように、放熱性を考慮し、フィラーの粒径としては、例えば、最大で25μmものが用いられるが、スペーサー11A〜11Dにより、半導体素子2の下面の幅W1が、50μm程度確保されることで、樹脂は容易に流動し、半導体素子2下面の隙間及び分離溝10内は確実に充填される。そして、図6(C)に示すように、各搭載部36間の導電箔41も分離溝10と同様にエッチングされることで、図9(B)に示すように、各搭載部46では、全ての側辺側から半導体素子2下面へと樹脂が流入し易くなる。そのため、各側辺側から半導体素子2下面へと流れ込んだ樹脂の流路が短くなり、半導体素子2下面の狭い隙間での樹脂の充填性が向上される。

【0062】

また、トランスファーモールドを用いることで、樹脂注入時の圧力が大きくなり、樹脂の流動性が高められ、更に樹脂の充填性が向上される。そして、従前のように別工程にて半導体素子2の下面にアンダーフィル材を注入する工程が省略され、生産性が向上される。

【0063】

次に、図10に示す如く、導電箔41の裏面側から、例えば、研磨装置または研削装置により全面を削り、分離溝10から共通の樹脂封止体47の一部を露出させ、導電パターン9A〜9Cを分離させる。尚、導電箔41の裏面側からウェトエッチングを行い、導電パターン9A〜9Cを分離させる場合でも良い。あるいは、研磨工程または研削工程とウェトエッチング工程とを組み合わせる場合でも良い。

【0064】

この工程により、共通の樹脂封止体47の裏面から導電パターン9A〜9Cの裏面が露出する。そして、共通の樹脂封止体47の裏面側の導電パターン9A〜9Cを被覆するように、被覆層6を形成する。被覆層6としては、エポキシ樹脂等の熱硬化性樹脂またはポリエチレン等の熱可塑性樹脂やPSRが用いられる。そして、外部電極15、16が形成される導電パターン9B、9C上の被覆層6は開口され、その開口部を利用して外部電極15、16を形成する。

【0065】

最後に、図11に示す如く、各ブロック42毎に、共通の樹脂封止体47をダイシング装置の載置台に真空で吸着させ、ダイシングブレード48で各搭載部46間のダイシングライン49に沿って共通の樹脂封止体47をダイシングし、個別の半導体装置1に分離する。

【符号の説明】

【0066】

1 半導体装置

2 半導体素子

4 樹脂封止体

9A、9B、9C 導電パターン

10 分離溝

11A、11B、11C、11D スペーサー

12 導電性接着材

【技術分野】

【0001】

本発明は、放熱性を向上させる半導体装置およびその製造方法に関する。

【背景技術】

【0002】

従来の半導体装置の実施例として、下記の構造が知られている。

【0003】

図12(A)は、半導体装置51の平面図を示し、樹脂封止体52内には、半導体素子53や導電パターン54が配置される。点線55は、半導体素子53の外形ラインを示し、半導体素子53の外周囲に沿って複数のパッド電極56が配置される。そして、導電パターン54は、主に、放熱用の電極54A、配線54B及び外部接続電極54Cから構成され、半導体素子53の下面に配置される。

【0004】

図12(B)は、図12(A)に示す半導体装置51のF−F線方向の断面図を示す。半導体素子53が導電パターン54上にフェイスダウンにて実装される。半導体素子53のパッド電極56と外部接続電極54Cとは、半田等の導電性接着材58により電気的に接続される。そして、導電パターン54は、分離溝59によりパターニングされ、半導体素子53と導電パターン54との間には、アンダーフィル材60が充填される。導電パターン54同士は分離溝59により分離されるが、アンダーフィル材60により支持され、導電パターン54は樹脂封止体52内に支持される。また、半導体素子53は、アンダーフィル材60により放熱用の電極54A上に固着される。

【0005】

図示したように、半導体装置51の裏面側には絶縁被膜61が形成され、絶縁被膜61に形成された開口領域を利用して、導電パターン54と接続する電極62が形成される(例えば、特許文献1参照。)。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2002−83903号公報(第5−8頁、第1−4図)

【発明の概要】

【発明が解決しようとする課題】

【0007】

図12(B)に示す如く、半導体装置51は、支持基板を有さず、導電パターン54上に半導体素子53が固着される構造となる。そして、半導体素子53は、導電パターン54上にフェイスダウンにて実装され、導電パターン54同士のショートを防止するため、導電パターン54は、分離溝59を用いて分離される必要がある。この構造により、導電パターン54が樹脂封止体52から抜け落ちることを防止するため、半導体素子53下面にはアンダーフィル材60が充填され、導電パターン54同士がアンダーフィル材60により支持される必要がある。

【0008】

このとき、半導体素子53と導電パターン54との間の隙間は、導電性接着材58の厚みとなり、その幅W3は狭くなる。そのため、アンダーフィル材60としては、狭い空間に浸透可能な絶縁材料が用いられ、樹脂封止体52の形成前に半導体素子53下面の隙間が、アンダーフィル材60により充填される。そして、アンダーフィル材60内のフィラーの含有率を高めるとアンダーフィル材の流動性が悪化するため、アンダーフィル材内のフィラーの含有率を高くし難く、放熱性の悪い材料となる。

【0009】

この構造により、半導体素子53の下面には放熱用の電極54Aが配置されるが、両者間にはアンダーフィル材60が介在することで、半導体素子53からの熱の伝導性が悪化し、半導体装置51としての放熱性が悪化するという問題がある。特に、パワー系の半導体素子では、半導体素子の温度上昇が著しく、優れた放熱性が要求される。

【0010】

その一方、半導体装置51の放熱性を向上させるためには、半導体素子53下面にフィラーの含有率の高い樹脂が充填される必要がある。更に、フィラーの粒径を大きくする程熱伝導率も向上する。そのため、半導体素子53下面の隙間に放熱性に優れた樹脂を充填するためには、その隙間の幅W3が一定幅に保たれる必要がある。しかしながら、半導体素子53下面の隙間の幅W3は、導電性接着材58の厚みとなるため、導電性接着材58の塗布量によりばらつき、一定幅として確保し難いという問題がある。更に、フェイスダウン型の半導体素子53では、リフローの際に半導体素子53の自重により導電性接着材58の厚みを所望の厚みとして確保し難いという問題がある。

【0011】

そのため、樹脂封止体52を形成する工程において、例えば、トランスファーモールドにより、半導体素子53下面の隙間にフィラーが含有された樹脂を充填することも難しく、量産性に適さないという問題がある。特に、放熱性を重視し、樹脂内のフィラーの含有率を増大させた場合には、樹脂の流動性が悪化し、より半導体素子54下面の隙間にその樹脂を充填し難くなる。そして、支持基板を有しない半導体装置51では、導電パターン54間に未充填領域が発生し、導電パターン54が半導体装置51内に支持されず、抜け落ちる等の不良品が発生し易くなる。

【0012】

また、半導体素子53下面の隙間の幅W3を広げるために導電性接着材58の塗布量を増大させることも考えられる。しかしながら、導電性接着材58の塗布量を増大させることで、リフローの際に半導体素子53の自重により導電性接着材58が導電パターン54上から流れ出し、隣り合う導電パターン54同士が、導電性接着材58を介してショートするという新たな問題が発生する。

【課題を解決するための手段】

【0013】

前述した各事情に鑑みて成されたものであり、本発明の半導体装置では、少なくともその一主面側に複数のパッド電極が配置された半導体素子と、前記半導体素子の一主面側に配置されたパッド電極と対応して形成され、前記半導体素子の一主面側がフェイスダウンにて電気的に接続された導電パターンと、前記導電パターンの一主面と対向する他の主面側が露出するように前記半導体素子を封止する樹脂封止体とを有し、前記導電パターンの一主面上には、前記半導体素子の一主面側と当接するスペーサーが配置され、前記半導体素子と前記導電パターンの一主面との間の隙間には、前記樹脂封止体を構成する樹脂が充填されることを特徴とする。

【0014】

また、本発明の半導体装置の製造方法では、導電箔を用意し、前記導電箔の一主面側に前記導電箔の膜厚よりも浅い分離溝を形成し、導電パターンを形成する工程と、前記導電パターンの一主面上にスペーサーを形成し、前記スペーサーと当接するように前記導電パターンの一主面上に半導体素子をフェイスダウンにて電気的に接続する工程と、前記導電パターンの一主面と対向する他の主面側が露出するように、前記半導体素子を封止する樹脂封止体を形成する工程と、前記導電箔の一主面側と対向する他の主面側から、前記分離溝を充填する前記樹脂封止体が露出するまで前記導電箔を除去する工程とを有することを特徴とする。

【発明の効果】

【0015】

本発明では、フェイスダウン型の半導体素子と導電パターンとの間にスペーサーが配置され、両者間の隙間の幅が一定に保たれ、その隙間への樹脂の充填性が向上される。

【0016】

また、本発明では、半導体素子のコーナー部の下面にスペーサーが配置されることで、スペーサーが応力緩和部材として機能し、半導体素子のチッピングが防止される。

【0017】

また、本発明では、半導体素子の下面への樹脂の充填性が向上されることで、半導体素子の下面の導電パターンが樹脂により確実に絶縁される。

【0018】

また、本発明では、半導体素子の下面への樹脂の充填性が向上されることで、樹脂内のフィラーの含有率が高められ、放熱性が向上される。

【0019】

また、本発明では、トランスファーモールドにより半導体素子の下面の隙間へ樹脂を充填することで、量産性が向上される。

【0020】

また、本発明では、スペーサーを利用して半導体素子を導電パターン上に固着することで、半導体素子の下面の幅を一定幅に保つことができる。

【図面の簡単な説明】

【0021】

【図1】本発明の実施の形態における半導体装置を説明する(A)平面図、(B)断面図である。

【図2】本発明の実施の形態における半導体装置を説明する(A)断面図、(B)断面図、(C)平面図である。

【図3】本発明の実施の形態における半導体装置を説明する(A)平面図、(B)断面図である。

【図4】本発明の実施の形態における半導体装置を説明する(A)断面図、(B)平面図である。

【図5】本発明の実施の形態における半導体装置の製造方法を説明する(A)断面図、(B)平面図である。

【図6】本発明の実施の形態における半導体装置の製造方法を説明する(A)断面図、(B)平面図、(C)平面図である。

【図7】本発明の実施の形態における半導体装置の製造方法を説明する(A)断面図、(B)平面図である。

【図8】本発明の実施の形態における半導体装置の製造方法を説明する(A)断面図、(B)断面図である。

【図9】本発明の実施の形態における半導体装置の製造方法を説明する(A)断面図、(B)平面図である。

【図10】本発明の実施の形態における半導体装置の製造方法を説明する断面図である。

【図11】本発明の実施の形態における半導体装置の製造方法を説明する断面図である。

【図12】従来の実施の形態における半導体装置を説明する(A)平面図、(B)断面図である。

【発明を実施するための形態】

【0022】

以下に、本発明の第1の実施の形態である半導体装置について説明する。図1(B)は、図1(A)に示す半導体装置のA−A線方向の断面図である。図2(A)は、図1(A)に示す半導体装置のB−B線方向の断面図である。図2(B)は、図1(A)に示すC−C線方向の断面図である。図2(C)は、図1(A)に示す半導体装置の裏面側からの平面図である。尚、図1(A)の説明では、半導体装置1の表面側からは封止樹脂体により見えない部分も実線や点線により示し、説明している。

【0023】

図1(A)に示す如く、半導体装置1は、内蔵される半導体素子2よりも外形寸法が若干大きいサイズの樹脂封止型のCSP(Chip Size Package)である。最外周の実線3による矩形形状は、樹脂封止体4の外形を示し、その内側に示す点線5による矩形形状は、半導体素子2の外形を示す。そして、半導体素子2の表面側には、点線にて示すように、紙面Y軸方向に延在する複数のパッド電極6、7A〜7C、8A〜8Cが配置される。

【0024】

一方、実線3の内側に示す実線は、半導体素子2が固着される導電パターン9A〜9Cを示し、導電パターン9A〜9Cは、分離溝10により区分され、電気的にショートしない構造となる。そして、導電パターン9Aは、半導体素子2のパッド電極6と電気的に接続し、導電パターン9Bは、半導体素子2のパッド電極7A〜7Cと電気的に接続し、導電パターン9Cは、半導体素子2のパッド電極8A〜8Cと電気的に接続する。導電パターン9B、9Cは、それぞれ紙面Y軸方向に延在し、櫛歯状に配置される。

【0025】

図示したように、半導体装置1の4つのコーナー部近傍には、斜線のハッチングで示すスペーサー11A〜11Dが、導電パターン9A〜9C上に配置される。そして、スペーサー11A〜11Dは、半導体素子2の4つのコーナー部下面にそれぞれ配置される。尚、スペーサー11A〜11Dは、その上面に半導体素子2が安定した状態にて配置される領域に配置される場合でも良い。

【0026】

図1(B)に示す如く、導電パターン9B、9Cは、Cuを主材料とした導電箔、Alを主材料とした導電箔、またはFe−Ni等の合金から成る導電箔等を用いて形成される。そして、分離溝10は、前述した導電箔を非異方性のエッチング、例えば、ウエットエッチングすることで形成され、導電パターン9B、9Cの側面は、湾曲構造を有する。尚、導電パターン9B、9Cの材料としては、他の導電材料でも可能であり、特にエッチングできる導電材、レーザで蒸発する導電材が好ましい。また、ハーフエッチング性、メッキの形成性、熱応力等を考慮すると、圧延で形成されたCuを主材料とする導電材料が好ましい。

【0027】

スペーサー11A、11Dは、例えば、PSR(Photo solder resist)を用いて形成される。例えば、導電パターン9B、9C上にPSRを塗布した後、そのPSRを露光処理した後、現像処理することで、スペーサー11A、11Dは所望の領域に形成される。そして、スペーサー11A、11Dの膜厚は、導電パターン9B、9C上に塗布されたPSRの膜厚となり、用途に応じて任意の設計変更が可能である。スペーサー11A、11Dの膜厚は、半導体素子2を導電パターン9B、9C上に実装する際のリフロー工程では、その膜厚は変わらないため、半導体素子2と導電パターン9B、9Cとの隙間の幅W1は、スペーサー11A、11Dの膜厚となる。尚、スペーサー11A、11Dは、前述した隙間の幅W1が一定に保たれる構造であれば、半田バンプや金属バンプから形成される場合でも良い。

【0028】

半導体素子2は、導電パターン9B、9C上に半田クリーム、ロウ材または導電性ペースト等の導電性接着材12を介してフェイスダウンにて実装される。そして、半導体素子2としては、IC、LSI、ディスクリート型のトランジスタ、ダイオード等の能動素子が用いられる。例えば、図1(A)に示す半導体素子2は、窒化ガリウムを用いたパワートランジスタであり、パッド電極6がゲート電極であり、パッド電極7A〜7Cはソース電極であり、パッド電極8A〜8Cはドレイン電極として用いられる。このパワートランジスタは、シリコンを用いたパワートランジスタよりも高耐圧及び高速性を有する素子であり、大電流を流すことが可能となり、素子の放熱性が重要なテーマとなる。

【0029】

樹脂封止体4は、半導体素子2を被覆するように形成され、トランスファーモールドにより形成される場合には熱硬化性樹脂により形成され、または、インジェクションモールドにより形成される場合には熱可塑性樹脂により形成される。図示したように、樹脂封止体4は、半導体素子2と導電パターン9B、9Cとの間の隙間や分離溝10にも配置される。そして、半導体装置1は支持基板を有しないため、半導体素子2下面に位置する導電パターン9B、9Cは、その樹脂封止体4と密着することで、樹脂封止体4内に支持される。

【0030】

被覆層13は、半導体装置1の裏面側を被覆し、外部電極14、15が形成される箇所の被覆層13には開口部が形成される。そして、被覆層13は、エポキシ樹脂等の熱硬化性樹脂、ポリエチレン等の熱可塑性樹脂またはPSRから形成される。

【0031】

外部電極14、15は、半田等の導電性材料から成り、被覆層13の開口部から露出する導電パターン9B、9C上に形成される。そして、外部電極14、15は、半導体装置1に内蔵される半導体素子2と導電パターン9B、9Cを介して電気的に接続される。

【0032】

図2(A)に示すB−B線方向の断面では、導電パターン9A、9B上にスペーサー11A、11Bが配置され、半導体素子2のコーナー部が、スペーサー11A、11B上に配置される。そして、スペーサー11A、11Bにより確保された幅W1の隙間や分離溝10内には、樹脂封止体4が形成され、導電パターン9A、9Bは、樹脂封止体4と密着し、半導体装置1内に支持される。また、被覆層13の開口部から露出する導電パターン9A、9B上には外部電極15、16が形成される。尚、導電パターン9A、スペーサー11Bや外部電極16の構造及び材料は、前述した導電パターン9B、9C、スペーサー11A、11Dや外部電極14、15と同様である。

【0033】

図2(B)に示すC−C線方向の断面では、導電パターン9C上にスペーサー11C、11Dが配置され、半導体素子2のコーナー部が、スペーサー11C、11D上に配置される。そして、スペーサー11C、11Dにより確保された幅W1の隙間内には、樹脂封止体4が形成される。また、被覆層13の開口部から露出する導電パターン9A上には外部電極14が形成される。尚、スペーサー11Cの構造及び材料は、前述したスペーサー11A、11Dと同様である。

【0034】

図2(C)は、半導体装置1の裏面側を示し、被覆層13の開口部から露出する導電パターン9A〜9C上には外部電極14〜16が形成される。そして、導電パターン9A〜9Cは点線にて表示するが、前述したように、半導体素子2が、窒化ガリウムを用いたパワートランジスタである場合には、外部電極16がゲート電極であり、外部電極15はソース電極であり、外部電極14はドレイン電極として用いられる。図示したように、外部電極14〜16は、それぞれ紙面Y軸方向に延在して配置され、ソース電極用の外部電極15とドレイン電極用の外部電極14は、紙面X軸方向に交互に配置される。

【0035】

前述したように、半導体素子2の4つのコーナー部下面には、それぞれスペーサー11A〜11Dが配置され、そのスペーサー11A〜11Dの膜厚により、半導体素子2と導電パターン9A〜9Cとの隙間の幅W1が、一定幅に保たれる。そのため、半導体素子2下面の幅W1は、トランスファーモールドにより樹脂が充填されるのに必要な幅に容易に調整される。また、スペーサー11A〜11Dの膜厚は、半導体素子2を実装する際の作業熱によりその膜厚が変化することもなく、トランスファーモールドを用いた場合でも半導体素子2下面に未充填領域が発生し難く、量産性に適した構造となる。そして、トランスファーモールドを用いることで、樹脂注入時の圧力を強めることが可能となり、フィラーの含有率を高め、樹脂の流動性が低下した場合でも、前述した未充填領域の発生を防止できる。

【0036】

特に、半導体素子2として、パワー系の半導体素子を用いた場合には、半導体素子2と導電パターン9A〜9Cとの間の領域は電流経路となり、高温領域となる。そのため、半導体素子2の下面に配置される樹脂封止体4は、放熱性に優れた材料により構成される必要があり、樹脂封止体4内のフィラーの含有率が増大されることが望ましい。また、樹脂封止体4内に含有されるフィラーの粒径が大きくなるほど、熱伝導率が向上される。そこで、半導体装置1では、スペーサー11A〜11Dの膜厚を50μm程度とすることで、樹脂封止体4内に含有されるフィラーの粒径を最大で25μm程度のものを用いることが可能となる。尚、スペーサー11A〜11Dの膜厚やフィラーの粒径は、使用される半導体素子に対する放熱性やパッケージ寸法等が考慮され、任意の設計変更が可能である。

【0037】

また、半導体装置1を実装基板(図示せず)上に実装し、電気回路として駆動することで、導電性接着材12を含めた半導体装置1全体としての熱膨張、熱収縮を繰り返す。特に、フェイスダウン型の半導体素子2では、半導体素子2と導電パターン9A〜9Cとの間が高温領域となり、熱膨張、熱収縮する量も大きくなる。そして、半導体素子2は、導電性接着材12との接着面積も広く、導電性接着材12による熱膨張や熱収縮の影響を受け易く、半導体装置1の厚み方向や幅方向への伸縮を繰り返す。そのため、熱膨張や熱収縮により応力集中し易い半導体素子2の4つのコーナー部下面には、スペーサー11A〜11Dが配置される。この構造により、半導体素子2の4つのコーナー部は、スペーサー11A〜11Dに食い込む等により集中した応力の一部が分散し、半導体素子2のチッピングが防止される。

【0038】

尚、本実施の形態では、CSP型の半導体装置1として説明するが、複数の受動素子や能動素子が組み込まれ、樹脂封止された回路装置の場合でも、前述したスペーサー構造を用いることで同様な効果が得られる。あるいは、放熱性が必要とされる受動素子や能動素子のみ、前述したスペーサー構造を用いる場合でも良い。

【0039】

また、半導体素子2下面の導電パターン9A〜9Cが櫛歯状に配置される場合について説明したが、この場合に限定するものではない。導電パターン9A〜9Cが、半導体素子2下面でパターニングされ、樹脂封止体にて電気的に絶縁される構造において、前述したスペーサー構造を用いることで同様な効果が得られる。その他、本発明の要旨を逸脱しない範囲で、種々の変更が可能である。

【0040】

次に、本発明の第2の実施の形態である半導体装置について説明する。図3(B)は、図3(A)に示す半導体装置のD−D線方向の断面図である。図4(A)は、図3(A)に示す半導体装置のE−E線方向の断面図である。図4(B)は、図3(A)に示す半導体装置の裏面側からの平面図である。尚、図3(A)の説明では、半導体装置の表面側からは封止樹脂体により見えない部分も実線、点線や一点鎖線により示し、説明している。

【0041】

図3(A)に示す半導体装置21は、半導体素子22及び半導体素子22のパッド電極と接続する導電プレート23を含め樹脂封止するパッケージである。

【0042】

図示したように、最外周の実線24による矩形形状は、樹脂封止体25の外形を示し、その内側に示す点線26による矩形形状は、半導体素子22の外形を示す。そして、一点鎖線27による矩形形状は、導電プレート23を示す。また、実線24の内側に示す実線は、半導体素子22や導電プレート23が固着される導電パターン28A〜28Cを示し、導電パターン28A〜28Cは、分離溝29により区分され、電気的にショートしない構造となる。

【0043】

前述した第1の実施の形態と同様に、斜線のハッチングで示すスペーサー30A〜30Dが、導電パターン28B上に配置される。そして、スペーサー30A〜30Dは、半導体素子22の4つのコーナー部下面に配置される。尚、スペーサー30A〜30Dは、その上面に半導体素子22が安定した状態にて配置される領域に配置される場合でも良い。

【0044】

図3(B)に示すD−D線方向の断面では、半導体素子22が、導電パターン28A、28B上にフェイスダウンにて実装される。半導体素子22は、例えば、MOSトランジスタであり、その表面側にゲート電極用のパッド電極32とソース電極用のパッド電極33が配置される。そして、導電パターン28Aは、導電性接着材31を介してパッド電極32と電気的に接続され、導電パターン28Bは、導電性接着材31を介してパッド電極33と電気的に接続される。

【0045】

一方、半導体素子22の裏面側には、ドレイン電極用のパッド電極34が配置され、導電プレート23とパッド電極34とは導電性接着材31を介して電気的に接続される。導電プレート23は、Cuフレーム等の導電性材料より形成され、パッド電極34及び導電パターン28Cとの接続領域には、半田濡れ性を高めるメッキ処理が施される。そして、導電パターン28Cは、導電性接着材31及び導電プレート23を介してパッド電極34と電気的に接続される。導電プレート23を用いることで、金属細線を用いる場合と比較して、オン抵抗値や寄生抵抗値が低減でき、大電流に対応することが可能となり、また、放熱性にも優れた構造が実現される。

【0046】

図示したように、半導体装置21の裏面側には、被覆層35が形成される。そして、外部電極36、37、38が、被覆層35の開口部から露出する導電パターン28A〜28C上に形成される。

【0047】

尚、樹脂封止体25、導電パターン28A〜28C、導電性接着材31、被覆層35及び外部電極36〜38の材料や構造は、図1及び図2を用いて説明した第1の実施の形態の材料や構造と同様であり、その説明を参酌する。

【0048】

図4(A)に示すE−E線方向の断面では、導電パターン28A、28B上にスペーサー30A、30Bが配置され、半導体素子22のコーナー部が、スペーサー30A、30B上に配置される。そして、スペーサー30A、30Bにより確保された幅W2の隙間や分離溝29内には、樹脂封止体25が形成され、導電パターン28A、28Bは、樹脂封止体25と密着し、半導体装置21内に支持される。尚、図示していないが、半導体素子22のその他のコーナー部下面にもスペーサー30C、30Dが配置され、半導体素子22と導電パターン28A〜28Cとの間の隙間の幅W2は、一定幅に保たれる。

【0049】

図4(B)は、半導体装置21の裏面側を示し、被覆層35の開口部から露出する導電パターン28A〜28C上には外部電極36〜38が形成される。図示したように、外部電極36〜38は、点線にて示す導電パターン28A〜28Cに対応し、それぞれ紙面Y軸方向に延在して配置される。

【0050】

尚、本実施の形態においても、前述した第1の実施の形態と同様に、半導体素子22のコーナー部下面にスペーサー30A〜30Dが配置されることで、同様な効果が得られる。その他、本発明の要旨を逸脱しない範囲で、種々の変更が可能である。

【0051】

次に、本発明の第3の実施の形態である半導体装置の製造方法について、図5〜図11を参照して説明する。尚、本実施の形態では、主に、図1(B)に示す断面構造を用いてその製造方法を説明するため、図1及び図2に示す同一の構成部材には同一の符番を付している。

【0052】

先ず、図5(A)に示す如く、シート状の導電箔41を用意する。導電箔41は、Cuを主材料とした導電箔、Alを主材料とした導電箔またはFe−Ni等の合金から成る導電箔等が採用される。そして、導電箔41の厚さは、後のエッチングを考慮すると10μm〜300μm程度が好ましい。尚、シート状の導電箔41は、所定の幅、例えば45mmでロール状に巻かれて用意され、これが後述する各工程に搬送されても良いし、所定の大きさにカットされた短冊状の導電箔41が用意され、後述する各工程に搬送されても良い。

【0053】

図5(B)に示す如く、短冊状の導電箔41には、多数の搭載部が形成されるブロック42が4〜5個離間して並べられる。各ブロック42間にはスリット43が設けられ、モールド工程等での加熱処理で発生する導電箔41の応力を吸収する。また、導電箔41の上下周端にはインデックス孔44が一定の間隔で設けられ、各工程での位置決めに用いられる。

【0054】

次に、図6(A)に示す如く、導電箔41上に、フォトレジスト(耐エッチングマスク)45を形成し、導電パターン9B、9Cとなる領域を除いた導電箔41が露出するようにフォトレジスト45をパターニングする。そして、フォトレジスト45をマスクとして用い導電箔41を選択的にエッチングすることで、図6(B)に示すように、導電パターン9A〜9Cが形成される。砂状のハッチングにて示す領域が、分離溝10の領域及び搭載部46周囲の領域であり、そのエッチングされる深さは、例えば、50μmである。

【0055】

図6(C)では、導電箔41に形成されたブロック42の1個を示し、例えば、1つのブロック42には、図6(B)に示す搭載部46がマトリックス状に多数配列され、各搭載部46毎に同一の導電パターン9A〜9Cが形成される。そして、各搭載部46間の導電箔41もエッチングされ、後工程での樹脂の注入効率を向上させる。

【0056】

次に、図7(A)に示す如く、導電箔41上のフォトレジスト45(図6(A)参照)を除去した後、導電パターン9A〜9Cが形成された導電箔41上にPSRを、例えば、50μmの膜厚にて形成する。そして、図7(B)に示すように、各搭載部46毎に、点線5にて示す半導体素子2の4つのコーナー部下面にPSRが残存するように、PSRを露光処理した後、現像処理することで、導電パターン9A〜9C上の所望領域にスペーサー11A〜11Dが形成される。

【0057】

次に、図8(A)に示す如く、各搭載部46毎に、導電パターン9A〜9C上に、例えば、半田クリーム等の導電性接着材12をスクリーン印刷により塗布する。そして、半導体素子2をフェイスダウンにてスペーサー11A〜11D上に位置するようにマウントした後、リフローする。このとき、スクリーン印刷される導電性接着材12の膜厚は、スペーサー11A〜11Dの膜厚と同等か、若干、厚い膜厚となる。この製造方法により、図8(B)に示すように、リフローした際に、半導体素子2の自重により、半導体素子2は導電パターン9A〜9C側へと沈むが、スペーサー11A〜11Dにより一定の高さに保たれる。そして、半導体素子2のパッド電極8A、8B、7B、7Cと導電パターン9B、9Cとは、導電性接着材12の表面張力を利用し接着される。尚、導電性接着材12は、導電パターン9A〜9Cの幅よりも狭い領域にスクリーン印刷されることで、導電性接着材12が、導電パターン9A〜9C上から分離溝10へと流れ込むこともなく、導電パターン9A〜9C同士が、導電性接着材12を介してショートすることもない。また、導電パターン9A〜9C上にPSRをパターン配置し、導電性接着材12が広がる範囲を規制し、電パターン9A〜9C同士が、導電性接着材12を介してショートすること防止する場合でも良い。この場合のPSRは、スペーサー11A〜11Dの膜厚よりも薄く形成される。

【0058】

次に、図9(A)に示す如く、トランスファーモールドあるいはインジェクションモールドを用い、各ブロック42毎に1つの共通のモールド金型に導電箔41を収納し、図11に示すように、各ブロック毎に共通の樹脂封止体47を形成する。そして、トランスファーモールドにより共通の樹脂封止体47を形成する際には、エポキシ樹脂等の熱硬化性樹脂が用いられ、インジェクションモールドにより共通の樹脂封止体47を形成する際には、ポリイミド樹脂、ポリフェニレンサルファイド等の熱可塑性樹脂が用いられる。

【0059】

図示したように、共通の樹脂封止体47を形成するまでは、導電パターン9A〜9Cとなる導電箔41が支持基板となる。そして、分離溝10は、導電箔41の厚みよりも浅く形成されるため、この樹脂モールド工程では導電箔41の導電パターン9A〜9Cは個々に分離されていない。そのため、シート状の導電箔41として一体に取り扱え、金型への搬送、金型への実装の作業が容易に行われる。

【0060】

また、この樹脂モールド工程では、半導体素子2下面の隙間及び分離溝10内が、共通の樹脂封止体47を構成する樹脂により充填されなければならない。図1(B)に示すように、半導体装置1は支持基板を有しない構造のため、導電パターン9A〜9Cが、共通の樹脂封止体47を構成する樹脂と密着しなければならないからである。そして、半導体素子2として、パワー系の半導体素子を用いた場合には、この領域の放熱性を向上させる必要もあり、共通の樹脂封止体47を構成する樹脂にはフィラーが含有される。

【0061】

前述したように、放熱性を考慮し、フィラーの粒径としては、例えば、最大で25μmものが用いられるが、スペーサー11A〜11Dにより、半導体素子2の下面の幅W1が、50μm程度確保されることで、樹脂は容易に流動し、半導体素子2下面の隙間及び分離溝10内は確実に充填される。そして、図6(C)に示すように、各搭載部36間の導電箔41も分離溝10と同様にエッチングされることで、図9(B)に示すように、各搭載部46では、全ての側辺側から半導体素子2下面へと樹脂が流入し易くなる。そのため、各側辺側から半導体素子2下面へと流れ込んだ樹脂の流路が短くなり、半導体素子2下面の狭い隙間での樹脂の充填性が向上される。

【0062】

また、トランスファーモールドを用いることで、樹脂注入時の圧力が大きくなり、樹脂の流動性が高められ、更に樹脂の充填性が向上される。そして、従前のように別工程にて半導体素子2の下面にアンダーフィル材を注入する工程が省略され、生産性が向上される。

【0063】

次に、図10に示す如く、導電箔41の裏面側から、例えば、研磨装置または研削装置により全面を削り、分離溝10から共通の樹脂封止体47の一部を露出させ、導電パターン9A〜9Cを分離させる。尚、導電箔41の裏面側からウェトエッチングを行い、導電パターン9A〜9Cを分離させる場合でも良い。あるいは、研磨工程または研削工程とウェトエッチング工程とを組み合わせる場合でも良い。

【0064】

この工程により、共通の樹脂封止体47の裏面から導電パターン9A〜9Cの裏面が露出する。そして、共通の樹脂封止体47の裏面側の導電パターン9A〜9Cを被覆するように、被覆層6を形成する。被覆層6としては、エポキシ樹脂等の熱硬化性樹脂またはポリエチレン等の熱可塑性樹脂やPSRが用いられる。そして、外部電極15、16が形成される導電パターン9B、9C上の被覆層6は開口され、その開口部を利用して外部電極15、16を形成する。

【0065】

最後に、図11に示す如く、各ブロック42毎に、共通の樹脂封止体47をダイシング装置の載置台に真空で吸着させ、ダイシングブレード48で各搭載部46間のダイシングライン49に沿って共通の樹脂封止体47をダイシングし、個別の半導体装置1に分離する。

【符号の説明】

【0066】

1 半導体装置

2 半導体素子

4 樹脂封止体

9A、9B、9C 導電パターン

10 分離溝

11A、11B、11C、11D スペーサー

12 導電性接着材

【特許請求の範囲】

【請求項1】

少なくともその一主面側に複数のパッド電極が配置された半導体素子と、

前記半導体素子の一主面側に配置されたパッド電極と対応して形成され、前記半導体素子の一主面側がフェイスダウンにて電気的に接続された導電パターンと、

前記導電パターンの一主面と対向する他の主面側が露出するように前記半導体素子を封止する樹脂封止体とを有し、

前記導電パターンの一主面上には、前記半導体素子の一主面側と当接するスペーサーが配置され、前記半導体素子と前記導電パターンの一主面との間の隙間には、前記樹脂封止体を構成する樹脂が充填されることを特徴とする半導体装置。

【請求項2】

前記スペーサーは、前記半導体素子のコーナー部毎にその下面に配置され、前記半導体素子と前記導電パターンの一主面との間の隙間の幅は、前記スペーサーの膜厚であることを特徴とする請求項1に記載の半導体装置。

【請求項3】

前記導電パターンは、前記半導体素子の一主面側に配置された第1のパッド電極と電気的に接続された第1の導電パターンと、前記半導体素子の一主面側に配置された第2のパッド電極と電気的に接続された第2の導電パターンとを有し、

前記第1の導電パターンと前記第2の導電パターンとは、前記半導体素子の下面にて櫛歯状に配置され、前記第1の導電パターンと前記第2の導電パターン間には、前記樹脂封止体を構成する樹脂が充填されることを特徴とする請求項1または請求項2に記載の半導体装置。

【請求項4】

前記半導体素子の一主面と対向する他の主面側には第3のパッド電極が配置され、前記第3のパッド電極と電気的に接続する導電プレートは、前記半導体素子の周囲に配置された第3の導電パターンと電気的に接続し、前記樹脂封止体に被服されることを特徴とする請求項3に記載の半導体装置。

【請求項5】

前記樹脂封止体内には、前記スペーサーの膜厚よりも粒径の小さいファイラーが含有されることを特徴とする請求項4に記載の半導体装置。

【請求項6】

導電箔を用意し、前記導電箔の一主面側に前記導電箔の膜厚よりも浅い分離溝を形成し、導電パターンを形成する工程と、

前記導電パターンの一主面上にスペーサーを形成し、前記スペーサーと当接するように前記導電パターンの一主面上に半導体素子をフェイスダウンにて電気的に接続する工程と、

前記導電パターンの一主面と対向する他の主面側が露出するように、前記半導体素子を封止する樹脂封止体を形成する工程と、

前記導電箔の一主面側と対向する他の主面側から、前記分離溝を充填する前記樹脂封止体が露出するまで前記導電箔を除去する工程とを有することを特徴とする半導体装置の製造方法。

【請求項7】

前記スペーサーにより前記半導体素子と前記導電パターンの一主面側に隙間を確保した後、トランスファーモールドにより前記樹脂封止体を形成し、前記樹脂封止体により前記隙間を充填することを特徴とする請求項6に記載の半導体装置の製造方法。

【請求項8】

前記導電パターンの一主面上に前記スペーサーを形成し、前記導電パターンの一主面上に前記スペーサーの膜厚以上の導電性接着材を塗布した後、リフローすることで前記半導体素子と前記導電パターンとを電気的に接続することを特徴とする請求項6または請求項7に記載の半導体装置の製造方法。

【請求項1】

少なくともその一主面側に複数のパッド電極が配置された半導体素子と、

前記半導体素子の一主面側に配置されたパッド電極と対応して形成され、前記半導体素子の一主面側がフェイスダウンにて電気的に接続された導電パターンと、

前記導電パターンの一主面と対向する他の主面側が露出するように前記半導体素子を封止する樹脂封止体とを有し、

前記導電パターンの一主面上には、前記半導体素子の一主面側と当接するスペーサーが配置され、前記半導体素子と前記導電パターンの一主面との間の隙間には、前記樹脂封止体を構成する樹脂が充填されることを特徴とする半導体装置。

【請求項2】

前記スペーサーは、前記半導体素子のコーナー部毎にその下面に配置され、前記半導体素子と前記導電パターンの一主面との間の隙間の幅は、前記スペーサーの膜厚であることを特徴とする請求項1に記載の半導体装置。

【請求項3】

前記導電パターンは、前記半導体素子の一主面側に配置された第1のパッド電極と電気的に接続された第1の導電パターンと、前記半導体素子の一主面側に配置された第2のパッド電極と電気的に接続された第2の導電パターンとを有し、

前記第1の導電パターンと前記第2の導電パターンとは、前記半導体素子の下面にて櫛歯状に配置され、前記第1の導電パターンと前記第2の導電パターン間には、前記樹脂封止体を構成する樹脂が充填されることを特徴とする請求項1または請求項2に記載の半導体装置。

【請求項4】

前記半導体素子の一主面と対向する他の主面側には第3のパッド電極が配置され、前記第3のパッド電極と電気的に接続する導電プレートは、前記半導体素子の周囲に配置された第3の導電パターンと電気的に接続し、前記樹脂封止体に被服されることを特徴とする請求項3に記載の半導体装置。

【請求項5】

前記樹脂封止体内には、前記スペーサーの膜厚よりも粒径の小さいファイラーが含有されることを特徴とする請求項4に記載の半導体装置。

【請求項6】

導電箔を用意し、前記導電箔の一主面側に前記導電箔の膜厚よりも浅い分離溝を形成し、導電パターンを形成する工程と、

前記導電パターンの一主面上にスペーサーを形成し、前記スペーサーと当接するように前記導電パターンの一主面上に半導体素子をフェイスダウンにて電気的に接続する工程と、

前記導電パターンの一主面と対向する他の主面側が露出するように、前記半導体素子を封止する樹脂封止体を形成する工程と、

前記導電箔の一主面側と対向する他の主面側から、前記分離溝を充填する前記樹脂封止体が露出するまで前記導電箔を除去する工程とを有することを特徴とする半導体装置の製造方法。

【請求項7】

前記スペーサーにより前記半導体素子と前記導電パターンの一主面側に隙間を確保した後、トランスファーモールドにより前記樹脂封止体を形成し、前記樹脂封止体により前記隙間を充填することを特徴とする請求項6に記載の半導体装置の製造方法。

【請求項8】

前記導電パターンの一主面上に前記スペーサーを形成し、前記導電パターンの一主面上に前記スペーサーの膜厚以上の導電性接着材を塗布した後、リフローすることで前記半導体素子と前記導電パターンとを電気的に接続することを特徴とする請求項6または請求項7に記載の半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【公開番号】特開2011−204862(P2011−204862A)

【公開日】平成23年10月13日(2011.10.13)

【国際特許分類】

【出願番号】特願2010−70098(P2010−70098)

【出願日】平成22年3月25日(2010.3.25)

【出願人】(000001889)三洋電機株式会社 (18,308)

【Fターム(参考)】

【公開日】平成23年10月13日(2011.10.13)

【国際特許分類】

【出願日】平成22年3月25日(2010.3.25)

【出願人】(000001889)三洋電機株式会社 (18,308)

【Fターム(参考)】

[ Back to top ]