半導体装置およびその製造方法

【課題】相対的に厚いゲート絶縁膜を有するMOSトランジスタと相対的に薄いゲート絶縁膜を有するMOSトランジスタを同時に形成する半導体装置およびその製造方法の提供。

【解決手段】相対的に薄いゲート絶縁膜25を有するMOSトランジスタが形成される領域のフィールド絶縁膜端23を相対的に厚いゲート絶縁膜24で覆うことにより、フィールド絶縁膜下部に形成された反転防止拡散層31から相対的に薄いゲート絶縁膜25を有するMOSトランジスタのチャネル領域33をオフセットさせることによって、フィールド絶縁膜の膜厚ばらつきや相対的に厚い第一のゲート絶縁膜24のエッチングばらつき、および反転防止拡散層によるチャネル端の濃度変動の影響を受けず、MOSトランジスタのチャネル幅を短く設計した際に生じる狭チャネル効果の影響を抑制することが可能となり、素子特性が安定した半導体装置。

【解決手段】相対的に薄いゲート絶縁膜25を有するMOSトランジスタが形成される領域のフィールド絶縁膜端23を相対的に厚いゲート絶縁膜24で覆うことにより、フィールド絶縁膜下部に形成された反転防止拡散層31から相対的に薄いゲート絶縁膜25を有するMOSトランジスタのチャネル領域33をオフセットさせることによって、フィールド絶縁膜の膜厚ばらつきや相対的に厚い第一のゲート絶縁膜24のエッチングばらつき、および反転防止拡散層によるチャネル端の濃度変動の影響を受けず、MOSトランジスタのチャネル幅を短く設計した際に生じる狭チャネル効果の影響を抑制することが可能となり、素子特性が安定した半導体装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、相対的に厚いゲート絶縁膜を有するMOSトランジスタと相対的に薄いゲート絶縁膜を有するMOSトランジスタを同時に形成する半導体装置およびその製造方法に関する。

【背景技術】

【0002】

近年、多種多様な携帯機器が流通するようになり、その電源には高エネルギー密度を有し、メモリー効果が発生しないLiイオン電池が多用されている。それに伴い、Liイオン電池の過充電、過放電を検出する保護用ICも必須となっている。例えば、携帯電話向けのLiイオン電池に関しては、3.6V程度の電池電圧となるが、充電する際は20V以上の電圧がかかる事になり、ICとしては高耐圧を有する素子を含むことが要求される。

【0003】

この際、CMOSトランジスタプロセスで上記ICの仕様を満たそうとした場合、低耐圧に適したMOSトランジスタおよび高耐圧に適したMOSトランジスタを形成しなければならない。なぜなら、高耐圧素子はその仕様を満たす為には素子サイズをある程度大きくする必要があり、ICの全体を高耐圧素子で構成した場合、最終的なチップサイズが増大し、コスト競争力のないICとなり、市場の価格に対する要求を満たすことは困難になってしまうからである。その為、高電圧が印加される回路部分に高耐圧素子を使用し、その他の回路領域は低耐圧素子を使用することでチップサイズを抑制しなければならない。

【0004】

このような理由により、半導体装置の製造方法としては、高耐圧、低耐圧それぞれに見合った異なるゲート酸化膜厚を形成することが可能な半導体装置およびその製造方法が必須となっている。

【0005】

以下に、異なるゲート酸化膜厚を有する半導体装置の従来の製造方法を示す。図4(a)から(e)は従来の半導体装置の製造フローを示している。まず図4(a)に示すように、半導体基板52上の素子分離領域に所謂LOCOS法を用いて、フィールド絶縁膜23を形成する。フィールド絶縁膜23の下部には、反転防止拡散層31が形成されている。この拡散層は、フィールド絶縁膜23の形成時に形成する窒化膜をマスクとして、例えばイオン注入法を用いて形成される。

【0006】

次に図4(b)に示すように相対的に厚い第一のゲート絶縁膜24を熱酸化により形成する。その後、図4(c)に示すようにフォトリソグラフィ法を用いて高耐圧素子が形成される領域にフォトレジスト41を形成し、そのフォトレジスト41をマスクとして、低耐圧素子が形成される領域の第一のゲート絶縁膜24をエッチングし除去する。

【0007】

次に、相対的に薄い第二のゲート酸化膜25を熱酸化により形成し、図4(d)に示す構造を得る。次に、図4(e)に示すように、例えば多結晶シリコン膜を用いてゲート電極51を形成し、半導体基板52上にゲート酸化膜厚が異なるMOS構造を得ることが可能となる(例えば特許文献1乃至3参照のこと)。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特開昭58−100450号公報

【特許文献2】特開平1−110761号公報

【特許文献3】特開平3−231456号公報

【発明の概要】

【発明が解決しようとする課題】

【0009】

前述した従来の半導体装置の製造方法においては、低耐圧素子が形成される領域の第一のゲート絶縁膜24を確実に除去する必要があり、第一のゲート絶縁膜24の厚さに対して工程ばらつきを加味し、オーバーエッチングを行う必要がある。この際に、低耐圧素子が形成される領域においてはLOCOS法によって形成されたフィールド絶縁膜23の細った領域、所謂バーズビークと呼ばれる領域もエッチングされることになり、半導体基板52の表面が抉れたような状態で露出することになる。

【0010】

これらにより、低耐圧素子が形成される領域のサイズは、フィールド絶縁膜23のバーズビーク長および第一のゲート酸化膜24のエッチングばらつきにより変動することになる。つまり、MOSトランジスタの幅が変動しやすくなり、MOSトランジスタの特性ばらつきが発生しやすい構造となる。また、低耐圧素子が形成される領域にフィールド絶縁膜23下部に形成した反転防止拡散層31が結果的に迫り出したような構造となる。これらの影響により、MOSトランジスタのチャネル幅を小さく設計した際に閾値電圧が上昇してしまう所謂狭チャネル効果が現れやすく、さらにチャネル幅のばらつきにより、狭チャネル効果の程度が大きく変動することになるので、制御性の悪い製造方法によってMOSトランジスタが作られることになってしまう。

【0011】

また、第一のゲート絶縁膜24がエッチングされたバーズビーク部分の半導体基板表面はLOCOS法によるフィールド絶縁膜形成時に窒化膜があることで発生する応力により、結晶構造が歪んでいると考えられ、第二のゲート絶縁膜25を形成した際に膜質が悪い可能性があり、ゲート絶縁膜の信頼性といった点で懸念を残す。

【0012】

上記のように従来の半導体装置の製造方法においては、素子特性のばらつきを低減する為には素子サイズを大きく設定する必要があり、チップサイズの増加に繋がってしまうというデメリットが問題点としてあり、さらに、ゲート絶縁膜の信頼性という点では素子サイズを大きくしたとしても懸念が残ってしまうという問題点がある。

【課題を解決するための手段】

【0013】

上記の課題を解決するために、本発明は以下の手段を用いた。

(1)相対的に厚いゲート絶縁膜を有するMOSトランジスタと相対的に薄いゲート絶縁膜を有するMOSトランジスタを同時に形成する半導体装置において、相対的に薄いゲート絶縁膜を有するMOSトランジスタ領域のフィールド絶縁膜端を相対的に厚いゲート絶縁膜で覆うことにより、相対的に薄いゲート絶縁膜を有するMOSトランジスタのチャネル領域がフィールド絶縁膜のバーズビーク領域からオフセットされていることを特徴とする半導体装置とした。

(2)(1)記載の相対的に厚いゲート酸化膜を有するMOSトランジスタは、ソースおよびドレインの高濃度拡散層がフィールド絶縁膜によってオフセットされている構造であることを特徴とする半導体装置とした。

(3)第1導電型の半導体基板上にパッド酸化膜を形成する工程と

前記パッド酸化膜上に窒化膜を形成する工程と、

フォトレジストを用いたパターンによって所望の領域のみ前記窒化膜をエッチングする工程と、

窒化膜が開口した領域にイオン注入法を用いて第1導電型の反転防止拡散層および第2導電型のオフセット拡散層を形成する工程と、

前記窒化膜がエッチングされた領域にフィールド絶縁膜を形成する工程と、

前記窒化膜および前記パッド酸化膜を除去する工程と、

前記半導体基板表面に相対的に厚いゲート絶縁膜を形成する工程と、

前記相対的に厚いゲート絶縁膜をフォトレジストを用いたパターンによって所望の領域のみ除去する工程と、

相対的に薄いゲート絶縁膜を形成する工程と、

多結晶シリコン膜を形成する工程と、

多結晶シリコン膜に導電性を持たせる工程と、

フォトレジストを用いたパターンによって所望の領域のみ多結晶シリコン膜をエッチングする工程と、

フォトレジストを用いたパターンによって所望の領域のみにイオン注入法を用いて、第2導電型の高濃度拡散層を形成する工程

を有することを特徴とする半導体装置の製造方法とした。

(4)相対的に厚いゲート絶縁膜を相対的に薄いゲート絶縁膜よりも早い工程で形成することを特徴とした半導体装置の製造方法とした。

(5)(3)記載の相対的に厚いゲート絶縁膜をフォトレジストを用いたパターンによって所望の領域のみ除去する工程において、フォトレジストのパターンは相対的に薄いゲート絶縁膜を有するMOSトランジスタが形成される領域のフィールド絶縁膜端のバーズビーク部分を覆っていることを特徴とする半導体装置の製造方法とした。

(6)(3)記載の相対的に厚いゲート絶縁膜をフォトレジストを用いたパターンによって所望の領域のみ除去する工程において、フォトレジストのパターンは相対的に厚いゲート絶縁膜を有するMOSトランジスタの高濃度拡散層となる領域が開口するように形成されることを特徴とする半導体装置の製造方法とした。

(7)(3)記載のフォトレジストを用いたパターンによって所望の領域のみにイオン注入法を用いて、第2導電型の高濃度拡散層を形成する工程において、イオン注入を行う際の注入エネルギーは相対的に厚いゲート絶縁膜を突き抜けないエネルギーであることを特徴とする半導体装置の製造方法とした。

【発明の効果】

【0014】

相対的に薄いゲート絶縁膜を有するMOSトランジスタが形成される領域のフィールド絶縁膜端を相対的に厚いゲート絶縁膜で覆うことで、フィールド絶縁膜下部に形成された反転防止拡散層から相対的に薄いゲート絶縁膜を有するMOSトランジスタのチャネル領域をオフセットさせることによって、フィールド絶縁膜の膜厚ばらつきや相対的に厚い第一のゲート絶縁膜のエッチングばらつき、および反転防止拡散層によるチャネル端の濃度変動の影響を受けず、MOSトランジスタのチャネル幅を短く設計した際に生じる狭チャネル効果の影響を抑制することが可能となり、素子特性が安定した半導体装置を提供することが可能となる。

【図面の簡単な説明】

【0015】

【図1】本発明の実施例である半導体装置の製造方法を示す模式的断面フロー図である。

【図2】本発明の実施例である半導体装置の製造方法を示す模式的断面フロー図である。

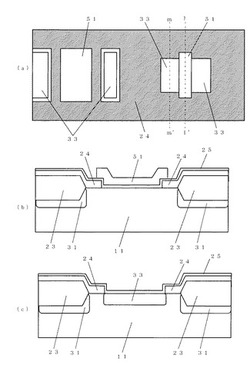

【図3】本発明の実施例である半導体装置を示す模式的平面図および模式的断面図である。

【図4】従来の実施例による半導体装置の製造方法を示す模式的断面フロー図である。

【発明を実施するための形態】

【0016】

以下、本発明による半導体装置およびその製造方法について図面を用いて詳細に説明を行なう。

【0017】

図1および図2に本発明の実施例である半導体装置の製造方法について示す。なお、以下の説明においては、Nチャネル型MOSトランジスタを例に説明を行う。P型半導体基板11上にパッド酸化膜22を形成し、パッド酸化膜22上に窒化膜21を形成し、所望の領域が開口するように窒化膜21をパターニングした後、開口した領域のP型半導体基板11の表面領域にイオン注入法を用いて反転防止拡散層31およびオフセット拡散層32を形成し、図1(a)を得る。なお、窒化膜22のパターニングにおいては、フォトリソグラフィ法を用いてパターニングされたフォトレジストをマスクとして、例えばフッ素系ガスを用いてドライエッチングにて行う。また、素子分離領域には半導体基板と同導電型である例えばボロンをイオン注入し、MOSトランジスタのオフセットとなる領域には、半導体基板と逆導電型である例えばリンをイオン注入し、それぞれ反転防止拡散層31およびオフセット拡散層32を形成する。注入する領域は、フォトリソグラフィ法を用いてパターニングされたレジストをマスクとして使用し、選択的に不純物導入をおこなう。

【0018】

次に窒化膜21をマスクとして、例えばウェット酸素雰囲気中にて熱酸化処理を行い、窒化膜21で覆われていない半導体基板の表面に膜厚が600nm〜800nm程度のフィールド絶縁膜23を形成する。その後、窒化膜21およびパッド酸化膜22を除去し、図1(b)の状態となる。

【0019】

次に図1(c)に示すように、相対的に厚い第一のゲート絶縁膜24を例えばウェット酸素雰囲気中で熱酸化によって形成する。その際、第一のゲート絶縁膜の厚さは、ソースおよびドレインとなる高濃度拡散層を形成する際の不純物イオン注入時に、P型半導体基板11上に不純物が導入されない、つまりイオン注入された不純物が第一のゲート絶縁膜24を突き抜けない厚さに設定する。しかし、その一方で、相対的に厚いゲート絶縁膜を有したMOSトランジスタが、高耐圧素子に要求される最大印加電圧を長時間印加しても破壊しない、もしくは動作が最終的な製品となった際の製品仕様に対して規格外とならない範囲でなるべく薄くなるように決定する。つまり、最終的に膜厚は、両者の兼ね合いで決定することになる。

【0020】

次に、図1(d)に示すように、フォトリソグラフィ法を用いてパターニングされたフォトレジスト41を形成し、相対的に厚い第一のゲート絶縁膜24をエッチングするためのマスクとする。フォトレジスト41は相対的に薄いゲート絶縁膜を有するMOSトランジスタが形成される領域を開口するようにパターニングするが、この領域端にあるフィールド絶縁膜23のバーズビーク領域がフォトレジスト41で覆われるように形成する。

【0021】

また、フォトレジスト41がフィールド絶縁膜23のバーズビークを覆う幅は、フォトレジスト41のアライメントずれおよび厚い第一のゲート絶縁膜24をエッチングする際の横方向へのエッチング量を加味して、バーズビーク領域が露出しないように設定する。また、フォトレジスト41は相対的に厚いゲート絶縁膜を有するMOSトランジスタのソースおよびドレインとなる高濃度拡散層形成領域も開口するようにパターニングする。この時、上記高濃度拡散層形成領域を開口しない場合、厚い第一のゲート絶縁膜24が残ることになる。これにより、別工程にて残った絶縁膜を除去するか、イオン注入による不純物導入工程を追加しなければ、厚いゲート絶縁膜を有するMOSトランジスタの高濃度拡散層を形成できないことになり、工程数の増加に繋がる。よって、工程数を低減させる為に本工程において、前記領域の第一のゲート絶縁膜24を除去することが必要となる。またこの際に、相対的に厚いゲート絶縁膜を有するMOSトランジスタの構造が、フィールド絶縁膜によるオフセットを用いない構造であった場合、ゲート電極となる多結晶シリコン膜が形成される領域にのみ厚いゲート絶縁膜が残るようにフォトレジストを形成しなければならなくなる。しかし、上記のような構造の場合、厚い第一のゲート絶縁膜24をエッチングする際にウェットエッチングを行うと等方性のため、厚い第一のゲート絶縁膜24のサイドもエッチングされてしまうことになり、所謂“す”が発生することになる。仮に異方性のドライエッチングで行ったとしても、ゲート電極となる多結晶シリコン膜と厚い第一のゲート絶縁膜24とのアライメントずれの問題があり、安定した素子を形成することは非常に困難となる。よって、相対的に厚いゲート絶縁膜を有するMOSトランジスタの構造は、フィールド絶縁膜23によるオフセットを有したLOCOSオフセット型MOSトランジスタを用いて、チャネル形成領域とソースおよびドレインが形成される高濃度拡散層領域を分離し、上記課題を回避する必要がある。

【0022】

次に、フォトレジスト41をマスクとして、第一のゲート絶縁膜24をエッチングし、図2(a)の状態を得る。

【0023】

次に、図2(b)に示すように相対的に薄い第二のゲート絶縁膜25を例えばウェット酸素雰囲気中で熱酸化によって形成する。第二のゲート絶縁膜厚は、相対的に薄いゲート絶縁膜を有したMOSトランジスタが、低耐圧素子に要求される最大印加電圧を長時間印加しても破壊しない、もしくは動作が最終的な製品となった際の製品仕様に対して規格外とならない範囲でなるべく薄くなるように決定する。

【0024】

次に、第二のゲート絶縁膜25上に例えば化学気相成長法によって膜厚200nm〜400nmの多結晶シリコン膜を全面に形成し、固層拡散法により例えばリンを1×1020atom/cm3程度の不純物濃度となるように多結晶シリコンに拡散させ、導電性を持たせる。このとき、固層拡散法ではなくイオン注入により不純物を多結晶シリコンに注入する場合もある。その後、導電性を持った多結晶シリコン膜をパターニングし、所望の位置にゲート電極51を形成する。

【0025】

次に、パターニングされたゲート電極51をマスクとして、イオン注入法を用いて例えば砒素を導入し、ソースおよびドレインの高濃度拡散層33を形成し、図2(c)に示す構造を得る。この際、イオン注入される不純物が相対的に厚い第一のゲート絶縁膜24を突き抜けず、相対的に薄い第二のゲート絶縁膜は通過するようにイオン注入のエネルギーを設定する。すなわち、不純物は相対的に厚い第一のゲート絶縁膜24をマスクとして自己整合的に半導体基板11へ導入されることになる。ここで、イオン注入のエネルギー条件は、不純物を導入する領域のP半導体基板11表面に存在する第二のゲート絶縁膜25の厚さのばらつきやイオン注入時の飛程ばらつきを考慮して、安定的に高濃度拡散層33が形成されるエネルギーとする。これより、第一のゲート絶縁膜24の膜厚を決定する際には、以上のようにして定められたイオン注入エネルギーを考慮して行うこととなる。

【0026】

続いて、本発明における効果について図面を用いて説明する。図3(a)は、図2(c)に示す断面構造を平面的に表した図となる。さらに図3(b)は、図3(a)におけるlからl'における一点鎖線部分での断面図となり、図3(c)は図3(a)におけるmからm'における一点鎖線部分での断面図を表している。

【0027】

図3(b)に示すように、相対的に薄いゲート絶縁膜を有するMOSトランジスタのゲート電極51は、フィールド絶縁膜23およびフィールド絶縁膜23の下部に形成される比較的高濃度である反転防止拡散層31からオフセットされた構造となる。これにより、従来の製造方法にて問題となるフィールド絶縁膜23の膜厚ばらつきや第一のゲート絶縁膜24のエッチングばらつき、および反転防止拡散層31によるチャネル端の濃度変動などの影響を受けない、安定した構造となっている。また、図3(c)に示すようにソースおよびドレインとなる高濃度拡散層33も同様にフィールド絶縁膜23からオフセットした構造とすることで、チャネル幅と高濃度拡散層33の幅を合わせる構造としている。

【0028】

以上より、相対的に厚いゲート絶縁膜を有するMOSトランジスタと相対的に薄いゲート絶縁膜を有するMOSトランジスタを同時に形成する半導体装置およびその製造方法において、相対的に薄いゲート酸化膜を有するMOSトランジスタの狭チャネル効果が抑制された、安定した素子特定である半導体装置とその製造方法を提供することが可能となる。

【0029】

本説明では、Nチャネル型MOSトランジスタを例に詳細な説明を行っているが、Pチャネル型MOSトランジスタにおいてもその効果は変わることはない。また、相対的に薄いゲート絶縁膜を有するMOSトランジスタの構造は最も単純なMOSトランジスタの構造で表しているが、例えばLDD(Lightly Doped Drain)構造やLOCOSオフセット構造であったとしても同様の効果が得られる。

【符号の説明】

【0030】

11 P型半導体基板

21 窒化膜

22 パッド酸化膜

23 フィールド絶縁膜

24 第一のゲート絶縁膜

25 第二のゲート絶縁膜

31 反転防止拡散層

32 オフセット拡散層

33 高濃度拡散層

41 フォトレジスト

51 ゲート電極

52 半導体基板

【技術分野】

【0001】

本発明は、相対的に厚いゲート絶縁膜を有するMOSトランジスタと相対的に薄いゲート絶縁膜を有するMOSトランジスタを同時に形成する半導体装置およびその製造方法に関する。

【背景技術】

【0002】

近年、多種多様な携帯機器が流通するようになり、その電源には高エネルギー密度を有し、メモリー効果が発生しないLiイオン電池が多用されている。それに伴い、Liイオン電池の過充電、過放電を検出する保護用ICも必須となっている。例えば、携帯電話向けのLiイオン電池に関しては、3.6V程度の電池電圧となるが、充電する際は20V以上の電圧がかかる事になり、ICとしては高耐圧を有する素子を含むことが要求される。

【0003】

この際、CMOSトランジスタプロセスで上記ICの仕様を満たそうとした場合、低耐圧に適したMOSトランジスタおよび高耐圧に適したMOSトランジスタを形成しなければならない。なぜなら、高耐圧素子はその仕様を満たす為には素子サイズをある程度大きくする必要があり、ICの全体を高耐圧素子で構成した場合、最終的なチップサイズが増大し、コスト競争力のないICとなり、市場の価格に対する要求を満たすことは困難になってしまうからである。その為、高電圧が印加される回路部分に高耐圧素子を使用し、その他の回路領域は低耐圧素子を使用することでチップサイズを抑制しなければならない。

【0004】

このような理由により、半導体装置の製造方法としては、高耐圧、低耐圧それぞれに見合った異なるゲート酸化膜厚を形成することが可能な半導体装置およびその製造方法が必須となっている。

【0005】

以下に、異なるゲート酸化膜厚を有する半導体装置の従来の製造方法を示す。図4(a)から(e)は従来の半導体装置の製造フローを示している。まず図4(a)に示すように、半導体基板52上の素子分離領域に所謂LOCOS法を用いて、フィールド絶縁膜23を形成する。フィールド絶縁膜23の下部には、反転防止拡散層31が形成されている。この拡散層は、フィールド絶縁膜23の形成時に形成する窒化膜をマスクとして、例えばイオン注入法を用いて形成される。

【0006】

次に図4(b)に示すように相対的に厚い第一のゲート絶縁膜24を熱酸化により形成する。その後、図4(c)に示すようにフォトリソグラフィ法を用いて高耐圧素子が形成される領域にフォトレジスト41を形成し、そのフォトレジスト41をマスクとして、低耐圧素子が形成される領域の第一のゲート絶縁膜24をエッチングし除去する。

【0007】

次に、相対的に薄い第二のゲート酸化膜25を熱酸化により形成し、図4(d)に示す構造を得る。次に、図4(e)に示すように、例えば多結晶シリコン膜を用いてゲート電極51を形成し、半導体基板52上にゲート酸化膜厚が異なるMOS構造を得ることが可能となる(例えば特許文献1乃至3参照のこと)。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特開昭58−100450号公報

【特許文献2】特開平1−110761号公報

【特許文献3】特開平3−231456号公報

【発明の概要】

【発明が解決しようとする課題】

【0009】

前述した従来の半導体装置の製造方法においては、低耐圧素子が形成される領域の第一のゲート絶縁膜24を確実に除去する必要があり、第一のゲート絶縁膜24の厚さに対して工程ばらつきを加味し、オーバーエッチングを行う必要がある。この際に、低耐圧素子が形成される領域においてはLOCOS法によって形成されたフィールド絶縁膜23の細った領域、所謂バーズビークと呼ばれる領域もエッチングされることになり、半導体基板52の表面が抉れたような状態で露出することになる。

【0010】

これらにより、低耐圧素子が形成される領域のサイズは、フィールド絶縁膜23のバーズビーク長および第一のゲート酸化膜24のエッチングばらつきにより変動することになる。つまり、MOSトランジスタの幅が変動しやすくなり、MOSトランジスタの特性ばらつきが発生しやすい構造となる。また、低耐圧素子が形成される領域にフィールド絶縁膜23下部に形成した反転防止拡散層31が結果的に迫り出したような構造となる。これらの影響により、MOSトランジスタのチャネル幅を小さく設計した際に閾値電圧が上昇してしまう所謂狭チャネル効果が現れやすく、さらにチャネル幅のばらつきにより、狭チャネル効果の程度が大きく変動することになるので、制御性の悪い製造方法によってMOSトランジスタが作られることになってしまう。

【0011】

また、第一のゲート絶縁膜24がエッチングされたバーズビーク部分の半導体基板表面はLOCOS法によるフィールド絶縁膜形成時に窒化膜があることで発生する応力により、結晶構造が歪んでいると考えられ、第二のゲート絶縁膜25を形成した際に膜質が悪い可能性があり、ゲート絶縁膜の信頼性といった点で懸念を残す。

【0012】

上記のように従来の半導体装置の製造方法においては、素子特性のばらつきを低減する為には素子サイズを大きく設定する必要があり、チップサイズの増加に繋がってしまうというデメリットが問題点としてあり、さらに、ゲート絶縁膜の信頼性という点では素子サイズを大きくしたとしても懸念が残ってしまうという問題点がある。

【課題を解決するための手段】

【0013】

上記の課題を解決するために、本発明は以下の手段を用いた。

(1)相対的に厚いゲート絶縁膜を有するMOSトランジスタと相対的に薄いゲート絶縁膜を有するMOSトランジスタを同時に形成する半導体装置において、相対的に薄いゲート絶縁膜を有するMOSトランジスタ領域のフィールド絶縁膜端を相対的に厚いゲート絶縁膜で覆うことにより、相対的に薄いゲート絶縁膜を有するMOSトランジスタのチャネル領域がフィールド絶縁膜のバーズビーク領域からオフセットされていることを特徴とする半導体装置とした。

(2)(1)記載の相対的に厚いゲート酸化膜を有するMOSトランジスタは、ソースおよびドレインの高濃度拡散層がフィールド絶縁膜によってオフセットされている構造であることを特徴とする半導体装置とした。

(3)第1導電型の半導体基板上にパッド酸化膜を形成する工程と

前記パッド酸化膜上に窒化膜を形成する工程と、

フォトレジストを用いたパターンによって所望の領域のみ前記窒化膜をエッチングする工程と、

窒化膜が開口した領域にイオン注入法を用いて第1導電型の反転防止拡散層および第2導電型のオフセット拡散層を形成する工程と、

前記窒化膜がエッチングされた領域にフィールド絶縁膜を形成する工程と、

前記窒化膜および前記パッド酸化膜を除去する工程と、

前記半導体基板表面に相対的に厚いゲート絶縁膜を形成する工程と、

前記相対的に厚いゲート絶縁膜をフォトレジストを用いたパターンによって所望の領域のみ除去する工程と、

相対的に薄いゲート絶縁膜を形成する工程と、

多結晶シリコン膜を形成する工程と、

多結晶シリコン膜に導電性を持たせる工程と、

フォトレジストを用いたパターンによって所望の領域のみ多結晶シリコン膜をエッチングする工程と、

フォトレジストを用いたパターンによって所望の領域のみにイオン注入法を用いて、第2導電型の高濃度拡散層を形成する工程

を有することを特徴とする半導体装置の製造方法とした。

(4)相対的に厚いゲート絶縁膜を相対的に薄いゲート絶縁膜よりも早い工程で形成することを特徴とした半導体装置の製造方法とした。

(5)(3)記載の相対的に厚いゲート絶縁膜をフォトレジストを用いたパターンによって所望の領域のみ除去する工程において、フォトレジストのパターンは相対的に薄いゲート絶縁膜を有するMOSトランジスタが形成される領域のフィールド絶縁膜端のバーズビーク部分を覆っていることを特徴とする半導体装置の製造方法とした。

(6)(3)記載の相対的に厚いゲート絶縁膜をフォトレジストを用いたパターンによって所望の領域のみ除去する工程において、フォトレジストのパターンは相対的に厚いゲート絶縁膜を有するMOSトランジスタの高濃度拡散層となる領域が開口するように形成されることを特徴とする半導体装置の製造方法とした。

(7)(3)記載のフォトレジストを用いたパターンによって所望の領域のみにイオン注入法を用いて、第2導電型の高濃度拡散層を形成する工程において、イオン注入を行う際の注入エネルギーは相対的に厚いゲート絶縁膜を突き抜けないエネルギーであることを特徴とする半導体装置の製造方法とした。

【発明の効果】

【0014】

相対的に薄いゲート絶縁膜を有するMOSトランジスタが形成される領域のフィールド絶縁膜端を相対的に厚いゲート絶縁膜で覆うことで、フィールド絶縁膜下部に形成された反転防止拡散層から相対的に薄いゲート絶縁膜を有するMOSトランジスタのチャネル領域をオフセットさせることによって、フィールド絶縁膜の膜厚ばらつきや相対的に厚い第一のゲート絶縁膜のエッチングばらつき、および反転防止拡散層によるチャネル端の濃度変動の影響を受けず、MOSトランジスタのチャネル幅を短く設計した際に生じる狭チャネル効果の影響を抑制することが可能となり、素子特性が安定した半導体装置を提供することが可能となる。

【図面の簡単な説明】

【0015】

【図1】本発明の実施例である半導体装置の製造方法を示す模式的断面フロー図である。

【図2】本発明の実施例である半導体装置の製造方法を示す模式的断面フロー図である。

【図3】本発明の実施例である半導体装置を示す模式的平面図および模式的断面図である。

【図4】従来の実施例による半導体装置の製造方法を示す模式的断面フロー図である。

【発明を実施するための形態】

【0016】

以下、本発明による半導体装置およびその製造方法について図面を用いて詳細に説明を行なう。

【0017】

図1および図2に本発明の実施例である半導体装置の製造方法について示す。なお、以下の説明においては、Nチャネル型MOSトランジスタを例に説明を行う。P型半導体基板11上にパッド酸化膜22を形成し、パッド酸化膜22上に窒化膜21を形成し、所望の領域が開口するように窒化膜21をパターニングした後、開口した領域のP型半導体基板11の表面領域にイオン注入法を用いて反転防止拡散層31およびオフセット拡散層32を形成し、図1(a)を得る。なお、窒化膜22のパターニングにおいては、フォトリソグラフィ法を用いてパターニングされたフォトレジストをマスクとして、例えばフッ素系ガスを用いてドライエッチングにて行う。また、素子分離領域には半導体基板と同導電型である例えばボロンをイオン注入し、MOSトランジスタのオフセットとなる領域には、半導体基板と逆導電型である例えばリンをイオン注入し、それぞれ反転防止拡散層31およびオフセット拡散層32を形成する。注入する領域は、フォトリソグラフィ法を用いてパターニングされたレジストをマスクとして使用し、選択的に不純物導入をおこなう。

【0018】

次に窒化膜21をマスクとして、例えばウェット酸素雰囲気中にて熱酸化処理を行い、窒化膜21で覆われていない半導体基板の表面に膜厚が600nm〜800nm程度のフィールド絶縁膜23を形成する。その後、窒化膜21およびパッド酸化膜22を除去し、図1(b)の状態となる。

【0019】

次に図1(c)に示すように、相対的に厚い第一のゲート絶縁膜24を例えばウェット酸素雰囲気中で熱酸化によって形成する。その際、第一のゲート絶縁膜の厚さは、ソースおよびドレインとなる高濃度拡散層を形成する際の不純物イオン注入時に、P型半導体基板11上に不純物が導入されない、つまりイオン注入された不純物が第一のゲート絶縁膜24を突き抜けない厚さに設定する。しかし、その一方で、相対的に厚いゲート絶縁膜を有したMOSトランジスタが、高耐圧素子に要求される最大印加電圧を長時間印加しても破壊しない、もしくは動作が最終的な製品となった際の製品仕様に対して規格外とならない範囲でなるべく薄くなるように決定する。つまり、最終的に膜厚は、両者の兼ね合いで決定することになる。

【0020】

次に、図1(d)に示すように、フォトリソグラフィ法を用いてパターニングされたフォトレジスト41を形成し、相対的に厚い第一のゲート絶縁膜24をエッチングするためのマスクとする。フォトレジスト41は相対的に薄いゲート絶縁膜を有するMOSトランジスタが形成される領域を開口するようにパターニングするが、この領域端にあるフィールド絶縁膜23のバーズビーク領域がフォトレジスト41で覆われるように形成する。

【0021】

また、フォトレジスト41がフィールド絶縁膜23のバーズビークを覆う幅は、フォトレジスト41のアライメントずれおよび厚い第一のゲート絶縁膜24をエッチングする際の横方向へのエッチング量を加味して、バーズビーク領域が露出しないように設定する。また、フォトレジスト41は相対的に厚いゲート絶縁膜を有するMOSトランジスタのソースおよびドレインとなる高濃度拡散層形成領域も開口するようにパターニングする。この時、上記高濃度拡散層形成領域を開口しない場合、厚い第一のゲート絶縁膜24が残ることになる。これにより、別工程にて残った絶縁膜を除去するか、イオン注入による不純物導入工程を追加しなければ、厚いゲート絶縁膜を有するMOSトランジスタの高濃度拡散層を形成できないことになり、工程数の増加に繋がる。よって、工程数を低減させる為に本工程において、前記領域の第一のゲート絶縁膜24を除去することが必要となる。またこの際に、相対的に厚いゲート絶縁膜を有するMOSトランジスタの構造が、フィールド絶縁膜によるオフセットを用いない構造であった場合、ゲート電極となる多結晶シリコン膜が形成される領域にのみ厚いゲート絶縁膜が残るようにフォトレジストを形成しなければならなくなる。しかし、上記のような構造の場合、厚い第一のゲート絶縁膜24をエッチングする際にウェットエッチングを行うと等方性のため、厚い第一のゲート絶縁膜24のサイドもエッチングされてしまうことになり、所謂“す”が発生することになる。仮に異方性のドライエッチングで行ったとしても、ゲート電極となる多結晶シリコン膜と厚い第一のゲート絶縁膜24とのアライメントずれの問題があり、安定した素子を形成することは非常に困難となる。よって、相対的に厚いゲート絶縁膜を有するMOSトランジスタの構造は、フィールド絶縁膜23によるオフセットを有したLOCOSオフセット型MOSトランジスタを用いて、チャネル形成領域とソースおよびドレインが形成される高濃度拡散層領域を分離し、上記課題を回避する必要がある。

【0022】

次に、フォトレジスト41をマスクとして、第一のゲート絶縁膜24をエッチングし、図2(a)の状態を得る。

【0023】

次に、図2(b)に示すように相対的に薄い第二のゲート絶縁膜25を例えばウェット酸素雰囲気中で熱酸化によって形成する。第二のゲート絶縁膜厚は、相対的に薄いゲート絶縁膜を有したMOSトランジスタが、低耐圧素子に要求される最大印加電圧を長時間印加しても破壊しない、もしくは動作が最終的な製品となった際の製品仕様に対して規格外とならない範囲でなるべく薄くなるように決定する。

【0024】

次に、第二のゲート絶縁膜25上に例えば化学気相成長法によって膜厚200nm〜400nmの多結晶シリコン膜を全面に形成し、固層拡散法により例えばリンを1×1020atom/cm3程度の不純物濃度となるように多結晶シリコンに拡散させ、導電性を持たせる。このとき、固層拡散法ではなくイオン注入により不純物を多結晶シリコンに注入する場合もある。その後、導電性を持った多結晶シリコン膜をパターニングし、所望の位置にゲート電極51を形成する。

【0025】

次に、パターニングされたゲート電極51をマスクとして、イオン注入法を用いて例えば砒素を導入し、ソースおよびドレインの高濃度拡散層33を形成し、図2(c)に示す構造を得る。この際、イオン注入される不純物が相対的に厚い第一のゲート絶縁膜24を突き抜けず、相対的に薄い第二のゲート絶縁膜は通過するようにイオン注入のエネルギーを設定する。すなわち、不純物は相対的に厚い第一のゲート絶縁膜24をマスクとして自己整合的に半導体基板11へ導入されることになる。ここで、イオン注入のエネルギー条件は、不純物を導入する領域のP半導体基板11表面に存在する第二のゲート絶縁膜25の厚さのばらつきやイオン注入時の飛程ばらつきを考慮して、安定的に高濃度拡散層33が形成されるエネルギーとする。これより、第一のゲート絶縁膜24の膜厚を決定する際には、以上のようにして定められたイオン注入エネルギーを考慮して行うこととなる。

【0026】

続いて、本発明における効果について図面を用いて説明する。図3(a)は、図2(c)に示す断面構造を平面的に表した図となる。さらに図3(b)は、図3(a)におけるlからl'における一点鎖線部分での断面図となり、図3(c)は図3(a)におけるmからm'における一点鎖線部分での断面図を表している。

【0027】

図3(b)に示すように、相対的に薄いゲート絶縁膜を有するMOSトランジスタのゲート電極51は、フィールド絶縁膜23およびフィールド絶縁膜23の下部に形成される比較的高濃度である反転防止拡散層31からオフセットされた構造となる。これにより、従来の製造方法にて問題となるフィールド絶縁膜23の膜厚ばらつきや第一のゲート絶縁膜24のエッチングばらつき、および反転防止拡散層31によるチャネル端の濃度変動などの影響を受けない、安定した構造となっている。また、図3(c)に示すようにソースおよびドレインとなる高濃度拡散層33も同様にフィールド絶縁膜23からオフセットした構造とすることで、チャネル幅と高濃度拡散層33の幅を合わせる構造としている。

【0028】

以上より、相対的に厚いゲート絶縁膜を有するMOSトランジスタと相対的に薄いゲート絶縁膜を有するMOSトランジスタを同時に形成する半導体装置およびその製造方法において、相対的に薄いゲート酸化膜を有するMOSトランジスタの狭チャネル効果が抑制された、安定した素子特定である半導体装置とその製造方法を提供することが可能となる。

【0029】

本説明では、Nチャネル型MOSトランジスタを例に詳細な説明を行っているが、Pチャネル型MOSトランジスタにおいてもその効果は変わることはない。また、相対的に薄いゲート絶縁膜を有するMOSトランジスタの構造は最も単純なMOSトランジスタの構造で表しているが、例えばLDD(Lightly Doped Drain)構造やLOCOSオフセット構造であったとしても同様の効果が得られる。

【符号の説明】

【0030】

11 P型半導体基板

21 窒化膜

22 パッド酸化膜

23 フィールド絶縁膜

24 第一のゲート絶縁膜

25 第二のゲート絶縁膜

31 反転防止拡散層

32 オフセット拡散層

33 高濃度拡散層

41 フォトレジスト

51 ゲート電極

52 半導体基板

【特許請求の範囲】

【請求項1】

相対的に厚いゲート絶縁膜を有するMOSトランジスタと相対的に薄いゲート絶縁膜を有するMOSトランジスタを同時に形成する半導体装置において、相対的に薄いゲート絶縁膜を有するMOSトランジスタ領域のフィールド絶縁膜端を相対的に厚いゲート絶縁膜で覆うことにより、相対的に薄いゲート絶縁膜を有するMOSトランジスタのチャネル領域がフィールド絶縁膜のバーズビーク領域からオフセットされていることを特徴とする半導体装置。

【請求項2】

前記相対的に厚いゲート酸化膜を有するMOSトランジスタは、ソースおよびドレインの高濃度拡散層がフィールド絶縁膜によってオフセットされている構造であることを特徴とする請求項1記載の半導体装置。

【請求項3】

相対的に厚いゲート絶縁膜を有するMOSトランジスタと相対的に薄いゲート絶縁膜を有するMOSトランジスタを同時に形成する半導体装置の製造方法において、

第1導電型の半導体基板上にパッド酸化膜を形成する工程と

前記パッド酸化膜上に窒化膜を形成する工程と、

前記窒化膜の所定の領域をエッチングする工程と、

前記エッチングにて形成された窒化膜の開口領域を通じて、後に第1導電型の反転防止拡散層および第2導電型のオフセット拡散層を形成するための不純物を前記半導体基板にイオン注入する工程と、

前記窒化膜がエッチングされた領域にフィールド絶縁膜を形成するとともに前記第1導電型の反転防止拡散層および前記第2導電型のオフセット拡散層を形成する工程と、

前記窒化膜および前記パッド酸化膜を除去する工程と、

前記半導体基板表面に相対的に厚いゲート絶縁膜を形成する工程と、

前記相対的に厚いゲート絶縁膜を所望の領域のみ除去する工程と、

前記相対的に薄いゲート絶縁膜を形成する工程と、

前記相対的に厚いゲート絶縁膜および前記相対的に薄いゲート絶縁膜上に多結晶シリコン膜を堆積する工程と、

前記多結晶シリコン膜に導電性を持たせる工程と、

前記多結晶シリコン膜をエッチングしてゲート電極を形成する工程と、

前記相対的に厚いゲート絶縁膜をマスクとして、第2導電型の高濃度拡散層となる領域に自己整合的に不純物をイオン注入する工程と、

を有することを特徴とする半導体装置の製造方法。

【請求項4】

前記相対的に厚いゲート絶縁膜を形成する工程は、前記相対的に薄いゲート絶縁膜を形成する工程よりも早く行われることを特徴とする請求項3記載の半導体装置の製造方法。

【請求項5】

前記相対的に厚いゲート絶縁膜を所望の領域のみ除去する工程において、前記相対的に薄いゲート絶縁膜を有するMOSトランジスタが形成される領域のフィールド絶縁膜端のバーズビーク部分は除去されないことを特徴とする請求項3または4記載の半導体装置の製造方法。

【請求項6】

前記相対的に厚いゲート絶縁膜を所望の領域のみ除去する工程において、前記相対的に厚いゲート絶縁膜を有するMOSトランジスタの高濃度拡散層となる領域の前記相対的に厚いゲート絶縁膜が除去されることを特徴とする請求項3乃至5のいずれか1項記載の半導体装置の製造方法。

【請求項7】

前記相対的に厚いゲート絶縁膜をマスクとして、第2導電型の高濃度拡散層となる領域に自己整合的に不純物をイオン注入する工程において、イオン注入を行うときの注入エネルギーは相対的に厚いゲート絶縁膜を突き抜けないエネルギーであることを特徴とする請求項3乃至6のいずれか1項記載の半導体装置の製造方法。

【請求項1】

相対的に厚いゲート絶縁膜を有するMOSトランジスタと相対的に薄いゲート絶縁膜を有するMOSトランジスタを同時に形成する半導体装置において、相対的に薄いゲート絶縁膜を有するMOSトランジスタ領域のフィールド絶縁膜端を相対的に厚いゲート絶縁膜で覆うことにより、相対的に薄いゲート絶縁膜を有するMOSトランジスタのチャネル領域がフィールド絶縁膜のバーズビーク領域からオフセットされていることを特徴とする半導体装置。

【請求項2】

前記相対的に厚いゲート酸化膜を有するMOSトランジスタは、ソースおよびドレインの高濃度拡散層がフィールド絶縁膜によってオフセットされている構造であることを特徴とする請求項1記載の半導体装置。

【請求項3】

相対的に厚いゲート絶縁膜を有するMOSトランジスタと相対的に薄いゲート絶縁膜を有するMOSトランジスタを同時に形成する半導体装置の製造方法において、

第1導電型の半導体基板上にパッド酸化膜を形成する工程と

前記パッド酸化膜上に窒化膜を形成する工程と、

前記窒化膜の所定の領域をエッチングする工程と、

前記エッチングにて形成された窒化膜の開口領域を通じて、後に第1導電型の反転防止拡散層および第2導電型のオフセット拡散層を形成するための不純物を前記半導体基板にイオン注入する工程と、

前記窒化膜がエッチングされた領域にフィールド絶縁膜を形成するとともに前記第1導電型の反転防止拡散層および前記第2導電型のオフセット拡散層を形成する工程と、

前記窒化膜および前記パッド酸化膜を除去する工程と、

前記半導体基板表面に相対的に厚いゲート絶縁膜を形成する工程と、

前記相対的に厚いゲート絶縁膜を所望の領域のみ除去する工程と、

前記相対的に薄いゲート絶縁膜を形成する工程と、

前記相対的に厚いゲート絶縁膜および前記相対的に薄いゲート絶縁膜上に多結晶シリコン膜を堆積する工程と、

前記多結晶シリコン膜に導電性を持たせる工程と、

前記多結晶シリコン膜をエッチングしてゲート電極を形成する工程と、

前記相対的に厚いゲート絶縁膜をマスクとして、第2導電型の高濃度拡散層となる領域に自己整合的に不純物をイオン注入する工程と、

を有することを特徴とする半導体装置の製造方法。

【請求項4】

前記相対的に厚いゲート絶縁膜を形成する工程は、前記相対的に薄いゲート絶縁膜を形成する工程よりも早く行われることを特徴とする請求項3記載の半導体装置の製造方法。

【請求項5】

前記相対的に厚いゲート絶縁膜を所望の領域のみ除去する工程において、前記相対的に薄いゲート絶縁膜を有するMOSトランジスタが形成される領域のフィールド絶縁膜端のバーズビーク部分は除去されないことを特徴とする請求項3または4記載の半導体装置の製造方法。

【請求項6】

前記相対的に厚いゲート絶縁膜を所望の領域のみ除去する工程において、前記相対的に厚いゲート絶縁膜を有するMOSトランジスタの高濃度拡散層となる領域の前記相対的に厚いゲート絶縁膜が除去されることを特徴とする請求項3乃至5のいずれか1項記載の半導体装置の製造方法。

【請求項7】

前記相対的に厚いゲート絶縁膜をマスクとして、第2導電型の高濃度拡散層となる領域に自己整合的に不純物をイオン注入する工程において、イオン注入を行うときの注入エネルギーは相対的に厚いゲート絶縁膜を突き抜けないエネルギーであることを特徴とする請求項3乃至6のいずれか1項記載の半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図2】

【図3】

【図4】

【公開番号】特開2011−71243(P2011−71243A)

【公開日】平成23年4月7日(2011.4.7)

【国際特許分類】

【出願番号】特願2009−219781(P2009−219781)

【出願日】平成21年9月24日(2009.9.24)

【出願人】(000002325)セイコーインスツル株式会社 (3,629)

【Fターム(参考)】

【公開日】平成23年4月7日(2011.4.7)

【国際特許分類】

【出願日】平成21年9月24日(2009.9.24)

【出願人】(000002325)セイコーインスツル株式会社 (3,629)

【Fターム(参考)】

[ Back to top ]