半導体装置およびその製造方法

【課題】ゲート電極同士の間の突合わせ部を挟むように形成されたコンタクトプラグ同士が、当該突合わせ部の絶縁膜内に形成されたボイドを介してショートすることを防ぐ。

【解決手段】ゲート電極G2およびG5間の突合わせ部において対向するサイドウォールSW上には、ライナー絶縁膜6と層間絶縁膜7が形成されている。サイドウォールSW同士の間において、サイドウォールSWの側壁にそれぞれ形成されたライナー絶縁膜6を接触させてサイドウォールSW間を閉塞させることにより、層間絶縁膜7とライナー絶縁膜6の内部にボイドが発生することを防ぐ。

【解決手段】ゲート電極G2およびG5間の突合わせ部において対向するサイドウォールSW上には、ライナー絶縁膜6と層間絶縁膜7が形成されている。サイドウォールSW同士の間において、サイドウォールSWの側壁にそれぞれ形成されたライナー絶縁膜6を接触させてサイドウォールSW間を閉塞させることにより、層間絶縁膜7とライナー絶縁膜6の内部にボイドが発生することを防ぐ。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置およびその製造方法に関し、特に、突合わせ部の間隔が狭いゲート電極を有する半導体素子の製造に適用して有効な技術に関する。

【背景技術】

【0002】

半導体装置の微細化が進むにつれて、例えばSRAM(Static Random Access Memory)を構成するゲートの延在方向と平行な方向、すなわちゲート突き合わせ方向(ゲート幅方向)のデザインを縮小する際に、SRAMを構成するゲート電極のパターニングを2回の露光および2回のエッチングにより行う方法がある。この方法は半導体装置の微細化のためにゲート端部を切り離すマスクを追加して加工する技術であり、一方向に断続的に複数並び、その方向に延在するゲート電極を有するMIS(Metal Insulator Semiconductor)型のFET(Field Effect Transistor:電界効果トランジスタ)などに利用される。本願では、このようにゲート電極同士の突合わせ部を加工するためにマスクを追加してパターニングする技術をエンドカットと呼ぶ。エンドカットを用いることにより、ゲートパターンをその延在方向に一列に複数並べる際に、各ゲート電極同士の突合わせ部の間隔を精度良く狭めてゲート電極を形成することができる。

【0003】

特許文献1(特開2009−252825号公報)には、狭いゲート電極間に形成する層間絶縁膜内にボイドが発生することを防ぎ、当該ゲート電極間の領域を挟んで配置された導電材料がボイドにより導通することを防ぐことが記載されている。ここでは、隣接するゲート電極間の一部領域のアスペクト比を低減させることが記載されている。なお、特許文献1に記載の技術はゲート電極の端部同士が対向して近接する突合わせ部に関するものではない。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2009−252825号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

エンドカットを用いて形成されるようなゲート電極を有する半導体装置において、ゲート電極のゲート長方向に隣り合うゲート電極同士の間では、上述した突合わせ部のゲート電極同士の間隔よりもゲート電極間の間隔が広いため、ゲート電極間に形成する層間絶縁膜の埋め込み性は問題とならない。これに対し、微細化された半導体装置であって、例えば32nmノード以降の半導体装置では、ゲート電極の延在方向に隣り合うゲート電極同士の間(突合わせ部)での層間絶縁膜の埋め込み性が問題となる虞がある。

【0006】

32nmノードまたは28nmノードなどの半導体装置の製造工程でエンドカットを行うと、ゲート電極の延在方向において隣り合うゲート電極同士の間(突合わせ部)の距離は30〜50nm程度となる。このような狭い間隔を有する複数のゲート電極上に層間絶縁膜を形成した場合、突合わせ部ではゲートパターン間の距離が狭いために埋め込み性が悪くなり、層間絶縁膜内にボイド(空隙)が形成される可能性がある。その後に、ボイドが形成された突合わせ部を挟むように層間絶縁膜にコンタクトホールを形成し、各コンタクトホール内にW(タングステン)などの導電部材を埋め込むことでコンタクトプラグを形成しようとすると、前記ボイドにも導電部材が充填され、前記ボイド内の導電部材を介して二つのコンタクトプラグがショート(短絡)を起こし、歩留まりが悪化し、あるいは、半導体装置の信頼性が低下する問題がある。

【0007】

本発明の目的は、製造工程における歩留まりを向上させること、あるいは、半導体装置の信頼性を向上させることにある。

【0008】

特に、本発明の目的は、ゲート電極間のボイドを介してコンタクトプラグ同士がショートすることを防ぐことにある。

【0009】

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

【課題を解決するための手段】

【0010】

本願において開示される実施の形態のうち、代表的なものの概要を簡単に説明すれば、次のとおりである。

【0011】

本発明の好ましい一実施の形態である半導体装置は、

半導体基板の主面に沿う第1方向に延在し、前記第1方向に並んで前記半導体基板上に形成された複数のゲート電極と、

前記第1方向に隣り合う前記複数のゲート電極同士の間に形成された第1絶縁膜と、

前記第1方向に直交する第2方向における前記複数のゲート電極の側方であって、前記ゲート電極から露出する前記半導体基板の上面に形成された第2絶縁膜と、

前記第1絶縁膜の両側に配置され、前記半導体基板に接続された複数のコンタクトプラグと、

を有し、

前記第1絶縁膜および前記第2絶縁膜は前記半導体基板および前記複数のゲート電極を覆うように形成された第3絶縁膜を構成し、

前記第1絶縁膜の上面の最も低い位置は、前記第2絶縁膜の上面の最も低い位置よりも高いものである。

【0012】

また、本発明の好ましい一実施の形態である半導体装置の製造方法は、

(a)半導体基板の主面に沿う第1方向に延在し、前記第1方向に並ぶ複数のゲート電極を前記半導体基板上にゲート絶縁膜を介して形成する工程、

(b)前記複数のゲート電極の両側の半導体基板の主面にソース・ドレイン領域を形成する工程、

(c)前記複数のゲート電極の側壁にサイドウォールを形成する工程、

(d)前記(b)工程および前記(c)工程の後に、前記半導体基板上に前記複数のゲート電極、前記ソース・ドレイン領域および前記サイドウォールを覆うように第2絶縁膜および第3絶縁膜を前記半導体基板側から順に形成する工程、

(e)前記第1方向に隣り合う前記複数のゲート電極同士の間の領域の両側に、前記第2絶縁膜および前記第3絶縁膜を貫通する複数の貫通孔を形成した後、前記ソース・ドレイン領域に接続されたコンタクトプラグを前記複数の貫通孔のそれぞれの内側に形成する工程、

を有し、

前記第1方向に隣り合う前記複数のゲート電極同士の間の前記第2絶縁膜の上面の最も低い位置は、前記第1方向に直交する第2方向において前記複数のゲート電極および前記サイドウォールから露出する前記半導体基板の上面に形成された前記第2絶縁膜の上面の最も低い位置よりも高いものである。

【発明の効果】

【0013】

本願において開示される発明のうち、代表的なものによって得られる効果を簡単に説明すれば以下のとおりである。

【0014】

半導体装置の製造工程における歩留まりを向上させることができ、または、半導体装置の信頼性を向上させることができる。

【0015】

ゲート電極間のボイドを介してコンタクトプラグ同士がショートすることを防ぐことができる。

【図面の簡単な説明】

【0016】

【図1】本発明の実施の形態1である半導体装置を示す平面レイアウトである。

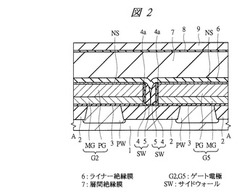

【図2】図1のA−A線における断面図である。

【図3】図1のB−B線における断面図である。

【図4】図1のC−C線における断面図である。

【図5】(a)は実施の形態1のSRAMの等価回路図である。(b)は実施の形態1の半導体装置の断面図である。

【図6】(a)は実施の形態1の半導体装置の製造工程を説明するための断面図である。(b)は実施の形態1の半導体装置の製造工程を説明するための断面図である。

【図7】(a)は図6(a)に続く半導体装置の製造工程中の断面図である。(b)は図6(b)に続く半導体装置の製造工程中の断面図である。

【図8】図7(a)および図7(b)に続く半導体装置の製造工程中の平面レイアウトである。

【図9】(a)は図7(a)に続く半導体装置の製造工程中の断面図である。(b)は図7(b)に続く半導体装置の製造工程中の断面図である。

【図10】図9(a)および図9(b)に続く半導体装置の製造工程中の平面レイアウトである。

【図11】(a)は図9(a)に続く半導体装置の製造工程中の断面図である。(b)は図9(b)に続く半導体装置の製造工程中の断面図である。

【図12】(a)は図11(a)に続く半導体装置の製造工程中の断面図である。(b)は図11(b)に続く半導体装置の製造工程中の断面図である。

【図13】(a)は図12(a)に続く半導体装置の製造工程中の断面図である。(b)は図12(b)に続く半導体装置の製造工程中の断面図である。。

【図14】(a)は図13(a)に続く半導体装置の製造工程中の断面図である。(b)は図13(b)に続く半導体装置の製造工程中の断面図である。

【図15】(a)は図14(a)に続く半導体装置の製造工程中の断面図である。(b)は図14(b)に続く半導体装置の製造工程中の断面図である。

【図16】(a)は図15(a)に続く半導体装置の製造工程中の断面図である。(b)は図15(b)に続く半導体装置の製造工程中の断面図である。

【図17】(a)は図16(a)に続く半導体装置の製造工程中の断面図である。(b)は図16(b)に続く半導体装置の製造工程中の断面図である。

【図18】(a)は実施の形態1の第1変形例を示す断面図である。(b)は実施の形態1の第1変形例を示す断面図である。

【図19】実施の形態1の第2変形例を示す断面図である。

【図20】実施の形態1の第3変形例を示す断面図である。

【図21】実施の形態1の第3変形例を示す断面図である。

【図22】本発明の実施の形態2である半導体装置を示す断面図である。

【図23】本発明の実施の形態2である半導体装置を示す断面図である。

【図24】比較例である半導体装置の平面レイアウトである。

【図25】比較例である半導体装置の断面図である。

【発明を実施するための形態】

【0017】

以下、本発明の実施の形態を図面に基づいて詳細に説明する。なお、実施の形態を説明するための全図において、同一の機能を有する部材には同一の符号を付し、その繰り返しの説明は省略する。また、以下の実施の形態では、特に必要なとき以外は同一または同様な部分の説明を原則として繰り返さない。

【0018】

(実施の形態1)

本実施の形態の半導体装置を、図1〜図5(a)を参照して説明する。図1は半導体基板上に形成された複数のMISFETにより構成されるSRAMを含む半導体装置の平面レイアウトである。図2は半導体基板1上に形成されたMISFETを構成するゲート電極を含む断面図であり、図1のA−A線におけるゲート電極同士の突合わせ部(ゲート端対向部)の断面を示している。図3は、図1のB−B線における断面図であり、ゲート電極間の突合わせ部と、ゲート電極上に形成されたコンタクトプラグとを示している。図4は図1のC−C線における断面図であり、図1に示すSRAMを構成するMISFETのゲート電極、ソース・ドレイン領域およびそれらの上部に形成されたコンタクトプラグの断面を示している。図1のA−A線およびB−B線はゲート電極の延在方向、すなわちゲート幅方向に沿う線であり、C−C線はA−A線およびB−B線に直交し、ゲート電極のゲート長方向に沿う線である。図5(a)は図1に示すSRAMの等価回路図である。

【0019】

SRAMは、フリップフロップ等の順序回路を用いてデータを記憶し、電力の供給がなくなると記憶内容が失われる揮発性メモリである。SRAMはDRAM(Dynamic Random Access Memory)と異なり、記憶部にフリップフロップ回路を用いているためリフレッシュ操作が不要であり、記憶保持状態での消費電力を小さくすることができる記憶回路である。SRAMは、そのメモリセルの構造として、4個のトランジスタと2個の高抵抗素子で構成される高抵抗負荷型と、6個のトランジスタで構成されるCMOS(Complementary MOS)型とがある。本実施の形態では、データ保持時のリーク電流が非常に小さいために信頼性が高く、現在の主流となっているCMOS型のSRAMを例として説明する。

【0020】

図1では、図を分かりやすくするために半導体基板の上面に形成されたソース・ドレイン領域および半導体基板上に形成されたゲート電極からなる複数のMISFETと、各ソース・ドレイン領域上およびゲート電極上に形成に形成されたコンタクトプラグと、半導体基板の上面に形成された素子分離領域とを示しており、他の配線または層間絶縁膜などは示していない。図1の破線で囲まれた領域は一つのSRAMを構成する6つのMISFETQ1〜Q6を含んでおり、半導体基板上にはこのように破線で囲まれて示される構造を一つのユニットとするSRAMが多数形成されている。

【0021】

MISFETQ1〜Q6を構成するゲート電極はいずれも半導体基板の主面に沿う第1方向に延在している。MISFETQ1およびMISFETQ3を構成するゲート電極G1はMISFETQ6を構成するゲート電極G3と第1方向に並んで形成されており、MISFETQ2およびMISFETQ4を構成するゲート電極G2はMISFETQ5を構成するゲート電極G4と第1方向に並んで形成されている。すなわち、ゲート電極G1の延在する延長線上にゲート電極G3が形成されており、ゲート電極G2の延在する延長線上にゲート電極G4が形成されている。

【0022】

ゲート電極G1およびG3の対向する端部は互いに近接しており、本願では、このように同一方向に延在し、当該方向に並んで隣り合うゲート電極同士の対向する端部の間の領域(ゲート端対向部)をゲート電極の突合わせ部と呼ぶ。なお、同様にゲート電極G2およびG4の対向する端部は互いに近接しており、ゲート電極G2およびG4の間にも突合わせ部が存在する。本実施の形態の第1方向の各ゲート電極同士の間の突合わせ部の間隔は例えば40nmとする。

【0023】

ゲート電極G1〜G4は同層に形成された電極であり、ゲート電極G2およびゲート電極G4は、ゲート電極G1の延在方向に直交し半導体基板の主面に沿う方向、すなわち第2方向に並んで配置されている。また、ゲート電極G3とゲート電極G2は第2方向に隣り合うように形成されている。なお、第1方向はゲート電極G1〜G4のゲート幅方向であり、第2方向はゲート電極G1〜G4のゲート長方向である。ゲート電極G1の第2方向の側方にはゲート電極G2、G4の突合わせ部が存在しており、ゲート電極G2の第2方向の側方にはゲート電極G1、G3の突合わせ部が存在している。

【0024】

また、ゲート電極G2を挟むようにして、ゲート電極G4の反対側にはゲート電極G5が形成されている。ゲート電極G5はゲート電極G2との間に突合わせ部を有し、他のSRAMに含まれるMISFETを構成している。さらに、ゲート電極G1の第2方向の側方であってゲート電極G2、G4が無い方にはゲート電極G6が形成されており、ゲート電極G6は他のSRAMに含まれるMISFETを構成している。

【0025】

MISFETQ1、Q3はゲート電極G1を有し、MISFETQ2、Q4はゲート電極G2を有し、MISFETQ5はゲート電極G4を有し、MISFETQ6はゲート電極G3を有している。ゲート電極G1とゲート電極G2との間の領域の半導体基板の主面にはp型の半導体領域であるソース領域S3が形成され、ゲート電極G1を挟むようにして、ソース領域S3の反対側の半導体基板の主面にはp型の半導体領域であるドレイン領域D3が形成されており、ソース領域S3、ドレイン領域D3およびゲート電極G1によりMISFETQ3が構成されている。また、ゲート電極G1とゲート電極G2との間の領域の半導体基板の主面にはp型の半導体領域であるソース領域S4が形成され、ゲート電極G2を挟むようにして、ソース領域S4の反対側の半導体基板の主面にはp型の半導体領域であるドレイン領域D4が形成されており、ソース領域S4、ドレイン領域D4およびゲート電極G2によりMISFETQ4が構成されている。つまり、MISFETQ3、Q4はpチャネル型の電界効果トランジスタである。

【0026】

ゲート電極G1とゲート電極G4との間の領域の半導体基板の主面にはn型の半導体領域であるドレイン領域D15が形成され、ゲート電極G1を挟むようにして、ドレイン領域D15の反対側の半導体基板の主面にはn型の半導体領域であるソース領域S1が形成されており、ドレイン領域D15、ソース領域S1およびゲート電極G1によりMISFETQ1が構成されている。さらに、ゲート電極G4を挟むようにして、ドレイン領域D15の反対側の半導体基板の主面にはn型の半導体領域であるソース領域S5が形成されており、ドレイン領域D15、ソース領域S5およびゲート電極G4によりMISFETQ5が構成されている。

【0027】

同様に、ゲート電極G2とゲート電極G3との間の領域の半導体基板の主面にはn型の半導体領域であるドレイン領域D26が形成され、ゲート電極G2を挟むようにして、ドレイン領域D26の反対側の半導体基板の主面にはn型の半導体領域であるソース領域S2が形成されており、ドレイン領域D26、ソース領域S2およびゲート電極G2によりMISFETQ2が構成されている。さらに、ゲート電極G3を挟むようにして、ドレイン領域D26の反対側の半導体基板の主面にはn型の半導体領域であるソース領域S6が形成されており、ドレイン領域D26、ソース領域S6およびゲート電極G3によりMISFETQ6が構成されている。

【0028】

つまり、MISFETQ1、Q2、Q5およびQ6はnチャネル型の電界効果トランジスタである。また、MISFETQ1およびMISFETQ5はドレイン領域D15を共有しており、MISFETQ2およびMISFETQ6はドレイン領域D26を共有している。

【0029】

第1方向において、ソース領域S3はソース領域S4とドレイン領域D15との間に配置されている。ゲート電極G2とゲート電極G4の突合わせ部の近傍のゲート電極G2の端部の上部およびソース領域S3上には半導体基板の主面に対して垂直に延在する柱状のコンタクトプラグP2が連続的に形成されており、コンタクトプラグP2はゲート電極G2およびソース領域S3のそれぞれに電気的に接続されているため、ゲート電極G2およびソース領域S3は電気的に接続されている(図4参照)。同様に、ゲート電極G3に近い方のゲート電極G1の端部の上部およびソース領域S4上にはコンタクトプラグP1が連続的に形成されており、コンタクトプラグP1によってゲート電極G1およびソース領域S4は電気的に接続されている。

【0030】

また、ソース領域S1、S2、S5、S6、ドレイン領域D15、D3、D26、D4、ゲート電極G3およびG4のそれぞれの上部にはそれぞれコンタクトプラグPLが形成されている。ソース領域S1上およびソース領域S2上のコンタクトプラグPLは上層の配線(図示しない)により電気的に接続され、同一の電位をソース領域S1およびソース領域S2に供給する。ドレイン領域D15上のコンタクトプラグPLとコンタクトプラグP2とは上層の配線(図示しない)により電気的に接続されており、同様に、ドレイン領域D26上のコンタクトプラグPLとコンタクトプラグP1とは上層の配線(図示しない)により電気的に接続されている。

【0031】

ここで、図1に示すゲート電極G1〜G4のパターンは、半導体基板上に形成した膜を1回の露光および1回のエッチングにより加工して形成したものではなく、少なくとも2回の露光および2回のエッチングにより形成しているものである。これはゲート電極の突合わせ部を精度良く微細加工する目的で用いられる加工方法であり、ゲート電極の第1方向に沿う側壁を形成するパターニングと第2方向に沿う側壁を形成するパターニングとの2回のパターニングに分けてゲート電極を加工することで、第1方向のゲート電極間の突合わせ部の間隔をより小さくすることを可能としている。本実施の形態ではこのようにゲート電極を形成する際に複数回のパターニングを行っている。本願では、前記複数回のパターニングのうちの、ゲート電極の突合わせ部を加工して形成する際のパターニング工程をエンドカットと呼ぶ。

【0032】

例えば、本実施の形態では、ゲート電極G1〜G4を形成する際、まず第1方向のゲート電極間の突合わせ部を形成するため、各ゲート電極の第2方向に沿う側壁を形成するパターニング(エンドカット)を行った後、各ゲート電極の第1方向に沿う側壁を形成するパターニングを行うことで、第2方向に並ぶゲート電極同士の間の半導体基板の主面を露出させるものとする。ただし、エンドカットを行う場合のパターニングの順序はこれに限られず、逆にゲート電極の第1方向に沿う側壁を形成するパターニングを行った後、各ゲート電極の第2方向に沿う側壁を形成するパターニング(エンドカット)を行っても構わない。

【0033】

次に、以上に説明したSRAMの構成を図5(a)を用いて説明する。図5(a)の等価回路図に示すように、本実施の形態のSRAMは6つのMISFETQ1〜Q6を有し、MISFETQ5、Q6のソース(図1に示すソース領域S5、S6)はビット線BL1およびBL2にそれぞれ接続されており、MISFETQ5、Q6のゲート電極(図1に示すゲート電極G3、G4)はワード線WLに接続されている。

【0034】

MISFETQ5のドレイン(図1に示すドレイン領域D15)は、第1ノードE1を介してMISFETQ1のドレイン(図1に示すドレイン領域D15)、MISFETQ3のソース(図1に示すソース領域S3)、MISFETQ2およびQ4のゲート(図1に示すゲート電極G2)に接続されている。同様に、MISFETQ6のドレイン(図1に示すドレイン領域D26)は、第2ノードE2を介してMISFETQ2のドレイン(図1に示すドレイン領域D26)、MISFETQ4のソース(図1に示すソース領域S4)、MISFETQ1およびQ3のゲート(図1に示すゲート電極G1)に接続されている。

【0035】

MISFETQ3、Q4のドレイン(図1に示すドレイン領域D3、D4)はいずれも電源電位線Vddに接続され、MISFETQ1、Q2のソース(図1に示すソース領域S1、S2)はいずれも設置電位線Vssに接続されている。MISFETQ5、Q6はいずれも転送用の電界効果トランジスタであり、MISFETQ1、Q2とMISFETQ3、Q4とはそれぞれnチャネル型のトランジスタとpチャネル型のトランジスタとを組み合わせたCMIS(Complementary MIS)インバータである。ここではデータの書込み・読出しのために、MISFETQ1、Q2のCMISとMISFETQ3、Q4のCMISとをたすき掛けするように接続されたフリップフロップ回路が構成されている。

【0036】

SRAMの動作方法について、以下に説明する。SRAMの書込み動作では、図5(a)に示すワード線WLの電圧を上げてMISFETQ5、Q6のゲートをオン状態にし、ビット線BL1の電圧を上げ、ビット線BL2の電圧を下げることにより、フリップフロップ回路の左側の第1ノードE1にはデータ「1」が記憶され、フリップフロップ回路の右側の第2ノードE2にはデータ「0」が記憶される。逆にビット線BL1の電圧を下げ、ビット線BL2の電圧を上げると、第1ノードE1にはデータ「0」が記憶され、第2ノードE2にはデータ「1」が記憶される。このとき、ワード線WLの電圧を下げて0Vにしても、書き込まれた「1」、「0」のデータは、装置の電源が入っている限り記憶され続ける。

【0037】

データの読出し動作時には、ワード線WLの電圧を上げてMISFETQ5、Q6のゲートをオン状態にし、そのときに記憶している状態(第1ノードE1および第2ノードE2の「1」、「0」の組み合わせ)によって、ビット線BL1およびBL2の間に電位差が生じるため、この電位差をセンスアンプにより増幅して検出する。

【0038】

図2に示すように、例えば単結晶シリコンからなる半導体基板1の主面にはp型の不純物(例えばB(ホウ素))が導入されたpウエルPWと素子分離領域2とが形成されており、半導体基板1の主面上には酸化シリコン膜からなるゲート絶縁膜3を介してゲート電極G2およびG5がそれぞれ形成されている。pウエルPWはゲート電極G2、G5の直下にそれぞれ形成され、ゲート電極G2およびG5の対向する端部同士の間の突合わせ部の直下の半導体基板1の主面には例えば酸化シリコン膜からなる素子分離領域2が形成されている。ゲート電極G2、G5はそれぞれゲート絶縁膜3上に半導体基板1側から順に積層されたTiN(窒化チタン)膜などからなるメタルゲート層MGおよびポリシリコン層PGを含み、ポリシリコン層PG上には例えばニッケル(Ni)などを含むシリサイド層NSが形成されている。

【0039】

ゲート電極G2、G5のそれぞれの側壁には酸化シリコン膜4および窒化シリコン膜5を半導体基板1側から順に積層した積層構造を有するサイドウォールSWが形成されており、ゲート電極G2、G5の間の領域である突合わせ部の殆どの領域はサイドウォールSWが占めている。ゲート電極G2、G5のそれぞれの側壁とサイドウォールSWとの間には、酸化シリコン膜からなるオフセットスペーサ4aが介在している。

【0040】

サイドウォールSWはゲート電極G2、G5の側壁に自己整合的に形成されており、サイドウォールSWのゲート電極に接していない方の側壁およびサイドウォールSWの上面は連続した曲面を有している。このため。ゲート電極G2の側壁のサイドウォールSWとゲート電極G5の側壁のサイドウォールSWとの間の距離は、半導体基板1の主面から高くなるにつれて間隔が開いており、それぞれのサイドウォールSW同士の間には、ゲート電極G2、G5を含む半導体基板の主面を覆うように形成されたライナー絶縁膜6が形成されている。すなわち、ライナー絶縁膜6とゲート電極G2、G5のそれぞれの側壁との間にはサイドウォールSWおよびオフセットスペーサ4aが形成されている。

【0041】

ライナー絶縁膜6は例えばSiN(窒化シリコン)膜からなる絶縁膜であり、図1に示すコンタクトプラグP1、P2およびPLなどを埋め込むコンタクトホールを形成する際のエッチングストッパ膜として機能する。ライナー絶縁膜6は、図2に示すように第1方向に隣り合うゲート電極同士の間に形成されており、また、図4に示すように、第2方向における各ゲート電極の側方であって、各ゲート電極およびその側壁に形成されたサイドウォールSWから露出する半導体基板1の上面にも形成されている。ここでは、ゲート電極G2、G5の突合わせ部の上部のライナー絶縁膜6の上面の最も低い位置は、ゲート電極G2、G5の上面の高さよりも高い領域に位置している。また、ライナー絶縁膜6上には層間絶縁膜7、ストッパ絶縁膜8、層間絶縁膜9が半導体基板1の主面側から順に形成されている。層間絶縁膜7、9は例えば酸化シリコン膜からなり、ストッパ絶縁膜8は例えば窒化シリコン膜からなる。ストッパ絶縁膜8は、層間絶縁膜9内に金属配線を埋め込む配線溝を形成する際にエッチングストッパ膜として機能する絶縁膜である。

【0042】

図3に示すように、ゲート電極G1、G3を含む断面は図2と似たような構造を有している。ただし、ゲート電極G1、G3の直上にはコンタクトプラグP1、PLがそれぞれ形成されており、コンタクトプラグP1の直下の半導体基板1の主面には素子分離領域2が形成されている。メタルゲート層MGおよびポリシリコン層PGからなるゲート電極G1、G3は、ポリシリコン層PG上に形成されたシリサイド層NSを介してコンタクトプラグP1、PLにそれぞれ電気的に接続されている。コンタクトプラグP1、PLは、それぞれの上部に形成された金属配線M1に電気的に接続されている。

【0043】

シリサイド層NSは、ゲート電極およびソース・ドレイン領域とコンタクトプラグとの間に介在することでゲート電極およびソース・ドレイン領域とコンタクトプラグとの接触抵抗を低減する働きを有する。シリサイド層NSは金属とシリコンとの反応層であり、その材料としては、例えばニッケルシリサイド、コバルトシリサイド、プラチナシリサイドまたはチタンシリサイドなどを用いることができる。

【0044】

コンタクトプラグP1、PLは、コンタクトホール7aの内壁および底部に形成されたバリア導体膜(図示しない)を介して形成された接続部材である。コンタクトプラグP1、PLは例えばタングステンなどからなり、その側壁および底部に形成されたバリア導体膜は、例えば窒化チタンなどからなる。

【0045】

金属配線M1は、SRAMを構成するMISFETに所定の電位を供給する配線であり、周知のダマシンプロセスによって形成されている。金属配線M1は、配線溝9aの内壁および底部に形成されたバリア導体膜と、前記バリア導体膜を介して配線溝9a内に充填された金属膜からなる。前記バリア導体膜は例えばTa(タンタル)とTaN(窒化タンタル)との積層膜からなり、前記金属膜は、主にCu(銅)からなる膜である。前記バリア導体膜は、前記金属膜内の金属元素が層間絶縁膜9内などに拡散することを防ぐ目的で設けられている。なお、バリア導体膜の部材としては、タンタルの他に、チタン(Ti)、ルテニウム(Ru)、マンガン(Mn)またはそれらの化合物などを用いてもよい。

【0046】

ここでも、図2で示した構造と同様にゲート電極G1、G3の突合わせ部にはサイドウォールSWがゲート電極G1、G3の対向する側壁にそれぞれ形成されており、互いのサイドウォールSWが殆ど接するように配置されている。このため、ゲート電極間の突合わせ部にライナー絶縁膜6が埋め込まれるスペースは少なく、突合わせ部の直上のライナー絶縁膜6の上面の最も低い位置は、ゲート電極G1、G3の上面よりも高い領域に位置しているので、突合わせ部上のライナー絶縁膜6の上面には大きな凹凸が形成されておらず、比較的平坦な形状となっている。

【0047】

図4に示すように、図1のC−C線における第2方向に沿った断面では、MISFETQ3を構成するゲート電極G1、ソース領域S3およびドレイン領域D3を含む断面が示されている。半導体基板1の主面には素子分離領域2およびn型の不純物(例えばP(リン))が導入されたn型の半導体領域であるnウエルNWが形成されている。半導体基板1上にはゲート絶縁膜3を介してゲート電極G2、G1およびG6が形成されており、各ゲート電極の両側の側壁にはオフセットスペーサ4aを介してサイドウォールSWが形成されている。ゲート電極G1の両側の半導体基板1の主面にはソース領域S3およびドレイン領域D3がゲート電極G1の直下のnウエルNWを挟むように形成されている。

【0048】

ソース領域S3およびドレイン領域D3は、p型の不純物(例えばB(ホウ素))が高濃度で導入された、接合深さが深い半導体領域である拡散層PSと、p型の不純物(例えばB(ホウ素))が拡散層PSよりも低い濃度で導入され、接合深さが拡散層PSよりも浅い半導体領域であるp−型半導体領域PEとを有している。p−型半導体領域PEはサイドウォールSWの下部のnウエルNW上に形成され、拡散層PSはゲート電極G1、G2、G6およびサイドウォールSWから露出しているnウエルNWの上面に自己整合的に形成されている。ゲート電極G2およびその側壁の一方のサイドウォールSWのそれぞれの直下には素子分離領域2が形成されており、半導体基板1の主面にはnウエルNWは形成されていない。

【0049】

拡散層PS、ゲート電極G1、G2およびG6のそれぞれの上面にはシリサイド層NSが形成されており、ドレイン領域D3を構成する拡散層PS上にはシリサイド層NSを介してコンタクトプラグPLが形成され、ソース領域S3を構成する拡散層PS上およびゲート電極G2上にはシリサイド層NSを介してコンタクトプラグP2が形成されている。コンタクトプラグP2はゲート電極G2の上面からソース領域S3を構成する拡散層PSの上面にかけて連続的に一体となって形成されており、また、ゲート電極G2の側壁であってゲート電極G1に近い方の側壁を覆うように形成されている。

【0050】

図3に示した構造と同様に、図4に示すコンタクトプラグP2、PLはゲート電極G1、G2およびサイドウォールSWを有する半導体基板1の主面上に順に形成されたライナー絶縁膜6および層間絶縁膜を貫くコンタクトホール7a内に形成されている。コンタクトプラグP2、PLのそれぞれの上部にはストッパ絶縁膜8および層間絶縁膜9が順に形成され、層間絶縁膜9およびストッパ絶縁膜8を貫く配線溝9a内には金属配線M1が複数形成されており、ドレイン領域D3はシリサイド層NSおよびコンタクトプラグPLを介して金属配線M1に電気的に接続されている。また、ゲート電極G2およびMISFETQ3のソース領域S3はシリサイド層NSおよびコンタクトプラグP2を介して電気的に接続されている。

【0051】

図4に示すゲート電極G1、G2は図2、図3に示すゲート電極と同様に、メタルゲート層MGと、その上部に形成されたポリシリコン層PGとにより構成されている。ただし、図2、図3とは異なり、図4にはゲート電極同士の間の突合わせ部は示されておらず、第2方向に隣り合うゲート電極G1、G2の間隔は図2、図3に示す突合わせ部よりも広く設けられている。これは、ゲート電極同士の間にソース・ドレイン領域およびコンタクトプラグを形成するためである。したがって、第1方向のゲート電極間の突合わせ部とは異なり、第2方向に隣り合うゲート電極の間ではサイドウォールSW同士の間隔が突合わせ部よりも広く、ライナー絶縁膜6が半導体基板の主面にゲート電極またはサイドウォールSWを介さず広く形成される。ここで、図2に示す第1方向に隣り合うゲート電極間の突合わせ部のライナー絶縁膜6の最も低い上面の高さは、図4に示す第2方向に隣り合うゲート電極間のライナー絶縁膜6の最も低い上面の高さよりも高い領域に位置している。

【0052】

次に、本実施の形態の半導体装置の効果について説明する。図1に示すSRAMのように、第1方向に複数のゲート電極が並んで配置される半導体装置では、装置の微細化に伴い、ゲート電極同士の突合わせ部が30〜50nm程度の狭い間隔で形成されることにより、ゲート電極間の突合わせ部の絶縁膜の埋め込み性が悪くなる問題がある。ここでいう突合わせ部の絶縁膜とは、例えば図2および図3に示すライナー絶縁膜6のことである。ゲート電極のパターン同士の間隔が狭い突合わせ部では、ライナー絶縁膜6をゲート電極同士の間の深い溝に密に埋め込むことが困難であるため、突合わせ部のライナー膜内にはボイド(空隙)が発生しやすくなる。

【0053】

ここで、上記ボイドが発生した場合に特に問題が起こりやすい構成を説明するために、図24に比較例である半導体装置のゲート電極およびソース・ドレイン領域を示した平面レイアウト図を示す。図24には、半導体基板(図示しない)上に形成され、半導体基板の主面に沿う第1方向に延在する複数のゲート電極GNと、第1方向に直交する第2方向においてゲート電極GNを挟むように半導体基板の主面に形成された二つのソース・ドレイン領域SDと、各ソース・ドレイン領域SD上にそれぞれ形成されたコンタクトプラグPLを示している。図1に示す本実施の形態の半導体装置と同様に、ゲート電極GNはそれぞれの延在する方向である第1方向に並んで複数配置されており、隣り合うゲート電極GNの対向する端部間(突き合せ部)の間隔は40nm程度の狭い間隔となっている。ここでは、ゲート電極の突合わせ部の形成の際にはエンドカットを用いている。

【0054】

図24において、ソース・ドレイン領域SDは第1方向に延在するゲート電極GNに沿うように第1方向に延在して形成されている。ゲート電極GNは第1方向に延在するパターンが途中で途切れるようにして断続的に形成されているのに対し、ソース・ドレイン領域SDは、ゲート電極GNが途切れている突合わせ部の近傍においても途切れておらず、図24に示す領域では複数のゲート電極GNおよびそれらの間の突合わせ部に沿って連続的に形成されている。

【0055】

すなわち、ソース・ドレイン領域SDは、ゲート電極GNの突合わせ部を第2方向において挟むように半導体基板の主面に形成されている。また、各ソース・ドレイン領域SD上には、突合わせ部を挟むようにコンタクトプラグPLが形成されており、ここでは一方のコンタクトプラグPL、突合わせ部およびもう一方のコンタクトプラグPLが第2方向に並んで配置されている。つまり、ゲート電極GNを挟むように配置されたソース・ドレイン領域SDのそれぞれの上のコンタクトプラグPL同士の間には、ゲート電極GNが形成されていない領域がある。図示はしていないが、前記半導体基板の主面上には、ソース・ドレイン領域SD、ゲート電極GNを覆うように絶縁膜が形成されている。前記絶縁膜はコンタクトプラグPL同士の間の領域であるゲート電極の突合わせ部にも形成され、コンタクトプラグPLは前記絶縁膜を貫通してソース・ドレイン領域SDに接続されている。

【0056】

また、図25に他の比較例である半導体装置の断面図を示す。図25は半導体基板1の主面に沿う第1方向に延在する二つのゲート電極GM同士の対向する端部の間の領域を含む、第1方向に沿う断面図である。図25に示す比較例の半導体装置のゲート電極GMはエンドカットを用い、2回のエッチング工程によりパターニングされており、第1方向に隣り合うゲート電極GM同士の間の距離は例えば40nmであるものとする。

【0057】

図2に示す本実施の形態の半導体装置と同様に、図25に示すゲート電極GMおよびその側壁のサイドウォールSWは積層構造を有している。また、図24に示す平面レイアウトと同様に、図25に示すゲート電極GM同士の間の突合わせ部の側方であって、第1方向に直交する第2方向には突合わせ部を挟むようにコンタクトプラグ(図示しない)が形成されている。なお、図24を用いて説明した絶縁膜は、図25に示すライナー絶縁膜6aに対応している。

【0058】

図25に示すように、ゲート電極GMの側壁のサイドウォールSW同士の間の距離が離れているために、ゲート電極GMの突合わせ部には半導体基板1の上面を露出する溝が形成されており、ライナー絶縁膜6aの上面は突合わせ部において大きく凹んだ形状を有している。具体的には、ライナー絶縁膜6aの上面は突合わせ部においてゲート電極GMの上面よりも低い領域であって、半導体基板1の上面に近い領域に位置している。なお、半導体基板1の主面がゲート電極GMの突合わせ部において一部凹んでいるのは、サイドウォールSWを形成するエッチング工程などにより半導体基板1の上面が一部除去されるためである。したがって、突合わせ部に限らず、ゲート電極GMの第2方向の側方の半導体基板1の上面も一部凹んでいることが考えられる。

【0059】

これは、ゲート電極GMの突合わせ部において、対向するサイドウォールSWの上面から側壁にかけて形成されたそれぞれのライナー絶縁膜6a同士が接触しておらず、ライナー絶縁膜6aが突合わせ部において閉塞していないためである。すなわち、突合わせ部においては、いずれの領域においても、対向するサイドウォールSW同士間の幅の値が、サイドウォールSWの側壁に形成されるライナー絶縁膜6aの第1方向の膜厚の値の2倍より大きくなっている。

【0060】

なお、ライナー絶縁膜6aの膜厚は、ゲート電極の上面上では20nm程度であり、突合わせ部のサイドウォールSWから露出している半導体基板1の主面では10〜15nm程度である。サイドウォールSWの表面に形成されたライナー絶縁膜6aの膜厚は、サイドウォールSWの表面の上部から下部にかけて徐々に薄くなるが、例えば最も薄い箇所では、サイドウォールSWの表面に垂直な方向のライナー絶縁膜6aの膜厚は10nm程度となる。なお、ここでいう膜厚とは、ライナー絶縁膜6aの下面に接する下地表面に対して垂直な方向のライナー絶縁膜6aの下面から上面までの距離のことである。

【0061】

半導体基板1上にライナー絶縁膜6aをCVD(Chemical Vapor Deposition)法などを用いて形成する場合、ゲート電極GMなどのパターンの側壁に形成されるライナー絶縁膜6aの膜厚は、突合わせ部よりも広い面積が露出している半導体基板1の主面上またはゲート電極GM上などのように半導体基板1の主面と平行な面に形成されるライナー絶縁膜6aの膜厚に比べて薄くなる。これは、パターンの側壁に形成される絶縁膜のカバレッジ(被膜率)がゲート電極GMの上面のような面に形成される絶縁膜よりも悪くなる性質があるためであり、ゲート電極GMの側壁にサイドウォールSWを介してライナー絶縁膜6aが形成される場合も同様である。

【0062】

ライナー絶縁膜のカバレッジが例えば100%の場合には、ゲート電極の上面に形成されたライナー絶縁膜の膜厚と、ゲート電極の側壁に形成されたライナー絶縁膜の膜厚とはいずれの領域においても同一になる。しかし、カバレッジは特に狭い溝の内壁において悪化する傾向があり、カバレッジが悪いとゲート電極の側壁のライナー絶縁膜は前記側壁の上部から下部に近付くにつれて膜厚が薄くなる。

【0063】

ライナー絶縁膜6aが形成されるゲート電極GM間の突合わせ部が30〜50nm程度の狭い間隔であり、対向するサイドウォールSW間の間隔が狭く、サイドウォールSW間において露出する半導体基板1の上面が小さい場合には、突合わせ部においてサイドウォールSWから露出する半導体基板1上のライナー絶縁膜6aの膜厚も、ゲート電極GM上のライナー絶縁膜6aの膜厚に比べて薄くなることが考えられる。

【0064】

すなわち、図25に示すように、ゲート電極GMの突合わせ部においてゲート電極GMの上面から半導体基板1の上面に対して深い溝が形成されていると、対向するサイドウォールSW間のライナー絶縁膜6aのカバレッジが悪くなり、ライナー絶縁膜6a内に上述したボイドが形成されやすくなる。なお、図25にはボイドは示していない。

【0065】

このような比較例の半導体装置では、図25に示す第1方向に隣り合うゲート電極GM間のライナー絶縁膜6aの上面の最も低い位置に対し、ゲート電極GMの第2方向の側方のゲート電極GMおよびその側壁のサイドウォールSWから露出する半導体基板1の上面に形成されたライナー絶縁膜6aの上面の最も低い位置の方が高い領域に形成されていることが考えられる。これは、ゲート電極GM同士の突合わせ部のような狭い溝の底部においてはライナー絶縁膜6aのカバレッジが低下し、前述したゲート電極GMの第2方向の側方の半導体基板1の上面のライナー絶縁膜6aのように広い領域に形成された膜よりも膜厚が薄くなるためである。

【0066】

図24および図25に示すような構成の半導体装置において、前述したようにゲート電極GN間の突合わせ部に形成される絶縁膜(例えば図25に示すライナー絶縁膜6a)内にボイドが形成された場合、突合わせ部を挟んで近接しているコンタクトプラグPL同士が、前記ボイド内に形成された金属部材によりショート(短絡)し、半導体装置が正常に動作しなくなる問題がある。ショート不良が発生すると、半導体装置の信頼性が低下し、また、歩留まりが悪化することとなる。これは、突合わせ部にボイドを有する絶縁膜(例えばライナー絶縁膜)を形成した後に、前記絶縁膜と前記絶縁膜上に形成した層間絶縁膜とを貫通する二つのコンタクトホールを突合わせ部を挟むように形成し、続いて各コンタクトホール内にコンタクトプラグPLを構成する金属材料を充填する際、前記ボイド内にも当該金属材料が充填され、二つのコンタクトプラグPLがボイドにより接続されてしまうことに起因する。

【0067】

つまり、突合わせ部に形成された絶縁膜がボイドを有する場合、突合わせ部の近傍であって、第1方向に隣り合うゲート電極およびそれらの間の突合わせ部の第2方向の両側の側方にコンタクトプラグをそれぞれ形成すると、それぞれのコンタクトプラグ同士がボイド内に形成された金属部材を介してショートする虞がある。

【0068】

このような問題は、図24に示すように、突合わせ部を挟むようにしてコンタクトプラグPL同士が特に近接する構造において起こりやすくなる。ただし、図1に示すような構造においても、例えばコンタクトプラグP2とソース領域S5上のコンタクトプラグPLとの間で、ゲート電極G2およびゲート電極G4の間の突合わせ部に形成された絶縁膜内のボイドを介してショートが発生する虞がある。言い換えれば、突合わせ部の近傍であって、突合わせ部に形成されたライナー絶縁膜6の両側にソース・ドレイン領域に接続されたコンタクトプラグが形成されている場合、当該ライナー絶縁膜6内にボイドが形成されていると、コンタクトプラグ間でショート不良が発生する。

【0069】

なお、本実施の形態の半導体装置では図1に示すように、ゲート電極が第2方向に並んで配置されているが、第2方向に並ぶゲート電極間の間隔は第1方向のゲート電極間の突合わせ部よりも広く設けられており、ライナー絶縁膜6(図4参照)の埋め込み性は突合わせ部よりも良好になるため、ゲート電極間にボイドは発生しない。これは、ボイドの発生の問題が、突合わせ部の間隔が30〜50nm程度の狭い距離で設けられている場合に顕著になるためである。したがって、図24、図25を用いて説明した比較例および図1に示す本実施の形態のように、突合わせ部を精度良く微細加工する目的でエンドカットを用いてゲート電極を形成している場合、ゲート電極同士の間隔を狭く形成することが可能であるので、上述したボイドの発生に起因するコンタクトプラグ間のショート不良がより発生しやすくなる。

【0070】

また、図1に示すSRAMのように、例えばエンドカットを用いて第1方向のゲート電極間の間隔を小さく形成した半導体装置では、半導体基板上のいずれかの領域に、図24に示すようにゲート電極の突合わせ部を挟むようにコンタクトプラグを配置するレイアウトを形成する可能性がある。これに対し、上記ショート不良の発生を防ぐために、図24に示すようにゲート電極の突合わせ部を挟むようにコンタクトプラグを配置するレイアウトを形成しないようにすると、半導体素子のレイアウトの自由度が低下するため、半導体装置の面積が増大するなどの問題が生じる。

【0071】

また、上記ショート不良の発生を防ぐために突合わせ部の間隔を図1に示す第2方向に隣り合うゲート電極同士の間隔のように広く設ける方法が考えられるが、この場合、ゲート電極の突合わせ部の間隔を縮小することができないため、半導体装置の微細化が困難となる。

【0072】

上述した絶縁膜内のボイドは、ゲート端同士の間隔が30〜50nm程度で狭く形成されている領域であって、特に、ゲート電極の上面から半導体基板の主面までの高さ、すなわち突合わせ部の溝の深さが大きいほど形成されやすくなる。つまり、ライナー絶縁膜6により深い溝を埋め込む場合に、ボイドが発生しやすくなる。これに対し、本実施の形態では、図2に示すように、第1方向に隣り合うゲート電極同士の間の突合わせ部のサイドウォールSW同士が殆ど接するように対向するサイドウォールSW同士を近接させて形成し、突合わせ部に形成されるライナー絶縁膜6が埋め込まれる溝を小さくすることで、ライナー絶縁膜6のカバレッジが悪くなることを防ぎ、ライナー絶縁膜6内にボイドが形成されることを抑制することを可能としている。なお、突合わせ部において対向するサイドウォールSWは側面の一部が接触して一体となっていても良い。

【0073】

例えば、図2に示す半導体装置ではライナー絶縁膜6は突合わせ部においてその上面に大きな凹みが形成されることがなく、図25に示すライナー絶縁膜6aに比べて平坦に形成されているため、ライナー絶縁膜6の最も低い上面の高さはゲート電極G2およびG5のそれぞれの上面の高さよりも高くなっている。すなわち、図2に示す第1方向に隣り合うゲート電極間の突合わせ部のライナー絶縁膜6の最も低い上面の高さは、図4に示す第2方向に隣り合うゲート電極間のライナー絶縁膜6の最も低い上面の高さよりも高い領域に位置している。言い換えれば、半導体基板上に形成された、同一方向(第1方向)に延在する複数のゲート電極および前記複数のゲート電極を有する半導体装置において、ゲート幅方向(第1方向)に並ぶゲート電極間の絶縁膜の上面の一番低い位置は、ゲート長方向(第2方向)のゲート電極間の絶縁膜の上面の一番低い位置よりも高い領域に位置している。

【0074】

これは、突合わせ部において対向するサイドウォールSWが接近することで、サイドウォールSWの上面から側壁にかけて形成されたライナー絶縁膜6同士が対向するサイドウォールSW同士の間で接触し、閉塞するためである。つまり、突合わせ部には、対向するサイドウォールSW同士間の幅の値が、サイドウォールSWの側壁に形成されるライナー絶縁膜6の第1方向の膜厚の値の2倍以下となっている領域がある。これにより、図24および図25を用いて説明した比較例に比べ、突合わせ部上のライナー絶縁膜6の平坦性を向上させ、ライナー絶縁膜6のカバレッジの悪化を抑制することで、ライナー絶縁膜6内にボイドが発生することを防いでいる。

【0075】

上記の構成を式で表わした場合、以下の式のようになる。

【0076】

S1≦2×(a+αt) (1)

ここで、図5(b)に示すように、S1は第1方向に隣り合うゲート電極GL同士の間の距離である。ただし、ゲート電極GLの側壁にオフセットスペーサ4aが形成されている場合は、S1は対向するオフセットスペーサ4a同士の間の距離とする。aはサイドウォールSWの上端の幅である。サイドウォールSWの上端において、窒化シリコン膜5は殆ど除去されているため、式(1)に示すaは酸化シリコン膜4の第1方向の膜厚であるものとして考えることができる。αはゲート電極GLの上面の第1方向の端部のライナー絶縁膜6のカバレッジ(%)であり、tはライナー絶縁膜6の膜厚設定である。αtはサイドウォールSWの側壁のライナー絶縁膜6の膜厚の値である。なお、図5(b)は式(1)を説明するための本実施の形態の半導体装置の断面図である。図5(b)に示す半導体装置は図2に示す半導体装置と同様の構造を有しているが、図5(b)ではライナー絶縁膜6より上に形成された構造は示していない。

【0077】

本実施の形態では、上記の式(1)が成り立つように構造パラメータ設計をすることにより、突合わせ部においてライナー絶縁膜6を閉塞させ、ライナー絶縁膜6が突合わせ部の深い溝の下部に形成されることを防いでいる。上記ボイドは、ライナー絶縁膜6が深い溝の下部に形成された場合に発生しやすいため、ライナー絶縁膜6が突合わせ部の下部に形成されることを抑制することで、ライナー絶縁膜6により深い溝を埋める必要をなくし、ボイドが発生することを防ぐことができる。

【0078】

したがって、本実施の形態の半導体装置では、突合わせ部の絶縁膜内にボイドが形成されることを防ぎ、半導体基板の主面に沿う方向に延在する複数のゲート電極GLおよびゲート電極GL間の突合わせ部の両側に形成された複数のコンタクトプラグが、ボイド内に形成された金属部材を介してショートすることを防ぐことができる。これにより、例えばSRAMなどの半導体素子が正常に動作しなくなることを防ぎ、半導体装置の信頼性を向上することができる。

【0079】

なお、式(1)が成り立つ条件で形成したライナー絶縁膜6は、対向するサイドウォールSWの側壁の下部ではなく、突合わせ部の対向するゲート電極GLの側壁の上端の近傍、すなわちゲート電極GLの上面よりも高い位置で閉塞する。この場合、ライナー絶縁膜6が突合わせ部内であってゲート電極GLの上面よりも低い位置で閉塞する場合、すなわち突合わせ部のライナー絶縁膜6の上面の最も低い位置がゲート電極GLの上面よりも低い領域に位置している場合に比べてライナー絶縁膜6が突合わせ部においてより平坦に形成され、その内部にボイドが形成されにくくなる。

【0080】

また、図25を用いて説明したように、サイドウォールSWを形成するエッチング工程によって半導体基板1の上面が一部除去され、凹んだような形状になっているとしても、本実施の形態の半導体装置では、図2に示す第1方向に隣り合うゲート電極間の突合わせ部のライナー絶縁膜6の最も低い上面の高さは、図4に示す第2方向に隣り合うゲート電極間のライナー絶縁膜6の最も低い上面の高さよりも高い領域に位置している。

【0081】

次に、本実施の形態の半導体装置の製造工程を図面を参照して説明する。図6、図7、図9および図11〜図17は、本発明の一実施の形態である半導体装置、例えばSRAMを有する半導体装置の製造工程中の断面図である。図6(a)、図7(a)、図9(a)、図11(a)、図12(a)、図13(a)、図14(a)、図15(a)、図16(a)および図17(a)は図2と同じ断面における断面図である。また、図6(b)、図7(b)、図9(b)、図11(b)、図12(b)、図13(b)、図14(b)、図15(b)、図16(b)および図17(b)は図4と同じ断面における断面図である。図8および図10は、本発明の一実施の形態である半導体装置、例えばSRAMを有する半導体装置の製造工程中の平面レイアウトである。

【0082】

まず、図6(a)および図6(b)に示すように、例えば1〜10Ωcm程度の比抵抗を有するp型の単結晶シリコンなどからなる半導体基板(半導体ウエハ)1を準備する。次に、この半導体基板1を熱酸化してその表面に例えば厚さ11nm程度の第1絶縁膜を形成した後、その上層にCVD法などにより、例えば厚さ90nm程度の第2絶縁膜を堆積する。第1絶縁膜は酸化シリコンなどからなり、第2絶縁膜は窒化シリコン膜などからなる。それから、フォトレジストパターン(図示しない)をエッチングマスクとして第2絶縁膜、第1絶縁膜および半導体基板1を順次ドライエッチングすることにより、素子分離形成予定領域の半導体基板1に、例えば深さ300nm程度の溝(素子分離用の溝)2aを形成する。溝2aは、素子分離用の溝であり、すなわち後述する素子分離領域2形成用の溝である。

【0083】

続いて、溝2aの内部(側壁および底部)を含む半導体基板1の主面上に、例えば厚み10nm程度の第3絶縁膜を形成する。それから、半導体基板1の主面上(すなわち第3絶縁膜上)に、溝2a内を埋めるように、第4絶縁膜をCVD法などにより形成(堆積)する。

【0084】

第3絶縁膜は、酸化シリコン膜または酸窒化シリコン膜からなる。第3絶縁膜が酸窒化シリコン膜の場合には、第3絶縁膜形成工程以降の熱処理によって溝2aの側壁が酸化することによる体積膨張を防止でき、半導体基板1に働く圧縮応力を低減できる効果がある。

【0085】

第4絶縁膜は、HDP−CVD(High Density Plasma CVD:高密度プラズマCVD)法により成膜された酸化シリコン膜、またはO3−TEOS酸化膜などである。なお、O3−TEOS酸化膜とは、O3(オゾン)およびTEOS(Tetraethoxysilane:テトラエトキシシラン、Tetra Ethyl Ortho Silicateともいう)を原料ガス(ソースガス)として用いて熱CVD法により形成した酸化シリコン膜である。

【0086】

それから、半導体基板1を例えば1150℃程度で熱処理することにより、溝2aに埋め込んだ第4絶縁膜を焼き締めた後、第4絶縁膜をCMP(Chemical Mechanical Polishing:化学的機械的研磨)法により研磨して第2絶縁膜を露出させ、熱リン酸などを用いたウェットエッチングにより第2絶縁膜を除去した後、HFなどにより溝2aの外部の第4絶縁膜および第1絶縁膜を除去し、溝2aの内部に第3絶縁膜、第4絶縁膜を残すことにより、素子分離領域(素子分離)2を形成する。

【0087】

このようにして、溝2a内に埋め込まれた第3絶縁膜、第4絶縁膜からなる素子分離領域2が形成される。本実施の形態では、素子分離領域2は、LOCOS(Local Oxidization of Silicon)法ではなく、好ましくはSTI(Shallow Trench Isolation)法により形成される。すなわち、本実施の形態の素子分離領域2は、好ましくは、半導体基板1に形成された素子分離用の溝2a内に埋め込まれた絶縁体(ここでは第3絶縁膜、第4絶縁膜)からなる。後述するnチャネル型MISFET(すなわちnチャネル型MISFETを構成するゲート絶縁膜、ゲート電極およびソース・ドレイン用のn−型半導体領域およびn+型半導体領域)およびpチャネル型MISFET(すなわちpチャネル型MISFETを構成するゲート絶縁膜、ゲート電極およびソース・ドレイン用のp−型半導体領域およびp+型半導体領域)は、素子分離領域2で規定された(囲まれた)活性領域に形成される。

【0088】

続いて、半導体基板1の主面から所定の深さに渡ってpウエルPW(図6(a)参照)およびnウエルNW(図6(b)参照)を形成する。pウエルPWは、pチャネル型MISFET形成予定領域を覆うフォトレジスト膜(図示しない)をイオン注入阻止マスクとして、nチャネル型MISFET形成予定領域の半導体基板1に例えばホウ素(B)などのp型の不純物をイオン注入することなどによって形成することができるp型半導体領域である。また、nウエルNWは、nチャネル型MISFET形成予定領域を覆う他のフォトレジスト膜(図示しない)をイオン注入阻止マスクとして、pチャネル型MISFET形成予定領域の半導体基板1に例えばリン(P)またはヒ素(As)などのn型の不純物をイオン注入することなどによって形成することができるn型半導体領域である。pウエルPWおよびnウエルNWは同時に形成することが出来ないので順に形成するが、どちらを先に形成しても構わない。

【0089】

次に、図7(a)および図7(b)に示すように、例えばフッ酸(HF)水溶液を用いたウェットエッチングなどにより半導体基板1の表面を清浄化(洗浄)した後、半導体基板1の表面(すなわちpウエルPWおよびnウエルNWの表面)上にゲート絶縁膜3を形成する。ゲート絶縁膜3は、例えば薄い酸化シリコン膜などからなり、例えば熱酸化法などによって形成することができる。

【0090】

続いて、半導体基板1上(すなわちpウエルPWおよびnウエルNWのゲート絶縁膜3上)に、ゲート電極形成用の導体膜として、金属層MGaおよびポリシリコン層PGaを半導体基板1側から順に積層する。金属層MGaはTiN(窒化チタン)膜などからなり、例えばスパッタリングなどにより半導体基板1上に形成される。ポリシリコン層PGaは、成膜時にはアモルファスシリコン膜であったものを、成膜後(イオン注入後)の熱処理により多結晶シリコン膜に変えることもできる。

【0091】

次に、図8、図9(a)および図9(b)に示すように、金属層MGa、ポリシリコン層PGaおよびゲート絶縁膜3をフォトリソグラフィ法およびドライエッチング法を用いてパターニングすることにより、素子分離領域2を有する半導体基板1の主面を一部露出させる。図8は、半導体装置の製造工程を説明するための平面レイアウトである。図9(a)は図8のA−A線における断面図であり、図9(b)は図8のC−C線における断面図である。

【0092】

このパターニングは半導体基板の主面に沿う第1方向に延在するゲート電極を形成するための工程であるが、ここでは図8に示すように、後の工程で形成するゲート電極の一部の側壁のみを形成するものである。すなわち、後の工程で形成されるゲート電極は、平面視において第1方向に延在する側壁と第2方向に沿う側壁からなる矩形の形状を有するものであり、このパターニングでは第2方向に沿う側壁のみを形成する。これにより、半導体基板上に形成されたポリシリコン層PGaから素子分離領域2の上面が複数の箇所において露出する。

【0093】

ゲート電極は第1方向に並んで複数形成されるので、ゲート電極同士の突合わせ部を示す断面図である図9(a)では金属層MGa、ポリシリコン層PGaおよびゲート絶縁膜3が一部除去されるが、ゲート電極が形成される領域であって第2方向に沿う断面図である図9(b)では金属層MGa、ポリシリコン層PGaおよびゲート絶縁膜3は除去されない。

【0094】

次に、図10、図11(a)および図11(b)に示すように、金属層MGa、ポリシリコン層PGaおよびゲート絶縁膜3をフォトリソグラフィ法およびドライエッチング法を用いてパターニングすることにより、金属層MGaおよびポリシリコン層PGaからなるゲート電極G1〜G6を形成する。ここでは、各ゲート電極の第1方向に沿う側壁を形成するようにパターニングを行う。この工程で形成された各ゲート電極の第1方向に沿う側壁と、図8、図9(a)および図9(b)を用いて説明したパターニング工程により予め形成された各ゲート電極の側壁とにより、第1方向に延在する矩形のゲート電極が第1方向に並んで複数形成される。また、このように第1方向に断続的に形成された複数のゲート電極からなる構成は、第1方向に直交する第2方向に並んで複数形成される。図10には、この工程により形成されたゲート電極G1〜G6および半導体基板の上面に形成され、ゲート電極G1〜G6から露出した素子分離領域2、pウエルPWおよびnウエルNWが示されている。

【0095】

このとき、ゲート電極G2およびG5の突合わせ部を示し第1方向に沿う断面図である図11(a)では金属層MGa、ポリシリコン層PGaおよびゲート絶縁膜3は加工されないが、第2方向に層断面図である図11(b)には、第2方向に並んで形成されたゲート電極G2、G1およびG6が示されている。

【0096】

1回のパターニングによりゲート電極を形成する方法も考えられるが、上述したように、本実施の形態では図8、図9(a)および図9(b)を用いて説明したパターニング工程と、図10、図11(a)および図11(b)を用いて説明したパターニング工程との2回のパターニングを用いている。図8、図9(a)および図9(b)を用いて説明したパターニング工程は第1方向に延在し、第1方向に並んで複数形成されるゲート電極同士の間の突合わせ部を形成するための、エンドカットと呼ばれる工程である。ゲート電極の形成を1回のパターニングで一括で行う場合に比べ、エンドカット工程を設けて各ゲート電極の突合わせ部を形成した場合の方が、突合わせ部の金属層MGa、ポリシリコン層PGaおよびゲート絶縁膜3の除去を精度良く行うことができる。つまり、ゲート電極の形成の際のパターニング工程を複数回に分けてエンドカットを行うことにより、より突合わせ部の間隔が狭いゲート電極を形成することができるため、半導体装置の微細化が容易となる。

【0097】

なお、本実施の形態では、エンドカット工程を含むゲート電極のパターニングでは、エンドカットを先に行った後にパターニングを行うことでゲート電極G1〜G6を形成しているが、これに限られず、先にゲート電極の第1方向に沿う側面を形成し、その後にエンドカットを行ってゲート電極G1〜G6を形成しても良い。この場合、まず第1方向に延在する長いパターンを形成した後に、当該パターンを複数のパターンに分離することでゲート電極G1〜G6を形成することになる。このとき、第1方向に隣り合うゲート電極同士の間(突合わせ部)の間隔は40nm程度とする。

【0098】

次に、図12(a)および図12(b)に示すように、pウエルPW上のゲート電極の両側のpウエルPWにリン(P)またはヒ素(As)などのn型の不純物をイオン注入することにより、(一対の)n−型半導体領域(図示しない)を形成する。また、nウエルNW上のゲート電極の両側のnウエルNWにホウ素(B)などのp型の不純物をイオン注入することにより、(一対の)p−型半導体領域PEを形成する。n−型半導体領域を形成する際はn型の不純物がp−型半導体領域PEの形成される領域に導入されることを防ぐために、p−型半導体領域PEの形成される領域上にフォトレジスト膜を形成し、逆に、p−型半導体領域を形成する際はp型の不純物がn−型半導体領域の形成される領域に導入されることを防ぐために、n−型半導体領域の形成される領域上にフォトレジスト膜を形成する。したがってn−型半導体領域およびp−型半導体領域PEの形成は別工程で行われるが、n−型半導体領域およびp−型半導体領域PEの形成工程はどちらを先であっても構わない。なお、図12(a)に示すpウエルPWはゲート電極G2およびG5の直下のチャネル領域であるので、この工程においてn型の不純物は導入されず、n−型半導体領域は形成されない。

【0099】

次に、ゲート電極G1、G2、G5およびG6の側壁に、例えば酸化シリコン膜からなるオフセットスペーサ4aを形成した後、絶縁膜として、酸化シリコン膜4および窒化シリコン膜5を順に積層した積層膜からなるサイドウォール(側壁絶縁膜)SWを形成する。オフセットスペーサ4aは、半導体基板1上にCVD法などで形成した酸化シリコン膜をドライエッチング法により一部除去することにより、自己整合的に各ゲート電極の側壁に前記酸化シリコン膜を残すことで形成する。サイドウォールSWは、例えば、CVD法などにより半導体基板1上に酸化シリコン膜4および窒化シリコン膜5を半導体基板1側から順に堆積し、酸化シリコン膜4および窒化シリコン膜5の積層膜をRIE(Reactive Ion Etching)法などにより異方性エッチングすることによって形成することができる。

【0100】

このとき、図12(a)に示すように、ゲート電極G2およびG5の突合わせ部では、各ゲート電極の側壁のサイドウォールSW同士が殆ど接するようにサイドウォールSWを形成し、ゲート電極G2およびG5の間のスペースを極力埋め込むようにする。つまり、突合わせ部においてはサイドウォールSWにより半導体基板1の上面が完全に覆われていることが望ましく、半導体基板1の上面が露出している場合でも、露出している半導体基板1の面積が極力小さいことが望ましい。突合わせ部において対向するサイドウォールSW同士を近接させるのは、後の工程でサイドウォールSWの表面に形成するライナー絶縁膜をサイドウォールSW同士の間で閉塞させるためである。そのため、対向するサイドウォールSW同士が最も近接する箇所の距離は、その箇所に後に形成されるライナー絶縁膜の膜厚の2倍以下の幅を有するものとする。なお、サイドウォールSWを形成するエッチング工程により、露出する半導体基板1の上面は表面が一部除去されて凹んだような形状(図25参照)となり、ゲート電極G1、G2、G5、G6、オフセットスペーサ4aおよびサイドウォールSWに覆われている半導体基板1の上面に比べて露出する半導体基板1の上面の高さが低くなることが考えられる。ただし、図12(b)〜図17(b)では、半導体基板1の主面が一部除去されて凹んでいる形状は示していない。

【0101】

次に、図13(a)および図13(b)に示すように、n+型半導体領域である拡散層(図示しない)を、例えば、ゲート電極およびサイドウォールSWの両側のpウエルPW(図示しない)にリン(P)またはヒ素(As)などのn型の不純物をイオン注入することにより形成する。また、p+型半導体領域である拡散層PSを、例えば、ゲート電極G1、G2およびG6およびそれらの側壁のサイドウォールSWの両側のnウエルNWにホウ素(B)などのp型の不純物をイオン注入することにより形成する。n+型の拡散層を先に形成しても、あるいはp+型の拡散層PSを先に形成しても良い。イオン注入後、導入した不純物の活性化のためのアニール処理を、例えば1050℃程度で5秒程度の熱処理(スパイクアニール処理)にて行うこともできる。n+型の拡散層の深さ(接合深さ)は、n−型半導体領域の深さ(接合深さ)よりも深く、p+型の拡散層PSの深さ(接合深さ)は、p−型半導体領域PEの深さ(接合深さ)よりも深く形成する。

【0102】

n+型の拡散層の不純物濃度はn−型半導体領域の不純物濃度よりも高く、p+型の拡散層PSの不純物濃度は、p−型半導体領域PEの不純物濃度よりも高くする。これにより、nチャネル型MISFETのソースまたはドレインとして機能するn型の半導体領域(不純物拡散層)が、n+型の拡散層およびn−型半導体領域により形成され、pチャネル型MISFETのソースまたはドレインとして機能するp型の半導体領域(不純物拡散層)が、p+型の拡散層PSおよびp−型半導体領域PEにより形成される。つまり、nチャネル型MISFETおよびpチャネル型MISFETのソース・ドレイン領域は、LDD(Lightly doped Drain)構造を有している。n−型半導体領域およびp−型半導体領域PEはゲート電極G1、G2およびG6に対して自己整合的に形成され、n+型の拡散層およびp+型の拡散層PSは、ゲート電極G1、G2およびG6のそれぞれの側壁に形成されたサイドウォールSWに対して自己整合的に形成される。

【0103】

なお、図13(a)に示すpウエルPWはゲート電極G2およびG5の直下のチャネル領域であるので、この工程においてn型の不純物は導入されず、n+型の拡散層は形成されない。また、図13(b)に示すように、ゲート電極G1およびG2の間の領域に形成された拡散層PSおよびp−型半導体領域PEはソース領域S3を構成し、ゲート電極G1およびG6の間の領域に形成された拡散層PSおよびp−型半導体領域PEはドレイン領域D3を構成している。

【0104】

このようにして、pウエルPW上に、電界効果トランジスタとしてnチャネル型のMISFETQ2(図1参照)が形成される。また、nウエルNW上に、ゲート電極G1と、ゲート電極G1の両側のソース領域S3およびドレイン領域D3とを有する電界効果トランジスタであるpチャネル型のMISFETQ3が形成される。

【0105】

その後、サリサイド(Salicide:Self Aligned Silicide)技術により、ゲート電極G1、G2、G5、G6、n+型の拡散層(図示しない)および拡散層PSのそれぞれの上面に、低抵抗のシリサイド層NSを形成する。シリサイド層NSを形成する方法としては、まず各ゲート電極を含む半導体基板1の主面(全面)上に金属膜を、例えばスパッタリング法を用いて形成(堆積)する。金属膜は例えばNi(ニッケル)−Pt(白金)合金膜(NiとPtの合金膜)からなるものである。

【0106】

このようにして金属膜を形成した後、不活性ガスまたは窒素ガス雰囲気中でRTA(Rapid Thermal Anneal)法を用いて半導体基板1を熱処理することで、金属膜と接しているシリコン膜と金属膜とを選択的に反応させて、金属・半導体反応層であるシリサイド層NSを形成する。続いて、ウェット洗浄処理を行うことにより、未反応の金属膜を除去した後、二度目の熱処理を行うことで、シリサイド層NSの焼きしめをする。

【0107】

次に、図14(a)および図14(b)に示すように、半導体基板1の主面上にライナー絶縁膜6を形成する。すなわち、ゲート電極G1、G2、G5およびG6を覆うように、シリサイド層NSを含む半導体基板1上に、例えば窒化シリコン膜からなるライナー絶縁膜6を形成する。ライナー絶縁膜6は、例えば成膜温度(基板温度)450℃程度のプラズマCVD法などにより形成することができる。

【0108】

このとき、図14(b)に示すように、第2方向におけるゲート電極G1、G2間またはゲート電極G1、G6間の距離は図14(a)に示す第1方向におけるゲート電極G2、G5間の距離に比べて長く、サイドウォールSWの側壁に形成されたライナー絶縁膜6の膜厚の2倍の長さよりも長い間隔を有している。このため、第2方向に隣り合うゲート電極間の対向するサイドウォールSWの側面のライナー絶縁膜6同士が互いに接触することはなく、ライナー絶縁膜6によってサイドウォールSW同士の間が閉塞することはない。また、第2方向に隣り合うゲート電極間のサイドウォールSWから露出する半導体基板1の上面の直上のライナー絶縁膜6は突合わせ部よりも広い領域に、半導体基板1の主面に沿うように形成される。

【0109】

これに対し、図14(a)に示すゲート電極G2およびG5の間の突合わせ部では、半導体基板1が殆ど露出しておらず、サイドウォールSW同士の間の距離がサイドウォールSWの側壁に形成されるライナー絶縁膜6の膜厚の2倍の距離以下の間隔であるため、サイドウォールSW同士の間ではそれらの側壁のライナー絶縁膜6が接触している。すなわち、突合わせ部ではライナー絶縁膜6は平坦な半導体基板1の上面の広い領域に半導体基板1の上面に沿って形成されるのではなく、対向して近接するサイドウォールSW同士の間の狭い領域に埋め込まれるように形成される。したがって、突合わせ部のサイドウォールSW間に形成されるライナー絶縁膜6の上面の高さは、最も低い位置であっても、上述した図14(b)に示す第2方向におけるゲート電極G1、G2間またはゲート電極G1、G6間の半導体基板1に沿って形成されたライナー絶縁膜6の上面の高さよりも高くなる。

【0110】

比較例である半導体装置を示した図24および図25を用いて説明したように、ゲート電極の突合わせ部では、対向するサイドウォールSW同士の間の距離がサイドウォールSWの側壁に形成されるライナー絶縁膜6aの膜厚の2倍の値より大きいとき、半導体基板1の主面に形成されたライナー絶縁膜6aは閉塞しない。そのため、突合わせ部のライナー絶縁膜6aの上面の最も低い位置での高さは、第2方向に隣り合うゲート電極同士の間のライナー絶縁膜6aの上面の最も低い位置の高さとほぼ同様の高さになる。または、突合わせ部でのライナー絶縁膜6aのカバレッジの低下により、突合わせ部のライナー絶縁膜6aの上面の最も低い位置での高さは、第2方向に隣り合うゲート電極同士の間のライナー絶縁膜6aの上面の最も低い位置の高さよりも低くなることが考えられる。この場合、突合わせ部ではライナー絶縁膜6aが半導体基板1の主面に沿って形成され、ゲート電極間の深い溝の下部の狭い領域にライナー絶縁膜6aが本実施の形態に比べて大きい体積で形成される。

【0111】

ライナー絶縁膜6aは図25に示すような深い狭い溝の下部ではライナー絶縁膜6a内にボイドを形成する可能性が高くなる。半導体基板1上に形成された複数のコンタクトプラグ同士の間にボイドが形成されたとき、前記ボイド内にコンタクトプラグを構成する金属部材が形成されると、前記複数のコンタクトプラグ同士がボイド内の金属部材により電気的に接続され、半導体素子が正常に動作しなくなる虞がある。このため、ゲート電極の突合わせ部のような狭い溝では、ライナー絶縁膜内にボイドが形成されることを防ぐため、溝の下部に極力ライナー絶縁膜を形成しないことが望ましい。

【0112】

これに対し、本実施の形態では、ゲート電極の突合わせ部の対向するサイドウォールSWのそれぞれの側壁に形成されたライナー絶縁膜6同士が接触し閉塞するようにサイドウォールSW同士の間隔を狭めることにより、突合わせ部の下部のサイドウォールSW間のスペースを小さくしている。このため、突合わせ部のライナー絶縁膜6の上面の最も低い位置は第2方向に隣り合うゲート電極同士の間の半導体基板1の主面に形成されたライナー絶縁膜6の上面の最も低い位置よりも高くなり、突合わせ部の下部、すなわち半導体基板1の主面の近傍にライナー絶縁膜6が殆ど形成されないようにすることができる。

【0113】

これにより、本実施の形態では、第1方向に延在するゲート電極同士の端部が対向している突合わせ部において、半導体基板上の絶縁膜内にボイドが発生することを防ぐことができる。したがって、ボイドの発生に起因するコンタクトプラグ同士の間でのショート(短絡)を防ぐことが可能であるため、半導体装置の信頼性を向上し、また、半導体装置の歩留まりを向上させることができる。

【0114】

次に、図15(a)および図15(b)に示すように、ライナー絶縁膜6上にライナー絶縁膜6よりも厚い層間絶縁膜7を形成する。層間絶縁膜7は例えば酸化シリコン膜などからなり、TEOSを用いて成膜温度450℃程度のプラズマCVD法などにより形成することができる。その後、層間絶縁膜7の表面をCMP法により研磨するなどして、層間絶縁膜7の上面を平坦化する。下地段差に起因してライナー絶縁膜6の表面に凹凸形状が形成されていても、層間絶縁膜7の表面をCMP法により研磨することにより、その表面が平坦化された層間膜を得ることができる。

【0115】

次に、図16(a)および図16(b)に示すように、層間絶縁膜7上に形成したフォトレジストパターン(図示しない)をエッチングマスクとして用いて、層間絶縁膜7およびライナー絶縁膜6をドライエッチングすることにより、ライナー絶縁膜6および層間絶縁膜7にコンタクトホール(貫通孔、孔)7aを形成する。この際、まずライナー絶縁膜6に比較して層間絶縁膜7がエッチングされやすい条件で層間絶縁膜7のドライエッチングを行い、ライナー絶縁膜6をエッチングストッパ膜として機能させることで、層間絶縁膜7にコンタクトホール7aを形成してから、層間絶縁膜7に比較してライナー絶縁膜6がエッチングされやすい条件でコンタクトホール7aの底部のライナー絶縁膜6をドライエッチングして除去する。コンタクトホール7aの底部では、半導体基板1の主面の一部、例えばn+型の拡散層、拡散層PS、ゲート電極G1、G2、G5およびG6のそれぞれの上部のシリサイド層NSの一部などが露出される。このとき、ゲート電極G2の側壁であってゲート電極G1に近い方の側壁のサイドウォールSWおよびオフセットスペーサ4aは除去され、一つのコンタクトホール7a内において、ゲート電極G2およびソース領域S3が露出される。

【0116】

次に、コンタクトホール7a内に、タングステン(W)などからなるコンタクトプラグ(接続用導体部、埋め込みプラグ、埋め込み導体部)PL、P2を形成する。コンタクトプラグPLはドレイン領域D3が露出しているコンタクトホール7a内に形成され、コンタクトプラグP2はゲート電極G2およびソース領域S3が露出しているコンタクトホール7a内に形成される。コンタクトプラグPL、P2を形成するには、例えば、コンタクトホール7aの内部(底部および側壁上)を含む層間絶縁膜7上に、成膜温度(基板温度)450℃程度のプラズマCVD法によりバリア導体膜(例えばチタン膜、窒化チタン膜、あるいはそれらの積層膜)を形成する。それから、タングステン膜などからなる主導体膜をCVD法などによってバリア導体膜上にコンタクトホール7aを埋めるように形成し、層間絶縁膜7上の不要な主導体膜およびバリア導体膜をCMP法またはエッチバック法などによって除去することにより、主導体膜およびバリア導体膜からなるコンタクトプラグPL、P2を形成することができる。n+型の拡散層、拡散層PS、ゲート電極G1、G5およびG6のそれぞれの上に形成されたコンタクトプラグPLは、その底部でn+型の拡散層、拡散層PS、ゲート電極G1、G5およびG6のそれぞれの表面上のシリサイド層NSと接して、電気的に接続される。

【0117】

ここで、図16(a)に示す突合わせ部のライナー絶縁膜6内にボイドが形成されている場合、コンタクトホール7aと繋がって露出した前記ボイド内にコンタクトプラグを構成する金属部材の一部が形成され、ボイド内の金属部材を介してコンタクトプラグと他のコンタクトプラグとがショートする虞がある。しかし本実施の形態の半導体装置では、上述したようにライナー絶縁膜6内にボイドが発生することを防いでいるため、コンタクトプラグ同士がショートすることを防ぐことを可能としている。

【0118】

なお、図16(a)には示されていないが、ゲート電極G2、G5またはそれらの突合わせ部を挟むようにして、ゲート電極G2、G5およびそれらの突合わせ部の第2方向の両側にコンタクトプラグが突合わせ部の近傍にそれぞれ配置されている。また、図16(a)および図16(b)に示されていない領域のゲート電極、ソース・ドレイン領域上にもコンタクトプラグは形成されており、ゲート電極G1、G5およびG6も、図示されていない他の領域において、それぞれの上部に形成されたコンタクトプラグと電気的に接続されている。

【0119】

次に、図17(a)および図17(b)に示すように、コンタクトプラグPL、P2が埋め込まれた層間絶縁膜7上に、ストッパ絶縁膜8および配線形成用の層間絶縁膜9を順次形成する。ストッパ絶縁膜8は層間絶縁膜9への溝加工の際にエッチングストッパとなる膜であり、層間絶縁膜9に対してエッチング選択比を有する材料を用いる。ストッパ絶縁膜8は、例えばプラズマCVD法により形成される窒化シリコン膜とし、層間絶縁膜9は、例えばプラズマCVD法により形成される酸化シリコン膜とすることができる。なお、ストッパ絶縁膜8と層間絶縁膜9には次に説明する第1層目の配線が形成される。

【0120】

続いて、シングルダマシン法により第1層目の配線を形成する。まず、レジストパターン(図示しない)をマスクとしたドライエッチングによって層間絶縁膜9およびストッパ絶縁膜8の所定の領域に配線溝9aを形成した後、半導体基板1の主面上(すなわち配線溝9aの底部および内壁を含む層間絶縁膜9上)にバリア導体膜(バリアメタル膜)を形成する。バリア導体膜は、例えば窒化チタン膜、タンタル膜または窒化タンタル膜などを用いることができる。続いて、CVD法またはスパッタリング法などによりバリア導体膜上に銅のシード層を形成し、さらに電解めっき法などを用いてシード層上に銅めっき膜を形成する。銅めっき膜により配線溝9aの内部を埋め込む。それから、配線溝9a以外の領域の銅めっき膜、シード層およびバリア導体膜をCMP法により除去して、銅を主導電材料とし、銅メッキ膜、シード層およびバリア導体膜からなる第1層目の金属配線M1を形成する。複数の金属配線M1は、コンタクトプラグPLまたはP2を介してn+型の拡散層、拡散層PS、ゲート電極G1、G2、G5およびG6とそれぞれ電気的に接続されている。その後、デュアルダマシン法により金属配線M1上に第2層目の配線を形成するが、ここでは図示およびその説明は省略する。以上により、本実施の形態の半導体装置が完成する。

【0121】

本実施の形態では、上述したように、ゲート電極の突合わせ部の対向するサイドウォールSW同士の間隔を狭め、図25に示す比較例のようにライナー絶縁膜が突合わせ部の下部に形成されることを防ぐことで、ライナー絶縁膜内にボイドが形成されることを防ぎ、前記ボイドを介して複数のコンタクトプラグ同士がショートすることを防ぐことを可能としている。

【0122】

このとき、ライナー絶縁膜6内にボイドが形成されることをより効果的に防ぐ観点から、突合わせ部におけるライナー絶縁膜6の上面の最も低い位置は、ゲート電極G2、G5の上面の高さよりも高い領域に位置していることが望ましい。

【0123】

なお、本実施の形態ではエンドカットを用いて形成したゲート電極を有するSRAMについて説明したが、ゲート電極のパターニング工程では、エンドカットを用いず、一回のエッチングにより一括でゲート電極を形成しても良い。本願発明が解決しようとする課題は、ゲート電極同士の間の突合わせ部の間隔が狭ければ、エンドカットを用いない方法でゲート電極を形成していても起こり得るためである。

【0124】

また、本発明はSRAMを有する半導体装置に限らず、他の半導体装置にも適用することができる。具体的には、第1方向に延在する二つのゲート電極が、第1方向に隣り合っており、各ゲート電極の突合わせ部の近傍において、突合わせ部を挟んで対向するゲート電極の端部または突合わせ部を挟むように配置され、動作時に電位差が生じる複数のコンタクトプラグを有する半導体装置に適用することができる。

【0125】

また、本実施の形態では各ゲート電極の側壁にオフセットスペーサを形成する構造について説明したが、オフセットスペーサは形成されていなくても良い。

【0126】

以下に、本実施の形態の半導体装置の変形例である第1変形例の半導体装置、第2変形例および第3変形例の半導体装置について説明する。

【0127】

第1変形例の半導体装置は、図18(a)および図18(b)に示すように、図2に示す半導体装置に比べて、ゲート電極G2およびG5同士の間の突合わせ部に形成された対向するサイドウォールSW間の間隔が広いものである。ここで、第1変形例の図1〜図4に示す半導体装置とほぼ同様の構造を有する半導体装置であり、図18は図1のA−A線と同じ位置における断面図である。図18(b)は下記の式(2)を説明するための本実施の形態の第1変形例の半導体装置の断面図である。図18(b)は図18(a)の一部を拡大した図であるが、図18(b)ではライナー絶縁膜6より上に形成された構造は示していない。

【0128】

図18(a)および図18(b)に示すように、ゲート電極の突合わせ部の対向するサイドウォールSW同士の間の間隔は図2に示すサイドウォールSW間の間隔よりも広いが、図18(a)および図18(b)の半導体装置においても、サイドウォールSWの側壁に形成されるライナー絶縁膜6の膜厚の2倍以下の間隔で配置されている点は図2に示す構造と同様である。このため、ライナー絶縁膜6は突合わせ部の下部においてサイドウォールSW同士の間で閉塞しており、第1方向のゲート電極間(突合わせ部)のライナー絶縁膜6の上面の最も低い位置は、第2方向に隣り合うゲート電極間のライナー絶縁膜6の上面の最も低い位置よりも高くなっている。したがって、上述した効果と同様の効果、すなわち突合わせ部のライナー絶縁膜6内にボイドが発生することを防ぐことにより、異なるコンタクトプラグ同士の間でショート不良が起こることを防ぐことができる。

【0129】

図18(b)に示す上記の半導体装置の構成を式で表わした場合、以下の式のようになる。

【0130】

S2≦2×βt (2)

ここで、S2は突合わせ部において第1方向に隣り合うサイドウォールSW間の距離である。βは第1方向のサイドウォールSWの端部であって、ゲート電極またはオフセットスペーサ4aと接していない方の端部におけるライナー絶縁膜6のカバレッジ(%)であり、tはライナー絶縁膜6の膜厚設定である。なお、βtはサイドウォールSWの前記端部に形成されたライナー絶縁膜6の膜厚の値である。式(2)は、サイドウォールSW同士の間の距離S2がサイドウォールSWの前記端部に形成されたライナー絶縁膜6の膜厚の2倍以下であることを示す。したがって式(2)により、図18(b)に示す半導体装置では、向かい合うサイドウォールSWの対向する端部に形成されたライナー絶縁膜6が接触して突合わせ部内において閉塞していることが規定されている。

【0131】

また、第2変形例の半導体装置は、図1〜図4に示す半導体装置とほぼ同様の構造を有しているが、図19に示すように、ゲート電極G2およびG5同士の間の突合わせ部のライナー絶縁膜6内に意図的に空隙SPが形成されている点が図2に示す半導体装置と異なる。なお、図19は図1のA−A線と同じ位置における断面図である。

【0132】

MISFETを有する半導体装置には、電極同士の容量結合による寄生容量が半導体装置の回路スピード(動作速度)を低下させる要因として存在しており、動作速度の向上のため、高集積化により電極パターンが密に配置される近年の半導体装置では、寄生容量の低減が求められている。

【0133】

これに対し、本実施の形態の第2変形例である図19に示す半導体装置では、ゲート電極の突合わせ部において対向するサイドウォールSW同士の間に意図的にライナー絶縁膜6に覆われた空隙SPを形成することにより、絶縁膜などが形成されていないスペースを設けている。空隙SPはサイドウォールSW、ライナー絶縁膜6または層間絶縁膜7などよりも低い誘電率を有する領域であるため、空隙SPがゲート電極間に形成されることにより、ゲート電極間の寄生容量を低減することができる。

【0134】

図19に示す第2変形例の半導体装置では、図1〜図5(b)を用いて説明した半導体装置の効果に加え、上述したように寄生容量を低減する効果も奏する。なお、空隙SPは比較例を用いて説明したコンタクトプラグ間のショートの原因となるボイドとは異なり、コンタクトホールを形成した状態でもライナー絶縁膜6内により塞がれているため、コンタクトプラグを構成する金属部材が空隙SP内に形成されることはない。つまり、空隙SPはコンタクトホールが形成される領域には形成されない。

【0135】

また、第3変形例の半導体装置は、図1〜図4に示す半導体装置とほぼ同様の構造を有しているが、図20に示すように、ゲート電極G2およびG5同士の間には図2でサイドウォールSWを構成していた窒化シリコン膜5が形成されておらず、ゲート電極G2およびG5の側壁にはオフセットスペーサ4aを介してL字型の断面を有する酸化シリコン膜4が形成されている。第3変形例において、図2において窒化シリコン膜5が形成されていた領域には、図20に示すようにライナー絶縁膜6が形成されている。つまり、突合わせ部には、半導体基板1の上面およびゲート電極G2、G5の側壁に沿って酸化シリコン膜4が連続的に形成されており、ライナー絶縁膜6とゲート電極G2、G5のそれぞれの側壁との間には酸化シリコン膜4が介在している。なお、図20は図1のA−A線と同じ位置における断面図である。

【0136】

図20に示すように、突合わせ部における酸化シリコン膜4同士は半導体基板1の主面と平行に形成された底部の端部同士が殆ど接するように配置されており、対向する酸化シリコン膜4同士の間にはライナー絶縁膜6が埋め込まれている。ゲート電極G2およびG5のそれぞれの側壁に沿って形成された酸化シリコン膜4同士の間の距離は、ゲート電極G2およびG5のそれぞれの側壁に形成されたライナー絶縁膜6の膜厚の2倍以下の値であるため、突合わせ部ではライナー絶縁膜6同士が接触することでゲート電極間の溝を閉塞させている。

【0137】

この場合、ゲート電極にストレス(応力)を与えるライナー絶縁膜6が図2に示す半導体装置よりもゲート電極G2またはG5に近付くので、ゲート電極G2またはG5のチャネルに与えられるストレスは大きくなる。MISFETは、チャネルの一定の方向にストレスが掛かる程チャネルに電流が流れやすくなる性質を有するため、図20に示す第3変形例の半導体装置では、図1〜図5(b)を用いて説明した半導体装置の効果に加え、MISFETの動作速度を向上させる効果を奏する。

【0138】

図20に示す構造を形成するためには、図12(a)および図12(b)の工程でサイドウォールSWを形成した後に、リン酸などを用いたウェットエッチングにより窒化シリコン膜5を除去し、その後は図13(a)および図13(b)を用いて説明した工程から図17(a)および図17(b)を用いて説明した工程を行えば良い。

【0139】

また、第3変形例の半導体装置において、第2変形例の構造を適用することも可能である。すなわち、図21に示すように、図20の半導体装置とほぼ同様の構造を有する半導体装置において、突合わせ部の閉塞しているライナー絶縁膜6の内部に意図的に空隙SPを設けても良い。これにより、上述したようにコンタクトプラグ間のショートを防ぐ効果と、ゲート電極に与えるストレスを増大させてMISFETの動作速度を向上する効果とに加えて、第2変形例と同様にゲート電極間の寄生容量を低減し、半導体装置の動作速度を向上させる効果を得ることができる。

【0140】

(実施の形態2)

前記実施の形態では、図1〜図4に示すように金属膜であるメタルゲート層MGおよびポリシリコン層PGからなるゲート電極G1〜G6を有するSRAMについて説明した。本実施の形態の半導体装置は、図1〜図4に示すSRAMとほぼ同様の構造を有するが、図22および図23に示すように、メタルゲート層を含まず、ポリシリコン層PGのみからなるゲート電極G1、G2、G5およびG6を有する点で前記実施の形態1の半導体装置と異なる。なお、図22は図2と同じ位置における本実施の形態の半導体装置の断面図であり、図23は図4と同じ位置における本実施の形態の半導体装置の断面図である。

【0141】

ポリシリコン層PGのみからなるゲート電極G1、G2、G5およびG6を有する半導体装置であっても、第1方向に隣り合うゲート電極の間の突合わせ部においてライナー絶縁膜6を閉塞させることにより、ライナー絶縁膜6内にボイドが形成されることを防ぎ、前記実施の形態1と同様の効果を得ることができる。すなわち、前記実施の形態1と同様に、ポリシリコンゲートを有するSRAMを備えた半導体装置において、上述した第1変形例〜第3変形例を適用することが可能である。

【0142】

前記実施の形態1、2においては、複数回のパターニングを用い、エンドカットを行ってゲート電極を形成した場合であって、形成したゲート電極同士の間の狭い間隔を有する突合わせ部に本願発明を適用することを記載している。しかし、複数回のパターニングを行わなくても、1回のパターニングによって30〜50nm程度の狭い間隔で突合わせ部形成される場合でも、本願発明を適用することにより上記効果が得られることはいうまでもない。

【0143】

以上、本発明者らによってなされた発明をその実施の形態に基づき具体的に説明したが、本発明は前記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることはいうまでもない。

【産業上の利用可能性】

【0144】

本発明は、突合わせ部の間隔が狭いゲート電極を有する半導体素子を備えた半導体装置の製造技術に適用して有効である。

【符号の説明】

【0145】

1 半導体基板

2 素子分離領域

2a 溝

3 ゲート絶縁膜

4 酸化シリコン膜

4a オフセットスペーサ

5 窒化シリコン膜

6 ライナー絶縁膜

6a ライナー絶縁膜

7 層間絶縁膜

7a コンタクトホール

8 ストッパ絶縁膜

9 層間絶縁膜

9a 配線溝

BL1 ビット線

BL2 ビット線

D15 ドレイン領域

D26 ドレイン領域

D3 ドレイン領域

D4 ドレイン領域

E1 第1ノード

E2 第2ノード

G1〜G6 ゲート電極

GL、GM、GN ゲート電極

M1 金属配線

MG メタルゲート層

MGa 金属層

NS シリサイド層

NW nウエル

P1 コンタクトプラグ

P2 コンタクトプラグ

PE p−型半導体領域

PG ポリシリコン層

PGa ポリシリコン層

PL コンタクトプラグ

PS 拡散層

PW pウエル

Q1〜Q6 MISFET

S1〜S6 ソース領域

SD ソース・ドレイン領域

SP 空隙

SW サイドウォール

Vdd 電源電位線

Vss 設置電位線

WL ワード線

【技術分野】

【0001】

本発明は、半導体装置およびその製造方法に関し、特に、突合わせ部の間隔が狭いゲート電極を有する半導体素子の製造に適用して有効な技術に関する。

【背景技術】

【0002】

半導体装置の微細化が進むにつれて、例えばSRAM(Static Random Access Memory)を構成するゲートの延在方向と平行な方向、すなわちゲート突き合わせ方向(ゲート幅方向)のデザインを縮小する際に、SRAMを構成するゲート電極のパターニングを2回の露光および2回のエッチングにより行う方法がある。この方法は半導体装置の微細化のためにゲート端部を切り離すマスクを追加して加工する技術であり、一方向に断続的に複数並び、その方向に延在するゲート電極を有するMIS(Metal Insulator Semiconductor)型のFET(Field Effect Transistor:電界効果トランジスタ)などに利用される。本願では、このようにゲート電極同士の突合わせ部を加工するためにマスクを追加してパターニングする技術をエンドカットと呼ぶ。エンドカットを用いることにより、ゲートパターンをその延在方向に一列に複数並べる際に、各ゲート電極同士の突合わせ部の間隔を精度良く狭めてゲート電極を形成することができる。

【0003】

特許文献1(特開2009−252825号公報)には、狭いゲート電極間に形成する層間絶縁膜内にボイドが発生することを防ぎ、当該ゲート電極間の領域を挟んで配置された導電材料がボイドにより導通することを防ぐことが記載されている。ここでは、隣接するゲート電極間の一部領域のアスペクト比を低減させることが記載されている。なお、特許文献1に記載の技術はゲート電極の端部同士が対向して近接する突合わせ部に関するものではない。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2009−252825号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

エンドカットを用いて形成されるようなゲート電極を有する半導体装置において、ゲート電極のゲート長方向に隣り合うゲート電極同士の間では、上述した突合わせ部のゲート電極同士の間隔よりもゲート電極間の間隔が広いため、ゲート電極間に形成する層間絶縁膜の埋め込み性は問題とならない。これに対し、微細化された半導体装置であって、例えば32nmノード以降の半導体装置では、ゲート電極の延在方向に隣り合うゲート電極同士の間(突合わせ部)での層間絶縁膜の埋め込み性が問題となる虞がある。

【0006】

32nmノードまたは28nmノードなどの半導体装置の製造工程でエンドカットを行うと、ゲート電極の延在方向において隣り合うゲート電極同士の間(突合わせ部)の距離は30〜50nm程度となる。このような狭い間隔を有する複数のゲート電極上に層間絶縁膜を形成した場合、突合わせ部ではゲートパターン間の距離が狭いために埋め込み性が悪くなり、層間絶縁膜内にボイド(空隙)が形成される可能性がある。その後に、ボイドが形成された突合わせ部を挟むように層間絶縁膜にコンタクトホールを形成し、各コンタクトホール内にW(タングステン)などの導電部材を埋め込むことでコンタクトプラグを形成しようとすると、前記ボイドにも導電部材が充填され、前記ボイド内の導電部材を介して二つのコンタクトプラグがショート(短絡)を起こし、歩留まりが悪化し、あるいは、半導体装置の信頼性が低下する問題がある。

【0007】

本発明の目的は、製造工程における歩留まりを向上させること、あるいは、半導体装置の信頼性を向上させることにある。

【0008】

特に、本発明の目的は、ゲート電極間のボイドを介してコンタクトプラグ同士がショートすることを防ぐことにある。

【0009】

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

【課題を解決するための手段】

【0010】

本願において開示される実施の形態のうち、代表的なものの概要を簡単に説明すれば、次のとおりである。

【0011】

本発明の好ましい一実施の形態である半導体装置は、

半導体基板の主面に沿う第1方向に延在し、前記第1方向に並んで前記半導体基板上に形成された複数のゲート電極と、

前記第1方向に隣り合う前記複数のゲート電極同士の間に形成された第1絶縁膜と、

前記第1方向に直交する第2方向における前記複数のゲート電極の側方であって、前記ゲート電極から露出する前記半導体基板の上面に形成された第2絶縁膜と、

前記第1絶縁膜の両側に配置され、前記半導体基板に接続された複数のコンタクトプラグと、

を有し、

前記第1絶縁膜および前記第2絶縁膜は前記半導体基板および前記複数のゲート電極を覆うように形成された第3絶縁膜を構成し、

前記第1絶縁膜の上面の最も低い位置は、前記第2絶縁膜の上面の最も低い位置よりも高いものである。

【0012】

また、本発明の好ましい一実施の形態である半導体装置の製造方法は、

(a)半導体基板の主面に沿う第1方向に延在し、前記第1方向に並ぶ複数のゲート電極を前記半導体基板上にゲート絶縁膜を介して形成する工程、

(b)前記複数のゲート電極の両側の半導体基板の主面にソース・ドレイン領域を形成する工程、

(c)前記複数のゲート電極の側壁にサイドウォールを形成する工程、

(d)前記(b)工程および前記(c)工程の後に、前記半導体基板上に前記複数のゲート電極、前記ソース・ドレイン領域および前記サイドウォールを覆うように第2絶縁膜および第3絶縁膜を前記半導体基板側から順に形成する工程、

(e)前記第1方向に隣り合う前記複数のゲート電極同士の間の領域の両側に、前記第2絶縁膜および前記第3絶縁膜を貫通する複数の貫通孔を形成した後、前記ソース・ドレイン領域に接続されたコンタクトプラグを前記複数の貫通孔のそれぞれの内側に形成する工程、

を有し、

前記第1方向に隣り合う前記複数のゲート電極同士の間の前記第2絶縁膜の上面の最も低い位置は、前記第1方向に直交する第2方向において前記複数のゲート電極および前記サイドウォールから露出する前記半導体基板の上面に形成された前記第2絶縁膜の上面の最も低い位置よりも高いものである。

【発明の効果】

【0013】

本願において開示される発明のうち、代表的なものによって得られる効果を簡単に説明すれば以下のとおりである。

【0014】

半導体装置の製造工程における歩留まりを向上させることができ、または、半導体装置の信頼性を向上させることができる。

【0015】

ゲート電極間のボイドを介してコンタクトプラグ同士がショートすることを防ぐことができる。

【図面の簡単な説明】

【0016】

【図1】本発明の実施の形態1である半導体装置を示す平面レイアウトである。

【図2】図1のA−A線における断面図である。

【図3】図1のB−B線における断面図である。

【図4】図1のC−C線における断面図である。

【図5】(a)は実施の形態1のSRAMの等価回路図である。(b)は実施の形態1の半導体装置の断面図である。

【図6】(a)は実施の形態1の半導体装置の製造工程を説明するための断面図である。(b)は実施の形態1の半導体装置の製造工程を説明するための断面図である。

【図7】(a)は図6(a)に続く半導体装置の製造工程中の断面図である。(b)は図6(b)に続く半導体装置の製造工程中の断面図である。

【図8】図7(a)および図7(b)に続く半導体装置の製造工程中の平面レイアウトである。

【図9】(a)は図7(a)に続く半導体装置の製造工程中の断面図である。(b)は図7(b)に続く半導体装置の製造工程中の断面図である。

【図10】図9(a)および図9(b)に続く半導体装置の製造工程中の平面レイアウトである。

【図11】(a)は図9(a)に続く半導体装置の製造工程中の断面図である。(b)は図9(b)に続く半導体装置の製造工程中の断面図である。

【図12】(a)は図11(a)に続く半導体装置の製造工程中の断面図である。(b)は図11(b)に続く半導体装置の製造工程中の断面図である。

【図13】(a)は図12(a)に続く半導体装置の製造工程中の断面図である。(b)は図12(b)に続く半導体装置の製造工程中の断面図である。。

【図14】(a)は図13(a)に続く半導体装置の製造工程中の断面図である。(b)は図13(b)に続く半導体装置の製造工程中の断面図である。

【図15】(a)は図14(a)に続く半導体装置の製造工程中の断面図である。(b)は図14(b)に続く半導体装置の製造工程中の断面図である。

【図16】(a)は図15(a)に続く半導体装置の製造工程中の断面図である。(b)は図15(b)に続く半導体装置の製造工程中の断面図である。

【図17】(a)は図16(a)に続く半導体装置の製造工程中の断面図である。(b)は図16(b)に続く半導体装置の製造工程中の断面図である。

【図18】(a)は実施の形態1の第1変形例を示す断面図である。(b)は実施の形態1の第1変形例を示す断面図である。

【図19】実施の形態1の第2変形例を示す断面図である。

【図20】実施の形態1の第3変形例を示す断面図である。

【図21】実施の形態1の第3変形例を示す断面図である。

【図22】本発明の実施の形態2である半導体装置を示す断面図である。

【図23】本発明の実施の形態2である半導体装置を示す断面図である。

【図24】比較例である半導体装置の平面レイアウトである。

【図25】比較例である半導体装置の断面図である。

【発明を実施するための形態】

【0017】

以下、本発明の実施の形態を図面に基づいて詳細に説明する。なお、実施の形態を説明するための全図において、同一の機能を有する部材には同一の符号を付し、その繰り返しの説明は省略する。また、以下の実施の形態では、特に必要なとき以外は同一または同様な部分の説明を原則として繰り返さない。

【0018】

(実施の形態1)

本実施の形態の半導体装置を、図1〜図5(a)を参照して説明する。図1は半導体基板上に形成された複数のMISFETにより構成されるSRAMを含む半導体装置の平面レイアウトである。図2は半導体基板1上に形成されたMISFETを構成するゲート電極を含む断面図であり、図1のA−A線におけるゲート電極同士の突合わせ部(ゲート端対向部)の断面を示している。図3は、図1のB−B線における断面図であり、ゲート電極間の突合わせ部と、ゲート電極上に形成されたコンタクトプラグとを示している。図4は図1のC−C線における断面図であり、図1に示すSRAMを構成するMISFETのゲート電極、ソース・ドレイン領域およびそれらの上部に形成されたコンタクトプラグの断面を示している。図1のA−A線およびB−B線はゲート電極の延在方向、すなわちゲート幅方向に沿う線であり、C−C線はA−A線およびB−B線に直交し、ゲート電極のゲート長方向に沿う線である。図5(a)は図1に示すSRAMの等価回路図である。

【0019】

SRAMは、フリップフロップ等の順序回路を用いてデータを記憶し、電力の供給がなくなると記憶内容が失われる揮発性メモリである。SRAMはDRAM(Dynamic Random Access Memory)と異なり、記憶部にフリップフロップ回路を用いているためリフレッシュ操作が不要であり、記憶保持状態での消費電力を小さくすることができる記憶回路である。SRAMは、そのメモリセルの構造として、4個のトランジスタと2個の高抵抗素子で構成される高抵抗負荷型と、6個のトランジスタで構成されるCMOS(Complementary MOS)型とがある。本実施の形態では、データ保持時のリーク電流が非常に小さいために信頼性が高く、現在の主流となっているCMOS型のSRAMを例として説明する。

【0020】

図1では、図を分かりやすくするために半導体基板の上面に形成されたソース・ドレイン領域および半導体基板上に形成されたゲート電極からなる複数のMISFETと、各ソース・ドレイン領域上およびゲート電極上に形成に形成されたコンタクトプラグと、半導体基板の上面に形成された素子分離領域とを示しており、他の配線または層間絶縁膜などは示していない。図1の破線で囲まれた領域は一つのSRAMを構成する6つのMISFETQ1〜Q6を含んでおり、半導体基板上にはこのように破線で囲まれて示される構造を一つのユニットとするSRAMが多数形成されている。

【0021】

MISFETQ1〜Q6を構成するゲート電極はいずれも半導体基板の主面に沿う第1方向に延在している。MISFETQ1およびMISFETQ3を構成するゲート電極G1はMISFETQ6を構成するゲート電極G3と第1方向に並んで形成されており、MISFETQ2およびMISFETQ4を構成するゲート電極G2はMISFETQ5を構成するゲート電極G4と第1方向に並んで形成されている。すなわち、ゲート電極G1の延在する延長線上にゲート電極G3が形成されており、ゲート電極G2の延在する延長線上にゲート電極G4が形成されている。

【0022】

ゲート電極G1およびG3の対向する端部は互いに近接しており、本願では、このように同一方向に延在し、当該方向に並んで隣り合うゲート電極同士の対向する端部の間の領域(ゲート端対向部)をゲート電極の突合わせ部と呼ぶ。なお、同様にゲート電極G2およびG4の対向する端部は互いに近接しており、ゲート電極G2およびG4の間にも突合わせ部が存在する。本実施の形態の第1方向の各ゲート電極同士の間の突合わせ部の間隔は例えば40nmとする。

【0023】

ゲート電極G1〜G4は同層に形成された電極であり、ゲート電極G2およびゲート電極G4は、ゲート電極G1の延在方向に直交し半導体基板の主面に沿う方向、すなわち第2方向に並んで配置されている。また、ゲート電極G3とゲート電極G2は第2方向に隣り合うように形成されている。なお、第1方向はゲート電極G1〜G4のゲート幅方向であり、第2方向はゲート電極G1〜G4のゲート長方向である。ゲート電極G1の第2方向の側方にはゲート電極G2、G4の突合わせ部が存在しており、ゲート電極G2の第2方向の側方にはゲート電極G1、G3の突合わせ部が存在している。

【0024】

また、ゲート電極G2を挟むようにして、ゲート電極G4の反対側にはゲート電極G5が形成されている。ゲート電極G5はゲート電極G2との間に突合わせ部を有し、他のSRAMに含まれるMISFETを構成している。さらに、ゲート電極G1の第2方向の側方であってゲート電極G2、G4が無い方にはゲート電極G6が形成されており、ゲート電極G6は他のSRAMに含まれるMISFETを構成している。

【0025】

MISFETQ1、Q3はゲート電極G1を有し、MISFETQ2、Q4はゲート電極G2を有し、MISFETQ5はゲート電極G4を有し、MISFETQ6はゲート電極G3を有している。ゲート電極G1とゲート電極G2との間の領域の半導体基板の主面にはp型の半導体領域であるソース領域S3が形成され、ゲート電極G1を挟むようにして、ソース領域S3の反対側の半導体基板の主面にはp型の半導体領域であるドレイン領域D3が形成されており、ソース領域S3、ドレイン領域D3およびゲート電極G1によりMISFETQ3が構成されている。また、ゲート電極G1とゲート電極G2との間の領域の半導体基板の主面にはp型の半導体領域であるソース領域S4が形成され、ゲート電極G2を挟むようにして、ソース領域S4の反対側の半導体基板の主面にはp型の半導体領域であるドレイン領域D4が形成されており、ソース領域S4、ドレイン領域D4およびゲート電極G2によりMISFETQ4が構成されている。つまり、MISFETQ3、Q4はpチャネル型の電界効果トランジスタである。

【0026】

ゲート電極G1とゲート電極G4との間の領域の半導体基板の主面にはn型の半導体領域であるドレイン領域D15が形成され、ゲート電極G1を挟むようにして、ドレイン領域D15の反対側の半導体基板の主面にはn型の半導体領域であるソース領域S1が形成されており、ドレイン領域D15、ソース領域S1およびゲート電極G1によりMISFETQ1が構成されている。さらに、ゲート電極G4を挟むようにして、ドレイン領域D15の反対側の半導体基板の主面にはn型の半導体領域であるソース領域S5が形成されており、ドレイン領域D15、ソース領域S5およびゲート電極G4によりMISFETQ5が構成されている。

【0027】

同様に、ゲート電極G2とゲート電極G3との間の領域の半導体基板の主面にはn型の半導体領域であるドレイン領域D26が形成され、ゲート電極G2を挟むようにして、ドレイン領域D26の反対側の半導体基板の主面にはn型の半導体領域であるソース領域S2が形成されており、ドレイン領域D26、ソース領域S2およびゲート電極G2によりMISFETQ2が構成されている。さらに、ゲート電極G3を挟むようにして、ドレイン領域D26の反対側の半導体基板の主面にはn型の半導体領域であるソース領域S6が形成されており、ドレイン領域D26、ソース領域S6およびゲート電極G3によりMISFETQ6が構成されている。

【0028】

つまり、MISFETQ1、Q2、Q5およびQ6はnチャネル型の電界効果トランジスタである。また、MISFETQ1およびMISFETQ5はドレイン領域D15を共有しており、MISFETQ2およびMISFETQ6はドレイン領域D26を共有している。

【0029】

第1方向において、ソース領域S3はソース領域S4とドレイン領域D15との間に配置されている。ゲート電極G2とゲート電極G4の突合わせ部の近傍のゲート電極G2の端部の上部およびソース領域S3上には半導体基板の主面に対して垂直に延在する柱状のコンタクトプラグP2が連続的に形成されており、コンタクトプラグP2はゲート電極G2およびソース領域S3のそれぞれに電気的に接続されているため、ゲート電極G2およびソース領域S3は電気的に接続されている(図4参照)。同様に、ゲート電極G3に近い方のゲート電極G1の端部の上部およびソース領域S4上にはコンタクトプラグP1が連続的に形成されており、コンタクトプラグP1によってゲート電極G1およびソース領域S4は電気的に接続されている。

【0030】

また、ソース領域S1、S2、S5、S6、ドレイン領域D15、D3、D26、D4、ゲート電極G3およびG4のそれぞれの上部にはそれぞれコンタクトプラグPLが形成されている。ソース領域S1上およびソース領域S2上のコンタクトプラグPLは上層の配線(図示しない)により電気的に接続され、同一の電位をソース領域S1およびソース領域S2に供給する。ドレイン領域D15上のコンタクトプラグPLとコンタクトプラグP2とは上層の配線(図示しない)により電気的に接続されており、同様に、ドレイン領域D26上のコンタクトプラグPLとコンタクトプラグP1とは上層の配線(図示しない)により電気的に接続されている。

【0031】

ここで、図1に示すゲート電極G1〜G4のパターンは、半導体基板上に形成した膜を1回の露光および1回のエッチングにより加工して形成したものではなく、少なくとも2回の露光および2回のエッチングにより形成しているものである。これはゲート電極の突合わせ部を精度良く微細加工する目的で用いられる加工方法であり、ゲート電極の第1方向に沿う側壁を形成するパターニングと第2方向に沿う側壁を形成するパターニングとの2回のパターニングに分けてゲート電極を加工することで、第1方向のゲート電極間の突合わせ部の間隔をより小さくすることを可能としている。本実施の形態ではこのようにゲート電極を形成する際に複数回のパターニングを行っている。本願では、前記複数回のパターニングのうちの、ゲート電極の突合わせ部を加工して形成する際のパターニング工程をエンドカットと呼ぶ。

【0032】

例えば、本実施の形態では、ゲート電極G1〜G4を形成する際、まず第1方向のゲート電極間の突合わせ部を形成するため、各ゲート電極の第2方向に沿う側壁を形成するパターニング(エンドカット)を行った後、各ゲート電極の第1方向に沿う側壁を形成するパターニングを行うことで、第2方向に並ぶゲート電極同士の間の半導体基板の主面を露出させるものとする。ただし、エンドカットを行う場合のパターニングの順序はこれに限られず、逆にゲート電極の第1方向に沿う側壁を形成するパターニングを行った後、各ゲート電極の第2方向に沿う側壁を形成するパターニング(エンドカット)を行っても構わない。

【0033】

次に、以上に説明したSRAMの構成を図5(a)を用いて説明する。図5(a)の等価回路図に示すように、本実施の形態のSRAMは6つのMISFETQ1〜Q6を有し、MISFETQ5、Q6のソース(図1に示すソース領域S5、S6)はビット線BL1およびBL2にそれぞれ接続されており、MISFETQ5、Q6のゲート電極(図1に示すゲート電極G3、G4)はワード線WLに接続されている。

【0034】

MISFETQ5のドレイン(図1に示すドレイン領域D15)は、第1ノードE1を介してMISFETQ1のドレイン(図1に示すドレイン領域D15)、MISFETQ3のソース(図1に示すソース領域S3)、MISFETQ2およびQ4のゲート(図1に示すゲート電極G2)に接続されている。同様に、MISFETQ6のドレイン(図1に示すドレイン領域D26)は、第2ノードE2を介してMISFETQ2のドレイン(図1に示すドレイン領域D26)、MISFETQ4のソース(図1に示すソース領域S4)、MISFETQ1およびQ3のゲート(図1に示すゲート電極G1)に接続されている。

【0035】

MISFETQ3、Q4のドレイン(図1に示すドレイン領域D3、D4)はいずれも電源電位線Vddに接続され、MISFETQ1、Q2のソース(図1に示すソース領域S1、S2)はいずれも設置電位線Vssに接続されている。MISFETQ5、Q6はいずれも転送用の電界効果トランジスタであり、MISFETQ1、Q2とMISFETQ3、Q4とはそれぞれnチャネル型のトランジスタとpチャネル型のトランジスタとを組み合わせたCMIS(Complementary MIS)インバータである。ここではデータの書込み・読出しのために、MISFETQ1、Q2のCMISとMISFETQ3、Q4のCMISとをたすき掛けするように接続されたフリップフロップ回路が構成されている。

【0036】

SRAMの動作方法について、以下に説明する。SRAMの書込み動作では、図5(a)に示すワード線WLの電圧を上げてMISFETQ5、Q6のゲートをオン状態にし、ビット線BL1の電圧を上げ、ビット線BL2の電圧を下げることにより、フリップフロップ回路の左側の第1ノードE1にはデータ「1」が記憶され、フリップフロップ回路の右側の第2ノードE2にはデータ「0」が記憶される。逆にビット線BL1の電圧を下げ、ビット線BL2の電圧を上げると、第1ノードE1にはデータ「0」が記憶され、第2ノードE2にはデータ「1」が記憶される。このとき、ワード線WLの電圧を下げて0Vにしても、書き込まれた「1」、「0」のデータは、装置の電源が入っている限り記憶され続ける。

【0037】

データの読出し動作時には、ワード線WLの電圧を上げてMISFETQ5、Q6のゲートをオン状態にし、そのときに記憶している状態(第1ノードE1および第2ノードE2の「1」、「0」の組み合わせ)によって、ビット線BL1およびBL2の間に電位差が生じるため、この電位差をセンスアンプにより増幅して検出する。

【0038】

図2に示すように、例えば単結晶シリコンからなる半導体基板1の主面にはp型の不純物(例えばB(ホウ素))が導入されたpウエルPWと素子分離領域2とが形成されており、半導体基板1の主面上には酸化シリコン膜からなるゲート絶縁膜3を介してゲート電極G2およびG5がそれぞれ形成されている。pウエルPWはゲート電極G2、G5の直下にそれぞれ形成され、ゲート電極G2およびG5の対向する端部同士の間の突合わせ部の直下の半導体基板1の主面には例えば酸化シリコン膜からなる素子分離領域2が形成されている。ゲート電極G2、G5はそれぞれゲート絶縁膜3上に半導体基板1側から順に積層されたTiN(窒化チタン)膜などからなるメタルゲート層MGおよびポリシリコン層PGを含み、ポリシリコン層PG上には例えばニッケル(Ni)などを含むシリサイド層NSが形成されている。

【0039】

ゲート電極G2、G5のそれぞれの側壁には酸化シリコン膜4および窒化シリコン膜5を半導体基板1側から順に積層した積層構造を有するサイドウォールSWが形成されており、ゲート電極G2、G5の間の領域である突合わせ部の殆どの領域はサイドウォールSWが占めている。ゲート電極G2、G5のそれぞれの側壁とサイドウォールSWとの間には、酸化シリコン膜からなるオフセットスペーサ4aが介在している。

【0040】

サイドウォールSWはゲート電極G2、G5の側壁に自己整合的に形成されており、サイドウォールSWのゲート電極に接していない方の側壁およびサイドウォールSWの上面は連続した曲面を有している。このため。ゲート電極G2の側壁のサイドウォールSWとゲート電極G5の側壁のサイドウォールSWとの間の距離は、半導体基板1の主面から高くなるにつれて間隔が開いており、それぞれのサイドウォールSW同士の間には、ゲート電極G2、G5を含む半導体基板の主面を覆うように形成されたライナー絶縁膜6が形成されている。すなわち、ライナー絶縁膜6とゲート電極G2、G5のそれぞれの側壁との間にはサイドウォールSWおよびオフセットスペーサ4aが形成されている。

【0041】

ライナー絶縁膜6は例えばSiN(窒化シリコン)膜からなる絶縁膜であり、図1に示すコンタクトプラグP1、P2およびPLなどを埋め込むコンタクトホールを形成する際のエッチングストッパ膜として機能する。ライナー絶縁膜6は、図2に示すように第1方向に隣り合うゲート電極同士の間に形成されており、また、図4に示すように、第2方向における各ゲート電極の側方であって、各ゲート電極およびその側壁に形成されたサイドウォールSWから露出する半導体基板1の上面にも形成されている。ここでは、ゲート電極G2、G5の突合わせ部の上部のライナー絶縁膜6の上面の最も低い位置は、ゲート電極G2、G5の上面の高さよりも高い領域に位置している。また、ライナー絶縁膜6上には層間絶縁膜7、ストッパ絶縁膜8、層間絶縁膜9が半導体基板1の主面側から順に形成されている。層間絶縁膜7、9は例えば酸化シリコン膜からなり、ストッパ絶縁膜8は例えば窒化シリコン膜からなる。ストッパ絶縁膜8は、層間絶縁膜9内に金属配線を埋め込む配線溝を形成する際にエッチングストッパ膜として機能する絶縁膜である。

【0042】

図3に示すように、ゲート電極G1、G3を含む断面は図2と似たような構造を有している。ただし、ゲート電極G1、G3の直上にはコンタクトプラグP1、PLがそれぞれ形成されており、コンタクトプラグP1の直下の半導体基板1の主面には素子分離領域2が形成されている。メタルゲート層MGおよびポリシリコン層PGからなるゲート電極G1、G3は、ポリシリコン層PG上に形成されたシリサイド層NSを介してコンタクトプラグP1、PLにそれぞれ電気的に接続されている。コンタクトプラグP1、PLは、それぞれの上部に形成された金属配線M1に電気的に接続されている。

【0043】

シリサイド層NSは、ゲート電極およびソース・ドレイン領域とコンタクトプラグとの間に介在することでゲート電極およびソース・ドレイン領域とコンタクトプラグとの接触抵抗を低減する働きを有する。シリサイド層NSは金属とシリコンとの反応層であり、その材料としては、例えばニッケルシリサイド、コバルトシリサイド、プラチナシリサイドまたはチタンシリサイドなどを用いることができる。

【0044】

コンタクトプラグP1、PLは、コンタクトホール7aの内壁および底部に形成されたバリア導体膜(図示しない)を介して形成された接続部材である。コンタクトプラグP1、PLは例えばタングステンなどからなり、その側壁および底部に形成されたバリア導体膜は、例えば窒化チタンなどからなる。

【0045】

金属配線M1は、SRAMを構成するMISFETに所定の電位を供給する配線であり、周知のダマシンプロセスによって形成されている。金属配線M1は、配線溝9aの内壁および底部に形成されたバリア導体膜と、前記バリア導体膜を介して配線溝9a内に充填された金属膜からなる。前記バリア導体膜は例えばTa(タンタル)とTaN(窒化タンタル)との積層膜からなり、前記金属膜は、主にCu(銅)からなる膜である。前記バリア導体膜は、前記金属膜内の金属元素が層間絶縁膜9内などに拡散することを防ぐ目的で設けられている。なお、バリア導体膜の部材としては、タンタルの他に、チタン(Ti)、ルテニウム(Ru)、マンガン(Mn)またはそれらの化合物などを用いてもよい。

【0046】

ここでも、図2で示した構造と同様にゲート電極G1、G3の突合わせ部にはサイドウォールSWがゲート電極G1、G3の対向する側壁にそれぞれ形成されており、互いのサイドウォールSWが殆ど接するように配置されている。このため、ゲート電極間の突合わせ部にライナー絶縁膜6が埋め込まれるスペースは少なく、突合わせ部の直上のライナー絶縁膜6の上面の最も低い位置は、ゲート電極G1、G3の上面よりも高い領域に位置しているので、突合わせ部上のライナー絶縁膜6の上面には大きな凹凸が形成されておらず、比較的平坦な形状となっている。

【0047】

図4に示すように、図1のC−C線における第2方向に沿った断面では、MISFETQ3を構成するゲート電極G1、ソース領域S3およびドレイン領域D3を含む断面が示されている。半導体基板1の主面には素子分離領域2およびn型の不純物(例えばP(リン))が導入されたn型の半導体領域であるnウエルNWが形成されている。半導体基板1上にはゲート絶縁膜3を介してゲート電極G2、G1およびG6が形成されており、各ゲート電極の両側の側壁にはオフセットスペーサ4aを介してサイドウォールSWが形成されている。ゲート電極G1の両側の半導体基板1の主面にはソース領域S3およびドレイン領域D3がゲート電極G1の直下のnウエルNWを挟むように形成されている。

【0048】

ソース領域S3およびドレイン領域D3は、p型の不純物(例えばB(ホウ素))が高濃度で導入された、接合深さが深い半導体領域である拡散層PSと、p型の不純物(例えばB(ホウ素))が拡散層PSよりも低い濃度で導入され、接合深さが拡散層PSよりも浅い半導体領域であるp−型半導体領域PEとを有している。p−型半導体領域PEはサイドウォールSWの下部のnウエルNW上に形成され、拡散層PSはゲート電極G1、G2、G6およびサイドウォールSWから露出しているnウエルNWの上面に自己整合的に形成されている。ゲート電極G2およびその側壁の一方のサイドウォールSWのそれぞれの直下には素子分離領域2が形成されており、半導体基板1の主面にはnウエルNWは形成されていない。

【0049】

拡散層PS、ゲート電極G1、G2およびG6のそれぞれの上面にはシリサイド層NSが形成されており、ドレイン領域D3を構成する拡散層PS上にはシリサイド層NSを介してコンタクトプラグPLが形成され、ソース領域S3を構成する拡散層PS上およびゲート電極G2上にはシリサイド層NSを介してコンタクトプラグP2が形成されている。コンタクトプラグP2はゲート電極G2の上面からソース領域S3を構成する拡散層PSの上面にかけて連続的に一体となって形成されており、また、ゲート電極G2の側壁であってゲート電極G1に近い方の側壁を覆うように形成されている。

【0050】

図3に示した構造と同様に、図4に示すコンタクトプラグP2、PLはゲート電極G1、G2およびサイドウォールSWを有する半導体基板1の主面上に順に形成されたライナー絶縁膜6および層間絶縁膜を貫くコンタクトホール7a内に形成されている。コンタクトプラグP2、PLのそれぞれの上部にはストッパ絶縁膜8および層間絶縁膜9が順に形成され、層間絶縁膜9およびストッパ絶縁膜8を貫く配線溝9a内には金属配線M1が複数形成されており、ドレイン領域D3はシリサイド層NSおよびコンタクトプラグPLを介して金属配線M1に電気的に接続されている。また、ゲート電極G2およびMISFETQ3のソース領域S3はシリサイド層NSおよびコンタクトプラグP2を介して電気的に接続されている。

【0051】

図4に示すゲート電極G1、G2は図2、図3に示すゲート電極と同様に、メタルゲート層MGと、その上部に形成されたポリシリコン層PGとにより構成されている。ただし、図2、図3とは異なり、図4にはゲート電極同士の間の突合わせ部は示されておらず、第2方向に隣り合うゲート電極G1、G2の間隔は図2、図3に示す突合わせ部よりも広く設けられている。これは、ゲート電極同士の間にソース・ドレイン領域およびコンタクトプラグを形成するためである。したがって、第1方向のゲート電極間の突合わせ部とは異なり、第2方向に隣り合うゲート電極の間ではサイドウォールSW同士の間隔が突合わせ部よりも広く、ライナー絶縁膜6が半導体基板の主面にゲート電極またはサイドウォールSWを介さず広く形成される。ここで、図2に示す第1方向に隣り合うゲート電極間の突合わせ部のライナー絶縁膜6の最も低い上面の高さは、図4に示す第2方向に隣り合うゲート電極間のライナー絶縁膜6の最も低い上面の高さよりも高い領域に位置している。

【0052】

次に、本実施の形態の半導体装置の効果について説明する。図1に示すSRAMのように、第1方向に複数のゲート電極が並んで配置される半導体装置では、装置の微細化に伴い、ゲート電極同士の突合わせ部が30〜50nm程度の狭い間隔で形成されることにより、ゲート電極間の突合わせ部の絶縁膜の埋め込み性が悪くなる問題がある。ここでいう突合わせ部の絶縁膜とは、例えば図2および図3に示すライナー絶縁膜6のことである。ゲート電極のパターン同士の間隔が狭い突合わせ部では、ライナー絶縁膜6をゲート電極同士の間の深い溝に密に埋め込むことが困難であるため、突合わせ部のライナー膜内にはボイド(空隙)が発生しやすくなる。

【0053】

ここで、上記ボイドが発生した場合に特に問題が起こりやすい構成を説明するために、図24に比較例である半導体装置のゲート電極およびソース・ドレイン領域を示した平面レイアウト図を示す。図24には、半導体基板(図示しない)上に形成され、半導体基板の主面に沿う第1方向に延在する複数のゲート電極GNと、第1方向に直交する第2方向においてゲート電極GNを挟むように半導体基板の主面に形成された二つのソース・ドレイン領域SDと、各ソース・ドレイン領域SD上にそれぞれ形成されたコンタクトプラグPLを示している。図1に示す本実施の形態の半導体装置と同様に、ゲート電極GNはそれぞれの延在する方向である第1方向に並んで複数配置されており、隣り合うゲート電極GNの対向する端部間(突き合せ部)の間隔は40nm程度の狭い間隔となっている。ここでは、ゲート電極の突合わせ部の形成の際にはエンドカットを用いている。

【0054】

図24において、ソース・ドレイン領域SDは第1方向に延在するゲート電極GNに沿うように第1方向に延在して形成されている。ゲート電極GNは第1方向に延在するパターンが途中で途切れるようにして断続的に形成されているのに対し、ソース・ドレイン領域SDは、ゲート電極GNが途切れている突合わせ部の近傍においても途切れておらず、図24に示す領域では複数のゲート電極GNおよびそれらの間の突合わせ部に沿って連続的に形成されている。

【0055】

すなわち、ソース・ドレイン領域SDは、ゲート電極GNの突合わせ部を第2方向において挟むように半導体基板の主面に形成されている。また、各ソース・ドレイン領域SD上には、突合わせ部を挟むようにコンタクトプラグPLが形成されており、ここでは一方のコンタクトプラグPL、突合わせ部およびもう一方のコンタクトプラグPLが第2方向に並んで配置されている。つまり、ゲート電極GNを挟むように配置されたソース・ドレイン領域SDのそれぞれの上のコンタクトプラグPL同士の間には、ゲート電極GNが形成されていない領域がある。図示はしていないが、前記半導体基板の主面上には、ソース・ドレイン領域SD、ゲート電極GNを覆うように絶縁膜が形成されている。前記絶縁膜はコンタクトプラグPL同士の間の領域であるゲート電極の突合わせ部にも形成され、コンタクトプラグPLは前記絶縁膜を貫通してソース・ドレイン領域SDに接続されている。

【0056】

また、図25に他の比較例である半導体装置の断面図を示す。図25は半導体基板1の主面に沿う第1方向に延在する二つのゲート電極GM同士の対向する端部の間の領域を含む、第1方向に沿う断面図である。図25に示す比較例の半導体装置のゲート電極GMはエンドカットを用い、2回のエッチング工程によりパターニングされており、第1方向に隣り合うゲート電極GM同士の間の距離は例えば40nmであるものとする。

【0057】

図2に示す本実施の形態の半導体装置と同様に、図25に示すゲート電極GMおよびその側壁のサイドウォールSWは積層構造を有している。また、図24に示す平面レイアウトと同様に、図25に示すゲート電極GM同士の間の突合わせ部の側方であって、第1方向に直交する第2方向には突合わせ部を挟むようにコンタクトプラグ(図示しない)が形成されている。なお、図24を用いて説明した絶縁膜は、図25に示すライナー絶縁膜6aに対応している。

【0058】

図25に示すように、ゲート電極GMの側壁のサイドウォールSW同士の間の距離が離れているために、ゲート電極GMの突合わせ部には半導体基板1の上面を露出する溝が形成されており、ライナー絶縁膜6aの上面は突合わせ部において大きく凹んだ形状を有している。具体的には、ライナー絶縁膜6aの上面は突合わせ部においてゲート電極GMの上面よりも低い領域であって、半導体基板1の上面に近い領域に位置している。なお、半導体基板1の主面がゲート電極GMの突合わせ部において一部凹んでいるのは、サイドウォールSWを形成するエッチング工程などにより半導体基板1の上面が一部除去されるためである。したがって、突合わせ部に限らず、ゲート電極GMの第2方向の側方の半導体基板1の上面も一部凹んでいることが考えられる。

【0059】

これは、ゲート電極GMの突合わせ部において、対向するサイドウォールSWの上面から側壁にかけて形成されたそれぞれのライナー絶縁膜6a同士が接触しておらず、ライナー絶縁膜6aが突合わせ部において閉塞していないためである。すなわち、突合わせ部においては、いずれの領域においても、対向するサイドウォールSW同士間の幅の値が、サイドウォールSWの側壁に形成されるライナー絶縁膜6aの第1方向の膜厚の値の2倍より大きくなっている。

【0060】

なお、ライナー絶縁膜6aの膜厚は、ゲート電極の上面上では20nm程度であり、突合わせ部のサイドウォールSWから露出している半導体基板1の主面では10〜15nm程度である。サイドウォールSWの表面に形成されたライナー絶縁膜6aの膜厚は、サイドウォールSWの表面の上部から下部にかけて徐々に薄くなるが、例えば最も薄い箇所では、サイドウォールSWの表面に垂直な方向のライナー絶縁膜6aの膜厚は10nm程度となる。なお、ここでいう膜厚とは、ライナー絶縁膜6aの下面に接する下地表面に対して垂直な方向のライナー絶縁膜6aの下面から上面までの距離のことである。

【0061】

半導体基板1上にライナー絶縁膜6aをCVD(Chemical Vapor Deposition)法などを用いて形成する場合、ゲート電極GMなどのパターンの側壁に形成されるライナー絶縁膜6aの膜厚は、突合わせ部よりも広い面積が露出している半導体基板1の主面上またはゲート電極GM上などのように半導体基板1の主面と平行な面に形成されるライナー絶縁膜6aの膜厚に比べて薄くなる。これは、パターンの側壁に形成される絶縁膜のカバレッジ(被膜率)がゲート電極GMの上面のような面に形成される絶縁膜よりも悪くなる性質があるためであり、ゲート電極GMの側壁にサイドウォールSWを介してライナー絶縁膜6aが形成される場合も同様である。

【0062】

ライナー絶縁膜のカバレッジが例えば100%の場合には、ゲート電極の上面に形成されたライナー絶縁膜の膜厚と、ゲート電極の側壁に形成されたライナー絶縁膜の膜厚とはいずれの領域においても同一になる。しかし、カバレッジは特に狭い溝の内壁において悪化する傾向があり、カバレッジが悪いとゲート電極の側壁のライナー絶縁膜は前記側壁の上部から下部に近付くにつれて膜厚が薄くなる。

【0063】

ライナー絶縁膜6aが形成されるゲート電極GM間の突合わせ部が30〜50nm程度の狭い間隔であり、対向するサイドウォールSW間の間隔が狭く、サイドウォールSW間において露出する半導体基板1の上面が小さい場合には、突合わせ部においてサイドウォールSWから露出する半導体基板1上のライナー絶縁膜6aの膜厚も、ゲート電極GM上のライナー絶縁膜6aの膜厚に比べて薄くなることが考えられる。

【0064】

すなわち、図25に示すように、ゲート電極GMの突合わせ部においてゲート電極GMの上面から半導体基板1の上面に対して深い溝が形成されていると、対向するサイドウォールSW間のライナー絶縁膜6aのカバレッジが悪くなり、ライナー絶縁膜6a内に上述したボイドが形成されやすくなる。なお、図25にはボイドは示していない。

【0065】

このような比較例の半導体装置では、図25に示す第1方向に隣り合うゲート電極GM間のライナー絶縁膜6aの上面の最も低い位置に対し、ゲート電極GMの第2方向の側方のゲート電極GMおよびその側壁のサイドウォールSWから露出する半導体基板1の上面に形成されたライナー絶縁膜6aの上面の最も低い位置の方が高い領域に形成されていることが考えられる。これは、ゲート電極GM同士の突合わせ部のような狭い溝の底部においてはライナー絶縁膜6aのカバレッジが低下し、前述したゲート電極GMの第2方向の側方の半導体基板1の上面のライナー絶縁膜6aのように広い領域に形成された膜よりも膜厚が薄くなるためである。

【0066】

図24および図25に示すような構成の半導体装置において、前述したようにゲート電極GN間の突合わせ部に形成される絶縁膜(例えば図25に示すライナー絶縁膜6a)内にボイドが形成された場合、突合わせ部を挟んで近接しているコンタクトプラグPL同士が、前記ボイド内に形成された金属部材によりショート(短絡)し、半導体装置が正常に動作しなくなる問題がある。ショート不良が発生すると、半導体装置の信頼性が低下し、また、歩留まりが悪化することとなる。これは、突合わせ部にボイドを有する絶縁膜(例えばライナー絶縁膜)を形成した後に、前記絶縁膜と前記絶縁膜上に形成した層間絶縁膜とを貫通する二つのコンタクトホールを突合わせ部を挟むように形成し、続いて各コンタクトホール内にコンタクトプラグPLを構成する金属材料を充填する際、前記ボイド内にも当該金属材料が充填され、二つのコンタクトプラグPLがボイドにより接続されてしまうことに起因する。

【0067】

つまり、突合わせ部に形成された絶縁膜がボイドを有する場合、突合わせ部の近傍であって、第1方向に隣り合うゲート電極およびそれらの間の突合わせ部の第2方向の両側の側方にコンタクトプラグをそれぞれ形成すると、それぞれのコンタクトプラグ同士がボイド内に形成された金属部材を介してショートする虞がある。

【0068】

このような問題は、図24に示すように、突合わせ部を挟むようにしてコンタクトプラグPL同士が特に近接する構造において起こりやすくなる。ただし、図1に示すような構造においても、例えばコンタクトプラグP2とソース領域S5上のコンタクトプラグPLとの間で、ゲート電極G2およびゲート電極G4の間の突合わせ部に形成された絶縁膜内のボイドを介してショートが発生する虞がある。言い換えれば、突合わせ部の近傍であって、突合わせ部に形成されたライナー絶縁膜6の両側にソース・ドレイン領域に接続されたコンタクトプラグが形成されている場合、当該ライナー絶縁膜6内にボイドが形成されていると、コンタクトプラグ間でショート不良が発生する。

【0069】

なお、本実施の形態の半導体装置では図1に示すように、ゲート電極が第2方向に並んで配置されているが、第2方向に並ぶゲート電極間の間隔は第1方向のゲート電極間の突合わせ部よりも広く設けられており、ライナー絶縁膜6(図4参照)の埋め込み性は突合わせ部よりも良好になるため、ゲート電極間にボイドは発生しない。これは、ボイドの発生の問題が、突合わせ部の間隔が30〜50nm程度の狭い距離で設けられている場合に顕著になるためである。したがって、図24、図25を用いて説明した比較例および図1に示す本実施の形態のように、突合わせ部を精度良く微細加工する目的でエンドカットを用いてゲート電極を形成している場合、ゲート電極同士の間隔を狭く形成することが可能であるので、上述したボイドの発生に起因するコンタクトプラグ間のショート不良がより発生しやすくなる。

【0070】

また、図1に示すSRAMのように、例えばエンドカットを用いて第1方向のゲート電極間の間隔を小さく形成した半導体装置では、半導体基板上のいずれかの領域に、図24に示すようにゲート電極の突合わせ部を挟むようにコンタクトプラグを配置するレイアウトを形成する可能性がある。これに対し、上記ショート不良の発生を防ぐために、図24に示すようにゲート電極の突合わせ部を挟むようにコンタクトプラグを配置するレイアウトを形成しないようにすると、半導体素子のレイアウトの自由度が低下するため、半導体装置の面積が増大するなどの問題が生じる。

【0071】

また、上記ショート不良の発生を防ぐために突合わせ部の間隔を図1に示す第2方向に隣り合うゲート電極同士の間隔のように広く設ける方法が考えられるが、この場合、ゲート電極の突合わせ部の間隔を縮小することができないため、半導体装置の微細化が困難となる。

【0072】

上述した絶縁膜内のボイドは、ゲート端同士の間隔が30〜50nm程度で狭く形成されている領域であって、特に、ゲート電極の上面から半導体基板の主面までの高さ、すなわち突合わせ部の溝の深さが大きいほど形成されやすくなる。つまり、ライナー絶縁膜6により深い溝を埋め込む場合に、ボイドが発生しやすくなる。これに対し、本実施の形態では、図2に示すように、第1方向に隣り合うゲート電極同士の間の突合わせ部のサイドウォールSW同士が殆ど接するように対向するサイドウォールSW同士を近接させて形成し、突合わせ部に形成されるライナー絶縁膜6が埋め込まれる溝を小さくすることで、ライナー絶縁膜6のカバレッジが悪くなることを防ぎ、ライナー絶縁膜6内にボイドが形成されることを抑制することを可能としている。なお、突合わせ部において対向するサイドウォールSWは側面の一部が接触して一体となっていても良い。

【0073】

例えば、図2に示す半導体装置ではライナー絶縁膜6は突合わせ部においてその上面に大きな凹みが形成されることがなく、図25に示すライナー絶縁膜6aに比べて平坦に形成されているため、ライナー絶縁膜6の最も低い上面の高さはゲート電極G2およびG5のそれぞれの上面の高さよりも高くなっている。すなわち、図2に示す第1方向に隣り合うゲート電極間の突合わせ部のライナー絶縁膜6の最も低い上面の高さは、図4に示す第2方向に隣り合うゲート電極間のライナー絶縁膜6の最も低い上面の高さよりも高い領域に位置している。言い換えれば、半導体基板上に形成された、同一方向(第1方向)に延在する複数のゲート電極および前記複数のゲート電極を有する半導体装置において、ゲート幅方向(第1方向)に並ぶゲート電極間の絶縁膜の上面の一番低い位置は、ゲート長方向(第2方向)のゲート電極間の絶縁膜の上面の一番低い位置よりも高い領域に位置している。

【0074】

これは、突合わせ部において対向するサイドウォールSWが接近することで、サイドウォールSWの上面から側壁にかけて形成されたライナー絶縁膜6同士が対向するサイドウォールSW同士の間で接触し、閉塞するためである。つまり、突合わせ部には、対向するサイドウォールSW同士間の幅の値が、サイドウォールSWの側壁に形成されるライナー絶縁膜6の第1方向の膜厚の値の2倍以下となっている領域がある。これにより、図24および図25を用いて説明した比較例に比べ、突合わせ部上のライナー絶縁膜6の平坦性を向上させ、ライナー絶縁膜6のカバレッジの悪化を抑制することで、ライナー絶縁膜6内にボイドが発生することを防いでいる。

【0075】

上記の構成を式で表わした場合、以下の式のようになる。

【0076】

S1≦2×(a+αt) (1)

ここで、図5(b)に示すように、S1は第1方向に隣り合うゲート電極GL同士の間の距離である。ただし、ゲート電極GLの側壁にオフセットスペーサ4aが形成されている場合は、S1は対向するオフセットスペーサ4a同士の間の距離とする。aはサイドウォールSWの上端の幅である。サイドウォールSWの上端において、窒化シリコン膜5は殆ど除去されているため、式(1)に示すaは酸化シリコン膜4の第1方向の膜厚であるものとして考えることができる。αはゲート電極GLの上面の第1方向の端部のライナー絶縁膜6のカバレッジ(%)であり、tはライナー絶縁膜6の膜厚設定である。αtはサイドウォールSWの側壁のライナー絶縁膜6の膜厚の値である。なお、図5(b)は式(1)を説明するための本実施の形態の半導体装置の断面図である。図5(b)に示す半導体装置は図2に示す半導体装置と同様の構造を有しているが、図5(b)ではライナー絶縁膜6より上に形成された構造は示していない。

【0077】

本実施の形態では、上記の式(1)が成り立つように構造パラメータ設計をすることにより、突合わせ部においてライナー絶縁膜6を閉塞させ、ライナー絶縁膜6が突合わせ部の深い溝の下部に形成されることを防いでいる。上記ボイドは、ライナー絶縁膜6が深い溝の下部に形成された場合に発生しやすいため、ライナー絶縁膜6が突合わせ部の下部に形成されることを抑制することで、ライナー絶縁膜6により深い溝を埋める必要をなくし、ボイドが発生することを防ぐことができる。

【0078】

したがって、本実施の形態の半導体装置では、突合わせ部の絶縁膜内にボイドが形成されることを防ぎ、半導体基板の主面に沿う方向に延在する複数のゲート電極GLおよびゲート電極GL間の突合わせ部の両側に形成された複数のコンタクトプラグが、ボイド内に形成された金属部材を介してショートすることを防ぐことができる。これにより、例えばSRAMなどの半導体素子が正常に動作しなくなることを防ぎ、半導体装置の信頼性を向上することができる。

【0079】

なお、式(1)が成り立つ条件で形成したライナー絶縁膜6は、対向するサイドウォールSWの側壁の下部ではなく、突合わせ部の対向するゲート電極GLの側壁の上端の近傍、すなわちゲート電極GLの上面よりも高い位置で閉塞する。この場合、ライナー絶縁膜6が突合わせ部内であってゲート電極GLの上面よりも低い位置で閉塞する場合、すなわち突合わせ部のライナー絶縁膜6の上面の最も低い位置がゲート電極GLの上面よりも低い領域に位置している場合に比べてライナー絶縁膜6が突合わせ部においてより平坦に形成され、その内部にボイドが形成されにくくなる。

【0080】

また、図25を用いて説明したように、サイドウォールSWを形成するエッチング工程によって半導体基板1の上面が一部除去され、凹んだような形状になっているとしても、本実施の形態の半導体装置では、図2に示す第1方向に隣り合うゲート電極間の突合わせ部のライナー絶縁膜6の最も低い上面の高さは、図4に示す第2方向に隣り合うゲート電極間のライナー絶縁膜6の最も低い上面の高さよりも高い領域に位置している。

【0081】

次に、本実施の形態の半導体装置の製造工程を図面を参照して説明する。図6、図7、図9および図11〜図17は、本発明の一実施の形態である半導体装置、例えばSRAMを有する半導体装置の製造工程中の断面図である。図6(a)、図7(a)、図9(a)、図11(a)、図12(a)、図13(a)、図14(a)、図15(a)、図16(a)および図17(a)は図2と同じ断面における断面図である。また、図6(b)、図7(b)、図9(b)、図11(b)、図12(b)、図13(b)、図14(b)、図15(b)、図16(b)および図17(b)は図4と同じ断面における断面図である。図8および図10は、本発明の一実施の形態である半導体装置、例えばSRAMを有する半導体装置の製造工程中の平面レイアウトである。

【0082】

まず、図6(a)および図6(b)に示すように、例えば1〜10Ωcm程度の比抵抗を有するp型の単結晶シリコンなどからなる半導体基板(半導体ウエハ)1を準備する。次に、この半導体基板1を熱酸化してその表面に例えば厚さ11nm程度の第1絶縁膜を形成した後、その上層にCVD法などにより、例えば厚さ90nm程度の第2絶縁膜を堆積する。第1絶縁膜は酸化シリコンなどからなり、第2絶縁膜は窒化シリコン膜などからなる。それから、フォトレジストパターン(図示しない)をエッチングマスクとして第2絶縁膜、第1絶縁膜および半導体基板1を順次ドライエッチングすることにより、素子分離形成予定領域の半導体基板1に、例えば深さ300nm程度の溝(素子分離用の溝)2aを形成する。溝2aは、素子分離用の溝であり、すなわち後述する素子分離領域2形成用の溝である。

【0083】

続いて、溝2aの内部(側壁および底部)を含む半導体基板1の主面上に、例えば厚み10nm程度の第3絶縁膜を形成する。それから、半導体基板1の主面上(すなわち第3絶縁膜上)に、溝2a内を埋めるように、第4絶縁膜をCVD法などにより形成(堆積)する。

【0084】

第3絶縁膜は、酸化シリコン膜または酸窒化シリコン膜からなる。第3絶縁膜が酸窒化シリコン膜の場合には、第3絶縁膜形成工程以降の熱処理によって溝2aの側壁が酸化することによる体積膨張を防止でき、半導体基板1に働く圧縮応力を低減できる効果がある。

【0085】

第4絶縁膜は、HDP−CVD(High Density Plasma CVD:高密度プラズマCVD)法により成膜された酸化シリコン膜、またはO3−TEOS酸化膜などである。なお、O3−TEOS酸化膜とは、O3(オゾン)およびTEOS(Tetraethoxysilane:テトラエトキシシラン、Tetra Ethyl Ortho Silicateともいう)を原料ガス(ソースガス)として用いて熱CVD法により形成した酸化シリコン膜である。

【0086】

それから、半導体基板1を例えば1150℃程度で熱処理することにより、溝2aに埋め込んだ第4絶縁膜を焼き締めた後、第4絶縁膜をCMP(Chemical Mechanical Polishing:化学的機械的研磨)法により研磨して第2絶縁膜を露出させ、熱リン酸などを用いたウェットエッチングにより第2絶縁膜を除去した後、HFなどにより溝2aの外部の第4絶縁膜および第1絶縁膜を除去し、溝2aの内部に第3絶縁膜、第4絶縁膜を残すことにより、素子分離領域(素子分離)2を形成する。

【0087】

このようにして、溝2a内に埋め込まれた第3絶縁膜、第4絶縁膜からなる素子分離領域2が形成される。本実施の形態では、素子分離領域2は、LOCOS(Local Oxidization of Silicon)法ではなく、好ましくはSTI(Shallow Trench Isolation)法により形成される。すなわち、本実施の形態の素子分離領域2は、好ましくは、半導体基板1に形成された素子分離用の溝2a内に埋め込まれた絶縁体(ここでは第3絶縁膜、第4絶縁膜)からなる。後述するnチャネル型MISFET(すなわちnチャネル型MISFETを構成するゲート絶縁膜、ゲート電極およびソース・ドレイン用のn−型半導体領域およびn+型半導体領域)およびpチャネル型MISFET(すなわちpチャネル型MISFETを構成するゲート絶縁膜、ゲート電極およびソース・ドレイン用のp−型半導体領域およびp+型半導体領域)は、素子分離領域2で規定された(囲まれた)活性領域に形成される。

【0088】

続いて、半導体基板1の主面から所定の深さに渡ってpウエルPW(図6(a)参照)およびnウエルNW(図6(b)参照)を形成する。pウエルPWは、pチャネル型MISFET形成予定領域を覆うフォトレジスト膜(図示しない)をイオン注入阻止マスクとして、nチャネル型MISFET形成予定領域の半導体基板1に例えばホウ素(B)などのp型の不純物をイオン注入することなどによって形成することができるp型半導体領域である。また、nウエルNWは、nチャネル型MISFET形成予定領域を覆う他のフォトレジスト膜(図示しない)をイオン注入阻止マスクとして、pチャネル型MISFET形成予定領域の半導体基板1に例えばリン(P)またはヒ素(As)などのn型の不純物をイオン注入することなどによって形成することができるn型半導体領域である。pウエルPWおよびnウエルNWは同時に形成することが出来ないので順に形成するが、どちらを先に形成しても構わない。

【0089】

次に、図7(a)および図7(b)に示すように、例えばフッ酸(HF)水溶液を用いたウェットエッチングなどにより半導体基板1の表面を清浄化(洗浄)した後、半導体基板1の表面(すなわちpウエルPWおよびnウエルNWの表面)上にゲート絶縁膜3を形成する。ゲート絶縁膜3は、例えば薄い酸化シリコン膜などからなり、例えば熱酸化法などによって形成することができる。

【0090】

続いて、半導体基板1上(すなわちpウエルPWおよびnウエルNWのゲート絶縁膜3上)に、ゲート電極形成用の導体膜として、金属層MGaおよびポリシリコン層PGaを半導体基板1側から順に積層する。金属層MGaはTiN(窒化チタン)膜などからなり、例えばスパッタリングなどにより半導体基板1上に形成される。ポリシリコン層PGaは、成膜時にはアモルファスシリコン膜であったものを、成膜後(イオン注入後)の熱処理により多結晶シリコン膜に変えることもできる。

【0091】

次に、図8、図9(a)および図9(b)に示すように、金属層MGa、ポリシリコン層PGaおよびゲート絶縁膜3をフォトリソグラフィ法およびドライエッチング法を用いてパターニングすることにより、素子分離領域2を有する半導体基板1の主面を一部露出させる。図8は、半導体装置の製造工程を説明するための平面レイアウトである。図9(a)は図8のA−A線における断面図であり、図9(b)は図8のC−C線における断面図である。

【0092】

このパターニングは半導体基板の主面に沿う第1方向に延在するゲート電極を形成するための工程であるが、ここでは図8に示すように、後の工程で形成するゲート電極の一部の側壁のみを形成するものである。すなわち、後の工程で形成されるゲート電極は、平面視において第1方向に延在する側壁と第2方向に沿う側壁からなる矩形の形状を有するものであり、このパターニングでは第2方向に沿う側壁のみを形成する。これにより、半導体基板上に形成されたポリシリコン層PGaから素子分離領域2の上面が複数の箇所において露出する。

【0093】

ゲート電極は第1方向に並んで複数形成されるので、ゲート電極同士の突合わせ部を示す断面図である図9(a)では金属層MGa、ポリシリコン層PGaおよびゲート絶縁膜3が一部除去されるが、ゲート電極が形成される領域であって第2方向に沿う断面図である図9(b)では金属層MGa、ポリシリコン層PGaおよびゲート絶縁膜3は除去されない。

【0094】

次に、図10、図11(a)および図11(b)に示すように、金属層MGa、ポリシリコン層PGaおよびゲート絶縁膜3をフォトリソグラフィ法およびドライエッチング法を用いてパターニングすることにより、金属層MGaおよびポリシリコン層PGaからなるゲート電極G1〜G6を形成する。ここでは、各ゲート電極の第1方向に沿う側壁を形成するようにパターニングを行う。この工程で形成された各ゲート電極の第1方向に沿う側壁と、図8、図9(a)および図9(b)を用いて説明したパターニング工程により予め形成された各ゲート電極の側壁とにより、第1方向に延在する矩形のゲート電極が第1方向に並んで複数形成される。また、このように第1方向に断続的に形成された複数のゲート電極からなる構成は、第1方向に直交する第2方向に並んで複数形成される。図10には、この工程により形成されたゲート電極G1〜G6および半導体基板の上面に形成され、ゲート電極G1〜G6から露出した素子分離領域2、pウエルPWおよびnウエルNWが示されている。

【0095】

このとき、ゲート電極G2およびG5の突合わせ部を示し第1方向に沿う断面図である図11(a)では金属層MGa、ポリシリコン層PGaおよびゲート絶縁膜3は加工されないが、第2方向に層断面図である図11(b)には、第2方向に並んで形成されたゲート電極G2、G1およびG6が示されている。

【0096】

1回のパターニングによりゲート電極を形成する方法も考えられるが、上述したように、本実施の形態では図8、図9(a)および図9(b)を用いて説明したパターニング工程と、図10、図11(a)および図11(b)を用いて説明したパターニング工程との2回のパターニングを用いている。図8、図9(a)および図9(b)を用いて説明したパターニング工程は第1方向に延在し、第1方向に並んで複数形成されるゲート電極同士の間の突合わせ部を形成するための、エンドカットと呼ばれる工程である。ゲート電極の形成を1回のパターニングで一括で行う場合に比べ、エンドカット工程を設けて各ゲート電極の突合わせ部を形成した場合の方が、突合わせ部の金属層MGa、ポリシリコン層PGaおよびゲート絶縁膜3の除去を精度良く行うことができる。つまり、ゲート電極の形成の際のパターニング工程を複数回に分けてエンドカットを行うことにより、より突合わせ部の間隔が狭いゲート電極を形成することができるため、半導体装置の微細化が容易となる。

【0097】

なお、本実施の形態では、エンドカット工程を含むゲート電極のパターニングでは、エンドカットを先に行った後にパターニングを行うことでゲート電極G1〜G6を形成しているが、これに限られず、先にゲート電極の第1方向に沿う側面を形成し、その後にエンドカットを行ってゲート電極G1〜G6を形成しても良い。この場合、まず第1方向に延在する長いパターンを形成した後に、当該パターンを複数のパターンに分離することでゲート電極G1〜G6を形成することになる。このとき、第1方向に隣り合うゲート電極同士の間(突合わせ部)の間隔は40nm程度とする。

【0098】

次に、図12(a)および図12(b)に示すように、pウエルPW上のゲート電極の両側のpウエルPWにリン(P)またはヒ素(As)などのn型の不純物をイオン注入することにより、(一対の)n−型半導体領域(図示しない)を形成する。また、nウエルNW上のゲート電極の両側のnウエルNWにホウ素(B)などのp型の不純物をイオン注入することにより、(一対の)p−型半導体領域PEを形成する。n−型半導体領域を形成する際はn型の不純物がp−型半導体領域PEの形成される領域に導入されることを防ぐために、p−型半導体領域PEの形成される領域上にフォトレジスト膜を形成し、逆に、p−型半導体領域を形成する際はp型の不純物がn−型半導体領域の形成される領域に導入されることを防ぐために、n−型半導体領域の形成される領域上にフォトレジスト膜を形成する。したがってn−型半導体領域およびp−型半導体領域PEの形成は別工程で行われるが、n−型半導体領域およびp−型半導体領域PEの形成工程はどちらを先であっても構わない。なお、図12(a)に示すpウエルPWはゲート電極G2およびG5の直下のチャネル領域であるので、この工程においてn型の不純物は導入されず、n−型半導体領域は形成されない。

【0099】

次に、ゲート電極G1、G2、G5およびG6の側壁に、例えば酸化シリコン膜からなるオフセットスペーサ4aを形成した後、絶縁膜として、酸化シリコン膜4および窒化シリコン膜5を順に積層した積層膜からなるサイドウォール(側壁絶縁膜)SWを形成する。オフセットスペーサ4aは、半導体基板1上にCVD法などで形成した酸化シリコン膜をドライエッチング法により一部除去することにより、自己整合的に各ゲート電極の側壁に前記酸化シリコン膜を残すことで形成する。サイドウォールSWは、例えば、CVD法などにより半導体基板1上に酸化シリコン膜4および窒化シリコン膜5を半導体基板1側から順に堆積し、酸化シリコン膜4および窒化シリコン膜5の積層膜をRIE(Reactive Ion Etching)法などにより異方性エッチングすることによって形成することができる。

【0100】

このとき、図12(a)に示すように、ゲート電極G2およびG5の突合わせ部では、各ゲート電極の側壁のサイドウォールSW同士が殆ど接するようにサイドウォールSWを形成し、ゲート電極G2およびG5の間のスペースを極力埋め込むようにする。つまり、突合わせ部においてはサイドウォールSWにより半導体基板1の上面が完全に覆われていることが望ましく、半導体基板1の上面が露出している場合でも、露出している半導体基板1の面積が極力小さいことが望ましい。突合わせ部において対向するサイドウォールSW同士を近接させるのは、後の工程でサイドウォールSWの表面に形成するライナー絶縁膜をサイドウォールSW同士の間で閉塞させるためである。そのため、対向するサイドウォールSW同士が最も近接する箇所の距離は、その箇所に後に形成されるライナー絶縁膜の膜厚の2倍以下の幅を有するものとする。なお、サイドウォールSWを形成するエッチング工程により、露出する半導体基板1の上面は表面が一部除去されて凹んだような形状(図25参照)となり、ゲート電極G1、G2、G5、G6、オフセットスペーサ4aおよびサイドウォールSWに覆われている半導体基板1の上面に比べて露出する半導体基板1の上面の高さが低くなることが考えられる。ただし、図12(b)〜図17(b)では、半導体基板1の主面が一部除去されて凹んでいる形状は示していない。

【0101】

次に、図13(a)および図13(b)に示すように、n+型半導体領域である拡散層(図示しない)を、例えば、ゲート電極およびサイドウォールSWの両側のpウエルPW(図示しない)にリン(P)またはヒ素(As)などのn型の不純物をイオン注入することにより形成する。また、p+型半導体領域である拡散層PSを、例えば、ゲート電極G1、G2およびG6およびそれらの側壁のサイドウォールSWの両側のnウエルNWにホウ素(B)などのp型の不純物をイオン注入することにより形成する。n+型の拡散層を先に形成しても、あるいはp+型の拡散層PSを先に形成しても良い。イオン注入後、導入した不純物の活性化のためのアニール処理を、例えば1050℃程度で5秒程度の熱処理(スパイクアニール処理)にて行うこともできる。n+型の拡散層の深さ(接合深さ)は、n−型半導体領域の深さ(接合深さ)よりも深く、p+型の拡散層PSの深さ(接合深さ)は、p−型半導体領域PEの深さ(接合深さ)よりも深く形成する。

【0102】

n+型の拡散層の不純物濃度はn−型半導体領域の不純物濃度よりも高く、p+型の拡散層PSの不純物濃度は、p−型半導体領域PEの不純物濃度よりも高くする。これにより、nチャネル型MISFETのソースまたはドレインとして機能するn型の半導体領域(不純物拡散層)が、n+型の拡散層およびn−型半導体領域により形成され、pチャネル型MISFETのソースまたはドレインとして機能するp型の半導体領域(不純物拡散層)が、p+型の拡散層PSおよびp−型半導体領域PEにより形成される。つまり、nチャネル型MISFETおよびpチャネル型MISFETのソース・ドレイン領域は、LDD(Lightly doped Drain)構造を有している。n−型半導体領域およびp−型半導体領域PEはゲート電極G1、G2およびG6に対して自己整合的に形成され、n+型の拡散層およびp+型の拡散層PSは、ゲート電極G1、G2およびG6のそれぞれの側壁に形成されたサイドウォールSWに対して自己整合的に形成される。

【0103】

なお、図13(a)に示すpウエルPWはゲート電極G2およびG5の直下のチャネル領域であるので、この工程においてn型の不純物は導入されず、n+型の拡散層は形成されない。また、図13(b)に示すように、ゲート電極G1およびG2の間の領域に形成された拡散層PSおよびp−型半導体領域PEはソース領域S3を構成し、ゲート電極G1およびG6の間の領域に形成された拡散層PSおよびp−型半導体領域PEはドレイン領域D3を構成している。

【0104】

このようにして、pウエルPW上に、電界効果トランジスタとしてnチャネル型のMISFETQ2(図1参照)が形成される。また、nウエルNW上に、ゲート電極G1と、ゲート電極G1の両側のソース領域S3およびドレイン領域D3とを有する電界効果トランジスタであるpチャネル型のMISFETQ3が形成される。

【0105】

その後、サリサイド(Salicide:Self Aligned Silicide)技術により、ゲート電極G1、G2、G5、G6、n+型の拡散層(図示しない)および拡散層PSのそれぞれの上面に、低抵抗のシリサイド層NSを形成する。シリサイド層NSを形成する方法としては、まず各ゲート電極を含む半導体基板1の主面(全面)上に金属膜を、例えばスパッタリング法を用いて形成(堆積)する。金属膜は例えばNi(ニッケル)−Pt(白金)合金膜(NiとPtの合金膜)からなるものである。

【0106】

このようにして金属膜を形成した後、不活性ガスまたは窒素ガス雰囲気中でRTA(Rapid Thermal Anneal)法を用いて半導体基板1を熱処理することで、金属膜と接しているシリコン膜と金属膜とを選択的に反応させて、金属・半導体反応層であるシリサイド層NSを形成する。続いて、ウェット洗浄処理を行うことにより、未反応の金属膜を除去した後、二度目の熱処理を行うことで、シリサイド層NSの焼きしめをする。

【0107】

次に、図14(a)および図14(b)に示すように、半導体基板1の主面上にライナー絶縁膜6を形成する。すなわち、ゲート電極G1、G2、G5およびG6を覆うように、シリサイド層NSを含む半導体基板1上に、例えば窒化シリコン膜からなるライナー絶縁膜6を形成する。ライナー絶縁膜6は、例えば成膜温度(基板温度)450℃程度のプラズマCVD法などにより形成することができる。

【0108】

このとき、図14(b)に示すように、第2方向におけるゲート電極G1、G2間またはゲート電極G1、G6間の距離は図14(a)に示す第1方向におけるゲート電極G2、G5間の距離に比べて長く、サイドウォールSWの側壁に形成されたライナー絶縁膜6の膜厚の2倍の長さよりも長い間隔を有している。このため、第2方向に隣り合うゲート電極間の対向するサイドウォールSWの側面のライナー絶縁膜6同士が互いに接触することはなく、ライナー絶縁膜6によってサイドウォールSW同士の間が閉塞することはない。また、第2方向に隣り合うゲート電極間のサイドウォールSWから露出する半導体基板1の上面の直上のライナー絶縁膜6は突合わせ部よりも広い領域に、半導体基板1の主面に沿うように形成される。

【0109】

これに対し、図14(a)に示すゲート電極G2およびG5の間の突合わせ部では、半導体基板1が殆ど露出しておらず、サイドウォールSW同士の間の距離がサイドウォールSWの側壁に形成されるライナー絶縁膜6の膜厚の2倍の距離以下の間隔であるため、サイドウォールSW同士の間ではそれらの側壁のライナー絶縁膜6が接触している。すなわち、突合わせ部ではライナー絶縁膜6は平坦な半導体基板1の上面の広い領域に半導体基板1の上面に沿って形成されるのではなく、対向して近接するサイドウォールSW同士の間の狭い領域に埋め込まれるように形成される。したがって、突合わせ部のサイドウォールSW間に形成されるライナー絶縁膜6の上面の高さは、最も低い位置であっても、上述した図14(b)に示す第2方向におけるゲート電極G1、G2間またはゲート電極G1、G6間の半導体基板1に沿って形成されたライナー絶縁膜6の上面の高さよりも高くなる。

【0110】

比較例である半導体装置を示した図24および図25を用いて説明したように、ゲート電極の突合わせ部では、対向するサイドウォールSW同士の間の距離がサイドウォールSWの側壁に形成されるライナー絶縁膜6aの膜厚の2倍の値より大きいとき、半導体基板1の主面に形成されたライナー絶縁膜6aは閉塞しない。そのため、突合わせ部のライナー絶縁膜6aの上面の最も低い位置での高さは、第2方向に隣り合うゲート電極同士の間のライナー絶縁膜6aの上面の最も低い位置の高さとほぼ同様の高さになる。または、突合わせ部でのライナー絶縁膜6aのカバレッジの低下により、突合わせ部のライナー絶縁膜6aの上面の最も低い位置での高さは、第2方向に隣り合うゲート電極同士の間のライナー絶縁膜6aの上面の最も低い位置の高さよりも低くなることが考えられる。この場合、突合わせ部ではライナー絶縁膜6aが半導体基板1の主面に沿って形成され、ゲート電極間の深い溝の下部の狭い領域にライナー絶縁膜6aが本実施の形態に比べて大きい体積で形成される。

【0111】

ライナー絶縁膜6aは図25に示すような深い狭い溝の下部ではライナー絶縁膜6a内にボイドを形成する可能性が高くなる。半導体基板1上に形成された複数のコンタクトプラグ同士の間にボイドが形成されたとき、前記ボイド内にコンタクトプラグを構成する金属部材が形成されると、前記複数のコンタクトプラグ同士がボイド内の金属部材により電気的に接続され、半導体素子が正常に動作しなくなる虞がある。このため、ゲート電極の突合わせ部のような狭い溝では、ライナー絶縁膜内にボイドが形成されることを防ぐため、溝の下部に極力ライナー絶縁膜を形成しないことが望ましい。

【0112】

これに対し、本実施の形態では、ゲート電極の突合わせ部の対向するサイドウォールSWのそれぞれの側壁に形成されたライナー絶縁膜6同士が接触し閉塞するようにサイドウォールSW同士の間隔を狭めることにより、突合わせ部の下部のサイドウォールSW間のスペースを小さくしている。このため、突合わせ部のライナー絶縁膜6の上面の最も低い位置は第2方向に隣り合うゲート電極同士の間の半導体基板1の主面に形成されたライナー絶縁膜6の上面の最も低い位置よりも高くなり、突合わせ部の下部、すなわち半導体基板1の主面の近傍にライナー絶縁膜6が殆ど形成されないようにすることができる。

【0113】

これにより、本実施の形態では、第1方向に延在するゲート電極同士の端部が対向している突合わせ部において、半導体基板上の絶縁膜内にボイドが発生することを防ぐことができる。したがって、ボイドの発生に起因するコンタクトプラグ同士の間でのショート(短絡)を防ぐことが可能であるため、半導体装置の信頼性を向上し、また、半導体装置の歩留まりを向上させることができる。

【0114】

次に、図15(a)および図15(b)に示すように、ライナー絶縁膜6上にライナー絶縁膜6よりも厚い層間絶縁膜7を形成する。層間絶縁膜7は例えば酸化シリコン膜などからなり、TEOSを用いて成膜温度450℃程度のプラズマCVD法などにより形成することができる。その後、層間絶縁膜7の表面をCMP法により研磨するなどして、層間絶縁膜7の上面を平坦化する。下地段差に起因してライナー絶縁膜6の表面に凹凸形状が形成されていても、層間絶縁膜7の表面をCMP法により研磨することにより、その表面が平坦化された層間膜を得ることができる。

【0115】

次に、図16(a)および図16(b)に示すように、層間絶縁膜7上に形成したフォトレジストパターン(図示しない)をエッチングマスクとして用いて、層間絶縁膜7およびライナー絶縁膜6をドライエッチングすることにより、ライナー絶縁膜6および層間絶縁膜7にコンタクトホール(貫通孔、孔)7aを形成する。この際、まずライナー絶縁膜6に比較して層間絶縁膜7がエッチングされやすい条件で層間絶縁膜7のドライエッチングを行い、ライナー絶縁膜6をエッチングストッパ膜として機能させることで、層間絶縁膜7にコンタクトホール7aを形成してから、層間絶縁膜7に比較してライナー絶縁膜6がエッチングされやすい条件でコンタクトホール7aの底部のライナー絶縁膜6をドライエッチングして除去する。コンタクトホール7aの底部では、半導体基板1の主面の一部、例えばn+型の拡散層、拡散層PS、ゲート電極G1、G2、G5およびG6のそれぞれの上部のシリサイド層NSの一部などが露出される。このとき、ゲート電極G2の側壁であってゲート電極G1に近い方の側壁のサイドウォールSWおよびオフセットスペーサ4aは除去され、一つのコンタクトホール7a内において、ゲート電極G2およびソース領域S3が露出される。

【0116】

次に、コンタクトホール7a内に、タングステン(W)などからなるコンタクトプラグ(接続用導体部、埋め込みプラグ、埋め込み導体部)PL、P2を形成する。コンタクトプラグPLはドレイン領域D3が露出しているコンタクトホール7a内に形成され、コンタクトプラグP2はゲート電極G2およびソース領域S3が露出しているコンタクトホール7a内に形成される。コンタクトプラグPL、P2を形成するには、例えば、コンタクトホール7aの内部(底部および側壁上)を含む層間絶縁膜7上に、成膜温度(基板温度)450℃程度のプラズマCVD法によりバリア導体膜(例えばチタン膜、窒化チタン膜、あるいはそれらの積層膜)を形成する。それから、タングステン膜などからなる主導体膜をCVD法などによってバリア導体膜上にコンタクトホール7aを埋めるように形成し、層間絶縁膜7上の不要な主導体膜およびバリア導体膜をCMP法またはエッチバック法などによって除去することにより、主導体膜およびバリア導体膜からなるコンタクトプラグPL、P2を形成することができる。n+型の拡散層、拡散層PS、ゲート電極G1、G5およびG6のそれぞれの上に形成されたコンタクトプラグPLは、その底部でn+型の拡散層、拡散層PS、ゲート電極G1、G5およびG6のそれぞれの表面上のシリサイド層NSと接して、電気的に接続される。

【0117】

ここで、図16(a)に示す突合わせ部のライナー絶縁膜6内にボイドが形成されている場合、コンタクトホール7aと繋がって露出した前記ボイド内にコンタクトプラグを構成する金属部材の一部が形成され、ボイド内の金属部材を介してコンタクトプラグと他のコンタクトプラグとがショートする虞がある。しかし本実施の形態の半導体装置では、上述したようにライナー絶縁膜6内にボイドが発生することを防いでいるため、コンタクトプラグ同士がショートすることを防ぐことを可能としている。

【0118】

なお、図16(a)には示されていないが、ゲート電極G2、G5またはそれらの突合わせ部を挟むようにして、ゲート電極G2、G5およびそれらの突合わせ部の第2方向の両側にコンタクトプラグが突合わせ部の近傍にそれぞれ配置されている。また、図16(a)および図16(b)に示されていない領域のゲート電極、ソース・ドレイン領域上にもコンタクトプラグは形成されており、ゲート電極G1、G5およびG6も、図示されていない他の領域において、それぞれの上部に形成されたコンタクトプラグと電気的に接続されている。

【0119】

次に、図17(a)および図17(b)に示すように、コンタクトプラグPL、P2が埋め込まれた層間絶縁膜7上に、ストッパ絶縁膜8および配線形成用の層間絶縁膜9を順次形成する。ストッパ絶縁膜8は層間絶縁膜9への溝加工の際にエッチングストッパとなる膜であり、層間絶縁膜9に対してエッチング選択比を有する材料を用いる。ストッパ絶縁膜8は、例えばプラズマCVD法により形成される窒化シリコン膜とし、層間絶縁膜9は、例えばプラズマCVD法により形成される酸化シリコン膜とすることができる。なお、ストッパ絶縁膜8と層間絶縁膜9には次に説明する第1層目の配線が形成される。

【0120】