半導体装置およびその製造方法

【課題】配線部を通じた信号伝搬速度を向上できるようにした半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、半導体基板上に形成された第1絶縁膜と、前記第1絶縁膜上に形成された、前記第1絶縁膜より比誘電率が高い第2絶縁膜と、前記第2絶縁膜と隣接する側面が順テーパ形状を有し、前記第1絶縁膜および前記第2絶縁膜を貫通して形成された複数の縦柱状プラグと、前記第2絶縁膜上に形成された、前記第2絶縁膜よりも比誘電率が低い第3絶縁膜と、前記複数の縦柱状プラグの上部に到達するように前記第3絶縁膜に形成された複数の溝と、前記複数の溝内にそれぞれ形成され、前記複数の縦柱状プラグの上部に一部がそれぞれ接触する金属からなる複数の配線部と、を備える。

【解決手段】半導体装置は、半導体基板上に形成された第1絶縁膜と、前記第1絶縁膜上に形成された、前記第1絶縁膜より比誘電率が高い第2絶縁膜と、前記第2絶縁膜と隣接する側面が順テーパ形状を有し、前記第1絶縁膜および前記第2絶縁膜を貫通して形成された複数の縦柱状プラグと、前記第2絶縁膜上に形成された、前記第2絶縁膜よりも比誘電率が低い第3絶縁膜と、前記複数の縦柱状プラグの上部に到達するように前記第3絶縁膜に形成された複数の溝と、前記複数の溝内にそれぞれ形成され、前記複数の縦柱状プラグの上部に一部がそれぞれ接触する金属からなる複数の配線部と、を備える。

【発明の詳細な説明】

【技術分野】

【0001】

本発明の実施形態は、半導体装置およびその製造方法に関する。

【背景技術】

【0002】

半導体装置は、素子の微細化、集積化が進められるに従い、各種電気的配線の配線幅やピッチも小さくなってきている。これに伴い、各種プラグの径やその間隔も狭くなってきている。プラグが近接すると隣接プラグ間の容量値が増加し、さらにその上の溝内に配線部が形成されていると、当該配線部に信号が伝達する際の伝播遅延が生じやすくなる。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開平11−74345号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

配線部を通じて伝達する信号の伝搬遅延を極力抑制できるようにした半導体装置およびその製造方法を提供する。

【課題を解決するための手段】

【0005】

実施形態に係る半導体装置は、半導体基板上に形成された第1絶縁膜を備える。また、第1絶縁膜上に形成された第1絶縁膜より比誘電率が高い第2絶縁膜を備える。また、第2絶縁膜と隣接する側面が順テーパ形状を有し第1絶縁膜および第2絶縁膜を貫通して形成された複数の縦柱状プラグを備える。また、第2絶縁膜上に形成された第2絶縁膜よりも比誘電率が低い第3絶縁膜を備える。また、複数の縦柱状プラグの上部にそれぞれ到達するように第3絶縁膜に形成された複数の溝を備えると共に、複数の溝内にそれぞれ形成され複数の縦柱状プラグの上部に一部がそれぞれ接触する金属からなる複数の配線部を備える。

【0006】

実施形態に係る半導体装置は、半導体基板上に形成された第1絶縁膜を備える。また、第1絶縁膜上に形成され当該第1絶縁膜よりも比誘電率が高い第2絶縁膜を備える。また、第1絶縁膜に貫通形成されその上面が第2絶縁膜の下面と略同一高さにある複数の縦柱状プラグを備える。また、第2絶縁膜上に形成され第2絶縁膜よりも比誘電率が低い第3絶縁膜を備える。また、複数の縦柱状プラグの上部にそれぞれ到達するように第2絶縁膜および第3絶縁膜に形成された複数の溝を備えると共に、複数の溝内にそれぞれ形成され複数の縦柱状プラグの上部に一部がそれぞれ接触する金属からなる複数の配線部を備える。そして、縦柱状プラグは、その上部が前記第1絶縁膜と隣接する側面に順テーパ形状を有している。

【0007】

実施形態に係る半導体装置の製造方法は、第1層間絶縁膜に形成された複数のホール内にそれぞれ縦柱状プラグを形成する工程を備える。また、第1層間絶縁膜の上部を除去して形成された複数の縦柱状プラグの上部側面を露出させる工程を備える。また、露出した縦柱状プラグの上部側面をスリミングする工程を備える。また、複数の縦柱状プラグの上部側面間にエッチングストッパ膜を形成する工程を備える。また、エッチングストッパ膜上に当該エッチングストッパ膜とエッチング選択性を有する第2層間絶縁膜を形成する工程を備える。また、第2層間絶縁膜にエッチングストッパ膜の上面上に至るまで複数の縦柱状プラグにそれぞれ達する複数の溝を形成する工程を備える。また、複数の縦柱状プラグの上部とそれぞれ接触する複数の配線部を複数の溝内にそれぞれ形成する工程を備える。

【図面の簡単な説明】

【0008】

【図1】第1の実施形態についてフラッシュメモリ装置のメモリセル領域の電気的構成の一部を示す回路図

【図2】メモリセル領域の一部の下層部分における平面レイアウトパターンを模式的に示す図

【図3】メモリセル領域の一部の特にビット線コンタクトの上層配線構造の平面レイアウトパターンを模式的に示す図

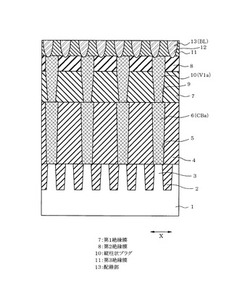

【図4】図2の切断線A−A線で示す部分を模式的に表す縦断側面図

【図5】製造工程の一段階における図4に対応する部分を模式的に示す縦断面図(その1)

【図6】製造工程の一段階における図4に対応する部分を模式的に示す縦断面図(その2)

【図7】製造工程の一段階における図4に対応する部分を模式的に示す縦断面図(その3)

【図8】製造工程の一段階における図4に対応する部分を模式的に示す縦断面図(その4)

【図9】製造工程の一段階における図4に対応する部分を模式的に示す縦断面図(その5)

【図10】製造工程の一段階における図4に対応する部分を模式的に示す縦断面図(その6)

【図11】第2の実施形態について示す図4相当図

【図12】製造工程の一段階における図4に対応する部分を模式的に示す縦断面図(その7)

【図13】製造工程の一段階における図4に対応する部分を模式的に示す縦断面図(その8)

【図14】製造工程の一段階における図4に対応する部分を模式的に示す縦断面図(その9)

【図15】製造工程の一段階における図4に対応する部分を模式的に示す縦断面図(その10)

【図16】第3の実施形態について示す図4相当図

【図17】製造工程の一段階における図4に対応する部分を模式的に示す縦断面図(その11)

【図18】製造工程の一段階における図4に対応する部分を模式的に示す縦断面図(その12)

【図19】製造工程の一段階における図4に対応する部分を模式的に示す縦断面図(その13)

【図20】製造工程の一段階における図4に対応する部分を模式的に示す縦断面図(その14)

【図21】製造工程の一段階における図4に対応する部分を模式的に示す縦断面図(その15)

【発明を実施するための形態】

【0009】

(第1の実施形態)

以下、本発明をNAND型フラッシュメモリ装置に適用した場合の第1の実施形態について図1ないし図10を参照しながら説明する。なお、以下の図面の記載において、同一又は類似の部分には同一又は類似の符号で表している。但し、図面は模式的なものであり、厚みと平面寸法との関係、各層の厚みの比率等は現実のものとは異なる場合があることを留意する。

【0010】

先ず、本実施形態のNAND型フラッシュメモリ装置の構成を説明する。図1は、NAND型のフラッシュメモリ装置のメモリセル領域に形成されるメモリセルアレイの一部の等価回路図である。

【0011】

NAND型フラッシュメモリ装置のメモリセルアレイは、2個の選択ゲートトランジスタTrs1、Trs2と、当該選択ゲートトランジスタTrs1、Trs2間に直列接続された複数個(例えば64個:2のn乗個(nは正整数))のメモリセルトランジスタTrmとからなるNANDセルユニット(メモリユニット)Suが行列状に形成されることで構成されている。NANDセルユニットSu内において、複数個のメモリセルトランジスタTrmは隣接するもの同士でソース/ドレイン領域を共用して形成されている。

【0012】

図1中、X方向(ワード線方向に相当)に配列されたメモリセルトランジスタTrmは、ワード線(制御ゲート線)WLにより共通接続されている。また、図1中、X方向に配列された選択ゲートトランジスタTrs1は選択ゲート線SGL1で共通接続され、選択ゲートトランジスタTrs2は選択ゲート線SGL2で共通接続されている。選択ゲートトランジスタTrs1のドレイン領域にはビット線コンタクトCBが接続されている。このビット線コンタクトCBは図1中X方向に直交するY方向(ビット線方向に相当)に延びるビット線BLに接続されている。また、選択ゲートトランジスタTrs2はソース領域を介して図1中X方向に延びるソース線SLに接続されている。

【0013】

図2および図3は、メモリセル領域の一部のレイアウトパターンを平面図により示している。この図2は、主に半導体基板の表層部およびその直ぐ上層部分の構造を示している。また、図3は、当該該当部分のさらに上層部分の構造を示している。

【0014】

図2に示すように、半導体基板(例えばシリコン基板)1には、素子分離領域としてのSTI(shallow trench isolation)2が図2中Y方向に沿って形成されている。このSTI2はX方向に離間して複数形成されており、これにより活性領域3が図2中X方向に分離した状態に形成されている。メモリセルトランジスタのワード線WLが、活性領域3の延伸方向であるY方向に直交する図2中X方向に沿って形成されている。

【0015】

また、図2中X方向に沿って一対の選択ゲートトランジスタTrs1−Trs1の選択ゲート線SGL1,SGL1が形成されている。選択ゲート線SGL1−SGL1間の活性領域3上にはビット線コンタクトCBが千鳥状に配置されている。

【0016】

選択ゲート線SGL1と所定本数のワード線WLを存した位置に、上述同様にして、図2中X方向に沿って一対の選択ゲートトランジスタの選択ゲート線SGL2が形成されている。そして、一対の選択ゲート線SGL2間の活性領域3にはソース線コンタクトCSが千鳥状に配置されている。

【0017】

図4は、図2中の切断線A−Aで示す部分の縦断面図を模式的に示している。すなわち、図4は、ビット線コンタクトCBaとその上層のビット線ヴィアプラグV1aとを選択ゲート線SGL1の延伸方向に沿って切断した縦断面図を示している。

【0018】

この図4において、半導体基板(例えばシリコン基板)1は、その表層部が素子分離領域2によって活性領域3に分離形成されている。素子分離領域2は、半導体基板1の表層部に所定間隔で形成したトレンチ(素子分離溝)の内部にシリコン酸化膜などの絶縁膜を埋込み形成して構成されている。

【0019】

半導体基板1の上面上には、図示しないが前述した選択ゲートトランジスタTrs1、Trs2、メモリセルトランジスタTrmの各ゲート電極がゲート絶縁膜を介して積層形成されている。なお、図4に示した部分は、当該トランジスタTrs1、Trs2、Trmの各ゲート電極の積層構造が予め形成され、その後のエッチング処理により除去された部分を示している。

【0020】

図4において、半導体基板1の上面上には一対の選択ゲート線SGL1−SGL1間を埋めるようにシリコン酸化膜4が所定膜厚で形成されている。なお、一対の選択ゲート線SGL2−SGL2間においても同様であるため説明を省略している。

【0021】

このシリコン酸化膜4にはその上面から下面まで貫通するコンタクトホール5が形成されている。このコンタクトホール5は、半導体基板1の活性領域3を1個おきに露出させるように形成されており、半導体基板1にほぼ垂直な側面を有するように形成されている。

【0022】

なお、ビット線コンタクトCBaおよびCBbのコンタクトホール5は、図4に示す活性領域3の全てについて1つずつ千鳥状に形成されており、それぞれ縦方向に延伸形成されている。図4の断面では現れていないが、図2に示したビット線コンタクトCBbに対応する部分にも形成されている。このように平面的には千鳥状に配置されている理由は、素子の縮小化、設計ルールの縮小化に伴い、隣接コンタクトCBaおよびCBb間の間隔が狭くなってきているためであり、隣接コンタクトCBaおよびCBb間の距離を確保することで所望の特性を得るためである。

【0023】

コンタクトホール5内には、チタン/窒化チタン(Ti/TiN)などのバリアメタルを介してタングステン(W)などの導電性材料が埋め込まれており、コンタクトプラグ6がビット線コンタクトCBaとして形成されている。

【0024】

シリコン酸化膜4の上面上には、シリコン酸化膜7が第1絶縁膜、第1層間絶縁膜として所定膜厚で形成されている。また、シリコン酸化膜7の上面上にはエッチングストッパ膜、第2絶縁膜としてシリコン窒化膜8が構成されている。本実施形態では、第2絶縁膜としてシリコン窒化膜8を適用した実施形態を示すが、これに代えてシリコン窒化物を含有したシリコン炭窒化膜(SiCN)を適用しても良い。

【0025】

これらのシリコン酸化膜7およびシリコン窒化膜8には、コンタクトプラグ6の直上の位置にシリコン酸化膜7およびシリコン窒化膜8を上端から下端まで貫通するヴィアホール(ホールに相当)9が形成されている。

【0026】

ヴィアホール9はシリコン酸化膜7の下面からシリコン窒化膜8の上面にかけて横断面積が増加するよう側面が順テーパ状となるように形成されている。ヴィアホール9の内側には窒化チタン(TiN)などのバリアメタルを介してタングステン(W)などの導電性材料がヴィアプラグ10として埋込形成されている。

【0027】

これにより、ヴィアプラグ10がシリコン窒化膜8の上面からシリコン酸化膜7の下面にかけて柱状に貫通形成されている。このヴィアプラグ10はビット線ヴィアプラグV1aに対応し縦柱状プラグに相当する。なお、図4の断面では現れていないが、ヴィアプラグ10は、図2に示したビット線コンタクトCBbの直上の部分にもビット線ヴィアプラグV1bとして形成されている。ヴィアプラグ10の下端はコンタクトプラグ6の上端と接触する。

【0028】

シリコン窒化膜8の上面とヴィアプラグ10の上面とはほぼ面一に形成されている。これらのシリコン窒化膜8およびヴィアプラグ10の上面上にはシリコン酸化膜11が第3絶縁膜、第2層間絶縁膜として形成されている。シリコン窒化膜8とシリコン酸化膜11とは適切に条件を設定すれば選択的にエッチング可能な膜の関係にある。このシリコン酸化膜11にはビット線BL形成用の溝12が形成されており、当該溝12内に配線層(配線部に相当)13がビット線BLとして形成されている。

【0029】

この配線層13は、Y方向に延伸するビット線用の溝12内に埋込まれて形成されるものであり、当該溝12内には銅(Cu)などの導電性材料が埋め込まれている。このビット線BLの配線層13は、そのX方向の幅寸法がヴィアプラグ10の上面の径に対応する幅寸法で形成されている。これらの配線層13は図2中のY方向に沿って形成されている。

【0030】

本実施形態では、配線層13と当該配線層13に隣接するヴィアプラグ10との間にシリコン窒化膜8が形成されておらずシリコン酸化膜11が形成されている。シリコン酸化膜7および11は、シリコン窒化膜8(またはシリコン炭窒化膜)に比較して比誘電率が低い。

【0031】

したがって、本実施形態の構造によれば、シリコン窒化膜8が配線層13とヴィアプラグ10との間に形成された構造に比較して当該配線層13とヴィアプラグ10との間の容量を低減できる。また、シリコン窒化膜8が隣り合う配線層13間に形成されていないため、隣り合う配線層13間の容量を低減できる。信号の伝搬速度は抵抗および他配線との間の配線間容量に依存するが、配線層13とヴィアプラグ10との間の容量を低減することで時定数を小さくすることができ、配線層13を通じて伝達する信号の伝搬遅延を極力抑制できる。

【0032】

次に、前記した構造の製造工程について図5ないし図10を参照しながら説明する。なお、ここでは、ヴィアプラグ10およびビット線BLの配線層13の構造の製造工程を中心に説明し、コンタクトプラグ6の製造工程説明は簡略的に行う。

【0033】

製造方法の特徴部分を中心に説明するが、一般的な工程であれば付加しても良いし、前述実施形態にて説明した製造工程は必要に応じて入れ替えても良い。また、必要に応じて工程を省いても良い。

【0034】

図5に示すように、半導体基板1に素子分離領域2を形成することで活性領域3を分離し、その後、シリコン酸化膜4をCVD法により堆積し、当該シリコン酸化膜4をRIE(Reactive Ion Etching)等により異方性エッチングし、コンタクトホール5を形成し、当該コンタクトホール5内にコンタクトプラグ6を埋込む。

【0035】

この図5に示す工程では、一対の選択ゲート線SGL1間の活性領域3に対応して、図2に示したように、一対の選択ゲート線SGL1の何れかに近づいた位置となるように千鳥状にコンタクトホール5を形成する。

【0036】

また、コンタクトホール5を形成した後には、コンタクトホール5の内面に沿って導電性材料としてチタン/窒化チタンなどのバリアメタルを形成し、当該バリアメタルの内側にタングステン(W)を埋込む。この後、シリコン酸化膜4の上面上に堆積したタングステンをCMP(Chemical Mechanical Polishing)法により平坦化する。これにより図5に示す構造を形成できる。

【0037】

次に、図6に示すように、TEOSガスを用いたプラズマCVD法によりシリコン酸化膜7を堆積する。その後、シリコン酸化膜7の上面上にシリコン窒化膜8をプラズマCVD法により堆積する。

【0038】

次に、図7に示すように、シリコン窒化膜8の上面上にレジスト(図示せず)をパターニングし、当該パターニングされたレジストをマスクとしてシリコン窒化膜8をRIE法により異方性エッチングし、続いてシリコン酸化膜7をRIE法により異方性エッチングすることでヴィアホール9を形成する。

【0039】

次に、図8に示すように、ヴィアホール9の内面に沿って窒化チタン(TiN)などのバリアメタルを形成し当該バリアメタルを介して例えばタングステン(W)をヴィアホール9の内側に埋込み、シリコン窒化膜8をストッパとしてCMP法により平坦化することでヴィアプラグ10を形成する。

【0040】

次に、図9に示すように、ヴィアプラグ10およびシリコン窒化膜8の上面上にCVD法によりシリコン酸化膜11を堆積する。

次に、図10に示すように、シリコン酸化膜11の上面上にレジスト(図示せず)をパターニングし当該レジストをマスクとしてビット線BL用の溝12を形成する。この場合、シリコン窒化膜8に対して高選択性を有する条件によってシリコン酸化膜11を異方性エッチングすることで溝12を形成する。これにより、シリコン窒化膜8のほぼ上面位置で溝12形成の際にエッチングストップすることができ溝12の深さをほぼ一定に揃えることができる。次に、図4に示すように、当該ビット線BL用の溝12内に配線用導体として銅(Cu)を埋込み形成してビット線BL用の配線層13を形成する。ビット線BLの配線層13は、全てのコンタクトプラグ6(CBa、CBb)に対応して形成される。

【0041】

溝12の深さがほぼ一定の深さに形成されるため、配線層13が溝12内に埋め込まれたとしても、配線層13とヴィアプラグ10との間の距離をほぼ一定に保つことができる。したがって、配線層13およびヴィアプラグ10間の容量を一定に保持でき、複数の配線層13およびヴィアプラグ10を通じて伝達する信号の伝搬遅延時間もほぼ同一となる。これにより特性のばらつきを抑制できる。

【0042】

本実施形態の製造方法によれば、次に示す特徴的な工程を備える。すなわち、半導体基板1の上方にシリコン酸化膜7、シリコン窒化膜8を順次形成する。シリコン窒化膜8の上面からシリコン酸化膜7の下面にかけて貫通するヴィアホール9を形成する。当該ヴィアホール9内に導電性材料を埋込んでヴィアプラグ10を形成する。シリコン窒化膜8およびヴィアプラグ9の上面上にシリコン酸化膜11を形成する。シリコン窒化膜8をストッパとしてシリコン酸化膜11に溝12を形成する。溝12内にビット線BL用の配線層13を形成する。このような製造方法を適用することで、溝12の深さをほぼ一定の深さに揃えることができる。これにより、特性ばらつきを抑制できる。

【0043】

(第2の実施形態)

図11ないし図15は、第2の実施形態を示している。本実施形態が前述第1の実施形態と異なるところは、ヴィアプラグの上部が上面から半導体基板方向にかけて横断面積が増大するように(順テーパで)形成されているところにある。前述実施形態と同一または類似材料、同一または類似機能を奏する部分については同一符号を付して説明を省略し、以下、異なる部分について説明する。

【0044】

図11に示すように、ヴィアプラグ10に代わるヴィアプラグ20は、コンタクトプラグ6の上面上に形成されている。ヴィアプラグ20の下部20bはシリコン酸化膜7の上面高さから下面高さに至るまで横断面積が縮小するように(逆テーパで)構成されている。

【0045】

また、このヴィアプラグ20は、シリコン酸化膜7およびシリコン窒化膜8の界面を境界としてその上下で互いに径が異なる。ヴィアプラグ20は、シリコン酸化膜7およびシリコン窒化膜8の界面より下側においてその下部20bの径が大きく、当該界面より上側においてその上部20aの径が小さい。

【0046】

そして、ヴィアプラグ20の上部20aは、シリコン窒化膜8の下面高さから上面高さにかけて横断面積が縮小するように形成されている。このヴィアプラグ20の上側面上には配線層13が接触形成されている。したがって、前述実施形態の構造と比較して上部20aとビット線BLの配線層13との距離は拡大し、当該上部20aと配線層13との容量低減を図ることができる。

【0047】

また、本実施形態の構造においても、複数の配線層13間に比誘電率の高いシリコン窒化膜8がほとんど形成されない構造となる。このため、配線層13とヴィアプラグ10との間の容量を低減することで時定数を小さくすることができ、配線層13を通じて伝達する信号の伝搬遅延を極力抑制できる。

【0048】

前記した構造の製造工程について図12ないし図15を参照しながら説明する。本実施形態においてはヴィアプラグ20の製造工程を中心に説明し、その他の部分の説明を省略する。図12に示すように、シリコン酸化膜4およびコンタクトプラグ6の上面上にシリコン酸化膜7をCVD法により堆積した後、当該シリコン酸化膜7にRIE法などの異方性エッチングによってヴィアホール9を形成し、当該ヴィアホール9の内面に沿って窒化チタン(TiN)などのバリアメタルを形成し、その後、バリアメタルの内側にタングステン(W)などの埋込材を埋込むことでヴィアプラグ20を形成し、CMP法により平坦化する。

【0049】

次に、図13に示すように、シリコン酸化膜7の上部をエッチバックすることでヴィアプラグ20の上部10aの側面を露出させる。

次に、図14に示すように、ヴィアプラグ20の上部20aの側面をスリミング処理しヴィアプラグ20の上部20aの径を縮小させる。このスリミング処理を行うときには、例えばRIE法による異方性エッチングを行った後、例えばCDE(Chemical Dry Etching)法による等方性エッチングによりスリミングすると良い。

【0050】

次に、図15に示すように、シリコン窒化膜8をプラズマCVD法により堆積し、当該シリコン窒化膜8を全面エッチバックすることで、ヴィアプラグ20の上部20aの上面を露出させる。なお、全面エッチバックに代えてシリコン窒化膜8の上面をストッパとしてCMP法により平坦化することでヴィアプラグ20の上部20aの上面を露出させるようにしても良い。

【0051】

次に、図11に示すように、ヴィアプラグ20およびシリコン窒化膜8の上面上にシリコン酸化膜11をCVD法により堆積し、当該シリコン酸化膜11に溝12を形成した後、当該溝12内に配線層13を形成するが、この工程は前述実施形態と同様であるため説明を省略する。

【0052】

このような多層配線構造を採用すると、例えばリソグラフィ技術によりレジストマスクの合わせずれが生じた場合、複数のビット線BLの配線層13の全体がヴィアプラグ20の直上からX方向にずれて形成されることもある。

【0053】

この場合、配線層13と隣接するヴィアプラグ20との間の距離が耐圧に影響を及ぼす。本実施形態では、ヴィアプラグ20の上部20aの側面をスリミングしているため、ヴィアプラグ20と当該ヴィアプラグ20の直脇に隣接する配線層13との間の距離を長くできる。これにより、所望の耐圧特性を得られる。

【0054】

また、本実施形態によれば、次に示す特徴的な製造工程を備える。すなわち、シリコン酸化膜7にヴィアホール9を形成し、当該ヴィアホール9内にヴィアプラグ20を形成する。ヴィアプラグ20(の上部20a)の上面より下方にシリコン酸化膜7の上面が位置するようにシリコン酸化膜7の上部を除去することでヴィアプラグ20の上部20aの側面を露出させる。ヴィアプラグ20の上部20aの側面をスリミングする。スリミングしたヴィアプラグ20の上部20aの側面の脇の複数の上部20a間にシリコン窒化膜8を形成する。ヴィアプラグ20の上部20aに接触するように配線層13を形成する。このような製造工程を適用することで、前述実施形態と同様の作用効果を奏する。

【0055】

(第3の実施形態)

図16ないし図21は、第3の実施形態を示している。本実施形態が前述第2の実施形態と異なるところは、エッチングストッパ膜がヴィアプラグの上面上に沿って形成されているところにある。前述実施形態と同一または類似材料および同一または類似機能を奏する部分については同一符号を付して説明を省略し、以下、異なる部分について説明する。

【0056】

図16に示すように、ヴィアプラグ20がシリコン酸化膜7に形成されたヴィアホール9内に埋込み形成されている。ヴィアプラグ20の上部20aの脇にはシリコン窒化膜8が形成されておらず、シリコン酸化膜7が形成されている。したがって、シリコン酸化膜7はヴィアプラグ20の全側面脇に構成される。

【0057】

シリコン窒化膜8は、シリコン酸化膜7の上面上に形成されており、シリコン酸化膜11がシリコン窒化膜8の上面上に形成されている。ヴィアプラグ20の上面は、シリコン窒化膜8の下面と略同一高さに位置している。シリコン窒化膜8およびシリコン酸化膜11には複数の溝12が形成されており、複数の溝12内にそれぞれ配線層13が形成されている。

【0058】

前記の構造の製造方法について図17ないし図21を参照しながら説明する。本実施形態でも同様にヴィアプラグ20の製造工程を中心に説明し、その他の部分の説明を省略する。

図17に示すように、シリコン酸化膜4およびコンタクトプラグ6の上面上にシリコン酸化膜7を堆積した後、当該シリコン酸化膜7にRIE法などの異方性エッチングによりヴィアホール9を形成し、当該ヴィアホール9の内面に沿って窒化チタン(TiN)などのバリアメタルを形成し、その後、バリアメタルの内側にタングステン(W)などの埋込材を埋込むことでヴィアプラグ20を形成し、CMP法により平坦化する。次に、シリコン酸化膜7の上部をエッチバックすることで、シリコン酸化膜7の上面をヴィアプラグ20の上部20aの上面より下方に位置するように形成する。

【0059】

次に、図18に示すように、ヴィアプラグ20の上部20aをスリミングすることでヴィアプラグ20の上部20aの径を細らせる。このスリミング工程は前述実施形態に説明した方法と同様の方法で行われる。

【0060】

次に、図19に示すように、シリコン酸化膜7の上面上に当該シリコン酸化膜7と同質の膜となるシリコン酸化膜7aを再度プラズマCVD法により堆積することでヴィアプラグ20の上部20aの側脇に埋め戻す。そして、全面エッチバック処理することでヴィアプラグ20の上部20aの上面を露出させる。なお、全面エッチバック処理に代えてCMP法による平坦化を行うことでヴィアプラグ20の上部20aの上面を露出させても良い。

【0061】

次に、図20に示すように、シリコン酸化膜7および7a並びにヴィアプラグ20の上部20aの上面上にシリコン窒化膜8をプラズマCVD法により堆積し、続いてシリコン窒化膜8の上面上にシリコン酸化膜11をプラズマCVD法により堆積する。次に、図21に示すように、シリコン酸化膜11およびシリコン窒化膜8に溝12を形成し、図16に示すように、溝12内に配線層13を形成する。

【0062】

要するに、本実施形態によれば、次に示す特徴的な製造方法を備える。シリコン酸化膜7にヴィアホール9を形成し、当該ヴィアホール9内にヴィアプラグ20を形成する。ヴィアプラグ20の上部20aの上面より下方にシリコン酸化膜7の上面が位置するようにシリコン酸化膜7の上部を除去することでヴィアプラグ20の上部20aの側面を露出させる。ヴィアプラグ20の上部20aの側面をスリミングする。スリミングしたヴィアプラグ20の上部20aの側面の脇の複数の上部20a間にシリコン酸化膜7aを形成する。シリコン酸化膜7aおよびヴィアプラグ20の上部20aの上面上にシリコン窒化膜8を形成し、当該シリコン窒化膜8の上面上にシリコン酸化膜11を形成する。シリコン酸化膜11およびシリコン窒化膜8に溝12を形成する。溝12の内側に配線層13を形成する。このような製造工程を適用することで、前述実施形態と同様の作用効果を奏する。

【0063】

(他の実施形態)

前述実施形態に限定されるものではなく、例えば、以下に示す変形または拡張が可能である。

コンタクトプラグ6、ヴィアプラグ10および20は、共にバリアメタル膜とタングステン膜とで形成した場合を示したが、銅などの他の導電性材料を用いても良い。さらには、不純物を高濃度でドープした多結晶シリコンを導電性材料として用いることもできる。

【0064】

ヴィアホール9について順テーパを有する形状に加工した例で示したが、必ずしも順テーパを有する形状に形成する必要はない。ビット線コンタクトCBの場合で説明したが、ソース線コンタクトCSのコンタクトプラグについても同様にして適用できる。

NAND型フラッシュメモリ装置に限らず、NOR型フラッシュメモリ装置あるいは他のコンタクトプラグおよびヴィアプラグを有する構成の半導体装置全般に適用することができる。

【0065】

本発明のいくつかの実施形態を説明したが、各実施形態に示した構成、各種条件に限定されることはなく、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

【符号の説明】

【0066】

図面中、1は半導体基板、2は素子分離領域、3は活性領域、4はシリコン酸化膜、5はコンタクトホール、6はコンタクトプラグ、CBa、CBbはビット線コンタクト、7はシリコン酸化膜(第1絶縁膜、第1層間絶縁膜)、8はシリコン窒化膜(第2絶縁膜、エッチングストッパ膜)、9はヴィアホール(ホール)、10、20はヴィアプラグ(縦柱状プラグ)、V1a、V1bはビット線ヴィアプラグ、11はシリコン酸化膜(第3絶縁膜、第2層間絶縁膜)、12は溝、13は配線層(配線部)、20aはヴィアプラグの上部を示す。

【技術分野】

【0001】

本発明の実施形態は、半導体装置およびその製造方法に関する。

【背景技術】

【0002】

半導体装置は、素子の微細化、集積化が進められるに従い、各種電気的配線の配線幅やピッチも小さくなってきている。これに伴い、各種プラグの径やその間隔も狭くなってきている。プラグが近接すると隣接プラグ間の容量値が増加し、さらにその上の溝内に配線部が形成されていると、当該配線部に信号が伝達する際の伝播遅延が生じやすくなる。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開平11−74345号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

配線部を通じて伝達する信号の伝搬遅延を極力抑制できるようにした半導体装置およびその製造方法を提供する。

【課題を解決するための手段】

【0005】

実施形態に係る半導体装置は、半導体基板上に形成された第1絶縁膜を備える。また、第1絶縁膜上に形成された第1絶縁膜より比誘電率が高い第2絶縁膜を備える。また、第2絶縁膜と隣接する側面が順テーパ形状を有し第1絶縁膜および第2絶縁膜を貫通して形成された複数の縦柱状プラグを備える。また、第2絶縁膜上に形成された第2絶縁膜よりも比誘電率が低い第3絶縁膜を備える。また、複数の縦柱状プラグの上部にそれぞれ到達するように第3絶縁膜に形成された複数の溝を備えると共に、複数の溝内にそれぞれ形成され複数の縦柱状プラグの上部に一部がそれぞれ接触する金属からなる複数の配線部を備える。

【0006】

実施形態に係る半導体装置は、半導体基板上に形成された第1絶縁膜を備える。また、第1絶縁膜上に形成され当該第1絶縁膜よりも比誘電率が高い第2絶縁膜を備える。また、第1絶縁膜に貫通形成されその上面が第2絶縁膜の下面と略同一高さにある複数の縦柱状プラグを備える。また、第2絶縁膜上に形成され第2絶縁膜よりも比誘電率が低い第3絶縁膜を備える。また、複数の縦柱状プラグの上部にそれぞれ到達するように第2絶縁膜および第3絶縁膜に形成された複数の溝を備えると共に、複数の溝内にそれぞれ形成され複数の縦柱状プラグの上部に一部がそれぞれ接触する金属からなる複数の配線部を備える。そして、縦柱状プラグは、その上部が前記第1絶縁膜と隣接する側面に順テーパ形状を有している。

【0007】

実施形態に係る半導体装置の製造方法は、第1層間絶縁膜に形成された複数のホール内にそれぞれ縦柱状プラグを形成する工程を備える。また、第1層間絶縁膜の上部を除去して形成された複数の縦柱状プラグの上部側面を露出させる工程を備える。また、露出した縦柱状プラグの上部側面をスリミングする工程を備える。また、複数の縦柱状プラグの上部側面間にエッチングストッパ膜を形成する工程を備える。また、エッチングストッパ膜上に当該エッチングストッパ膜とエッチング選択性を有する第2層間絶縁膜を形成する工程を備える。また、第2層間絶縁膜にエッチングストッパ膜の上面上に至るまで複数の縦柱状プラグにそれぞれ達する複数の溝を形成する工程を備える。また、複数の縦柱状プラグの上部とそれぞれ接触する複数の配線部を複数の溝内にそれぞれ形成する工程を備える。

【図面の簡単な説明】

【0008】

【図1】第1の実施形態についてフラッシュメモリ装置のメモリセル領域の電気的構成の一部を示す回路図

【図2】メモリセル領域の一部の下層部分における平面レイアウトパターンを模式的に示す図

【図3】メモリセル領域の一部の特にビット線コンタクトの上層配線構造の平面レイアウトパターンを模式的に示す図

【図4】図2の切断線A−A線で示す部分を模式的に表す縦断側面図

【図5】製造工程の一段階における図4に対応する部分を模式的に示す縦断面図(その1)

【図6】製造工程の一段階における図4に対応する部分を模式的に示す縦断面図(その2)

【図7】製造工程の一段階における図4に対応する部分を模式的に示す縦断面図(その3)

【図8】製造工程の一段階における図4に対応する部分を模式的に示す縦断面図(その4)

【図9】製造工程の一段階における図4に対応する部分を模式的に示す縦断面図(その5)

【図10】製造工程の一段階における図4に対応する部分を模式的に示す縦断面図(その6)

【図11】第2の実施形態について示す図4相当図

【図12】製造工程の一段階における図4に対応する部分を模式的に示す縦断面図(その7)

【図13】製造工程の一段階における図4に対応する部分を模式的に示す縦断面図(その8)

【図14】製造工程の一段階における図4に対応する部分を模式的に示す縦断面図(その9)

【図15】製造工程の一段階における図4に対応する部分を模式的に示す縦断面図(その10)

【図16】第3の実施形態について示す図4相当図

【図17】製造工程の一段階における図4に対応する部分を模式的に示す縦断面図(その11)

【図18】製造工程の一段階における図4に対応する部分を模式的に示す縦断面図(その12)

【図19】製造工程の一段階における図4に対応する部分を模式的に示す縦断面図(その13)

【図20】製造工程の一段階における図4に対応する部分を模式的に示す縦断面図(その14)

【図21】製造工程の一段階における図4に対応する部分を模式的に示す縦断面図(その15)

【発明を実施するための形態】

【0009】

(第1の実施形態)

以下、本発明をNAND型フラッシュメモリ装置に適用した場合の第1の実施形態について図1ないし図10を参照しながら説明する。なお、以下の図面の記載において、同一又は類似の部分には同一又は類似の符号で表している。但し、図面は模式的なものであり、厚みと平面寸法との関係、各層の厚みの比率等は現実のものとは異なる場合があることを留意する。

【0010】

先ず、本実施形態のNAND型フラッシュメモリ装置の構成を説明する。図1は、NAND型のフラッシュメモリ装置のメモリセル領域に形成されるメモリセルアレイの一部の等価回路図である。

【0011】

NAND型フラッシュメモリ装置のメモリセルアレイは、2個の選択ゲートトランジスタTrs1、Trs2と、当該選択ゲートトランジスタTrs1、Trs2間に直列接続された複数個(例えば64個:2のn乗個(nは正整数))のメモリセルトランジスタTrmとからなるNANDセルユニット(メモリユニット)Suが行列状に形成されることで構成されている。NANDセルユニットSu内において、複数個のメモリセルトランジスタTrmは隣接するもの同士でソース/ドレイン領域を共用して形成されている。

【0012】

図1中、X方向(ワード線方向に相当)に配列されたメモリセルトランジスタTrmは、ワード線(制御ゲート線)WLにより共通接続されている。また、図1中、X方向に配列された選択ゲートトランジスタTrs1は選択ゲート線SGL1で共通接続され、選択ゲートトランジスタTrs2は選択ゲート線SGL2で共通接続されている。選択ゲートトランジスタTrs1のドレイン領域にはビット線コンタクトCBが接続されている。このビット線コンタクトCBは図1中X方向に直交するY方向(ビット線方向に相当)に延びるビット線BLに接続されている。また、選択ゲートトランジスタTrs2はソース領域を介して図1中X方向に延びるソース線SLに接続されている。

【0013】

図2および図3は、メモリセル領域の一部のレイアウトパターンを平面図により示している。この図2は、主に半導体基板の表層部およびその直ぐ上層部分の構造を示している。また、図3は、当該該当部分のさらに上層部分の構造を示している。

【0014】

図2に示すように、半導体基板(例えばシリコン基板)1には、素子分離領域としてのSTI(shallow trench isolation)2が図2中Y方向に沿って形成されている。このSTI2はX方向に離間して複数形成されており、これにより活性領域3が図2中X方向に分離した状態に形成されている。メモリセルトランジスタのワード線WLが、活性領域3の延伸方向であるY方向に直交する図2中X方向に沿って形成されている。

【0015】

また、図2中X方向に沿って一対の選択ゲートトランジスタTrs1−Trs1の選択ゲート線SGL1,SGL1が形成されている。選択ゲート線SGL1−SGL1間の活性領域3上にはビット線コンタクトCBが千鳥状に配置されている。

【0016】

選択ゲート線SGL1と所定本数のワード線WLを存した位置に、上述同様にして、図2中X方向に沿って一対の選択ゲートトランジスタの選択ゲート線SGL2が形成されている。そして、一対の選択ゲート線SGL2間の活性領域3にはソース線コンタクトCSが千鳥状に配置されている。

【0017】

図4は、図2中の切断線A−Aで示す部分の縦断面図を模式的に示している。すなわち、図4は、ビット線コンタクトCBaとその上層のビット線ヴィアプラグV1aとを選択ゲート線SGL1の延伸方向に沿って切断した縦断面図を示している。

【0018】

この図4において、半導体基板(例えばシリコン基板)1は、その表層部が素子分離領域2によって活性領域3に分離形成されている。素子分離領域2は、半導体基板1の表層部に所定間隔で形成したトレンチ(素子分離溝)の内部にシリコン酸化膜などの絶縁膜を埋込み形成して構成されている。

【0019】

半導体基板1の上面上には、図示しないが前述した選択ゲートトランジスタTrs1、Trs2、メモリセルトランジスタTrmの各ゲート電極がゲート絶縁膜を介して積層形成されている。なお、図4に示した部分は、当該トランジスタTrs1、Trs2、Trmの各ゲート電極の積層構造が予め形成され、その後のエッチング処理により除去された部分を示している。

【0020】

図4において、半導体基板1の上面上には一対の選択ゲート線SGL1−SGL1間を埋めるようにシリコン酸化膜4が所定膜厚で形成されている。なお、一対の選択ゲート線SGL2−SGL2間においても同様であるため説明を省略している。

【0021】

このシリコン酸化膜4にはその上面から下面まで貫通するコンタクトホール5が形成されている。このコンタクトホール5は、半導体基板1の活性領域3を1個おきに露出させるように形成されており、半導体基板1にほぼ垂直な側面を有するように形成されている。

【0022】

なお、ビット線コンタクトCBaおよびCBbのコンタクトホール5は、図4に示す活性領域3の全てについて1つずつ千鳥状に形成されており、それぞれ縦方向に延伸形成されている。図4の断面では現れていないが、図2に示したビット線コンタクトCBbに対応する部分にも形成されている。このように平面的には千鳥状に配置されている理由は、素子の縮小化、設計ルールの縮小化に伴い、隣接コンタクトCBaおよびCBb間の間隔が狭くなってきているためであり、隣接コンタクトCBaおよびCBb間の距離を確保することで所望の特性を得るためである。

【0023】

コンタクトホール5内には、チタン/窒化チタン(Ti/TiN)などのバリアメタルを介してタングステン(W)などの導電性材料が埋め込まれており、コンタクトプラグ6がビット線コンタクトCBaとして形成されている。

【0024】

シリコン酸化膜4の上面上には、シリコン酸化膜7が第1絶縁膜、第1層間絶縁膜として所定膜厚で形成されている。また、シリコン酸化膜7の上面上にはエッチングストッパ膜、第2絶縁膜としてシリコン窒化膜8が構成されている。本実施形態では、第2絶縁膜としてシリコン窒化膜8を適用した実施形態を示すが、これに代えてシリコン窒化物を含有したシリコン炭窒化膜(SiCN)を適用しても良い。

【0025】

これらのシリコン酸化膜7およびシリコン窒化膜8には、コンタクトプラグ6の直上の位置にシリコン酸化膜7およびシリコン窒化膜8を上端から下端まで貫通するヴィアホール(ホールに相当)9が形成されている。

【0026】

ヴィアホール9はシリコン酸化膜7の下面からシリコン窒化膜8の上面にかけて横断面積が増加するよう側面が順テーパ状となるように形成されている。ヴィアホール9の内側には窒化チタン(TiN)などのバリアメタルを介してタングステン(W)などの導電性材料がヴィアプラグ10として埋込形成されている。

【0027】

これにより、ヴィアプラグ10がシリコン窒化膜8の上面からシリコン酸化膜7の下面にかけて柱状に貫通形成されている。このヴィアプラグ10はビット線ヴィアプラグV1aに対応し縦柱状プラグに相当する。なお、図4の断面では現れていないが、ヴィアプラグ10は、図2に示したビット線コンタクトCBbの直上の部分にもビット線ヴィアプラグV1bとして形成されている。ヴィアプラグ10の下端はコンタクトプラグ6の上端と接触する。

【0028】

シリコン窒化膜8の上面とヴィアプラグ10の上面とはほぼ面一に形成されている。これらのシリコン窒化膜8およびヴィアプラグ10の上面上にはシリコン酸化膜11が第3絶縁膜、第2層間絶縁膜として形成されている。シリコン窒化膜8とシリコン酸化膜11とは適切に条件を設定すれば選択的にエッチング可能な膜の関係にある。このシリコン酸化膜11にはビット線BL形成用の溝12が形成されており、当該溝12内に配線層(配線部に相当)13がビット線BLとして形成されている。

【0029】

この配線層13は、Y方向に延伸するビット線用の溝12内に埋込まれて形成されるものであり、当該溝12内には銅(Cu)などの導電性材料が埋め込まれている。このビット線BLの配線層13は、そのX方向の幅寸法がヴィアプラグ10の上面の径に対応する幅寸法で形成されている。これらの配線層13は図2中のY方向に沿って形成されている。

【0030】

本実施形態では、配線層13と当該配線層13に隣接するヴィアプラグ10との間にシリコン窒化膜8が形成されておらずシリコン酸化膜11が形成されている。シリコン酸化膜7および11は、シリコン窒化膜8(またはシリコン炭窒化膜)に比較して比誘電率が低い。

【0031】

したがって、本実施形態の構造によれば、シリコン窒化膜8が配線層13とヴィアプラグ10との間に形成された構造に比較して当該配線層13とヴィアプラグ10との間の容量を低減できる。また、シリコン窒化膜8が隣り合う配線層13間に形成されていないため、隣り合う配線層13間の容量を低減できる。信号の伝搬速度は抵抗および他配線との間の配線間容量に依存するが、配線層13とヴィアプラグ10との間の容量を低減することで時定数を小さくすることができ、配線層13を通じて伝達する信号の伝搬遅延を極力抑制できる。

【0032】

次に、前記した構造の製造工程について図5ないし図10を参照しながら説明する。なお、ここでは、ヴィアプラグ10およびビット線BLの配線層13の構造の製造工程を中心に説明し、コンタクトプラグ6の製造工程説明は簡略的に行う。

【0033】

製造方法の特徴部分を中心に説明するが、一般的な工程であれば付加しても良いし、前述実施形態にて説明した製造工程は必要に応じて入れ替えても良い。また、必要に応じて工程を省いても良い。

【0034】

図5に示すように、半導体基板1に素子分離領域2を形成することで活性領域3を分離し、その後、シリコン酸化膜4をCVD法により堆積し、当該シリコン酸化膜4をRIE(Reactive Ion Etching)等により異方性エッチングし、コンタクトホール5を形成し、当該コンタクトホール5内にコンタクトプラグ6を埋込む。

【0035】

この図5に示す工程では、一対の選択ゲート線SGL1間の活性領域3に対応して、図2に示したように、一対の選択ゲート線SGL1の何れかに近づいた位置となるように千鳥状にコンタクトホール5を形成する。

【0036】

また、コンタクトホール5を形成した後には、コンタクトホール5の内面に沿って導電性材料としてチタン/窒化チタンなどのバリアメタルを形成し、当該バリアメタルの内側にタングステン(W)を埋込む。この後、シリコン酸化膜4の上面上に堆積したタングステンをCMP(Chemical Mechanical Polishing)法により平坦化する。これにより図5に示す構造を形成できる。

【0037】

次に、図6に示すように、TEOSガスを用いたプラズマCVD法によりシリコン酸化膜7を堆積する。その後、シリコン酸化膜7の上面上にシリコン窒化膜8をプラズマCVD法により堆積する。

【0038】

次に、図7に示すように、シリコン窒化膜8の上面上にレジスト(図示せず)をパターニングし、当該パターニングされたレジストをマスクとしてシリコン窒化膜8をRIE法により異方性エッチングし、続いてシリコン酸化膜7をRIE法により異方性エッチングすることでヴィアホール9を形成する。

【0039】

次に、図8に示すように、ヴィアホール9の内面に沿って窒化チタン(TiN)などのバリアメタルを形成し当該バリアメタルを介して例えばタングステン(W)をヴィアホール9の内側に埋込み、シリコン窒化膜8をストッパとしてCMP法により平坦化することでヴィアプラグ10を形成する。

【0040】

次に、図9に示すように、ヴィアプラグ10およびシリコン窒化膜8の上面上にCVD法によりシリコン酸化膜11を堆積する。

次に、図10に示すように、シリコン酸化膜11の上面上にレジスト(図示せず)をパターニングし当該レジストをマスクとしてビット線BL用の溝12を形成する。この場合、シリコン窒化膜8に対して高選択性を有する条件によってシリコン酸化膜11を異方性エッチングすることで溝12を形成する。これにより、シリコン窒化膜8のほぼ上面位置で溝12形成の際にエッチングストップすることができ溝12の深さをほぼ一定に揃えることができる。次に、図4に示すように、当該ビット線BL用の溝12内に配線用導体として銅(Cu)を埋込み形成してビット線BL用の配線層13を形成する。ビット線BLの配線層13は、全てのコンタクトプラグ6(CBa、CBb)に対応して形成される。

【0041】

溝12の深さがほぼ一定の深さに形成されるため、配線層13が溝12内に埋め込まれたとしても、配線層13とヴィアプラグ10との間の距離をほぼ一定に保つことができる。したがって、配線層13およびヴィアプラグ10間の容量を一定に保持でき、複数の配線層13およびヴィアプラグ10を通じて伝達する信号の伝搬遅延時間もほぼ同一となる。これにより特性のばらつきを抑制できる。

【0042】

本実施形態の製造方法によれば、次に示す特徴的な工程を備える。すなわち、半導体基板1の上方にシリコン酸化膜7、シリコン窒化膜8を順次形成する。シリコン窒化膜8の上面からシリコン酸化膜7の下面にかけて貫通するヴィアホール9を形成する。当該ヴィアホール9内に導電性材料を埋込んでヴィアプラグ10を形成する。シリコン窒化膜8およびヴィアプラグ9の上面上にシリコン酸化膜11を形成する。シリコン窒化膜8をストッパとしてシリコン酸化膜11に溝12を形成する。溝12内にビット線BL用の配線層13を形成する。このような製造方法を適用することで、溝12の深さをほぼ一定の深さに揃えることができる。これにより、特性ばらつきを抑制できる。

【0043】

(第2の実施形態)

図11ないし図15は、第2の実施形態を示している。本実施形態が前述第1の実施形態と異なるところは、ヴィアプラグの上部が上面から半導体基板方向にかけて横断面積が増大するように(順テーパで)形成されているところにある。前述実施形態と同一または類似材料、同一または類似機能を奏する部分については同一符号を付して説明を省略し、以下、異なる部分について説明する。

【0044】

図11に示すように、ヴィアプラグ10に代わるヴィアプラグ20は、コンタクトプラグ6の上面上に形成されている。ヴィアプラグ20の下部20bはシリコン酸化膜7の上面高さから下面高さに至るまで横断面積が縮小するように(逆テーパで)構成されている。

【0045】

また、このヴィアプラグ20は、シリコン酸化膜7およびシリコン窒化膜8の界面を境界としてその上下で互いに径が異なる。ヴィアプラグ20は、シリコン酸化膜7およびシリコン窒化膜8の界面より下側においてその下部20bの径が大きく、当該界面より上側においてその上部20aの径が小さい。

【0046】

そして、ヴィアプラグ20の上部20aは、シリコン窒化膜8の下面高さから上面高さにかけて横断面積が縮小するように形成されている。このヴィアプラグ20の上側面上には配線層13が接触形成されている。したがって、前述実施形態の構造と比較して上部20aとビット線BLの配線層13との距離は拡大し、当該上部20aと配線層13との容量低減を図ることができる。

【0047】

また、本実施形態の構造においても、複数の配線層13間に比誘電率の高いシリコン窒化膜8がほとんど形成されない構造となる。このため、配線層13とヴィアプラグ10との間の容量を低減することで時定数を小さくすることができ、配線層13を通じて伝達する信号の伝搬遅延を極力抑制できる。

【0048】

前記した構造の製造工程について図12ないし図15を参照しながら説明する。本実施形態においてはヴィアプラグ20の製造工程を中心に説明し、その他の部分の説明を省略する。図12に示すように、シリコン酸化膜4およびコンタクトプラグ6の上面上にシリコン酸化膜7をCVD法により堆積した後、当該シリコン酸化膜7にRIE法などの異方性エッチングによってヴィアホール9を形成し、当該ヴィアホール9の内面に沿って窒化チタン(TiN)などのバリアメタルを形成し、その後、バリアメタルの内側にタングステン(W)などの埋込材を埋込むことでヴィアプラグ20を形成し、CMP法により平坦化する。

【0049】

次に、図13に示すように、シリコン酸化膜7の上部をエッチバックすることでヴィアプラグ20の上部10aの側面を露出させる。

次に、図14に示すように、ヴィアプラグ20の上部20aの側面をスリミング処理しヴィアプラグ20の上部20aの径を縮小させる。このスリミング処理を行うときには、例えばRIE法による異方性エッチングを行った後、例えばCDE(Chemical Dry Etching)法による等方性エッチングによりスリミングすると良い。

【0050】

次に、図15に示すように、シリコン窒化膜8をプラズマCVD法により堆積し、当該シリコン窒化膜8を全面エッチバックすることで、ヴィアプラグ20の上部20aの上面を露出させる。なお、全面エッチバックに代えてシリコン窒化膜8の上面をストッパとしてCMP法により平坦化することでヴィアプラグ20の上部20aの上面を露出させるようにしても良い。

【0051】

次に、図11に示すように、ヴィアプラグ20およびシリコン窒化膜8の上面上にシリコン酸化膜11をCVD法により堆積し、当該シリコン酸化膜11に溝12を形成した後、当該溝12内に配線層13を形成するが、この工程は前述実施形態と同様であるため説明を省略する。

【0052】

このような多層配線構造を採用すると、例えばリソグラフィ技術によりレジストマスクの合わせずれが生じた場合、複数のビット線BLの配線層13の全体がヴィアプラグ20の直上からX方向にずれて形成されることもある。

【0053】

この場合、配線層13と隣接するヴィアプラグ20との間の距離が耐圧に影響を及ぼす。本実施形態では、ヴィアプラグ20の上部20aの側面をスリミングしているため、ヴィアプラグ20と当該ヴィアプラグ20の直脇に隣接する配線層13との間の距離を長くできる。これにより、所望の耐圧特性を得られる。

【0054】

また、本実施形態によれば、次に示す特徴的な製造工程を備える。すなわち、シリコン酸化膜7にヴィアホール9を形成し、当該ヴィアホール9内にヴィアプラグ20を形成する。ヴィアプラグ20(の上部20a)の上面より下方にシリコン酸化膜7の上面が位置するようにシリコン酸化膜7の上部を除去することでヴィアプラグ20の上部20aの側面を露出させる。ヴィアプラグ20の上部20aの側面をスリミングする。スリミングしたヴィアプラグ20の上部20aの側面の脇の複数の上部20a間にシリコン窒化膜8を形成する。ヴィアプラグ20の上部20aに接触するように配線層13を形成する。このような製造工程を適用することで、前述実施形態と同様の作用効果を奏する。

【0055】

(第3の実施形態)

図16ないし図21は、第3の実施形態を示している。本実施形態が前述第2の実施形態と異なるところは、エッチングストッパ膜がヴィアプラグの上面上に沿って形成されているところにある。前述実施形態と同一または類似材料および同一または類似機能を奏する部分については同一符号を付して説明を省略し、以下、異なる部分について説明する。

【0056】

図16に示すように、ヴィアプラグ20がシリコン酸化膜7に形成されたヴィアホール9内に埋込み形成されている。ヴィアプラグ20の上部20aの脇にはシリコン窒化膜8が形成されておらず、シリコン酸化膜7が形成されている。したがって、シリコン酸化膜7はヴィアプラグ20の全側面脇に構成される。

【0057】

シリコン窒化膜8は、シリコン酸化膜7の上面上に形成されており、シリコン酸化膜11がシリコン窒化膜8の上面上に形成されている。ヴィアプラグ20の上面は、シリコン窒化膜8の下面と略同一高さに位置している。シリコン窒化膜8およびシリコン酸化膜11には複数の溝12が形成されており、複数の溝12内にそれぞれ配線層13が形成されている。

【0058】

前記の構造の製造方法について図17ないし図21を参照しながら説明する。本実施形態でも同様にヴィアプラグ20の製造工程を中心に説明し、その他の部分の説明を省略する。

図17に示すように、シリコン酸化膜4およびコンタクトプラグ6の上面上にシリコン酸化膜7を堆積した後、当該シリコン酸化膜7にRIE法などの異方性エッチングによりヴィアホール9を形成し、当該ヴィアホール9の内面に沿って窒化チタン(TiN)などのバリアメタルを形成し、その後、バリアメタルの内側にタングステン(W)などの埋込材を埋込むことでヴィアプラグ20を形成し、CMP法により平坦化する。次に、シリコン酸化膜7の上部をエッチバックすることで、シリコン酸化膜7の上面をヴィアプラグ20の上部20aの上面より下方に位置するように形成する。

【0059】

次に、図18に示すように、ヴィアプラグ20の上部20aをスリミングすることでヴィアプラグ20の上部20aの径を細らせる。このスリミング工程は前述実施形態に説明した方法と同様の方法で行われる。

【0060】

次に、図19に示すように、シリコン酸化膜7の上面上に当該シリコン酸化膜7と同質の膜となるシリコン酸化膜7aを再度プラズマCVD法により堆積することでヴィアプラグ20の上部20aの側脇に埋め戻す。そして、全面エッチバック処理することでヴィアプラグ20の上部20aの上面を露出させる。なお、全面エッチバック処理に代えてCMP法による平坦化を行うことでヴィアプラグ20の上部20aの上面を露出させても良い。

【0061】

次に、図20に示すように、シリコン酸化膜7および7a並びにヴィアプラグ20の上部20aの上面上にシリコン窒化膜8をプラズマCVD法により堆積し、続いてシリコン窒化膜8の上面上にシリコン酸化膜11をプラズマCVD法により堆積する。次に、図21に示すように、シリコン酸化膜11およびシリコン窒化膜8に溝12を形成し、図16に示すように、溝12内に配線層13を形成する。

【0062】

要するに、本実施形態によれば、次に示す特徴的な製造方法を備える。シリコン酸化膜7にヴィアホール9を形成し、当該ヴィアホール9内にヴィアプラグ20を形成する。ヴィアプラグ20の上部20aの上面より下方にシリコン酸化膜7の上面が位置するようにシリコン酸化膜7の上部を除去することでヴィアプラグ20の上部20aの側面を露出させる。ヴィアプラグ20の上部20aの側面をスリミングする。スリミングしたヴィアプラグ20の上部20aの側面の脇の複数の上部20a間にシリコン酸化膜7aを形成する。シリコン酸化膜7aおよびヴィアプラグ20の上部20aの上面上にシリコン窒化膜8を形成し、当該シリコン窒化膜8の上面上にシリコン酸化膜11を形成する。シリコン酸化膜11およびシリコン窒化膜8に溝12を形成する。溝12の内側に配線層13を形成する。このような製造工程を適用することで、前述実施形態と同様の作用効果を奏する。

【0063】

(他の実施形態)

前述実施形態に限定されるものではなく、例えば、以下に示す変形または拡張が可能である。

コンタクトプラグ6、ヴィアプラグ10および20は、共にバリアメタル膜とタングステン膜とで形成した場合を示したが、銅などの他の導電性材料を用いても良い。さらには、不純物を高濃度でドープした多結晶シリコンを導電性材料として用いることもできる。

【0064】

ヴィアホール9について順テーパを有する形状に加工した例で示したが、必ずしも順テーパを有する形状に形成する必要はない。ビット線コンタクトCBの場合で説明したが、ソース線コンタクトCSのコンタクトプラグについても同様にして適用できる。

NAND型フラッシュメモリ装置に限らず、NOR型フラッシュメモリ装置あるいは他のコンタクトプラグおよびヴィアプラグを有する構成の半導体装置全般に適用することができる。

【0065】

本発明のいくつかの実施形態を説明したが、各実施形態に示した構成、各種条件に限定されることはなく、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

【符号の説明】

【0066】

図面中、1は半導体基板、2は素子分離領域、3は活性領域、4はシリコン酸化膜、5はコンタクトホール、6はコンタクトプラグ、CBa、CBbはビット線コンタクト、7はシリコン酸化膜(第1絶縁膜、第1層間絶縁膜)、8はシリコン窒化膜(第2絶縁膜、エッチングストッパ膜)、9はヴィアホール(ホール)、10、20はヴィアプラグ(縦柱状プラグ)、V1a、V1bはビット線ヴィアプラグ、11はシリコン酸化膜(第3絶縁膜、第2層間絶縁膜)、12は溝、13は配線層(配線部)、20aはヴィアプラグの上部を示す。

【特許請求の範囲】

【請求項1】

半導体基板上に形成された第1絶縁膜と、

前記第1絶縁膜上に形成された、前記第1絶縁膜より比誘電率が高い第2絶縁膜と、

前記第2絶縁膜と隣接する側面が順テーパ形状を有し、前記第1絶縁膜および前記第2絶縁膜を貫通して形成された複数の縦柱状プラグと、

前記第2絶縁膜上に形成された、前記第2絶縁膜よりも比誘電率が低い第3絶縁膜と、

前記複数の縦柱状プラグの上部にそれぞれ到達するように前記第3絶縁膜に形成された複数の溝と、

前記複数の溝内にそれぞれ形成され、前記複数の縦柱状プラグの上部に一部がそれぞれ接触する金属からなる複数の配線部と、を備えたことを特徴とする半導体装置。

【請求項2】

前記第2絶縁膜は、シリコン窒化物を含むことを特徴とする請求項1記載の半導体装置。

【請求項3】

半導体基板上に形成された第1絶縁膜と、

前記第1絶縁膜上に形成された、当該第1絶縁膜よりも比誘電率が高い第2絶縁膜と、

前記第1絶縁膜に貫通形成され、その上面が前記第2絶縁膜の下面と略同一高さにある複数の縦柱状プラグと、

前記第2絶縁膜上に形成された、前記第2絶縁膜よりも比誘電率が低い第3絶縁膜と、 前記複数の縦柱状プラグの上部にそれぞれ到達するように前記第2絶縁膜および前記第3絶縁膜に形成された複数の溝と、

前記複数の溝内にそれぞれ形成され、前記複数の縦柱状プラグの上部に一部がそれぞれ接触する金属からなる複数の配線部と、を備え、

前記縦柱状プラグは、その上部が前記第1絶縁膜と隣接する側面に順テーパ形状を有していることを特徴とする半導体装置。

【請求項4】

第1層間絶縁膜に形成された複数のホール内にそれぞれ縦柱状プラグを形成する工程と、

前記第1層間絶縁膜の上部を除去して前記形成された複数の縦柱状プラグの上部側面を露出させる工程と、

前記露出した縦柱状プラグの上部側面をスリミングする工程と、

前記複数の縦柱状プラグの上部側面間にエッチングストッパ膜を形成する工程と、

前記エッチングストッパ膜上に当該エッチングストッパ膜とエッチング選択性を有する第2層間絶縁膜を形成する工程と、

前記第2層間絶縁膜に前記エッチングストッパ膜の上面上に至るまで前記複数の縦柱状プラグにそれぞれ達する複数の溝を形成する工程と、

前記複数の縦柱状プラグの上部とそれぞれ接触する複数の配線部を前記複数の溝内にそれぞれ形成する工程とを備えたことを特徴とする半導体装置の製造方法。

【請求項5】

前記縦柱状プラグの上部側面をスリミングする工程は、異方性エッチングを行った後、等方性エッチングを行うことを特徴とする請求項4記載の半導体装置の製造方法。

【請求項1】

半導体基板上に形成された第1絶縁膜と、

前記第1絶縁膜上に形成された、前記第1絶縁膜より比誘電率が高い第2絶縁膜と、

前記第2絶縁膜と隣接する側面が順テーパ形状を有し、前記第1絶縁膜および前記第2絶縁膜を貫通して形成された複数の縦柱状プラグと、

前記第2絶縁膜上に形成された、前記第2絶縁膜よりも比誘電率が低い第3絶縁膜と、

前記複数の縦柱状プラグの上部にそれぞれ到達するように前記第3絶縁膜に形成された複数の溝と、

前記複数の溝内にそれぞれ形成され、前記複数の縦柱状プラグの上部に一部がそれぞれ接触する金属からなる複数の配線部と、を備えたことを特徴とする半導体装置。

【請求項2】

前記第2絶縁膜は、シリコン窒化物を含むことを特徴とする請求項1記載の半導体装置。

【請求項3】

半導体基板上に形成された第1絶縁膜と、

前記第1絶縁膜上に形成された、当該第1絶縁膜よりも比誘電率が高い第2絶縁膜と、

前記第1絶縁膜に貫通形成され、その上面が前記第2絶縁膜の下面と略同一高さにある複数の縦柱状プラグと、

前記第2絶縁膜上に形成された、前記第2絶縁膜よりも比誘電率が低い第3絶縁膜と、 前記複数の縦柱状プラグの上部にそれぞれ到達するように前記第2絶縁膜および前記第3絶縁膜に形成された複数の溝と、

前記複数の溝内にそれぞれ形成され、前記複数の縦柱状プラグの上部に一部がそれぞれ接触する金属からなる複数の配線部と、を備え、

前記縦柱状プラグは、その上部が前記第1絶縁膜と隣接する側面に順テーパ形状を有していることを特徴とする半導体装置。

【請求項4】

第1層間絶縁膜に形成された複数のホール内にそれぞれ縦柱状プラグを形成する工程と、

前記第1層間絶縁膜の上部を除去して前記形成された複数の縦柱状プラグの上部側面を露出させる工程と、

前記露出した縦柱状プラグの上部側面をスリミングする工程と、

前記複数の縦柱状プラグの上部側面間にエッチングストッパ膜を形成する工程と、

前記エッチングストッパ膜上に当該エッチングストッパ膜とエッチング選択性を有する第2層間絶縁膜を形成する工程と、

前記第2層間絶縁膜に前記エッチングストッパ膜の上面上に至るまで前記複数の縦柱状プラグにそれぞれ達する複数の溝を形成する工程と、

前記複数の縦柱状プラグの上部とそれぞれ接触する複数の配線部を前記複数の溝内にそれぞれ形成する工程とを備えたことを特徴とする半導体装置の製造方法。

【請求項5】

前記縦柱状プラグの上部側面をスリミングする工程は、異方性エッチングを行った後、等方性エッチングを行うことを特徴とする請求項4記載の半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【公開番号】特開2012−199381(P2012−199381A)

【公開日】平成24年10月18日(2012.10.18)

【国際特許分類】

【出願番号】特願2011−62395(P2011−62395)

【出願日】平成23年3月22日(2011.3.22)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

【公開日】平成24年10月18日(2012.10.18)

【国際特許分類】

【出願日】平成23年3月22日(2011.3.22)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

[ Back to top ]