半導体装置およびその製造方法

【課題】信号速度の遅延を防止することができる半導体装置を提供する。

【解決手段】本実施形態の半導体装置は、基板上に成膜された第1の絶縁膜と、配線と、第2の絶縁膜とを持つ。前記配線は、前記第1の絶縁膜に互いに平行に所定間隔で形成されたトレンチを埋め込むように金属で形成される。前記第2の絶縁膜は、前記第1の絶縁膜と前記配線とを覆うように前記第1の絶縁膜よりも誘電率の高い材料で成膜される。前記配線間の領域における前記第2の絶縁膜の下面は、前記配線の上面の周縁を互いに結ぶ面に対して上方へ離隔している。

【解決手段】本実施形態の半導体装置は、基板上に成膜された第1の絶縁膜と、配線と、第2の絶縁膜とを持つ。前記配線は、前記第1の絶縁膜に互いに平行に所定間隔で形成されたトレンチを埋め込むように金属で形成される。前記第2の絶縁膜は、前記第1の絶縁膜と前記配線とを覆うように前記第1の絶縁膜よりも誘電率の高い材料で成膜される。前記配線間の領域における前記第2の絶縁膜の下面は、前記配線の上面の周縁を互いに結ぶ面に対して上方へ離隔している。

【発明の詳細な説明】

【技術分野】

【0001】

本発明の実施形態は、半導体装置およびその製造方法に関する。

【背景技術】

【0002】

従来、例えば半導体記憶装置のメモリセルの上方に金属材料を用いてビットラインを形成する場合、コンタミネーションを防止するため、ビットラインを覆うようにキャップ材を設けることがある。

【0003】

しかしながら、該キャップ材が、誘電率の高い材料、例えばシリコンナイトライドで成膜される場合は、ビットラインがシリコンナイトライド膜の高い容量の影響を受けやすくなる。半導体装置の微細化が今後更に進展すると、これに応じて配線信号速度の遅延が顕著になり製品不良が発生するおそれがあり、問題視されてきている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開平5−326501号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

本発明が解決しようとする課題は、信号速度の遅延を防止することができる半導体装置およびその製造方法を提供することにある。

【課題を解決するための手段】

【0006】

本実施形態の半導体装置は、基板上に成膜された第1の絶縁膜と、配線と、第2の絶縁膜とを持つ。前記配線は、前記第1の絶縁膜に互いに平行に所定間隔で形成されたトレンチを埋め込むように金属で形成される。前記第2の絶縁膜は、前記第1の絶縁膜と前記配線とを覆うように前記第1の絶縁膜よりも誘電率の高い材料で成膜される。前記配線間の領域における前記第2の絶縁膜の下面は、前記配線の上面の周縁を互いに結ぶ面に対して上方へ離隔している。

【図面の簡単な説明】

【0007】

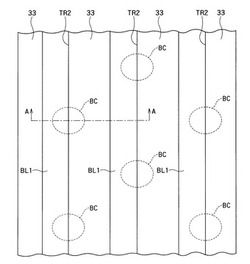

【図1】実施形態1の半導体装置の概略構造を示す平面図。

【図2】図1のA−A切断線による断面図。

【図3】実施形態2の半導体装置の断面図。

【図4A】実施形態1の半導体装置の製造方法を説明する断面図。

【図4B】実施形態1の半導体装置の製造方法を説明する断面図。

【図4C】実施形態1の半導体装置の製造方法を説明する断面図。

【図4D】実施形態1の半導体装置の製造方法を説明する断面図。

【図4E】実施形態1の半導体装置の製造方法を説明する断面図。

【図4F】実施形態1の半導体装置の製造方法を説明する断面図。

【図5】実施形態2の半導体装置の製造方法を説明する断面図。

【発明を実施するための形態】

【0008】

以下、実施形態のいくつかについて図面を参照しながら説明する。図面において、同一の部分には同一の参照符号を付してその重複説明は省略する。なお、本明細書において、「下方」という用語は基板に垂直な方向において基板の裏面側を表し、「上方」という用語は、基板に垂直な方向において裏面側とは逆の頂面側を表す。

【0009】

(1)半導体装置

図1は、実施形態1の半導体装置の概略構造を示す平面図である。図1に示す半導体装置は、基板S(図2参照)上に成膜された酸化膜33と、ビットラインBL1と、ビットラインコンタクトBCと、を備える。

ビットラインBL1は、酸化膜33に互いに平行に所定間隔で形成されたトレンチTR2を、薄い金属膜、例えばチタン(Ti)膜を介して金属、例えば銅(Cu)で埋め込むことにより形成される。本実施形態において、ビットラインBLは例えば配線に対応し、酸化膜33は例えば第1の絶縁膜に対応する。

ビットラインコンタクトBCは、ビットラインBL1に接続されるようにビットラインBL1の下方に形成される。本実施形態において、ビットラインBL1の下方には図示しない半導体素子、例えばMOSトランジスタやフラッシュメモリが形成され、ビットラインBL1は該半導体素子に接続される。

【0010】

図1において、ビットラインBL1の長手方向に直交するA−A線に沿った断面図を図2に示す。図2に示すように、本実施形態の半導体装置は、基板S上に形成された、酸化膜33およびビットラインBL1を覆うように成膜されたシリコンナイトライド膜46をさらに備える。シリコンナイトライド膜46は、ビットラインBL1を組成する金属が拡散してコンタミネーションをもたらすことを防止するためのキャップ層として機能する。なお、図2中、符号31で示す部材は、後述するとおり、トレンチTR2を形成する際にエッチングストッパ膜として機能するシリコンナイトライド膜である。以下、シリコンナイトライド膜31を第1のシリコンナイトライド膜、シリコンナイトライド膜46を第2のシリコンナイトライド膜という。第2のシリコンナイトライド膜46は、本実施形態において例えば第2の絶縁膜に対応する。なお、図1の平面図において第2のシリコンナイトライド膜46は省略されている。

【0011】

本実施形態の半導体装置の特徴は、酸化膜33が、隣り合うビットラインBL1の間の領域で段差を有するように形成され、この酸化膜33の形状に応じて第2のシリコンナイトライド膜47の下面が、隣り合うビットラインBL1の間の領域において、ビットラインBL1の上面の周縁を互いに結ぶ面SFに対して上方へ離隔するようにシリコンナイトライド膜47が成膜されている点にある。図2の断面形状において、シリコンナイトライド膜47の下面は、隣り合うビットラインBL1の間の領域においてアーチをなすような形状を有する。

【0012】

図3は、実施形態2を示す断面図である。実施形態2の略示平面図は、図1と同様であり、図3は、図2の断面図と同様に、図1のA−A切断線に対応する断面図である。

【0013】

実施形態2の半導体装置の特徴点は、ビットラインBL2とシリコンナイトライド膜47の形状にある。まず、ビットラインBL2は、その上面においてその中心部分が周縁部分よりも窪んでいる。次に、酸化膜34は、図3の断面図において隣り合うビットラインBLの間の領域でほぼ逆V字の形状をなすように形成され、この形状に応じて第2のシリコンナイトライド膜47も、隣り合うビットラインBLの間の領域においてその下面がほぼ逆V字の形状をなすように形成されている。

【0014】

このように、以上述べた第1および第2の実施形態の半導体装置によれば、第2のシリコンナイトライド膜46,47の下面が、隣り合うビットラインBL1間,BL2間の領域で、各ビットラインBL1,BL2の上面の周縁を互いに結ぶ面SFに対して上方へ離隔するように、誘電率の高いシリコンナイトライド膜46,47が成膜されているので、ビットラインBL1,BL2における信号速度の遅延を防止することが可能になる。これにより、より一層の微細化の進展に対応した高い信頼性を有する半導体装置が提供される。

【0015】

(2)半導体装置の製造方法

上述した実施形態の半導体装置は、以下に説明する製造方法により実施可能である。

【0016】

図4A乃至図4Fは、実施形態1の半導体装置の製造方法を説明する断面図である。

【0017】

まず、プラズマCVD(Plasma Chemical Vapour Deposition)法により、基板S上に約220nmの厚さでシリコン酸化膜11を成膜し、光蝕刻技術を用いてフォトレジスト(図示せず)を所望のパタ−ンに加工し、これをマスクとしてリアクティブイオンエッチング(Reactive Ion Etching)法でシリコン酸化膜11を選択的に除去することにより、溝パターンTR1(図4A参照)を形成する。

【0018】

次いで、O2プラズマでレジストマスク(図示せず)を除去し、70℃、5分間のコリン処理で自然酸化膜を除去した後、PVD(Physical Vapour Deposition)法により、6nmの窒化チタン(TiN)膜21、250nmのタングステン(W)膜22を順次に成膜し、その後、CMP(Chemical Mechanical Polishing)法により、シリコン酸化膜11が露出するまで窒化チタン(TiN)膜21とタングステン(W)膜22とを除去する。続いて、シリコン酸化膜11を約100nmだけ削り込んで平坦化させることにより、図4Aに示すように、コンタクトプラグBCを形成する。

【0019】

次に、図4Bに示すように、プラズマCVD法で約20nmの第1のシリコンナイトライド膜31、80nm以上のシリコン酸化膜33を順次に成膜する。

【0020】

続いて、フォトレジスト(図示せず)を塗布した後、光蝕刻技術によりフォトレジスト(図示せず)を所望のパタ−ンに加工し、これをマスクとしてRIE法でシリコン酸化膜33および第1のシリコンナイトライド膜31を選択的に除去し、さらに、第1のシリコンナイトライド膜31をエッチングストッパ膜として使用することによってシリコン酸化膜11を約5nmだけ削り込むように加工し、その後、O2プラズマでレジストを除去することにより、図4Cに示すように、トレンチTR2を形成する。

【0021】

次に、70℃、5分間のコリン処理でビットラインコンタクトBC上の自然酸化膜を除去した後、PVD法により8nmのTi膜35、15nmのCu膜37を順次に成膜した後、図4Dに示すように、メッキ法によりCu膜37、Ti膜35、および酸化膜33を覆うように450nmのCu膜39をさらに推積し、水素を含む150℃の窒素性雰囲気で30分間加熱することにより、Cu膜中での欠陥の発生を抑制する。

【0022】

次に、図4Eに示すように、CMP法によりシリコン酸化膜33が露出するまで、Cu膜39,37、Ti膜35を除去する。このときの除去量は、シリコン酸化膜33の上面の位置が、狙いとする第2のシリコンナイトライド膜46の下面中でビットラインBL間の最も高い位置(図2の符号SM参照)に対応するように設定する。

【0023】

次いで、図4Fに示すように、常温または70℃の塩酸を用い、シリコン酸化膜33に対する高い選択比でのWet法により、Cu膜37およびTi膜35を5分間エッチングして後退させることにより、ビットラインBL1を形成する。この工程により、シリコン酸化膜33は、前記ビットラインBL1間の領域において、ビットラインBL1の上面の周縁を互いに結ぶ面SFから上方へ隆起する段差を有する形状となる。

【0024】

その後は、プラズマCVD法によりシリコン酸化膜33およびビットラインBLを覆うように、約50nmのシリコンナイトライド膜46を推積させることにより、図2に示す半導体装置が製造される。

【0025】

次に、図4A乃至4Eに加えて図5を参照しながら、実施形態2の半導体装置の製造方法について説明する。

【0026】

ビットラインコンタクトBCの形成、第1のシリコンナイトライド膜31の成膜、並びに、シリコン酸化膜34、Ti膜36、Cu膜38(図5参照)の各成膜、更なるCu膜の成膜およびCMP法による除去までの工程は、図4A乃至4Eを参照して説明した実施形態1と同様である。

【0027】

本実施形態の特徴は、Cu膜38およびTi膜36を後退させるために、シリコン酸化膜34に対して高選択比の条件でRIE法によりCu膜38およびTi膜36をエッチング除去する点にある。その結果、図5に示すように、ビットラインBL2の上面は、その中心部分が周縁部分よりも窪んだ形状となり、ビットラインBL間2の領域におけるシリコン酸化膜34の段差もより急峻な側面形状となり、断面視においてほぼ逆V字の形状となる。そして、プラズマCVD法によりシリコン酸化膜34、ビットラインBL2を覆うように、約50nmのシリコンナイトライド膜47を推積させることにより、図3に示す半導体装置が製造される。

【0028】

このように、以上述べた第1および第2の実施形態の半導体装置の製造方法によれば、ビットラインBL1,BL2における信号速度の遅延を防止できる半導体装置を簡易なプロセスで製造することができる。

【0029】

以上、本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。上述の実施形態やその変形は、発明の範囲や要旨に含まれると同様に、特許請求の範囲に記載された発明とその均等の範囲に含まれるものである。

【符号の説明】

【0030】

33,34:シリコン酸化膜

46,47:第2のシリコンナイトライド膜

BC:ビットラインコンタクト

BL1,BL2:ビットライン

S:基板

SF:ビットラインの上面の周縁を互いに結ぶ面

SM:第2のシリコンナイトライド膜の下面中最も高い位置

TR1,TR2:トレンチ

【技術分野】

【0001】

本発明の実施形態は、半導体装置およびその製造方法に関する。

【背景技術】

【0002】

従来、例えば半導体記憶装置のメモリセルの上方に金属材料を用いてビットラインを形成する場合、コンタミネーションを防止するため、ビットラインを覆うようにキャップ材を設けることがある。

【0003】

しかしながら、該キャップ材が、誘電率の高い材料、例えばシリコンナイトライドで成膜される場合は、ビットラインがシリコンナイトライド膜の高い容量の影響を受けやすくなる。半導体装置の微細化が今後更に進展すると、これに応じて配線信号速度の遅延が顕著になり製品不良が発生するおそれがあり、問題視されてきている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開平5−326501号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

本発明が解決しようとする課題は、信号速度の遅延を防止することができる半導体装置およびその製造方法を提供することにある。

【課題を解決するための手段】

【0006】

本実施形態の半導体装置は、基板上に成膜された第1の絶縁膜と、配線と、第2の絶縁膜とを持つ。前記配線は、前記第1の絶縁膜に互いに平行に所定間隔で形成されたトレンチを埋め込むように金属で形成される。前記第2の絶縁膜は、前記第1の絶縁膜と前記配線とを覆うように前記第1の絶縁膜よりも誘電率の高い材料で成膜される。前記配線間の領域における前記第2の絶縁膜の下面は、前記配線の上面の周縁を互いに結ぶ面に対して上方へ離隔している。

【図面の簡単な説明】

【0007】

【図1】実施形態1の半導体装置の概略構造を示す平面図。

【図2】図1のA−A切断線による断面図。

【図3】実施形態2の半導体装置の断面図。

【図4A】実施形態1の半導体装置の製造方法を説明する断面図。

【図4B】実施形態1の半導体装置の製造方法を説明する断面図。

【図4C】実施形態1の半導体装置の製造方法を説明する断面図。

【図4D】実施形態1の半導体装置の製造方法を説明する断面図。

【図4E】実施形態1の半導体装置の製造方法を説明する断面図。

【図4F】実施形態1の半導体装置の製造方法を説明する断面図。

【図5】実施形態2の半導体装置の製造方法を説明する断面図。

【発明を実施するための形態】

【0008】

以下、実施形態のいくつかについて図面を参照しながら説明する。図面において、同一の部分には同一の参照符号を付してその重複説明は省略する。なお、本明細書において、「下方」という用語は基板に垂直な方向において基板の裏面側を表し、「上方」という用語は、基板に垂直な方向において裏面側とは逆の頂面側を表す。

【0009】

(1)半導体装置

図1は、実施形態1の半導体装置の概略構造を示す平面図である。図1に示す半導体装置は、基板S(図2参照)上に成膜された酸化膜33と、ビットラインBL1と、ビットラインコンタクトBCと、を備える。

ビットラインBL1は、酸化膜33に互いに平行に所定間隔で形成されたトレンチTR2を、薄い金属膜、例えばチタン(Ti)膜を介して金属、例えば銅(Cu)で埋め込むことにより形成される。本実施形態において、ビットラインBLは例えば配線に対応し、酸化膜33は例えば第1の絶縁膜に対応する。

ビットラインコンタクトBCは、ビットラインBL1に接続されるようにビットラインBL1の下方に形成される。本実施形態において、ビットラインBL1の下方には図示しない半導体素子、例えばMOSトランジスタやフラッシュメモリが形成され、ビットラインBL1は該半導体素子に接続される。

【0010】

図1において、ビットラインBL1の長手方向に直交するA−A線に沿った断面図を図2に示す。図2に示すように、本実施形態の半導体装置は、基板S上に形成された、酸化膜33およびビットラインBL1を覆うように成膜されたシリコンナイトライド膜46をさらに備える。シリコンナイトライド膜46は、ビットラインBL1を組成する金属が拡散してコンタミネーションをもたらすことを防止するためのキャップ層として機能する。なお、図2中、符号31で示す部材は、後述するとおり、トレンチTR2を形成する際にエッチングストッパ膜として機能するシリコンナイトライド膜である。以下、シリコンナイトライド膜31を第1のシリコンナイトライド膜、シリコンナイトライド膜46を第2のシリコンナイトライド膜という。第2のシリコンナイトライド膜46は、本実施形態において例えば第2の絶縁膜に対応する。なお、図1の平面図において第2のシリコンナイトライド膜46は省略されている。

【0011】

本実施形態の半導体装置の特徴は、酸化膜33が、隣り合うビットラインBL1の間の領域で段差を有するように形成され、この酸化膜33の形状に応じて第2のシリコンナイトライド膜47の下面が、隣り合うビットラインBL1の間の領域において、ビットラインBL1の上面の周縁を互いに結ぶ面SFに対して上方へ離隔するようにシリコンナイトライド膜47が成膜されている点にある。図2の断面形状において、シリコンナイトライド膜47の下面は、隣り合うビットラインBL1の間の領域においてアーチをなすような形状を有する。

【0012】

図3は、実施形態2を示す断面図である。実施形態2の略示平面図は、図1と同様であり、図3は、図2の断面図と同様に、図1のA−A切断線に対応する断面図である。

【0013】

実施形態2の半導体装置の特徴点は、ビットラインBL2とシリコンナイトライド膜47の形状にある。まず、ビットラインBL2は、その上面においてその中心部分が周縁部分よりも窪んでいる。次に、酸化膜34は、図3の断面図において隣り合うビットラインBLの間の領域でほぼ逆V字の形状をなすように形成され、この形状に応じて第2のシリコンナイトライド膜47も、隣り合うビットラインBLの間の領域においてその下面がほぼ逆V字の形状をなすように形成されている。

【0014】

このように、以上述べた第1および第2の実施形態の半導体装置によれば、第2のシリコンナイトライド膜46,47の下面が、隣り合うビットラインBL1間,BL2間の領域で、各ビットラインBL1,BL2の上面の周縁を互いに結ぶ面SFに対して上方へ離隔するように、誘電率の高いシリコンナイトライド膜46,47が成膜されているので、ビットラインBL1,BL2における信号速度の遅延を防止することが可能になる。これにより、より一層の微細化の進展に対応した高い信頼性を有する半導体装置が提供される。

【0015】

(2)半導体装置の製造方法

上述した実施形態の半導体装置は、以下に説明する製造方法により実施可能である。

【0016】

図4A乃至図4Fは、実施形態1の半導体装置の製造方法を説明する断面図である。

【0017】

まず、プラズマCVD(Plasma Chemical Vapour Deposition)法により、基板S上に約220nmの厚さでシリコン酸化膜11を成膜し、光蝕刻技術を用いてフォトレジスト(図示せず)を所望のパタ−ンに加工し、これをマスクとしてリアクティブイオンエッチング(Reactive Ion Etching)法でシリコン酸化膜11を選択的に除去することにより、溝パターンTR1(図4A参照)を形成する。

【0018】

次いで、O2プラズマでレジストマスク(図示せず)を除去し、70℃、5分間のコリン処理で自然酸化膜を除去した後、PVD(Physical Vapour Deposition)法により、6nmの窒化チタン(TiN)膜21、250nmのタングステン(W)膜22を順次に成膜し、その後、CMP(Chemical Mechanical Polishing)法により、シリコン酸化膜11が露出するまで窒化チタン(TiN)膜21とタングステン(W)膜22とを除去する。続いて、シリコン酸化膜11を約100nmだけ削り込んで平坦化させることにより、図4Aに示すように、コンタクトプラグBCを形成する。

【0019】

次に、図4Bに示すように、プラズマCVD法で約20nmの第1のシリコンナイトライド膜31、80nm以上のシリコン酸化膜33を順次に成膜する。

【0020】

続いて、フォトレジスト(図示せず)を塗布した後、光蝕刻技術によりフォトレジスト(図示せず)を所望のパタ−ンに加工し、これをマスクとしてRIE法でシリコン酸化膜33および第1のシリコンナイトライド膜31を選択的に除去し、さらに、第1のシリコンナイトライド膜31をエッチングストッパ膜として使用することによってシリコン酸化膜11を約5nmだけ削り込むように加工し、その後、O2プラズマでレジストを除去することにより、図4Cに示すように、トレンチTR2を形成する。

【0021】

次に、70℃、5分間のコリン処理でビットラインコンタクトBC上の自然酸化膜を除去した後、PVD法により8nmのTi膜35、15nmのCu膜37を順次に成膜した後、図4Dに示すように、メッキ法によりCu膜37、Ti膜35、および酸化膜33を覆うように450nmのCu膜39をさらに推積し、水素を含む150℃の窒素性雰囲気で30分間加熱することにより、Cu膜中での欠陥の発生を抑制する。

【0022】

次に、図4Eに示すように、CMP法によりシリコン酸化膜33が露出するまで、Cu膜39,37、Ti膜35を除去する。このときの除去量は、シリコン酸化膜33の上面の位置が、狙いとする第2のシリコンナイトライド膜46の下面中でビットラインBL間の最も高い位置(図2の符号SM参照)に対応するように設定する。

【0023】

次いで、図4Fに示すように、常温または70℃の塩酸を用い、シリコン酸化膜33に対する高い選択比でのWet法により、Cu膜37およびTi膜35を5分間エッチングして後退させることにより、ビットラインBL1を形成する。この工程により、シリコン酸化膜33は、前記ビットラインBL1間の領域において、ビットラインBL1の上面の周縁を互いに結ぶ面SFから上方へ隆起する段差を有する形状となる。

【0024】

その後は、プラズマCVD法によりシリコン酸化膜33およびビットラインBLを覆うように、約50nmのシリコンナイトライド膜46を推積させることにより、図2に示す半導体装置が製造される。

【0025】

次に、図4A乃至4Eに加えて図5を参照しながら、実施形態2の半導体装置の製造方法について説明する。

【0026】

ビットラインコンタクトBCの形成、第1のシリコンナイトライド膜31の成膜、並びに、シリコン酸化膜34、Ti膜36、Cu膜38(図5参照)の各成膜、更なるCu膜の成膜およびCMP法による除去までの工程は、図4A乃至4Eを参照して説明した実施形態1と同様である。

【0027】

本実施形態の特徴は、Cu膜38およびTi膜36を後退させるために、シリコン酸化膜34に対して高選択比の条件でRIE法によりCu膜38およびTi膜36をエッチング除去する点にある。その結果、図5に示すように、ビットラインBL2の上面は、その中心部分が周縁部分よりも窪んだ形状となり、ビットラインBL間2の領域におけるシリコン酸化膜34の段差もより急峻な側面形状となり、断面視においてほぼ逆V字の形状となる。そして、プラズマCVD法によりシリコン酸化膜34、ビットラインBL2を覆うように、約50nmのシリコンナイトライド膜47を推積させることにより、図3に示す半導体装置が製造される。

【0028】

このように、以上述べた第1および第2の実施形態の半導体装置の製造方法によれば、ビットラインBL1,BL2における信号速度の遅延を防止できる半導体装置を簡易なプロセスで製造することができる。

【0029】

以上、本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。上述の実施形態やその変形は、発明の範囲や要旨に含まれると同様に、特許請求の範囲に記載された発明とその均等の範囲に含まれるものである。

【符号の説明】

【0030】

33,34:シリコン酸化膜

46,47:第2のシリコンナイトライド膜

BC:ビットラインコンタクト

BL1,BL2:ビットライン

S:基板

SF:ビットラインの上面の周縁を互いに結ぶ面

SM:第2のシリコンナイトライド膜の下面中最も高い位置

TR1,TR2:トレンチ

【特許請求の範囲】

【請求項1】

基板上に成膜された第1の絶縁膜と、

前記第1の絶縁膜に互いに平行に所定間隔で形成されたトレンチを埋め込むように金属で形成された配線と、

前記第1の絶縁膜と前記配線とを覆うように前記第1の絶縁膜よりも誘電率の高い材料で成膜された第2の絶縁膜と、

を備え、

前記配線間の領域における前記第2の絶縁膜の下面は、前記配線の上面の周縁を互いに結ぶ面に対して上方へ離隔し、

前記配線間の領域における前記第2の絶縁膜は、前記配線の長手方向に直交する方向に沿った断面視においてアーチ形状をなし、

前記配線の上面は、中心部分が周縁部分よりも窪んでいる、

半導体装置。

【請求項2】

基板上に成膜された第1の絶縁膜と、

前記第1の絶縁膜に互いに平行に所定間隔で形成されたトレンチを埋め込むように金属で形成された配線と、

前記第1の絶縁膜と前記配線とを覆うように前記第1の絶縁膜よりも誘電率の高い材料で成膜された第2の絶縁膜と、

を備え、

前記配線間の領域における前記第2の絶縁膜の下面は、前記配線の上面の周縁を互いに結ぶ面に対して上方へ離隔している、

半導体装置。

【請求項3】

前記配線間の領域における前記第2の絶縁膜は、前記配線の長手方向に直交する方向に沿った断面視においてアーチ形状をなす、

ことを特徴とする請求項2に記載の半導体装置。

【請求項4】

前記配線の上面は、中心部分が周縁部分よりも窪んでいる、

ことを特徴とする請求項2に記載の半導体装置。

【請求項5】

基板上に第1の絶縁膜を成膜する工程と、

前記第1の絶縁膜に互いに平行なトレンチを所定間隔で形成する工程と、

前記トレンチを金属で埋め込み配線を形成する工程と、

前記第1の絶縁膜に対して選択比の高い条件のエッチングにより前記配線を後退させる工程と、

前記第1の絶縁膜よりも誘電率の高い材料を用いて、前記第1の絶縁膜と前記後退した配線とを覆う第2の絶縁膜を成膜する工程と、

を備える半導体装置の製造方法。

【請求項6】

前記配線を形成する工程は、

前記第1の絶縁膜の上面が、前記第2の絶縁膜の下面のうちで最も高いと予定される位置に対応する位置に至るまで、前記トレンチを埋め込んだ金属と前記第1の絶縁膜とを削除する工程を含む、

ことを特徴とする請求項5に記載の半導体装置の製造方法。

【請求項1】

基板上に成膜された第1の絶縁膜と、

前記第1の絶縁膜に互いに平行に所定間隔で形成されたトレンチを埋め込むように金属で形成された配線と、

前記第1の絶縁膜と前記配線とを覆うように前記第1の絶縁膜よりも誘電率の高い材料で成膜された第2の絶縁膜と、

を備え、

前記配線間の領域における前記第2の絶縁膜の下面は、前記配線の上面の周縁を互いに結ぶ面に対して上方へ離隔し、

前記配線間の領域における前記第2の絶縁膜は、前記配線の長手方向に直交する方向に沿った断面視においてアーチ形状をなし、

前記配線の上面は、中心部分が周縁部分よりも窪んでいる、

半導体装置。

【請求項2】

基板上に成膜された第1の絶縁膜と、

前記第1の絶縁膜に互いに平行に所定間隔で形成されたトレンチを埋め込むように金属で形成された配線と、

前記第1の絶縁膜と前記配線とを覆うように前記第1の絶縁膜よりも誘電率の高い材料で成膜された第2の絶縁膜と、

を備え、

前記配線間の領域における前記第2の絶縁膜の下面は、前記配線の上面の周縁を互いに結ぶ面に対して上方へ離隔している、

半導体装置。

【請求項3】

前記配線間の領域における前記第2の絶縁膜は、前記配線の長手方向に直交する方向に沿った断面視においてアーチ形状をなす、

ことを特徴とする請求項2に記載の半導体装置。

【請求項4】

前記配線の上面は、中心部分が周縁部分よりも窪んでいる、

ことを特徴とする請求項2に記載の半導体装置。

【請求項5】

基板上に第1の絶縁膜を成膜する工程と、

前記第1の絶縁膜に互いに平行なトレンチを所定間隔で形成する工程と、

前記トレンチを金属で埋め込み配線を形成する工程と、

前記第1の絶縁膜に対して選択比の高い条件のエッチングにより前記配線を後退させる工程と、

前記第1の絶縁膜よりも誘電率の高い材料を用いて、前記第1の絶縁膜と前記後退した配線とを覆う第2の絶縁膜を成膜する工程と、

を備える半導体装置の製造方法。

【請求項6】

前記配線を形成する工程は、

前記第1の絶縁膜の上面が、前記第2の絶縁膜の下面のうちで最も高いと予定される位置に対応する位置に至るまで、前記トレンチを埋め込んだ金属と前記第1の絶縁膜とを削除する工程を含む、

ことを特徴とする請求項5に記載の半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4A】

【図4B】

【図4C】

【図4D】

【図4E】

【図4F】

【図5】

【図2】

【図3】

【図4A】

【図4B】

【図4C】

【図4D】

【図4E】

【図4F】

【図5】

【公開番号】特開2012−256671(P2012−256671A)

【公開日】平成24年12月27日(2012.12.27)

【国際特許分類】

【出願番号】特願2011−128111(P2011−128111)

【出願日】平成23年6月8日(2011.6.8)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

【公開日】平成24年12月27日(2012.12.27)

【国際特許分類】

【出願日】平成23年6月8日(2011.6.8)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

[ Back to top ]