半導体装置およびその製造方法

【課題】ダマシン構造を有するCu配線において、バリア膜の拡散防止機能を低下させずにCu配線内のCuの埋め込み性を改善し、半導体装置の歩留まりおよび信頼性を向上する。

【解決手段】ダマシン配線を有する半導体装置において、第2層間絶縁膜6に形成した配線溝G2およびビアホールV2のそれぞれの内壁にバリア膜としてTaN膜7およびCuと濡れ性の良いTiからなるTi膜8とを順に形成することにより、Ti膜8上に均一にCuシード膜9aを形成することを可能とする。これにより、Cuシード膜9aを電極として電界メッキ法によりCu膜9を形成した際に、配線溝G2およびビアホールV2内に空隙が形成されることを防ぐ。

【解決手段】ダマシン配線を有する半導体装置において、第2層間絶縁膜6に形成した配線溝G2およびビアホールV2のそれぞれの内壁にバリア膜としてTaN膜7およびCuと濡れ性の良いTiからなるTi膜8とを順に形成することにより、Ti膜8上に均一にCuシード膜9aを形成することを可能とする。これにより、Cuシード膜9aを電極として電界メッキ法によりCu膜9を形成した際に、配線溝G2およびビアホールV2内に空隙が形成されることを防ぐ。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置およびその製造方法に関し、特に、銅配線を有する半導体装置およびその製造方法に適用して有効な技術に関するものである。

【背景技術】

【0002】

先端のLSI(Large Scale Integration)において、半導体素子に所定の電位を供給する用途、または電気信号を伝達する用途などに用いられる配線の材料には、配線の低抵抗化を目的として、Al(アルミ)を主体とした合金材料(Al−Cu合金など)に代わり、Cu(銅)が広く用いられるようになってきている。銅の導入により、配線の形成工程においては、ドライエッチングを用いて直接配線材料を加工するのではなく、予め層間絶縁膜中に配線・ビアとなる溝やホールを形成し、その後配線材料(例えばCu(銅))を埋め込み、余分な部分の配線材料をCMP(Chemical Mechanical Polishing:化学的機械的研磨)法により取り除く、所謂ダマシン法が用いられる様になってきている。

【0003】

Cu配線構造では、Cu(銅)が層間絶縁膜に拡散することを防止するため、Cu配線の表面部分を全て拡散防止膜(バリア膜、シード膜)で覆う必要がある。通常、このバリア膜は、Cu配線の上面に対しては絶縁膜系のバリア材として、銅の拡散防止機能を有する絶縁膜であるライナー膜を用いる。このライナー膜はCu配線上部の層間絶縁膜の一部としても用いる。一方、Cu配線の側壁・底部に対しては金属系のバリア材(バリアメタル)からなるバリア膜を用いる。バリアメタルは配線用の溝またはビアホール内壁に成膜されるため、配線材料の一部として用いられることとなる。

【0004】

現在、バリアメタルとして広く用いられている材料は、Ta(タンタル)およびその化合物(例えばTaN)である。これは、一般的に、Ta(タンタル)を主とするバリア材料は銅の拡散に対して優れた防止性能を示すためである。

【0005】

特許文献1(特開2004−79802号公報)には、デュアルダマシン法により金属配線層を形成する場合に、バリア膜による金属配線層の抵抗上昇を抑える技術が開示されている。具体的には、有機SOG(Spin On Glass)膜からなる有機層間絶縁膜上に、配線となる金属膜を形成する際、有機層間絶縁膜と金属膜との界面に金属拡散防止用の炭化金属膜をバリア膜として形成する。これにより、抵抗が高いバリア膜の占める割合を少なくし、バリア膜に十分な金属拡散防止機能を持たせた状態で配線層の抵抗を低くすることができるとしている。

【0006】

ここでは、バリア膜の材料に、炭化金属膜としてTaC(炭化タンタル)を用いているが、Ti(チタン)またはTi(チタン)の窒化物をバリア膜の材料として用いても良いとしている。ただし、バリア膜に用いるTi膜の膜厚に関する記載はない。また、バリア膜に用いるTiN膜のTi(チタン)とN(窒素)の具体的な原子数の比率についての記載はない。また、バリア膜の材料としてTi酸化物を用いる旨の記載はない。

【0007】

特許文献2(特開2003−124313号公報)には、Cu(銅)を配線材料とする多層配線構造において、銅の拡散による汚染を防止する一方で、Cuビアにおける下層配線層との密着性を改善してコンタクト抵抗を低減する技術が開示されている。具体的には、デュアルダマシン法により層間絶縁膜間に形成されたCu配線層と、該層間絶縁膜に開口されたビアホール内に形成され、Cu配線層に接続されたCuビアとを備える半導体装置において、Cuビアの側面に層間絶縁膜と密着性のあるTaNバリア膜と、銅と密着性のあるTaバリア膜とを積層し、Cuビアの底面にTaバリア膜のみを形成するものである。これにより、Taバリア膜およびTaNバリア膜によってCuの拡散による汚染を防止し、銅と層間絶縁膜との密着性を高め、Cuビアの剥離を防止することができるとしている。また、Cuビアの底面とCu配線層との密着性を高め、CuビアとCu配線層との界面でのCu原子の移動を抑制し、エレクトロマイグレーション耐性または熱ストレス耐性を高め、コンタクト抵抗を低減することができるとしている。

【0008】

ここでは、バリア膜の材料としてTa(タンタル)およびTaN(窒化タンタル)を用いているが、Ti(チタン)およびTiN(窒化チタン)の組み合わせをバリア膜の材料として用いても良いとしている。ただし、バリア膜に用いるTi膜の膜厚に関する記載はない。また、バリア膜に用いるTiN膜のTi(チタン)とN(窒素)の具体的な原子数の比率についての記載はない。また、バリア膜の材料としてTi酸化物を用いる旨の記載はない。

【先行技術文献】

【特許文献】

【0009】

【特許文献1】特開2004−79802号公報

【特許文献2】特開2003−124313号公報

【発明の概要】

【発明が解決しようとする課題】

【0010】

前述したように、近年、Cu(銅)を含む配線を有するLSIなどの半導体装置では、Cuの拡散防止のためにTaを含むバリア膜をCu配線の側壁および底面に形成する方法が用いられるようになってきている。

【0011】

しかし、Ta(タンタル)を含むバリア膜は、バリア膜を構成する金属(バリアメタル)の材料として要求される拡散防止機能以外の特性、および量産に際し注目される材料コスト等の観点からは、必ずしも最良の材料とは言い難い面がある。例えば、Ta(タンタル)を含むバリア膜は銅との濡れ性が良くないため、絶縁膜に形成された配線溝内において、Ta(タンタル)を含むバリア膜を介して形成される配線材料である銅の埋め込み性が悪くなり、信頼性が低下する問題がある。

【0012】

ここで、前述したTa(タンタル)を含むバリア膜の問題点について、図25〜図28を用い、Ta(タンタル)およびTaN(窒化タンタル)をバリア膜として形成した場合のCu配線を例として説明する。図25は、Ta(タンタル)およびTaN(窒化タンタル)をバリア膜として形成した場合に、正常に形成されたCu配線の近傍を示す要部断面図である。図26〜図28は、それぞれTa(タンタル)およびTaN(窒化タンタル)をバリア膜として形成した場合の、デュアルダマシン配線の製造工程を示す要部断面図である。

【0013】

図25に示す半導体装置内において、Ta(タンタル)を主体とするバリアメタル材料を用いた配線は、ダマシン法により形成されている。すなわち、例として示す半導体装置は、絶縁膜If上の第1層間絶縁膜1およびストッパ絶縁膜Sfに形成された配線溝G1内にシングルダマシン法により形成された下層配線M1と、第1層間絶縁膜1上のライナー膜5および第2層間絶縁膜6に形成されたビアホールV2内および第2層間絶縁膜6に形成された配線溝G2内にデュアルダマシン法により埋め込まれ、下層配線M1と電気的に接続された上層配線M2とを有している。ビアホールV2は配線溝G1の底面において開口し、下層配線M1の上面に達する孔部である。

【0014】

下層配線M1は主にCu膜4からなり、Cu膜4と第1層間絶縁膜1との間にはTa(タンタル)からなるTa膜3aが形成され、Ta膜3aと第1層間絶縁膜1との間にはTaN(窒化タンタル)からなるTaN膜2aが形成されている。Cu膜4とTa膜3aとの間には、Cu(銅)からなるCuシード膜4aが形成されている。

【0015】

同様に、上層配線M2は主にCu膜9からなり、Cu膜9とライナー膜5および第2層間絶縁膜6との間にはTa(タンタル)からなるTa膜8aが形成され、Ta膜8aとライナー膜5および第2層間絶縁膜6との間にはTaN(窒化タンタル)からなるTaN膜7aが形成されている。また、Cu膜9とTa膜8aとの間には、Cu(銅)からなるCuシード膜9aが形成されている。下層配線M1は、下層配線M1の下部のコンタクトプラグCpを介して第1層間絶縁膜1よりも下層の半導体基板上に形成された半導体素子に電気的に接続されている。

【0016】

図25に示す断面図は、Ta膜8a、TaN膜7a、Cuシード膜9aおよびCu膜9がそれぞれ正常に形成されたCu配線を示している。このとき、Cu膜9内には空隙(ボイド)は形成されておらず、配線溝G2内およびビアホールV2内ではバリア膜およびCuシード膜9aを介して均一にCu膜9が埋め込まれている。

【0017】

しかし、バリア膜として使用されているTa膜3a、8aおよびTaN膜2a、7aはCuシード膜9aとの濡れ性が悪く、Cuシード膜9aは配線溝G2内およびビアホールV2内のTa膜8aの表面に均一に形成されない場合がある。

【0018】

ここで、バリア膜にTa(タンタル)を含む材料を用いた半導体装置の製造工程中の要部断面図を図26〜図28に示す。図26では、第1層間絶縁膜1の上面に下層配線M1を形成した後、第1層間絶縁膜1上にライナー膜5および第2層間絶縁膜6を形成し、ライナー膜5および第2層間絶縁膜6を貫通するビアホールV2を形成し、配線溝G2を形成した構造において、TaN膜7aを形成する工程を示している。

【0019】

図26に示すように、PVD(Physical Vapor Deposition)法によってTaN膜7aおよびTa膜8aを順次形成した後に、PVD法によってTa膜8aの表面にCuシード膜を堆積する。しかし、Ta(タンタル)とCu(銅)とは濡れ性が悪いため、Cuシード膜9bは配線溝G2内およびビアホールV2内のTa膜8aの表面において均一に延びず、複数の固まりとなって点在するように形成されやすい。

【0020】

このようにCuシード膜9bが配線溝G2内およびビアホールV2内において不連続に形成された場合、図26の工程の後にCuシード膜上に電界メッキ法によりCu膜を形成すると、図27に示すように、Cu膜9内に空隙(ボイド)11が形成されたり、図28に示すように、配線溝G2内およびビアホールV2内に空隙11が形成されることでCu膜9がビアホールV2内の底部にまで埋め込まれなくなるおそれがある。

【0021】

図27または図28に示した工程においてCu膜9を形成した後、CMP法によって第2層間絶縁膜6上に形成されたCu膜9、Cuシード膜9a、Ta膜8aおよびTaN膜7aを除去し、Cu膜9の上面の高さを第2層間絶縁膜6の上面の高さと揃え、主にCu膜9からなる上層配線を形成する。その後、第2層間絶縁膜6上および前記上層配線上にライナー膜(図示しない)および第3層間絶縁膜(図示しない)を形成し、前記上層配線の更に上層に配線が形成される。

【0022】

ここで、図27および図28で説明したようにCu膜9の埋め込み性が悪くなるのは、配線溝G2内およびビアホールV2内において不連続に形成されたCuシード膜を電極として、Cu膜9を電界メッキ法によって形成しているためである。すなわち、Cu膜9は、電界メッキ工程において電極となるCuシード膜9aの表面に形成されるため、通電しているCuシード膜9aと不連続に形成されているCuシード膜9bの表面にはCu膜9が形成されにくい。このため、図27および図28に示すように、配線溝G2内およびビアホールV2内に空隙11が形成されやすく、前記上層配線が途中で途切れたり、前記上層配線と下層配線M1とが電気的に接続されず、前記上層配線から下層配線M1に所定の電位を供給できなくなる可能性がある。

【0023】

また、Cu膜9を形成する電界メッキ工程において、Cuシード膜9aおよび9bから露出しているTa膜8aが通電して電極として機能したとしても、Cuシード膜9aの表面に比べてTa膜8aの表面ではCu膜9は形成されにくい。これは、Cu(銅)に比べて(タンタル)の抵抗値が高いためであり、これによって配線溝G2内およびビアホールV2内において形成されるCu膜9の膜厚が均一でなくなり、空隙11が形成されやすくなる。

【0024】

上記のように、Ta(タンタル)を配線のバリア膜に用いて半導体装置を製造すると、Cuシード膜との濡れ性に起因するCu配線の埋め込み性の悪化によって、半導体装置の歩留まりおよび信頼性が低下する。

【0025】

また、Ta(タンタル)自体が比較的高価な材料であるため、Ta(タンタル)を配線のバリア膜に用いて半導体装置を製造すると、製品のコストが増大する問題がある。

【0026】

以上のことから、本発明者らはTa(タンタル)に変わるバリアメタルとして、銅との濡れ性に優れているTi(チタン)を用いることを検討した。しかし、Ti(チタン)は銅と合金を形成しやすい性質を有しているため、バリア膜としてTi膜を形成した場合、Ti膜とCu膜との界面に純粋な銅よりも抵抗値が高いTi/Cu合金膜が形成され、Ti/Cu合金膜によって配線抵抗が上昇する問題がある。

【0027】

本発明の目的は、銅を含む配線を有する半導体装置において、銅配線の表面に形成されたバリア膜の拡散防止機能を低下させずに銅配線の埋め込み性を向上させることにある。

【0028】

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

【課題を解決するための手段】

【0029】

本願において開示される実施の形態のうち、代表的なものの概要を簡単に説明すれば、次のとおりである。

【0030】

本発明の好ましい一実施の形態である半導体装置は、

半導体基板上に形成された層間絶縁膜と、

前記層間絶縁膜に形成された配線溝と、

前記配線溝内に第1バリア膜を介して形成されたCuを主成分とする金属膜と、

を有し、

前記第1バリア膜は、Taを含む第3バリア膜と、前記第3バリア膜上に前記金属膜と接して形成されたTiを含む第2バリア膜とを有するものである。

【0031】

また、本発明の好ましい一実施の形態である半導体装置の製造方法は、

(a)半導体基板を準備する工程と、

(b)前記半導体基板上に層間絶縁膜を形成する工程と、

(c)前記層間絶縁膜の上面に配線溝を形成する工程と、

(d)前記配線溝内に第1バリア膜を形成する工程と、

(e)前記第1バリア膜の表面にCuを主成分とするシード膜を形成する工程と、

(f)前記シード膜を電極として電界メッキ法により前記シード膜上にCuを主成分とする金属膜を形成し、前記金属膜によって前記配線溝内を埋め込む工程と、

(g)前記半導体基板の上面を研磨して前記層間絶縁膜の上面を露出させ、前記配線溝内に前記第1バリア膜および前記金属膜を含む金属配線を形成する工程と、

を有し、

前記(d)工程では、前記配線溝内にTaを含む第2バリア膜を形成した後に、前記第2バリア膜上にTiまたはTi化合物からなる第3バリア膜を形成することにより、前記第2バリア膜および前記第3バリア膜を有する前記第1バリア膜を形成するものである。

【発明の効果】

【0032】

本願において開示される発明のうち、代表的なものによって得られる効果を簡単に説明すれば以下のとおりである。

【0033】

上記した本発明の好ましい一実施の形態によれば、銅を含む配線を有する半導体装置において、銅配線の表面に形成されたバリア膜の拡散防止機能を低下させずに銅配線の埋め込み性を向上させることができる。

【図面の簡単な説明】

【0034】

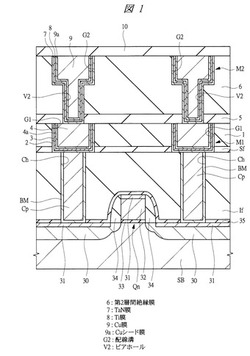

【図1】本発明の実施の形態1である半導体装置の要部断面図である。

【図2】本発明の実施の形態1である半導体装置の製造方法を示す要部断面図である。

【図3】図2に続く半導体装置の製造方法を示す要部断面図である。

【図4】図3に続く半導体装置の製造方法を示す断面図であって、図3の一部を拡大して示す要部断面図である。

【図5】図4に続く半導体装置の製造方法を示す要部断面図である。

【図6】図5に続く半導体装置の製造方法を示す要部断面図である。

【図7】図6に続く半導体装置の製造方法を示す要部断面図である。

【図8】図7に続く半導体装置の製造方法を示す要部断面図である。

【図9】図8に続く半導体装置の製造方法を示す要部断面図である。

【図10】図9の製造工程中の半導体装置を示す俯瞰図である。

【図11】図10に続く半導体装置の製造方法を示す要部断面図である。

【図12】図11の製造工程中の半導体装置を示す俯瞰図である。

【図13】図12に続く半導体装置の製造方法を示す要部断面図である。

【図14】図13に続く半導体装置の製造方法を示す要部断面図である。

【図15】図14に続く半導体装置の製造方法を示す要部断面図である。

【図16】数種類のバリア膜に対する、それらのバリア膜を用いた配線の抵抗値を示すグラフである。

【図17】本発明の実施の形態2である半導体装置の要部断面図である。

【図18】2種類のバリア膜に対する、それらのバリア膜を用いた配線の配線間耐圧を示すグラフである。

【図19】本発明の実施の形態3である半導体装置の要部断面図である。

【図20】本発明の実施の形態3である半導体装置の製造方法を示す要部断面図である。

【図21】図20に続く半導体装置の製造方法を示す要部断面図である。

【図22】図21に続く半導体装置の製造方法を示す要部断面図である。

【図23】図22に続く半導体装置の製造方法を示す要部断面図である。

【図24】図23に続く半導体装置の製造方法を示す要部断面図である。

【図25】比較例として示す半導体装置の要部断面図である。

【図26】比較例として示す半導体装置の製造方法を示す要部断面図である。

【図27】図26に続く半導体装置の製造方法を示す要部断面図である。

【図28】図26に続く半導体装置の製造方法を示す要部断面図である。

【発明を実施するための形態】

【0035】

以下、本発明の実施の形態を図面に基づいて詳細に説明する。なお、実施の形態を説明するための全図において、同一の機能を有する部材には同一の符号を付し、その繰り返しの説明は省略する。また、以下の実施の形態では、特に必要なときを除き、同一または同様な部分の説明を原則として繰り返さない。

【0036】

(実施の形態1)

本発明の実施の形態によるダマシン配線の構造の一例を図1を用いて説明する。図1は半導体基板上に電界効果トランジスであるMOSFET(Metal Oxide Semiconductor Field Effect Transistor)と、MOSFET上の層間絶縁膜に形成された金属配線とを含む半導体装置の一部を示す要部断面図である。

【0037】

図1に示すように本実施の形態の半導体装置は半導体基板SB上にMOSFETQnを形成したものである。半導体基板SB上にはゲート絶縁膜33を介してゲート電極32が形成され、ゲート電極32の下部の半導体基板SBの上面を挟むように、一対のソース・ドレイン領域30が半導体基板SBの上面に形成されている。ゲート電極32およびゲート絶縁膜33の側壁には絶縁膜からなるサイドウォール34が形成され、ソース・ドレイン領域30およびゲート電極32の上面にはそれぞれシリサイド層31が形成されている。

【0038】

MOSFETQnはストッパ絶縁膜35および絶縁膜Ifに覆われており、ストッパ絶縁膜35および絶縁膜Ifには、ソース・ドレイン領域30の上部のシリサイド層31の上面に達するコンタクトホールChが形成されている。コンタクトホールCh内の側壁および底面にはバリア膜BMが形成されており、コンタクトホールCh内には、バリア膜BMを介してコンタクトプラグCpが埋め込まれている。ここで、コンタクトプラグCp、バリア膜BMおよび絶縁膜Ifのそれぞれの上面は同一の高さを有している。

【0039】

絶縁膜If上にはストッパ絶縁膜Sfが形成され、ストッパ絶縁膜Sf上には第1層間絶縁膜1が形成されている。第1層間絶縁膜1およびストッパ絶縁膜Sfからなる絶縁層は、コンタクトプラグCp、バリア膜BMおよび絶縁膜Ifのそれぞれの上面に達する配線溝G1を有しており、配線溝G1内の側壁および底面にはTaN膜2が形成されている。すなわち、配線溝G1内において、第1層間絶縁膜1およびストッパ絶縁膜Sfの側壁並びにコンタクトプラグCp上、バリア膜BM上および絶縁膜If上にTaN膜2が形成されている。

【0040】

配線溝G1底部のTaN膜2上並びに、TaN膜2の側面であって第1層間絶縁膜1およびストッパ絶縁膜Sfと接していない方の側面にはTi膜3が形成されている。配線溝G1底部のTi膜3上並びに、Ti膜3の側面であってTaN膜2と接していない方の側面にはCuシード膜4aが形成されている。配線溝G1底部のCuシード膜4a上並びに、Cuシード膜4aの側面であってTi膜3と接していない方の側面にはCu膜4が形成されており、Cu膜4はTaN膜2、Ti膜3およびCuシード膜4aを介して配線溝G1内に埋め込まれている。

【0041】

すなわち、配線溝G1内に形成されたCu膜4と、第1層間絶縁膜1、ストッパ絶縁膜Sf、絶縁膜If、バリア膜BMおよびコンタクトプラグCpとの間には、Cu膜4側から順に、Cuシード膜4a、Ti膜3、TaN膜2が形成されている。なお、第1層間絶縁膜1、Cu膜4、並びに配線溝G1の側壁に形成されたTaN膜2、Ti膜3およびCuシード膜4aのそれぞれの上面は同一の高さを有している。なお、TaN膜2の膜厚は例えば5nm程度である。Ti膜3の膜厚は10nm未満の膜厚とし、例えば5nmとする。

【0042】

第1層間絶縁膜1上、Cu膜4上、並びに配線溝G1の側壁に形成されたTaN膜2上、Ti膜3上およびCuシード膜4a上にはライナー膜5が形成され、ライナー膜5上には第2層間絶縁膜6が形成されている。第2層間絶縁膜6は、第2層間絶縁膜6の途中深さまで達する配線溝G2を有しており、第2層間絶縁膜6およびライナー膜5からなる絶縁層は、配線溝G2の底面に開口され、Cu膜4の上面に達するビアホールV2を有している。

【0043】

配線溝G2内の側壁および底面並びにビアホールV2の側壁および底面には、TaN膜7が形成されている。すなわち、配線溝G2内およびビアホールV2内において、第1層間絶縁膜1およびライナー膜5の側壁並、配線溝G2の底部である第1層間絶縁膜1の上面上並びにビアホールV2の底面のCu膜4上に、TaN膜7が形成されている。配線溝G2底部およびビアホールV2底部のTaN膜7上並びに、TaN膜7の側面であって第2層間絶縁膜6およびライナー膜5と接していない方の側面にはTi膜8が形成されている。配線溝G2底部およびビアホールV2底部のTi膜8上並びに、Ti膜8の側面であってTaN膜7と接していない方の側面にはCuシード膜9aが形成されている。配線溝G2底部およびビアホールV2底部のCuシード膜9a上並びに、Cuシード膜9aの側面であってTi膜8と接していない方の側面にはCu膜9が形成されており、Cu膜9はTaN膜7、Ti膜8およびCuシード膜9aを介して配線溝G2内およびビアホールV2内に埋め込まれている。

【0044】

なお、本実施の形態では、Ti膜3および8の部材をTi(チタン)としているが、Ti膜3および8の部材には、TiN(窒化チタン)など、チタンを含む他のTi化合物を用いても良い。

【0045】

すなわち、配線溝G2内およびビアホールV2内に形成されたCu膜9と、第2層間絶縁膜6、ライナー膜5およびCu膜4との間には、Cu膜9側から順に、Cuシード膜9a、Ti膜8、TaN膜7が形成されている。なお、第2層間絶縁膜6、Cu膜9、並びに配線溝G2の側壁に形成されたTaN膜7、Ti膜8およびCuシード膜9aのそれぞれの上面は同一の高さを有している。

【0046】

また、第2層間絶縁膜6上、Cu膜9上、並びに配線溝G2の側壁に形成されたTaN膜7上、Ti膜8上およびCuシード膜9a上にはライナー膜10が形成されている。ソース・ドレイン領域30とCu膜9とは、Cuシード膜9a、Ti膜8、TaN膜7、Cu膜4、Cuシード膜4a、Ti膜3、TaN膜2、コンタクトプラグCpおよびシリサイド層31を介して電気的に接続されている。

【0047】

図1に示すMOSFETQnはn型のチャネル領域を有するnチャネル型MOSFETであり、例えば電気信号をスイッチングするスイッチング素子、または電気信号を増幅するための増幅素子として使用されるものである。半導体基板SBは例えばSi(シリコン)からなり、上面にp型の半導体領域を有している。ゲート絶縁膜33、サイドウォール34および絶縁膜Ifはそれぞれ例えばSiO2(酸化シリコン)からなる。ストッパ絶縁膜35は例えばSiN(窒化シリコン)からなり、コンタクトホールChをドライエッチによって開口する際、エッチングストッパ膜として機能するものである。ゲート電極32は例えばP(リン)またはAs(ヒ素)などのn型の不純物が導入された低抵抗のn型半導体膜(ドープトポリシリコン膜)であり、MOSFETQnのゲートとして機能するものである。ソース・ドレイン領域30はn型の不純物が導入されたn型半導体領域であり、MOSFETQnのソースまたはドレインとして機能するものである。

【0048】

シリサイド層31は、例えばNi(ニッケル)とSi(シリコン)の化合物であるNiSi(ニッケルシリサイド)からなり、W(タングステン)からなるコンタクトプラグCpとソース・ドレイン領域30とを電気的に接続している。バリア膜BMは例えばTiまたはTi化合物からなり、コンタクトプラグCp内のW(タングステン)が絶縁膜If内に拡散することを防ぐ機能を有する。ライナー膜5は例えばCVD(Chemical Vapor Deposition)法により形成されるSiC(炭化シリコン)からなる絶縁膜であるが、SiC以外の部材としては、SiN(窒化シリコン)、SiCN(炭窒化シリコン)またはSiOC(炭酸化シリコン)などを例示することができる。第1層間絶縁膜1および第2層間絶縁膜6はSiO2(酸化シリコン)よりも吸湿性が高く、水分を含みやすい絶縁膜により形成されており、例えば、第1層間絶縁膜1および第2層間絶縁膜6はそれぞれ主にSiOCからなる。

【0049】

TaN膜2は主にTaN(窒化タンタル、タンタルナイトライド)からなる導電性の金属膜であり、Cu膜4内のCu(銅)が第1層間絶縁膜1、ストッパ絶縁膜Sfまたは絶縁膜Ifなどに拡散することを防いでいる。また、Ti膜3は主にTi(チタン)からなる導電性の金属膜であり、Cu膜4内のCu(銅)が第1層間絶縁膜1、ストッパ絶縁膜Sfまたは絶縁膜Ifなどに拡散することを防いでいる。また、Ti膜3はCu(銅)との密着性が高く、Ti膜を形成することで配線溝G1内においてCuシード膜4aおよびCu膜4がTaN膜2およびTi膜3を介して隙間なく埋め込まれるようにしている。Cu膜4、9およびCuシード膜4a、9aは主にCu(銅)またはCu(銅)と他の金属(例えばAl(アルミニウム)、Si(シリコン)、Ge(ゲルマニウム)、Ga(ガリウム)またはSn(錫)など)との合金からなる導電膜であり、ソース・ドレイン領域30に所定の電位を供給する導電経路の一部である。

【0050】

ライナー膜5および10は、Cu膜4または9内のCu(銅)がCu膜4または9のそれぞれの上方に拡散することを防ぐ働きを有する。ライナー膜5および10は、それぞれSiN、SiC、SiCNおよびSiOCの内の少なくとも一つを主に含む絶縁膜である。

【0051】

TaN膜7はTaN膜2と同様に、主にTaN(窒化タンタル、タンタルナイトライド)からなる導電性の金属膜であり、Cu膜9内のCu(銅)が第2層間絶縁膜6などに拡散することを防いでいる。Ti膜8は主にTi(チタン)からなる導電性の金属膜であり、Ti膜3と同様にCu膜9内のCu(銅)が第2層間絶縁膜6などに拡散することを防いでいる。Ti膜3と同様に、Ti膜8は配線溝G1内におけるCuシード膜9aおよびCu膜9の埋め込み性を向上させている。

【0052】

次に本実施の形態の半導体装置の製造方法について、図2〜図15を用いて説明する。図2および図3はMOSFETQnを含む本実施の形態の半導体装置の要部断面図であり、図4〜図9、図11および図13〜図15は、図3に示すコンタクトプラグCpの上部を拡大して示す要部断面図である。また、図10および図12は、それぞれ図9および図11に示す領域のビアホールおよび配線溝を示す俯瞰図である。なお、本発明は金属配線に関する発明であり、MOSFET以外のダイオードまたはキャパシタなど他の半導体装置にも適応できるため、ここではMOSFETQnを形成する詳しい工程の説明は省略する。

【0053】

まず、図2に示すように、周知の技術を用いて半導体基板SBの上面にMOSFETQnを形成する。MOSFETQnは半導体基板SBの上面上にゲート絶縁膜33を介して形成されたゲート電極32と、半導体基板SBの上面に形成されたn型半導体領域であるソース・ドレイン領域30を有するものである。ゲート電極32の側壁には主に酸化シリコンからなるサイドウォール34が形成され、ゲート電極32およびソース・ドレイン領域30の上面にはそれぞれシリサイド層31が形成されている。

【0054】

次に、ゲート電極32、ソース・ドレイン領域30、サイドウォール34およびシリサイド層31を含む半導体基板SBの主面(全面)を覆うようにストッパ絶縁膜35を形成する。ストッパ絶縁膜35は例えば窒化シリコン膜からなり、成膜温度(基板温度)450℃程度のプラズマCVD法などにより形成することができる。ストッパ絶縁膜35はMOSFETQn上にコンタクトホールを形成する際のエッチングストッパ膜として機能する。

【0055】

その後、ストッパ絶縁膜35上にストッパ絶縁膜35よりも厚い絶縁膜Ifを形成する。絶縁膜Ifは例えば酸化シリコン膜などからなり、TEOSを用いて成膜温度450℃程度のプラズマCVD法などにより形成することができる。その後、絶縁膜Ifの表面をCMP法により研磨するなどして、絶縁膜Ifの上面を平坦化する。下地段差に起因して絶縁膜Ifの表面に凹凸形状が形成されていても、絶縁膜Ifの表面をCMP法により研磨することにより、その表面が平坦化された絶縁膜を得ることができる。

【0056】

次に、図3に示すように、絶縁膜If上に形成したフォトレジストパターン(図示しない)をエッチングマスクとして用いて、絶縁膜35および絶縁膜Ifをドライエッチングすることにより、ストッパ絶縁膜35および絶縁膜Ifを貫通するコンタクトホール(貫通孔、孔)Chを形成する。コンタクトホールChの底部では、半導体基板SBの主面の一部、例えばソース・ドレイン領域30の表面上のシリサイド層31の上面が露出され、図示していない領域では、ゲート電極32と同層のゲート接続部の上面のシリサイド層の上面が露出される。

【0057】

その後、コンタクトホールCh内および絶縁膜If上にTi(チタン)を含むバリア膜BMを形成した後、コンタクトホールCh内にW(タングステン)膜を充填し、バリア膜BMおよびタングステン膜を研磨することで絶縁膜Ifの上面を露出させ、コンタクトプラグCpを形成する。

【0058】

コンタクトプラグCpを形成するには、例えば、コンタクトホールChの内部(底部および側壁上)を含む絶縁膜If上に、成膜温度(基板温度)450℃程度のプラズマCVD法によりバリア膜(例えばチタン膜、窒化チタン膜、あるいはそれらの積層膜)BMを形成する。それから、タングステン膜などからなる主導体膜をCVD法などによってバリア膜BM上にコンタクトホールChを埋めるように形成した後、絶縁膜If上の不要な主導体膜およびバリア膜BMをCMP法またはエッチバック法などによって除去することにより、コンタクトプラグCpを形成することができる。図示は省略するが、このとき、ゲート電極32と一体となってゲート電極32と同層に形成された接続部の上面にもシリサイド層が形成され、接続部上にはシリサイド層を介してコンタクトプラグが形成される。

【0059】

次に、図4に示すように、コンタクトプラグCpが埋め込まれた絶縁膜If上に、ストッパ絶縁膜Sfおよび配線形成用の第1層間絶縁膜1を順次形成する。なお、図4〜図9、図11および図13〜図15は、図3で示した破線で囲まれた領域を拡大して示す要部断面図であり、コンタクトプラグCpの上部の配線形成領域を示している。ストッパ絶縁膜Sfは第1層間絶縁膜1への溝加工の際にエッチングストッパ膜となる膜であり、第1層間絶縁膜1に対してエッチング選択比を有する材料を用いる。ストッパ絶縁膜Sfは、例えばプラズマCVD法により形成されるSiN(窒化シリコン)膜とし、第1層間絶縁膜1は、例えばプラズマCVD法により形成されるSiOC(炭酸化シリコン)膜とすることができる。

【0060】

次に、図5に示すように、シングルダマシン法により第1層目の配線を形成する。まず、レジストパターン(図示しない)をマスクとしたドライエッチングによって第1層間絶縁膜1およびストッパ絶縁膜Sfの所定の領域に、絶縁膜If、コンタクトプラグCpおよびバリア膜BMの上面を露出する配線溝G1を形成する。

【0061】

次に、図6に示すように、半導体基板SB(図示しない)の主面上(すなわち配線溝G1の底部および側壁上を含む第1層間絶縁膜1上)にTaN(窒化タンタル、タンタルナイトライド)からなるバリア導体膜(バリアメタル膜)であるTaN膜2およびTi(チタン)からなるバリア導体膜であるTi膜3を順次PVD法により形成する。TaN膜2の膜厚は5nm程度である。Ti膜3の膜厚は10nm未満の膜厚とし、例えば5nmとする。ここではバリア導体膜としてTi膜3の下層にTaN膜2を形成しているが、TaN膜2の代わりに、Ta(タンタル)膜またはその他のタンタル化合物、タンタル合金、チタン化合物、チタン合金、タングステン、タングステン化合物、Ru(ルテニウム)若しくはルテニウム化合物などを主に含む導体膜をバリア導体膜として用いることができる。

【0062】

続いて、PVD法によりTi膜3上にCu(銅)からなるCuシード膜4aを形成し、さらに電解メッキ法を用いてCuシード膜4a上にCu膜4を形成することにより、TaN膜2、Ti膜3、Cuシード膜4aおよびCu膜4によって配線溝G1の内部を埋め込む。その後、N2(窒素)などの不活性ガスの雰囲気において製造工程中の半導体装置を熱処理することでCuシード膜4aおよびCu膜4を一体化させ、また、Cuの結晶粒径を成長させて大きくする。なお、このときの熱処理を不活性ガスの雰囲気において行うのは、銅が酸化しやすい材料であり、できるだけ酸素を除去した雰囲気において熱処理を行うことが好ましいためである。Cu膜4が酸化した場合、Cu膜4の導電率が下がり、また、半導体装置の信頼性が低下する。ここでは、熱処理によりCuシード膜4aおよびCu膜4を一体化するが、図ではCuシード膜4aおよびCu膜4を区別して示すものとする。

【0063】

また、TaN膜2およびTi膜3を形成する前に、必要に応じてH2(水素)ガスを用いたアニール処理やプラズマ処理といった前処理(プリクリーン)を行っても良い。

【0064】

次に、図7に示すように、配線溝G1内以外の領域のCu膜4、Cuシード膜4a、Ti膜3およびTaN膜2をCMP法により除去して第1層間絶縁膜1の上面を露出することで、TaN膜2、Ti膜3、Cuシード膜4aおよびCu膜4からなり、銅を主導電材料とする第1層目の金属配線(下層配線M1)を形成する。

【0065】

なお、前述したCuシード膜4aおよびCu膜4を一体化させる熱処理は、図7を用いて説明したCMP法による研磨工程の前ではなく後に行っても良い。

【0066】

次に、図8に示すように、半導体基板SB(図示しない)の主面上(すなわち第1層間絶縁膜1上、TaN膜2上、Ti膜3上、Cuシード膜4a上およびCu膜4上)にSiC(炭化シリコン)からなるライナー膜5およびSiOC(炭酸化シリコン)からなる第2層間絶縁膜6を順次CVD法により形成する。

【0067】

次に、図9および図10に示すように、Cu膜4の上面を露出するビアホールV2を形成する。図10は図9に示す製造工程中の半導体装置の断面を示す俯瞰図である。ビアホールV2は、レジストパターン(図示しない)をマスクとしたドライエッチングによって第2層間絶縁膜6およびライナー膜5の所定の領域に形成する。図10に示すように、例えばビアホールV2は断続的に複数形成する孔であり、溝状の形状を有するものではない。

【0068】

次に、図11および図12に示すように、第2層目の配線を形成するための配線溝G2を形成する。図12は図11に示す製造工程中の半導体装置の断面を示す俯瞰図である。配線溝G2は、レジストパターン(図示しない)をマスクとしたドライエッチングによって第2層間絶縁膜6の所定の領域に形成する。配線溝G2は第2層間絶縁膜6の途中深さまでドライエッチングして形成し、下部のCu膜4の上面は露出しない。

【0069】

なお、本実施の形態では図9および図10に示した工程でビアホールV2を形成した後に図11および図12に示した工程で配線溝G2を形成したが、これらの工程の順番は逆でも良い。すなわち、図8に示すような第2層間絶縁膜6が形成された製造工程中の半導体装置に配線溝G2およびビアホールV2を形成する場合、配線溝G2を形成してから、レジストパターンをマスクとしたドライエッチングによってビアホールV2を形成しても構わない。

【0070】

次に、下層配線M1を形成した工程と同様の工程により第2層目の配線を形成する。ここでは、デュアルダマシン法を用いて第2層目の配線を形成する。つまり、図13に示すように、半導体基板SB(図示しない)の主面上(すなわち配線溝G2の底部および側壁上を含む第2層間絶縁膜6上並びにビアホールV2の底部および側壁上)にTaN(窒化タンタル、タンタルナイトライド)からなるバリア導体膜であるTaN膜7およびTi(チタン)からなるバリア導体膜であるTi膜8を順次PVD法により形成する。TaN膜7の膜厚は5nm程度である。Ti膜8の膜厚は10nm未満の膜厚とし、例えば5nmとする。ここではバリア導体膜としてTi膜8の下層にTaN膜7を形成しているが、TaN膜7の代わりに、Ta(タンタル)膜またはその他のタンタル化合物、タンタル合金、チタン化合物、チタン合金、タングステン、タングステン化合物、Ru(ルテニウム)若しくはルテニウム化合物などを主に含む導体膜をバリア導体膜として用いることができる。

【0071】

続いて、PVD法によりTi膜8上にCuシード膜9aを形成し、さらに電解メッキ法を用いてCuシード膜9a上にCu膜9を形成することにより、TaN膜7、Ti膜8、Cuシード膜9aおよびCu膜9によって配線溝G2およびビアホールV2の内部を埋め込む。その後、N2(窒素)などの不活性ガスの雰囲気において製造工程中の半導体装置を熱処理することでCuシード膜9aおよびCu膜9を一体化させ、また、銅の結晶粒径を成長させて大きくする。なお、このときの熱処理を不活性ガスの雰囲気において行うのは、下層配線M1の形成工程と同様にCu膜9およびCuシード膜9a内の銅が酸化するのを防ぐためである。

【0072】

なお、TaN膜7およびTi膜8を形成する前に、必要に応じてH2(水素)ガスを用いたアニール処理やプラズマ処理といった前処理(プリクリーン)を行っても良い。

【0073】

次に、図14に示すように、配線溝G2内およびビアホールV2内以外の領域のCu膜9、Cuシード膜9a、Ti膜8およびTaN膜7をCMP法により除去して第2層間絶縁膜6の上面を露出することで、TaN膜7、Ti膜8、Cuシード膜9aおよびCu膜9からなり、銅を主導電材料とする第2層目の金属配線(上層配線M2)を形成する。

【0074】

なお、前述したCuシード膜9aおよびCu膜9を一体化させる熱処理は、図14を用いて説明したCMP法による研磨工程の前ではなく後に行っても良い。

【0075】

次に、図15に示すように、半導体基板SB(図示しない)の主面上(すなわち第2層間絶縁膜6上、TaN膜7上、Ti膜8上、Cuシード膜9a上およびCu膜9上)にSiC(炭化シリコン)からなるライナー膜10をCVD法により形成することにより、図1に示す本実施の形態の半導体装置が完成する。本実施の形態では説明を省略するが、上層配線M2よりも上層の領域においては、上層配線M2と同様の工程を行うことで多層のCu配線を形成することができる。

【0076】

次に、図6および図13を用いて説明したバリア膜の形成工程において、Ti膜3および8の膜厚を10nm未満とし、本実施の形態では5nmとした理由を、図16を用いて説明する。図16はバリアメタルの部材および膜厚の異なる5種類のバリア膜を用いた場合のCu配線の抵抗値を計測した累計度数分布を示すグラフである。図16に示すグラフの横軸はCu配線の抵抗値を示し、図16に示すグラフの縦軸は複数回行った実験における正規分布の分位点を示している。

【0077】

図16に示すように、バリア膜を10nmのTa膜および5nmのTaN膜により構成するTa/TaN=10/5nmの抵抗値に対し、バリア膜を5nmのTi膜および5nmのTaN膜により構成するTi/TaN=5/5nmの抵抗値は殆ど差がない。しかし、Ta/TaN=10/5nmの抵抗値に対し、Ti/TaN=10/5nmの抵抗値は顕著に抵抗値が上昇していることが分かる。これは、Ti(チタン)がCu(銅)と合金を形成しやすく、Ti/Cuの合金は純粋なCu(銅)に比べて抵抗値が上がるためである。すなわち、Ti/TaN=10/5nmでは、Cu膜と反応して合金を形成するTi(チタン)の量が多いため、Ti/TaN=5/5nmよりも抵抗値が高くなっている。このことから、Cu膜の界面のTi膜の膜厚を10nmよりも薄くすることで、合金化による実質的な抵抗の上昇が配線抵抗に与える影響を無視できる程度に抑えることができることが分かる。よって、本実施の形態では配線抵抗を下げるためTi膜3および8(図1参照)の膜厚を10nm未満とし、好ましくは5nmとしている。

【0078】

次に、本実施の形態の半導体装置の効果について説明する。

【0079】

従来の技術では、特許文献1および2に示されるように、金属の拡散防止機能の高い材料であるTa(タンタル)を含むバリア膜を用いて、Cu配線内のCu(銅)が層間絶縁膜内に拡散することを防ぐ配線構造とすることが一般的である。

【0080】

しかし、Ta(タンタル)を主に含むバリア膜はTi(チタン)またはW(タングステン)などの他の金属を主に含むバリア膜に比べて金属拡散防止機能は優れているが、Cu(銅)との濡れ性がTi(チタン)に比べて悪い。このため、配線溝内のTa膜またはTaN膜などのバリア膜の表面にCuシード膜を均一に連続的に形成することが難しく、比較例として図26に示すように、Ta膜8aの表面においてCuシード膜9bが複数の固まりとなるおそれがある。すなわち、Ta膜8aの表面を完全に覆わず、Cuシード膜9bの皮膜率が低くなり、Cuシード膜9bが不連続に形成される。この場合、図27および図28に比較例として示すように、Cu膜9を形成した際に、配線溝G2内およびビアホールV2内に空隙(ボイド)11が形成されやすい。

【0081】

図1に示すCuシード膜4aおよび9aはCu膜4および9を電界メッキ法によって形成する際の電極となる膜であり、Cu膜4および9の膜厚を均一に形成する働きを有する。これは、電界メッキ法によって形成されるCu膜4および9の膜厚の均一性は、Cu膜4および9の下地の部材の抵抗値によって左右されるためである。従って、図26に示すように、Cuシード膜9bが配線溝G2内およびビアホールV2内のTa膜8aの表面に均一に形成されなければ、Cu膜9を形成する際の電界メッキ工程においてTa膜8aが電極として働いたとしても、Cu膜9の下地にはCuシード膜9bまたはTa膜8aなど抵抗値の異なる部材が存在することになる。このため、図27または図28に示すように、Cu膜9は膜厚が均一に形成されないため、場合によっては空隙(ボイド)11が形成される。

【0082】

空隙11が形成されると、主にCu膜9からなる配線が途中で途切れたり、ビアホール内で配線が途切れることで上層配線と下層配線とが電気的に接続されなくなるおそれがあり、半導体装置の歩留まりまたは信頼性の低下に繋がる。

【0083】

また、Ta(タンタル)はTi(チタン)に比べて材料の価格が高いため、Ta(タンタル)をバリア膜に用いると半導体装置を用いた製品のコストが増大する問題がある。

【0084】

そこで、本発明者らは、配線のバリア膜にTi(チタン)を主に含む金属膜を用いることを検討した。本実施の形態では、図1に示すように、下層配線M1において銅の拡散を防ぐバリア膜として、Ti膜3およびTi膜3の下層のTaN膜2を形成しており、同様に、上層配線M2において銅の拡散を防ぐバリア膜として、Ti膜8およびTi膜8の下層のTaN膜7を形成している。

【0085】

Ti(チタン)を含むバリア膜はTa(タンタル)またはTa化合物を含むバリア膜に比べ、銅との濡れ性が良い特徴がある。すなわち、Ti(チタン)を含むバリア膜であるTi膜8の表面にCuシード膜9aをPVD法により形成した場合に、Cuシード膜9aが複数の固まりとなることはなく均一に延びるため、Cuシード膜9aがTi膜8の表面を露出することなく覆う。Cu膜9は電界メッキ法によりCuシード膜9a上に均一な膜厚で形成されるため、図26〜図28に示した比較例とは異なり、配線溝G2内およびビアホールV2内に空隙11が形成されることを防ぐことができる。

【0086】

また、Ti(チタン)はTa(タンタル)よりも安価な材料であるため、Ti(チタン)を含むバリア膜を用いることにより、図25に示すようなTa(タンタル)およびTaN(窒化タンタル)をバリア膜として用いた場合に比べて半導体装置を用いた製品のコストを低減することができる。

【0087】

なお、Ti(チタン)はTa(タンタル)に比べて金属の拡散防止機能が低い材料であるが、図1に示すように、Ti膜3および8の下層にTaN膜2および7を形成することにより、拡散防止機能が低下することを防いでいる。

【0088】

以上に述べたように、本実施の形態の半導体装置では、銅を主に含むダマシン配線のバリア膜にTi(チタン)を主に含む10nm未満の金属膜を用いることにより、配線抵抗を上昇させずに、配線内における空隙の発生を防ぎ、半導体装置の歩留まりおよび信頼性を向上させ、また、半導体装置を用いた製品のコストを低減することを可能としている。

【0089】

(実施の形態2)

前記実施の形態では、Cu配線のバリア膜として、Cu膜との界面にTi(チタン)を主に含む金属膜を用い、Ti膜の下層に他のバリア膜を形成する半導体装置について説明した。本実施の形態では、原子数がTi(チタン)よりもN(窒素)の方が多いTiNX(窒化チタン)膜をバリア膜に用いる半導体装置について図16〜図18を用いて説明する。図17は本実施の形態の半導体装置において、MOSFETおよびダマシン配線を含む領域を示す要部断面図である。

【0090】

図17に示すように、本実施の形態の半導体装置は前記実施の形態1における半導体装置とほぼ同様の構造を有しており、前記実施の形態1における半導体装置とほぼ同様の製造工程で製造することができる。本実施の形態の半導体装置は、前記実施の形態1において図1に示したバリア膜であるTaN膜2およびTi膜3に代わって、金属拡散防止機能を有するTiNX膜12が形成され、TaN膜7およびTi膜8に代わって、金属拡散防止機能を有するTiNX膜13が形成されている点で前記実施の形態1における半導体装置と異なる。

【0091】

すなわち、本実施の形態の半導体装置は、半導体基板SB上に形成されたMOSFETQnを有し、MOSFETQnを覆うように形成された絶縁膜If上の第1層間絶縁膜1および第2層間絶縁膜6のそれぞれに配線溝G1およびG2が形成されている。第1層間絶縁膜1と第1層間絶縁膜1の下層のストッパ絶縁膜Sfに形成された配線溝G1内の側壁および底部には膜厚が例えば10nmのTiNX膜12のバリア膜が形成されており、配線溝G1内には、TiNX膜12を介してCuシード膜4aが形成されている。配線溝G1内はTiNX膜12およびCuシード膜4aを介してCu膜4が埋め込まれており、Cu膜4、Cuシード膜4aおよびTiNX膜12によって下層配線M1が構成されている。

【0092】

また、第1層間絶縁膜1および下層配線M1上にライナー膜5を介して第2層間絶縁膜6が配置され、第2層間絶縁膜6には配線溝G2と、配線溝G2の底部から第2層間絶縁膜6およびライナー膜5を貫いて下層配線M1の上面(Cu膜4の上面)に達するビアホールV2とが形成されている。配線溝G2内およびビアホールV2内には、配線溝G1内の下層配線M1と同様に、膜厚が例えば10nmのTiNX膜13およびCuシード膜9aを介してCu膜9が埋め込まれており、Cu膜9、Cuシード膜9aおよびTiNX膜13によって上層配線M2が構成されている。

【0093】

ここで、TiNX膜12および13は金属拡散防止機能を有する導電性の金属膜であり、それぞれの膜厚は10nmである。これは、図16のグラフに示すように、TiN=10nmのバリア膜を有する配線の配線抵抗はTa/TaN=10/5nmのバリア膜を有する配線の配線抵抗とほぼ変わらないためであり、TiNX膜12および13のそれぞれの膜厚を10nm以下にすることで、Ta/TaN=10/5nmのバリア膜に比べて配線抵抗が上昇することを防ぐことができる。

【0094】

本実施の形態の半導体装置の形成方法は、前記実施の形態1のTaN膜2およびTi膜3の形成工程(図6参照)においてTaN膜2およびTi膜3の代わりにTiNX膜12を形成し、TaN膜7およびTi膜8の形成工程(図13参照)においてTaN膜7およびTi膜8の代わりにTiNX膜13を形成する工程以外は前記実施の形態1の半導体装置の製造方法と同様であるので、詳しい説明は省略する。

【0095】

つまり、前記実施の形態1において図6を用いて説明した工程では、半導体基板SB(図示しない)の主面上(すなわち配線溝G1の底部および側壁上を含む第1層間絶縁膜1上)にTiNX(窒化チタン)からなるバリア導体膜であるTiNX膜12をPVD法により形成する。続いて、PVD法によりTiNX膜12上にCu(銅)からなるCuシード膜4aを形成し、さらに電解メッキ法を用いてCuシード膜4a上にCu膜4を形成することにより、TiNX膜12、Cuシード膜4aおよびCu膜4によって配線溝G1の内部を埋め込む。その後、N2(窒素)などの不活性ガスの雰囲気において製造工程中の半導体装置を熱処理することでCuシード膜4aおよびCu膜4を一体化させ、また、Cuの結晶粒径を成長させて大きくする。

【0096】

同様に、前記実施の形態1において図13を用いて説明した工程では、半導体基板SB(図示しない)の主面上(すなわち配線溝G2の底部および側壁上を含む第2層間絶縁膜6上並びにビアホールV2の底部および側壁上)にTiNX(窒化チタン)からなるバリア導体膜であるTiNX膜13をPVD法により形成する。続いて、PVD法によりTiNX膜13上にCuシード膜9aを形成し、さらに電解メッキ法を用いてCuシード膜9a上にCu膜9を形成することにより、TiNX膜13、Cuシード膜9aおよびCu膜9によって配線溝G2およびビアホールV2の内部を埋め込む。その後、N2(窒素)などの不活性ガスの雰囲気において製造工程中の半導体装置を熱処理することでCuシード膜9aおよびCu膜9を一体化させ、また、銅の結晶粒径を成長させて大きくする。

【0097】

上記の工程以外は、前記実施の形態1における半導体装置の製造工程と同様の工程を行うことで、図17に示す本実施の形態の半導体装置が完成する。

【0098】

ここで、TiNX膜12および13を構成するTiNX(窒化チタン)は、原子数がTi(チタン)よりもN(窒素)の方が多い。すなわち、TiNX(窒化チタン)内の一つのTi(チタン)の原子に対するN(窒素)の原子数を表わすXは1未満(X<1)であり、例えばX=0.5とする。つまり、ここではTi(チタン)とN(窒素)の原子数の比はTi:N=2:1となっている。

【0099】

上記のようにバリア膜の材料にTiNX(X<1)を用いる理由を、図18を用いて説明する。図18は、Ti(チタン)とN(窒素)の原子数の比が1対1であるTiNX(X=1)をバリア材料として用いた場合と、TiNX(X=0.5)をバリア材料として用いた場合とにおいて、一定の距離(例えば70nm)を保って配置された2本の金属配線同士の間における配線間耐圧を示したグラフである。図18に示すグラフの横軸は、配線間の電位差を上昇させた場合に電流がショート(短絡)した時の配線間の電位差を示し、図18に示すグラフの縦軸は、複数回行った配線間耐圧の実験における正規分布の分位点を示している。図18に示す白丸はTiNX(X=1)をバリア膜として用いたCu配線の配線間耐圧を示しており、黒丸はTiNX(X=0.5)をバリア膜として用いたCu配線の配線間耐圧を示している。

【0100】

図18に示すように、TiNX(X=1)をバリア膜として用いたCu配線は、TiNX(X=0.5)をバリア膜として用いたCu配線の配線間耐圧よりも低い電位差で配線間がショートしている。すなわち、TiNX(X=0.5)をバリア膜として用いたCu配線の配線間耐圧は約50Vの値を示しているが、TiNX(X=1)をバリア膜として用いたCu配線は、17V〜50Vの範囲にばらついた配線間耐圧の値を示している。このことから、TiNX膜内におけるN(窒素)の比率が大きくなるほど、TiNX膜をバリア膜として用いたCu配線の配線間耐圧が下がることがわかる。

【0101】

また、図18に示すように、TiNX(X=1)をバリア膜として用いたCu配線は横軸方向のばらつきが大きく、配線間耐圧の信頼性が低い。これに対し、TiNX(X=0.5)をバリア膜として用いたCu配線の配線間耐圧は横軸方向のばらつきが少なく、ほぼ縦軸に沿う方向に正規分位点が分布していることから、配線間耐圧の信頼性が高いことがわかる。

【0102】

従って、バリア膜に用いるTiNX(窒化チタン)内のN(窒素)の原子数Xは、X<1ならばほぼ問題ない配線間耐圧および信頼性を示すため、本実施の形態ではX<1とし、好ましくはX=0.5とする。すなわち、本実施の形態におけるバリア膜を構成する窒化チタン膜内のTi(チタン)とN(窒素)の組成比はTi>Nであり、特に、Ti=1としたときにN=0.5であることが好ましい。

【0103】

上記のように、TiNX(窒化チタン)をバリア膜に用いた場合、図25に示すような、Ta(タンタル)およびTaN(窒化タンタル)をバリア膜として形成した場合と同等の金属拡散防止機能を有し、銅と濡れ性および密着性の良いバリア膜を形成することができる。これは、Ti(チタン)にN(窒素)を化合させることにより、バリア膜内において他の元素(例えばCu(銅))と合金化しやすいTi(チタン)を減少させることができるためである。

【0104】

すなわち、N(窒素)がTi(チタン)に化合しているTiNX(窒化チタン)膜は、純粋なTi膜に比べて銅と合金化しにくい。通常、Ti(チタン)とCu(銅)は合金化し易く、銅と合金化したチタン膜は抵抗値が上がる。Ta(タンタル)よりも拡散防止機能の低いTi膜に十分な拡散防止機能を持たせるにはTi膜の膜厚を厚くする必要があるが、銅と合金化し易いTi膜は膜厚が厚すぎると抵抗値が大幅に上昇するため、バリア膜として使用することができなくなる。従って、純粋なTi膜をバリア膜として用いる場合、その膜厚および拡散防止機能に限界があった。

【0105】

これに対し、本実施の形態では、N(窒素)が化合していることで銅と合金化しにくくなったTiNX膜をバリア膜に用いるため、TiNX膜の膜厚を厚くしてもTiNX膜の抵抗値は殆ど上昇しない。従って、TiNX膜の膜厚を厚くすることで十分な拡散防止機能を得ることを可能としている。本実施の形態では、図17に示すTiNX膜12および13のそれぞれの膜厚を10nmとしたが、拡散防止機能をより高めるためにTiNX膜12および13のそれぞれの膜厚を10nmよりも厚い膜厚としても良い。

【0106】

なお、上記の理由から、一つのTi(チタン)原子に対するN(窒素)の原子数を示すXの値は、0.5未満の更に小さい値でも良いが、0よりも大きい値でなければいけない。すなわち、窒素の原子数が0であればバリア膜は純粋なTi膜となるため、銅との合金化によりバリア膜の抵抗値が大幅に上昇し、バリア膜として使用する際に問題が生じる。従って、X>0である必要がある。

【0107】

本実施の形態によれば、銅との濡れ性の良いTi(チタン)を含むTiNX膜をバリア膜に用いることで、図17に示すCu膜4および9の埋め込み性を向上させ、歩留まりを向上させ、半導体装置の信頼性を向上させることができる。また、Ta(タンタル)よりも安価な材料であるTi(チタン)を用いたバリア膜を使用することで、半導体装置を用いた製品のコストを低減することができる。

【0108】

(実施の形態3)

前記実施の形態1における半導体装置ではCu配線のバリア膜としてTi膜およびTaN膜を用いる技術について説明した。これに対し、本実施の形態では、バリア膜を形成する際にTi膜(またはTi合金膜)のみを形成し、その後にTi膜内の下層に形成される酸化チタン膜と、前記Ti膜とによる二層構造のバリア膜を用いた半導体装置について、図19〜図24を用いて説明する。

【0109】

図19に示すように、本実施の形態の半導体装置は前記実施の形態1における半導体装置とほぼ同様の構造を有しており、前記実施の形態1における半導体装置とほぼ同様の製造工程で製造することができる。本実施の形態の半導体装置は、前記実施の形態1において図1に示したバリア膜であるTaN膜2および7に代わって、金属拡散防止機能を有する酸化Ti膜14および16がそれぞれ形成され、Ti膜3および8に代わって、金属拡散防止機能を有するTi膜15および17が形成されている点で前記実施の形態1における半導体装置と異なる。

【0110】

Ti膜15および17並びに酸化Ti膜14および16は導電性を有するバリア膜であり、酸化Ti膜14および16は具体的にはTiOX膜またはTiSiXOYからなる反応層である。なお、前記実施の形態2において説明したTiNX膜12(図17参照)のN(窒素)の原子数Xと、本実施の形態のTiOX膜のO(酸素)の原子数Xと、TiSiXOY膜のSi(シリコン)の原子数Xとは、それぞれ同一の値を示すものではない。

【0111】

ここで、本実施の形態の半導体装置の製造工程を説明する。図19に示す半導体装置を製造するには、まず前記実施の形態1で図5を用いて説明したように、絶縁膜If上のストッパ絶縁膜Sfおよび第1層間絶縁膜1に配線溝G1を形成した後、図20に示すように、PVD法により第1層間絶縁膜1上、配線溝G1の内壁および底面にTi膜14aを形成(堆積)する。Ti膜14aの膜厚は、例えば10nmとする。

【0112】

このとき、Ti膜14aは純粋なTi(チタン)またはその合金からなる膜であるが、PVD法の工程中の熱(例えば450℃程度)により、第1層間絶縁膜1中の水分と反応して酸化される。この場合、図21に示すように、第1層間絶縁膜1との界面を含む第1層間絶縁膜1上、配線溝G1の内壁および底面に酸化Ti膜14が形成され、第1層間絶縁膜1との界面を含む第1層間絶縁膜1上、配線溝G1の内壁および底面には酸化Ti膜14を介してTi膜15が形成される。

【0113】

この後の工程は、配線溝G2を形成する工程まで前記実施の形態1と同様に行う。すなわち、図22に示すように、Ti膜15上にCuシード膜4aおよびCu膜4を形成した後、CMP法により第1層間絶縁膜1上のCu膜4、Cuシード膜4a、Ti膜15および酸化Ti膜14を除去し、第1層間絶縁膜1の上面を露出することで、Cu膜4、Cuシード膜4a、Ti膜15および酸化Ti膜14からなる下層配線M1を形成する。続いて、図23に示すように、第1層間絶縁膜1上および下層配線M1上にライナー膜5および第2層間絶縁膜6を形成し、ライナー膜5および第2層間絶縁膜6を貫通してCu膜4の上面を露出するビアホールV2を形成した後、第2層間絶縁膜6の上面に配線溝G2を形成し、図23の構造を得る。

【0114】

次に、図20および図21を用いて説明した工程と同様に、PVD法によりTi膜を堆積した後に、前記Ti膜内の下層のTi(チタン)が、PVD法の工程中の熱によって第2層間絶縁膜6中の水分と反応して酸化することにより、図24に示すように、第2層間絶縁膜6上および配線溝G2の内壁および底面に、酸化Ti膜16を介してTi膜17が形成される。

【0115】

この後の工程は、前記実施の形態1と同様に行う。すなわち、Ti膜17上にCuシード膜9aおよびCu膜9を形成した後、CMP法により第2層間絶縁膜6上のCu膜9、Cuシード膜9a、Ti膜17および酸化Ti膜16を除去し、第2層間絶縁膜6の上面を露出することで、Cu膜9、Cuシード膜9a、Ti膜17および酸化Ti膜16からなる上層配線M2を形成する。その後、第2層間絶縁膜6上および上層配線M2上にライナー膜10を形成し、図19に示す半導体装置が完成する。

【0116】

本実施の形態では、下層配線M1および上層配線M2のバリア膜を形成する際、Ti膜以外の膜を堆積する工程を有しておらず、堆積したTi膜の底部が酸化することにより、Ti膜とその下層の酸化Ti膜との2層構造のバリア膜を形成している。ここで、図16に示すグラフから、バリア膜としてTi膜を10nm形成した場合(Ti=10nm)と、バリア膜として10nmのTi膜と、その下層の5nmのTaN膜とを積層した場合(Ti/TaN=10/5nm)とを比べると、Ti=10nmよりもTi/TaN=10/5nmの方が配線抵抗が高いことが分かる。

【0117】

Ti/Ta=10/5nmでは、Ta膜上のTi膜の全てがTi膜上に形成されたCuシード膜内およびCu膜内の銅と化合するため、厚さ10nm分のTi(チタン)とCu(銅)との化合物が形成され、バリア膜の抵抗値が大幅に増大する。

【0118】

しかし、本実施の形態のように、バリア膜としてTi膜のみを10nm体積したTi=10nmの場合、層間絶縁膜に含まれる水分によって層間絶縁膜との界面のTi膜は酸化され、TiOXまたはTiSiXOYからなる反応層が形成される。すなわち、層間絶縁膜とTi膜との反応により、Cuシード膜内およびCu膜内の銅と化合することができるTi(チタン)の量は、上述したTi/Ta=10/5nmに対して少ない。このため、Ti(チタン)とCu(銅)との化合物が形成される量は少なく、配線抵抗の上昇を抑えることができる。

【0119】

本実施の形態では配線抵抗の低いバリア膜を形成することができるため、前記実施の形態1と違い、Ti膜の膜厚を厚くすることができる。本実施の形態では配線溝内に形成するTi膜の膜厚を10nmとしているが、それよりも厚い膜厚としても構わない。Ti(チタン)は金属拡散防止機能においてTa(タンタル)に劣るが、本実施の形態では形成するバリア膜の膜厚を厚くすることにより、バリア膜に必要な拡散防止機能を得ることができる。

【0120】

なお、層間絶縁膜と接するTi膜が酸化し易いように、本実施の形態では、水分を吸収し易い(吸湿性が高い)層間絶縁膜を形成することが望ましい。ここでは、図19に示す第1層間絶縁膜1および第2層間絶縁膜6を構成する部材は、SiO2(二酸化シリコン)よりも吸湿性の高い部材であって、例えばSiOC(炭酸化シリコン)を用いるものとする。SiO2(二酸化シリコン)は吸湿性が低いため、SiO2からなる層間絶縁膜に接するTi膜には、殆ど酸化Ti膜は形成されず、SiO2からなる層間絶縁膜に形成された配線溝内にTi膜を介してCu配線を形成した場合、配線抵抗が大幅に高くなる。SiOCはH2O(水)と結びつきやすく、その内部に水分を含みやすい材料であるので、バリア膜として酸化Ti膜を形成するのに適している。

【0121】

なお、図20で配線溝G1内に形成したTi膜14aおよび図24において配線溝G2内に形成したTi膜(図示しない)の部材は、純粋なTi(チタン)からなる膜に限らず、Tiの化合物であっても構わない。例えば、TiNX(X<1)のようなTiN膜でも良い。

【0122】

本実施の形態では、銅との濡れ性の良いTi(チタン)を含むTi膜をバリア膜に用いることで、図19に示すCu膜4および9の埋め込み性を向上させ、歩留まりを向上させ、半導体装置の信頼性を向上させることができる。また、Ta(タンタル)よりも安価な材料であるTi(チタン)を用いたバリア膜を使用することで、半導体装置を用いた製品のコストを低減することができる。

【0123】

以上、本発明者によってなされた発明を実施の形態に基づき具体的に説明したが、本発明は前記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることはいうまでもない。

【0124】

例えば、前記実施の形態1〜3では、図1、図17および図19に示すように、半導体基板上に形成されたMOSFETQnに所定の電位を供給する配線について説明したが、本発明のダマシン配線はMOSFETの上層配線以外のあらゆる用途の配線に広く適用することができる。

【産業上の利用可能性】

【0125】

本発明は、銅配線を有する半導体装置に幅広く利用されるものである。

【符号の説明】

【0126】

1 第1層間絶縁膜

2 TaN膜

2a TaN膜

3 Ti膜

3a Ta膜

4 Cu膜

4a Cuシード膜

5 ライナー膜

6 第2層間絶縁膜

7 TaN膜

7a TaN膜

8 Ti膜

8a Ta膜

9 Cu膜

9a Cuシード膜

9b Cuシード膜

10 ライナー膜

11 空隙

12 TiNX膜

13 TiNX膜

14 酸化Ti膜

14a Ti膜

15 Ti膜

16 酸化Ti膜

17 Ti膜

30 ソース・ドレイン領域

31 シリサイド層

32 ゲート電極

33 ゲート絶縁膜

34 サイドウォール

35 ストッパ絶縁膜

BM バリア膜

Ch コンタクトホール

Cp コンタクトプラグ

G1、G2 配線溝

If 絶縁膜

M1 下層配線

M2 上層配線

Qn MOSFET

SB 半導体基板

Sf ストッパ絶縁膜

V2 ビアホール

【技術分野】

【0001】

本発明は、半導体装置およびその製造方法に関し、特に、銅配線を有する半導体装置およびその製造方法に適用して有効な技術に関するものである。

【背景技術】

【0002】

先端のLSI(Large Scale Integration)において、半導体素子に所定の電位を供給する用途、または電気信号を伝達する用途などに用いられる配線の材料には、配線の低抵抗化を目的として、Al(アルミ)を主体とした合金材料(Al−Cu合金など)に代わり、Cu(銅)が広く用いられるようになってきている。銅の導入により、配線の形成工程においては、ドライエッチングを用いて直接配線材料を加工するのではなく、予め層間絶縁膜中に配線・ビアとなる溝やホールを形成し、その後配線材料(例えばCu(銅))を埋め込み、余分な部分の配線材料をCMP(Chemical Mechanical Polishing:化学的機械的研磨)法により取り除く、所謂ダマシン法が用いられる様になってきている。

【0003】

Cu配線構造では、Cu(銅)が層間絶縁膜に拡散することを防止するため、Cu配線の表面部分を全て拡散防止膜(バリア膜、シード膜)で覆う必要がある。通常、このバリア膜は、Cu配線の上面に対しては絶縁膜系のバリア材として、銅の拡散防止機能を有する絶縁膜であるライナー膜を用いる。このライナー膜はCu配線上部の層間絶縁膜の一部としても用いる。一方、Cu配線の側壁・底部に対しては金属系のバリア材(バリアメタル)からなるバリア膜を用いる。バリアメタルは配線用の溝またはビアホール内壁に成膜されるため、配線材料の一部として用いられることとなる。

【0004】

現在、バリアメタルとして広く用いられている材料は、Ta(タンタル)およびその化合物(例えばTaN)である。これは、一般的に、Ta(タンタル)を主とするバリア材料は銅の拡散に対して優れた防止性能を示すためである。

【0005】

特許文献1(特開2004−79802号公報)には、デュアルダマシン法により金属配線層を形成する場合に、バリア膜による金属配線層の抵抗上昇を抑える技術が開示されている。具体的には、有機SOG(Spin On Glass)膜からなる有機層間絶縁膜上に、配線となる金属膜を形成する際、有機層間絶縁膜と金属膜との界面に金属拡散防止用の炭化金属膜をバリア膜として形成する。これにより、抵抗が高いバリア膜の占める割合を少なくし、バリア膜に十分な金属拡散防止機能を持たせた状態で配線層の抵抗を低くすることができるとしている。

【0006】

ここでは、バリア膜の材料に、炭化金属膜としてTaC(炭化タンタル)を用いているが、Ti(チタン)またはTi(チタン)の窒化物をバリア膜の材料として用いても良いとしている。ただし、バリア膜に用いるTi膜の膜厚に関する記載はない。また、バリア膜に用いるTiN膜のTi(チタン)とN(窒素)の具体的な原子数の比率についての記載はない。また、バリア膜の材料としてTi酸化物を用いる旨の記載はない。

【0007】

特許文献2(特開2003−124313号公報)には、Cu(銅)を配線材料とする多層配線構造において、銅の拡散による汚染を防止する一方で、Cuビアにおける下層配線層との密着性を改善してコンタクト抵抗を低減する技術が開示されている。具体的には、デュアルダマシン法により層間絶縁膜間に形成されたCu配線層と、該層間絶縁膜に開口されたビアホール内に形成され、Cu配線層に接続されたCuビアとを備える半導体装置において、Cuビアの側面に層間絶縁膜と密着性のあるTaNバリア膜と、銅と密着性のあるTaバリア膜とを積層し、Cuビアの底面にTaバリア膜のみを形成するものである。これにより、Taバリア膜およびTaNバリア膜によってCuの拡散による汚染を防止し、銅と層間絶縁膜との密着性を高め、Cuビアの剥離を防止することができるとしている。また、Cuビアの底面とCu配線層との密着性を高め、CuビアとCu配線層との界面でのCu原子の移動を抑制し、エレクトロマイグレーション耐性または熱ストレス耐性を高め、コンタクト抵抗を低減することができるとしている。

【0008】

ここでは、バリア膜の材料としてTa(タンタル)およびTaN(窒化タンタル)を用いているが、Ti(チタン)およびTiN(窒化チタン)の組み合わせをバリア膜の材料として用いても良いとしている。ただし、バリア膜に用いるTi膜の膜厚に関する記載はない。また、バリア膜に用いるTiN膜のTi(チタン)とN(窒素)の具体的な原子数の比率についての記載はない。また、バリア膜の材料としてTi酸化物を用いる旨の記載はない。

【先行技術文献】

【特許文献】

【0009】

【特許文献1】特開2004−79802号公報

【特許文献2】特開2003−124313号公報

【発明の概要】

【発明が解決しようとする課題】

【0010】

前述したように、近年、Cu(銅)を含む配線を有するLSIなどの半導体装置では、Cuの拡散防止のためにTaを含むバリア膜をCu配線の側壁および底面に形成する方法が用いられるようになってきている。

【0011】

しかし、Ta(タンタル)を含むバリア膜は、バリア膜を構成する金属(バリアメタル)の材料として要求される拡散防止機能以外の特性、および量産に際し注目される材料コスト等の観点からは、必ずしも最良の材料とは言い難い面がある。例えば、Ta(タンタル)を含むバリア膜は銅との濡れ性が良くないため、絶縁膜に形成された配線溝内において、Ta(タンタル)を含むバリア膜を介して形成される配線材料である銅の埋め込み性が悪くなり、信頼性が低下する問題がある。

【0012】

ここで、前述したTa(タンタル)を含むバリア膜の問題点について、図25〜図28を用い、Ta(タンタル)およびTaN(窒化タンタル)をバリア膜として形成した場合のCu配線を例として説明する。図25は、Ta(タンタル)およびTaN(窒化タンタル)をバリア膜として形成した場合に、正常に形成されたCu配線の近傍を示す要部断面図である。図26〜図28は、それぞれTa(タンタル)およびTaN(窒化タンタル)をバリア膜として形成した場合の、デュアルダマシン配線の製造工程を示す要部断面図である。

【0013】

図25に示す半導体装置内において、Ta(タンタル)を主体とするバリアメタル材料を用いた配線は、ダマシン法により形成されている。すなわち、例として示す半導体装置は、絶縁膜If上の第1層間絶縁膜1およびストッパ絶縁膜Sfに形成された配線溝G1内にシングルダマシン法により形成された下層配線M1と、第1層間絶縁膜1上のライナー膜5および第2層間絶縁膜6に形成されたビアホールV2内および第2層間絶縁膜6に形成された配線溝G2内にデュアルダマシン法により埋め込まれ、下層配線M1と電気的に接続された上層配線M2とを有している。ビアホールV2は配線溝G1の底面において開口し、下層配線M1の上面に達する孔部である。

【0014】

下層配線M1は主にCu膜4からなり、Cu膜4と第1層間絶縁膜1との間にはTa(タンタル)からなるTa膜3aが形成され、Ta膜3aと第1層間絶縁膜1との間にはTaN(窒化タンタル)からなるTaN膜2aが形成されている。Cu膜4とTa膜3aとの間には、Cu(銅)からなるCuシード膜4aが形成されている。

【0015】

同様に、上層配線M2は主にCu膜9からなり、Cu膜9とライナー膜5および第2層間絶縁膜6との間にはTa(タンタル)からなるTa膜8aが形成され、Ta膜8aとライナー膜5および第2層間絶縁膜6との間にはTaN(窒化タンタル)からなるTaN膜7aが形成されている。また、Cu膜9とTa膜8aとの間には、Cu(銅)からなるCuシード膜9aが形成されている。下層配線M1は、下層配線M1の下部のコンタクトプラグCpを介して第1層間絶縁膜1よりも下層の半導体基板上に形成された半導体素子に電気的に接続されている。

【0016】

図25に示す断面図は、Ta膜8a、TaN膜7a、Cuシード膜9aおよびCu膜9がそれぞれ正常に形成されたCu配線を示している。このとき、Cu膜9内には空隙(ボイド)は形成されておらず、配線溝G2内およびビアホールV2内ではバリア膜およびCuシード膜9aを介して均一にCu膜9が埋め込まれている。

【0017】

しかし、バリア膜として使用されているTa膜3a、8aおよびTaN膜2a、7aはCuシード膜9aとの濡れ性が悪く、Cuシード膜9aは配線溝G2内およびビアホールV2内のTa膜8aの表面に均一に形成されない場合がある。

【0018】

ここで、バリア膜にTa(タンタル)を含む材料を用いた半導体装置の製造工程中の要部断面図を図26〜図28に示す。図26では、第1層間絶縁膜1の上面に下層配線M1を形成した後、第1層間絶縁膜1上にライナー膜5および第2層間絶縁膜6を形成し、ライナー膜5および第2層間絶縁膜6を貫通するビアホールV2を形成し、配線溝G2を形成した構造において、TaN膜7aを形成する工程を示している。

【0019】

図26に示すように、PVD(Physical Vapor Deposition)法によってTaN膜7aおよびTa膜8aを順次形成した後に、PVD法によってTa膜8aの表面にCuシード膜を堆積する。しかし、Ta(タンタル)とCu(銅)とは濡れ性が悪いため、Cuシード膜9bは配線溝G2内およびビアホールV2内のTa膜8aの表面において均一に延びず、複数の固まりとなって点在するように形成されやすい。

【0020】

このようにCuシード膜9bが配線溝G2内およびビアホールV2内において不連続に形成された場合、図26の工程の後にCuシード膜上に電界メッキ法によりCu膜を形成すると、図27に示すように、Cu膜9内に空隙(ボイド)11が形成されたり、図28に示すように、配線溝G2内およびビアホールV2内に空隙11が形成されることでCu膜9がビアホールV2内の底部にまで埋め込まれなくなるおそれがある。

【0021】

図27または図28に示した工程においてCu膜9を形成した後、CMP法によって第2層間絶縁膜6上に形成されたCu膜9、Cuシード膜9a、Ta膜8aおよびTaN膜7aを除去し、Cu膜9の上面の高さを第2層間絶縁膜6の上面の高さと揃え、主にCu膜9からなる上層配線を形成する。その後、第2層間絶縁膜6上および前記上層配線上にライナー膜(図示しない)および第3層間絶縁膜(図示しない)を形成し、前記上層配線の更に上層に配線が形成される。

【0022】

ここで、図27および図28で説明したようにCu膜9の埋め込み性が悪くなるのは、配線溝G2内およびビアホールV2内において不連続に形成されたCuシード膜を電極として、Cu膜9を電界メッキ法によって形成しているためである。すなわち、Cu膜9は、電界メッキ工程において電極となるCuシード膜9aの表面に形成されるため、通電しているCuシード膜9aと不連続に形成されているCuシード膜9bの表面にはCu膜9が形成されにくい。このため、図27および図28に示すように、配線溝G2内およびビアホールV2内に空隙11が形成されやすく、前記上層配線が途中で途切れたり、前記上層配線と下層配線M1とが電気的に接続されず、前記上層配線から下層配線M1に所定の電位を供給できなくなる可能性がある。

【0023】

また、Cu膜9を形成する電界メッキ工程において、Cuシード膜9aおよび9bから露出しているTa膜8aが通電して電極として機能したとしても、Cuシード膜9aの表面に比べてTa膜8aの表面ではCu膜9は形成されにくい。これは、Cu(銅)に比べて(タンタル)の抵抗値が高いためであり、これによって配線溝G2内およびビアホールV2内において形成されるCu膜9の膜厚が均一でなくなり、空隙11が形成されやすくなる。

【0024】

上記のように、Ta(タンタル)を配線のバリア膜に用いて半導体装置を製造すると、Cuシード膜との濡れ性に起因するCu配線の埋め込み性の悪化によって、半導体装置の歩留まりおよび信頼性が低下する。

【0025】

また、Ta(タンタル)自体が比較的高価な材料であるため、Ta(タンタル)を配線のバリア膜に用いて半導体装置を製造すると、製品のコストが増大する問題がある。

【0026】

以上のことから、本発明者らはTa(タンタル)に変わるバリアメタルとして、銅との濡れ性に優れているTi(チタン)を用いることを検討した。しかし、Ti(チタン)は銅と合金を形成しやすい性質を有しているため、バリア膜としてTi膜を形成した場合、Ti膜とCu膜との界面に純粋な銅よりも抵抗値が高いTi/Cu合金膜が形成され、Ti/Cu合金膜によって配線抵抗が上昇する問題がある。

【0027】

本発明の目的は、銅を含む配線を有する半導体装置において、銅配線の表面に形成されたバリア膜の拡散防止機能を低下させずに銅配線の埋め込み性を向上させることにある。

【0028】

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

【課題を解決するための手段】

【0029】

本願において開示される実施の形態のうち、代表的なものの概要を簡単に説明すれば、次のとおりである。

【0030】

本発明の好ましい一実施の形態である半導体装置は、

半導体基板上に形成された層間絶縁膜と、

前記層間絶縁膜に形成された配線溝と、

前記配線溝内に第1バリア膜を介して形成されたCuを主成分とする金属膜と、

を有し、

前記第1バリア膜は、Taを含む第3バリア膜と、前記第3バリア膜上に前記金属膜と接して形成されたTiを含む第2バリア膜とを有するものである。

【0031】

また、本発明の好ましい一実施の形態である半導体装置の製造方法は、

(a)半導体基板を準備する工程と、

(b)前記半導体基板上に層間絶縁膜を形成する工程と、

(c)前記層間絶縁膜の上面に配線溝を形成する工程と、

(d)前記配線溝内に第1バリア膜を形成する工程と、

(e)前記第1バリア膜の表面にCuを主成分とするシード膜を形成する工程と、

(f)前記シード膜を電極として電界メッキ法により前記シード膜上にCuを主成分とする金属膜を形成し、前記金属膜によって前記配線溝内を埋め込む工程と、

(g)前記半導体基板の上面を研磨して前記層間絶縁膜の上面を露出させ、前記配線溝内に前記第1バリア膜および前記金属膜を含む金属配線を形成する工程と、

を有し、

前記(d)工程では、前記配線溝内にTaを含む第2バリア膜を形成した後に、前記第2バリア膜上にTiまたはTi化合物からなる第3バリア膜を形成することにより、前記第2バリア膜および前記第3バリア膜を有する前記第1バリア膜を形成するものである。

【発明の効果】

【0032】

本願において開示される発明のうち、代表的なものによって得られる効果を簡単に説明すれば以下のとおりである。

【0033】

上記した本発明の好ましい一実施の形態によれば、銅を含む配線を有する半導体装置において、銅配線の表面に形成されたバリア膜の拡散防止機能を低下させずに銅配線の埋め込み性を向上させることができる。

【図面の簡単な説明】

【0034】

【図1】本発明の実施の形態1である半導体装置の要部断面図である。

【図2】本発明の実施の形態1である半導体装置の製造方法を示す要部断面図である。

【図3】図2に続く半導体装置の製造方法を示す要部断面図である。

【図4】図3に続く半導体装置の製造方法を示す断面図であって、図3の一部を拡大して示す要部断面図である。

【図5】図4に続く半導体装置の製造方法を示す要部断面図である。

【図6】図5に続く半導体装置の製造方法を示す要部断面図である。

【図7】図6に続く半導体装置の製造方法を示す要部断面図である。

【図8】図7に続く半導体装置の製造方法を示す要部断面図である。

【図9】図8に続く半導体装置の製造方法を示す要部断面図である。

【図10】図9の製造工程中の半導体装置を示す俯瞰図である。

【図11】図10に続く半導体装置の製造方法を示す要部断面図である。

【図12】図11の製造工程中の半導体装置を示す俯瞰図である。

【図13】図12に続く半導体装置の製造方法を示す要部断面図である。

【図14】図13に続く半導体装置の製造方法を示す要部断面図である。

【図15】図14に続く半導体装置の製造方法を示す要部断面図である。

【図16】数種類のバリア膜に対する、それらのバリア膜を用いた配線の抵抗値を示すグラフである。

【図17】本発明の実施の形態2である半導体装置の要部断面図である。

【図18】2種類のバリア膜に対する、それらのバリア膜を用いた配線の配線間耐圧を示すグラフである。

【図19】本発明の実施の形態3である半導体装置の要部断面図である。

【図20】本発明の実施の形態3である半導体装置の製造方法を示す要部断面図である。

【図21】図20に続く半導体装置の製造方法を示す要部断面図である。

【図22】図21に続く半導体装置の製造方法を示す要部断面図である。

【図23】図22に続く半導体装置の製造方法を示す要部断面図である。

【図24】図23に続く半導体装置の製造方法を示す要部断面図である。

【図25】比較例として示す半導体装置の要部断面図である。

【図26】比較例として示す半導体装置の製造方法を示す要部断面図である。

【図27】図26に続く半導体装置の製造方法を示す要部断面図である。

【図28】図26に続く半導体装置の製造方法を示す要部断面図である。

【発明を実施するための形態】

【0035】

以下、本発明の実施の形態を図面に基づいて詳細に説明する。なお、実施の形態を説明するための全図において、同一の機能を有する部材には同一の符号を付し、その繰り返しの説明は省略する。また、以下の実施の形態では、特に必要なときを除き、同一または同様な部分の説明を原則として繰り返さない。

【0036】

(実施の形態1)

本発明の実施の形態によるダマシン配線の構造の一例を図1を用いて説明する。図1は半導体基板上に電界効果トランジスであるMOSFET(Metal Oxide Semiconductor Field Effect Transistor)と、MOSFET上の層間絶縁膜に形成された金属配線とを含む半導体装置の一部を示す要部断面図である。

【0037】

図1に示すように本実施の形態の半導体装置は半導体基板SB上にMOSFETQnを形成したものである。半導体基板SB上にはゲート絶縁膜33を介してゲート電極32が形成され、ゲート電極32の下部の半導体基板SBの上面を挟むように、一対のソース・ドレイン領域30が半導体基板SBの上面に形成されている。ゲート電極32およびゲート絶縁膜33の側壁には絶縁膜からなるサイドウォール34が形成され、ソース・ドレイン領域30およびゲート電極32の上面にはそれぞれシリサイド層31が形成されている。

【0038】

MOSFETQnはストッパ絶縁膜35および絶縁膜Ifに覆われており、ストッパ絶縁膜35および絶縁膜Ifには、ソース・ドレイン領域30の上部のシリサイド層31の上面に達するコンタクトホールChが形成されている。コンタクトホールCh内の側壁および底面にはバリア膜BMが形成されており、コンタクトホールCh内には、バリア膜BMを介してコンタクトプラグCpが埋め込まれている。ここで、コンタクトプラグCp、バリア膜BMおよび絶縁膜Ifのそれぞれの上面は同一の高さを有している。

【0039】

絶縁膜If上にはストッパ絶縁膜Sfが形成され、ストッパ絶縁膜Sf上には第1層間絶縁膜1が形成されている。第1層間絶縁膜1およびストッパ絶縁膜Sfからなる絶縁層は、コンタクトプラグCp、バリア膜BMおよび絶縁膜Ifのそれぞれの上面に達する配線溝G1を有しており、配線溝G1内の側壁および底面にはTaN膜2が形成されている。すなわち、配線溝G1内において、第1層間絶縁膜1およびストッパ絶縁膜Sfの側壁並びにコンタクトプラグCp上、バリア膜BM上および絶縁膜If上にTaN膜2が形成されている。

【0040】

配線溝G1底部のTaN膜2上並びに、TaN膜2の側面であって第1層間絶縁膜1およびストッパ絶縁膜Sfと接していない方の側面にはTi膜3が形成されている。配線溝G1底部のTi膜3上並びに、Ti膜3の側面であってTaN膜2と接していない方の側面にはCuシード膜4aが形成されている。配線溝G1底部のCuシード膜4a上並びに、Cuシード膜4aの側面であってTi膜3と接していない方の側面にはCu膜4が形成されており、Cu膜4はTaN膜2、Ti膜3およびCuシード膜4aを介して配線溝G1内に埋め込まれている。

【0041】

すなわち、配線溝G1内に形成されたCu膜4と、第1層間絶縁膜1、ストッパ絶縁膜Sf、絶縁膜If、バリア膜BMおよびコンタクトプラグCpとの間には、Cu膜4側から順に、Cuシード膜4a、Ti膜3、TaN膜2が形成されている。なお、第1層間絶縁膜1、Cu膜4、並びに配線溝G1の側壁に形成されたTaN膜2、Ti膜3およびCuシード膜4aのそれぞれの上面は同一の高さを有している。なお、TaN膜2の膜厚は例えば5nm程度である。Ti膜3の膜厚は10nm未満の膜厚とし、例えば5nmとする。

【0042】

第1層間絶縁膜1上、Cu膜4上、並びに配線溝G1の側壁に形成されたTaN膜2上、Ti膜3上およびCuシード膜4a上にはライナー膜5が形成され、ライナー膜5上には第2層間絶縁膜6が形成されている。第2層間絶縁膜6は、第2層間絶縁膜6の途中深さまで達する配線溝G2を有しており、第2層間絶縁膜6およびライナー膜5からなる絶縁層は、配線溝G2の底面に開口され、Cu膜4の上面に達するビアホールV2を有している。

【0043】

配線溝G2内の側壁および底面並びにビアホールV2の側壁および底面には、TaN膜7が形成されている。すなわち、配線溝G2内およびビアホールV2内において、第1層間絶縁膜1およびライナー膜5の側壁並、配線溝G2の底部である第1層間絶縁膜1の上面上並びにビアホールV2の底面のCu膜4上に、TaN膜7が形成されている。配線溝G2底部およびビアホールV2底部のTaN膜7上並びに、TaN膜7の側面であって第2層間絶縁膜6およびライナー膜5と接していない方の側面にはTi膜8が形成されている。配線溝G2底部およびビアホールV2底部のTi膜8上並びに、Ti膜8の側面であってTaN膜7と接していない方の側面にはCuシード膜9aが形成されている。配線溝G2底部およびビアホールV2底部のCuシード膜9a上並びに、Cuシード膜9aの側面であってTi膜8と接していない方の側面にはCu膜9が形成されており、Cu膜9はTaN膜7、Ti膜8およびCuシード膜9aを介して配線溝G2内およびビアホールV2内に埋め込まれている。

【0044】

なお、本実施の形態では、Ti膜3および8の部材をTi(チタン)としているが、Ti膜3および8の部材には、TiN(窒化チタン)など、チタンを含む他のTi化合物を用いても良い。

【0045】

すなわち、配線溝G2内およびビアホールV2内に形成されたCu膜9と、第2層間絶縁膜6、ライナー膜5およびCu膜4との間には、Cu膜9側から順に、Cuシード膜9a、Ti膜8、TaN膜7が形成されている。なお、第2層間絶縁膜6、Cu膜9、並びに配線溝G2の側壁に形成されたTaN膜7、Ti膜8およびCuシード膜9aのそれぞれの上面は同一の高さを有している。

【0046】

また、第2層間絶縁膜6上、Cu膜9上、並びに配線溝G2の側壁に形成されたTaN膜7上、Ti膜8上およびCuシード膜9a上にはライナー膜10が形成されている。ソース・ドレイン領域30とCu膜9とは、Cuシード膜9a、Ti膜8、TaN膜7、Cu膜4、Cuシード膜4a、Ti膜3、TaN膜2、コンタクトプラグCpおよびシリサイド層31を介して電気的に接続されている。

【0047】

図1に示すMOSFETQnはn型のチャネル領域を有するnチャネル型MOSFETであり、例えば電気信号をスイッチングするスイッチング素子、または電気信号を増幅するための増幅素子として使用されるものである。半導体基板SBは例えばSi(シリコン)からなり、上面にp型の半導体領域を有している。ゲート絶縁膜33、サイドウォール34および絶縁膜Ifはそれぞれ例えばSiO2(酸化シリコン)からなる。ストッパ絶縁膜35は例えばSiN(窒化シリコン)からなり、コンタクトホールChをドライエッチによって開口する際、エッチングストッパ膜として機能するものである。ゲート電極32は例えばP(リン)またはAs(ヒ素)などのn型の不純物が導入された低抵抗のn型半導体膜(ドープトポリシリコン膜)であり、MOSFETQnのゲートとして機能するものである。ソース・ドレイン領域30はn型の不純物が導入されたn型半導体領域であり、MOSFETQnのソースまたはドレインとして機能するものである。

【0048】

シリサイド層31は、例えばNi(ニッケル)とSi(シリコン)の化合物であるNiSi(ニッケルシリサイド)からなり、W(タングステン)からなるコンタクトプラグCpとソース・ドレイン領域30とを電気的に接続している。バリア膜BMは例えばTiまたはTi化合物からなり、コンタクトプラグCp内のW(タングステン)が絶縁膜If内に拡散することを防ぐ機能を有する。ライナー膜5は例えばCVD(Chemical Vapor Deposition)法により形成されるSiC(炭化シリコン)からなる絶縁膜であるが、SiC以外の部材としては、SiN(窒化シリコン)、SiCN(炭窒化シリコン)またはSiOC(炭酸化シリコン)などを例示することができる。第1層間絶縁膜1および第2層間絶縁膜6はSiO2(酸化シリコン)よりも吸湿性が高く、水分を含みやすい絶縁膜により形成されており、例えば、第1層間絶縁膜1および第2層間絶縁膜6はそれぞれ主にSiOCからなる。

【0049】

TaN膜2は主にTaN(窒化タンタル、タンタルナイトライド)からなる導電性の金属膜であり、Cu膜4内のCu(銅)が第1層間絶縁膜1、ストッパ絶縁膜Sfまたは絶縁膜Ifなどに拡散することを防いでいる。また、Ti膜3は主にTi(チタン)からなる導電性の金属膜であり、Cu膜4内のCu(銅)が第1層間絶縁膜1、ストッパ絶縁膜Sfまたは絶縁膜Ifなどに拡散することを防いでいる。また、Ti膜3はCu(銅)との密着性が高く、Ti膜を形成することで配線溝G1内においてCuシード膜4aおよびCu膜4がTaN膜2およびTi膜3を介して隙間なく埋め込まれるようにしている。Cu膜4、9およびCuシード膜4a、9aは主にCu(銅)またはCu(銅)と他の金属(例えばAl(アルミニウム)、Si(シリコン)、Ge(ゲルマニウム)、Ga(ガリウム)またはSn(錫)など)との合金からなる導電膜であり、ソース・ドレイン領域30に所定の電位を供給する導電経路の一部である。

【0050】

ライナー膜5および10は、Cu膜4または9内のCu(銅)がCu膜4または9のそれぞれの上方に拡散することを防ぐ働きを有する。ライナー膜5および10は、それぞれSiN、SiC、SiCNおよびSiOCの内の少なくとも一つを主に含む絶縁膜である。

【0051】

TaN膜7はTaN膜2と同様に、主にTaN(窒化タンタル、タンタルナイトライド)からなる導電性の金属膜であり、Cu膜9内のCu(銅)が第2層間絶縁膜6などに拡散することを防いでいる。Ti膜8は主にTi(チタン)からなる導電性の金属膜であり、Ti膜3と同様にCu膜9内のCu(銅)が第2層間絶縁膜6などに拡散することを防いでいる。Ti膜3と同様に、Ti膜8は配線溝G1内におけるCuシード膜9aおよびCu膜9の埋め込み性を向上させている。

【0052】

次に本実施の形態の半導体装置の製造方法について、図2〜図15を用いて説明する。図2および図3はMOSFETQnを含む本実施の形態の半導体装置の要部断面図であり、図4〜図9、図11および図13〜図15は、図3に示すコンタクトプラグCpの上部を拡大して示す要部断面図である。また、図10および図12は、それぞれ図9および図11に示す領域のビアホールおよび配線溝を示す俯瞰図である。なお、本発明は金属配線に関する発明であり、MOSFET以外のダイオードまたはキャパシタなど他の半導体装置にも適応できるため、ここではMOSFETQnを形成する詳しい工程の説明は省略する。

【0053】

まず、図2に示すように、周知の技術を用いて半導体基板SBの上面にMOSFETQnを形成する。MOSFETQnは半導体基板SBの上面上にゲート絶縁膜33を介して形成されたゲート電極32と、半導体基板SBの上面に形成されたn型半導体領域であるソース・ドレイン領域30を有するものである。ゲート電極32の側壁には主に酸化シリコンからなるサイドウォール34が形成され、ゲート電極32およびソース・ドレイン領域30の上面にはそれぞれシリサイド層31が形成されている。

【0054】

次に、ゲート電極32、ソース・ドレイン領域30、サイドウォール34およびシリサイド層31を含む半導体基板SBの主面(全面)を覆うようにストッパ絶縁膜35を形成する。ストッパ絶縁膜35は例えば窒化シリコン膜からなり、成膜温度(基板温度)450℃程度のプラズマCVD法などにより形成することができる。ストッパ絶縁膜35はMOSFETQn上にコンタクトホールを形成する際のエッチングストッパ膜として機能する。

【0055】

その後、ストッパ絶縁膜35上にストッパ絶縁膜35よりも厚い絶縁膜Ifを形成する。絶縁膜Ifは例えば酸化シリコン膜などからなり、TEOSを用いて成膜温度450℃程度のプラズマCVD法などにより形成することができる。その後、絶縁膜Ifの表面をCMP法により研磨するなどして、絶縁膜Ifの上面を平坦化する。下地段差に起因して絶縁膜Ifの表面に凹凸形状が形成されていても、絶縁膜Ifの表面をCMP法により研磨することにより、その表面が平坦化された絶縁膜を得ることができる。

【0056】

次に、図3に示すように、絶縁膜If上に形成したフォトレジストパターン(図示しない)をエッチングマスクとして用いて、絶縁膜35および絶縁膜Ifをドライエッチングすることにより、ストッパ絶縁膜35および絶縁膜Ifを貫通するコンタクトホール(貫通孔、孔)Chを形成する。コンタクトホールChの底部では、半導体基板SBの主面の一部、例えばソース・ドレイン領域30の表面上のシリサイド層31の上面が露出され、図示していない領域では、ゲート電極32と同層のゲート接続部の上面のシリサイド層の上面が露出される。

【0057】

その後、コンタクトホールCh内および絶縁膜If上にTi(チタン)を含むバリア膜BMを形成した後、コンタクトホールCh内にW(タングステン)膜を充填し、バリア膜BMおよびタングステン膜を研磨することで絶縁膜Ifの上面を露出させ、コンタクトプラグCpを形成する。

【0058】

コンタクトプラグCpを形成するには、例えば、コンタクトホールChの内部(底部および側壁上)を含む絶縁膜If上に、成膜温度(基板温度)450℃程度のプラズマCVD法によりバリア膜(例えばチタン膜、窒化チタン膜、あるいはそれらの積層膜)BMを形成する。それから、タングステン膜などからなる主導体膜をCVD法などによってバリア膜BM上にコンタクトホールChを埋めるように形成した後、絶縁膜If上の不要な主導体膜およびバリア膜BMをCMP法またはエッチバック法などによって除去することにより、コンタクトプラグCpを形成することができる。図示は省略するが、このとき、ゲート電極32と一体となってゲート電極32と同層に形成された接続部の上面にもシリサイド層が形成され、接続部上にはシリサイド層を介してコンタクトプラグが形成される。

【0059】

次に、図4に示すように、コンタクトプラグCpが埋め込まれた絶縁膜If上に、ストッパ絶縁膜Sfおよび配線形成用の第1層間絶縁膜1を順次形成する。なお、図4〜図9、図11および図13〜図15は、図3で示した破線で囲まれた領域を拡大して示す要部断面図であり、コンタクトプラグCpの上部の配線形成領域を示している。ストッパ絶縁膜Sfは第1層間絶縁膜1への溝加工の際にエッチングストッパ膜となる膜であり、第1層間絶縁膜1に対してエッチング選択比を有する材料を用いる。ストッパ絶縁膜Sfは、例えばプラズマCVD法により形成されるSiN(窒化シリコン)膜とし、第1層間絶縁膜1は、例えばプラズマCVD法により形成されるSiOC(炭酸化シリコン)膜とすることができる。

【0060】

次に、図5に示すように、シングルダマシン法により第1層目の配線を形成する。まず、レジストパターン(図示しない)をマスクとしたドライエッチングによって第1層間絶縁膜1およびストッパ絶縁膜Sfの所定の領域に、絶縁膜If、コンタクトプラグCpおよびバリア膜BMの上面を露出する配線溝G1を形成する。

【0061】

次に、図6に示すように、半導体基板SB(図示しない)の主面上(すなわち配線溝G1の底部および側壁上を含む第1層間絶縁膜1上)にTaN(窒化タンタル、タンタルナイトライド)からなるバリア導体膜(バリアメタル膜)であるTaN膜2およびTi(チタン)からなるバリア導体膜であるTi膜3を順次PVD法により形成する。TaN膜2の膜厚は5nm程度である。Ti膜3の膜厚は10nm未満の膜厚とし、例えば5nmとする。ここではバリア導体膜としてTi膜3の下層にTaN膜2を形成しているが、TaN膜2の代わりに、Ta(タンタル)膜またはその他のタンタル化合物、タンタル合金、チタン化合物、チタン合金、タングステン、タングステン化合物、Ru(ルテニウム)若しくはルテニウム化合物などを主に含む導体膜をバリア導体膜として用いることができる。

【0062】

続いて、PVD法によりTi膜3上にCu(銅)からなるCuシード膜4aを形成し、さらに電解メッキ法を用いてCuシード膜4a上にCu膜4を形成することにより、TaN膜2、Ti膜3、Cuシード膜4aおよびCu膜4によって配線溝G1の内部を埋め込む。その後、N2(窒素)などの不活性ガスの雰囲気において製造工程中の半導体装置を熱処理することでCuシード膜4aおよびCu膜4を一体化させ、また、Cuの結晶粒径を成長させて大きくする。なお、このときの熱処理を不活性ガスの雰囲気において行うのは、銅が酸化しやすい材料であり、できるだけ酸素を除去した雰囲気において熱処理を行うことが好ましいためである。Cu膜4が酸化した場合、Cu膜4の導電率が下がり、また、半導体装置の信頼性が低下する。ここでは、熱処理によりCuシード膜4aおよびCu膜4を一体化するが、図ではCuシード膜4aおよびCu膜4を区別して示すものとする。

【0063】

また、TaN膜2およびTi膜3を形成する前に、必要に応じてH2(水素)ガスを用いたアニール処理やプラズマ処理といった前処理(プリクリーン)を行っても良い。

【0064】

次に、図7に示すように、配線溝G1内以外の領域のCu膜4、Cuシード膜4a、Ti膜3およびTaN膜2をCMP法により除去して第1層間絶縁膜1の上面を露出することで、TaN膜2、Ti膜3、Cuシード膜4aおよびCu膜4からなり、銅を主導電材料とする第1層目の金属配線(下層配線M1)を形成する。

【0065】

なお、前述したCuシード膜4aおよびCu膜4を一体化させる熱処理は、図7を用いて説明したCMP法による研磨工程の前ではなく後に行っても良い。

【0066】

次に、図8に示すように、半導体基板SB(図示しない)の主面上(すなわち第1層間絶縁膜1上、TaN膜2上、Ti膜3上、Cuシード膜4a上およびCu膜4上)にSiC(炭化シリコン)からなるライナー膜5およびSiOC(炭酸化シリコン)からなる第2層間絶縁膜6を順次CVD法により形成する。

【0067】

次に、図9および図10に示すように、Cu膜4の上面を露出するビアホールV2を形成する。図10は図9に示す製造工程中の半導体装置の断面を示す俯瞰図である。ビアホールV2は、レジストパターン(図示しない)をマスクとしたドライエッチングによって第2層間絶縁膜6およびライナー膜5の所定の領域に形成する。図10に示すように、例えばビアホールV2は断続的に複数形成する孔であり、溝状の形状を有するものではない。

【0068】

次に、図11および図12に示すように、第2層目の配線を形成するための配線溝G2を形成する。図12は図11に示す製造工程中の半導体装置の断面を示す俯瞰図である。配線溝G2は、レジストパターン(図示しない)をマスクとしたドライエッチングによって第2層間絶縁膜6の所定の領域に形成する。配線溝G2は第2層間絶縁膜6の途中深さまでドライエッチングして形成し、下部のCu膜4の上面は露出しない。

【0069】

なお、本実施の形態では図9および図10に示した工程でビアホールV2を形成した後に図11および図12に示した工程で配線溝G2を形成したが、これらの工程の順番は逆でも良い。すなわち、図8に示すような第2層間絶縁膜6が形成された製造工程中の半導体装置に配線溝G2およびビアホールV2を形成する場合、配線溝G2を形成してから、レジストパターンをマスクとしたドライエッチングによってビアホールV2を形成しても構わない。

【0070】

次に、下層配線M1を形成した工程と同様の工程により第2層目の配線を形成する。ここでは、デュアルダマシン法を用いて第2層目の配線を形成する。つまり、図13に示すように、半導体基板SB(図示しない)の主面上(すなわち配線溝G2の底部および側壁上を含む第2層間絶縁膜6上並びにビアホールV2の底部および側壁上)にTaN(窒化タンタル、タンタルナイトライド)からなるバリア導体膜であるTaN膜7およびTi(チタン)からなるバリア導体膜であるTi膜8を順次PVD法により形成する。TaN膜7の膜厚は5nm程度である。Ti膜8の膜厚は10nm未満の膜厚とし、例えば5nmとする。ここではバリア導体膜としてTi膜8の下層にTaN膜7を形成しているが、TaN膜7の代わりに、Ta(タンタル)膜またはその他のタンタル化合物、タンタル合金、チタン化合物、チタン合金、タングステン、タングステン化合物、Ru(ルテニウム)若しくはルテニウム化合物などを主に含む導体膜をバリア導体膜として用いることができる。

【0071】

続いて、PVD法によりTi膜8上にCuシード膜9aを形成し、さらに電解メッキ法を用いてCuシード膜9a上にCu膜9を形成することにより、TaN膜7、Ti膜8、Cuシード膜9aおよびCu膜9によって配線溝G2およびビアホールV2の内部を埋め込む。その後、N2(窒素)などの不活性ガスの雰囲気において製造工程中の半導体装置を熱処理することでCuシード膜9aおよびCu膜9を一体化させ、また、銅の結晶粒径を成長させて大きくする。なお、このときの熱処理を不活性ガスの雰囲気において行うのは、下層配線M1の形成工程と同様にCu膜9およびCuシード膜9a内の銅が酸化するのを防ぐためである。

【0072】

なお、TaN膜7およびTi膜8を形成する前に、必要に応じてH2(水素)ガスを用いたアニール処理やプラズマ処理といった前処理(プリクリーン)を行っても良い。

【0073】

次に、図14に示すように、配線溝G2内およびビアホールV2内以外の領域のCu膜9、Cuシード膜9a、Ti膜8およびTaN膜7をCMP法により除去して第2層間絶縁膜6の上面を露出することで、TaN膜7、Ti膜8、Cuシード膜9aおよびCu膜9からなり、銅を主導電材料とする第2層目の金属配線(上層配線M2)を形成する。

【0074】

なお、前述したCuシード膜9aおよびCu膜9を一体化させる熱処理は、図14を用いて説明したCMP法による研磨工程の前ではなく後に行っても良い。

【0075】

次に、図15に示すように、半導体基板SB(図示しない)の主面上(すなわち第2層間絶縁膜6上、TaN膜7上、Ti膜8上、Cuシード膜9a上およびCu膜9上)にSiC(炭化シリコン)からなるライナー膜10をCVD法により形成することにより、図1に示す本実施の形態の半導体装置が完成する。本実施の形態では説明を省略するが、上層配線M2よりも上層の領域においては、上層配線M2と同様の工程を行うことで多層のCu配線を形成することができる。

【0076】

次に、図6および図13を用いて説明したバリア膜の形成工程において、Ti膜3および8の膜厚を10nm未満とし、本実施の形態では5nmとした理由を、図16を用いて説明する。図16はバリアメタルの部材および膜厚の異なる5種類のバリア膜を用いた場合のCu配線の抵抗値を計測した累計度数分布を示すグラフである。図16に示すグラフの横軸はCu配線の抵抗値を示し、図16に示すグラフの縦軸は複数回行った実験における正規分布の分位点を示している。

【0077】

図16に示すように、バリア膜を10nmのTa膜および5nmのTaN膜により構成するTa/TaN=10/5nmの抵抗値に対し、バリア膜を5nmのTi膜および5nmのTaN膜により構成するTi/TaN=5/5nmの抵抗値は殆ど差がない。しかし、Ta/TaN=10/5nmの抵抗値に対し、Ti/TaN=10/5nmの抵抗値は顕著に抵抗値が上昇していることが分かる。これは、Ti(チタン)がCu(銅)と合金を形成しやすく、Ti/Cuの合金は純粋なCu(銅)に比べて抵抗値が上がるためである。すなわち、Ti/TaN=10/5nmでは、Cu膜と反応して合金を形成するTi(チタン)の量が多いため、Ti/TaN=5/5nmよりも抵抗値が高くなっている。このことから、Cu膜の界面のTi膜の膜厚を10nmよりも薄くすることで、合金化による実質的な抵抗の上昇が配線抵抗に与える影響を無視できる程度に抑えることができることが分かる。よって、本実施の形態では配線抵抗を下げるためTi膜3および8(図1参照)の膜厚を10nm未満とし、好ましくは5nmとしている。

【0078】

次に、本実施の形態の半導体装置の効果について説明する。

【0079】

従来の技術では、特許文献1および2に示されるように、金属の拡散防止機能の高い材料であるTa(タンタル)を含むバリア膜を用いて、Cu配線内のCu(銅)が層間絶縁膜内に拡散することを防ぐ配線構造とすることが一般的である。

【0080】

しかし、Ta(タンタル)を主に含むバリア膜はTi(チタン)またはW(タングステン)などの他の金属を主に含むバリア膜に比べて金属拡散防止機能は優れているが、Cu(銅)との濡れ性がTi(チタン)に比べて悪い。このため、配線溝内のTa膜またはTaN膜などのバリア膜の表面にCuシード膜を均一に連続的に形成することが難しく、比較例として図26に示すように、Ta膜8aの表面においてCuシード膜9bが複数の固まりとなるおそれがある。すなわち、Ta膜8aの表面を完全に覆わず、Cuシード膜9bの皮膜率が低くなり、Cuシード膜9bが不連続に形成される。この場合、図27および図28に比較例として示すように、Cu膜9を形成した際に、配線溝G2内およびビアホールV2内に空隙(ボイド)11が形成されやすい。

【0081】

図1に示すCuシード膜4aおよび9aはCu膜4および9を電界メッキ法によって形成する際の電極となる膜であり、Cu膜4および9の膜厚を均一に形成する働きを有する。これは、電界メッキ法によって形成されるCu膜4および9の膜厚の均一性は、Cu膜4および9の下地の部材の抵抗値によって左右されるためである。従って、図26に示すように、Cuシード膜9bが配線溝G2内およびビアホールV2内のTa膜8aの表面に均一に形成されなければ、Cu膜9を形成する際の電界メッキ工程においてTa膜8aが電極として働いたとしても、Cu膜9の下地にはCuシード膜9bまたはTa膜8aなど抵抗値の異なる部材が存在することになる。このため、図27または図28に示すように、Cu膜9は膜厚が均一に形成されないため、場合によっては空隙(ボイド)11が形成される。

【0082】

空隙11が形成されると、主にCu膜9からなる配線が途中で途切れたり、ビアホール内で配線が途切れることで上層配線と下層配線とが電気的に接続されなくなるおそれがあり、半導体装置の歩留まりまたは信頼性の低下に繋がる。

【0083】

また、Ta(タンタル)はTi(チタン)に比べて材料の価格が高いため、Ta(タンタル)をバリア膜に用いると半導体装置を用いた製品のコストが増大する問題がある。

【0084】

そこで、本発明者らは、配線のバリア膜にTi(チタン)を主に含む金属膜を用いることを検討した。本実施の形態では、図1に示すように、下層配線M1において銅の拡散を防ぐバリア膜として、Ti膜3およびTi膜3の下層のTaN膜2を形成しており、同様に、上層配線M2において銅の拡散を防ぐバリア膜として、Ti膜8およびTi膜8の下層のTaN膜7を形成している。

【0085】

Ti(チタン)を含むバリア膜はTa(タンタル)またはTa化合物を含むバリア膜に比べ、銅との濡れ性が良い特徴がある。すなわち、Ti(チタン)を含むバリア膜であるTi膜8の表面にCuシード膜9aをPVD法により形成した場合に、Cuシード膜9aが複数の固まりとなることはなく均一に延びるため、Cuシード膜9aがTi膜8の表面を露出することなく覆う。Cu膜9は電界メッキ法によりCuシード膜9a上に均一な膜厚で形成されるため、図26〜図28に示した比較例とは異なり、配線溝G2内およびビアホールV2内に空隙11が形成されることを防ぐことができる。

【0086】

また、Ti(チタン)はTa(タンタル)よりも安価な材料であるため、Ti(チタン)を含むバリア膜を用いることにより、図25に示すようなTa(タンタル)およびTaN(窒化タンタル)をバリア膜として用いた場合に比べて半導体装置を用いた製品のコストを低減することができる。

【0087】

なお、Ti(チタン)はTa(タンタル)に比べて金属の拡散防止機能が低い材料であるが、図1に示すように、Ti膜3および8の下層にTaN膜2および7を形成することにより、拡散防止機能が低下することを防いでいる。

【0088】

以上に述べたように、本実施の形態の半導体装置では、銅を主に含むダマシン配線のバリア膜にTi(チタン)を主に含む10nm未満の金属膜を用いることにより、配線抵抗を上昇させずに、配線内における空隙の発生を防ぎ、半導体装置の歩留まりおよび信頼性を向上させ、また、半導体装置を用いた製品のコストを低減することを可能としている。

【0089】

(実施の形態2)

前記実施の形態では、Cu配線のバリア膜として、Cu膜との界面にTi(チタン)を主に含む金属膜を用い、Ti膜の下層に他のバリア膜を形成する半導体装置について説明した。本実施の形態では、原子数がTi(チタン)よりもN(窒素)の方が多いTiNX(窒化チタン)膜をバリア膜に用いる半導体装置について図16〜図18を用いて説明する。図17は本実施の形態の半導体装置において、MOSFETおよびダマシン配線を含む領域を示す要部断面図である。

【0090】

図17に示すように、本実施の形態の半導体装置は前記実施の形態1における半導体装置とほぼ同様の構造を有しており、前記実施の形態1における半導体装置とほぼ同様の製造工程で製造することができる。本実施の形態の半導体装置は、前記実施の形態1において図1に示したバリア膜であるTaN膜2およびTi膜3に代わって、金属拡散防止機能を有するTiNX膜12が形成され、TaN膜7およびTi膜8に代わって、金属拡散防止機能を有するTiNX膜13が形成されている点で前記実施の形態1における半導体装置と異なる。

【0091】

すなわち、本実施の形態の半導体装置は、半導体基板SB上に形成されたMOSFETQnを有し、MOSFETQnを覆うように形成された絶縁膜If上の第1層間絶縁膜1および第2層間絶縁膜6のそれぞれに配線溝G1およびG2が形成されている。第1層間絶縁膜1と第1層間絶縁膜1の下層のストッパ絶縁膜Sfに形成された配線溝G1内の側壁および底部には膜厚が例えば10nmのTiNX膜12のバリア膜が形成されており、配線溝G1内には、TiNX膜12を介してCuシード膜4aが形成されている。配線溝G1内はTiNX膜12およびCuシード膜4aを介してCu膜4が埋め込まれており、Cu膜4、Cuシード膜4aおよびTiNX膜12によって下層配線M1が構成されている。

【0092】

また、第1層間絶縁膜1および下層配線M1上にライナー膜5を介して第2層間絶縁膜6が配置され、第2層間絶縁膜6には配線溝G2と、配線溝G2の底部から第2層間絶縁膜6およびライナー膜5を貫いて下層配線M1の上面(Cu膜4の上面)に達するビアホールV2とが形成されている。配線溝G2内およびビアホールV2内には、配線溝G1内の下層配線M1と同様に、膜厚が例えば10nmのTiNX膜13およびCuシード膜9aを介してCu膜9が埋め込まれており、Cu膜9、Cuシード膜9aおよびTiNX膜13によって上層配線M2が構成されている。

【0093】

ここで、TiNX膜12および13は金属拡散防止機能を有する導電性の金属膜であり、それぞれの膜厚は10nmである。これは、図16のグラフに示すように、TiN=10nmのバリア膜を有する配線の配線抵抗はTa/TaN=10/5nmのバリア膜を有する配線の配線抵抗とほぼ変わらないためであり、TiNX膜12および13のそれぞれの膜厚を10nm以下にすることで、Ta/TaN=10/5nmのバリア膜に比べて配線抵抗が上昇することを防ぐことができる。

【0094】

本実施の形態の半導体装置の形成方法は、前記実施の形態1のTaN膜2およびTi膜3の形成工程(図6参照)においてTaN膜2およびTi膜3の代わりにTiNX膜12を形成し、TaN膜7およびTi膜8の形成工程(図13参照)においてTaN膜7およびTi膜8の代わりにTiNX膜13を形成する工程以外は前記実施の形態1の半導体装置の製造方法と同様であるので、詳しい説明は省略する。

【0095】

つまり、前記実施の形態1において図6を用いて説明した工程では、半導体基板SB(図示しない)の主面上(すなわち配線溝G1の底部および側壁上を含む第1層間絶縁膜1上)にTiNX(窒化チタン)からなるバリア導体膜であるTiNX膜12をPVD法により形成する。続いて、PVD法によりTiNX膜12上にCu(銅)からなるCuシード膜4aを形成し、さらに電解メッキ法を用いてCuシード膜4a上にCu膜4を形成することにより、TiNX膜12、Cuシード膜4aおよびCu膜4によって配線溝G1の内部を埋め込む。その後、N2(窒素)などの不活性ガスの雰囲気において製造工程中の半導体装置を熱処理することでCuシード膜4aおよびCu膜4を一体化させ、また、Cuの結晶粒径を成長させて大きくする。

【0096】

同様に、前記実施の形態1において図13を用いて説明した工程では、半導体基板SB(図示しない)の主面上(すなわち配線溝G2の底部および側壁上を含む第2層間絶縁膜6上並びにビアホールV2の底部および側壁上)にTiNX(窒化チタン)からなるバリア導体膜であるTiNX膜13をPVD法により形成する。続いて、PVD法によりTiNX膜13上にCuシード膜9aを形成し、さらに電解メッキ法を用いてCuシード膜9a上にCu膜9を形成することにより、TiNX膜13、Cuシード膜9aおよびCu膜9によって配線溝G2およびビアホールV2の内部を埋め込む。その後、N2(窒素)などの不活性ガスの雰囲気において製造工程中の半導体装置を熱処理することでCuシード膜9aおよびCu膜9を一体化させ、また、銅の結晶粒径を成長させて大きくする。

【0097】

上記の工程以外は、前記実施の形態1における半導体装置の製造工程と同様の工程を行うことで、図17に示す本実施の形態の半導体装置が完成する。

【0098】

ここで、TiNX膜12および13を構成するTiNX(窒化チタン)は、原子数がTi(チタン)よりもN(窒素)の方が多い。すなわち、TiNX(窒化チタン)内の一つのTi(チタン)の原子に対するN(窒素)の原子数を表わすXは1未満(X<1)であり、例えばX=0.5とする。つまり、ここではTi(チタン)とN(窒素)の原子数の比はTi:N=2:1となっている。

【0099】

上記のようにバリア膜の材料にTiNX(X<1)を用いる理由を、図18を用いて説明する。図18は、Ti(チタン)とN(窒素)の原子数の比が1対1であるTiNX(X=1)をバリア材料として用いた場合と、TiNX(X=0.5)をバリア材料として用いた場合とにおいて、一定の距離(例えば70nm)を保って配置された2本の金属配線同士の間における配線間耐圧を示したグラフである。図18に示すグラフの横軸は、配線間の電位差を上昇させた場合に電流がショート(短絡)した時の配線間の電位差を示し、図18に示すグラフの縦軸は、複数回行った配線間耐圧の実験における正規分布の分位点を示している。図18に示す白丸はTiNX(X=1)をバリア膜として用いたCu配線の配線間耐圧を示しており、黒丸はTiNX(X=0.5)をバリア膜として用いたCu配線の配線間耐圧を示している。

【0100】

図18に示すように、TiNX(X=1)をバリア膜として用いたCu配線は、TiNX(X=0.5)をバリア膜として用いたCu配線の配線間耐圧よりも低い電位差で配線間がショートしている。すなわち、TiNX(X=0.5)をバリア膜として用いたCu配線の配線間耐圧は約50Vの値を示しているが、TiNX(X=1)をバリア膜として用いたCu配線は、17V〜50Vの範囲にばらついた配線間耐圧の値を示している。このことから、TiNX膜内におけるN(窒素)の比率が大きくなるほど、TiNX膜をバリア膜として用いたCu配線の配線間耐圧が下がることがわかる。

【0101】

また、図18に示すように、TiNX(X=1)をバリア膜として用いたCu配線は横軸方向のばらつきが大きく、配線間耐圧の信頼性が低い。これに対し、TiNX(X=0.5)をバリア膜として用いたCu配線の配線間耐圧は横軸方向のばらつきが少なく、ほぼ縦軸に沿う方向に正規分位点が分布していることから、配線間耐圧の信頼性が高いことがわかる。

【0102】

従って、バリア膜に用いるTiNX(窒化チタン)内のN(窒素)の原子数Xは、X<1ならばほぼ問題ない配線間耐圧および信頼性を示すため、本実施の形態ではX<1とし、好ましくはX=0.5とする。すなわち、本実施の形態におけるバリア膜を構成する窒化チタン膜内のTi(チタン)とN(窒素)の組成比はTi>Nであり、特に、Ti=1としたときにN=0.5であることが好ましい。

【0103】

上記のように、TiNX(窒化チタン)をバリア膜に用いた場合、図25に示すような、Ta(タンタル)およびTaN(窒化タンタル)をバリア膜として形成した場合と同等の金属拡散防止機能を有し、銅と濡れ性および密着性の良いバリア膜を形成することができる。これは、Ti(チタン)にN(窒素)を化合させることにより、バリア膜内において他の元素(例えばCu(銅))と合金化しやすいTi(チタン)を減少させることができるためである。

【0104】

すなわち、N(窒素)がTi(チタン)に化合しているTiNX(窒化チタン)膜は、純粋なTi膜に比べて銅と合金化しにくい。通常、Ti(チタン)とCu(銅)は合金化し易く、銅と合金化したチタン膜は抵抗値が上がる。Ta(タンタル)よりも拡散防止機能の低いTi膜に十分な拡散防止機能を持たせるにはTi膜の膜厚を厚くする必要があるが、銅と合金化し易いTi膜は膜厚が厚すぎると抵抗値が大幅に上昇するため、バリア膜として使用することができなくなる。従って、純粋なTi膜をバリア膜として用いる場合、その膜厚および拡散防止機能に限界があった。

【0105】

これに対し、本実施の形態では、N(窒素)が化合していることで銅と合金化しにくくなったTiNX膜をバリア膜に用いるため、TiNX膜の膜厚を厚くしてもTiNX膜の抵抗値は殆ど上昇しない。従って、TiNX膜の膜厚を厚くすることで十分な拡散防止機能を得ることを可能としている。本実施の形態では、図17に示すTiNX膜12および13のそれぞれの膜厚を10nmとしたが、拡散防止機能をより高めるためにTiNX膜12および13のそれぞれの膜厚を10nmよりも厚い膜厚としても良い。

【0106】

なお、上記の理由から、一つのTi(チタン)原子に対するN(窒素)の原子数を示すXの値は、0.5未満の更に小さい値でも良いが、0よりも大きい値でなければいけない。すなわち、窒素の原子数が0であればバリア膜は純粋なTi膜となるため、銅との合金化によりバリア膜の抵抗値が大幅に上昇し、バリア膜として使用する際に問題が生じる。従って、X>0である必要がある。

【0107】

本実施の形態によれば、銅との濡れ性の良いTi(チタン)を含むTiNX膜をバリア膜に用いることで、図17に示すCu膜4および9の埋め込み性を向上させ、歩留まりを向上させ、半導体装置の信頼性を向上させることができる。また、Ta(タンタル)よりも安価な材料であるTi(チタン)を用いたバリア膜を使用することで、半導体装置を用いた製品のコストを低減することができる。

【0108】

(実施の形態3)

前記実施の形態1における半導体装置ではCu配線のバリア膜としてTi膜およびTaN膜を用いる技術について説明した。これに対し、本実施の形態では、バリア膜を形成する際にTi膜(またはTi合金膜)のみを形成し、その後にTi膜内の下層に形成される酸化チタン膜と、前記Ti膜とによる二層構造のバリア膜を用いた半導体装置について、図19〜図24を用いて説明する。

【0109】

図19に示すように、本実施の形態の半導体装置は前記実施の形態1における半導体装置とほぼ同様の構造を有しており、前記実施の形態1における半導体装置とほぼ同様の製造工程で製造することができる。本実施の形態の半導体装置は、前記実施の形態1において図1に示したバリア膜であるTaN膜2および7に代わって、金属拡散防止機能を有する酸化Ti膜14および16がそれぞれ形成され、Ti膜3および8に代わって、金属拡散防止機能を有するTi膜15および17が形成されている点で前記実施の形態1における半導体装置と異なる。

【0110】

Ti膜15および17並びに酸化Ti膜14および16は導電性を有するバリア膜であり、酸化Ti膜14および16は具体的にはTiOX膜またはTiSiXOYからなる反応層である。なお、前記実施の形態2において説明したTiNX膜12(図17参照)のN(窒素)の原子数Xと、本実施の形態のTiOX膜のO(酸素)の原子数Xと、TiSiXOY膜のSi(シリコン)の原子数Xとは、それぞれ同一の値を示すものではない。

【0111】

ここで、本実施の形態の半導体装置の製造工程を説明する。図19に示す半導体装置を製造するには、まず前記実施の形態1で図5を用いて説明したように、絶縁膜If上のストッパ絶縁膜Sfおよび第1層間絶縁膜1に配線溝G1を形成した後、図20に示すように、PVD法により第1層間絶縁膜1上、配線溝G1の内壁および底面にTi膜14aを形成(堆積)する。Ti膜14aの膜厚は、例えば10nmとする。

【0112】

このとき、Ti膜14aは純粋なTi(チタン)またはその合金からなる膜であるが、PVD法の工程中の熱(例えば450℃程度)により、第1層間絶縁膜1中の水分と反応して酸化される。この場合、図21に示すように、第1層間絶縁膜1との界面を含む第1層間絶縁膜1上、配線溝G1の内壁および底面に酸化Ti膜14が形成され、第1層間絶縁膜1との界面を含む第1層間絶縁膜1上、配線溝G1の内壁および底面には酸化Ti膜14を介してTi膜15が形成される。

【0113】

この後の工程は、配線溝G2を形成する工程まで前記実施の形態1と同様に行う。すなわち、図22に示すように、Ti膜15上にCuシード膜4aおよびCu膜4を形成した後、CMP法により第1層間絶縁膜1上のCu膜4、Cuシード膜4a、Ti膜15および酸化Ti膜14を除去し、第1層間絶縁膜1の上面を露出することで、Cu膜4、Cuシード膜4a、Ti膜15および酸化Ti膜14からなる下層配線M1を形成する。続いて、図23に示すように、第1層間絶縁膜1上および下層配線M1上にライナー膜5および第2層間絶縁膜6を形成し、ライナー膜5および第2層間絶縁膜6を貫通してCu膜4の上面を露出するビアホールV2を形成した後、第2層間絶縁膜6の上面に配線溝G2を形成し、図23の構造を得る。

【0114】

次に、図20および図21を用いて説明した工程と同様に、PVD法によりTi膜を堆積した後に、前記Ti膜内の下層のTi(チタン)が、PVD法の工程中の熱によって第2層間絶縁膜6中の水分と反応して酸化することにより、図24に示すように、第2層間絶縁膜6上および配線溝G2の内壁および底面に、酸化Ti膜16を介してTi膜17が形成される。

【0115】

この後の工程は、前記実施の形態1と同様に行う。すなわち、Ti膜17上にCuシード膜9aおよびCu膜9を形成した後、CMP法により第2層間絶縁膜6上のCu膜9、Cuシード膜9a、Ti膜17および酸化Ti膜16を除去し、第2層間絶縁膜6の上面を露出することで、Cu膜9、Cuシード膜9a、Ti膜17および酸化Ti膜16からなる上層配線M2を形成する。その後、第2層間絶縁膜6上および上層配線M2上にライナー膜10を形成し、図19に示す半導体装置が完成する。

【0116】

本実施の形態では、下層配線M1および上層配線M2のバリア膜を形成する際、Ti膜以外の膜を堆積する工程を有しておらず、堆積したTi膜の底部が酸化することにより、Ti膜とその下層の酸化Ti膜との2層構造のバリア膜を形成している。ここで、図16に示すグラフから、バリア膜としてTi膜を10nm形成した場合(Ti=10nm)と、バリア膜として10nmのTi膜と、その下層の5nmのTaN膜とを積層した場合(Ti/TaN=10/5nm)とを比べると、Ti=10nmよりもTi/TaN=10/5nmの方が配線抵抗が高いことが分かる。

【0117】

Ti/Ta=10/5nmでは、Ta膜上のTi膜の全てがTi膜上に形成されたCuシード膜内およびCu膜内の銅と化合するため、厚さ10nm分のTi(チタン)とCu(銅)との化合物が形成され、バリア膜の抵抗値が大幅に増大する。

【0118】

しかし、本実施の形態のように、バリア膜としてTi膜のみを10nm体積したTi=10nmの場合、層間絶縁膜に含まれる水分によって層間絶縁膜との界面のTi膜は酸化され、TiOXまたはTiSiXOYからなる反応層が形成される。すなわち、層間絶縁膜とTi膜との反応により、Cuシード膜内およびCu膜内の銅と化合することができるTi(チタン)の量は、上述したTi/Ta=10/5nmに対して少ない。このため、Ti(チタン)とCu(銅)との化合物が形成される量は少なく、配線抵抗の上昇を抑えることができる。

【0119】

本実施の形態では配線抵抗の低いバリア膜を形成することができるため、前記実施の形態1と違い、Ti膜の膜厚を厚くすることができる。本実施の形態では配線溝内に形成するTi膜の膜厚を10nmとしているが、それよりも厚い膜厚としても構わない。Ti(チタン)は金属拡散防止機能においてTa(タンタル)に劣るが、本実施の形態では形成するバリア膜の膜厚を厚くすることにより、バリア膜に必要な拡散防止機能を得ることができる。

【0120】

なお、層間絶縁膜と接するTi膜が酸化し易いように、本実施の形態では、水分を吸収し易い(吸湿性が高い)層間絶縁膜を形成することが望ましい。ここでは、図19に示す第1層間絶縁膜1および第2層間絶縁膜6を構成する部材は、SiO2(二酸化シリコン)よりも吸湿性の高い部材であって、例えばSiOC(炭酸化シリコン)を用いるものとする。SiO2(二酸化シリコン)は吸湿性が低いため、SiO2からなる層間絶縁膜に接するTi膜には、殆ど酸化Ti膜は形成されず、SiO2からなる層間絶縁膜に形成された配線溝内にTi膜を介してCu配線を形成した場合、配線抵抗が大幅に高くなる。SiOCはH2O(水)と結びつきやすく、その内部に水分を含みやすい材料であるので、バリア膜として酸化Ti膜を形成するのに適している。

【0121】

なお、図20で配線溝G1内に形成したTi膜14aおよび図24において配線溝G2内に形成したTi膜(図示しない)の部材は、純粋なTi(チタン)からなる膜に限らず、Tiの化合物であっても構わない。例えば、TiNX(X<1)のようなTiN膜でも良い。

【0122】

本実施の形態では、銅との濡れ性の良いTi(チタン)を含むTi膜をバリア膜に用いることで、図19に示すCu膜4および9の埋め込み性を向上させ、歩留まりを向上させ、半導体装置の信頼性を向上させることができる。また、Ta(タンタル)よりも安価な材料であるTi(チタン)を用いたバリア膜を使用することで、半導体装置を用いた製品のコストを低減することができる。

【0123】

以上、本発明者によってなされた発明を実施の形態に基づき具体的に説明したが、本発明は前記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることはいうまでもない。

【0124】

例えば、前記実施の形態1〜3では、図1、図17および図19に示すように、半導体基板上に形成されたMOSFETQnに所定の電位を供給する配線について説明したが、本発明のダマシン配線はMOSFETの上層配線以外のあらゆる用途の配線に広く適用することができる。

【産業上の利用可能性】

【0125】

本発明は、銅配線を有する半導体装置に幅広く利用されるものである。

【符号の説明】

【0126】

1 第1層間絶縁膜

2 TaN膜

2a TaN膜

3 Ti膜

3a Ta膜

4 Cu膜

4a Cuシード膜

5 ライナー膜

6 第2層間絶縁膜

7 TaN膜

7a TaN膜

8 Ti膜

8a Ta膜

9 Cu膜

9a Cuシード膜

9b Cuシード膜

10 ライナー膜

11 空隙

12 TiNX膜

13 TiNX膜

14 酸化Ti膜

14a Ti膜

15 Ti膜

16 酸化Ti膜

17 Ti膜

30 ソース・ドレイン領域

31 シリサイド層

32 ゲート電極

33 ゲート絶縁膜

34 サイドウォール

35 ストッパ絶縁膜

BM バリア膜

Ch コンタクトホール

Cp コンタクトプラグ

G1、G2 配線溝

If 絶縁膜

M1 下層配線

M2 上層配線

Qn MOSFET

SB 半導体基板

Sf ストッパ絶縁膜

V2 ビアホール

【特許請求の範囲】

【請求項1】

半導体基板上に形成された層間絶縁膜と、

前記層間絶縁膜に形成された配線溝と、

前記配線溝内に第1バリア膜を介して形成されたCuを主成分とする金属膜と、

を有し、

前記第1バリア膜は、Taを含む第3バリア膜と、前記第3バリア膜上に前記金属膜と接して形成されたTiを含む第2バリア膜とを有することを特徴とする半導体装置。

【請求項2】

前記第2バリア膜の膜厚は10nm未満であることを特徴とする請求項1記載の半導体装置。

【請求項3】

前記第3バリア膜はTaNからなることを特徴とする請求項1記載の半導体装置。

【請求項4】

前記配線溝の下部には下層配線が形成され、

前記配線溝の底部には、前記配線溝の底面から前記下層配線に達するビアホールが形成され、

前記ビアホールの内壁および底部には前記第1バリア膜が形成され、前記ビアホール内には前記第1バリア膜を介して形成された前記金属膜が埋め込まれていることを特徴とする請求項1記載の半導体装置。

【請求項5】

半導体基板上に形成された層間絶縁膜と、

前記層間絶縁膜に形成された配線溝と、

前記配線溝内にバリア膜を介して形成されたCuを主成分とする金属膜と、

を有し、

前記バリア膜はTiNXからなり、前記バリア膜内のTiの原子数は前記バリア膜内のNの原子数より多いことを特徴とする半導体装置。

【請求項6】

前記バリア膜は、TiNX(ただし、X=0.5)からなることを特徴とする請求項5記載の半導体装置。

【請求項7】

前記配線溝の下部には下層配線が形成され、

前記配線溝の底部には、前記配線溝の底面から前記下層配線に達するビアホールが形成され、

前記ビアホールの内壁および底部には前記バリア膜が形成され、前記ビアホール内には前記バリア膜を介して形成された前記金属膜が埋め込まれていることを特徴とする請求項5記載の半導体装置。

【請求項8】

半導体基板上に形成された層間絶縁膜と、

前記層間絶縁膜に形成された配線溝と、

前記配線溝内にTiまたはTi化合物からなる第1バリア膜を介して形成されたCuを主成分とする金属膜と、

を有し、

前記層間絶縁膜と前記第1バリア膜との界面には、TiSiXOYまたはTiOXからなる反応層がさらに介在していることを特徴とする半導体装置。

【請求項9】

前記層間絶縁膜はSiOCを含むことを特徴とする請求項8記載の半導体装置。

【請求項10】

前記配線溝の下部には下層配線が形成され、

前記配線溝の底部には、前記配線溝の底面から前記下層配線に達するビアホールが形成され、

前記ビアホールの内壁および底部には前記第1バリア膜が形成され、前記ビアホール内には前記第1バリア膜を介して形成された前記金属膜が埋め込まれていることを特徴とする請求項8記載の半導体装置。

【請求項11】

(a)半導体基板を準備する工程と、

(b)前記半導体基板上に層間絶縁膜を形成する工程と、

(c)前記層間絶縁膜の上面に配線溝を形成する工程と、

(d)前記配線溝内に第1バリア膜を形成する工程と、

(e)前記第1バリア膜の表面にCuを主成分とするシード膜を形成する工程と、

(f)前記シード膜を電極として電界メッキ法により前記シード膜上にCuを主成分とする金属膜を形成し、前記金属膜によって前記配線溝内を埋め込む工程と、

(g)前記半導体基板の上面を研磨して前記層間絶縁膜の上面を露出させ、前記配線溝内に前記第1バリア膜および前記金属膜を含む金属配線を形成する工程と、

を有し、

前記(d)工程では、前記配線溝内にTaを含む第2バリア膜を形成した後に、前記第2バリア膜上にTiまたはTi化合物からなる第3バリア膜を形成することにより、前記第2バリア膜および前記第3バリア膜を有する前記第1バリア膜を形成することを特徴とする半導体装置の製造方法。

【請求項12】

前記(d)工程で形成する前記第3バリア膜の膜厚は10nm未満とすることを特徴とする請求項11記載の半導体装置の製造方法。

【請求項13】

前記第2バリア膜はTaNからなることを特徴とする請求項12記載の半導体装置の製造方法。

【請求項14】

(a)前記半導体基板を準備する工程と、

(b)前記半導体基板上に層間絶縁膜を形成する工程と、

(c)前記層間絶縁膜の上面に配線溝を形成する工程と、

(d)前記配線溝内にTiNXからなるバリア膜を形成する工程と、

(e)前記バリア膜の表面にCuを主成分とするシード膜を形成する工程と、

(f)前記シード膜を電極として電界メッキ法により前記シード膜上にCuを主成分とする金属膜を形成し、前記金属膜によって前記配線溝内を埋め込む工程と、

(g)前記半導体基板の上面を研磨して前記層間絶縁膜の上面を露出させ、前記配線溝内に前記バリア膜および前記金属膜を含む金属配線を形成する工程と、

を有し、

前記バリア膜内のTiの原子数は前記バリア膜内のNの原子数より多いことを特徴とする半導体装置の製造方法。

【請求項15】

前記バリア膜は、TiNX(ただし、X=0.5)からなることを特徴とする請求項14記載の半導体装置の製造方法。

【請求項16】

(a)半導体基板を準備する工程と、

(b)前記半導体基板上に層間絶縁膜を形成する工程と、

(c)前記層間絶縁膜の上面に配線溝を形成する工程と、

(d)前記配線溝内に第1バリア膜を形成する工程と、

(e)前記第1バリア膜の表面にCuを主成分とするシード膜を形成する工程と、

(f)前記シード膜を電極として電界メッキ法により前記シード膜上にCuを主成分とする金属膜を形成し、前記金属膜によって前記配線溝内を埋め込む工程と、

(g)前記半導体基板の上面を研磨して前記層間絶縁膜の上面を露出させ、前記配線溝内に前記第1バリア膜および前記金属膜を含む金属配線を形成する工程と、

を有し、

前記(d)工程では、前記配線溝内上にTiを含む第2バリア膜を形成し、前記第2バリア膜の成膜工程において生じる熱により、前記層間絶縁膜と前記第2バリア膜との界面にTiSiXOYまたはTiOXからなる反応層を形成し、前記第2バリア膜と前記反応層とからなる前記第1バリア膜を形成することを特徴とする半導体装置の製造方法。

【請求項17】

前記(b)工程では、SiOCを含む前記層間絶縁膜を形成することを特徴とする請求項16記載の半導体装置の製造方法。

【請求項1】

半導体基板上に形成された層間絶縁膜と、

前記層間絶縁膜に形成された配線溝と、

前記配線溝内に第1バリア膜を介して形成されたCuを主成分とする金属膜と、

を有し、

前記第1バリア膜は、Taを含む第3バリア膜と、前記第3バリア膜上に前記金属膜と接して形成されたTiを含む第2バリア膜とを有することを特徴とする半導体装置。

【請求項2】

前記第2バリア膜の膜厚は10nm未満であることを特徴とする請求項1記載の半導体装置。

【請求項3】

前記第3バリア膜はTaNからなることを特徴とする請求項1記載の半導体装置。

【請求項4】

前記配線溝の下部には下層配線が形成され、

前記配線溝の底部には、前記配線溝の底面から前記下層配線に達するビアホールが形成され、

前記ビアホールの内壁および底部には前記第1バリア膜が形成され、前記ビアホール内には前記第1バリア膜を介して形成された前記金属膜が埋め込まれていることを特徴とする請求項1記載の半導体装置。

【請求項5】

半導体基板上に形成された層間絶縁膜と、

前記層間絶縁膜に形成された配線溝と、

前記配線溝内にバリア膜を介して形成されたCuを主成分とする金属膜と、

を有し、

前記バリア膜はTiNXからなり、前記バリア膜内のTiの原子数は前記バリア膜内のNの原子数より多いことを特徴とする半導体装置。

【請求項6】

前記バリア膜は、TiNX(ただし、X=0.5)からなることを特徴とする請求項5記載の半導体装置。

【請求項7】

前記配線溝の下部には下層配線が形成され、

前記配線溝の底部には、前記配線溝の底面から前記下層配線に達するビアホールが形成され、

前記ビアホールの内壁および底部には前記バリア膜が形成され、前記ビアホール内には前記バリア膜を介して形成された前記金属膜が埋め込まれていることを特徴とする請求項5記載の半導体装置。

【請求項8】

半導体基板上に形成された層間絶縁膜と、

前記層間絶縁膜に形成された配線溝と、

前記配線溝内にTiまたはTi化合物からなる第1バリア膜を介して形成されたCuを主成分とする金属膜と、

を有し、

前記層間絶縁膜と前記第1バリア膜との界面には、TiSiXOYまたはTiOXからなる反応層がさらに介在していることを特徴とする半導体装置。

【請求項9】

前記層間絶縁膜はSiOCを含むことを特徴とする請求項8記載の半導体装置。

【請求項10】

前記配線溝の下部には下層配線が形成され、

前記配線溝の底部には、前記配線溝の底面から前記下層配線に達するビアホールが形成され、

前記ビアホールの内壁および底部には前記第1バリア膜が形成され、前記ビアホール内には前記第1バリア膜を介して形成された前記金属膜が埋め込まれていることを特徴とする請求項8記載の半導体装置。

【請求項11】

(a)半導体基板を準備する工程と、

(b)前記半導体基板上に層間絶縁膜を形成する工程と、

(c)前記層間絶縁膜の上面に配線溝を形成する工程と、

(d)前記配線溝内に第1バリア膜を形成する工程と、

(e)前記第1バリア膜の表面にCuを主成分とするシード膜を形成する工程と、

(f)前記シード膜を電極として電界メッキ法により前記シード膜上にCuを主成分とする金属膜を形成し、前記金属膜によって前記配線溝内を埋め込む工程と、

(g)前記半導体基板の上面を研磨して前記層間絶縁膜の上面を露出させ、前記配線溝内に前記第1バリア膜および前記金属膜を含む金属配線を形成する工程と、

を有し、

前記(d)工程では、前記配線溝内にTaを含む第2バリア膜を形成した後に、前記第2バリア膜上にTiまたはTi化合物からなる第3バリア膜を形成することにより、前記第2バリア膜および前記第3バリア膜を有する前記第1バリア膜を形成することを特徴とする半導体装置の製造方法。

【請求項12】

前記(d)工程で形成する前記第3バリア膜の膜厚は10nm未満とすることを特徴とする請求項11記載の半導体装置の製造方法。

【請求項13】

前記第2バリア膜はTaNからなることを特徴とする請求項12記載の半導体装置の製造方法。

【請求項14】

(a)前記半導体基板を準備する工程と、

(b)前記半導体基板上に層間絶縁膜を形成する工程と、

(c)前記層間絶縁膜の上面に配線溝を形成する工程と、

(d)前記配線溝内にTiNXからなるバリア膜を形成する工程と、

(e)前記バリア膜の表面にCuを主成分とするシード膜を形成する工程と、

(f)前記シード膜を電極として電界メッキ法により前記シード膜上にCuを主成分とする金属膜を形成し、前記金属膜によって前記配線溝内を埋め込む工程と、

(g)前記半導体基板の上面を研磨して前記層間絶縁膜の上面を露出させ、前記配線溝内に前記バリア膜および前記金属膜を含む金属配線を形成する工程と、

を有し、

前記バリア膜内のTiの原子数は前記バリア膜内のNの原子数より多いことを特徴とする半導体装置の製造方法。

【請求項15】

前記バリア膜は、TiNX(ただし、X=0.5)からなることを特徴とする請求項14記載の半導体装置の製造方法。

【請求項16】

(a)半導体基板を準備する工程と、

(b)前記半導体基板上に層間絶縁膜を形成する工程と、

(c)前記層間絶縁膜の上面に配線溝を形成する工程と、

(d)前記配線溝内に第1バリア膜を形成する工程と、

(e)前記第1バリア膜の表面にCuを主成分とするシード膜を形成する工程と、

(f)前記シード膜を電極として電界メッキ法により前記シード膜上にCuを主成分とする金属膜を形成し、前記金属膜によって前記配線溝内を埋め込む工程と、

(g)前記半導体基板の上面を研磨して前記層間絶縁膜の上面を露出させ、前記配線溝内に前記第1バリア膜および前記金属膜を含む金属配線を形成する工程と、

を有し、

前記(d)工程では、前記配線溝内上にTiを含む第2バリア膜を形成し、前記第2バリア膜の成膜工程において生じる熱により、前記層間絶縁膜と前記第2バリア膜との界面にTiSiXOYまたはTiOXからなる反応層を形成し、前記第2バリア膜と前記反応層とからなる前記第1バリア膜を形成することを特徴とする半導体装置の製造方法。

【請求項17】

前記(b)工程では、SiOCを含む前記層間絶縁膜を形成することを特徴とする請求項16記載の半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【公開番号】特開2012−39019(P2012−39019A)

【公開日】平成24年2月23日(2012.2.23)

【国際特許分類】

【出願番号】特願2010−179956(P2010−179956)

【出願日】平成22年8月11日(2010.8.11)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【出願人】(000005821)パナソニック株式会社 (73,050)

【Fターム(参考)】

【公開日】平成24年2月23日(2012.2.23)

【国際特許分類】

【出願日】平成22年8月11日(2010.8.11)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【出願人】(000005821)パナソニック株式会社 (73,050)

【Fターム(参考)】

[ Back to top ]