半導体装置およびその製造方法

【課題】 外部接続用電極の周囲を封止膜で覆ったCSPと呼ばれる半導体装置において、封止膜の上面側を研削するとき、外部接続用電極の上面にバリが発生しないようにする。

【解決手段】 メッキレジスト膜を用いた電解メッキにより外部接続用電極10を形成した後に、サーフェスプレーナーを用いて全ての外部接続用電極10の上部およびそれに対応するメッキレジスト膜の上面側を切って除去し、外部接続用電極10の高さを揃える。この場合、外部接続用電極10の上面にバリが発生することはない。次に、メッキレジスト膜を剥離し、封止膜11を形成し、封止膜11の上面側を研削し、外部接続用電極10上に封止膜11が僅か例えば厚さ数μm〜10μm残るようにする。この場合、外部接続用電極10の上部は研削しないため、外部接続用電極10の上面にバリが発生することはない。次に、外部接続用電極10の上面中央部に対応する部分における封止膜11に、レーザビームを照射するレーザ加工により、開口部12を形成する。

【解決手段】 メッキレジスト膜を用いた電解メッキにより外部接続用電極10を形成した後に、サーフェスプレーナーを用いて全ての外部接続用電極10の上部およびそれに対応するメッキレジスト膜の上面側を切って除去し、外部接続用電極10の高さを揃える。この場合、外部接続用電極10の上面にバリが発生することはない。次に、メッキレジスト膜を剥離し、封止膜11を形成し、封止膜11の上面側を研削し、外部接続用電極10上に封止膜11が僅か例えば厚さ数μm〜10μm残るようにする。この場合、外部接続用電極10の上部は研削しないため、外部接続用電極10の上面にバリが発生することはない。次に、外部接続用電極10の上面中央部に対応する部分における封止膜11に、レーザビームを照射するレーザ加工により、開口部12を形成する。

【発明の詳細な説明】

【技術分野】

【0001】

この発明は半導体装置およびその製造方法に関する。

【背景技術】

【0002】

従来の半導体装置には、CSP(Chip Size

Package)と呼ばれるものが知られている(例えば、特許文献1参照)。この半導体装置は半導体基板を備えている。半導体基板上に設けられた絶縁膜の上面には配線が設けられている。配線のランド上面には外部接続用電極が設けられている。配線を含む絶縁膜の上面において外部接続用電極の周囲には封止膜が設けられている。外部接続用電極の上面には半田バンプが設けられている。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2008−218731号公報

【0004】

上記従来の半導体装置の製造方法では、配線および外部接続用電極を形成した後に、配線および外部接続用電極を含む絶縁膜の上面にエポキシ樹脂からなる封止膜をその厚さが外部接続用電極の高さよりもやや厚くなるように形成している。したがって、この状態では、外部接続用電極の上面は封止膜によって覆われている。次に、封止膜の上面側および外部接続用電極の上部を研削し、外部接続用電極の上面を露出させている(特許文献1の第29段落参照)。次に、露出された外部接続用電極の上面に半田バンプを形成している。

【0005】

ところで、特許文献1に記載はないが、封止膜の上面側および外部接続用電極の上部を研削するとき、研削砥石を用いて研削(少しずつ削り取る)しているので、外部接続用電極の上面に研削により引きちぎられたバリが発生し、外部接続用電極の上面からその周囲における封止膜の上面にバリが形成されてしまう。そこで、一般的には、後処理として、硫酸系のエッチング液を用いてウェットエッチングを行うことにより、外部接続用電極の上面からその周囲における封止膜の上面に形成されたバリを除去することが多い。

【発明の概要】

【発明が解決しようとする課題】

【0006】

しかしながら、外部接続用電極の上面からその周囲における封止膜の上面に形成されたバリを除去すると、このバリの除去に応じて、外部接続用電極の周囲における封止膜の上面に不要な凹部が形成され、またオーバーエッチングにより外部接続用電極の高さが不必要に低くなり、さらに外部接続用電極と封止膜との間にエッチング液が浸み込むと、外部接続用電極の上部外周部が不要にエッチングされて細くなり、外部接続用電極と封止膜との間の密着性の低下の原因となってしまうという問題があった。

また、WLP(Wafer Level Package)をプリント配線板に直接埋込む技術であるEWLP(Embedded Wafer Level Package)では、WLPを埋めん込んだ後に外部接続用電極上の上層絶縁膜に開口部を設けて上層配線と電気的に接続している。しかし、外部接続用電極は、周囲の封止膜と開口部周縁部の上層絶縁膜の二層と接触しているため、層の境界付近において密着性が良くないという問題もあった。

【0007】

そこで、この発明は、外部接続用電極の上面にバリが発生しないようにすることができる半導体装置およびその製造方法を提供することを目的とする。

また、この発明は、外部接続用電極の周側面と上面との境界付近においても密着性が良くなるようにすることができる半導体装置を提供することを目的とする。

【課題を解決するための手段】

【0008】

請求項1に記載の発明に係る半導体装置は、半導体基板と、該半導体基板上に設けられた外部接続用電極と、該外部接続用電極を覆うように設けられ、前記外部接続用電極上面の一部の領域に開口部が設けられている封止膜と、を備えていることを特徴とするものである。

請求項2に記載の発明に係る半導体装置は、請求項1に記載の発明において、前記半導体基板上に絶縁膜が設けられ、前記絶縁膜上に配線が設けられ、前記配線のランド上に前記外部接続用電極が設けられていることを特徴とするものである。

請求項3に記載の発明に係る半導体装置は、請求項1に記載の発明において、前記開口部を除く前記封止膜の上面は平坦であることを特徴とするものである。

請求項4に記載の発明に係る半導体装置は、請求項3に記載の発明において、前記外部接続用電極上における前記封止膜の厚さは数μm〜10μmであることを特徴とするものである。

請求項5に記載の発明に係る半導体装置は、請求項3に記載の発明において、前記封止膜の開口部の直径は、前記外部接続用電極の直径よりも数μm〜10μm小さくなっていることを特徴とするものである。

請求項6に記載の発明に係る半導体装置は、請求項1または2に記載の発明において、前記封止膜の開口部内およびその上方に、半田バンプが少なくとも前記外部接続用電極上面の中心を含む領域に接続されて設けられていることを特徴とするものである。

請求項7に記載の発明に係る半導体装置の製造方法は、半導体基板上に形成された外部接続用電極の周側面および上面を覆うように封止膜を形成し、前記外部接続用電極上面の一部の領域における前記封止膜に開口部を形成することを特徴とするものである。

請求項8に記載の発明に係る半導体装置の製造方法は、請求項7に記載の発明において、前記外部接続用電極の上部をサーフェスプレーナーで除去した後、前記外部接続用電極を覆うように前記封止膜を形成し、前記封止膜に前記開口部を形成する前に、前記外部接続用電極上に前記封止膜が残るように前記封止膜を形成することを特徴とするものである。

請求項9に記載の発明に係る半導体装置の製造方法は、請求項7に記載の発明において、前記外部接続用電極の形成はメッキレジスト膜を用いた電解メッキにより行い、前記メッキレジスト膜を残した状態で前記外部接続用電極の上部およびそれに対応する前記メッキレジスト膜の上面側を切って除去し、この後前記メッキレジスト膜を剥離することを特徴とするものである。

請求項10に記載の発明に係る半導体装置の製造方法は、請求項9に記載の発明において、前記外部接続用電極の上部およびそれに対応する前記メッキレジスト膜の上面側は、サーフェスプレーナーを用いて切ることを特徴とするものである。

請求項11に記載の発明に係る半導体装置の製造方法は、請求項7または9に記載の発明において、前記封止膜の上面側の研削は前記外部接続用電極上に前記封止膜が厚さ数μm〜10μm残るように研削することを特徴とするものである。

請求項12に記載の発明に係る半導体装置の製造方法は、請求項7または9に記載の発明において、前記封止膜の開口部の形成はレーザビームを照射するレーザ加工により行うことを特徴とするものである。

請求項13に記載の発明に係る半導体装置の製造方法は、請求項12に記載の発明において、前記封止膜の開口部の直径は前記外部接続用電極の直径よりも数μm〜10μm小さくなるようにすることを特徴とするものである。

請求項14に記載の発明に係る半導体装置の製造方法は、請求項7または9に記載の発明において、前記封止膜の開口部内およびその上方に、半田バンプを少なくとも前記外部接続用電極上面の中心を含む領域に接続させて形成することを特徴とするものである。

【発明の効果】

【0009】

この発明によれば、半導体基板上に形成された外部接続用電極の周側面および上面を覆うように封止膜を形成し、外部接続用電極上面の一部の領域における封止膜に開口部を形成することにより、外部接続用電極の上面にバリが発生しないようにすることができ、また外部接続用電極の周側面と上面との境界付近においても密着性が良くなるようにすることができる。

【図面の簡単な説明】

【0010】

【図1】この発明の一実施形態としての半導体装置の平面図。

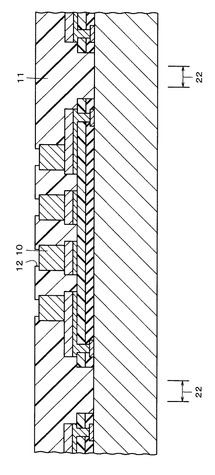

【図2】図1のII−II線にほぼ沿う部分の断面図。

【図3】図1および図2に示す半導体装置の製造方法の一例において、当初準備したものの断面図。

【図4】図3に続く工程の断面図。

【図5】図4に続く工程の断面図。

【図6】図5に続く工程の断面図。

【図7】図6に続く工程の断面図。

【図8】図7に続く工程の断面図。

【図9】図8に続く工程の断面図。

【図10】図9に続く工程の断面図。

【図11】図10に続く工程の断面図。

【図12】図11に続く工程の断面図。

【図13】図12に続く工程の断面図。

【図14】図13に続く工程の断面図。

【発明を実施するための形態】

【0011】

図1はこの発明の一実施形態としての半導体装置の平面図を示し、図2は図1のII−II線にほぼ沿う部分の断面図を示す。この半導体装置は、一般的にはCSPと呼ばれるものであり、シリコン基板(半導体基板)1を備えている。シリコン基板1の上面には、図示していないが、所定の機能の集積回路を構成する素子、例えば、トランジスタ、ダイオード、抵抗、コンデンサなどの素子が形成されている。シリコン基板1の上面周辺部には、上記集積回路の各素子に接続されたアルミニウム系金属などからなる複数の接続パッド2が設けられている。

【0012】

シリコン基板1の周辺部および接続パッド2の中央部を除くシリコン基板1の上面には酸化シリコン、窒化シリコンなどからなるパッシベーション膜(絶縁膜)3が設けられ、接続パッド2の中央部はパッシベーション膜3に設けられた開口部4を介して露出されている。パッシベーション膜3の上面にはポリイミド系樹脂などからなる保護膜(絶縁膜)5が設けられている。パッシベーション膜3の開口部4に対応する部分における保護膜5には開口部6が設けられている。

【0013】

保護膜5の上面には複数の配線7が設けられている。配線7は、保護膜5の上面に設けられた銅などからなる下地金属層8と、下地金属層8の上面に設けられた銅からなる上部金属層9との2層構造となっている。配線7の一端部7aは、パッシベーション膜3および保護膜5の開口部4、6を介して接続パッド2に接続されており、他端部はランド7bとなっており、その間は引き回し線部7cとなっている。配線7のランド7bの上面には、銅からなる柱状の外部接続用電極10が設けられている。

【0014】

配線7を含む保護膜5の上面において外部接続用電極10の周囲にはシリカフィラーを含むエポキシ系樹脂などからなる封止膜11がその上面を平坦とされて設けられている。この場合、外部接続用電極10の上面外周部は封止膜11によって覆われ、外部接続用電極10の上面中央部に対応する部分における封止膜11には開口部12が設けられている。封止膜11の開口部12内およびその上方には半田バンプが外部接続用電極10の上面中央部に接続されて設けられている。

【0015】

次に、この半導体装置の製造方法の一例について説明する。まず、図3に示すように、ウエハ状態のシリコン基板(以下、半導体ウエハ21という)の上面にアルミニウム軽金属などからなる接続パッド2、酸化シリコンなどからなるパッシベーション膜3およびポリイミド系樹脂などからなる保護膜5が形成され、接続パッド2の中央部がパッシベーション膜3および保護膜5の開口部4、6を介して露出されたものを準備する。

【0016】

この場合、半導体ウエハ21の厚さは、図2に示すシリコン基板1の厚さよりも厚くなっている。なお、図2において、符号22で示す領域はダイシングストリートである。そして、ダイシングストリート22およびその両側におけるパッシベーション膜3および保護膜5は除去されている。

【0017】

次に、図4に示すように、パッシベーション膜3および保護膜5の開口部4、6を介して露出された接続パッド2の上面を含む保護膜5の上面並びにダイシングストリート22およびその両側に対応する部分における半導体ウエハ21の上面に下地金属層8を形成する。この場合、下地金属層8は、無電解メッキにより形成された銅層のみであってもよく、またスパッタ法により形成された銅層のみであってもよく、さらにスパッタ法により形成されたチタンなどの薄膜層上にスパッタ法により銅層を形成したものであってもよい。

【0018】

次に、下地金属層8の上面にポジ型の液状レジストからなるメッキレジスト膜23をパターン形成する。この場合、上部金属層9形成領域に対応する部分におけるメッキレジスト膜23には開口部24が形成されている。次に、下地金属層8をメッキ電流路とした銅の電解メッキを行なうと、メッキレジスト膜23の開口部24内の下地金属層8の上面に上部金属層9が形成される。次に、メッキレジスト膜23を剥離する。

【0019】

次に、図5に示すように、上部金属層9を含む下地金属層8の上面にネガ型のドライフィルムレジストからなるメッキレジスト膜25をパターン形成する。この場合、上部金属層9のランド(外部接続用電極10形成領域)に対応する部分におけるメッキレジスト膜25には開口部26が形成されている。

【0020】

次に、下地金属層8をメッキ電流路とした銅の電解メッキを行なうと、メッキレジスト膜25の開口部26内の上部金属層9のランド上面に外部接続用電極10が形成される。この場合、外部接続用電極10の上部は、平坦ではなく、ドーム状となっている。また、外部接続用電極10の高さは、図2に示す外部接続用電極10の高さよりも高くなっている。

【0021】

次に、図6に示すように、サーフェスプレーナー27を準備する。このサーフェスプレーナー27は、固定されて配置され、回転円板28の周辺部下面にバイト29が設けられたものを有し、駆動手段(図示せず)の駆動により、回転円板28と共にバイト29が回転されるようになっている。

【0022】

そして、バイト29の刃先を外部接続用電極10の最終的な高さ位置に位置させ、回転円板28と共にバイト29を回転させる。この状態において、外部接続用電極10およびメッキレジスト膜25などを有する半導体ウエハ21を水平方向に移動させると、回転円板28と共に回転するバイト29により全ての外部接続用電極10の上部およびそれに対応するメッキレジスト膜25の上面側が切られて除去され、図7に示すように、外部接続用電極10の高さが最終的な高さ位置に揃えられ、且つ、外部接続用電極10およびメッキレジスト膜25の上面が面一となる。このように、銅を含む外部接続用電極や金等の柔らかい金属、メッキレジスト膜25であれば、サーフェスプレーナー27で切ることができ、表面を平滑にできる。

【0023】

この場合、全ての外部接続用電極10の上部およびそれに対応するメッキレジスト膜25の上面側がバイト29の刃先により1回でずばっと切られて除去されるため、研削砥石を用いる場合と異なり、外部接続用電極10の上面にバリが発生することはない。したがって、バリを除去するためのウェットエッチングによる後処理を行う必要はなく、外部接続用電極10の高さが不必要に低くなったり、外部接続用電極10の上部外周部が不要に細くなったりすることがない。

【0024】

次に、メッキレジスト膜25を剥離する。なお、メッキレジスト膜25を剥離した後に、サーフェスプレーナー27を用いて外部接続用電極10の上部を切って除去するようにしてもよい。ただし、上述の如く、メッキレジスト膜25を残した状態で外部接続用電極10の上部を切って除去すると、メッキレジスト膜25の存在により、外部接続用電極10が全く倒れないようにすることができる。また、外部接続用電極10の削りかすが上部金属層9に付くことがなく、メッキレジスト膜25を剥離する際に削りかすも一緒に除去できる。

【0025】

次に、上部金属層9をマスクとして上部金属層9下以外の領域における下地金属層8をエッチングして除去すると、図8に示すように、上部金属層9下にのみ下地金属層8が残存される。この状態では、上部金属層9とその下に残存された下地金属層8とにより、2層構造の配線7が形成されている。

【0026】

次に、図9に示すように、ダイシングストリート22およびその両側における半導体ウエハ21の上面並びに配線7および外部接続用電極10を含む保護膜5の上面にスクリーン印刷法などによりシリカフィラーを含むエポキシ系樹脂などからなる封止膜11をその厚さが外部接続用電極10の高さよりもやや厚くなるように形成する。したがって、この状態では、外部接続用電極10の上面は封止膜11によって覆われている。

【0027】

次に、封止膜11の上面側を研削砥石(図示せず)を用いて研削し、図10に示すように、外部接続用電極10上に封止膜11が僅か例えば厚さ数μm〜10μm残るようにするとともに、封止膜11の上面を平坦化する。したがって、この状態では、外部接続用電極10の上面は薄い封止膜11によって覆われている。また、外部接続用電極10の上部は研削しないので、外部接続用電極10の上面にバリが発生することはない。

【0028】

次に、図11に示すように、外部接続用電極10の上面中央部に対応する部分における封止膜11に、CO2、YAGなどのレーザビームを照射するレーザ加工により、開口部12を形成する。開口部12の直径は外部接続用電極10の直径よりも僅か例えば数μm〜10μm小さくなるようにする。したがって、この状態では、外部接続用電極10の上面外周部は封止膜11によって覆われており、外部接続用電極10と封止膜11との間に剥離が生じにくいようにすることができる。

【0029】

次に、図12に示すように、半導体ウエハ21の下面側を適宜に削り、半導体ウエハ21の厚さを薄くする。次に、図13に示すように、封止膜11の開口部12内およびその上方に半田バンプ13を外部接続用電極10の上面中央部に接続させて形成する。次に、図14に示すように、封止膜11および半導体ウエハ21をダイシングストリート22に沿って切断すると、図2に示す半導体装置が複数個得られる。

【符号の説明】

【0030】

1 シリコン基板

2 接続パッド

3 パッシベーション膜

5 保護膜

7 配線

10 外部接続用電極

11 封止膜

12 開口部

13 半田バンプ

21 半導体ウエハ

22 ダイシングストリート

27 サーフェスプレーナー

【技術分野】

【0001】

この発明は半導体装置およびその製造方法に関する。

【背景技術】

【0002】

従来の半導体装置には、CSP(Chip Size

Package)と呼ばれるものが知られている(例えば、特許文献1参照)。この半導体装置は半導体基板を備えている。半導体基板上に設けられた絶縁膜の上面には配線が設けられている。配線のランド上面には外部接続用電極が設けられている。配線を含む絶縁膜の上面において外部接続用電極の周囲には封止膜が設けられている。外部接続用電極の上面には半田バンプが設けられている。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2008−218731号公報

【0004】

上記従来の半導体装置の製造方法では、配線および外部接続用電極を形成した後に、配線および外部接続用電極を含む絶縁膜の上面にエポキシ樹脂からなる封止膜をその厚さが外部接続用電極の高さよりもやや厚くなるように形成している。したがって、この状態では、外部接続用電極の上面は封止膜によって覆われている。次に、封止膜の上面側および外部接続用電極の上部を研削し、外部接続用電極の上面を露出させている(特許文献1の第29段落参照)。次に、露出された外部接続用電極の上面に半田バンプを形成している。

【0005】

ところで、特許文献1に記載はないが、封止膜の上面側および外部接続用電極の上部を研削するとき、研削砥石を用いて研削(少しずつ削り取る)しているので、外部接続用電極の上面に研削により引きちぎられたバリが発生し、外部接続用電極の上面からその周囲における封止膜の上面にバリが形成されてしまう。そこで、一般的には、後処理として、硫酸系のエッチング液を用いてウェットエッチングを行うことにより、外部接続用電極の上面からその周囲における封止膜の上面に形成されたバリを除去することが多い。

【発明の概要】

【発明が解決しようとする課題】

【0006】

しかしながら、外部接続用電極の上面からその周囲における封止膜の上面に形成されたバリを除去すると、このバリの除去に応じて、外部接続用電極の周囲における封止膜の上面に不要な凹部が形成され、またオーバーエッチングにより外部接続用電極の高さが不必要に低くなり、さらに外部接続用電極と封止膜との間にエッチング液が浸み込むと、外部接続用電極の上部外周部が不要にエッチングされて細くなり、外部接続用電極と封止膜との間の密着性の低下の原因となってしまうという問題があった。

また、WLP(Wafer Level Package)をプリント配線板に直接埋込む技術であるEWLP(Embedded Wafer Level Package)では、WLPを埋めん込んだ後に外部接続用電極上の上層絶縁膜に開口部を設けて上層配線と電気的に接続している。しかし、外部接続用電極は、周囲の封止膜と開口部周縁部の上層絶縁膜の二層と接触しているため、層の境界付近において密着性が良くないという問題もあった。

【0007】

そこで、この発明は、外部接続用電極の上面にバリが発生しないようにすることができる半導体装置およびその製造方法を提供することを目的とする。

また、この発明は、外部接続用電極の周側面と上面との境界付近においても密着性が良くなるようにすることができる半導体装置を提供することを目的とする。

【課題を解決するための手段】

【0008】

請求項1に記載の発明に係る半導体装置は、半導体基板と、該半導体基板上に設けられた外部接続用電極と、該外部接続用電極を覆うように設けられ、前記外部接続用電極上面の一部の領域に開口部が設けられている封止膜と、を備えていることを特徴とするものである。

請求項2に記載の発明に係る半導体装置は、請求項1に記載の発明において、前記半導体基板上に絶縁膜が設けられ、前記絶縁膜上に配線が設けられ、前記配線のランド上に前記外部接続用電極が設けられていることを特徴とするものである。

請求項3に記載の発明に係る半導体装置は、請求項1に記載の発明において、前記開口部を除く前記封止膜の上面は平坦であることを特徴とするものである。

請求項4に記載の発明に係る半導体装置は、請求項3に記載の発明において、前記外部接続用電極上における前記封止膜の厚さは数μm〜10μmであることを特徴とするものである。

請求項5に記載の発明に係る半導体装置は、請求項3に記載の発明において、前記封止膜の開口部の直径は、前記外部接続用電極の直径よりも数μm〜10μm小さくなっていることを特徴とするものである。

請求項6に記載の発明に係る半導体装置は、請求項1または2に記載の発明において、前記封止膜の開口部内およびその上方に、半田バンプが少なくとも前記外部接続用電極上面の中心を含む領域に接続されて設けられていることを特徴とするものである。

請求項7に記載の発明に係る半導体装置の製造方法は、半導体基板上に形成された外部接続用電極の周側面および上面を覆うように封止膜を形成し、前記外部接続用電極上面の一部の領域における前記封止膜に開口部を形成することを特徴とするものである。

請求項8に記載の発明に係る半導体装置の製造方法は、請求項7に記載の発明において、前記外部接続用電極の上部をサーフェスプレーナーで除去した後、前記外部接続用電極を覆うように前記封止膜を形成し、前記封止膜に前記開口部を形成する前に、前記外部接続用電極上に前記封止膜が残るように前記封止膜を形成することを特徴とするものである。

請求項9に記載の発明に係る半導体装置の製造方法は、請求項7に記載の発明において、前記外部接続用電極の形成はメッキレジスト膜を用いた電解メッキにより行い、前記メッキレジスト膜を残した状態で前記外部接続用電極の上部およびそれに対応する前記メッキレジスト膜の上面側を切って除去し、この後前記メッキレジスト膜を剥離することを特徴とするものである。

請求項10に記載の発明に係る半導体装置の製造方法は、請求項9に記載の発明において、前記外部接続用電極の上部およびそれに対応する前記メッキレジスト膜の上面側は、サーフェスプレーナーを用いて切ることを特徴とするものである。

請求項11に記載の発明に係る半導体装置の製造方法は、請求項7または9に記載の発明において、前記封止膜の上面側の研削は前記外部接続用電極上に前記封止膜が厚さ数μm〜10μm残るように研削することを特徴とするものである。

請求項12に記載の発明に係る半導体装置の製造方法は、請求項7または9に記載の発明において、前記封止膜の開口部の形成はレーザビームを照射するレーザ加工により行うことを特徴とするものである。

請求項13に記載の発明に係る半導体装置の製造方法は、請求項12に記載の発明において、前記封止膜の開口部の直径は前記外部接続用電極の直径よりも数μm〜10μm小さくなるようにすることを特徴とするものである。

請求項14に記載の発明に係る半導体装置の製造方法は、請求項7または9に記載の発明において、前記封止膜の開口部内およびその上方に、半田バンプを少なくとも前記外部接続用電極上面の中心を含む領域に接続させて形成することを特徴とするものである。

【発明の効果】

【0009】

この発明によれば、半導体基板上に形成された外部接続用電極の周側面および上面を覆うように封止膜を形成し、外部接続用電極上面の一部の領域における封止膜に開口部を形成することにより、外部接続用電極の上面にバリが発生しないようにすることができ、また外部接続用電極の周側面と上面との境界付近においても密着性が良くなるようにすることができる。

【図面の簡単な説明】

【0010】

【図1】この発明の一実施形態としての半導体装置の平面図。

【図2】図1のII−II線にほぼ沿う部分の断面図。

【図3】図1および図2に示す半導体装置の製造方法の一例において、当初準備したものの断面図。

【図4】図3に続く工程の断面図。

【図5】図4に続く工程の断面図。

【図6】図5に続く工程の断面図。

【図7】図6に続く工程の断面図。

【図8】図7に続く工程の断面図。

【図9】図8に続く工程の断面図。

【図10】図9に続く工程の断面図。

【図11】図10に続く工程の断面図。

【図12】図11に続く工程の断面図。

【図13】図12に続く工程の断面図。

【図14】図13に続く工程の断面図。

【発明を実施するための形態】

【0011】

図1はこの発明の一実施形態としての半導体装置の平面図を示し、図2は図1のII−II線にほぼ沿う部分の断面図を示す。この半導体装置は、一般的にはCSPと呼ばれるものであり、シリコン基板(半導体基板)1を備えている。シリコン基板1の上面には、図示していないが、所定の機能の集積回路を構成する素子、例えば、トランジスタ、ダイオード、抵抗、コンデンサなどの素子が形成されている。シリコン基板1の上面周辺部には、上記集積回路の各素子に接続されたアルミニウム系金属などからなる複数の接続パッド2が設けられている。

【0012】

シリコン基板1の周辺部および接続パッド2の中央部を除くシリコン基板1の上面には酸化シリコン、窒化シリコンなどからなるパッシベーション膜(絶縁膜)3が設けられ、接続パッド2の中央部はパッシベーション膜3に設けられた開口部4を介して露出されている。パッシベーション膜3の上面にはポリイミド系樹脂などからなる保護膜(絶縁膜)5が設けられている。パッシベーション膜3の開口部4に対応する部分における保護膜5には開口部6が設けられている。

【0013】

保護膜5の上面には複数の配線7が設けられている。配線7は、保護膜5の上面に設けられた銅などからなる下地金属層8と、下地金属層8の上面に設けられた銅からなる上部金属層9との2層構造となっている。配線7の一端部7aは、パッシベーション膜3および保護膜5の開口部4、6を介して接続パッド2に接続されており、他端部はランド7bとなっており、その間は引き回し線部7cとなっている。配線7のランド7bの上面には、銅からなる柱状の外部接続用電極10が設けられている。

【0014】

配線7を含む保護膜5の上面において外部接続用電極10の周囲にはシリカフィラーを含むエポキシ系樹脂などからなる封止膜11がその上面を平坦とされて設けられている。この場合、外部接続用電極10の上面外周部は封止膜11によって覆われ、外部接続用電極10の上面中央部に対応する部分における封止膜11には開口部12が設けられている。封止膜11の開口部12内およびその上方には半田バンプが外部接続用電極10の上面中央部に接続されて設けられている。

【0015】

次に、この半導体装置の製造方法の一例について説明する。まず、図3に示すように、ウエハ状態のシリコン基板(以下、半導体ウエハ21という)の上面にアルミニウム軽金属などからなる接続パッド2、酸化シリコンなどからなるパッシベーション膜3およびポリイミド系樹脂などからなる保護膜5が形成され、接続パッド2の中央部がパッシベーション膜3および保護膜5の開口部4、6を介して露出されたものを準備する。

【0016】

この場合、半導体ウエハ21の厚さは、図2に示すシリコン基板1の厚さよりも厚くなっている。なお、図2において、符号22で示す領域はダイシングストリートである。そして、ダイシングストリート22およびその両側におけるパッシベーション膜3および保護膜5は除去されている。

【0017】

次に、図4に示すように、パッシベーション膜3および保護膜5の開口部4、6を介して露出された接続パッド2の上面を含む保護膜5の上面並びにダイシングストリート22およびその両側に対応する部分における半導体ウエハ21の上面に下地金属層8を形成する。この場合、下地金属層8は、無電解メッキにより形成された銅層のみであってもよく、またスパッタ法により形成された銅層のみであってもよく、さらにスパッタ法により形成されたチタンなどの薄膜層上にスパッタ法により銅層を形成したものであってもよい。

【0018】

次に、下地金属層8の上面にポジ型の液状レジストからなるメッキレジスト膜23をパターン形成する。この場合、上部金属層9形成領域に対応する部分におけるメッキレジスト膜23には開口部24が形成されている。次に、下地金属層8をメッキ電流路とした銅の電解メッキを行なうと、メッキレジスト膜23の開口部24内の下地金属層8の上面に上部金属層9が形成される。次に、メッキレジスト膜23を剥離する。

【0019】

次に、図5に示すように、上部金属層9を含む下地金属層8の上面にネガ型のドライフィルムレジストからなるメッキレジスト膜25をパターン形成する。この場合、上部金属層9のランド(外部接続用電極10形成領域)に対応する部分におけるメッキレジスト膜25には開口部26が形成されている。

【0020】

次に、下地金属層8をメッキ電流路とした銅の電解メッキを行なうと、メッキレジスト膜25の開口部26内の上部金属層9のランド上面に外部接続用電極10が形成される。この場合、外部接続用電極10の上部は、平坦ではなく、ドーム状となっている。また、外部接続用電極10の高さは、図2に示す外部接続用電極10の高さよりも高くなっている。

【0021】

次に、図6に示すように、サーフェスプレーナー27を準備する。このサーフェスプレーナー27は、固定されて配置され、回転円板28の周辺部下面にバイト29が設けられたものを有し、駆動手段(図示せず)の駆動により、回転円板28と共にバイト29が回転されるようになっている。

【0022】

そして、バイト29の刃先を外部接続用電極10の最終的な高さ位置に位置させ、回転円板28と共にバイト29を回転させる。この状態において、外部接続用電極10およびメッキレジスト膜25などを有する半導体ウエハ21を水平方向に移動させると、回転円板28と共に回転するバイト29により全ての外部接続用電極10の上部およびそれに対応するメッキレジスト膜25の上面側が切られて除去され、図7に示すように、外部接続用電極10の高さが最終的な高さ位置に揃えられ、且つ、外部接続用電極10およびメッキレジスト膜25の上面が面一となる。このように、銅を含む外部接続用電極や金等の柔らかい金属、メッキレジスト膜25であれば、サーフェスプレーナー27で切ることができ、表面を平滑にできる。

【0023】

この場合、全ての外部接続用電極10の上部およびそれに対応するメッキレジスト膜25の上面側がバイト29の刃先により1回でずばっと切られて除去されるため、研削砥石を用いる場合と異なり、外部接続用電極10の上面にバリが発生することはない。したがって、バリを除去するためのウェットエッチングによる後処理を行う必要はなく、外部接続用電極10の高さが不必要に低くなったり、外部接続用電極10の上部外周部が不要に細くなったりすることがない。

【0024】

次に、メッキレジスト膜25を剥離する。なお、メッキレジスト膜25を剥離した後に、サーフェスプレーナー27を用いて外部接続用電極10の上部を切って除去するようにしてもよい。ただし、上述の如く、メッキレジスト膜25を残した状態で外部接続用電極10の上部を切って除去すると、メッキレジスト膜25の存在により、外部接続用電極10が全く倒れないようにすることができる。また、外部接続用電極10の削りかすが上部金属層9に付くことがなく、メッキレジスト膜25を剥離する際に削りかすも一緒に除去できる。

【0025】

次に、上部金属層9をマスクとして上部金属層9下以外の領域における下地金属層8をエッチングして除去すると、図8に示すように、上部金属層9下にのみ下地金属層8が残存される。この状態では、上部金属層9とその下に残存された下地金属層8とにより、2層構造の配線7が形成されている。

【0026】

次に、図9に示すように、ダイシングストリート22およびその両側における半導体ウエハ21の上面並びに配線7および外部接続用電極10を含む保護膜5の上面にスクリーン印刷法などによりシリカフィラーを含むエポキシ系樹脂などからなる封止膜11をその厚さが外部接続用電極10の高さよりもやや厚くなるように形成する。したがって、この状態では、外部接続用電極10の上面は封止膜11によって覆われている。

【0027】

次に、封止膜11の上面側を研削砥石(図示せず)を用いて研削し、図10に示すように、外部接続用電極10上に封止膜11が僅か例えば厚さ数μm〜10μm残るようにするとともに、封止膜11の上面を平坦化する。したがって、この状態では、外部接続用電極10の上面は薄い封止膜11によって覆われている。また、外部接続用電極10の上部は研削しないので、外部接続用電極10の上面にバリが発生することはない。

【0028】

次に、図11に示すように、外部接続用電極10の上面中央部に対応する部分における封止膜11に、CO2、YAGなどのレーザビームを照射するレーザ加工により、開口部12を形成する。開口部12の直径は外部接続用電極10の直径よりも僅か例えば数μm〜10μm小さくなるようにする。したがって、この状態では、外部接続用電極10の上面外周部は封止膜11によって覆われており、外部接続用電極10と封止膜11との間に剥離が生じにくいようにすることができる。

【0029】

次に、図12に示すように、半導体ウエハ21の下面側を適宜に削り、半導体ウエハ21の厚さを薄くする。次に、図13に示すように、封止膜11の開口部12内およびその上方に半田バンプ13を外部接続用電極10の上面中央部に接続させて形成する。次に、図14に示すように、封止膜11および半導体ウエハ21をダイシングストリート22に沿って切断すると、図2に示す半導体装置が複数個得られる。

【符号の説明】

【0030】

1 シリコン基板

2 接続パッド

3 パッシベーション膜

5 保護膜

7 配線

10 外部接続用電極

11 封止膜

12 開口部

13 半田バンプ

21 半導体ウエハ

22 ダイシングストリート

27 サーフェスプレーナー

【特許請求の範囲】

【請求項1】

半導体基板と、

該半導体基板上に設けられた外部接続用電極と、

該外部接続用電極を覆うように設けられ、前記外部接続用電極上面の一部の領域に開口部が設けられている封止膜と、

を備えていることを特徴とする半導体装置。

【請求項2】

請求項1に記載の発明において、前記半導体基板上に絶縁膜が設けられ、前記絶縁膜上に配線が設けられ、前記配線のランド上に前記外部接続用電極が設けられていることを特徴とする半導体装置。

【請求項3】

請求項1に記載の発明において、前記開口部を除く前記封止膜の上面は平坦であることを特徴とする半導体装置。

【請求項4】

請求項3に記載の発明において、前記外部接続用電極上における前記封止膜の厚さは数μm〜10μmであることを特徴とする半導体装置。

【請求項5】

請求項3に記載の発明において、前記封止膜の開口部の直径は、前記外部接続用電極の直径よりも数μm〜10μm小さくなっていることを特徴とする半導体装置。

【請求項6】

請求項1または2に記載の発明において、前記封止膜の開口部内およびその上方に、半田バンプが少なくとも前記外部接続用電極上面の中心を含む領域に接続されて設けられていることを特徴とする半導体装置。

【請求項7】

半導体基板上に形成された外部接続用電極の周側面および上面を覆うように封止膜を形成し、

前記外部接続用電極上面の一部の領域における前記封止膜に開口部を形成することを特徴とする半導体装置の製造方法。

【請求項8】

請求項7に記載の発明において、

前記外部接続用電極の上部をサーフェスプレーナーで除去した後、前記外部接続用電極を覆うように前記封止膜を形成し、

前記封止膜に前記開口部を形成する前に、前記外部接続用電極上に前記封止膜が残るように前記封止膜を形成することを特徴とする半導体装置の製造方法。

【請求項9】

請求項7に記載の発明において、前記外部接続用電極の形成はメッキレジスト膜を用いた電解メッキにより行い、前記メッキレジスト膜を残した状態で前記外部接続用電極の上部およびそれに対応する前記メッキレジスト膜の上面側を切って除去し、この後前記メッキレジスト膜を剥離することを特徴とする半導体装置の製造方法。

【請求項10】

請求項9に記載の発明において、前記外部接続用電極の上部およびそれに対応する前記メッキレジスト膜の上面側は、サーフェスプレーナーを用いて切ることを特徴とする半導体装置の製造方法。

【請求項11】

請求項7または9に記載の発明において、前記封止膜の上面側の研削は前記外部接続用電極上に前記封止膜が厚さ数μm〜10μm残るように研削することを特徴とする半導体装置の製造方法。

【請求項12】

請求項7または9に記載の発明において、前記封止膜の開口部の形成はレーザビームを照射するレーザ加工により行うことを特徴とする半導体装置の製造方法。

【請求項13】

請求項12に記載の発明において、前記封止膜の開口部の直径は前記外部接続用電極の直径よりも数μm〜10μm小さくなるようにすることを特徴とする半導体装置の製造方法。

【請求項14】

請求項7または9に記載の発明において、前記封止膜の開口部内およびその上方に、半田バンプを少なくとも前記外部接続用電極上面の中心を含む領域に接続させて形成することを特徴とする半導体装置の製造方法。

【請求項1】

半導体基板と、

該半導体基板上に設けられた外部接続用電極と、

該外部接続用電極を覆うように設けられ、前記外部接続用電極上面の一部の領域に開口部が設けられている封止膜と、

を備えていることを特徴とする半導体装置。

【請求項2】

請求項1に記載の発明において、前記半導体基板上に絶縁膜が設けられ、前記絶縁膜上に配線が設けられ、前記配線のランド上に前記外部接続用電極が設けられていることを特徴とする半導体装置。

【請求項3】

請求項1に記載の発明において、前記開口部を除く前記封止膜の上面は平坦であることを特徴とする半導体装置。

【請求項4】

請求項3に記載の発明において、前記外部接続用電極上における前記封止膜の厚さは数μm〜10μmであることを特徴とする半導体装置。

【請求項5】

請求項3に記載の発明において、前記封止膜の開口部の直径は、前記外部接続用電極の直径よりも数μm〜10μm小さくなっていることを特徴とする半導体装置。

【請求項6】

請求項1または2に記載の発明において、前記封止膜の開口部内およびその上方に、半田バンプが少なくとも前記外部接続用電極上面の中心を含む領域に接続されて設けられていることを特徴とする半導体装置。

【請求項7】

半導体基板上に形成された外部接続用電極の周側面および上面を覆うように封止膜を形成し、

前記外部接続用電極上面の一部の領域における前記封止膜に開口部を形成することを特徴とする半導体装置の製造方法。

【請求項8】

請求項7に記載の発明において、

前記外部接続用電極の上部をサーフェスプレーナーで除去した後、前記外部接続用電極を覆うように前記封止膜を形成し、

前記封止膜に前記開口部を形成する前に、前記外部接続用電極上に前記封止膜が残るように前記封止膜を形成することを特徴とする半導体装置の製造方法。

【請求項9】

請求項7に記載の発明において、前記外部接続用電極の形成はメッキレジスト膜を用いた電解メッキにより行い、前記メッキレジスト膜を残した状態で前記外部接続用電極の上部およびそれに対応する前記メッキレジスト膜の上面側を切って除去し、この後前記メッキレジスト膜を剥離することを特徴とする半導体装置の製造方法。

【請求項10】

請求項9に記載の発明において、前記外部接続用電極の上部およびそれに対応する前記メッキレジスト膜の上面側は、サーフェスプレーナーを用いて切ることを特徴とする半導体装置の製造方法。

【請求項11】

請求項7または9に記載の発明において、前記封止膜の上面側の研削は前記外部接続用電極上に前記封止膜が厚さ数μm〜10μm残るように研削することを特徴とする半導体装置の製造方法。

【請求項12】

請求項7または9に記載の発明において、前記封止膜の開口部の形成はレーザビームを照射するレーザ加工により行うことを特徴とする半導体装置の製造方法。

【請求項13】

請求項12に記載の発明において、前記封止膜の開口部の直径は前記外部接続用電極の直径よりも数μm〜10μm小さくなるようにすることを特徴とする半導体装置の製造方法。

【請求項14】

請求項7または9に記載の発明において、前記封止膜の開口部内およびその上方に、半田バンプを少なくとも前記外部接続用電極上面の中心を含む領域に接続させて形成することを特徴とする半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【公開番号】特開2012−74461(P2012−74461A)

【公開日】平成24年4月12日(2012.4.12)

【国際特許分類】

【出願番号】特願2010−216881(P2010−216881)

【出願日】平成22年9月28日(2010.9.28)

【出願人】(311014314)株式会社テラミクロス (42)

【Fターム(参考)】

【公開日】平成24年4月12日(2012.4.12)

【国際特許分類】

【出願日】平成22年9月28日(2010.9.28)

【出願人】(311014314)株式会社テラミクロス (42)

【Fターム(参考)】

[ Back to top ]