半導体装置およびその製造方法

【課題】トンネルFETのオン電流の劣化を抑制しつつ、オフ電流を低減することが可能な半導体装置を提供する。

【解決手段】実施形態によれば、半導体装置は、溝が形成された基板と、前記基板上の前記溝に隣接する位置にゲート絶縁膜を介して形成され、前記溝の反対側に位置する第1側面と、前記溝側に位置する第2側面とを有するゲート電極とを備える。さらに、前記装置は、前記ゲート電極の前記第1側面に形成された第1の側壁絶縁膜と、前記ゲート電極の前記第2側面と前記溝の側面に形成された第2の側壁絶縁膜とを備える。さらに、前記装置は、前記基板内において、前記ゲート電極の前記第1側面に対し前記第1の側壁絶縁膜側に形成された、第1導電型のソース領域と、前記基板内において、前記ゲート電極の前記第2側面と前記溝の側面に対し前記第2の側壁絶縁膜側に形成された、第2導電型のドレイン領域とを備える。

【解決手段】実施形態によれば、半導体装置は、溝が形成された基板と、前記基板上の前記溝に隣接する位置にゲート絶縁膜を介して形成され、前記溝の反対側に位置する第1側面と、前記溝側に位置する第2側面とを有するゲート電極とを備える。さらに、前記装置は、前記ゲート電極の前記第1側面に形成された第1の側壁絶縁膜と、前記ゲート電極の前記第2側面と前記溝の側面に形成された第2の側壁絶縁膜とを備える。さらに、前記装置は、前記基板内において、前記ゲート電極の前記第1側面に対し前記第1の側壁絶縁膜側に形成された、第1導電型のソース領域と、前記基板内において、前記ゲート電極の前記第2側面と前記溝の側面に対し前記第2の側壁絶縁膜側に形成された、第2導電型のドレイン領域とを備える。

【発明の詳細な説明】

【技術分野】

【0001】

本発明の実施形態は、半導体装置およびその製造方法に関する。

【背景技術】

【0002】

近年、MOSFETを越える高性能化、低消費電力化を目指して、トンネルFET(TFET)が精力的に研究されている。トンネルFETでは、ソース領域とドレイン領域の導電型が異なるため、ゲート電圧が正でも負でもトンネルFETがオンになるスイッチングの両極性が問題となる。これは、オフ電流の増大や、トンネルFETの特性ばらつきの増大などをもたらす。このオフ電流を抑制する手法はいくつか提案されているが、これらの多くは、オン電流の劣化や、SS(Sub-threshold Swing)が緩やかになるなどの弊害をもたらし、トンネルFETの低消費電力化を妨げる要因となってしまう。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開平11−17184号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

トンネルFETのオン電流の劣化を抑制しつつ、オフ電流を低減することが可能な半導体装置およびその製造方法を提供する。

【課題を解決するための手段】

【0005】

一の実施形態による半導体装置は、溝が形成された基板と、前記基板上の前記溝に隣接する位置にゲート絶縁膜を介して形成され、前記溝の反対側に位置する第1側面と、前記溝側に位置する第2側面とを有するゲート電極とを備える。さらに、前記装置は、前記ゲート電極の前記第1側面に形成された第1の側壁絶縁膜と、前記ゲート電極の前記第2側面と前記溝の側面に形成された第2の側壁絶縁膜とを備える。さらに、前記装置は、前記基板内において、前記ゲート電極の前記第1側面に対し前記第1の側壁絶縁膜側に形成された、第1導電型のソース領域と、前記基板内において、前記ゲート電極の前記第2側面と前記溝の側面に対し前記第2の側壁絶縁膜側に形成された、第2導電型のドレイン領域とを備える。

【図面の簡単な説明】

【0006】

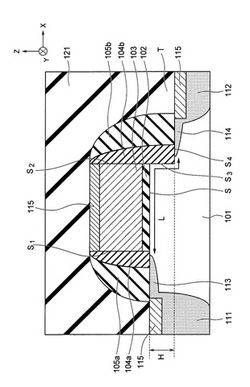

【図1】第1実施形態の半導体装置の構造を示す断面図である。

【図2】第1実施形態の半導体装置の製造方法を示す断面図(1/4)である。

【図3】第1実施形態の半導体装置の製造方法を示す断面図(2/4)である。

【図4】第1実施形態の半導体装置の製造方法を示す断面図(3/4)である。

【図5】第1実施形態の半導体装置の製造方法を示す断面図(4/4)である。

【図6】第2実施形態の半導体装置の構造を示す断面図である。

【図7】第2実施形態の半導体装置の製造方法を示す断面図(1/3)である。

【図8】第2実施形態の半導体装置の製造方法を示す断面図(2/3)である。

【図9】第2実施形態の半導体装置の製造方法を示す断面図(3/3)である。

【発明を実施するための最良の形態】

【0007】

以下、本発明の実施形態を、図面を参照して説明する。

【0008】

(第1実施形態)

図1は、第1実施形態の半導体装置の構造を示す断面図である。

【0009】

図1の半導体装置は、トンネルFETの構成要素として、基板101と、ゲート絶縁膜102と、ゲート電極103と、第1、第2の側壁絶縁膜104a、104bと、第3、第4の側壁絶縁膜105a、105bと、ソース領域111と、ドレイン領域112と、ソースエクステンション領域113と、ドレインエクステンション領域114と、シリサイド層115と、層間絶縁膜121とを備えている。

【0010】

基板101は例えば、Si基板、GaAs基板、InP基板などの半導体基板である。図1には、基板101の主面に平行で、互いに垂直なX方向およびY方向と、基板101の主面に垂直なZ方向が示されている。基板101は、図1に示すように、Y方向に延びる溝Tを有している。符号S3、S4はそれぞれ、溝Tの側面と底面を示す。本実施形態の基板101は、i型基板、またはソース領域111やドレイン領域112よりも不純物濃度が低いp型基板またはn型基板である。なお、基板101は、SOI(Silicon on Insulator)基板またはGOI(Germanium on Insulator)基板でもよい。

【0011】

ゲート電極103は、基板101上の溝Tに隣接する位置に、ゲート絶縁膜102を介して形成されている。ゲート絶縁膜102の例としては、シリコン酸化膜(SiO2)、シリコン酸窒化膜(SiON)、high−k絶縁膜などが挙げられる。また、ゲート電極103の例としては、ポリシリコン層、シリサイド層、メタル層や、これらの2種類以上を含む積層膜などが挙げられる。符号S1、S2はそれぞれ、ゲート電極103の第1側面と第2側面を示す。第1側面S1は、溝Tの反対側に位置し、第2側面S1は、溝T側に位置している。

【0012】

第1の側壁絶縁膜104aは、ゲート電極103の第1側面S1に形成されている。また、第2の側壁絶縁膜104bは、ゲート電極103の第2側面S2と溝Tの側面S3に形成されている。よって、第2の側壁絶縁膜104bの底面の高さは、基板101の上面Sや、第1の側壁絶縁膜104aの底面よりも低くなっている。第1、第2の側壁絶縁膜104a、104bの例としては、シリコン酸化膜や、シリコン窒化膜(SiN)などが挙げられる。

【0013】

第3の側壁絶縁膜105aは、ゲート電極103の第1側面S1に、第1の側壁絶縁膜104aを介して形成されている。また、第4の側壁絶縁膜105bは、ゲート電極103の第2側面S2と溝Tの側面S3に、第2の側壁絶縁膜104bを介して形成されている。よって、第4の側壁絶縁膜105bの底面の高さは、基板101の上面Sや、第3の側壁絶縁膜105aの底面よりも低くなっている。第3、第4の側壁絶縁膜105a、105bの例としては、シリコン酸化膜や、シリコン窒化膜などが挙げられる。

【0014】

ソース領域111とドレイン領域112は、基板101内にゲート電極103を挟むように形成されている。具体的には、ソース領域111は、基板101内において、ゲート電極103の第1側面S1に対し、第1の側壁絶縁膜104a側に形成されている。また、ドレイン領域112は、基板101内において、ゲート電極103の第2側面S2と溝Tの側面S3に対し、第2の側壁絶縁膜104b側に形成されている。本実施形態では、ソース領域111は、p型領域であり、ドレイン領域112は、ソース領域111とは逆導電型のn型領域である。p導電型とn導電型はそれぞれ、第1導電型と第2導電型の例である。

【0015】

ソースエクステンション領域113は、ソース領域111とドレイン領域112との間において、第1、第3の側壁絶縁膜104a、105aの下部に形成されている。また、ドレインエクステンション領域114は、ソース領域111とドレイン領域112との間において、第2、第4の側壁絶縁膜104b、105bの下部に形成されている。本実施形態では、ソースエクステンション領域113と、ドレインエクステンション領域114はそれぞれ、p型領域とn型領域である。

【0016】

シリサイド層115は、ゲート電極103、ソース領域111、ドレイン領域112内の上部に形成されている。シリサイド層115の例としては、NiSi層、PtSi層、NiPtSi層、NiCoSi層、Co2Si層などが挙げられる。なお、基板101やゲート電極103がシリコン以外の半導体(例えばゲルマニウム)で形成されている場合には、シリサイド層115の代わりに、この半導体と金属との合金層を形成してもよい。このような合金層の例としては、NiGe層などが挙げられる。

【0017】

層間絶縁膜121は、基板101上に、トンネルFETを覆うように形成されている。層間絶縁膜121の例としては、シリコン酸化膜などが挙げられる。

【0018】

なお、図1のトンネルFETは、n型FETであるが、p型FETとしてもよい。この場合、ソース領域111とソースエクステンション領域113は、n型領域となり、ドレイン領域112とドレインエクステンション領域114は、p型領域となる。

【0019】

また、第2の側壁絶縁膜104bは、第1の絶縁材料を用いて、ゲート電極103の第2側面S2に形成された第1部分と、第1の絶縁材料と異なる第2の絶縁材料を用いて、溝Tの側面S3に形成された第2部分を有していてもよい。すなわち、第2側面S2に形成された第1部分と、側面S3に形成された第2部分は、別々の絶縁膜で形成されていてもよい。

【0020】

同様に、第4の側壁絶縁膜105bは、第3の絶縁材料を用いて、ゲート電極103の第2側面S2に形成された第3部分と、第3の絶縁材料と異なる第4の絶縁材料を用いて、溝Tの側面S3に形成された第4部分を有していてもよい。

【0021】

(1)第1実施形態のトンネルFETの利点

以上のように、図1では、第2の側壁絶縁膜104bが、ゲート電極103の第2側面S2と溝Tの側面S3に形成されている。その結果、第2の側壁絶縁膜104bは、ゲート絶縁膜102よりも下に埋め込まれている。以下、このような第2の側壁絶縁膜104bを有するトンネルFETの利点について説明する。

【0022】

図1では、ゲート電極103に正の電圧を印加すると、ソース領域111の価電子帯を占有する電子が、BTBT(Band to Band Tunneling)と呼ばれるトンネル効果により、チャネル領域中の伝導帯に移動する。そして、この電子がドレイン領域112に到達することで、ソース領域111とドレイン領域112との間にオン電流が流れる。

【0023】

一方、ゲート電極103に負の電圧を印加すると、チャネル領域の価電子帯を占有する電子が、BTBTにより、ドレイン領域112中の伝導帯に移動する。そして、電子の移動に伴いチャネル領域内に生じた正孔がソース領域111に到達することで、ソース領域111とドレイン領域112との間にオフ電流が流れる。この電流は、GIDL(Gate Induced Drain Leakage)電流と呼ばれる。

【0024】

一般に、GIDL電流の原因となるBTBTは、ドレイン領域112の端部で生じる。本実施形態では、第2の側壁絶縁膜104bにより、このBTBTの際の電子のトンネリング確率を減少させ、GIDL電流を低減することができる。理由は、第2の側壁絶縁膜104bにより、トンネルFETの実効的チャネル長Lを長くすることができるからである。実効的チャネル長Lの増加は、BTBTのトンネリング距離を増大させ、トンネリング距離の増大は、トンネリング確率を指数関数的に減少させる。本実施形態では、実効的チャネル長Lが、溝Tの深さHの分だけ、本来のチャネル長よりも長くなっている。

【0025】

また、第2の側壁絶縁膜104bは、チャネル領域とドレイン領域112との間を移動する電子の障壁として機能する。この観点から言うと、第2の側壁絶縁膜104bの材料は、バンドギャップの大きい絶縁体とすることが望ましい。理由は、トンネリングパス中にバンドギャップの大きい材料を挟むことで、トンネリング確率を減少させることができるからである。トンネリング確率は、このバンドギャップの増大と共に指数関数的に減少する。よって、本実施形態では、バンドギャップの大きい第2の側壁絶縁膜104bにより、GIDL電流をさらに低減することができる。

【0026】

また、GIDL電流の原因となるBTBTが、ドレイン領域112の端部で生じるのに対し、オン電流を発生させるBTBTは、ソース領域111の端部で生じる。本実施形態では、第2の側壁絶縁膜104bは、ゲート絶縁膜102よりも下に埋め込むが、第1の側壁絶縁膜104aは、ゲート絶縁膜102よりも下には埋め込まない。よって、本実施形態によれば、オン電流を減少させずに、GIDL電流を減少させることができる。

【0027】

なお、MOSFETでは、チャネル長の増大はオン電流を低減するが、トンネルFETでは、オン電流はチャネル長にほとんど依存しないことが知られている。よって、本実施形態では、実効的チャネル長Lを長くしても、オン電流の大きな減少は回避することができる。

【0028】

以上のように、本実施形態では、第2の側壁絶縁膜104bを、ゲート絶縁膜102よりも深い位置に形成する。よって、本実施形態によれば、トンネルFETのオン電流の劣化を抑制しつつ、オフ電流を低減することができる。その結果、トンネルFETにおけるスイッチングの両極性の問題を解決することができる。

【0029】

(2)半導体装置の製造方法

次に、図2〜図5を参照し、第1実施形態の半導体装置の製造方法を説明する。図2〜図5は、第1実施形態の半導体装置の製造方法を示す断面図である。

【0030】

まず、基板101を用意する(図2(a))。基板101は、例えばシリコン基板である。次に、基板101内の所定の領域に、例えばSTI(Shallow Trench Isolation)法を用いて、素子分離領域を形成する。次に、基板101内の素子領域の表面に、ゲート絶縁膜102を形成する(図2(a))。ゲート絶縁膜102は例えば、熱酸化法により形成されたシリコン酸化膜である。

【0031】

次に、基板101上の全面に、ゲート電極103用の電極材を堆積する(図2(a))。この電極材は、例えばポリシリコンである。次に、基板101上の全面に、キャップ層201用の絶縁材を堆積する(図2(a))。この絶縁材は、例えばシリコン窒化膜である。

【0032】

次に、リソグラフィとRIE(Reactive Ion Etching)により、上記の絶縁材と電極材をエッチングする。その結果、図2(a)に示すように、基板101上に、ゲート絶縁膜102を介してゲート電極103が形成される。

【0033】

次に、図2(b)に示すように、CVD(Chemical Vapor Deposition)により、基板101上の全面に、ライナー層202を堆積する。ライナー層202は例えば、シリコン窒化膜である。

【0034】

次に、図2(c)に示すように、リソグラフィにより、ソース領域111を形成予定の領域を覆うレジスト膜203を形成する。次に、図2(d)に示すように、レジスト膜203をマスクとするウェットエッチングにより、ライナー層202をエッチングする。

【0035】

次に、図3(a)に示すように、レジスト膜203とライナー層202をマスクとするRIEにより、基板101をエッチングする。その結果、基板101内に、ゲート電極103に隣接して溝Tが形成される。なお、エッチングを停止するタイミングは、時間により制御する。次に、図3(b)、図3(c)に示すように、レジスト膜203とライナー層202を除去する。

【0036】

次に、図3(d)に示すように、CVDにより、第1、第2の側壁絶縁膜104a、104bの材料となる絶縁膜104を堆積する。絶縁膜104は、例えばシリコン酸化膜である。次に、図4(a)に示すように、RIEにより、絶縁膜104を加工する。その結果、ゲート電極103の第1側面S1に、第1の側壁絶縁膜104aが形成される。さらには、ゲート電極103の第2側面S2と溝Tの側面S3に、第2の側壁絶縁膜104bが形成される。

【0037】

次に、図4(a)に示すように、リソグラフィにより、ドレイン領域112を形成予定の領域を覆うレジスト膜204を形成する。次に、レジスト膜204をマスクとして、基板101内に不純物イオンを注入する。その結果、その後のアニーリング等により、基板101内にソースエクステンション領域113が形成される。

【0038】

次に、図4(b)に示すように、リソグラフィにより、ソース領域111を形成予定の領域を覆うレジスト膜205を形成する。次に、レジスト膜205をマスクとして、基板101内に不純物イオンを注入する。その結果、その後のアニーリング等により、基板101内にドレインエクステンション領域114が形成される。なお、図4(b)の工程は、ドレインエクステンション領域114がゲート電極103の直下に形成されないように実行する。

【0039】

次に、図4(c)に示すように、CVDにより、第3、第4の側壁絶縁膜105a、105bの材料となる絶縁膜105を堆積する。絶縁膜105は、例えばシリコン酸化膜である。次に、図4(d)に示すように、RIEにより、絶縁膜105を加工する。その結果、ゲート電極103の第1側面S1に、第1の側壁絶縁膜104aを介して第3の側壁絶縁膜105aが形成される。さらには、ゲート電極103の第2側面S2と溝Tの側面S3に、第2の側壁絶縁膜104bを介して第4の側壁絶縁膜105bが形成される。

【0040】

次に、図5(a)に示すように、リソグラフィにより、ドレイン領域112を形成予定の領域を覆うレジスト膜206を形成する。次に、レジスト膜206をマスクとして、基板101内に不純物イオンを注入する。その結果、その後のアニーリング等により、基板101内にソース領域111が形成される。なお、ソース領域111は、ソースエクステンション領域113よりも深い不純物濃度プロファイルを持つように形成する。次に、レジスト膜206を除去する。

【0041】

次に、図5(b)に示すように、リソグラフィにより、ソース領域111を形成予定の領域を覆うレジスト膜207を形成する。次に、レジスト膜207をマスクとして、基板101内に不純物イオンを注入する。その結果、その後のアニーリング等により、基板101内にドレイン領域112が形成される。なお、ドレイン領域112は、ドレインエクステンション領域114よりも深い不純物濃度プロファイルを持つように形成する。次に、レジスト膜207を除去する。

【0042】

次に、図5(c)に示すように、ウェットエッチング等により、キャップ層201を除去する。なお、本実施形態では、キャップ層201を、第1〜第4の側壁絶縁膜104a〜105bとエッチング選択比が取れる材料で形成する。また、第1〜第4の側壁絶縁膜104a〜105bの突出部分は、そのまま残存させてもよいし、CMP(Chemical Vapor Deposition)などにより除去してもよい。

【0043】

次に、図5(d)に示すように、サリサイドプロセスにより、ゲート電極103、ソース領域111、ドレイン領域112内の上部にシリサイド層115を形成する。シリサイド層115は、例えばNiSi層である。

【0044】

その後、本実施形態では、基板101上に、層間絶縁膜、コンタクトプラグ、ビアプラグ、配線層などを形成する。こうして、図1の半導体装置が製造される。

【0045】

なお、図2(a)〜図5(d)のフローは、n型TFETの作製フローであるが、これと同様のフローによりp型TFETも作製可能である。

【0046】

以上のように、本実施形態では、第2の側壁絶縁膜104bを、ゲート電極103の第2側面S2と溝Tの側面S3に形成し、ゲート絶縁膜102よりも深い位置に形成する。よって、本実施形態によれば、トンネルFETのオン電流の劣化を抑制しつつ、オフ電流を低減することが可能となる。

【0047】

(第2実施形態)

図6は、第2実施形態の半導体装置の構造を示す断面図である。

【0048】

図6の半導体装置は、図1に示す構成要素に加えて、半導体層106を備えている。半導体層106は、溝T内に、第2の側壁絶縁膜104bに隣接して形成されている。本実施形態では、半導体層106を、基板101と同じ材料で形成するが、基板101と異なる材料で形成してもよい。半導体層106の例としては、Si層、SiGe層、Ge層などが挙げられる。

【0049】

本実施形態では、後述するように、半導体層114の形成後に、第4の側壁絶縁膜105b、ドレイン領域112、ドレインエクステンション領域114を形成する。よって、第4の側壁絶縁膜105bは、半導体層106上において、ゲート電極103の第2側面S2に、第2の側壁絶縁膜104bを介して形成されている。また、ドレイン領域112とドレインエクステンション領域114は、基板101内と半導体層106内に連続して形成されている。

【0050】

図6に示す符号S5は、半導体層106の上面を示す。本実施形態では、半導体層106の上面S5の高さは、基板101の上面Sの高さとほぼ等しいが、基板101の上面Sの高さよりも高くまたは低くしてもよい。

【0051】

本実施形態では、ドレイン領域112内のシリサイド層115が、半導体層106内に形成されている。このシリサイド層115は、ドレイン領域112内とドレインエクステンション領域114内に連続して形成されていてもよい。このような構成には、ジャンクションリーク電流を抑制できるという利点がある。なお、この場合、半導体層106の膜厚は、ドレインエクステンション領域114内にシリサイド層115を形成しやすくするために、20nm以上に設定することが望ましい。

【0052】

(1)半導体装置の製造方法

次に、図7〜図9を参照し、第2実施形態の半導体装置の製造方法を説明する。図7〜図9は、第2実施形態の半導体装置の製造方法を示す断面図である。

【0053】

まず、第1実施形態と同様に、図2(a)〜図4(a)の工程を実行する。

【0054】

次に、図7(a)に示すように、基板101上の全面に、ライナー層301を堆積する。ライナー層301は、例えばシリコン窒化膜である。

【0055】

次に、図7(b)に示すように、リソグラフィにより、ソース領域111を形成予定の領域を覆うレジスト膜302を形成する。次に、図7(c)に示すように、レジスト膜302をマスクとするウェットエッチングにより、ライナー層301をエッチングする。なお、本実施形態では、ライナー層301を、第1、第2の側壁絶縁膜104a、104bとエッチング選択比が取れる材料で形成する。次に、レジスト膜302を除去する。

【0056】

次に、図7(d)に示すように、エピタキシャルCVDにより、溝T内に、第2の側壁絶縁膜104bに隣接して半導体層106を形成する。半導体層106は、例えばシリコン層である。次に、図8(a)に示すように、ウェットエッチングにより、ライナー層301を除去する。

【0057】

次に、図8(b)に示すように、リソグラフィにより、ソース領域111を形成予定の領域を覆うレジスト膜303を形成する。次に、レジスト膜303をマスクとして、半導体層106および基板101内に不純物イオンを注入する。その結果、その後のアニーリング等により、半導体層106および基板101内にドレインエクステンション領域114が形成される。なお、図8(b)の工程は、ドレインエクステンション領域114がゲート電極103の直下に形成されないように実行する。

【0058】

次に、図8(c)〜図9(d)の工程を、図4(c)〜図5(d)の工程と同様に実行する。なお、符号304、305はいずれも、レジスト膜を示す。

【0059】

その後、本実施形態では、基板101上に、層間絶縁膜、コンタクトプラグ、ビアプラグ、配線層などを形成する。こうして、図6の半導体装置が製造される。

【0060】

以上のように、本実施形態では、第2の側壁絶縁膜104bを、ゲート電極103の第2側面S2と溝Tの側面S3に形成し、ゲート絶縁膜102よりも深い位置に形成する。よって、本実施形態によれば、第1実施形態と同様に、トンネルFETのオン電流の劣化を抑制しつつ、オフ電流を低減することが可能となる。

【0061】

以上、第1及び第2実施形態について説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することを意図したものではない。これらの実施形態は、その他の様々な形態で実施することができる。また、これらの実施形態に対し、発明の要旨を逸脱しない範囲内で、種々の省略、置換、変更を行うことにより、様々な変形例を得ることもできる。これらの形態や変形例は、発明の範囲や要旨に含まれており、特許請求の範囲及びこれに均等な範囲には、これらの形態や変形例が含まれる。

【符号の説明】

【0062】

101:基板、102:ゲート絶縁膜、103:ゲート電極、

104a:第1の側壁絶縁膜、104b:第2の側壁絶縁膜、

105a:第3の側壁絶縁膜、105b:第4の側壁絶縁膜、106:半導体層、

111:ソース領域、112:ドレイン領域、

113:ソースエクステンション領域、114:ドレインエクステンション領域、

115:シリサイド層、121:層間絶縁膜、

201:キャップ層、202:ライナー層、203〜207:レジスト膜、

301:ライナー層、302〜305:レジスト膜

【技術分野】

【0001】

本発明の実施形態は、半導体装置およびその製造方法に関する。

【背景技術】

【0002】

近年、MOSFETを越える高性能化、低消費電力化を目指して、トンネルFET(TFET)が精力的に研究されている。トンネルFETでは、ソース領域とドレイン領域の導電型が異なるため、ゲート電圧が正でも負でもトンネルFETがオンになるスイッチングの両極性が問題となる。これは、オフ電流の増大や、トンネルFETの特性ばらつきの増大などをもたらす。このオフ電流を抑制する手法はいくつか提案されているが、これらの多くは、オン電流の劣化や、SS(Sub-threshold Swing)が緩やかになるなどの弊害をもたらし、トンネルFETの低消費電力化を妨げる要因となってしまう。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開平11−17184号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

トンネルFETのオン電流の劣化を抑制しつつ、オフ電流を低減することが可能な半導体装置およびその製造方法を提供する。

【課題を解決するための手段】

【0005】

一の実施形態による半導体装置は、溝が形成された基板と、前記基板上の前記溝に隣接する位置にゲート絶縁膜を介して形成され、前記溝の反対側に位置する第1側面と、前記溝側に位置する第2側面とを有するゲート電極とを備える。さらに、前記装置は、前記ゲート電極の前記第1側面に形成された第1の側壁絶縁膜と、前記ゲート電極の前記第2側面と前記溝の側面に形成された第2の側壁絶縁膜とを備える。さらに、前記装置は、前記基板内において、前記ゲート電極の前記第1側面に対し前記第1の側壁絶縁膜側に形成された、第1導電型のソース領域と、前記基板内において、前記ゲート電極の前記第2側面と前記溝の側面に対し前記第2の側壁絶縁膜側に形成された、第2導電型のドレイン領域とを備える。

【図面の簡単な説明】

【0006】

【図1】第1実施形態の半導体装置の構造を示す断面図である。

【図2】第1実施形態の半導体装置の製造方法を示す断面図(1/4)である。

【図3】第1実施形態の半導体装置の製造方法を示す断面図(2/4)である。

【図4】第1実施形態の半導体装置の製造方法を示す断面図(3/4)である。

【図5】第1実施形態の半導体装置の製造方法を示す断面図(4/4)である。

【図6】第2実施形態の半導体装置の構造を示す断面図である。

【図7】第2実施形態の半導体装置の製造方法を示す断面図(1/3)である。

【図8】第2実施形態の半導体装置の製造方法を示す断面図(2/3)である。

【図9】第2実施形態の半導体装置の製造方法を示す断面図(3/3)である。

【発明を実施するための最良の形態】

【0007】

以下、本発明の実施形態を、図面を参照して説明する。

【0008】

(第1実施形態)

図1は、第1実施形態の半導体装置の構造を示す断面図である。

【0009】

図1の半導体装置は、トンネルFETの構成要素として、基板101と、ゲート絶縁膜102と、ゲート電極103と、第1、第2の側壁絶縁膜104a、104bと、第3、第4の側壁絶縁膜105a、105bと、ソース領域111と、ドレイン領域112と、ソースエクステンション領域113と、ドレインエクステンション領域114と、シリサイド層115と、層間絶縁膜121とを備えている。

【0010】

基板101は例えば、Si基板、GaAs基板、InP基板などの半導体基板である。図1には、基板101の主面に平行で、互いに垂直なX方向およびY方向と、基板101の主面に垂直なZ方向が示されている。基板101は、図1に示すように、Y方向に延びる溝Tを有している。符号S3、S4はそれぞれ、溝Tの側面と底面を示す。本実施形態の基板101は、i型基板、またはソース領域111やドレイン領域112よりも不純物濃度が低いp型基板またはn型基板である。なお、基板101は、SOI(Silicon on Insulator)基板またはGOI(Germanium on Insulator)基板でもよい。

【0011】

ゲート電極103は、基板101上の溝Tに隣接する位置に、ゲート絶縁膜102を介して形成されている。ゲート絶縁膜102の例としては、シリコン酸化膜(SiO2)、シリコン酸窒化膜(SiON)、high−k絶縁膜などが挙げられる。また、ゲート電極103の例としては、ポリシリコン層、シリサイド層、メタル層や、これらの2種類以上を含む積層膜などが挙げられる。符号S1、S2はそれぞれ、ゲート電極103の第1側面と第2側面を示す。第1側面S1は、溝Tの反対側に位置し、第2側面S1は、溝T側に位置している。

【0012】

第1の側壁絶縁膜104aは、ゲート電極103の第1側面S1に形成されている。また、第2の側壁絶縁膜104bは、ゲート電極103の第2側面S2と溝Tの側面S3に形成されている。よって、第2の側壁絶縁膜104bの底面の高さは、基板101の上面Sや、第1の側壁絶縁膜104aの底面よりも低くなっている。第1、第2の側壁絶縁膜104a、104bの例としては、シリコン酸化膜や、シリコン窒化膜(SiN)などが挙げられる。

【0013】

第3の側壁絶縁膜105aは、ゲート電極103の第1側面S1に、第1の側壁絶縁膜104aを介して形成されている。また、第4の側壁絶縁膜105bは、ゲート電極103の第2側面S2と溝Tの側面S3に、第2の側壁絶縁膜104bを介して形成されている。よって、第4の側壁絶縁膜105bの底面の高さは、基板101の上面Sや、第3の側壁絶縁膜105aの底面よりも低くなっている。第3、第4の側壁絶縁膜105a、105bの例としては、シリコン酸化膜や、シリコン窒化膜などが挙げられる。

【0014】

ソース領域111とドレイン領域112は、基板101内にゲート電極103を挟むように形成されている。具体的には、ソース領域111は、基板101内において、ゲート電極103の第1側面S1に対し、第1の側壁絶縁膜104a側に形成されている。また、ドレイン領域112は、基板101内において、ゲート電極103の第2側面S2と溝Tの側面S3に対し、第2の側壁絶縁膜104b側に形成されている。本実施形態では、ソース領域111は、p型領域であり、ドレイン領域112は、ソース領域111とは逆導電型のn型領域である。p導電型とn導電型はそれぞれ、第1導電型と第2導電型の例である。

【0015】

ソースエクステンション領域113は、ソース領域111とドレイン領域112との間において、第1、第3の側壁絶縁膜104a、105aの下部に形成されている。また、ドレインエクステンション領域114は、ソース領域111とドレイン領域112との間において、第2、第4の側壁絶縁膜104b、105bの下部に形成されている。本実施形態では、ソースエクステンション領域113と、ドレインエクステンション領域114はそれぞれ、p型領域とn型領域である。

【0016】

シリサイド層115は、ゲート電極103、ソース領域111、ドレイン領域112内の上部に形成されている。シリサイド層115の例としては、NiSi層、PtSi層、NiPtSi層、NiCoSi層、Co2Si層などが挙げられる。なお、基板101やゲート電極103がシリコン以外の半導体(例えばゲルマニウム)で形成されている場合には、シリサイド層115の代わりに、この半導体と金属との合金層を形成してもよい。このような合金層の例としては、NiGe層などが挙げられる。

【0017】

層間絶縁膜121は、基板101上に、トンネルFETを覆うように形成されている。層間絶縁膜121の例としては、シリコン酸化膜などが挙げられる。

【0018】

なお、図1のトンネルFETは、n型FETであるが、p型FETとしてもよい。この場合、ソース領域111とソースエクステンション領域113は、n型領域となり、ドレイン領域112とドレインエクステンション領域114は、p型領域となる。

【0019】

また、第2の側壁絶縁膜104bは、第1の絶縁材料を用いて、ゲート電極103の第2側面S2に形成された第1部分と、第1の絶縁材料と異なる第2の絶縁材料を用いて、溝Tの側面S3に形成された第2部分を有していてもよい。すなわち、第2側面S2に形成された第1部分と、側面S3に形成された第2部分は、別々の絶縁膜で形成されていてもよい。

【0020】

同様に、第4の側壁絶縁膜105bは、第3の絶縁材料を用いて、ゲート電極103の第2側面S2に形成された第3部分と、第3の絶縁材料と異なる第4の絶縁材料を用いて、溝Tの側面S3に形成された第4部分を有していてもよい。

【0021】

(1)第1実施形態のトンネルFETの利点

以上のように、図1では、第2の側壁絶縁膜104bが、ゲート電極103の第2側面S2と溝Tの側面S3に形成されている。その結果、第2の側壁絶縁膜104bは、ゲート絶縁膜102よりも下に埋め込まれている。以下、このような第2の側壁絶縁膜104bを有するトンネルFETの利点について説明する。

【0022】

図1では、ゲート電極103に正の電圧を印加すると、ソース領域111の価電子帯を占有する電子が、BTBT(Band to Band Tunneling)と呼ばれるトンネル効果により、チャネル領域中の伝導帯に移動する。そして、この電子がドレイン領域112に到達することで、ソース領域111とドレイン領域112との間にオン電流が流れる。

【0023】

一方、ゲート電極103に負の電圧を印加すると、チャネル領域の価電子帯を占有する電子が、BTBTにより、ドレイン領域112中の伝導帯に移動する。そして、電子の移動に伴いチャネル領域内に生じた正孔がソース領域111に到達することで、ソース領域111とドレイン領域112との間にオフ電流が流れる。この電流は、GIDL(Gate Induced Drain Leakage)電流と呼ばれる。

【0024】

一般に、GIDL電流の原因となるBTBTは、ドレイン領域112の端部で生じる。本実施形態では、第2の側壁絶縁膜104bにより、このBTBTの際の電子のトンネリング確率を減少させ、GIDL電流を低減することができる。理由は、第2の側壁絶縁膜104bにより、トンネルFETの実効的チャネル長Lを長くすることができるからである。実効的チャネル長Lの増加は、BTBTのトンネリング距離を増大させ、トンネリング距離の増大は、トンネリング確率を指数関数的に減少させる。本実施形態では、実効的チャネル長Lが、溝Tの深さHの分だけ、本来のチャネル長よりも長くなっている。

【0025】

また、第2の側壁絶縁膜104bは、チャネル領域とドレイン領域112との間を移動する電子の障壁として機能する。この観点から言うと、第2の側壁絶縁膜104bの材料は、バンドギャップの大きい絶縁体とすることが望ましい。理由は、トンネリングパス中にバンドギャップの大きい材料を挟むことで、トンネリング確率を減少させることができるからである。トンネリング確率は、このバンドギャップの増大と共に指数関数的に減少する。よって、本実施形態では、バンドギャップの大きい第2の側壁絶縁膜104bにより、GIDL電流をさらに低減することができる。

【0026】

また、GIDL電流の原因となるBTBTが、ドレイン領域112の端部で生じるのに対し、オン電流を発生させるBTBTは、ソース領域111の端部で生じる。本実施形態では、第2の側壁絶縁膜104bは、ゲート絶縁膜102よりも下に埋め込むが、第1の側壁絶縁膜104aは、ゲート絶縁膜102よりも下には埋め込まない。よって、本実施形態によれば、オン電流を減少させずに、GIDL電流を減少させることができる。

【0027】

なお、MOSFETでは、チャネル長の増大はオン電流を低減するが、トンネルFETでは、オン電流はチャネル長にほとんど依存しないことが知られている。よって、本実施形態では、実効的チャネル長Lを長くしても、オン電流の大きな減少は回避することができる。

【0028】

以上のように、本実施形態では、第2の側壁絶縁膜104bを、ゲート絶縁膜102よりも深い位置に形成する。よって、本実施形態によれば、トンネルFETのオン電流の劣化を抑制しつつ、オフ電流を低減することができる。その結果、トンネルFETにおけるスイッチングの両極性の問題を解決することができる。

【0029】

(2)半導体装置の製造方法

次に、図2〜図5を参照し、第1実施形態の半導体装置の製造方法を説明する。図2〜図5は、第1実施形態の半導体装置の製造方法を示す断面図である。

【0030】

まず、基板101を用意する(図2(a))。基板101は、例えばシリコン基板である。次に、基板101内の所定の領域に、例えばSTI(Shallow Trench Isolation)法を用いて、素子分離領域を形成する。次に、基板101内の素子領域の表面に、ゲート絶縁膜102を形成する(図2(a))。ゲート絶縁膜102は例えば、熱酸化法により形成されたシリコン酸化膜である。

【0031】

次に、基板101上の全面に、ゲート電極103用の電極材を堆積する(図2(a))。この電極材は、例えばポリシリコンである。次に、基板101上の全面に、キャップ層201用の絶縁材を堆積する(図2(a))。この絶縁材は、例えばシリコン窒化膜である。

【0032】

次に、リソグラフィとRIE(Reactive Ion Etching)により、上記の絶縁材と電極材をエッチングする。その結果、図2(a)に示すように、基板101上に、ゲート絶縁膜102を介してゲート電極103が形成される。

【0033】

次に、図2(b)に示すように、CVD(Chemical Vapor Deposition)により、基板101上の全面に、ライナー層202を堆積する。ライナー層202は例えば、シリコン窒化膜である。

【0034】

次に、図2(c)に示すように、リソグラフィにより、ソース領域111を形成予定の領域を覆うレジスト膜203を形成する。次に、図2(d)に示すように、レジスト膜203をマスクとするウェットエッチングにより、ライナー層202をエッチングする。

【0035】

次に、図3(a)に示すように、レジスト膜203とライナー層202をマスクとするRIEにより、基板101をエッチングする。その結果、基板101内に、ゲート電極103に隣接して溝Tが形成される。なお、エッチングを停止するタイミングは、時間により制御する。次に、図3(b)、図3(c)に示すように、レジスト膜203とライナー層202を除去する。

【0036】

次に、図3(d)に示すように、CVDにより、第1、第2の側壁絶縁膜104a、104bの材料となる絶縁膜104を堆積する。絶縁膜104は、例えばシリコン酸化膜である。次に、図4(a)に示すように、RIEにより、絶縁膜104を加工する。その結果、ゲート電極103の第1側面S1に、第1の側壁絶縁膜104aが形成される。さらには、ゲート電極103の第2側面S2と溝Tの側面S3に、第2の側壁絶縁膜104bが形成される。

【0037】

次に、図4(a)に示すように、リソグラフィにより、ドレイン領域112を形成予定の領域を覆うレジスト膜204を形成する。次に、レジスト膜204をマスクとして、基板101内に不純物イオンを注入する。その結果、その後のアニーリング等により、基板101内にソースエクステンション領域113が形成される。

【0038】

次に、図4(b)に示すように、リソグラフィにより、ソース領域111を形成予定の領域を覆うレジスト膜205を形成する。次に、レジスト膜205をマスクとして、基板101内に不純物イオンを注入する。その結果、その後のアニーリング等により、基板101内にドレインエクステンション領域114が形成される。なお、図4(b)の工程は、ドレインエクステンション領域114がゲート電極103の直下に形成されないように実行する。

【0039】

次に、図4(c)に示すように、CVDにより、第3、第4の側壁絶縁膜105a、105bの材料となる絶縁膜105を堆積する。絶縁膜105は、例えばシリコン酸化膜である。次に、図4(d)に示すように、RIEにより、絶縁膜105を加工する。その結果、ゲート電極103の第1側面S1に、第1の側壁絶縁膜104aを介して第3の側壁絶縁膜105aが形成される。さらには、ゲート電極103の第2側面S2と溝Tの側面S3に、第2の側壁絶縁膜104bを介して第4の側壁絶縁膜105bが形成される。

【0040】

次に、図5(a)に示すように、リソグラフィにより、ドレイン領域112を形成予定の領域を覆うレジスト膜206を形成する。次に、レジスト膜206をマスクとして、基板101内に不純物イオンを注入する。その結果、その後のアニーリング等により、基板101内にソース領域111が形成される。なお、ソース領域111は、ソースエクステンション領域113よりも深い不純物濃度プロファイルを持つように形成する。次に、レジスト膜206を除去する。

【0041】

次に、図5(b)に示すように、リソグラフィにより、ソース領域111を形成予定の領域を覆うレジスト膜207を形成する。次に、レジスト膜207をマスクとして、基板101内に不純物イオンを注入する。その結果、その後のアニーリング等により、基板101内にドレイン領域112が形成される。なお、ドレイン領域112は、ドレインエクステンション領域114よりも深い不純物濃度プロファイルを持つように形成する。次に、レジスト膜207を除去する。

【0042】

次に、図5(c)に示すように、ウェットエッチング等により、キャップ層201を除去する。なお、本実施形態では、キャップ層201を、第1〜第4の側壁絶縁膜104a〜105bとエッチング選択比が取れる材料で形成する。また、第1〜第4の側壁絶縁膜104a〜105bの突出部分は、そのまま残存させてもよいし、CMP(Chemical Vapor Deposition)などにより除去してもよい。

【0043】

次に、図5(d)に示すように、サリサイドプロセスにより、ゲート電極103、ソース領域111、ドレイン領域112内の上部にシリサイド層115を形成する。シリサイド層115は、例えばNiSi層である。

【0044】

その後、本実施形態では、基板101上に、層間絶縁膜、コンタクトプラグ、ビアプラグ、配線層などを形成する。こうして、図1の半導体装置が製造される。

【0045】

なお、図2(a)〜図5(d)のフローは、n型TFETの作製フローであるが、これと同様のフローによりp型TFETも作製可能である。

【0046】

以上のように、本実施形態では、第2の側壁絶縁膜104bを、ゲート電極103の第2側面S2と溝Tの側面S3に形成し、ゲート絶縁膜102よりも深い位置に形成する。よって、本実施形態によれば、トンネルFETのオン電流の劣化を抑制しつつ、オフ電流を低減することが可能となる。

【0047】

(第2実施形態)

図6は、第2実施形態の半導体装置の構造を示す断面図である。

【0048】

図6の半導体装置は、図1に示す構成要素に加えて、半導体層106を備えている。半導体層106は、溝T内に、第2の側壁絶縁膜104bに隣接して形成されている。本実施形態では、半導体層106を、基板101と同じ材料で形成するが、基板101と異なる材料で形成してもよい。半導体層106の例としては、Si層、SiGe層、Ge層などが挙げられる。

【0049】

本実施形態では、後述するように、半導体層114の形成後に、第4の側壁絶縁膜105b、ドレイン領域112、ドレインエクステンション領域114を形成する。よって、第4の側壁絶縁膜105bは、半導体層106上において、ゲート電極103の第2側面S2に、第2の側壁絶縁膜104bを介して形成されている。また、ドレイン領域112とドレインエクステンション領域114は、基板101内と半導体層106内に連続して形成されている。

【0050】

図6に示す符号S5は、半導体層106の上面を示す。本実施形態では、半導体層106の上面S5の高さは、基板101の上面Sの高さとほぼ等しいが、基板101の上面Sの高さよりも高くまたは低くしてもよい。

【0051】

本実施形態では、ドレイン領域112内のシリサイド層115が、半導体層106内に形成されている。このシリサイド層115は、ドレイン領域112内とドレインエクステンション領域114内に連続して形成されていてもよい。このような構成には、ジャンクションリーク電流を抑制できるという利点がある。なお、この場合、半導体層106の膜厚は、ドレインエクステンション領域114内にシリサイド層115を形成しやすくするために、20nm以上に設定することが望ましい。

【0052】

(1)半導体装置の製造方法

次に、図7〜図9を参照し、第2実施形態の半導体装置の製造方法を説明する。図7〜図9は、第2実施形態の半導体装置の製造方法を示す断面図である。

【0053】

まず、第1実施形態と同様に、図2(a)〜図4(a)の工程を実行する。

【0054】

次に、図7(a)に示すように、基板101上の全面に、ライナー層301を堆積する。ライナー層301は、例えばシリコン窒化膜である。

【0055】

次に、図7(b)に示すように、リソグラフィにより、ソース領域111を形成予定の領域を覆うレジスト膜302を形成する。次に、図7(c)に示すように、レジスト膜302をマスクとするウェットエッチングにより、ライナー層301をエッチングする。なお、本実施形態では、ライナー層301を、第1、第2の側壁絶縁膜104a、104bとエッチング選択比が取れる材料で形成する。次に、レジスト膜302を除去する。

【0056】

次に、図7(d)に示すように、エピタキシャルCVDにより、溝T内に、第2の側壁絶縁膜104bに隣接して半導体層106を形成する。半導体層106は、例えばシリコン層である。次に、図8(a)に示すように、ウェットエッチングにより、ライナー層301を除去する。

【0057】

次に、図8(b)に示すように、リソグラフィにより、ソース領域111を形成予定の領域を覆うレジスト膜303を形成する。次に、レジスト膜303をマスクとして、半導体層106および基板101内に不純物イオンを注入する。その結果、その後のアニーリング等により、半導体層106および基板101内にドレインエクステンション領域114が形成される。なお、図8(b)の工程は、ドレインエクステンション領域114がゲート電極103の直下に形成されないように実行する。

【0058】

次に、図8(c)〜図9(d)の工程を、図4(c)〜図5(d)の工程と同様に実行する。なお、符号304、305はいずれも、レジスト膜を示す。

【0059】

その後、本実施形態では、基板101上に、層間絶縁膜、コンタクトプラグ、ビアプラグ、配線層などを形成する。こうして、図6の半導体装置が製造される。

【0060】

以上のように、本実施形態では、第2の側壁絶縁膜104bを、ゲート電極103の第2側面S2と溝Tの側面S3に形成し、ゲート絶縁膜102よりも深い位置に形成する。よって、本実施形態によれば、第1実施形態と同様に、トンネルFETのオン電流の劣化を抑制しつつ、オフ電流を低減することが可能となる。

【0061】

以上、第1及び第2実施形態について説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することを意図したものではない。これらの実施形態は、その他の様々な形態で実施することができる。また、これらの実施形態に対し、発明の要旨を逸脱しない範囲内で、種々の省略、置換、変更を行うことにより、様々な変形例を得ることもできる。これらの形態や変形例は、発明の範囲や要旨に含まれており、特許請求の範囲及びこれに均等な範囲には、これらの形態や変形例が含まれる。

【符号の説明】

【0062】

101:基板、102:ゲート絶縁膜、103:ゲート電極、

104a:第1の側壁絶縁膜、104b:第2の側壁絶縁膜、

105a:第3の側壁絶縁膜、105b:第4の側壁絶縁膜、106:半導体層、

111:ソース領域、112:ドレイン領域、

113:ソースエクステンション領域、114:ドレインエクステンション領域、

115:シリサイド層、121:層間絶縁膜、

201:キャップ層、202:ライナー層、203〜207:レジスト膜、

301:ライナー層、302〜305:レジスト膜

【特許請求の範囲】

【請求項1】

溝が形成された基板と、

前記基板上の前記溝に隣接する位置にゲート絶縁膜を介して形成され、前記溝の反対側に位置する第1側面と、前記溝側に位置する第2側面とを有するゲート電極と、

前記ゲート電極の前記第1側面に形成された第1の側壁絶縁膜と、

前記ゲート電極の前記第2側面と前記溝の側面に形成された第2の側壁絶縁膜と、

前記基板内において、前記ゲート電極の前記第1側面に対し前記第1の側壁絶縁膜側に形成された、第1導電型のソース領域と、

前記基板内において、前記ゲート電極の前記第2側面と前記溝の側面に対し前記第2の側壁絶縁膜側に形成された、第2導電型のドレイン領域と、

前記ソース領域と前記ドレイン領域との間において、前記第1の側壁絶縁膜の下部に形成された前記第1導電型のソースエクステンション領域と、

前記ソース領域と前記ドレイン領域との間において、前記第2の側壁絶縁膜の下部に形成された前記第2導電型のドレインエクステンション領域と、

前記溝内に、前記第2の側壁絶縁膜に隣接して形成された半導体層と、

前記ゲート電極の前記第1側面に、前記第1の側壁絶縁膜を介して形成された第3の側壁絶縁膜と、

前記半導体層上において、前記ゲート電極の前記第2側面に、前記第2の側壁絶縁膜を介して形成された第4の側壁絶縁膜とを備え、

前記ドレイン領域は、前記基板内と前記半導体層内に連続して形成されており、

前記半導体層の上面の高さは、前記基板の上面の高さよりも高いまたは低い、

半導体装置。

【請求項2】

溝が形成された基板と、

前記基板上の前記溝に隣接する位置にゲート絶縁膜を介して形成され、前記溝の反対側に位置する第1側面と、前記溝側に位置する第2側面とを有するゲート電極と、

前記ゲート電極の前記第1側面に形成された第1の側壁絶縁膜と、

前記ゲート電極の前記第2側面と前記溝の側面に形成された第2の側壁絶縁膜と、

前記基板内において、前記ゲート電極の前記第1側面に対し前記第1の側壁絶縁膜側に形成された、第1導電型のソース領域と、

前記基板内において、前記ゲート電極の前記第2側面と前記溝の側面に対し前記第2の側壁絶縁膜側に形成された、第2導電型のドレイン領域と、

を備える半導体装置。

【請求項3】

さらに、

前記ゲート電極の前記第1側面に、前記第1の側壁絶縁膜を介して形成された第3の側壁絶縁膜と、

前記ゲート電極の前記第2側面と前記溝の側面に、前記第2の側壁絶縁膜を介して形成された第4の側壁絶縁膜と、

を備える請求項2に記載の半導体装置。

【請求項4】

さらに、

前記溝内に、前記第2の側壁絶縁膜に隣接して形成された半導体層と、

前記ゲート電極の前記第1側面に、前記第1の側壁絶縁膜を介して形成された第3の側壁絶縁膜と、

前記半導体層上において、前記ゲート電極の前記第2側面に、前記第2の側壁絶縁膜を介して形成された第4の側壁絶縁膜と、

を備える請求項2に記載の半導体装置。

【請求項5】

前記ドレイン領域は、前記基板内と前記半導体層内に連続して形成されている、請求項4に記載の半導体装置。

【請求項6】

前記半導体層の上面の高さは、前記基板の上面の高さよりも高いまたは低い、請求項4または5に記載の半導体装置。

【請求項7】

さらに、

前記ソース領域と前記ドレイン領域との間において、前記第1の側壁絶縁膜の下部に形成された前記第1導電型のソースエクステンション領域と、

前記ソース領域と前記ドレイン領域との間において、前記第2の側壁絶縁膜の下部に形成された前記第2導電型のドレインエクステンション領域と、

を備える請求項2から6のいずれか1項に記載の半導体装置。

【請求項8】

基板上にゲート絶縁膜を介してゲート電極を形成し、

前記基板内に、前記ゲート電極に隣接して溝を形成し、

前記ゲート電極の第1側面に第1の側壁絶縁膜を形成し、

前記ゲート電極の第2側面と前記溝の側面に第2の側壁絶縁膜を形成し、

前記基板内において、前記ゲート電極の前記第1側面に対し前記第1の側壁絶縁膜側に第1導電型のソース領域を形成し、

前記基板内において、前記ゲート電極の前記第2側面と前記溝の側面に対し前記第2の側壁絶縁膜側に第2導電型のドレイン領域を形成する、

半導体装置の製造方法。

【請求項1】

溝が形成された基板と、

前記基板上の前記溝に隣接する位置にゲート絶縁膜を介して形成され、前記溝の反対側に位置する第1側面と、前記溝側に位置する第2側面とを有するゲート電極と、

前記ゲート電極の前記第1側面に形成された第1の側壁絶縁膜と、

前記ゲート電極の前記第2側面と前記溝の側面に形成された第2の側壁絶縁膜と、

前記基板内において、前記ゲート電極の前記第1側面に対し前記第1の側壁絶縁膜側に形成された、第1導電型のソース領域と、

前記基板内において、前記ゲート電極の前記第2側面と前記溝の側面に対し前記第2の側壁絶縁膜側に形成された、第2導電型のドレイン領域と、

前記ソース領域と前記ドレイン領域との間において、前記第1の側壁絶縁膜の下部に形成された前記第1導電型のソースエクステンション領域と、

前記ソース領域と前記ドレイン領域との間において、前記第2の側壁絶縁膜の下部に形成された前記第2導電型のドレインエクステンション領域と、

前記溝内に、前記第2の側壁絶縁膜に隣接して形成された半導体層と、

前記ゲート電極の前記第1側面に、前記第1の側壁絶縁膜を介して形成された第3の側壁絶縁膜と、

前記半導体層上において、前記ゲート電極の前記第2側面に、前記第2の側壁絶縁膜を介して形成された第4の側壁絶縁膜とを備え、

前記ドレイン領域は、前記基板内と前記半導体層内に連続して形成されており、

前記半導体層の上面の高さは、前記基板の上面の高さよりも高いまたは低い、

半導体装置。

【請求項2】

溝が形成された基板と、

前記基板上の前記溝に隣接する位置にゲート絶縁膜を介して形成され、前記溝の反対側に位置する第1側面と、前記溝側に位置する第2側面とを有するゲート電極と、

前記ゲート電極の前記第1側面に形成された第1の側壁絶縁膜と、

前記ゲート電極の前記第2側面と前記溝の側面に形成された第2の側壁絶縁膜と、

前記基板内において、前記ゲート電極の前記第1側面に対し前記第1の側壁絶縁膜側に形成された、第1導電型のソース領域と、

前記基板内において、前記ゲート電極の前記第2側面と前記溝の側面に対し前記第2の側壁絶縁膜側に形成された、第2導電型のドレイン領域と、

を備える半導体装置。

【請求項3】

さらに、

前記ゲート電極の前記第1側面に、前記第1の側壁絶縁膜を介して形成された第3の側壁絶縁膜と、

前記ゲート電極の前記第2側面と前記溝の側面に、前記第2の側壁絶縁膜を介して形成された第4の側壁絶縁膜と、

を備える請求項2に記載の半導体装置。

【請求項4】

さらに、

前記溝内に、前記第2の側壁絶縁膜に隣接して形成された半導体層と、

前記ゲート電極の前記第1側面に、前記第1の側壁絶縁膜を介して形成された第3の側壁絶縁膜と、

前記半導体層上において、前記ゲート電極の前記第2側面に、前記第2の側壁絶縁膜を介して形成された第4の側壁絶縁膜と、

を備える請求項2に記載の半導体装置。

【請求項5】

前記ドレイン領域は、前記基板内と前記半導体層内に連続して形成されている、請求項4に記載の半導体装置。

【請求項6】

前記半導体層の上面の高さは、前記基板の上面の高さよりも高いまたは低い、請求項4または5に記載の半導体装置。

【請求項7】

さらに、

前記ソース領域と前記ドレイン領域との間において、前記第1の側壁絶縁膜の下部に形成された前記第1導電型のソースエクステンション領域と、

前記ソース領域と前記ドレイン領域との間において、前記第2の側壁絶縁膜の下部に形成された前記第2導電型のドレインエクステンション領域と、

を備える請求項2から6のいずれか1項に記載の半導体装置。

【請求項8】

基板上にゲート絶縁膜を介してゲート電極を形成し、

前記基板内に、前記ゲート電極に隣接して溝を形成し、

前記ゲート電極の第1側面に第1の側壁絶縁膜を形成し、

前記ゲート電極の第2側面と前記溝の側面に第2の側壁絶縁膜を形成し、

前記基板内において、前記ゲート電極の前記第1側面に対し前記第1の側壁絶縁膜側に第1導電型のソース領域を形成し、

前記基板内において、前記ゲート電極の前記第2側面と前記溝の側面に対し前記第2の側壁絶縁膜側に第2導電型のドレイン領域を形成する、

半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【公開番号】特開2013−115113(P2013−115113A)

【公開日】平成25年6月10日(2013.6.10)

【国際特許分類】

【出願番号】特願2011−257618(P2011−257618)

【出願日】平成23年11月25日(2011.11.25)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

【公開日】平成25年6月10日(2013.6.10)

【国際特許分類】

【出願日】平成23年11月25日(2011.11.25)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

[ Back to top ]