半導体装置およびその製造方法

【課題】ゲート電極の一部にメタルゲート電極を有するMISEFTにおいて、メタルゲート電極を構成するグレインの配向性のばらつきに起因するMISFETのしきい値電圧のばらつきを小さくする。

【解決手段】メタルゲート電極4a、4bに炭素(C)を導入することにより、メタルゲート電極4a、4b内のグレインの粒径が大きくなることを防ぎ、メタルゲート電極4a、4bの中に多数の小さいグレインを形成することにより、グレインの配向性を均一化し、ゲート電極の仕事関数のばらつきを低減する。

【解決手段】メタルゲート電極4a、4bに炭素(C)を導入することにより、メタルゲート電極4a、4b内のグレインの粒径が大きくなることを防ぎ、メタルゲート電極4a、4bの中に多数の小さいグレインを形成することにより、グレインの配向性を均一化し、ゲート電極の仕事関数のばらつきを低減する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置およびその製造方法に関し、特に、メタルゲート電極を具備する電界効果トランジスタの製造に適用して有効な技術に関する。

【背景技術】

【0002】

微細化が求められているMISFET(Metal Insulator Semiconductor Field Effect Transistor:MIS型電界効果トランジスタ)では、ゲート絶縁膜の一部に高い誘電率を有するhigh−k膜を用い、また、ゲート電極の一部に金属材料からなるメタルゲート電極を用いることにより、MISFETのゲート絶縁膜を薄膜化し、かつリーク電流を低減することを可能としている。また、high−k膜およびメタルゲート電極の構成を変えることにより、MISFETのしきい値電圧を制御することが可能である。

【0003】

特許文献1(特開2010−109214号公報)には、ゲート電極の形成後に熱処理が施される場合でも、金属から成るゲート電極の仕事関数を比較的容易に制御する技術が記載されている。ただし、特許文献1に記載の技術の目的はN型のFETとP型のFETとが異なる仕事関数を有するように仕事関数の値を制御することであり、仕事関数のばらつきを抑えることではない。

【0004】

特許文献2(特開2007−8099号公報)には、トランジスタのゲート電極およびゲート絶縁膜を構成する元素と異なる電気陰性度を有する元素、例えば炭素(C)、フッ素(F)、塩素(Cl)、リン(P)、ヒ素(As)またはアンチモン(Sb)を含む層を形成することにより、ゲート電極の実効仕事関数をしきい値電圧が最適なものとなるように制御することが記載されている。ただし、特許文献2に記載の技術の目的はトランジスタの仕事関数およびしきい値電圧の値を制御することであり、仕事関数のばらつきを抑えることではない。

【0005】

特許文献3(特開2006−245324号公報)には、例えばTi(チタン)炭化物、Ta(タンタル)炭化物、W(タングステン)炭化物などの金属の炭素化合物を含むゲート電極を有するMISトランジスタを形成することが記載されている。

【0006】

特許文献4(特開2004−319722号公報)には、シリコン膜上に金属膜を堆積したデュアルポリメタルゲート電極を有するMISFETにおいて、前記金属膜に炭素を注入することで金属膜(例えばタングステン)に不純物が拡散することを防ぎ、それによってMISFETのしきい値電圧変動を少なくすることが記載されている。

【0007】

特許文献5(特開平11−224947号公報)には、結晶粒径が30nm以下のメタルゲート電極を形成することで、MOS(Metal Oxide Semiconductor)トランジスタのしきい値電圧のばらつきを防止することが記載されている。ここではスパッタリング法を用いてメタルゲート電極に炭素を導入することにより、MOSトランジスタのしきい値電圧のばらつき抑えている。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特開2010−109214号公報

【特許文献2】特開2007−8099号公報

【特許文献3】特開2006−245324号公報

【特許文献4】特開2004−319722号公報

【特許文献5】特開平11−224947号公報

【発明の概要】

【発明が解決しようとする課題】

【0009】

MISFETを微細化した場合、それに伴ってMISFETのチャネル領域は小さくなり、大きなチャネル領域を有するMISFETに比べてチャネル領域内の単位体積当たりの不純物数が多くなる。このようなMISFETでは、チャネル領域内の不純物の分布が全体的にばらつくため、MISFETのしきい値電圧(以下、単に「しきい値」または「Vth」ともいう)のばらつきが大きくなる。これに対し、MISFETのゲート絶縁膜にhigh−k膜(高誘電率膜)を用い、さらにゲート電極にメタルゲート電極(金属電極)を用いた場合、チャネル領域に導入する不純物数を低減することができるため、チャネル領域内の不純物数を少なくしてVthのばらつきを抑えることが可能となる。

【0010】

メタルゲート電極とhigh−k膜とを含むMISFETのしきい値は、メタルゲート電極の仕事関数およびhigh−k膜の材質などで決まる。ゲート電極の一部であるメタルゲート電極は複数の金属粒子により構成されており、複数の金属粒子のそれぞれを構成する結晶(グレイン)は隣接し合うグレイン同士であっても異なる結晶の向き(配向性)を有している。ここで、配向性が異なるグレインのそれぞれの中を電子が通る場合、それぞれのグレイン毎に仕事関数が異なることとなる。

【0011】

ゲート電極のサイズが縮小されたMISFETでは、メタルゲート電極が配向性の異なる小数の大きなグレインにより構成されている場合が考えられる。この場合、例えばメタルゲート電極端部と反対側の端部とで仕事関数が大きく異なる可能性が高くなる。つまり、一つのメタルゲート電極内であっても場所によって仕事関数が異なるため、メタルゲート電極の仕事関数がメタルゲート電極内で全体的にばらつくことになる。メタルゲート電極の仕事関数のばらつきはそのメタルゲート電極を有するMISFETのVthがばらつく原因となるため、high−k膜およびメタルゲート電極を用いてMISFETを構成するメリットを損なう問題がある。つまり、メタルゲート電極中の材料不均一が原因となり、MISFETのしきい値のばらつきを引き起こす。また、MISFETのVthがばらつくと、半導体装置の信頼性が低下し、また、製品の歩留まりが減少する問題もある。これらの問題は、半導体装置の微細化の大きな妨げとなる。

【0012】

本発明の目的は、メタルゲート電極を有するMISFETの特性ばらつきを抑制することにある。

【0013】

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

【課題を解決するための手段】

【0014】

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、次のとおりである。

【0015】

本発明の好ましい一態様である半導体装置は、半導体基板上に第1ゲート絶縁膜を介して形成された炭素を含む第1金属ゲート電極と、

前記第1金属ゲート電極の直下の前記半導体基板の主面に形成された第1導電型の第1チャネル領域と、

前記半導体基板の主面に前記第1チャネル領域を挟むように形成された前記第1導電型と異なる第2導電型の第1ソース・ドレイン領域と、

を有する第1電荷効果トランジスタを含むものである。

【0016】

また、本発明の好ましい一態様である半導体装置の製造方法は、半導体基板上の第1領域に形成された金属ゲート電極、第1導電型を有するチャネル領域および前記第1導電型と異なる第2導電型を有するソース・ドレイン領域を有する電界効果トランジスタを含む半導体装置の製造方法であって、

(a)前記半導体基板の主面の前記第1領域に前記第1導電型を有する不純物を注入して前記チャネル領域を形成する工程と、

(b)前記半導体基板上に絶縁膜および金属膜を順次積層する工程と、

(c)前記金属膜に炭素を導入する工程と、

(d)前記(c)工程後、前記金属膜を加工して前記金属ゲート電極を形成する工程と、

(e)前記半導体基板の主面に前記第2導電型の不純物を注入して前記チャネル領域を挟むように前記ソース・ドレイン領域を形成する工程と、

を有するものである。

【発明の効果】

【0017】

本願において開示される発明のうち、代表的なものによって得られる効果を簡単に説明すれば以下のとおりである。

【0018】

代表的な実施の形態によれば、メタルゲート電極を有するMISFETの特性ばらつきを抑制することができる。

【図面の簡単な説明】

【0019】

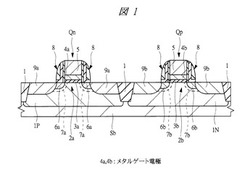

【図1】本発明の実施の形態1である半導体装置の断面図である。

【図2】本発明の実施の形態1である半導体装置の断面図である。

【図3】本発明の実施の形態1である半導体装置の製造工程を示す断面図である。

【図4】図3に続く半導体装置の製造工程中の断面図である。

【図5】図4に続く半導体装置の製造工程中の断面図である。

【図6】図5に続く半導体装置の製造工程中の断面図である。

【図7】図6に続く半導体装置の製造工程中の断面図である。

【図8】図7に続く半導体装置の製造工程中の断面図である。

【図9】図8に続く半導体装置の製造工程中の断面図である。

【図10】図9に続く半導体装置の製造工程中の断面図である。

【図11】本発明の実施の形態2である半導体装置の製造工程を示す断面図である。

【図12】図11に続く半導体装置の製造工程中の断面図である。

【図13】図12に続く半導体装置の製造工程中の断面図である。

【図14】図13に続く半導体装置の製造工程中の断面図である。

【図15】図14に続く半導体装置の製造工程中の断面図である。

【図16】本発明の実施の形態2である半導体装置の平面図である。

【図17】本発明の実施の形態3である半導体装置の製造工程を示す断面図である。

【図18】図17に続く半導体装置の製造工程中の断面図である。

【図19】本発明の実施の形態4である半導体装置の製造工程を示す断面図である。

【図20】図19に続く半導体装置の製造工程中の断面図である。

【図21】比較例として示す半導体装置の断面図である。

【発明を実施するための形態】

【0020】

以下、本発明の実施の形態を図面に基づいて詳細に説明する。なお、実施の形態を説明するための全図において、同一の機能を有する部材には同一の符号を付し、その繰り返しの説明は省略する。また、以下の実施の形態では、特に必要なとき以外は同一または同様な部分の説明を原則として繰り返さない。

【0021】

(実施の形態1)

図1を用いて、本実施の形態を説明する。図1は、本実施の形態のCMISFET(Complementary MISFET:相補型MISトランジスタ)を示す断面図である。図1に示すCMISFET(以下、単に「CMIS」という)は、例えばSOC(System on a chip)の半導体チップ上に形成された素子である。図1では、半導体基板の主面に形成された半導体素子よりも上層のプラグ、層間絶縁膜および配線などを含む積層構造体の図示は省略している。

【0022】

図1に示すように、本実施の形態のCMISは半導体基板Sbの主面に形成されており、半導体基板Sbの主面に形成された複数の素子分離領域1などにより複数の領域に区切られている。すなわち、半導体基板Sbの主面にはNチャネル型のMISFET(N型MISFETQn)と、Pチャネル型のMISFET(P型MISFETQp)とが形成された領域とがある。

【0023】

N型MISFETQnは半導体基板Sbの主面にP型の不純物(たとえばB(ホウ素))が導入されて形成されたPウエル1P上にゲート絶縁膜3aを介して形成されたゲート電極と、ゲート電極の横の半導体基板Sbの主面にN型の不純物(たとえばAs(ヒ素))が導入されて形成されたソース・ドレイン領域を構成するエクステンション領域6aおよび拡散層9aとを有している。N型MISFETQnのゲート電極はゲート絶縁膜3a上に形成されたメタルゲート電極(金属ゲート電極)4aと、メタルゲート電極4a上に接して形成されたポリシリコン(多結晶シリコン)からなるポリシリコンゲート電極5とからなる。

【0024】

エクステンション領域6aはゲート電極の直下のPウエル1Pの上面のチャネル領域2aを挟むように半導体基板Sbの主面に形成されており、拡散層9aはチャネル領域2aおよびエクステンション領域6aを含む領域を挟むように配置されている。拡散層9aはエクステンション領域6aよりも接合深さが深く、エクステンション領域6aよりも不純物濃度が高いN型の半導体領域である。すなわち、拡散層9aはエクステンション領域6aよりも半導体基板Sbの主面から半導体基板Sbの裏面方向に向けて深い位置にまでN型の不純物(例えばAs(ヒ素))を導入して形成されている。Pウエル1Pは拡散層9aよりも接合深さが深く、比較的不純物濃度が低いP型の半導体領域である。

【0025】

また、半導体基板Sb内であってPウエル1Pの上面には、接合深さがエクステンション領域6aよりも深く拡散層9aよりも浅い領域にホウ素(B)が導入されたハロー領域7aが形成されている。ハロー領域7aはソース・ドレイン間のリーク電流の発生を防ぐために形成される半導体領域であり、ソース・ドレイン領域とは異なる導電型の不純物を半導体基板Sbに打ち込むことで形成される。ハロー領域7aは半導体基板Sbの主面からPウエル1Pとエクステンション領域6aとの接合部の近傍に亘って形成されている。

【0026】

ゲート絶縁膜3aは酸化シリコン膜などよりも誘電率が高い高誘電率膜(high−k膜)を含む絶縁膜である。図示はしていないが、ゲート絶縁膜3aと半導体基板Sbとの間には酸化シリコン膜からなるゲート絶縁膜が介在していてもよい。

【0027】

N型MISFETQnと同様に、P型MISFETQpは、半導体基板Sbの主面にN型の不純物(たとえばAs(ヒ素))が導入されて形成されたNウエル1N上にゲート絶縁膜3bを介して形成されたゲート電極と、半導体基板Sbの主面にP型の不純物(たとえばB(ホウ素))が導入されて形成されたソース・ドレイン領域を構成するエクステンション領域6bおよび拡散層9bとを有している。エクステンション領域6bおよび拡散層9bはP型MISFETQpのソース・ドレイン領域を構成し、拡散層9a、エクステンション領域6aと同様に、P型MISFETQpのチャネル領域2bを挟むようにエクステンション領域6bが形成され、チャネル領域2bおよびエクステンション領域6bを挟むように拡散層9bが形成されている。チャネル領域2bはメタルゲート電極4bを含むゲート電極の直下に形成されている。P型MISFETQpのゲート電極はゲート絶縁膜3b上に形成されたメタルゲート電極(金属ゲート電極)4bと、メタルゲート電極4b上に形成されたポリシリコンからなるポリシリコンゲート電極5とからなる。

【0028】

また、半導体基板Sb内であってNウエル1Nの上面には、接合深さがエクステンション領域6bよりも深く拡散層9bよりも浅い領域にホウ素(B)が導入されたハロー領域7bが形成されている。ハロー領域7bはソース・ドレイン間のリーク電流の発生を防ぐために形成される半導体領域であり、ソース・ドレイン領域とは異なる導電型の不純物を半導体基板Sbに打ち込むことで形成される。ハロー領域7bは半導体基板Sbの主面からNウエル1Nとエクステンション領域6bとの接合部の近傍に亘って形成されている。

【0029】

ゲート絶縁膜3bは酸化シリコン膜などよりも誘電率が高い高誘電率膜(high−k膜)を含む絶縁膜である。図示はしていないが、ゲート絶縁膜3bと半導体基板Sbとの間には酸化シリコン膜からなるゲート絶縁膜が介在していてもよい。

【0030】

メタルゲート電極4a、4bは例えば窒化チタン、窒化タングステンまたはニッケルシリサイドからなる金属膜である。ポリシリコンゲート電極5、メタルゲート電極4aおよびゲート絶縁膜3aからなる積層パターンの側壁には、酸化シリコン膜または窒化シリコン膜もしくはそれらの積層膜により構成されたサイドウォール8が形成されている。また、ポリシリコンゲート電極5、メタルゲート電極4bおよびゲート絶縁膜3bからなる積層パターンの側壁にも、酸化シリコン膜または窒化シリコン膜もしくはそれらの積層膜により構成されたサイドウォール8が形成されている。

【0031】

ここで、金属ゲート電極であるメタルゲート電極4a、4bには炭素(C)がイオン注入法により注入されている。ただし、ポリシリコンゲート電極5、ゲート絶縁膜3a、3bおよび半導体基板Sbには炭素は注入されていない。つまり、N型MISFETQnではメタルゲート電極4aにのみ炭素が注入されており、P型MISFETQpではメタルゲート電極4bにのみ炭素が注入されている。

【0032】

次に、本実施の形態の半導体装置の効果を説明する。

【0033】

半導体装置の微細化によりチャネル領域の幅が狭まったMISFETは、比較的狭いチャネル領域内に多数の不純物を含むことになる。チャネル領域の幅、つまりソース・ドレイン領域を構成するエクステンション領域の間の距離が小さくなるほど、チャネル領域内の単位体積当たりの不純物数は増加し、チャネル領域内の不純物の分布にばらつきが生じやすくなる。狭いチャネル領域内に多数の不純物を含むMISFETでは、チャネル領域内の不純物の分布がばらつくことで、しきい値(Vth)のばらつきが増大する問題がある。半導体装置内に多数のMISFETが形成されている場合、隣接するMISFET間でも大きくしきい値(Vth)が異なる現象が起こるため、それらのMISFETを含む半導体装置を有する製品の歩留まりが低下する問題がある。

【0034】

MISFETは、性能を保持したまま消費電力を低減させるために、ゲート電極に金属材料を使用することでゲートの空乏化を抑制するとともに、ゲート絶縁膜に高誘電率を有する材料(high−k膜)を用いることで電気的な容量膜厚を変えずに物理的なゲート絶縁膜膜厚を確保することができる。さらに、ゲート電極に用いた金属材料層(メタルゲート電極)の仕事関数でしきい値を制御することができるため、チャネル領域に導入する不純物の量を低減することが可能となる。つまり、メタルゲート電極を用いてゲート電極の仕事関数を低減することによりMISFETのしきい値を低減することができるため、チャネル領域に導入する不純物の量が少なくてもMISFETを駆動することができる。ゲート電極に多結晶シリコンのみを用い、ゲート絶縁膜にシリコン酸化膜のみを用いる構造のMISFETに比べ、メタルゲート電極およびhigh−k膜を用いたMISFETではチャネル領域内の不純物数を減らすことができるので、チャネル領域内の不純物の離散に起因するばらつきを大幅に低減することが可能である。

【0035】

しかしながら、メタルゲート電極を有するMISFETであっても、メタルゲート電極を構成するグレイン(結晶)の粒径が大きいことに起因して、MISFETのしきい値がばらつく問題がある。このような問題の存在は半導体装置の微細化の大きな障壁となり、これを解決しなければ、将来的に高集積度でかつ低コストな製品を製造することが困難となる。

【0036】

上記のように、グレインの粒径が大きい場合のMISFETの断面図を、比較例として図21に示す。図21に示すN型MISFETQxは、図1に示すN型MISFETQnとほぼ同様の構造を有しているが、N型MISFETQnと異なりN型MISFETQxのメタルゲート電極4x内には炭素(C)が導入されていない。図21ではメタルゲート電極4xを構成するグレインを示しており、また、グレインの結晶の方位(配向)を各グレイン内に矢印で示している。図21に示すように、各グレインの結晶の配向は一定ではない。ここでは、メタルゲート電極4xのグレインの粒径が大きく、例えばグレインの直径または半径がメタルゲート電極4xの膜厚以上の大きさを有している場合、すなわち、メタルゲート電極4x内の一つのグレインの下面と上面とがメタルゲート電極4xの下面と上面とに露出している場合を示している。

【0037】

メタルゲート電極4xの仕事関数はグレインの配向性によって異なり、また、ゲート電極の仕事関数のばらつきはMISFETのしきい値のばらつかせる性質を有している。したがって、仕事関数はグレイン毎に異なる値となるため、複数の大きな粒径のグレインにより構成されるメタルゲート電極4xはその内部の一部と他の部分とで仕事関数が異なる状態となる。

【0038】

これに対し、本実施の形態ではメタルゲート電極4a、4bに炭素を導入しているため、図2に示すように、メタルゲート電極4a、4bのそれぞれを構成するグレインの大きさが小さくなっている。図2は図1と同一の領域を示す断面図であるが、メタルゲート電極4a、4bのそれぞれを構成するグレインの形状を示している。

【0039】

図2に示すように、本実施の形態のMISFETを構成するメタルゲート電極4a、4b内のグレインの粒径は、比較例である図21のN型MISFETQxを構成するメタルゲート電極4x内のグレインに比べて小さい。つまり、メタルゲート電極4a、4b内のグレインの平均の粒径は、比較例であるメタルゲート電極4x内のグレインの平均の粒径に比べて小さい。このため、図2および図21に示したメタルゲート電極がほぼ同一の膜厚を有している場合、図2に示すメタルゲート電極4a、4bの方が図21に示すメタルゲート電極4xよりもメタルゲート電極内のグレイン数が多くなる。このような違いは、図2のメタルゲート電極4a、4b内に炭素を導入し、熱負荷時などにグレインが大きく成長することを防いでいることにより生じるものである。なお、ここでいうグレインの粒径とは、各グレイン内の二つの端部を結ぶ直線的な距離のうち、最も大きい距離のことを指すものとする。

【0040】

図2に示す本実施の形態のMISFETであっても、メタルゲート電極4a、4bを構成する複数のグレインはそれぞれ異なった配向性を有しており、グレイン毎に仕事関数が異なる。しかし、ここではグレインの粒径を小さく抑えることによりメタルゲート電極4a内およびメタルゲート電極4b内のグレイン数を増やしているため、グレインの結晶の配向のばらつきがメタルゲート電極内において全体的に平均化される。したがって、メタルゲート電極の一部と、そのメタルゲート電極の他の部分とで仕事関数が異なることを避けることができる。また、半導体装置内に複数形成されるMISFET同士の間でゲート電極の仕事関数が大きく異なることに起因してMISFET同士の間でしきい値電圧がばらつくことを防ぐことができる。

【0041】

上記のように、本実施の形態の半導体装置では、MISFETのメタルゲート電極内に炭素を導入することで、メタルゲート電極を構成するグレインの粒径を小さくしてメタルゲート電極内のグレイン数を増やしている。これにより、グレインの配向性を平均化しているため、グレインの配向性のばらつきに起因して仕事関数がばらつくことを抑えることができる。これにより、ゲート電極の仕事関数のばらつきの発生によりMISFETのしきい値電圧がばらつくことを防ぐことができるため、半導体装置の信頼性を向上させることができる。また、MISFETのしきい値のばらつきを抑えることができるので、MISFETの微細化が容易になり、半導体装置の性能を向上させることができる。

【0042】

次に、図3〜図11を用いて、本実施の形態の半導体装置を構成するCMISFETの製造方法を説明する。

【0043】

まず、図3に示すように、主面に表面保護膜(図示しない)を形成した半導体基板Sbに、フォトリソグラフィー技術、ドライエッチング法、成膜工程、CMP(化学機械研磨:Chemical Mechanical Polishing)法を用いて、浅溝素子分離構造である素子分離領域1を形成する。ここで、半導体基板Sbの主面は、半導体基板Sbの主面に形成された複数の素子分離領域1などにより複数の領域に区切られている。すなわち、半導体基板Sbの主面にはN型MISFET形成領域1Aと、P型MISFET形成領域1Bとがある。

【0044】

次に、図4に示すように、フォトリソグラフィー技術、イオン注入法を用いて、半導体基板Sb上に形成したレジスト膜の開口部の下部のN型MISFET形成領域1Aの半導体基板Sbの主面に、接合深さが比較的深いPウエル1Pを形成する。同様にして、P型MISFET形成領域1Bの半導体基板Sbの主面に比較的深い接合深さを有するNウエル1Nを形成する。

【0045】

Pウエル1Pは、P型の不純物(例えばホウ素(B))を半導体基板Sbの主面にイオン注入して形成する。このとき、レジスト膜をマスクとすることでP型MISFET形成領域1Bの半導体基板Sbの主面にP型の不純物が注入されないようにする。Nウエル1Nは、N型の不純物(例えばヒ素(As)またはリン(P))を半導体基板Sbの主面にイオン注入して形成する。このとき、レジスト膜をマスクとすることでN型MISFET形成領域1Aの半導体基板Sbの主面にN型の不純物が注入されないようにする。このようにしてPウエル1PとNウエル1Nとの打ち分けを行うが、Pウエル1PおよびNウエル1Nはどちらを先に形成しても構わない。

【0046】

次に、図5に示すように、半導体基板Sbの表面を洗浄した後に、絶縁膜3および金属膜4を順次形成する。絶縁膜3は酸化シリコン膜よりも誘電率が高い、例えばHf(ハフニウム)を含むhigh−k膜(高誘電率膜)である。ここでは、後の工程で形成するN型MISFETおよびP型MISFETのそれぞれのしきい値を目的の値とするために、N型MISFET形成領域1AとP型MISFET形成領域1Bとで絶縁膜3の材質を異なるものとしてもよい。その場合は、例えば絶縁膜3上にN型MISFET形成領域1AとP型MISFET形成領域1Bとで異なる部材からなる膜をそれぞれ配置し、その状態で熱処理を行って絶縁膜3と絶縁膜3上の膜とを反応させる方法が考えられる。

【0047】

金属膜4は例えば窒化チタン、窒化タングステンまたはニッケルシリサイドからなり、絶縁膜3を形成した後にスパッタリング法などを用いて半導体基板Sbの全面の上部に形成する。ここでは、後のドライエッチング法によるゲート電極のパターニングを容易にするために、金属膜4の膜厚を20〜50nmで形成する。

【0048】

金属膜4を形成した後に、半導体基板Sbの主面の上方から炭素(C)をイオン注入することにより、金属膜4内に炭素(C)を導入する。ここでのイオン注入の加速エネルギーは10〜50keVとし、注入量は1014〜1016cm−2とし、投影飛程が金属膜4内に存在するように設定する。なお、投影飛程とは、注入物が固体表面から侵入した深さである。すなわち、投影飛程はイオン注入を行う対象の上面から、イオン注入を行って注入されたイオンが打ち込まれた深さ方向の距離のことを指す。つまり、金属膜4に炭素を打ち込む上記工程では、金属膜4のみに炭素を注入し、絶縁膜3および半導体基板Sbには炭素が注入されないようにする。

【0049】

次に、図6に示すように、高濃度でリン(P)が導入されたポリシリコン膜SFを金属膜4上にCVD(Chemical Vapor Deposition)法などを用いて形成する。

【0050】

次に、図7に示すように、フォトリソグラフィー技術およびドライエッチング法を用いてポリシリコン膜SF、金属膜4および絶縁膜3をパターニングすることで、N型MISFET形成領域1Aにポリシリコン膜SFからなるポリシリコンゲート電極5および金属膜4からなるメタルゲート電極4aを含むゲート電極を形成し、絶縁膜3からなるゲート絶縁膜3aを形成する。また、同一のパターニング工程により、P型MISFET形成領域1Bにポリシリコン膜SFからなるポリシリコンゲート電極5および金属膜4からなるメタルゲート電極4bを含むゲート電極を形成し、絶縁膜3からなるゲート絶縁膜3bを形成する。

【0051】

次に、図8に示すように、N型MISFET形成領域1Aを露出するレジスト膜(図示しない)を半導体基板Sb上に形成し、半導体基板Sbの主面に低い濃度でN型の不純物であるヒ素イオンを10keVのエネルギー、1×1015cm−2の注入量で打ち込むことにより、Pウエル1Pよりも接合深さが浅いN−領域であるエクステンション領域6aを形成する。続いて、前記レジスト膜をマスクとしてN型MISFET形成領域1Aの半導体基板Sbの主面にP型の不純物であるボロンイオンを10keVのエネルギー、2×1013cm−2の注入量で打ち込むことにより、エクステンション領域6aとほぼ同じ領域にハロー領域7aを形成する。ハロー領域7aはエクステンション領域6aよりも接合深さが深く、Pウエル1Pよりも接合深さが浅いP型の半導体領域である。

【0052】

同様に、P型MISFET形成領域1Bを露出するレジスト膜(図示しない)を半導体基板Sb上に形成し、半導体基板Sbの主面に低い濃度でP型の不純物であるフッ化ボロンイオンを5keVのエネルギー、1×1015cm−2の注入量で打ち込むことにより、Nウエル1Nよりも接合深さが浅いP−領域であるエクステンション領域6bを形成する。続いて、前記レジスト膜をマスクとしてP型MISFET形成領域1Bの半導体基板Sbの主面にN型の不純物であるヒ素を70keVのエネルギー、2×1013cm−2の注入量で打ち込むか、またはリンイオンを30keVのエネルギー、2×1013cm−2の注入量で打ち込むことにより、エクステンション領域6bとほぼ同じ領域にハロー領域7bを形成する。ハロー領域7bはエクステンション領域6bよりも接合深さが深く、Nウエル1Nよりも接合深さが浅いN型の半導体領域である。

【0053】

ここで、ソース・ドレイン領域であるエクステンション領域6a、6bを形成するイオン注入時、およびハロー領域7a、7bを形成するイオン注入時に、半導体基板Sbの主面に対して入射するイオンビームの角度を傾斜させることで、ゲート電極と、不純物添加層、すなわちエクステンション領域およびハロー領域とのオーバーラップの調整をすることも可能である。また、図4を用いて説明したイオン注入工程と同様に、エクステンション領域6a、6bはどちらを先に形成しても構わない。

【0054】

次に、図9に示すように、半導体基板Sbの表面を洗浄した後に、成膜とドライエッチング法を用いて、N型MISFET形成領域1A(図8参照)およびP型MISFET形成領域1B(図8参照)のゲート電極のそれぞれの側壁に絶縁膜からなるサイドウォール8を自己整合的に形成する。

【0055】

その後、N型MISFET形成領域1Aを露出するレジスト膜(図示しない)を半導体基板Sb上に形成し、半導体基板Sbの主面に高い濃度でN型の不純物であるヒ素イオンを70keVのエネルギー、1×1016cm−2の注入量で打ち込むことにより、Pウエル1Pよりも接合深さが浅く、エクステンション領域6aおよびハロー領域7aよりも接合深さが深いN+領域である拡散層9aを形成する。

【0056】

同様に、P型MISFET形成領域1Bを露出するレジスト膜(図示しない)を半導体基板Sb上に形成し、半導体基板Sbの主面に高い濃度でP型の不純物であるホウ素イオンを30keVのエネルギー、1×1015cm−2の注入量で打ち込むことにより、Nウエル1Nよりも接合深さが浅く、エクステンション領域6bおよびハロー領域7bよりも接合深さが深いP+領域である拡散層9bを形成する。拡散層9aおよび拡散層9bは、どちらを先に形成しても構わない。

【0057】

これにより、N型MISFET形成領域1A(図8参照)には、Pウエル1P上にゲート絶縁膜3aを介して形成されたメタルゲート電極4aおよびポリシリコンゲート電極5からなるゲート電極と、ソース・ドレイン領域を構成するエクステンション領域6aおよび拡散層9aとを有するN型MISFETQnが形成される。P型MISFET形成領域1B(図8参照)には、Nウエル1N上にゲート絶縁膜3bを介して形成されたメタルゲート電極4bおよびポリシリコンゲート電極5からなるゲート電極と、ソース・ドレイン領域を構成するエクステンション領域6bおよび拡散層9bとを有するP型MISFETQpが形成される。

【0058】

その後、エクステンション領域6a、6b、拡散層9aおよび9bなどの不純物拡散層を形成するために導入した不純物を活性化するための熱処理を行う。この熱処理工程では、導入した不純物の拡散を抑制するために、スパイクアニールを1050℃で窒素雰囲気中で実施する。スパイクアニール以外にも、瞬時熱アニール、あるいはフラッシュアニール、炉体を用いたアニールなどを用いることも可能である。図5を用いて説明したようにメタルゲート電極となる金属膜4に炭素(C)を注入しない場合、上記のような熱処理により半導体基板が高温になると、メタルゲート電極を構成するグレインが急速に成長するため、図21に示す比較例のようにメタルゲート電極内のグレインの粒径が大きくなる。これに対し、本実施の形態の半導体装置の製造工程ではメタルゲート電極4a、4bとなる金属膜4(図5参照)に炭素(C)を導入することにより、熱負荷時にメタルゲート電極4a、4bを構成するグレインの成長速度を遅くすることができる。このため、完成後の半導体装置内のメタルゲート電極4a、4bを構成するグレインの粒径を小さくし、より多くのグレインによりメタルゲート電極4a、4bを構成することができる。

【0059】

本発明は半導体基板Sb上に導入する不純物に係るものであるので、この後の工程の詳しい説明は省略するが、上記工程の後は、以下の工程を行うことで図10に示す半導体装置が完成する。すなわち、図9に示す構造を得た後、コンタクトプラグを形成する領域に金属シリサイド領域を形成する。つまり、半導体膜が露出している領域であるポリシリコンゲート電極5の表面および各MISFETのソース・ドレイン領域の表面に例えばニッケル(Ni)などを含むシリサイド層10を形成する。このとき、シリサイド層10を形成するために金属膜と半導体基板Sbのシリコンとを反応させることを目的として高温のアニール(熱処理)を行う。

【0060】

続いて、半導体基板Sb上シリコン窒化膜および絶縁膜を堆積することにより層間絶縁膜11を形成した後、CMP法などにより層間絶縁膜11の上面を平坦化する。その後、周知の技術を用い、層間絶縁膜11を貫通してポリシリコンゲート電極5および各トランジスタのソース・ドレイン領域に電気的に接続されるコンタクトプラグ12を形成し、層間絶縁膜11上に層間絶縁膜13を形成する。続いて、層間絶縁膜13に配線溝を形成した後、周知のシングルダマシンプロセスを用いて前記配線溝を埋め込む配線14を形成することで、図10に示す半導体装置が完成する。

【0061】

本実施の形態では、ゲート電極内にメタルゲート電極を含むMISFETを有する半導体装置の製造工程において、メタルゲート電極4a、4bのそれぞれに炭素(C)を導入することにより、メタルゲート電極4a、4bの形成後の熱処理工程などによりメタルゲート電極4a、4bを構成するグレイン(結晶)の粒径が大きくなることを防いでいる。これにより、メタルゲート電極4a、4bは炭素が導入されない場合に比べてより小さく、より多いグレインを含むことになる。上述したように、メタルゲート電極を構成するグレインの数が多ければグレインの配向性を均一化することができるため、グレインの配向性に起因した仕事関数のばらつきの発生を抑えることができる。これによりゲート電極の仕事関数のばらつきが抑えられるため、当該ゲート電極を含むMISFETのしきい値電圧(Vth)がばらつくをことを防ぐことが可能となる。

【0062】

このように、本実施の形態ではMISFETを構成するメタルゲート電極に炭素(C)をイオン注入により打ち込むことによりMISFETのしきい値のばらつきを抑えることができるため、当該MISFETを含む半導体製品の歩留まりを向上させることができる。

【0063】

また、上記のようにゲート電極の仕事関数のばらつきの発生によりMISFETのしきい値電圧がばらつくことを防ぐことができるため、半導体装置の信頼性を向上させることができる。また、MISFETのしきい値のばらつきを抑えることができるので、MISFET微細化が容易になり、半導体装置の性能を向上させることができる。

【0064】

(実施の形態2)

前記実施の形態では、後の工程でメタルゲート電極となる金属膜全てに炭素を注入する半導体装置について説明した。本実施の形態では図11〜図16を用い、本実施の形態の半導体装置であって、領域によって炭素を注入しないメタルゲート電極を有するMISFETを含む半導体装置を実現する製造プロセスの詳細を説明する。ここでは例としてSRAM(Static Random Access Memory)を構成するMISFETを形成する工程を説明する。

【0065】

まず、前記実施の形態1で図3および図4を用いて説明した工程と同様の工程を行うことにより、図11に示す構造を得る。なお、ここでは半導体基板Sb上にN型MISEFT形成領域2A、P型MISFET形成領域2B、N型MISEFT形成領域2CおよびP型MISFET形成領域2Dが存在する。つまり、図11に示すように、半導体基板Sbの主面には複数の素子分離領域1が形成されており、半導体基板Sbの主面は素子分離領域1によりN型MISEFT形成領域2A、P型MISFET形成領域2B、N型MISEFT形成領域2CおよびP型MISFET形成領域2Dに区切られている。N型MISEFT形成領域2AおよびN型MISEFT形成領域2Cの半導体基板Sbの主面にはPウエル1Pが形成されており、P型MISFET形成領域2BおよびP型MISFET形成領域2Dの半導体基板Sbの主面にはNウエル1Nが形成されている。

【0066】

ここで、N型MISEFT形成領域2Aは高電圧に対応する入出力回路を構成するN型MISFETを形成する領域であり、P型MISFET形成領域2Bは高電圧に対応する入出力回路を構成するP型MISFETを形成する領域である。また、N型MISEFT形成領域2Cは低耐圧対応のN型MISFETを形成する領域であり、P型MISFET形成領域2Dは低耐圧対応のP型MISFETを形成する領域である。

【0067】

次に、図12に示すように、high−k膜(高誘電率絶縁膜)である絶縁膜23a、23b、23cおよび23dを形成する。この際、後の工程で形成する各MISFETのしきい値を目標に合わせるために、MISFETのN型とP型とで前記high−k膜に異なる材質を用いる。また、高耐圧領域であるN型MISEFT形成領域2AおよびP型MISFET形成領域2Bの絶縁膜23a、23bは高電圧が印加されるゲート絶縁膜となるため、たとえば膜厚を7nm程度に増加させる。絶縁膜23a、23bの膜厚は入力時に対応する電圧により調整する。なお、図12では絶縁膜23a、23b、23cおよび23dのそれぞれの膜厚を同一の大きさで表わしている。続いて、半導体基板Sbの主面上に金属膜24を形成する。

【0068】

次に、図13に示すように、フォトリソグラフィー技術により、N型MISEFT形成領域2A、P型MISFET形成領域2Bをレジスト膜PR1で覆い、レジスト膜PR1から露出した低電圧MIS型トランジスタ形成領域であるN型MISEFT形成領域2C、P型MISFET形成領域2Dの金属膜24に、炭素イオンをイオン注入により添加し、金属膜24からなる金属膜24sを形成する。この際、炭素(C)のイオン注入は加速エネルギーを10〜50keVとし、注入量を1014〜1016cm−2とし、投影飛程が金属膜中に存在するように設定する。つまり、レジスト膜PR1から露出している金属膜24内にのみ炭素(C)が打ち込まれるようにし、金属膜24よりも下の構造物には炭素(C)が導入されないようにする。

【0069】

次に、図14に示すように、レジスト膜PR1を除去し、高濃度にリンが添加されたポリシリコン膜を堆積した後、フォトリソグラフィー技術およびドライエッチング法を用いてゲートのパターニングを行う。これにより、N型MISEFT形成領域2Aには、前記ポリシリコン膜からなるポリシリコンゲート電極5と、金属膜24からなるメタルゲート電極24aとを含むゲート電極が形成され、P型MISFET形成領域2Bには、前記ポリシリコン膜からなるポリシリコンゲート電極5と、金属膜24からなるメタルゲート電極24bとを含むゲート電極が形成される。また、N型MISEFT形成領域2Cには前記ポリシリコン膜からなるポリシリコンゲート電極5と、金属膜24sからなるメタルゲート電極24cとを含むゲート電極が形成され、P型MISFET形成領域2Dには前記ポリシリコン膜からなるポリシリコンゲート電極5と、金属膜24sからなるメタルゲート電極24dとを含むゲート電極が形成される。メタルゲート電極24a、24b、24cおよび24dは、半導体基板Sb上にそれぞれゲート絶縁膜25a、25b、25cおよび25dを介して形成されている。ゲート絶縁膜25a、25b、25cおよび25dはそれぞれ絶縁膜23a、23b、23cおよび23dからなるhigh−k膜である。なお、N型MISEFT形成領域2A、P型MISFET形成領域2Bのゲート電極高耐圧用MISFETに用いられるゲート電極であるので、N型MISEFT形成領域2C、P型MISFET形成領域2Dのゲート電極よりもゲート長が大きいパターンとする。

【0070】

この後の工程は前記実施の形態1で図8〜図10を用いて説明した工程と同様の工程を行うことにより、図15に示す本実施の形態の半導体装置が完成する。すなわち、レジスト膜(図示しない)を用いてN型MISEFT形成領域2A、2C、P型MISFET形成領域2Bおよび2Dのそれぞれの半導体基板Sbの主面に不純物を打ち分けることにより、エクステンション領域およびハロー領域を形成する。つまり、P型MISEFT形成領域2B、2Dにはフッ化ボロンイオンを例えばエネルギー5keV、注入量1×1015cm−2とする条件で注入してP−型のエクステンション領域26bを形成し、ヒ素イオンを例えばエネルギー70keV、注入量2×1013cm−2の条件でイオン注入するか、またはリンイオンをエネルギー30keV、注入量2×1013cm−2の条件でイオン注入してハロー領域27bを形成する。また、同様に、N型MISEFT形成領域2A、2Cにはヒ素イオンを例えばエネルギー10keV、注入量1×1015cm−2とする条件で注入してN−型のエクステンション領域26aを形成し、ホウ素イオンを例えばエネルギー10keV、注入量2×1013cm−2の条件でイオン注入してハロー領域27aを形成する。

【0071】

その後、各ゲート電極の側壁にサイドウォール8を形成した後、レジスト膜(図示しない)を用いてコンタクトのための拡散層29a、29bを形成する。ここでは、N+型の拡散層9aは、ヒ素イオンをエネルギー70keV、注入量1×1015cm−2の条件でイオン注入して形成し、P+型の拡散層9bは、ホウ素イオンをエネルギー30keV、注入量1×1015cm−2の条件でイオン注入して形成する。その後、半導体基板Sbの主面を洗浄した後に、拡散層などに導入した不純物を活性化するための熱処理を行う。これにより、N型MISFET形成領域2AおよびP型MISFET形成領域2Bには、比較的高耐圧なMISFETであるN型MISFETQa、P型MISFETQbがそれぞれ形成され、N型MISFET形成領域2CおよびP型MISFET形成領域2Dには、比較的低耐圧なMISFETであるN型MISFETQc、P型MISFETQdがそれぞれ形成される。続いて、前記実施の形態1と同様にして、シリコン表面が露出している領域にシリサイド層10を形成した後、層間絶縁膜11、コンタクトプラグ12、層間絶縁膜13および配線14を形成する。

【0072】

上記のようにして形成した本実施の形態のMISFETを含むSRAMの平面図を図16に示す。図16に示すSRAMを含む半導体装置は、主に情報を記憶する機能を有する記憶領域SRと、情報の入出力動作を行う入出力領域IOとを有しており、記憶領域SRには図15に示すN型MISEFT形成領域2C、P型MISFET形成領域2Dの低耐圧MISFETが形成され、入出力領域IOには、図15に示す高耐圧なMISFETであるN型MISEFTQaおよびP型MISFET形成領域Qbが形成されている。

【0073】

本実施の形態の半導体装置の特徴は、特にしきい値のばらつきを抑える必要がある低耐圧のMISFETのメタルゲート電極にのみ炭素(C)を注入し、周辺回路部を構成する高耐圧のMISFETのメタルゲート電極に炭素を注入しないことにある。これにより、低耐圧MISFETについては前記実施の形態1と同様の効果を得ることができる。また、高耐圧MISFETなどの炭素注入を必要としないMISFETのメタルゲート電極にまで炭素を注入することで高耐圧MISFETの配線抵抗が上昇するなどし、周辺回路部の再設計が必要となることを防ぐことができる。

【0074】

つまり、例えばゲート長、ゲート幅を最小の設計ルールで形成したMIS型トランジスタを用いるSRAMでは、メタルゲート電極に炭素を注入することにより、情報の書込み、読出しのマージンが設計基準よりも向上し、製品不良の発生率を大幅に低減することができる。また、前記炭素注入工程では、入出力領域IOなどの周辺回路部のメタルゲート電極形成領域をレジスト膜により覆って不純物(炭素)導入を抑制する。

【0075】

このとき、炭素が導入された金属膜24s(図13参照)からなるメタルゲート電極24c、24d(図15参照)を構成する複数のグレインの平均の粒径は、炭素が導入されなかった金属膜24(図13参照)からなるメタルゲート電極24a、24b(図15参照)を構成する複数のグレインの平均の粒径よりも小さくなる。つまり、周辺回路部のメタルゲート電極はメモリセル部に比べて大きなグレインを有することになるが、配線抵抗の上昇を抑制することができる。したがって、周辺回路部の再設計は不要となり、メモリセル部のみの再設計で済むため、短期間でマージン性不良率が少ないSOC製品の提供が可能となる。

【0076】

(実施の形態3)

本実施の形態では、図17〜図18を用いて本発明の実施の形態2を実現する半導体装置の製造プロセスの詳細を説明する。ここでは、前記実施の形態2とほぼ同様の製造工程を説明するが、本実施の形態と前記実施の形態2とでは異なる領域の対象のメタルゲート電極に炭素を注入する。ここでは、本実施の形態の半導体装置としてSOCを形成するものとして説明をする。

【0077】

まず、前記実施の形態2で図11、図12を用いて説明した工程と同様の工程を行う。ただし、半導体基板Sbの主面には、図17に示すようにN型MISEFT形成領域3A、P型MISFET形成領域3B、N型MISEFT形成領域3CおよびP型MISFET形成領域3Dが存在する。N型MISEFT形成領域3AおよびN型MISEFT形成領域3Cの半導体基板Sbの主面にはPウエル1Pが形成されており、P型MISFET形成領域3BおよびP型MISFET形成領域3Dの半導体基板Sbの主面にはNウエル1Nが形成されている。また、N型MISEFT形成領域3A、P型MISFET形成領域3B、N型MISEFT形成領域3CおよびP型MISFET形成領域3Dの半導体基板Sbの主面にはそれぞれhigh−k膜(高誘電率絶縁膜)である絶縁膜23a、23b、23cおよび23dが形成されている。絶縁膜23a、23b、23cおよび23d上には、金属膜24が形成されている。

【0078】

ここで、N型MISEFT形成領域3Aは高電圧N型MISFETを形成する領域であり、P型MISFET形成領域2Bは高電圧P型MISFETを形成する領域である。また、N型MISEFT形成領域2Cは低耐圧対応のN型MISFETを形成する領域であり、P型MISFET形成領域2Dは低耐圧対応のP型MISFETを形成する領域である。

【0079】

次に、図17に示すように、フォトリソグラフィー技術により、P型MISFET形成領域3B、3Dをレジスト膜PR2で覆い、レジスト膜PR2から露出したN型MISEFT形成領域3A、3Dの金属膜24に、炭素イオンをイオン注入により添加し、金属膜24からなる金属膜34sを形成する。この際、炭素(C)のイオン注入は加速エネルギーを10〜50keVとし、注入量を1014〜1016cm−2とし、投影飛程が金属膜中に存在するように設定する。つまり、金属膜24内にのみ炭素(C)が打ち込まれるようにし、金属膜24よりも下の構造物には炭素(C)が導入されないようにする。本実施の形態の半導体装置は、上記のように後の工程により形成されるN型のMISFETを構成する金属膜のみに炭素を注入していることが特徴となっている。なお、ここではN型MISFETのメタルゲート電極にのみ炭素を注入する方法について説明するが、逆にP型のMISFETのメタルゲート電極にのみ炭素を注入しても構わない。

【0080】

次に、図18に示すように、レジスト膜PR2を除去した後は、図14〜図15を用いて説明した工程を行うことにより、本実施の形態の半導体装置が完成する。つまり、金属膜24、34s上にポリシリコン膜を形成し、パターニングを行ってゲート電極を形成する。このとき、N型MISEFT形成領域3Aには絶縁膜23aからなるゲート絶縁膜25a上に金属膜34sからなるメタルゲート電極34aが形成され、P型MISFET形成領域3Bには絶縁膜23bからなるゲート絶縁膜25b上に金属膜24からなるメタルゲート電極34bが形成される。また、N型MISEFT形成領域3Cには絶縁膜23cからなるゲート絶縁膜25c上に金属膜34sからなるメタルゲート電極34cが形成され、P型MISFET形成領域3Dには絶縁膜23dからなるゲート絶縁膜25d上に金属膜24からなるメタルゲート電極34dが形成される。

【0081】

その後、各MISFET形成領域のエクステンション領域、ハロー領域、サイドウォール、拡散層、シリサイド層、層間絶縁膜、コンタクトプラグおよび配線などを形成することにより、図18に示す本実施の形態の半導体装置が完成する。

【0082】

本実施の形態の半導体装置の特徴は、炭素(C)をメタルゲート電極に導入しない場合に特にしきい値のばらつきが大きくなってしまうMISFETのメタルゲート電極のみに不純物(炭素)添加を実施し、グレインサイズの拡大を抑制することで、メタルゲートにおけるグレインの配向性による仕事関数ばらつきを押さえ、MISFETのしきい値ばらつきを小さくすることを可能としている。

【0083】

さらに、周辺回路部や炭素注入による対策が不要なメタルゲート電極には炭素注入工程においてレジスト膜などによりマスクをすることで、不純物導入を防ぐ。その結果、炭素(C)を導入しなかったメタルゲート電極を有するMISFETでは、配線抵抗の上昇を抑制することができる。したがって、周辺回路部の再設計は不要となり、短期間でマージン性不良率の少ないSOC製品の提供が可能となる。つまり、例えば図18に示すP型MISFET形成領域3D(図17参照)のゲート電極がMISFETの一部として機能するゲート電極ではなく、他のMISFETのゲート電極などに特定の電位を供給するための配線として機能する導体部である場合、MISFETとして機能しないゲート配線にまでしきい値ばらつきを防ぐ目的で炭素(C)を導入する必要はない。したがって、メタルゲート電極を含む当該ゲート配線に炭素(C)が打ち込まれることを防ぐことで、ゲート配線の配線抵抗が上昇することを防ぐことができる。

【0084】

このように、全てのメタルゲート電極に炭素(C)を導入するのではなく、そのゲート電極の特性および役割などに応じて炭素(C)を打ち分けることにより、配線抵抗の上昇を防ぐことができる。また、同様に炭素(C)の打ち分けを行うことにより、周辺回路部の再設計の手間を省くことができるため、半導体装置の製造コストの増大を防ぐことが可能となる。

【0085】

(実施の形態4)

本実施の形態の半導体装置では、前記実施の形態1の半導体装置とほぼ同様の構造を有し、MISFETのしきい値のばらつき低減を目的としてメタルゲート電極に導入する不純物を炭素以外の物質とする半導体装置について説明する。

【0086】

本実施の形態の半導体装置の製造工程では、まず前記実施の形態1において図4を用いて説明した工程を行う。

【0087】

次に、図19に示すように、図5を用いて説明した工程と同様にして半導体基板Sb上に絶縁膜3および金属膜4uを順次形成する。続いて、金属膜4uに不純物をイオン注入するが、ここで前記実施の形態1〜3と異なり、金属膜4uを構成するグレインの成長を抑えるための不純物としてハロゲン元素であるフッ素(F)、塩素(Cl)または不活性元素である窒素(N)をイオン注入する。このとき、注入するイオンにより、加速エネルギーを10〜100keVの範囲で調整し、イオン注入した元素が絶縁膜3内および半導体基板Sb内に漏れないようにすることが重要となる。また、前記不純物の添加量は、約1×1015cm−2程度とする。

【0088】

その後の工程は、前記実施の形態1で図6〜図10を用いて説明した工程と同様の工程を行うことで、図20に示す半導体装置が完成する。図20に示す半導体装置は図10に示した半導体装置とほぼ同一の構造を有しているが、メタルゲート電極に導入された不純物種が前記実施の形態1と異なる。N型MISFET形成領域1AおよびP型MISFET形成領域1Bの金属膜4u(図19参照)はパターニングされてそれぞれメタルゲート電極4p、4qとなっている。

【0089】

本実施の形態の半導体装置では、MISFETのメタルゲート電極のグレインサイズの拡大を抑制することが可能となり、その結果、メタルゲート電極におけるグレインの配向性による仕事関数ばらつきを押さえ、MISFETのしきい値ばらつきを小さくことができ、前記実施の形態1と同様の効果を得ることができる。このように、MISFETのしきい値ばらつきを抑えるためにメタルゲート電極に注入する元素は炭素(C)以外にフッ素(F)、塩素(Cl)または窒素(N)であってもよい。

【0090】

以上、本発明者らによってなされた発明をその実施の形態に基づき具体的に説明したが、本発明は前記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることはいうまでもない。

【0091】

例えば、前記実施の形態4ではメタルゲート電極にフッ素(F)、塩素(Cl)または窒素(N)を導入することで本発明の効果を得ているが、実施の形態2または実施の形態3で説明した半導体装置であってもメタルゲート電極にフッ素(F)、塩素(Cl)または窒素(N)を導入することで、実施の形態2または実施の形態3と同様の効果を得ることができる。

【産業上の利用可能性】

【0092】

本発明は、メタルゲート電極を有するMISFETを含む半導体装置の製造技術に適用して有効である。

【符号の説明】

【0093】

1 素子分離領域

1A、2A、2C、3A、3CA N型MISFET形成領域

1B、2B、2D、3B、3D P型MISFET形成領域

1N Nウエル

1P Pウエル

2a、2b チャネル領域

3 絶縁膜

3a、3b ゲート絶縁膜

4、4u 金属膜

4a、4b、4p、4q、4x メタルゲート電極

5 ポリシリコンゲート電極

6a、6b エクステンション領域

7a、7b ハロー領域

8 サイドウォール

9a、9b、29a、29b 拡散層

10 シリサイド層

11、13 層間絶縁膜

12 コンタクトプラグ

14 配線

23a〜23d 絶縁膜

24、24s、34s 金属膜

24a〜24d、34a〜34d メタルゲート電極

25a〜25d ゲート絶縁膜

26a、26b エクステンション領域

27a、27b ハロー領域

IO 入出力領域

PR1、PR2 レジスト膜

Qa、Qc、Qn、Qx N型MISFET

Qb、Qd、Qp P型MISFET

SF ポリシリコン膜

SR 記憶領域

Sb 半導体基板

【技術分野】

【0001】

本発明は、半導体装置およびその製造方法に関し、特に、メタルゲート電極を具備する電界効果トランジスタの製造に適用して有効な技術に関する。

【背景技術】

【0002】

微細化が求められているMISFET(Metal Insulator Semiconductor Field Effect Transistor:MIS型電界効果トランジスタ)では、ゲート絶縁膜の一部に高い誘電率を有するhigh−k膜を用い、また、ゲート電極の一部に金属材料からなるメタルゲート電極を用いることにより、MISFETのゲート絶縁膜を薄膜化し、かつリーク電流を低減することを可能としている。また、high−k膜およびメタルゲート電極の構成を変えることにより、MISFETのしきい値電圧を制御することが可能である。

【0003】

特許文献1(特開2010−109214号公報)には、ゲート電極の形成後に熱処理が施される場合でも、金属から成るゲート電極の仕事関数を比較的容易に制御する技術が記載されている。ただし、特許文献1に記載の技術の目的はN型のFETとP型のFETとが異なる仕事関数を有するように仕事関数の値を制御することであり、仕事関数のばらつきを抑えることではない。

【0004】

特許文献2(特開2007−8099号公報)には、トランジスタのゲート電極およびゲート絶縁膜を構成する元素と異なる電気陰性度を有する元素、例えば炭素(C)、フッ素(F)、塩素(Cl)、リン(P)、ヒ素(As)またはアンチモン(Sb)を含む層を形成することにより、ゲート電極の実効仕事関数をしきい値電圧が最適なものとなるように制御することが記載されている。ただし、特許文献2に記載の技術の目的はトランジスタの仕事関数およびしきい値電圧の値を制御することであり、仕事関数のばらつきを抑えることではない。

【0005】

特許文献3(特開2006−245324号公報)には、例えばTi(チタン)炭化物、Ta(タンタル)炭化物、W(タングステン)炭化物などの金属の炭素化合物を含むゲート電極を有するMISトランジスタを形成することが記載されている。

【0006】

特許文献4(特開2004−319722号公報)には、シリコン膜上に金属膜を堆積したデュアルポリメタルゲート電極を有するMISFETにおいて、前記金属膜に炭素を注入することで金属膜(例えばタングステン)に不純物が拡散することを防ぎ、それによってMISFETのしきい値電圧変動を少なくすることが記載されている。

【0007】

特許文献5(特開平11−224947号公報)には、結晶粒径が30nm以下のメタルゲート電極を形成することで、MOS(Metal Oxide Semiconductor)トランジスタのしきい値電圧のばらつきを防止することが記載されている。ここではスパッタリング法を用いてメタルゲート電極に炭素を導入することにより、MOSトランジスタのしきい値電圧のばらつき抑えている。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特開2010−109214号公報

【特許文献2】特開2007−8099号公報

【特許文献3】特開2006−245324号公報

【特許文献4】特開2004−319722号公報

【特許文献5】特開平11−224947号公報

【発明の概要】

【発明が解決しようとする課題】

【0009】

MISFETを微細化した場合、それに伴ってMISFETのチャネル領域は小さくなり、大きなチャネル領域を有するMISFETに比べてチャネル領域内の単位体積当たりの不純物数が多くなる。このようなMISFETでは、チャネル領域内の不純物の分布が全体的にばらつくため、MISFETのしきい値電圧(以下、単に「しきい値」または「Vth」ともいう)のばらつきが大きくなる。これに対し、MISFETのゲート絶縁膜にhigh−k膜(高誘電率膜)を用い、さらにゲート電極にメタルゲート電極(金属電極)を用いた場合、チャネル領域に導入する不純物数を低減することができるため、チャネル領域内の不純物数を少なくしてVthのばらつきを抑えることが可能となる。

【0010】

メタルゲート電極とhigh−k膜とを含むMISFETのしきい値は、メタルゲート電極の仕事関数およびhigh−k膜の材質などで決まる。ゲート電極の一部であるメタルゲート電極は複数の金属粒子により構成されており、複数の金属粒子のそれぞれを構成する結晶(グレイン)は隣接し合うグレイン同士であっても異なる結晶の向き(配向性)を有している。ここで、配向性が異なるグレインのそれぞれの中を電子が通る場合、それぞれのグレイン毎に仕事関数が異なることとなる。

【0011】

ゲート電極のサイズが縮小されたMISFETでは、メタルゲート電極が配向性の異なる小数の大きなグレインにより構成されている場合が考えられる。この場合、例えばメタルゲート電極端部と反対側の端部とで仕事関数が大きく異なる可能性が高くなる。つまり、一つのメタルゲート電極内であっても場所によって仕事関数が異なるため、メタルゲート電極の仕事関数がメタルゲート電極内で全体的にばらつくことになる。メタルゲート電極の仕事関数のばらつきはそのメタルゲート電極を有するMISFETのVthがばらつく原因となるため、high−k膜およびメタルゲート電極を用いてMISFETを構成するメリットを損なう問題がある。つまり、メタルゲート電極中の材料不均一が原因となり、MISFETのしきい値のばらつきを引き起こす。また、MISFETのVthがばらつくと、半導体装置の信頼性が低下し、また、製品の歩留まりが減少する問題もある。これらの問題は、半導体装置の微細化の大きな妨げとなる。

【0012】

本発明の目的は、メタルゲート電極を有するMISFETの特性ばらつきを抑制することにある。

【0013】

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

【課題を解決するための手段】

【0014】

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、次のとおりである。

【0015】

本発明の好ましい一態様である半導体装置は、半導体基板上に第1ゲート絶縁膜を介して形成された炭素を含む第1金属ゲート電極と、

前記第1金属ゲート電極の直下の前記半導体基板の主面に形成された第1導電型の第1チャネル領域と、

前記半導体基板の主面に前記第1チャネル領域を挟むように形成された前記第1導電型と異なる第2導電型の第1ソース・ドレイン領域と、

を有する第1電荷効果トランジスタを含むものである。

【0016】

また、本発明の好ましい一態様である半導体装置の製造方法は、半導体基板上の第1領域に形成された金属ゲート電極、第1導電型を有するチャネル領域および前記第1導電型と異なる第2導電型を有するソース・ドレイン領域を有する電界効果トランジスタを含む半導体装置の製造方法であって、

(a)前記半導体基板の主面の前記第1領域に前記第1導電型を有する不純物を注入して前記チャネル領域を形成する工程と、

(b)前記半導体基板上に絶縁膜および金属膜を順次積層する工程と、

(c)前記金属膜に炭素を導入する工程と、

(d)前記(c)工程後、前記金属膜を加工して前記金属ゲート電極を形成する工程と、

(e)前記半導体基板の主面に前記第2導電型の不純物を注入して前記チャネル領域を挟むように前記ソース・ドレイン領域を形成する工程と、

を有するものである。

【発明の効果】

【0017】

本願において開示される発明のうち、代表的なものによって得られる効果を簡単に説明すれば以下のとおりである。

【0018】

代表的な実施の形態によれば、メタルゲート電極を有するMISFETの特性ばらつきを抑制することができる。

【図面の簡単な説明】

【0019】

【図1】本発明の実施の形態1である半導体装置の断面図である。

【図2】本発明の実施の形態1である半導体装置の断面図である。

【図3】本発明の実施の形態1である半導体装置の製造工程を示す断面図である。

【図4】図3に続く半導体装置の製造工程中の断面図である。

【図5】図4に続く半導体装置の製造工程中の断面図である。

【図6】図5に続く半導体装置の製造工程中の断面図である。

【図7】図6に続く半導体装置の製造工程中の断面図である。

【図8】図7に続く半導体装置の製造工程中の断面図である。

【図9】図8に続く半導体装置の製造工程中の断面図である。

【図10】図9に続く半導体装置の製造工程中の断面図である。

【図11】本発明の実施の形態2である半導体装置の製造工程を示す断面図である。

【図12】図11に続く半導体装置の製造工程中の断面図である。

【図13】図12に続く半導体装置の製造工程中の断面図である。

【図14】図13に続く半導体装置の製造工程中の断面図である。

【図15】図14に続く半導体装置の製造工程中の断面図である。

【図16】本発明の実施の形態2である半導体装置の平面図である。

【図17】本発明の実施の形態3である半導体装置の製造工程を示す断面図である。

【図18】図17に続く半導体装置の製造工程中の断面図である。

【図19】本発明の実施の形態4である半導体装置の製造工程を示す断面図である。

【図20】図19に続く半導体装置の製造工程中の断面図である。

【図21】比較例として示す半導体装置の断面図である。

【発明を実施するための形態】

【0020】

以下、本発明の実施の形態を図面に基づいて詳細に説明する。なお、実施の形態を説明するための全図において、同一の機能を有する部材には同一の符号を付し、その繰り返しの説明は省略する。また、以下の実施の形態では、特に必要なとき以外は同一または同様な部分の説明を原則として繰り返さない。

【0021】

(実施の形態1)

図1を用いて、本実施の形態を説明する。図1は、本実施の形態のCMISFET(Complementary MISFET:相補型MISトランジスタ)を示す断面図である。図1に示すCMISFET(以下、単に「CMIS」という)は、例えばSOC(System on a chip)の半導体チップ上に形成された素子である。図1では、半導体基板の主面に形成された半導体素子よりも上層のプラグ、層間絶縁膜および配線などを含む積層構造体の図示は省略している。

【0022】

図1に示すように、本実施の形態のCMISは半導体基板Sbの主面に形成されており、半導体基板Sbの主面に形成された複数の素子分離領域1などにより複数の領域に区切られている。すなわち、半導体基板Sbの主面にはNチャネル型のMISFET(N型MISFETQn)と、Pチャネル型のMISFET(P型MISFETQp)とが形成された領域とがある。

【0023】

N型MISFETQnは半導体基板Sbの主面にP型の不純物(たとえばB(ホウ素))が導入されて形成されたPウエル1P上にゲート絶縁膜3aを介して形成されたゲート電極と、ゲート電極の横の半導体基板Sbの主面にN型の不純物(たとえばAs(ヒ素))が導入されて形成されたソース・ドレイン領域を構成するエクステンション領域6aおよび拡散層9aとを有している。N型MISFETQnのゲート電極はゲート絶縁膜3a上に形成されたメタルゲート電極(金属ゲート電極)4aと、メタルゲート電極4a上に接して形成されたポリシリコン(多結晶シリコン)からなるポリシリコンゲート電極5とからなる。

【0024】

エクステンション領域6aはゲート電極の直下のPウエル1Pの上面のチャネル領域2aを挟むように半導体基板Sbの主面に形成されており、拡散層9aはチャネル領域2aおよびエクステンション領域6aを含む領域を挟むように配置されている。拡散層9aはエクステンション領域6aよりも接合深さが深く、エクステンション領域6aよりも不純物濃度が高いN型の半導体領域である。すなわち、拡散層9aはエクステンション領域6aよりも半導体基板Sbの主面から半導体基板Sbの裏面方向に向けて深い位置にまでN型の不純物(例えばAs(ヒ素))を導入して形成されている。Pウエル1Pは拡散層9aよりも接合深さが深く、比較的不純物濃度が低いP型の半導体領域である。

【0025】

また、半導体基板Sb内であってPウエル1Pの上面には、接合深さがエクステンション領域6aよりも深く拡散層9aよりも浅い領域にホウ素(B)が導入されたハロー領域7aが形成されている。ハロー領域7aはソース・ドレイン間のリーク電流の発生を防ぐために形成される半導体領域であり、ソース・ドレイン領域とは異なる導電型の不純物を半導体基板Sbに打ち込むことで形成される。ハロー領域7aは半導体基板Sbの主面からPウエル1Pとエクステンション領域6aとの接合部の近傍に亘って形成されている。

【0026】

ゲート絶縁膜3aは酸化シリコン膜などよりも誘電率が高い高誘電率膜(high−k膜)を含む絶縁膜である。図示はしていないが、ゲート絶縁膜3aと半導体基板Sbとの間には酸化シリコン膜からなるゲート絶縁膜が介在していてもよい。

【0027】

N型MISFETQnと同様に、P型MISFETQpは、半導体基板Sbの主面にN型の不純物(たとえばAs(ヒ素))が導入されて形成されたNウエル1N上にゲート絶縁膜3bを介して形成されたゲート電極と、半導体基板Sbの主面にP型の不純物(たとえばB(ホウ素))が導入されて形成されたソース・ドレイン領域を構成するエクステンション領域6bおよび拡散層9bとを有している。エクステンション領域6bおよび拡散層9bはP型MISFETQpのソース・ドレイン領域を構成し、拡散層9a、エクステンション領域6aと同様に、P型MISFETQpのチャネル領域2bを挟むようにエクステンション領域6bが形成され、チャネル領域2bおよびエクステンション領域6bを挟むように拡散層9bが形成されている。チャネル領域2bはメタルゲート電極4bを含むゲート電極の直下に形成されている。P型MISFETQpのゲート電極はゲート絶縁膜3b上に形成されたメタルゲート電極(金属ゲート電極)4bと、メタルゲート電極4b上に形成されたポリシリコンからなるポリシリコンゲート電極5とからなる。

【0028】

また、半導体基板Sb内であってNウエル1Nの上面には、接合深さがエクステンション領域6bよりも深く拡散層9bよりも浅い領域にホウ素(B)が導入されたハロー領域7bが形成されている。ハロー領域7bはソース・ドレイン間のリーク電流の発生を防ぐために形成される半導体領域であり、ソース・ドレイン領域とは異なる導電型の不純物を半導体基板Sbに打ち込むことで形成される。ハロー領域7bは半導体基板Sbの主面からNウエル1Nとエクステンション領域6bとの接合部の近傍に亘って形成されている。

【0029】

ゲート絶縁膜3bは酸化シリコン膜などよりも誘電率が高い高誘電率膜(high−k膜)を含む絶縁膜である。図示はしていないが、ゲート絶縁膜3bと半導体基板Sbとの間には酸化シリコン膜からなるゲート絶縁膜が介在していてもよい。

【0030】

メタルゲート電極4a、4bは例えば窒化チタン、窒化タングステンまたはニッケルシリサイドからなる金属膜である。ポリシリコンゲート電極5、メタルゲート電極4aおよびゲート絶縁膜3aからなる積層パターンの側壁には、酸化シリコン膜または窒化シリコン膜もしくはそれらの積層膜により構成されたサイドウォール8が形成されている。また、ポリシリコンゲート電極5、メタルゲート電極4bおよびゲート絶縁膜3bからなる積層パターンの側壁にも、酸化シリコン膜または窒化シリコン膜もしくはそれらの積層膜により構成されたサイドウォール8が形成されている。

【0031】

ここで、金属ゲート電極であるメタルゲート電極4a、4bには炭素(C)がイオン注入法により注入されている。ただし、ポリシリコンゲート電極5、ゲート絶縁膜3a、3bおよび半導体基板Sbには炭素は注入されていない。つまり、N型MISFETQnではメタルゲート電極4aにのみ炭素が注入されており、P型MISFETQpではメタルゲート電極4bにのみ炭素が注入されている。

【0032】

次に、本実施の形態の半導体装置の効果を説明する。

【0033】

半導体装置の微細化によりチャネル領域の幅が狭まったMISFETは、比較的狭いチャネル領域内に多数の不純物を含むことになる。チャネル領域の幅、つまりソース・ドレイン領域を構成するエクステンション領域の間の距離が小さくなるほど、チャネル領域内の単位体積当たりの不純物数は増加し、チャネル領域内の不純物の分布にばらつきが生じやすくなる。狭いチャネル領域内に多数の不純物を含むMISFETでは、チャネル領域内の不純物の分布がばらつくことで、しきい値(Vth)のばらつきが増大する問題がある。半導体装置内に多数のMISFETが形成されている場合、隣接するMISFET間でも大きくしきい値(Vth)が異なる現象が起こるため、それらのMISFETを含む半導体装置を有する製品の歩留まりが低下する問題がある。

【0034】

MISFETは、性能を保持したまま消費電力を低減させるために、ゲート電極に金属材料を使用することでゲートの空乏化を抑制するとともに、ゲート絶縁膜に高誘電率を有する材料(high−k膜)を用いることで電気的な容量膜厚を変えずに物理的なゲート絶縁膜膜厚を確保することができる。さらに、ゲート電極に用いた金属材料層(メタルゲート電極)の仕事関数でしきい値を制御することができるため、チャネル領域に導入する不純物の量を低減することが可能となる。つまり、メタルゲート電極を用いてゲート電極の仕事関数を低減することによりMISFETのしきい値を低減することができるため、チャネル領域に導入する不純物の量が少なくてもMISFETを駆動することができる。ゲート電極に多結晶シリコンのみを用い、ゲート絶縁膜にシリコン酸化膜のみを用いる構造のMISFETに比べ、メタルゲート電極およびhigh−k膜を用いたMISFETではチャネル領域内の不純物数を減らすことができるので、チャネル領域内の不純物の離散に起因するばらつきを大幅に低減することが可能である。

【0035】

しかしながら、メタルゲート電極を有するMISFETであっても、メタルゲート電極を構成するグレイン(結晶)の粒径が大きいことに起因して、MISFETのしきい値がばらつく問題がある。このような問題の存在は半導体装置の微細化の大きな障壁となり、これを解決しなければ、将来的に高集積度でかつ低コストな製品を製造することが困難となる。

【0036】

上記のように、グレインの粒径が大きい場合のMISFETの断面図を、比較例として図21に示す。図21に示すN型MISFETQxは、図1に示すN型MISFETQnとほぼ同様の構造を有しているが、N型MISFETQnと異なりN型MISFETQxのメタルゲート電極4x内には炭素(C)が導入されていない。図21ではメタルゲート電極4xを構成するグレインを示しており、また、グレインの結晶の方位(配向)を各グレイン内に矢印で示している。図21に示すように、各グレインの結晶の配向は一定ではない。ここでは、メタルゲート電極4xのグレインの粒径が大きく、例えばグレインの直径または半径がメタルゲート電極4xの膜厚以上の大きさを有している場合、すなわち、メタルゲート電極4x内の一つのグレインの下面と上面とがメタルゲート電極4xの下面と上面とに露出している場合を示している。

【0037】

メタルゲート電極4xの仕事関数はグレインの配向性によって異なり、また、ゲート電極の仕事関数のばらつきはMISFETのしきい値のばらつかせる性質を有している。したがって、仕事関数はグレイン毎に異なる値となるため、複数の大きな粒径のグレインにより構成されるメタルゲート電極4xはその内部の一部と他の部分とで仕事関数が異なる状態となる。

【0038】

これに対し、本実施の形態ではメタルゲート電極4a、4bに炭素を導入しているため、図2に示すように、メタルゲート電極4a、4bのそれぞれを構成するグレインの大きさが小さくなっている。図2は図1と同一の領域を示す断面図であるが、メタルゲート電極4a、4bのそれぞれを構成するグレインの形状を示している。

【0039】

図2に示すように、本実施の形態のMISFETを構成するメタルゲート電極4a、4b内のグレインの粒径は、比較例である図21のN型MISFETQxを構成するメタルゲート電極4x内のグレインに比べて小さい。つまり、メタルゲート電極4a、4b内のグレインの平均の粒径は、比較例であるメタルゲート電極4x内のグレインの平均の粒径に比べて小さい。このため、図2および図21に示したメタルゲート電極がほぼ同一の膜厚を有している場合、図2に示すメタルゲート電極4a、4bの方が図21に示すメタルゲート電極4xよりもメタルゲート電極内のグレイン数が多くなる。このような違いは、図2のメタルゲート電極4a、4b内に炭素を導入し、熱負荷時などにグレインが大きく成長することを防いでいることにより生じるものである。なお、ここでいうグレインの粒径とは、各グレイン内の二つの端部を結ぶ直線的な距離のうち、最も大きい距離のことを指すものとする。

【0040】

図2に示す本実施の形態のMISFETであっても、メタルゲート電極4a、4bを構成する複数のグレインはそれぞれ異なった配向性を有しており、グレイン毎に仕事関数が異なる。しかし、ここではグレインの粒径を小さく抑えることによりメタルゲート電極4a内およびメタルゲート電極4b内のグレイン数を増やしているため、グレインの結晶の配向のばらつきがメタルゲート電極内において全体的に平均化される。したがって、メタルゲート電極の一部と、そのメタルゲート電極の他の部分とで仕事関数が異なることを避けることができる。また、半導体装置内に複数形成されるMISFET同士の間でゲート電極の仕事関数が大きく異なることに起因してMISFET同士の間でしきい値電圧がばらつくことを防ぐことができる。

【0041】

上記のように、本実施の形態の半導体装置では、MISFETのメタルゲート電極内に炭素を導入することで、メタルゲート電極を構成するグレインの粒径を小さくしてメタルゲート電極内のグレイン数を増やしている。これにより、グレインの配向性を平均化しているため、グレインの配向性のばらつきに起因して仕事関数がばらつくことを抑えることができる。これにより、ゲート電極の仕事関数のばらつきの発生によりMISFETのしきい値電圧がばらつくことを防ぐことができるため、半導体装置の信頼性を向上させることができる。また、MISFETのしきい値のばらつきを抑えることができるので、MISFETの微細化が容易になり、半導体装置の性能を向上させることができる。

【0042】

次に、図3〜図11を用いて、本実施の形態の半導体装置を構成するCMISFETの製造方法を説明する。

【0043】

まず、図3に示すように、主面に表面保護膜(図示しない)を形成した半導体基板Sbに、フォトリソグラフィー技術、ドライエッチング法、成膜工程、CMP(化学機械研磨:Chemical Mechanical Polishing)法を用いて、浅溝素子分離構造である素子分離領域1を形成する。ここで、半導体基板Sbの主面は、半導体基板Sbの主面に形成された複数の素子分離領域1などにより複数の領域に区切られている。すなわち、半導体基板Sbの主面にはN型MISFET形成領域1Aと、P型MISFET形成領域1Bとがある。

【0044】

次に、図4に示すように、フォトリソグラフィー技術、イオン注入法を用いて、半導体基板Sb上に形成したレジスト膜の開口部の下部のN型MISFET形成領域1Aの半導体基板Sbの主面に、接合深さが比較的深いPウエル1Pを形成する。同様にして、P型MISFET形成領域1Bの半導体基板Sbの主面に比較的深い接合深さを有するNウエル1Nを形成する。

【0045】

Pウエル1Pは、P型の不純物(例えばホウ素(B))を半導体基板Sbの主面にイオン注入して形成する。このとき、レジスト膜をマスクとすることでP型MISFET形成領域1Bの半導体基板Sbの主面にP型の不純物が注入されないようにする。Nウエル1Nは、N型の不純物(例えばヒ素(As)またはリン(P))を半導体基板Sbの主面にイオン注入して形成する。このとき、レジスト膜をマスクとすることでN型MISFET形成領域1Aの半導体基板Sbの主面にN型の不純物が注入されないようにする。このようにしてPウエル1PとNウエル1Nとの打ち分けを行うが、Pウエル1PおよびNウエル1Nはどちらを先に形成しても構わない。

【0046】

次に、図5に示すように、半導体基板Sbの表面を洗浄した後に、絶縁膜3および金属膜4を順次形成する。絶縁膜3は酸化シリコン膜よりも誘電率が高い、例えばHf(ハフニウム)を含むhigh−k膜(高誘電率膜)である。ここでは、後の工程で形成するN型MISFETおよびP型MISFETのそれぞれのしきい値を目的の値とするために、N型MISFET形成領域1AとP型MISFET形成領域1Bとで絶縁膜3の材質を異なるものとしてもよい。その場合は、例えば絶縁膜3上にN型MISFET形成領域1AとP型MISFET形成領域1Bとで異なる部材からなる膜をそれぞれ配置し、その状態で熱処理を行って絶縁膜3と絶縁膜3上の膜とを反応させる方法が考えられる。

【0047】

金属膜4は例えば窒化チタン、窒化タングステンまたはニッケルシリサイドからなり、絶縁膜3を形成した後にスパッタリング法などを用いて半導体基板Sbの全面の上部に形成する。ここでは、後のドライエッチング法によるゲート電極のパターニングを容易にするために、金属膜4の膜厚を20〜50nmで形成する。

【0048】

金属膜4を形成した後に、半導体基板Sbの主面の上方から炭素(C)をイオン注入することにより、金属膜4内に炭素(C)を導入する。ここでのイオン注入の加速エネルギーは10〜50keVとし、注入量は1014〜1016cm−2とし、投影飛程が金属膜4内に存在するように設定する。なお、投影飛程とは、注入物が固体表面から侵入した深さである。すなわち、投影飛程はイオン注入を行う対象の上面から、イオン注入を行って注入されたイオンが打ち込まれた深さ方向の距離のことを指す。つまり、金属膜4に炭素を打ち込む上記工程では、金属膜4のみに炭素を注入し、絶縁膜3および半導体基板Sbには炭素が注入されないようにする。

【0049】

次に、図6に示すように、高濃度でリン(P)が導入されたポリシリコン膜SFを金属膜4上にCVD(Chemical Vapor Deposition)法などを用いて形成する。

【0050】

次に、図7に示すように、フォトリソグラフィー技術およびドライエッチング法を用いてポリシリコン膜SF、金属膜4および絶縁膜3をパターニングすることで、N型MISFET形成領域1Aにポリシリコン膜SFからなるポリシリコンゲート電極5および金属膜4からなるメタルゲート電極4aを含むゲート電極を形成し、絶縁膜3からなるゲート絶縁膜3aを形成する。また、同一のパターニング工程により、P型MISFET形成領域1Bにポリシリコン膜SFからなるポリシリコンゲート電極5および金属膜4からなるメタルゲート電極4bを含むゲート電極を形成し、絶縁膜3からなるゲート絶縁膜3bを形成する。

【0051】

次に、図8に示すように、N型MISFET形成領域1Aを露出するレジスト膜(図示しない)を半導体基板Sb上に形成し、半導体基板Sbの主面に低い濃度でN型の不純物であるヒ素イオンを10keVのエネルギー、1×1015cm−2の注入量で打ち込むことにより、Pウエル1Pよりも接合深さが浅いN−領域であるエクステンション領域6aを形成する。続いて、前記レジスト膜をマスクとしてN型MISFET形成領域1Aの半導体基板Sbの主面にP型の不純物であるボロンイオンを10keVのエネルギー、2×1013cm−2の注入量で打ち込むことにより、エクステンション領域6aとほぼ同じ領域にハロー領域7aを形成する。ハロー領域7aはエクステンション領域6aよりも接合深さが深く、Pウエル1Pよりも接合深さが浅いP型の半導体領域である。

【0052】

同様に、P型MISFET形成領域1Bを露出するレジスト膜(図示しない)を半導体基板Sb上に形成し、半導体基板Sbの主面に低い濃度でP型の不純物であるフッ化ボロンイオンを5keVのエネルギー、1×1015cm−2の注入量で打ち込むことにより、Nウエル1Nよりも接合深さが浅いP−領域であるエクステンション領域6bを形成する。続いて、前記レジスト膜をマスクとしてP型MISFET形成領域1Bの半導体基板Sbの主面にN型の不純物であるヒ素を70keVのエネルギー、2×1013cm−2の注入量で打ち込むか、またはリンイオンを30keVのエネルギー、2×1013cm−2の注入量で打ち込むことにより、エクステンション領域6bとほぼ同じ領域にハロー領域7bを形成する。ハロー領域7bはエクステンション領域6bよりも接合深さが深く、Nウエル1Nよりも接合深さが浅いN型の半導体領域である。

【0053】

ここで、ソース・ドレイン領域であるエクステンション領域6a、6bを形成するイオン注入時、およびハロー領域7a、7bを形成するイオン注入時に、半導体基板Sbの主面に対して入射するイオンビームの角度を傾斜させることで、ゲート電極と、不純物添加層、すなわちエクステンション領域およびハロー領域とのオーバーラップの調整をすることも可能である。また、図4を用いて説明したイオン注入工程と同様に、エクステンション領域6a、6bはどちらを先に形成しても構わない。

【0054】

次に、図9に示すように、半導体基板Sbの表面を洗浄した後に、成膜とドライエッチング法を用いて、N型MISFET形成領域1A(図8参照)およびP型MISFET形成領域1B(図8参照)のゲート電極のそれぞれの側壁に絶縁膜からなるサイドウォール8を自己整合的に形成する。

【0055】

その後、N型MISFET形成領域1Aを露出するレジスト膜(図示しない)を半導体基板Sb上に形成し、半導体基板Sbの主面に高い濃度でN型の不純物であるヒ素イオンを70keVのエネルギー、1×1016cm−2の注入量で打ち込むことにより、Pウエル1Pよりも接合深さが浅く、エクステンション領域6aおよびハロー領域7aよりも接合深さが深いN+領域である拡散層9aを形成する。

【0056】

同様に、P型MISFET形成領域1Bを露出するレジスト膜(図示しない)を半導体基板Sb上に形成し、半導体基板Sbの主面に高い濃度でP型の不純物であるホウ素イオンを30keVのエネルギー、1×1015cm−2の注入量で打ち込むことにより、Nウエル1Nよりも接合深さが浅く、エクステンション領域6bおよびハロー領域7bよりも接合深さが深いP+領域である拡散層9bを形成する。拡散層9aおよび拡散層9bは、どちらを先に形成しても構わない。

【0057】

これにより、N型MISFET形成領域1A(図8参照)には、Pウエル1P上にゲート絶縁膜3aを介して形成されたメタルゲート電極4aおよびポリシリコンゲート電極5からなるゲート電極と、ソース・ドレイン領域を構成するエクステンション領域6aおよび拡散層9aとを有するN型MISFETQnが形成される。P型MISFET形成領域1B(図8参照)には、Nウエル1N上にゲート絶縁膜3bを介して形成されたメタルゲート電極4bおよびポリシリコンゲート電極5からなるゲート電極と、ソース・ドレイン領域を構成するエクステンション領域6bおよび拡散層9bとを有するP型MISFETQpが形成される。

【0058】

その後、エクステンション領域6a、6b、拡散層9aおよび9bなどの不純物拡散層を形成するために導入した不純物を活性化するための熱処理を行う。この熱処理工程では、導入した不純物の拡散を抑制するために、スパイクアニールを1050℃で窒素雰囲気中で実施する。スパイクアニール以外にも、瞬時熱アニール、あるいはフラッシュアニール、炉体を用いたアニールなどを用いることも可能である。図5を用いて説明したようにメタルゲート電極となる金属膜4に炭素(C)を注入しない場合、上記のような熱処理により半導体基板が高温になると、メタルゲート電極を構成するグレインが急速に成長するため、図21に示す比較例のようにメタルゲート電極内のグレインの粒径が大きくなる。これに対し、本実施の形態の半導体装置の製造工程ではメタルゲート電極4a、4bとなる金属膜4(図5参照)に炭素(C)を導入することにより、熱負荷時にメタルゲート電極4a、4bを構成するグレインの成長速度を遅くすることができる。このため、完成後の半導体装置内のメタルゲート電極4a、4bを構成するグレインの粒径を小さくし、より多くのグレインによりメタルゲート電極4a、4bを構成することができる。

【0059】

本発明は半導体基板Sb上に導入する不純物に係るものであるので、この後の工程の詳しい説明は省略するが、上記工程の後は、以下の工程を行うことで図10に示す半導体装置が完成する。すなわち、図9に示す構造を得た後、コンタクトプラグを形成する領域に金属シリサイド領域を形成する。つまり、半導体膜が露出している領域であるポリシリコンゲート電極5の表面および各MISFETのソース・ドレイン領域の表面に例えばニッケル(Ni)などを含むシリサイド層10を形成する。このとき、シリサイド層10を形成するために金属膜と半導体基板Sbのシリコンとを反応させることを目的として高温のアニール(熱処理)を行う。

【0060】

続いて、半導体基板Sb上シリコン窒化膜および絶縁膜を堆積することにより層間絶縁膜11を形成した後、CMP法などにより層間絶縁膜11の上面を平坦化する。その後、周知の技術を用い、層間絶縁膜11を貫通してポリシリコンゲート電極5および各トランジスタのソース・ドレイン領域に電気的に接続されるコンタクトプラグ12を形成し、層間絶縁膜11上に層間絶縁膜13を形成する。続いて、層間絶縁膜13に配線溝を形成した後、周知のシングルダマシンプロセスを用いて前記配線溝を埋め込む配線14を形成することで、図10に示す半導体装置が完成する。

【0061】

本実施の形態では、ゲート電極内にメタルゲート電極を含むMISFETを有する半導体装置の製造工程において、メタルゲート電極4a、4bのそれぞれに炭素(C)を導入することにより、メタルゲート電極4a、4bの形成後の熱処理工程などによりメタルゲート電極4a、4bを構成するグレイン(結晶)の粒径が大きくなることを防いでいる。これにより、メタルゲート電極4a、4bは炭素が導入されない場合に比べてより小さく、より多いグレインを含むことになる。上述したように、メタルゲート電極を構成するグレインの数が多ければグレインの配向性を均一化することができるため、グレインの配向性に起因した仕事関数のばらつきの発生を抑えることができる。これによりゲート電極の仕事関数のばらつきが抑えられるため、当該ゲート電極を含むMISFETのしきい値電圧(Vth)がばらつくをことを防ぐことが可能となる。

【0062】

このように、本実施の形態ではMISFETを構成するメタルゲート電極に炭素(C)をイオン注入により打ち込むことによりMISFETのしきい値のばらつきを抑えることができるため、当該MISFETを含む半導体製品の歩留まりを向上させることができる。

【0063】

また、上記のようにゲート電極の仕事関数のばらつきの発生によりMISFETのしきい値電圧がばらつくことを防ぐことができるため、半導体装置の信頼性を向上させることができる。また、MISFETのしきい値のばらつきを抑えることができるので、MISFET微細化が容易になり、半導体装置の性能を向上させることができる。

【0064】

(実施の形態2)

前記実施の形態では、後の工程でメタルゲート電極となる金属膜全てに炭素を注入する半導体装置について説明した。本実施の形態では図11〜図16を用い、本実施の形態の半導体装置であって、領域によって炭素を注入しないメタルゲート電極を有するMISFETを含む半導体装置を実現する製造プロセスの詳細を説明する。ここでは例としてSRAM(Static Random Access Memory)を構成するMISFETを形成する工程を説明する。

【0065】

まず、前記実施の形態1で図3および図4を用いて説明した工程と同様の工程を行うことにより、図11に示す構造を得る。なお、ここでは半導体基板Sb上にN型MISEFT形成領域2A、P型MISFET形成領域2B、N型MISEFT形成領域2CおよびP型MISFET形成領域2Dが存在する。つまり、図11に示すように、半導体基板Sbの主面には複数の素子分離領域1が形成されており、半導体基板Sbの主面は素子分離領域1によりN型MISEFT形成領域2A、P型MISFET形成領域2B、N型MISEFT形成領域2CおよびP型MISFET形成領域2Dに区切られている。N型MISEFT形成領域2AおよびN型MISEFT形成領域2Cの半導体基板Sbの主面にはPウエル1Pが形成されており、P型MISFET形成領域2BおよびP型MISFET形成領域2Dの半導体基板Sbの主面にはNウエル1Nが形成されている。

【0066】

ここで、N型MISEFT形成領域2Aは高電圧に対応する入出力回路を構成するN型MISFETを形成する領域であり、P型MISFET形成領域2Bは高電圧に対応する入出力回路を構成するP型MISFETを形成する領域である。また、N型MISEFT形成領域2Cは低耐圧対応のN型MISFETを形成する領域であり、P型MISFET形成領域2Dは低耐圧対応のP型MISFETを形成する領域である。

【0067】

次に、図12に示すように、high−k膜(高誘電率絶縁膜)である絶縁膜23a、23b、23cおよび23dを形成する。この際、後の工程で形成する各MISFETのしきい値を目標に合わせるために、MISFETのN型とP型とで前記high−k膜に異なる材質を用いる。また、高耐圧領域であるN型MISEFT形成領域2AおよびP型MISFET形成領域2Bの絶縁膜23a、23bは高電圧が印加されるゲート絶縁膜となるため、たとえば膜厚を7nm程度に増加させる。絶縁膜23a、23bの膜厚は入力時に対応する電圧により調整する。なお、図12では絶縁膜23a、23b、23cおよび23dのそれぞれの膜厚を同一の大きさで表わしている。続いて、半導体基板Sbの主面上に金属膜24を形成する。

【0068】

次に、図13に示すように、フォトリソグラフィー技術により、N型MISEFT形成領域2A、P型MISFET形成領域2Bをレジスト膜PR1で覆い、レジスト膜PR1から露出した低電圧MIS型トランジスタ形成領域であるN型MISEFT形成領域2C、P型MISFET形成領域2Dの金属膜24に、炭素イオンをイオン注入により添加し、金属膜24からなる金属膜24sを形成する。この際、炭素(C)のイオン注入は加速エネルギーを10〜50keVとし、注入量を1014〜1016cm−2とし、投影飛程が金属膜中に存在するように設定する。つまり、レジスト膜PR1から露出している金属膜24内にのみ炭素(C)が打ち込まれるようにし、金属膜24よりも下の構造物には炭素(C)が導入されないようにする。

【0069】

次に、図14に示すように、レジスト膜PR1を除去し、高濃度にリンが添加されたポリシリコン膜を堆積した後、フォトリソグラフィー技術およびドライエッチング法を用いてゲートのパターニングを行う。これにより、N型MISEFT形成領域2Aには、前記ポリシリコン膜からなるポリシリコンゲート電極5と、金属膜24からなるメタルゲート電極24aとを含むゲート電極が形成され、P型MISFET形成領域2Bには、前記ポリシリコン膜からなるポリシリコンゲート電極5と、金属膜24からなるメタルゲート電極24bとを含むゲート電極が形成される。また、N型MISEFT形成領域2Cには前記ポリシリコン膜からなるポリシリコンゲート電極5と、金属膜24sからなるメタルゲート電極24cとを含むゲート電極が形成され、P型MISFET形成領域2Dには前記ポリシリコン膜からなるポリシリコンゲート電極5と、金属膜24sからなるメタルゲート電極24dとを含むゲート電極が形成される。メタルゲート電極24a、24b、24cおよび24dは、半導体基板Sb上にそれぞれゲート絶縁膜25a、25b、25cおよび25dを介して形成されている。ゲート絶縁膜25a、25b、25cおよび25dはそれぞれ絶縁膜23a、23b、23cおよび23dからなるhigh−k膜である。なお、N型MISEFT形成領域2A、P型MISFET形成領域2Bのゲート電極高耐圧用MISFETに用いられるゲート電極であるので、N型MISEFT形成領域2C、P型MISFET形成領域2Dのゲート電極よりもゲート長が大きいパターンとする。

【0070】

この後の工程は前記実施の形態1で図8〜図10を用いて説明した工程と同様の工程を行うことにより、図15に示す本実施の形態の半導体装置が完成する。すなわち、レジスト膜(図示しない)を用いてN型MISEFT形成領域2A、2C、P型MISFET形成領域2Bおよび2Dのそれぞれの半導体基板Sbの主面に不純物を打ち分けることにより、エクステンション領域およびハロー領域を形成する。つまり、P型MISEFT形成領域2B、2Dにはフッ化ボロンイオンを例えばエネルギー5keV、注入量1×1015cm−2とする条件で注入してP−型のエクステンション領域26bを形成し、ヒ素イオンを例えばエネルギー70keV、注入量2×1013cm−2の条件でイオン注入するか、またはリンイオンをエネルギー30keV、注入量2×1013cm−2の条件でイオン注入してハロー領域27bを形成する。また、同様に、N型MISEFT形成領域2A、2Cにはヒ素イオンを例えばエネルギー10keV、注入量1×1015cm−2とする条件で注入してN−型のエクステンション領域26aを形成し、ホウ素イオンを例えばエネルギー10keV、注入量2×1013cm−2の条件でイオン注入してハロー領域27aを形成する。

【0071】

その後、各ゲート電極の側壁にサイドウォール8を形成した後、レジスト膜(図示しない)を用いてコンタクトのための拡散層29a、29bを形成する。ここでは、N+型の拡散層9aは、ヒ素イオンをエネルギー70keV、注入量1×1015cm−2の条件でイオン注入して形成し、P+型の拡散層9bは、ホウ素イオンをエネルギー30keV、注入量1×1015cm−2の条件でイオン注入して形成する。その後、半導体基板Sbの主面を洗浄した後に、拡散層などに導入した不純物を活性化するための熱処理を行う。これにより、N型MISFET形成領域2AおよびP型MISFET形成領域2Bには、比較的高耐圧なMISFETであるN型MISFETQa、P型MISFETQbがそれぞれ形成され、N型MISFET形成領域2CおよびP型MISFET形成領域2Dには、比較的低耐圧なMISFETであるN型MISFETQc、P型MISFETQdがそれぞれ形成される。続いて、前記実施の形態1と同様にして、シリコン表面が露出している領域にシリサイド層10を形成した後、層間絶縁膜11、コンタクトプラグ12、層間絶縁膜13および配線14を形成する。

【0072】

上記のようにして形成した本実施の形態のMISFETを含むSRAMの平面図を図16に示す。図16に示すSRAMを含む半導体装置は、主に情報を記憶する機能を有する記憶領域SRと、情報の入出力動作を行う入出力領域IOとを有しており、記憶領域SRには図15に示すN型MISEFT形成領域2C、P型MISFET形成領域2Dの低耐圧MISFETが形成され、入出力領域IOには、図15に示す高耐圧なMISFETであるN型MISEFTQaおよびP型MISFET形成領域Qbが形成されている。

【0073】

本実施の形態の半導体装置の特徴は、特にしきい値のばらつきを抑える必要がある低耐圧のMISFETのメタルゲート電極にのみ炭素(C)を注入し、周辺回路部を構成する高耐圧のMISFETのメタルゲート電極に炭素を注入しないことにある。これにより、低耐圧MISFETについては前記実施の形態1と同様の効果を得ることができる。また、高耐圧MISFETなどの炭素注入を必要としないMISFETのメタルゲート電極にまで炭素を注入することで高耐圧MISFETの配線抵抗が上昇するなどし、周辺回路部の再設計が必要となることを防ぐことができる。

【0074】

つまり、例えばゲート長、ゲート幅を最小の設計ルールで形成したMIS型トランジスタを用いるSRAMでは、メタルゲート電極に炭素を注入することにより、情報の書込み、読出しのマージンが設計基準よりも向上し、製品不良の発生率を大幅に低減することができる。また、前記炭素注入工程では、入出力領域IOなどの周辺回路部のメタルゲート電極形成領域をレジスト膜により覆って不純物(炭素)導入を抑制する。

【0075】

このとき、炭素が導入された金属膜24s(図13参照)からなるメタルゲート電極24c、24d(図15参照)を構成する複数のグレインの平均の粒径は、炭素が導入されなかった金属膜24(図13参照)からなるメタルゲート電極24a、24b(図15参照)を構成する複数のグレインの平均の粒径よりも小さくなる。つまり、周辺回路部のメタルゲート電極はメモリセル部に比べて大きなグレインを有することになるが、配線抵抗の上昇を抑制することができる。したがって、周辺回路部の再設計は不要となり、メモリセル部のみの再設計で済むため、短期間でマージン性不良率が少ないSOC製品の提供が可能となる。

【0076】

(実施の形態3)

本実施の形態では、図17〜図18を用いて本発明の実施の形態2を実現する半導体装置の製造プロセスの詳細を説明する。ここでは、前記実施の形態2とほぼ同様の製造工程を説明するが、本実施の形態と前記実施の形態2とでは異なる領域の対象のメタルゲート電極に炭素を注入する。ここでは、本実施の形態の半導体装置としてSOCを形成するものとして説明をする。

【0077】

まず、前記実施の形態2で図11、図12を用いて説明した工程と同様の工程を行う。ただし、半導体基板Sbの主面には、図17に示すようにN型MISEFT形成領域3A、P型MISFET形成領域3B、N型MISEFT形成領域3CおよびP型MISFET形成領域3Dが存在する。N型MISEFT形成領域3AおよびN型MISEFT形成領域3Cの半導体基板Sbの主面にはPウエル1Pが形成されており、P型MISFET形成領域3BおよびP型MISFET形成領域3Dの半導体基板Sbの主面にはNウエル1Nが形成されている。また、N型MISEFT形成領域3A、P型MISFET形成領域3B、N型MISEFT形成領域3CおよびP型MISFET形成領域3Dの半導体基板Sbの主面にはそれぞれhigh−k膜(高誘電率絶縁膜)である絶縁膜23a、23b、23cおよび23dが形成されている。絶縁膜23a、23b、23cおよび23d上には、金属膜24が形成されている。

【0078】

ここで、N型MISEFT形成領域3Aは高電圧N型MISFETを形成する領域であり、P型MISFET形成領域2Bは高電圧P型MISFETを形成する領域である。また、N型MISEFT形成領域2Cは低耐圧対応のN型MISFETを形成する領域であり、P型MISFET形成領域2Dは低耐圧対応のP型MISFETを形成する領域である。

【0079】

次に、図17に示すように、フォトリソグラフィー技術により、P型MISFET形成領域3B、3Dをレジスト膜PR2で覆い、レジスト膜PR2から露出したN型MISEFT形成領域3A、3Dの金属膜24に、炭素イオンをイオン注入により添加し、金属膜24からなる金属膜34sを形成する。この際、炭素(C)のイオン注入は加速エネルギーを10〜50keVとし、注入量を1014〜1016cm−2とし、投影飛程が金属膜中に存在するように設定する。つまり、金属膜24内にのみ炭素(C)が打ち込まれるようにし、金属膜24よりも下の構造物には炭素(C)が導入されないようにする。本実施の形態の半導体装置は、上記のように後の工程により形成されるN型のMISFETを構成する金属膜のみに炭素を注入していることが特徴となっている。なお、ここではN型MISFETのメタルゲート電極にのみ炭素を注入する方法について説明するが、逆にP型のMISFETのメタルゲート電極にのみ炭素を注入しても構わない。

【0080】

次に、図18に示すように、レジスト膜PR2を除去した後は、図14〜図15を用いて説明した工程を行うことにより、本実施の形態の半導体装置が完成する。つまり、金属膜24、34s上にポリシリコン膜を形成し、パターニングを行ってゲート電極を形成する。このとき、N型MISEFT形成領域3Aには絶縁膜23aからなるゲート絶縁膜25a上に金属膜34sからなるメタルゲート電極34aが形成され、P型MISFET形成領域3Bには絶縁膜23bからなるゲート絶縁膜25b上に金属膜24からなるメタルゲート電極34bが形成される。また、N型MISEFT形成領域3Cには絶縁膜23cからなるゲート絶縁膜25c上に金属膜34sからなるメタルゲート電極34cが形成され、P型MISFET形成領域3Dには絶縁膜23dからなるゲート絶縁膜25d上に金属膜24からなるメタルゲート電極34dが形成される。

【0081】

その後、各MISFET形成領域のエクステンション領域、ハロー領域、サイドウォール、拡散層、シリサイド層、層間絶縁膜、コンタクトプラグおよび配線などを形成することにより、図18に示す本実施の形態の半導体装置が完成する。

【0082】

本実施の形態の半導体装置の特徴は、炭素(C)をメタルゲート電極に導入しない場合に特にしきい値のばらつきが大きくなってしまうMISFETのメタルゲート電極のみに不純物(炭素)添加を実施し、グレインサイズの拡大を抑制することで、メタルゲートにおけるグレインの配向性による仕事関数ばらつきを押さえ、MISFETのしきい値ばらつきを小さくすることを可能としている。

【0083】

さらに、周辺回路部や炭素注入による対策が不要なメタルゲート電極には炭素注入工程においてレジスト膜などによりマスクをすることで、不純物導入を防ぐ。その結果、炭素(C)を導入しなかったメタルゲート電極を有するMISFETでは、配線抵抗の上昇を抑制することができる。したがって、周辺回路部の再設計は不要となり、短期間でマージン性不良率の少ないSOC製品の提供が可能となる。つまり、例えば図18に示すP型MISFET形成領域3D(図17参照)のゲート電極がMISFETの一部として機能するゲート電極ではなく、他のMISFETのゲート電極などに特定の電位を供給するための配線として機能する導体部である場合、MISFETとして機能しないゲート配線にまでしきい値ばらつきを防ぐ目的で炭素(C)を導入する必要はない。したがって、メタルゲート電極を含む当該ゲート配線に炭素(C)が打ち込まれることを防ぐことで、ゲート配線の配線抵抗が上昇することを防ぐことができる。

【0084】

このように、全てのメタルゲート電極に炭素(C)を導入するのではなく、そのゲート電極の特性および役割などに応じて炭素(C)を打ち分けることにより、配線抵抗の上昇を防ぐことができる。また、同様に炭素(C)の打ち分けを行うことにより、周辺回路部の再設計の手間を省くことができるため、半導体装置の製造コストの増大を防ぐことが可能となる。

【0085】

(実施の形態4)

本実施の形態の半導体装置では、前記実施の形態1の半導体装置とほぼ同様の構造を有し、MISFETのしきい値のばらつき低減を目的としてメタルゲート電極に導入する不純物を炭素以外の物質とする半導体装置について説明する。

【0086】

本実施の形態の半導体装置の製造工程では、まず前記実施の形態1において図4を用いて説明した工程を行う。

【0087】

次に、図19に示すように、図5を用いて説明した工程と同様にして半導体基板Sb上に絶縁膜3および金属膜4uを順次形成する。続いて、金属膜4uに不純物をイオン注入するが、ここで前記実施の形態1〜3と異なり、金属膜4uを構成するグレインの成長を抑えるための不純物としてハロゲン元素であるフッ素(F)、塩素(Cl)または不活性元素である窒素(N)をイオン注入する。このとき、注入するイオンにより、加速エネルギーを10〜100keVの範囲で調整し、イオン注入した元素が絶縁膜3内および半導体基板Sb内に漏れないようにすることが重要となる。また、前記不純物の添加量は、約1×1015cm−2程度とする。

【0088】

その後の工程は、前記実施の形態1で図6〜図10を用いて説明した工程と同様の工程を行うことで、図20に示す半導体装置が完成する。図20に示す半導体装置は図10に示した半導体装置とほぼ同一の構造を有しているが、メタルゲート電極に導入された不純物種が前記実施の形態1と異なる。N型MISFET形成領域1AおよびP型MISFET形成領域1Bの金属膜4u(図19参照)はパターニングされてそれぞれメタルゲート電極4p、4qとなっている。

【0089】

本実施の形態の半導体装置では、MISFETのメタルゲート電極のグレインサイズの拡大を抑制することが可能となり、その結果、メタルゲート電極におけるグレインの配向性による仕事関数ばらつきを押さえ、MISFETのしきい値ばらつきを小さくことができ、前記実施の形態1と同様の効果を得ることができる。このように、MISFETのしきい値ばらつきを抑えるためにメタルゲート電極に注入する元素は炭素(C)以外にフッ素(F)、塩素(Cl)または窒素(N)であってもよい。

【0090】

以上、本発明者らによってなされた発明をその実施の形態に基づき具体的に説明したが、本発明は前記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることはいうまでもない。

【0091】

例えば、前記実施の形態4ではメタルゲート電極にフッ素(F)、塩素(Cl)または窒素(N)を導入することで本発明の効果を得ているが、実施の形態2または実施の形態3で説明した半導体装置であってもメタルゲート電極にフッ素(F)、塩素(Cl)または窒素(N)を導入することで、実施の形態2または実施の形態3と同様の効果を得ることができる。

【産業上の利用可能性】

【0092】

本発明は、メタルゲート電極を有するMISFETを含む半導体装置の製造技術に適用して有効である。

【符号の説明】

【0093】

1 素子分離領域

1A、2A、2C、3A、3CA N型MISFET形成領域

1B、2B、2D、3B、3D P型MISFET形成領域

1N Nウエル

1P Pウエル

2a、2b チャネル領域

3 絶縁膜

3a、3b ゲート絶縁膜

4、4u 金属膜

4a、4b、4p、4q、4x メタルゲート電極

5 ポリシリコンゲート電極

6a、6b エクステンション領域

7a、7b ハロー領域

8 サイドウォール

9a、9b、29a、29b 拡散層

10 シリサイド層

11、13 層間絶縁膜

12 コンタクトプラグ

14 配線

23a〜23d 絶縁膜

24、24s、34s 金属膜

24a〜24d、34a〜34d メタルゲート電極

25a〜25d ゲート絶縁膜

26a、26b エクステンション領域

27a、27b ハロー領域

IO 入出力領域

PR1、PR2 レジスト膜

Qa、Qc、Qn、Qx N型MISFET

Qb、Qd、Qp P型MISFET

SF ポリシリコン膜

SR 記憶領域

Sb 半導体基板

【特許請求の範囲】

【請求項1】

半導体基板上に第1ゲート絶縁膜を介して形成された炭素を含む第1金属ゲート電極と、

前記第1金属ゲート電極の直下の前記半導体基板の主面に形成された第1導電型の第1チャネル領域と、

前記半導体基板の主面に前記第1チャネル領域を挟むように形成された前記第1導電型と異なる第2導電型の第1ソース・ドレイン領域と、

を有する第1電荷効果トランジスタを含むことを特徴とする半導体装置。

【請求項2】

前記第1ゲート絶縁膜は酸化シリコン膜よりも誘電率が高い高誘電率膜を含むことを特徴とする請求項1記載の半導体装置。

【請求項3】

前記半導体基板、前記第1ゲート絶縁膜、前記第1金属ゲート電極のうち、炭素が導入されているのは前記第1金属ゲート電極のみであることを特徴とする請求項1記載の半導体装置。

【請求項4】

前記第1金属ゲート電極上にはポリシリコンゲート電極が前記第1金属ゲート電極に接して形成されていることを特徴とする請求項1記載の半導体装置。

【請求項5】

前記第1金属ゲート電極は窒化チタン、窒化タングステンまたはニッケルシリサイドを含むことを特徴とする請求項1記載の半導体装置。

【請求項6】

前記半導体基板上に第2ゲート絶縁膜を介して形成された第2金属ゲート電極と、

前記第2金属ゲート電極の直下の前記半導体基板の主面に形成された第2チャネル領域と、

前記半導体基板の主面に前記第2チャネル領域を挟むように形成された第2ソース・ドレイン領域と、

を有する第2電界効果トランジスタを含み、

前記第1金属ゲート電極および前記第2金属ゲート電極のうち、炭素が導入されているのは前記第1金属ゲート電極のみであることを特徴とする請求項1記載の半導体装置。

【請求項7】

前記第1金属ゲート電極を構成する複数のグレインの平均の粒径は、前記第2金属ゲート電極を構成する複数のグレインの平均の粒径よりも小さいことを特徴とする請求項6記載の半導体装置。

【請求項8】

半導体基板上に第1ゲート絶縁膜を介して形成されたハロゲン元素を含む第1金属ゲート電極と、

前記第1金属ゲート電極の直下の前記半導体基板の主面に形成された第1導電型の第1チャネル領域と、

前記半導体基板の主面に前記第1チャネル領域を挟むように形成された前記第1導電型と異なる第2導電型の第1ソース・ドレイン領域と、

を有する第1電荷効果トランジスタを含むことを特徴とする半導体装置。

【請求項9】

前記ハロゲン元素はフッ素または塩素であることを特徴とする請求項8記載の半導体装置。

【請求項10】

半導体基板上に第1ゲート絶縁膜を介して形成された不活性元素を含む第1金属ゲート電極と、

前記第1金属ゲート電極の直下の前記半導体基板の主面に形成された第1導電型の第1チャネル領域と、

前記半導体基板の主面に前記第1チャネル領域を挟むように形成された前記第1導電型と異なる第2導電型の第1ソース・ドレイン領域と、

を有する第1電荷効果トランジスタを含むことを特徴とする半導体装置。

【請求項11】

前記不活性元素は窒素であることを特徴とする請求項10記載の半導体装置。

【請求項12】

半導体基板上の第1領域に形成された金属ゲート電極、第1導電型を有するチャネル領域および前記第1導電型と異なる第2導電型を有するソース・ドレイン領域を有する電界効果トランジスタを含む半導体装置の製造方法であって、

(a)前記半導体基板の主面の前記第1領域に前記第1導電型を有する不純物を注入して前記チャネル領域を形成する工程と、

(b)前記半導体基板上に絶縁膜および金属膜を順次積層する工程と、

(c)前記金属膜に炭素を導入する工程と、

(d)前記(c)工程後、前記金属膜を加工して前記金属ゲート電極を形成する工程と、

(e)前記半導体基板の主面に前記第2導電型の不純物を注入して前記チャネル領域を挟むように前記ソース・ドレイン領域を形成する工程と、

を有することを特徴とする半導体装置の製造方法。

【請求項13】

前記(c)工程では、イオン注入法を用いて前記金属膜に炭素を注入することを特徴とする請求項12記載の半導体装置の製造方法。

【請求項14】

前記(c)工程では、前記金属膜のみに炭素を導入することを特徴とする請求項12記載の半導体装置の製造方法。

【請求項15】

(c1)前記(c)工程前に、前記第1領域と異なる第2領域の前記金属膜の上面をマスクにより覆う工程をさらに有し、

前記(c)工程では前記マスク上から炭素を前記金属膜に打ち込むことにより、前記マスクから露出する前記金属膜の一部のみに炭素を注入することを特徴とする請求項12記載の半導体装置の製造方法。

【請求項16】

前記(c)工程で炭素を注入した前記第1領域の前記金属膜からなる前記金属ゲート電極を構成するグレインの平均の粒径は、炭素が注入されなかった前記第2領域の前記金属膜を構成するグレインの平均の粒径よりも小さいことを特徴とする請求項15記載の半導体装置の製造方法。

【請求項17】

半導体基板上の第1領域に形成された金属ゲート電極、第1導電型を有するチャネル領域および前記第1導電型と異なる第2導電型を有するソース・ドレイン領域を有する電界効果トランジスタを含む半導体装置の製造方法であって、

(a)前記半導体基板の主面の前記第1領域に前記第1導電型を有する不純物を注入して前記チャネル領域を形成する工程と、

(b)前記半導体基板上に絶縁膜および金属膜を順次積層する工程と、

(c)前記金属膜にハロゲン元素を導入する工程と、

(d)前記(c)工程後、前記金属膜を加工して前記金属ゲート電極を形成する工程と、

(e)前記半導体基板の主面に前記第2導電型の不純物を注入して前記チャネル領域を挟むように前記ソース・ドレイン領域を形成する工程と、

を有することを特徴とする半導体装置の製造方法。

【請求項18】

前記ハロゲン元素はフッ素または塩素であり、

前記(c)工程では、イオン注入法を用いて前記金属膜に前記ハロゲン元素を注入することを特徴とする請求項17記載の半導体装置の製造方法。

【請求項19】

半導体基板上の第1領域に形成された金属ゲート電極、第1導電型を有するチャネル領域および前記第1導電型と異なる第2導電型を有するソース・ドレイン領域を有する電界効果トランジスタを含む半導体装置の製造方法であって、

(a)前記半導体基板の主面の前記第1領域に前記第1導電型を有する不純物を注入して前記チャネル領域を形成する工程と、

(b)前記半導体基板上に絶縁膜および金属膜を順次積層する工程と、

(c)前記金属膜に不活性元素を導入する工程と、

(d)前記(c)工程後、前記金属膜を加工して前記金属ゲート電極を形成する工程と、

(e)前記半導体基板の主面に前記第2導電型の不純物を注入して前記チャネル領域を挟むように前記ソース・ドレイン領域を形成する工程と、

を有することを特徴とする半導体装置の製造方法。

【請求項20】

前記不活性元素は窒素であり、

前記(c)工程では、イオン注入法を用いて前記金属膜に前記不活性元素を注入することを特徴とする請求項19記載の半導体装置の製造方法。

【請求項1】

半導体基板上に第1ゲート絶縁膜を介して形成された炭素を含む第1金属ゲート電極と、

前記第1金属ゲート電極の直下の前記半導体基板の主面に形成された第1導電型の第1チャネル領域と、

前記半導体基板の主面に前記第1チャネル領域を挟むように形成された前記第1導電型と異なる第2導電型の第1ソース・ドレイン領域と、

を有する第1電荷効果トランジスタを含むことを特徴とする半導体装置。

【請求項2】

前記第1ゲート絶縁膜は酸化シリコン膜よりも誘電率が高い高誘電率膜を含むことを特徴とする請求項1記載の半導体装置。

【請求項3】

前記半導体基板、前記第1ゲート絶縁膜、前記第1金属ゲート電極のうち、炭素が導入されているのは前記第1金属ゲート電極のみであることを特徴とする請求項1記載の半導体装置。

【請求項4】

前記第1金属ゲート電極上にはポリシリコンゲート電極が前記第1金属ゲート電極に接して形成されていることを特徴とする請求項1記載の半導体装置。

【請求項5】

前記第1金属ゲート電極は窒化チタン、窒化タングステンまたはニッケルシリサイドを含むことを特徴とする請求項1記載の半導体装置。

【請求項6】

前記半導体基板上に第2ゲート絶縁膜を介して形成された第2金属ゲート電極と、

前記第2金属ゲート電極の直下の前記半導体基板の主面に形成された第2チャネル領域と、

前記半導体基板の主面に前記第2チャネル領域を挟むように形成された第2ソース・ドレイン領域と、

を有する第2電界効果トランジスタを含み、

前記第1金属ゲート電極および前記第2金属ゲート電極のうち、炭素が導入されているのは前記第1金属ゲート電極のみであることを特徴とする請求項1記載の半導体装置。

【請求項7】

前記第1金属ゲート電極を構成する複数のグレインの平均の粒径は、前記第2金属ゲート電極を構成する複数のグレインの平均の粒径よりも小さいことを特徴とする請求項6記載の半導体装置。

【請求項8】

半導体基板上に第1ゲート絶縁膜を介して形成されたハロゲン元素を含む第1金属ゲート電極と、

前記第1金属ゲート電極の直下の前記半導体基板の主面に形成された第1導電型の第1チャネル領域と、

前記半導体基板の主面に前記第1チャネル領域を挟むように形成された前記第1導電型と異なる第2導電型の第1ソース・ドレイン領域と、

を有する第1電荷効果トランジスタを含むことを特徴とする半導体装置。

【請求項9】

前記ハロゲン元素はフッ素または塩素であることを特徴とする請求項8記載の半導体装置。

【請求項10】

半導体基板上に第1ゲート絶縁膜を介して形成された不活性元素を含む第1金属ゲート電極と、

前記第1金属ゲート電極の直下の前記半導体基板の主面に形成された第1導電型の第1チャネル領域と、

前記半導体基板の主面に前記第1チャネル領域を挟むように形成された前記第1導電型と異なる第2導電型の第1ソース・ドレイン領域と、

を有する第1電荷効果トランジスタを含むことを特徴とする半導体装置。

【請求項11】

前記不活性元素は窒素であることを特徴とする請求項10記載の半導体装置。

【請求項12】

半導体基板上の第1領域に形成された金属ゲート電極、第1導電型を有するチャネル領域および前記第1導電型と異なる第2導電型を有するソース・ドレイン領域を有する電界効果トランジスタを含む半導体装置の製造方法であって、

(a)前記半導体基板の主面の前記第1領域に前記第1導電型を有する不純物を注入して前記チャネル領域を形成する工程と、

(b)前記半導体基板上に絶縁膜および金属膜を順次積層する工程と、

(c)前記金属膜に炭素を導入する工程と、

(d)前記(c)工程後、前記金属膜を加工して前記金属ゲート電極を形成する工程と、

(e)前記半導体基板の主面に前記第2導電型の不純物を注入して前記チャネル領域を挟むように前記ソース・ドレイン領域を形成する工程と、

を有することを特徴とする半導体装置の製造方法。

【請求項13】

前記(c)工程では、イオン注入法を用いて前記金属膜に炭素を注入することを特徴とする請求項12記載の半導体装置の製造方法。

【請求項14】

前記(c)工程では、前記金属膜のみに炭素を導入することを特徴とする請求項12記載の半導体装置の製造方法。

【請求項15】

(c1)前記(c)工程前に、前記第1領域と異なる第2領域の前記金属膜の上面をマスクにより覆う工程をさらに有し、

前記(c)工程では前記マスク上から炭素を前記金属膜に打ち込むことにより、前記マスクから露出する前記金属膜の一部のみに炭素を注入することを特徴とする請求項12記載の半導体装置の製造方法。

【請求項16】

前記(c)工程で炭素を注入した前記第1領域の前記金属膜からなる前記金属ゲート電極を構成するグレインの平均の粒径は、炭素が注入されなかった前記第2領域の前記金属膜を構成するグレインの平均の粒径よりも小さいことを特徴とする請求項15記載の半導体装置の製造方法。

【請求項17】

半導体基板上の第1領域に形成された金属ゲート電極、第1導電型を有するチャネル領域および前記第1導電型と異なる第2導電型を有するソース・ドレイン領域を有する電界効果トランジスタを含む半導体装置の製造方法であって、

(a)前記半導体基板の主面の前記第1領域に前記第1導電型を有する不純物を注入して前記チャネル領域を形成する工程と、

(b)前記半導体基板上に絶縁膜および金属膜を順次積層する工程と、

(c)前記金属膜にハロゲン元素を導入する工程と、

(d)前記(c)工程後、前記金属膜を加工して前記金属ゲート電極を形成する工程と、

(e)前記半導体基板の主面に前記第2導電型の不純物を注入して前記チャネル領域を挟むように前記ソース・ドレイン領域を形成する工程と、

を有することを特徴とする半導体装置の製造方法。

【請求項18】

前記ハロゲン元素はフッ素または塩素であり、

前記(c)工程では、イオン注入法を用いて前記金属膜に前記ハロゲン元素を注入することを特徴とする請求項17記載の半導体装置の製造方法。

【請求項19】

半導体基板上の第1領域に形成された金属ゲート電極、第1導電型を有するチャネル領域および前記第1導電型と異なる第2導電型を有するソース・ドレイン領域を有する電界効果トランジスタを含む半導体装置の製造方法であって、

(a)前記半導体基板の主面の前記第1領域に前記第1導電型を有する不純物を注入して前記チャネル領域を形成する工程と、

(b)前記半導体基板上に絶縁膜および金属膜を順次積層する工程と、

(c)前記金属膜に不活性元素を導入する工程と、

(d)前記(c)工程後、前記金属膜を加工して前記金属ゲート電極を形成する工程と、

(e)前記半導体基板の主面に前記第2導電型の不純物を注入して前記チャネル領域を挟むように前記ソース・ドレイン領域を形成する工程と、

を有することを特徴とする半導体装置の製造方法。

【請求項20】

前記不活性元素は窒素であり、

前記(c)工程では、イオン注入法を用いて前記金属膜に前記不活性元素を注入することを特徴とする請求項19記載の半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【公開番号】特開2013−21141(P2013−21141A)

【公開日】平成25年1月31日(2013.1.31)

【国際特許分類】

【出願番号】特願2011−153483(P2011−153483)

【出願日】平成23年7月12日(2011.7.12)

【国等の委託研究の成果に係る記載事項】(出願人による申告)平成20年度 独立行政法人新エネルギー・産業技術総合開発機構 「次世代半導体材料・プロセス基盤(MIRAI)プロジェクト」委託研究、産業技術力強化法第19条の適用を受ける特許出願

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

【公開日】平成25年1月31日(2013.1.31)

【国際特許分類】

【出願日】平成23年7月12日(2011.7.12)

【国等の委託研究の成果に係る記載事項】(出願人による申告)平成20年度 独立行政法人新エネルギー・産業技術総合開発機構 「次世代半導体材料・プロセス基盤(MIRAI)プロジェクト」委託研究、産業技術力強化法第19条の適用を受ける特許出願

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

[ Back to top ]