半導体装置およびその製造方法

【課題】第1の領域のゲート絶縁膜への酸化剤の進入を防止しつつ、第2の領域の複数の第1の配線間に設けられた酸化アルミニウム膜を選択的に除去する。

【解決手段】第1の領域において第1の積層体の側壁を覆い、第2の領域において複数の第1の配線を覆うように形成した第1の絶縁膜をマスクとして、第1の領域に第1のイオン注入を施す。その後、第1の領域において第1の積層体の側壁を覆い、第2の領域において複数の第1の配線間を埋設するように形成した、酸化アルミニウムを主体とする第2の絶縁膜をマスクとして、第1の領域に第2のイオン注入を施す。第2の絶縁膜を、第1の絶縁膜に対して選択的に除去する。

【解決手段】第1の領域において第1の積層体の側壁を覆い、第2の領域において複数の第1の配線を覆うように形成した第1の絶縁膜をマスクとして、第1の領域に第1のイオン注入を施す。その後、第1の領域において第1の積層体の側壁を覆い、第2の領域において複数の第1の配線間を埋設するように形成した、酸化アルミニウムを主体とする第2の絶縁膜をマスクとして、第1の領域に第2のイオン注入を施す。第2の絶縁膜を、第1の絶縁膜に対して選択的に除去する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置およびその製造方法に関する。

【背景技術】

【0002】

特許文献1(特開2000−216373号公報)には、半導体基板上へのMOSトランジスタの形成方法が記載されている。ここでは、基板上にゲート絶縁膜を介して配置されたゲート電極を形成する。この後、ゲート電極の側壁上にオフセットスペーサを形成し、ゲート電極およびオフセットスペーサをマスクとして基板にイオン注入を施すことにより、LDD領域を形成する。オフセットスペーサを用いることで、イオン注入により導入された不純物がゲート電極下の基板に熱拡散しにくくなり、ゲート−ドレイン間容量を低減できる。更に、オフセットスペーサの外部側壁上にサイドウォールスペーサを形成し、ゲート電極およびサイドウォールスペーサをマスクとして基板にイオン注入を施すことで、ソース及びドレインを形成する。ここで、特許文献1では、オフセットスペーサおよびサイドウォールスペーサを形成する材料として、酸化シリコンまたは窒化シリコンからなる絶縁膜が挙げられている。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2000−216373号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

本発明者がこの技術について検討したところ、以下のような課題を有することが明らかとなった。酸化シリコン膜やそれよりも高い誘電率を持つ高誘電率膜(high−k膜)からなるゲート絶縁膜は、MISトランジスタの電気特性に関わる構成要素の一つである。特に、ゲート絶縁膜の膜厚(等価酸化膜厚(Equivalent Oxide Thickness:EOT)で表される)は、閾値電圧や電流値に影響するため、EOTの制御が重要となる。

【0005】

従来、MISトランジスタの形成工程では、特許文献1の図3に示されるように、オフセットスペーサやサイドウォールスペーサ(第2スペーサ)を構成する材料として、酸化シリコンや窒化シリコンからなる絶縁膜が適用されていた。このような技術について本発明者が検討したところ、以下の課題を有することが分かった。

【0006】

例えば、オフセットスペーサやサイドウォールスペーサとして酸化シリコンを適用した場合、ソース及びドレイン用の不純物活性化のためのアニール時などに、これらのスペーサや層間絶縁膜の酸化シリコンに由来する酸化剤がゲート絶縁膜に侵入し、ゲート絶縁膜のEOTを増加させることが分かった。このような酸化剤の進入によるゲート絶縁膜のEOTの増加は、酸化シリコンよりも誘電率の高い高誘電率膜(high−k膜)をゲート絶縁膜として用いた場合に、より顕著となっていた。また、酸化剤作用によりゲート絶縁膜中に負の固定チャージが誘起され、閾値電圧のシフトが起こることが分かった。

【0007】

また、オフセットスペーサとして窒化シリコン膜を適用した場合であっても、サイドウォールスペーサなどと比較して薄いオフセットスペーサでは酸化剤の進入に対するバリア性は不十分であった。一方、厚い窒化シリコン膜からなるオフセットスペーサを用いることは、ゲート電極下のチャネル領域とLDD領域との離間による抵抗の増加が懸念されるため、好ましくない。

【0008】

そこで、本発明者は、周辺回路領域のトランジスタ用のオフセットスペーサおよびサイドウォールスペーサの両スペーサを窒化シリコン膜とする構造を更に検討した。このように、オフセットスペーサに加え、比較的厚いサイドウォールスペーサを窒化シリコン膜とすることで、酸化剤の進入によるEOTの増加の抑制が期待できる。

【0009】

しかしながら、本発明者の更なる検討によれば、以下のような課題を有することが分かった。例えば、埋め込みワード線構造のDRAMメモリセルにおいて、周辺回路領域のゲート電極と同時にパターニングされるビット線の間隔は、周辺回路領域のゲート電極の間隔よりも狭くなる。また、一般的に半導体集積回路の高集積化に伴って半導体素子は微細化され、複数併設されるゲート電極の間隔は狭くなる。このように狭いビット線やゲート電極間は、スペーサ膜やエッチングストッパ膜で埋設される場合がある。換言すれば、ビット線間やゲート電極間が窒化シリコン膜のみで埋設されることになる。これにより、当該ビット線間やゲート電極間に、自己整合的手法によるコンタクト(Self Align Contact:SAC)を形成することが困難となる。そこで、ビット線間のサイドウォールスペーサを選択的に除去することが考えられる。しかし、上述のようにオフセットスペーサとサイドウォールスペーサが同一の窒化シリコン膜で形成されている場合、サイドウォールスペーサのみを選択的に除去できなくなる。

【課題を解決するための手段】

【0010】

一実施形態は、

基板の第1の領域の主面に、ゲート絶縁膜を形成する工程と、

前記ゲート絶縁膜を覆うゲート電極を形成する工程と、

前記基板の第1の領域では前記ゲート電極を覆い、前記第1の領域と異なる第2の領域では前記基板の主面を覆うように、前記基板に第1の導体膜を形成する工程と、

前記第1の導体膜、前記ゲート電極および前記ゲート絶縁膜を加工して、前記第1の領域には前記第1の導体膜、前記ゲート電極および前記ゲート絶縁膜からなる第1の積層体を形成し、前記第2の領域には前記第1の導体膜からなる複数の第1の配線を形成する工程と、

前記第1の積層体の側壁を覆い、かつ、前記複数の第1の配線を覆うように、第1の絶縁膜を形成する工程と、

前記第1の絶縁膜をマスクとして、前記基板の第1の領域の主面に第1のイオン注入を施す工程と、

前記第1の積層体の側壁を覆い、かつ、前記複数の第1の配線間を埋設するように、前記第1の絶縁膜とは異なる絶縁膜であって、酸化アルミニウムを主体とする第2の絶縁膜を形成する工程と、

前記第2の絶縁膜をマスクとして、前記基板の第1の領域の主面に第2のイオン注入を施す工程と、

前記第1の絶縁膜に対して選択的に、前記第2の絶縁膜を除去する工程と、

を有することを特徴とする半導体装置の製造方法に関する。

【0011】

他の実施形態は、

基板と、

前記基板の第1の領域の主面上に順に形成されたゲート絶縁膜、ゲート電極、および第1の導体膜からなる第1の積層体と、

前記第1の積層体の側壁を覆う第1の絶縁膜と、

前記第1の積層体の側壁を覆い、かつ、前記第1の絶縁膜とは異なる絶縁膜であって、酸化アルミニウムを主体とする第2の絶縁膜と、

前記第1の積層体の両側の側方下部の基板内に設けられたLDD領域およびソース/ドレイン領域と、

前記基板の第2の領域の主面上に形成された、第1の導体膜からなる複数の第1の配線と、

を有することを特徴とする半導体装置に関する。

【0012】

なお、本明細書及び特許請求の範囲では、完成前のメモリセル領域を形成する予定の領域を「メモリセル形成領域」、完成前の周辺回路領域を形成する予定の領域を「周辺回路形成領域」とする。これらの領域は、完成前で製造途中の領域である点でそれぞれ、「メモリセル領域」及び「周辺回路領域」と区別される。以下では、メモリセル形成領域を「第2の領域」、周辺回路形成領域を第1の領域と呼ぶ場合がある。

【発明の効果】

【0013】

第1の領域において、ゲート絶縁膜を含む第1の積層体を覆うサイドウォールスペーサ(第2の絶縁膜)として酸化アルミニウムを主体とする絶縁膜を適用することにより、ゲート絶縁膜への酸化剤の進入を低減することができる。また、この第2の絶縁膜として第1の絶縁膜と異なる絶縁膜を適用することにより、第2の領域において、複数の第1の配線間に設けられた第2の絶縁膜を第1の絶縁膜に対して選択的に除去することができる。

【図面の簡単な説明】

【0014】

【図1】第1実施例の半導体装置の製造方法の一工程を表す図である。

【図2】第1実施例の半導体装置の製造方法の一工程を表す図である。

【図3】第1実施例の半導体装置の製造方法の一工程を表す図である。

【図4】第1実施例の半導体装置の製造方法の一工程を表す図である。

【図5】第1実施例の半導体装置の製造方法の一工程を表す図である。

【図6】第1実施例の半導体装置の製造方法の一工程を表す図である。

【図7】第1実施例の半導体装置の製造方法の一工程を表す図である。

【図8】第1実施例の半導体装置の製造方法の一工程を表す図である。

【図9】第1実施例の半導体装置の製造方法の一工程を表す図である。

【図10】第1実施例の半導体装置の製造方法の一工程を表す図である。

【図11】第1実施例の半導体装置の製造方法の一工程を表す図である。

【図12】第1実施例の半導体装置の製造方法の一工程を表す図である。

【図13】第1実施例の半導体装置を表す図である。

【図14】第2実施例の半導体装置の製造方法の一工程を表す図である。

【図15】第2実施例の半導体装置の製造方法の一工程を表す図である。

【図16】第2実施例の半導体装置の製造方法の一工程を表す図である。

【図17】第2実施例の半導体装置を表す図である。

【図18】第1実施例の変形例の製造方法の一工程を表す図である。

【発明を実施するための形態】

【0015】

(第1実施例)

本実施例は、本発明の構造を周辺回路領域の第1の電界効果トランジスタ及びメモリセル領域のビット線(第1の配線)に適用した、DRAM(Dynamic Random Access Memory)を有する半導体装置の製造方法に関するものである。本実施例では、メモリセル形成領域(第2の領域)のビット線と、周辺回路形成領域(第1の領域)の第1の電界効果トランジスタのゲート電極を、同一の工程でパターニングして形成する。

【0016】

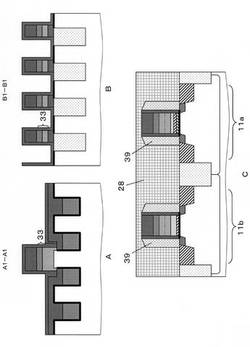

以下、図面を参照して、本実施例の半導体装置の製造方法を説明する。図1はメモリセル形成領域を表す平面図を表す。また、図2Aは図1のA1−A1方向の断面図、図2Bは図1のB1−B1方向の断面図、図2Cは周辺回路形成領域の断面図を表す。以下、平面図と断面図との関係は特記しない限り同様である。なお、構成要素を分かり易くするために、上層を覆う絶縁膜などを適宜省略して示すこととする。

【0017】

まず、図1及び2に示すように、STI法により、半導体基板のメモリセル形成領域(第2の領域)及び周辺回路形成領域(第1の領域)内に、素子分離領域10を形成する。これにより、半導体基板内では、素子分離領域10で区画された領域が活性領域11となる。次に、公知の方法により、周辺回路領域のnチャネル型のトランジスタを形成する領域11bにPウェル14を形成し、pチャネル型のトランジスタを形成する領域11aにNウェル15を形成する。

【0018】

続いて、公知の方法により、メモリセル形成領域内に、素子分離領域10と交差する方向に延在する溝状のトレンチ16を形成する。そして、トレンチ16の内壁をISSG(in−situ steam generation)法により酸化して、酸化シリコン膜からなるゲート絶縁膜17を形成する。次に、トレンチ16内を導体膜で埋め込むことで、溝型のゲート電極19を形成する。そして、半導体基板上の主面に、窒化シリコン膜からなるビットコンタクト層間絶縁膜22を形成する。ウェットエッチングにより、周辺回路形成領域上の窒化シリコン膜22、及びパッド酸化膜12を除去する。

【0019】

次に、図3に示すように、周辺回路形成領域の主面上に酸化シリコン膜23を形成する。Pウェル14上に半導体基板側から順に、HfO2(酸化ハフニウム)膜24、窒化チタン膜(金属膜)25、及び多結晶シリコン膜(導電膜)26を形成する。酸化シリコン膜23及びHfO2膜24はゲート絶縁膜を構成し、窒化チタン膜25及び多結晶シリコン膜(多結晶シリコン膜)26はゲート電極を構成する。また、Nウェル15上に半導体基板側から順に、HfO2膜24、Al2O3(酸化アルミニウム)膜27、窒化チタン膜(金属膜)25及び多結晶シリコン膜(導電膜)26を形成する。酸化シリコン膜23、HfO2膜24及びAl2O3膜27は、ゲート絶縁膜を構成し、窒化チタン膜25及び多結晶シリコン膜26はゲート電極を構成する。酸化ハフニウムや酸化アルミニウムを含む絶縁膜は、二酸化シリコンを主体とする絶縁膜よりも誘電率が高く、高誘電率絶縁膜やHigh−K絶縁膜と呼ばれる。本第1実施例の半導体装置では、周辺回路領域にこのような高誘電率絶縁膜をゲート絶縁膜に適用した第1の電界効果トランジスタを形成する。

【0020】

なお、高誘電率ゲート絶縁膜は上記の材料に限定されず、例えば、ケイ酸化ハフニウム(HfSiO)や、酸化ランタン(La2O3)などもある。酸化剤の影響を受けてEOTが増加し得るゲート絶縁膜であれば、本願を適用して同様に効果的である。また、高誘電率ゲート絶縁膜と相性の良いゲート電極として、金属材料を適用することがあり、上記の窒化チタン膜もその一種である。金属ゲート電極はこれに限定されず、例えば、窒化タンタル(TaN)膜などもある。

【0021】

次に、図4に示すように、フォトリソグラフィ法およびドライエッチング法などによって、ビットコンタクト層間絶縁膜22の一部を除去することで、ビットコンタクト開口部から活性領域11の一部を露出させる。その上で、半導体基板上の全面に多結晶シリコン膜(導電膜)29、窒化タングステン膜(導電膜)及びタングステン膜(導電膜)30(図4中には窒化タングステン膜とタングステン膜の境界を示さない)、並びに窒化シリコン膜31を形成する。この多結晶シリコン膜29、窒化タングステン膜及びタングステン膜30が第1の導体膜を構成する。この工程により、周辺回路形成領域ではゲート電極を覆い、メモリセル形成領域ではビットコンタクト開口部において基板を覆うように、第1の導体膜を形成する。

【0022】

次に、図5及び6に示すように、フォトリソグラフィ法およびエッチング法などにより、第1の窒化シリコン膜31、窒化タングステン膜及びタングステン膜30、多結晶シリコン膜29,26、および、ゲート絶縁膜24,27を加工する。この加工により、メモリセル形成領域上では、多結晶シリコン膜29、窒化タングステン膜及びタングステン膜30(以上、第1の導体膜)からなるビット線33(第1の配線)が形成される。また、この加工により、周辺回路形成領域のPウェル14上では、高誘電率ゲート絶縁膜、窒化チタン膜25、多結晶シリコン膜26及び29、並びに窒化タングステン膜及びタングステン膜30からなるゲート構造(第1の積層体)が形成される。Pウェル14上では、酸化シリコン膜23、及びパターニングされた高誘電率絶縁膜(HfO2膜24)は、ゲート絶縁膜を構成する。また、この加工により、周辺回路形成領域のNウェル15上では、高誘電率ゲート絶縁膜、窒化チタン膜25、多結晶シリコン膜26及び29、並びに窒化タングステン膜及びタングステン膜30からなるゲート構造(第1の積層体)が形成される。Nウェル15上では、酸化シリコン膜23、及びパターニングされた高誘電率絶縁膜(HfO2膜24及びAl2O3膜27)は、ゲート絶縁膜を構成する。

【0023】

次に、図7に示すように、半導体基板上の全面に、ALD(Atomic Layer Deposition)法により、窒化シリコン膜36(第1の絶縁膜)を形成する。半導体基板上の全面にフォトレジスト28を形成した後、周辺回路形成領域上のフォトレジスト28を除去して、フォトレジストパターンを形成する。周辺回路形成領域上の窒化シリコン膜36をエッチバックして、ゲート絶縁膜、ゲート電極及びハードマスクの側壁を覆うように、オフセットスペーサ(第1の絶縁膜)36aとして窒化シリコン膜を残留させる。フォトレジスト28で覆われたメモリセル形成領域は当該エッチングには曝されず、窒化シリコン膜36は複数のビット線33を覆うように形成される。

【0024】

フォトレジストパターン28を除去した後、メモリセル形成領域及び周辺回路形成領域のNウェル15上に、第1のマスク(図示していない)を設ける。ハードマスク13、オフセットスペーサ36a及び第1のマスクを用いて、周辺回路形成領域のPウェル14内にn型導電型の不純物をイオン注入して、第1の積層体の側方下部にLDD領域37aを形成する(第1のイオン注入)。第1のマスクを除去した後、メモリセル形成領域及び周辺回路形成領域のPウェル14上に、第2のマスク(図示していない)を設ける。ハードマスク13、オフセットスペーサ36a及び第2のマスクを用いて、周辺回路形成領域のNウェル15内にp型導電型の不純物をイオン注入して、第1の積層体の側方下部にLDD領域37bを形成する(第1のイオン注入)。この後、第2のマスクを除去する。

【0025】

次に、図8に示すように、半導体基板上の全面に、酸化アルミニウム膜38(第2の絶縁膜)を形成する。半導体基板上の全面にフォトレジスト28を形成した後、周辺回路形成領域上のフォトレジスト28を除去して、フォトレジストパターンを形成する。周辺回路形成領域上の酸化アルミニウム膜38をエッチバックして、オフセットスペーサ(第1の絶縁膜)36a上であるゲート電極及びハードマスクの側壁を覆うように、サイドウォールスペーサ(第2の絶縁膜)39として酸化アルミニウム膜を残留させる。フォトレジスト28で覆われたメモリセル形成領域は当該エッチングには曝されず、酸化アルミニウム膜38は複数のビット線33の間を埋設するように形成される。

【0026】

フォトレジストパターン28を除去した後、メモリセル形成領域及び周辺回路形成領域のNウェル15上に、第3のマスク(図示していない)を設ける。ハードマスク13、オフセットスペーサ39、サイドウォールスペーサ36a、及び第3のマスクを用いて、周辺回路形成領域のPウェル14内に、第1のイオン注入よりも高濃度のn型導電型の不純物のイオン注入を行う(第2のイオン注入)。これにより、第1の積層体の側方下部にソース及びドレイン40aを形成する。第3のマスクを除去した後、メモリセル形成領域及び周辺回路形成領域のPウェル14上に、第4のマスク(図示していない)を設ける。ハードマスク13、オフセットスペーサ36a、サイドウォールスペーサ39、及び第4のマスクを用いて、周辺回路形成領域のNウェル15内に、第1のイオン注入よりも高濃度のp型導電型の不純物のイオン注入を行う(第2のイオン注入)。これにより、第1の積層体の側方下部にソース及びドレイン40bを形成する。この後、第4のマスクを除去する。

【0027】

続いて、図9に示すように、半導体基板上の全面にフォトレジスト28を形成した後、メモリセル形成領域上のフォトレジストを除去して、フォトレジストパターンを形成する。このフォトレジストパターンをマスクに用いたウェットエッチングにより、メモリセル形成領域上の酸化アルミニウム膜38を除去する。ここでは、酸化アルミニウム膜38と窒化シリコン膜36とが異なる絶縁膜であるため、メモリセル形成領域のビット線33間に埋設された酸化アルミニウム膜38を、ビット線33を覆う窒化シリコン膜36に対して選択的に除去できる。この観点から、メモリセル形成領域においてビット線33を覆うように形成する第1の絶縁膜の材料は、酸化アルミニウムと異なり(第2の絶縁膜を選択的に除去するため)、かつ、酸化剤として寄与しない絶縁膜であれば良く、窒化シリコンに限定されない。その後、フォトレジストパターンを除去する。

【0028】

次に、図10に示すように、半導体基板上の全面に、CVD法により、ライナー膜として窒化シリコン膜41を形成する。この際、メモリセル形成領域上の酸化アルミニウム膜38は除去されているため、ビット線間を完全に埋設させることなく、窒化シリコン膜41を形成することができる。この結果、後述する図11の工程で、窒化シリコン膜41を、容量コンタクトホール開口時のエッチングストッパとして用いることができる。次に、SOD(Spin On Dielectric;層間絶縁膜)膜42を形成した後、熱処理を行う。ライナー膜41をストッパとして、SOD膜42に対してCMP法を行うことにより、SOD膜42を平坦化させる。

【0029】

図11に示すように、フォトリソグラフィ法およびエッチング法などにより、SOD膜42からなる層間絶縁膜に、容量コンタクトホール43(接続孔)およびコンタクトホール45を形成する。具体的には、メモリセル形成領域では、SOD膜42からなる層間絶縁膜に、その表面から、ビット線33間に位置する活性領域11(ソースまたはドレイン領域である基板の主面)までを貫通するように、層間絶縁膜に容量コンタクトホール43を形成する。ここでは、ライナー膜41および窒化シリコン膜36がドライエッチング保護膜として機能し、ビット線33の間に自己整合的に容量コンタクトホール43を形成することができる。

【0030】

続いて、図12に示すように、公知の技術により容量コンタクトホール43およびコンタクトホール45の中に導電性の膜を埋め込むことで、コンタクトプラグ(接続プラグ)44を形成する。この際、図12に示すように、容量コンタクトホール43の側壁には窒化シリコンからなるサイドウォール膜60を形成しても良い。

【0031】

続いて、図13に示すように、メモリセル形成領域内では容量コンタクトプラグに電気的に接続された容量コンタクトパッド49、周辺回路形成領域内ではソース及びドレイン40a及び40bに電気的に接続された配線を、公知の方法により形成する。続いて、メモリセル形成領域には、公知の方法により、下部電極50、容量絶縁膜52、及び上部電極51からなるクラウン型のキャパシタを形成する。キャパシタは、容量コンタクトパッド49に電気的に接続されている。これにより、キャパシタ、電界効果トランジスタ、及びビット線を有するDRAMを備えた、本実施例の半導体装置が完成する。

【0032】

本実施例の半導体装置のメモリセル領域には、半導体基板内に設けられた溝型のゲート電極19と、ゲート絶縁膜17と、ソース及びドレインを備えた電界効果トランジスタが設けられている。半導体基板上の層間絶縁膜内には、この電界効果トランジスタのソースまたはドレイン領域に電気的に接続されるようにビット線33が設けられている。ビット線33は、ソースまたはドレイン領域の側から順に、多結晶シリコン膜29、並びに窒化タングステン膜及びタングステン膜30の第1の導体膜から構成されている。ビット線33上には、窒化シリコン膜からなるハードマスク31が設けられている。

【0033】

また、電界効果トランジスタのソースまたはドレイン領域に接続されるように容量コンタクトプラグ44が設けられている。ビット線33と容量コンタクトプラグ44との間は、オフセットスペーサ36aとサイドウォール膜60によって電気的に絶縁されている。容量コンタクトプラグ44は、容量コンタクトパッド49を介して、キャパシタに電気的に接続されている。キャパシタは、下部電極50、容量絶縁膜52及び上部電極51から構成されている。

【0034】

周辺回路領域には、プレナー型のnチャネル型とpチャネル型の第1の電界効果トランジスタが形成されている。各チャネル型のトランジスタは、半導体基板上に順に設けられた、ゲート絶縁膜及びゲート電極を有する。nチャネル型のトランジスタのゲート絶縁膜は、酸化シリコン膜23、及びHfO2膜24の高誘電率膜(High−K膜)からなり、pチャネル型のトランジスタのゲート絶縁膜は、酸化シリコン膜23、及びHfO2膜24とAl2O3膜27の高誘電率膜(High−K膜)からなる。各チャネル型のトランジスタのゲート電極は窒化チタン膜25、多結晶シリコン膜26及び29、並びに窒化タングステン膜及びタングステン膜30からなり、ゲート電極上にはハードマスク31が設けられている。各チャネル型のトランジスタのゲート絶縁膜及びゲート電極の側壁上には、LDD領域を形成するためのオフセットスペーサ36aとして窒化シリコン膜が形成され、ソース及びドレイン領域用のサイドウォールスペーサ39として酸化アルミニウム膜が形成されている。

【0035】

本実施例の半導体装置では、周辺回路領域の第1の電界効果トランジスタに設けたサイドウォールスペーサ39としての酸化アルミニウム膜は、ゲート電極及びゲート絶縁膜への酸化剤の進入を防止する。従って、周辺回路領域の第1の電界効果トランジスタにおいて、酸化剤の進入によるゲート絶縁膜のEOTの増加および負の固定チャージの誘起を抑制できる。これにより、閾値電圧の変動やオン電流の低下を抑制できる。

【0036】

また、半導体装置の構成によっては、メモリセル領域のビット線の間隔は、周辺回路領域のトランジスタのゲート電極の間隔よりも狭いことがある。この場合、周辺回路領域のサイドウォールスペーサ用に形成した絶縁膜が、メモリセル領域のビット線間を埋設してしまう。ビット線間に容量コンタクトプラグを形成する際には、層間絶縁膜(酸化シリコン膜)内に容量コンタクトホールを形成するためのドライエッチングに対するエッチストッパとしてライナー膜(窒化シリコン膜)を形成する。そこで、このライナー膜を形成するためには、ビット線間に埋設されたサイドウォールスペーサ用の絶縁膜を、ウェットエッチングにより等方的に除去する必要がある。

【0037】

この際、関連する半導体装置の製造方法では、ライナー膜とサイドウォールスペーサ用の絶縁膜を窒化シリコン膜で形成している。このため、サイドウォールスペーサ用の絶縁膜をウェットエッチングで除去する際に、ライナー膜も除去されて、ビット線がウェットエッチングに曝されるおそれがあり、好ましくない。

【0038】

これに対して、本実施例では、ライナー膜を窒化シリコン膜で形成し、ビット線間は酸化アルミニウム膜で埋設するため、この埋設膜(酸化アルミニウム膜)を選択的に除去できる。このため、ビット線がウェットエッチングに曝されるといった問題が生じない。

【0039】

以上のように、本実施例によれば、ゲート電極及びゲート絶縁膜への酸化剤の影響による素子特性の劣化を抑制しつつ、ビット線間に埋設された絶縁膜を選択的に除去し得ることで素子の微細化を実現できる。

【0040】

なお、本実施例では、酸化アルミニウム膜からなるサイドウォールスペーサ39を形成したが、変形例として、酸化シリコン膜及び酸化アルミニウム膜からなるサイドウォールスペーサ39を形成することもできる。本変形例では、第1実施例の図1〜7の工程を実施した後、図18に示すように、半導体基板上に酸化アルミニウム膜及び酸化シリコン膜を順に形成する。メモリセル形成領域上にマスクを設けた後、ウェットエッチングにより、酸化アルミニウム膜及び酸化シリコン膜をエッチバックする。この結果、周辺回路形成領域のゲート電極側壁上には、サイドウォールスペーサ(第2の絶縁膜)として、酸化アルミニウム膜39a及び酸化シリコン膜39bが形成される。ウェットエッチングにより、メモリセル形成領域上の酸化アルミニウム膜及び酸化シリコン膜を除去する以外は、第1実施例の図9と同様の工程を実施する。この後、第1実施例の図10〜13の工程を実施して、半導体装置が完成する。

【0041】

本変形例においても、周辺回路領域において、酸化アルミニウム膜39aが、酸化シリコン膜39b及びSOD膜からゲート構造への酸素の拡散を防止するため、第1実施例と同様の効果を奏することができる。

【0042】

(第2実施例)

本実施例は、下記の点が、第1実施例とは異なる。

(a)周辺回路形成領域において、ゲート絶縁膜として酸化シリコン膜を形成する点、

(b)メモリセル形成領域の溝型のゲート電極よりも先に、周辺回路形成領域にゲート絶縁膜及び多結晶シリコン膜を形成する点。

【0043】

以下では、本実施例の半導体装置の製造方法を説明するが、第1実施例と同じ工程についてはその説明を省略する。

【0044】

まず、図14に示すように、上記第1実施例において図2を用いて説明した方法と同様にして、半導体基板のメモリセル形成領域(第2の領域)及び周辺回路形成領域(第1の領域)内に、素子分離領域10を形成し、周辺回路形成領域のnチャネル型のトランジスタを形成する領域11b内にPウェル14、pチャネル型のトランジスタを形成する領域11a内にNウェル15を形成する。その後、周辺回路形成領域のNウェル15及びPウェル14の表面に、周知のISSG法により、酸化シリコン膜12(ゲート絶縁膜)を形成する。半導体基板上の全面に、CVD法により多結晶シリコン膜53を形成した後、周辺回路形成領域上に第5のマスクを設ける。続いて、公知のフォトリソグラフィ法およびエッチング法などにより、メモリセル形成領域上の多結晶シリコン膜53を除去して、周辺回路形成領域上に多結晶シリコン膜53を残留させる。

【0045】

次に、上記第1実施例において図2を用いて説明した方法と同様にして、メモリセル形成領域にトレンチ16、ゲート絶縁膜17、および、溝型のゲート電極19を形成する。その後、半導体基板上の全面に、LP−TEOS(Low Pressure −tetra ethyl ortho silicate;TEOSは、Si(OC2H5)4を表す)膜54を形成する。この後、公知のフォトリソグラフィ技術により、周辺回路形成領域上のLP−TEOS膜54を除去する。本第2実施例におけるこのLP−TEOS膜54は、上記第1実施例におけるビットコンタクト層間絶縁膜22として機能する。

【0046】

その後、上記第1実施例において図3〜図6を用いて説明した方法と同様にして、図15に示す構造を得る。図15に示した構成要素において、上記図3〜図6に示された構成要素と同じ符号のものは、同様の方法で形成または加工されるものとする。この加工により、メモリセル形成領域上では、多結晶シリコン膜(導電膜)29、窒化タングステン膜(導電膜)及びタングステン膜(導電膜)30(以上、第1の導体膜)からなるビット線33(第1の配線)が形成される。また、この加工により、周辺回路形成領域のPウェル14上では酸化シリコン膜12、多結晶シリコン膜29及び53、並びに窒化タングステン膜及びタングステン膜30からなるゲート構造(第1の積層体)が形成される。また、この加工により、周辺回路形成領域のNウェル15上では酸化シリコン膜12、多結晶シリコン膜29及び53並びに窒化タングステン膜及びタングステン膜30からなるゲート構造(第1の積層体)が形成される。

【0047】

次に、図16に示すように、上記第1実施例において図7〜9を用いて説明した方法と同様にして、窒化シリコン膜36、オフセットスペーサ36a、LDD領域37a,37b、酸化アルミニウム膜38、ソース及びドレイン40a,40bを形成する。そして、上記図9を用いて説明した方法と同様にして、メモリセル形成領域においてビット線33間に埋設されていた酸化アルミニウム膜38をウェットエッチングにより除去する。ここでは、酸化アルミニウム膜38と窒化シリコン膜36とが異なる絶縁膜であるため、メモリセル形成領域のビット線33間に埋設された酸化アルミニウム膜38を、ビット線33を覆う窒化シリコン膜36に対して選択的に除去できる。この観点から、メモリセル形成領域においてビット線33を覆うように形成する第1の絶縁膜の材料は、酸化アルミニウムと異なり(第2の絶縁膜を選択的に除去するため)、かつ、酸化剤として寄与しない絶縁膜であれば良く、窒化シリコンに限定されない。

【0048】

続いて、上記第1実施例において図10〜図13を用いて説明した方法と同様にして、本第2実施例の半導体装置が完成する。図17は、本実施例の半導体装置のメモリセル領域を表す断面図である。図17に示すように、本実施例の半導体装置では、第1実施例の半導体装置とは異なり、周辺回路領域のnチャネル型及びpチャネル型の第1の電界効果トランジスタは、共にゲート絶縁膜が酸化シリコン膜から構成されている。また、第1の電界効果トランジスタのゲート電極は、共に多結晶シリコン膜、窒化タングステン膜、及びタングステン膜から構成されている。本実施例の半導体装置において、その他の基本構成は第1実施例の半導体装置と同様である。このため、周辺回路領域に形成するサイドウォールスペーサ(第2の絶縁膜)としての酸化アルミニウム膜は、ゲート電極及びゲート絶縁膜への酸化剤の進入を防止して、ゲート絶縁膜のEOTの増加および負の固定チャージの誘起を抑制できる。これにより、閾値電圧の変動やオン電流の低下を抑制できる。また、本実施例の半導体装置の製造工程では、メモリセル領域に形成するビット線間の間隔が狭い場合であっても、ビット線間に埋設されるサイドウォールスペーサ用の酸化アルミニウム膜を選択的に除去して、素子の微細化を実現することができる。

【符号の説明】

【0049】

10 素子分離領域

11 活性領域

11a pチャネル型のトランジスタを形成する領域

11b nチャネル型のトランジスタを形成する領域

14 Pウェル

15 Nウェル

16 トレンチ

17 ゲート絶縁膜

19 埋め込みゲート電極

22 ビットコンタクト層間絶縁膜

23 酸化シリコン膜

24 HfO2膜

25 窒化チタン膜

26、29 多結晶シリコン膜

27 Al2O3膜

28 フォトレジスト

30 窒化タングステン膜及びタングステン膜

31 窒化シリコン膜

33 ビット線

34 ゲート電極

36 窒化シリコン膜

36a オフセットスペーサ

37a、37b LDD領域

38 酸化アルミニウム膜

39、39a、39b サイドウォールスペーサ

40a、40b ソース及びドレイン

41、60 窒化シリコン膜

42 SOD膜

43 容量コンタクトホール

45 コンタクトホール

49 容量コンタクトパッド

50 下部電極

51 上部電極

52 容量絶縁膜

53 多結晶シリコン膜

54 LP−TEOS膜

【技術分野】

【0001】

本発明は、半導体装置およびその製造方法に関する。

【背景技術】

【0002】

特許文献1(特開2000−216373号公報)には、半導体基板上へのMOSトランジスタの形成方法が記載されている。ここでは、基板上にゲート絶縁膜を介して配置されたゲート電極を形成する。この後、ゲート電極の側壁上にオフセットスペーサを形成し、ゲート電極およびオフセットスペーサをマスクとして基板にイオン注入を施すことにより、LDD領域を形成する。オフセットスペーサを用いることで、イオン注入により導入された不純物がゲート電極下の基板に熱拡散しにくくなり、ゲート−ドレイン間容量を低減できる。更に、オフセットスペーサの外部側壁上にサイドウォールスペーサを形成し、ゲート電極およびサイドウォールスペーサをマスクとして基板にイオン注入を施すことで、ソース及びドレインを形成する。ここで、特許文献1では、オフセットスペーサおよびサイドウォールスペーサを形成する材料として、酸化シリコンまたは窒化シリコンからなる絶縁膜が挙げられている。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2000−216373号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

本発明者がこの技術について検討したところ、以下のような課題を有することが明らかとなった。酸化シリコン膜やそれよりも高い誘電率を持つ高誘電率膜(high−k膜)からなるゲート絶縁膜は、MISトランジスタの電気特性に関わる構成要素の一つである。特に、ゲート絶縁膜の膜厚(等価酸化膜厚(Equivalent Oxide Thickness:EOT)で表される)は、閾値電圧や電流値に影響するため、EOTの制御が重要となる。

【0005】

従来、MISトランジスタの形成工程では、特許文献1の図3に示されるように、オフセットスペーサやサイドウォールスペーサ(第2スペーサ)を構成する材料として、酸化シリコンや窒化シリコンからなる絶縁膜が適用されていた。このような技術について本発明者が検討したところ、以下の課題を有することが分かった。

【0006】

例えば、オフセットスペーサやサイドウォールスペーサとして酸化シリコンを適用した場合、ソース及びドレイン用の不純物活性化のためのアニール時などに、これらのスペーサや層間絶縁膜の酸化シリコンに由来する酸化剤がゲート絶縁膜に侵入し、ゲート絶縁膜のEOTを増加させることが分かった。このような酸化剤の進入によるゲート絶縁膜のEOTの増加は、酸化シリコンよりも誘電率の高い高誘電率膜(high−k膜)をゲート絶縁膜として用いた場合に、より顕著となっていた。また、酸化剤作用によりゲート絶縁膜中に負の固定チャージが誘起され、閾値電圧のシフトが起こることが分かった。

【0007】

また、オフセットスペーサとして窒化シリコン膜を適用した場合であっても、サイドウォールスペーサなどと比較して薄いオフセットスペーサでは酸化剤の進入に対するバリア性は不十分であった。一方、厚い窒化シリコン膜からなるオフセットスペーサを用いることは、ゲート電極下のチャネル領域とLDD領域との離間による抵抗の増加が懸念されるため、好ましくない。

【0008】

そこで、本発明者は、周辺回路領域のトランジスタ用のオフセットスペーサおよびサイドウォールスペーサの両スペーサを窒化シリコン膜とする構造を更に検討した。このように、オフセットスペーサに加え、比較的厚いサイドウォールスペーサを窒化シリコン膜とすることで、酸化剤の進入によるEOTの増加の抑制が期待できる。

【0009】

しかしながら、本発明者の更なる検討によれば、以下のような課題を有することが分かった。例えば、埋め込みワード線構造のDRAMメモリセルにおいて、周辺回路領域のゲート電極と同時にパターニングされるビット線の間隔は、周辺回路領域のゲート電極の間隔よりも狭くなる。また、一般的に半導体集積回路の高集積化に伴って半導体素子は微細化され、複数併設されるゲート電極の間隔は狭くなる。このように狭いビット線やゲート電極間は、スペーサ膜やエッチングストッパ膜で埋設される場合がある。換言すれば、ビット線間やゲート電極間が窒化シリコン膜のみで埋設されることになる。これにより、当該ビット線間やゲート電極間に、自己整合的手法によるコンタクト(Self Align Contact:SAC)を形成することが困難となる。そこで、ビット線間のサイドウォールスペーサを選択的に除去することが考えられる。しかし、上述のようにオフセットスペーサとサイドウォールスペーサが同一の窒化シリコン膜で形成されている場合、サイドウォールスペーサのみを選択的に除去できなくなる。

【課題を解決するための手段】

【0010】

一実施形態は、

基板の第1の領域の主面に、ゲート絶縁膜を形成する工程と、

前記ゲート絶縁膜を覆うゲート電極を形成する工程と、

前記基板の第1の領域では前記ゲート電極を覆い、前記第1の領域と異なる第2の領域では前記基板の主面を覆うように、前記基板に第1の導体膜を形成する工程と、

前記第1の導体膜、前記ゲート電極および前記ゲート絶縁膜を加工して、前記第1の領域には前記第1の導体膜、前記ゲート電極および前記ゲート絶縁膜からなる第1の積層体を形成し、前記第2の領域には前記第1の導体膜からなる複数の第1の配線を形成する工程と、

前記第1の積層体の側壁を覆い、かつ、前記複数の第1の配線を覆うように、第1の絶縁膜を形成する工程と、

前記第1の絶縁膜をマスクとして、前記基板の第1の領域の主面に第1のイオン注入を施す工程と、

前記第1の積層体の側壁を覆い、かつ、前記複数の第1の配線間を埋設するように、前記第1の絶縁膜とは異なる絶縁膜であって、酸化アルミニウムを主体とする第2の絶縁膜を形成する工程と、

前記第2の絶縁膜をマスクとして、前記基板の第1の領域の主面に第2のイオン注入を施す工程と、

前記第1の絶縁膜に対して選択的に、前記第2の絶縁膜を除去する工程と、

を有することを特徴とする半導体装置の製造方法に関する。

【0011】

他の実施形態は、

基板と、

前記基板の第1の領域の主面上に順に形成されたゲート絶縁膜、ゲート電極、および第1の導体膜からなる第1の積層体と、

前記第1の積層体の側壁を覆う第1の絶縁膜と、

前記第1の積層体の側壁を覆い、かつ、前記第1の絶縁膜とは異なる絶縁膜であって、酸化アルミニウムを主体とする第2の絶縁膜と、

前記第1の積層体の両側の側方下部の基板内に設けられたLDD領域およびソース/ドレイン領域と、

前記基板の第2の領域の主面上に形成された、第1の導体膜からなる複数の第1の配線と、

を有することを特徴とする半導体装置に関する。

【0012】

なお、本明細書及び特許請求の範囲では、完成前のメモリセル領域を形成する予定の領域を「メモリセル形成領域」、完成前の周辺回路領域を形成する予定の領域を「周辺回路形成領域」とする。これらの領域は、完成前で製造途中の領域である点でそれぞれ、「メモリセル領域」及び「周辺回路領域」と区別される。以下では、メモリセル形成領域を「第2の領域」、周辺回路形成領域を第1の領域と呼ぶ場合がある。

【発明の効果】

【0013】

第1の領域において、ゲート絶縁膜を含む第1の積層体を覆うサイドウォールスペーサ(第2の絶縁膜)として酸化アルミニウムを主体とする絶縁膜を適用することにより、ゲート絶縁膜への酸化剤の進入を低減することができる。また、この第2の絶縁膜として第1の絶縁膜と異なる絶縁膜を適用することにより、第2の領域において、複数の第1の配線間に設けられた第2の絶縁膜を第1の絶縁膜に対して選択的に除去することができる。

【図面の簡単な説明】

【0014】

【図1】第1実施例の半導体装置の製造方法の一工程を表す図である。

【図2】第1実施例の半導体装置の製造方法の一工程を表す図である。

【図3】第1実施例の半導体装置の製造方法の一工程を表す図である。

【図4】第1実施例の半導体装置の製造方法の一工程を表す図である。

【図5】第1実施例の半導体装置の製造方法の一工程を表す図である。

【図6】第1実施例の半導体装置の製造方法の一工程を表す図である。

【図7】第1実施例の半導体装置の製造方法の一工程を表す図である。

【図8】第1実施例の半導体装置の製造方法の一工程を表す図である。

【図9】第1実施例の半導体装置の製造方法の一工程を表す図である。

【図10】第1実施例の半導体装置の製造方法の一工程を表す図である。

【図11】第1実施例の半導体装置の製造方法の一工程を表す図である。

【図12】第1実施例の半導体装置の製造方法の一工程を表す図である。

【図13】第1実施例の半導体装置を表す図である。

【図14】第2実施例の半導体装置の製造方法の一工程を表す図である。

【図15】第2実施例の半導体装置の製造方法の一工程を表す図である。

【図16】第2実施例の半導体装置の製造方法の一工程を表す図である。

【図17】第2実施例の半導体装置を表す図である。

【図18】第1実施例の変形例の製造方法の一工程を表す図である。

【発明を実施するための形態】

【0015】

(第1実施例)

本実施例は、本発明の構造を周辺回路領域の第1の電界効果トランジスタ及びメモリセル領域のビット線(第1の配線)に適用した、DRAM(Dynamic Random Access Memory)を有する半導体装置の製造方法に関するものである。本実施例では、メモリセル形成領域(第2の領域)のビット線と、周辺回路形成領域(第1の領域)の第1の電界効果トランジスタのゲート電極を、同一の工程でパターニングして形成する。

【0016】

以下、図面を参照して、本実施例の半導体装置の製造方法を説明する。図1はメモリセル形成領域を表す平面図を表す。また、図2Aは図1のA1−A1方向の断面図、図2Bは図1のB1−B1方向の断面図、図2Cは周辺回路形成領域の断面図を表す。以下、平面図と断面図との関係は特記しない限り同様である。なお、構成要素を分かり易くするために、上層を覆う絶縁膜などを適宜省略して示すこととする。

【0017】

まず、図1及び2に示すように、STI法により、半導体基板のメモリセル形成領域(第2の領域)及び周辺回路形成領域(第1の領域)内に、素子分離領域10を形成する。これにより、半導体基板内では、素子分離領域10で区画された領域が活性領域11となる。次に、公知の方法により、周辺回路領域のnチャネル型のトランジスタを形成する領域11bにPウェル14を形成し、pチャネル型のトランジスタを形成する領域11aにNウェル15を形成する。

【0018】

続いて、公知の方法により、メモリセル形成領域内に、素子分離領域10と交差する方向に延在する溝状のトレンチ16を形成する。そして、トレンチ16の内壁をISSG(in−situ steam generation)法により酸化して、酸化シリコン膜からなるゲート絶縁膜17を形成する。次に、トレンチ16内を導体膜で埋め込むことで、溝型のゲート電極19を形成する。そして、半導体基板上の主面に、窒化シリコン膜からなるビットコンタクト層間絶縁膜22を形成する。ウェットエッチングにより、周辺回路形成領域上の窒化シリコン膜22、及びパッド酸化膜12を除去する。

【0019】

次に、図3に示すように、周辺回路形成領域の主面上に酸化シリコン膜23を形成する。Pウェル14上に半導体基板側から順に、HfO2(酸化ハフニウム)膜24、窒化チタン膜(金属膜)25、及び多結晶シリコン膜(導電膜)26を形成する。酸化シリコン膜23及びHfO2膜24はゲート絶縁膜を構成し、窒化チタン膜25及び多結晶シリコン膜(多結晶シリコン膜)26はゲート電極を構成する。また、Nウェル15上に半導体基板側から順に、HfO2膜24、Al2O3(酸化アルミニウム)膜27、窒化チタン膜(金属膜)25及び多結晶シリコン膜(導電膜)26を形成する。酸化シリコン膜23、HfO2膜24及びAl2O3膜27は、ゲート絶縁膜を構成し、窒化チタン膜25及び多結晶シリコン膜26はゲート電極を構成する。酸化ハフニウムや酸化アルミニウムを含む絶縁膜は、二酸化シリコンを主体とする絶縁膜よりも誘電率が高く、高誘電率絶縁膜やHigh−K絶縁膜と呼ばれる。本第1実施例の半導体装置では、周辺回路領域にこのような高誘電率絶縁膜をゲート絶縁膜に適用した第1の電界効果トランジスタを形成する。

【0020】

なお、高誘電率ゲート絶縁膜は上記の材料に限定されず、例えば、ケイ酸化ハフニウム(HfSiO)や、酸化ランタン(La2O3)などもある。酸化剤の影響を受けてEOTが増加し得るゲート絶縁膜であれば、本願を適用して同様に効果的である。また、高誘電率ゲート絶縁膜と相性の良いゲート電極として、金属材料を適用することがあり、上記の窒化チタン膜もその一種である。金属ゲート電極はこれに限定されず、例えば、窒化タンタル(TaN)膜などもある。

【0021】

次に、図4に示すように、フォトリソグラフィ法およびドライエッチング法などによって、ビットコンタクト層間絶縁膜22の一部を除去することで、ビットコンタクト開口部から活性領域11の一部を露出させる。その上で、半導体基板上の全面に多結晶シリコン膜(導電膜)29、窒化タングステン膜(導電膜)及びタングステン膜(導電膜)30(図4中には窒化タングステン膜とタングステン膜の境界を示さない)、並びに窒化シリコン膜31を形成する。この多結晶シリコン膜29、窒化タングステン膜及びタングステン膜30が第1の導体膜を構成する。この工程により、周辺回路形成領域ではゲート電極を覆い、メモリセル形成領域ではビットコンタクト開口部において基板を覆うように、第1の導体膜を形成する。

【0022】

次に、図5及び6に示すように、フォトリソグラフィ法およびエッチング法などにより、第1の窒化シリコン膜31、窒化タングステン膜及びタングステン膜30、多結晶シリコン膜29,26、および、ゲート絶縁膜24,27を加工する。この加工により、メモリセル形成領域上では、多結晶シリコン膜29、窒化タングステン膜及びタングステン膜30(以上、第1の導体膜)からなるビット線33(第1の配線)が形成される。また、この加工により、周辺回路形成領域のPウェル14上では、高誘電率ゲート絶縁膜、窒化チタン膜25、多結晶シリコン膜26及び29、並びに窒化タングステン膜及びタングステン膜30からなるゲート構造(第1の積層体)が形成される。Pウェル14上では、酸化シリコン膜23、及びパターニングされた高誘電率絶縁膜(HfO2膜24)は、ゲート絶縁膜を構成する。また、この加工により、周辺回路形成領域のNウェル15上では、高誘電率ゲート絶縁膜、窒化チタン膜25、多結晶シリコン膜26及び29、並びに窒化タングステン膜及びタングステン膜30からなるゲート構造(第1の積層体)が形成される。Nウェル15上では、酸化シリコン膜23、及びパターニングされた高誘電率絶縁膜(HfO2膜24及びAl2O3膜27)は、ゲート絶縁膜を構成する。

【0023】

次に、図7に示すように、半導体基板上の全面に、ALD(Atomic Layer Deposition)法により、窒化シリコン膜36(第1の絶縁膜)を形成する。半導体基板上の全面にフォトレジスト28を形成した後、周辺回路形成領域上のフォトレジスト28を除去して、フォトレジストパターンを形成する。周辺回路形成領域上の窒化シリコン膜36をエッチバックして、ゲート絶縁膜、ゲート電極及びハードマスクの側壁を覆うように、オフセットスペーサ(第1の絶縁膜)36aとして窒化シリコン膜を残留させる。フォトレジスト28で覆われたメモリセル形成領域は当該エッチングには曝されず、窒化シリコン膜36は複数のビット線33を覆うように形成される。

【0024】

フォトレジストパターン28を除去した後、メモリセル形成領域及び周辺回路形成領域のNウェル15上に、第1のマスク(図示していない)を設ける。ハードマスク13、オフセットスペーサ36a及び第1のマスクを用いて、周辺回路形成領域のPウェル14内にn型導電型の不純物をイオン注入して、第1の積層体の側方下部にLDD領域37aを形成する(第1のイオン注入)。第1のマスクを除去した後、メモリセル形成領域及び周辺回路形成領域のPウェル14上に、第2のマスク(図示していない)を設ける。ハードマスク13、オフセットスペーサ36a及び第2のマスクを用いて、周辺回路形成領域のNウェル15内にp型導電型の不純物をイオン注入して、第1の積層体の側方下部にLDD領域37bを形成する(第1のイオン注入)。この後、第2のマスクを除去する。

【0025】

次に、図8に示すように、半導体基板上の全面に、酸化アルミニウム膜38(第2の絶縁膜)を形成する。半導体基板上の全面にフォトレジスト28を形成した後、周辺回路形成領域上のフォトレジスト28を除去して、フォトレジストパターンを形成する。周辺回路形成領域上の酸化アルミニウム膜38をエッチバックして、オフセットスペーサ(第1の絶縁膜)36a上であるゲート電極及びハードマスクの側壁を覆うように、サイドウォールスペーサ(第2の絶縁膜)39として酸化アルミニウム膜を残留させる。フォトレジスト28で覆われたメモリセル形成領域は当該エッチングには曝されず、酸化アルミニウム膜38は複数のビット線33の間を埋設するように形成される。

【0026】

フォトレジストパターン28を除去した後、メモリセル形成領域及び周辺回路形成領域のNウェル15上に、第3のマスク(図示していない)を設ける。ハードマスク13、オフセットスペーサ39、サイドウォールスペーサ36a、及び第3のマスクを用いて、周辺回路形成領域のPウェル14内に、第1のイオン注入よりも高濃度のn型導電型の不純物のイオン注入を行う(第2のイオン注入)。これにより、第1の積層体の側方下部にソース及びドレイン40aを形成する。第3のマスクを除去した後、メモリセル形成領域及び周辺回路形成領域のPウェル14上に、第4のマスク(図示していない)を設ける。ハードマスク13、オフセットスペーサ36a、サイドウォールスペーサ39、及び第4のマスクを用いて、周辺回路形成領域のNウェル15内に、第1のイオン注入よりも高濃度のp型導電型の不純物のイオン注入を行う(第2のイオン注入)。これにより、第1の積層体の側方下部にソース及びドレイン40bを形成する。この後、第4のマスクを除去する。

【0027】

続いて、図9に示すように、半導体基板上の全面にフォトレジスト28を形成した後、メモリセル形成領域上のフォトレジストを除去して、フォトレジストパターンを形成する。このフォトレジストパターンをマスクに用いたウェットエッチングにより、メモリセル形成領域上の酸化アルミニウム膜38を除去する。ここでは、酸化アルミニウム膜38と窒化シリコン膜36とが異なる絶縁膜であるため、メモリセル形成領域のビット線33間に埋設された酸化アルミニウム膜38を、ビット線33を覆う窒化シリコン膜36に対して選択的に除去できる。この観点から、メモリセル形成領域においてビット線33を覆うように形成する第1の絶縁膜の材料は、酸化アルミニウムと異なり(第2の絶縁膜を選択的に除去するため)、かつ、酸化剤として寄与しない絶縁膜であれば良く、窒化シリコンに限定されない。その後、フォトレジストパターンを除去する。

【0028】

次に、図10に示すように、半導体基板上の全面に、CVD法により、ライナー膜として窒化シリコン膜41を形成する。この際、メモリセル形成領域上の酸化アルミニウム膜38は除去されているため、ビット線間を完全に埋設させることなく、窒化シリコン膜41を形成することができる。この結果、後述する図11の工程で、窒化シリコン膜41を、容量コンタクトホール開口時のエッチングストッパとして用いることができる。次に、SOD(Spin On Dielectric;層間絶縁膜)膜42を形成した後、熱処理を行う。ライナー膜41をストッパとして、SOD膜42に対してCMP法を行うことにより、SOD膜42を平坦化させる。

【0029】

図11に示すように、フォトリソグラフィ法およびエッチング法などにより、SOD膜42からなる層間絶縁膜に、容量コンタクトホール43(接続孔)およびコンタクトホール45を形成する。具体的には、メモリセル形成領域では、SOD膜42からなる層間絶縁膜に、その表面から、ビット線33間に位置する活性領域11(ソースまたはドレイン領域である基板の主面)までを貫通するように、層間絶縁膜に容量コンタクトホール43を形成する。ここでは、ライナー膜41および窒化シリコン膜36がドライエッチング保護膜として機能し、ビット線33の間に自己整合的に容量コンタクトホール43を形成することができる。

【0030】

続いて、図12に示すように、公知の技術により容量コンタクトホール43およびコンタクトホール45の中に導電性の膜を埋め込むことで、コンタクトプラグ(接続プラグ)44を形成する。この際、図12に示すように、容量コンタクトホール43の側壁には窒化シリコンからなるサイドウォール膜60を形成しても良い。

【0031】

続いて、図13に示すように、メモリセル形成領域内では容量コンタクトプラグに電気的に接続された容量コンタクトパッド49、周辺回路形成領域内ではソース及びドレイン40a及び40bに電気的に接続された配線を、公知の方法により形成する。続いて、メモリセル形成領域には、公知の方法により、下部電極50、容量絶縁膜52、及び上部電極51からなるクラウン型のキャパシタを形成する。キャパシタは、容量コンタクトパッド49に電気的に接続されている。これにより、キャパシタ、電界効果トランジスタ、及びビット線を有するDRAMを備えた、本実施例の半導体装置が完成する。

【0032】

本実施例の半導体装置のメモリセル領域には、半導体基板内に設けられた溝型のゲート電極19と、ゲート絶縁膜17と、ソース及びドレインを備えた電界効果トランジスタが設けられている。半導体基板上の層間絶縁膜内には、この電界効果トランジスタのソースまたはドレイン領域に電気的に接続されるようにビット線33が設けられている。ビット線33は、ソースまたはドレイン領域の側から順に、多結晶シリコン膜29、並びに窒化タングステン膜及びタングステン膜30の第1の導体膜から構成されている。ビット線33上には、窒化シリコン膜からなるハードマスク31が設けられている。

【0033】

また、電界効果トランジスタのソースまたはドレイン領域に接続されるように容量コンタクトプラグ44が設けられている。ビット線33と容量コンタクトプラグ44との間は、オフセットスペーサ36aとサイドウォール膜60によって電気的に絶縁されている。容量コンタクトプラグ44は、容量コンタクトパッド49を介して、キャパシタに電気的に接続されている。キャパシタは、下部電極50、容量絶縁膜52及び上部電極51から構成されている。

【0034】

周辺回路領域には、プレナー型のnチャネル型とpチャネル型の第1の電界効果トランジスタが形成されている。各チャネル型のトランジスタは、半導体基板上に順に設けられた、ゲート絶縁膜及びゲート電極を有する。nチャネル型のトランジスタのゲート絶縁膜は、酸化シリコン膜23、及びHfO2膜24の高誘電率膜(High−K膜)からなり、pチャネル型のトランジスタのゲート絶縁膜は、酸化シリコン膜23、及びHfO2膜24とAl2O3膜27の高誘電率膜(High−K膜)からなる。各チャネル型のトランジスタのゲート電極は窒化チタン膜25、多結晶シリコン膜26及び29、並びに窒化タングステン膜及びタングステン膜30からなり、ゲート電極上にはハードマスク31が設けられている。各チャネル型のトランジスタのゲート絶縁膜及びゲート電極の側壁上には、LDD領域を形成するためのオフセットスペーサ36aとして窒化シリコン膜が形成され、ソース及びドレイン領域用のサイドウォールスペーサ39として酸化アルミニウム膜が形成されている。

【0035】

本実施例の半導体装置では、周辺回路領域の第1の電界効果トランジスタに設けたサイドウォールスペーサ39としての酸化アルミニウム膜は、ゲート電極及びゲート絶縁膜への酸化剤の進入を防止する。従って、周辺回路領域の第1の電界効果トランジスタにおいて、酸化剤の進入によるゲート絶縁膜のEOTの増加および負の固定チャージの誘起を抑制できる。これにより、閾値電圧の変動やオン電流の低下を抑制できる。

【0036】

また、半導体装置の構成によっては、メモリセル領域のビット線の間隔は、周辺回路領域のトランジスタのゲート電極の間隔よりも狭いことがある。この場合、周辺回路領域のサイドウォールスペーサ用に形成した絶縁膜が、メモリセル領域のビット線間を埋設してしまう。ビット線間に容量コンタクトプラグを形成する際には、層間絶縁膜(酸化シリコン膜)内に容量コンタクトホールを形成するためのドライエッチングに対するエッチストッパとしてライナー膜(窒化シリコン膜)を形成する。そこで、このライナー膜を形成するためには、ビット線間に埋設されたサイドウォールスペーサ用の絶縁膜を、ウェットエッチングにより等方的に除去する必要がある。

【0037】

この際、関連する半導体装置の製造方法では、ライナー膜とサイドウォールスペーサ用の絶縁膜を窒化シリコン膜で形成している。このため、サイドウォールスペーサ用の絶縁膜をウェットエッチングで除去する際に、ライナー膜も除去されて、ビット線がウェットエッチングに曝されるおそれがあり、好ましくない。

【0038】

これに対して、本実施例では、ライナー膜を窒化シリコン膜で形成し、ビット線間は酸化アルミニウム膜で埋設するため、この埋設膜(酸化アルミニウム膜)を選択的に除去できる。このため、ビット線がウェットエッチングに曝されるといった問題が生じない。

【0039】

以上のように、本実施例によれば、ゲート電極及びゲート絶縁膜への酸化剤の影響による素子特性の劣化を抑制しつつ、ビット線間に埋設された絶縁膜を選択的に除去し得ることで素子の微細化を実現できる。

【0040】

なお、本実施例では、酸化アルミニウム膜からなるサイドウォールスペーサ39を形成したが、変形例として、酸化シリコン膜及び酸化アルミニウム膜からなるサイドウォールスペーサ39を形成することもできる。本変形例では、第1実施例の図1〜7の工程を実施した後、図18に示すように、半導体基板上に酸化アルミニウム膜及び酸化シリコン膜を順に形成する。メモリセル形成領域上にマスクを設けた後、ウェットエッチングにより、酸化アルミニウム膜及び酸化シリコン膜をエッチバックする。この結果、周辺回路形成領域のゲート電極側壁上には、サイドウォールスペーサ(第2の絶縁膜)として、酸化アルミニウム膜39a及び酸化シリコン膜39bが形成される。ウェットエッチングにより、メモリセル形成領域上の酸化アルミニウム膜及び酸化シリコン膜を除去する以外は、第1実施例の図9と同様の工程を実施する。この後、第1実施例の図10〜13の工程を実施して、半導体装置が完成する。

【0041】

本変形例においても、周辺回路領域において、酸化アルミニウム膜39aが、酸化シリコン膜39b及びSOD膜からゲート構造への酸素の拡散を防止するため、第1実施例と同様の効果を奏することができる。

【0042】

(第2実施例)

本実施例は、下記の点が、第1実施例とは異なる。

(a)周辺回路形成領域において、ゲート絶縁膜として酸化シリコン膜を形成する点、

(b)メモリセル形成領域の溝型のゲート電極よりも先に、周辺回路形成領域にゲート絶縁膜及び多結晶シリコン膜を形成する点。

【0043】

以下では、本実施例の半導体装置の製造方法を説明するが、第1実施例と同じ工程についてはその説明を省略する。

【0044】

まず、図14に示すように、上記第1実施例において図2を用いて説明した方法と同様にして、半導体基板のメモリセル形成領域(第2の領域)及び周辺回路形成領域(第1の領域)内に、素子分離領域10を形成し、周辺回路形成領域のnチャネル型のトランジスタを形成する領域11b内にPウェル14、pチャネル型のトランジスタを形成する領域11a内にNウェル15を形成する。その後、周辺回路形成領域のNウェル15及びPウェル14の表面に、周知のISSG法により、酸化シリコン膜12(ゲート絶縁膜)を形成する。半導体基板上の全面に、CVD法により多結晶シリコン膜53を形成した後、周辺回路形成領域上に第5のマスクを設ける。続いて、公知のフォトリソグラフィ法およびエッチング法などにより、メモリセル形成領域上の多結晶シリコン膜53を除去して、周辺回路形成領域上に多結晶シリコン膜53を残留させる。

【0045】

次に、上記第1実施例において図2を用いて説明した方法と同様にして、メモリセル形成領域にトレンチ16、ゲート絶縁膜17、および、溝型のゲート電極19を形成する。その後、半導体基板上の全面に、LP−TEOS(Low Pressure −tetra ethyl ortho silicate;TEOSは、Si(OC2H5)4を表す)膜54を形成する。この後、公知のフォトリソグラフィ技術により、周辺回路形成領域上のLP−TEOS膜54を除去する。本第2実施例におけるこのLP−TEOS膜54は、上記第1実施例におけるビットコンタクト層間絶縁膜22として機能する。

【0046】

その後、上記第1実施例において図3〜図6を用いて説明した方法と同様にして、図15に示す構造を得る。図15に示した構成要素において、上記図3〜図6に示された構成要素と同じ符号のものは、同様の方法で形成または加工されるものとする。この加工により、メモリセル形成領域上では、多結晶シリコン膜(導電膜)29、窒化タングステン膜(導電膜)及びタングステン膜(導電膜)30(以上、第1の導体膜)からなるビット線33(第1の配線)が形成される。また、この加工により、周辺回路形成領域のPウェル14上では酸化シリコン膜12、多結晶シリコン膜29及び53、並びに窒化タングステン膜及びタングステン膜30からなるゲート構造(第1の積層体)が形成される。また、この加工により、周辺回路形成領域のNウェル15上では酸化シリコン膜12、多結晶シリコン膜29及び53並びに窒化タングステン膜及びタングステン膜30からなるゲート構造(第1の積層体)が形成される。

【0047】

次に、図16に示すように、上記第1実施例において図7〜9を用いて説明した方法と同様にして、窒化シリコン膜36、オフセットスペーサ36a、LDD領域37a,37b、酸化アルミニウム膜38、ソース及びドレイン40a,40bを形成する。そして、上記図9を用いて説明した方法と同様にして、メモリセル形成領域においてビット線33間に埋設されていた酸化アルミニウム膜38をウェットエッチングにより除去する。ここでは、酸化アルミニウム膜38と窒化シリコン膜36とが異なる絶縁膜であるため、メモリセル形成領域のビット線33間に埋設された酸化アルミニウム膜38を、ビット線33を覆う窒化シリコン膜36に対して選択的に除去できる。この観点から、メモリセル形成領域においてビット線33を覆うように形成する第1の絶縁膜の材料は、酸化アルミニウムと異なり(第2の絶縁膜を選択的に除去するため)、かつ、酸化剤として寄与しない絶縁膜であれば良く、窒化シリコンに限定されない。

【0048】

続いて、上記第1実施例において図10〜図13を用いて説明した方法と同様にして、本第2実施例の半導体装置が完成する。図17は、本実施例の半導体装置のメモリセル領域を表す断面図である。図17に示すように、本実施例の半導体装置では、第1実施例の半導体装置とは異なり、周辺回路領域のnチャネル型及びpチャネル型の第1の電界効果トランジスタは、共にゲート絶縁膜が酸化シリコン膜から構成されている。また、第1の電界効果トランジスタのゲート電極は、共に多結晶シリコン膜、窒化タングステン膜、及びタングステン膜から構成されている。本実施例の半導体装置において、その他の基本構成は第1実施例の半導体装置と同様である。このため、周辺回路領域に形成するサイドウォールスペーサ(第2の絶縁膜)としての酸化アルミニウム膜は、ゲート電極及びゲート絶縁膜への酸化剤の進入を防止して、ゲート絶縁膜のEOTの増加および負の固定チャージの誘起を抑制できる。これにより、閾値電圧の変動やオン電流の低下を抑制できる。また、本実施例の半導体装置の製造工程では、メモリセル領域に形成するビット線間の間隔が狭い場合であっても、ビット線間に埋設されるサイドウォールスペーサ用の酸化アルミニウム膜を選択的に除去して、素子の微細化を実現することができる。

【符号の説明】

【0049】

10 素子分離領域

11 活性領域

11a pチャネル型のトランジスタを形成する領域

11b nチャネル型のトランジスタを形成する領域

14 Pウェル

15 Nウェル

16 トレンチ

17 ゲート絶縁膜

19 埋め込みゲート電極

22 ビットコンタクト層間絶縁膜

23 酸化シリコン膜

24 HfO2膜

25 窒化チタン膜

26、29 多結晶シリコン膜

27 Al2O3膜

28 フォトレジスト

30 窒化タングステン膜及びタングステン膜

31 窒化シリコン膜

33 ビット線

34 ゲート電極

36 窒化シリコン膜

36a オフセットスペーサ

37a、37b LDD領域

38 酸化アルミニウム膜

39、39a、39b サイドウォールスペーサ

40a、40b ソース及びドレイン

41、60 窒化シリコン膜

42 SOD膜

43 容量コンタクトホール

45 コンタクトホール

49 容量コンタクトパッド

50 下部電極

51 上部電極

52 容量絶縁膜

53 多結晶シリコン膜

54 LP−TEOS膜

【特許請求の範囲】

【請求項1】

基板の第1の領域の主面に、ゲート絶縁膜を形成する工程と、

前記ゲート絶縁膜を覆うゲート電極を形成する工程と、

前記基板の第1の領域では前記ゲート電極を覆い、前記第1の領域と異なる第2の領域では前記基板の主面を覆うように、前記基板に第1の導体膜を形成する工程と、

前記第1の導体膜、前記ゲート電極および前記ゲート絶縁膜を加工して、前記第1の領域には前記第1の導体膜、前記ゲート電極および前記ゲート絶縁膜からなる第1の積層体を形成し、前記第2の領域には前記第1の導体膜からなる複数の第1の配線を形成する工程と、

前記第1の積層体の側壁を覆い、かつ、前記複数の第1の配線を覆うように、第1の絶縁膜を形成する工程と、

前記第1の絶縁膜をマスクとして、前記基板の第1の領域の主面に第1のイオン注入を施す工程と、

前記第1の積層体の側壁を覆い、かつ、前記複数の第1の配線間を埋設するように、前記第1の絶縁膜とは異なる絶縁膜であって、酸化アルミニウムを主体とする第2の絶縁膜を形成する工程と、

前記第2の絶縁膜をマスクとして、前記基板の第1の領域の主面に第2のイオン注入を施す工程と、

前記第1の絶縁膜に対して選択的に、前記第2の絶縁膜を除去する工程と、

を有することを特徴とする半導体装置の製造方法。

【請求項2】

前記ゲート絶縁膜を形成する工程では、酸化シリコンを主体とする絶縁膜よりも誘電率が高い絶縁膜を形成することを特徴とする請求項1に記載の半導体装置の製造方法。

【請求項3】

前記ゲート電極を形成する工程では、窒化チタンを主体とする金属膜と、不純物を含む導電性の多結晶シリコンを主体とする導電膜とをこの順に形成することを特徴とする請求項1または2に記載の半導体装置の製造方法。

【請求項4】

前記第1の絶縁膜を形成する工程では、窒化シリコンを主体とする絶縁膜を形成することを特徴とする請求項1乃至3のいずれか1項に記載の半導体装置の製造方法。

【請求項5】

前記第2の絶縁膜を除去する工程では、ウェットエッチングにより前記第2の絶縁膜を除去することを特徴とする請求項1乃至4のいずれか1項に記載の半導体装置の製造方法。

【請求項6】

前記第2の絶縁膜を除去する工程の後、

前記基板の主面を覆うように、酸化シリコンを主体とする層間絶縁膜を形成する工程と、

前記層間絶縁膜を形成した後の前記基板に熱処理を施す工程と、

を更に有することを特徴とする請求項1乃至5のいずれか1項に記載の半導体装置の製造方法。

【請求項7】

前記層間絶縁膜を形成する工程の後、

前記層間絶縁膜をその表面から、前記複数の第1の配線間に位置する前記基板の主面までを貫通するように、前記層間絶縁膜に接続孔を形成する工程を更に有することを特徴とする請求項6に記載の半導体装置の製造方法。

【請求項8】

前記基板に前記第1の導体膜を形成する工程の前に、

前記基板の第2の領域に、溝型のゲート電極を備えた電界効果トランジスタを形成する工程を更に有し、

前記層間絶縁膜に前記接続孔を形成する工程の後に、

前記接続孔を導電膜で埋め込んで接続プラグを形成する工程と、

前記接続プラグに電気的に接続するキャパシタを形成する工程と、を更に有し、

前記接続孔を形成する工程では、前記層間絶縁膜をその表面から、前記複数の第1の配線間に位置する前記基板の主面であって、前記電界効果トランジスタのソースまたはドレイン領域である前記基板の主面までを貫通するように形成することを特徴とする請求項7に記載の半導体装置の製造方法。

【請求項9】

前記第1のイオン注入を施す工程と、前記第2のイオン注入を施す工程とでは、互いに同じ導電型となる不純物イオンを注入し、

前記第2のイオン注入を施す工程では、前記第1のイオン注入を施す工程よりも高い濃度の前記不純物イオンを注入し、

前記第1のイオン注入を施す工程では前記第1の積層体の側方下部の前記基板にLDD領域を形成し、

前記第2のイオン注入を施す工程では前記第1の積層体の側方下部の前記基板にソース/ドレイン領域を形成し、

前記第1の領域には、前記ゲート絶縁膜、前記ゲート電極、前記LDD領域、および、前記ソース/ドレイン領域を有する第1の電界効果トランジスタを形成することを特徴とする請求項1乃至8のいずれか1項に記載の半導体装置の製造方法。

【請求項10】

前記第1の導体膜を形成する工程では、不純物を含む導電性の多結晶シリコンを主体とする導電膜と、窒化タングステンを主体とする導電膜と、タングステンを主体とする導電膜とをこの順に形成することを特徴とする請求項1乃至9のいずれか1項に記載の半導体装置の製造方法。

【請求項11】

前記第2の絶縁膜を形成する工程では、前記酸化アルミニウムを主体とする絶縁膜と、酸化シリコンを主体とする絶縁膜とをこの順に積層した絶縁膜を形成することを特徴とする請求項1乃至10のいずれか1項に記載の半導体装置の製造方法。

【請求項12】

基板と、

前記基板の第1の領域の主面上に順に形成されたゲート絶縁膜、ゲート電極、および第1の導体膜からなる第1の積層体と、

前記第1の積層体の側壁を覆う第1の絶縁膜と、

前記第1の積層体の側壁を覆い、かつ、前記第1の絶縁膜とは異なる絶縁膜であって、酸化アルミニウムを主体とする第2の絶縁膜と、

前記第1の積層体の両側の側方下部の基板内に設けられたLDD領域およびソース/ドレイン領域と、

前記基板の第2の領域の主面上に形成された、第1の導体膜からなる複数の第1の配線と、

を有することを特徴とする半導体装置。

【請求項13】

前記ゲート絶縁膜は、酸化シリコンを主体とする絶縁膜よりも誘電率が高い絶縁膜を有することを特徴とする請求項12に記載の半導体装置。

【請求項14】

前記ゲート電極は前記基板の主面側から順に、窒化チタンを主体とする金属膜と、不純物を含む導電性の多結晶シリコンを主体とする導電膜とを有することを特徴とする請求項12または13に記載の半導体装置。

【請求項15】

前記第1の絶縁膜は、窒化シリコンを主体とする絶縁膜であることを特徴とする請求項12乃至14のいずれか1項に記載の半導体装置。

【請求項16】

前記基板の第2の領域は、

溝型のゲート電極を備えた電界効果トランジスタと、

前記複数の第1の配線間に位置する前記基板の主面であって、前記電界効果トランジスタのソースまたはドレイン領域である前記基板の主面に電気的に接続された接続プラグと、

前記接続プラグに電気的に接続されたキャパシタと、

を更に有することを特徴とする請求項12乃至15のいずれか1項に記載の半導体装置。

【請求項17】

前記第1の導体膜は前記基板の主面側から順に、不純物を含む導電性の多結晶シリコンを主体とする導電膜と、窒化タングステンを主体とする導電膜と、タングステンを主体とする導電膜とを有することを特徴とする請求項12乃至16のいずれか1項に記載の半導体装置。

【請求項18】

前記第2の絶縁膜は、前記第1の積層体の側壁上に順に形成された酸化アルミニウムを主体とする絶縁膜と、酸化シリコンを主体とする絶縁膜とを有することを特徴とする請求項12乃至17のいずれか1項に記載の半導体装置。

【請求項1】

基板の第1の領域の主面に、ゲート絶縁膜を形成する工程と、

前記ゲート絶縁膜を覆うゲート電極を形成する工程と、

前記基板の第1の領域では前記ゲート電極を覆い、前記第1の領域と異なる第2の領域では前記基板の主面を覆うように、前記基板に第1の導体膜を形成する工程と、

前記第1の導体膜、前記ゲート電極および前記ゲート絶縁膜を加工して、前記第1の領域には前記第1の導体膜、前記ゲート電極および前記ゲート絶縁膜からなる第1の積層体を形成し、前記第2の領域には前記第1の導体膜からなる複数の第1の配線を形成する工程と、

前記第1の積層体の側壁を覆い、かつ、前記複数の第1の配線を覆うように、第1の絶縁膜を形成する工程と、

前記第1の絶縁膜をマスクとして、前記基板の第1の領域の主面に第1のイオン注入を施す工程と、

前記第1の積層体の側壁を覆い、かつ、前記複数の第1の配線間を埋設するように、前記第1の絶縁膜とは異なる絶縁膜であって、酸化アルミニウムを主体とする第2の絶縁膜を形成する工程と、

前記第2の絶縁膜をマスクとして、前記基板の第1の領域の主面に第2のイオン注入を施す工程と、

前記第1の絶縁膜に対して選択的に、前記第2の絶縁膜を除去する工程と、

を有することを特徴とする半導体装置の製造方法。

【請求項2】

前記ゲート絶縁膜を形成する工程では、酸化シリコンを主体とする絶縁膜よりも誘電率が高い絶縁膜を形成することを特徴とする請求項1に記載の半導体装置の製造方法。

【請求項3】

前記ゲート電極を形成する工程では、窒化チタンを主体とする金属膜と、不純物を含む導電性の多結晶シリコンを主体とする導電膜とをこの順に形成することを特徴とする請求項1または2に記載の半導体装置の製造方法。

【請求項4】

前記第1の絶縁膜を形成する工程では、窒化シリコンを主体とする絶縁膜を形成することを特徴とする請求項1乃至3のいずれか1項に記載の半導体装置の製造方法。

【請求項5】

前記第2の絶縁膜を除去する工程では、ウェットエッチングにより前記第2の絶縁膜を除去することを特徴とする請求項1乃至4のいずれか1項に記載の半導体装置の製造方法。

【請求項6】

前記第2の絶縁膜を除去する工程の後、

前記基板の主面を覆うように、酸化シリコンを主体とする層間絶縁膜を形成する工程と、

前記層間絶縁膜を形成した後の前記基板に熱処理を施す工程と、

を更に有することを特徴とする請求項1乃至5のいずれか1項に記載の半導体装置の製造方法。

【請求項7】

前記層間絶縁膜を形成する工程の後、

前記層間絶縁膜をその表面から、前記複数の第1の配線間に位置する前記基板の主面までを貫通するように、前記層間絶縁膜に接続孔を形成する工程を更に有することを特徴とする請求項6に記載の半導体装置の製造方法。

【請求項8】

前記基板に前記第1の導体膜を形成する工程の前に、

前記基板の第2の領域に、溝型のゲート電極を備えた電界効果トランジスタを形成する工程を更に有し、

前記層間絶縁膜に前記接続孔を形成する工程の後に、

前記接続孔を導電膜で埋め込んで接続プラグを形成する工程と、

前記接続プラグに電気的に接続するキャパシタを形成する工程と、を更に有し、

前記接続孔を形成する工程では、前記層間絶縁膜をその表面から、前記複数の第1の配線間に位置する前記基板の主面であって、前記電界効果トランジスタのソースまたはドレイン領域である前記基板の主面までを貫通するように形成することを特徴とする請求項7に記載の半導体装置の製造方法。

【請求項9】

前記第1のイオン注入を施す工程と、前記第2のイオン注入を施す工程とでは、互いに同じ導電型となる不純物イオンを注入し、

前記第2のイオン注入を施す工程では、前記第1のイオン注入を施す工程よりも高い濃度の前記不純物イオンを注入し、

前記第1のイオン注入を施す工程では前記第1の積層体の側方下部の前記基板にLDD領域を形成し、

前記第2のイオン注入を施す工程では前記第1の積層体の側方下部の前記基板にソース/ドレイン領域を形成し、

前記第1の領域には、前記ゲート絶縁膜、前記ゲート電極、前記LDD領域、および、前記ソース/ドレイン領域を有する第1の電界効果トランジスタを形成することを特徴とする請求項1乃至8のいずれか1項に記載の半導体装置の製造方法。

【請求項10】

前記第1の導体膜を形成する工程では、不純物を含む導電性の多結晶シリコンを主体とする導電膜と、窒化タングステンを主体とする導電膜と、タングステンを主体とする導電膜とをこの順に形成することを特徴とする請求項1乃至9のいずれか1項に記載の半導体装置の製造方法。

【請求項11】

前記第2の絶縁膜を形成する工程では、前記酸化アルミニウムを主体とする絶縁膜と、酸化シリコンを主体とする絶縁膜とをこの順に積層した絶縁膜を形成することを特徴とする請求項1乃至10のいずれか1項に記載の半導体装置の製造方法。

【請求項12】

基板と、

前記基板の第1の領域の主面上に順に形成されたゲート絶縁膜、ゲート電極、および第1の導体膜からなる第1の積層体と、

前記第1の積層体の側壁を覆う第1の絶縁膜と、

前記第1の積層体の側壁を覆い、かつ、前記第1の絶縁膜とは異なる絶縁膜であって、酸化アルミニウムを主体とする第2の絶縁膜と、

前記第1の積層体の両側の側方下部の基板内に設けられたLDD領域およびソース/ドレイン領域と、

前記基板の第2の領域の主面上に形成された、第1の導体膜からなる複数の第1の配線と、

を有することを特徴とする半導体装置。

【請求項13】

前記ゲート絶縁膜は、酸化シリコンを主体とする絶縁膜よりも誘電率が高い絶縁膜を有することを特徴とする請求項12に記載の半導体装置。

【請求項14】

前記ゲート電極は前記基板の主面側から順に、窒化チタンを主体とする金属膜と、不純物を含む導電性の多結晶シリコンを主体とする導電膜とを有することを特徴とする請求項12または13に記載の半導体装置。

【請求項15】

前記第1の絶縁膜は、窒化シリコンを主体とする絶縁膜であることを特徴とする請求項12乃至14のいずれか1項に記載の半導体装置。

【請求項16】

前記基板の第2の領域は、

溝型のゲート電極を備えた電界効果トランジスタと、

前記複数の第1の配線間に位置する前記基板の主面であって、前記電界効果トランジスタのソースまたはドレイン領域である前記基板の主面に電気的に接続された接続プラグと、

前記接続プラグに電気的に接続されたキャパシタと、

を更に有することを特徴とする請求項12乃至15のいずれか1項に記載の半導体装置。

【請求項17】

前記第1の導体膜は前記基板の主面側から順に、不純物を含む導電性の多結晶シリコンを主体とする導電膜と、窒化タングステンを主体とする導電膜と、タングステンを主体とする導電膜とを有することを特徴とする請求項12乃至16のいずれか1項に記載の半導体装置。

【請求項18】

前記第2の絶縁膜は、前記第1の積層体の側壁上に順に形成された酸化アルミニウムを主体とする絶縁膜と、酸化シリコンを主体とする絶縁膜とを有することを特徴とする請求項12乃至17のいずれか1項に記載の半導体装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【公開番号】特開2013−26494(P2013−26494A)

【公開日】平成25年2月4日(2013.2.4)

【国際特許分類】

【出願番号】特願2011−160791(P2011−160791)

【出願日】平成23年7月22日(2011.7.22)

【出願人】(500174247)エルピーダメモリ株式会社 (2,599)

【Fターム(参考)】

【公開日】平成25年2月4日(2013.2.4)

【国際特許分類】

【出願日】平成23年7月22日(2011.7.22)

【出願人】(500174247)エルピーダメモリ株式会社 (2,599)

【Fターム(参考)】

[ Back to top ]