半導体装置およびその製造方法

【課題】シリコン基板表面に到達する深い溝部であっても、所望の保護溝部形成を安定して行うことができる半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、活性素子が形成された素子領域を有する基板と、前記基板上に形成され、多層配線構造を含む積層体と、前記積層体中に、前記素子領域を囲んで連続的に延在する耐湿リングと、前記積層体中、前記耐湿リングの外側に、前記耐湿リングに沿って連続的に、前記基板の表面に達して形成された保護溝部と、前記積層体上に形成され、前記保護溝部の外縁に沿って延在する第1のマスクパターンと、前記積層体上に形成され、前記保護溝部の内縁に沿って延在する第2の金属マスクパターンと、を有する。

【解決手段】半導体装置は、活性素子が形成された素子領域を有する基板と、前記基板上に形成され、多層配線構造を含む積層体と、前記積層体中に、前記素子領域を囲んで連続的に延在する耐湿リングと、前記積層体中、前記耐湿リングの外側に、前記耐湿リングに沿って連続的に、前記基板の表面に達して形成された保護溝部と、前記積層体上に形成され、前記保護溝部の外縁に沿って延在する第1のマスクパターンと、前記積層体上に形成され、前記保護溝部の内縁に沿って延在する第2の金属マスクパターンと、を有する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は一般に半導体装置に係り、特に耐湿リングを有する半導体装置およびその製造方法に関する。

【背景技術】

【0002】

一般に半導体装置の製造技術では、シリコンウェハなどの半導体基板上に半導体素子を多数、行列状に形成し、さらにかかる半導体基板をスクライブラインに沿って切断することにより、個々の半導体素子が形成された半導体チップを、半導体装置として得ている。

【0003】

このような半導体チップでは、その切断面において半導体装置を構成する半導体層や絶縁層、金属層などが露出されるため、かかる切断面を介した大気中の水分の半導体装置中への侵入を抑制するため、その周辺部に、半導体装置中の多層配線構造と同じ層構造の耐湿リングが形成されるのが一般的である。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2004−47575号公報

【特許文献2】特開2004−134450号公報

【特許文献3】特開2004−79596号公報

【特許文献4】特開2003−273043号公報

【特許文献5】特開2004−119468号公報

【特許文献6】特開2005−217411号公報

【特許文献7】特開2005−260059号公報

【特許文献8】特開2004−296904号公報

【特許文献9】特開2006−114723号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

図1は、シリコン基板11上に形成された本発明の関連技術による半導体素子の一部を示す平面図、図2はかかる半導体素子の、耐湿リングを含む部分断面図を示す。

【0006】

図1を参照するに、シリコン基板11上には素子領域11A,11B,11C,11Dが、一点鎖線で示したスクライブラインにより画成されており、各々の素子領域11A,11B,11C,11Dは、耐湿リング12A,12B,12C,12Dの内側に、それぞれの半導体素子を構成する回路領域13を含んでいる。図示の例では、素子領域11Aに回路領域13が形成されているが、同様な回路領域は、他の素子領域11B〜11Dのいずれにも形成されている。

【0007】

さらに図1の構成では、前記素子領域11A〜11Dの各々には、対応する耐湿リング12A〜12Dの外側で、かつ一点鎖線で示したスクライブラインの内側に、スクライブ時のクラック伝播を遮断するため、保護溝部14A〜14Dのいずれかが形成されている。

【0008】

そこで、図1の平面図において、前記一点鎖線で示したスクライブラインに沿ってシリコン基板11を切断することにより、個々の半導体装置が、半導体チップの形で分離される。

【0009】

図2は、このようにして得られた半導体装置10の断面図を示す。

【0010】

図2を参照するに、前記半導体素子10は、素子分離領域15Iおよびトランジスタ15Trが形成されたシリコン基板15上に形成されており、前記トランジスタ15TrはSiN膜17Aにより覆われており、前記シリコン基板15上には、前記トランジスタ15TrおよびSiN膜17Aを覆って、各々シリコン酸化膜よりなる層間絶縁膜16A,16B,・・・16Gを、間にシリコン窒化膜17B,17C・・・17Fを交互に挟んで積層した構成の多層配線構造が形成されている。

【0011】

図示の例では、前記層間絶縁膜16A中にはWなどよりなるビアパターン16aRが前記耐湿リング12Aに対応して、前記シリコン基板15の表面にコンタクトして連続的に形成されており、また前記回路領域13にビアプラグ16aが、前記トランジスタ15Trの拡散領域15a,15bを覆うシリサイド層15c,15dにコンタクトして形成されている。

【0012】

さらに前記層間絶縁膜16B中にはCuパターン16bRが前記耐湿リング12Aに対応して、前記ビアパターン16aRにコンタクトしてシングルダマシン法により、連続的に形成されており、また前記回路領域13にはCu配線パターン16bが、前記Wビアパターン16aRにコンタクトして、やはりシングルダマシン法により形成されている。

【0013】

さらに前記層間絶縁膜16C中にはCuパターン16cRが前記耐湿リング12Aに対応して、その下の前記Cuパターン16bRにコンタクトしてシングルまたはデュアルダマシン法により連続的に形成されており、また前記回路領域13にはビアプラグを有するCu配線パターン16cが、前記Cu配線パターン16bにコンタクトして、やはりシングルまたはデュアルダマシン法により形成されている。

【0014】

さらに前記層間絶縁膜16D中にはCuパターン16dRが前記耐湿リング12Aに対応して、その下の前記Cuパターン16cRにコンタクトして、シングルまたはデュアルダマシン法により連続的に形成されており、また前記回路領域13にはビアプラグを有するCu配線パターン16dが、前記Cu配線パターン16cにコンタクトして、やはりシングルまたはデュアルダマシン法により形成されている。

【0015】

さらに前記層間絶縁膜16E中にはCuパターン16eRが前記耐湿リング12Aに対応して、その下の前記Cuパターン(図示せず)にコンタクトしてデュアルダマシン法により連続的に形成されており、また前記回路領域13にはビアプラグを有するCu配線パターン16eが、前記Cu配線パターン(図示せず)にコンタクトして、やはりデュアルダマシン法により形成されている。

【0016】

さらに前記層間絶縁膜16F中にはCuパターン16fRが前記耐湿リング12Aに対応して、その下の前記Cuパターン16eRにコンタクトしてデュアルダマシン法により連続的に形成されており、また前記回路領域13にはビアプラグを有するCu配線パターン16fRが、その下の対応するCu配線パターン16eにコンタクトして、やはりデュアルダマシン法により形成されている。

【0017】

さらに前記層間絶縁膜16G中にはWパターン16gRが前記耐湿リング12Aに対応して、その下の前記Cuパターン16fRにコンタクトしてダマシン法により連続的に形成されており、また前記回路領域13にWビアプラグ16gが、前記Cu配線パターン16fにコンタクトして、やはりダマシン法により形成されている。

【0018】

ここで、前記Cu配線パターン16b〜16fおよびCuパターン16bR〜16fRは、Taなどのバリアメタル膜により覆われており、また前記Wビアプラグ16a,16gおよびWパターン16aR,16gRは、TiNなどのバリア膜により覆われていることに注意すべきである。

【0019】

さらに前記層間絶縁膜16G上には、前記耐湿リングに対応してTi/TiN構造の密着膜により挟持されたAlパターン18Aが、前記Wパターン16gRにコンタクトして形成され、また前記ビアプラグ16g上に、同様な構造のパッド電極18Bが、前記ビアプラグ16gにコンタクトして形成されている。

【0020】

さらに前記Alパターン18Aおよびパッド電極18Bは、前記層間絶縁膜16G上において高密度プラズマCVD法により堆積されたシリコン酸化膜18により覆われ、さらにその上に、SiN膜よりなるパッシベーション膜19が形成されている。前記パッシベーション膜19およびシリコン酸化膜18中には、前記パッド電極18Bを露出する開口部19Aが形成される。

【0021】

図2の構成では、矢印で示すように図中左側端部においてダイシングソーによるスクライブが行われるが、その際のクラック伝播を阻止するため、前記耐湿リングの外側には、先に図1で説明した保護溝部14Aが形成されている。

【0022】

一方、図2の構成の半導体装置では、図中左側端部が大気曝露されるため、図3に示すように、層間絶縁膜16A〜16Fのうち、耐湿リング12Aの外側の部分には水分が侵入するが、このような水分の、回路領域13への侵入は前記耐湿リング12が阻止しており、このため耐湿リング12の負荷が大きく、腐食しやすい問題を有している。耐湿リング12の一部に欠陥が発生すると、水分はその部分を伝って、半導体装置内部に侵入する。図3では、破線で囲んだ、耐湿リング12Aを構成するCuパターン16cRに、このような欠陥が生じている。

【0023】

このような耐湿リング12の負荷の問題は、特に層間絶縁膜16A〜16Fとして、密度の低い低誘電率膜、いわゆるLow−K膜を使った場合に特に顕著となる。

【0024】

図4は、このような耐湿リングの負荷を軽減する、本発明の関連技術による半導体装置の構成を示す。ただし図5中、先に説明した部分には同一の参照符号を付し、説明を省略する。

【0025】

図4を参照するに、図4の構成では、前記保護溝部14Aがシリコン基板15の表面まで到達するように深く形成され、さらにその表面を覆ってSiNパッシベーション膜19が連続して形成されている。

【0026】

その結果、前記層間絶縁膜16A〜16F、および層間絶縁膜16Gは、それぞれの端部が連続してSiNパッシベーション膜により覆われており、前記耐湿リングへの負荷は実質的に軽減され、半導体装置の信頼性が向上すると期待される。

【0027】

しかし、前記図4の構造を形成しようとすると、層間絶縁膜16A〜16Gよりなる積層体中に深い溝14Aを形成する必要があり、特にレジストパターンをマスクにパターニングを行う場合、パターニング精度に問題が生じることがある。

【0028】

また前記SiNパッシベーション膜19は、応力を蓄積した膜であり、特に前記層間絶縁膜16A〜16Fが低誘電率膜である場合、密着力が低下し、剥離しやすい問題が生じる。

【0029】

かかるパッシベーション膜19を、高密度プラズマCVD法により形成されたシリコン酸化膜により形成することも考えられようが、特に前記層間絶縁膜16A〜16Fが有機系の低誘電率膜、あるいは有機基を多く含む低誘電率膜の場合、成膜時の酸素雰囲気により前記層間絶縁膜が侵食される恐れがあり、かかる手法を適用することは困難であると考えられる。

【0030】

さらに図4の構成では、前記パッシベーション膜19が応力を蓄積したSiN膜より構成される場合、スクライブ時の破断が前記パッシベーション膜19を伝って、耐湿リング12Aより内側の回路領域13に到達し、半導体装置の信頼性を低下させる恐れがある。

【課題を解決するための手段】

【0031】

一の側面によれば半導体装置は、活性素子が形成された素子領域を有する基板と、前記基板上に形成され、多層配線構造を含む積層体と、前記積層体中に、前記素子領域を囲んで連続的に延在する耐湿リングと、前記積層体中、前記耐湿リングの外側に、前記耐湿リングに沿って連続的に、前記基板の表面に達して形成された保護溝部と、前記積層体上に形成され、前記保護溝部の外縁に沿って延在する第1のマスクパターンと、前記積層体上に形成され、前記保護溝部の内縁に沿って延在する第2の金属マスクパターンと、を有する。

【0032】

他の側面によれば半導体装置の製造方法は、活性素子が形成された素子領域を有する基板上に、前記素子領域を囲んで位置する耐湿リングと多層配線構造とを含む積層体と、前記耐湿リングの外側の前記積層体上に、前記耐湿リングを連続して囲んで位置する金属膜と、を形成する工程と、前記金属膜の少なくとも一部及び前記金属膜の下の前記積層体を除去して、前記耐湿リングを囲んで位置し、前記基板に達する保護溝部を形成する工程と、を有する。

【発明の効果】

【0033】

本発明によれば、基板上に多層配線構造を構成する積層体を有する半導体装置において、耐湿リングの外側に、基板面に到達して形成される深い保護溝部を形成することにより、前記耐湿リング内側の半導体装置主要部をダイシング時のクラックから保護することができる。その際、かかる保護溝部の少なくとも内壁面を保護膜により覆うことにより、かかる保護溝部側壁面からの半導体素子中への水分の侵入を阻止することができる。

【0034】

特にかかる多層配線構造が、低誘電率層間絶縁膜の積層により構成される場合、保護膜形成時に前記保護溝部側壁面において露出している層間絶縁膜端面が侵食される恐れがあるが、本発明によれば、かかる側壁面をSiとCを主成分とする界面膜により覆うことにより、かかる保護膜形成時の溝部側壁面の侵食の問題を回避することが可能となる。

【0035】

また本発明によれば、前記保護溝部を前記積層体中に形成する場合、前記積層体表面に形成された金属パターンをハードマスクとして保護溝部形成を行うことにより、シリコン基板表面に到達する深い溝部であっても、所望の保護溝部形成を安定して行うことができる。

【0036】

さらに本発明によれば、前記保護膜を、前記保護溝部の外側側壁面あるいは保護溝部の外側において除去することにより、前記半導体装置をスクライブ工程により切り離す場合にも、クラックが、歪みを蓄積した保護膜を伝播して半導体装置内部に侵入するのが抑制され、半導体装置の製造歩留まりを向上させることが可能となる。

【図面の簡単な説明】

【0037】

【図1】本発明の関連技術による半導体ウェハ表面の一部を示す平面図である。

【図2】本発明の関連技術による半導体装置の一部を示す断面図である。

【図3】本発明の他の関連技術による半導体装置の一部を示す断面図である。

【図4】本発明の他の関連技術による半導体装置の一部を示す断面図である。

【図5】本発明の第1の実施形態による半導体装置の構成を示す断面図である。

【図6A】図5の半導体装置の製造工程を説明する図(その1)である。

【図6B】図5の半導体装置の製造工程を説明する図(その2)である。

【図6C】図5の半導体装置の製造工程を説明する図(その3)である。

【図6D】図5の半導体装置の製造工程を説明する図(その4)である。

【図6E】図5の半導体装置の製造工程を説明する図(その5)である。

【図6F】図5の半導体装置の製造工程を説明する図(その6)である。

【図7】図5の半導体装置の一変形例を示す断面図である。

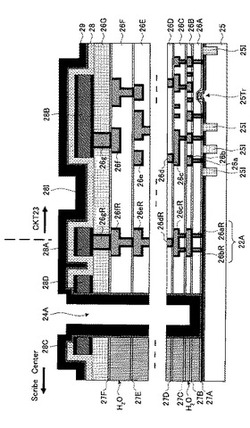

【図8A】本発明の第2の実施形態による半導体装置の製造工程を説明する図(その1)である。

【図8B】本発明の第2の実施形態による半導体装置の製造工程を説明する図(その2)である。

【図8C】本発明の第2の実施形態による半導体装置の製造工程を説明する図(その3)である。

【図9】本発明の第2の実施形態の一変形例を示す図である。

【図10】本発明の第2の実施形態の他の変形例を示す図である。

【図11】本発明の第3の実施形態による半導体装置の構成を示す図である。

【図12】図11の半導体装置の一変形例を示す図である。

【図13】図11の半導体装置の一変形例を示す図である。

【図14】本発明の第4の実施形態による半導体装置の構成を示す図である。

【図15】図14の半導体装置の一変形例を示す図である。

【図16】本発明の第5の実施形態による半導体装置の構成を示す図である。

【発明を実施するための形態】

【0038】

図5は、本発明の第1の実施形態による半導体装置20の構成を示す。

【0039】

図5を参照するに、前記半導体装置20は、素子分離領域25Iおよびトランジスタ25Trが形成されたシリコン基板25上に形成されており、前記トランジスタ25TrはSiN膜27Aにより覆われており、前記シリコン基板25上には、前記トランジスタ15TrおよびSiN膜27Aを覆って、層間絶縁膜26A,26B,・・・,26Gを、間にSiNあるいはSiCよりなるエッチングストッパ膜27B,27C・・・27Fを交互に挟んで積層した構成の、多層配線構造を含む積層体が形成されている。

【0040】

図示の例では、前記層間絶縁膜26A中にはWなどよりなるビアパターン26aRが耐湿リング22Aに対応して、前記シリコン基板25の表面にコンタクトして連続的に形成されており、また前記耐湿リング22Aで囲まれた回路領域23に、ビアプラグ26aが、前記トランジスタ25Trの拡散領域25a,25bを覆うシリサイド層25c,25dにコンタクトして形成されている。

【0041】

さらに前記層間絶縁膜26B中にはCuパターン26bRが前記耐湿リング22Aに対応して、前記ビアパターン26aRにコンタクトしてシングルダマシン法により、連続的に形成されており、また前記回路領域23にはCu配線パターン26bが、前記Wビアパターン26aにコンタクトして、やはりシングルダマシン法により形成されている。

【0042】

さらに前記層間絶縁膜26C中にはCuパターン26cRが前記耐湿リング22Aに対応して、その下の前記Cuパターン26bRにコンタクトしてデュアルダマシン法により連続的に形成されており、また前記回路領域23にはビアプラグを有するCu配線パターン26cが、前記Cu配線パターン26bにコンタクトして、やはりシングル又はデュアルダマシン法により形成されている。

【0043】

さらに前記層間絶縁膜26D中にはCuパターン26dRが前記耐湿リング12Aに対応して、その下の前記Cuパターン26cRにコンタクトして、シングルまたはデュアルダマシン法により連続的に形成されており、また前記回路領域23にはビアプラグを有するCu配線パターン26dが、前記Cu配線パターン26cにコンタクトして、やはりデュアルダマシン法により形成されている。

【0044】

さらに前記層間絶縁膜26E中にはCuパターン26eRが前記耐湿リング22Aに対応して、その下の前記Cuパターン(図示せず)にコンタクトしてデュアルダマシン法により連続的に形成されており、また前記回路領域23にはビアプラグを有するCu配線パターン26eが、前記Cu配線パターン(図示せず)にコンタクトして、やはりデュアルダマシン法により形成されている。

【0045】

さらに前記層間絶縁膜26F中にはCuパターン26fRが前記耐湿リング22Aに対応して、その下の前記Cuパターン26eRにコンタクトしてデュアルダマシン法により連続的に形成されており、また前記回路領域23にはビアプラグを有するCu配線パターン26fが、その下の対応するCu配線パターン26eにコンタクトして、やはりデュアルダマシン法により形成されている。

【0046】

さらに前記層間絶縁膜26G中にはWパターン26gRが前記耐湿リング22Aに対応して、その下の前記Cuパターン26fRにコンタクトしてダマシン法により連続的に形成されており、また前記回路領域23にはWビアプラグ26gが、前記Cu配線パターン26fにコンタクトして、やはりダマシン法により形成されている。

【0047】

ここで、前記Cu配線パターン26b〜26fおよびCuパターン26bR〜26fRは、Ta膜あるいはTa/TaN積層膜などのバリアメタル膜により覆われており、また前記Wビアプラグ26a,26gおよびWパターン26aR,26gRは、TiNなどのバリア膜により覆われていることに注意すべきである。

【0048】

さらに前記層間絶縁膜26G上には、前記耐湿リングに対応してTi/TiN構造の密着膜により挟持されたAlパターン28Aが、前記Wパターン26gRにコンタクトして形成され、また前記ビアプラグ26g上に、同様な構造のパッド電極28Bが、前記ビアプラグ26gにコンタクトして形成されている。図示の例では、前記層間絶縁膜26Gは、シリコン酸化膜より形成されている。

【0049】

さらに前記Alパターン28Aおよびパッド電極28Bは、前記層間絶縁膜26G上において高密度プラズマCVD法により堆積されたシリコン酸化膜28により覆われ、さらにその上に、SiN膜よりなるパッシベーション膜29が、例えばプラズマCVD法により形成されている。前記パッシベーション膜29およびシリコン酸化膜28中には、前記パッド電極28Bを露出する開口部29Aが形成される。

【0050】

前記層間絶縁膜26A〜26Fとしては、登録商標FlareやSiLKなどの名称で市販の炭化水素系絶縁膜、有機あるいは無機シロキサン膜、あるいはこれらの多孔質膜を使うことができる。これらの層間絶縁膜は、プラズマCVD法あるいは塗布法により形成できる。前記層間絶縁膜26A〜26Dは、例えば200〜400nm程度の膜厚に形成され、前記層間絶縁膜26E,26Fは、例えば400〜600nm程度の膜厚に形成される。

【0051】

その際、本実施形態では、前記積層体中、前記耐湿リング22Aの外側に、前記シリコン基板25の表面に到達する保護溝部24Aが、先の図1の保護溝部14Aと同様に、前記耐湿リング22Aに沿って連続的に形成されており、前記シリコン酸化膜28およびパッシベーション膜29は、かかる保護溝部24Aの内壁面、底面および外壁面を連続して覆っている。

【0052】

また前記保護溝部24Aは、前記層間絶縁膜26A〜26Gを積層した積層体を、レジストパターンをマスクとしたドライエッチングを、前記シリコン基板25の表面が露出するまで実行することにより、形成される。

【0053】

さらに本実施形態では、前記シリコン酸化膜28と前記保護溝部24Aの内壁面、底面および外壁面の間に、SiC界面膜28Iが、プラズマCVD法により、5〜200nmの膜厚に形成されている。

【0054】

かかる界面膜28Iを形成することにより、前記シリコン酸化膜28を前記保護溝部24Aの内壁面、底面および外壁面に形成する際に、前記内壁面あるいは外壁面に露出されている低誘電率層間絶縁膜26A〜26Fの損傷を抑制することができる。

【0055】

なお前記界面膜28Iとしては、組成がSiCの膜に限定されることはなく、SiとCを主成分とする、例えばSiCH膜やSiOC膜、SiOCH膜などであっても、界面膜の成膜時に前記低誘電率層間絶縁膜26A〜26Fの損傷を抑制できるものであれば、使うことができる。

【0056】

前記界面膜28IをSiC膜より形成する場合には、例えば原料としてテトラメチルシランを供給し、これを350〜400℃の基板温度においてプラズマ励起するプラズマCVD法により形成することができる。

【0057】

このように、本実施形態によれば、前記保護溝部24Aの表面、すなわち内側側壁面、底面および外側側壁面、に高密度プラズマCVD法により前記シリコン酸化膜28を形成するに先立って、前記保護溝部24Aの表面を界面膜28Iにより連続して覆うことにより、前記シリコン酸化膜28形成時における前記保護溝部24A表面の酸素ラジカルおよびイオンによる損傷が抑制される。前記界面膜28Iの形成は、酸素の少ない条件で行われるため、前記層間絶縁膜26A〜26Fの前記保護溝部24Aにおける露出端面の損傷は実質的に生じない。

【0058】

また、かかるシリコン酸化膜28をSiNパッシベーション膜29の直下に形成することにより、応力を蓄積しやすいSiNパッシベーション膜29の剥離を抑制することが可能となる。

【0059】

図示の例では、図中、左端がスクライブされており、端面が大気露出しているが、大気中の水分は主に前記保護溝部24Aにおいて前記SiNパッシベーション膜29により阻止され、耐湿リング22Aの負荷が大きく軽減される。

【0060】

以下、図6A〜6Gを参照しながら、前記半導体装置20の製造工程を説明する。

【0061】

図6Aを参照するに、活性素子25Trが形成されたシリコン基板25上には、前記層間絶縁膜26A〜26Gを積層した積層体が形成されており、前記積層体中には、前記耐湿リング22Aに対応して、WあるいはCuパターン26aR〜26gRを積層した構造が形成され、最上部にAlパターン28Aが形成されている。また前記積層体中には、前記回路領域23中の多層配線構造に対応して、WあるいはCuパターン26a〜26gを積層した構造が形成され、図6Bの工程において、前記耐湿リング22Aの外側に、前記シリコン基板25を露出するように、保護溝部24Aが、CF系ガスおよびO2,Ar等の混合ガスをエッチングガスとしたドライエッチングにより、形成される。図6Bの工程において前記ドライエッチング工程は、前記積層体表面のうち、前記保護溝部24Aの形成領域を除き、レジストマスクにより保護した状態で実行される。

【0062】

前記図6Bの工程では、前記保護溝部24Aの形成に伴って前記層間絶縁膜26A〜26Fが前記保護溝部24Aにおいて大気曝露され、前記層間絶縁膜26A〜26Fは、スクライブ前の状態であるにもかかわらず、前記耐湿リング22Aの外側において吸湿するが、図6Cの工程において、前記図6Bの構造は脱水処理され、さらに前記図6Bの構造上に前記SiC膜28Iが、先に説明したプラズマCVD法により、先に説明した膜厚で形成される。前記SiC膜28Iの膜厚が5nm以下になると、前記SiC膜28Iの界面膜としての効果が得られず、また前記SiC膜28Iの膜厚が200nm以上になると、処理時間が不必要に長くなってしまう。

【0063】

次に図6Dの工程において前記図6Cの構造上に、前記シリコン酸化膜28が、原料としてシランと酸素を使い、700W程度のプラズマパワーで400℃程度の基板温度において、4kW程度の基板バイアスを印加しながら、例えば1200〜1500nmの膜厚に形成され、さらに図6Eの工程において前記図6Dの構造上に、前記SiNパッシベーション膜29が、原料としてシランとアンモニアを使い、400℃程度の基板温度において750W程度のプラズマパワーで、500nmの膜厚に形成される。

【0064】

さらに図6Fの工程において、前記SiNパッシベーション膜29中に、前記電極パッド28Bを露出する開口部29Aが形成される。

【0065】

さらに図6Fの工程の後、図1のスクライブラインに沿って前記シリコンウェハをスクライブすることにより、図5の半導体装置20が得られる。

【0066】

なお、前記SiNパッシベーション膜29に十分な密着性が得られる場合には、前記シリコン酸化膜28を前記保護溝部24Aを形成する前に成膜し、前記保護溝部24Aに対応して基板25に達する溝が形成された後、図7に示すようにSiNパッシベーション膜29を、前記保護溝部24Aにおいて直接に前記界面膜28Iに接して形成することも可能である。

[第2の実施形態]

次に本発明の第2の実施形態を、図8A〜8Cを参照しながら説明する。ただし図8A〜8C中、先に説明した部分に対応する部分には同一の参照符号を付し、説明を省略する。

【0067】

先の実施形態では、図6Bの工程において前記保護溝部24Aをドライエッチングにより形成するのに、レジストプロセスを使っていたが、このように深い保護溝部24Aを形成しようとすると、ドライエッチング時間が長くなり、特に層間絶縁膜の数が多い半導体装置では、レジストパターンが長時間のドライエッチングに耐えられなくなる問題が生じる。

【0068】

本実施形態は、このような多層配線構造中の層間絶縁膜の数が多く、前記保護溝部24Aの形成に長時間を要する場合を想定したものであり、図8Aに示すように、前記最上層のシリコン酸化膜26G上に、前記保護溝部24Aの形成領域を画成するように、Alパターン28Cおよび28Dを、前記Alパターン28Aおよび28Bと同時に、同一のマスクを使って形成し、かかるAlパターン28Cおよび28Dをハードマスクに、前記層間絶縁膜26A〜26Gの積層体を、前記パターン28Cおよび28Dの間においてドライエッチングし、前記保護溝部24Aを形成する。

【0069】

本実施形態では、次に図8Bの工程において前記図8Aの構造を脱水処理後、前記界面膜28Iを、先の図6Cの工程と同様にして形成し、さらに図8Cの工程において、前記パッシベーション膜29が、前記界面膜28I上に、先の図6Eの工程と同様にして形成される。なお図8Cは、さらに半導体装置がスクライブされた状態を示している。

【0070】

かかる構成によれば、先にも説明したように前記保護溝部24Aが安定して形成され、例えば前記保護溝部24Aを形成するドライエッチングプロセスが側方に進行し、耐湿リング22Aを露出してしまうなどの問題を回避することができる。

【0071】

図8A〜8Cでは、SiNパッシベーション膜29が前記界面膜28Iに直接に接している場合を説明したが、本実施形態はかかる特定の場合に限定されるものではなく、前記界面膜28IとSiNパッシベーション膜29の間に高密度プラズマCVD法により形成された、前記シリコン酸化膜28と同様なシリコン酸化膜が介在する場合についても、同様に有効である。

【0072】

このように前記Alパターン28Cおよび28Dを形成しても、マスク枚数が増えることはなく、半導体装置の製造工程が複雑になることはない。

【0073】

図9は、前記図8Aの一変形例を示す。

【0074】

図9を参照するに、本実施形態では前記Alパターン28Aが図8(A)のAlパターン28Dを兼用しており、これにより、図9中、矢印Wで示すように、チップサイズを、図8(A)の場合に比べて減少させることができる。

【0075】

図10は、前記図8Aの別の変形例を示す。

【0076】

図10を参照するに、本実施形態では、前記保護溝部24Aの外側に、CuあるいはWパターン26aP〜26bPの積層よりなる、前記耐湿リング22Aと同様な別の耐湿リング22Bが形成されており、前記Alパターン28Cが、前記耐湿リング22Bの最上部パターンとして形成されている。

【0077】

かかる構成でも、前記Alパターン28Aおよび28Cをマスクとしてドライエッチングを行うことにより、前記保護溝部24Aの形状を正確に制御することが可能となる。

【0078】

このような別の耐湿リング22Bは、前記耐湿リング22Aと同時に形成でき、工程数が増加することはない。また、前記保護溝部24Aより外側に耐湿リングが存在することで、界面伝播するクラックは、かかる追加の耐湿リング構造により、その進行が抑制される。

[第3の実施形態]

図11は、本発明の第3の実施形態による半導体装置40の構成を示す。ただし図中、先に説明した部分に対応する部分には同一の参照符号を付し、説明を省略する。

【0079】

図11を参照するに、本実施形態では、前記SiNパッシベーション膜29が前記保護溝部24Aの内側側壁面および底面を直接に覆っているが、前記パッシベーション膜29のうち、前記溝部24Aの外側側壁面を覆う部分が、前記溝部24Aを形成するのに使われたマスクデータをスクライブライン方向にわずかにずらして形成したマスクパターンを使い、前記溝部24Aを形成するのと同様なドライエッチング工程を行うことにより、除去されている。またかかるドライエッチング工程の結果、図11の例では、前記保護溝部24Aの外側側壁面に、段部24aが形成されている。

【0080】

かかる構成により、前記半導体装置をスクライブ工程により分離する際に、クラックが歪みを蓄積したSiNパッシベーション膜29を使って耐湿リング22A内側の回路領域に侵入するのが阻止される。

【0081】

また、本実施形態では、前記保護溝部22AにおけるSiNパッシベーション膜29の除去工程を、前記パッド電極28Bを露出する開口部29Aの形成工程と同時に行うことにより、マスク枚数の増加を回避することができる。その場合、前記開口部29Aではエッチングは、前記パッド電極22Bが露出した時点で実質的に停止し、保護溝部24Aの外側側壁面においてのみ、エッチングがさらに進行する。

【0082】

図11の例では、前記層間絶縁膜26A〜26Fがシリコン酸化膜よりなり、前記SiNパッシベーション膜29が前記保護溝部24Aにおいて前記層間絶縁膜26A〜26Fと直接に接しているが、先に図5あるいは図7で説明したように、前記層間絶縁膜26A〜26Fが、SiO2よりも比誘電率が低い低誘電率膜である場合、前記保護溝部24Aにおいて前記SiNパッシベーション膜29と保護溝部表面の間にシリコン酸化膜28と界面膜28I、あるいは界面膜28Iを介在させるのが好ましい。

【0083】

図12は、前記図11の一変形例であり、前記保護溝部24Aの外側側壁面の一部に前記SiNパッシベーション膜が残留している場合を示す。

【0084】

本実施形態は、このような場合をも含むものである。

【0085】

さらに図13は、前記図11の他の変形例であり、前記保護溝部24A外側の側壁面をエッチングする際に、SiNパッシベーション膜29の一部が残って突出部を形成した場合を示す。

【0086】

本実施形態は、このような場合をも含むものである。

[第4の実施形態]

図14は、本発明の第4の実施形態による半導体装置60の構成を示す。

【0087】

図14を参照するに、本実施形態では、前記SiNパッシベーション膜29が前記保護溝部24Aの内側側壁面、底面および外側側壁面を連続して覆っており、前記層間絶縁膜26A〜26Gの積層体表面のうち、前記溝部24Aの外側において、開口部29Bが、前記開口部29Aと同時に、前記保護溝部24Aを囲むように連続的に形成されている。

【0088】

かかる構成により、前記半導体装置のスクライブ工程において前記SiNパッシベーション膜29にクラックが発生しても、クラック伝播は前記開口部29Bにより阻止され、耐湿リング22A内側の回路領域に侵入することがない。

【0089】

図14は、前記半導体装置がスクライブされる前の状態を示しているが、前記開口部29Bより、前記積層体のうち、前記保護溝部24A外側の部分に水分の侵入が生じているのがわかる。またこの部分は、スクライブ時にも大気曝露され、水分が侵入するが、前記保護溝部24Aの内側では、前記SiNパッシベーション膜29により、水分の侵入が阻止され、耐湿リング22Aの負荷が大きく軽減される。

【0090】

図14の例では、前記層間絶縁膜26A〜26Fがシリコン酸化膜よりなり、前記SiNパッシベーション膜29が前記保護溝部24Aにおいて前記層間絶縁膜26A〜26Fと直接に接しているが、先に図5あるいは図7で説明したように、前記層間絶縁膜26A〜26Fが、SiO2よりも比誘電率が低い低誘電率膜である場合、前記溝部24Aにおいて前記SiNパッシベーション膜29と保護溝部表面の間にシリコン酸化膜28と界面膜28I、あるいは界面膜28Iを介在させるのが好ましい。

【0091】

図15は、前記図14の一変形例であり、前記積層体上に前記開口部29Cに対応してAlパターン28Eが、前記Alパターン28Aおよび28Bと同時に、前記保護溝部24Aを連続して囲むように形成されている。

【0092】

本実施形態では、前記開口部29Cを形成する際に、該当部位に前記Alパターン28Eが形成されているため、前記開口部29Cを形成するドライエッチングがかかるAlパターン29Cで停止し、積層体内部に深く侵入することがない。

【0093】

また前記積層体のうち、前記保護溝部外側の部分は、スクライブ前の状態では水分の侵入が生じない。

[第5の実施形態]

図15は本発明の第5の実施形態による半導体装置80の構成を示す。ただし図中、先に説明した部分に対応する部分には同一の参照符号を付し、説明を省略する。

【0094】

図15を参照するに、本実施形態では、シリコン基板25上に層間絶縁膜26A〜26Gの積層により形成された積層体中、前記耐湿リング22Aの外側に形成された保護溝部24Aが、SiNパッシベーション膜29により連続的に覆われており、さらにかかるパッシベーション膜29上に、前記保護溝部24Aを充填するように、水溶性樹脂等の樹脂層30が形成されている。

【0095】

本実施形態では、かかる樹脂層30を形成した状態でシリコンウェハのスクライブを実行するため、クラックのエネルギがかかる樹脂層30により吸収され、回路部分23へのクラック伝播が抑制される。

【0096】

なおかかる樹脂層30は、図15の構成に限定されるものではなく、先に説明した全ての実施形態について適用可能である。

【0097】

以上、本発明を好ましい実施形態について説明したが、本発明かかかる特定の実施形態に限定されるものではなく、特許請求の範囲に記載した要旨内において様々な変形・変更が可能である。

【符号の説明】

【0098】

10,20,40,60 半導体装置

11A〜11D 素子領域

12A,12B,12C,12D,22A 耐湿リング

13,23 回路領域

14A,24A 保護溝部

15,25 半導体基板

15Tr,25Tr トランジスタ

15a,15b,25a,25b 拡散領域

15c,15d,25c,25d シリサイド層

16A,16B,16C,16D,16E,16F,16G,26A、26B,26C,26D,26E,26F 層間絶縁膜

16a,16b,16c,16d,16e,16f,16g,26a,26b,26c,26d,26e,26f 配線パターン、ビアプラグ

16aR,16bR,16cR,16dR,16eR,16fR,16gR,26aR,26bR,26cR,26dR,26eR,26fR 耐湿リングパターン

17A,17B,17C,17D,17E,17F,27A,27B,27C,27D,27E,27F エッチングストッパ膜

18,28 シリコン酸化膜

18A,28A,28C,29D,28E Alパターン

18B,28B Alパッド電極

19,29 SiNパッシベーション膜

【技術分野】

【0001】

本発明は一般に半導体装置に係り、特に耐湿リングを有する半導体装置およびその製造方法に関する。

【背景技術】

【0002】

一般に半導体装置の製造技術では、シリコンウェハなどの半導体基板上に半導体素子を多数、行列状に形成し、さらにかかる半導体基板をスクライブラインに沿って切断することにより、個々の半導体素子が形成された半導体チップを、半導体装置として得ている。

【0003】

このような半導体チップでは、その切断面において半導体装置を構成する半導体層や絶縁層、金属層などが露出されるため、かかる切断面を介した大気中の水分の半導体装置中への侵入を抑制するため、その周辺部に、半導体装置中の多層配線構造と同じ層構造の耐湿リングが形成されるのが一般的である。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2004−47575号公報

【特許文献2】特開2004−134450号公報

【特許文献3】特開2004−79596号公報

【特許文献4】特開2003−273043号公報

【特許文献5】特開2004−119468号公報

【特許文献6】特開2005−217411号公報

【特許文献7】特開2005−260059号公報

【特許文献8】特開2004−296904号公報

【特許文献9】特開2006−114723号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

図1は、シリコン基板11上に形成された本発明の関連技術による半導体素子の一部を示す平面図、図2はかかる半導体素子の、耐湿リングを含む部分断面図を示す。

【0006】

図1を参照するに、シリコン基板11上には素子領域11A,11B,11C,11Dが、一点鎖線で示したスクライブラインにより画成されており、各々の素子領域11A,11B,11C,11Dは、耐湿リング12A,12B,12C,12Dの内側に、それぞれの半導体素子を構成する回路領域13を含んでいる。図示の例では、素子領域11Aに回路領域13が形成されているが、同様な回路領域は、他の素子領域11B〜11Dのいずれにも形成されている。

【0007】

さらに図1の構成では、前記素子領域11A〜11Dの各々には、対応する耐湿リング12A〜12Dの外側で、かつ一点鎖線で示したスクライブラインの内側に、スクライブ時のクラック伝播を遮断するため、保護溝部14A〜14Dのいずれかが形成されている。

【0008】

そこで、図1の平面図において、前記一点鎖線で示したスクライブラインに沿ってシリコン基板11を切断することにより、個々の半導体装置が、半導体チップの形で分離される。

【0009】

図2は、このようにして得られた半導体装置10の断面図を示す。

【0010】

図2を参照するに、前記半導体素子10は、素子分離領域15Iおよびトランジスタ15Trが形成されたシリコン基板15上に形成されており、前記トランジスタ15TrはSiN膜17Aにより覆われており、前記シリコン基板15上には、前記トランジスタ15TrおよびSiN膜17Aを覆って、各々シリコン酸化膜よりなる層間絶縁膜16A,16B,・・・16Gを、間にシリコン窒化膜17B,17C・・・17Fを交互に挟んで積層した構成の多層配線構造が形成されている。

【0011】

図示の例では、前記層間絶縁膜16A中にはWなどよりなるビアパターン16aRが前記耐湿リング12Aに対応して、前記シリコン基板15の表面にコンタクトして連続的に形成されており、また前記回路領域13にビアプラグ16aが、前記トランジスタ15Trの拡散領域15a,15bを覆うシリサイド層15c,15dにコンタクトして形成されている。

【0012】

さらに前記層間絶縁膜16B中にはCuパターン16bRが前記耐湿リング12Aに対応して、前記ビアパターン16aRにコンタクトしてシングルダマシン法により、連続的に形成されており、また前記回路領域13にはCu配線パターン16bが、前記Wビアパターン16aRにコンタクトして、やはりシングルダマシン法により形成されている。

【0013】

さらに前記層間絶縁膜16C中にはCuパターン16cRが前記耐湿リング12Aに対応して、その下の前記Cuパターン16bRにコンタクトしてシングルまたはデュアルダマシン法により連続的に形成されており、また前記回路領域13にはビアプラグを有するCu配線パターン16cが、前記Cu配線パターン16bにコンタクトして、やはりシングルまたはデュアルダマシン法により形成されている。

【0014】

さらに前記層間絶縁膜16D中にはCuパターン16dRが前記耐湿リング12Aに対応して、その下の前記Cuパターン16cRにコンタクトして、シングルまたはデュアルダマシン法により連続的に形成されており、また前記回路領域13にはビアプラグを有するCu配線パターン16dが、前記Cu配線パターン16cにコンタクトして、やはりシングルまたはデュアルダマシン法により形成されている。

【0015】

さらに前記層間絶縁膜16E中にはCuパターン16eRが前記耐湿リング12Aに対応して、その下の前記Cuパターン(図示せず)にコンタクトしてデュアルダマシン法により連続的に形成されており、また前記回路領域13にはビアプラグを有するCu配線パターン16eが、前記Cu配線パターン(図示せず)にコンタクトして、やはりデュアルダマシン法により形成されている。

【0016】

さらに前記層間絶縁膜16F中にはCuパターン16fRが前記耐湿リング12Aに対応して、その下の前記Cuパターン16eRにコンタクトしてデュアルダマシン法により連続的に形成されており、また前記回路領域13にはビアプラグを有するCu配線パターン16fRが、その下の対応するCu配線パターン16eにコンタクトして、やはりデュアルダマシン法により形成されている。

【0017】

さらに前記層間絶縁膜16G中にはWパターン16gRが前記耐湿リング12Aに対応して、その下の前記Cuパターン16fRにコンタクトしてダマシン法により連続的に形成されており、また前記回路領域13にWビアプラグ16gが、前記Cu配線パターン16fにコンタクトして、やはりダマシン法により形成されている。

【0018】

ここで、前記Cu配線パターン16b〜16fおよびCuパターン16bR〜16fRは、Taなどのバリアメタル膜により覆われており、また前記Wビアプラグ16a,16gおよびWパターン16aR,16gRは、TiNなどのバリア膜により覆われていることに注意すべきである。

【0019】

さらに前記層間絶縁膜16G上には、前記耐湿リングに対応してTi/TiN構造の密着膜により挟持されたAlパターン18Aが、前記Wパターン16gRにコンタクトして形成され、また前記ビアプラグ16g上に、同様な構造のパッド電極18Bが、前記ビアプラグ16gにコンタクトして形成されている。

【0020】

さらに前記Alパターン18Aおよびパッド電極18Bは、前記層間絶縁膜16G上において高密度プラズマCVD法により堆積されたシリコン酸化膜18により覆われ、さらにその上に、SiN膜よりなるパッシベーション膜19が形成されている。前記パッシベーション膜19およびシリコン酸化膜18中には、前記パッド電極18Bを露出する開口部19Aが形成される。

【0021】

図2の構成では、矢印で示すように図中左側端部においてダイシングソーによるスクライブが行われるが、その際のクラック伝播を阻止するため、前記耐湿リングの外側には、先に図1で説明した保護溝部14Aが形成されている。

【0022】

一方、図2の構成の半導体装置では、図中左側端部が大気曝露されるため、図3に示すように、層間絶縁膜16A〜16Fのうち、耐湿リング12Aの外側の部分には水分が侵入するが、このような水分の、回路領域13への侵入は前記耐湿リング12が阻止しており、このため耐湿リング12の負荷が大きく、腐食しやすい問題を有している。耐湿リング12の一部に欠陥が発生すると、水分はその部分を伝って、半導体装置内部に侵入する。図3では、破線で囲んだ、耐湿リング12Aを構成するCuパターン16cRに、このような欠陥が生じている。

【0023】

このような耐湿リング12の負荷の問題は、特に層間絶縁膜16A〜16Fとして、密度の低い低誘電率膜、いわゆるLow−K膜を使った場合に特に顕著となる。

【0024】

図4は、このような耐湿リングの負荷を軽減する、本発明の関連技術による半導体装置の構成を示す。ただし図5中、先に説明した部分には同一の参照符号を付し、説明を省略する。

【0025】

図4を参照するに、図4の構成では、前記保護溝部14Aがシリコン基板15の表面まで到達するように深く形成され、さらにその表面を覆ってSiNパッシベーション膜19が連続して形成されている。

【0026】

その結果、前記層間絶縁膜16A〜16F、および層間絶縁膜16Gは、それぞれの端部が連続してSiNパッシベーション膜により覆われており、前記耐湿リングへの負荷は実質的に軽減され、半導体装置の信頼性が向上すると期待される。

【0027】

しかし、前記図4の構造を形成しようとすると、層間絶縁膜16A〜16Gよりなる積層体中に深い溝14Aを形成する必要があり、特にレジストパターンをマスクにパターニングを行う場合、パターニング精度に問題が生じることがある。

【0028】

また前記SiNパッシベーション膜19は、応力を蓄積した膜であり、特に前記層間絶縁膜16A〜16Fが低誘電率膜である場合、密着力が低下し、剥離しやすい問題が生じる。

【0029】

かかるパッシベーション膜19を、高密度プラズマCVD法により形成されたシリコン酸化膜により形成することも考えられようが、特に前記層間絶縁膜16A〜16Fが有機系の低誘電率膜、あるいは有機基を多く含む低誘電率膜の場合、成膜時の酸素雰囲気により前記層間絶縁膜が侵食される恐れがあり、かかる手法を適用することは困難であると考えられる。

【0030】

さらに図4の構成では、前記パッシベーション膜19が応力を蓄積したSiN膜より構成される場合、スクライブ時の破断が前記パッシベーション膜19を伝って、耐湿リング12Aより内側の回路領域13に到達し、半導体装置の信頼性を低下させる恐れがある。

【課題を解決するための手段】

【0031】

一の側面によれば半導体装置は、活性素子が形成された素子領域を有する基板と、前記基板上に形成され、多層配線構造を含む積層体と、前記積層体中に、前記素子領域を囲んで連続的に延在する耐湿リングと、前記積層体中、前記耐湿リングの外側に、前記耐湿リングに沿って連続的に、前記基板の表面に達して形成された保護溝部と、前記積層体上に形成され、前記保護溝部の外縁に沿って延在する第1のマスクパターンと、前記積層体上に形成され、前記保護溝部の内縁に沿って延在する第2の金属マスクパターンと、を有する。

【0032】

他の側面によれば半導体装置の製造方法は、活性素子が形成された素子領域を有する基板上に、前記素子領域を囲んで位置する耐湿リングと多層配線構造とを含む積層体と、前記耐湿リングの外側の前記積層体上に、前記耐湿リングを連続して囲んで位置する金属膜と、を形成する工程と、前記金属膜の少なくとも一部及び前記金属膜の下の前記積層体を除去して、前記耐湿リングを囲んで位置し、前記基板に達する保護溝部を形成する工程と、を有する。

【発明の効果】

【0033】

本発明によれば、基板上に多層配線構造を構成する積層体を有する半導体装置において、耐湿リングの外側に、基板面に到達して形成される深い保護溝部を形成することにより、前記耐湿リング内側の半導体装置主要部をダイシング時のクラックから保護することができる。その際、かかる保護溝部の少なくとも内壁面を保護膜により覆うことにより、かかる保護溝部側壁面からの半導体素子中への水分の侵入を阻止することができる。

【0034】

特にかかる多層配線構造が、低誘電率層間絶縁膜の積層により構成される場合、保護膜形成時に前記保護溝部側壁面において露出している層間絶縁膜端面が侵食される恐れがあるが、本発明によれば、かかる側壁面をSiとCを主成分とする界面膜により覆うことにより、かかる保護膜形成時の溝部側壁面の侵食の問題を回避することが可能となる。

【0035】

また本発明によれば、前記保護溝部を前記積層体中に形成する場合、前記積層体表面に形成された金属パターンをハードマスクとして保護溝部形成を行うことにより、シリコン基板表面に到達する深い溝部であっても、所望の保護溝部形成を安定して行うことができる。

【0036】

さらに本発明によれば、前記保護膜を、前記保護溝部の外側側壁面あるいは保護溝部の外側において除去することにより、前記半導体装置をスクライブ工程により切り離す場合にも、クラックが、歪みを蓄積した保護膜を伝播して半導体装置内部に侵入するのが抑制され、半導体装置の製造歩留まりを向上させることが可能となる。

【図面の簡単な説明】

【0037】

【図1】本発明の関連技術による半導体ウェハ表面の一部を示す平面図である。

【図2】本発明の関連技術による半導体装置の一部を示す断面図である。

【図3】本発明の他の関連技術による半導体装置の一部を示す断面図である。

【図4】本発明の他の関連技術による半導体装置の一部を示す断面図である。

【図5】本発明の第1の実施形態による半導体装置の構成を示す断面図である。

【図6A】図5の半導体装置の製造工程を説明する図(その1)である。

【図6B】図5の半導体装置の製造工程を説明する図(その2)である。

【図6C】図5の半導体装置の製造工程を説明する図(その3)である。

【図6D】図5の半導体装置の製造工程を説明する図(その4)である。

【図6E】図5の半導体装置の製造工程を説明する図(その5)である。

【図6F】図5の半導体装置の製造工程を説明する図(その6)である。

【図7】図5の半導体装置の一変形例を示す断面図である。

【図8A】本発明の第2の実施形態による半導体装置の製造工程を説明する図(その1)である。

【図8B】本発明の第2の実施形態による半導体装置の製造工程を説明する図(その2)である。

【図8C】本発明の第2の実施形態による半導体装置の製造工程を説明する図(その3)である。

【図9】本発明の第2の実施形態の一変形例を示す図である。

【図10】本発明の第2の実施形態の他の変形例を示す図である。

【図11】本発明の第3の実施形態による半導体装置の構成を示す図である。

【図12】図11の半導体装置の一変形例を示す図である。

【図13】図11の半導体装置の一変形例を示す図である。

【図14】本発明の第4の実施形態による半導体装置の構成を示す図である。

【図15】図14の半導体装置の一変形例を示す図である。

【図16】本発明の第5の実施形態による半導体装置の構成を示す図である。

【発明を実施するための形態】

【0038】

図5は、本発明の第1の実施形態による半導体装置20の構成を示す。

【0039】

図5を参照するに、前記半導体装置20は、素子分離領域25Iおよびトランジスタ25Trが形成されたシリコン基板25上に形成されており、前記トランジスタ25TrはSiN膜27Aにより覆われており、前記シリコン基板25上には、前記トランジスタ15TrおよびSiN膜27Aを覆って、層間絶縁膜26A,26B,・・・,26Gを、間にSiNあるいはSiCよりなるエッチングストッパ膜27B,27C・・・27Fを交互に挟んで積層した構成の、多層配線構造を含む積層体が形成されている。

【0040】

図示の例では、前記層間絶縁膜26A中にはWなどよりなるビアパターン26aRが耐湿リング22Aに対応して、前記シリコン基板25の表面にコンタクトして連続的に形成されており、また前記耐湿リング22Aで囲まれた回路領域23に、ビアプラグ26aが、前記トランジスタ25Trの拡散領域25a,25bを覆うシリサイド層25c,25dにコンタクトして形成されている。

【0041】

さらに前記層間絶縁膜26B中にはCuパターン26bRが前記耐湿リング22Aに対応して、前記ビアパターン26aRにコンタクトしてシングルダマシン法により、連続的に形成されており、また前記回路領域23にはCu配線パターン26bが、前記Wビアパターン26aにコンタクトして、やはりシングルダマシン法により形成されている。

【0042】

さらに前記層間絶縁膜26C中にはCuパターン26cRが前記耐湿リング22Aに対応して、その下の前記Cuパターン26bRにコンタクトしてデュアルダマシン法により連続的に形成されており、また前記回路領域23にはビアプラグを有するCu配線パターン26cが、前記Cu配線パターン26bにコンタクトして、やはりシングル又はデュアルダマシン法により形成されている。

【0043】

さらに前記層間絶縁膜26D中にはCuパターン26dRが前記耐湿リング12Aに対応して、その下の前記Cuパターン26cRにコンタクトして、シングルまたはデュアルダマシン法により連続的に形成されており、また前記回路領域23にはビアプラグを有するCu配線パターン26dが、前記Cu配線パターン26cにコンタクトして、やはりデュアルダマシン法により形成されている。

【0044】

さらに前記層間絶縁膜26E中にはCuパターン26eRが前記耐湿リング22Aに対応して、その下の前記Cuパターン(図示せず)にコンタクトしてデュアルダマシン法により連続的に形成されており、また前記回路領域23にはビアプラグを有するCu配線パターン26eが、前記Cu配線パターン(図示せず)にコンタクトして、やはりデュアルダマシン法により形成されている。

【0045】

さらに前記層間絶縁膜26F中にはCuパターン26fRが前記耐湿リング22Aに対応して、その下の前記Cuパターン26eRにコンタクトしてデュアルダマシン法により連続的に形成されており、また前記回路領域23にはビアプラグを有するCu配線パターン26fが、その下の対応するCu配線パターン26eにコンタクトして、やはりデュアルダマシン法により形成されている。

【0046】

さらに前記層間絶縁膜26G中にはWパターン26gRが前記耐湿リング22Aに対応して、その下の前記Cuパターン26fRにコンタクトしてダマシン法により連続的に形成されており、また前記回路領域23にはWビアプラグ26gが、前記Cu配線パターン26fにコンタクトして、やはりダマシン法により形成されている。

【0047】

ここで、前記Cu配線パターン26b〜26fおよびCuパターン26bR〜26fRは、Ta膜あるいはTa/TaN積層膜などのバリアメタル膜により覆われており、また前記Wビアプラグ26a,26gおよびWパターン26aR,26gRは、TiNなどのバリア膜により覆われていることに注意すべきである。

【0048】

さらに前記層間絶縁膜26G上には、前記耐湿リングに対応してTi/TiN構造の密着膜により挟持されたAlパターン28Aが、前記Wパターン26gRにコンタクトして形成され、また前記ビアプラグ26g上に、同様な構造のパッド電極28Bが、前記ビアプラグ26gにコンタクトして形成されている。図示の例では、前記層間絶縁膜26Gは、シリコン酸化膜より形成されている。

【0049】

さらに前記Alパターン28Aおよびパッド電極28Bは、前記層間絶縁膜26G上において高密度プラズマCVD法により堆積されたシリコン酸化膜28により覆われ、さらにその上に、SiN膜よりなるパッシベーション膜29が、例えばプラズマCVD法により形成されている。前記パッシベーション膜29およびシリコン酸化膜28中には、前記パッド電極28Bを露出する開口部29Aが形成される。

【0050】

前記層間絶縁膜26A〜26Fとしては、登録商標FlareやSiLKなどの名称で市販の炭化水素系絶縁膜、有機あるいは無機シロキサン膜、あるいはこれらの多孔質膜を使うことができる。これらの層間絶縁膜は、プラズマCVD法あるいは塗布法により形成できる。前記層間絶縁膜26A〜26Dは、例えば200〜400nm程度の膜厚に形成され、前記層間絶縁膜26E,26Fは、例えば400〜600nm程度の膜厚に形成される。

【0051】

その際、本実施形態では、前記積層体中、前記耐湿リング22Aの外側に、前記シリコン基板25の表面に到達する保護溝部24Aが、先の図1の保護溝部14Aと同様に、前記耐湿リング22Aに沿って連続的に形成されており、前記シリコン酸化膜28およびパッシベーション膜29は、かかる保護溝部24Aの内壁面、底面および外壁面を連続して覆っている。

【0052】

また前記保護溝部24Aは、前記層間絶縁膜26A〜26Gを積層した積層体を、レジストパターンをマスクとしたドライエッチングを、前記シリコン基板25の表面が露出するまで実行することにより、形成される。

【0053】

さらに本実施形態では、前記シリコン酸化膜28と前記保護溝部24Aの内壁面、底面および外壁面の間に、SiC界面膜28Iが、プラズマCVD法により、5〜200nmの膜厚に形成されている。

【0054】

かかる界面膜28Iを形成することにより、前記シリコン酸化膜28を前記保護溝部24Aの内壁面、底面および外壁面に形成する際に、前記内壁面あるいは外壁面に露出されている低誘電率層間絶縁膜26A〜26Fの損傷を抑制することができる。

【0055】

なお前記界面膜28Iとしては、組成がSiCの膜に限定されることはなく、SiとCを主成分とする、例えばSiCH膜やSiOC膜、SiOCH膜などであっても、界面膜の成膜時に前記低誘電率層間絶縁膜26A〜26Fの損傷を抑制できるものであれば、使うことができる。

【0056】

前記界面膜28IをSiC膜より形成する場合には、例えば原料としてテトラメチルシランを供給し、これを350〜400℃の基板温度においてプラズマ励起するプラズマCVD法により形成することができる。

【0057】

このように、本実施形態によれば、前記保護溝部24Aの表面、すなわち内側側壁面、底面および外側側壁面、に高密度プラズマCVD法により前記シリコン酸化膜28を形成するに先立って、前記保護溝部24Aの表面を界面膜28Iにより連続して覆うことにより、前記シリコン酸化膜28形成時における前記保護溝部24A表面の酸素ラジカルおよびイオンによる損傷が抑制される。前記界面膜28Iの形成は、酸素の少ない条件で行われるため、前記層間絶縁膜26A〜26Fの前記保護溝部24Aにおける露出端面の損傷は実質的に生じない。

【0058】

また、かかるシリコン酸化膜28をSiNパッシベーション膜29の直下に形成することにより、応力を蓄積しやすいSiNパッシベーション膜29の剥離を抑制することが可能となる。

【0059】

図示の例では、図中、左端がスクライブされており、端面が大気露出しているが、大気中の水分は主に前記保護溝部24Aにおいて前記SiNパッシベーション膜29により阻止され、耐湿リング22Aの負荷が大きく軽減される。

【0060】

以下、図6A〜6Gを参照しながら、前記半導体装置20の製造工程を説明する。

【0061】

図6Aを参照するに、活性素子25Trが形成されたシリコン基板25上には、前記層間絶縁膜26A〜26Gを積層した積層体が形成されており、前記積層体中には、前記耐湿リング22Aに対応して、WあるいはCuパターン26aR〜26gRを積層した構造が形成され、最上部にAlパターン28Aが形成されている。また前記積層体中には、前記回路領域23中の多層配線構造に対応して、WあるいはCuパターン26a〜26gを積層した構造が形成され、図6Bの工程において、前記耐湿リング22Aの外側に、前記シリコン基板25を露出するように、保護溝部24Aが、CF系ガスおよびO2,Ar等の混合ガスをエッチングガスとしたドライエッチングにより、形成される。図6Bの工程において前記ドライエッチング工程は、前記積層体表面のうち、前記保護溝部24Aの形成領域を除き、レジストマスクにより保護した状態で実行される。

【0062】

前記図6Bの工程では、前記保護溝部24Aの形成に伴って前記層間絶縁膜26A〜26Fが前記保護溝部24Aにおいて大気曝露され、前記層間絶縁膜26A〜26Fは、スクライブ前の状態であるにもかかわらず、前記耐湿リング22Aの外側において吸湿するが、図6Cの工程において、前記図6Bの構造は脱水処理され、さらに前記図6Bの構造上に前記SiC膜28Iが、先に説明したプラズマCVD法により、先に説明した膜厚で形成される。前記SiC膜28Iの膜厚が5nm以下になると、前記SiC膜28Iの界面膜としての効果が得られず、また前記SiC膜28Iの膜厚が200nm以上になると、処理時間が不必要に長くなってしまう。

【0063】

次に図6Dの工程において前記図6Cの構造上に、前記シリコン酸化膜28が、原料としてシランと酸素を使い、700W程度のプラズマパワーで400℃程度の基板温度において、4kW程度の基板バイアスを印加しながら、例えば1200〜1500nmの膜厚に形成され、さらに図6Eの工程において前記図6Dの構造上に、前記SiNパッシベーション膜29が、原料としてシランとアンモニアを使い、400℃程度の基板温度において750W程度のプラズマパワーで、500nmの膜厚に形成される。

【0064】

さらに図6Fの工程において、前記SiNパッシベーション膜29中に、前記電極パッド28Bを露出する開口部29Aが形成される。

【0065】

さらに図6Fの工程の後、図1のスクライブラインに沿って前記シリコンウェハをスクライブすることにより、図5の半導体装置20が得られる。

【0066】

なお、前記SiNパッシベーション膜29に十分な密着性が得られる場合には、前記シリコン酸化膜28を前記保護溝部24Aを形成する前に成膜し、前記保護溝部24Aに対応して基板25に達する溝が形成された後、図7に示すようにSiNパッシベーション膜29を、前記保護溝部24Aにおいて直接に前記界面膜28Iに接して形成することも可能である。

[第2の実施形態]

次に本発明の第2の実施形態を、図8A〜8Cを参照しながら説明する。ただし図8A〜8C中、先に説明した部分に対応する部分には同一の参照符号を付し、説明を省略する。

【0067】

先の実施形態では、図6Bの工程において前記保護溝部24Aをドライエッチングにより形成するのに、レジストプロセスを使っていたが、このように深い保護溝部24Aを形成しようとすると、ドライエッチング時間が長くなり、特に層間絶縁膜の数が多い半導体装置では、レジストパターンが長時間のドライエッチングに耐えられなくなる問題が生じる。

【0068】

本実施形態は、このような多層配線構造中の層間絶縁膜の数が多く、前記保護溝部24Aの形成に長時間を要する場合を想定したものであり、図8Aに示すように、前記最上層のシリコン酸化膜26G上に、前記保護溝部24Aの形成領域を画成するように、Alパターン28Cおよび28Dを、前記Alパターン28Aおよび28Bと同時に、同一のマスクを使って形成し、かかるAlパターン28Cおよび28Dをハードマスクに、前記層間絶縁膜26A〜26Gの積層体を、前記パターン28Cおよび28Dの間においてドライエッチングし、前記保護溝部24Aを形成する。

【0069】

本実施形態では、次に図8Bの工程において前記図8Aの構造を脱水処理後、前記界面膜28Iを、先の図6Cの工程と同様にして形成し、さらに図8Cの工程において、前記パッシベーション膜29が、前記界面膜28I上に、先の図6Eの工程と同様にして形成される。なお図8Cは、さらに半導体装置がスクライブされた状態を示している。

【0070】

かかる構成によれば、先にも説明したように前記保護溝部24Aが安定して形成され、例えば前記保護溝部24Aを形成するドライエッチングプロセスが側方に進行し、耐湿リング22Aを露出してしまうなどの問題を回避することができる。

【0071】

図8A〜8Cでは、SiNパッシベーション膜29が前記界面膜28Iに直接に接している場合を説明したが、本実施形態はかかる特定の場合に限定されるものではなく、前記界面膜28IとSiNパッシベーション膜29の間に高密度プラズマCVD法により形成された、前記シリコン酸化膜28と同様なシリコン酸化膜が介在する場合についても、同様に有効である。

【0072】

このように前記Alパターン28Cおよび28Dを形成しても、マスク枚数が増えることはなく、半導体装置の製造工程が複雑になることはない。

【0073】

図9は、前記図8Aの一変形例を示す。

【0074】

図9を参照するに、本実施形態では前記Alパターン28Aが図8(A)のAlパターン28Dを兼用しており、これにより、図9中、矢印Wで示すように、チップサイズを、図8(A)の場合に比べて減少させることができる。

【0075】

図10は、前記図8Aの別の変形例を示す。

【0076】

図10を参照するに、本実施形態では、前記保護溝部24Aの外側に、CuあるいはWパターン26aP〜26bPの積層よりなる、前記耐湿リング22Aと同様な別の耐湿リング22Bが形成されており、前記Alパターン28Cが、前記耐湿リング22Bの最上部パターンとして形成されている。

【0077】

かかる構成でも、前記Alパターン28Aおよび28Cをマスクとしてドライエッチングを行うことにより、前記保護溝部24Aの形状を正確に制御することが可能となる。

【0078】

このような別の耐湿リング22Bは、前記耐湿リング22Aと同時に形成でき、工程数が増加することはない。また、前記保護溝部24Aより外側に耐湿リングが存在することで、界面伝播するクラックは、かかる追加の耐湿リング構造により、その進行が抑制される。

[第3の実施形態]

図11は、本発明の第3の実施形態による半導体装置40の構成を示す。ただし図中、先に説明した部分に対応する部分には同一の参照符号を付し、説明を省略する。

【0079】

図11を参照するに、本実施形態では、前記SiNパッシベーション膜29が前記保護溝部24Aの内側側壁面および底面を直接に覆っているが、前記パッシベーション膜29のうち、前記溝部24Aの外側側壁面を覆う部分が、前記溝部24Aを形成するのに使われたマスクデータをスクライブライン方向にわずかにずらして形成したマスクパターンを使い、前記溝部24Aを形成するのと同様なドライエッチング工程を行うことにより、除去されている。またかかるドライエッチング工程の結果、図11の例では、前記保護溝部24Aの外側側壁面に、段部24aが形成されている。

【0080】

かかる構成により、前記半導体装置をスクライブ工程により分離する際に、クラックが歪みを蓄積したSiNパッシベーション膜29を使って耐湿リング22A内側の回路領域に侵入するのが阻止される。

【0081】

また、本実施形態では、前記保護溝部22AにおけるSiNパッシベーション膜29の除去工程を、前記パッド電極28Bを露出する開口部29Aの形成工程と同時に行うことにより、マスク枚数の増加を回避することができる。その場合、前記開口部29Aではエッチングは、前記パッド電極22Bが露出した時点で実質的に停止し、保護溝部24Aの外側側壁面においてのみ、エッチングがさらに進行する。

【0082】

図11の例では、前記層間絶縁膜26A〜26Fがシリコン酸化膜よりなり、前記SiNパッシベーション膜29が前記保護溝部24Aにおいて前記層間絶縁膜26A〜26Fと直接に接しているが、先に図5あるいは図7で説明したように、前記層間絶縁膜26A〜26Fが、SiO2よりも比誘電率が低い低誘電率膜である場合、前記保護溝部24Aにおいて前記SiNパッシベーション膜29と保護溝部表面の間にシリコン酸化膜28と界面膜28I、あるいは界面膜28Iを介在させるのが好ましい。

【0083】

図12は、前記図11の一変形例であり、前記保護溝部24Aの外側側壁面の一部に前記SiNパッシベーション膜が残留している場合を示す。

【0084】

本実施形態は、このような場合をも含むものである。

【0085】

さらに図13は、前記図11の他の変形例であり、前記保護溝部24A外側の側壁面をエッチングする際に、SiNパッシベーション膜29の一部が残って突出部を形成した場合を示す。

【0086】

本実施形態は、このような場合をも含むものである。

[第4の実施形態]

図14は、本発明の第4の実施形態による半導体装置60の構成を示す。

【0087】

図14を参照するに、本実施形態では、前記SiNパッシベーション膜29が前記保護溝部24Aの内側側壁面、底面および外側側壁面を連続して覆っており、前記層間絶縁膜26A〜26Gの積層体表面のうち、前記溝部24Aの外側において、開口部29Bが、前記開口部29Aと同時に、前記保護溝部24Aを囲むように連続的に形成されている。

【0088】

かかる構成により、前記半導体装置のスクライブ工程において前記SiNパッシベーション膜29にクラックが発生しても、クラック伝播は前記開口部29Bにより阻止され、耐湿リング22A内側の回路領域に侵入することがない。

【0089】

図14は、前記半導体装置がスクライブされる前の状態を示しているが、前記開口部29Bより、前記積層体のうち、前記保護溝部24A外側の部分に水分の侵入が生じているのがわかる。またこの部分は、スクライブ時にも大気曝露され、水分が侵入するが、前記保護溝部24Aの内側では、前記SiNパッシベーション膜29により、水分の侵入が阻止され、耐湿リング22Aの負荷が大きく軽減される。

【0090】

図14の例では、前記層間絶縁膜26A〜26Fがシリコン酸化膜よりなり、前記SiNパッシベーション膜29が前記保護溝部24Aにおいて前記層間絶縁膜26A〜26Fと直接に接しているが、先に図5あるいは図7で説明したように、前記層間絶縁膜26A〜26Fが、SiO2よりも比誘電率が低い低誘電率膜である場合、前記溝部24Aにおいて前記SiNパッシベーション膜29と保護溝部表面の間にシリコン酸化膜28と界面膜28I、あるいは界面膜28Iを介在させるのが好ましい。

【0091】

図15は、前記図14の一変形例であり、前記積層体上に前記開口部29Cに対応してAlパターン28Eが、前記Alパターン28Aおよび28Bと同時に、前記保護溝部24Aを連続して囲むように形成されている。

【0092】

本実施形態では、前記開口部29Cを形成する際に、該当部位に前記Alパターン28Eが形成されているため、前記開口部29Cを形成するドライエッチングがかかるAlパターン29Cで停止し、積層体内部に深く侵入することがない。

【0093】

また前記積層体のうち、前記保護溝部外側の部分は、スクライブ前の状態では水分の侵入が生じない。

[第5の実施形態]

図15は本発明の第5の実施形態による半導体装置80の構成を示す。ただし図中、先に説明した部分に対応する部分には同一の参照符号を付し、説明を省略する。

【0094】

図15を参照するに、本実施形態では、シリコン基板25上に層間絶縁膜26A〜26Gの積層により形成された積層体中、前記耐湿リング22Aの外側に形成された保護溝部24Aが、SiNパッシベーション膜29により連続的に覆われており、さらにかかるパッシベーション膜29上に、前記保護溝部24Aを充填するように、水溶性樹脂等の樹脂層30が形成されている。

【0095】

本実施形態では、かかる樹脂層30を形成した状態でシリコンウェハのスクライブを実行するため、クラックのエネルギがかかる樹脂層30により吸収され、回路部分23へのクラック伝播が抑制される。

【0096】

なおかかる樹脂層30は、図15の構成に限定されるものではなく、先に説明した全ての実施形態について適用可能である。

【0097】

以上、本発明を好ましい実施形態について説明したが、本発明かかかる特定の実施形態に限定されるものではなく、特許請求の範囲に記載した要旨内において様々な変形・変更が可能である。

【符号の説明】

【0098】

10,20,40,60 半導体装置

11A〜11D 素子領域

12A,12B,12C,12D,22A 耐湿リング

13,23 回路領域

14A,24A 保護溝部

15,25 半導体基板

15Tr,25Tr トランジスタ

15a,15b,25a,25b 拡散領域

15c,15d,25c,25d シリサイド層

16A,16B,16C,16D,16E,16F,16G,26A、26B,26C,26D,26E,26F 層間絶縁膜

16a,16b,16c,16d,16e,16f,16g,26a,26b,26c,26d,26e,26f 配線パターン、ビアプラグ

16aR,16bR,16cR,16dR,16eR,16fR,16gR,26aR,26bR,26cR,26dR,26eR,26fR 耐湿リングパターン

17A,17B,17C,17D,17E,17F,27A,27B,27C,27D,27E,27F エッチングストッパ膜

18,28 シリコン酸化膜

18A,28A,28C,29D,28E Alパターン

18B,28B Alパッド電極

19,29 SiNパッシベーション膜

【特許請求の範囲】

【請求項1】

活性素子が形成された素子領域を有する基板と、

前記基板上に形成され、多層配線構造を含む積層体と、

前記積層体中に、前記素子領域を囲んで連続的に延在する耐湿リングと、

前記積層体中、前記耐湿リングの外側に、前記耐湿リングに沿って連続的に、前記基板の表面に達して形成された保護溝部と、

前記積層体上に形成され、前記保護溝部の外縁に沿って延在する第1の金属マスクパターンと、

前記積層体上に形成され、前記保護溝部の内縁に沿って延在する第2の金属マスクパターンと、

を有することを特徴とする半導体装置。

【請求項2】

前記耐湿リングは積層構造を有し、

前記耐湿リングは、前記積層構造の最上層に最上層パターンを有し、

前記第2の金属マスクパターンは、前記最上層パターンより構成されることを特徴とする請求項1記載の半導体装置。

【請求項3】

前記積層体中、前記保護溝部の外側には、前記耐湿リングと同じ層構造の別のリングが、連続的に延在しており、

前記別のリングは積層構造を有し、

前記別のリングは、前記積層構造の最上層に最上層パターンを有し、

前記第1の金属マスクパターンは、前記最上層パターンより構成されることを特徴とする請求項1記載の半導体装置。

【請求項4】

前記保護溝部の側壁上及び底面上に形成された保護膜を有することを特徴とした請求項1乃至3のいずれか1項に記載の半導体装置。

【請求項5】

前記保護溝部の前記側壁と前記保護膜との間に形成され、SiとCを主成分とする界面膜を有することを特徴とする請求項4に記載の半導体装置。

【請求項6】

活性素子が形成された素子領域を有する基板上に、前記素子領域を囲んで位置する耐湿リングと多層配線構造とを含む積層体と、前記耐湿リングの外側の前記積層体上に、前記耐湿リングを連続して囲んで位置する金属膜と、を形成する工程と、

前記金属膜の少なくとも一部及び前記金属膜の下の前記積層体を除去して、前記耐湿リングを囲んで位置し、前記基板に達する保護溝部を形成する工程と、

を有することを特徴とする半導体装置の製造方法。

【請求項7】

前記保護溝部を形成する工程は、前記保護溝部の外側及び内側のそれぞれに前記金属膜を残すように行われることを特徴とする請求項6に記載の半導体装置の製造方法。

【請求項8】

前記保護溝部を形成する工程の後に、前記保護溝部の側壁面及び底面上に保護膜を形成する工程を有することを特徴とする請求項6または7に記載の半導体装置の製造方法。

【請求項1】

活性素子が形成された素子領域を有する基板と、

前記基板上に形成され、多層配線構造を含む積層体と、

前記積層体中に、前記素子領域を囲んで連続的に延在する耐湿リングと、

前記積層体中、前記耐湿リングの外側に、前記耐湿リングに沿って連続的に、前記基板の表面に達して形成された保護溝部と、

前記積層体上に形成され、前記保護溝部の外縁に沿って延在する第1の金属マスクパターンと、

前記積層体上に形成され、前記保護溝部の内縁に沿って延在する第2の金属マスクパターンと、

を有することを特徴とする半導体装置。

【請求項2】

前記耐湿リングは積層構造を有し、

前記耐湿リングは、前記積層構造の最上層に最上層パターンを有し、

前記第2の金属マスクパターンは、前記最上層パターンより構成されることを特徴とする請求項1記載の半導体装置。

【請求項3】

前記積層体中、前記保護溝部の外側には、前記耐湿リングと同じ層構造の別のリングが、連続的に延在しており、

前記別のリングは積層構造を有し、

前記別のリングは、前記積層構造の最上層に最上層パターンを有し、

前記第1の金属マスクパターンは、前記最上層パターンより構成されることを特徴とする請求項1記載の半導体装置。

【請求項4】

前記保護溝部の側壁上及び底面上に形成された保護膜を有することを特徴とした請求項1乃至3のいずれか1項に記載の半導体装置。

【請求項5】

前記保護溝部の前記側壁と前記保護膜との間に形成され、SiとCを主成分とする界面膜を有することを特徴とする請求項4に記載の半導体装置。

【請求項6】

活性素子が形成された素子領域を有する基板上に、前記素子領域を囲んで位置する耐湿リングと多層配線構造とを含む積層体と、前記耐湿リングの外側の前記積層体上に、前記耐湿リングを連続して囲んで位置する金属膜と、を形成する工程と、

前記金属膜の少なくとも一部及び前記金属膜の下の前記積層体を除去して、前記耐湿リングを囲んで位置し、前記基板に達する保護溝部を形成する工程と、

を有することを特徴とする半導体装置の製造方法。

【請求項7】

前記保護溝部を形成する工程は、前記保護溝部の外側及び内側のそれぞれに前記金属膜を残すように行われることを特徴とする請求項6に記載の半導体装置の製造方法。

【請求項8】

前記保護溝部を形成する工程の後に、前記保護溝部の側壁面及び底面上に保護膜を形成する工程を有することを特徴とする請求項6または7に記載の半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6A】

【図6B】

【図6C】

【図6D】

【図6E】

【図6F】

【図7】

【図8A】

【図8B】

【図8C】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図2】

【図3】

【図4】

【図5】

【図6A】

【図6B】

【図6C】

【図6D】

【図6E】

【図6F】

【図7】

【図8A】

【図8B】

【図8C】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【公開番号】特開2013−30818(P2013−30818A)

【公開日】平成25年2月7日(2013.2.7)

【国際特許分類】

【出願番号】特願2012−247938(P2012−247938)

【出願日】平成24年11月9日(2012.11.9)

【分割の表示】特願2009−508816(P2009−508816)の分割

【原出願日】平成19年3月30日(2007.3.30)

【出願人】(308014341)富士通セミコンダクター株式会社 (2,507)

【Fターム(参考)】

【公開日】平成25年2月7日(2013.2.7)

【国際特許分類】

【出願日】平成24年11月9日(2012.11.9)

【分割の表示】特願2009−508816(P2009−508816)の分割

【原出願日】平成19年3月30日(2007.3.30)

【出願人】(308014341)富士通セミコンダクター株式会社 (2,507)

【Fターム(参考)】

[ Back to top ]