半導体装置およびその製造方法

【課題】実施形態は、一括して形成することが可能なメモリセルを有し、その直下に制御回路を設けた構成を実現する半導体装置およびその製造方法を提供する。

【解決手段】実施形態は、基板上に設けられたメモリアレイと、前記基板と前記メモリアレイとの間の前記基板の表面に設けられた制御回路と、を有する半導体装置の製造方法であって、前記制御回路のp形半導体領域およびn形半導体領域を覆う絶縁層に、前記p形半導体領域に連通する第1のコンタクトホールを形成する工程と、前記第1のコンタクトホールの内部に、前記p形半導体領域に接したコンタクトプラグを形成する工程と、を備える。さらに、前記n形半導体領域に連通する第2のコンタクトホールを前記絶縁層に形成する工程と、前記コンタクトプラグと、前記第2のコンタクトホールの内部に露出した前記n形半導体領域と、に接する配線を形成する工程と、を備える。

【解決手段】実施形態は、基板上に設けられたメモリアレイと、前記基板と前記メモリアレイとの間の前記基板の表面に設けられた制御回路と、を有する半導体装置の製造方法であって、前記制御回路のp形半導体領域およびn形半導体領域を覆う絶縁層に、前記p形半導体領域に連通する第1のコンタクトホールを形成する工程と、前記第1のコンタクトホールの内部に、前記p形半導体領域に接したコンタクトプラグを形成する工程と、を備える。さらに、前記n形半導体領域に連通する第2のコンタクトホールを前記絶縁層に形成する工程と、前記コンタクトプラグと、前記第2のコンタクトホールの内部に露出した前記n形半導体領域と、に接する配線を形成する工程と、を備える。

【発明の詳細な説明】

【技術分野】

【0001】

本発明の実施形態は、半導体装置およびその製造方法に関する。

【背景技術】

【0002】

半導体装置の製造過程における微細加工技術の進展により、半導体メモリの大容量化が実現されてきた。一方、その中核を担うフォトリソグラフィのコストは、微細加工の高度化と共に著しく増加している。そこで、基板上に積層された複数の電極層を貫く複数の孔を一括して形成し、その内部にメモリ構造を形成する半導体装置が提案されている。この方法によれば、複数のメモリストリングを含む3次元メモリアレイを一括して形成することが可能であり、フォトリソグラフィの回数を減らし製造コストの低減を図ることができる。

【0003】

半導体メモリには、大容量化と共に小型化も求められる。例えば、メモリセルを駆動する制御回路をメモリアレイの直下に設け、チップサイズを縮小する半導体装置が提案されている。しかしながら、メモリアレイの製造過程における高温の熱処理がその実現を阻んでいる。そこで、一括して形成することが可能なメモリセルを有し、その直下に制御回路を設けた構成を実現する半導体装置およびその製造方法が必要とされている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2009−94236号公報

【特許文献2】特開平10−50989号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

実施形態は、一括して形成することが可能なメモリセルを有し、その直下に制御回路を設けた構成を実現する半導体装置およびその製造方法を提供する。

【課題を解決するための手段】

【0006】

実施形態は、基板上に設けられたメモリアレイと、前記基板と前記メモリアレイとの間の前記基板の表面に設けられた制御回路と、を有する半導体装置の製造方法であって、前記制御回路のp形半導体領域およびn形半導体領域を覆う絶縁層に、前記p形半導体領域に連通する第1のコンタクトホールを形成する工程と、前記第1のコンタクトホールの内部に、前記p形半導体領域に接したp形不純物を含有するコンタクトプラグを形成する工程と、を備える。さらに、前記絶縁層に前記n形半導体領域に連通する第2のコンタクトホールを形成する工程と、前記コンタクトプラグと、前記第2のコンタクトホールの内部に露出した前記n形半導体領域と、に接する配線を形成する工程と、を備える。

【図面の簡単な説明】

【0007】

【図1】第1の実施形態に係る半導体装置を模式的に例示する斜視図である。

【図2】第1の実施形態に係るメモリアレイを模式的に例示する斜視図である。

【図3】第1の実施形態に係る別のメモリアレイを模式的に例示する斜視図である。

【図4】第1の実施形態に係る半導体装置の製造過程を模式的に示す斜視図である。

【図5】図4に続く製造過程を模式的に示す断面図である。

【図6】図5に続く製造過程を模式的に示す断面図である。

【図7】第2の実施形態に係る半導体装置の製造過程を模式的に示す斜視図である。

【図8】図7に続く製造過程を模式的に示す断面図である。

【図9】図8に続く製造過程を模式的に示す断面図である。

【図10】図9に続く製造過程を模式的に示す断面図である。

【図11】第2の実施形態の第1変形例に係る半導体装置の製造過程を模式的に示す断面図である。

【図12】図11に続く製造過程を模式的に示す断面図である。

【図13】第2の実施形態の第2変形例に係る半導体装置の製造過程を模式的に示す断面図である。

【図14】図13に続く製造過程を模式的に示す断面図である。

【図15】第2の実施形態の第3変形例に係る半導体装置の製造過程を模式的に示す断面図である。

【図16】図15に続く製造過程を模式的に示す断面図である。

【図17】第2の実施形態の第4変形例に係る半導体装置の製造過程を模式的に示す断面図である。

【図18】図15に続く製造過程を模式的に示す断面図である。

【発明を実施するための形態】

【0008】

以下、本発明の実施の形態について図面を参照しながら説明する。なお、図面中の同一部分には同一番号を付してその詳しい説明は適宜省略し、異なる部分について適宜説明する。

【0009】

[第1の実施形態]

図1は、第1の実施形態に係る半導体装置100を模式的に例示する斜視図である。同図に示すように、半導体装置100は、例えば、基板2の上に設けられたメモリアレイ3と、基板2とメモリアレイ3との間の基板2の表面に設けられた制御回路7および8と、を有する。基板2とメモリアレイ3との間には、メモリアレイ3と、制御回路7、8を電気的に分離する絶縁層5が設けられる。さらに、絶縁層5の中には、配線9が形成され、制御回路7、8と、メモリアレイ3と、の間を、電気的に接続する。図1中に示す配線9は単層であるが、複数の配線層と層間絶縁膜が交互に設けられる多層配線であっても良い。

【0010】

制御回路7および8は、例えば、センスアンプ、ワード線ドライバおよび高電圧を発生するポンプ回路であり、メモリアレイ3を駆動するために基板2の表面に設けられる。制御回路7および8は、例えば、複数のMOSトランジスタを含む集積回路である。

【0011】

半導体装置100を製作する場合、まず、基板2の表面に、制御回路7および8と、配線9と、を形成する。次に、絶縁層5を介してメモリアレイ3を形成する。したがって、基板2の表面に集積回路を完成させてから、再度、メモリアレイ3の製造プロセスを実行することになる。このため、メモリアレイ3の製造過程における高温の熱処理を受けた後に、制御回路7および8の特性が変化しない、もしくは、制御回路7および8が正常に動作することが望まれる。

【0012】

次に、図2および図3を参照して、本実施形態に係るメモリアレイ3の例を説明する。図2は、基板2の表面に垂直なZ方向に延在するメモリストリングを含む垂直型のメモリアレイ10を模式的に示す斜視図である。一方、図3は、基板2の表面に平行なX方向に延在するメモリストリングスを含む横型のメモリアレイ20を模式的に示す斜視図である。

【0013】

図2に示すメモリアレイ10では、基板2の上に絶縁層5を介して、複数の電極層12、13、14およびソース線18が積層される。そして、電極層12、13、14をZ方向に貫く複数のシリコンピラー15が設けられる。シリコンピラー15の両端は、ビット線17と、ソース線18と、に接続される。電極層12、13、14、ソース線18およびビット線17の間には、図示しない絶縁層が設けられ、それぞれを電気的に分離する。

【0014】

シリコンピラー15には、チャネル層と、ゲート絶縁膜と、電荷蓄積層と、を含むメモリ構造が設けられる(図3参照)。複数の電極層12のそれぞれはワード線として機能し、メモリ構造に保持される電荷を制御する。電極層13および14は、選択トランジスタの選択ゲートとして機能する。すなわち、シリコンピラー15および電極層12、13、14により、複数のメモリセルが直列につながったNAND型メモリストリングが形成される。

【0015】

前述したように、基板2とメモリアレイ10との間の基板2の表面には、制御回路7が設けられる。そして、図示しない部分において、絶縁層5に設けられた配線9により、制御回路7と、メモリアレイ10と、が電気的に接続される。

【0016】

メモリアレイ10の製造過程では、基板2の上に設けられた複数の電極層12、13および14を貫く複数の開口を一括して形成し、その中にメモリ構造を形成する。これにより、例えば、1回のフォトリソグラフィで、3次元メモリアレイの主要部を形成することが可能となる。

【0017】

一方、図3に示す横型のメモリアレイ20では、複数のワード線21をX方向に貫くシリコンビーム23が設けられる。この場合も、Z方向にシリコン酸化膜を介して積層された複数のポリシリコン(多結晶シリコン)層を、X方向に延在するストライプ形状に一括して加工することにより、複数のシリコンビーム23を形成する。

【0018】

そして、Y−Z面に平行に延在し、且つ、X方向に離間して並んだ複数のシリコン酸化層31を形成する。この際、隣り合うシリコン酸化層31の間に、シリコンビーム23の一部が露出した空間が形成される。そして、その空間に、シリコン酸化膜24aと、シリコン窒化膜24bと、シリコン酸化膜24cと、ポリシリコン層21と、を順に形成する。これにより、シリコンビーム23の周りを囲んだONO構造(シリコン酸化膜24a/シリコン窒化膜24b/シリコン酸化膜24cの積層構造)と、隣り合うシリコンビーム23の間を埋めたポリシリコン層21と、を形成することができる。

【0019】

メモリアレイ20では、シリコンビーム23はチャネル層として機能し、シリコン酸化膜24aはゲート絶縁膜、シリコン窒化膜24bは電荷蓄積層として機能する。シリコン酸化膜24cは、ポリシリコン層21とシリコン窒化膜24bとの間を絶縁する。そして、ポリシリコン層21はワード線として機能し、シリコン窒化膜24bに蓄積される電荷を制御し、さらに、シリコンビーム23とシリコン酸化膜24aとの間に形成されるチャネルをオン・オフ制御する。

【0020】

メモリアレイ20では、シリコンビーム23と、複数のワード線21と、により、横方向に延在するメモリストリングが形成される。シリコンビーム23の図示しない両端には、ビット線およびソース線が設けられる。また、複数のワード線21の両側には、図示しない選択ゲートが設けられる。そして、基板2とメモリアレイ20との間の、基板2の表面に設けられた制御回路7と、例えば、ワード線、ビット線および選択ゲートとが、配線9を介して電気的に接続される。

【0021】

上記のような、メモリアレイ10および20では、その特性を向上させるために、例えば、シリコンピラー15およびシリコンビーム23と、ONO構造の積層膜と、を高温で熱処理することが好ましい。そして、その熱処理に対し、基板2の表面に設けられる制御回路は、その特性の変化を抑制できる構造を備えることが望まれる。

【0022】

次に、図4〜図6を参照して、本実施形態に係る半導体装置100の製造過程を説明する。ここに示す図4〜図6(b)は、シリコン基板2の表面に設けられる制御回路の製造過程の一部を例示する模式図である。

【0023】

最初に、制御回路として、例えば、PMOSトランジスタとNMOSトランジスタを含むCMOS回路を設ける。続いて、シリコン基板2の表面を覆う絶縁層25を形成し、例えば、制御回路とメモリアレイをつなぐ配線、および、電源もしくは接地電位に接続される配線などを設ける。

【0024】

図4は、制御回路のp形半導体領域33およびn形半導体領域34を覆う絶縁層25に、p形半導体領域33に連通する第1のコンタクトホール28と、n形半導体領域34に連通する第2のコンタクトホール29と、を形成した状態を示す斜視図である。同図に示すように、コンタクトホール28および29は、配線溝27の底部に形成される。

【0025】

コンタクトホール28および29を形成する過程には、高度な微細加工技術を適用する。このため、p形半導体領域33に連通するコンタクトホール28と、n形半導体領域34に連通するコンタクトホール29と、を同時に形成することにより、フォトリソグラフィのコストを低減することが好ましい。

【0026】

p形半導体領域33は、例えば、PMOSトランジスタのソースもしくはドレイン領域、または、それらにつながるコンタクト領域である。また、NMOSトランジスタのボディ領域につながるコンタクト領域であっても良い。これらのp形半導体領域33には、例えば、p形不純物であるボロン(B)がドープされる。一方、n形半導体領域34は、例えば、NMOSトランジスタのソースもしくはドレイン領域、または、それらにつながるコンタクト領域である。また、PMOSトランジスタのボディ領域につながるコンタクト領域の場合もある。これらのn形半導体領域34には、例えば、n形不純物である砒素(As)がドープされる。

【0027】

p形半導体領域33とn形半導体領域34との間には、例えば、STI(Shallow Trench Isolation)35が形成される。そして、p形半導体領域33とn形半導体領域34とを覆う絶縁層25には、例えば、TEOS(TetraEthOxySilane)を用いたCVD(Chemical Vapor Deposition)法により形成されるシリコン酸化膜を用いることができる。

【0028】

次に、図5に示すように、コンタクトホール28の底部に露出したp形半導体領域33に炭素イオン(C+)を注入する。この際、n形半導体領域34に連通するコンタクトホール29をレジスト膜36で覆い、n形半導体領域34に炭素が注入されないようにする。

【0029】

炭素のイオン注入は、例えば、注入エネルギーを3keVとし、ドーズ量を1×1015cm−2として行う。さらに、p形不純物であるボロン(B)をイオン注入してから炭素イオンを注入しても良い。例えば、注入エネルギー5keV、ドーズ量3×1015cm−2の条件でボロンをイオン注入した後に、上記の条件で炭素をイオン注入する。

【0030】

レジスト膜36は、コンタクトホール29を覆い、コンタクトホール29の底部に炭素がイオン注入されないようにするために設けられるので、粗い精度のフォトリソグラフィにより形成することができる。すなわち、低コストのフォトリソグラフィ技術を用いることができる。

【0031】

次に、レジスト膜36を除去し、注入した元素を活性化させるために、熱処理を行う。例えば、RTA(Rapid thermal annealing)法により950℃、10秒間程度の熱処理を行う。そして、希釈したフッ酸溶液を用いて、コンタクトホール28および29の底部に露出したp形半導体領域33およびn形半導体領域34の自然酸化膜を除去し、コンタクトプラグとなる金属膜を堆積する。

【0032】

図6(a)に示すように、例えば,チタン(Ti)層と窒化チタン(TiN)層とを積層したTi/TiN膜37と、タングステン(W)膜38と、をCVD法により順次堆積する。最初に堆積されるTi層は、コンタクトホール28の底部に露出したp形半導体領域と、コンタクトホール29の底部に露出したn形半導体領域34と、絶縁層25の表面と、に接して形成される。

【0033】

例えば、Ti層は、塩化チタン(TiCl4)を原料として、CVD法を用いて堆積される。この際、堆積温度を600℃以上とすることにより、p形半導体領域33およびn形半導体領域34と、Ti層と、の界面に、シリサイド層41aおよび41bがそれぞれ形成される。

【0034】

続いて、Ti層の上にTiN膜を形成し、さらに、W膜38をTi/TiN膜37よりも厚く形成し、コンタクトホール28および29の内部、および、配線溝27の内部を埋め込む。

【0035】

続いて、図6(b)に示すように、絶縁層25の上面に形成されたTi/TiN膜37およびW膜38をCMP(Chemical mechanical polishing)法により除去する。これにより、コンタクトホール28および29の内部に埋め込まれたコンタクトプラグと、配線溝27に埋め込まれた層間配線と、を含む、所謂デュアルダマシン配線が形成される。

【0036】

さらに、本実施形態では、図6(a)および(b)に示すように、コンタクトホール28の底部において、Ti/TiN膜37に接するp形半導体領域33の表面に、炭素(C)が注入された層39と、その一部に重なるシリサイド層41aが形成される。

【0037】

以降の工程では、例えば、絶縁層25の上に層間絶縁膜を配し、2層目のコンタクトプラグおよび配線を形成した多層配線構造を設ける。そして、その多層配線構造の上に絶縁層を形成し、その後、メモリアレイ3を形成する。例えば、図1に示す基板2とメモリアレイ3との間の絶縁層5は、絶縁層25と、多層配線と、その上に設けられる絶縁層と、を含む層である。さらに,メモリアレイ3の上部に、電源線やグローバルな信号線を配し半導体装置100を完成する。

【0038】

前述したように、メモリアレイ3の製造過程では、高温の熱処理が施される。例えば、ポリシリコン層を熱処理して結晶化させ、移動度を向上させれば、読み出し電流値を大きくすることができる。このために、例えば、制御回路7および8を形成した基板2を、900℃以上の温度に設定した熱処理炉に搬入し、10分以上の処理を行う場合がある。これは、同じ温度に設定したRTA法による短時間の熱処理に比べて、過酷な処理となる。

【0039】

例えば、上記の多層配線では、第2層目の配線として、第1層目と同じTi/TiN/Wの積層構造を有する金属膜を用いることができる。第2層目のコンタクトプラグと、第1層目の配線と、の接点では、第2層目のTi層と、第1層目のW膜38と、が接触する。このため、低抵抗のコンタクトが形成され、熱的にも安定した配線となる。これにより、メモリアレイ3の製造工程における熱処理に耐える金属配線を実現することができる。

【0040】

また、上記の配線に代えて、例えば、導電性のポリシリコンを用いた配線を形成することも考えられる。しかしながら、ポリシリコンによる配線は、金属配線に比べて高抵抗である。このため、メモリアレイと制御回路との間の信号伝送の速度が低下し、半導体装置100の動作が遅くなるという問題を生じる。したがって、メモリアレイと制御回路との間に設けられる配線には、金属を用いることが好ましい。さらに、メモリアレイの製造過程における高温の熱処理に耐えるように、Ti、W等の高融点金属を用いることが望ましい。

【0041】

さらに、本実施形態では、図6(b)に示すように、p形半導体領域33と、コンタクトプラグ(Ti/TiN膜37+W膜38)と、が接する界面に炭素の注入層39を介在させる。これにより、p形半導体領域33にドープされたボロンの拡散を抑制し、p形半導体領域33とコンタクトプラグとの間におけるシリサイド層41aを介した低抵抗のオーミックコンタクトを維持することができる。

【0042】

すなわち、炭素の注入層39では、メモリアレイ3の製造過程における高温処理においてボロンの拡散が抑えられ、p形不純物の濃度の低下が抑制される。これにより、低抵抗のオーミックコンタクトを維持することができる。

【0043】

本実施形態のように、低加速エネルギーでイオンの注入を行った場合、炭素(C)はp形半導体領域33の表面近傍に分布する。このため、例えば、Ti/TiN膜37とp形半導体領域33とが反応して形成されるシリサイド層41aの中にもカーボンが取り込まれる。これにより、シリサイド層41aへのボロン(B)の吸い上げが抑えられ、p形半導体領域33の側のボロン濃度の低下を抑制することができる。

【0044】

また、MOSトランジスタのゲート電極から離間して設けられるコンタクトホール28の底部に炭素をイオン注入するため、炭素のトランジスタ特性への影響を回避することが可能であり、信頼性の高い半導体装置を実現することができる。

【0045】

一方、n形半導体領域34では、n形不純物として砒素(As)がドープされている。砒素の拡散係数は、例えば、ボロンに比べて小さい。このため、メモリアレイ3の製造過程における高温の熱処理を受けても、As濃度の変化は小さく、n形半導体領域34と、コンタクトプラグと、の間のコンタクト抵抗を低く維持することができる。

【0046】

上記の通り、本実施形態に係る半導体装置100では、基板2に設けられた制御回路と、メモリアレイ3と、の間を高融点金属の配線により接続し、p形半導体領域33と、コンタクトプラグと、の間に炭素をイオン注入した注入層39を介在させる。これにより、メモリアレイ3の製造過程における高温の熱処理に耐える配線の形成が可能となり、メモリアレイ3の下に制御回路を配した構造によるチップサイズ縮小と高速化とが実現される。

【0047】

本実施形態では、p形半導体領域33に炭素をイオン注入する例を示したが、これに限られる訳ではない。シリコンを含む半導体結晶に炭素をイオン注入した場合、結晶欠陥と、注入された炭素原子と、が結合して不純物の拡散を抑制する。したがって、ボロンがドープされたp形半導体領域33に限らず、他の不純物がドープされたp形半導体領域、もしくは、n形半導体領域においても同様の効果が得られる場合があり、本実施形態を変形して適用することが可能である。また、基板2の上に設けられるメモリアレイ3は、図2および図3に示した構造に限らず、他の3次元メモリアレイであっても良い。

【0048】

[第2の実施形態]

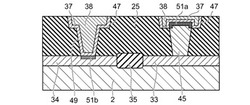

図7〜図10は、第2の実施形態に係る半導体装置100の製造過程を模式的に示す斜視図である。本実施形態に係る半導体装置100は、p形半導体領域33に接続されたポリシリコンからなるコンタクトプラグを有する点で、第1の実施形態と相違する。以下、図7〜図10を参照して、その製造過程について説明する。

【0049】

まず、図7に示すように、基板2の上に設けられた制御回路のp形半導体領域33およびn形半導体領域34を覆う絶縁層25aに、p形半導体領域33に連通する第1のコンタクトホール43を形成する。

【0050】

次に、コンタクトホール43の底部に露出したp形半導体領域33の表面の自然酸化膜を、希釈したフッ酸溶液で除去する。そして、図8(a)に示すように、例えば、CVD法を用いて、絶縁層25aの上にポリシリコン層45aを堆積し、コンタクトホール43の内部を埋め込む。ポリシリコン層45aは、好ましくは、p形半導体領域33よりも高濃度のp形不純物を含む導電層である。例えば、1×1021cm−3以上のボロン(B)を含むp形の導電層とする。

【0051】

続いて、絶縁層25aの上面に堆積したポリシリコン層45aを、例えば、CMP法を用いて除去し、コンタクトホール43の内部に埋め込まれたコンタクトプラグ45を形成する。さらに、図8(b)に示すように、絶縁層25aの上に絶縁層25bを形成する。絶縁層25aおよび絶縁層25bは、例えば、TEOSを原料とするCVD法を用いて形成されるシリコン酸化膜である。

【0052】

次に、図9(a)に示すように、n形半導体領域34に連通するコンタクトホール49、および、配線溝47を形成する。同時に、図示しないゲート電極のコンタクトホールを形成しても良い。p形半導体領域33の側では、コンタクトプラグ45の一部が配線溝47の底部から突出した状態に形成する。これにより、配線溝47に形成される金属配線と、コンタクトプラグ45と、の間の接触面積を広くしてコンタクト抵抗を下げることができる。なお、図9(a)に示す絶縁層25は、絶縁層25aと絶縁層25bとを含む。

【0053】

続いて、コンタクトホール49の底部に露出するn形半導体領域34の表面や、配線溝47の底面から突出したコンタクトプラグ45の表面の自然酸化膜を、希釈したフッ酸溶液により除去する。そして、図9(b)に示すように、コンタクトホール49の内部、および、配線溝47の内部に金属膜を堆積する。例えば、Ti/TiN膜37と、W膜38と、をCVD法を用いて順次堆積する。この際、前述したように、コンタクトプラグ45と、Ti/TiN膜37と、の間の界面、および、n形半導体領域34と、Ti/TiN膜37と、の間の界面に、それぞれシリサイド層51aおよび51bが形成される。

【0054】

次に、図10に示すように、絶縁層25の上面に堆積した金属膜を、例えば、CMP法を用いて除去する。さらに、前述したように、層間絶縁膜を配して複数の配線層を形成し、メモリアレイ3を形成して半導体装置100を完成する。

【0055】

このように、本実施形態によれば、n形半導体領域34の側では、コンタクトプラグおよび配線が同時に形成されるデュアルダマシン構造となり、p形半導体領域33の側では、コンタクトプラグ45と、配線とが、それぞれ別に形成されるシングルダマシン構造となる。

【0056】

また、p形半導体領域33に接するコンタクトプラグ45は、高濃度のp形不純物を含む。そして、コンタクトプラグ45の内部では、p形不純物の拡散が結晶粒界を介して速やかに行われる。このため、例えば、メモリアレイ3の製造過程における高温の熱処理が施され、コンタクトプラグ45から金属配線(Ti/TiN膜37)側にp形不純物が拡散したとしても、コンタクトプラグ45の内部のp形不純物が界面に供給され不純物濃度の低下を抑制する。このため、金属配線とコンタクトプラグ45との間で、低抵抗のオーミックコンタクトを維持することができる。

【0057】

一方、p形半導体領域33と、コンタクトプラグ45と、の間においても、コンタクトプラグ45の側からp形半導体領域33へp形不純物が供給される。これにより、p形半導体領域33の側で生じるp形不純物濃度の低下が補償され、低抵抗のオーミックコンタクトを維持することが可能である。

【0058】

さらに、図8(a)に示すポリシリコン層45aの堆積の際に、C2H6等のドーピングガスを添加することができる。これにより、p形不純物に加えて、炭素を含むポリシリコン層45aを形成することができる。そして、コンタクトプラグ45にも、p形不純物と炭素とを含有させることができる。その結果、コンタクトプラグ45から金属配線、および、p形半導体領域へのp形不純物の過度な拡散を抑制することが可能となる。これにより、コンタクトプラグ45と金属配線との間、および、コンタクトプラグ45とp形半導体領域との間の耐熱性を向上させることができる。

【0059】

このように、本実施形態では、p形半導体領域33へ連通するコンタクトホールのみにポリシリコンのコンタクトプラグを介在させることにより、耐熱性の高い金属配線を形成することができる。これにより、メモリアレイ3の下に制御回路を設け、その間を金属配線で結線することが可能となり、半導体装置100のチップサイズ縮小と、高速化と、を低コストで実現することができる。

【0060】

図11〜図12は、第2の実施形態の第1変形例に係る半導体装置の製造過程を模式的に示す断面図である。

【0061】

本変形例では、図11(a)に示すように、p形半導体領域33に連通するコンタクトホール43の内部にコンタクトプラグ45を形成した後、炭素をイオン注入する。これにより、コンタクトプラグ45の上部に注入層39が形成される。この場合、n形半導体領域34に連通するコンタクトホールが形成されていないので、レジスト膜36を形成する工程を省くことができる。すなわち、絶縁層25aの上面に堆積した金属配線を除去した後、基板2の全面に炭素をイオン注入すれば良い。

【0062】

続いて、絶縁層25aの上に絶縁層25bを形成し(図8(b)参照)、図11(b)に示すように、n形半導体領域34に連通するコンタクトホール49と、配線溝27と、を形成する。

【0063】

さらに、図12(a)に示すように、コンタクトホール49の内部、および、配線溝47の内部に、Ti/TiN膜37およびW膜38を堆積する。そして、コンタクトプラグ45の上部には、注入層39と、それに重なるシリサイド層51aが形成される。

【0064】

続いて、図12(b)に示すように、絶縁層25の上面に堆積した金属配線(Ti/TiN膜37およびW膜38)を除去し、第1層目の金属配線を完成させる。

【0065】

このように、本変形例では、フォトリソグラフィーの追加なしに,コンタクトプラグ45の上部に炭素の注入層39を形成し、金属配線とコンタクトプラグ45との間の熱耐性を向上させることができる。これにより、メモリアレイ3の製造過程における熱処理の影響を、より低コストで効果的に抑制することができる。

【0066】

図13〜図14は、第2の実施形態の第2変形例に係る半導体装置の製造過程を模式的に示す断面図である。

【0067】

本変形例では、図13(a)に示すように、p形半導体領域33とn形半導体領域34とを覆う絶縁層25aに、p形半導体領域33に連通するコンタクトホール43を形成し、その後に、炭素のイオン注入を行う。この場合も、n形半導体領域34に連通するコンタクトホールが形成されていないので、基板2の全面にイオン注入することができる。すなわち、フォトリソグラフィを省力した低コストの工程により、p形半導体領域33の表面に、選択的に炭素の注入層39を形成することができる。

【0068】

続いて、図13(b)に示すように、コンタクトホール43の内部に、p形ポリシリコンからなるコンタクトプラグ45を形成する。

【0069】

次に、絶縁層25aの上に絶縁層25bを形成し(図8(b)参照)、図14(a)に示すように、n形半導体領域34に連通するコンタクトホール49と、配線溝27と、を形成する。続いて、コンタクトホール49の内部、および、配線溝47の内部に、Ti/TiN膜37およびW膜38を堆積する。そして、図14(b)に示すように、絶縁層25の上面に堆積した金属配線を除去し、第1層目の金属配線を完成させる。

【0070】

本変形例によれば、コンタクトホール43の底部において、p形半導体領域33の表面に炭素の注入層39を形成することによりp形不純物の拡散を抑制し、コンタクトプラグ45と、p形半導体領域33と、の界面の熱耐性を向上させることができる。

【0071】

図15〜図16は、第2の実施形態の第3変形例に係る半導体装置の製造過程を模式的に示す断面図である。

【0072】

本変形例では、図15(a)に示すように、p形半導体領域33とn形半導体領域34とを覆う絶縁層25aに、p形半導体領域33に連通するコンタクトホール43を形成し、さらに、コンタクトホール43の側面である絶縁層25aの表面にシリコン窒化膜53を形成する。シリコン窒化膜53は、例えば、CVD法を用いて絶縁層25aの上面およびコンタクトホール43の内面に形成する。そして、異方性のドライエッチングにより、絶縁層25aの上面およびコンタクトホール43の底面に形成されたシリコン窒化膜を除去することにより、コンタクトホール43の側面にのみシリコン窒化膜53を残すことができる。

【0073】

続いて、図15(b)に示すように、コンタクトホール43の内部に、p形ポリシリコンからなるコンタクトプラグ45を形成する。

【0074】

次に、絶縁層25aの上に絶縁層25bを形成し、図16(a)に示すように、n形半導体領域34に連通するコンタクトホール49と、配線溝27と、を形成する。続いて、コンタクトホール49の内部、および、配線溝47の内部に、Ti/TiN膜37およびW膜38を堆積する。そして、図14(b)に示すように、絶縁層25の上面に堆積した金属配線を除去して第1層目の金属配線を完成させる。

【0075】

本変形例によれば、コンタクトホール43の側面に設けられたシリコン窒化膜53が、コンタクトプラグ45から絶縁層25に向かうp形不純物の拡散を抑える。これにより、コンタクトプラグ45の中のp形不純物の濃度の低下を抑制し、その熱耐性を向上させることができる。

【0076】

図17〜図18は、第2の実施形態の第4変形例に係る半導体装置の製造過程を模式的に示す断面図である。

【0077】

本変形例では、図17(a)に示すように、p形半導体領域33とn形半導体領域34とを覆う絶縁層25aに、p形半導体領域33に連通するコンタクトホール43を形成する。そして、p形半導体領域33の表面の自然酸化膜を除去した後、コンタクトホール43の内部にポリシリコン層45a(図8(a)参照)を堆積する前に、例えば、アンモニア(NH3)を含む高温の雰囲気にさらす。これにより、コンタクトホール43の底部に露出したp形半導体領域33の表面に、薄いシリコン窒化膜55を形成することができる。

【0078】

続いて、図17(b)に示すように、コンタクトホール43の内部に、p形ポリシリコンからなるコンタクトプラグ45を形成する。

【0079】

次に、絶縁層25aの上に絶縁層25bを形成し、図18(a)に示すように、n形半導体領域34に連通するコンタクトホール49と、配線溝27と、を形成する。さらに、コンタクトホール49の内部、および、配線溝47の内部に、Ti/TiN膜37およびW膜38を堆積する。そして、図18(b)に示すように、絶縁層25の上面に堆積した金属配線を除去し、第1層目の金属配線を完成させる。

【0080】

本変形例によれば、コンタクトホール43の底部に設けられたシリコン窒化膜55が、コンタクトプラグ45からp形半導体領域33に向かうp形不純物の拡散を抑える。これにより、コンタクトプラグ45の中のp形不純物の濃度の低下を抑制し、その熱耐性を向上させることができる。

【0081】

シリコン窒化膜55の厚さは、例えば、1nm以下とする。これにより、p形半導体領域33とコンタクトプラグ45との間の電気抵抗に大きな影響を与えることなく、p形不純物の拡散を抑制することができる。

【0082】

上記の第2の実施形態に係る製造過程、および、第1〜第4変形例に係る製造工程は、組み合わせて実施することが可能であり、コンタクトプラグ45と、p形半導体領域33および金属配線と、の間の熱耐性をさらに向上させることができる。

【0083】

以上、本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

また、前述した各具体例が備える各要素は、可能な限りにおいて組み合わせることができ、これら組み合わせたものも、本発明の特徴を含む限り本発明の範囲に包含される。

【符号の説明】

【0084】

2・・・基板(シリコン基板)、 3、10、20・・・メモリアレイ、 5・・・絶縁層、 7、8・・・制御回路、 9・・・配線、 12、13・・・電極層、 15・・・シリコンピラー、 17・・・ビット線、 18・・・ソース線、 21・・・ワード線(ポリシリコン層)、 23・・・シリコンビーム、 24a、24c、31・・・シリコン酸化膜、 24b、53、55・・・シリコン窒化膜、 25、25a、25b・・・絶縁層、 27・・・配線溝、 28、29、43、49・・・コンタクトホール、 33・・・p形半導体領域、 34・・・n形半導体領域、 36・・・レジスト膜、 37・・・Ti/TiN膜、 38・・・W膜、 39・・・注入層、 41a、41b、51a、51b・・・シリサイド層、 45・・・コンタクトプラグ、 45a・・・ポリシリコン層、 47・・・配線溝、 100・・・半導体装置

【技術分野】

【0001】

本発明の実施形態は、半導体装置およびその製造方法に関する。

【背景技術】

【0002】

半導体装置の製造過程における微細加工技術の進展により、半導体メモリの大容量化が実現されてきた。一方、その中核を担うフォトリソグラフィのコストは、微細加工の高度化と共に著しく増加している。そこで、基板上に積層された複数の電極層を貫く複数の孔を一括して形成し、その内部にメモリ構造を形成する半導体装置が提案されている。この方法によれば、複数のメモリストリングを含む3次元メモリアレイを一括して形成することが可能であり、フォトリソグラフィの回数を減らし製造コストの低減を図ることができる。

【0003】

半導体メモリには、大容量化と共に小型化も求められる。例えば、メモリセルを駆動する制御回路をメモリアレイの直下に設け、チップサイズを縮小する半導体装置が提案されている。しかしながら、メモリアレイの製造過程における高温の熱処理がその実現を阻んでいる。そこで、一括して形成することが可能なメモリセルを有し、その直下に制御回路を設けた構成を実現する半導体装置およびその製造方法が必要とされている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2009−94236号公報

【特許文献2】特開平10−50989号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

実施形態は、一括して形成することが可能なメモリセルを有し、その直下に制御回路を設けた構成を実現する半導体装置およびその製造方法を提供する。

【課題を解決するための手段】

【0006】

実施形態は、基板上に設けられたメモリアレイと、前記基板と前記メモリアレイとの間の前記基板の表面に設けられた制御回路と、を有する半導体装置の製造方法であって、前記制御回路のp形半導体領域およびn形半導体領域を覆う絶縁層に、前記p形半導体領域に連通する第1のコンタクトホールを形成する工程と、前記第1のコンタクトホールの内部に、前記p形半導体領域に接したp形不純物を含有するコンタクトプラグを形成する工程と、を備える。さらに、前記絶縁層に前記n形半導体領域に連通する第2のコンタクトホールを形成する工程と、前記コンタクトプラグと、前記第2のコンタクトホールの内部に露出した前記n形半導体領域と、に接する配線を形成する工程と、を備える。

【図面の簡単な説明】

【0007】

【図1】第1の実施形態に係る半導体装置を模式的に例示する斜視図である。

【図2】第1の実施形態に係るメモリアレイを模式的に例示する斜視図である。

【図3】第1の実施形態に係る別のメモリアレイを模式的に例示する斜視図である。

【図4】第1の実施形態に係る半導体装置の製造過程を模式的に示す斜視図である。

【図5】図4に続く製造過程を模式的に示す断面図である。

【図6】図5に続く製造過程を模式的に示す断面図である。

【図7】第2の実施形態に係る半導体装置の製造過程を模式的に示す斜視図である。

【図8】図7に続く製造過程を模式的に示す断面図である。

【図9】図8に続く製造過程を模式的に示す断面図である。

【図10】図9に続く製造過程を模式的に示す断面図である。

【図11】第2の実施形態の第1変形例に係る半導体装置の製造過程を模式的に示す断面図である。

【図12】図11に続く製造過程を模式的に示す断面図である。

【図13】第2の実施形態の第2変形例に係る半導体装置の製造過程を模式的に示す断面図である。

【図14】図13に続く製造過程を模式的に示す断面図である。

【図15】第2の実施形態の第3変形例に係る半導体装置の製造過程を模式的に示す断面図である。

【図16】図15に続く製造過程を模式的に示す断面図である。

【図17】第2の実施形態の第4変形例に係る半導体装置の製造過程を模式的に示す断面図である。

【図18】図15に続く製造過程を模式的に示す断面図である。

【発明を実施するための形態】

【0008】

以下、本発明の実施の形態について図面を参照しながら説明する。なお、図面中の同一部分には同一番号を付してその詳しい説明は適宜省略し、異なる部分について適宜説明する。

【0009】

[第1の実施形態]

図1は、第1の実施形態に係る半導体装置100を模式的に例示する斜視図である。同図に示すように、半導体装置100は、例えば、基板2の上に設けられたメモリアレイ3と、基板2とメモリアレイ3との間の基板2の表面に設けられた制御回路7および8と、を有する。基板2とメモリアレイ3との間には、メモリアレイ3と、制御回路7、8を電気的に分離する絶縁層5が設けられる。さらに、絶縁層5の中には、配線9が形成され、制御回路7、8と、メモリアレイ3と、の間を、電気的に接続する。図1中に示す配線9は単層であるが、複数の配線層と層間絶縁膜が交互に設けられる多層配線であっても良い。

【0010】

制御回路7および8は、例えば、センスアンプ、ワード線ドライバおよび高電圧を発生するポンプ回路であり、メモリアレイ3を駆動するために基板2の表面に設けられる。制御回路7および8は、例えば、複数のMOSトランジスタを含む集積回路である。

【0011】

半導体装置100を製作する場合、まず、基板2の表面に、制御回路7および8と、配線9と、を形成する。次に、絶縁層5を介してメモリアレイ3を形成する。したがって、基板2の表面に集積回路を完成させてから、再度、メモリアレイ3の製造プロセスを実行することになる。このため、メモリアレイ3の製造過程における高温の熱処理を受けた後に、制御回路7および8の特性が変化しない、もしくは、制御回路7および8が正常に動作することが望まれる。

【0012】

次に、図2および図3を参照して、本実施形態に係るメモリアレイ3の例を説明する。図2は、基板2の表面に垂直なZ方向に延在するメモリストリングを含む垂直型のメモリアレイ10を模式的に示す斜視図である。一方、図3は、基板2の表面に平行なX方向に延在するメモリストリングスを含む横型のメモリアレイ20を模式的に示す斜視図である。

【0013】

図2に示すメモリアレイ10では、基板2の上に絶縁層5を介して、複数の電極層12、13、14およびソース線18が積層される。そして、電極層12、13、14をZ方向に貫く複数のシリコンピラー15が設けられる。シリコンピラー15の両端は、ビット線17と、ソース線18と、に接続される。電極層12、13、14、ソース線18およびビット線17の間には、図示しない絶縁層が設けられ、それぞれを電気的に分離する。

【0014】

シリコンピラー15には、チャネル層と、ゲート絶縁膜と、電荷蓄積層と、を含むメモリ構造が設けられる(図3参照)。複数の電極層12のそれぞれはワード線として機能し、メモリ構造に保持される電荷を制御する。電極層13および14は、選択トランジスタの選択ゲートとして機能する。すなわち、シリコンピラー15および電極層12、13、14により、複数のメモリセルが直列につながったNAND型メモリストリングが形成される。

【0015】

前述したように、基板2とメモリアレイ10との間の基板2の表面には、制御回路7が設けられる。そして、図示しない部分において、絶縁層5に設けられた配線9により、制御回路7と、メモリアレイ10と、が電気的に接続される。

【0016】

メモリアレイ10の製造過程では、基板2の上に設けられた複数の電極層12、13および14を貫く複数の開口を一括して形成し、その中にメモリ構造を形成する。これにより、例えば、1回のフォトリソグラフィで、3次元メモリアレイの主要部を形成することが可能となる。

【0017】

一方、図3に示す横型のメモリアレイ20では、複数のワード線21をX方向に貫くシリコンビーム23が設けられる。この場合も、Z方向にシリコン酸化膜を介して積層された複数のポリシリコン(多結晶シリコン)層を、X方向に延在するストライプ形状に一括して加工することにより、複数のシリコンビーム23を形成する。

【0018】

そして、Y−Z面に平行に延在し、且つ、X方向に離間して並んだ複数のシリコン酸化層31を形成する。この際、隣り合うシリコン酸化層31の間に、シリコンビーム23の一部が露出した空間が形成される。そして、その空間に、シリコン酸化膜24aと、シリコン窒化膜24bと、シリコン酸化膜24cと、ポリシリコン層21と、を順に形成する。これにより、シリコンビーム23の周りを囲んだONO構造(シリコン酸化膜24a/シリコン窒化膜24b/シリコン酸化膜24cの積層構造)と、隣り合うシリコンビーム23の間を埋めたポリシリコン層21と、を形成することができる。

【0019】

メモリアレイ20では、シリコンビーム23はチャネル層として機能し、シリコン酸化膜24aはゲート絶縁膜、シリコン窒化膜24bは電荷蓄積層として機能する。シリコン酸化膜24cは、ポリシリコン層21とシリコン窒化膜24bとの間を絶縁する。そして、ポリシリコン層21はワード線として機能し、シリコン窒化膜24bに蓄積される電荷を制御し、さらに、シリコンビーム23とシリコン酸化膜24aとの間に形成されるチャネルをオン・オフ制御する。

【0020】

メモリアレイ20では、シリコンビーム23と、複数のワード線21と、により、横方向に延在するメモリストリングが形成される。シリコンビーム23の図示しない両端には、ビット線およびソース線が設けられる。また、複数のワード線21の両側には、図示しない選択ゲートが設けられる。そして、基板2とメモリアレイ20との間の、基板2の表面に設けられた制御回路7と、例えば、ワード線、ビット線および選択ゲートとが、配線9を介して電気的に接続される。

【0021】

上記のような、メモリアレイ10および20では、その特性を向上させるために、例えば、シリコンピラー15およびシリコンビーム23と、ONO構造の積層膜と、を高温で熱処理することが好ましい。そして、その熱処理に対し、基板2の表面に設けられる制御回路は、その特性の変化を抑制できる構造を備えることが望まれる。

【0022】

次に、図4〜図6を参照して、本実施形態に係る半導体装置100の製造過程を説明する。ここに示す図4〜図6(b)は、シリコン基板2の表面に設けられる制御回路の製造過程の一部を例示する模式図である。

【0023】

最初に、制御回路として、例えば、PMOSトランジスタとNMOSトランジスタを含むCMOS回路を設ける。続いて、シリコン基板2の表面を覆う絶縁層25を形成し、例えば、制御回路とメモリアレイをつなぐ配線、および、電源もしくは接地電位に接続される配線などを設ける。

【0024】

図4は、制御回路のp形半導体領域33およびn形半導体領域34を覆う絶縁層25に、p形半導体領域33に連通する第1のコンタクトホール28と、n形半導体領域34に連通する第2のコンタクトホール29と、を形成した状態を示す斜視図である。同図に示すように、コンタクトホール28および29は、配線溝27の底部に形成される。

【0025】

コンタクトホール28および29を形成する過程には、高度な微細加工技術を適用する。このため、p形半導体領域33に連通するコンタクトホール28と、n形半導体領域34に連通するコンタクトホール29と、を同時に形成することにより、フォトリソグラフィのコストを低減することが好ましい。

【0026】

p形半導体領域33は、例えば、PMOSトランジスタのソースもしくはドレイン領域、または、それらにつながるコンタクト領域である。また、NMOSトランジスタのボディ領域につながるコンタクト領域であっても良い。これらのp形半導体領域33には、例えば、p形不純物であるボロン(B)がドープされる。一方、n形半導体領域34は、例えば、NMOSトランジスタのソースもしくはドレイン領域、または、それらにつながるコンタクト領域である。また、PMOSトランジスタのボディ領域につながるコンタクト領域の場合もある。これらのn形半導体領域34には、例えば、n形不純物である砒素(As)がドープされる。

【0027】

p形半導体領域33とn形半導体領域34との間には、例えば、STI(Shallow Trench Isolation)35が形成される。そして、p形半導体領域33とn形半導体領域34とを覆う絶縁層25には、例えば、TEOS(TetraEthOxySilane)を用いたCVD(Chemical Vapor Deposition)法により形成されるシリコン酸化膜を用いることができる。

【0028】

次に、図5に示すように、コンタクトホール28の底部に露出したp形半導体領域33に炭素イオン(C+)を注入する。この際、n形半導体領域34に連通するコンタクトホール29をレジスト膜36で覆い、n形半導体領域34に炭素が注入されないようにする。

【0029】

炭素のイオン注入は、例えば、注入エネルギーを3keVとし、ドーズ量を1×1015cm−2として行う。さらに、p形不純物であるボロン(B)をイオン注入してから炭素イオンを注入しても良い。例えば、注入エネルギー5keV、ドーズ量3×1015cm−2の条件でボロンをイオン注入した後に、上記の条件で炭素をイオン注入する。

【0030】

レジスト膜36は、コンタクトホール29を覆い、コンタクトホール29の底部に炭素がイオン注入されないようにするために設けられるので、粗い精度のフォトリソグラフィにより形成することができる。すなわち、低コストのフォトリソグラフィ技術を用いることができる。

【0031】

次に、レジスト膜36を除去し、注入した元素を活性化させるために、熱処理を行う。例えば、RTA(Rapid thermal annealing)法により950℃、10秒間程度の熱処理を行う。そして、希釈したフッ酸溶液を用いて、コンタクトホール28および29の底部に露出したp形半導体領域33およびn形半導体領域34の自然酸化膜を除去し、コンタクトプラグとなる金属膜を堆積する。

【0032】

図6(a)に示すように、例えば,チタン(Ti)層と窒化チタン(TiN)層とを積層したTi/TiN膜37と、タングステン(W)膜38と、をCVD法により順次堆積する。最初に堆積されるTi層は、コンタクトホール28の底部に露出したp形半導体領域と、コンタクトホール29の底部に露出したn形半導体領域34と、絶縁層25の表面と、に接して形成される。

【0033】

例えば、Ti層は、塩化チタン(TiCl4)を原料として、CVD法を用いて堆積される。この際、堆積温度を600℃以上とすることにより、p形半導体領域33およびn形半導体領域34と、Ti層と、の界面に、シリサイド層41aおよび41bがそれぞれ形成される。

【0034】

続いて、Ti層の上にTiN膜を形成し、さらに、W膜38をTi/TiN膜37よりも厚く形成し、コンタクトホール28および29の内部、および、配線溝27の内部を埋め込む。

【0035】

続いて、図6(b)に示すように、絶縁層25の上面に形成されたTi/TiN膜37およびW膜38をCMP(Chemical mechanical polishing)法により除去する。これにより、コンタクトホール28および29の内部に埋め込まれたコンタクトプラグと、配線溝27に埋め込まれた層間配線と、を含む、所謂デュアルダマシン配線が形成される。

【0036】

さらに、本実施形態では、図6(a)および(b)に示すように、コンタクトホール28の底部において、Ti/TiN膜37に接するp形半導体領域33の表面に、炭素(C)が注入された層39と、その一部に重なるシリサイド層41aが形成される。

【0037】

以降の工程では、例えば、絶縁層25の上に層間絶縁膜を配し、2層目のコンタクトプラグおよび配線を形成した多層配線構造を設ける。そして、その多層配線構造の上に絶縁層を形成し、その後、メモリアレイ3を形成する。例えば、図1に示す基板2とメモリアレイ3との間の絶縁層5は、絶縁層25と、多層配線と、その上に設けられる絶縁層と、を含む層である。さらに,メモリアレイ3の上部に、電源線やグローバルな信号線を配し半導体装置100を完成する。

【0038】

前述したように、メモリアレイ3の製造過程では、高温の熱処理が施される。例えば、ポリシリコン層を熱処理して結晶化させ、移動度を向上させれば、読み出し電流値を大きくすることができる。このために、例えば、制御回路7および8を形成した基板2を、900℃以上の温度に設定した熱処理炉に搬入し、10分以上の処理を行う場合がある。これは、同じ温度に設定したRTA法による短時間の熱処理に比べて、過酷な処理となる。

【0039】

例えば、上記の多層配線では、第2層目の配線として、第1層目と同じTi/TiN/Wの積層構造を有する金属膜を用いることができる。第2層目のコンタクトプラグと、第1層目の配線と、の接点では、第2層目のTi層と、第1層目のW膜38と、が接触する。このため、低抵抗のコンタクトが形成され、熱的にも安定した配線となる。これにより、メモリアレイ3の製造工程における熱処理に耐える金属配線を実現することができる。

【0040】

また、上記の配線に代えて、例えば、導電性のポリシリコンを用いた配線を形成することも考えられる。しかしながら、ポリシリコンによる配線は、金属配線に比べて高抵抗である。このため、メモリアレイと制御回路との間の信号伝送の速度が低下し、半導体装置100の動作が遅くなるという問題を生じる。したがって、メモリアレイと制御回路との間に設けられる配線には、金属を用いることが好ましい。さらに、メモリアレイの製造過程における高温の熱処理に耐えるように、Ti、W等の高融点金属を用いることが望ましい。

【0041】

さらに、本実施形態では、図6(b)に示すように、p形半導体領域33と、コンタクトプラグ(Ti/TiN膜37+W膜38)と、が接する界面に炭素の注入層39を介在させる。これにより、p形半導体領域33にドープされたボロンの拡散を抑制し、p形半導体領域33とコンタクトプラグとの間におけるシリサイド層41aを介した低抵抗のオーミックコンタクトを維持することができる。

【0042】

すなわち、炭素の注入層39では、メモリアレイ3の製造過程における高温処理においてボロンの拡散が抑えられ、p形不純物の濃度の低下が抑制される。これにより、低抵抗のオーミックコンタクトを維持することができる。

【0043】

本実施形態のように、低加速エネルギーでイオンの注入を行った場合、炭素(C)はp形半導体領域33の表面近傍に分布する。このため、例えば、Ti/TiN膜37とp形半導体領域33とが反応して形成されるシリサイド層41aの中にもカーボンが取り込まれる。これにより、シリサイド層41aへのボロン(B)の吸い上げが抑えられ、p形半導体領域33の側のボロン濃度の低下を抑制することができる。

【0044】

また、MOSトランジスタのゲート電極から離間して設けられるコンタクトホール28の底部に炭素をイオン注入するため、炭素のトランジスタ特性への影響を回避することが可能であり、信頼性の高い半導体装置を実現することができる。

【0045】

一方、n形半導体領域34では、n形不純物として砒素(As)がドープされている。砒素の拡散係数は、例えば、ボロンに比べて小さい。このため、メモリアレイ3の製造過程における高温の熱処理を受けても、As濃度の変化は小さく、n形半導体領域34と、コンタクトプラグと、の間のコンタクト抵抗を低く維持することができる。

【0046】

上記の通り、本実施形態に係る半導体装置100では、基板2に設けられた制御回路と、メモリアレイ3と、の間を高融点金属の配線により接続し、p形半導体領域33と、コンタクトプラグと、の間に炭素をイオン注入した注入層39を介在させる。これにより、メモリアレイ3の製造過程における高温の熱処理に耐える配線の形成が可能となり、メモリアレイ3の下に制御回路を配した構造によるチップサイズ縮小と高速化とが実現される。

【0047】

本実施形態では、p形半導体領域33に炭素をイオン注入する例を示したが、これに限られる訳ではない。シリコンを含む半導体結晶に炭素をイオン注入した場合、結晶欠陥と、注入された炭素原子と、が結合して不純物の拡散を抑制する。したがって、ボロンがドープされたp形半導体領域33に限らず、他の不純物がドープされたp形半導体領域、もしくは、n形半導体領域においても同様の効果が得られる場合があり、本実施形態を変形して適用することが可能である。また、基板2の上に設けられるメモリアレイ3は、図2および図3に示した構造に限らず、他の3次元メモリアレイであっても良い。

【0048】

[第2の実施形態]

図7〜図10は、第2の実施形態に係る半導体装置100の製造過程を模式的に示す斜視図である。本実施形態に係る半導体装置100は、p形半導体領域33に接続されたポリシリコンからなるコンタクトプラグを有する点で、第1の実施形態と相違する。以下、図7〜図10を参照して、その製造過程について説明する。

【0049】

まず、図7に示すように、基板2の上に設けられた制御回路のp形半導体領域33およびn形半導体領域34を覆う絶縁層25aに、p形半導体領域33に連通する第1のコンタクトホール43を形成する。

【0050】

次に、コンタクトホール43の底部に露出したp形半導体領域33の表面の自然酸化膜を、希釈したフッ酸溶液で除去する。そして、図8(a)に示すように、例えば、CVD法を用いて、絶縁層25aの上にポリシリコン層45aを堆積し、コンタクトホール43の内部を埋め込む。ポリシリコン層45aは、好ましくは、p形半導体領域33よりも高濃度のp形不純物を含む導電層である。例えば、1×1021cm−3以上のボロン(B)を含むp形の導電層とする。

【0051】

続いて、絶縁層25aの上面に堆積したポリシリコン層45aを、例えば、CMP法を用いて除去し、コンタクトホール43の内部に埋め込まれたコンタクトプラグ45を形成する。さらに、図8(b)に示すように、絶縁層25aの上に絶縁層25bを形成する。絶縁層25aおよび絶縁層25bは、例えば、TEOSを原料とするCVD法を用いて形成されるシリコン酸化膜である。

【0052】

次に、図9(a)に示すように、n形半導体領域34に連通するコンタクトホール49、および、配線溝47を形成する。同時に、図示しないゲート電極のコンタクトホールを形成しても良い。p形半導体領域33の側では、コンタクトプラグ45の一部が配線溝47の底部から突出した状態に形成する。これにより、配線溝47に形成される金属配線と、コンタクトプラグ45と、の間の接触面積を広くしてコンタクト抵抗を下げることができる。なお、図9(a)に示す絶縁層25は、絶縁層25aと絶縁層25bとを含む。

【0053】

続いて、コンタクトホール49の底部に露出するn形半導体領域34の表面や、配線溝47の底面から突出したコンタクトプラグ45の表面の自然酸化膜を、希釈したフッ酸溶液により除去する。そして、図9(b)に示すように、コンタクトホール49の内部、および、配線溝47の内部に金属膜を堆積する。例えば、Ti/TiN膜37と、W膜38と、をCVD法を用いて順次堆積する。この際、前述したように、コンタクトプラグ45と、Ti/TiN膜37と、の間の界面、および、n形半導体領域34と、Ti/TiN膜37と、の間の界面に、それぞれシリサイド層51aおよび51bが形成される。

【0054】

次に、図10に示すように、絶縁層25の上面に堆積した金属膜を、例えば、CMP法を用いて除去する。さらに、前述したように、層間絶縁膜を配して複数の配線層を形成し、メモリアレイ3を形成して半導体装置100を完成する。

【0055】

このように、本実施形態によれば、n形半導体領域34の側では、コンタクトプラグおよび配線が同時に形成されるデュアルダマシン構造となり、p形半導体領域33の側では、コンタクトプラグ45と、配線とが、それぞれ別に形成されるシングルダマシン構造となる。

【0056】

また、p形半導体領域33に接するコンタクトプラグ45は、高濃度のp形不純物を含む。そして、コンタクトプラグ45の内部では、p形不純物の拡散が結晶粒界を介して速やかに行われる。このため、例えば、メモリアレイ3の製造過程における高温の熱処理が施され、コンタクトプラグ45から金属配線(Ti/TiN膜37)側にp形不純物が拡散したとしても、コンタクトプラグ45の内部のp形不純物が界面に供給され不純物濃度の低下を抑制する。このため、金属配線とコンタクトプラグ45との間で、低抵抗のオーミックコンタクトを維持することができる。

【0057】

一方、p形半導体領域33と、コンタクトプラグ45と、の間においても、コンタクトプラグ45の側からp形半導体領域33へp形不純物が供給される。これにより、p形半導体領域33の側で生じるp形不純物濃度の低下が補償され、低抵抗のオーミックコンタクトを維持することが可能である。

【0058】

さらに、図8(a)に示すポリシリコン層45aの堆積の際に、C2H6等のドーピングガスを添加することができる。これにより、p形不純物に加えて、炭素を含むポリシリコン層45aを形成することができる。そして、コンタクトプラグ45にも、p形不純物と炭素とを含有させることができる。その結果、コンタクトプラグ45から金属配線、および、p形半導体領域へのp形不純物の過度な拡散を抑制することが可能となる。これにより、コンタクトプラグ45と金属配線との間、および、コンタクトプラグ45とp形半導体領域との間の耐熱性を向上させることができる。

【0059】

このように、本実施形態では、p形半導体領域33へ連通するコンタクトホールのみにポリシリコンのコンタクトプラグを介在させることにより、耐熱性の高い金属配線を形成することができる。これにより、メモリアレイ3の下に制御回路を設け、その間を金属配線で結線することが可能となり、半導体装置100のチップサイズ縮小と、高速化と、を低コストで実現することができる。

【0060】

図11〜図12は、第2の実施形態の第1変形例に係る半導体装置の製造過程を模式的に示す断面図である。

【0061】

本変形例では、図11(a)に示すように、p形半導体領域33に連通するコンタクトホール43の内部にコンタクトプラグ45を形成した後、炭素をイオン注入する。これにより、コンタクトプラグ45の上部に注入層39が形成される。この場合、n形半導体領域34に連通するコンタクトホールが形成されていないので、レジスト膜36を形成する工程を省くことができる。すなわち、絶縁層25aの上面に堆積した金属配線を除去した後、基板2の全面に炭素をイオン注入すれば良い。

【0062】

続いて、絶縁層25aの上に絶縁層25bを形成し(図8(b)参照)、図11(b)に示すように、n形半導体領域34に連通するコンタクトホール49と、配線溝27と、を形成する。

【0063】

さらに、図12(a)に示すように、コンタクトホール49の内部、および、配線溝47の内部に、Ti/TiN膜37およびW膜38を堆積する。そして、コンタクトプラグ45の上部には、注入層39と、それに重なるシリサイド層51aが形成される。

【0064】

続いて、図12(b)に示すように、絶縁層25の上面に堆積した金属配線(Ti/TiN膜37およびW膜38)を除去し、第1層目の金属配線を完成させる。

【0065】

このように、本変形例では、フォトリソグラフィーの追加なしに,コンタクトプラグ45の上部に炭素の注入層39を形成し、金属配線とコンタクトプラグ45との間の熱耐性を向上させることができる。これにより、メモリアレイ3の製造過程における熱処理の影響を、より低コストで効果的に抑制することができる。

【0066】

図13〜図14は、第2の実施形態の第2変形例に係る半導体装置の製造過程を模式的に示す断面図である。

【0067】

本変形例では、図13(a)に示すように、p形半導体領域33とn形半導体領域34とを覆う絶縁層25aに、p形半導体領域33に連通するコンタクトホール43を形成し、その後に、炭素のイオン注入を行う。この場合も、n形半導体領域34に連通するコンタクトホールが形成されていないので、基板2の全面にイオン注入することができる。すなわち、フォトリソグラフィを省力した低コストの工程により、p形半導体領域33の表面に、選択的に炭素の注入層39を形成することができる。

【0068】

続いて、図13(b)に示すように、コンタクトホール43の内部に、p形ポリシリコンからなるコンタクトプラグ45を形成する。

【0069】

次に、絶縁層25aの上に絶縁層25bを形成し(図8(b)参照)、図14(a)に示すように、n形半導体領域34に連通するコンタクトホール49と、配線溝27と、を形成する。続いて、コンタクトホール49の内部、および、配線溝47の内部に、Ti/TiN膜37およびW膜38を堆積する。そして、図14(b)に示すように、絶縁層25の上面に堆積した金属配線を除去し、第1層目の金属配線を完成させる。

【0070】

本変形例によれば、コンタクトホール43の底部において、p形半導体領域33の表面に炭素の注入層39を形成することによりp形不純物の拡散を抑制し、コンタクトプラグ45と、p形半導体領域33と、の界面の熱耐性を向上させることができる。

【0071】

図15〜図16は、第2の実施形態の第3変形例に係る半導体装置の製造過程を模式的に示す断面図である。

【0072】

本変形例では、図15(a)に示すように、p形半導体領域33とn形半導体領域34とを覆う絶縁層25aに、p形半導体領域33に連通するコンタクトホール43を形成し、さらに、コンタクトホール43の側面である絶縁層25aの表面にシリコン窒化膜53を形成する。シリコン窒化膜53は、例えば、CVD法を用いて絶縁層25aの上面およびコンタクトホール43の内面に形成する。そして、異方性のドライエッチングにより、絶縁層25aの上面およびコンタクトホール43の底面に形成されたシリコン窒化膜を除去することにより、コンタクトホール43の側面にのみシリコン窒化膜53を残すことができる。

【0073】

続いて、図15(b)に示すように、コンタクトホール43の内部に、p形ポリシリコンからなるコンタクトプラグ45を形成する。

【0074】

次に、絶縁層25aの上に絶縁層25bを形成し、図16(a)に示すように、n形半導体領域34に連通するコンタクトホール49と、配線溝27と、を形成する。続いて、コンタクトホール49の内部、および、配線溝47の内部に、Ti/TiN膜37およびW膜38を堆積する。そして、図14(b)に示すように、絶縁層25の上面に堆積した金属配線を除去して第1層目の金属配線を完成させる。

【0075】

本変形例によれば、コンタクトホール43の側面に設けられたシリコン窒化膜53が、コンタクトプラグ45から絶縁層25に向かうp形不純物の拡散を抑える。これにより、コンタクトプラグ45の中のp形不純物の濃度の低下を抑制し、その熱耐性を向上させることができる。

【0076】

図17〜図18は、第2の実施形態の第4変形例に係る半導体装置の製造過程を模式的に示す断面図である。

【0077】

本変形例では、図17(a)に示すように、p形半導体領域33とn形半導体領域34とを覆う絶縁層25aに、p形半導体領域33に連通するコンタクトホール43を形成する。そして、p形半導体領域33の表面の自然酸化膜を除去した後、コンタクトホール43の内部にポリシリコン層45a(図8(a)参照)を堆積する前に、例えば、アンモニア(NH3)を含む高温の雰囲気にさらす。これにより、コンタクトホール43の底部に露出したp形半導体領域33の表面に、薄いシリコン窒化膜55を形成することができる。

【0078】

続いて、図17(b)に示すように、コンタクトホール43の内部に、p形ポリシリコンからなるコンタクトプラグ45を形成する。

【0079】

次に、絶縁層25aの上に絶縁層25bを形成し、図18(a)に示すように、n形半導体領域34に連通するコンタクトホール49と、配線溝27と、を形成する。さらに、コンタクトホール49の内部、および、配線溝47の内部に、Ti/TiN膜37およびW膜38を堆積する。そして、図18(b)に示すように、絶縁層25の上面に堆積した金属配線を除去し、第1層目の金属配線を完成させる。

【0080】

本変形例によれば、コンタクトホール43の底部に設けられたシリコン窒化膜55が、コンタクトプラグ45からp形半導体領域33に向かうp形不純物の拡散を抑える。これにより、コンタクトプラグ45の中のp形不純物の濃度の低下を抑制し、その熱耐性を向上させることができる。

【0081】

シリコン窒化膜55の厚さは、例えば、1nm以下とする。これにより、p形半導体領域33とコンタクトプラグ45との間の電気抵抗に大きな影響を与えることなく、p形不純物の拡散を抑制することができる。

【0082】

上記の第2の実施形態に係る製造過程、および、第1〜第4変形例に係る製造工程は、組み合わせて実施することが可能であり、コンタクトプラグ45と、p形半導体領域33および金属配線と、の間の熱耐性をさらに向上させることができる。

【0083】

以上、本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

また、前述した各具体例が備える各要素は、可能な限りにおいて組み合わせることができ、これら組み合わせたものも、本発明の特徴を含む限り本発明の範囲に包含される。

【符号の説明】

【0084】

2・・・基板(シリコン基板)、 3、10、20・・・メモリアレイ、 5・・・絶縁層、 7、8・・・制御回路、 9・・・配線、 12、13・・・電極層、 15・・・シリコンピラー、 17・・・ビット線、 18・・・ソース線、 21・・・ワード線(ポリシリコン層)、 23・・・シリコンビーム、 24a、24c、31・・・シリコン酸化膜、 24b、53、55・・・シリコン窒化膜、 25、25a、25b・・・絶縁層、 27・・・配線溝、 28、29、43、49・・・コンタクトホール、 33・・・p形半導体領域、 34・・・n形半導体領域、 36・・・レジスト膜、 37・・・Ti/TiN膜、 38・・・W膜、 39・・・注入層、 41a、41b、51a、51b・・・シリサイド層、 45・・・コンタクトプラグ、 45a・・・ポリシリコン層、 47・・・配線溝、 100・・・半導体装置

【特許請求の範囲】

【請求項1】

基板上に設けられたメモリアレイと、前記基板と前記メモリアレイとの間の前記基板の表面に設けられた制御回路と、を有する半導体装置の製造方法であって、

前記制御回路のp形半導体領域およびn形半導体領域を覆う絶縁層に、前記p形半導体領域に連通する第1のコンタクトホールを形成する工程と、

前記第1のコンタクトホールの内部に、前記p形半導体領域に接したコンタクトプラグを形成する工程と、

前記n形半導体領域に連通する第2のコンタクトホールを前記絶縁層に形成する工程と、

前記コンタクトプラグと、前記第2のコンタクトホールの内部に露出した前記n形半導体領域と、に接する配線を形成する工程と、

を備えたことを特徴とする半導体装置の製造方法。

【請求項2】

前記コンタクトプラグは、多結晶シリコンからなり、前記p形半導体領域よりも高濃度の前記p形不純物を含有することを特徴とする請求項1記載の半導体装置の製造方法。

【請求項3】

前記コンタクトプラグの表面に炭素をイオン注入する工程をさらに備えたことを特徴とする請求項1または2に記載の半導体装置の製造方法。

【請求項4】

前記第1コンタクトホールの底部に炭素をイオン注入する工程をさらに備えたことを特徴とする請求項1〜3のいずれか1つに記載の半導体装置の製造方法。

【請求項5】

前記コンタクトプラグは、炭素をさらに含有することを特徴とする請求項1〜4のいずれか1つに記載の半導体装置の製造方法。

【請求項6】

前記コンタクトプラグと、前記p形半導体領域と、の間に、厚さ1nm以下のシリコン窒化膜を形成する工程をさらに備えたことを特徴とする請求項1〜5のいずれか1つに記載の半導体装置の製造方法。

【請求項7】

前記第1のコンタクトホールの内面において、前記絶縁膜の表面にシリコン窒化膜を形成する工程をさらに備えたことを特徴とする請求項1〜6のいずれか1つに記載の半導体装置の製造方法。

【請求項8】

前記配線は、金属配線であることを特徴とする請求項1〜7のいずれか1つに記載の半導体装置の製造方法。

【請求項9】

基板上に設けられたメモリアレイと、前記基板と前記メモリアレイとの間の前記基板の表面に設けられた制御回路と、を有する半導体装置であって、

前記制御回路のp形半導体領域およびn形半導体領域を覆う絶縁層と

前記絶縁膜の表面から前記p形半導体領域に連通する第1のコンタクトホールの内部に設けられたコンタクトプラグであって、前記p形半導体領域に接するコンタクトプラグと、

前記絶縁層の表面から前記n形半導体領域に連通する第2のコンタクトホールの内部に露出した前記n形半導体領域と、前記コンタクトプラグと、に接続され配線と、

を備えたことを特徴とする半導体装置。

【請求項1】

基板上に設けられたメモリアレイと、前記基板と前記メモリアレイとの間の前記基板の表面に設けられた制御回路と、を有する半導体装置の製造方法であって、

前記制御回路のp形半導体領域およびn形半導体領域を覆う絶縁層に、前記p形半導体領域に連通する第1のコンタクトホールを形成する工程と、

前記第1のコンタクトホールの内部に、前記p形半導体領域に接したコンタクトプラグを形成する工程と、

前記n形半導体領域に連通する第2のコンタクトホールを前記絶縁層に形成する工程と、

前記コンタクトプラグと、前記第2のコンタクトホールの内部に露出した前記n形半導体領域と、に接する配線を形成する工程と、

を備えたことを特徴とする半導体装置の製造方法。

【請求項2】

前記コンタクトプラグは、多結晶シリコンからなり、前記p形半導体領域よりも高濃度の前記p形不純物を含有することを特徴とする請求項1記載の半導体装置の製造方法。

【請求項3】

前記コンタクトプラグの表面に炭素をイオン注入する工程をさらに備えたことを特徴とする請求項1または2に記載の半導体装置の製造方法。

【請求項4】

前記第1コンタクトホールの底部に炭素をイオン注入する工程をさらに備えたことを特徴とする請求項1〜3のいずれか1つに記載の半導体装置の製造方法。

【請求項5】

前記コンタクトプラグは、炭素をさらに含有することを特徴とする請求項1〜4のいずれか1つに記載の半導体装置の製造方法。

【請求項6】

前記コンタクトプラグと、前記p形半導体領域と、の間に、厚さ1nm以下のシリコン窒化膜を形成する工程をさらに備えたことを特徴とする請求項1〜5のいずれか1つに記載の半導体装置の製造方法。

【請求項7】

前記第1のコンタクトホールの内面において、前記絶縁膜の表面にシリコン窒化膜を形成する工程をさらに備えたことを特徴とする請求項1〜6のいずれか1つに記載の半導体装置の製造方法。

【請求項8】

前記配線は、金属配線であることを特徴とする請求項1〜7のいずれか1つに記載の半導体装置の製造方法。

【請求項9】

基板上に設けられたメモリアレイと、前記基板と前記メモリアレイとの間の前記基板の表面に設けられた制御回路と、を有する半導体装置であって、

前記制御回路のp形半導体領域およびn形半導体領域を覆う絶縁層と

前記絶縁膜の表面から前記p形半導体領域に連通する第1のコンタクトホールの内部に設けられたコンタクトプラグであって、前記p形半導体領域に接するコンタクトプラグと、

前記絶縁層の表面から前記n形半導体領域に連通する第2のコンタクトホールの内部に露出した前記n形半導体領域と、前記コンタクトプラグと、に接続され配線と、

を備えたことを特徴とする半導体装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【公開番号】特開2013−65604(P2013−65604A)

【公開日】平成25年4月11日(2013.4.11)

【国際特許分類】

【出願番号】特願2011−201903(P2011−201903)

【出願日】平成23年9月15日(2011.9.15)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

【公開日】平成25年4月11日(2013.4.11)

【国際特許分類】

【出願日】平成23年9月15日(2011.9.15)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

[ Back to top ]