半導体装置およびその製造方法

【課題】高耐圧MOSFETの耐圧を向上させる。

【解決手段】MOSFETのドレイン領域を構成するLDD層6内に、LDD層6よりも不純物濃度層が低いN−−層11を形成して、チャネル領域側のドレイン領域端部の不純物濃度を低下させる。また、ソース領域側のLDD層7をLDD層6よりも浅い接合深さで、且つLDD層6よりも低い不純物濃度で形成する。これにより、オン状態およびオフ状態のいずれの状態においてもドレイン領域の電界を緩和し、インパクトイオンおよびパンチスルーの発生を防ぐ。

【解決手段】MOSFETのドレイン領域を構成するLDD層6内に、LDD層6よりも不純物濃度層が低いN−−層11を形成して、チャネル領域側のドレイン領域端部の不純物濃度を低下させる。また、ソース領域側のLDD層7をLDD層6よりも浅い接合深さで、且つLDD層6よりも低い不純物濃度で形成する。これにより、オン状態およびオフ状態のいずれの状態においてもドレイン領域の電界を緩和し、インパクトイオンおよびパンチスルーの発生を防ぐ。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置およびその製造方法に関し、特に、高耐圧の半導体素子の製造に適用して有効な技術に関する。

【背景技術】

【0002】

LSI(Large Scale Integration)内に形成される素子の一つに、入出力(インプット/アウトプット:I/O)に用いられる高耐圧な電界効果トランジスタ(Metal Oxide Semiconductor Field Effect Transistor:MOSFET)がある。

【0003】

特許文献1(特開平6−318698号公報)には、チャネル領域の表面の両端部分にN−ソース/ドレイン領域の下方にまで延びる高濃度のP層を形成し、さらにN+ソース/ドレイン領域とN−ソース/ドレイン領域との境界領域の一部に高濃度のP層を形成することで、素子の遅延時間の増加と基板バイアス電圧によるしきい値電圧の上昇を低減するとともに、基板パンチスルー現象を防止することが記載されている。

【0004】

特許文献2(特開2002−134743号公報)には、MIS(Metal Insulator Semiconductor)トランジスタにおいて、入出力パッドからサージが入力された場合に、高濃度ドレイン領域から基板領域に形成されるpn接合部の濃度変化が急峻なことを利用してサージを逃すことが記載されている。

【0005】

特許文献3(特開2007−103837号公報)には、左右非対称のソース・ドレイン領域を有する電界効果トランジスタ(以下単にMOSFETという)において、ドレイン領域を、基板主面のエクステンションと、その周辺を囲むエクステンションと、さらにそれよりも外側に形成されたポケット層とにより構成することが記載されている。

【0006】

特許文献4(米国特許第7,393,752号公報)では、基板上の不純物濃度が低いエピタキシャル層上に形成されたゲート電極と、ソース領域側のエピタキシャル層に高いエネルギーで不純物が注入されて形成されたウエルと、ウエルに自己整合的に形成されたハロー領域と、ドレイン領域側にゲート電極と重なるように形成されたLDD(Lightly Doped Drain)層とによりパワーMOSFETを構成することが記載されている。これにより、マスクおよび処理工程を追加せずに、パワーMOSFETを微細化することができるとしている。

【0007】

特許文献5(特開2009−245998号公報)には、左右非対称のソース・ドレイン領域を有する高耐圧トランジスタにおいて、チャネル領域を、p型不純物を高濃度に有する高濃度領域と、n型不純物領域(オフセット不純物領域)の端部と高濃度領域の端部との間の領域であって高濃度領域よりもp型不純物を低濃度に有する低濃度領域とから構成することにより、オン抵抗が低く十分な耐圧を有する高耐圧トランジスタを提供することが記載されている。

【0008】

特許文献6(特開2008−235407号公報)には、ドレイン不純物拡散領域の不純物拡散プロファイルにおけるLDD層のチャネル側端がゲート絶縁膜から離隔して基板内部に埋め込まれたトランジスタを形成することにより、ゲート電極とドレイン電極との間でゲート絶縁膜に加わる電界を低減することが記載されている。ここではP型の不純物を傾斜注入することによって、ソース領域側とドレイン領域側のLDD層を非対称に形成している。

【0009】

なお、特許文献3〜6では、いずれも電界をオン状態とオフ状態に分けて議論していないため、オン状態およびオフ状態のいずれの場合でも耐圧を向上できるのかどうかが不明である。

【先行技術文献】

【特許文献】

【0010】

【特許文献1】特開平6−318698号公報

【特許文献2】特開2002−134743号公報

【特許文献3】特開2007−103837号公報

【特許文献4】米国特許第7,393,752号公報

【特許文献5】特開2009−245998号公報

【特許文献6】特開2008−235407号公報

【発明の概要】

【発明が解決しようとする課題】

【0011】

半導体装置内の入出力に使用される素子を含む領域(I/O部)において用いられるMOSFETは、動作電圧が外部の装置から供給される電圧により決まるため、スケーリング側に従って動作電圧を小さくすることができない。したがって、I/O部において用いられる高耐圧MOSFETを微細化する場合は、決められた動作電圧下でソース・ドレイン間においてパンチスルーを起こさず、さらにドレイン端の電界を緩和し、インパクトイオンの発生を防ぐ必要がある。また、耐圧を確保するため、ドレイン領域側のLDD層とウエルとの間の電界が、MOSFETがオン状態であってもオフ状態であっても緩和されるような構造を実現し、ソース領域側への空乏層の伸びを小さくすることが重要となる。

【0012】

本発明の目的は、半導体装置の性能を向上させることにある。

【0013】

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

【課題を解決するための手段】

【0014】

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、次のとおりである。

【0015】

本発明の好ましい一態様である半導体装置は、MOSFETのドレイン領域側のLDD層内に、前記LDD層よりも不純物濃度層が低いN−−層を形成してドレイン領域のチャネル領域側の端部の不純物濃度を低下させ、さらにソース領域側のLDD層をドレイン領域側のLDD層よりも浅い接合深さで、且つ低い不純物濃度で形成するものである。

【発明の効果】

【0016】

本願において開示される発明のうち、代表的なものによって得られる効果を簡単に説明すれば以下のとおりである。

【0017】

代表的な実施の形態によれば、半導体装置の性能を向上させることができる。

【図面の簡単な説明】

【0018】

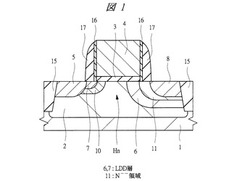

【図1】本発明の実施の形態1である半導体装置の断面図である。

【図2】基板表面の不純物濃度の分布を示すグラフである。

【図3】ソース領域における深さ方向の不純物の濃度分布を示すグラフである。

【図4】ドレイン領域における深さ方向の不純物の濃度分布を示すグラフである。

【図5】本発明の実施の形態1である半導体装置の製造工程を示す断面図である。

【図6】図5に続く半導体装置の製造工程中の断面図である。

【図7】図6に続く半導体装置の製造工程中の断面図である。

【図8】図7に続く半導体装置の製造工程中の断面図である。

【図9】図8に続く半導体装置の製造工程中の断面図である。

【図10】図9に続く半導体装置の製造工程中の断面図である。

【図11】図10に続く半導体装置の製造工程中の断面図である。

【図12】図11に続く半導体装置の製造工程中の断面図である。

【図13】図12に続く半導体装置の製造工程中の断面図である。

【図14】図13に続く半導体装置の製造工程中の断面図である。

【図15】図14に続く半導体装置の製造工程中の断面図である。

【図16】図15に続く半導体装置の製造工程中の断面図である。

【図17】図16に続く半導体装置の製造工程中の断面図である。

【図18】図17に続く半導体装置の製造工程中の断面図である。

【図19】図18に続く半導体装置の製造工程中の断面図である。

【図20】図19に続く半導体装置の製造工程中の断面図である。

【図21】図20に続く半導体装置の製造工程中の断面図である。

【図22】図21に続く半導体装置の製造工程中の断面図である。

【図23】本発明の実施の形態2である半導体装置の断面図である。

【図24】本発明の実施の形態2である半導体装置の製造工程を示す断面図である。

【図25】図24に続く半導体装置の製造工程中の断面図である。

【図26】図25に続く半導体装置の製造工程中の断面図である。

【図27】本発明の実施の形態3である半導体装置の断面図である。

【図28】本発明の実施の形態3である半導体装置の製造工程を示す断面図である。

【図29】図28に続く半導体装置の製造工程中の断面図である。

【図30】図29に続く半導体装置の製造工程中の断面図である。

【図31】本発明の実施の形態4である半導体装置の断面図である。

【図32】本発明の実施の形態4である半導体装置の製造工程を示す断面図である。

【図33】第1の比較例である半導体装置の断面図である。

【図34】第2の比較例である半導体装置の断面図である。

【図35】第3の比較例である半導体装置の断面図である。

【発明を実施するための形態】

【0019】

以下、本発明の実施の形態を図面に基づいて詳細に説明する。なお、実施の形態を説明するための全図において、同一の機能を有する部材には同一の符号を付し、その繰り返しの説明は省略する。また、以下の実施の形態では、特に必要なとき以外は同一または同様な部分の説明を原則として繰り返さない。

【0020】

(実施の形態1)

まず、図1を用いて本発明の実施の形態の半導体装置を説明する。図1には、本実施の形態の半導体装置を構成するNチャネル型高耐圧MOSFET(高耐圧トランジスタ)Hnの断面図を示している。図1に示すNチャネル型高耐圧MOSFETHnは半導体装置のI/O部に設けられ、例えばNチャネル型高耐圧MOSFETHnが形成された半導体チップの外部から供給される入力電圧により動作し、または半導体チップの外部に出力するために用いられる半導体素子である。図1では半導体基板1およびその上面に形成されたNチャネル型高耐圧MOSFETHnのみを示しており、その他のMOSFET、素子分離領域は図示しておらず、また、半導体基板1上に形成されたコンタクトプラグ、層間絶縁膜および配線の図示は省略している。

【0021】

図1に示すように、本実施の形態の半導体装置は例えば単結晶のSi(シリコン)からなる半導体基板1を有し、半導体基板1の主面にはP型の不純物(例えばB(ホウ素))が導入されたPウエル2が形成されており、半導体基板1の主面上にはPウエル2の上面に接して例えば酸化シリコン膜などからなるゲート絶縁膜3が形成され、ゲート絶縁膜3上には例えばポリシリコン膜からなるゲート電極4が形成されている。ゲート電極4のゲート長方向において、ゲート電極の横の半導体基板1の主面にはソース領域およびドレイン領域が形成されている。ゲート電極4の両側の側壁には、例えば酸化シリコン膜および窒化シリコン膜の積層膜からなるサイドウォールが形成されている。

【0022】

ソース領域およびドレイン領域はゲート電極4の直下の半導体基板1の主面に形成されたPウエル2を挟むように位置している。

【0023】

ソース領域側の半導体基板1の主面には、拡散層5、LDD層(N−領域)7およびPウエル(P−領域)10が形成されている。拡散層5およびLDD層7はいずれもN型の不純物(例えばP(リン))が導入された半導体領域であり、N+層である拡散層5の方がN−層であるLDD層7よりも高い不純物濃度を有し、拡散層5の方がLDD層7よりも深い接合深さを有している。LDD層7は拡散層5よりもゲート電極4の直下の半導体基板1の主面に形成されたPウエル2に近い領域に形成されている。Pウエル10はLDD層7よりもゲート電極4の直下の半導体基板1の主面に形成されたPウエル2に近い領域に形成され、また、LDD層7よりも深く拡散層5よりも浅い接合深さを有している。Pウエル10は、半導体基板1内において拡散層5と接していない領域のLDD層7の外側を覆うように形成されている。また、Pウェル10はPウエル2よりも不純物濃度が高い領域である。LDD層7およびPウエル10はゲート電極4の直下の領域に形成され、平面視においてゲート電極4と重なるように配置されている。ソース領域は、拡散層5およびLDD層7により構成されている。

【0024】

ドレイン領域側の半導体基板1の主面には、拡散層8、N−−領域11およびLDD層(N−領域)6が形成されている。N−−領域11は拡散層8よりも深い接合深さで形成されており、LDD層(N−領域)6はN−−領域11よりも深い接合深さで形成されている。つまり、半導体基板1の主面から反対側の裏面方向に向かって、拡散層8、N−−領域11およびLDD層6が順に形成されている。ドレイン領域は、拡散層8、N−−領域11およびLDD層6により構成されている。Nチャネル型高耐圧MOSFETHnは、ゲート電極4、拡散層5、LDD層7、Pウエル10、Pウエル2、拡散層8、N−−領域11およびLDD層6を含んでいる。

【0025】

拡散層8、N−−領域11およびLDD層6はいずれもN型の不純物(例えばP(リン))が導入された半導体領域であり、N−領域であるLDD層6はN−−領域11よりもN型の不純物濃度が高く、N+領域である拡散層8はLDD層6よりもN型の不純物濃度が高い。

【0026】

また、半導体基板1の主面において、ゲート電極4の直下の半導体基板1の主面からゲート長方向に離れるように、LDD層6、N−−領域11および拡散層8が順に形成されている。つまり、半導体基板1の主面に形成された拡散層8、N−−領域11およびLDD層6のうち、ゲート電極4の直下の半導体基板1の主面の最も近くに形成されているのはLDD層6であり、ゲート電極4の直下の半導体基板1の主面に対してLDD層6よりも遠い位置にN−−領域11が形成され、さらに遠い位置に拡散層8が形成されている。

【0027】

つまり、半導体基板1内においては、拡散層8の外側を覆うようにN−−領域11が形成され、さらにN−−領域11の外側を覆うようにLDD層6が形成されている。したがって、ゲート長方向における半導体基板1の主面には、ソース領域側の拡散層5からドレイン領域側の拡散層8にかけて、順に拡散層5、LDD層7、Pウエル10、Pウエル2、LDD層6、N−−領域11および拡散層8が形成されている。

【0028】

なお、LDD層6、7は半導体基板1の主面に対して斜めの方向からイオン注入を行って不純物が導入されているため、半導体基板1の主面に対して垂直な方向からイオン注入を行って不純物が導入する場合に比べてゲート電極4の直下の半導体基板1の主面に深く潜り込むように形成されている。つまり、LDD層6、7は半導体基板1の主面に対して垂直な方向からイオン注入を行って不純物が導入してN型層を形成する場合に比べてゲート電極4とのオーバーラップ量、すなわち平面視においてゲート電極4と重なる面積が大きくなっている。

【0029】

ただし、ドレイン領域側のLDD層6はソース領域側のLDD層7よりも深い接合深さを有しており、また、N型の不純物(例えばP(リン))の濃度はLDD層7よりもLDD層6の方が高い。

【0030】

次に、図33〜図35に示す比較例の半導体装置および図1に示す半導体装置を用いて本実施の形態の半導体装置の効果を説明する。なお、図33〜図35は半導体基板上に形成された比較例の半導体装置を構成するNチャネル型のMOSFETを示す断面図であり、半導体基板の主面上のその他の配線、層間絶縁膜などの構造体は図示を省略している。

【0031】

I/O部などに用いられる高耐圧MOSFETは、その動作電圧が外部の装置から供給される電圧または外部に供給する電圧により決まるため、スケーリング則に従って動作電圧を小さくすることができない。このような高耐圧MOSFETを微細化する際には、決められた動作電圧においてソース・ドレイン間でパンチスルーが起きることを防ぐことが重要となる。また、MOSFETの耐圧は当該MOSFETがオン状態およびオフ状態のいずれの場合でも十分に確保されている必要がある。

【0032】

そのための構造としては、例えば図33に示すような構造がある。図33は第1の比較例として示すNチャネル型のMOSFETであるが、ここで示す比較例の半導体装置はPチャネル型のMOSFETであっても構わない。

【0033】

図33に示すように、第1の比較例のNチャネル型のMOSFETを構成する半導体基板1の上面にはP型不純物(たとえばB(ホウ素))が添加されたPウエル2が形成されており、半導体基板1上にはゲート絶縁膜3を介してゲート電極4が形成されている。ゲート電極4の両側の側壁には、酸化シリコン膜などからなる絶縁膜であるオフセットスペーサ16を介して、絶縁膜であるサイドウォール17が形成されている。また、ゲート電極4を挟むように、半導体基板1の主面にはN型の不純物(例えばP(リン))が導入されて形成されたLDD層(N−領域)6e、7eが形成されている。LDD層6e、7e内には、LDD層6e、7eよりもN型不純物(例えばP(リン))が高い濃度で添加された拡散層(ソース電極)5および拡散層(ドレイン電極)8がイオン注入法によりそれぞれ形成されている。拡散層5および拡散層8は、ゲート電極4と、ゲート電極4の側壁に当該側壁側から順に形成されたオフセットスペーサ16およびサイドウォール17とを含む構造体を挟むように、半導体基板1の主面に形成されている。つまりゲート長方向において、拡散層5、拡散層8はゲート電極4を中心として左右対称に形成されており、LDD層6e、7eはゲート電極4を中心として左右対称に形成されている。このMOSFETを形成する工程では、ゲート電極4をマスクとして半導体基板1の主面に不純物をイオン注入することにより、LDD層6e、7eを同時に形成する。

【0034】

図33のMOSFETのように、LDD層6e、7eを深く左右対称に形成した構造では、半導体装置の微細化のためにゲート長を縮小した際、Pウエル2とLDD層6e、7eとによって形成されたPN接合での空乏層が拡がることによってパンチスルーが起こることがある。また同時にオン状態における電流値が増加し、それによって誘起されるインパクトイオン化の増加も懸念される。これは、ドレイン領域を構成するLDD層のチャネル領域側の端部のN型不純物の濃度が高いと、オン状態において電流の経路である基板表面における電界が強くなるためであり、オン状態の耐圧が劣化する原因となる。

【0035】

なお、ここでいうインパクトイオン化とは、MOSFETにおいて、ソースからドレインに流れる電子がドレイン部の高電界で加速されて結晶格子と衝突することにより、電子、正孔を発生させる現象を指す。この衝突によるイオン化が起こると、MOSFETの耐圧が低下し、また、雑音(ノイズ)が大きくなるなどの問題が発生する。

【0036】

したがって、高耐圧MOSFETのゲート長を縮小するなどして半導体装置を微細化する際には、ソース・ドレイン間でパンチスルーが起きることを防ぎ、さらにドレイン端の電界を緩和してインパクトイオンの発生を抑え、耐圧が低下することを防ぐ必要がある。

【0037】

以上の問題を解決する手段として、例えば図34または図35に示すような半導体装置を用いることが考えられる。図34に示す第2の比較例の半導体装置は図33の半導体装置と似たような構造を有しているが、ソース領域側のLDD層(N−領域)7fとドレイン領域側のLDD層(N−領域)6fとを別のマスクを用いた別工程のイオン注入により形成している点で前記第1の比較例とは異なる。また、ソース領域側のPウエル10fをLDD層7fの下部に形成することで、ソース領域側のP型の不純物濃度を高めてソース領域側に空乏層が伸びることを防ぎ、ソース・ドレイン間のパンチスルーが起きることを防止している。しかし、図34のような構造ではドレイン領域側のLDD層6f、拡散層8およびPウエル2の関係で電界が決まるため、それ以上に電界を緩和させることはできない。

【0038】

一方、図35に示す第3の比較例の半導体装置では、ソース領域側の拡散層5gを図33および図34のMOSFETと同様にゲート電極4に隣接して形成し、ドレイン領域側の拡散層8gをゲート電極4およびサイドウォール17からオフセットして形成している。つまり、拡散層5gとゲート電極4との距離に比べて、拡散層8gとゲート電極4とは大きく離れている。これにより、拡散層8g側に空乏層を伸ばすことができるため、図34に示すMOSFETに対してさらなる電界緩和が期待できる。また、図35のMOSFETは拡散層5gおよび拡散層8gを囲うように半導体基板1内にLDD層(N−領域)6g、7gがそれぞれ形成されており、ソース領域側の半導体基板1の主面には、LDD層7gよりもゲート電極4に近い領域に高い不純物濃度を有するPウエル10gが形成されている。ただし、図35に示すような構造では拡散層8gをオフセットして形成することによりMOSFETの占有面積が増加することになる。

【0039】

また、図示はしないが、MOSFETの耐圧を向上させる構造としては、第4の比較例として、図34に示した不純物濃度が高いPウエル10fまたは図35に示した不純物濃度が高いPウエル10gをいずれも形成せず、ゲート電極の片側からP型の不純物(例えばB(ホウ素))を傾斜注入することにより、ソース領域側とドレイン領域側のLDD層を非対称に形成する半導体装置も考えられる。この場合、ドレイン領域側のLDD層の最表面の濃度を下げることで、ドレイン・ゲート間の耐圧向上が期待できる。

【0040】

ただし、このような装置ではP型の不純物(例えばB(ホウ素))の注入エネルギーが低く、ドレイン端の電界を緩和することができない。さらに、このような構造はドレイン領域側から空乏層が伸びることを防げず、パンチスルーしやすい構造であると考えられる。

【0041】

図33〜図35に示した半導体装置は、ドレイン領域側のLDD層から伸びる空乏層の広がりを小さくする効果があると考えられるが、ドレイン端の電界を緩和するものではなく、ドレイン領域側のLDD層の濃度を調整することでしか、ドレイン領域側のLDD層とPウエル2との間の電界を緩和することができない。

【0042】

また、上述した図示しない第4の比較例の半導体装置では、傾斜注入を用いてP型の不純物(例えばB(ホウ素))をドレイン領域側のLDD層に注入して形成しているが、これはゲート電極とドレイン領域側のLDD層との間の電界を緩和するためであり、このような方法を用いてもドレイン領域側のLDD層と、チャネル領域であるPウエルとの間の電界を緩和することはできない。

【0043】

これに対し、本実施の形態の半導体装置は、MOSFETがオフ状態でもオン状態でもいずれの状態であってもドレイン領域側のLDD層とチャネル領域であるPウエルとの間の電界を緩和することを可能とし、さらにソース領域側への空乏層の伸びを小さくするものである。

【0044】

図1を用いて説明したように、本実施の形態ではソース領域側のLDD層7をLDD層6よりも浅く且つ不純物濃度を低く形成し、さらに不純物濃度が高いPウエル10をLDD層7の周囲に形成することによってソース・ドレイン間に空乏層が伸びることを防ぎ、ソース・ドレイン間におけるパンチスルーの発生を防ぐことを可能としている。Nチャネル型MOSFETのしきい値電圧はソース領域側のP型の不純物(例えばB(ホウ素))の濃度で決まるため、LDD層7の濃度を下げることにより高いしきい値電圧を実現することができる。LDD層7の接合深さをLDD層6と同様に深くした場合、LDD層7のN型不純物の濃度を高める必要がでてくるが、LDD層7のN型不純物の濃度がLDD層6と同等に高くなると、パンチスルーが生じやすくなるため、ここではLDD層7の接合深さをLDD層6よりも低くしている。また、Pウエル10の不純物濃度を高くすることによってしきい値電圧を上げることも可能であるが、素子ばらつきの観点からPウエルの濃度は高くし過ぎない方が好ましい。

【0045】

さらに、ドレイン領域側のLDD層6内にN型の不純物濃度が低いN−−領域11を形成することにより、オン状態でもオフ状態でもインパクトイオン化が起こりにくいMOSFETを実現することができる。その理由を以下に記す。

【0046】

MOSFETのインパクトイオン化を防ぐ観点におけるドレイン側のLDD層の最適な不純物濃度は、オン状態よりもオフ状態の方が高いという性質がある。これは、オン状態では電流が流れる経路の電界と電流量とでインパクトイオンが発生率が決まり、一方、オフ状態ではPウエルとドレイン領域側のLDD層との界面のPN接合における最も強い電界によってインパクトイオンの発生率が決まるためである。よって、良好な耐圧を得るためのドレイン領域側のLDD層の最適な不純物濃度は、オフ状態とオン状態とで異なっている。

【0047】

つまり、ドレイン領域側のLDD層内の、特にチャネル領域に近い端部のN型不純物の濃度が高くなると、ソース・ドレイン間の電流経路における電界が強くなるために、MOSFETのオン状態での耐圧が低下してしまう。そこで、本実施の形態ではドレイン領域内の電界が高くなることを防ぐため、図1に示すN−層であるLDD層6とN+層である拡散層8との間に、N型の逆種であるP型の不純物(例えばB(ホウ素))を導入することで、半導体基板1の主面にLDD層6よりも不純物濃度が低いN−−領域11を形成している。これにより、特に半導体基板1の主面では図2に示すようなN型不純物の濃度分布となる。

【0048】

図2は本実施の形態の半導体装置のMOSFETにおける半導体基板1(図1参照)の主面に導入されたN型不純物の濃度を示すグラフである。図2の横軸はゲート電極4の中心部の直下の位置を0とした場合のゲート長方向における距離であり、横軸の負の方向をソース領域側とし、正の方向をドレイン領域側としている。

【0049】

また、図3および図4に、本実施の形態のMOSFETのソース領域およびドレイン領域のそれぞれの半導体基板1(図1参照)の主面から深さ方向にかけての半導体基板1内のN型不純物の濃度分布を表わしたグラフを示す。図3はソース領域の半導体基板1の主面から半導体基板1の裏面に向かう方向である深さ方向における半導体基板1内の不純物濃度の分布を示したグラフであり、縦軸は不純物の濃度を示し、横軸は半導体基板1の主面の位置を0として半導体基板1の主面から深さ方向に向かう距離を示している。図4はドレイン領域の半導体基板1の主面から半導体基板1の裏面に向かう方向である深さ方向における半導体基板1内の不純物濃度の分布を示したグラフであり、縦軸は不純物の濃度を示し、横軸は半導体基板1の主面の位置を0として半導体基板1の主面から深さ方向に向かう距離を示している。

【0050】

図3に示すように、ソース領域では半導体基板1の主面側から裏面側に向かって、N+層(拡散層5)およびP層(Pウエル2)が形成されている。また、図4に示すように、ドレイン領域では半導体基板1の主面側から裏面側に向かって、N+層(拡散層8)、N−−領域11、N−層(LDD層6)およびP層(Pウエル2)が形成されている。図4に示すようにドレイン領域にはN−−領域11が形成されているため、N+層(拡散層8)とN−層(LDD層6)との間で不純物濃度がN−層(LDD層6)よりも低くなっている。

【0051】

ここで、図2に示すように、半導体基板1の主面には、ソース領域側からドレイン領域側に向かってN+層(拡散層5)、P+層(Pウエル10)、N−層(LDD層6)、N−−領域11、N+層(拡散層8)が順に形成されており、N−−領域11が形成された領域では、LDD層6よりも不純物濃度が低くなっている。本実施の形態の半導体装置では、このように半導体基板1の主面においてドレイン領域側のLDD層6と拡散層5との間に不純物濃度が低いN−−領域11を形成することにより、半導体基板1の主面におけるドレイン領域の電界を緩和し、インパクトイオンの発生を防ぐことを可能としている。これにより、Pウエル2とLDD層6との間の耐圧が向上するため、半導体装置の性能を向上させることができる。

【0052】

また、本実施の形態では、ドレイン領域側のLDD層6を形成する際のN型不純物(例えばP(リン))の注入濃度を調整することにより、ドレイン領域側のLDD層6の不純物濃度をLDD層7よりも高くしているため、オン状態で電流が流れる経路の電界は強くなり、一方で、オフ状態でのPウエル2およびLDD層6間のPN接合での電界は弱くなる。したがって、Pウエル2とLDD層6との間でインパクトイオンが発生することを防ぎ、耐圧を向上させることができるため、半導体装置の性能を向上させることができる。

【0053】

また、ゲート電極4の側壁に形成するサイドウォールのゲート長方向の厚さを大きくする方法、または図35を用いて説明したように拡散層をオフセットして形成する方法などを用いて、ソース・ドレイン間の間隔を広げてMOSFETに流れる電流を小さくし、インパクトイオンの発生を低減することが考えられるが、このような構造を採用するとMOSFETの面積が大きくなるため、素子の微細化の妨げとなる。これに対して、本実施の形態の半導体装置では、サイドウォールの厚さを大きくするなどしてソース・ドレイン間の間隔を広げることを行わずにMOSFETの高耐圧化を可能としている。したがって、高耐圧なMOSFETの微細化が容易になるため、半導体装置の性能を向上させることができる。

【0054】

以下に、図5〜図22を用いて本実施の形態の半導体装置を構成するNチャネル型高耐圧MOSFETの製造方法を説明する。図5〜図22は本実施の形態の半導体装置の製造工程を示す断面図であり、図1と異なり、本実施の形態の特徴を有するNチャネル型の高耐圧MOSFETの他に、Pチャネル型の高耐圧MOSFET、Nチャネル型の低耐圧MOSFETおよびPチャネル型の低耐圧MOSFETを形成する領域も図示している。図5〜図22では、図の左側から右側にかけて順にNチャネル型高耐圧MOSFET形成領域1A、Pチャネル型高耐圧MOSFET形成領域1B、Nチャネル型低耐圧MOSFET形成領域1CおよびPチャネル型低耐圧MOSFET形成領域1Dを示している。Nチャネル型またはPチャネル型の高耐圧MOSFETは例えばI/O部に設けられるトランジスタであり、比較的高い電圧により駆動する。Nチャネル型またはPチャネル型の低耐圧MOSFETはNチャネル型またはPチャネル型の高耐圧MOSFETよりも小さい電流および電圧で駆動するトランジスタであり、半導体装置内のコア部においてスイッチングなどの用途に用いられるものである。なお、ここで言うコア部とは、上記したI/O部とは異なり、I/O部よりも低い電流・電圧で駆動される素子により構成される回路などを含む領域である。

【0055】

まず、図5に示すように、半導体基板1の主面に周知の技術を用いて素子分離領域15を複数形成する。Nチャネル型高耐圧MOSFET形成領域1A、Pチャネル型高耐圧MOSFET形成領域1B、Nチャネル型低耐圧MOSFET形成領域1CおよびPチャネル型低耐圧MOSFET形成領域1Dはそれぞれ素子分離領域15によりその範囲を規定され、互いに分離されている。素子分離領域15は例えばSTI(Shallow Trench Isolation)であるものとする。このとき、半導体基板1の主面の保護などを目的として半導体基板1の主面に熱酸化膜などを形成することが考えられるが、ここではその図示を省略する。

【0056】

次に、図6に示すように、フォトリソグラフィ技術を用い、Nチャネル型高耐圧MOSFET形成領域1Aのみを露出するようなフォトレジスト膜P1を半導体基板1上に形成する。続いて、Nチャネル型高耐圧MOSFET形成領域1Aの半導体基板1の主面にP型の不純物(例えばB(ホウ素))をイオン注入法により注入し、半導体基板1の主面にPウエル2を形成する。このとき、フォトレジスト膜P1により半導体基板1の主面の一部を覆うことで、Nチャネル型高耐圧MOSFET形成領域1A以外の領域に不純物が導入されることを防ぐ。

【0057】

次に、図7に示すように、フォトレジスト膜P1を除去した後、図6を用いて説明した方法と同様にして、Pチャネル型高耐圧MOSFET形成領域1B、Nチャネル型低耐圧MOSFET形成領域1CおよびPチャネル型低耐圧MOSFET形成領域1DにN型の不純物(例えばP(リン))、P型の不純物(例えばB(ホウ素))およびN型の不純物(例えばP(リン))をそれぞれイオン注入する。これにより、Pチャネル型高耐圧MOSFET形成領域1B、Nチャネル型低耐圧MOSFET形成領域1CおよびPチャネル型低耐圧MOSFET形成領域1DにNウエル2b、Pウエル2cおよびNウエル2dを形成する。このとき、図6を用いて説明したイオン注入工程と同様に、目的の領域以外に不純物が導入されることを防ぐため、各イオン注入工程の前に目的の領域以外を覆うフォトレジスト膜(図示しない)を半導体基板1上に形成し、マスクとして利用する。このように、Nチャネル型高耐圧MOSFET形成領域1A、Pチャネル型高耐圧MOSFET形成領域1B、Nチャネル型低耐圧MOSFET形成領域1CおよびPチャネル型低耐圧MOSFET形成領域1Dのそれぞれには別工程により不純物を導入し、ウエルを形成するものとするが、Pウエル2およびPウエル2cは同一工程で形成してもよく、同様にNウエル2bおよびNウエル2dは同一工程で形成してもよい。

【0058】

次に、図8に示すように、Nチャネル型高耐圧MOSFET形成領域1AおよびPチャネル型高耐圧MOSFET形成領域1Bと、Nチャネル型低耐圧MOSFET形成領域1CおよびPチャネル型低耐圧MOSFET形成領域1Dとで厚さが異なる2種類の絶縁膜を半導体基板1の上面に形成する。つまり、Nチャネル型高耐圧MOSFET形成領域1AおよびPチャネル型高耐圧MOSFET形成領域1Bの半導体基板1の主面には比較的膜厚が厚い絶縁膜3abを形成し、Nチャネル型低耐圧MOSFET形成領域1CおよびPチャネル型低耐圧MOSFET形成領域1Dの半導体基板1の主面には絶縁膜3abよりも膜厚が薄い絶縁膜3cdを形成する。

【0059】

この場合は、例えば熱酸化法またはCVD(Chemical Vapor Deposition)法を用いて半導体基板1の主面の全面上に絶縁膜3abを形成した後に、フォトリソグラフィ技術およびウェットエッチング法などを用いてNチャネル型低耐圧MOSFET形成領域1CおよびPチャネル型低耐圧MOSFET形成領域1Dの絶縁膜3abを除去する。その後、例えば熱酸化法を用いて半導体基板1の主面を加熱し、Nチャネル型低耐圧MOSFET形成領域1CおよびPチャネル型低耐圧MOSFET形成領域1Dの半導体基板1の主面に絶縁膜3cdを形成する。絶縁膜3ab、3cdは例えば酸化シリコンからなる膜である。

【0060】

次に、図9に示すように、半導体基板1の主面上の全面に例えばCVD法を用いてポリシリコン膜を形成(堆積)した後、フォトリソグラフィ技術およびドライエッチング法を用いて前記ポリシリコン膜およびその下部の絶縁膜3ab、3cdを加工(パターニング)し、前記ポリシリコン膜からなるゲート電極4と、絶縁膜3abからなるゲート絶縁膜3、3bと、絶縁膜3cdからなるゲート絶縁膜3c、3dとを形成する。Nチャネル型高耐圧MOSFET形成領域1Aでは半導体基板1上にゲート絶縁膜3を介してゲート電極4が形成され、Pチャネル型高耐圧MOSFET形成領域1Bでは半導体基板1上にゲート絶縁膜3bを介してゲート電極4が形成され、Nチャネル型低耐圧MOSFET形成領域1Cでは半導体基板1上にゲート絶縁膜3cを介してゲート電極4が形成され、Pチャネル型低耐圧MOSFET形成領域1Dではゲート絶縁膜3dを介してゲート電極4が形成される。Nチャネル型高耐圧MOSFET形成領域1AおよびPチャネル型高耐圧MOSFET形成領域1Bのゲート電極4、ゲート絶縁膜3および3bのゲート長方向の幅は、Nチャネル型低耐圧MOSFET形成領域1CおよびPチャネル型低耐圧MOSFET形成領域1Dのゲート電極4、ゲート絶縁膜3cおよび3dのゲート長方向の幅よりも大きく形成する。

【0061】

次に、図10に示すように、Pチャネル型高耐圧MOSFET形成領域1B、Nチャネル型低耐圧MOSFET形成領域1CおよびPチャネル型低耐圧MOSFET形成領域1Dと、Nチャネル型高耐圧MOSFET形成領域1Aの一部の半導体基板1の主面およびゲート電極4の一部とを覆うようにフォトレジスト膜P2を形成する。なお、ここでフォトレジスト膜P2により覆ったNチャネル型高耐圧MOSFET形成領域1Aの半導体基板1の主面の一部は、後の工程により形成されるNチャネル型高耐圧MOSFETのドレイン領域となる部分である。つまり、ここではNチャネル型高耐圧MOSFET形成領域1Aのゲート電極4の左右の半導体基板1の主面のうち、ドレイン領域側をフォトレジスト膜P2で覆い、ソース領域側を露出させる。

【0062】

続いて、フォトレジスト膜P2、ゲート電極4およびゲート絶縁膜3から露出しているNチャネル型高耐圧MOSFET形成領域1Aのソース領域側の半導体基板1の主面のみにP型不純物(例えばB(ホウ素))を斜めイオン注入(傾斜注入)し、Pウエル10を形成する。この工程でのイオン注入では、例えばB(ホウ素)を5〜30keVのエネルギー、1×1013〜3×1013cm−2のドーズ量および10°〜45°の角度で注入を行う。このように、半導体基板1の主面に対して垂直な方向からイオン注入を行うのではなく、半導体基板1の主面に対して斜めの方向から注入を行うことで、ゲート電極4の直下の半導体基板1の主面においてよりドレイン領域側に近い箇所にまでPウエル10が形成され、Pウエル10のゲート電極4に対するオーバーラップする面積が大きくなる。

【0063】

次に、図11に示すように、フォトレジスト膜P2およびゲート電極4をマスクとして、半導体基板1の主面に対して垂直な方向からN型の不純物(例えばP(リン))をイオン注入することにより、ソース領域側のLDD層7を形成する。この注入工程では、例えばP(リン)を5〜15keVのエネルギー、5×1012〜2×1013cm−2のドーズ量でイオン注入を行う。ここでは、Pウエル10よりも浅い接合深さでLDD層7を形成する。また、LDD層7は半導体基板1の主面に対して垂直な方向にイオン注入をしているのに対し、Pウエル10は斜めイオン注入により形成されているため、Pウエル10の方がLDD層7よりもゲート電極4とのオーバーラップ量、すなわち平面視においてPウエル10とゲート電極4とが重なる領域が大きくなる。

【0064】

次に、図12に示すように、フォトレジスト膜P2を除去した後、Pウエル10およびLDD層7が形成されたNチャネル型高耐圧MOSFET形成領域1Aのソース領域側と、Pチャネル型高耐圧MOSFET形成領域1B、Nチャネル型低耐圧MOSFET形成領域1CおよびPチャネル型低耐圧MOSFET形成領域1Dとを覆うように半導体基板1上にフォトレジスト膜P3を形成する。これにより、図10および図11を用いて説明した工程ではフォトレジスト膜P2に覆われていたNチャネル型高耐圧MOSFET形成領域1Aのドレイン領域側の半導体基板1の主面が露出する。

【0065】

続いて、フォトレジスト膜P3から露出している半導体基板1の主面にN型不純物(例えばP(リン))を斜めイオン注入することで、高耐圧MOSFETのドレイン領域を構成するLDD層6を形成する。ドレイン領域側のLDD層6の不純物の注入は、高耐圧MOSFETがオフの状態での耐圧が最も高くなる条件で行う。つまり、イオン注入は例えばP(リン)を65keVのエネルギー、5×1013〜1.5×1014cm−2のドーズ量、45°の角度で行う。このとき、LDD層6はLDD層7よりも深く、また、Pウエル10よりも深い接合深さで形成する。LDD層6は斜めイオン注入法により形成されるため、半導体基板1の主面に対して垂直にイオン注入を行う場合に比べてゲート電極4との平面視におけるオーバーラップ量が大きくなる。

【0066】

次に、図13に示すように、ドレイン領域側のLDD層6を形成した半導体基板1の主面にP型の不純物(例えばB(ホウ素))を、半導体基板1の主面に対して垂直な方向からイオン注入することで、N−−領域11を形成する。注入条件は、例えばB(ホウ素)を5〜20keVのエネルギー、5×1013〜2×1014cm−2のドーズ量とする。N−−領域11を形成する前記注入工程では、高耐圧MOSFETの電流経路で電界が一番強い領域にイオン注入し、ドレイン領域側のLDD層6を中性化する。これによってドレイン領域側のLDD層6の中にN型不純物(例えばP(リン))の濃度が低いN−−領域11を作製する。

【0067】

ここで注入するP型の不純物(例えばB(ホウ素))は、N−−領域11がLDD層6よりもゲート電極4とのオーバーラップ量が少なくなるように注入する。つまり、LDD層6の方がN−−領域11よりもソース領域側に配置されるようにN−−領域11を形成する。P型の不純物(例えばB(ホウ素))を打ち込んで形成する領域(N−−領域11)の方がLDD層6よりもゲート電極4とのオーバーラップ量が大きい場合、ドレイン領域からの空乏層の伸びを抑え、短チャネル効果を改善する効果が期待できるが、電界が強くなり耐圧が劣化するため、耐圧を確保する観点から上記のようにLDD層6よりもN−−領域11の方がゲート電極4とのオーバーラップ量が小さくなるようにする必要がある。

【0068】

なお、ここではソース領域を構成するLDD層7などを先に形成する製造工程を説明しているが、ドレイン領域側のLDD層6、N−−領域11などをソース領域側のLDD層7などより先に形成しても良い。

【0069】

続いて、イオン注入した不純物の拡散などを目的として半導体基板1を熱処理するが、この場合、N−−領域11中を形成するために打ち込んだP型不純物(例えばB(ホウ素))が、LDD層6の外側のチャネル領域などに拡散しないような熱処理を行う。これは、LDD層6の外側に濃度が高いP型半導体領域が形成されると、当該P型半導体領域とLDD層6との間に強いPN接合が形成され、電界が強くなるためである。したがって、ここではLDD層6端部の電界が大きくなって耐圧が低下することを防ぐため、N−−領域11中を形成するために打ち込んだP型不純物(例えばB(ホウ素))がLDD層6の外側に拡散しないように当該P型不純物の注入および熱処理による拡散を行っている。よって、チャネル層とN−−領域11との間にはN−−領域11よりもN型不純物濃度が高いLDD層6が介在することとなる。これにより、N−−領域11はLDD層6内においてLDD層6よりも接合深さが浅く、N型不純物(例えばP(リン))の濃度が低い半導体領域として形成される。

【0070】

次に、図14に示すように、フォトレジスト膜P3を除去した後、Pチャネル型高耐圧MOSFET形成領域1Bを露出し、Nチャネル型高耐圧MOSFET形成領域1A、Nチャネル型低耐圧MOSFET形成領域1CおよびPチャネル型低耐圧MOSFET形成領域1Dを覆うフォトレジスト膜P4を半導体基板1上に形成する。続いて、露出した半導体基板1の主面にP型不純物(例えばB(ホウ素))を斜めイオン注入法により注入することにより、Pチャネル型高耐圧MOSFET形成領域1Bのゲート電極4の左右の半導体基板1の主面に一対のLDD層(N−領域)6bを形成する。

【0071】

次に、図15に示すように、フォトレジスト膜P4を除去した後、複数のゲート電極4の表面を覆うように半導体基板1の主面上に例えばCVD法などにより酸化シリコン膜を形成し、続いてドライエッチング法により前記酸化シリコン膜を一部除去して半導体基板1の主面を露出させる。これにより、各ゲート電極4の側壁に前記酸化シリコン膜からなるオフセットスペーサ16を自己整合的に形成する。

【0072】

次に、図16に示すように、Nチャネル型低耐圧MOSFET形成領域1Cを露出するフォトレジスト膜P5を形成し、露出した半導体基板1の主面にP型の不純物(例えばB(ホウ素))をイオン注入することで、Nチャネル型低耐圧MOSFET形成領域1Cのゲート電極4の両側の半導体基板1の主面に一対のハロー領域(P−領域)10cを形成する。続いて、フォトレジスト膜P5から露出した半導体基板1の主面にN型の不純物(例えばP(リン))をイオン注入することで、Nチャネル型低耐圧MOSFET形成領域1Cのゲート電極4の両側の半導体基板1の主面に一対のLDD層(N−領域)6cを形成する。ハロー領域10cはLDD層6cよりも深い接合深さを有しており、半導体基板1内においてLDD層6cを囲むように形成されている。

【0073】

なお、図16に示したハロー領域10cおよびLDD層6cを形成する工程は、前述のオフセットスペーサ16を形成する前に行ってもよい。

【0074】

次に、図17に示すように、フォトレジスト膜P5を除去した後、Pチャネル型低耐圧MOSFET形成領域1Dを露出するフォトレジスト膜P6を形成し、露出した半導体基板1の主面にN型の不純物(例えばP(リン))をイオン注入することで、Pチャネル型低耐圧MOSFET形成領域1Dのゲート電極4の両側の半導体基板1の主面に一対のハロー領域(P−領域)10dを形成する。続いて、フォトレジスト膜P6から露出した半導体基板1の主面にP型の不純物(例えばB(ホウ素))をイオン注入することで、Pチャネル型低耐圧MOSFET形成領域1Dのゲート電極4の両側の半導体基板1の主面に一対のLDD層(N−領域)6dを形成する。ハロー領域10dはLDD層6dよりも深い接合深さを有しており、半導体基板1内においてLDD層6dを囲むように形成されている。

【0075】

次に、図18に示すように、フォトレジスト膜P6を除去した後、複数のゲート電極4の表面を覆うように半導体基板1の主面上に例えばCVD法などにより絶縁膜を形成し、続いてドライエッチング法により前記絶縁膜を一部除去して半導体基板1の主面を露出させる。これにより、各ゲート電極4の側壁に前記酸化シリコン膜からなるサイドウォール17を自己整合的に形成する。前記絶縁膜は、例えば酸化シリコン膜および窒化シリコン膜の積層膜などからなる。

【0076】

次に、図19に示すように、Pチャネル型高耐圧MOSFET形成領域1B(図18参照)およびPチャネル型低耐圧MOSFET形成領域1D(図18参照)を露出するフォトレジスト膜P7を形成した後、露出した半導体基板1の主面にP型の不純物(例えばB(ホウ素))を高い濃度でイオン注入する。これにより、Pチャネル型高耐圧MOSFET形成領域1Bのゲート電極4の両側の半導体基板1の主面に一対の拡散層8bを形成し、Pチャネル型低耐圧MOSFET形成領域1Dのゲート電極4の両側の半導体基板1の主面に一対の拡散層8dを形成する。この工程により、半導体基板1の主面のI/O部には、ゲート電極4、拡散層8bおよびLDD層6bを含むPチャネル型高耐圧MOSFETHpが形成され、半導体基板1の主面のコア部には、ゲート電極4、ハロー領域10d、拡散層8dおよびLDD層6dを含むPチャネル型低耐圧MOSFETLpが形成される。

【0077】

次に、図20に示すように、フォトレジスト膜P7を除去した後、Nチャネル型高耐圧MOSFET形成領域1A(図19参照)およびNチャネル型低耐圧MOSFET形成領域1C(図19参照)を露出するフォトレジスト膜P8を形成した後、露出した半導体基板1の主面にN型の不純物(例えばP(リン))を高い濃度でイオン注入する。これにより、Nチャネル型高耐圧MOSFET形成領域1Aのゲート電極4の両側の半導体基板1の主面に一対の拡散層5、8を形成し、Nチャネル型低耐圧MOSFET形成領域1Cのゲート電極4の両側の半導体基板1の主面に一対の拡散層8cを形成する。この工程により、半導体基板1の主面のI/O部には、ゲート電極4、拡散層5、LDD層7、Pウエル10、拡散層8、N−−領域11およびLDD層6を含むNチャネル型高耐圧MOSFETHnが形成され、半導体基板1の主面のコア部には、ゲート電極4、ハロー領域10c、拡散層8cおよびLDD層6cを含むNチャネル型低耐圧MOSFETLnが形成される。

【0078】

このとき、Nチャネル型低耐圧MOSFETHnのドレイン領域側の拡散層8は、N−−層11よりも浅い接合深さで形成し、また、ソース領域側の拡散層5は、Pウエル10よりも深い接合深さで形成する。

【0079】

次に、図21に示すように、フォトレジスト膜P8を除去した後、周知のサリサイド技術により拡散層5、8b、8c、8dおよびゲート電極4のそれぞれの上面にシリサイド層14を形成する。このとき形成するシリサイド層14の部材は、NiSi(ニッケルシリサイド)またはCoSi(コバルトシリサイド)などとすることができる。ここでは、半導体基板1上に形成したNi(ニッケル)などを含む金属膜を、熱処理により下部の半導体層と反応させることで金属シリサイド層を形成する。

【0080】

続いて、半導体基板1の主面上に、ゲート電極4を覆うようにエッチストッパ膜19aおよび層間絶縁膜19を順次形成する。エッチストッパ膜19aは、例えば酸化シリコン膜の単体膜または薄い窒化シリコン膜からなり、その上の層間絶縁膜19は厚い酸化シリコン膜からなる。エッチストッパ膜19aおよび層間絶縁膜19の形成後、層間絶縁膜19の表面を、例えばCMP(Chemical Mechanical Polishing)法を使用して平坦化する。

【0081】

次に、図22に示すように、層間絶縁膜19上に形成したフォトレジスト膜(図示せず)をエッチングマスクとして用いて、エッチストッパ膜19aおよび層間絶縁膜19をドライエッチングすることにより、エッチストッパ膜19aおよび層間絶縁膜19を貫通する複数のコンタクトホール(貫通孔、孔)を形成する。前記複数のコンタクトホールは、拡散層5、8b、8c、8dおよびゲート電極4のそれぞれの上部のシリサイド層14に達する孔である。

【0082】

続いて、前記複数のコンタクトホール内に、タングステン(W)などからなる導電性のコンタクトプラグ(接続用導体部)20を形成する。コンタクトプラグ20を形成するには、例えば、コンタクトホールの底部および側壁を含む層間絶縁膜19上に、バリア導体膜(例えばチタン膜、窒化チタン膜、あるいはそれらの積層膜)を形成する。それから、前記バリア導体膜上にタングステン膜などからなる主導体膜を形成して前記コンタクトホールを埋め込み、層間絶縁膜19上の不要な前記主導体膜および前記バリア導体膜をCMP法またはエッチバック法などによって除去することにより、コンタクトプラグ20を形成する。なお、図面の簡略化のために、図22ではコンタクトプラグ20を構成するバリア導体膜および主導体膜(タングステン膜)を一体化して示している。

【0083】

続いて、コンタクトプラグ20が埋め込まれた層間絶縁膜19上に、ストッパ絶縁膜(エッチングストッパ用絶縁膜)21および配線形成用の層間絶縁膜22を順次形成する。ストッパ絶縁膜21は、層間絶縁膜22への溝加工の際にエッチングストッパとなる膜であり、層間絶縁膜22に対してエッチング選択性を有する材料を用い、例えば、ストッパ絶縁膜21を窒化シリコン膜とし、層間絶縁膜22を酸化シリコン膜とすることができる。

【0084】

その後、シングルダマシン法により第1層目の配線を形成する。まず、フォトレジスト膜(図示せず)をマスクとしたドライエッチングによって層間絶縁膜22およびストッパ絶縁膜21の所定の領域にコンタクトプラグ20を露出する複数の配線溝を形成した後、半導体基板1の主面上に例えば窒化チタン膜、タンタル膜または窒化タンタル膜などからなるバリアメタル膜を形成する。続いて、CVD法またはスパッタリング法などによりバリアメタル膜上に銅のシード層を形成し、さらに電解めっき法などを用いてシード層上に銅めっき膜を形成し、前記銅めっき膜により前記配線溝の内部を埋め込む。それから、配線溝以外の領域の銅めっき膜、シード層およびバリアメタル膜をCMP法により除去して、銅を主導電材料とする第1層目の配線M1を形成する。なお、図面の簡略化のために、図20では、配線M1を構成する銅めっき膜、シード層およびバリアメタル膜を一体化して示してある。

【0085】

配線M1は、コンタクトプラグ20を介して各MOSFETのソース・ドレインおよびゲート電極などと電気的に接続されている。その後、デュアルダマシン法などにより配線M1上に2層目以降の配線を形成することで本実施の形態の半導体装置が完成するが、ここでは2層目以降の配線の図示およびその製造工程の説明は省略する。また、配線M1はダマシン配線に限定されず、配線用の導電体膜をパターニングして形成することもでき、例えばタングステン配線またはアルミニウム配線などとすることもできる。

【0086】

本実施の形態では、図10〜図13を用いて説明したような斜めイオン注入法を利用して不純物の打ち込みを行うことにより、ゲート電極4を中心として左右非対称のソース・ドレイン領域を形成している。つまり、図10を用いて説明したPウエル10の形成工程では、傾斜注入によってソース領域側のPウエル10のゲート電極4に対するオーバーラップ量を大きくすることで、MOSFETの動作時にドレイン領域側から伸びる空乏層を止め、短チャネル効果を改善することを可能としている。また、図11を用いて説明したLDD層7の形成工程では、LDD層7を形成することによってNチャネル型高耐圧MOSFETのソース領域側の抵抗を低減することを可能にすると共に、LDD層7をドレイン領域側のLDD層6(図1参照)よりも深さが浅く濃度が低い領域とすることによって、半導体基板1の主面から深い位置でパンチスルーしにくく、素子ばらつきの小さい構造とすることを可能としている。

【0087】

これらの工程により、ソース領域側のLDD層7をLDD層6よりも浅く且つ不純物濃度を低く形成し、さらに不純物濃度が高いPウエル10をLDD層7の周囲に形成することによってソース・ドレイン間に空乏層が伸びことを防ぎ、ソース・ドレイン間におけるパンチスルーの発生を防ぐことを可能としている。

【0088】

また、図1を用いて説明したように、ドレイン領域側のLDD層6内に不純物濃度が低いN−−領域11を形成することにより、ドレイン領域内の電界が高くなることを防ぎ、オン状態でもオフ状態でもインパクトイオン化が起こりにくいMOSFETを実現することができる。

【0089】

また、本実施の形態では、ドレイン領域側のLDD層6を形成する際のN型不純物(例えばP(リン))の注入濃度を調整することにより、ドレイン領域側のLDD層6の不純物濃度をLDD層7よりも高くしているため、オン状態で電流が流れる経路の電界は強くなり、一方で、オフ状態でのPウエル2およびLDD層6間のPN接合での電界は弱くなる。したがって、Pウエル2とLDD層6との間でインパクトイオンが発生することを防ぎ、耐圧を向上させることができる。上記のように、MOSFETの面積を大きくしなくても高耐圧化が可能となり、素子の微細化も容易になるため、半導体装置の性能を向上させることができる。

【0090】

(実施の形態2)

本実施の形態では、I/O部のNチャネル型高耐圧MOSFETのドレイン側の半導体基板1の主面をエピタキシャル成長させることにより、Nチャネル型高耐圧MOSFETのドレインを構成するエピタキシャル層を設けた半導体装置について説明する。

【0091】

図23に示すように、本実施の形態の半導体装置のNチャネル型高耐圧MOSFETは前記実施の形態1において図1を用いて説明したNチャネル型高耐圧MOSFETとほぼ同様の構造を有しているが、ドレイン側の半導体基板1内にはN−−領域11は形成されておらず、LDD層6のみが形成されており、LDD層6上にエピタキシャル層12がLDD層6の上面に接して形成され、エピタキシャル層12の上面に拡散層8が形成されている。なお、拡散層8はエピタキシャル層12の底面に達しておらず、エピタキシャル層12内の上部のみに形成されている。よって、半導体基板の主面には、ソース領域側からドレイン領域側にかけて順に拡散層5、LDD層7、Pウエル10、Pウエル2およびLDD層6が形成されており、チャネル領域側のLDD層6の端部と拡散層8との間にはエピタキシャル層12が形成されている。

【0092】

エピタキシャル層12はLDD層6よりもN型の不純物濃度が低いN型の半導体領域であり、ゲート電極4の一方の側壁に例えば酸化シリコンからなるオフセットスペーサ16を介して配置されており、ゲート電極4と絶縁して形成されている。またエピタキシャル層12は、LDD層6が形成された半導体基板1の主面上に10〜40nmの膜厚で形成されている。なお、図23が本実施の形態の半導体装置のNチャネル型高耐圧MOSFETを示す断面図であり、図23ではMOSFET上のシリサイド層、層間絶縁膜、コンタクトプラグおよび配線層などの図示は省略している。

【0093】

エピタキシャル層12は主にSi(シリコン)からなり、N型の不純物(例えばP(リン))が導入されている。また、エピタキシャル層12の上面にはN型の不純物(例えばP(リン))がLDD層6およびエピタキシャル層12よりも高濃度で導入された拡散層8が形成されており、エピタキシャル層12の直上にはゲート電極4の側壁にオフセットスペーサ16を介してサイドウォール17が形成されている。ここでは、LDD層6、エピタキシャル層12および拡散層8がドレイン領域を構成している。なお、エピタキシャル層12の側壁であって、ゲート電極4の側壁のオフセットスペーサ16と接していない方の側壁にもサイドウォール17が形成されている。

【0094】

図23に示すように、本実施の形態のNチャネル型高耐圧MOSFETHnは、ゲート電極4、拡散層5、LDD層7、Pウエル10、Pウエル2、拡散層8、LDD層6およびエピタキシャル層12を含んでいる。

【0095】

ここでは、前記実施の形態1のようにP型の不純物(例えばB(ホウ素))を打ち込むのではなく、半導体基板1の一部の上面にエピタキシャル層を形成することで、ドレイン領域内にLDD層6よりも不純物濃度が低い領域を形成している。このようにしてMOSFETのチャネル領域の近傍のドレイン端の一部の不純物濃度を低減することにより、前記実施の形態1と同様に電界を小さくしてインパクトイオン化を防ぎ、オン状態およびオフ状態のMOSFETの耐圧を向上させている。

【0096】

次に、本実施の形態の半導体装置の製造方法を図24〜図26を用いて説明する。図24〜図26は本実施の形態の半導体装置の製造工程を示す断面図であり、図5などと同様にNチャネル型高耐圧MOSFET形成領域1A、Pチャネル型高耐圧MOSFET形成領域1B、Nチャネル型低耐圧MOSFET形成領域1CおよびPチャネル型低耐圧MOSFET形成領域1Dを示している。

【0097】

まず、図5〜図12を用いて説明した工程と同様の工程を行うことにより、Nチャネル型高耐圧MOSFET形成領域1Aの半導体基板1の主面上にゲート電極4を形成し、半導体基板1の主面にPウエル10、LDD層6および7を形成する。その後、図13を用いて説明したイオン注入工程は行わずに、図14を用いて説明したイオン注入工程を行うことでPチャネル型高耐圧MOSFET形成領域1Bの半導体基板1の主面にLDD層6bを形成する。

【0098】

続いて、図24に示すように、CVD法などを用いて半導体基板1の主面上に例えば酸化シリコン膜からなる膜厚5〜20nmの絶縁膜23を形成した後、フォトリソグラフィ技術およびエッチング法を用いて、Nチャネル型高耐圧MOSFET形成領域1Aのドレイン領域側の半導体基板1の主面上に形成された絶縁膜23をドライエッチング法により除去し、他の領域の絶縁膜23を残す。これにより、Nチャネル型高耐圧MOSFET形成領域1Aのドレイン領域側の半導体基板1の主面のみを露出させるように絶縁膜23を開口させる。

【0099】

なお、図24ではゲート電極4の上面全体に絶縁膜23が残される場合を例示しているが、ゲート電極4の上面の一部を露出するようにしてもよい。すなわち、ドライエッチングは異方性エッチングで行い、ゲート電極4の側面に絶縁膜23を残し、フォトレジスト膜で覆われていないゲート電極4の上面の一部を露出するようにしてもよい。この場合、ゲート電極4のドレイン側の上面にもエピタキシャル層12が形成されるが、Nチャネル型高耐圧MOSFETの特性に問題はない。

【0100】

次に、図25に示すように、絶縁膜23から露出している半導体基板1の主面上、すなわちNチャネル型高耐圧MOSFET形成領域1Aのドレイン領域側の半導体基板1の主面上にのみエピタキシャル成長法を用いて10〜40nmの膜厚を有するエピタキシャル層12を形成する。このとき、エピタキシャル層12のN型の不純物濃度はLDD層6よりも低くなる。

【0101】

続いて、半導体基板1上の絶縁膜23の一部をドライエッチング法により除去し、ゲート電極4の上面および半導体基板1の主面を露出させる。これにより、ゲート電極4の側壁に絶縁膜23からなるオフセットスペーサ16が自己整合的に形成される。

【0102】

なお、図24におけるNチャネル型高耐圧MOSFET形成領域1Aのドレイン領域側の絶縁膜23を除去する工程は、前述の図12および図13に示すフォトレジスト膜P3を形成するために用いたマスクと同じマスクを用いても良い。これによりマスクの数を削減できるため、製造コストを減少させることができる。なお、この場合には、上述のように、ゲート電極4のドレイン側の部分にもエピタキシャル層12が形成されることになる。

【0103】

この後の工程は、前記実施の形態1において図16〜図22を用いて説明した工程と同様の工程を行うことにより、図26に示す本実施の形態の半導体装置が完成する。ただし、図20に対応する拡散層の形成工程では、Nチャネル型高耐圧MOSFET形成領域1A(図25参照)のドレイン領域側に拡散層8を形成する際、エピタキシャル層12の上面にN型の不純物(例えばP(リン))をイオン注入して拡散層8を形成する。

【0104】

図26に示すように、完成した本実施の形態の半導体装置のNチャネル型高耐圧MOSFETは図23に示す構造と同様の構造上にシリサイド層14、エッチストッパ膜19a、層間絶縁膜19、コンタクトプラグ20、ストッパ絶縁膜21、層間絶縁膜22、配線M1が形成された構造となっており、Pチャネル型高耐圧MOSFET、Nチャネル型低耐圧MOSFETおよびPチャネル型低耐圧MOSFETは前記実施の形態1と同様の構造となっている。

【0105】

上記の製造工程により形成した半導体装置では、前記実施の形態1において説明したN−−領域11(図1参照)と同様に、Nチャネル型高耐圧MOSFETのドレイン領域内にLDD層6よりも不純物濃度が低い層であるエピタキシャル層12を形成することにより、ドレイン領域の電界が大きくなることを防ぐことができ、前記実施の形態1と同様の効果を得ることができる。

【0106】

また、本実施の形態の半導体装置ではN−−領域11(図1参照)を形成するためのP型の不純物(例えばB(ホウ素))の打ち込み工程がないため、不純物の分布のばらつきに起因した素子間の性能のばらつきの発生を抑えることができる。

【0107】

なお、ここでは図23に示す拡散層8がエピタキシャル層12の底面に達していない場合について説明したが、拡散層8はエピタキシャル層12の上面から半導体基板1の内部にかけて形成されていても構わない。ただし、本実施の形態の半導体装置の特徴は、エピタキシャル層12を形成することにより、ドレイン領域内のチャネル領域近傍の端部にLDD層6よりも不純物濃度が低い領域を設けることにあるため、エピタキシャル層12内のゲート電極4側の端部に拡散層8が形成されていない領域を残す必要がある。

【0108】

(実施の形態3)

本実施の形態では、高耐圧MOSFETのゲート電極の一方の側壁にサイドウォールを追加して形成することにより、図1を用いて説明したN−−領域11を形成するためのP型不純物(例えばB(ホウ素))が過度に拡散することを防ぐことを可能とする半導体装置について説明する。

【0109】

図27に本実施の形態の半導体装置の断面図を示す。図27に示す半導体装置は図1に示す前記実施の形態1の半導体装置とほぼ同様の構造を有しているが、図1の構造に加えて、ゲート電極4の一方の側壁にオフセットスペーサ16を介してサイドウォール24および17が前記一方の側壁側から順に形成されている。ただし、ゲート電極4のもう一方の側壁にはサイドウォール24は形成されておらず、前記もう一方の側壁側から順にオフセットスペーサ16およびサイドウォール17が形成されている。つまり、本実施の形態のNチャネル型高耐圧MOSFETのゲート電極4の側壁のサイドウォールを構成する絶縁膜はドレイン領域側の方がソース領域側よりも多いため、ゲート電極4の側壁のサイドウォールは左右非対称の構造を有しており、ドレイン領域側のサイドウォールはソース領域側のサイドウォールに比べてゲート長方向の厚さが大きく形成されている。

【0110】

したがって、ゲート電極4およびゲート電極4の側壁のサイドウォールをマスクとしたイオン注入法により自己整合的に半導体基板1の主面に形成される拡散層5および8は、ゲート電極4を中心として左右対称に形成されていない。サイドウォール24は例えば窒化シリコン膜などの絶縁膜からなり、ゲート電極4の一方の側壁に自己整合的に形成されている。

【0111】

微細化されたMOSFETでは、ソース・ドレイン領域を構成する拡散層よりも接合深さが深いLDD層を形成するイオン注入工程において、打ち込まれたイオン(不純物)がゲート電極を突き抜けないように注入エネルギーを調整する必要がある。特に低耐圧のMOSFETを有するコア部では素子の微細化が進むにつれてゲート電極の高さが低くなるため、LDD層を形成するためのイオン注入のエネルギーは低くする必要がある。このとき、LDD層を形成するために打ち込むN型の不純物(例えばP(リン))に比べて、図1に示すようなN−−領域11を形成するために打ち込むP型の不純物(例えばB(ホウ素))の方が半導体基板内において広範囲に拡散しやすくなり、P型の不純物(例えばB(ホウ素))のゲート電極に対するオーバーラップ量が大きくなり、MOSFETの耐圧が低下する虞がある。

【0112】

そこで、本実施の形態の半導体装置では、図27に示すように、MOSFETのドレイン領域側のゲート電極の側壁にのみサイドウォール24を形成した状態でイオン注入を行ってN−−領域11を形成することで、N−−領域11の形成工程において注入するP型不純物(例えばB(ホウ素))がLDD層6よりも大きくゲート電極4にオーバーラップすることを防いでいる。

【0113】

これにより、N−−領域11のLDD層6の内側に形成され、N−−領域11を構成するP型不純物(例えばB(ホウ素))がチャネル領域側のLDD層6の端部よりも外側に導入されることを防ぐことができる。従って、微細化された半導体装置であってLDD層6を形成するためのイオン注入エネルギーを低く抑える必要がある半導体装置でも、P型の不純物(例えばB(ホウ素))がLDD層6よりも大きくゲート電極4にオーバーラップすることに起因する耐圧の低下を防ぎ、前記実施の形態1と同様の効果を得ることができる。よって、半導体装置の微細化の際に起きる低耐圧化の問題が発生することを防ぎ、半導体装置の微細化を容易にすることで半導体装置の性能を向上させることができる。

【0114】

以下に、図28〜図30を用いて本実施の形態の半導体装置の製造工程を説明する。

【0115】

まず、図5〜図12を用いて説明した工程と同様の工程を行うことにより、Nチャネル型高耐圧MOSFET形成領域1Aの半導体基板1の主面上にゲート電極4を形成し、半導体基板1の主面にPウエル10、LDD層6および7を形成する。その後、図13を用いて説明したイオン注入工程は行わずに、図14および図15を用いて説明したイオン注入工程を行うことでPチャネル型高耐圧MOSFET形成領域1Bの半導体基板1の主面にLDD層6bを形成し、複数のゲート電極4のそれぞれの側壁にオフセットスペーサ16を形成する。

【0116】

続いて、図28に示すように、複数のゲート電極4を覆うように半導体基板1の主面上の全面にCVD法などにより例えば窒化シリコン膜からなる絶縁膜を形成(堆積)した後、ドライエッチング法を用いて前記絶縁膜を一部除去し、ゲート電極4の上面および半導体基板1の主面を露出させることにより、各ゲート電極4の両側の側壁に前記絶縁膜からなるサイドウォール24を自己整合的に形成する。なお、ここではオフセットスペーサ16およびサイドウォール24のそれぞれの膜の部材に別の材料を用いるものとする。例えば、オフセットスペーサ16に酸化シリコン膜を用いた場合、サイドウォール24には窒化シリコン膜を用いる。

【0117】

次に、図29に示すように、Nチャネル型高耐圧MOSFET形成領域1Aのドレイン領域側のゲート電極4の側壁に形成されたサイドウォール24を覆い、Nチャネル型高耐圧MOSFET形成領域1Aのゲート電極4のもう一方の側壁と、Nチャネル型高耐圧MOSFET形成領域1A以外の領域の各ゲート電極4の両側の側壁とに形成されたサイドウォール24を露出するフォトレジスト膜P9を形成する。

【0118】

続いて、フォトレジスト膜P9をエッチングマスクとしてエッチングを行うことにより、Nチャネル型高耐圧MOSFET形成領域1Aのソース領域側のゲート電極4の側壁と、Pチャネル型高耐圧MOSFET形成領域1B、Nチャネル型低耐圧MOSFET形成領域1CおよびPチャネル型低耐圧MOSFET形成領域1Dのゲート電極4の側壁とに形成されたサイドウォール24を除去する。このとき、Nチャネル型高耐圧MOSFET形成領域1Aのドレイン領域側のゲート電極4の側壁に形成されたサイドウォール24はフォトレジスト膜P9により覆われているため、エッチングにより除去されずに残る。

【0119】

次に、Nチャネル型高耐圧MOSFET形成領域1Aのゲート電極4の一方の側壁にサイドウォール24を残した状態で、図13を用いて説明したP型不純物(例えばB(ホウ素))の注入をNチャネル型高耐圧MOSFET形成領域1Aのドレイン領域側のみに行うことにより、LDD層6内にLDD層6よりも不純物濃度が低いN−−領域11を形成する。

【0120】

なお、図29におけるNチャネル型高耐圧MOSFET形成領域1Aのドレイン領域側にサイドウォール24を残す工程は、前述の図12および図13に示すフォトレジスト膜P3を形成するために用いたマスクと同じマスクを用いても良い。この場合、フォトレジスト膜のネガ・ポジを反転させることで、図29のフォトレジスト膜P9のようなパターンを形成できる。これによりマスクの数を削減できるため、製造コストを減少させることができる。

【0121】

次に、図16〜図22を用いて説明した工程と同様の工程を行うことにより、図30に示す本実施の形態の半導体装置が完成する。

【0122】

本実施の形態の半導体装置の製造工程では、前記実施の形態1と異なり、Nチャネル型高耐圧MOSFETのゲート電極4のドレイン領域側の側壁にのみサイドウォール24を形成している。これにより、半導体装置の微細化によりゲート電極の膜厚を小さくする必要があるMOSFETにおいて、ゲート電極をイオンが突き抜けない程度にLDD層を形成する際のイオン注入エネルギーが制限される場合に、図27に示すN−−領域11を形成するために打ち込むP型不純物(例えばB(ホウ素))がLDD層6よりも大きくゲート電極4にオーバーラップすることを防ぐことを可能としている。

【0123】

これにより、P型不純物(例えばB(ホウ素))が、ゲート電極4直下の領域であってLDD層6の外側の領域に拡散することによる耐圧の低下を防ぐことができる。したがって、半導体装置を微細化に伴いLDD層の形成のための注入エネルギーを低減する場合であっても、前記実施の形態1と同様の効果を得ることができる。

【0124】

なお、図27および図30ではN−−領域11がゲート電極4にオーバーラップしていないが、ここではN−−領域11を形成するために打ち込んだP型不純物がLDD層6よりも外側に導入されること防ぐことが重要であるため、N−−領域11はゲート電極4とオーバーラップしてもしていなくてもよい。

【0125】

(実施の形態4)

本実施の形態では、前記実施の形態1で示したNチャネル型高耐圧MOSFET形成領域1A(図9参照)のソース領域に、炭素を注入することによって、半導体領域13(図31参照)を形成している。なお、以下の説明では炭素(C)を例示しているが、半導体領域13を形成するために注入する他の元素として、ゲルマニウム(Ge)、フッ素(F)または窒素(N2)が挙げられる。

【0126】

図31に本実施の形態の半導体装置の断面図を示す。炭素(C)をソース領域側に注入して半導体領域13を形成することによって、半導体領域13の底部付近に結晶欠陥を形成することができる。この結晶欠陥は、ドレイン端部でのインパクトイオン化によって発生したキャリアを回収し、イオンパクトイオン化による耐圧低下を防ぐ働きを有する。また半導体領域13をPウエル(P−領域)10よりも深い領域に高いエネルギーで注入することによって、不純物に起因した素子同士の性能ばらつきの低減効果も期待できる。

【0127】

以下に、本実施の形態の半導体装置の製造方法について、図32を用いて説明する。図32は製造工程中の本実施の形態の半導体装置の断面図である。

【0128】

まず、前記実施の形態1の図5〜図9と同様の工程を行う。そして、図10の工程を行う前に、図32に示すように、Nチャネル型高耐圧MOSFET形成領域1Aのソース領域側のみを露出するようにフォトレジスト膜で半導体基板1の主面を覆い、半導体基板1に炭素を注入して半導体領域13を形成する。この時、炭素の注入エネルギーは10〜50keVとし、ドーズ量は1×1014〜1×1015cm−2、注入角度は0°〜25°とする。半導体領域13は、Pウエル(P−領域)10よりも接合深さが深く、ドレイン側のLDD層6と同程度の接合深さを有する。このように深い位置に半導体領域13を形成する理由は、ゲート電極4近傍のドレイン領域の端部近くに結晶欠陥があるとリーク電流の発生源となる可能性があるためである。信頼性を考慮すると、半導体領域13の底部の結晶欠陥はゲート電極4から遠い位置に形成されることが望ましい。

【0129】

この後の工程は、図10〜図22と同様の工程を行うことで、図31の構造を得ることができる。なお、炭素を注入する工程は、図10の工程の前に限られず、図10のPウエル(P−領域)10を形成する工程の後に行ってもよく、図11のLDD層7を形成する工程の後に行ってもよい。

【0130】

また、炭素(C)に代えて、ゲルマニウム(Ge)、フッ素(F)または窒素(N2)を注入することで半導体領域13を形成する場合は、図32を用いて説明したイオン注入を以下の条件で行う。ゲルマニウム(Ge)の場合は、注入エネルギーは40〜150keVとし、ドーズ量は1×1014〜1×1015cm−2とする。フッ素(F)の場合は、注入エネルギーは10〜50keVとし、ドーズ量は1×1014〜1×1015cm−2とする。窒素(N2)の場合は、注入エネルギーは30〜70keVとし、ドーズ量は1×1014〜1×1015cm−2とする。

【0131】

なお、本実施の形態は、他の実施の形態2および3に適用することも可能であり、それにより、本実施の形態と同様の効果を得ることができる。

【0132】

以上、本発明者らによってなされた発明をその実施の形態に基づき具体的に説明したが、本発明は前記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることはいうまでもない。

【0133】

例えば、前記実施の形態1〜4では、N型不純物としてP(リン)を例示し、P型不純物としてB(ボロン)を例示しているが、これに限られず、N型不純物としてAs(ヒ素)や、P型不純物としてBF2(フッ化ボロン)を用いてもよい。

【産業上の利用可能性】

【0134】

本発明は、P型不純物(ホウ素またはフッ化ホウ素などの拡散しやすい不純物)を含む半導体領域を有する装置の製造技術に適用して有効である。

【符号の説明】

【0135】

1 半導体基板

1A Nチャネル型高耐圧MOSFET形成領域

1B Pチャネル型高耐圧MOSFET形成領域

1C Nチャネル型低耐圧MOSFET形成領域

1D Pチャネル型低耐圧MOSFET形成領域

2 Pウエル

2b Nウエル

2c Pウエル

2d Nウエル

3 ゲート絶縁膜

3ab、3cd 絶縁膜

3b、3c、3d ゲート絶縁膜

4 ゲート電極

5、5g 拡散層

6、6b〜6g LDD層(N−領域)

7、7e〜7g LDD層(N−領域)

8、8b〜8d、8g 拡散層

10 Pウエル(P−領域)

10c、10d ハロー領域(P−領域)

10f、g Pウエル

11 N−−領域

12 エピタキシャル層

13 半導体領域

14 シリサイド層

15 素子分離領域

16 オフセットスペーサ

17 サイドウォール

19 層間絶縁膜

19a エッチストッパ膜

20 コンタクトプラグ

21 ストッパ絶縁膜

22 層間絶縁膜

23 絶縁膜

24 サイドウォール

Hn Nチャネル型高耐圧MOSFET

Hp Pチャネル型高耐圧MOSFET

Ln Nチャネル型低耐圧MOSFET

Lp Pチャネル型低耐圧MOSFET

M1 配線

P1〜P9 フォトレジスト膜

【技術分野】

【0001】

本発明は、半導体装置およびその製造方法に関し、特に、高耐圧の半導体素子の製造に適用して有効な技術に関する。

【背景技術】

【0002】

LSI(Large Scale Integration)内に形成される素子の一つに、入出力(インプット/アウトプット:I/O)に用いられる高耐圧な電界効果トランジスタ(Metal Oxide Semiconductor Field Effect Transistor:MOSFET)がある。

【0003】

特許文献1(特開平6−318698号公報)には、チャネル領域の表面の両端部分にN−ソース/ドレイン領域の下方にまで延びる高濃度のP層を形成し、さらにN+ソース/ドレイン領域とN−ソース/ドレイン領域との境界領域の一部に高濃度のP層を形成することで、素子の遅延時間の増加と基板バイアス電圧によるしきい値電圧の上昇を低減するとともに、基板パンチスルー現象を防止することが記載されている。

【0004】

特許文献2(特開2002−134743号公報)には、MIS(Metal Insulator Semiconductor)トランジスタにおいて、入出力パッドからサージが入力された場合に、高濃度ドレイン領域から基板領域に形成されるpn接合部の濃度変化が急峻なことを利用してサージを逃すことが記載されている。

【0005】

特許文献3(特開2007−103837号公報)には、左右非対称のソース・ドレイン領域を有する電界効果トランジスタ(以下単にMOSFETという)において、ドレイン領域を、基板主面のエクステンションと、その周辺を囲むエクステンションと、さらにそれよりも外側に形成されたポケット層とにより構成することが記載されている。

【0006】

特許文献4(米国特許第7,393,752号公報)では、基板上の不純物濃度が低いエピタキシャル層上に形成されたゲート電極と、ソース領域側のエピタキシャル層に高いエネルギーで不純物が注入されて形成されたウエルと、ウエルに自己整合的に形成されたハロー領域と、ドレイン領域側にゲート電極と重なるように形成されたLDD(Lightly Doped Drain)層とによりパワーMOSFETを構成することが記載されている。これにより、マスクおよび処理工程を追加せずに、パワーMOSFETを微細化することができるとしている。

【0007】

特許文献5(特開2009−245998号公報)には、左右非対称のソース・ドレイン領域を有する高耐圧トランジスタにおいて、チャネル領域を、p型不純物を高濃度に有する高濃度領域と、n型不純物領域(オフセット不純物領域)の端部と高濃度領域の端部との間の領域であって高濃度領域よりもp型不純物を低濃度に有する低濃度領域とから構成することにより、オン抵抗が低く十分な耐圧を有する高耐圧トランジスタを提供することが記載されている。

【0008】

特許文献6(特開2008−235407号公報)には、ドレイン不純物拡散領域の不純物拡散プロファイルにおけるLDD層のチャネル側端がゲート絶縁膜から離隔して基板内部に埋め込まれたトランジスタを形成することにより、ゲート電極とドレイン電極との間でゲート絶縁膜に加わる電界を低減することが記載されている。ここではP型の不純物を傾斜注入することによって、ソース領域側とドレイン領域側のLDD層を非対称に形成している。

【0009】

なお、特許文献3〜6では、いずれも電界をオン状態とオフ状態に分けて議論していないため、オン状態およびオフ状態のいずれの場合でも耐圧を向上できるのかどうかが不明である。

【先行技術文献】

【特許文献】

【0010】

【特許文献1】特開平6−318698号公報

【特許文献2】特開2002−134743号公報

【特許文献3】特開2007−103837号公報

【特許文献4】米国特許第7,393,752号公報

【特許文献5】特開2009−245998号公報

【特許文献6】特開2008−235407号公報

【発明の概要】

【発明が解決しようとする課題】

【0011】

半導体装置内の入出力に使用される素子を含む領域(I/O部)において用いられるMOSFETは、動作電圧が外部の装置から供給される電圧により決まるため、スケーリング側に従って動作電圧を小さくすることができない。したがって、I/O部において用いられる高耐圧MOSFETを微細化する場合は、決められた動作電圧下でソース・ドレイン間においてパンチスルーを起こさず、さらにドレイン端の電界を緩和し、インパクトイオンの発生を防ぐ必要がある。また、耐圧を確保するため、ドレイン領域側のLDD層とウエルとの間の電界が、MOSFETがオン状態であってもオフ状態であっても緩和されるような構造を実現し、ソース領域側への空乏層の伸びを小さくすることが重要となる。

【0012】

本発明の目的は、半導体装置の性能を向上させることにある。

【0013】

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

【課題を解決するための手段】

【0014】

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、次のとおりである。

【0015】

本発明の好ましい一態様である半導体装置は、MOSFETのドレイン領域側のLDD層内に、前記LDD層よりも不純物濃度層が低いN−−層を形成してドレイン領域のチャネル領域側の端部の不純物濃度を低下させ、さらにソース領域側のLDD層をドレイン領域側のLDD層よりも浅い接合深さで、且つ低い不純物濃度で形成するものである。

【発明の効果】

【0016】

本願において開示される発明のうち、代表的なものによって得られる効果を簡単に説明すれば以下のとおりである。

【0017】

代表的な実施の形態によれば、半導体装置の性能を向上させることができる。

【図面の簡単な説明】

【0018】

【図1】本発明の実施の形態1である半導体装置の断面図である。

【図2】基板表面の不純物濃度の分布を示すグラフである。

【図3】ソース領域における深さ方向の不純物の濃度分布を示すグラフである。

【図4】ドレイン領域における深さ方向の不純物の濃度分布を示すグラフである。

【図5】本発明の実施の形態1である半導体装置の製造工程を示す断面図である。

【図6】図5に続く半導体装置の製造工程中の断面図である。

【図7】図6に続く半導体装置の製造工程中の断面図である。

【図8】図7に続く半導体装置の製造工程中の断面図である。

【図9】図8に続く半導体装置の製造工程中の断面図である。

【図10】図9に続く半導体装置の製造工程中の断面図である。

【図11】図10に続く半導体装置の製造工程中の断面図である。

【図12】図11に続く半導体装置の製造工程中の断面図である。

【図13】図12に続く半導体装置の製造工程中の断面図である。

【図14】図13に続く半導体装置の製造工程中の断面図である。

【図15】図14に続く半導体装置の製造工程中の断面図である。

【図16】図15に続く半導体装置の製造工程中の断面図である。

【図17】図16に続く半導体装置の製造工程中の断面図である。

【図18】図17に続く半導体装置の製造工程中の断面図である。

【図19】図18に続く半導体装置の製造工程中の断面図である。

【図20】図19に続く半導体装置の製造工程中の断面図である。

【図21】図20に続く半導体装置の製造工程中の断面図である。

【図22】図21に続く半導体装置の製造工程中の断面図である。

【図23】本発明の実施の形態2である半導体装置の断面図である。

【図24】本発明の実施の形態2である半導体装置の製造工程を示す断面図である。

【図25】図24に続く半導体装置の製造工程中の断面図である。

【図26】図25に続く半導体装置の製造工程中の断面図である。

【図27】本発明の実施の形態3である半導体装置の断面図である。

【図28】本発明の実施の形態3である半導体装置の製造工程を示す断面図である。

【図29】図28に続く半導体装置の製造工程中の断面図である。

【図30】図29に続く半導体装置の製造工程中の断面図である。

【図31】本発明の実施の形態4である半導体装置の断面図である。

【図32】本発明の実施の形態4である半導体装置の製造工程を示す断面図である。

【図33】第1の比較例である半導体装置の断面図である。

【図34】第2の比較例である半導体装置の断面図である。

【図35】第3の比較例である半導体装置の断面図である。

【発明を実施するための形態】

【0019】

以下、本発明の実施の形態を図面に基づいて詳細に説明する。なお、実施の形態を説明するための全図において、同一の機能を有する部材には同一の符号を付し、その繰り返しの説明は省略する。また、以下の実施の形態では、特に必要なとき以外は同一または同様な部分の説明を原則として繰り返さない。

【0020】

(実施の形態1)

まず、図1を用いて本発明の実施の形態の半導体装置を説明する。図1には、本実施の形態の半導体装置を構成するNチャネル型高耐圧MOSFET(高耐圧トランジスタ)Hnの断面図を示している。図1に示すNチャネル型高耐圧MOSFETHnは半導体装置のI/O部に設けられ、例えばNチャネル型高耐圧MOSFETHnが形成された半導体チップの外部から供給される入力電圧により動作し、または半導体チップの外部に出力するために用いられる半導体素子である。図1では半導体基板1およびその上面に形成されたNチャネル型高耐圧MOSFETHnのみを示しており、その他のMOSFET、素子分離領域は図示しておらず、また、半導体基板1上に形成されたコンタクトプラグ、層間絶縁膜および配線の図示は省略している。

【0021】

図1に示すように、本実施の形態の半導体装置は例えば単結晶のSi(シリコン)からなる半導体基板1を有し、半導体基板1の主面にはP型の不純物(例えばB(ホウ素))が導入されたPウエル2が形成されており、半導体基板1の主面上にはPウエル2の上面に接して例えば酸化シリコン膜などからなるゲート絶縁膜3が形成され、ゲート絶縁膜3上には例えばポリシリコン膜からなるゲート電極4が形成されている。ゲート電極4のゲート長方向において、ゲート電極の横の半導体基板1の主面にはソース領域およびドレイン領域が形成されている。ゲート電極4の両側の側壁には、例えば酸化シリコン膜および窒化シリコン膜の積層膜からなるサイドウォールが形成されている。

【0022】

ソース領域およびドレイン領域はゲート電極4の直下の半導体基板1の主面に形成されたPウエル2を挟むように位置している。

【0023】

ソース領域側の半導体基板1の主面には、拡散層5、LDD層(N−領域)7およびPウエル(P−領域)10が形成されている。拡散層5およびLDD層7はいずれもN型の不純物(例えばP(リン))が導入された半導体領域であり、N+層である拡散層5の方がN−層であるLDD層7よりも高い不純物濃度を有し、拡散層5の方がLDD層7よりも深い接合深さを有している。LDD層7は拡散層5よりもゲート電極4の直下の半導体基板1の主面に形成されたPウエル2に近い領域に形成されている。Pウエル10はLDD層7よりもゲート電極4の直下の半導体基板1の主面に形成されたPウエル2に近い領域に形成され、また、LDD層7よりも深く拡散層5よりも浅い接合深さを有している。Pウエル10は、半導体基板1内において拡散層5と接していない領域のLDD層7の外側を覆うように形成されている。また、Pウェル10はPウエル2よりも不純物濃度が高い領域である。LDD層7およびPウエル10はゲート電極4の直下の領域に形成され、平面視においてゲート電極4と重なるように配置されている。ソース領域は、拡散層5およびLDD層7により構成されている。

【0024】

ドレイン領域側の半導体基板1の主面には、拡散層8、N−−領域11およびLDD層(N−領域)6が形成されている。N−−領域11は拡散層8よりも深い接合深さで形成されており、LDD層(N−領域)6はN−−領域11よりも深い接合深さで形成されている。つまり、半導体基板1の主面から反対側の裏面方向に向かって、拡散層8、N−−領域11およびLDD層6が順に形成されている。ドレイン領域は、拡散層8、N−−領域11およびLDD層6により構成されている。Nチャネル型高耐圧MOSFETHnは、ゲート電極4、拡散層5、LDD層7、Pウエル10、Pウエル2、拡散層8、N−−領域11およびLDD層6を含んでいる。

【0025】

拡散層8、N−−領域11およびLDD層6はいずれもN型の不純物(例えばP(リン))が導入された半導体領域であり、N−領域であるLDD層6はN−−領域11よりもN型の不純物濃度が高く、N+領域である拡散層8はLDD層6よりもN型の不純物濃度が高い。

【0026】

また、半導体基板1の主面において、ゲート電極4の直下の半導体基板1の主面からゲート長方向に離れるように、LDD層6、N−−領域11および拡散層8が順に形成されている。つまり、半導体基板1の主面に形成された拡散層8、N−−領域11およびLDD層6のうち、ゲート電極4の直下の半導体基板1の主面の最も近くに形成されているのはLDD層6であり、ゲート電極4の直下の半導体基板1の主面に対してLDD層6よりも遠い位置にN−−領域11が形成され、さらに遠い位置に拡散層8が形成されている。

【0027】

つまり、半導体基板1内においては、拡散層8の外側を覆うようにN−−領域11が形成され、さらにN−−領域11の外側を覆うようにLDD層6が形成されている。したがって、ゲート長方向における半導体基板1の主面には、ソース領域側の拡散層5からドレイン領域側の拡散層8にかけて、順に拡散層5、LDD層7、Pウエル10、Pウエル2、LDD層6、N−−領域11および拡散層8が形成されている。

【0028】

なお、LDD層6、7は半導体基板1の主面に対して斜めの方向からイオン注入を行って不純物が導入されているため、半導体基板1の主面に対して垂直な方向からイオン注入を行って不純物が導入する場合に比べてゲート電極4の直下の半導体基板1の主面に深く潜り込むように形成されている。つまり、LDD層6、7は半導体基板1の主面に対して垂直な方向からイオン注入を行って不純物が導入してN型層を形成する場合に比べてゲート電極4とのオーバーラップ量、すなわち平面視においてゲート電極4と重なる面積が大きくなっている。

【0029】

ただし、ドレイン領域側のLDD層6はソース領域側のLDD層7よりも深い接合深さを有しており、また、N型の不純物(例えばP(リン))の濃度はLDD層7よりもLDD層6の方が高い。

【0030】

次に、図33〜図35に示す比較例の半導体装置および図1に示す半導体装置を用いて本実施の形態の半導体装置の効果を説明する。なお、図33〜図35は半導体基板上に形成された比較例の半導体装置を構成するNチャネル型のMOSFETを示す断面図であり、半導体基板の主面上のその他の配線、層間絶縁膜などの構造体は図示を省略している。

【0031】

I/O部などに用いられる高耐圧MOSFETは、その動作電圧が外部の装置から供給される電圧または外部に供給する電圧により決まるため、スケーリング則に従って動作電圧を小さくすることができない。このような高耐圧MOSFETを微細化する際には、決められた動作電圧においてソース・ドレイン間でパンチスルーが起きることを防ぐことが重要となる。また、MOSFETの耐圧は当該MOSFETがオン状態およびオフ状態のいずれの場合でも十分に確保されている必要がある。

【0032】

そのための構造としては、例えば図33に示すような構造がある。図33は第1の比較例として示すNチャネル型のMOSFETであるが、ここで示す比較例の半導体装置はPチャネル型のMOSFETであっても構わない。

【0033】

図33に示すように、第1の比較例のNチャネル型のMOSFETを構成する半導体基板1の上面にはP型不純物(たとえばB(ホウ素))が添加されたPウエル2が形成されており、半導体基板1上にはゲート絶縁膜3を介してゲート電極4が形成されている。ゲート電極4の両側の側壁には、酸化シリコン膜などからなる絶縁膜であるオフセットスペーサ16を介して、絶縁膜であるサイドウォール17が形成されている。また、ゲート電極4を挟むように、半導体基板1の主面にはN型の不純物(例えばP(リン))が導入されて形成されたLDD層(N−領域)6e、7eが形成されている。LDD層6e、7e内には、LDD層6e、7eよりもN型不純物(例えばP(リン))が高い濃度で添加された拡散層(ソース電極)5および拡散層(ドレイン電極)8がイオン注入法によりそれぞれ形成されている。拡散層5および拡散層8は、ゲート電極4と、ゲート電極4の側壁に当該側壁側から順に形成されたオフセットスペーサ16およびサイドウォール17とを含む構造体を挟むように、半導体基板1の主面に形成されている。つまりゲート長方向において、拡散層5、拡散層8はゲート電極4を中心として左右対称に形成されており、LDD層6e、7eはゲート電極4を中心として左右対称に形成されている。このMOSFETを形成する工程では、ゲート電極4をマスクとして半導体基板1の主面に不純物をイオン注入することにより、LDD層6e、7eを同時に形成する。

【0034】

図33のMOSFETのように、LDD層6e、7eを深く左右対称に形成した構造では、半導体装置の微細化のためにゲート長を縮小した際、Pウエル2とLDD層6e、7eとによって形成されたPN接合での空乏層が拡がることによってパンチスルーが起こることがある。また同時にオン状態における電流値が増加し、それによって誘起されるインパクトイオン化の増加も懸念される。これは、ドレイン領域を構成するLDD層のチャネル領域側の端部のN型不純物の濃度が高いと、オン状態において電流の経路である基板表面における電界が強くなるためであり、オン状態の耐圧が劣化する原因となる。

【0035】

なお、ここでいうインパクトイオン化とは、MOSFETにおいて、ソースからドレインに流れる電子がドレイン部の高電界で加速されて結晶格子と衝突することにより、電子、正孔を発生させる現象を指す。この衝突によるイオン化が起こると、MOSFETの耐圧が低下し、また、雑音(ノイズ)が大きくなるなどの問題が発生する。

【0036】

したがって、高耐圧MOSFETのゲート長を縮小するなどして半導体装置を微細化する際には、ソース・ドレイン間でパンチスルーが起きることを防ぎ、さらにドレイン端の電界を緩和してインパクトイオンの発生を抑え、耐圧が低下することを防ぐ必要がある。

【0037】

以上の問題を解決する手段として、例えば図34または図35に示すような半導体装置を用いることが考えられる。図34に示す第2の比較例の半導体装置は図33の半導体装置と似たような構造を有しているが、ソース領域側のLDD層(N−領域)7fとドレイン領域側のLDD層(N−領域)6fとを別のマスクを用いた別工程のイオン注入により形成している点で前記第1の比較例とは異なる。また、ソース領域側のPウエル10fをLDD層7fの下部に形成することで、ソース領域側のP型の不純物濃度を高めてソース領域側に空乏層が伸びることを防ぎ、ソース・ドレイン間のパンチスルーが起きることを防止している。しかし、図34のような構造ではドレイン領域側のLDD層6f、拡散層8およびPウエル2の関係で電界が決まるため、それ以上に電界を緩和させることはできない。

【0038】

一方、図35に示す第3の比較例の半導体装置では、ソース領域側の拡散層5gを図33および図34のMOSFETと同様にゲート電極4に隣接して形成し、ドレイン領域側の拡散層8gをゲート電極4およびサイドウォール17からオフセットして形成している。つまり、拡散層5gとゲート電極4との距離に比べて、拡散層8gとゲート電極4とは大きく離れている。これにより、拡散層8g側に空乏層を伸ばすことができるため、図34に示すMOSFETに対してさらなる電界緩和が期待できる。また、図35のMOSFETは拡散層5gおよび拡散層8gを囲うように半導体基板1内にLDD層(N−領域)6g、7gがそれぞれ形成されており、ソース領域側の半導体基板1の主面には、LDD層7gよりもゲート電極4に近い領域に高い不純物濃度を有するPウエル10gが形成されている。ただし、図35に示すような構造では拡散層8gをオフセットして形成することによりMOSFETの占有面積が増加することになる。

【0039】

また、図示はしないが、MOSFETの耐圧を向上させる構造としては、第4の比較例として、図34に示した不純物濃度が高いPウエル10fまたは図35に示した不純物濃度が高いPウエル10gをいずれも形成せず、ゲート電極の片側からP型の不純物(例えばB(ホウ素))を傾斜注入することにより、ソース領域側とドレイン領域側のLDD層を非対称に形成する半導体装置も考えられる。この場合、ドレイン領域側のLDD層の最表面の濃度を下げることで、ドレイン・ゲート間の耐圧向上が期待できる。

【0040】

ただし、このような装置ではP型の不純物(例えばB(ホウ素))の注入エネルギーが低く、ドレイン端の電界を緩和することができない。さらに、このような構造はドレイン領域側から空乏層が伸びることを防げず、パンチスルーしやすい構造であると考えられる。

【0041】

図33〜図35に示した半導体装置は、ドレイン領域側のLDD層から伸びる空乏層の広がりを小さくする効果があると考えられるが、ドレイン端の電界を緩和するものではなく、ドレイン領域側のLDD層の濃度を調整することでしか、ドレイン領域側のLDD層とPウエル2との間の電界を緩和することができない。

【0042】

また、上述した図示しない第4の比較例の半導体装置では、傾斜注入を用いてP型の不純物(例えばB(ホウ素))をドレイン領域側のLDD層に注入して形成しているが、これはゲート電極とドレイン領域側のLDD層との間の電界を緩和するためであり、このような方法を用いてもドレイン領域側のLDD層と、チャネル領域であるPウエルとの間の電界を緩和することはできない。

【0043】

これに対し、本実施の形態の半導体装置は、MOSFETがオフ状態でもオン状態でもいずれの状態であってもドレイン領域側のLDD層とチャネル領域であるPウエルとの間の電界を緩和することを可能とし、さらにソース領域側への空乏層の伸びを小さくするものである。

【0044】

図1を用いて説明したように、本実施の形態ではソース領域側のLDD層7をLDD層6よりも浅く且つ不純物濃度を低く形成し、さらに不純物濃度が高いPウエル10をLDD層7の周囲に形成することによってソース・ドレイン間に空乏層が伸びることを防ぎ、ソース・ドレイン間におけるパンチスルーの発生を防ぐことを可能としている。Nチャネル型MOSFETのしきい値電圧はソース領域側のP型の不純物(例えばB(ホウ素))の濃度で決まるため、LDD層7の濃度を下げることにより高いしきい値電圧を実現することができる。LDD層7の接合深さをLDD層6と同様に深くした場合、LDD層7のN型不純物の濃度を高める必要がでてくるが、LDD層7のN型不純物の濃度がLDD層6と同等に高くなると、パンチスルーが生じやすくなるため、ここではLDD層7の接合深さをLDD層6よりも低くしている。また、Pウエル10の不純物濃度を高くすることによってしきい値電圧を上げることも可能であるが、素子ばらつきの観点からPウエルの濃度は高くし過ぎない方が好ましい。

【0045】

さらに、ドレイン領域側のLDD層6内にN型の不純物濃度が低いN−−領域11を形成することにより、オン状態でもオフ状態でもインパクトイオン化が起こりにくいMOSFETを実現することができる。その理由を以下に記す。

【0046】

MOSFETのインパクトイオン化を防ぐ観点におけるドレイン側のLDD層の最適な不純物濃度は、オン状態よりもオフ状態の方が高いという性質がある。これは、オン状態では電流が流れる経路の電界と電流量とでインパクトイオンが発生率が決まり、一方、オフ状態ではPウエルとドレイン領域側のLDD層との界面のPN接合における最も強い電界によってインパクトイオンの発生率が決まるためである。よって、良好な耐圧を得るためのドレイン領域側のLDD層の最適な不純物濃度は、オフ状態とオン状態とで異なっている。

【0047】

つまり、ドレイン領域側のLDD層内の、特にチャネル領域に近い端部のN型不純物の濃度が高くなると、ソース・ドレイン間の電流経路における電界が強くなるために、MOSFETのオン状態での耐圧が低下してしまう。そこで、本実施の形態ではドレイン領域内の電界が高くなることを防ぐため、図1に示すN−層であるLDD層6とN+層である拡散層8との間に、N型の逆種であるP型の不純物(例えばB(ホウ素))を導入することで、半導体基板1の主面にLDD層6よりも不純物濃度が低いN−−領域11を形成している。これにより、特に半導体基板1の主面では図2に示すようなN型不純物の濃度分布となる。

【0048】

図2は本実施の形態の半導体装置のMOSFETにおける半導体基板1(図1参照)の主面に導入されたN型不純物の濃度を示すグラフである。図2の横軸はゲート電極4の中心部の直下の位置を0とした場合のゲート長方向における距離であり、横軸の負の方向をソース領域側とし、正の方向をドレイン領域側としている。

【0049】

また、図3および図4に、本実施の形態のMOSFETのソース領域およびドレイン領域のそれぞれの半導体基板1(図1参照)の主面から深さ方向にかけての半導体基板1内のN型不純物の濃度分布を表わしたグラフを示す。図3はソース領域の半導体基板1の主面から半導体基板1の裏面に向かう方向である深さ方向における半導体基板1内の不純物濃度の分布を示したグラフであり、縦軸は不純物の濃度を示し、横軸は半導体基板1の主面の位置を0として半導体基板1の主面から深さ方向に向かう距離を示している。図4はドレイン領域の半導体基板1の主面から半導体基板1の裏面に向かう方向である深さ方向における半導体基板1内の不純物濃度の分布を示したグラフであり、縦軸は不純物の濃度を示し、横軸は半導体基板1の主面の位置を0として半導体基板1の主面から深さ方向に向かう距離を示している。

【0050】

図3に示すように、ソース領域では半導体基板1の主面側から裏面側に向かって、N+層(拡散層5)およびP層(Pウエル2)が形成されている。また、図4に示すように、ドレイン領域では半導体基板1の主面側から裏面側に向かって、N+層(拡散層8)、N−−領域11、N−層(LDD層6)およびP層(Pウエル2)が形成されている。図4に示すようにドレイン領域にはN−−領域11が形成されているため、N+層(拡散層8)とN−層(LDD層6)との間で不純物濃度がN−層(LDD層6)よりも低くなっている。

【0051】

ここで、図2に示すように、半導体基板1の主面には、ソース領域側からドレイン領域側に向かってN+層(拡散層5)、P+層(Pウエル10)、N−層(LDD層6)、N−−領域11、N+層(拡散層8)が順に形成されており、N−−領域11が形成された領域では、LDD層6よりも不純物濃度が低くなっている。本実施の形態の半導体装置では、このように半導体基板1の主面においてドレイン領域側のLDD層6と拡散層5との間に不純物濃度が低いN−−領域11を形成することにより、半導体基板1の主面におけるドレイン領域の電界を緩和し、インパクトイオンの発生を防ぐことを可能としている。これにより、Pウエル2とLDD層6との間の耐圧が向上するため、半導体装置の性能を向上させることができる。

【0052】

また、本実施の形態では、ドレイン領域側のLDD層6を形成する際のN型不純物(例えばP(リン))の注入濃度を調整することにより、ドレイン領域側のLDD層6の不純物濃度をLDD層7よりも高くしているため、オン状態で電流が流れる経路の電界は強くなり、一方で、オフ状態でのPウエル2およびLDD層6間のPN接合での電界は弱くなる。したがって、Pウエル2とLDD層6との間でインパクトイオンが発生することを防ぎ、耐圧を向上させることができるため、半導体装置の性能を向上させることができる。

【0053】

また、ゲート電極4の側壁に形成するサイドウォールのゲート長方向の厚さを大きくする方法、または図35を用いて説明したように拡散層をオフセットして形成する方法などを用いて、ソース・ドレイン間の間隔を広げてMOSFETに流れる電流を小さくし、インパクトイオンの発生を低減することが考えられるが、このような構造を採用するとMOSFETの面積が大きくなるため、素子の微細化の妨げとなる。これに対して、本実施の形態の半導体装置では、サイドウォールの厚さを大きくするなどしてソース・ドレイン間の間隔を広げることを行わずにMOSFETの高耐圧化を可能としている。したがって、高耐圧なMOSFETの微細化が容易になるため、半導体装置の性能を向上させることができる。

【0054】

以下に、図5〜図22を用いて本実施の形態の半導体装置を構成するNチャネル型高耐圧MOSFETの製造方法を説明する。図5〜図22は本実施の形態の半導体装置の製造工程を示す断面図であり、図1と異なり、本実施の形態の特徴を有するNチャネル型の高耐圧MOSFETの他に、Pチャネル型の高耐圧MOSFET、Nチャネル型の低耐圧MOSFETおよびPチャネル型の低耐圧MOSFETを形成する領域も図示している。図5〜図22では、図の左側から右側にかけて順にNチャネル型高耐圧MOSFET形成領域1A、Pチャネル型高耐圧MOSFET形成領域1B、Nチャネル型低耐圧MOSFET形成領域1CおよびPチャネル型低耐圧MOSFET形成領域1Dを示している。Nチャネル型またはPチャネル型の高耐圧MOSFETは例えばI/O部に設けられるトランジスタであり、比較的高い電圧により駆動する。Nチャネル型またはPチャネル型の低耐圧MOSFETはNチャネル型またはPチャネル型の高耐圧MOSFETよりも小さい電流および電圧で駆動するトランジスタであり、半導体装置内のコア部においてスイッチングなどの用途に用いられるものである。なお、ここで言うコア部とは、上記したI/O部とは異なり、I/O部よりも低い電流・電圧で駆動される素子により構成される回路などを含む領域である。

【0055】

まず、図5に示すように、半導体基板1の主面に周知の技術を用いて素子分離領域15を複数形成する。Nチャネル型高耐圧MOSFET形成領域1A、Pチャネル型高耐圧MOSFET形成領域1B、Nチャネル型低耐圧MOSFET形成領域1CおよびPチャネル型低耐圧MOSFET形成領域1Dはそれぞれ素子分離領域15によりその範囲を規定され、互いに分離されている。素子分離領域15は例えばSTI(Shallow Trench Isolation)であるものとする。このとき、半導体基板1の主面の保護などを目的として半導体基板1の主面に熱酸化膜などを形成することが考えられるが、ここではその図示を省略する。

【0056】

次に、図6に示すように、フォトリソグラフィ技術を用い、Nチャネル型高耐圧MOSFET形成領域1Aのみを露出するようなフォトレジスト膜P1を半導体基板1上に形成する。続いて、Nチャネル型高耐圧MOSFET形成領域1Aの半導体基板1の主面にP型の不純物(例えばB(ホウ素))をイオン注入法により注入し、半導体基板1の主面にPウエル2を形成する。このとき、フォトレジスト膜P1により半導体基板1の主面の一部を覆うことで、Nチャネル型高耐圧MOSFET形成領域1A以外の領域に不純物が導入されることを防ぐ。

【0057】

次に、図7に示すように、フォトレジスト膜P1を除去した後、図6を用いて説明した方法と同様にして、Pチャネル型高耐圧MOSFET形成領域1B、Nチャネル型低耐圧MOSFET形成領域1CおよびPチャネル型低耐圧MOSFET形成領域1DにN型の不純物(例えばP(リン))、P型の不純物(例えばB(ホウ素))およびN型の不純物(例えばP(リン))をそれぞれイオン注入する。これにより、Pチャネル型高耐圧MOSFET形成領域1B、Nチャネル型低耐圧MOSFET形成領域1CおよびPチャネル型低耐圧MOSFET形成領域1DにNウエル2b、Pウエル2cおよびNウエル2dを形成する。このとき、図6を用いて説明したイオン注入工程と同様に、目的の領域以外に不純物が導入されることを防ぐため、各イオン注入工程の前に目的の領域以外を覆うフォトレジスト膜(図示しない)を半導体基板1上に形成し、マスクとして利用する。このように、Nチャネル型高耐圧MOSFET形成領域1A、Pチャネル型高耐圧MOSFET形成領域1B、Nチャネル型低耐圧MOSFET形成領域1CおよびPチャネル型低耐圧MOSFET形成領域1Dのそれぞれには別工程により不純物を導入し、ウエルを形成するものとするが、Pウエル2およびPウエル2cは同一工程で形成してもよく、同様にNウエル2bおよびNウエル2dは同一工程で形成してもよい。

【0058】

次に、図8に示すように、Nチャネル型高耐圧MOSFET形成領域1AおよびPチャネル型高耐圧MOSFET形成領域1Bと、Nチャネル型低耐圧MOSFET形成領域1CおよびPチャネル型低耐圧MOSFET形成領域1Dとで厚さが異なる2種類の絶縁膜を半導体基板1の上面に形成する。つまり、Nチャネル型高耐圧MOSFET形成領域1AおよびPチャネル型高耐圧MOSFET形成領域1Bの半導体基板1の主面には比較的膜厚が厚い絶縁膜3abを形成し、Nチャネル型低耐圧MOSFET形成領域1CおよびPチャネル型低耐圧MOSFET形成領域1Dの半導体基板1の主面には絶縁膜3abよりも膜厚が薄い絶縁膜3cdを形成する。

【0059】

この場合は、例えば熱酸化法またはCVD(Chemical Vapor Deposition)法を用いて半導体基板1の主面の全面上に絶縁膜3abを形成した後に、フォトリソグラフィ技術およびウェットエッチング法などを用いてNチャネル型低耐圧MOSFET形成領域1CおよびPチャネル型低耐圧MOSFET形成領域1Dの絶縁膜3abを除去する。その後、例えば熱酸化法を用いて半導体基板1の主面を加熱し、Nチャネル型低耐圧MOSFET形成領域1CおよびPチャネル型低耐圧MOSFET形成領域1Dの半導体基板1の主面に絶縁膜3cdを形成する。絶縁膜3ab、3cdは例えば酸化シリコンからなる膜である。

【0060】

次に、図9に示すように、半導体基板1の主面上の全面に例えばCVD法を用いてポリシリコン膜を形成(堆積)した後、フォトリソグラフィ技術およびドライエッチング法を用いて前記ポリシリコン膜およびその下部の絶縁膜3ab、3cdを加工(パターニング)し、前記ポリシリコン膜からなるゲート電極4と、絶縁膜3abからなるゲート絶縁膜3、3bと、絶縁膜3cdからなるゲート絶縁膜3c、3dとを形成する。Nチャネル型高耐圧MOSFET形成領域1Aでは半導体基板1上にゲート絶縁膜3を介してゲート電極4が形成され、Pチャネル型高耐圧MOSFET形成領域1Bでは半導体基板1上にゲート絶縁膜3bを介してゲート電極4が形成され、Nチャネル型低耐圧MOSFET形成領域1Cでは半導体基板1上にゲート絶縁膜3cを介してゲート電極4が形成され、Pチャネル型低耐圧MOSFET形成領域1Dではゲート絶縁膜3dを介してゲート電極4が形成される。Nチャネル型高耐圧MOSFET形成領域1AおよびPチャネル型高耐圧MOSFET形成領域1Bのゲート電極4、ゲート絶縁膜3および3bのゲート長方向の幅は、Nチャネル型低耐圧MOSFET形成領域1CおよびPチャネル型低耐圧MOSFET形成領域1Dのゲート電極4、ゲート絶縁膜3cおよび3dのゲート長方向の幅よりも大きく形成する。

【0061】

次に、図10に示すように、Pチャネル型高耐圧MOSFET形成領域1B、Nチャネル型低耐圧MOSFET形成領域1CおよびPチャネル型低耐圧MOSFET形成領域1Dと、Nチャネル型高耐圧MOSFET形成領域1Aの一部の半導体基板1の主面およびゲート電極4の一部とを覆うようにフォトレジスト膜P2を形成する。なお、ここでフォトレジスト膜P2により覆ったNチャネル型高耐圧MOSFET形成領域1Aの半導体基板1の主面の一部は、後の工程により形成されるNチャネル型高耐圧MOSFETのドレイン領域となる部分である。つまり、ここではNチャネル型高耐圧MOSFET形成領域1Aのゲート電極4の左右の半導体基板1の主面のうち、ドレイン領域側をフォトレジスト膜P2で覆い、ソース領域側を露出させる。

【0062】

続いて、フォトレジスト膜P2、ゲート電極4およびゲート絶縁膜3から露出しているNチャネル型高耐圧MOSFET形成領域1Aのソース領域側の半導体基板1の主面のみにP型不純物(例えばB(ホウ素))を斜めイオン注入(傾斜注入)し、Pウエル10を形成する。この工程でのイオン注入では、例えばB(ホウ素)を5〜30keVのエネルギー、1×1013〜3×1013cm−2のドーズ量および10°〜45°の角度で注入を行う。このように、半導体基板1の主面に対して垂直な方向からイオン注入を行うのではなく、半導体基板1の主面に対して斜めの方向から注入を行うことで、ゲート電極4の直下の半導体基板1の主面においてよりドレイン領域側に近い箇所にまでPウエル10が形成され、Pウエル10のゲート電極4に対するオーバーラップする面積が大きくなる。

【0063】

次に、図11に示すように、フォトレジスト膜P2およびゲート電極4をマスクとして、半導体基板1の主面に対して垂直な方向からN型の不純物(例えばP(リン))をイオン注入することにより、ソース領域側のLDD層7を形成する。この注入工程では、例えばP(リン)を5〜15keVのエネルギー、5×1012〜2×1013cm−2のドーズ量でイオン注入を行う。ここでは、Pウエル10よりも浅い接合深さでLDD層7を形成する。また、LDD層7は半導体基板1の主面に対して垂直な方向にイオン注入をしているのに対し、Pウエル10は斜めイオン注入により形成されているため、Pウエル10の方がLDD層7よりもゲート電極4とのオーバーラップ量、すなわち平面視においてPウエル10とゲート電極4とが重なる領域が大きくなる。

【0064】

次に、図12に示すように、フォトレジスト膜P2を除去した後、Pウエル10およびLDD層7が形成されたNチャネル型高耐圧MOSFET形成領域1Aのソース領域側と、Pチャネル型高耐圧MOSFET形成領域1B、Nチャネル型低耐圧MOSFET形成領域1CおよびPチャネル型低耐圧MOSFET形成領域1Dとを覆うように半導体基板1上にフォトレジスト膜P3を形成する。これにより、図10および図11を用いて説明した工程ではフォトレジスト膜P2に覆われていたNチャネル型高耐圧MOSFET形成領域1Aのドレイン領域側の半導体基板1の主面が露出する。

【0065】

続いて、フォトレジスト膜P3から露出している半導体基板1の主面にN型不純物(例えばP(リン))を斜めイオン注入することで、高耐圧MOSFETのドレイン領域を構成するLDD層6を形成する。ドレイン領域側のLDD層6の不純物の注入は、高耐圧MOSFETがオフの状態での耐圧が最も高くなる条件で行う。つまり、イオン注入は例えばP(リン)を65keVのエネルギー、5×1013〜1.5×1014cm−2のドーズ量、45°の角度で行う。このとき、LDD層6はLDD層7よりも深く、また、Pウエル10よりも深い接合深さで形成する。LDD層6は斜めイオン注入法により形成されるため、半導体基板1の主面に対して垂直にイオン注入を行う場合に比べてゲート電極4との平面視におけるオーバーラップ量が大きくなる。

【0066】

次に、図13に示すように、ドレイン領域側のLDD層6を形成した半導体基板1の主面にP型の不純物(例えばB(ホウ素))を、半導体基板1の主面に対して垂直な方向からイオン注入することで、N−−領域11を形成する。注入条件は、例えばB(ホウ素)を5〜20keVのエネルギー、5×1013〜2×1014cm−2のドーズ量とする。N−−領域11を形成する前記注入工程では、高耐圧MOSFETの電流経路で電界が一番強い領域にイオン注入し、ドレイン領域側のLDD層6を中性化する。これによってドレイン領域側のLDD層6の中にN型不純物(例えばP(リン))の濃度が低いN−−領域11を作製する。

【0067】

ここで注入するP型の不純物(例えばB(ホウ素))は、N−−領域11がLDD層6よりもゲート電極4とのオーバーラップ量が少なくなるように注入する。つまり、LDD層6の方がN−−領域11よりもソース領域側に配置されるようにN−−領域11を形成する。P型の不純物(例えばB(ホウ素))を打ち込んで形成する領域(N−−領域11)の方がLDD層6よりもゲート電極4とのオーバーラップ量が大きい場合、ドレイン領域からの空乏層の伸びを抑え、短チャネル効果を改善する効果が期待できるが、電界が強くなり耐圧が劣化するため、耐圧を確保する観点から上記のようにLDD層6よりもN−−領域11の方がゲート電極4とのオーバーラップ量が小さくなるようにする必要がある。

【0068】

なお、ここではソース領域を構成するLDD層7などを先に形成する製造工程を説明しているが、ドレイン領域側のLDD層6、N−−領域11などをソース領域側のLDD層7などより先に形成しても良い。

【0069】

続いて、イオン注入した不純物の拡散などを目的として半導体基板1を熱処理するが、この場合、N−−領域11中を形成するために打ち込んだP型不純物(例えばB(ホウ素))が、LDD層6の外側のチャネル領域などに拡散しないような熱処理を行う。これは、LDD層6の外側に濃度が高いP型半導体領域が形成されると、当該P型半導体領域とLDD層6との間に強いPN接合が形成され、電界が強くなるためである。したがって、ここではLDD層6端部の電界が大きくなって耐圧が低下することを防ぐため、N−−領域11中を形成するために打ち込んだP型不純物(例えばB(ホウ素))がLDD層6の外側に拡散しないように当該P型不純物の注入および熱処理による拡散を行っている。よって、チャネル層とN−−領域11との間にはN−−領域11よりもN型不純物濃度が高いLDD層6が介在することとなる。これにより、N−−領域11はLDD層6内においてLDD層6よりも接合深さが浅く、N型不純物(例えばP(リン))の濃度が低い半導体領域として形成される。

【0070】

次に、図14に示すように、フォトレジスト膜P3を除去した後、Pチャネル型高耐圧MOSFET形成領域1Bを露出し、Nチャネル型高耐圧MOSFET形成領域1A、Nチャネル型低耐圧MOSFET形成領域1CおよびPチャネル型低耐圧MOSFET形成領域1Dを覆うフォトレジスト膜P4を半導体基板1上に形成する。続いて、露出した半導体基板1の主面にP型不純物(例えばB(ホウ素))を斜めイオン注入法により注入することにより、Pチャネル型高耐圧MOSFET形成領域1Bのゲート電極4の左右の半導体基板1の主面に一対のLDD層(N−領域)6bを形成する。

【0071】

次に、図15に示すように、フォトレジスト膜P4を除去した後、複数のゲート電極4の表面を覆うように半導体基板1の主面上に例えばCVD法などにより酸化シリコン膜を形成し、続いてドライエッチング法により前記酸化シリコン膜を一部除去して半導体基板1の主面を露出させる。これにより、各ゲート電極4の側壁に前記酸化シリコン膜からなるオフセットスペーサ16を自己整合的に形成する。

【0072】

次に、図16に示すように、Nチャネル型低耐圧MOSFET形成領域1Cを露出するフォトレジスト膜P5を形成し、露出した半導体基板1の主面にP型の不純物(例えばB(ホウ素))をイオン注入することで、Nチャネル型低耐圧MOSFET形成領域1Cのゲート電極4の両側の半導体基板1の主面に一対のハロー領域(P−領域)10cを形成する。続いて、フォトレジスト膜P5から露出した半導体基板1の主面にN型の不純物(例えばP(リン))をイオン注入することで、Nチャネル型低耐圧MOSFET形成領域1Cのゲート電極4の両側の半導体基板1の主面に一対のLDD層(N−領域)6cを形成する。ハロー領域10cはLDD層6cよりも深い接合深さを有しており、半導体基板1内においてLDD層6cを囲むように形成されている。

【0073】

なお、図16に示したハロー領域10cおよびLDD層6cを形成する工程は、前述のオフセットスペーサ16を形成する前に行ってもよい。

【0074】

次に、図17に示すように、フォトレジスト膜P5を除去した後、Pチャネル型低耐圧MOSFET形成領域1Dを露出するフォトレジスト膜P6を形成し、露出した半導体基板1の主面にN型の不純物(例えばP(リン))をイオン注入することで、Pチャネル型低耐圧MOSFET形成領域1Dのゲート電極4の両側の半導体基板1の主面に一対のハロー領域(P−領域)10dを形成する。続いて、フォトレジスト膜P6から露出した半導体基板1の主面にP型の不純物(例えばB(ホウ素))をイオン注入することで、Pチャネル型低耐圧MOSFET形成領域1Dのゲート電極4の両側の半導体基板1の主面に一対のLDD層(N−領域)6dを形成する。ハロー領域10dはLDD層6dよりも深い接合深さを有しており、半導体基板1内においてLDD層6dを囲むように形成されている。

【0075】

次に、図18に示すように、フォトレジスト膜P6を除去した後、複数のゲート電極4の表面を覆うように半導体基板1の主面上に例えばCVD法などにより絶縁膜を形成し、続いてドライエッチング法により前記絶縁膜を一部除去して半導体基板1の主面を露出させる。これにより、各ゲート電極4の側壁に前記酸化シリコン膜からなるサイドウォール17を自己整合的に形成する。前記絶縁膜は、例えば酸化シリコン膜および窒化シリコン膜の積層膜などからなる。

【0076】

次に、図19に示すように、Pチャネル型高耐圧MOSFET形成領域1B(図18参照)およびPチャネル型低耐圧MOSFET形成領域1D(図18参照)を露出するフォトレジスト膜P7を形成した後、露出した半導体基板1の主面にP型の不純物(例えばB(ホウ素))を高い濃度でイオン注入する。これにより、Pチャネル型高耐圧MOSFET形成領域1Bのゲート電極4の両側の半導体基板1の主面に一対の拡散層8bを形成し、Pチャネル型低耐圧MOSFET形成領域1Dのゲート電極4の両側の半導体基板1の主面に一対の拡散層8dを形成する。この工程により、半導体基板1の主面のI/O部には、ゲート電極4、拡散層8bおよびLDD層6bを含むPチャネル型高耐圧MOSFETHpが形成され、半導体基板1の主面のコア部には、ゲート電極4、ハロー領域10d、拡散層8dおよびLDD層6dを含むPチャネル型低耐圧MOSFETLpが形成される。

【0077】

次に、図20に示すように、フォトレジスト膜P7を除去した後、Nチャネル型高耐圧MOSFET形成領域1A(図19参照)およびNチャネル型低耐圧MOSFET形成領域1C(図19参照)を露出するフォトレジスト膜P8を形成した後、露出した半導体基板1の主面にN型の不純物(例えばP(リン))を高い濃度でイオン注入する。これにより、Nチャネル型高耐圧MOSFET形成領域1Aのゲート電極4の両側の半導体基板1の主面に一対の拡散層5、8を形成し、Nチャネル型低耐圧MOSFET形成領域1Cのゲート電極4の両側の半導体基板1の主面に一対の拡散層8cを形成する。この工程により、半導体基板1の主面のI/O部には、ゲート電極4、拡散層5、LDD層7、Pウエル10、拡散層8、N−−領域11およびLDD層6を含むNチャネル型高耐圧MOSFETHnが形成され、半導体基板1の主面のコア部には、ゲート電極4、ハロー領域10c、拡散層8cおよびLDD層6cを含むNチャネル型低耐圧MOSFETLnが形成される。

【0078】

このとき、Nチャネル型低耐圧MOSFETHnのドレイン領域側の拡散層8は、N−−層11よりも浅い接合深さで形成し、また、ソース領域側の拡散層5は、Pウエル10よりも深い接合深さで形成する。

【0079】

次に、図21に示すように、フォトレジスト膜P8を除去した後、周知のサリサイド技術により拡散層5、8b、8c、8dおよびゲート電極4のそれぞれの上面にシリサイド層14を形成する。このとき形成するシリサイド層14の部材は、NiSi(ニッケルシリサイド)またはCoSi(コバルトシリサイド)などとすることができる。ここでは、半導体基板1上に形成したNi(ニッケル)などを含む金属膜を、熱処理により下部の半導体層と反応させることで金属シリサイド層を形成する。

【0080】

続いて、半導体基板1の主面上に、ゲート電極4を覆うようにエッチストッパ膜19aおよび層間絶縁膜19を順次形成する。エッチストッパ膜19aは、例えば酸化シリコン膜の単体膜または薄い窒化シリコン膜からなり、その上の層間絶縁膜19は厚い酸化シリコン膜からなる。エッチストッパ膜19aおよび層間絶縁膜19の形成後、層間絶縁膜19の表面を、例えばCMP(Chemical Mechanical Polishing)法を使用して平坦化する。

【0081】

次に、図22に示すように、層間絶縁膜19上に形成したフォトレジスト膜(図示せず)をエッチングマスクとして用いて、エッチストッパ膜19aおよび層間絶縁膜19をドライエッチングすることにより、エッチストッパ膜19aおよび層間絶縁膜19を貫通する複数のコンタクトホール(貫通孔、孔)を形成する。前記複数のコンタクトホールは、拡散層5、8b、8c、8dおよびゲート電極4のそれぞれの上部のシリサイド層14に達する孔である。

【0082】

続いて、前記複数のコンタクトホール内に、タングステン(W)などからなる導電性のコンタクトプラグ(接続用導体部)20を形成する。コンタクトプラグ20を形成するには、例えば、コンタクトホールの底部および側壁を含む層間絶縁膜19上に、バリア導体膜(例えばチタン膜、窒化チタン膜、あるいはそれらの積層膜)を形成する。それから、前記バリア導体膜上にタングステン膜などからなる主導体膜を形成して前記コンタクトホールを埋め込み、層間絶縁膜19上の不要な前記主導体膜および前記バリア導体膜をCMP法またはエッチバック法などによって除去することにより、コンタクトプラグ20を形成する。なお、図面の簡略化のために、図22ではコンタクトプラグ20を構成するバリア導体膜および主導体膜(タングステン膜)を一体化して示している。

【0083】

続いて、コンタクトプラグ20が埋め込まれた層間絶縁膜19上に、ストッパ絶縁膜(エッチングストッパ用絶縁膜)21および配線形成用の層間絶縁膜22を順次形成する。ストッパ絶縁膜21は、層間絶縁膜22への溝加工の際にエッチングストッパとなる膜であり、層間絶縁膜22に対してエッチング選択性を有する材料を用い、例えば、ストッパ絶縁膜21を窒化シリコン膜とし、層間絶縁膜22を酸化シリコン膜とすることができる。

【0084】

その後、シングルダマシン法により第1層目の配線を形成する。まず、フォトレジスト膜(図示せず)をマスクとしたドライエッチングによって層間絶縁膜22およびストッパ絶縁膜21の所定の領域にコンタクトプラグ20を露出する複数の配線溝を形成した後、半導体基板1の主面上に例えば窒化チタン膜、タンタル膜または窒化タンタル膜などからなるバリアメタル膜を形成する。続いて、CVD法またはスパッタリング法などによりバリアメタル膜上に銅のシード層を形成し、さらに電解めっき法などを用いてシード層上に銅めっき膜を形成し、前記銅めっき膜により前記配線溝の内部を埋め込む。それから、配線溝以外の領域の銅めっき膜、シード層およびバリアメタル膜をCMP法により除去して、銅を主導電材料とする第1層目の配線M1を形成する。なお、図面の簡略化のために、図20では、配線M1を構成する銅めっき膜、シード層およびバリアメタル膜を一体化して示してある。

【0085】

配線M1は、コンタクトプラグ20を介して各MOSFETのソース・ドレインおよびゲート電極などと電気的に接続されている。その後、デュアルダマシン法などにより配線M1上に2層目以降の配線を形成することで本実施の形態の半導体装置が完成するが、ここでは2層目以降の配線の図示およびその製造工程の説明は省略する。また、配線M1はダマシン配線に限定されず、配線用の導電体膜をパターニングして形成することもでき、例えばタングステン配線またはアルミニウム配線などとすることもできる。

【0086】

本実施の形態では、図10〜図13を用いて説明したような斜めイオン注入法を利用して不純物の打ち込みを行うことにより、ゲート電極4を中心として左右非対称のソース・ドレイン領域を形成している。つまり、図10を用いて説明したPウエル10の形成工程では、傾斜注入によってソース領域側のPウエル10のゲート電極4に対するオーバーラップ量を大きくすることで、MOSFETの動作時にドレイン領域側から伸びる空乏層を止め、短チャネル効果を改善することを可能としている。また、図11を用いて説明したLDD層7の形成工程では、LDD層7を形成することによってNチャネル型高耐圧MOSFETのソース領域側の抵抗を低減することを可能にすると共に、LDD層7をドレイン領域側のLDD層6(図1参照)よりも深さが浅く濃度が低い領域とすることによって、半導体基板1の主面から深い位置でパンチスルーしにくく、素子ばらつきの小さい構造とすることを可能としている。

【0087】

これらの工程により、ソース領域側のLDD層7をLDD層6よりも浅く且つ不純物濃度を低く形成し、さらに不純物濃度が高いPウエル10をLDD層7の周囲に形成することによってソース・ドレイン間に空乏層が伸びことを防ぎ、ソース・ドレイン間におけるパンチスルーの発生を防ぐことを可能としている。

【0088】

また、図1を用いて説明したように、ドレイン領域側のLDD層6内に不純物濃度が低いN−−領域11を形成することにより、ドレイン領域内の電界が高くなることを防ぎ、オン状態でもオフ状態でもインパクトイオン化が起こりにくいMOSFETを実現することができる。

【0089】

また、本実施の形態では、ドレイン領域側のLDD層6を形成する際のN型不純物(例えばP(リン))の注入濃度を調整することにより、ドレイン領域側のLDD層6の不純物濃度をLDD層7よりも高くしているため、オン状態で電流が流れる経路の電界は強くなり、一方で、オフ状態でのPウエル2およびLDD層6間のPN接合での電界は弱くなる。したがって、Pウエル2とLDD層6との間でインパクトイオンが発生することを防ぎ、耐圧を向上させることができる。上記のように、MOSFETの面積を大きくしなくても高耐圧化が可能となり、素子の微細化も容易になるため、半導体装置の性能を向上させることができる。

【0090】

(実施の形態2)

本実施の形態では、I/O部のNチャネル型高耐圧MOSFETのドレイン側の半導体基板1の主面をエピタキシャル成長させることにより、Nチャネル型高耐圧MOSFETのドレインを構成するエピタキシャル層を設けた半導体装置について説明する。

【0091】

図23に示すように、本実施の形態の半導体装置のNチャネル型高耐圧MOSFETは前記実施の形態1において図1を用いて説明したNチャネル型高耐圧MOSFETとほぼ同様の構造を有しているが、ドレイン側の半導体基板1内にはN−−領域11は形成されておらず、LDD層6のみが形成されており、LDD層6上にエピタキシャル層12がLDD層6の上面に接して形成され、エピタキシャル層12の上面に拡散層8が形成されている。なお、拡散層8はエピタキシャル層12の底面に達しておらず、エピタキシャル層12内の上部のみに形成されている。よって、半導体基板の主面には、ソース領域側からドレイン領域側にかけて順に拡散層5、LDD層7、Pウエル10、Pウエル2およびLDD層6が形成されており、チャネル領域側のLDD層6の端部と拡散層8との間にはエピタキシャル層12が形成されている。

【0092】

エピタキシャル層12はLDD層6よりもN型の不純物濃度が低いN型の半導体領域であり、ゲート電極4の一方の側壁に例えば酸化シリコンからなるオフセットスペーサ16を介して配置されており、ゲート電極4と絶縁して形成されている。またエピタキシャル層12は、LDD層6が形成された半導体基板1の主面上に10〜40nmの膜厚で形成されている。なお、図23が本実施の形態の半導体装置のNチャネル型高耐圧MOSFETを示す断面図であり、図23ではMOSFET上のシリサイド層、層間絶縁膜、コンタクトプラグおよび配線層などの図示は省略している。

【0093】

エピタキシャル層12は主にSi(シリコン)からなり、N型の不純物(例えばP(リン))が導入されている。また、エピタキシャル層12の上面にはN型の不純物(例えばP(リン))がLDD層6およびエピタキシャル層12よりも高濃度で導入された拡散層8が形成されており、エピタキシャル層12の直上にはゲート電極4の側壁にオフセットスペーサ16を介してサイドウォール17が形成されている。ここでは、LDD層6、エピタキシャル層12および拡散層8がドレイン領域を構成している。なお、エピタキシャル層12の側壁であって、ゲート電極4の側壁のオフセットスペーサ16と接していない方の側壁にもサイドウォール17が形成されている。

【0094】

図23に示すように、本実施の形態のNチャネル型高耐圧MOSFETHnは、ゲート電極4、拡散層5、LDD層7、Pウエル10、Pウエル2、拡散層8、LDD層6およびエピタキシャル層12を含んでいる。

【0095】

ここでは、前記実施の形態1のようにP型の不純物(例えばB(ホウ素))を打ち込むのではなく、半導体基板1の一部の上面にエピタキシャル層を形成することで、ドレイン領域内にLDD層6よりも不純物濃度が低い領域を形成している。このようにしてMOSFETのチャネル領域の近傍のドレイン端の一部の不純物濃度を低減することにより、前記実施の形態1と同様に電界を小さくしてインパクトイオン化を防ぎ、オン状態およびオフ状態のMOSFETの耐圧を向上させている。

【0096】

次に、本実施の形態の半導体装置の製造方法を図24〜図26を用いて説明する。図24〜図26は本実施の形態の半導体装置の製造工程を示す断面図であり、図5などと同様にNチャネル型高耐圧MOSFET形成領域1A、Pチャネル型高耐圧MOSFET形成領域1B、Nチャネル型低耐圧MOSFET形成領域1CおよびPチャネル型低耐圧MOSFET形成領域1Dを示している。

【0097】

まず、図5〜図12を用いて説明した工程と同様の工程を行うことにより、Nチャネル型高耐圧MOSFET形成領域1Aの半導体基板1の主面上にゲート電極4を形成し、半導体基板1の主面にPウエル10、LDD層6および7を形成する。その後、図13を用いて説明したイオン注入工程は行わずに、図14を用いて説明したイオン注入工程を行うことでPチャネル型高耐圧MOSFET形成領域1Bの半導体基板1の主面にLDD層6bを形成する。

【0098】

続いて、図24に示すように、CVD法などを用いて半導体基板1の主面上に例えば酸化シリコン膜からなる膜厚5〜20nmの絶縁膜23を形成した後、フォトリソグラフィ技術およびエッチング法を用いて、Nチャネル型高耐圧MOSFET形成領域1Aのドレイン領域側の半導体基板1の主面上に形成された絶縁膜23をドライエッチング法により除去し、他の領域の絶縁膜23を残す。これにより、Nチャネル型高耐圧MOSFET形成領域1Aのドレイン領域側の半導体基板1の主面のみを露出させるように絶縁膜23を開口させる。

【0099】

なお、図24ではゲート電極4の上面全体に絶縁膜23が残される場合を例示しているが、ゲート電極4の上面の一部を露出するようにしてもよい。すなわち、ドライエッチングは異方性エッチングで行い、ゲート電極4の側面に絶縁膜23を残し、フォトレジスト膜で覆われていないゲート電極4の上面の一部を露出するようにしてもよい。この場合、ゲート電極4のドレイン側の上面にもエピタキシャル層12が形成されるが、Nチャネル型高耐圧MOSFETの特性に問題はない。

【0100】

次に、図25に示すように、絶縁膜23から露出している半導体基板1の主面上、すなわちNチャネル型高耐圧MOSFET形成領域1Aのドレイン領域側の半導体基板1の主面上にのみエピタキシャル成長法を用いて10〜40nmの膜厚を有するエピタキシャル層12を形成する。このとき、エピタキシャル層12のN型の不純物濃度はLDD層6よりも低くなる。

【0101】

続いて、半導体基板1上の絶縁膜23の一部をドライエッチング法により除去し、ゲート電極4の上面および半導体基板1の主面を露出させる。これにより、ゲート電極4の側壁に絶縁膜23からなるオフセットスペーサ16が自己整合的に形成される。

【0102】

なお、図24におけるNチャネル型高耐圧MOSFET形成領域1Aのドレイン領域側の絶縁膜23を除去する工程は、前述の図12および図13に示すフォトレジスト膜P3を形成するために用いたマスクと同じマスクを用いても良い。これによりマスクの数を削減できるため、製造コストを減少させることができる。なお、この場合には、上述のように、ゲート電極4のドレイン側の部分にもエピタキシャル層12が形成されることになる。

【0103】

この後の工程は、前記実施の形態1において図16〜図22を用いて説明した工程と同様の工程を行うことにより、図26に示す本実施の形態の半導体装置が完成する。ただし、図20に対応する拡散層の形成工程では、Nチャネル型高耐圧MOSFET形成領域1A(図25参照)のドレイン領域側に拡散層8を形成する際、エピタキシャル層12の上面にN型の不純物(例えばP(リン))をイオン注入して拡散層8を形成する。

【0104】

図26に示すように、完成した本実施の形態の半導体装置のNチャネル型高耐圧MOSFETは図23に示す構造と同様の構造上にシリサイド層14、エッチストッパ膜19a、層間絶縁膜19、コンタクトプラグ20、ストッパ絶縁膜21、層間絶縁膜22、配線M1が形成された構造となっており、Pチャネル型高耐圧MOSFET、Nチャネル型低耐圧MOSFETおよびPチャネル型低耐圧MOSFETは前記実施の形態1と同様の構造となっている。

【0105】

上記の製造工程により形成した半導体装置では、前記実施の形態1において説明したN−−領域11(図1参照)と同様に、Nチャネル型高耐圧MOSFETのドレイン領域内にLDD層6よりも不純物濃度が低い層であるエピタキシャル層12を形成することにより、ドレイン領域の電界が大きくなることを防ぐことができ、前記実施の形態1と同様の効果を得ることができる。

【0106】

また、本実施の形態の半導体装置ではN−−領域11(図1参照)を形成するためのP型の不純物(例えばB(ホウ素))の打ち込み工程がないため、不純物の分布のばらつきに起因した素子間の性能のばらつきの発生を抑えることができる。

【0107】

なお、ここでは図23に示す拡散層8がエピタキシャル層12の底面に達していない場合について説明したが、拡散層8はエピタキシャル層12の上面から半導体基板1の内部にかけて形成されていても構わない。ただし、本実施の形態の半導体装置の特徴は、エピタキシャル層12を形成することにより、ドレイン領域内のチャネル領域近傍の端部にLDD層6よりも不純物濃度が低い領域を設けることにあるため、エピタキシャル層12内のゲート電極4側の端部に拡散層8が形成されていない領域を残す必要がある。

【0108】

(実施の形態3)

本実施の形態では、高耐圧MOSFETのゲート電極の一方の側壁にサイドウォールを追加して形成することにより、図1を用いて説明したN−−領域11を形成するためのP型不純物(例えばB(ホウ素))が過度に拡散することを防ぐことを可能とする半導体装置について説明する。

【0109】

図27に本実施の形態の半導体装置の断面図を示す。図27に示す半導体装置は図1に示す前記実施の形態1の半導体装置とほぼ同様の構造を有しているが、図1の構造に加えて、ゲート電極4の一方の側壁にオフセットスペーサ16を介してサイドウォール24および17が前記一方の側壁側から順に形成されている。ただし、ゲート電極4のもう一方の側壁にはサイドウォール24は形成されておらず、前記もう一方の側壁側から順にオフセットスペーサ16およびサイドウォール17が形成されている。つまり、本実施の形態のNチャネル型高耐圧MOSFETのゲート電極4の側壁のサイドウォールを構成する絶縁膜はドレイン領域側の方がソース領域側よりも多いため、ゲート電極4の側壁のサイドウォールは左右非対称の構造を有しており、ドレイン領域側のサイドウォールはソース領域側のサイドウォールに比べてゲート長方向の厚さが大きく形成されている。

【0110】

したがって、ゲート電極4およびゲート電極4の側壁のサイドウォールをマスクとしたイオン注入法により自己整合的に半導体基板1の主面に形成される拡散層5および8は、ゲート電極4を中心として左右対称に形成されていない。サイドウォール24は例えば窒化シリコン膜などの絶縁膜からなり、ゲート電極4の一方の側壁に自己整合的に形成されている。

【0111】

微細化されたMOSFETでは、ソース・ドレイン領域を構成する拡散層よりも接合深さが深いLDD層を形成するイオン注入工程において、打ち込まれたイオン(不純物)がゲート電極を突き抜けないように注入エネルギーを調整する必要がある。特に低耐圧のMOSFETを有するコア部では素子の微細化が進むにつれてゲート電極の高さが低くなるため、LDD層を形成するためのイオン注入のエネルギーは低くする必要がある。このとき、LDD層を形成するために打ち込むN型の不純物(例えばP(リン))に比べて、図1に示すようなN−−領域11を形成するために打ち込むP型の不純物(例えばB(ホウ素))の方が半導体基板内において広範囲に拡散しやすくなり、P型の不純物(例えばB(ホウ素))のゲート電極に対するオーバーラップ量が大きくなり、MOSFETの耐圧が低下する虞がある。

【0112】

そこで、本実施の形態の半導体装置では、図27に示すように、MOSFETのドレイン領域側のゲート電極の側壁にのみサイドウォール24を形成した状態でイオン注入を行ってN−−領域11を形成することで、N−−領域11の形成工程において注入するP型不純物(例えばB(ホウ素))がLDD層6よりも大きくゲート電極4にオーバーラップすることを防いでいる。

【0113】

これにより、N−−領域11のLDD層6の内側に形成され、N−−領域11を構成するP型不純物(例えばB(ホウ素))がチャネル領域側のLDD層6の端部よりも外側に導入されることを防ぐことができる。従って、微細化された半導体装置であってLDD層6を形成するためのイオン注入エネルギーを低く抑える必要がある半導体装置でも、P型の不純物(例えばB(ホウ素))がLDD層6よりも大きくゲート電極4にオーバーラップすることに起因する耐圧の低下を防ぎ、前記実施の形態1と同様の効果を得ることができる。よって、半導体装置の微細化の際に起きる低耐圧化の問題が発生することを防ぎ、半導体装置の微細化を容易にすることで半導体装置の性能を向上させることができる。

【0114】

以下に、図28〜図30を用いて本実施の形態の半導体装置の製造工程を説明する。

【0115】

まず、図5〜図12を用いて説明した工程と同様の工程を行うことにより、Nチャネル型高耐圧MOSFET形成領域1Aの半導体基板1の主面上にゲート電極4を形成し、半導体基板1の主面にPウエル10、LDD層6および7を形成する。その後、図13を用いて説明したイオン注入工程は行わずに、図14および図15を用いて説明したイオン注入工程を行うことでPチャネル型高耐圧MOSFET形成領域1Bの半導体基板1の主面にLDD層6bを形成し、複数のゲート電極4のそれぞれの側壁にオフセットスペーサ16を形成する。

【0116】

続いて、図28に示すように、複数のゲート電極4を覆うように半導体基板1の主面上の全面にCVD法などにより例えば窒化シリコン膜からなる絶縁膜を形成(堆積)した後、ドライエッチング法を用いて前記絶縁膜を一部除去し、ゲート電極4の上面および半導体基板1の主面を露出させることにより、各ゲート電極4の両側の側壁に前記絶縁膜からなるサイドウォール24を自己整合的に形成する。なお、ここではオフセットスペーサ16およびサイドウォール24のそれぞれの膜の部材に別の材料を用いるものとする。例えば、オフセットスペーサ16に酸化シリコン膜を用いた場合、サイドウォール24には窒化シリコン膜を用いる。

【0117】

次に、図29に示すように、Nチャネル型高耐圧MOSFET形成領域1Aのドレイン領域側のゲート電極4の側壁に形成されたサイドウォール24を覆い、Nチャネル型高耐圧MOSFET形成領域1Aのゲート電極4のもう一方の側壁と、Nチャネル型高耐圧MOSFET形成領域1A以外の領域の各ゲート電極4の両側の側壁とに形成されたサイドウォール24を露出するフォトレジスト膜P9を形成する。

【0118】

続いて、フォトレジスト膜P9をエッチングマスクとしてエッチングを行うことにより、Nチャネル型高耐圧MOSFET形成領域1Aのソース領域側のゲート電極4の側壁と、Pチャネル型高耐圧MOSFET形成領域1B、Nチャネル型低耐圧MOSFET形成領域1CおよびPチャネル型低耐圧MOSFET形成領域1Dのゲート電極4の側壁とに形成されたサイドウォール24を除去する。このとき、Nチャネル型高耐圧MOSFET形成領域1Aのドレイン領域側のゲート電極4の側壁に形成されたサイドウォール24はフォトレジスト膜P9により覆われているため、エッチングにより除去されずに残る。

【0119】

次に、Nチャネル型高耐圧MOSFET形成領域1Aのゲート電極4の一方の側壁にサイドウォール24を残した状態で、図13を用いて説明したP型不純物(例えばB(ホウ素))の注入をNチャネル型高耐圧MOSFET形成領域1Aのドレイン領域側のみに行うことにより、LDD層6内にLDD層6よりも不純物濃度が低いN−−領域11を形成する。

【0120】

なお、図29におけるNチャネル型高耐圧MOSFET形成領域1Aのドレイン領域側にサイドウォール24を残す工程は、前述の図12および図13に示すフォトレジスト膜P3を形成するために用いたマスクと同じマスクを用いても良い。この場合、フォトレジスト膜のネガ・ポジを反転させることで、図29のフォトレジスト膜P9のようなパターンを形成できる。これによりマスクの数を削減できるため、製造コストを減少させることができる。

【0121】

次に、図16〜図22を用いて説明した工程と同様の工程を行うことにより、図30に示す本実施の形態の半導体装置が完成する。

【0122】

本実施の形態の半導体装置の製造工程では、前記実施の形態1と異なり、Nチャネル型高耐圧MOSFETのゲート電極4のドレイン領域側の側壁にのみサイドウォール24を形成している。これにより、半導体装置の微細化によりゲート電極の膜厚を小さくする必要があるMOSFETにおいて、ゲート電極をイオンが突き抜けない程度にLDD層を形成する際のイオン注入エネルギーが制限される場合に、図27に示すN−−領域11を形成するために打ち込むP型不純物(例えばB(ホウ素))がLDD層6よりも大きくゲート電極4にオーバーラップすることを防ぐことを可能としている。

【0123】

これにより、P型不純物(例えばB(ホウ素))が、ゲート電極4直下の領域であってLDD層6の外側の領域に拡散することによる耐圧の低下を防ぐことができる。したがって、半導体装置を微細化に伴いLDD層の形成のための注入エネルギーを低減する場合であっても、前記実施の形態1と同様の効果を得ることができる。

【0124】

なお、図27および図30ではN−−領域11がゲート電極4にオーバーラップしていないが、ここではN−−領域11を形成するために打ち込んだP型不純物がLDD層6よりも外側に導入されること防ぐことが重要であるため、N−−領域11はゲート電極4とオーバーラップしてもしていなくてもよい。

【0125】

(実施の形態4)

本実施の形態では、前記実施の形態1で示したNチャネル型高耐圧MOSFET形成領域1A(図9参照)のソース領域に、炭素を注入することによって、半導体領域13(図31参照)を形成している。なお、以下の説明では炭素(C)を例示しているが、半導体領域13を形成するために注入する他の元素として、ゲルマニウム(Ge)、フッ素(F)または窒素(N2)が挙げられる。

【0126】

図31に本実施の形態の半導体装置の断面図を示す。炭素(C)をソース領域側に注入して半導体領域13を形成することによって、半導体領域13の底部付近に結晶欠陥を形成することができる。この結晶欠陥は、ドレイン端部でのインパクトイオン化によって発生したキャリアを回収し、イオンパクトイオン化による耐圧低下を防ぐ働きを有する。また半導体領域13をPウエル(P−領域)10よりも深い領域に高いエネルギーで注入することによって、不純物に起因した素子同士の性能ばらつきの低減効果も期待できる。

【0127】

以下に、本実施の形態の半導体装置の製造方法について、図32を用いて説明する。図32は製造工程中の本実施の形態の半導体装置の断面図である。

【0128】

まず、前記実施の形態1の図5〜図9と同様の工程を行う。そして、図10の工程を行う前に、図32に示すように、Nチャネル型高耐圧MOSFET形成領域1Aのソース領域側のみを露出するようにフォトレジスト膜で半導体基板1の主面を覆い、半導体基板1に炭素を注入して半導体領域13を形成する。この時、炭素の注入エネルギーは10〜50keVとし、ドーズ量は1×1014〜1×1015cm−2、注入角度は0°〜25°とする。半導体領域13は、Pウエル(P−領域)10よりも接合深さが深く、ドレイン側のLDD層6と同程度の接合深さを有する。このように深い位置に半導体領域13を形成する理由は、ゲート電極4近傍のドレイン領域の端部近くに結晶欠陥があるとリーク電流の発生源となる可能性があるためである。信頼性を考慮すると、半導体領域13の底部の結晶欠陥はゲート電極4から遠い位置に形成されることが望ましい。

【0129】

この後の工程は、図10〜図22と同様の工程を行うことで、図31の構造を得ることができる。なお、炭素を注入する工程は、図10の工程の前に限られず、図10のPウエル(P−領域)10を形成する工程の後に行ってもよく、図11のLDD層7を形成する工程の後に行ってもよい。

【0130】

また、炭素(C)に代えて、ゲルマニウム(Ge)、フッ素(F)または窒素(N2)を注入することで半導体領域13を形成する場合は、図32を用いて説明したイオン注入を以下の条件で行う。ゲルマニウム(Ge)の場合は、注入エネルギーは40〜150keVとし、ドーズ量は1×1014〜1×1015cm−2とする。フッ素(F)の場合は、注入エネルギーは10〜50keVとし、ドーズ量は1×1014〜1×1015cm−2とする。窒素(N2)の場合は、注入エネルギーは30〜70keVとし、ドーズ量は1×1014〜1×1015cm−2とする。

【0131】

なお、本実施の形態は、他の実施の形態2および3に適用することも可能であり、それにより、本実施の形態と同様の効果を得ることができる。

【0132】

以上、本発明者らによってなされた発明をその実施の形態に基づき具体的に説明したが、本発明は前記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることはいうまでもない。

【0133】

例えば、前記実施の形態1〜4では、N型不純物としてP(リン)を例示し、P型不純物としてB(ボロン)を例示しているが、これに限られず、N型不純物としてAs(ヒ素)や、P型不純物としてBF2(フッ化ボロン)を用いてもよい。

【産業上の利用可能性】

【0134】

本発明は、P型不純物(ホウ素またはフッ化ホウ素などの拡散しやすい不純物)を含む半導体領域を有する装置の製造技術に適用して有効である。

【符号の説明】

【0135】

1 半導体基板

1A Nチャネル型高耐圧MOSFET形成領域

1B Pチャネル型高耐圧MOSFET形成領域

1C Nチャネル型低耐圧MOSFET形成領域

1D Pチャネル型低耐圧MOSFET形成領域

2 Pウエル

2b Nウエル

2c Pウエル

2d Nウエル

3 ゲート絶縁膜

3ab、3cd 絶縁膜

3b、3c、3d ゲート絶縁膜

4 ゲート電極

5、5g 拡散層

6、6b〜6g LDD層(N−領域)

7、7e〜7g LDD層(N−領域)

8、8b〜8d、8g 拡散層

10 Pウエル(P−領域)

10c、10d ハロー領域(P−領域)

10f、g Pウエル

11 N−−領域

12 エピタキシャル層

13 半導体領域

14 シリサイド層

15 素子分離領域

16 オフセットスペーサ

17 サイドウォール

19 層間絶縁膜

19a エッチストッパ膜

20 コンタクトプラグ

21 ストッパ絶縁膜

22 層間絶縁膜

23 絶縁膜

24 サイドウォール

Hn Nチャネル型高耐圧MOSFET

Hp Pチャネル型高耐圧MOSFET

Ln Nチャネル型低耐圧MOSFET

Lp Pチャネル型低耐圧MOSFET

M1 配線

P1〜P9 フォトレジスト膜

【特許請求の範囲】

【請求項1】

半導体基板上にゲート絶縁膜を介して形成されたゲート電極と、

前記ゲート電極の直下に形成された第1P型ウエルと、

前記第1PウエルよりもP型不純物濃度が高い第2P型ウエルと、

第1N型LDD層と、

前記第1N型LDD層よりもN型不純物濃度が高い第1N型拡散層と、

前記第1N型LDD層よりもN型不純物濃度が高く、前記第1N型LDD層よりも前記半導体基板の主面からの接合深さが深い第2N型LDD層と、

前記第2N型LDD層よりもN型不純物濃度が高い第2N型拡散層と、

前記第2N型LDD層よりもN型不純物濃度が低い半導体層と、

を有し、

前記半導体基板の主面には、前記ゲート電極のゲート長方向に順に前記第1N型拡散層、前記第1N型LDD層、前記第2P型ウエル、前記第1P型ウエル、前記第2N型LDD層、前記半導体層および前記第2N型拡散層が形成されていることを特徴とする半導体装置。

【請求項2】

前記半導体基板の主面から反対側の裏面方向に向かって、前記第2N型拡散層、前記半導体層および前記第2N型LDD層が順に形成されていることを特徴とする請求項1記載の半導体装置。

【請求項3】

前記半導体基板の主面には、前記ゲート電極、前記第1N型拡散層、前記第1N型LDD層、前記第2P型ウエル、前記第1P型ウエル、前記第2N型LDD層、前記半導体層および前記第2N型拡散層を有する第1電界効果トランジスタと、

前記第1電界効果トランジスタよりも低い電流で駆動する第2電界効果トランジスタが形成されていることを特徴とする請求項1記載の半導体装置。

【請求項4】

前記第2P型ウエルは前記第1N型LDD層よりも接合深さが深く、前記第1N型拡散層は前記第2P型ウエルよりも接合深さが深いことを特徴とする請求項1記載の半導体装置。

【請求項5】

前記第1N型拡散層側の前記ゲート電極の側壁に第1サイドウォールが形成されており、

前記第2N型拡散層側の前記ゲート電極の側壁に前記第1サイドウォールよりも前記ゲート長方向における膜厚が厚い第2サイドウォールが形成されていることを特徴とする請求項1記載の半導体装置。

【請求項6】

前記第2P型ウエルよりも深い位置に、炭素、ゲルマニウム、フッ素または窒素を含む半導体領域が形成されていることを特徴とする請求項1記載の半導体装置。

【請求項7】

半導体基板上にゲート絶縁膜を介して形成されたゲート電極と、

前記ゲート電極の直下に形成された第1P型ウエルと、

前記第1PウエルよりもP型不純物濃度が高い第2P型ウエルと、

第1N型LDD層と、

前記第1N型LDD層よりもN型不純物濃度が高い第1N型拡散層と、

前記第1N型LDD層よりもN型不純物濃度が高く、前記第1N型LDD層よりも前記半導体基板の主面からの接合深さが深い第2N型LDD層と、

前記第2N型LDD層の上面に接し、前記ゲート電極と絶縁されて形成された、前記第2N型LDD層よりもN型不純物濃度が低いエピタキシャル層と、

前記エピタキシャル層の上面に形成され、前記第2N型LDD層よりもN型不純物濃度が高い第2N型拡散層と、

を有し、

前記半導体基板の主面には、前記ゲート電極のゲート長方向に順に前記第1N型拡散層、前記第1N型LDD層、前記第2P型ウエル、前記第1P型ウエルおよび前記第2N型LDD層が形成されていることを特徴とする半導体装置。

【請求項8】

前記半導体基板の主面には、前記ゲート電極、前記第1N型拡散層、前記第1N型LDD層、前記第2P型ウエル、前記第1P型ウエル、前記第2N型LDD層、前記エピタキシャル層および前記第2N型拡散層を有する第1電界効果トランジスタと、

前記第1電界効果トランジスタよりも低い電流で駆動する第2電界効果トランジスタが形成されていることを特徴とする請求項7記載の半導体装置。

【請求項9】

前記第2P型ウエルは前記第1N型LDD層よりも接合深さが深く、前記第1N型拡散層は前記第2P型ウエルよりも接合深さが深いことを特徴とする請求項7記載の半導体装置。

【請求項10】

前記第2P型ウエルよりも深い位置に、炭素、ゲルマニウム、フッ素または窒素を含む半導体領域が形成されていることを特徴とする請求項7記載の半導体装置。

【請求項11】

(a)半導体基板にP型の不純物を注入して第1P型ウエルを形成する工程と、

(b)前記第1P型ウエルの上面の第1領域および第2領域の間の前記半導体基板上に第1ゲート絶縁膜を介して第1ゲート電極を形成する工程と、

(c)前記第2領域をマスクで覆う工程と、

(d)前記(c)工程の後、前記第1領域にP型の不純物を傾斜注入して第2P型ウエルを形成する工程と、

(e)前記(c)工程の後、前記第1領域にN型の不純物を注入して第1N型LDD層を形成する工程と、

(f)前記第1領域をマスクで覆う工程と、

(g)前記(f)工程の後、前記第2領域にN型の不純物を傾斜法入して第2N型LDD層を形成する工程と、

(h)前記第2N型LDD層にP型の不純物を注入して、前記第2N型LDD層よりも不純物濃度が低い半導体層を形成する工程と、

(i)前記(a)〜(h)工程の後、前記第1ゲート電極の側壁にサイドウォールを形成する工程と、

(j)前記第1領域および前記第2領域に前記サイドウォールをマスクとしてN型の不純物を注入し、前記第1N型LDD層および前記第2N型LDD層よりも不純物濃度が高い第1N型拡散層および第2N型拡散層をそれぞれ形成する工程と、

を有し、

前記半導体基板の主面には、前記第1ゲート電極のゲート長方向に順に前記第1N型拡散層、前記第1N型LDD層、前記第2P型ウエル、前記第1P型ウエル、前記第2N型LDD層、前記半導体層および前記第2N型拡散層が配置され、

前記第2N型LDD層は前記第1N型LDD層よりも不純物濃度が高く、且つ前記第1N型LDD層よりも接合深さが深いことを特徴とする半導体装置の製造方法。

【請求項12】

前記第2領域では、前記半導体基板の主面から裏面方向へ順に、前記第2N型拡散層、前記半導体層および前記第2N型LDD層が形成されていることを特徴とする請求項11記載の半導体装置の製造方法。

【請求項13】

前記第1N型拡散層は前記第1N型LDD層よりも接合深さが深く、前記第2P型ウエルは前記第1N型LDD層よりも接合深さが浅いことを特徴とする請求項11記載の半導体装置の製造方法。

【請求項14】

前記(b)工程では前記半導体基板の主面上に第2ゲート絶縁膜を介して第2ゲート電極を形成し、

(k)前記(b)工程の後、前記第2ゲート電極の横の前記半導体基板の主面にN型またはP型の不純物を導入して拡散層を形成することで、前記第2ゲート電極および前記拡散層を有する第2電界効果トランジスタを形成する工程をさらに有し、

前記第1ゲート電極、前記第1N型拡散層、前記第1N型LDD層、前記第2P型ウエル、前記第1P型ウエル、前記第2N型LDD層、前記半導体層および前記第2N型拡散層は第1電界効果トランジスタを構成し、

前記第2電界効果トランジスタは前記第1電界効果トランジスタよりも低い電流で駆動することを特徴とする請求項11記載の半導体装置の製造方法。

【請求項15】

前記(g)工程は、

(g1)前記第1ゲート電極の側壁に第1絶縁膜を自己整合的に形成する工程と、

(g2)前記第1ゲート電極の第1領域側の側壁の前記第1絶縁膜を除去する工程と、

(g3)前記(g2)工程の後、前記第1ゲート電極の側壁に第2絶縁膜を自己整合的に形成する工程と、

を含み、

前記第1領域側の前記サイドウォールは前記第2絶縁膜により構成され、前記第2領域側の前記サイドウォールは前記第1絶縁膜および前記第2絶縁膜により構成されていることを特徴とする請求項11記載の半導体装置の製造方法。

【請求項16】

前記(c)工程で用いる前記マスクは第1フォトレジスト膜であり、

前記(g2)工程では、前記第1フォトレジスト膜のパターンを反転させた第2フォトレジスト膜を用いて前記第1ゲート電極の第1領域側の側壁の前記第1絶縁膜を除去することを特徴とする請求項15記載の半導体装置の製造方法。

【請求項17】

前記(c)工程後であって、前記(f)工程前に、前記第2P型ウエルよりも深い位置に、炭素、ゲルマニウム、フッ素または窒素からなる半導体領域を形成する工程をさらに有することを特徴とする請求項11記載の半導体装置の製造方法。

【請求項18】

(a)半導体基板にP型の不純物を注入して第1P型ウエルを形成する工程と、

(b)前記第1P型ウエルの上面の第1領域および第2領域の間の前記半導体基板上に第1ゲート絶縁膜を介して第1ゲート電極を形成する工程と、

(c)前記第2領域をマスクで覆う工程と、

(d)前記(c)工程の後、前記第1領域にP型の不純物を傾斜注入して第2P型ウエルを形成する工程と、

(e)前記(c)工程の後、前記第1領域にN型の不純物を注入して第1N型LDD層を形成する工程と、

(f)前記第1領域をマスクで覆う工程と、

(g)前記(f)工程の後、前記第2領域にN型の不純物を傾斜法入して第2N型LDD層を形成する工程と、

(h)前記(a)〜(f)工程の後、前記第1ゲート電極の側壁にサイドウォールを形成する工程と、

(i)前記(f)工程の後、前記半導体基板の上面を覆う膜を形成する工程と、

(j)前記膜を開口して前記第2N型LDD層を露出させる工程と、

(k)前記第2N型LDD層上に前記2N型LDD層よりもN型の不純物濃度が低いエピタキシャル層を形成する工程と、

(l)前記第1領域および前記第2N型LDD層に前記サイドウォールをマスクとしてN型の不純物を注入し、前記第1N型LDD層および前記第2N型LDD層よりも不純物濃度が高い第1N型拡散層および第2N型拡散層をそれぞれ形成する工程と、

を有し、

前記半導体基板の主面には、前記第1ゲート電極のゲート長方向に順に前記第1N型拡散層、前記第1N型LDD層、前記第2P型ウエル、前記第1P型ウエルおよび前記第2N型LDD層が配置され、

第2N型LDD層は前記第1N型LDD層よりも不純物濃度が高く、且つ前記第1N型LDD層よりも接合深さが深いことを特徴とする半導体装置の製造方法。

【請求項19】

前記第1N型拡散層は前記第1N型LDD層よりも接合深さが深く、前記第2P型ウエルは前記第1N型LDD層よりも接合深さが浅いことを特徴とする請求項18記載の半導体装置の製造方法。

【請求項20】

前記(b)工程では前記半導体基板の主面上に第2ゲート絶縁膜を介して第2ゲート電極を形成し、

(m)前記(b)工程の後、前記第2ゲート電極の横の前記半導体基板の主面にN型またはP型の不純物を導入して拡散層を形成することで、前記第2ゲート電極および前記拡散層を有する第2電界効果トランジスタを形成する工程をさらに有し、

前記第1ゲート電極、前記第1N型拡散層、前記第1N型LDD層、前記第2P型ウエル、前記第1P型ウエル、前記第2N型LDD層、前記エピタキシャル層および前記第2N型拡散層は第1電界効果トランジスタを構成し、

前記第2電界効果トランジスタは前記第1電界効果トランジスタよりも低い電流で駆動することを特徴とする請求項18記載の半導体装置の製造方法。

【請求項21】

前記(c)工程で用いる前記マスクは第1フォトレジスト膜であり、

前記(j)工程では、前記第1フォトレジスト膜と同じパターンの第3フォトレジスト膜を用いて前記膜を開口することを特徴とする請求項18記載の半導体装置の製造方法。

【請求項22】

前記(c)工程後であって、前記(f)工程前に、前記第2P型ウエルよりも深い位置に、炭素、ゲルマニウム、フッ素または窒素からなる半導体領域を形成する工程をさらに有することを特徴とする請求項18記載の半導体装置の製造方法。

【請求項1】

半導体基板上にゲート絶縁膜を介して形成されたゲート電極と、

前記ゲート電極の直下に形成された第1P型ウエルと、

前記第1PウエルよりもP型不純物濃度が高い第2P型ウエルと、

第1N型LDD層と、

前記第1N型LDD層よりもN型不純物濃度が高い第1N型拡散層と、

前記第1N型LDD層よりもN型不純物濃度が高く、前記第1N型LDD層よりも前記半導体基板の主面からの接合深さが深い第2N型LDD層と、

前記第2N型LDD層よりもN型不純物濃度が高い第2N型拡散層と、

前記第2N型LDD層よりもN型不純物濃度が低い半導体層と、

を有し、

前記半導体基板の主面には、前記ゲート電極のゲート長方向に順に前記第1N型拡散層、前記第1N型LDD層、前記第2P型ウエル、前記第1P型ウエル、前記第2N型LDD層、前記半導体層および前記第2N型拡散層が形成されていることを特徴とする半導体装置。

【請求項2】

前記半導体基板の主面から反対側の裏面方向に向かって、前記第2N型拡散層、前記半導体層および前記第2N型LDD層が順に形成されていることを特徴とする請求項1記載の半導体装置。

【請求項3】

前記半導体基板の主面には、前記ゲート電極、前記第1N型拡散層、前記第1N型LDD層、前記第2P型ウエル、前記第1P型ウエル、前記第2N型LDD層、前記半導体層および前記第2N型拡散層を有する第1電界効果トランジスタと、

前記第1電界効果トランジスタよりも低い電流で駆動する第2電界効果トランジスタが形成されていることを特徴とする請求項1記載の半導体装置。

【請求項4】

前記第2P型ウエルは前記第1N型LDD層よりも接合深さが深く、前記第1N型拡散層は前記第2P型ウエルよりも接合深さが深いことを特徴とする請求項1記載の半導体装置。

【請求項5】

前記第1N型拡散層側の前記ゲート電極の側壁に第1サイドウォールが形成されており、

前記第2N型拡散層側の前記ゲート電極の側壁に前記第1サイドウォールよりも前記ゲート長方向における膜厚が厚い第2サイドウォールが形成されていることを特徴とする請求項1記載の半導体装置。

【請求項6】

前記第2P型ウエルよりも深い位置に、炭素、ゲルマニウム、フッ素または窒素を含む半導体領域が形成されていることを特徴とする請求項1記載の半導体装置。

【請求項7】

半導体基板上にゲート絶縁膜を介して形成されたゲート電極と、

前記ゲート電極の直下に形成された第1P型ウエルと、

前記第1PウエルよりもP型不純物濃度が高い第2P型ウエルと、

第1N型LDD層と、

前記第1N型LDD層よりもN型不純物濃度が高い第1N型拡散層と、

前記第1N型LDD層よりもN型不純物濃度が高く、前記第1N型LDD層よりも前記半導体基板の主面からの接合深さが深い第2N型LDD層と、

前記第2N型LDD層の上面に接し、前記ゲート電極と絶縁されて形成された、前記第2N型LDD層よりもN型不純物濃度が低いエピタキシャル層と、

前記エピタキシャル層の上面に形成され、前記第2N型LDD層よりもN型不純物濃度が高い第2N型拡散層と、

を有し、

前記半導体基板の主面には、前記ゲート電極のゲート長方向に順に前記第1N型拡散層、前記第1N型LDD層、前記第2P型ウエル、前記第1P型ウエルおよび前記第2N型LDD層が形成されていることを特徴とする半導体装置。

【請求項8】

前記半導体基板の主面には、前記ゲート電極、前記第1N型拡散層、前記第1N型LDD層、前記第2P型ウエル、前記第1P型ウエル、前記第2N型LDD層、前記エピタキシャル層および前記第2N型拡散層を有する第1電界効果トランジスタと、

前記第1電界効果トランジスタよりも低い電流で駆動する第2電界効果トランジスタが形成されていることを特徴とする請求項7記載の半導体装置。

【請求項9】

前記第2P型ウエルは前記第1N型LDD層よりも接合深さが深く、前記第1N型拡散層は前記第2P型ウエルよりも接合深さが深いことを特徴とする請求項7記載の半導体装置。

【請求項10】

前記第2P型ウエルよりも深い位置に、炭素、ゲルマニウム、フッ素または窒素を含む半導体領域が形成されていることを特徴とする請求項7記載の半導体装置。

【請求項11】

(a)半導体基板にP型の不純物を注入して第1P型ウエルを形成する工程と、

(b)前記第1P型ウエルの上面の第1領域および第2領域の間の前記半導体基板上に第1ゲート絶縁膜を介して第1ゲート電極を形成する工程と、

(c)前記第2領域をマスクで覆う工程と、

(d)前記(c)工程の後、前記第1領域にP型の不純物を傾斜注入して第2P型ウエルを形成する工程と、

(e)前記(c)工程の後、前記第1領域にN型の不純物を注入して第1N型LDD層を形成する工程と、

(f)前記第1領域をマスクで覆う工程と、

(g)前記(f)工程の後、前記第2領域にN型の不純物を傾斜法入して第2N型LDD層を形成する工程と、

(h)前記第2N型LDD層にP型の不純物を注入して、前記第2N型LDD層よりも不純物濃度が低い半導体層を形成する工程と、

(i)前記(a)〜(h)工程の後、前記第1ゲート電極の側壁にサイドウォールを形成する工程と、

(j)前記第1領域および前記第2領域に前記サイドウォールをマスクとしてN型の不純物を注入し、前記第1N型LDD層および前記第2N型LDD層よりも不純物濃度が高い第1N型拡散層および第2N型拡散層をそれぞれ形成する工程と、

を有し、

前記半導体基板の主面には、前記第1ゲート電極のゲート長方向に順に前記第1N型拡散層、前記第1N型LDD層、前記第2P型ウエル、前記第1P型ウエル、前記第2N型LDD層、前記半導体層および前記第2N型拡散層が配置され、

前記第2N型LDD層は前記第1N型LDD層よりも不純物濃度が高く、且つ前記第1N型LDD層よりも接合深さが深いことを特徴とする半導体装置の製造方法。

【請求項12】

前記第2領域では、前記半導体基板の主面から裏面方向へ順に、前記第2N型拡散層、前記半導体層および前記第2N型LDD層が形成されていることを特徴とする請求項11記載の半導体装置の製造方法。

【請求項13】