半導体装置およびその製造方法

【課題】半導体基板に形成されたプレーナ型トランジスタと3次元トランジスタを含む半導体装置の形成プロセスを簡略化できるようにする。

【解決手段】半導体基板に形成されたプレーナ型トランジスタと3次元トランジスタを含む半導体装置であり、前記プレーナ型トランジスタ、前記3次元トランジスタはともに高誘電率材料によるゲート絶縁膜を有し、前記プレーナ型トランジスタは、前記ゲート絶縁膜上に、下側が第1のメタル材料(A)、上側が第2のメタル材料(B)からなるゲート電極を有し、前記3次元トランジスタは埋め込みゲート電極を有し、該埋め込みゲート電極の下側のほうに前記第1のメタル材料(A)と同一の材料が、該埋め込みゲート電極の上側のほうに前記第2のメタル材料(B)と同一の材料がそれぞれ使用されている。

【解決手段】半導体基板に形成されたプレーナ型トランジスタと3次元トランジスタを含む半導体装置であり、前記プレーナ型トランジスタ、前記3次元トランジスタはともに高誘電率材料によるゲート絶縁膜を有し、前記プレーナ型トランジスタは、前記ゲート絶縁膜上に、下側が第1のメタル材料(A)、上側が第2のメタル材料(B)からなるゲート電極を有し、前記3次元トランジスタは埋め込みゲート電極を有し、該埋め込みゲート電極の下側のほうに前記第1のメタル材料(A)と同一の材料が、該埋め込みゲート電極の上側のほうに前記第2のメタル材料(B)と同一の材料がそれぞれ使用されている。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体基板に形成されたプレーナ型トランジスタと、3次元トランジスタを含む半導体装置およびその製造方法に関する。

【背景技術】

【0002】

半導体基板上にゲート絶縁膜を形成した後、ゲート絶縁膜上にゲート電極を形成し、イオン注入などによってソース領域、ドレイン領域を形成することでMISFET(Metal Insulator Semiconductor Field Effect Transistor)を形成することが出来る。ゲート絶縁膜としては酸化シリコン膜を、ゲート電極としてはポリシリコン膜をそれぞれ使用するのが一般的である。

【0003】

しかしながら、近年、MISFET素子の微細化に伴いゲート絶縁膜の薄膜化が進み、ポリシリコン膜をゲート電極に使用した場合におけるゲート電極の空乏化の影響が無視できなくなってきている。このため、ゲート電極としてメタルゲート電極を用い、ゲート電極の空乏化現象を抑制する技術が提案されている。

【0004】

また、MISFET素子の微細化に伴いゲート絶縁膜の薄膜化が進み、薄い酸化シリコン膜をゲート絶縁膜として使用すると、MISFETのチャネルを流れる電子が酸化膜によって形成される障壁をトンネルしてゲート電極に流れる、いわゆるトンネル電流が発生してしまう。このため、ゲート絶縁膜として、酸化シリコン膜より誘電率の高い材料(高誘電率材料:以下、高誘電率をHigh-Kと呼ぶことがある)を使用することにより、容量を同じにしても物理的膜厚を増加させることでリーク電流を低減する技術がある。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2008−218642号公報

【特許文献2】特開2009−099955号公報

【特許文献3】特開2004−134666号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

近年、DRAMをはじめとするメモリ等で、デバイスの3次元化技術がある。3次元化とはトランジスタの構造をプレーナ型ではない構造にすることであり、例えばトレンチゲート、Fin-FET等が挙げられる。

【0007】

これらの構造も形成しつつ、メタルゲート、高誘電率材料のトランジスタも形成すると、形成プロセスが煩雑になるという問題があった。プロセスが煩雑になると、製造コストが上がってしまう。

【0008】

そこで、本発明の課題は、半導体基板に形成されたプレーナ型トランジスタと3次元トランジスタを含む半導体装置の形成プロセスを簡略化できるようにすることにある。

【0009】

本発明の他の課題は、プレーナ型トランジスタと3次元トランジスタの閾値電圧を容易に制御できるようにすることにある。

【課題を解決するための手段】

【0010】

本発明は、半導体基板にプレーナ型トランジスタと3次元トランジスタの両方を形成するが、それらのトランジスタの構成材料、特にメタルゲートの構成材料を同一にする。すなわち、一度のメタル材料の成膜により、プレーナ型トランジスタと3次元トランジスタの両方に成膜を行い、それらのメタル材料をメタルゲートとして利用するものである。

【0011】

このとき、プレーナ型トランジスタのHigh-K絶縁膜上の第1のメタル材料(A)と、3次元トランジスタのゲート電極の下側のほうの材料を同一のものにする。一方、プレーナ型トランジスタの第1のメタル材料(A)の上に成膜する第2のメタル材料(B)と、3次元トランジスタのゲート電極の上側のほうの材料を同一のものにする。

【0012】

具体的には、本発明による半導体装置は、半導体基板に形成されたプレーナ型トランジスタと3次元トランジスタを含み、前記プレーナ型トランジスタ、前記3次元トランジスタはともに高誘電率材料によるゲート絶縁膜を有し、前記プレーナ型トランジスタは、前記ゲート絶縁膜上に、下側が第1のメタル材料(A)、上側が第2のメタル材料(B)からなるゲート電極を有し、前記3次元トランジスタは埋め込みゲート電極を有し、該埋め込みゲート電極の下側のほうに前記第1のメタル材料(A)と同一の材料が、該埋め込みゲート電極の上側のほうに前記第2のメタル材料(B)と同一の材料がそれぞれ使用されていることを特徴とする。

【0013】

本発明による半導体装置の製造方法は、プレーナ型トランジスタのゲート絶縁膜と3次元トランジスタのゲート絶縁膜を高誘電率材料により同時に成膜し、前記プレーナ型トランジスタの前記ゲート絶縁膜上でメタルゲート電極の下側のほうを構成する第1のメタル材料(A)と、前記3次元トランジスタの前記ゲート絶縁膜上で埋め込みゲート電極の下側のほうを構成するメタル材料を同時に成膜することを特徴とし、さらに前記プレーナ型トランジスタの前記第1のメタル材料(A)の上で前記メタルゲート電極の上側のほうを構成する第2のメタル材料(B)と、前記3次元トランジスタの前記埋め込みゲート電極の上側のほうを構成するメタル材料を同時に成膜することが望ましい。

【発明の効果】

【0014】

本発明によれば、プレーナ型トランジスタと3次元トランジスタを含む半導体装置の形成を少ない工程数で実現できる。特に、メタルゲート電極の形成と材料について改良したことにより、プレーナ型トランジスタと3次元トランジスタの閾値電圧の制御を容易に実現することができる。

【図面の簡単な説明】

【0015】

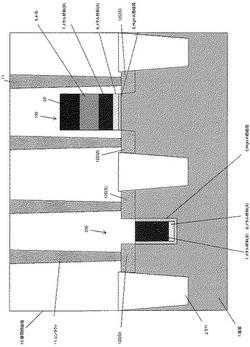

【図1】本発明の第1の実施例による半導体装置の製造方法を説明するための断面図である。

【図2】図1に続く、本発明の第1の実施例による半導体装置の製造方法を説明するための断面図である。

【図3】図2に続く、本発明の第1の実施例による半導体装置の製造方法を説明するための断面図である。

【図4】図3に続く、本発明の第1の実施例による半導体装置の製造方法を説明するための断面図である。

【図5】図4に続く、本発明の第1の実施例による半導体装置の製造方法を説明するための断面図である。

【図6】図5に続く、本発明の第1の実施例による半導体装置の製造方法を説明するための断面図である。

【図7】図6に続く、本発明の第1の実施例による半導体装置の製造方法を説明するための断面図である。

【図8】図7に続く、本発明の第1の実施例による半導体装置の製造方法を説明するための断面図である。

【図9】図8に続く、本発明の第1の実施例による半導体装置の製造方法を説明するための断面図である。

【図10】図9に続く、本発明の第1の実施例による半導体装置の製造方法を説明するための断面図である。

【図11】本発明の第2の実施例による半導体装置の製造方法のうち、図9に対応する製造工程を説明するための断面図である。

【発明を実施するための形態】

【0016】

[発明の原理]

本発明の実施例について説明する前に、原理を説明する。

【0017】

本発明による半導体装置においては、プレーナ型トランジスタの閾値電圧Vtpは、プレーナ型トランジスタのゲート電極の仕事関数により制御される。すなわち第1のメタル材料(A)の材料の構成を変えることで、閾値電圧Vtpを容易に制御することが出来る。

【0018】

また、下記のようにデバイス作成を行なうことで、3次元トランジスタの閾値電圧Vttは第2のメタル材料(B)の材料を変えることで制御することが出来る。

【0019】

<N型トランジスタの場合>

“第1のメタル材料(A)の仕事関数“<“第2のメタル材料(B)の仕事関数“の関係にあれば、第2のメタル材料(B)により閾値電圧Vttを制御することができる。

【0020】

一方、“第1のメタル材料(A)の仕事関数“>“第2のメタル材料(B)の仕事関数“の場合、後述する図11のように3次元トランジスタの第1のメタル材料(A)6から見てHigh-K絶縁膜5をはさんで反対側にN型拡散層が形成されるようにイオン注入等を行うことで、第2のメタル材料(B)により閾値電圧Vttを制御できる。すなわち、プレーナ型トランジスタとは別のパラメータで自由に3次元トランジスタの閾値電圧Vttを制御することができる。このため、プロセス設計しやすい。

【0021】

<P型トランジスタの場合>

“第1のメタル材料(A)の仕事関数“>“第2のメタル材料(B)の仕事関数“の関係にあれば、第2のメタル材料(B)により閾値電圧Vttを制御することができる。

【0022】

一方、“第1のメタル材料(A)の仕事関数“<“第2のメタル材料(B)の仕事関数“の場合、図11のように3次元トランジスタの第1のメタル材料(A)6から見てHigh-K絶縁膜5をはさんで反対側にP型拡散層が形成されるようにイオン注入等を行うことで、第2のメタル材料(B)により閾値電圧Vttを制御することができる。すなわち、プレーナ型トランジスタとは別のパラメータで自由に3次元トランジスタの閾値電圧Vttを制御することができる。このため、プロセス設計しやすい。

【0023】

また、本発明による半導体装置の製造方法では、上記のような構造を、少ない工程数で形成することが出来るため、製造コストが安価である。

【0024】

本発明によれば、プレーナ型トランジスタと3次元トランジスタを含む半導体装置の形成を少ない工程数で実現できる。特に、メタルゲート電極の形成と材料について改良したことにより、プレーナ型トランジスタと3次元トランジスタの閾値電圧の制御を容易に実現することができる。以下に、そのことを説明する。

【0025】

通常、トランジスタの閾値電圧Vtは、下記の式にて表現できる。

【0026】

Vt=Vfb+2Φ+√(4εqNΦ)/C

Vfb:フラットバンド電圧

Φ:フェルミポテンシャルと真性ポテンシャルの差

ε:シリコンの誘電率

q:電子の電荷

N:チャネルのアクセプタ密度

C:ゲート絶縁膜容量

また、Vfbは下記の式にて表現できる。

【0027】

Vfb=Wdif-Q/C

Q:等価酸化膜電荷

Wdif:ゲート電極のメタルとシリコンの仕事関数差

すなわち、閾値電圧Vtは、

(1)C:ゲート絶縁膜容量

(2)N:チャネルのアクセプタ密度

(3)Wdif:ゲート電極のメタルとシリコンの仕事関数差

等でコントロールできる。

【0028】

ただし、閾値電圧Vtを、例えば上げるためにCを小さくすると、飽和時の電流は、近似的にCに比例することから、飽和時の電流が小さくなるという弊害がある(i)。

【0029】

また、閾値電圧Vtを、例えば上げるためにNを大きくすると、一般的に閾値電圧Vtのバラツキが大きくなるという弊害がある(ii)。

【0030】

一方、閾値電圧Vtを上げるためにWdifを大きくする方法は、そういう弊害がない。

【0031】

Wdifはシリコンの仕事関数は定数とすると、ゲート電極のメタルの仕事関数で決まる。本発明の方法における“閾値電圧の制御を容易にする”とは、言い換えれば、上記(i)、(ii)の弊害に悩まされること無く、デバイス設計が出来るということである。

【0032】

半導体製造の分野で常用されている主な材料の仕事関数は以下の値である。金属であるチタン(Ti)の仕事関数は4.14eV、タングステン(W)は4.52eV、ニッケル(Ni)は5.2eV、タンタル(Ta)は4.19eV、プラチナ(Pt)は5.65eVである。また、金属化合物である窒化チタン(TiN)の仕事関数は4.7eV、窒化タングステン(WN)は5.0eV、窒化タンタル(TaN)は5.43eVである。さらに、金属シリサイドであるチタンシリサイド(TiSi2)の仕事関数は4.5eV、タングステンシリサイド(WSi2)は4.4eV、ニッケルシリサイド(NiSi2)は4.9eVである。

【0033】

上記材料の中で、半導体基板表面に形成する2つのMOSトランジスタがあり、第1のトランジスタのゲート電極にTiNを用い、第2のトランジスタのゲート電極にWを用いた場合、各々の仕事関数は4.7eV、4.52eVであるので、各々のトランジスタの閾値電圧Vtには0.18eVの差を生じさせることができる。また、TiNのような化合物の場合、TiとNの組成を制御することにより4.14〜4.7eVの範囲で閾値電圧Vtを変化させることができる。したがって、異なる材料をゲート電極として選択すれば、同一半導体基板上に異なる閾値電圧Vtを有するトランジスタを形成することができる。

【0034】

[実施例]

(構成の説明)

はじめに、本発明の実施例の構成について説明する。

【0035】

本実施例に係る半導体装置は、半導体基板に形成されたプレーナ型トランジスタと3次元トランジスタを含む。両方のトランジスタともにゲート絶縁膜にHigh-K絶縁膜を使用し、プレーナ型トランジスタのHigh-K絶縁膜上のメタルゲートの第1のメタル材料(A)と同一の材料が、3次元トランジスタのゲート電極の下側のほうに使用され、プレーナ型トランジスタの第1のメタル材料(A)の上の第2のメタル材料(B)が、3次元トランジスタのゲート電極の上側のほうに使用される。第1のメタル材料(A)、(B)は仕事関数の異なるものが用いられる。

【0036】

(製法(プロセス等)の説明)

次に、図1〜図10を参照して、実施例の製法について説明する。

【0037】

図1において、半導体基板(シリコン基板)1に、200nmの深さを持つ複数のSTI(Shallow Trench Isolation)2の形成及び酸化膜3の形成を公知の方法で行う。図中、STI2は空白となっているが、実際には絶縁物で埋め戻されている。

【0038】

次に、図2に示すように、酸化膜3上に、3次元トランジスタ形成のためのハードマスク4を50nm厚で成膜する。

【0039】

その後、ハードマスク4にレジストを塗布し、リソグラフィーでパターニングを行って形成したレジストマスクを利用してハードマスク4のエッチングと酸化膜3のエッチングと半導体基板1の深さ150nmの溝16のエッチングを行う。その後、レジストマスクをアッシングにより除去する(図3)。

【0040】

その後、図4に示すように、半導体基板1に形成した溝16の内壁に対して5nm分の酸化を行って酸化膜3’を形成し、その後ハードマスク4をウエットエッチングで除去する(図4)。

【0041】

続いて酸化膜3、3’をウエットエッチングし、その後、溝16の内壁を含む全面にHigh-K(高誘電率)材料を含む絶縁膜(High-K絶縁膜5)(ゲート絶縁膜)の成長を2.5nm厚で行う。High-K材料は、例えばHfO、HfSiOである(図5)。

【0042】

その後、図6に示すように、スパッタ法によるPVD(Physical Vapor Deposition)により、第1のメタル材料(A)6を成膜する。第1のメタル材料(A)の材料はTiN、Ti、Wなどである。TiNは、TiとNの比率を変えることが出来る。第1のメタル材料(A)6の膜厚は、例えば10nmとする。ここで、スパッタ法は指向性が強いので、第1のメタル材料(A)6は半導体基板1の表面と、溝16の底面に形成されるが、溝16の側壁には形成されない。

【0043】

その後、図7に示すように、溝16を埋めるように第1のメタル材料(A)6上に、第2のメタル材料(B)7をCVD(Chemical Vapor Deposition)で成膜する。第2のメタル材料(B)7の材料はTiN、Ti、Wなどである。第2のメタル材料(B)7の成膜の膜厚は、例えば25nmである。

【0044】

その後、図8に示すように、第2のメタル材料(B)7上にa-Si(非晶質シリコン)8を30nm厚で成膜し、Pイオンの注入を全面に行う(a-Si 8の代わりにPがin-situドープされたポリシリコン膜でも良い)。その後、a-Si8上にさらにメタル材料20を成膜する。メタル材料20は30nm厚で成膜する。メタル材料20の例としては、WSi、W、Ti、TiNを含むもので良い。その後、レジストを塗布し、リソグラフィーでパターニングをする。9はレジストパターンを示す。

【0045】

その後、レジストパターン9をマスクとしてエッチング加工を行い、プレーナ型トランジスタと3次元トランジスタのゲート形状を形成する。続いてレジストをアッシングにより除去する。その後、レジスト塗布工程と、リソグラフィー工程と、イオン注入工程と、剥離工程を複数行い、更にソース、ドレインとなるべき領域にイオン注入を行ってソース12S(ドレイン12D)の形成を行ない、プレーナ型トランジスタ100、3次元トランジスタ200を形成する。その後、層間絶縁膜10を堆積形成した後、CMP(Chemical Mechanical Polishing)で平坦化を行い、更にソース12S、ドレイン12Dのそれぞれに至るコンタクト11の形成を行う(図9)。

【0046】

以上のようにして、プレーナ型トランジスタ100においては半導体基板1の表面に第1のメタル材料(A)6と第2のメタル材料(B)7の積層によるゲート電極が形成され、3次元トランジスタ200においては溝内に第1のメタル材料(A)6と第2のメタル材料(B)7の積層による埋め込みゲート電極が形成される。

【0047】

なお、図8から図9までの加工は公知の方法で行うことが出来る。

【0048】

さらにシリンダ加工工程や、コンタクト11に接続するための上部配線15、コンタクト等を形成する工程を行い、プレーナ型トランジスタ100と3次元トランジスタ200を含む半導体デバイスを形成する(図10)。

【0049】

上記実施例の説明を要約すると以下の通りである。

【0050】

本実施例では、以下に概略される製造工程を経て、2種類のトランジスタのゲート電極を同時に形成することにより各々のトランジスタの閾値電圧を変化させることができるようにしている。

【0051】

半導体基板の第1の領域に溝(トレンチ)を形成した後、基板表面全面にHigh-K(高誘電率)ゲート絶縁膜を形成する。

【0052】

次いで、スパッタ(PVD)法により第1のメタル材料(A)を全面に形成する。スパッタ法は指向性が強いので第1のメタル材料(A)は基板表面と溝の底面に形成されるが、溝の側壁には形成されない。

【0053】

次いで、CVD法により、溝を埋設するように、全面に第2のメタル材料(B)を形成する。

【0054】

さらに、マスクとなる非晶質Si(a-Si)を全面に形成し、リソグラフィーとドライエッチング法により非晶質Si,第2のメタル材料(B)、第1のメタル材料(A)を順次エッチングし、半導体基板表面にプレーナ型トランジスタのゲート電極を、溝内に第1のメタル材料(A)と第2のメタル材料(B)が積層された埋め込みゲート電極を形成する。

【0055】

ここで、第1のメタル材料(A)の仕事関数が第2のメタル材料(B)の仕事関数よりも小さい材料を選択すれば、プレーナ型トランジスタの閾値電圧Vtpは第1のメタル材料(A)の仕事関数で律則され、3次元トランジスタ(埋め込みゲート型トランジスタ)では側壁部に形成されている、仕事関数が相対的に大きい第2のメタル材料(B)の仕事関数で閾値電圧Vttを律則させることができる。

【0056】

逆に、第1のメタル材料(A)の仕事関数が第2のメタル材料(B)の仕事関数よりも大きい場合、いずれのトランジスタの閾値電圧も第1のメタル材料(A)で律則されることとなる。しかし、この場合には、図11(後述する)に示されているように、溝底の半導体基板表面に予め高濃度不純物層を形成しておき、底面部分はトランジスタ動作しない構成としておく。これにより、3次元トランジスタにおける第1のメタル材料(A)の寄与はなくなるので、プレーナ型トランジスタの閾値電圧Vtpは第1のメタル材料(A)、3次元トランジスタの閾値電圧Vttは第2のメタル材料(B)で律則される状態をつくることができる。

【0057】

また、ゲート電極を、例えばTiNなどの2元系で構成すれば、TiとNの含有比を変えることによっても仕事関数の制御が可能であり、これをスパッタ法、もしくはCVD法で組成を変えて成膜すれば、上記の閾値電圧制御ができる。あるいは、TiNに他の金属を含有させた場合とさせない場合とで仕事関数を変化させることもできる。

【0058】

いずれにしても、上記実施例をメモリチップに適用する場合には、3次元トランジスタ200はメモリセル部に使用し、プレーナ型トランジスタ100を周辺回路用のトランジスタとして使用することができる。

【0059】

[別の実施例]

上記実施例に代わる別の実施例として、図11に示すように、3次元トランジスタ200の埋め込みゲート電極からみて、High-K絶縁膜(ゲート絶縁膜)5をはさんで下側の半導体基板1にイオン注入により拡散層12S(D)’を形成するようにしたものでも良い。

【0060】

[別の実施例の製造方法]

この別の実施例は、図3の工程において溝16を形成した後、ソース領域、ドレイン領域形成のためのイオン注入と同じ型の拡散層となるようにイオン注入を行う。その他の製造方法は、上記の(製法(プロセス等)の説明)と同様のプロセスで良い。図11は、図9と対応する図である。

【0061】

以上、本発明を、複数の実施例を参照して説明したが、本発明は上記実施例に限定されるものではない。本発明の構成や詳細には、請求項に記載された本発明の精神や範囲内で当業者が理解し得る様々な変更をすることができる。

【符号の説明】

【0062】

1 半導体基板

2 STI

3、3’ 酸化膜

4 ハードマスク

5 High-K絶縁膜

6 第1のメタル材料(A)

7 第2のメタル材料(B)

8 a-Si

9 レジストパターン

16 溝

【技術分野】

【0001】

本発明は、半導体基板に形成されたプレーナ型トランジスタと、3次元トランジスタを含む半導体装置およびその製造方法に関する。

【背景技術】

【0002】

半導体基板上にゲート絶縁膜を形成した後、ゲート絶縁膜上にゲート電極を形成し、イオン注入などによってソース領域、ドレイン領域を形成することでMISFET(Metal Insulator Semiconductor Field Effect Transistor)を形成することが出来る。ゲート絶縁膜としては酸化シリコン膜を、ゲート電極としてはポリシリコン膜をそれぞれ使用するのが一般的である。

【0003】

しかしながら、近年、MISFET素子の微細化に伴いゲート絶縁膜の薄膜化が進み、ポリシリコン膜をゲート電極に使用した場合におけるゲート電極の空乏化の影響が無視できなくなってきている。このため、ゲート電極としてメタルゲート電極を用い、ゲート電極の空乏化現象を抑制する技術が提案されている。

【0004】

また、MISFET素子の微細化に伴いゲート絶縁膜の薄膜化が進み、薄い酸化シリコン膜をゲート絶縁膜として使用すると、MISFETのチャネルを流れる電子が酸化膜によって形成される障壁をトンネルしてゲート電極に流れる、いわゆるトンネル電流が発生してしまう。このため、ゲート絶縁膜として、酸化シリコン膜より誘電率の高い材料(高誘電率材料:以下、高誘電率をHigh-Kと呼ぶことがある)を使用することにより、容量を同じにしても物理的膜厚を増加させることでリーク電流を低減する技術がある。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2008−218642号公報

【特許文献2】特開2009−099955号公報

【特許文献3】特開2004−134666号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

近年、DRAMをはじめとするメモリ等で、デバイスの3次元化技術がある。3次元化とはトランジスタの構造をプレーナ型ではない構造にすることであり、例えばトレンチゲート、Fin-FET等が挙げられる。

【0007】

これらの構造も形成しつつ、メタルゲート、高誘電率材料のトランジスタも形成すると、形成プロセスが煩雑になるという問題があった。プロセスが煩雑になると、製造コストが上がってしまう。

【0008】

そこで、本発明の課題は、半導体基板に形成されたプレーナ型トランジスタと3次元トランジスタを含む半導体装置の形成プロセスを簡略化できるようにすることにある。

【0009】

本発明の他の課題は、プレーナ型トランジスタと3次元トランジスタの閾値電圧を容易に制御できるようにすることにある。

【課題を解決するための手段】

【0010】

本発明は、半導体基板にプレーナ型トランジスタと3次元トランジスタの両方を形成するが、それらのトランジスタの構成材料、特にメタルゲートの構成材料を同一にする。すなわち、一度のメタル材料の成膜により、プレーナ型トランジスタと3次元トランジスタの両方に成膜を行い、それらのメタル材料をメタルゲートとして利用するものである。

【0011】

このとき、プレーナ型トランジスタのHigh-K絶縁膜上の第1のメタル材料(A)と、3次元トランジスタのゲート電極の下側のほうの材料を同一のものにする。一方、プレーナ型トランジスタの第1のメタル材料(A)の上に成膜する第2のメタル材料(B)と、3次元トランジスタのゲート電極の上側のほうの材料を同一のものにする。

【0012】

具体的には、本発明による半導体装置は、半導体基板に形成されたプレーナ型トランジスタと3次元トランジスタを含み、前記プレーナ型トランジスタ、前記3次元トランジスタはともに高誘電率材料によるゲート絶縁膜を有し、前記プレーナ型トランジスタは、前記ゲート絶縁膜上に、下側が第1のメタル材料(A)、上側が第2のメタル材料(B)からなるゲート電極を有し、前記3次元トランジスタは埋め込みゲート電極を有し、該埋め込みゲート電極の下側のほうに前記第1のメタル材料(A)と同一の材料が、該埋め込みゲート電極の上側のほうに前記第2のメタル材料(B)と同一の材料がそれぞれ使用されていることを特徴とする。

【0013】

本発明による半導体装置の製造方法は、プレーナ型トランジスタのゲート絶縁膜と3次元トランジスタのゲート絶縁膜を高誘電率材料により同時に成膜し、前記プレーナ型トランジスタの前記ゲート絶縁膜上でメタルゲート電極の下側のほうを構成する第1のメタル材料(A)と、前記3次元トランジスタの前記ゲート絶縁膜上で埋め込みゲート電極の下側のほうを構成するメタル材料を同時に成膜することを特徴とし、さらに前記プレーナ型トランジスタの前記第1のメタル材料(A)の上で前記メタルゲート電極の上側のほうを構成する第2のメタル材料(B)と、前記3次元トランジスタの前記埋め込みゲート電極の上側のほうを構成するメタル材料を同時に成膜することが望ましい。

【発明の効果】

【0014】

本発明によれば、プレーナ型トランジスタと3次元トランジスタを含む半導体装置の形成を少ない工程数で実現できる。特に、メタルゲート電極の形成と材料について改良したことにより、プレーナ型トランジスタと3次元トランジスタの閾値電圧の制御を容易に実現することができる。

【図面の簡単な説明】

【0015】

【図1】本発明の第1の実施例による半導体装置の製造方法を説明するための断面図である。

【図2】図1に続く、本発明の第1の実施例による半導体装置の製造方法を説明するための断面図である。

【図3】図2に続く、本発明の第1の実施例による半導体装置の製造方法を説明するための断面図である。

【図4】図3に続く、本発明の第1の実施例による半導体装置の製造方法を説明するための断面図である。

【図5】図4に続く、本発明の第1の実施例による半導体装置の製造方法を説明するための断面図である。

【図6】図5に続く、本発明の第1の実施例による半導体装置の製造方法を説明するための断面図である。

【図7】図6に続く、本発明の第1の実施例による半導体装置の製造方法を説明するための断面図である。

【図8】図7に続く、本発明の第1の実施例による半導体装置の製造方法を説明するための断面図である。

【図9】図8に続く、本発明の第1の実施例による半導体装置の製造方法を説明するための断面図である。

【図10】図9に続く、本発明の第1の実施例による半導体装置の製造方法を説明するための断面図である。

【図11】本発明の第2の実施例による半導体装置の製造方法のうち、図9に対応する製造工程を説明するための断面図である。

【発明を実施するための形態】

【0016】

[発明の原理]

本発明の実施例について説明する前に、原理を説明する。

【0017】

本発明による半導体装置においては、プレーナ型トランジスタの閾値電圧Vtpは、プレーナ型トランジスタのゲート電極の仕事関数により制御される。すなわち第1のメタル材料(A)の材料の構成を変えることで、閾値電圧Vtpを容易に制御することが出来る。

【0018】

また、下記のようにデバイス作成を行なうことで、3次元トランジスタの閾値電圧Vttは第2のメタル材料(B)の材料を変えることで制御することが出来る。

【0019】

<N型トランジスタの場合>

“第1のメタル材料(A)の仕事関数“<“第2のメタル材料(B)の仕事関数“の関係にあれば、第2のメタル材料(B)により閾値電圧Vttを制御することができる。

【0020】

一方、“第1のメタル材料(A)の仕事関数“>“第2のメタル材料(B)の仕事関数“の場合、後述する図11のように3次元トランジスタの第1のメタル材料(A)6から見てHigh-K絶縁膜5をはさんで反対側にN型拡散層が形成されるようにイオン注入等を行うことで、第2のメタル材料(B)により閾値電圧Vttを制御できる。すなわち、プレーナ型トランジスタとは別のパラメータで自由に3次元トランジスタの閾値電圧Vttを制御することができる。このため、プロセス設計しやすい。

【0021】

<P型トランジスタの場合>

“第1のメタル材料(A)の仕事関数“>“第2のメタル材料(B)の仕事関数“の関係にあれば、第2のメタル材料(B)により閾値電圧Vttを制御することができる。

【0022】

一方、“第1のメタル材料(A)の仕事関数“<“第2のメタル材料(B)の仕事関数“の場合、図11のように3次元トランジスタの第1のメタル材料(A)6から見てHigh-K絶縁膜5をはさんで反対側にP型拡散層が形成されるようにイオン注入等を行うことで、第2のメタル材料(B)により閾値電圧Vttを制御することができる。すなわち、プレーナ型トランジスタとは別のパラメータで自由に3次元トランジスタの閾値電圧Vttを制御することができる。このため、プロセス設計しやすい。

【0023】

また、本発明による半導体装置の製造方法では、上記のような構造を、少ない工程数で形成することが出来るため、製造コストが安価である。

【0024】

本発明によれば、プレーナ型トランジスタと3次元トランジスタを含む半導体装置の形成を少ない工程数で実現できる。特に、メタルゲート電極の形成と材料について改良したことにより、プレーナ型トランジスタと3次元トランジスタの閾値電圧の制御を容易に実現することができる。以下に、そのことを説明する。

【0025】

通常、トランジスタの閾値電圧Vtは、下記の式にて表現できる。

【0026】

Vt=Vfb+2Φ+√(4εqNΦ)/C

Vfb:フラットバンド電圧

Φ:フェルミポテンシャルと真性ポテンシャルの差

ε:シリコンの誘電率

q:電子の電荷

N:チャネルのアクセプタ密度

C:ゲート絶縁膜容量

また、Vfbは下記の式にて表現できる。

【0027】

Vfb=Wdif-Q/C

Q:等価酸化膜電荷

Wdif:ゲート電極のメタルとシリコンの仕事関数差

すなわち、閾値電圧Vtは、

(1)C:ゲート絶縁膜容量

(2)N:チャネルのアクセプタ密度

(3)Wdif:ゲート電極のメタルとシリコンの仕事関数差

等でコントロールできる。

【0028】

ただし、閾値電圧Vtを、例えば上げるためにCを小さくすると、飽和時の電流は、近似的にCに比例することから、飽和時の電流が小さくなるという弊害がある(i)。

【0029】

また、閾値電圧Vtを、例えば上げるためにNを大きくすると、一般的に閾値電圧Vtのバラツキが大きくなるという弊害がある(ii)。

【0030】

一方、閾値電圧Vtを上げるためにWdifを大きくする方法は、そういう弊害がない。

【0031】

Wdifはシリコンの仕事関数は定数とすると、ゲート電極のメタルの仕事関数で決まる。本発明の方法における“閾値電圧の制御を容易にする”とは、言い換えれば、上記(i)、(ii)の弊害に悩まされること無く、デバイス設計が出来るということである。

【0032】

半導体製造の分野で常用されている主な材料の仕事関数は以下の値である。金属であるチタン(Ti)の仕事関数は4.14eV、タングステン(W)は4.52eV、ニッケル(Ni)は5.2eV、タンタル(Ta)は4.19eV、プラチナ(Pt)は5.65eVである。また、金属化合物である窒化チタン(TiN)の仕事関数は4.7eV、窒化タングステン(WN)は5.0eV、窒化タンタル(TaN)は5.43eVである。さらに、金属シリサイドであるチタンシリサイド(TiSi2)の仕事関数は4.5eV、タングステンシリサイド(WSi2)は4.4eV、ニッケルシリサイド(NiSi2)は4.9eVである。

【0033】

上記材料の中で、半導体基板表面に形成する2つのMOSトランジスタがあり、第1のトランジスタのゲート電極にTiNを用い、第2のトランジスタのゲート電極にWを用いた場合、各々の仕事関数は4.7eV、4.52eVであるので、各々のトランジスタの閾値電圧Vtには0.18eVの差を生じさせることができる。また、TiNのような化合物の場合、TiとNの組成を制御することにより4.14〜4.7eVの範囲で閾値電圧Vtを変化させることができる。したがって、異なる材料をゲート電極として選択すれば、同一半導体基板上に異なる閾値電圧Vtを有するトランジスタを形成することができる。

【0034】

[実施例]

(構成の説明)

はじめに、本発明の実施例の構成について説明する。

【0035】

本実施例に係る半導体装置は、半導体基板に形成されたプレーナ型トランジスタと3次元トランジスタを含む。両方のトランジスタともにゲート絶縁膜にHigh-K絶縁膜を使用し、プレーナ型トランジスタのHigh-K絶縁膜上のメタルゲートの第1のメタル材料(A)と同一の材料が、3次元トランジスタのゲート電極の下側のほうに使用され、プレーナ型トランジスタの第1のメタル材料(A)の上の第2のメタル材料(B)が、3次元トランジスタのゲート電極の上側のほうに使用される。第1のメタル材料(A)、(B)は仕事関数の異なるものが用いられる。

【0036】

(製法(プロセス等)の説明)

次に、図1〜図10を参照して、実施例の製法について説明する。

【0037】

図1において、半導体基板(シリコン基板)1に、200nmの深さを持つ複数のSTI(Shallow Trench Isolation)2の形成及び酸化膜3の形成を公知の方法で行う。図中、STI2は空白となっているが、実際には絶縁物で埋め戻されている。

【0038】

次に、図2に示すように、酸化膜3上に、3次元トランジスタ形成のためのハードマスク4を50nm厚で成膜する。

【0039】

その後、ハードマスク4にレジストを塗布し、リソグラフィーでパターニングを行って形成したレジストマスクを利用してハードマスク4のエッチングと酸化膜3のエッチングと半導体基板1の深さ150nmの溝16のエッチングを行う。その後、レジストマスクをアッシングにより除去する(図3)。

【0040】

その後、図4に示すように、半導体基板1に形成した溝16の内壁に対して5nm分の酸化を行って酸化膜3’を形成し、その後ハードマスク4をウエットエッチングで除去する(図4)。

【0041】

続いて酸化膜3、3’をウエットエッチングし、その後、溝16の内壁を含む全面にHigh-K(高誘電率)材料を含む絶縁膜(High-K絶縁膜5)(ゲート絶縁膜)の成長を2.5nm厚で行う。High-K材料は、例えばHfO、HfSiOである(図5)。

【0042】

その後、図6に示すように、スパッタ法によるPVD(Physical Vapor Deposition)により、第1のメタル材料(A)6を成膜する。第1のメタル材料(A)の材料はTiN、Ti、Wなどである。TiNは、TiとNの比率を変えることが出来る。第1のメタル材料(A)6の膜厚は、例えば10nmとする。ここで、スパッタ法は指向性が強いので、第1のメタル材料(A)6は半導体基板1の表面と、溝16の底面に形成されるが、溝16の側壁には形成されない。

【0043】

その後、図7に示すように、溝16を埋めるように第1のメタル材料(A)6上に、第2のメタル材料(B)7をCVD(Chemical Vapor Deposition)で成膜する。第2のメタル材料(B)7の材料はTiN、Ti、Wなどである。第2のメタル材料(B)7の成膜の膜厚は、例えば25nmである。

【0044】

その後、図8に示すように、第2のメタル材料(B)7上にa-Si(非晶質シリコン)8を30nm厚で成膜し、Pイオンの注入を全面に行う(a-Si 8の代わりにPがin-situドープされたポリシリコン膜でも良い)。その後、a-Si8上にさらにメタル材料20を成膜する。メタル材料20は30nm厚で成膜する。メタル材料20の例としては、WSi、W、Ti、TiNを含むもので良い。その後、レジストを塗布し、リソグラフィーでパターニングをする。9はレジストパターンを示す。

【0045】

その後、レジストパターン9をマスクとしてエッチング加工を行い、プレーナ型トランジスタと3次元トランジスタのゲート形状を形成する。続いてレジストをアッシングにより除去する。その後、レジスト塗布工程と、リソグラフィー工程と、イオン注入工程と、剥離工程を複数行い、更にソース、ドレインとなるべき領域にイオン注入を行ってソース12S(ドレイン12D)の形成を行ない、プレーナ型トランジスタ100、3次元トランジスタ200を形成する。その後、層間絶縁膜10を堆積形成した後、CMP(Chemical Mechanical Polishing)で平坦化を行い、更にソース12S、ドレイン12Dのそれぞれに至るコンタクト11の形成を行う(図9)。

【0046】

以上のようにして、プレーナ型トランジスタ100においては半導体基板1の表面に第1のメタル材料(A)6と第2のメタル材料(B)7の積層によるゲート電極が形成され、3次元トランジスタ200においては溝内に第1のメタル材料(A)6と第2のメタル材料(B)7の積層による埋め込みゲート電極が形成される。

【0047】

なお、図8から図9までの加工は公知の方法で行うことが出来る。

【0048】

さらにシリンダ加工工程や、コンタクト11に接続するための上部配線15、コンタクト等を形成する工程を行い、プレーナ型トランジスタ100と3次元トランジスタ200を含む半導体デバイスを形成する(図10)。

【0049】

上記実施例の説明を要約すると以下の通りである。

【0050】

本実施例では、以下に概略される製造工程を経て、2種類のトランジスタのゲート電極を同時に形成することにより各々のトランジスタの閾値電圧を変化させることができるようにしている。

【0051】

半導体基板の第1の領域に溝(トレンチ)を形成した後、基板表面全面にHigh-K(高誘電率)ゲート絶縁膜を形成する。

【0052】

次いで、スパッタ(PVD)法により第1のメタル材料(A)を全面に形成する。スパッタ法は指向性が強いので第1のメタル材料(A)は基板表面と溝の底面に形成されるが、溝の側壁には形成されない。

【0053】

次いで、CVD法により、溝を埋設するように、全面に第2のメタル材料(B)を形成する。

【0054】

さらに、マスクとなる非晶質Si(a-Si)を全面に形成し、リソグラフィーとドライエッチング法により非晶質Si,第2のメタル材料(B)、第1のメタル材料(A)を順次エッチングし、半導体基板表面にプレーナ型トランジスタのゲート電極を、溝内に第1のメタル材料(A)と第2のメタル材料(B)が積層された埋め込みゲート電極を形成する。

【0055】

ここで、第1のメタル材料(A)の仕事関数が第2のメタル材料(B)の仕事関数よりも小さい材料を選択すれば、プレーナ型トランジスタの閾値電圧Vtpは第1のメタル材料(A)の仕事関数で律則され、3次元トランジスタ(埋め込みゲート型トランジスタ)では側壁部に形成されている、仕事関数が相対的に大きい第2のメタル材料(B)の仕事関数で閾値電圧Vttを律則させることができる。

【0056】

逆に、第1のメタル材料(A)の仕事関数が第2のメタル材料(B)の仕事関数よりも大きい場合、いずれのトランジスタの閾値電圧も第1のメタル材料(A)で律則されることとなる。しかし、この場合には、図11(後述する)に示されているように、溝底の半導体基板表面に予め高濃度不純物層を形成しておき、底面部分はトランジスタ動作しない構成としておく。これにより、3次元トランジスタにおける第1のメタル材料(A)の寄与はなくなるので、プレーナ型トランジスタの閾値電圧Vtpは第1のメタル材料(A)、3次元トランジスタの閾値電圧Vttは第2のメタル材料(B)で律則される状態をつくることができる。

【0057】

また、ゲート電極を、例えばTiNなどの2元系で構成すれば、TiとNの含有比を変えることによっても仕事関数の制御が可能であり、これをスパッタ法、もしくはCVD法で組成を変えて成膜すれば、上記の閾値電圧制御ができる。あるいは、TiNに他の金属を含有させた場合とさせない場合とで仕事関数を変化させることもできる。

【0058】

いずれにしても、上記実施例をメモリチップに適用する場合には、3次元トランジスタ200はメモリセル部に使用し、プレーナ型トランジスタ100を周辺回路用のトランジスタとして使用することができる。

【0059】

[別の実施例]

上記実施例に代わる別の実施例として、図11に示すように、3次元トランジスタ200の埋め込みゲート電極からみて、High-K絶縁膜(ゲート絶縁膜)5をはさんで下側の半導体基板1にイオン注入により拡散層12S(D)’を形成するようにしたものでも良い。

【0060】

[別の実施例の製造方法]

この別の実施例は、図3の工程において溝16を形成した後、ソース領域、ドレイン領域形成のためのイオン注入と同じ型の拡散層となるようにイオン注入を行う。その他の製造方法は、上記の(製法(プロセス等)の説明)と同様のプロセスで良い。図11は、図9と対応する図である。

【0061】

以上、本発明を、複数の実施例を参照して説明したが、本発明は上記実施例に限定されるものではない。本発明の構成や詳細には、請求項に記載された本発明の精神や範囲内で当業者が理解し得る様々な変更をすることができる。

【符号の説明】

【0062】

1 半導体基板

2 STI

3、3’ 酸化膜

4 ハードマスク

5 High-K絶縁膜

6 第1のメタル材料(A)

7 第2のメタル材料(B)

8 a-Si

9 レジストパターン

16 溝

【特許請求の範囲】

【請求項1】

半導体基板に形成されたプレーナ型トランジスタと3次元トランジスタを含む半導体装置において、

前記プレーナ型トランジスタ、前記3次元トランジスタはともに高誘電率材料によるゲート絶縁膜を有し、

前記プレーナ型トランジスタは、前記ゲート絶縁膜上に、下側が第1のメタル材料(A)、上側が第2のメタル材料(B)からなるゲート電極を有し、

前記3次元トランジスタは埋め込みゲート電極を有し、該埋め込みゲート電極の下側のほうに前記第1のメタル材料(A)と同一の材料が、該埋め込みゲート電極の上側のほうに前記第2のメタル材料(B)と同一の材料がそれぞれ使用されていることを特徴とする半導体装置。

【請求項2】

請求項1に記載の半導体装置において、前記3次元トランジスタはメモリセル部を構成し、前記プレーナ型トランジスタは周辺トランジスタを構成することを特徴とする半導体装置。

【請求項3】

請求項1又は2に記載の半導体装置において、前記3次元トランジスタは、前記埋め込みゲート電極からみて、前記ゲート絶縁膜をはさんで下側となる前記半導体基板に形成された拡散層を有することを特徴とする半導体装置。

【請求項4】

請求項1〜3のいずれか1項に記載の半導体装置において、前記第1のメタル材料(A)と前記第2のメタル材料(B)は、仕事関数が異なる材料であることを特徴とする半導体装置。

【請求項5】

半導体基板にプレーナ型トランジスタと3次元トランジスタを形成する半導体装置の製造方法において、

前記プレーナ型トランジスタのゲート絶縁膜と前記3次元トランジスタのゲート絶縁膜を高誘電率材料により同時に成膜し、

前記プレーナ型トランジスタの前記ゲート絶縁膜上でメタルゲート電極の下側のほうを構成する第1のメタル材料(A)と、前記3次元トランジスタの前記ゲート絶縁膜上で埋め込みゲート電極の下側のほうを構成するメタル材料を同時に成膜することを特徴とする半導体装置の製造方法。

【請求項6】

請求項5に記載の半導体装置の製造方法において、さらに前記プレーナ型トランジスタの前記第1のメタル材料(A)の上で前記メタルゲート電極の上側のほうを構成する第2のメタル材料(B)と、前記3次元トランジスタの前記埋め込みゲート電極の上側のほうを構成するメタル材料を同時に成膜することを特徴とする半導体装置の製造方法。

【請求項7】

請求項5又は6に記載の半導体装置の製造方法において、前記第1のメタル材料(A)と前記3次元トランジスタの前記埋め込みゲート電極の下側のほうを構成するメタル材料の同時成膜はスパッタ法で行なわれ、前記第2のメタル材料(B)と前記3次元トランジスタの前記埋め込みゲート電極の上側のほうを構成するメタル材料の同時成膜はCVD法により行なわれることを特徴とする半導体装置の製造方法。

【請求項8】

請求項5〜7のいずれか1項に記載の半導体装置の製造方法において、前記ゲート絶縁膜の形成後であって、前記第1のメタル材料(A)と前記3次元トランジスタの前記埋め込みゲート電極の下側のほうを構成するメタル材料の同時成膜の前に、前記3次元トランジスタの前記埋め込みゲート電極となるべき箇所からみて、前記ゲート絶縁膜をはさんで下側となる前記半導体基板に拡散層を形成する工程を有することを特徴とする半導体装置の製造方法。

【請求項9】

請求項5〜8のいずれか1項に記載の半導体装置の製造方法において、前記第1のメタル材料(A)と前記第2のメタル材料(B)は、仕事関数が異なる材料であることを特徴とする半導体装置の製造方法。

【請求項1】

半導体基板に形成されたプレーナ型トランジスタと3次元トランジスタを含む半導体装置において、

前記プレーナ型トランジスタ、前記3次元トランジスタはともに高誘電率材料によるゲート絶縁膜を有し、

前記プレーナ型トランジスタは、前記ゲート絶縁膜上に、下側が第1のメタル材料(A)、上側が第2のメタル材料(B)からなるゲート電極を有し、

前記3次元トランジスタは埋め込みゲート電極を有し、該埋め込みゲート電極の下側のほうに前記第1のメタル材料(A)と同一の材料が、該埋め込みゲート電極の上側のほうに前記第2のメタル材料(B)と同一の材料がそれぞれ使用されていることを特徴とする半導体装置。

【請求項2】

請求項1に記載の半導体装置において、前記3次元トランジスタはメモリセル部を構成し、前記プレーナ型トランジスタは周辺トランジスタを構成することを特徴とする半導体装置。

【請求項3】

請求項1又は2に記載の半導体装置において、前記3次元トランジスタは、前記埋め込みゲート電極からみて、前記ゲート絶縁膜をはさんで下側となる前記半導体基板に形成された拡散層を有することを特徴とする半導体装置。

【請求項4】

請求項1〜3のいずれか1項に記載の半導体装置において、前記第1のメタル材料(A)と前記第2のメタル材料(B)は、仕事関数が異なる材料であることを特徴とする半導体装置。

【請求項5】

半導体基板にプレーナ型トランジスタと3次元トランジスタを形成する半導体装置の製造方法において、

前記プレーナ型トランジスタのゲート絶縁膜と前記3次元トランジスタのゲート絶縁膜を高誘電率材料により同時に成膜し、

前記プレーナ型トランジスタの前記ゲート絶縁膜上でメタルゲート電極の下側のほうを構成する第1のメタル材料(A)と、前記3次元トランジスタの前記ゲート絶縁膜上で埋め込みゲート電極の下側のほうを構成するメタル材料を同時に成膜することを特徴とする半導体装置の製造方法。

【請求項6】

請求項5に記載の半導体装置の製造方法において、さらに前記プレーナ型トランジスタの前記第1のメタル材料(A)の上で前記メタルゲート電極の上側のほうを構成する第2のメタル材料(B)と、前記3次元トランジスタの前記埋め込みゲート電極の上側のほうを構成するメタル材料を同時に成膜することを特徴とする半導体装置の製造方法。

【請求項7】

請求項5又は6に記載の半導体装置の製造方法において、前記第1のメタル材料(A)と前記3次元トランジスタの前記埋め込みゲート電極の下側のほうを構成するメタル材料の同時成膜はスパッタ法で行なわれ、前記第2のメタル材料(B)と前記3次元トランジスタの前記埋め込みゲート電極の上側のほうを構成するメタル材料の同時成膜はCVD法により行なわれることを特徴とする半導体装置の製造方法。

【請求項8】

請求項5〜7のいずれか1項に記載の半導体装置の製造方法において、前記ゲート絶縁膜の形成後であって、前記第1のメタル材料(A)と前記3次元トランジスタの前記埋め込みゲート電極の下側のほうを構成するメタル材料の同時成膜の前に、前記3次元トランジスタの前記埋め込みゲート電極となるべき箇所からみて、前記ゲート絶縁膜をはさんで下側となる前記半導体基板に拡散層を形成する工程を有することを特徴とする半導体装置の製造方法。

【請求項9】

請求項5〜8のいずれか1項に記載の半導体装置の製造方法において、前記第1のメタル材料(A)と前記第2のメタル材料(B)は、仕事関数が異なる材料であることを特徴とする半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【公開番号】特開2013−74143(P2013−74143A)

【公開日】平成25年4月22日(2013.4.22)

【国際特許分類】

【出願番号】特願2011−212432(P2011−212432)

【出願日】平成23年9月28日(2011.9.28)

【出願人】(500174247)エルピーダメモリ株式会社 (2,599)

【Fターム(参考)】

【公開日】平成25年4月22日(2013.4.22)

【国際特許分類】

【出願日】平成23年9月28日(2011.9.28)

【出願人】(500174247)エルピーダメモリ株式会社 (2,599)

【Fターム(参考)】

[ Back to top ]