半導体装置およびその製造方法

【課題】ソース−ドレイン間の耐圧を十分保持しながら、ゲートトレンチを浅くしてゲート電極とドレイン領域との対向面積を小さくし、ゲート−ドレイン間の容量を下げることができる半導体装置およびその製造方法を提供すること。

【解決手段】トレンチゲート型MOSトランジスタ1のチャネル領域14に、ゲートトレンチ3の側面11に沿って形成され、動作時にチャネルが形成されるチャネル部23と、Siエピタキシャル層8の裏面10側のチャネル部23の端部に対して当該裏面10側に突出した凸部24とを形成する。

【解決手段】トレンチゲート型MOSトランジスタ1のチャネル領域14に、ゲートトレンチ3の側面11に沿って形成され、動作時にチャネルが形成されるチャネル部23と、Siエピタキシャル層8の裏面10側のチャネル部23の端部に対して当該裏面10側に突出した凸部24とを形成する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、トレンチゲート型MOSFETを備える半導体装置およびその製造方法に関する。

【背景技術】

【0002】

トレンチゲート型MOSFETの一例として、たとえば、特許文献1の半導体装置は、ゲートトレンチが形成されたn−型第1ベース層と、ゲートトレンチの内面に形成されたゲート絶縁膜と、ゲート絶縁膜の内側に充填されたゲート電極と、ゲート電極を被覆するように形成された層間絶縁膜と、n−型第1ベース層の表面に形成され、ゲートトレンチの底面よりも浅く形成されたp型第2ベース層と、p型第2ベース層の表面に形成されたn+型ソース層と、n+型ソース層を貫通し、p型第2ベース層内まで形成されたセルフアラインコンタクト溝と、セルフアラインコンタクト溝の底面においてp型第2ベース層に接続され、セルフアラインコンタクト溝の側面において、n+型ソース層に接続されたソース電極と、n−型第1ベース層の裏面に形成されたn+型ドレイン層と、n+型ドレン層上に形成されたドレイン電極とを備えている。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2010−62477号公報

【特許文献2】特開2010−021176号公報

【発明の概要】

【課題を解決するための手段】

【0004】

本発明の半導体装置は、ゲートトレンチが形成された半導体層と、前記半導体層の表面側に露出するように形成され、前記ゲートトレンチの側面の一部を形成する第1導電型のソース領域と、前記ソース領域に対して前記半導体層の裏面側に前記ソース領域に接するように形成され、前記ゲートトレンチの前記側面の一部を形成する第2導電型のチャネル領域と、前記チャネル領域に対して前記半導体層の前記裏面側に前記チャネル領域に接するように形成され、前記ゲートトレンチの底面を形成する第1導電型のドレイン領域と、前記ゲートトレンチの内面に形成されたゲート絶縁膜と、前記ゲートトレンチにおいて前記ゲート絶縁膜の内側に埋め込まれたゲート電極とを含み、前記チャネル領域は、前記ゲートトレンチの前記側面に沿って形成され、動作時にチャネルが形成されるチャネル部と、前記半導体層の前記裏面側の前記チャネル部の端部に対して当該裏面側に突出した凸部とを含む。

【0005】

この構成によれば、チャネル領域の一部が、動作時にチャネルが形成される部分(チャネル部)とは異なる箇所において半導体層の裏面側に凸部として突出している。これにより、半導体層の表面からチャネル領域とドレイン領域との界面(pn接合界面)までの深さが一定である従来の構造に比べて、pn接合界面の面積を、半導体装置のチャネル特性に影響を与えずに大きくすることができる。そのため、当該pn接合から広がる空乏層の面積も大きくなるので、当該空乏層は大きな面積で電圧を受けることになる。その結果、空乏層の単位面積あたりで受ける電圧を低減することができる。

【0006】

したがって、チャネル領域とドレイン領域との界面に対して半導体層の裏面側へのゲートトレンチの突出量が小さく(ゲートトレンチが浅く)、ゲート絶縁膜とドレイン領域との小さな面積の界面から広がる空乏層だけでは耐圧を確保できない場合でも、チャネル領域の凸部付近に大きな面積の空乏層が存在するので、半導体装置全体としての耐圧を向上させることができる。

【0007】

よって、ソース−ドレイン間の耐圧を十分保持しながら、ゲートトレンチを浅くしてゲート電極とドレイン領域との対向面積を小さくし、ゲート−ドレイン間の容量を下げることができる。

また、前記半導体装置は、前記半導体層の前記表面から前記ソース領域を貫通し、最深部が前記チャネル領域に達するコンタクトトレンチと、前記コンタクトトレンチの底面に形成された第2導電型のチャネルコンタクト領域とをさらに含み、前記凸部は、前記チャネルコンタクト領域の直下に形成されていることが好ましい。

【0008】

このような構成の半導体装置は、たとえば、表面側に露出するように形成された第1導電型のソース領域、前記ソース領域に対して裏面側に前記ソース領域に接するように形成された第2導電型のチャネル領域、および前記チャネル領域に対して前記裏面側に前記チャネル領域に接するように形成された第1導電型のドレイン領域を有する半導体層に、前記ソース領域および前記チャネル領域を貫通し、最深部が前記ドレイン領域に達するゲートトレンチを形成する工程と、前記ゲートトレンチの内面にゲート絶縁膜を形成する工程と、前記ゲート絶縁膜の内側に電極材料を埋め込むことにより、ゲート電極を形成する工程と、前記半導体層に、前記ソース領域を貫通し、最深部が前記チャネル領域に達するコンタクトトレンチを形成する工程と、前記コンタクトトレンチの底面を通って、前記チャネル領域と前記ドレイン領域との界面近傍に達するように第2導電型イオンを注入することにより、前記コンタクトトレンチの直下に、前記ゲートトレンチの前記側面に沿って形成された前記チャネル領域のチャネル部の前記半導体層の前記裏面側の端部に対して当該裏面側に突出した凸部を形成する工程と、前記半導体層の前記コンタクトトレンチの前記底面近傍に第2導電型イオンを注入することにより、前記チャネル領域にチャネルコンタクト領域を形成する工程とを含む、本発明の半導体装置の製造方法により製造することができる。

【0009】

この方法によれば、従来のイオン注入(イオンインプランテーション)技術を利用して、半導体層の表面に対して1段低くなったコンタクトトレンチの底面へ向かって第2導電型イオンを入射させることにより、チャネル領域に凸部を簡単に形成することができる。なお、半導体層の材料の種類に応じて、第2導電型イオンの注入後にアニール処理を行って、第2導電型イオンを半導体層中に拡散させてもよい。このような拡散は、チャネルコンタクト領域を形成する際も、同様に行うことができる。

【0010】

また、形成される凸部は、半導体層の裏面側へ向かってチャネルコンタクト領域から離れる方向へ突出しているので、凸部とドレイン領域との界面から広がる空乏層とチャネルコンタクト領域との接触を防止することができる。したがって、両者の接触に起因する耐圧の低下を回避することができる。

この場合、前記チャネルコンタクト領域の直下の前記凸部の頂部は、前記コンタクトトレンチの前記底面の幅方向中央部の下方位置に沿って形成されていてもよい。

【0011】

このような構成の半導体装置は、たとえば、本発明の半導体装置の製造方法において、前記コンタクトトレンチの前記底面に対して垂直に前記第2導電型イオンを垂直注入する工程を実行することにより製造することができる。

この方法によれば、第2導電型イオンの注入の際に精密な角度調整をせずに済み、しかも、注入角度の切換えが必要なく、第2導電型イオンを常時垂直に注入しておけばよいので、より簡単に凸部を形成することができる。

【0012】

一方、前記チャネルコンタクト領域の直下の前記凸部の頂部は、前記コンタクトトレンチの前記底面の幅方向端部の下方位置に沿って形成されていてもよい。

このような構成の半導体装置は、たとえば、本発明の半導体装置の製造方法において、前記コンタクトトレンチの前記底面に対して傾斜する注入角度で前記第2導電型イオンを斜め注入する工程を実行することにより製造することができる。

【0013】

凸部の頂部は、コンタクトトレンチの底面の幅方向端部の下方位置に沿って形成される場合、特に、当該底面の幅方向両端部の下方位置に沿って互いに平行に形成された複数の頂部であることが好ましい。つまり、凸部が、単一の頂部(ピーク)ではなく、複数の頂部(ピーク)を持つように突出していることが好ましい。

このような構成の半導体装置は、第2導電型イオンを斜め注入する際に、前記コンタクトトレンチの前記底面の幅方向一端部へ向けて前記第2導電型イオンを注入する第1工程と、前記コンタクトトレンチの前記底面の幅方向他端部へ向けて、前記第1工程における前記第2導電型イオンの入射方向と交差する方向に第2導電型イオンを注入する第2工程とを実行することにより製造することができる。

【0014】

この方法によれば、第1工程から第2工程への移行時に、第2導電型イオンの注入角度の切換えが必要であるが、凸部が複数の頂部(ピーク)を持つので、凸部とドレイン領域との界面の面積を一層大きくすることができる。その結果、空乏層の単位面積あたりで受ける電圧を一層低減することができる。

また、本発明の半導体装置では、前記凸部の頂部は、前記ゲートトレンチの前記底面に対して前記半導体層の前記裏面側に位置していることが好ましく、前記凸部の不純物濃度は、前記チャネルコンタクト領域の濃度の1/100以下であることが好ましい。凸部の不純物濃度が上記条件を満たすことにより、耐圧をさらに向上させることができる。

【0015】

また、前記半導体層は、Si半導体層からなっていてもよい。

また、本発明の半導体装置の製造方法では、前記凸部を形成する工程は、前記コンタクトトレンチの前記底面から所定の深さの位置に前記第2導電型イオンを注入する1段注入工程を含んでいてもよいし、注入エネルギを変化させることにより、前記コンタクトトレンチの前記底面から所定の深さまで前記第2導電型イオンを複数段にわたって注入する多段注入工程を含んでいてもよい。

【0016】

さらに、1段注入工程では、前記チャネル領域と前記ドレイン領域との前記界面に対して前記半導体層の前記表面側および前記裏面側のどちらの深さ位置に前記第2導電型イオンを注入してもよい。

また、多段注入工程では、第2導電型イオンの注入深さのいくつかが前記半導体層の前記表面側となり、残りが前記裏面側となるように、複数段の注入部分により画成される領域が、前記チャネル領域と前記ドレイン領域との前記界面に対して前記半導体層の前記表面側および前記裏面側に跨るように第2導電型イオンを注入してもよい。また、全ての第2導電型イオンの注入深さが、前記チャネル領域と前記ドレイン領域との界面に対して前記半導体層の前記表面側もしくは前記裏面側となるように、第2導電型イオンを注入してもよい。

【0017】

このように、1段および多段といったイオンの注入方式や、イオンの注入深さを選択することにより、様々な形状の凸部を形成することができる。したがって、ゲートトレンチの形状・深さや、ソース領域、チャネル領域などの不純物領域の形状・大きさに応じて適切な形状の凸部を形成することができる。

【図面の簡単な説明】

【0018】

【図1】図1は、本発明の一実施形態に係るトレンチゲート型MOSトランジスタの模式的な平面図である。

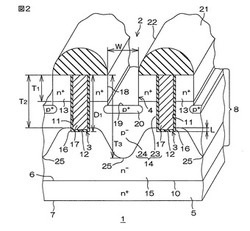

【図2】図2は、図1のトレンチゲート型MOSトランジスタの鳥瞰断面図であって、図1の切断線II−IIでの切断面を示す。

【図3A】図3Aは、図2のトレンチゲート型MOSトランジスタの製造工程の一部を示す図である。

【図3B】図3Bは、図3Aの次の工程を示す図である。

【図3C】図3Cは、図3Bの次の工程を示す図である。

【図3D】図3Dは、図3Cの次の工程を示す図である。

【図3E】図3Eは、図3Dの次の工程を示す図である。

【図3F】図3Fは、図3Eの次の工程を示す図である。

【図3G】図3Gは、図3Fの次の工程を示す図である。

【図3H】図3Hは、図3Gの次の工程を示す図である。

【図3I】図3Iは、図3Hの次の工程を示す図である。

【図3J】図3Jは、図3Iの次の工程を示す図である。

【図4】図4(a)〜(d)は、図3Gのイオン注入方式の変形例を示す図であって、図4(a)は1段注入、図4(b)〜(d)は多段注入の例をそれぞれ示す。

【図5】図5は、B11イオンのドーズ量とブレークダウン電圧との関係を示すグラフである。

【図6】図6は、図1のトレンチゲート型MOSトランジスタの凸部の変形例を示す図である。

【図7】図7は、図6の凸部を形成するときのイオン注入方法を説明するための図である。

【図8】図8は、図1のトレンチゲート型MOSトランジスタの単位セルの配置形態の第1変形例を示す図である。

【図9】図9は、図1のトレンチゲート型MOSトランジスタの単位セルの配置形態の第2変形例を示す図である。

【図10】図10は、参考例の一実施形態に係るMOSトランジスタの模式的な平面図である。

【図11】図11は、図10のMOSトランジスタの鳥瞰断面図であって、図10の切断線XI−XIでの切断面を示す。

【図12A】図12Aは、図11のMOSトランジスタの製造工程の一部を示す図である。

【図12B】図12Bは、図12Aの次の工程を示す図である。

【図12C】図12Cは、図12Bの次の工程を示す図である。

【図12D】図12Dは、図12Cの次の工程を示す図である。

【図12E】図12Eは、図12Dの次の工程を示す図である。

【図12F】図12Fは、図12Eの次の工程を示す図である。

【図12G】図12Gは、図12Fの次の工程を示す図である。

【図12H】図12Hは、図12Gの次の工程を示す図である。

【図13】図13(a)(b)は、図11のMOSトランジスタのオン時およびオフ時の状態を示す図であって、図13(a)はオン時、図13(b)はオフ時をそれぞれ示す。

【図14】図14は、図10のMOSトランジスタの単位セルの配置形態の第1変形例を示す図である。

【図15】図15は、図10のMOSトランジスタの単位セルの配置形態の第2変形例を示す図である。

【発明を実施するための形態】

【0019】

以下では、本発明の実施の形態を、添付図面を参照して詳細に説明する。

図1は、本発明の一実施形態に係るトレンチゲート型MOSトランジスタの模式的な平面図である。図2は、図1のトレンチゲート型MOSトランジスタの鳥瞰断面図であって、図1の切断線II−IIでの切断面を示す。

図1を参照して、半導体装置としてのMOSトランジスタ1は、トレンチゲート型MOSFET(Metal Oxide Semiconductor Field Effect Transistor)であり、互いに平行に配列されたストライプ状の単位セル2を複数備えている。各単位セル2は、ストライプ状のゲートトレンチ3により区画されており、隣り合うゲートトレンチ3の間隔(トレンチのピッチP)は、たとえば、0.9μm〜1.5μmである。また、単位セル2には、その長手方向一端から他端向かって延びる長尺(平面視長方形)なコンタクトトレンチ4が、各単位セル2に1つずつ形成されている。

【0020】

次に、図2を参照して、MOSトランジスタ1は、n+型(たとえば、濃度が1×1019〜5×1019cm−3)のSi基板5を備えている。Si基板5は、MOSトランジスタ1のドレインとして機能する。n型不純物としては、リン(P)、ヒ素(As)などが含まれている。以下同じ。

Si基板5の表面6(上面)には、Si基板5よりも低濃度のn−型(たとえば、濃度が1×1016〜1×1015cm−3)のSiエピタキシャル層8が積層されている。

半導体層としてのSiエピタキシャル層8の厚さは、たとえば、3μm〜10μmである。

【0021】

Siエピタキシャル層8には、その表面9からSi基板5へ向かって掘り下がった、側面11および底面12を有するゲートトレンチ3がストライプ状に形成されている。これにより、Siエピタキシャル層8には、ストライプ状のゲートトレンチ3の側面11により区画されたストライプ状の単位セル2が複数本形成されている。

Siエピタキシャル層8の表面9から測定されるゲートトレンチ3の深さD1は、たとえば、1.0μm〜1.5μmであり、具体的には、1.0μmである。

【0022】

Siエピタキシャル層8においてゲートトレンチ3の周囲には、n+型のソース領域13およびp−型(たとえば、濃度が1×1017〜5×1017cm−3)のチャネル領域14が、Siエピタキシャル層8の表面9に近い側からこの順に形成されている。チャネル領域14には、p型不純物として、たとえば、ボロン(B)、アルミニウム(Al)などが含まれている。以下同じ。

【0023】

ソース領域13は、Siエピタキシャル層8の表面9に露出するとともに、ゲートトレンチ3の側面11の上部(一部)を形成するように、各単位セル2の表層部に形成されている。表面9からSi基板5へ向かう方向に沿うソース領域13の厚さT1は、たとえば、0.2μm〜0.4μmである。なお、以下の説明で厚さを定義する場合には、特に断りのない限り、Siエピタキシャル層8の表面9からSi基板5へ向かう方向に沿った厚さのことをいう。

【0024】

チャネル領域14は、ソース領域13に対してSi基板5側(Siエピタキシャル層8の裏面10側)にソース領域13に接するように、かつ、ゲートトレンチ3の側面11の下部(一部)を形成するように形成されている。

一方、Siエピタキシャル層8における、チャネル領域14に対してSi基板5側の領域は、エピタキシャル成長後のままの状態が維持された、n−型のドレイン領域15となっている。ドレイン領域15は、チャネル領域14に対してSi基板5側にチャネル領域14に接しており、ゲートトレンチ3の底面12を形成している。

【0025】

ゲートトレンチ3の内面には、その全域を覆うように、ゲート絶縁膜16が形成されている。そして、ゲートトレンチ3において、n型不純物が高濃度にドーピングされたポリシリコンをゲート絶縁膜16の内側に埋め込むことにより、ゲートトレンチ3内にゲート電極17が埋設されている。こうして、ソース領域13とドレイン領域15とが、Siエピタキシャル層8の表面9に垂直な縦方向にチャネル領域14を介して離間して配置された、縦型MOSトランジスタ1構造が構成されている。

【0026】

各単位セル2には、Siエピタキシャル層8の表面9からソース領域13を貫通し、最深部がチャネル領域14に達するコンタクトトレンチ4が形成されている。コンタクトトレンチ4の開口幅Wは、その深さ方向において一定であり、たとえば、0.2μm〜0.5μmである。コンタクトトレンチ4の側面18にはソース領域13が露出し、コンタクトトレンチ4の底面19にはチャネル領域14が露出している。

【0027】

そして、コンタクトトレンチ4の底面19に露出したチャネル領域14には、p+型(たとえば、濃度が1×1019〜1×1020cm−3)のチャネルコンタクト領域20が形成されている。チャネルコンタクト領域20は、コンタクトトレンチ4の長手方向に沿って、コンタクトトレンチ4の底面19全面に直線状に形成されている。

Siエピタキシャル層8上には、層間絶縁膜21が形成されている。層間絶縁膜21には、コンタクトトレンチ4を露出させるコンタクトホール22が形成されている。

【0028】

なお、図示は省略するが、層間絶縁膜21上には、ソース電極が形成されており、このソース電極は、各コンタクトトレンチ4を介して、すべての単位セル2(ソース領域13およびチャネルコンタクト領域20)に一括して接している。すなわち、ソース電極は、すべての単位セル2に対して共通の配線となっている。また、Si基板5の裏面7には、その全域を覆うようにドレイン電極が形成されている。このドレイン電極は、すべての単位セル2に対して共通の電極となっている。

【0029】

そして、この実施形態では、各単位セル2において、チャネル領域14のコンタクトトレンチ4の直下の部分が、チャネルコンタクト領域20から離れる方向に断面視山状に突出(隆起)している。

具体的には、チャネル領域14は、MOSトランジスタ1の動作時にチャネルが形成されるチャネル領域14のチャネル部23付近を両端とし、当該両端からコンタクトトレンチ4の底面19の幅方向中央部の下方位置に1つのピーク(頂部25)がくるように描かれる放物線状に突出している。これにより、チャネル領域14は、当該放物線で区画される部分として、Siエピタキシャル層8の裏面10側のチャネル部23の端部に対して当該裏面10側に突出した凸部24を有している。

【0030】

凸部24の頂部25(放物線のピーク)は、Si基板5に接触しない範囲内で、ゲートトレンチ3の底面12に対してSiエピタキシャル層8の裏面10側に位置しており(つまり、ゲートトレンチ3の底面12よりも深く)、コンタクトトレンチ4に沿って直線状に形成されている。また、凸部24の導電型は、チャネル領域14と同じp−型(たとえば、濃度が1×1017〜5×1017cm−3)であり、その不純物濃度は、p+型(たとえば、濃度が1×1019〜1×1020cm−3)のチャネルコンタクト領域20の1/100以下であることが好ましい。

【0031】

また、チャネル領域14において、チャネル部23の厚さT2は、たとえば、0.5μm〜0.9μmであり、具体的には、0.8μmである。また、凸部24の頂部25までの厚さT3は、たとえば、1.0μm〜1.6μmであり、具体的には、1.4μmである。

図3A〜図3Jは、図2のトレンチゲート型MOSトランジスタの製造工程の一部を示す図であって、図2と同じ位置での切断面を示す。

【0032】

MOSトランジスタ1を製造するには、図3Aに示すように、CVD(Chemical Vapor Deposition:化学気相成長)法、LPE(Liquid Phase Epitaxy:液相エピタキシ)法、MBE(Molecular Beam Epitaxy:分子線エピタキシ)法などのエピタキシャル成長法により、Si基板5の表面6上に、n型不純物をドーピングしながらSi結晶を成長させる。これにより、Si基板5上に、n−型のSiエピタキシャル層8(ドレイン領域15)が形成される。次に、Siエピタキシャル層8の表面9へ向け、p型不純物およびn型不純物を順に注入する。注入後、アニール処理(たとえば、900℃〜1000℃で、10分〜30分)することによって、注入された各不純物が活性化されて、チャネル領域14およびソース領域13が同時に形成される。次に、たとえば、CVD法により、Siエピタキシャル層8の表面9にSiO2膜26を形成し、当該SiO2膜26上にSiN膜27を形成することにより、SiO2膜26およびSiN膜27の2層膜からなるハードマスク28を形成する。SiO2膜26の厚さは、たとえば、50Å〜100Åとし、SiN膜27の厚さは、たとえば、1000Å〜1500Åとする。

【0033】

次に、図3Bに示すように、このハードマスク28を利用して、Siエピタキシャル層8をエッチングする。これにより、Siエピタキシャル層8が表面9からドライエッチングされてゲートトレンチ3が形成される。それとともに、Siエピタキシャル層8に複数の単位セル2が形成される。

次に、図3Cに示すように、たとえば、熱酸化法(たとえば、850℃〜950℃で、10分〜30分)により、ゲートトレンチ3の内面(側面11および底面12)にゲート絶縁膜16を形成する。

【0034】

次に、図3Dに示すように、たとえば、CVD法により、ドーピングされたポリシリコン(電極材料)を、Siエピタキシャル層8の上方から堆積する。ポリシリコンの堆積は、少なくともSiエピタキシャル層8の表面9が隠れるまで続ける。その後、堆積したポリシリコンを、エッチバック面がSiエピタキシャル層8の表面9に対して面一になるまでエッチバックする。これにより、ゲートトレンチ3内に残存するポリシリコンからなるゲート電極17が形成される。

【0035】

次に、図3Eに示すように、たとえば、CVD法により、SiO2(絶縁材料)を、Siエピタキシャル層8の上方から堆積して、層間絶縁膜21を形成する。

次に、図3Fに示すように、たとえば、ドライエッチングにより、層間絶縁膜21にコンタクトホール22を形成する。コンタクトホール22の形成後、層間絶縁膜21をマスクとして利用して、露出したSiエピタキシャル層8をエッチングする。これにより、Siエピタキシャル層8が表面9からドライエッチングされて、層間絶縁膜21に対して自己整合的にコンタクトトレンチ4が形成される。

【0036】

次に、図3Gに示すように、コンタクトトレンチ4の底面12に対して垂直な方向に、不純物(B11イオン)を入射させることにより、チャネル領域14とドレイン領域15との界面29に対してSiエピタキシャル層8の表面9側(チャネル領域14における界面29の近傍)の深さ位置に不純物を1段注入する。不純物イオンの注入エネルギは、たとえば、100keV〜140keVであり、好ましくは、140keV程度である。また、不純物イオンのドーズ量は、たとえば、4×1012cm−2〜1×1013cm−2であり、好ましくは、6×1012cm−2〜8×1012cm−2である。

【0037】

注入後、アニール処理(たとえば、900℃〜950℃で、0.5分〜1分)することによって、図3Hに示すように、注入されたp型不純物が拡散・活性化されて、チャネル領域14の凸部24が形成される。

次に、図3Iに示すように、コンタクトトレンチ4の底面12に対して垂直な方向に、40keV程度の注入エネルギおよび1×1015cm−2程度のドーズ量で不純物(BF2イオン)を入射させることにより、チャネル領域14における底面12の近傍の深さ位置に不純物を1段注入する。

【0038】

注入後、アニール処理(たとえば、900℃〜950℃で、0.5分〜1分)することによって、図3Jに示すように、注入されたp型不純物が拡散・活性化されて、チャネルコンタクト領域20が形成される。

その後は、ソース電極(図示せず)、ドレイン電極(図示せず)などを形成することにより、図2に示すMOSトランジスタ1が得られる。

【0039】

以上、この実施形態によれば、チャネル領域14の一部が、チャネル領域14のチャネル部23付近を両端とし、当該両端からコンタクトトレンチ4の底面19の幅方向中央部の下方位置に1つのピークがくるように描かれる放物線状に凸部24として突出している。これにより、Siエピタキシャル層8の表面9からチャネル領域14とドレイン領域15との界面(pn接合界面)までの深さが一定である従来の構造に比べて、pn接合界面の面積を、MOSトランジスタ1のチャネル特性に影響を与えずに大きくすることができる。つまり、チャネル部23の長さ(チャネル長)を変えずに、チャネル領域14のコンタクトトレンチ4の直下の部分だけを突出させているため、チャネル特性への影響がほとんどない。そのため、当該pn接合から広がる空乏層の面積も大きくなるので、当該空乏層は大きな面積で電圧を受けることになる。その結果、空乏層の単位面積あたりで受ける電圧を低減することができる。

【0040】

したがって、チャネル部23とドレイン領域15との界面に対してSiエピタキシャル層8の裏面10側へのゲートトレンチ3の突出量L(この実施形態では、たとえば、0.2μm〜0.1μm)が小さく(ゲートトレンチ3が浅く)、ゲート絶縁膜16とドレイン領域15との小さな面積の界面から広がる空乏層だけでは耐圧を確保できない場合でも、チャネル領域14の凸部24付近に大きな面積の空乏層が存在するので、MOSトランジスタ1全体としての耐圧を向上させることができる。

【0041】

よって、ソース−ドレイン間の耐圧を十分保持しながら、ゲートトレンチ3を浅くしてゲート電極17とドレイン領域15との対向面積を小さくし、ゲート−ドレイン間の容量を下げることができる。

しかも、チャネル領域14の凸部24は、チャネルコンタクト領域20から離れる方向へ突出しているので、凸部24とドレイン領域15との界面から広がる空乏層とチャネルコンタクト領域20との接触を防止することができる。したがって、両者の接触に起因する耐圧の低下を回避することができる。

【0042】

また、このような凸部24は、従来のイオン注入(イオンインプランテーション)技術を利用して、Siエピタキシャル層8の表面9に対して1段低くなったコンタクトトレンチ4の底面12へ向かって不純物イオンを入射させることにより簡単に形成することができる。さらに、コンタクトトレンチ4の底面12に対して垂直に不純物イオンを入射して凸部24を形成できるので、不純物イオンの注入の際に精密な角度調整をせずに済み、しかも、注入角度の切換えが必要ない。

【0043】

なお、凸部24を形成するためのイオン注入の方式や注入深さは、ゲートトレンチ3の形状・深さや、ソース領域13、チャネル領域14などの不純物領域の形状・大きさに応じて変化させることができる。

たとえば、図4(a)に示すように、チャネル領域14とドレイン領域15との界面29に対してSiエピタキシャル層8の裏面10側(ドレイン領域15における界面29の近傍)の深さ位置に不純物を1段注入することができる。

【0044】

また、図4(b)に示すように、80keV〜180keVの範囲で注入エネルギを変化させることにより、不純物イオン(B11イオン)の注入深さのいくつかがSiエピタキシャル層8の表面9側となり、残りが裏面10側となるように、注入部分により画成される領域が、界面29に対してSiエピタキシャル層8の表面9側および裏面10側に跨るように不純物イオンを複数段にわたって多段注入することもできる。

【0045】

さらに、多段注入を採用する場合、図4(c)に示すように、全ての不純物イオンの注入深さが、界面29に対してSiエピタキシャル層8の裏面10側となるように、不純物イオンを注入してもよいし、図4(d)に示すように、全ての不純物イオンの注入深さが、界面29に対してSiエピタキシャル層8の表面9側となるように、不純物イオンを注入してもよい。

【0046】

このように、1段および多段といったイオンの注入方式や、イオンの注入深さを選択することにより、様々な形状の凸部24を形成することができる。したがって、ゲートトレンチ3の形状・深さや、ソース領域13、チャネル領域14などの不純物領域の形状・大きさに応じて適切な形状の凸部24を形成することができる。

また、不純物(B11イオン)のドーズ量を4×1012cm−2〜1×1013cm−2の範囲にすることによって、ドレイン−ソース間のブレークダウン電圧を向上させることができる。具体的には、図5に示すように(注入エネルギ=140keV)、B11イオンのドーズ量が4×1012cm−2〜1×1013cm−2の範囲では、ブレークダウン電圧を36V以上にすることができた。

【0047】

また、凸部24の形状は、断面視において、1つの放物線で区画される形状である必要はなく、たとえば、2つの放物線で区画される形状であってもよい。

具体的には、図6のチャネル領域30の凸部31のように、チャネル部23付近を両端とし、当該両端からコンタクトトレンチ4の底面19の幅方向一端部および他端部の下方位置それぞれにピーク(頂部32)が1つずつくるように描かれる2つの放物線状に突出していることが好ましい。この場合、各凸部31の頂部32は、コンタクトトレンチ4に沿って互いに平行に直線状に並ぶことになる。また、一方の凸部31および他方の凸部31は、コンタクトトレンチ4の底面19の幅方向中央部を通る垂線を対称軸sとする線対称であることが好ましく、この対称軸s上にある逆側の頂部33は、ゲートトレンチ3の底面12に対してSiエピタキシャル層8の裏面10側に位置していることが好ましい(つまり、ゲートトレンチ3の底面12よりも深い位置にある)。

【0048】

そして、図6の凸部31は、たとえば、図3Gの工程に代えて、コンタクトトレンチ4の底面12に対して7°〜14°で傾斜する注入角度θ1で、コンタクトトレンチ4の幅方向一端部へ向けて不純物イオンを注入する第1工程と、コンタクトトレンチ4の底面12に対して7°〜14°で傾斜する注入角度θ2で、第1工程における不純物イオンの入射方向と交差するように、コンタクトトレンチ4の幅方向他端部へ向けて不純物イオンを注入する第2工程とを実行することにより形成することができる。

【0049】

この方法によれば、第1工程から第2工程への移行時に、不純物イオンの注入角度の切換え(θ1→θ2)が必要であるが、凸部31が複数の頂部32(ピーク)を持つので、凸部31とドレイン領域15との界面の面積を一層大きくすることができる。その結果、空乏層の単位面積あたりで受ける電圧を一層低減することができる。

以上、本発明の実施形態を説明したが、本発明は、他の形態で実施することもできる。

【0050】

たとえば、単位セル2の配置形態は、ストライプ状である必要はなく、図8に示すような行列状、図9に示すような千鳥状であってもよい。

また、各単位セル2の形状は、ストライプ状(図1)、四角柱状(図8,図9)に限らず、たとえば、三角柱状、五角柱状、六角柱状等の他の多角柱状であってもよい。

また、MOSトランジスタ1において、各半導体部分の導電型を反転した構成が採用されてもよい。たとえば、MOSトランジスタ1において、p型の部分がn型であり、n型の部分がp型であってもよい。

【0051】

また、Siエピタキシャル層8に代えて、たとえば、SiCエピタキシャル層を用いることもできる。

また、チャネル領域の凸部は、凸部24,31のようにコンタクトトレンチ4の直下にある必要はなく、MOSトランジスタ1のチャネル特性に影響を与えない範囲で様々な場所に形成することもできる。

【0052】

その他、特許請求の範囲に記載された事項の範囲で種々の設計変更を施すことが可能である。

<参考例に係る発明>

(参考例の背景技術)

MOSFETの一例として、たとえば、特許文献2の半導体装置が公知である。

【0053】

この半導体装置は、トレンチゲートを含むpチャネル型パワーMOSFET(metal-oxide-semiconductor field-effect transistor)とすることができる。半導体装置は、p+型のシリコン基板と、その上に形成されたp型半導体層と、さらにその上に形成されたn型のチャネル層とから構成される半導体基板を含む。

半導体装置は、さらに、チャネル層上の半導体基板の表面に形成されたn+型のボディ領域と、平面視でボディ領域の四方を囲むp+型のソース領域とを含む。また、半導体装置は、チャネル層を貫通し、p型半導体層にまで到達するゲートトレンチと、ゲートトレンチの側面に形成されたゲート酸化膜と、ゲートトレンチの底面に形成され、ゲート酸化膜よりも膜厚が厚い厚膜酸化膜と、ゲートトレンチ内でゲート酸化膜および厚膜酸化膜上に形成され、ゲートトレンチを埋め込むゲート電極とを含む。

【0054】

また、半導体装置は、半導体基板上に形成されたソース電極と、ゲート電極上に形成され、ゲート電極とソース電極とを絶縁する層間絶縁膜と、半導体基板のソース電極が形成された面とは反対側の裏面にシリコン基板に接して設けられたドレイン電極とを含む。

(参考例が解決しようとする課題)

特許文献2では、ゲートトレンチの外部に露出したポリシリコンをエッチバックにより除去してゲート電極を形成した後、半導体基板に選択的に不純物イオンを注入し、熱処理することによりソース領域を形成している。

【0055】

しかしながら、このような方法では、イオン注入によるソース領域の深さが設計値よりも深くなり、その直下のチャネル層の一部がソース領域に変質するおそれがある。この変質により、チャネル層が設計値よりも薄くなり、チャネル長が短くなるという不具合がある。

この理由は、エッチバックの加工精度が低いため、エッチバック後のゲート電極の上面(エッチバック面)が半導体基板の表面に対して窪んでいる場合が多い。そのため、半導体基板の表面に不純物イオンを注入する際に、不純物イオンの一部がゲート電極のエッチバック面付近に露出したゲートトレンチの側面からも半導体基板の内部に注入されるからである。

【0056】

参考例の目的は、チャネル長を設計通りに精密に制御することができる半導体装置およびその製造方法を提供することである。

また、参考例の他の目的は、高耐圧化および低オン抵抗化を両立させることができる半導体装置およびその製造方法を提供することである。

(参考例の実施形態)

以下では、参考例の実施の形態を、添付図面を参照して詳細に説明する。

【0057】

図10は、参考例の一実施形態に係るMOSトランジスタの模式的な平面図である。図11は、図10のMOSトランジスタの鳥瞰断面図であって、図10の切断線XI−XIでの切断面を示す。

図10を参照して、半導体装置としてのMOSトランジスタ41は、互いに平行に配列されたストライプ状の単位セル42を複数備えている。各単位セル42は、ストライプ状のゲートトレンチ43により区画されており、隣り合うゲートトレンチ43の間隔(トレンチのピッチP)は、たとえば、0.9μm〜1.5μmである。また、単位セル42には、その長手方向一端から他端向かって延びる長尺(平面視長方形)なコンタクトトレンチ44が、各単位セル42に1つずつ形成されている。

【0058】

次に、図11を参照して、MOSトランジスタ41は、n+型(たとえば、濃度が1×1019〜5×1019cm−3)のSiからなる半導体層としての基板45を備えている。基板45は、MOSトランジスタ41のドレインとして機能する。n型不純物としては、リン(P)、ヒ素(As)などが含まれている。以下同じ。

基板45の表面46(上面)には、基板45よりも低濃度のn−型(たとえば、濃度が1×1016〜1×1015cm−3)のSiからなるエピタキシャル層48が積層されている。半導体層としてのエピタキシャル層48の厚さは、たとえば、3μm〜50μmであり、基板およびエピタキシャル層を合わせた半導体層の厚さは、たとえば、70μm〜300μmである。

【0059】

エピタキシャル層48には、その表面49から基板45へ向かって掘り下がった、側面51および底面52を有するゲートトレンチ43がストライプ状に形成されている。これにより、エピタキシャル層48には、ストライプ状のゲートトレンチ43の側面51により区画されたストライプ状の単位セル42が複数本形成されている。

ゲートトレンチ43は、エピタキシャル層48の表面49から測定される深さD1が、たとえば30μm〜50μm(具体的には、40μm)のディープトレンチであり、エピタキシャル層48を貫通して、その最深部が基板45の厚さ方向途中に位置している。

【0060】

ゲートトレンチ43の内面およびエピタキシャル層48の表面49におけるゲートトレンチ43の周縁部には、それらを一体的に覆うゲート絶縁膜53が形成されている。ゲート絶縁膜の厚さは、たとえば、0.025μm〜0.15μmである。

そして、ゲート絶縁膜53を挟んでエピタキシャル層48に対向するように、ゲート電極54が形成されている。ゲート電極54は、たとえば、不純物が高濃度にドーピングされたポリシリコンからなる。

【0061】

ゲート電極54は、ゲートトレンチ43に充填されたトレンチ部55と、当該トレンチ部55の開口端側の端部から、当該端部に対してゲートトレンチ43の幅方向(横方向)の両側にエピタキシャル層48の表面49に沿って引き出されたプレーナ部56とを一体的に含み、断面視T字状に形成されている。

エピタキシャル層48の表面49の近傍(表面部)においてゲートトレンチ43の周囲には、p−型(たとえば、濃度が1×1017〜5×1017cm−3)のチャネル層57が形成されている。チャネル層57には、p型不純物として、たとえば、ボロン(B)、アルミニウム(Al)などが含まれている。以下同じ。また、エピタキシャル層48において、チャネル層57に対してエピタキシャル層48の裏面50側の部分は、ドレイン層58である。

【0062】

チャネル層57は、ゲートトレンチ43の側面51とエピタキシャル層48の表面49とが交わって形成されたゲートトレンチ43の角部(トレンチ角部59)において、ゲートトレンチ43をその幅方向両側から挟むように形成されていて、エピタキシャル層48の表面49およびゲートトレンチ43の側面51の両方に露出している。これにより、チャネル層57には、ゲート電極54のトレンチ部55に対向する側面部60と、ゲート電極54のプレーナ部56に対向する表面部61とが、トレンチ角部59で垂直に交わるL字形に形成されている。また、チャネル層57の深さ(側面部60の深さ)D2は、ゲートトレンチ43よりも浅く、たとえば、0.5μm〜3.0μmである。

【0063】

チャネル層57におけるエピタキシャル層48の表面部には、表面49に露出するようにソース層62が形成されている。ソース層62は、その周囲および下方の全部がチャネル層57に取り囲まれるように形成されたソースウェルであり、ソース層62とドレイン層58との間には、チャネル層57が介在している。

ソース層62は、ゲート電極54のプレーナ部56の端部の下方に所定量入り込んでプレーナ部56の一部と重なり合い、チャネル層57の表面部61に対してゲートトレンチ43の反対側で隣接するオーバーラップ部63と、コンタクトトレンチ44の側面65(後述)で露出するコンタクト部64とを一体的に有している。

【0064】

ソース層62は、エピタキシャル層48の表面49に沿う位置により深さが異なっており、たとえば、オーバーラップ部63がコンタクト部64よりも浅い。具体的には、オーバーラップ部63の深さD3は、たとえば、0.2μm〜1.0μmであり、コンタクト部64の深さD4は、たとえば、0.3μm〜1.1μmである。なお、ソース層62の深さは、エピタキシャル層48の表面49に沿うどの位置から測定した場合でも、ゲート絶縁膜53の厚さの3倍以下である。

【0065】

各単位セル42には、エピタキシャル層48の表面49からソース層62を貫通し、最深部がチャネル層57に達するコンタクトトレンチ44が形成されている。コンタクトトレンチ44の開口幅Wは、その深さ方向において一定であり、たとえば、0.2μm〜0.5μmである。コンタクトトレンチ44の側面65にはソース層62のコンタクト部64が露出し、コンタクトトレンチ44の底面66にはチャネル層57が露出している。

【0066】

そして、コンタクトトレンチ44の底面66に露出したチャネル層57には、p+型(たとえば、濃度が1×1019〜1×1020cm−3)のチャネルコンタクト領域67が形成されている。チャネルコンタクト領域67は、コンタクトトレンチ44の長手方向に沿って、コンタクトトレンチ44の底面66全面に直線状に形成されている。

エピタキシャル層48上には、ゲート電極54(プレーナ部56)を覆うように層間絶縁膜68が形成されている。層間絶縁膜68には、コンタクトトレンチ44を露出させるコンタクトホール69が形成されている。

【0067】

なお、図示は省略するが、層間絶縁膜68上には、ソース電極が形成されており、このソース電極は、各コンタクトトレンチ44を介して、すべての単位セル42(ソース層62およびチャネルコンタクト領域67)に一括して接している。すなわち、ソース電極は、すべての単位セル42に対して共通の配線となっている。また、基板45の裏面47には、その全域を覆うようにドレイン電極が形成されている。このドレイン電極は、すべての単位セル42に対して共通の電極となっている。

【0068】

図12A〜図12Hは、図11のMOSトランジスタの製造工程の一部を工程順に示す図であって、図11と同じ位置での切断面を示す。

MOSトランジスタ41を製造するには、図12Aに示すように、CVD(Chemical Vapor Deposition:化学気相成長)法、LPE(Liquid Phase Epitaxy:液相エピタキシ)法、MBE(Molecular Beam Epitaxy:分子線エピタキシ)法などのエピタキシャル成長法により、基板45の表面46上に、n型不純物イオンをドーピングしながらSi結晶を成長させる。これにより、基板45上に、n−型のエピタキシャル層48(ドレイン層58)が形成される。次に、エピタキシャル層48の表面49へ向け、p型不純物イオン(Bイオン)を注入する。注入後、アニール処理(たとえば、900℃〜1000℃で、10分〜30分)することによって、注入されたp型不純物イオンが活性化されて、チャネル層57が形成される。

【0069】

次に、図12Bに示すように、たとえば、CVD法により、エピタキシャル層48の表面49にSiO2膜70を形成し、当該SiO2膜70上にSiN膜71を形成することにより、SiO2膜70およびSiN膜71の2層膜からなるハードマスク72を形成する。SiO2膜70の厚さは、たとえば、50Å〜100Åとし、SiN膜71の厚さは、たとえば、1000Å〜1500Åとする。次に、このハードマスク72を利用して、チャネル層57およびドレイン層58を貫通するようにエピタキシャル層48および基板45の一部をエッチングする。これにより、エピタキシャル層48が表面49からドライエッチングされてゲートトレンチ43が形成される。それとともに、エピタキシャル層48に複数の単位セル42が形成される。

【0070】

次に、図12Cに示すように、たとえば、熱酸化法(たとえば、850℃〜950℃で、10分〜30分)により、ゲートトレンチ43の内面(側面51および底面52)にゲート絶縁膜53を形成する。この際、ハードマスク72のSiO2膜70は、トレンチ角部59においてゲート絶縁膜53と一体化し、エピタキシャル層48の表面49上のゲート絶縁膜53となる。その後、ハードマスク72のSiN膜71を除去する。

【0071】

次に、図12Dに示すように、たとえば、CVD法により、ドーピングされたポリシリコンを、エピタキシャル層48の上方から堆積する。ポリシリコンの堆積は、少なくともゲートトレンチ43が満たされ、エピタキシャル層48の表面49が隠れるまで続ける。これにより、電極材料層73が形成される。次に、電極材料層73上に所定パターンのフォトレジスト74を形成し、このフォトレジスト74をマスクとしたドライエッチングにより、電極材料層73を選択的にエッチングする。

【0072】

これにより、図12Eに示すように、ゲートトレンチ43に充填されたトレンチ部55と、当該トレンチ部55の開口端側の端部から、当該端部に対してゲートトレンチ43の幅方向(横方向)の両側にエピタキシャル層48の表面49に沿って引き出されたプレーナ部56とを一体的に含むゲート電極54が形成される。

次に、図12Eに示すように、ゲート電極54(プレーナ部56)をマスクとして利用して、エピタキシャル層48の表面49に対して3°〜14°で傾斜する注入角度θ1で、エピタキシャル層48の表面49へ向けてn型不純物イオン(Asイオン)を注入する(第1工程)。

【0073】

次に、ゲートトレンチ43に対して第1工程の注入位置の反対側から、エピタキシャル層48の表面49に対して3°〜14°で傾斜する注入角度θ2で、第1工程におけるn型不純物イオンの入射方向と交差するように、エピタキシャル層48の表面49へ向けて同じn型不純物イオンを注入する。注入後、アニール処理(たとえば、900℃〜1000℃で、10分〜30分)することによって、注入されたn型不純物イオンが活性化されて、プレーナ部56に対して自己整合的にソース層62が形成される。

【0074】

第1工程および第2工程の際、ソース層62にはゲート電極54のプレーナ部56の下方に入り込んだオーバーラップ部63が形成されるが、チャネル層57におけるオーバーラップ部63が形成される部分は、イオン注入時にプレーナ部56で覆われている。そのため、n型不純物イオンが直接注入される部分(コンタクト部64)とは異なり、オーバーラップ部63は相対的に浅く形成される(D3<D4となる)。

【0075】

次に、図12Fに示すように、たとえば、CVD法により、SiO2(絶縁材料)を、エピタキシャル層48の上方から堆積して、層間絶縁膜68を形成する。

次に、図12Gに示すように、たとえば、ドライエッチングにより、層間絶縁膜68にコンタクトホール69を形成する。コンタクトホール69の形成後、層間絶縁膜68をマスクとして利用して、露出したエピタキシャル層48をエッチングする。これにより、エピタキシャル層48が表面49からドライエッチングされて、層間絶縁膜68に対して自己整合的にコンタクトトレンチ44が形成される。

【0076】

次に、図12Hに示すように、コンタクトトレンチ44の底面66に対して垂直な方向に、40keV程度の注入エネルギおよび1×1015cm−2程度のドーズ量でp型不純物イオン(BF2イオン)を入射させることにより、チャネル層57における底面66の近傍の深さ位置に不純物を1段注入する。注入後、アニール処理(たとえば、900℃〜950℃で、0.5分〜1分)することによって、注入されたp型不純物イオンが拡散・活性化されて、チャネルコンタクト領域67が形成される。

【0077】

その後は、ソース電極(図示せず)、ドレイン電極(図示せず)などを形成することにより、図11に示すMOSトランジスタ41が得られる。

以上、このMOSトランジスタ41によれば、ソース層62とドレイン層58との間(ソース−ドレイン間)にドレイン電圧が印加された状態でゲート電極54に閾値電圧以上の電圧を印加することにより、ゲート電極54から電界を発生させる(ON状態)。これにより、図13(a)に示すように、ゲートトレンチ43の側面51に沿って垂直方向に電流を流すチャネルをチャネル層57の側面部60に形成できると同時に、エピタキシャル層48の表面49に沿って横方向に電流を流すチャネルをチャネル層57の表面部61に形成することができる。つまり、チャネル層57では、垂直方向チャネルおよび横方向チャネルの2方向チャネルが形成され、これらのチャネルがトレンチ角部59で交わって、全体としてL字形のチャネルが形成される。

【0078】

L字形チャネルのチャネル長は、垂直方向チャネルおよび横方向チャネルのそれぞれのチャネル長を足し合わせた大きさである。そして、垂直方向のチャネル長はチャネル層57の側面部60の深さによって決められ、横方向のチャネル長はチャネル層57の表面部61の幅によって決められる。

本実施形態では、図12Aの工程において、p型不純物イオンの注入条件に基づいてチャネル層57が設計通りの深さで形成されれば、その後、図12Eに示すソース層62を形成するためのn型不純物イオン注入時は、チャネル層57の側面部60がゲート電極54のプレーナ部56(マスク)に覆われている。そのため、当該n型不純物イオンの影響を受けない。なお、本実施形態ではn型不純物イオンを斜め注入しているので、プレーナ部56の下方にもn型不純物イオンが若干注入されるが、その量は微量であり、しかも注入される位置もプレーナ部56の端部に留まるので、チャネル層57の側面部60がそのn型不純物イオンの影響を受けることはない。従って、本実施形態では、チャネル層57の側面部60の深さを設計通りに精密に保持することができるので、垂直方向のチャネル長を設計通りに精密に制御することができる。

【0079】

一方、チャネル層57の表面部61の幅は、その横に形成されるソース層62の形成精度によって左右されるが、本実施形態では、図12Eに示すように、加工精度に優れるエッチング技術により形成されたゲート電極54のプレーナ部56(マスク)に対して、ソース層62を自己整合的に形成する。そのため、プレーナ部56で覆われているチャネル層57の表面部61へのソース層62の過剰な進出を防止できるので、電極材料層73を設計通りにエッチングしてプレーナ部56を形成することにより、チャネル層57の表面部61の幅を設計通りに精密に制御することができる。その結果、横方向のチャネル長も、垂直方向のチャネル長と同様に、設計通りに精密に制御することができる。

【0080】

また、このMOSトランジスタ41によれば、ソース層62の一部がオーバーラップ部63としてゲート電極54のプレーナ部56と重なり合うように形成されるので、このオーバーラップ部63に隣接するチャネル層57の表面部61を、ゲート電極54のプレーナ部56に確実に対向させることができる。その結果、信頼性の高いトランジスタ動作を行なうことができる。

【0081】

そして、このようなオーバーラップ部63は、図12Eに示すように、斜め注入を採用することにより、n型不純物イオンを積極的にプレーナ部56の下方に注入して簡単に形成することができる。

さらに、このMOSトランジスタ41によれば、ゲートトレンチ43が、エピタキシャル層48の表面49からチャネル層57およびドレイン層58を貫通して基板45に達するディープトレンチであるため、MOSトランジスタ41をオンしたときには、ゲート電極54からの電界により、ドレイン層58に含まれるキャリア(電子)をゲートトレンチ43の側面51近傍に誘引させることができる。誘引されたキャリアは、側面51に沿ってゲートトレンチ43の深さ方向に一様に分布するように蓄積され、ゲートトレンチ43の側面51の近傍に層状のキャリア蓄積層75を形成する。

【0082】

そして、MOSトランジスタ41のオン時には、このキャリア蓄積層75を電流路として利用することができる。そのため、エピタキシャル層48の固有の抵抗値に関係なく、MOSトランジスタ41のオン抵抗を低くすることができる。従って、低オン抵抗を維持しながら、エピタキシャル層48を厚くして高耐圧化を達成することができる。

以上、参考例の実施形態を説明したが、参考例は、他の形態で実施することもできる。

【0083】

たとえば、単位セル42の配置形態は、ストライプ状である必要はなく、図14に示すような行列状、図15に示すような千鳥状であってもよい。

また、各単位セル42の形状は、ストライプ状(図10)、四角柱状(図14,図15)に限らず、たとえば、三角柱状、五角柱状、六角柱状等の他の多角柱状であってもよい。

【0084】

また、MOSトランジスタ41において、各半導体部分の導電型を反転した構成が採用されてもよい。たとえば、MOSトランジスタ41において、p型の部分がn型であり、n型の部分がp型であってもよい。

また、ソース層62を形成するときのイオン注入は、エピタキシャル層48の表面49に対して傾斜する方向にイオンを注入する斜め注入に限らず、たとえば、エピタキシャル層48の表面49に対して垂直な方向にイオンを注入する垂直注入を採用してもよい。

【0085】

また、エピタキシャル層48に代えて、たとえば、SiCエピタキシャル層を用いることもできる。

(参考例の実施形態の開示から把握されるべき特徴)

たとえば、参考例の実施形態の開示からは、下記(1)〜(14)の発明を把握することができる。

(1)ゲートトレンチが形成された第1導電型の半導体層と、

ゲート絶縁膜を挟んで前記半導体層に対向する電極であって、前記ゲートトレンチに充填されたトレンチ部と、当該トレンチ部の開口端側の端部から横方向に前記半導体層の表面に沿って引き出されたプレーナ部とを一体的に含むゲート電極と、

前記半導体層の前記表面および前記ゲートトレンチの前記側面の両方に露出するように前記半導体層の表面部に形成され、前記ゲートトレンチよりも浅い深さを有する第2導電型の層であって、前記ゲート電極の前記プレーナ部に対向する表面部と、前記ゲート電極の前記トレンチ部に対向する側面部とを含むチャネル層と、

前記半導体層の前記表面に露出するように前記チャネル層に形成され、前記チャネル層の前記表面部に対して前記ゲートトレンチの反対側で隣接する第1導電型のソース層とを含む、半導体装置。

(2)前記ソース層は、前記プレーナ部の端部の下方に所定量入り込んで前記プレーナ部の一部と重なり合うオーバーラップ部を有している、(1)に記載の半導体装置。

(3)前記ソース層の前記オーバーラップ部は、前記ソース層の残りの部分よりも浅い、(2)に記載の半導体装置。

(4)前記ソース層の深さは、前記ゲート絶縁膜の厚さの3倍以下である、(1)〜(3)のいずれか一項に記載の半導体装置。

(5)前記ゲートトレンチは、前記半導体装置がオンしたときに前記ゲート電極からの電界により、前記半導体層に含まれる第1導電型キャリアの蓄積層がその側面に沿って形成され得るディープトレンチを含む、(1)〜(4)のいずれか一項に記載の半導体装置。

(6)前記半導体層は、第1導電型の基板と、前記基板上に形成され、前記基板よりも不純物濃度が低いエピタキシャル層とを含み、

前記ディープトレンチは、前記エピタキシャル層を貫通して前記基板に達するトレンチを含む、(5)に記載の半導体装置。

(7)前記半導体層の厚さは、70μm〜300μmである、(1)〜(6)のいずれか一項に記載の半導体装置。

(8)前記ゲートトレンチの深さは、30μm〜50μmである、(1)〜(7)のいずれか一項に記載の半導体装置。

(9)前記ゲートトレンチは、ストライプ状に配列された単位セルを区画するように形成されている、(1)〜(8)のいずれか一項に記載の半導体装置。

(10)前記ゲートトレンチは、行列状に配列された単位セルを区画するように形成されている、(1)〜(8)のいずれか一項に記載の半導体装置。

(11)前記ゲートトレンチは、千鳥状に配列された単位セルを区画するように形成されている、(1)〜(8)のいずれか一項に記載の半導体装置。

(12)第1導電型の半導体層に第2導電型イオンを注入することにより、前記半導体層の表面に露出するようにチャネル層を形成する工程と、

前記チャネル層を貫通するように前記半導体層を前記表面からエッチングすることにより、前記チャネル層の深さよりも深いゲートトレンチを形成する工程と、

前記ゲートトレンチの内面および前記半導体層の前記表面にゲート絶縁膜を形成する工程と、

前記ゲートトレンチが満たされ、前記半導体層の前記表面が覆われるまで、前記ゲート絶縁膜上に電極材料を堆積させる工程と、

前記電極材料の前記ゲートトレンチ外の部分をエッチングによりパターニングすることにより、前記ゲートトレンチに充填されたトレンチ部と、当該トレンチ部の開口端側の端部から横方向に前記半導体層の表面に沿って引き出されたプレーナ部とを一体的に含むゲート電極を形成する工程と、

前記チャネル層の前記プレーナ部の下方の部分が前記プレーナ部で覆われた状態で、前記半導体層の前記表面を介して前記チャネル層に第1導電型イオンを注入することにより、前記プレーナ部に対して自己整合的にソース層を形成する工程とを含む、半導体装置の製造方法。

(13)前記ソース層を形成する工程は、前記ソース層の一部が前記プレーナ部の端部の下方に所定量入り込んで、前記プレーナ部の一部と重なり合うオーバーラップ部が形成されるように、前記半導体層の前記表面に対して傾斜する注入角度で前記第1導電型イオンを斜め注入する工程を含む、(12)に記載の半導体装置の製造方法。

(14)

前記ゲートトレンチを形成する工程が、前記半導体層に単位セルがストライプ状に配列されるようにストライプトレンチを形成する工程を含み、

前記第1導電型イオンを斜め注入する工程は、前記ストライプトレンチに対して幅方向一方側から前記第1導電型イオンを斜め注入する第1工程と、前記ストライプトレンチに対して前記第1工程の注入位置の反対側から、前記第1工程における前記第1導電型イオンの入射方向と交差する方向に前記第1導電型イオンを斜め注入する第2工程とを含む、(13)に記載の半導体装置の製造方法。

(上記把握されるべき特徴の効果)

(1)の半導体装置は、たとえば、(12)の半導体装置の製造方法により製造することができる。

【0086】

(1)および(12)の発明によれば、ゲート電極からの電界により、チャネル層の側面部に形成され、ゲートトレンチの側面に沿って垂直方向に電流を流すチャネル、およびチャネル層の表面部に形成され、半導体層の表面に沿って横方向に電流を流すチャネルの2方向チャネルを形成することができる。

垂直方向のチャネル長はチャネル層の側面部の深さによって決められ、横方向のチャネル長はチャネル層の表面部の幅によって決められる。

【0087】

参考例の発明では、第2導電型イオンの注入条件に基づいてチャネル層が設計通りの深さで形成されれば、その後、ソース層を形成するための第1導電型イオン注入時は、チャネル層の側面部がゲート電極のプレーナ部(マスク)に覆われているので、当該第1導電型イオンの影響を受けない。そのため、チャネル層の側面部の深さを設計通りに精密に保持することができるので、垂直方向のチャネル長を設計通りに精密に制御することができる。

【0088】

一方、チャネル層の表面部の幅は、その横に形成されるソース層の形成精度によって左右されるが、参考例の発明では、加工精度に優れるエッチング技術により形成されたゲート電極のプレーナ部(マスク)に対して、ソース層を自己整合的に形成する。プレーナ部で覆われているチャネル層の表面部へのソース層の過剰な進出を防止できるので、電極材料を設計通りにエッチングしてプレーナ部を形成することにより、チャネル層の表面部の幅を設計通りに精密に制御することができる。その結果、横方向のチャネル長も、垂直方向のチャネル長と同様に、設計通りに精密に制御することができる。

【0089】

参考例の半導体装置では、(2)記載のように、前記ソース層は、前記プレーナ部の端部の下方に所定量入り込んで前記プレーナ部の一部と重なり合うオーバーラップ部を有していることが好ましい。この場合、(3)記載のように、前記ソース層の前記オーバーラップ部は、前記ソース層の残りの部分よりも浅くてもよい。

この構成によれば、チャネル層の表面部がゲート電極のプレーナ部に確実に対向することになるので、信頼性の高いトランジスタ動作を行なうことができる。

【0090】

また、参考例の半導体装置では、(4)記載のように、前記ソース層の深さは、前記ゲート絶縁膜の厚さの3倍以下であってもよい。

また、参考例の半導体装置では、(5)記載のように、前記ゲートトレンチは、前記半導体装置がオンしたときに前記ゲート電極からの電界により、前記半導体層に含まれる第1導電型キャリアの蓄積層がその側面に沿って形成され得るディープトレンチを含むことが好ましい。

【0091】

この構成によれば、半導体層に低抵抗なキャリア蓄積層が形成されており、このキャリア蓄積層を、半導体装置のオン時の電流路として利用することができる。そのため、半導体層の固有の抵抗値に関係なく、半導体装置のオン抵抗を低くすることができる。従って、低オン抵抗を維持しながら、半導体層を厚くして高耐圧化を達成することができる。

具体的には、(6)記載のように、前記半導体層が、第1導電型の基板と、前記基板上に形成され、前記基板よりも不純物濃度が低いエピタキシャル層とを含む場合、前記ディープトトレンチは、前記エピタキシャル層を貫通して前記基板に達するトレンチを含むことが好ましい。

【0092】

これにより、不純物濃度が低く、低オン抵抗化の妨げとなるエピタキシャル層の厚さ方向全区間にキャリア蓄積層を形成することができるので、低オン抵抗化の効果が大きい。

また、参考例の半導体装置では、(7)記載のように、前記半導体層の厚さは、70μm〜300μmであってもよく、(8)記載のように、前記ゲートトレンチの深さは、30μm〜50μmであってもよい。

【0093】

また、前記ゲートトレンチは、(9)記載のように、ストライプ状に配列された単位セル、(10)記載のように、行列状に配列された単位セル、および(11)記載のように、千鳥状に配列された単位セルに代表されるいずれの形態の単位セルを区画するように形成されていてもよい。

また、参考例の半導体装置の製造方法では、(13)記載のように、前記ソース層を形成する工程は、前記ソース層の一部が前記プレーナ部の端部の下方に所定量入り込んで、前記プレーナ部の一部と重なり合うオーバーラップ部が形成されるように、前記半導体層の前記表面に対して傾斜する注入角度で前記第1導電型イオンを斜め注入する工程を含むことが好ましい。

【0094】

この方法により、第1導電型イオンを積極的にプレーナ部の下方に注入することができるので、ソース層のオーバーラップ部を簡単に形成することができる。

また、(14)記載のように、前記ゲートトレンチを形成する工程が、前記半導体層に単位セルがストライプ状に配列されるようにストライプトレンチを形成する工程を含む場合、前記第1導電型イオンを斜め注入する工程は、前記ストライプトレンチに対して幅方向一方側から前記第1導電型イオンを斜め注入する第1工程と、前記ストライプトレンチに対して前記第1工程の注入位置の反対側から、前記第1工程における前記第1導電型イオンの入射方向と交差する方向に前記第1導電型イオンを斜め注入する第2工程とを含むことが好ましい。

【符号の説明】

【0095】

1 MOSトランジスタ

2 単位セル

3 ゲートトレンチ

4 コンタクトトレンチ

5 Si基板

6 (Si基板の)表面

7 (Si基板の)裏面

8 Siエピタキシャル層

9 (Siエピタキシャル層の)表面

10 (Siエピタキシャル層の)裏面

11 (ゲートトレンチの)側面

12 (ゲートトレンチの)底面

13 ソース領域

14 チャネル領域

15 ドレイン領域

16 ゲート絶縁膜

17 ゲート電極

18 (コンタクトトレンチの)側面

19 (コンタクトトレンチの)底面

20 チャネルコンタクト領域

21 層間絶縁膜

22 コンタクトホール

23 チャネル部

24 凸部

25 頂部

26 SiO2膜

27 SiN膜

28 ハードマスク

29 界面

30 チャネル領域

31 凸部

32 頂部

33 頂部

41 MOSトランジスタ

42 単位セル

43 ゲートトレンチ

44 コンタクトトレンチ

45 基板

46 (基板の)表面

47 (基板の)裏面

48 エピタキシャル層

49 (エピタキシャル層の)表面

50 (エピタキシャル層の)裏面

51 (ゲートトレンチの)側面

52 (ゲートトレンチの)底面

53 ゲート絶縁膜

54 ゲート電極

55 (ゲート電極の)トレンチ部

56 (ゲート電極の)プレーナ部

57 チャネル層

58 ドレイン層

59 トレンチ角部

60 (チャネル層の)側面部

61 (チャネル層の)表面部

62 ソース層

63 オーバーラップ部

64 コンタクト部

65 (コンタクトトレンチの)側面

66 (コンタクトトレンチの)底面

67 チャネルコンタクト領域

68 層間絶縁膜

69 コンタクトホール

70 SiO2膜

71 SiN膜

72 ハードマスク

73 電極材料層

74 フォトレジスト

75 キャリア蓄積層

【技術分野】

【0001】

本発明は、トレンチゲート型MOSFETを備える半導体装置およびその製造方法に関する。

【背景技術】

【0002】

トレンチゲート型MOSFETの一例として、たとえば、特許文献1の半導体装置は、ゲートトレンチが形成されたn−型第1ベース層と、ゲートトレンチの内面に形成されたゲート絶縁膜と、ゲート絶縁膜の内側に充填されたゲート電極と、ゲート電極を被覆するように形成された層間絶縁膜と、n−型第1ベース層の表面に形成され、ゲートトレンチの底面よりも浅く形成されたp型第2ベース層と、p型第2ベース層の表面に形成されたn+型ソース層と、n+型ソース層を貫通し、p型第2ベース層内まで形成されたセルフアラインコンタクト溝と、セルフアラインコンタクト溝の底面においてp型第2ベース層に接続され、セルフアラインコンタクト溝の側面において、n+型ソース層に接続されたソース電極と、n−型第1ベース層の裏面に形成されたn+型ドレイン層と、n+型ドレン層上に形成されたドレイン電極とを備えている。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2010−62477号公報

【特許文献2】特開2010−021176号公報

【発明の概要】

【課題を解決するための手段】

【0004】

本発明の半導体装置は、ゲートトレンチが形成された半導体層と、前記半導体層の表面側に露出するように形成され、前記ゲートトレンチの側面の一部を形成する第1導電型のソース領域と、前記ソース領域に対して前記半導体層の裏面側に前記ソース領域に接するように形成され、前記ゲートトレンチの前記側面の一部を形成する第2導電型のチャネル領域と、前記チャネル領域に対して前記半導体層の前記裏面側に前記チャネル領域に接するように形成され、前記ゲートトレンチの底面を形成する第1導電型のドレイン領域と、前記ゲートトレンチの内面に形成されたゲート絶縁膜と、前記ゲートトレンチにおいて前記ゲート絶縁膜の内側に埋め込まれたゲート電極とを含み、前記チャネル領域は、前記ゲートトレンチの前記側面に沿って形成され、動作時にチャネルが形成されるチャネル部と、前記半導体層の前記裏面側の前記チャネル部の端部に対して当該裏面側に突出した凸部とを含む。

【0005】

この構成によれば、チャネル領域の一部が、動作時にチャネルが形成される部分(チャネル部)とは異なる箇所において半導体層の裏面側に凸部として突出している。これにより、半導体層の表面からチャネル領域とドレイン領域との界面(pn接合界面)までの深さが一定である従来の構造に比べて、pn接合界面の面積を、半導体装置のチャネル特性に影響を与えずに大きくすることができる。そのため、当該pn接合から広がる空乏層の面積も大きくなるので、当該空乏層は大きな面積で電圧を受けることになる。その結果、空乏層の単位面積あたりで受ける電圧を低減することができる。

【0006】

したがって、チャネル領域とドレイン領域との界面に対して半導体層の裏面側へのゲートトレンチの突出量が小さく(ゲートトレンチが浅く)、ゲート絶縁膜とドレイン領域との小さな面積の界面から広がる空乏層だけでは耐圧を確保できない場合でも、チャネル領域の凸部付近に大きな面積の空乏層が存在するので、半導体装置全体としての耐圧を向上させることができる。

【0007】

よって、ソース−ドレイン間の耐圧を十分保持しながら、ゲートトレンチを浅くしてゲート電極とドレイン領域との対向面積を小さくし、ゲート−ドレイン間の容量を下げることができる。

また、前記半導体装置は、前記半導体層の前記表面から前記ソース領域を貫通し、最深部が前記チャネル領域に達するコンタクトトレンチと、前記コンタクトトレンチの底面に形成された第2導電型のチャネルコンタクト領域とをさらに含み、前記凸部は、前記チャネルコンタクト領域の直下に形成されていることが好ましい。

【0008】

このような構成の半導体装置は、たとえば、表面側に露出するように形成された第1導電型のソース領域、前記ソース領域に対して裏面側に前記ソース領域に接するように形成された第2導電型のチャネル領域、および前記チャネル領域に対して前記裏面側に前記チャネル領域に接するように形成された第1導電型のドレイン領域を有する半導体層に、前記ソース領域および前記チャネル領域を貫通し、最深部が前記ドレイン領域に達するゲートトレンチを形成する工程と、前記ゲートトレンチの内面にゲート絶縁膜を形成する工程と、前記ゲート絶縁膜の内側に電極材料を埋め込むことにより、ゲート電極を形成する工程と、前記半導体層に、前記ソース領域を貫通し、最深部が前記チャネル領域に達するコンタクトトレンチを形成する工程と、前記コンタクトトレンチの底面を通って、前記チャネル領域と前記ドレイン領域との界面近傍に達するように第2導電型イオンを注入することにより、前記コンタクトトレンチの直下に、前記ゲートトレンチの前記側面に沿って形成された前記チャネル領域のチャネル部の前記半導体層の前記裏面側の端部に対して当該裏面側に突出した凸部を形成する工程と、前記半導体層の前記コンタクトトレンチの前記底面近傍に第2導電型イオンを注入することにより、前記チャネル領域にチャネルコンタクト領域を形成する工程とを含む、本発明の半導体装置の製造方法により製造することができる。

【0009】

この方法によれば、従来のイオン注入(イオンインプランテーション)技術を利用して、半導体層の表面に対して1段低くなったコンタクトトレンチの底面へ向かって第2導電型イオンを入射させることにより、チャネル領域に凸部を簡単に形成することができる。なお、半導体層の材料の種類に応じて、第2導電型イオンの注入後にアニール処理を行って、第2導電型イオンを半導体層中に拡散させてもよい。このような拡散は、チャネルコンタクト領域を形成する際も、同様に行うことができる。

【0010】

また、形成される凸部は、半導体層の裏面側へ向かってチャネルコンタクト領域から離れる方向へ突出しているので、凸部とドレイン領域との界面から広がる空乏層とチャネルコンタクト領域との接触を防止することができる。したがって、両者の接触に起因する耐圧の低下を回避することができる。

この場合、前記チャネルコンタクト領域の直下の前記凸部の頂部は、前記コンタクトトレンチの前記底面の幅方向中央部の下方位置に沿って形成されていてもよい。

【0011】

このような構成の半導体装置は、たとえば、本発明の半導体装置の製造方法において、前記コンタクトトレンチの前記底面に対して垂直に前記第2導電型イオンを垂直注入する工程を実行することにより製造することができる。

この方法によれば、第2導電型イオンの注入の際に精密な角度調整をせずに済み、しかも、注入角度の切換えが必要なく、第2導電型イオンを常時垂直に注入しておけばよいので、より簡単に凸部を形成することができる。

【0012】

一方、前記チャネルコンタクト領域の直下の前記凸部の頂部は、前記コンタクトトレンチの前記底面の幅方向端部の下方位置に沿って形成されていてもよい。

このような構成の半導体装置は、たとえば、本発明の半導体装置の製造方法において、前記コンタクトトレンチの前記底面に対して傾斜する注入角度で前記第2導電型イオンを斜め注入する工程を実行することにより製造することができる。

【0013】

凸部の頂部は、コンタクトトレンチの底面の幅方向端部の下方位置に沿って形成される場合、特に、当該底面の幅方向両端部の下方位置に沿って互いに平行に形成された複数の頂部であることが好ましい。つまり、凸部が、単一の頂部(ピーク)ではなく、複数の頂部(ピーク)を持つように突出していることが好ましい。

このような構成の半導体装置は、第2導電型イオンを斜め注入する際に、前記コンタクトトレンチの前記底面の幅方向一端部へ向けて前記第2導電型イオンを注入する第1工程と、前記コンタクトトレンチの前記底面の幅方向他端部へ向けて、前記第1工程における前記第2導電型イオンの入射方向と交差する方向に第2導電型イオンを注入する第2工程とを実行することにより製造することができる。

【0014】

この方法によれば、第1工程から第2工程への移行時に、第2導電型イオンの注入角度の切換えが必要であるが、凸部が複数の頂部(ピーク)を持つので、凸部とドレイン領域との界面の面積を一層大きくすることができる。その結果、空乏層の単位面積あたりで受ける電圧を一層低減することができる。

また、本発明の半導体装置では、前記凸部の頂部は、前記ゲートトレンチの前記底面に対して前記半導体層の前記裏面側に位置していることが好ましく、前記凸部の不純物濃度は、前記チャネルコンタクト領域の濃度の1/100以下であることが好ましい。凸部の不純物濃度が上記条件を満たすことにより、耐圧をさらに向上させることができる。

【0015】

また、前記半導体層は、Si半導体層からなっていてもよい。

また、本発明の半導体装置の製造方法では、前記凸部を形成する工程は、前記コンタクトトレンチの前記底面から所定の深さの位置に前記第2導電型イオンを注入する1段注入工程を含んでいてもよいし、注入エネルギを変化させることにより、前記コンタクトトレンチの前記底面から所定の深さまで前記第2導電型イオンを複数段にわたって注入する多段注入工程を含んでいてもよい。

【0016】

さらに、1段注入工程では、前記チャネル領域と前記ドレイン領域との前記界面に対して前記半導体層の前記表面側および前記裏面側のどちらの深さ位置に前記第2導電型イオンを注入してもよい。

また、多段注入工程では、第2導電型イオンの注入深さのいくつかが前記半導体層の前記表面側となり、残りが前記裏面側となるように、複数段の注入部分により画成される領域が、前記チャネル領域と前記ドレイン領域との前記界面に対して前記半導体層の前記表面側および前記裏面側に跨るように第2導電型イオンを注入してもよい。また、全ての第2導電型イオンの注入深さが、前記チャネル領域と前記ドレイン領域との界面に対して前記半導体層の前記表面側もしくは前記裏面側となるように、第2導電型イオンを注入してもよい。

【0017】

このように、1段および多段といったイオンの注入方式や、イオンの注入深さを選択することにより、様々な形状の凸部を形成することができる。したがって、ゲートトレンチの形状・深さや、ソース領域、チャネル領域などの不純物領域の形状・大きさに応じて適切な形状の凸部を形成することができる。

【図面の簡単な説明】

【0018】

【図1】図1は、本発明の一実施形態に係るトレンチゲート型MOSトランジスタの模式的な平面図である。

【図2】図2は、図1のトレンチゲート型MOSトランジスタの鳥瞰断面図であって、図1の切断線II−IIでの切断面を示す。

【図3A】図3Aは、図2のトレンチゲート型MOSトランジスタの製造工程の一部を示す図である。

【図3B】図3Bは、図3Aの次の工程を示す図である。

【図3C】図3Cは、図3Bの次の工程を示す図である。

【図3D】図3Dは、図3Cの次の工程を示す図である。

【図3E】図3Eは、図3Dの次の工程を示す図である。

【図3F】図3Fは、図3Eの次の工程を示す図である。

【図3G】図3Gは、図3Fの次の工程を示す図である。

【図3H】図3Hは、図3Gの次の工程を示す図である。

【図3I】図3Iは、図3Hの次の工程を示す図である。

【図3J】図3Jは、図3Iの次の工程を示す図である。

【図4】図4(a)〜(d)は、図3Gのイオン注入方式の変形例を示す図であって、図4(a)は1段注入、図4(b)〜(d)は多段注入の例をそれぞれ示す。

【図5】図5は、B11イオンのドーズ量とブレークダウン電圧との関係を示すグラフである。

【図6】図6は、図1のトレンチゲート型MOSトランジスタの凸部の変形例を示す図である。

【図7】図7は、図6の凸部を形成するときのイオン注入方法を説明するための図である。

【図8】図8は、図1のトレンチゲート型MOSトランジスタの単位セルの配置形態の第1変形例を示す図である。

【図9】図9は、図1のトレンチゲート型MOSトランジスタの単位セルの配置形態の第2変形例を示す図である。

【図10】図10は、参考例の一実施形態に係るMOSトランジスタの模式的な平面図である。

【図11】図11は、図10のMOSトランジスタの鳥瞰断面図であって、図10の切断線XI−XIでの切断面を示す。

【図12A】図12Aは、図11のMOSトランジスタの製造工程の一部を示す図である。

【図12B】図12Bは、図12Aの次の工程を示す図である。

【図12C】図12Cは、図12Bの次の工程を示す図である。

【図12D】図12Dは、図12Cの次の工程を示す図である。

【図12E】図12Eは、図12Dの次の工程を示す図である。

【図12F】図12Fは、図12Eの次の工程を示す図である。

【図12G】図12Gは、図12Fの次の工程を示す図である。

【図12H】図12Hは、図12Gの次の工程を示す図である。

【図13】図13(a)(b)は、図11のMOSトランジスタのオン時およびオフ時の状態を示す図であって、図13(a)はオン時、図13(b)はオフ時をそれぞれ示す。

【図14】図14は、図10のMOSトランジスタの単位セルの配置形態の第1変形例を示す図である。

【図15】図15は、図10のMOSトランジスタの単位セルの配置形態の第2変形例を示す図である。

【発明を実施するための形態】

【0019】

以下では、本発明の実施の形態を、添付図面を参照して詳細に説明する。

図1は、本発明の一実施形態に係るトレンチゲート型MOSトランジスタの模式的な平面図である。図2は、図1のトレンチゲート型MOSトランジスタの鳥瞰断面図であって、図1の切断線II−IIでの切断面を示す。

図1を参照して、半導体装置としてのMOSトランジスタ1は、トレンチゲート型MOSFET(Metal Oxide Semiconductor Field Effect Transistor)であり、互いに平行に配列されたストライプ状の単位セル2を複数備えている。各単位セル2は、ストライプ状のゲートトレンチ3により区画されており、隣り合うゲートトレンチ3の間隔(トレンチのピッチP)は、たとえば、0.9μm〜1.5μmである。また、単位セル2には、その長手方向一端から他端向かって延びる長尺(平面視長方形)なコンタクトトレンチ4が、各単位セル2に1つずつ形成されている。

【0020】

次に、図2を参照して、MOSトランジスタ1は、n+型(たとえば、濃度が1×1019〜5×1019cm−3)のSi基板5を備えている。Si基板5は、MOSトランジスタ1のドレインとして機能する。n型不純物としては、リン(P)、ヒ素(As)などが含まれている。以下同じ。

Si基板5の表面6(上面)には、Si基板5よりも低濃度のn−型(たとえば、濃度が1×1016〜1×1015cm−3)のSiエピタキシャル層8が積層されている。

半導体層としてのSiエピタキシャル層8の厚さは、たとえば、3μm〜10μmである。

【0021】

Siエピタキシャル層8には、その表面9からSi基板5へ向かって掘り下がった、側面11および底面12を有するゲートトレンチ3がストライプ状に形成されている。これにより、Siエピタキシャル層8には、ストライプ状のゲートトレンチ3の側面11により区画されたストライプ状の単位セル2が複数本形成されている。

Siエピタキシャル層8の表面9から測定されるゲートトレンチ3の深さD1は、たとえば、1.0μm〜1.5μmであり、具体的には、1.0μmである。

【0022】

Siエピタキシャル層8においてゲートトレンチ3の周囲には、n+型のソース領域13およびp−型(たとえば、濃度が1×1017〜5×1017cm−3)のチャネル領域14が、Siエピタキシャル層8の表面9に近い側からこの順に形成されている。チャネル領域14には、p型不純物として、たとえば、ボロン(B)、アルミニウム(Al)などが含まれている。以下同じ。

【0023】

ソース領域13は、Siエピタキシャル層8の表面9に露出するとともに、ゲートトレンチ3の側面11の上部(一部)を形成するように、各単位セル2の表層部に形成されている。表面9からSi基板5へ向かう方向に沿うソース領域13の厚さT1は、たとえば、0.2μm〜0.4μmである。なお、以下の説明で厚さを定義する場合には、特に断りのない限り、Siエピタキシャル層8の表面9からSi基板5へ向かう方向に沿った厚さのことをいう。

【0024】

チャネル領域14は、ソース領域13に対してSi基板5側(Siエピタキシャル層8の裏面10側)にソース領域13に接するように、かつ、ゲートトレンチ3の側面11の下部(一部)を形成するように形成されている。

一方、Siエピタキシャル層8における、チャネル領域14に対してSi基板5側の領域は、エピタキシャル成長後のままの状態が維持された、n−型のドレイン領域15となっている。ドレイン領域15は、チャネル領域14に対してSi基板5側にチャネル領域14に接しており、ゲートトレンチ3の底面12を形成している。

【0025】

ゲートトレンチ3の内面には、その全域を覆うように、ゲート絶縁膜16が形成されている。そして、ゲートトレンチ3において、n型不純物が高濃度にドーピングされたポリシリコンをゲート絶縁膜16の内側に埋め込むことにより、ゲートトレンチ3内にゲート電極17が埋設されている。こうして、ソース領域13とドレイン領域15とが、Siエピタキシャル層8の表面9に垂直な縦方向にチャネル領域14を介して離間して配置された、縦型MOSトランジスタ1構造が構成されている。

【0026】

各単位セル2には、Siエピタキシャル層8の表面9からソース領域13を貫通し、最深部がチャネル領域14に達するコンタクトトレンチ4が形成されている。コンタクトトレンチ4の開口幅Wは、その深さ方向において一定であり、たとえば、0.2μm〜0.5μmである。コンタクトトレンチ4の側面18にはソース領域13が露出し、コンタクトトレンチ4の底面19にはチャネル領域14が露出している。

【0027】

そして、コンタクトトレンチ4の底面19に露出したチャネル領域14には、p+型(たとえば、濃度が1×1019〜1×1020cm−3)のチャネルコンタクト領域20が形成されている。チャネルコンタクト領域20は、コンタクトトレンチ4の長手方向に沿って、コンタクトトレンチ4の底面19全面に直線状に形成されている。

Siエピタキシャル層8上には、層間絶縁膜21が形成されている。層間絶縁膜21には、コンタクトトレンチ4を露出させるコンタクトホール22が形成されている。

【0028】

なお、図示は省略するが、層間絶縁膜21上には、ソース電極が形成されており、このソース電極は、各コンタクトトレンチ4を介して、すべての単位セル2(ソース領域13およびチャネルコンタクト領域20)に一括して接している。すなわち、ソース電極は、すべての単位セル2に対して共通の配線となっている。また、Si基板5の裏面7には、その全域を覆うようにドレイン電極が形成されている。このドレイン電極は、すべての単位セル2に対して共通の電極となっている。

【0029】

そして、この実施形態では、各単位セル2において、チャネル領域14のコンタクトトレンチ4の直下の部分が、チャネルコンタクト領域20から離れる方向に断面視山状に突出(隆起)している。

具体的には、チャネル領域14は、MOSトランジスタ1の動作時にチャネルが形成されるチャネル領域14のチャネル部23付近を両端とし、当該両端からコンタクトトレンチ4の底面19の幅方向中央部の下方位置に1つのピーク(頂部25)がくるように描かれる放物線状に突出している。これにより、チャネル領域14は、当該放物線で区画される部分として、Siエピタキシャル層8の裏面10側のチャネル部23の端部に対して当該裏面10側に突出した凸部24を有している。

【0030】

凸部24の頂部25(放物線のピーク)は、Si基板5に接触しない範囲内で、ゲートトレンチ3の底面12に対してSiエピタキシャル層8の裏面10側に位置しており(つまり、ゲートトレンチ3の底面12よりも深く)、コンタクトトレンチ4に沿って直線状に形成されている。また、凸部24の導電型は、チャネル領域14と同じp−型(たとえば、濃度が1×1017〜5×1017cm−3)であり、その不純物濃度は、p+型(たとえば、濃度が1×1019〜1×1020cm−3)のチャネルコンタクト領域20の1/100以下であることが好ましい。

【0031】

また、チャネル領域14において、チャネル部23の厚さT2は、たとえば、0.5μm〜0.9μmであり、具体的には、0.8μmである。また、凸部24の頂部25までの厚さT3は、たとえば、1.0μm〜1.6μmであり、具体的には、1.4μmである。

図3A〜図3Jは、図2のトレンチゲート型MOSトランジスタの製造工程の一部を示す図であって、図2と同じ位置での切断面を示す。

【0032】

MOSトランジスタ1を製造するには、図3Aに示すように、CVD(Chemical Vapor Deposition:化学気相成長)法、LPE(Liquid Phase Epitaxy:液相エピタキシ)法、MBE(Molecular Beam Epitaxy:分子線エピタキシ)法などのエピタキシャル成長法により、Si基板5の表面6上に、n型不純物をドーピングしながらSi結晶を成長させる。これにより、Si基板5上に、n−型のSiエピタキシャル層8(ドレイン領域15)が形成される。次に、Siエピタキシャル層8の表面9へ向け、p型不純物およびn型不純物を順に注入する。注入後、アニール処理(たとえば、900℃〜1000℃で、10分〜30分)することによって、注入された各不純物が活性化されて、チャネル領域14およびソース領域13が同時に形成される。次に、たとえば、CVD法により、Siエピタキシャル層8の表面9にSiO2膜26を形成し、当該SiO2膜26上にSiN膜27を形成することにより、SiO2膜26およびSiN膜27の2層膜からなるハードマスク28を形成する。SiO2膜26の厚さは、たとえば、50Å〜100Åとし、SiN膜27の厚さは、たとえば、1000Å〜1500Åとする。

【0033】

次に、図3Bに示すように、このハードマスク28を利用して、Siエピタキシャル層8をエッチングする。これにより、Siエピタキシャル層8が表面9からドライエッチングされてゲートトレンチ3が形成される。それとともに、Siエピタキシャル層8に複数の単位セル2が形成される。

次に、図3Cに示すように、たとえば、熱酸化法(たとえば、850℃〜950℃で、10分〜30分)により、ゲートトレンチ3の内面(側面11および底面12)にゲート絶縁膜16を形成する。

【0034】

次に、図3Dに示すように、たとえば、CVD法により、ドーピングされたポリシリコン(電極材料)を、Siエピタキシャル層8の上方から堆積する。ポリシリコンの堆積は、少なくともSiエピタキシャル層8の表面9が隠れるまで続ける。その後、堆積したポリシリコンを、エッチバック面がSiエピタキシャル層8の表面9に対して面一になるまでエッチバックする。これにより、ゲートトレンチ3内に残存するポリシリコンからなるゲート電極17が形成される。

【0035】

次に、図3Eに示すように、たとえば、CVD法により、SiO2(絶縁材料)を、Siエピタキシャル層8の上方から堆積して、層間絶縁膜21を形成する。

次に、図3Fに示すように、たとえば、ドライエッチングにより、層間絶縁膜21にコンタクトホール22を形成する。コンタクトホール22の形成後、層間絶縁膜21をマスクとして利用して、露出したSiエピタキシャル層8をエッチングする。これにより、Siエピタキシャル層8が表面9からドライエッチングされて、層間絶縁膜21に対して自己整合的にコンタクトトレンチ4が形成される。

【0036】

次に、図3Gに示すように、コンタクトトレンチ4の底面12に対して垂直な方向に、不純物(B11イオン)を入射させることにより、チャネル領域14とドレイン領域15との界面29に対してSiエピタキシャル層8の表面9側(チャネル領域14における界面29の近傍)の深さ位置に不純物を1段注入する。不純物イオンの注入エネルギは、たとえば、100keV〜140keVであり、好ましくは、140keV程度である。また、不純物イオンのドーズ量は、たとえば、4×1012cm−2〜1×1013cm−2であり、好ましくは、6×1012cm−2〜8×1012cm−2である。

【0037】

注入後、アニール処理(たとえば、900℃〜950℃で、0.5分〜1分)することによって、図3Hに示すように、注入されたp型不純物が拡散・活性化されて、チャネル領域14の凸部24が形成される。

次に、図3Iに示すように、コンタクトトレンチ4の底面12に対して垂直な方向に、40keV程度の注入エネルギおよび1×1015cm−2程度のドーズ量で不純物(BF2イオン)を入射させることにより、チャネル領域14における底面12の近傍の深さ位置に不純物を1段注入する。

【0038】

注入後、アニール処理(たとえば、900℃〜950℃で、0.5分〜1分)することによって、図3Jに示すように、注入されたp型不純物が拡散・活性化されて、チャネルコンタクト領域20が形成される。

その後は、ソース電極(図示せず)、ドレイン電極(図示せず)などを形成することにより、図2に示すMOSトランジスタ1が得られる。

【0039】

以上、この実施形態によれば、チャネル領域14の一部が、チャネル領域14のチャネル部23付近を両端とし、当該両端からコンタクトトレンチ4の底面19の幅方向中央部の下方位置に1つのピークがくるように描かれる放物線状に凸部24として突出している。これにより、Siエピタキシャル層8の表面9からチャネル領域14とドレイン領域15との界面(pn接合界面)までの深さが一定である従来の構造に比べて、pn接合界面の面積を、MOSトランジスタ1のチャネル特性に影響を与えずに大きくすることができる。つまり、チャネル部23の長さ(チャネル長)を変えずに、チャネル領域14のコンタクトトレンチ4の直下の部分だけを突出させているため、チャネル特性への影響がほとんどない。そのため、当該pn接合から広がる空乏層の面積も大きくなるので、当該空乏層は大きな面積で電圧を受けることになる。その結果、空乏層の単位面積あたりで受ける電圧を低減することができる。

【0040】

したがって、チャネル部23とドレイン領域15との界面に対してSiエピタキシャル層8の裏面10側へのゲートトレンチ3の突出量L(この実施形態では、たとえば、0.2μm〜0.1μm)が小さく(ゲートトレンチ3が浅く)、ゲート絶縁膜16とドレイン領域15との小さな面積の界面から広がる空乏層だけでは耐圧を確保できない場合でも、チャネル領域14の凸部24付近に大きな面積の空乏層が存在するので、MOSトランジスタ1全体としての耐圧を向上させることができる。

【0041】

よって、ソース−ドレイン間の耐圧を十分保持しながら、ゲートトレンチ3を浅くしてゲート電極17とドレイン領域15との対向面積を小さくし、ゲート−ドレイン間の容量を下げることができる。

しかも、チャネル領域14の凸部24は、チャネルコンタクト領域20から離れる方向へ突出しているので、凸部24とドレイン領域15との界面から広がる空乏層とチャネルコンタクト領域20との接触を防止することができる。したがって、両者の接触に起因する耐圧の低下を回避することができる。

【0042】

また、このような凸部24は、従来のイオン注入(イオンインプランテーション)技術を利用して、Siエピタキシャル層8の表面9に対して1段低くなったコンタクトトレンチ4の底面12へ向かって不純物イオンを入射させることにより簡単に形成することができる。さらに、コンタクトトレンチ4の底面12に対して垂直に不純物イオンを入射して凸部24を形成できるので、不純物イオンの注入の際に精密な角度調整をせずに済み、しかも、注入角度の切換えが必要ない。

【0043】

なお、凸部24を形成するためのイオン注入の方式や注入深さは、ゲートトレンチ3の形状・深さや、ソース領域13、チャネル領域14などの不純物領域の形状・大きさに応じて変化させることができる。

たとえば、図4(a)に示すように、チャネル領域14とドレイン領域15との界面29に対してSiエピタキシャル層8の裏面10側(ドレイン領域15における界面29の近傍)の深さ位置に不純物を1段注入することができる。

【0044】

また、図4(b)に示すように、80keV〜180keVの範囲で注入エネルギを変化させることにより、不純物イオン(B11イオン)の注入深さのいくつかがSiエピタキシャル層8の表面9側となり、残りが裏面10側となるように、注入部分により画成される領域が、界面29に対してSiエピタキシャル層8の表面9側および裏面10側に跨るように不純物イオンを複数段にわたって多段注入することもできる。

【0045】

さらに、多段注入を採用する場合、図4(c)に示すように、全ての不純物イオンの注入深さが、界面29に対してSiエピタキシャル層8の裏面10側となるように、不純物イオンを注入してもよいし、図4(d)に示すように、全ての不純物イオンの注入深さが、界面29に対してSiエピタキシャル層8の表面9側となるように、不純物イオンを注入してもよい。

【0046】

このように、1段および多段といったイオンの注入方式や、イオンの注入深さを選択することにより、様々な形状の凸部24を形成することができる。したがって、ゲートトレンチ3の形状・深さや、ソース領域13、チャネル領域14などの不純物領域の形状・大きさに応じて適切な形状の凸部24を形成することができる。

また、不純物(B11イオン)のドーズ量を4×1012cm−2〜1×1013cm−2の範囲にすることによって、ドレイン−ソース間のブレークダウン電圧を向上させることができる。具体的には、図5に示すように(注入エネルギ=140keV)、B11イオンのドーズ量が4×1012cm−2〜1×1013cm−2の範囲では、ブレークダウン電圧を36V以上にすることができた。

【0047】

また、凸部24の形状は、断面視において、1つの放物線で区画される形状である必要はなく、たとえば、2つの放物線で区画される形状であってもよい。

具体的には、図6のチャネル領域30の凸部31のように、チャネル部23付近を両端とし、当該両端からコンタクトトレンチ4の底面19の幅方向一端部および他端部の下方位置それぞれにピーク(頂部32)が1つずつくるように描かれる2つの放物線状に突出していることが好ましい。この場合、各凸部31の頂部32は、コンタクトトレンチ4に沿って互いに平行に直線状に並ぶことになる。また、一方の凸部31および他方の凸部31は、コンタクトトレンチ4の底面19の幅方向中央部を通る垂線を対称軸sとする線対称であることが好ましく、この対称軸s上にある逆側の頂部33は、ゲートトレンチ3の底面12に対してSiエピタキシャル層8の裏面10側に位置していることが好ましい(つまり、ゲートトレンチ3の底面12よりも深い位置にある)。

【0048】

そして、図6の凸部31は、たとえば、図3Gの工程に代えて、コンタクトトレンチ4の底面12に対して7°〜14°で傾斜する注入角度θ1で、コンタクトトレンチ4の幅方向一端部へ向けて不純物イオンを注入する第1工程と、コンタクトトレンチ4の底面12に対して7°〜14°で傾斜する注入角度θ2で、第1工程における不純物イオンの入射方向と交差するように、コンタクトトレンチ4の幅方向他端部へ向けて不純物イオンを注入する第2工程とを実行することにより形成することができる。

【0049】

この方法によれば、第1工程から第2工程への移行時に、不純物イオンの注入角度の切換え(θ1→θ2)が必要であるが、凸部31が複数の頂部32(ピーク)を持つので、凸部31とドレイン領域15との界面の面積を一層大きくすることができる。その結果、空乏層の単位面積あたりで受ける電圧を一層低減することができる。

以上、本発明の実施形態を説明したが、本発明は、他の形態で実施することもできる。

【0050】

たとえば、単位セル2の配置形態は、ストライプ状である必要はなく、図8に示すような行列状、図9に示すような千鳥状であってもよい。

また、各単位セル2の形状は、ストライプ状(図1)、四角柱状(図8,図9)に限らず、たとえば、三角柱状、五角柱状、六角柱状等の他の多角柱状であってもよい。

また、MOSトランジスタ1において、各半導体部分の導電型を反転した構成が採用されてもよい。たとえば、MOSトランジスタ1において、p型の部分がn型であり、n型の部分がp型であってもよい。

【0051】

また、Siエピタキシャル層8に代えて、たとえば、SiCエピタキシャル層を用いることもできる。

また、チャネル領域の凸部は、凸部24,31のようにコンタクトトレンチ4の直下にある必要はなく、MOSトランジスタ1のチャネル特性に影響を与えない範囲で様々な場所に形成することもできる。

【0052】

その他、特許請求の範囲に記載された事項の範囲で種々の設計変更を施すことが可能である。

<参考例に係る発明>

(参考例の背景技術)

MOSFETの一例として、たとえば、特許文献2の半導体装置が公知である。

【0053】

この半導体装置は、トレンチゲートを含むpチャネル型パワーMOSFET(metal-oxide-semiconductor field-effect transistor)とすることができる。半導体装置は、p+型のシリコン基板と、その上に形成されたp型半導体層と、さらにその上に形成されたn型のチャネル層とから構成される半導体基板を含む。

半導体装置は、さらに、チャネル層上の半導体基板の表面に形成されたn+型のボディ領域と、平面視でボディ領域の四方を囲むp+型のソース領域とを含む。また、半導体装置は、チャネル層を貫通し、p型半導体層にまで到達するゲートトレンチと、ゲートトレンチの側面に形成されたゲート酸化膜と、ゲートトレンチの底面に形成され、ゲート酸化膜よりも膜厚が厚い厚膜酸化膜と、ゲートトレンチ内でゲート酸化膜および厚膜酸化膜上に形成され、ゲートトレンチを埋め込むゲート電極とを含む。

【0054】

また、半導体装置は、半導体基板上に形成されたソース電極と、ゲート電極上に形成され、ゲート電極とソース電極とを絶縁する層間絶縁膜と、半導体基板のソース電極が形成された面とは反対側の裏面にシリコン基板に接して設けられたドレイン電極とを含む。

(参考例が解決しようとする課題)

特許文献2では、ゲートトレンチの外部に露出したポリシリコンをエッチバックにより除去してゲート電極を形成した後、半導体基板に選択的に不純物イオンを注入し、熱処理することによりソース領域を形成している。

【0055】

しかしながら、このような方法では、イオン注入によるソース領域の深さが設計値よりも深くなり、その直下のチャネル層の一部がソース領域に変質するおそれがある。この変質により、チャネル層が設計値よりも薄くなり、チャネル長が短くなるという不具合がある。

この理由は、エッチバックの加工精度が低いため、エッチバック後のゲート電極の上面(エッチバック面)が半導体基板の表面に対して窪んでいる場合が多い。そのため、半導体基板の表面に不純物イオンを注入する際に、不純物イオンの一部がゲート電極のエッチバック面付近に露出したゲートトレンチの側面からも半導体基板の内部に注入されるからである。

【0056】

参考例の目的は、チャネル長を設計通りに精密に制御することができる半導体装置およびその製造方法を提供することである。

また、参考例の他の目的は、高耐圧化および低オン抵抗化を両立させることができる半導体装置およびその製造方法を提供することである。

(参考例の実施形態)

以下では、参考例の実施の形態を、添付図面を参照して詳細に説明する。

【0057】

図10は、参考例の一実施形態に係るMOSトランジスタの模式的な平面図である。図11は、図10のMOSトランジスタの鳥瞰断面図であって、図10の切断線XI−XIでの切断面を示す。

図10を参照して、半導体装置としてのMOSトランジスタ41は、互いに平行に配列されたストライプ状の単位セル42を複数備えている。各単位セル42は、ストライプ状のゲートトレンチ43により区画されており、隣り合うゲートトレンチ43の間隔(トレンチのピッチP)は、たとえば、0.9μm〜1.5μmである。また、単位セル42には、その長手方向一端から他端向かって延びる長尺(平面視長方形)なコンタクトトレンチ44が、各単位セル42に1つずつ形成されている。

【0058】

次に、図11を参照して、MOSトランジスタ41は、n+型(たとえば、濃度が1×1019〜5×1019cm−3)のSiからなる半導体層としての基板45を備えている。基板45は、MOSトランジスタ41のドレインとして機能する。n型不純物としては、リン(P)、ヒ素(As)などが含まれている。以下同じ。

基板45の表面46(上面)には、基板45よりも低濃度のn−型(たとえば、濃度が1×1016〜1×1015cm−3)のSiからなるエピタキシャル層48が積層されている。半導体層としてのエピタキシャル層48の厚さは、たとえば、3μm〜50μmであり、基板およびエピタキシャル層を合わせた半導体層の厚さは、たとえば、70μm〜300μmである。

【0059】

エピタキシャル層48には、その表面49から基板45へ向かって掘り下がった、側面51および底面52を有するゲートトレンチ43がストライプ状に形成されている。これにより、エピタキシャル層48には、ストライプ状のゲートトレンチ43の側面51により区画されたストライプ状の単位セル42が複数本形成されている。

ゲートトレンチ43は、エピタキシャル層48の表面49から測定される深さD1が、たとえば30μm〜50μm(具体的には、40μm)のディープトレンチであり、エピタキシャル層48を貫通して、その最深部が基板45の厚さ方向途中に位置している。

【0060】

ゲートトレンチ43の内面およびエピタキシャル層48の表面49におけるゲートトレンチ43の周縁部には、それらを一体的に覆うゲート絶縁膜53が形成されている。ゲート絶縁膜の厚さは、たとえば、0.025μm〜0.15μmである。

そして、ゲート絶縁膜53を挟んでエピタキシャル層48に対向するように、ゲート電極54が形成されている。ゲート電極54は、たとえば、不純物が高濃度にドーピングされたポリシリコンからなる。

【0061】

ゲート電極54は、ゲートトレンチ43に充填されたトレンチ部55と、当該トレンチ部55の開口端側の端部から、当該端部に対してゲートトレンチ43の幅方向(横方向)の両側にエピタキシャル層48の表面49に沿って引き出されたプレーナ部56とを一体的に含み、断面視T字状に形成されている。

エピタキシャル層48の表面49の近傍(表面部)においてゲートトレンチ43の周囲には、p−型(たとえば、濃度が1×1017〜5×1017cm−3)のチャネル層57が形成されている。チャネル層57には、p型不純物として、たとえば、ボロン(B)、アルミニウム(Al)などが含まれている。以下同じ。また、エピタキシャル層48において、チャネル層57に対してエピタキシャル層48の裏面50側の部分は、ドレイン層58である。

【0062】

チャネル層57は、ゲートトレンチ43の側面51とエピタキシャル層48の表面49とが交わって形成されたゲートトレンチ43の角部(トレンチ角部59)において、ゲートトレンチ43をその幅方向両側から挟むように形成されていて、エピタキシャル層48の表面49およびゲートトレンチ43の側面51の両方に露出している。これにより、チャネル層57には、ゲート電極54のトレンチ部55に対向する側面部60と、ゲート電極54のプレーナ部56に対向する表面部61とが、トレンチ角部59で垂直に交わるL字形に形成されている。また、チャネル層57の深さ(側面部60の深さ)D2は、ゲートトレンチ43よりも浅く、たとえば、0.5μm〜3.0μmである。

【0063】

チャネル層57におけるエピタキシャル層48の表面部には、表面49に露出するようにソース層62が形成されている。ソース層62は、その周囲および下方の全部がチャネル層57に取り囲まれるように形成されたソースウェルであり、ソース層62とドレイン層58との間には、チャネル層57が介在している。

ソース層62は、ゲート電極54のプレーナ部56の端部の下方に所定量入り込んでプレーナ部56の一部と重なり合い、チャネル層57の表面部61に対してゲートトレンチ43の反対側で隣接するオーバーラップ部63と、コンタクトトレンチ44の側面65(後述)で露出するコンタクト部64とを一体的に有している。

【0064】

ソース層62は、エピタキシャル層48の表面49に沿う位置により深さが異なっており、たとえば、オーバーラップ部63がコンタクト部64よりも浅い。具体的には、オーバーラップ部63の深さD3は、たとえば、0.2μm〜1.0μmであり、コンタクト部64の深さD4は、たとえば、0.3μm〜1.1μmである。なお、ソース層62の深さは、エピタキシャル層48の表面49に沿うどの位置から測定した場合でも、ゲート絶縁膜53の厚さの3倍以下である。

【0065】

各単位セル42には、エピタキシャル層48の表面49からソース層62を貫通し、最深部がチャネル層57に達するコンタクトトレンチ44が形成されている。コンタクトトレンチ44の開口幅Wは、その深さ方向において一定であり、たとえば、0.2μm〜0.5μmである。コンタクトトレンチ44の側面65にはソース層62のコンタクト部64が露出し、コンタクトトレンチ44の底面66にはチャネル層57が露出している。

【0066】

そして、コンタクトトレンチ44の底面66に露出したチャネル層57には、p+型(たとえば、濃度が1×1019〜1×1020cm−3)のチャネルコンタクト領域67が形成されている。チャネルコンタクト領域67は、コンタクトトレンチ44の長手方向に沿って、コンタクトトレンチ44の底面66全面に直線状に形成されている。

エピタキシャル層48上には、ゲート電極54(プレーナ部56)を覆うように層間絶縁膜68が形成されている。層間絶縁膜68には、コンタクトトレンチ44を露出させるコンタクトホール69が形成されている。

【0067】

なお、図示は省略するが、層間絶縁膜68上には、ソース電極が形成されており、このソース電極は、各コンタクトトレンチ44を介して、すべての単位セル42(ソース層62およびチャネルコンタクト領域67)に一括して接している。すなわち、ソース電極は、すべての単位セル42に対して共通の配線となっている。また、基板45の裏面47には、その全域を覆うようにドレイン電極が形成されている。このドレイン電極は、すべての単位セル42に対して共通の電極となっている。

【0068】

図12A〜図12Hは、図11のMOSトランジスタの製造工程の一部を工程順に示す図であって、図11と同じ位置での切断面を示す。

MOSトランジスタ41を製造するには、図12Aに示すように、CVD(Chemical Vapor Deposition:化学気相成長)法、LPE(Liquid Phase Epitaxy:液相エピタキシ)法、MBE(Molecular Beam Epitaxy:分子線エピタキシ)法などのエピタキシャル成長法により、基板45の表面46上に、n型不純物イオンをドーピングしながらSi結晶を成長させる。これにより、基板45上に、n−型のエピタキシャル層48(ドレイン層58)が形成される。次に、エピタキシャル層48の表面49へ向け、p型不純物イオン(Bイオン)を注入する。注入後、アニール処理(たとえば、900℃〜1000℃で、10分〜30分)することによって、注入されたp型不純物イオンが活性化されて、チャネル層57が形成される。

【0069】

次に、図12Bに示すように、たとえば、CVD法により、エピタキシャル層48の表面49にSiO2膜70を形成し、当該SiO2膜70上にSiN膜71を形成することにより、SiO2膜70およびSiN膜71の2層膜からなるハードマスク72を形成する。SiO2膜70の厚さは、たとえば、50Å〜100Åとし、SiN膜71の厚さは、たとえば、1000Å〜1500Åとする。次に、このハードマスク72を利用して、チャネル層57およびドレイン層58を貫通するようにエピタキシャル層48および基板45の一部をエッチングする。これにより、エピタキシャル層48が表面49からドライエッチングされてゲートトレンチ43が形成される。それとともに、エピタキシャル層48に複数の単位セル42が形成される。

【0070】

次に、図12Cに示すように、たとえば、熱酸化法(たとえば、850℃〜950℃で、10分〜30分)により、ゲートトレンチ43の内面(側面51および底面52)にゲート絶縁膜53を形成する。この際、ハードマスク72のSiO2膜70は、トレンチ角部59においてゲート絶縁膜53と一体化し、エピタキシャル層48の表面49上のゲート絶縁膜53となる。その後、ハードマスク72のSiN膜71を除去する。

【0071】

次に、図12Dに示すように、たとえば、CVD法により、ドーピングされたポリシリコンを、エピタキシャル層48の上方から堆積する。ポリシリコンの堆積は、少なくともゲートトレンチ43が満たされ、エピタキシャル層48の表面49が隠れるまで続ける。これにより、電極材料層73が形成される。次に、電極材料層73上に所定パターンのフォトレジスト74を形成し、このフォトレジスト74をマスクとしたドライエッチングにより、電極材料層73を選択的にエッチングする。

【0072】

これにより、図12Eに示すように、ゲートトレンチ43に充填されたトレンチ部55と、当該トレンチ部55の開口端側の端部から、当該端部に対してゲートトレンチ43の幅方向(横方向)の両側にエピタキシャル層48の表面49に沿って引き出されたプレーナ部56とを一体的に含むゲート電極54が形成される。

次に、図12Eに示すように、ゲート電極54(プレーナ部56)をマスクとして利用して、エピタキシャル層48の表面49に対して3°〜14°で傾斜する注入角度θ1で、エピタキシャル層48の表面49へ向けてn型不純物イオン(Asイオン)を注入する(第1工程)。

【0073】

次に、ゲートトレンチ43に対して第1工程の注入位置の反対側から、エピタキシャル層48の表面49に対して3°〜14°で傾斜する注入角度θ2で、第1工程におけるn型不純物イオンの入射方向と交差するように、エピタキシャル層48の表面49へ向けて同じn型不純物イオンを注入する。注入後、アニール処理(たとえば、900℃〜1000℃で、10分〜30分)することによって、注入されたn型不純物イオンが活性化されて、プレーナ部56に対して自己整合的にソース層62が形成される。

【0074】

第1工程および第2工程の際、ソース層62にはゲート電極54のプレーナ部56の下方に入り込んだオーバーラップ部63が形成されるが、チャネル層57におけるオーバーラップ部63が形成される部分は、イオン注入時にプレーナ部56で覆われている。そのため、n型不純物イオンが直接注入される部分(コンタクト部64)とは異なり、オーバーラップ部63は相対的に浅く形成される(D3<D4となる)。

【0075】

次に、図12Fに示すように、たとえば、CVD法により、SiO2(絶縁材料)を、エピタキシャル層48の上方から堆積して、層間絶縁膜68を形成する。

次に、図12Gに示すように、たとえば、ドライエッチングにより、層間絶縁膜68にコンタクトホール69を形成する。コンタクトホール69の形成後、層間絶縁膜68をマスクとして利用して、露出したエピタキシャル層48をエッチングする。これにより、エピタキシャル層48が表面49からドライエッチングされて、層間絶縁膜68に対して自己整合的にコンタクトトレンチ44が形成される。

【0076】

次に、図12Hに示すように、コンタクトトレンチ44の底面66に対して垂直な方向に、40keV程度の注入エネルギおよび1×1015cm−2程度のドーズ量でp型不純物イオン(BF2イオン)を入射させることにより、チャネル層57における底面66の近傍の深さ位置に不純物を1段注入する。注入後、アニール処理(たとえば、900℃〜950℃で、0.5分〜1分)することによって、注入されたp型不純物イオンが拡散・活性化されて、チャネルコンタクト領域67が形成される。

【0077】

その後は、ソース電極(図示せず)、ドレイン電極(図示せず)などを形成することにより、図11に示すMOSトランジスタ41が得られる。

以上、このMOSトランジスタ41によれば、ソース層62とドレイン層58との間(ソース−ドレイン間)にドレイン電圧が印加された状態でゲート電極54に閾値電圧以上の電圧を印加することにより、ゲート電極54から電界を発生させる(ON状態)。これにより、図13(a)に示すように、ゲートトレンチ43の側面51に沿って垂直方向に電流を流すチャネルをチャネル層57の側面部60に形成できると同時に、エピタキシャル層48の表面49に沿って横方向に電流を流すチャネルをチャネル層57の表面部61に形成することができる。つまり、チャネル層57では、垂直方向チャネルおよび横方向チャネルの2方向チャネルが形成され、これらのチャネルがトレンチ角部59で交わって、全体としてL字形のチャネルが形成される。

【0078】

L字形チャネルのチャネル長は、垂直方向チャネルおよび横方向チャネルのそれぞれのチャネル長を足し合わせた大きさである。そして、垂直方向のチャネル長はチャネル層57の側面部60の深さによって決められ、横方向のチャネル長はチャネル層57の表面部61の幅によって決められる。

本実施形態では、図12Aの工程において、p型不純物イオンの注入条件に基づいてチャネル層57が設計通りの深さで形成されれば、その後、図12Eに示すソース層62を形成するためのn型不純物イオン注入時は、チャネル層57の側面部60がゲート電極54のプレーナ部56(マスク)に覆われている。そのため、当該n型不純物イオンの影響を受けない。なお、本実施形態ではn型不純物イオンを斜め注入しているので、プレーナ部56の下方にもn型不純物イオンが若干注入されるが、その量は微量であり、しかも注入される位置もプレーナ部56の端部に留まるので、チャネル層57の側面部60がそのn型不純物イオンの影響を受けることはない。従って、本実施形態では、チャネル層57の側面部60の深さを設計通りに精密に保持することができるので、垂直方向のチャネル長を設計通りに精密に制御することができる。

【0079】

一方、チャネル層57の表面部61の幅は、その横に形成されるソース層62の形成精度によって左右されるが、本実施形態では、図12Eに示すように、加工精度に優れるエッチング技術により形成されたゲート電極54のプレーナ部56(マスク)に対して、ソース層62を自己整合的に形成する。そのため、プレーナ部56で覆われているチャネル層57の表面部61へのソース層62の過剰な進出を防止できるので、電極材料層73を設計通りにエッチングしてプレーナ部56を形成することにより、チャネル層57の表面部61の幅を設計通りに精密に制御することができる。その結果、横方向のチャネル長も、垂直方向のチャネル長と同様に、設計通りに精密に制御することができる。

【0080】

また、このMOSトランジスタ41によれば、ソース層62の一部がオーバーラップ部63としてゲート電極54のプレーナ部56と重なり合うように形成されるので、このオーバーラップ部63に隣接するチャネル層57の表面部61を、ゲート電極54のプレーナ部56に確実に対向させることができる。その結果、信頼性の高いトランジスタ動作を行なうことができる。

【0081】

そして、このようなオーバーラップ部63は、図12Eに示すように、斜め注入を採用することにより、n型不純物イオンを積極的にプレーナ部56の下方に注入して簡単に形成することができる。

さらに、このMOSトランジスタ41によれば、ゲートトレンチ43が、エピタキシャル層48の表面49からチャネル層57およびドレイン層58を貫通して基板45に達するディープトレンチであるため、MOSトランジスタ41をオンしたときには、ゲート電極54からの電界により、ドレイン層58に含まれるキャリア(電子)をゲートトレンチ43の側面51近傍に誘引させることができる。誘引されたキャリアは、側面51に沿ってゲートトレンチ43の深さ方向に一様に分布するように蓄積され、ゲートトレンチ43の側面51の近傍に層状のキャリア蓄積層75を形成する。

【0082】

そして、MOSトランジスタ41のオン時には、このキャリア蓄積層75を電流路として利用することができる。そのため、エピタキシャル層48の固有の抵抗値に関係なく、MOSトランジスタ41のオン抵抗を低くすることができる。従って、低オン抵抗を維持しながら、エピタキシャル層48を厚くして高耐圧化を達成することができる。

以上、参考例の実施形態を説明したが、参考例は、他の形態で実施することもできる。

【0083】

たとえば、単位セル42の配置形態は、ストライプ状である必要はなく、図14に示すような行列状、図15に示すような千鳥状であってもよい。

また、各単位セル42の形状は、ストライプ状(図10)、四角柱状(図14,図15)に限らず、たとえば、三角柱状、五角柱状、六角柱状等の他の多角柱状であってもよい。

【0084】

また、MOSトランジスタ41において、各半導体部分の導電型を反転した構成が採用されてもよい。たとえば、MOSトランジスタ41において、p型の部分がn型であり、n型の部分がp型であってもよい。

また、ソース層62を形成するときのイオン注入は、エピタキシャル層48の表面49に対して傾斜する方向にイオンを注入する斜め注入に限らず、たとえば、エピタキシャル層48の表面49に対して垂直な方向にイオンを注入する垂直注入を採用してもよい。

【0085】

また、エピタキシャル層48に代えて、たとえば、SiCエピタキシャル層を用いることもできる。

(参考例の実施形態の開示から把握されるべき特徴)

たとえば、参考例の実施形態の開示からは、下記(1)〜(14)の発明を把握することができる。

(1)ゲートトレンチが形成された第1導電型の半導体層と、

ゲート絶縁膜を挟んで前記半導体層に対向する電極であって、前記ゲートトレンチに充填されたトレンチ部と、当該トレンチ部の開口端側の端部から横方向に前記半導体層の表面に沿って引き出されたプレーナ部とを一体的に含むゲート電極と、

前記半導体層の前記表面および前記ゲートトレンチの前記側面の両方に露出するように前記半導体層の表面部に形成され、前記ゲートトレンチよりも浅い深さを有する第2導電型の層であって、前記ゲート電極の前記プレーナ部に対向する表面部と、前記ゲート電極の前記トレンチ部に対向する側面部とを含むチャネル層と、

前記半導体層の前記表面に露出するように前記チャネル層に形成され、前記チャネル層の前記表面部に対して前記ゲートトレンチの反対側で隣接する第1導電型のソース層とを含む、半導体装置。

(2)前記ソース層は、前記プレーナ部の端部の下方に所定量入り込んで前記プレーナ部の一部と重なり合うオーバーラップ部を有している、(1)に記載の半導体装置。

(3)前記ソース層の前記オーバーラップ部は、前記ソース層の残りの部分よりも浅い、(2)に記載の半導体装置。

(4)前記ソース層の深さは、前記ゲート絶縁膜の厚さの3倍以下である、(1)〜(3)のいずれか一項に記載の半導体装置。

(5)前記ゲートトレンチは、前記半導体装置がオンしたときに前記ゲート電極からの電界により、前記半導体層に含まれる第1導電型キャリアの蓄積層がその側面に沿って形成され得るディープトレンチを含む、(1)〜(4)のいずれか一項に記載の半導体装置。

(6)前記半導体層は、第1導電型の基板と、前記基板上に形成され、前記基板よりも不純物濃度が低いエピタキシャル層とを含み、

前記ディープトレンチは、前記エピタキシャル層を貫通して前記基板に達するトレンチを含む、(5)に記載の半導体装置。

(7)前記半導体層の厚さは、70μm〜300μmである、(1)〜(6)のいずれか一項に記載の半導体装置。

(8)前記ゲートトレンチの深さは、30μm〜50μmである、(1)〜(7)のいずれか一項に記載の半導体装置。

(9)前記ゲートトレンチは、ストライプ状に配列された単位セルを区画するように形成されている、(1)〜(8)のいずれか一項に記載の半導体装置。

(10)前記ゲートトレンチは、行列状に配列された単位セルを区画するように形成されている、(1)〜(8)のいずれか一項に記載の半導体装置。

(11)前記ゲートトレンチは、千鳥状に配列された単位セルを区画するように形成されている、(1)〜(8)のいずれか一項に記載の半導体装置。

(12)第1導電型の半導体層に第2導電型イオンを注入することにより、前記半導体層の表面に露出するようにチャネル層を形成する工程と、

前記チャネル層を貫通するように前記半導体層を前記表面からエッチングすることにより、前記チャネル層の深さよりも深いゲートトレンチを形成する工程と、

前記ゲートトレンチの内面および前記半導体層の前記表面にゲート絶縁膜を形成する工程と、

前記ゲートトレンチが満たされ、前記半導体層の前記表面が覆われるまで、前記ゲート絶縁膜上に電極材料を堆積させる工程と、

前記電極材料の前記ゲートトレンチ外の部分をエッチングによりパターニングすることにより、前記ゲートトレンチに充填されたトレンチ部と、当該トレンチ部の開口端側の端部から横方向に前記半導体層の表面に沿って引き出されたプレーナ部とを一体的に含むゲート電極を形成する工程と、

前記チャネル層の前記プレーナ部の下方の部分が前記プレーナ部で覆われた状態で、前記半導体層の前記表面を介して前記チャネル層に第1導電型イオンを注入することにより、前記プレーナ部に対して自己整合的にソース層を形成する工程とを含む、半導体装置の製造方法。

(13)前記ソース層を形成する工程は、前記ソース層の一部が前記プレーナ部の端部の下方に所定量入り込んで、前記プレーナ部の一部と重なり合うオーバーラップ部が形成されるように、前記半導体層の前記表面に対して傾斜する注入角度で前記第1導電型イオンを斜め注入する工程を含む、(12)に記載の半導体装置の製造方法。

(14)

前記ゲートトレンチを形成する工程が、前記半導体層に単位セルがストライプ状に配列されるようにストライプトレンチを形成する工程を含み、

前記第1導電型イオンを斜め注入する工程は、前記ストライプトレンチに対して幅方向一方側から前記第1導電型イオンを斜め注入する第1工程と、前記ストライプトレンチに対して前記第1工程の注入位置の反対側から、前記第1工程における前記第1導電型イオンの入射方向と交差する方向に前記第1導電型イオンを斜め注入する第2工程とを含む、(13)に記載の半導体装置の製造方法。

(上記把握されるべき特徴の効果)

(1)の半導体装置は、たとえば、(12)の半導体装置の製造方法により製造することができる。

【0086】

(1)および(12)の発明によれば、ゲート電極からの電界により、チャネル層の側面部に形成され、ゲートトレンチの側面に沿って垂直方向に電流を流すチャネル、およびチャネル層の表面部に形成され、半導体層の表面に沿って横方向に電流を流すチャネルの2方向チャネルを形成することができる。

垂直方向のチャネル長はチャネル層の側面部の深さによって決められ、横方向のチャネル長はチャネル層の表面部の幅によって決められる。

【0087】

参考例の発明では、第2導電型イオンの注入条件に基づいてチャネル層が設計通りの深さで形成されれば、その後、ソース層を形成するための第1導電型イオン注入時は、チャネル層の側面部がゲート電極のプレーナ部(マスク)に覆われているので、当該第1導電型イオンの影響を受けない。そのため、チャネル層の側面部の深さを設計通りに精密に保持することができるので、垂直方向のチャネル長を設計通りに精密に制御することができる。

【0088】

一方、チャネル層の表面部の幅は、その横に形成されるソース層の形成精度によって左右されるが、参考例の発明では、加工精度に優れるエッチング技術により形成されたゲート電極のプレーナ部(マスク)に対して、ソース層を自己整合的に形成する。プレーナ部で覆われているチャネル層の表面部へのソース層の過剰な進出を防止できるので、電極材料を設計通りにエッチングしてプレーナ部を形成することにより、チャネル層の表面部の幅を設計通りに精密に制御することができる。その結果、横方向のチャネル長も、垂直方向のチャネル長と同様に、設計通りに精密に制御することができる。

【0089】

参考例の半導体装置では、(2)記載のように、前記ソース層は、前記プレーナ部の端部の下方に所定量入り込んで前記プレーナ部の一部と重なり合うオーバーラップ部を有していることが好ましい。この場合、(3)記載のように、前記ソース層の前記オーバーラップ部は、前記ソース層の残りの部分よりも浅くてもよい。

この構成によれば、チャネル層の表面部がゲート電極のプレーナ部に確実に対向することになるので、信頼性の高いトランジスタ動作を行なうことができる。

【0090】

また、参考例の半導体装置では、(4)記載のように、前記ソース層の深さは、前記ゲート絶縁膜の厚さの3倍以下であってもよい。

また、参考例の半導体装置では、(5)記載のように、前記ゲートトレンチは、前記半導体装置がオンしたときに前記ゲート電極からの電界により、前記半導体層に含まれる第1導電型キャリアの蓄積層がその側面に沿って形成され得るディープトレンチを含むことが好ましい。

【0091】

この構成によれば、半導体層に低抵抗なキャリア蓄積層が形成されており、このキャリア蓄積層を、半導体装置のオン時の電流路として利用することができる。そのため、半導体層の固有の抵抗値に関係なく、半導体装置のオン抵抗を低くすることができる。従って、低オン抵抗を維持しながら、半導体層を厚くして高耐圧化を達成することができる。

具体的には、(6)記載のように、前記半導体層が、第1導電型の基板と、前記基板上に形成され、前記基板よりも不純物濃度が低いエピタキシャル層とを含む場合、前記ディープトトレンチは、前記エピタキシャル層を貫通して前記基板に達するトレンチを含むことが好ましい。

【0092】

これにより、不純物濃度が低く、低オン抵抗化の妨げとなるエピタキシャル層の厚さ方向全区間にキャリア蓄積層を形成することができるので、低オン抵抗化の効果が大きい。

また、参考例の半導体装置では、(7)記載のように、前記半導体層の厚さは、70μm〜300μmであってもよく、(8)記載のように、前記ゲートトレンチの深さは、30μm〜50μmであってもよい。

【0093】

また、前記ゲートトレンチは、(9)記載のように、ストライプ状に配列された単位セル、(10)記載のように、行列状に配列された単位セル、および(11)記載のように、千鳥状に配列された単位セルに代表されるいずれの形態の単位セルを区画するように形成されていてもよい。

また、参考例の半導体装置の製造方法では、(13)記載のように、前記ソース層を形成する工程は、前記ソース層の一部が前記プレーナ部の端部の下方に所定量入り込んで、前記プレーナ部の一部と重なり合うオーバーラップ部が形成されるように、前記半導体層の前記表面に対して傾斜する注入角度で前記第1導電型イオンを斜め注入する工程を含むことが好ましい。

【0094】

この方法により、第1導電型イオンを積極的にプレーナ部の下方に注入することができるので、ソース層のオーバーラップ部を簡単に形成することができる。

また、(14)記載のように、前記ゲートトレンチを形成する工程が、前記半導体層に単位セルがストライプ状に配列されるようにストライプトレンチを形成する工程を含む場合、前記第1導電型イオンを斜め注入する工程は、前記ストライプトレンチに対して幅方向一方側から前記第1導電型イオンを斜め注入する第1工程と、前記ストライプトレンチに対して前記第1工程の注入位置の反対側から、前記第1工程における前記第1導電型イオンの入射方向と交差する方向に前記第1導電型イオンを斜め注入する第2工程とを含むことが好ましい。

【符号の説明】

【0095】

1 MOSトランジスタ

2 単位セル

3 ゲートトレンチ

4 コンタクトトレンチ

5 Si基板

6 (Si基板の)表面

7 (Si基板の)裏面

8 Siエピタキシャル層

9 (Siエピタキシャル層の)表面

10 (Siエピタキシャル層の)裏面

11 (ゲートトレンチの)側面

12 (ゲートトレンチの)底面

13 ソース領域

14 チャネル領域

15 ドレイン領域

16 ゲート絶縁膜

17 ゲート電極

18 (コンタクトトレンチの)側面

19 (コンタクトトレンチの)底面

20 チャネルコンタクト領域

21 層間絶縁膜

22 コンタクトホール

23 チャネル部

24 凸部

25 頂部

26 SiO2膜

27 SiN膜

28 ハードマスク

29 界面

30 チャネル領域

31 凸部

32 頂部

33 頂部

41 MOSトランジスタ

42 単位セル

43 ゲートトレンチ

44 コンタクトトレンチ

45 基板

46 (基板の)表面

47 (基板の)裏面

48 エピタキシャル層

49 (エピタキシャル層の)表面

50 (エピタキシャル層の)裏面

51 (ゲートトレンチの)側面

52 (ゲートトレンチの)底面

53 ゲート絶縁膜

54 ゲート電極

55 (ゲート電極の)トレンチ部

56 (ゲート電極の)プレーナ部

57 チャネル層

58 ドレイン層

59 トレンチ角部

60 (チャネル層の)側面部

61 (チャネル層の)表面部

62 ソース層

63 オーバーラップ部

64 コンタクト部

65 (コンタクトトレンチの)側面

66 (コンタクトトレンチの)底面

67 チャネルコンタクト領域

68 層間絶縁膜

69 コンタクトホール

70 SiO2膜

71 SiN膜

72 ハードマスク

73 電極材料層

74 フォトレジスト

75 キャリア蓄積層

【特許請求の範囲】

【請求項1】

ゲートトレンチが形成された半導体層と、

前記半導体層の表面側に露出するように形成され、前記ゲートトレンチの側面の一部を形成する第1導電型のソース領域と、

前記ソース領域に対して前記半導体層の裏面側に前記ソース領域に接するように形成され、前記ゲートトレンチの前記側面の一部を形成する第2導電型のチャネル領域と、

前記チャネル領域に対して前記半導体層の前記裏面側に前記チャネル領域に接するように形成され、前記ゲートトレンチの底面を形成する第1導電型のドレイン領域と、

前記ゲートトレンチの内面に形成されたゲート絶縁膜と、

前記ゲートトレンチにおいて前記ゲート絶縁膜の内側に埋め込まれたゲート電極とを含み、

前記チャネル領域は、前記ゲートトレンチの前記側面に沿って形成され、動作時にチャネルが形成されるチャネル部と、前記半導体層の前記裏面側の前記チャネル部の端部に対して当該裏面側に突出した凸部とを含む、半導体装置。

【請求項2】

前記半導体装置は、前記半導体層の前記表面から前記ソース領域を貫通し、最深部が前記チャネル領域に達するコンタクトトレンチと、前記コンタクトトレンチの底面に形成された第2導電型のチャネルコンタクト領域とをさらに含み、

前記凸部は、前記チャネルコンタクト領域の直下に形成されている、請求項1に記載の半導体装置。

【請求項3】

前記チャネルコンタクト領域の直下の前記凸部の頂部は、前記コンタクトトレンチの前記底面の幅方向中央部の下方位置に沿って形成されている、請求項2に記載の半導体装置。

【請求項4】

前記チャネルコンタクト領域の直下の前記凸部の頂部は、前記コンタクトトレンチの前記底面の幅方向端部の下方位置に沿って形成されている、請求項2に記載の半導体装置。

【請求項5】

前記凸部の前記頂部は、前記コンタクトトレンチの前記底面の幅方向両端部の下方位置に沿って互いに平行に形成された複数の頂部を含む、請求項4に記載の半導体装置。

【請求項6】

前記凸部の頂部は、前記ゲートトレンチの前記底面に対して前記半導体層の前記裏面側に位置している、請求項1〜5のいずれか一項に記載の半導体装置。

【請求項7】

前記凸部の不純物濃度は、前記チャネルコンタクト領域の濃度の1/100以下である、請求項2〜5のいずれか一項または請求項2に係る請求項6に記載の半導体装置。

【請求項8】

前記半導体層が、Si半導体層からなる、請求項1〜7のいずれか一項に記載の半導体装置。

【請求項9】

表面側に露出するように形成された第1導電型のソース領域、前記ソース領域に対して裏面側に前記ソース領域に接するように形成された第2導電型のチャネル領域、および前記チャネル領域に対して前記裏面側に前記チャネル領域に接するように形成された第1導電型のドレイン領域を有する半導体層に、前記ソース領域および前記チャネル領域を貫通し、最深部が前記ドレイン領域に達するゲートトレンチを形成する工程と、

前記ゲートトレンチの内面にゲート絶縁膜を形成する工程と、

前記ゲート絶縁膜の内側に電極材料を埋め込むことにより、ゲート電極を形成する工程と、

前記半導体層に、前記ソース領域を貫通し、最深部が前記チャネル領域に達するコンタクトトレンチを形成する工程と、

前記コンタクトトレンチの底面を通って、前記チャネル領域と前記ドレイン領域との界面近傍に達するように第2導電型イオンを注入することにより、前記コンタクトトレンチの直下に、前記ゲートトレンチの前記側面に沿って形成された前記チャネル領域のチャネル部の前記半導体層の前記裏面側の端部に対して当該裏面側に突出した凸部を形成する工程と、

前記半導体層の前記コンタクトトレンチの前記底面近傍に第2導電型イオンを注入することにより、前記チャネル領域にチャネルコンタクト領域を形成する工程とを含む、半導体装置の製造方法。

【請求項10】

前記凸部を形成する工程は、前記凸部の頂部が前記コンタクトトレンチの前記底面の幅方向中央部の下方位置に沿って形成されるように、前記コンタクトトレンチの前記底面に対して垂直に前記第2導電型イオンを垂直注入する工程を含む、請求項9に記載の半導体装置の製造方法。

【請求項11】

前記凸部を形成する工程は、前記凸部の頂部が前記コンタクトトレンチの前記底面の幅方向端部の下方位置に沿って形成されるように、前記コンタクトトレンチの前記底面に対して傾斜する注入角度で前記第2導電型イオンを斜め注入する工程を含む、請求項9に記載の半導体装置の製造方法。

【請求項12】

前記第2導電型イオンを斜め注入する工程は、前記コンタクトトレンチの前記底面の幅方向一端部へ向けて前記第2導電型イオンを注入する第1工程と、前記コンタクトトレンチの前記底面の幅方向他端部へ向けて、前記第1工程における前記第2導電型イオンの入射方向と交差する方向に第2導電型イオンを注入する第2工程とを含む、請求項11に記載の半導体装置の製造方法。

【請求項13】

前記凸部を形成する工程は、前記コンタクトトレンチの前記底面から所定の深さの位置に前記第2導電型イオンを注入する1段注入工程を含む、請求項9〜12のいずれか一項に記載の半導体装置の製造方法。

【請求項14】

前記1段注入工程では、前記チャネル領域と前記ドレイン領域との前記界面に対して前記半導体層の前記表面側の深さ位置に前記第2導電型イオンを注入する、請求項13に記載の半導体装置の製造方法。

【請求項15】

前記1段注入工程では、前記チャネル領域と前記ドレイン領域との前記界面に対して前記半導体層の前記裏面側の深さ位置に前記第2導電型イオンを注入する、請求項13に記載の半導体装置の製造方法。

【請求項16】

前記凸部を形成する工程は、注入エネルギを変化させることにより、前記コンタクトトレンチの前記底面から所定の深さまで前記第2導電型イオンを複数段にわたって注入する多段注入工程を含む、請求項13に記載の半導体装置の製造方法。

【請求項17】

前記多段注入工程では、前記第2導電型イオンの注入深さが、前記チャネル領域と前記ドレイン領域との前記界面に対して前記半導体層の前記表面側および前記裏面側に跨るように、前記第2導電型イオンを注入する、請求項16に記載の半導体装置の製造方法。

【請求項18】

前記多段注入工程では、全ての前記第2導電型イオンの注入深さが前記チャネル領域と前記ドレイン領域との前記界面に対して前記半導体層の前記表面側となるように、前記第2導電型イオンを注入する、請求項16に記載の半導体装置の製造方法。

【請求項19】

前記多段注入工程では、全ての前記第2導電型イオンの注入深さが前記チャネル領域と前記ドレイン領域との前記界面に対して前記半導体層の前記裏面側となるように、前記第2導電型イオンを注入する、請求項16に記載の半導体装置の製造方法。

【請求項1】

ゲートトレンチが形成された半導体層と、

前記半導体層の表面側に露出するように形成され、前記ゲートトレンチの側面の一部を形成する第1導電型のソース領域と、

前記ソース領域に対して前記半導体層の裏面側に前記ソース領域に接するように形成され、前記ゲートトレンチの前記側面の一部を形成する第2導電型のチャネル領域と、

前記チャネル領域に対して前記半導体層の前記裏面側に前記チャネル領域に接するように形成され、前記ゲートトレンチの底面を形成する第1導電型のドレイン領域と、

前記ゲートトレンチの内面に形成されたゲート絶縁膜と、

前記ゲートトレンチにおいて前記ゲート絶縁膜の内側に埋め込まれたゲート電極とを含み、

前記チャネル領域は、前記ゲートトレンチの前記側面に沿って形成され、動作時にチャネルが形成されるチャネル部と、前記半導体層の前記裏面側の前記チャネル部の端部に対して当該裏面側に突出した凸部とを含む、半導体装置。

【請求項2】

前記半導体装置は、前記半導体層の前記表面から前記ソース領域を貫通し、最深部が前記チャネル領域に達するコンタクトトレンチと、前記コンタクトトレンチの底面に形成された第2導電型のチャネルコンタクト領域とをさらに含み、

前記凸部は、前記チャネルコンタクト領域の直下に形成されている、請求項1に記載の半導体装置。

【請求項3】

前記チャネルコンタクト領域の直下の前記凸部の頂部は、前記コンタクトトレンチの前記底面の幅方向中央部の下方位置に沿って形成されている、請求項2に記載の半導体装置。

【請求項4】

前記チャネルコンタクト領域の直下の前記凸部の頂部は、前記コンタクトトレンチの前記底面の幅方向端部の下方位置に沿って形成されている、請求項2に記載の半導体装置。

【請求項5】

前記凸部の前記頂部は、前記コンタクトトレンチの前記底面の幅方向両端部の下方位置に沿って互いに平行に形成された複数の頂部を含む、請求項4に記載の半導体装置。

【請求項6】

前記凸部の頂部は、前記ゲートトレンチの前記底面に対して前記半導体層の前記裏面側に位置している、請求項1〜5のいずれか一項に記載の半導体装置。

【請求項7】

前記凸部の不純物濃度は、前記チャネルコンタクト領域の濃度の1/100以下である、請求項2〜5のいずれか一項または請求項2に係る請求項6に記載の半導体装置。

【請求項8】

前記半導体層が、Si半導体層からなる、請求項1〜7のいずれか一項に記載の半導体装置。

【請求項9】

表面側に露出するように形成された第1導電型のソース領域、前記ソース領域に対して裏面側に前記ソース領域に接するように形成された第2導電型のチャネル領域、および前記チャネル領域に対して前記裏面側に前記チャネル領域に接するように形成された第1導電型のドレイン領域を有する半導体層に、前記ソース領域および前記チャネル領域を貫通し、最深部が前記ドレイン領域に達するゲートトレンチを形成する工程と、

前記ゲートトレンチの内面にゲート絶縁膜を形成する工程と、

前記ゲート絶縁膜の内側に電極材料を埋め込むことにより、ゲート電極を形成する工程と、

前記半導体層に、前記ソース領域を貫通し、最深部が前記チャネル領域に達するコンタクトトレンチを形成する工程と、

前記コンタクトトレンチの底面を通って、前記チャネル領域と前記ドレイン領域との界面近傍に達するように第2導電型イオンを注入することにより、前記コンタクトトレンチの直下に、前記ゲートトレンチの前記側面に沿って形成された前記チャネル領域のチャネル部の前記半導体層の前記裏面側の端部に対して当該裏面側に突出した凸部を形成する工程と、

前記半導体層の前記コンタクトトレンチの前記底面近傍に第2導電型イオンを注入することにより、前記チャネル領域にチャネルコンタクト領域を形成する工程とを含む、半導体装置の製造方法。

【請求項10】

前記凸部を形成する工程は、前記凸部の頂部が前記コンタクトトレンチの前記底面の幅方向中央部の下方位置に沿って形成されるように、前記コンタクトトレンチの前記底面に対して垂直に前記第2導電型イオンを垂直注入する工程を含む、請求項9に記載の半導体装置の製造方法。

【請求項11】

前記凸部を形成する工程は、前記凸部の頂部が前記コンタクトトレンチの前記底面の幅方向端部の下方位置に沿って形成されるように、前記コンタクトトレンチの前記底面に対して傾斜する注入角度で前記第2導電型イオンを斜め注入する工程を含む、請求項9に記載の半導体装置の製造方法。

【請求項12】

前記第2導電型イオンを斜め注入する工程は、前記コンタクトトレンチの前記底面の幅方向一端部へ向けて前記第2導電型イオンを注入する第1工程と、前記コンタクトトレンチの前記底面の幅方向他端部へ向けて、前記第1工程における前記第2導電型イオンの入射方向と交差する方向に第2導電型イオンを注入する第2工程とを含む、請求項11に記載の半導体装置の製造方法。

【請求項13】

前記凸部を形成する工程は、前記コンタクトトレンチの前記底面から所定の深さの位置に前記第2導電型イオンを注入する1段注入工程を含む、請求項9〜12のいずれか一項に記載の半導体装置の製造方法。

【請求項14】

前記1段注入工程では、前記チャネル領域と前記ドレイン領域との前記界面に対して前記半導体層の前記表面側の深さ位置に前記第2導電型イオンを注入する、請求項13に記載の半導体装置の製造方法。

【請求項15】

前記1段注入工程では、前記チャネル領域と前記ドレイン領域との前記界面に対して前記半導体層の前記裏面側の深さ位置に前記第2導電型イオンを注入する、請求項13に記載の半導体装置の製造方法。

【請求項16】

前記凸部を形成する工程は、注入エネルギを変化させることにより、前記コンタクトトレンチの前記底面から所定の深さまで前記第2導電型イオンを複数段にわたって注入する多段注入工程を含む、請求項13に記載の半導体装置の製造方法。

【請求項17】

前記多段注入工程では、前記第2導電型イオンの注入深さが、前記チャネル領域と前記ドレイン領域との前記界面に対して前記半導体層の前記表面側および前記裏面側に跨るように、前記第2導電型イオンを注入する、請求項16に記載の半導体装置の製造方法。

【請求項18】

前記多段注入工程では、全ての前記第2導電型イオンの注入深さが前記チャネル領域と前記ドレイン領域との前記界面に対して前記半導体層の前記表面側となるように、前記第2導電型イオンを注入する、請求項16に記載の半導体装置の製造方法。

【請求項19】

前記多段注入工程では、全ての前記第2導電型イオンの注入深さが前記チャネル領域と前記ドレイン領域との前記界面に対して前記半導体層の前記裏面側となるように、前記第2導電型イオンを注入する、請求項16に記載の半導体装置の製造方法。

【図1】

【図2】

【図3A】

【図3B】

【図3C】

【図3D】

【図3E】

【図3F】

【図3G】

【図3H】

【図3I】

【図3J】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12A】

【図12B】

【図12C】

【図12D】

【図12E】

【図12F】

【図12G】

【図12H】

【図13】

【図14】

【図15】

【図2】

【図3A】

【図3B】

【図3C】

【図3D】

【図3E】

【図3F】

【図3G】

【図3H】

【図3I】

【図3J】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12A】

【図12B】

【図12C】

【図12D】

【図12E】

【図12F】

【図12G】

【図12H】

【図13】

【図14】

【図15】

【公開番号】特開2013−84899(P2013−84899A)

【公開日】平成25年5月9日(2013.5.9)

【国際特許分類】

【出願番号】特願2012−132261(P2012−132261)

【出願日】平成24年6月11日(2012.6.11)

【出願人】(000116024)ローム株式会社 (3,539)

【公開日】平成25年5月9日(2013.5.9)

【国際特許分類】

【出願日】平成24年6月11日(2012.6.11)

【出願人】(000116024)ローム株式会社 (3,539)

[ Back to top ]