半導体装置およびその製造方法

【課題】隣接するSOI領域とバルクシリコン領域とが短絡することを防止する。

【解決手段】一つの活性領域内にSOI領域およびバルクシリコン領域が隣接する半導体装置において、それぞれの領域の境界にダミーゲート電極8を形成することにより、BOX膜4上のSOI膜5の端部のひさし状の部分の下部の窪みにポリシリコン膜などの残渣が残ることを防ぐ。また、前記ダミーゲート電極8を形成することにより、それぞれの領域に形成されたシリサイド層14同士が接触することを防ぐ。

【解決手段】一つの活性領域内にSOI領域およびバルクシリコン領域が隣接する半導体装置において、それぞれの領域の境界にダミーゲート電極8を形成することにより、BOX膜4上のSOI膜5の端部のひさし状の部分の下部の窪みにポリシリコン膜などの残渣が残ることを防ぐ。また、前記ダミーゲート電極8を形成することにより、それぞれの領域に形成されたシリサイド層14同士が接触することを防ぐ。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置およびその製造方法に関し、特に、SOI領域およびバルクシリコン領域を有する半導体素子の製造に適用して有効な技術に関する。

【背景技術】

【0002】

近年、半導体基板の電位を制御することで当該半導体基板上に絶縁膜を介してSi(シリコン)膜を形成するSOI(Silicon On Insulator)構造を用いた半導体装置が研究されている。このような半導体装置では、半導体基板の電位を制御するためのコンタクトプラグなどの接続部材を、SOI構造の上面のSi膜ではなく半導体基板の主面のバルクシリコン領域に電気的に接続することになる。

【0003】

特許文献1(特開2000−223704号公報)には、STI構造などの素子分離を用いた高集積度半導体装置において、素子分離領域周縁部に形成される段差に起因するゲート電極パターニング時の残渣の発生を防ぐことが記載されている。

【0004】

特許文献2(特開2009−170590号公報)には、膜厚が異なるSOI層のそれぞれにトランジスタを形成した半導体装置において、複数種のトランジスタ間の素子分離を精度良く行うことが記載されている。

【0005】

非特許文献1には、SOI構造の上部にCMOS(Complementary Metal Oxide Semiconductor)を形成し、SOI構造の下部のシリコン基板に電位を供給することでCMOSのしきい値電圧を制御することが記載されている。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2000−223704号公報

【特許文献2】特開2009−170590号公報

【非特許文献】

【0007】

【非特許文献1】2010年4月アイ・イー・イー・イー トランスアクションズ オン エレクトロン デバイスズ57号4番835頁〜845頁(IEEE Transactions On Electron Devices, Vol.57, No.4, April 2010, pp. 835-845)

【発明の概要】

【発明が解決しようとする課題】

【0008】

非特許文献1に記載されている技術では、半導体基板に電位を供給する端子部と、比較的低い電圧で駆動するMOS型の電界効果トランジスタ(Metal Oxide Semiconductor Field Effect Transistor:MOSFET)が形成されるSOI領域とが、STI(Shallow Trench Isolation)などの素子分離領域を隔てて絶縁されている。なお、ここでは、通常の半導体装置に用いる単結晶シリコンウエハを、SOI領域と区別してバルクシリコンと呼ぶ。

【0009】

これに対し、半導体基板上にバルクシリコン領域とSOI領域とを有する半導体装置では、半導体基板に電位を供給する前記端子部を含むバルクシリコン領域とSOI領域との間に、半導体基板に埋込まれた素子分離領域を設けない構造を形成することが考えられる。この場合、バルクシリコン領域とSOI領域とが同一の活性領域内に隣接して配置されていることに起因して、半導体基板上に残渣が生じ、またはバルクシリコン領域とSOI領域とのそれぞれの上部のシリサイド層同士が接触するなどして、バルクシリコン領域とSOI領域とが短絡する虞がある。MOS型の電界効果トランジスタ(以下単にMOSFETという)を形成するSOI領域と前記端子部とは別々に電位を制御するために互いに絶縁されている必要があり、これらの領域が短絡(ショート)すると、半導体装置が正常に動作しなくなるため、半導体装置の信頼性が低下する。

【0010】

本発明の目的は、半導体装置の信頼性を向上させることにある。

【0011】

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

【課題を解決するための手段】

【0012】

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、次のとおりである。

【0013】

本発明の好ましい一態様である半導体装置は、半導体基板の主面上の一つの活性領域内に、互いに隣接するSOI領域とバルクシリコン領域とを有し、SOI領域のBOX膜上のSOI膜と半導体領域とに異なる電位を供給する場合に、隣接するSOI領域およびバルクシリコン領域の境界部分において、SOI膜の端部および半導体基板の主面を絶縁膜により覆うものである。

【0014】

また、本発明の好ましい一態様である半導体装置の製造方法は、

(a)半導体基板の主面の一つの活性領域上にBOX膜およびSOI膜を順次形成する工程と、

(b)前記活性領域を構成するバルクシリコン領域と隣接し、前記活性領域を構成するSOI領域にSOI膜を残す工程と、

(c)前記(b)工程の後、等方性エッチングによりBOX膜を加工する工程と、

(d)SOI領域およびバルクシリコン領域の境界において、SOI膜の端部および半導体基板の主面を覆う絶縁膜を形成する工程と、

を有するものである。

【発明の効果】

【0015】

本願において開示される発明のうち、代表的なものによって得られる効果を簡単に説明すれば以下のとおりである。

【0016】

代表的な実施の形態によれば、半導体装置の信頼性を向上させることができる。

【図面の簡単な説明】

【0017】

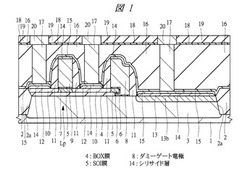

【図1】本発明の実施の形態1である半導体装置の断面図である。

【図2】本発明の実施の形態1である半導体装置の変形例を示す断面図である。

【図3】本発明の実施の形態1である半導体装置の製造工程を示す断面図である。

【図4】図3に続く半導体装置の製造工程中の断面図である。

【図5】図4に続く半導体装置の製造工程中の断面図である。

【図6】図5に続く半導体装置の製造工程中の断面図である。

【図7】図6に続く半導体装置の製造工程中の断面図である。

【図8】図7に続く半導体装置の製造工程中の断面図である。

【図9】図8に続く半導体装置の製造工程中の断面図である。

【図10】図9に続く半導体装置の製造工程中の断面図である。

【図11】図10に続く半導体装置の製造工程中の断面図である。

【図12】図11に続く半導体装置の製造工程中の断面図である。

【図13】図12に続く半導体装置の製造工程中の断面図である。

【図14】図13に続く半導体装置の製造工程中の断面図である。

【図15】図14に続く半導体装置の製造工程中の断面図である。

【図16】図15に続く半導体装置の製造工程中の断面図である。

【図17】図16に続く半導体装置の製造工程中の断面図である。

【図18】図17に続く半導体装置の製造工程中の断面図である。

【図19】本発明の実施の形態1である半導体装置の変形例の製造工程を示す断面図である。

【図20】図19に続く半導体装置の製造工程中の断面図である。

【図21】図20に続く半導体装置の製造工程中の断面図である。

【図22】図21に続く半導体装置の製造工程中の断面図である。

【図23】図22に続く半導体装置の製造工程中の断面図である。

【図24】本発明の実施の形態1である半導体装置の変形例を示す断面図である。

【図25】本発明の実施の形態2である半導体装置の製造工程を示す断面図である。

【図26】図25に続く半導体装置の製造工程中の断面図である。

【図27】本発明の実施の形態3である半導体装置の製造工程を示す断面図である。

【図28】図27に続く半導体装置の製造工程中の断面図である。

【図29】図28に続く半導体装置の製造工程中の断面図である。

【図30】本発明の実施の形態4である半導体装置の製造工程を示す断面図である。

【図31】図30に続く半導体装置の製造工程中の断面図である。

【図32】図31に続く半導体装置の製造工程中の断面図である。

【図33】本発明の実施の形態5である半導体装置の製造工程を示す断面図である。

【図34】図33に続く半導体装置の製造工程中の断面図である。

【図35】図34に続く半導体装置の製造工程中の断面図である。

【図36】図35に続く半導体装置の製造工程中の断面図である。

【図37】比較例である半導体装置の断面図である。

【図38】比較例である半導体装置の拡大した断面図である。

【図39】比較例である半導体装置の断面図である。

【発明を実施するための形態】

【0018】

以下、本発明の実施の形態を図面に基づいて詳細に説明する。なお、実施の形態を説明するための全図において、同一の機能を有する部材には同一の符号を付し、その繰り返しの説明は省略する。また、以下の実施の形態では、特に必要なとき以外は同一または同様な部分の説明を原則として繰り返さない。

【0019】

(実施の形態1)

まず、図1を用いて本発明の実施の形態の半導体装置を説明する。図1には、本実施の形態の半導体装置の断面図を示している。

【0020】

図1に示すように、本実施の形態の半導体装置は例えば単結晶のSi(シリコン)からなる半導体基板1を有し、半導体基板1の主面には素子分離領域2が複数形成されており、素子分離領域2によって活性領域(アクティブ領域)が規定されている。ここでは、半導体基板1の主面において素子分離領域2が形成されている領域を不活性領域(フィールド領域)と呼び、素子分離領域2が形成されていない領域を活性領域(アクティブ領域)と呼ぶものとする。素子分離領域2は主に酸化シリコン(SiO2)などを含み、半導体基板1の主面に形成された溝2a内に形成されている絶縁膜であって、例えばSTI構造を有する。なお、素子分離領域2の上面は半導体基板1の主面よりも高い領域に位置するものとするが、素子分離領域2の上面の高さの位置は、半導体基板1の主面と同等か、それよりも低い位置にあってもよい。

【0021】

半導体基板1の主面にはN型の不純物(例えばP(リン))が導入されたNウエル3が形成されており、半導体基板1の主面上には酸化シリコン膜からなるBOX(Buried Oxide)膜4を介して、主にSi(シリコン)を含むSOI膜5が形成されている。BOX膜4の膜厚は例えば10nmであり、SOI膜5の膜厚は例えば10nmである。

【0022】

本実施の形態の半導体装置では、素子分離領域2により挟まれた一つの活性領域内に、半導体基板1の主面を覆うBOX膜4およびSOI膜5が形成されたSOI領域と、半導体基板1の主面がBOX膜4およびSOI膜5から露出しているバルクシリコン領域とが互いに隣接して配置されている。つまり、BOX膜4およびSOI膜5からなる積層膜の少なくとも一方の端部は素子分離領域2に接しておらず、また、SOI膜5の当該端部の近傍には素子分離領域2は形成されていない。つまり、SOI領域およびバルクシリコン領域とが同一の活性領域内に形成されており、それらの領域の境界部分の近傍の半導体基板1の主面には素子分離領域2が形成されていない。また、図示はしていないが、SOI膜5内には、Nウエル3と同様にN型の不純物(例えばP(リン))が導入されたN型のウエルが形成されている。

【0023】

なお、本願でいうSOI領域およびバルクシリコン領域の境界の近傍とは、SOI領域およびバルクシリコン領域の境界を含むSOI領域またはバルクシリコン領域もしくはそれら両方の領域を含む箇所を指すものとする。例えば、SOI領域およびバルクシリコン領域の境界近傍のバルクシリコン領域とは、バルクシリコン領域の一部の領域であって、前記境界に隣接する領域を指す。

【0024】

バルクシリコン領域に隣接するSOI膜5の端部は、BOX膜4の端部よりもバルクシリコン領域側に突き出ており、SOI膜5の当該端部の直下にはBOX膜4が形成されていない領域がある。つまり、SOI膜5およびBOX膜4からなる積層膜のバルクシリコン領域側の端部は、SOI膜5の方がBOX膜4よりもバルクシリコン領域側に伸びているひさし状の構造を有している。言い換えれば、ゲート電極9のゲート長方向において、BOX膜4の端部からゲート電極9までの距離は、SOI膜5の端部からゲート電極9までの距離よりも近い。また、ゲート電極9のゲート長方向において、BOX膜4の端部は、ゲート電極9側へ向かって、SOI膜5の端部よりも後退している。このひさし状の形状は、半導体基板1の主面上に形成した絶縁膜上に、パターニングされたSOI膜5を形成した後、ウェットエッチング法を用いて前記絶縁膜を一部除去し、半導体基板1の主面を露出させることで前記絶縁膜からなるBOX膜4を形成した際に、SOI膜5の端部の直下の前記絶縁膜が除去されることで形成されるものである。

【0025】

BOX膜4を形成するパターニング工程では、ウェットエッチングなどの等方性エッチングではなく、ドライエッチングなどの異方性エッチングを用いて前記ひさし状の形状が形成されることを防ぐことが考えられるが、ゲート電極を形成する前に行うエッチング工程でドライエッチング法を用いると、エッチングによる過剰なダメージが半導体基板1の主面などに蓄積されて半導体装置の信頼性が低下するため、BOX膜4のパターニング工程ではウェットエッチング法を用いる必要がある。

【0026】

なお、図1には、半導体基板1の主面に対して垂直な方向において、SOI膜5の前記端部と半導体基板1の主面との間にBOX膜4が形成されていない構造を示しているが、後述する図38に示すように、SOI膜5の前記端部と半導体基板1の主面との間には、BOX膜4が例えば半導体基板1の主面に接して形成されている場合が考えられる。ただしこの場合も、SOI膜5の前記端部の下面にはBOX膜4が接していない場合などが考えられ、少なくともSOI膜5およびBOX膜4からなる積層膜のバルクシリコン領域側の端部の側面には、BOX膜4が一部後退することで形成された窪みが存在する。

【0027】

図1に示すように、SOI領域では、SOI膜5の上面に接して、例えば酸化シリコン膜からなるゲート絶縁膜7が形成され、ゲート絶縁膜7上には例えばポリシリコン膜からなるゲート電極9が形成されている。ゲート電極9のゲート長方向において、ゲート電極9の横のSOI膜5の主面にはソース・ドレイン領域を構成するLDD層10が形成されている。LDD層10はSOI膜5内にP型の不純物(例えばB(ホウ素))を比較的低い濃度で導入することで形成された半導体領域である。ゲート電極9の直下のSOI膜5であってLDD層10により挟まれた領域は、低耐圧MOSFETの動作時にチャネル領域として機能する。

【0028】

ゲート電極9の両側の側壁には、例えば酸化シリコン膜および窒化シリコン膜の積層膜からなるサイドウォール11が形成されている。ここでは、ゲート電極9の側壁に接して形成された酸化シリコン膜と、ゲート電極9の側壁に前記酸化シリコン膜を介して形成された窒化シリコン膜とからなる前記積層膜によってサイドウォール11が形成されているものとするが、図では前記積層膜を一層の膜として示している。

【0029】

SOI領域において、ゲート電極9およびサイドウォール11から露出するSOI膜5の上面に接して、ゲート電極9の横にエピタキシャル層(せり上げ層、選択成長層)である拡散層12が形成(選択成長)されている。拡散層12は低耐圧MOSFETのソース・ドレイン領域を構成する半導体層であり、主にSi(シリコン)を含む。拡散層12はゲート電極9の両側にサイドウォール11を介して配置されており、拡散層12はゲート電極9を挟むようにゲート電極9のゲート長方向の両側に配置されている。拡散層12には、LDD層10に打ち込まれた不純物と同じ導電型の不純物が、LDD層10よりも高い濃度で注入されている。

【0030】

なお、拡散層12を形成するためにSOI膜5上のエピタキシャル層に打ち込んだ不純物は、前記エピタキシャル層だけでなくSOI膜5内にも注入されているものとするが、ここではSOI膜5上のエピタキシャル層を拡散層12として説明する。拡散層12は前記エピタキシャル層の上面から、LDD層10が形成されたSOI膜5の底部まで達して形成されているものとして考えてもよい。ただし、拡散層12を形成するために注入された不純物が、前記エピタキシャル層のみに注入されていてもよい。SOI領域に形成されたゲート電極9、LDD層10および拡散層12はPチャネル型の低耐圧MOSFETLpを構成している。

【0031】

同様に、バルクシリコン領域の半導体基板1の主面上には、半導体基板1の主面に接してエピタキシャル層が形成されており、当該エピタキシャル層にはN型の不純物(例えばP(リン))が高濃度で導入された拡散層13が形成されている。また、拡散層13の直下の半導体基板1の主面には、拡散層13を形成する際にバルクシリコン領域の前記エピタキシャル層に注入した不純物が前記エピタキシャル層を通過して注入されており、半導体基板1の主面に高い不純物濃度を有する半導体層13bが形成されている。拡散層13および半導体層13bには、Nウエル3に打ち込まれた不純物と同じ導電型の不純物が、Nウエル3よりも高い濃度で注入されている。バルクシリコン領域は活性領域内においてのみ素子分離領域2から露出しているため、バルクシリコン領域の拡散層13およびその上部のシリサイド層14は、一方の端部が素子分離領域2と隣接する位置で終端している。

【0032】

拡散層12、13およびゲート電極9のそれぞれの上面には、例えばNiSi(ニッケルシリサイド)からなるシリサイド層14が形成されている。

【0033】

ここで、SOI領域とバルクシリコン領域との境界の、BOX膜4およびSOI膜5からなる積層膜の端部が形成されている領域には、ゲート電極9と同様の構造のダミーゲート電極8が形成されている。ダミーゲート電極8は、BOX膜4から露出する半導体基板上の直上からSOI膜5の直上に亘って連続的に形成されている。半導体基板1の主面およびSOI膜5の表面とダミーゲート電極8との間には、例えば酸化シリコン膜からなる絶縁膜6が形成されている。つまり絶縁膜6は、SOI領域とバルクシリコン領域との境界近傍の半導体基板1の主面を覆い、SOI膜5の端部の底面、側面および上面を覆って形成されており、ダミーゲート電極8は絶縁膜6上に形成されている。絶縁膜6とゲート絶縁膜7とは同等の膜厚を有しており、同一の工程で形成された同層の絶縁膜により形成されている。

【0034】

図1では、絶縁膜6がBOX膜4の側壁の上部と下部に接しており、BOX膜4の側面の一部を露出している構造を示しているが、絶縁膜6は半導体基板1の主面、BOX膜4の側壁、SOI領域の底部、側壁および上面に亘って連続的に形成されていてもよい。また図1では、ひさし形状となっているSOI膜5の端部の直下に絶縁膜6を介してダミーゲート電極8の一部が形成されている構造を示しているが、BOX膜4および絶縁膜6の膜厚によっては、SOI膜5の端部の直下にダミーゲート電極8が形成されない場合もある。

【0035】

ダミーゲート電極8の側壁には、低耐圧MOSFETLpと同様にサイドウォール11が形成されており、ダミーゲート電極8の上面にはシリサイド層14が形成されている。SOI領域とバルクシリコン領域との境界近傍において、半導体基板1の主面とSOI膜5の端部との間には絶縁膜6およびダミーゲート電極8が形成されているため、半導体基板1とSOI膜5とは電気的に絶縁されている。また、SOI領域とバルクシリコン領域との境界近傍にはダミーゲート電極8が形成されているため、エピタキシャル層は形成されておらず、エピタキシャル層上のシリサイド層14も形成されていない。したがって、拡散層12上のシリサイド層14と、拡散層13上のシリサイド層14とは、ダミーゲート電極8およびダミーゲート電極8の側壁のサイドウォール11により分離されている。

【0036】

半導体基板1上の全面には、素子分離領域2、シリサイド層14およびサイドウォール11を覆うようにエッチストッパ膜15および層間絶縁膜16が半導体基板1の主面側から順に形成されている。エッチストッパ膜15は例えば窒化シリコン膜からなり、層間絶縁膜16は酸化シリコン膜からなる。エッチストッパ膜15は層間絶縁膜16よりも薄い膜厚で形成されており、層間絶縁膜16の上面はゲート電極9の上面よりも高い位置に均一な高さで形成されている。層間絶縁膜16およびエッチストッパ膜15を貫通し、シリサイド層14の上面を露出するコンタクトホールが複数形成されている。各コンタクトホール内には例えばW(タングステン)を主に含む接続部材であるコンタクトプラグ17が埋込まれており、コンタクトプラグ17の上面の高さは層間絶縁膜16の上面の高さとほぼ均一に揃えられている。

【0037】

コンタクトプラグ17は、ゲート電極、ソース・ドレイン領域または半導体基板などに所定の電位を供給するための接続部材である。図1には示していないが、ゲート電極9の上部にも、シリサイド層14を介してコンタクトプラグ17が形成されている。ただし、ダミーゲート電極8は半導体装置を構成する回路に寄与せず、他の配線などの導電体から絶縁された膜であるので、ダミーゲート電極8上のシリサイド層14にはコンタクトプラグ17は接続されていない。

【0038】

層間絶縁膜16上には、エッチストッパ膜18を介して層間絶縁膜19が形成されており、エッチストッパ膜18および層間絶縁膜19からなる積層膜には、コンタクトプラグ17の上面を露出する溝が複数形成されており、各溝内には配線20が埋込まれている。配線20は例えばCu(銅)を主に含み、コンタクトプラグ17を介してゲート電極、ソース・ドレイン領域または半導体基板などに電気的に接続されている。エッチストッパ膜は例えば窒化シリコン膜からなり、層間絶縁膜19は例えば酸化シリコン膜からなるものとする。

【0039】

上記のように、本実施の形態の半導体装置は、隣り合う素子分離領域2によって規定された一つの活性領域内に、SOI領域とバルクシリコン領域とが形成されている場合において、SOI領域とバルクシリコン領域との境界部分に絶縁膜6および絶縁膜6上のダミーゲート電極8を形成するものである。

【0040】

なお、図1では絶縁膜6をゲート絶縁膜7と同等の膜厚で形成しているが、絶縁膜6の膜厚はゲート絶縁膜7よりも厚くても良い。図2に、本実施の形態の半導体装置の変形例の断面図を示す。図2に示す半導体装置は、図1に示す半導体装置とほぼ同様の構造を有しているが、ダミーゲート電極8の直下の絶縁膜21の膜厚はSOI領域の低耐圧MOSFETLpのゲート絶縁膜7よりも厚い。ここでは、BOX膜4の膜厚を10nmとし、SOI膜5の膜厚を10nmとし、絶縁膜21の膜厚を5nmとしている。

【0041】

また、図1と異なり、図2の変形例の半導体装置では、バルクシリコン領域に低耐圧MOSFETLpよりも高い電圧で駆動するPチャネル型の高耐圧MOSFETHpが形成されている。高耐圧MOSFETHpは、バルクシリコン領域において半導体基板1上にゲート絶縁膜22を介して形成されたゲート電極23と、ゲート電極23の横の半導体基板1の主面に形成されたLDD層24と、LDD層24上のエピタキシャル層であって、LDD層24と同じ導電型の不純物がLDD層24よりも高濃度で導入された拡散層25とを有している。ゲート電極23の両側の側壁にはサイドウォール11が形成されており、拡散層25はサイドウォール11およびゲート電極23をゲート電極23のゲート長方向において挟むように配置されている。ここでは、LDD層24および拡散層25にはP型の不純物(例えばB(ホウ素))が導入されているものとする。LDD層24はNウエル3が形成された半導体基板1の主面に形成されており、ゲート電極23の直下のNウエル3であるチャネル領域を挟むように形成されている。図2に示す領域には、半導体層13b(図1参照)は形成されていない。

【0042】

拡散層25およびゲート電極23の上面にはシリサイド層14が形成されており、拡散層25およびゲート電極23は、層間絶縁膜16およびエッチストッパ膜15を貫通するコンタクトプラグ17を介して層間絶縁膜16上の配線20に電気的に接続されている。図示していない領域では、ゲート電極23も、シリサイド層14およびコンタクトプラグを介して層間絶縁膜16上の配線と電気的に接続されている。

【0043】

ここでは、高耐圧MOSFETHpは例えば本実施の形態の半導体装置に外部から電気信号を入力し、また電気信号を外部に出力する入出力(インプット/アウトプット:I/O)動作に用いられる高耐圧な電界効果トランジスタであるものとする。つまり、高耐圧MOSFETHpは低耐圧MOSFETLpよりも高耐圧な半導体素子であり、高耐圧MOSFETHpが形成されたバルクシリコン領域はI/O領域であるものとする。高耐圧MOSFETHpはゲート電極23のゲート長方向の幅(ゲート長)が低耐圧MOSFETLpのゲート長方向の幅(ゲート長)よりも長く、ゲート絶縁膜22はゲート絶縁膜7よりも半導体基板1の主面に対して垂直な方向の膜厚が厚く形成されている。

【0044】

図2に示す変形例の半導体装置では、SOI領域とバルクシリコン領域との間に形成された絶縁膜21がゲート絶縁膜22と同等の膜厚を有し、BOX膜4の膜厚の半分以上の膜厚を有しており、ひさし状のSOI膜5の端部の直下の窪みには、SOI膜5の底部および半導体基板1の主面に絶縁膜21が形成されている。したがって、前記窪み内は絶縁膜21が埋込まれているため、ダミーゲート電極8を構成するポリシリコン膜が形成される余地がない。このように、絶縁膜21の膜厚を厚くすればよりSOI膜5および半導体基板1間の絶縁性を高めることができる。特に、絶縁膜21がBOX膜4の膜厚の半分以上の膜厚を有していればひさし状のSOI膜5の端部の直下にはポリシリコン膜が形成されず、当該ポリシリコンの残渣が残らないため、後述するように、より効果的にSOI膜5と半導体基板1との間にリーク電流が流れることを防ぐことができる。

【0045】

なお、図2に示す変形例では、絶縁膜21はゲート絶縁膜22と同層の絶縁膜であり、ゲート絶縁膜22を形成した工程と同一の工程で絶縁膜21を形成しているものとする。図2では半導体基板1の主面に形成された絶縁膜21とSOI膜5の端部の表面に形成された絶縁膜21とが別々の膜として形成され、SOI膜5と半導体基板1との間で接触している構造を示しているが、絶縁膜21はSOI膜5の表面から半導体基板1の主面に亘って連続した層として形成されていてもよい。

【0046】

以下に、図37に示す比較例を用いて本実施の形態の半導体装置の効果について説明する。図37の断面図に示す比較例の半導体装置は、図1に示す本実施の形態の半導体装置とほぼ同様の構造を有しているが、ダミーゲート電極8、絶縁膜6およびダミーゲート電極8の側壁のサイドウォール11が形成されていない点で、図1に示す半導体装置と構造が異なる。なお、図37では図を見やすくするために拡散層、シリサイド層、エッチストッパ膜、層間絶縁膜、コンタクトプラグおよび配線などは図示していない。

【0047】

一つの活性領域上にSOI領域とバルクシリコン領域とが存在する場合、図37に示すように、BOX膜4およびSOI膜5の積層膜を形成すると、BOX膜4がウェットエッチングによりSOI領域側にエッチングされて後退するため、BOX膜4上のSOI膜5はバルクシリコン領域側に突き出したひさし状の形状となる。このように、前記積層膜の側面に窪みがある状態で半導体基板上にゲート電極を形成する目的でポリシリコン膜を形成した後に当該ポリシリコン膜をフォトリソグラフィ技術を用いたドライエッチング法によりパターニングすると、ひさし形状のSOI膜5の端部の直下にポリシリコン膜9pが残る虞がある。

【0048】

なお、ここではゲート電極9の下部のゲート絶縁膜7を形成する際に半導体基板1上に熱酸化法などにより形成された絶縁膜6bが、ポリシリコン膜9pおよびSOI膜5の間と、ポリシリコン膜9pおよび半導体基板1との間のそれぞれに形成されている。

【0049】

この場合、図1に示すようなダミーゲート電極8が形成されていないため、ゲート電極9を形成するためのドライエッチング工程またはその後の洗浄工程などでポリシリコン膜9pがBOX膜4から一部剥がれて浮いたような状態になることが予想され、また、ポリシリコン膜9pの存在に起因して半導体基板1上に残渣が残ることが予想される。このような残渣を残したまま完成した半導体装置では、ポリシリコン膜9pまたはポリシリコン膜9pの存在に起因して発生した残渣を介してSOI膜5と半導体基板1とが短絡(ショート)し、半導体装置が正常に動作しなくなる問題がある。

【0050】

また、前記残渣が形成されず、ひさし形状のSOI膜5と半導体基板1との間がポリシリコン膜9pおよび絶縁膜6bで埋込まれている場合であっても、ポリシリコン膜9pを介してSOI膜5および半導体基板1とが短絡する虞がある。すなわち、ゲート電極9の形成時のドライエッチング工程により一部が除去された絶縁膜6bがSOI膜5の端部の直下のSOI膜5および半導体基板1の表面に形成されていたとしても、絶縁膜6bの絶縁性は十分に保たれておらず、半導体装置の動作時にSOI膜5と半導体基板1との間で短絡が起きることが考えられる。

【0051】

図37に示すように、SOI膜5、絶縁膜6bおよびポリシリコン膜9pのバルクシリコン領域側の側壁にはサイドウォール11aが形成されているが、サイドウォール11aのような絶縁膜によりひさし形状のSOI膜5の側面が覆われていても、上述したような残渣に起因する短絡および絶縁膜6bの絶縁性の低下に起因する短絡が起こる虞がある。

【0052】

なお、ウェットエッチング法により加工されたBOX膜4の端部は、図38の比較例に示すように、SOI膜5の底面の端部に近い領域から除去され、ひさし状のSOI膜5の直下の半導体基板1の表面にはBOX膜4の一部が残るような形状となることが考えられる。図38は比較例として示す半導体装置の一部であって、図37に示すBOX膜4およびSOI膜5の積層膜の端部を拡大して示す断面図であり、ここでは前記積層膜と半導体基板1のみを示している。このようにひさし状の形状を有する前記積層膜は、SOI膜5の上部を含む半導体基板1上にポリシリコン膜からなるゲート電極を形成する工程で、図37に示すようにポリシリコン膜9pがひさし部分の下部に残ることとなり、これに起因して上述したような短絡現象が起こる。BOX膜4の端部が図38に示すような構造になる可能性があることは、図1に示す本実施の形態の半導体装置でも同様である。

【0053】

図38に示すBOX膜4の膜厚は10nmであり、SOI膜5の下部の絶縁膜をパターニングしてBOX膜4を形成する際は膜厚が10nmの前記絶縁膜を除去するウェットエッチングを行うため、SOI膜5の端部の直下のBOX膜4もSOI膜5の底面の端部から10nm程度の範囲が除去され、SOI膜5の端部がひさし状に突き出す形状となる。したがって、SOI膜5の底面に接するBOX膜4は、SOI膜5の底面の端部から10nm後退して形成される。

【0054】

また、上記したひさし部分に残る残渣による短絡の問題の他に、図39の比較例に示すように、SOI膜5とバルクシリコン領域である半導体基板1の主面が、素子分離領域2のような構造を隔てずに隣接することにより、SOI膜5および半導体基板1の表面のそれぞれの上部のエピタキシャル層上のシリサイド層14a同士が接触することに起因して短絡が起こる問題がある。図39は、比較例として示す半導体装置の断面図であり、図37と同様の構造を示しているが、図39では図37の構造に加えて、SOI膜5上のエピタキシャル層である拡散層12bと、半導体基板1上のエピタキシャル層である拡散層13aと、拡散層12bおよび13aのそれぞれの上部のシリサイド層14aと、サイドウォール11および11aとを示している。

【0055】

サイドウォール11はゲート電極9の側壁に形成された絶縁膜であり、サイドウォール11aはサイドウォール11を形成した際にBOX膜4およびSOI膜5からなる積層膜の側壁に形成された絶縁膜である。ここでは、BOX膜4とサイドウォール11aとの間のひさし部分の下部に絶縁膜6bおよびポリシリコン膜9pが形成されているものとする。

【0056】

図39に示すような半導体装置では、ゲート電極9、サイドウォール11および11aを形成した後にエピタキシャル成長法(選択成長法)によりSOI膜5の表面上およびバルクシリコン領域の半導体基板1の表面上にエピタキシャル層(選択成長層)を形成し、そのエピタキシャル層に不純物を注入することで、SOI膜5上に拡散層12bを形成し、半導体基板1上に拡散層13aを形成している。この場合、SOI領域に形成される拡散層12bとバルクシリコン領域に形成される拡散層13aが互いに近い領域に形成されるため、拡散層12b、13aのそれぞれの上部にシリサイド層14aを形成した場合、SOI領域およびバルクシリコン領域に形成されるシリサイド層14aが互いに接触し、またはそれらのシリサイド層14aが一体となって連続的に形成される虞がある。また、SOI領域およびバルクシリコン領域にエピタキシャル層を形成せず、SOI膜5および半導体基板1のそれぞれの上面に直接不純物を注入して拡散層を形成し、その表面にシリサイド層を形成した場合でも、SOI領域およびバルクシリコン領域に形成した前記シリサイド層が短絡する虞がある。

【0057】

このようにしてSOI領域およびバルクシリコン領域のシリサイド層14aが電気的に接続されると、SOI膜5と半導体基板1とが短絡することになるため、半導体装置が正常に動作しない問題が生じる。なお、この問題は前述したひさし状の構造が形成されているかどうかには関係なく生じるものであり、SOI膜5の直下であってBOX膜4の側壁にポリシリコン膜9pおよび絶縁膜6bが形成されておらず、SOI膜5およびBOX膜4の端部が揃っていても、シリサイド層14a同士が接触する問題は起こる。

【0058】

本来、SOI膜5は半導体基板1上にBOX4を隔てて形成されているため半導体基板1と絶縁されており、SOI領域とバルクシリコン領域との間には素子分離領域がなくてもよい。このため、SOI領域とバルクシリコン領域との境界に素子分離領域を形成することを省略することで、半導体装置の面積を低減することができる。

【0059】

しかし、図37および図39の2通りの比較例を用いて述べたように、BOX膜4のエッチングプロセスに起因して半導体基板1上に残渣などが残るとSOI膜5と半導体基板1とが短絡する虞があり、また、SOI膜5の表面および半導体基板1の上に形成されたそれぞれのエピタキシャル層上のシリサイド層14a同士が互いに接触して形成されることにより、SOI膜5と半導体基板1とが短絡する虞がある。

【0060】

そこで、本実施の形態の半導体装置では、図1に示すように、SOI領域とバルクシリコン領域との境界近傍の半導体基板上およびSOI膜5上に絶縁膜6を介してダミーゲート電極8を形成することにより、SOI膜5の端部の直下に形成された絶縁膜およびポリシリコン膜がエッチングまたは洗浄液などに晒されることを防いでいる。

【0061】

つまり、SOI領域とバルクシリコン領域との境界にダミーゲート電極8を形成する場合、ひさし状のSOI膜5の端部とその直下の半導体基板1との間に形成された絶縁膜6およびポリシリコン膜(ダミーゲート電極8)はSOI膜5の側壁に合わせてドライエッチされることはなく、ひさし状の形状のBOX膜4およびSOI膜5の積層膜の端部はダミーゲート電極8および絶縁膜6に覆われたまま半導体装置が完成する。したがって、ひさし状のSOI膜5の端部の直下に微量のポリシリコン膜が残ることにより半導体基板1上に残渣が発生し、前記残渣によってSOI膜5および半導体基板1が短絡することを防ぐことができる。

【0062】

また、図2に示す変形例の半導体装置では、絶縁膜21を高耐圧MOSFETHp用のゲート絶縁膜22と同一工程で形成した厚い膜とすることで、より効果的にSOI膜5と半導体基板1との短絡を防ぐことができる。

【0063】

また、本実施の形態の半導体装置では、ダミーゲート電極8およびその側壁のサイドウォール11を形成することにより、SOI領域およびバルクシリコン領域に形成されるシリサイド層14のそれぞれが近接して形成されることを防いでいる。

【0064】

つまり、ダミーゲート電極8およびその側壁のサイドウォール11を形成すると、サイドウォール11の表面にはシリサイド層は形成されないため、SOI領域の拡散層12およびその上部のシリサイド層14と、バルクシリコン領域の拡散層13およびその上部のシリサイド層14とを分離することができる。このため、SOI領域およびバルクシリコン領域のそれぞれのシリサイド層14が近接して短絡することを防ぐことができる。

【0065】

以上に述べたように、本実施の形態では、半導体装置の微細化などを目的として一つの活性領域内にSOI領域およびバルクシリコン領域を設けた場合に、SOI領域およびバルクシリコン領域の境界にダミーゲート電極を設けることにより、SOI膜および半導体基板が短絡することを防ぐことが可能となるため、半導体装置の信頼性を向上させることができる。また、これにより一つの活性領域内にSOI領域およびバルクシリコン領域を設けた場合に短絡が起こることを防ぎ、半導体素子の微細化の際に生じる前記短絡の問題を解消し、半導体装置の微細化により半導体装置の性能を向上することが可能となる。

【0066】

以下に、図3〜図18を用いて本実施の形態の半導体装置の製造方法を説明する。図3〜図18は本実施の形態の半導体装置の製造工程を示す断面図である。図3〜図18では、図の左側から右側にかけて順に半導体基板上部のSOI領域1Aおよびバルクシリコン領域1Bを示している。SOI領域1Aは半導体基板上に絶縁膜を介して半導体層が形成されるSOI構造を含む領域であり、ここではSOI領域1AにPチャネル型の低耐圧MOSFETを形成する工程について説明する。また、バルクシリコン領域1Bは前記SOI構造を構成する絶縁膜および半導体層から露出する半導体基板コンタクトプラグを接続する領域であり、または低耐圧MOSFETよりも高い電圧により駆動する高耐圧MOSFETを含むI/O部などであるものとする。低耐圧MOSFETは高耐圧MOSFETよりも小さい電流および電圧で駆動するトランジスタであり、半導体装置内のコア部においてスイッチングなどの用途に用いられるものである。なお、ここで言うコア部とは、上記したI/O部とは異なり、I/O部の素子よりも低い電流・電圧で駆動される素子により構成される回路などを含む領域である。

【0067】

まず、図3に示すように、例えば1〜10Ωcm程度の比抵抗を有するN型の単結晶シリコンなどからなる半導体基板(半導体ウエハ)1を準備する。次に、この半導体基板1を熱酸化してその表面に例えば厚さ11nm程度の絶縁膜2bを形成した後、その上層にCVD(Chemical Vapor Deposition)法などにより、例えば厚さ90nm程度の絶縁膜2cを形成(堆積)する。絶縁膜2bは酸化シリコンなどからなり、絶縁膜2cは窒化シリコン膜などからなる。その後、半導体基板1上の全面にフォトレジスト膜PR1を塗布する。

【0068】

次に、図4に示すように、投影露光装置を用いてフォトレジスト膜PR1を露光し、続いて現像を行った後に、フォトレジスト膜PR1の不要な部分を取り除き、半導体基板1上にフォトレジスト膜PR1からなるフォトレジストパターンを残す。ここでは、隣接するSOI領域1Aおよびバルクシリコン領域1Bが覆われるように前記フォトレジストパターンを残す。

【0069】

次に、図5に示すように、フォトレジスト膜PR1をエッチングマスクとして絶縁膜2c、絶縁膜2bおよび半導体基板1を順次ドライエッチングすることにより、素子分離形成予定領域の半導体基板1に、例えば深さ300nm程度の溝(素子分離用の溝)2aを形成した後、酸素プラズマなど用いたアッシング(灰化)を行うことでフォトレジスト膜PR1を除去する。溝2aは、素子分離用の溝であり、すなわち後述する素子分離領域2形成用の溝である。

【0070】

次に、図6に示すように、溝2aの内部(側壁および底部)を含む半導体基板1の主面上に、例えば厚み10nm程度の絶縁膜2dを形成する。それから、半導体基板1の主面上(すなわち絶縁膜2d上)に、溝2a内を埋めるように、絶縁膜2eをCVD法などにより形成(堆積)する。

【0071】

絶縁膜2dは、酸化シリコン膜または酸窒化シリコン膜からなる。絶縁膜2dが酸窒化シリコン膜の場合には、絶縁膜2d形成工程以降の熱処理によって溝2aの側壁が酸化することによる体積膨張を防止でき、半導体基板1に働く圧縮応力を低減できる効果がある。

【0072】

絶縁膜2eは、HDP−CVD(High Density Plasma CVD:高密度プラズマCVD)法により成膜された酸化シリコン膜、またはO3−TEOS酸化膜などである。なお、O3−TEOS酸化膜とは、O3(オゾン)およびTEOS(Tetraethoxysilane:テトラエトキシシラン、Tetra Ethyl Ortho Silicateともいう)を原料ガス(ソースガス)として用いて熱CVD法により形成した酸化シリコン膜である。

【0073】

続いて、半導体基板1を例えば1150℃程度で熱処理することにより、溝2aに埋込んだ絶縁膜2eを焼き締める。焼き締め前の状態では、O3−TEOS酸化膜よりもHDP−CVD法により成膜された酸化シリコン膜の方が緻密である。このため、絶縁膜2eがO3−TEOS酸化膜の場合、焼き締めによる絶縁膜2eの収縮により、半導体基板1に働く圧縮応力を低減できる効果がある。一方、絶縁膜2eがHDP−CVD法により成膜された酸化シリコン膜の場合には、絶縁膜2eがO3−TEOS酸化膜の場合に比べて、焼き締め時の絶縁膜2eの収縮が少ないため、後の工程で形成する素子分離領域2によって半導体基板1に働く圧縮応力が大きくなる。

【0074】

次に、図7に示すように、絶縁膜2eをCMP(Chemical Mechanical Polishing:化学的機械的研磨)法により研磨して絶縁膜2cを露出させ、熱リン酸などを用いたウエットエッチングにより絶縁膜2cを除去した後、フッ酸(HF)水溶液などを用いて溝2aの外部の絶縁膜2eおよび絶縁膜2bを除去し、溝2aの内部に絶縁膜2d、2eを残すことにより、絶縁膜2d、2eからなる素子分離領域(素子分離)2を形成する。

【0075】

前述したCMP法による研磨では、素子分離領域2の上面の高さは半導体基板1の主面の高さにまで後退せず、素子分離領域2の上面と絶縁膜2cの上面との高さが揃うことになる。その後に絶縁膜2c、2bを除去しているため、図7に示すように素子分離領域2の上面の高さは半導体基板1の主面の高さよりも高い状態となる。ただし、素子分離領域2を形成した時点で、素子分離領域2の上面の高さと半導体基板1の主面の高さとが同一の高さで揃っていても構わない。

【0076】

本実施の形態では、素子分離領域2は、STI(Shallow Trench Isolation)法により形成されるものとして説明したが、LOCOS(Local Oxidization of Silicon)法により形成しても構わない。後述するPチャネル型の低耐圧MOSFETLpは、素子分離領域2で規定された(囲まれた)活性領域内に形成される。SOI領域1Aおよびバルクシリコン領域1Bは前記活性領域内に含まれる。

【0077】

次に、図8に示すように、半導体基板1の主面から所定の深さに渡ってNウエル3を形成する。Nウエル3は、半導体基板1の主面に例えばホウ素(B)などのN型の不純物をイオン注入することなどによって形成することができる。なお、図8以降の図では、図を見やすくするために積層構造を有する素子分離領域2を一層の膜として示す。

【0078】

その後、半導体基板1の主面上に、絶縁膜4aおよび半導体層5aを順次形成する。絶縁膜4aは酸化シリコン膜などからなり、例えば熱酸化法、ウェット酸化法、またはCVD法などを用いて、素子分離領域2から露出している半導体基板1の主面に接して形成する。半導体層5aは例えばシリコン膜からなり、絶縁膜4a上および素子分離領域2上にCVD法などを用いて形成する。絶縁膜4aおよび半導体層5aの膜厚はそれぞれ例えば10nmとする。

【0079】

次に、図9に示すように、フォトリソグラフィ技術およびウェットエッチング法を用いて、半導体層5aをパターニングした後に絶縁膜4aをパターニングし、SOI領域1Aの半導体基板1の主面上に絶縁膜4aからなるBOX膜4および半導体層5aからなるSOI膜5を残し、バルクシリコン領域1Bの半導体基板1の主面を露出する。このとき、BOX膜4を形成するエッチング工程では、半導体基板1の主面がエッチング工程により受けるダメージを低減するためにドライエッチング法ではなくウェットエッチング法を用いる必要がある。

【0080】

BOX膜4の側面はSOI膜5の側面と平面視において重なるように揃うことが望ましいが、BOX膜4を形成するエッチング工程はSOI膜5をマスクとして行われ、ウェットエッチング法は等方性のあるエッチング方法であるため、膜厚が10nmの絶縁膜4aを除去する工程では、SOI領域1Aおよびバルクシリコン領域1Bの境界部分のSOI膜5の側面の直下からSOI領域1A方向に絶縁膜4aの側面が後退する。つまり、SOI膜5およびBOX膜4からなる積層膜のバルクシリコン領域1B側の端部は、SOI膜5の端部の方がBOX膜4の端部よりも突出し、BOX膜4が後退した領域が窪んだひさし状の構造となる。

【0081】

次に、図10に示すように、SOI領域1AのSOI膜5の表面およびバルクシリコン領域1Bの半導体基板の主面に酸化シリコン膜からなる絶縁膜6aを形成し、続いて半導体基板1の主面の全面上に、例えばCVD法を用いてポリシリコン膜8aを形成(堆積)する。絶縁膜6aは例えば熱酸化法またはウェット酸化法を用いて形成するため、前記ひさし状の構造を有し、露出しているSOI膜5の端部の上面、側面および底面に形成され、ひさし構造のSOI膜5の端部の直下に露出している半導体基板1の主面にも形成される。

【0082】

このとき、絶縁膜6aの膜厚はBOX膜4の膜厚の半分未満の厚さであり、BOX膜4が後退して形成された窪みには絶縁膜6aにより完全に埋込まれておらず、ポリシリコン膜8aが埋込まれている。ここでは、ひさし状の構造を有するSOI膜5の端部と半導体装置の間には、絶縁膜6a、ポリシリコン膜8aおよび絶縁膜6aが順に形成されるものとする。

【0083】

次に、図11に示すように、フォトリソグラフィ技術およびドライエッチング法を用いて、ポリシリコン膜8aおよび絶縁膜6aをパターニングし、SOI領域1AのSOI膜5の上面と、バルクシリコン領域1Bの半導体基板1の主面とを露出させる。これにより、SOI領域1AのSOI膜5上に絶縁膜6aからなるゲート絶縁膜7を介してポリシリコン膜8aからなるゲート電極9を形成する。また、同工程により、SOI領域1Aおよびバルクシリコン領域1Bの境界近傍のSOI膜5上および半導体基板1上に絶縁膜6aからなる絶縁膜6を介してポリシリコン膜8aからなるダミーゲート電極8を形成する。その後、ゲート電極9およびダミーゲート電極8を形成した際のドライエッチングにより発生したエッチング残渣などを除去するため、半導体基板1を薬液および純水などを用いて洗浄する。

【0084】

このとき、絶縁膜6およびその上のダミーゲート電極8はSOI領域1Aおよびバルクシリコン領域1Bの境界に跨って形成されるため、ひさし状の構造を有するBOX膜4およびSOI膜5からなる積層膜の端部は絶縁膜6およびダミーゲート電極8により覆われる。

【0085】

次に、図12に示すように、バルクシリコン領域1Bを覆い、SOI領域1Aを露出するフォトレジスト膜PR2を半導体基板1上に形成する。なお、フォトレジスト膜PR2はダミーゲート電極8の上面の一部を覆っているものとする。続いて、フォトレジスト膜PR2をマスクとして、ゲート電極9から露出しているSOI膜5にイオン注入法を用いてP型の不純物(例えばB(ホウ素))を注入する。これにより、ゲート電極9のゲート長方向における両側のSOI膜5内に、P型の不純物(例えばB(ホウ素))が比較的低濃度で導入された半導体層であるLDD層10を形成する。

【0086】

次に、図13に示すように、フォトレジスト膜PR2を除去した後、半導体基板1の主面の全面上に例えばCVD法を用いて窒化シリコン膜および酸化シリコン膜を順次形成する。続いて、ドライエッチング法を用いて前記酸化シリコン膜および前記窒化シリコン膜を順次除去して半導体基板1およびSOI膜5のそれぞれの上面を露出させることで、ゲート電極9およびダミーゲート電極8のそれぞれの側壁に前記酸化シリコン膜および前記窒化シリコン膜の積層膜からなるサイドウォール11を自己整合的に形成する。ダミーゲート電極8はSOI膜5の上面から半導体基板1の上面に亘って連続的に形成されているため、ダミーゲート電極8の一方の側壁のサイドウォール11は半導体基板1の上面に接し、もう一方の側壁のサイドウォール11はSOI膜5の上面に接して形成される。

【0087】

その後、ゲート電極9、ダミーゲート電極8およびサイドウォール11から露出している半導体基板1およびSOI膜5のそれぞれの上面に、エピタキシャル成長法(選択成長法)を用いてエピタキシャル層(選択成長層)12aを形成する。このとき、ひさし状の構造を有するBOX膜4およびSOI膜5からなる積層膜の端部は絶縁膜6、ダミーゲート電極8およびダミーゲート電極8の側壁のサイドウォール11により覆われているため、当該積層膜の端部の近傍にはエピタキシャル層12aは形成されない。

【0088】

次に、図14に示すように、フォトリソグラフィ技術およびイオン注入法を用いて、SOI領域1Aおよびバルクシリコン領域1Bの領域のエピタキシャル層12aに、P型の不純物(例えばB(ホウ素))およびN型の不純物(例えばP(リン))をそれぞれ打ち分ける。SOI領域1Aのゲート電極9の両側のエピタキシャル層12aは、P型の不純物(例えばB(ホウ素))が比較的高濃度で導入されることで拡散層12となる。また、バルクシリコン領域1Bのエピタキシャル層12aは、N型の不純物(例えばP(リン))が比較的高濃度で導入されることにより、拡散層13となる。これにより、SOI領域1Aには、ゲート電極9、LDD層10および拡散層12を含む低耐圧MOSFETLpが形成される。また、拡散層13の直下の半導体基板1の主面には、拡散層13を形成する際にバルクシリコン領域1Bの前記エピタキシャル層に注入した不純物が前記エピタキシャル層を通過して注入されており、半導体基板1の主面にNウエル3よりも高い不純物濃度を有する半導体層13bが形成されている。

【0089】

拡散層12はLDD層10よりも高い不純物濃度を有しており、拡散層12およびLDD層10は低耐圧MOSFETLpのソース・ドレイン領域を構成している。また、バルクシリコン領域1Bでは、Nウエル3上にNウエル3よりもN型の不純物の濃度が高い拡散層13が形成されている。拡散層13は半導体基板1に電位を供給するためのボディ端子として機能する半導体領域である。その後、イオン注入した不純物の拡散などを目的として半導体基板1を熱処理する。なお、拡散層12を形成するためのP型の不純物(例えばB(ホウ素))のイオン注入工程と、拡散層13を形成するためのN型の不純物(例えばP(リン))のイオン注入工程とは、どちらを先に行ってもよい。

【0090】

次に、図15に示すように、周知のサリサイド技術により拡散層12、13、ゲート電極9およびダミーゲート電極8のそれぞれの上面にシリサイド層14を形成する。このとき形成するシリサイド層14の部材は、NiSi(ニッケルシリサイド)またはCoSi(コバルトシリサイド)などとすることができる。シリサイド層14は、半導体基板1上に形成したNi(ニッケル)などを含む金属膜を、熱処理により下部の半導体層と反応させることで形成する。シリサイド層14を形成した際、シリサイド層14と拡散層12または13とからなる積層膜の厚さは、シリサイド層14を形成する前の拡散層12または13の厚さよりも厚くなる。このとき、ひさし状の構造を有するBOX膜4およびSOI膜5からなる積層膜の端部は絶縁膜6およびダミーゲート電極8により覆われており、ダミーゲート電極8はサイドウォール11に挟まれているため、当該積層膜の端部の近傍にはシリサイド層14は形成されない。したがって、シリサイド層14はSOI領域1Aおよびバルクシリコン領域1Bの境界においてダミーゲート電極8およびその側壁のサイドウォール11を隔てて分断され、拡散層12上のシリサイド層14と拡散層13上のシリサイド層14とが接触することはない。

【0091】

次に、図16に示すように、半導体基板1の主面上に、低耐圧MOSFETLp、ダミーゲート電極8およびシリサイド層14を覆うようにエッチストッパ膜15および層間絶縁膜16を順次形成する。エッチストッパ膜15は、例えば酸化シリコン膜の単体膜または薄い窒化シリコン膜からなり、その上の層間絶縁膜16は厚い酸化シリコン膜からなる。エッチストッパ膜15および層間絶縁膜16は例えばCVD法により形成し、その後、層間絶縁膜16の表面を、例えばCMP法を使用して平坦化する。

【0092】

次に、図17に示すように、層間絶縁膜16上に形成したフォトレジスト膜(図示しない)をエッチングマスクとして用いて、エッチストッパ膜15および層間絶縁膜16をドライエッチングすることにより、エッチストッパ膜15および層間絶縁膜16を貫通する複数のコンタクトホール(貫通孔)を形成する。前記複数のコンタクトホールは、拡散層12、13およびゲート電極9のそれぞれの上部のシリサイド層14に達する貫通孔である。ただし、後の工程で完成する半導体装置において、ダミーゲート電極8は電気的に機能しない膜なのでダミーゲート電極8の上部のシリサイド層14を露出するコンタクトホールを形成する必要はない。

【0093】

続いて、前記複数のコンタクトホール内に、タングステン(W)などからなる導電性のコンタクトプラグ(接続用導体部)17を形成する。コンタクトプラグ17を形成するには、例えば、コンタクトホールの底部および側壁を含む層間絶縁膜16上に、バリア導体膜(例えばチタン膜、窒化チタン膜、あるいはそれらの積層膜)を形成する。それから、前記バリア導体膜上にタングステン膜などからなる主導体膜を形成して前記コンタクトホールを埋込み、層間絶縁膜16上の不要な前記主導体膜および前記バリア導体膜をCMP法またはエッチバック法などによって除去することにより、コンタクトプラグ17を形成する。なお、図面の簡略化のために、図17ではコンタクトプラグ17を構成するバリア導体膜および主導体膜(タングステン膜)を一体化して示している。

【0094】

次に、図18に示すように、コンタクトプラグ17が埋込まれた層間絶縁膜16上に、エッチストッパ膜(エッチングストッパ用絶縁膜)18および配線形成用の層間絶縁膜19を順次形成する。エッチストッパ膜18は、層間絶縁膜19への溝加工の際にエッチングストッパとなる膜であり、層間絶縁膜19に対してエッチング選択性を有する材料を用い、例えば、エッチストッパ膜18を窒化シリコン膜とし、層間絶縁膜19を酸化シリコン膜とすることができる。

【0095】

その後、シングルダマシン法により第1層目の配線を形成する。まず、フォトレジスト膜(図示しない)をマスクとしたドライエッチングによって層間絶縁膜19およびエッチストッパ膜18の所定の領域にコンタクトプラグ17を露出する複数の配線溝を形成した後、半導体基板1の主面上に例えば窒化チタン膜、タンタル膜または窒化タンタル膜などからなるバリアメタル膜を形成する。続いて、CVD法またはスパッタリング法などによりバリアメタル膜上に銅のシード層を形成し、さらに電解めっき法などを用いてシード層上に銅めっき膜を形成し、前記銅めっき膜により前記配線溝の内部を埋込む。それから、配線溝以外の領域の銅めっき膜、シード層およびバリアメタル膜をCMP法により除去して、銅を主導電材料とする第1層目の配線20を形成する。なお、図面の簡略化のために、図18では、配線20を構成する銅めっき膜、シード層およびバリアメタル膜を一体化して示してある。

【0096】

SOI領域1Aの配線20は、コンタクトプラグ17を介して低耐圧MOSFETLpのソース・ドレイン領域およびゲート電極9に電気的に接続されている。バルクシリコン領域1Bの配線20は、コンタクトプラグ17、シリサイド層14および拡散層13を介して半導体基板1に電気的に接続されている。また、その後、デュアルダマシン法などにより配線20上に2層目以降の配線を形成することで本実施の形態の半導体装置が完成するが、ここでは2層目以降の配線の図示およびその製造工程の説明は省略する。また、配線20はダマシン配線に限定されず、配線用の導電体膜をパターニングして形成することもでき、その場合、配線20は例えばタングステン配線またはアルミニウム配線などとすることもできる。

【0097】

このように、隣り合う素子分離領域に挟まれた一つの活性領域内にSOI領域およびバルクシリコン領域が隣接して存在する半導体装置を製造する場合、図37および図38を用いて説明したように、SOI領域およびバルクシリコン領域の境界近傍においてダミーゲート電極8(図18参照)を形成せずにゲート電極9を形成すると、ひさし状のSOI膜5の端部の下の窪みにゲート電極9を形成するためのポリシリコン膜9pが残る。この状態で半導体装置の製造工程を続けると、ポリシリコン膜9pが残渣となって半導体基板1上に残り、当該残渣を介するなどしてSOI膜5と半導体基板1とが短絡する虞がある。

【0098】

図37のような構造は、図11を用いて説明したパターニング工程においてSOI領域およびバルクシリコン領域の境界近傍にダミーゲート電極8を形成せず、その他の領域(例えばSOI領域)にゲート電極をドライエッチング法により加工形成することで形成される。図37に示すようなポリシリコン膜9pに起因して残渣が発生すれば、SOI膜5および半導体基板1が残渣を介して短絡することなどが考えられ、完成した半導体装置が正常に動作しなくなる虞がある。

【0099】

また、図39を用いて説明したように、前記残渣による短絡などの不具合が起こらなかったとしても、SOI膜5と半導体基板1とがSOI領域とバルクシリコン領域との境界において素子分離領域のように幅が広い絶縁体を隔てず極近い領域で隣接する場合、半導体基板1の表面に形成されたエピタキシャル層である拡散層13aが、SOI膜5およびSOI膜5の表面に形成されたエピタキシャル層である拡散層12bに接近する。この場合、SOI膜5および拡散層12bと、拡散層13aとのそれぞれの表面に形成されたシリサイド層14a同士が接触し、または一体化して形成されることで、SOI膜5および半導体基板1が短絡し、完成した半導体装置が正常に動作しなくなる。

【0100】

このような短絡が起こることに起因して半導体装置の信頼性が低下することを防ぐため、本実施の形態の半導体装置の製造工程では、図11に示すように、SOI領域とバルクシリコン領域との境界近傍の半導体基板上およびSOI膜5上に絶縁膜6を介してダミーゲート電極8を形成することにより、SOI膜5の端部の直下に形成された絶縁膜およびポリシリコン膜がエッチングまたは洗浄液などに晒されることを防いでいる。

【0101】

これにより、ひさし状のSOI膜5の端部の直下に微量のポリシリコン膜が残ることに起因して半導体基板1上に残渣が発生し、前記残渣によってSOI膜5および半導体基板1が短絡することを防ぐことができる。

【0102】

また、本実施の形態の半導体装置の製造工程では、図16に示すように、ダミーゲート電極8およびその側壁のサイドウォール11を形成することにより、SOI領域およびバルクシリコン領域に形成されるシリサイド層14のそれぞれが近接して形成されることを防いでいる。

【0103】

つまり、ダミーゲート電極8およびその側壁のサイドウォール11を形成すると、サイドウォール11の表面にはシリサイド層は形成されないため、SOI領域の拡散層12およびその上部のシリサイド層14と、バルクシリコン領域の拡散層13およびその上部のシリサイド層14とを分離することができる。よって、SOI領域およびバルクシリコン領域のそれぞれのシリサイド層14が近接して短絡することを防ぐことができる。

【0104】

したがって、本実施の形態の半導体装置の製造工程では、半導体装置の微細化などを目的として一つの活性領域内にSOI領域およびバルクシリコン領域を設けた場合に、SOI領域およびバルクシリコン領域の境界にダミーゲート電極を設けることにより、SOI膜および半導体基板が短絡することを防ぐことが可能となるため、半導体装置の信頼性を向上させることができる。また、これにより一つの活性領域内にSOI領域およびバルクシリコン領域を設けた場合に短絡が起こることを防ぎ、半導体素子の微細化の際に生じる前記短絡の問題を解消することができるため、半導体装置の微細化により半導体装置の性能を向上することが可能となる。

【0105】

また、本実施の形態の半導体装置の製造方法の変形例として、ダミーゲート電極8の下面に接する絶縁膜の膜厚をゲート絶縁膜7よりも厚くして、より効果的にSOI膜5と半導体基板1との短絡を防ぐことが考えられる。この場合の半導体装置の製造工程を図3〜図9および図19〜図23を用いて説明する。図19〜図23は本実施の形態の半導体装置の製造工程の変形例を説明する断面図である。

【0106】

まず、図3〜図9を用いて説明した工程を行った後、半導体基板1上に厚さが異なる2種類の絶縁膜を半導体基板1の上面に形成する。つまり、図19に示すように、半導体基板1の主面の全面に熱酸化法、ウェット酸化法またはCVD法などを用いて、比較的膜厚が厚い絶縁膜21aを形成した後に、フォトリソグラフィ技術およびウェットエッチング法などを用いてSOI領域1Aの絶縁膜21aを除去し、バルクシリコン領域1Bには絶縁膜21aを残す。ただし、このときにSOI膜5のバルクシリコン領域1B側の端部に形成された絶縁膜21aは除去しない。なお、絶縁膜21aは熱酸化法、ウェット酸化法により形成されるため、形成時には半導体基板1上に露出する半導体基板1の上面およびSOI膜5の表面に形成される。したがって、SOI膜5のバルクシリコン領域1B側の端部では、SOI膜5の上面、側壁および底面に亘って絶縁膜21aが連続的に形成され、その下部では半導体基板1の主面にも絶縁膜21aが形成される。その後、例えば熱酸化法またはウェット酸化法などを用いて半導体基板1の主面を酸化し、絶縁膜21aから露出するSOI膜5の上面に、絶縁膜21aよりも膜厚が薄い絶縁膜6aを形成する。絶縁膜6a、21aは例えば酸化シリコンからなる膜である。

【0107】

ここではBOX膜4の膜厚を10nmとし、絶縁膜21aの膜厚を5nmとしており、また、SOI領域1Aおよびバルクシリコン領域1Bの境界近傍におけるSOI膜5およびBOX膜4からなる積層膜の端部のひさし構造では、SOI膜5と半導体基板1との間隔がBOX膜4の膜厚となっている。SOI膜5と半導体基板1との間のSOI膜5の底面および半導体基板1の上面に形成された絶縁膜21aは、それぞれBOX膜4の膜厚の値の半分以上の膜厚を有しているため、SOI膜5と半導体基板1との間には絶縁膜21aが完全に埋込まれている。

【0108】

次に、図20に示すように、半導体基板1の主面上の全面に例えばCVD法を用いてポリシリコン膜を形成(堆積)した後、フォトリソグラフィ技術およびドライエッチング法を用いて前記ポリシリコン膜およびその下部の絶縁膜6a、21aを加工(パターニング)することで、前記ポリシリコン膜からなるゲート電極9、ダミーゲート電極8およびゲート電極23を形成する。また、同一の工程により、絶縁膜6aからなるゲート絶縁膜7をゲート電極9とSOI膜5との間に形成し、絶縁膜21aからなる絶縁膜21を、ダミーゲート電極8とSOI膜5との間およびダミーゲート電極8と半導体基板1との間に形成し、絶縁膜21aからなるゲート絶縁膜22をバルクシリコン領域1Bのゲート電極23と半導体基板1との間に形成する。

【0109】

絶縁膜21およびゲート絶縁膜22は絶縁膜21aからなるため、絶縁膜6aからなるゲート絶縁膜7よりも厚い膜厚を有している。また、ゲート電極23はゲート電極9よりもゲート長が大きく、その下部のゲート絶縁膜22はゲート絶縁膜7よりもゲート幅方向における幅が広い。

【0110】

次に、図12を用いて説明した工程を行うことでSOI領域1AにLDD層10を形成した後、図21に示すように、SOI領域1Aをフォトレジスト膜(図示しない)で覆い、続いて、バルクシリコン領域1Bに露出する半導体基板1の主面に、ゲート電極23をマスクとしてP型の不純物(例えばB(ホウ素))をイオン注入法により注入することにより、ゲート電極23の横の半導体基板1の主面にLDD層24を形成する。なお、LDD層10およびLDD層24はどちらを先に形成してもよく、同一工程により形成してもよい。

【0111】

次に、図13を用いて説明したエピタキシャル層の製造工程を行った後、図22に示すように、ゲート電極9、22のそれぞれの横に形成されたエピタキシャル層にP型の不純物(例えばB(ホウ素))を高い濃度でイオン注入することにより、前記エピタキシャル層からなるP型の拡散層12、25をゲート電極9、22のそれぞれの横に形成する。なお、LDD層10、24を形成した工程と同様に、拡散層12および拡散層25を形成する際には、それぞれの拡散層を別のイオン注入工程により形成しても構わない。

【0112】

これにより、SOI領域1AにはLDD層10、拡散層12およびゲート電極9を含む低耐圧MOSFETLpが形成され、バルクシリコン領域1BにはLDD層24、拡散層25およびゲート電極23を含む高耐圧MOSFETHpが形成される。高耐圧MOSFETHpは低耐圧MOSFETLpよりも大きい膜厚を有するゲート絶縁膜22と、低耐圧MOSFETLpよりも大きいゲート長を有するゲート電極23を含んでいる。これは、高耐圧MOSFETHpが低耐圧MOSFETLpよりも高い電圧により駆動するトランジスタであるためである。ここでは、高耐圧MOSFETHpは半導体装置の外部に出力し、または半導体装置の外部から入力される電流を制御するI/O部において用いられる半導体素子とする。

【0113】

その後の工程は、図15〜図18を用いて説明した工程と同様の工程を行うことで、図23に示す半導体装置が完成する。このとき、バルクシリコン領域1Bでは、高耐圧MOSFETHpのソース・ドレイン領域を構成するLDD層24および拡散層25に所定の電位を供給するため、拡散層25の上面のシリサイド層14に達するコンタクトプラグ17およびその上部の配線20を形成する。また、図示しない領域では、ゲート電極23上のシリサイド層14に接続されるコンタクトプラグ17も形成する。なお、図18に示したような半導体基板1の電圧を制御する目的で形成されたコンタクトプラグ17および配線20は、図23に示していない他の領域に形成されているものとする。

【0114】

このようにして形成した本実施の形態の半導体装置は、絶縁膜21を高耐圧MOSFETHp用のゲート絶縁膜22と同一工程で形成した厚い膜とすることで、図18に示す構造の半導体装置より効果的にSOI膜5と半導体基板1との短絡を防ぐことを可能としている。特に、絶縁膜21の膜厚をBOX膜4の膜厚の2分の1以上の厚さとすることは、SOI膜5の一方の端部の直下のBOX膜4が後退した領域に絶縁膜21を完全に埋込み、当該SOI膜5の直下にポリシリコン膜が入り込むことを防ぐことができるため、SOI膜5と半導体基板1とが短絡することを防ぐ観点から好ましい。

【0115】

本実施の形態では、MOSFETのゲート電極の横にエピタキシャル層を形成し、当該エピタキシャル層をソース・ドレイン領域とする半導体層装置について説明したが、エピタキシャル層を形成せず、SOI膜またはバルクシリコン領域の半導体基板の主面に直接イオン注入を行ってLDD層よりも不純物濃度が高い拡散層を形成してもよい。この場合であっても、図39に示す構造と同様にSOI領域およびバルクシリコン領域の境界にダミーゲート電極を形成しなければ、前記拡散層が形成されたSOI膜および半導体基板の表面のシリサイド層同士が短絡する虞がある。これに対し、図1に示すようにダミーゲート電極8およびその両側のサイドウォール11を形成することにより、SOI領域およびバルクシリコン領域のそれぞれのシリサイド層14同士が電気的に接続されることを防ぐことができる。

【0116】

また、図24に示すように、本実施の半導体装置の変形例として、バルクシリコン領域において半導体基板1に電位を供給するコンタクトプラグ17aを、平面視においてダミーゲート電極8に重なるように形成した構造を示す。つまり、コンタクトプラグはダミーゲート電極8と、ダミーゲート電極8およびその側壁のサイドウォール11から露出するバルクシリコン領域1Bの半導体基板1の主面とに平面視において重なるように形成されている。言い換えれば、コンタクトプラグ17aはダミーゲート電極8の直上およびバルクシリコン領域1Bに亘って形成され、ダミーゲート電極8上のシリサイド層14およびバルクシリコン領域1Bのシリサイド層14に接続されるている。これにより、コンタクトプラグ17aがダミーゲート電極8と電気的に接続されても、ダミーゲート電極8自体は他の素子と絶縁されているため問題はない。コンタクトプラグ17aがダミーゲート電極8の直上に形成されておらず、ダミーゲート電極8の上部のシリサイド層14の側面とコンタクトプラグ17の側面とが接触するなどしていても同様である。

【0117】

また、図示は省略するが、図24と異なり、半導体基板1に電位を供給するコンタクトプラグ17aはダミーゲート電極8から離れて絶縁され、SOI領域の低耐圧MOSFETLpのダミーゲート電極8に近い方のソース・ドレイン領域に電位を供給するコンタクトプラグ17がダミーゲート電極8に接触し、電気的に接続されていても同様に問題はない。つまり、ダミーゲート電極8が半導体装置内の回路を構成せず、他の素子および配線などから絶縁されているため、ダミーゲート電極8の隣接するコンタクトプラグ17または17aのいずれか一方に接続されたとしても半導体装置の動作に影響はない。このため、ダミーゲート電極8の横の一方のコンタクトプラグとダミーゲート電極8との間の距離を十分に離して互いに接触しないようにする必要がなく、マージンを小さくすることが可能となるため、半導体装置の微細化が容易となる。

【0118】

(実施の形態2)

本実施の形態では、SOI領域にシリサイド層を形成する際に、バルクシリコン領域の半導体層上にシリサイド層が形成されることを防ぐことにより、SOI領域およびバルクシリコン領域のそれぞれのシリサイド層同士が接続することで短絡が起きることを防ぐことができる半導体装置について説明する。

【0119】

図39を用いて説明したように、SOI膜5と半導体基板1とは、SOI領域およびバルクシリコン領域のそれぞれのシリサイド層14a同士が電気的に接続されることにより短絡する問題がある。前記実施の形態では、SOI領域およびバルクシリコン領域の境界にダミーゲート電極を形成し、SOI領域およびバルクシリコン領域のシリサイド層を分離することにより前記短絡を防ぐことを記載したが、本実施の形態ではダミーゲート電極を形成せず、バルクシリコン領域にシリサイド層を形成しないことで前記短絡が起こることを防ぐ。なお、以下に示す図25および図26は、本実施の形態の半導体装置の製造工程を説明する断面図である。

【0120】

上述したような半導体装置を形成する方法としては、まず、図3〜図14を用いて説明した工程と同様の工程を行った後に、図25に示すように、例えば酸化シリコンからなるマスク材である絶縁膜26をバルクシリコン領域1Bの半導体基板1上に形成し、バルクシリコン領域の拡散層13を絶縁膜26により覆う。なお、本実施の形態ではダミーゲート電極は形成しないため、図11を用いて説明した工程ではゲート電極9およびゲート絶縁膜7のみを形成し、ダミーゲート電極8およびその下部の絶縁膜6は形成しない。したがって、図37に示す半導体装置と同様に、SOI膜5の端部の直下であってBOX膜4の側壁にはポリシリコン膜9pおよび絶縁膜6bが残っているものとする。また、図13のサイドウォール形成工程では、SOI膜5とその端部の直下のポリシリコン膜9pおよび絶縁膜6bとからなる積層膜の側壁に自己整合的にサイドウォール11aが形成されているものとする。

【0121】

絶縁膜26は、例えば図14の工程の後に、半導体基板1の主面の全面上にCVD法などを用いて酸化シリコン膜を形成し、続いてフォトリソグラフィ技術およびドライエッチング法を用いてバルクシリコン領域1B以外の領域の前記酸化シリコン膜を除去することで形成する。図25ではSOI領域1Aおよびバルクシリコン領域1Bの境界近傍の絶縁膜26の端部がサイドウォール11a上に位置するような構造を示しているが、絶縁膜26のSOI領域1A側の端部は、バルクシリコン領域1Bの拡散層13を覆い、SOI領域1Aの拡散層12を覆わない位置であれば、どの位置にあっても構わない。つまり、絶縁膜26の前記端部はサイドウォール11aの直上か、拡散層12から露出するSOI膜5の直上にあるものとする。

【0122】

次に、図15〜図18を用いて説明した工程と同等の工程を行うことで、図26に示す本実施の形態の半導体装置が完成する。つまり、図25に示す構造を形成した後、絶縁膜26によりバルクシリコン領域1Bを覆った状態で半導体基板1の主面の全面上に例えばNi(ニッケル)などからなる金属膜を形成した後に半導体基板1を複数回熱処理することにより、絶縁膜26から露出している拡散層12の表面にシリサイド層14を形成する。このとき、拡散層13は絶縁膜(マスク材)26に覆われており前記金属膜に接していないため、拡散層13の表面にはシリサイド層は形成されない。このように、絶縁膜などを用いて一部の半導体層の表面にシリサイド層が形成されないようにすることを、ここではシリサイドプロテクションと呼ぶ。

【0123】

その後、絶縁膜26を残した状態で、エッチストッパ膜15、層間絶縁膜16を形成した後に、SOI領域1Aのシリサイド層14に達するコンタクトプラグ17と、バルクシリコン領域1Bの拡散層13の上面に達し、半導体基板1に電位を供給するためのコンタクトプラグ17とを形成し、続いて配線20を形成する。バルクシリコン領域1Bにコンタクトプラグ17を形成する際は、絶縁膜26、エッチストッパ膜15および層間絶縁膜16を貫通するコンタクトホールを形成する。

【0124】

このようにして形成した半導体装置では、シリサイドプロテクションを行うことでバルクシリコン領域1Bの拡散層13の上面にシリサイド層が形成されないため、図39に示したようにSOI領域およびバルクシリコン領域のそれぞれのシリサイド層14a同士が接続されることによりSOI膜5と半導体基板1とが短絡することを防ぐことができる。

【0125】

これにより、半導体装置が正常に動かなくなることを防ぐことが可能となるため、半導体装置の信頼性を向上させることができる。

【0126】

なお、図25および図26ではバルクシリコン領域1Bの拡散層13を絶縁膜26で完全に覆い、拡散層13の上面にシリサイド層を一切形成しない場合について説明したが、絶縁膜26を形成する領域をSOI領域1Aおよびバルクシリコン領域1Bの境界近傍のみに限り、拡散層13の上面の一部にシリサイド層を形成してもよい。つまり、SOI領域1Aおよびバルクシリコン領域1Bのそれぞれに形成されたシリサイド層同士が、SOI領域1Aおよびバルクシリコン領域1Bの境界において互いに接続されることを防げば上記効果が得られるため、前記境界近傍のバルクシリコン領域にシリサイド層が形成されていなければ、バルクシリコン領域内の他の領域にシリサイド層が形成されていてもよい。この場合は図18と同様に、バルクシリコン領域1Bではコンタクトプラグ17をシリサイド層14を介して拡散層13および半導体基板1に電気的に接続すればよい。

【0127】

また、SOI領域1Aおよびバルクシリコン領域1Bの境界近傍のみに絶縁膜26を形成する場合には、図19〜図23を用いて説明した工程と同様の工程を行い、バルクシリコン領域1BにMOSFETを形成することも可能である。なお、このとき前記境界近傍には絶縁膜26を形成しているため、前記実施の形態1で説明したダミーゲート電極は形成しない。

【0128】

(実施の形態3)

本実施の形態では、SOI領域およびバルクシリコン領域の境界近傍のひさし構造部を、膜厚が厚い絶縁膜により覆う半導体装置について説明する。以下に示す図27〜図29は本実施の形態の半導体装置の製造工程を示す断面図である。

【0129】

本実施の形態の半導体装置の製造工程では、まず、図3〜図9および図19を用いて説明した工程と同様の工程を行うことにより、SOI領域およびバルクシリコン領域の境界近傍のひさし構造部のBOX膜が後退した窪みに、比較的厚い膜厚を有する絶縁膜21aを埋込む。前記実施の形態1の半導体装置の変形例を図19〜図23を用いて説明したように、絶縁膜21aの膜厚はBOX膜4の膜厚の半分(2分の1)以上の膜厚を有しているため、前記窪みには絶縁膜21aが完全に埋込まれる。つまり、BOX膜4の膜厚が10nmの場合は、絶縁膜21aの膜厚は5nm以上あるものとする。

【0130】

次に、図27に示すように、半導体基板1の主面の全面上にCVD法などを用いてポリシリコン膜を形成した後、フォトリソグラフィ技術およびドライエッチング法を用いて前記ポリシリコン膜を加工し、SOI領域1Aの絶縁膜6aの直上にゲート電極9を形成する。その後、バルクシリコン領域1Bを覆い酸化シリコン膜などからなる絶縁膜27をフォトリソグラフィ技術およびドライエッチング法を用いて形成する。絶縁膜27はSOI領域1Aおよびバルクシリコン領域1Bの境界近傍の絶縁膜21aを覆うように形成されており、SOI膜5の直上で終端している。図27では、SOI領域1A側の絶縁膜27の側壁が絶縁膜21aの側壁と平面視において重なる構造を示しているが、絶縁膜27の端部はSOI膜5の直上に位置しており、SOI膜5上の絶縁膜27に覆われていない領域にMOSFETを形成する領域が確保されていればよい。

【0131】

次に、図28に示すように、SOI領域1Aに対し、図12〜図15を用いて説明した工程を行うことにより、SOI領域1Aに低耐圧MOSFETLpを形成し、絶縁膜27から露出している拡散層12およびゲート電極9の上面にシリサイド層14を形成する。このとき、バルクシリコン領域1Bは絶縁膜21aにより覆われたままなので、図13および図14で説明したバルクシリコン領域1Bに対するエピタキシャル成長(選択成長)および不純物イオンの注入は行わない。また、バルクシリコン領域1Bの半導体基板1の主面は絶縁膜21aにより覆われているため、シリサイド層14は形成されない。

【0132】

次に、図16〜図18に示す工程と同様の工程を行うことで、図29に示す本実施の形態の半導体装置が完成する。絶縁膜27は層間絶縁膜の一部と見なし、半導体基板1の主面に達するコンタクトプラグ17をバルクシリコン領域1Bに形成する際は、絶縁膜27および絶縁膜21aを貫通するコンタクトホールを形成し、当該コンタクトホールにコンタクトプラグ17を埋込むことで、コンタクトプラグ17と半導体基板1とを接続する。

【0133】

本実施の形態では、上記のようにして半導体装置を形成することにより、SOI領域1Aおよびバルクシリコン領域1Bの境界近傍のひさし構造部においてBOX膜4が後退して形成された窪みに、BOX膜4の膜厚の半分以上の膜厚を有する絶縁膜21aを完全に埋め込んでいる。このため、ひさし構造部の窪んだ領域には、ゲート電極9を形成する際に半導体基板1上に形成したポリシリコン膜が入り込むことはないため、ゲート電極9の形成工程において前記ポリシリコン膜が残渣として残ることを防ぐことができる。これにより、前記残渣に起因してSOI膜5と半導体基板1とが短絡することを防ぐことができるため、半導体装置の信頼性を向上させることができる。

【0134】

また、図27〜図29を用いて説明した工程では、バルクシリコン領域1Bを絶縁膜21aにより覆ったままエピタキシャル層および拡散層の形成などを行ったが、絶縁膜27を形成する領域をSOI領域1Aおよびバルクシリコン領域1Bの境界近傍のみとし、その後の工程で絶縁膜27から露出するバルクシリコン領域1Bの絶縁膜21aを除去して半導体基板1の主面の露出してもよい。この場合には、バルクシリコン領域1Bの半導体基板1の主面上に図13〜図18を用いて説明したようにエピタキシャル層からなる拡散層13および拡散層13上のシリサイド層14を形成してもよい。

【0135】

また、SOI領域1Aおよびバルクシリコン領域1Bの境界近傍のみに絶縁膜27を形成する場合には、図19〜図23を用いて説明した工程と同様の工程を行い、バルクシリコン領域1BにMOSFETを形成することも可能である。なお、このとき前記境界近傍には絶縁膜21a、27を形成しているため、前記実施の形態1で説明したダミーゲート電極は形成しない。

【0136】

また、上述した絶縁膜27の部材は例えば酸化シリコン膜であるものとして説明したが、絶縁膜27はフォトレジスト膜としてもよい。ただし、この場合は図28に示す構造を形成した後にフォトレジスト膜である絶縁膜27を除去してから、図29に示すエッチストッパ膜15および層間絶縁膜16などを形成する。フォトレジスト膜により絶縁膜27を形成したとしても、絶縁膜21aをSOI領域1Aおよびバルクシリコン領域1Bの境界近傍に残すことで、ポリシリコン膜の残渣が発生することを防ぐことができれば、上述したようにSOI膜5と半導体基板1とが短絡することを防ぐ効果を得ることができる。

【0137】

(実施の形態4)

本実施の形態では、SOI領域およびバルクシリコン領域の境界近傍のひさし構造が形成されることを防ぐために、SOI膜の形成後にSOI膜の端部を一部酸化し、その後BOX膜をパターニングする際にSOI膜の酸化した部分を除去し、SOI膜およびBOX膜の側壁を揃える半導体装置について説明する。以下に示す図30〜図32は本実施の形態の半導体装置の製造工程を示す断面図である。

【0138】

本実施の形態の半導体装置の製造工程では、まず、図3〜図8を用いて説明した工程を行った後、半導体層5a(図8参照)のみをフォトリソグラフィ技術およびエッチング法を用いてパターニングすることにより、半導体層5aからなるSOI膜5を形成する。なお、絶縁膜4aの膜厚は10nmであるものとする。その後、例えば熱酸化法を用いてSOI膜5の表面を酸化することにより、SOI膜5の上面および側壁に厚さ10nm程の酸化シリコン膜からなる絶縁膜28を形成する。

【0139】

つまり、半導体基板1の主面に対して垂直な方向における絶縁膜4aの膜厚と、同じ大きさの膜厚を有する絶縁膜28を、SOI膜5の表面の上面および側面に形成する。したがって、SOI膜5の側壁に形成された絶縁膜28の膜厚の10nm程度である。このときの酸化工程により、SOI膜5から露出している絶縁膜4aの直下の半導体基板1の主面は多少酸化されるため、SOI膜5から露出している領域の半導体基板1上の絶縁膜4aの膜厚は、SOI膜5の直下の絶縁膜4aの膜厚に比べて厚くなる。

【0140】

次に、図31に示すように、ウェットエッチング法を用いて半導体基板1上の絶縁膜4aを一部除去し、絶縁膜28を同工程において除去することにより、絶縁膜4aをパターニングし、SOI膜5を露出する。このとき、絶縁膜4aおよび絶縁膜28はそれぞれの露出している表面から等方的に除去されるため、SOI膜5のバルクシリコン領域1B側の側壁の絶縁膜28の表面から10nm程度の範囲の絶縁膜4aおよび絶縁膜28が除去される。このため、図31に示すように、バルクシリコン領域1B側のSOI膜5およびBOX膜4のそれぞれの側壁がほぼ揃う。つまり、バルクシリコン領域1B側のSOI膜5およびBOX膜4のそれぞれの側壁は、平面視においてほぼ重なる領域に位置するように形成される。言い換えれば、バルクシリコン領域1B側のSOI膜5およびBOX膜4のそれぞれの側壁は、同一面内に位置するよう形成される。

【0141】

したがって、BOX膜4およびSOI膜5からなる積層膜のバルクシリコン領域1B側の側壁には、前記実施の形態1で説明したひさしがほぼ存在しない構造を得ることができるため、この後の工程でポリシリコン膜を半導体基板1上にCVD法などを用いて形成(堆積)したとしても、前記積層膜の側壁にポリシリコン膜が残ることを防ぐことができる。

【0142】

すなわち、単に図3〜図9に示した工程のように、絶縁膜4a上にSOI膜5を形成した後に、SOI膜5をマスクとしてウェットエッチング法により絶縁膜4aをパターニングしてBOX膜4を形成したのでは、図38に示すようなひさし構造を形成することになる。図38に示すように、BOX膜4の側壁はBOX膜4の膜厚と同じ大きさだけ後退しているため、本実施の形態の半導体装置では、図30および図31に示すようにSOI膜5の側壁にBOX膜4と同等の厚さの酸化膜を形成することにより、BOX膜4を形成するためのウェットエッチング工程の際に、SOI膜5の側壁の酸化膜とBOX膜4とが同程度後退することを利用して、前記積層膜の側壁の位置を揃えている。

【0143】

したがって、図37を用いて説明したひさし構造部にポリシリコン膜が残ることで残渣が発生し、当該残渣を介してSOI膜5と半導体基板1とが短絡することを防ぐことができるため、半導体装置の信頼性を向上させることができる。

【0144】

この後の工程は、図10〜図18を用いて説明した工程とほぼ同様の工程を行うことで、図32に示す本実施の形態の半導体装置が完成する。ただし、BOX膜4およびSOI膜5からなる積層膜のバルクシリコン領域1B側の側壁にはひさし構造がないため、ダミーゲート電極を形成する必要がなく、ここではサイドウォール11を形成した工程において、前記積層膜の側壁にサイドウォール11aを形成する。なお、サイドウォール11aはBOX膜4およびSOI膜5の両方の側壁に接して形成されており、サイドウォール11aと前記積層膜の側壁との間にはポリシリコン膜は形成されていない。

【0145】

また、図19〜図23を用いて説明した工程と同様の工程を行い、バルクシリコン領域1BにMOSFETを形成してもよい。ただし、ひさし構造部に膜厚が厚い絶縁膜を埋込む必要はないため、ダミーゲート電極8および絶縁膜21aはSOI領域1Aおよびバルクシリコン領域1Bの境界に形成しない。

【0146】

(実施の形態5)

図39を用いて説明したように、SOI膜5と半導体基板1とが短絡する原因の一つとして、バルクシリコン領域の半導体基板1の上面にせり上げられたエピタキシャル層である拡散層13aが形成され、拡散層13aの上部に形成されたシリサイド層14aがSOI領域のシリサイド層14aに達することが挙げられる。つまり、バルクシリコン領域にエピタキシャル層である拡散層13aが形成されなければ、バルクシリコン領域に形成されるシリサイド層は半導体基板1の主面に接して形成されるため、SOI領域のエピタキシャル層の表面のシリサイド層に届かず、シリサイド層同士の接触による短絡の発生を防ぐことができる。

【0147】

この場合バルクシリコン領域にはエピタキシャル層が形成されないが、エピタキシャル層のようにせり上げた半導体層が必要なのは薄い膜厚を有するSOI膜5の上部のみであるため、バルクシリコン領域にはエピタキシャル層が形成されなくても問題はない。以下に、バルクシリコン領域にエピタキシャル層を形成しない半導体装置の製造方法について、図33〜図36を用いて説明する。図33〜図36は本実施の形態の半導体装置の製造工程を示す断面図である。

【0148】

本実施の形態の半導体装置の製造工程では、まず、図3〜図8を用いて説明した工程を行った後、前記実施の形態4で図30および図31を用いて説明したように、SOI膜5およびBOX膜4からなる積層膜を、側壁にひさし構造がない状態で形成する。

【0149】

次に、図10〜図12を用いて説明した工程と同様の工程を行うことで、SOI領域1AのSOI膜5上にゲート絶縁膜7を介してゲート電極9を形成し、その横のSOI膜5内にLDD層10を形成する。ただし、ここではSOI領域1Aおよびバルクシリコン領域1Bの境界にダミーゲート電極は形成しないものとする。

【0150】

次に、図33に示すように、半導体基板1の主面の全面上に例えばCVD法を用いて酸化シリコン膜からなる絶縁膜29を形成した後、フォトレジスト膜PR3をバルクシリコン領域1Bの絶縁膜29の上面を覆うように形成する。フォトレジスト膜PR3はゲート電極9の直上には形成せず、SOI膜5の端部の直上の絶縁膜29を一部覆うように形成する。ただし、フォトレジスト膜PR3はバルクシリコン領域1B側のLDD層10の直上の絶縁膜29の上面を完全に覆わないように形成する。

【0151】

次に、図34に示すように、フォトレジスト膜PR3をマスクとして絶縁膜29をドライエッチングした後、フォトレジスト膜PR3を除去することで、バルクシリコン領域1BおよびSOI膜5の端部を覆うような絶縁膜29を残し、同工程により、絶縁膜29からなるサイドウォール11をゲート電極9の側壁に形成する。サイドウォール11を例えば窒化シリコン膜および酸化シリコン膜からなる積層膜により形成する場合には、図33を用いて説明した工程において形成した絶縁膜29を窒化シリコン膜および前記窒化シリコン膜上に酸化シリコン膜を堆積した積層膜構造とすればよい。

【0152】

続いて、エピタキシャル成長法(選択成長法)により、ゲート電極9、サイドウォール11およびマスク材である絶縁膜29から露出するSOI膜5の上面上にエピタキシャル層(選択成長層)を形成した後、イオン注入法により前記エピタキシャル層にP型の不純物(例えばB(ホウ素))を注入することにより、前記エピタキシャル層からなる拡散層12を形成し、拡散層12、LDD層10およびゲート電極9を含む低耐圧MOSFETLpを形成する。このとき、マスク材である絶縁膜29に覆われたバルクシリコン領域1Bの半導体基板1の主面にはエピタキシャル層は形成されてない。

【0153】

次に、図35に示すように、低耐圧MOSFETLpを覆い、バルクシリコン領域1Bの絶縁膜29を露出するフォトレジスト膜(図示しない)を形成した後、例えばウェットエッチング法により絶縁膜29を除去することにより、バルクシリコン領域1Bの半導体基板1の上面を露出する。その後、前記フォトレジスト膜をマスクとしてN型の不純物(例えばP(リン))を半導体基板1の上面に注入することにより、半導体基板1の上面にN型の半導体層13bを形成する。

【0154】

ここではウェットエッチング法を用いて絶縁膜29を除去する方法について説明したが、ドライエッチング法を用いて絶縁膜29を除去しても構わない。その場合、SOI膜5およびBOX膜4からなる積層膜の側壁にはサイドウォールが形成される。

【0155】

また、絶縁膜29をエッチングにより除去する際に、SOI膜5の端部の上部、またはSOI領域1Aとバルクシリコン領域1Bの境界近傍に絶縁膜29が残っていてもよいが、ここでは図33に示すように、SOI領域1Aとバルクシリコン領域1Bの境界近傍も含め、絶縁膜29は除去されているものとする。このため、絶縁膜29を除去する際に低耐圧MOSFETLpを覆うフォトレジスト膜は、少なくともサイドウォール11を覆うような条件で、SOI領域1Aとバルクシリコン領域1Bの境界近傍の絶縁膜29を露出するように形成する。

【0156】

続いて、周知のシリサイドプロセスを用いて、拡散層12、ゲート電極9およびバルクシリコン領域1Bの半導体基板1の主面のそれぞれの露出した表面にシリサイド層14を形成する。このとき、例えば酸化シリコン膜などからなる絶縁膜であるBOX膜4の側壁にはシリサイド層14が形成されず、半導体基板1(半導体層13b)上に形成されたシリサイド層14と、SOI膜5およびその上部の拡散層12の表面に形成されたシリサイド層14とは、間にBOX膜4が介在することで分離されるため、互いに接触しない。

【0157】

この後の工程は、図16〜図18を用いて説明した工程と同様の工程を行うことにより、図36に示す本実施の形態の半導体装置が完成する。

【0158】

図39に示すようにSOI領域およびバルクシリコン領域の両方の半導体層上にエピタキシャル層を形成し、それらの上部にシリサイド層を形成すると、バルクシリコン領域のエピタキシャル層上のシリサイド層は下部にエピタキシャル層が形成されているためにSOI領域のシリサイド層に接近し、各領域のシリサイド層同士が接触して短絡する問題がある。

【0159】

これに対し、本実施の形態ではエピタキシャル層を形成する際に、予めバルクシリコン領域に露出する半導体基板の主面を絶縁膜により覆うことで、エピタキシャル層をSOI領域のみに形成しているため、前記絶縁膜により覆われたバルクシリコン領域にはエピタキシャル層の形成工程においてエピタキシャル層が形成されない。このため、その後の工程で前記エピタキシャル層の表面および前記半導体基板の主面のそれぞれに形成されたシリサイド層が、互いに接触するほど接近することを防ぐことができる。したがって、SOI領域とバルクシリコン領域の境界において、各領域のシリサイド層同士が接続されて半導体基板とSOI膜とが短絡することを防ぐことができるため、半導体装置の信頼性を向上することができる。

【0160】

なお、ここでは図33および図34に示すように、バルクシリコン領域1Bに新たな絶縁膜29を形成することでバルクシリコン領域1Bにエピタキシャル層が形成されない構造を実現する方法について説明したが、他の目的で形成された絶縁膜がバルクシリコン領域1Bを覆っていることを利用して、SOI領域1Aのみにエピタキシャル層を形成してもよい。つまり、図27および図28に示すように、例えばSOI膜5のひさし構造の下部の窪みを埋めるなどの目的で形成された厚い絶縁膜21aがバルクシリコン領域1Bに形成されている状態でエピタキシャル成長を行っても、上記した本実施の形態の半導体装置と同様の効果を得ることができる。

【0161】

また、本実施の形態はSOI領域およびバルクシリコン領域のシリサイド層同士が短絡を引き起こす問題を解消する構造およびその製造方法について説明するものであるため、SOI膜およびBOX膜からなる積層膜の端部の前記ひさし構造の有無は問題としない。したがって、図28に示すような前記ひさし構造が存在している場合にも、本実施の形態の半導体装置およびその製造方法を適用し、上記した本実施の形態の効果を得ることができる。

【0162】

以上、本発明者らによってなされた発明をその実施の形態に基づき具体的に説明したが、本発明は前記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることはいうまでもない。

【0163】

例えば、前記実施の形態1〜5では、P型不純物としてP(リン)を例示し、N型不純物としてB(ボロン)を例示しているが、これに限られず、P型不純物としてAs(ヒ素)や、N型不純物としてBF2(フッ化ボロン)を用いてもよい。

【0164】

また、前記実施の形態1〜5では半導体基板上に形成するMOSFETをPチャネル型のMOSFETとしたが、これに限らずNチャネル型のMOSFETを形成してもよい。また、半導体基板内に形成するウエルおよびその上部の拡散層の導電型をN型としたが、これはP型であっても構わない。

【0165】

また、前記実施の形態1〜5では半導体装置を構成する電界効果トランジスタをMOSFETとしたが、これらはMIS(Metal Insulator Semiconductor)型のFETであっても構わない。

【産業上の利用可能性】

【0166】

本発明は、SOI領域とバルクシリコン領域を有する装置の製造技術に適用して有効である。

【符号の説明】

【0167】

1 半導体基板

1A SOI領域

1B バルクシリコン領域

2 素子分離領域

2a 溝

2b〜2e 絶縁膜

3 Nウエル

4 BOX膜

4a 絶縁膜

5 SOI膜

5a 半導体層

6、6a、6b 絶縁膜

7 ゲート絶縁膜

8 ダミーゲート電極

8a ポリシリコン膜

9 ゲート電極

9p ポリシリコン膜

10 LDD層

11、11a サイドウォール

12 拡散層

12a エピタキシャル層

13、13a 拡散層

13b 半導体層

14、14a シリサイド層

15 エッチストッパ膜

16 層間絶縁膜

17、17a コンタクトプラグ

18 エッチストッパ絶縁膜

19 層間絶縁膜

20 配線

21、21a 絶縁膜

22 ゲート絶縁膜

23 ゲート電極

24 LDD層

25 拡散層

26〜29 絶縁膜

Hp 高耐圧MOSFET

Lp 低耐圧MOSFET

PR1〜PR3 フォトレジスト膜

【技術分野】

【0001】

本発明は、半導体装置およびその製造方法に関し、特に、SOI領域およびバルクシリコン領域を有する半導体素子の製造に適用して有効な技術に関する。

【背景技術】

【0002】

近年、半導体基板の電位を制御することで当該半導体基板上に絶縁膜を介してSi(シリコン)膜を形成するSOI(Silicon On Insulator)構造を用いた半導体装置が研究されている。このような半導体装置では、半導体基板の電位を制御するためのコンタクトプラグなどの接続部材を、SOI構造の上面のSi膜ではなく半導体基板の主面のバルクシリコン領域に電気的に接続することになる。

【0003】

特許文献1(特開2000−223704号公報)には、STI構造などの素子分離を用いた高集積度半導体装置において、素子分離領域周縁部に形成される段差に起因するゲート電極パターニング時の残渣の発生を防ぐことが記載されている。

【0004】

特許文献2(特開2009−170590号公報)には、膜厚が異なるSOI層のそれぞれにトランジスタを形成した半導体装置において、複数種のトランジスタ間の素子分離を精度良く行うことが記載されている。

【0005】

非特許文献1には、SOI構造の上部にCMOS(Complementary Metal Oxide Semiconductor)を形成し、SOI構造の下部のシリコン基板に電位を供給することでCMOSのしきい値電圧を制御することが記載されている。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2000−223704号公報

【特許文献2】特開2009−170590号公報

【非特許文献】

【0007】

【非特許文献1】2010年4月アイ・イー・イー・イー トランスアクションズ オン エレクトロン デバイスズ57号4番835頁〜845頁(IEEE Transactions On Electron Devices, Vol.57, No.4, April 2010, pp. 835-845)

【発明の概要】

【発明が解決しようとする課題】

【0008】

非特許文献1に記載されている技術では、半導体基板に電位を供給する端子部と、比較的低い電圧で駆動するMOS型の電界効果トランジスタ(Metal Oxide Semiconductor Field Effect Transistor:MOSFET)が形成されるSOI領域とが、STI(Shallow Trench Isolation)などの素子分離領域を隔てて絶縁されている。なお、ここでは、通常の半導体装置に用いる単結晶シリコンウエハを、SOI領域と区別してバルクシリコンと呼ぶ。

【0009】

これに対し、半導体基板上にバルクシリコン領域とSOI領域とを有する半導体装置では、半導体基板に電位を供給する前記端子部を含むバルクシリコン領域とSOI領域との間に、半導体基板に埋込まれた素子分離領域を設けない構造を形成することが考えられる。この場合、バルクシリコン領域とSOI領域とが同一の活性領域内に隣接して配置されていることに起因して、半導体基板上に残渣が生じ、またはバルクシリコン領域とSOI領域とのそれぞれの上部のシリサイド層同士が接触するなどして、バルクシリコン領域とSOI領域とが短絡する虞がある。MOS型の電界効果トランジスタ(以下単にMOSFETという)を形成するSOI領域と前記端子部とは別々に電位を制御するために互いに絶縁されている必要があり、これらの領域が短絡(ショート)すると、半導体装置が正常に動作しなくなるため、半導体装置の信頼性が低下する。

【0010】

本発明の目的は、半導体装置の信頼性を向上させることにある。

【0011】

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

【課題を解決するための手段】

【0012】

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、次のとおりである。

【0013】

本発明の好ましい一態様である半導体装置は、半導体基板の主面上の一つの活性領域内に、互いに隣接するSOI領域とバルクシリコン領域とを有し、SOI領域のBOX膜上のSOI膜と半導体領域とに異なる電位を供給する場合に、隣接するSOI領域およびバルクシリコン領域の境界部分において、SOI膜の端部および半導体基板の主面を絶縁膜により覆うものである。

【0014】

また、本発明の好ましい一態様である半導体装置の製造方法は、

(a)半導体基板の主面の一つの活性領域上にBOX膜およびSOI膜を順次形成する工程と、

(b)前記活性領域を構成するバルクシリコン領域と隣接し、前記活性領域を構成するSOI領域にSOI膜を残す工程と、

(c)前記(b)工程の後、等方性エッチングによりBOX膜を加工する工程と、

(d)SOI領域およびバルクシリコン領域の境界において、SOI膜の端部および半導体基板の主面を覆う絶縁膜を形成する工程と、

を有するものである。

【発明の効果】

【0015】

本願において開示される発明のうち、代表的なものによって得られる効果を簡単に説明すれば以下のとおりである。

【0016】

代表的な実施の形態によれば、半導体装置の信頼性を向上させることができる。

【図面の簡単な説明】

【0017】

【図1】本発明の実施の形態1である半導体装置の断面図である。

【図2】本発明の実施の形態1である半導体装置の変形例を示す断面図である。

【図3】本発明の実施の形態1である半導体装置の製造工程を示す断面図である。

【図4】図3に続く半導体装置の製造工程中の断面図である。

【図5】図4に続く半導体装置の製造工程中の断面図である。

【図6】図5に続く半導体装置の製造工程中の断面図である。

【図7】図6に続く半導体装置の製造工程中の断面図である。

【図8】図7に続く半導体装置の製造工程中の断面図である。

【図9】図8に続く半導体装置の製造工程中の断面図である。

【図10】図9に続く半導体装置の製造工程中の断面図である。

【図11】図10に続く半導体装置の製造工程中の断面図である。

【図12】図11に続く半導体装置の製造工程中の断面図である。

【図13】図12に続く半導体装置の製造工程中の断面図である。

【図14】図13に続く半導体装置の製造工程中の断面図である。

【図15】図14に続く半導体装置の製造工程中の断面図である。

【図16】図15に続く半導体装置の製造工程中の断面図である。

【図17】図16に続く半導体装置の製造工程中の断面図である。

【図18】図17に続く半導体装置の製造工程中の断面図である。

【図19】本発明の実施の形態1である半導体装置の変形例の製造工程を示す断面図である。

【図20】図19に続く半導体装置の製造工程中の断面図である。

【図21】図20に続く半導体装置の製造工程中の断面図である。

【図22】図21に続く半導体装置の製造工程中の断面図である。

【図23】図22に続く半導体装置の製造工程中の断面図である。

【図24】本発明の実施の形態1である半導体装置の変形例を示す断面図である。

【図25】本発明の実施の形態2である半導体装置の製造工程を示す断面図である。

【図26】図25に続く半導体装置の製造工程中の断面図である。

【図27】本発明の実施の形態3である半導体装置の製造工程を示す断面図である。

【図28】図27に続く半導体装置の製造工程中の断面図である。

【図29】図28に続く半導体装置の製造工程中の断面図である。

【図30】本発明の実施の形態4である半導体装置の製造工程を示す断面図である。

【図31】図30に続く半導体装置の製造工程中の断面図である。

【図32】図31に続く半導体装置の製造工程中の断面図である。

【図33】本発明の実施の形態5である半導体装置の製造工程を示す断面図である。

【図34】図33に続く半導体装置の製造工程中の断面図である。

【図35】図34に続く半導体装置の製造工程中の断面図である。

【図36】図35に続く半導体装置の製造工程中の断面図である。

【図37】比較例である半導体装置の断面図である。

【図38】比較例である半導体装置の拡大した断面図である。

【図39】比較例である半導体装置の断面図である。

【発明を実施するための形態】

【0018】

以下、本発明の実施の形態を図面に基づいて詳細に説明する。なお、実施の形態を説明するための全図において、同一の機能を有する部材には同一の符号を付し、その繰り返しの説明は省略する。また、以下の実施の形態では、特に必要なとき以外は同一または同様な部分の説明を原則として繰り返さない。

【0019】

(実施の形態1)

まず、図1を用いて本発明の実施の形態の半導体装置を説明する。図1には、本実施の形態の半導体装置の断面図を示している。

【0020】

図1に示すように、本実施の形態の半導体装置は例えば単結晶のSi(シリコン)からなる半導体基板1を有し、半導体基板1の主面には素子分離領域2が複数形成されており、素子分離領域2によって活性領域(アクティブ領域)が規定されている。ここでは、半導体基板1の主面において素子分離領域2が形成されている領域を不活性領域(フィールド領域)と呼び、素子分離領域2が形成されていない領域を活性領域(アクティブ領域)と呼ぶものとする。素子分離領域2は主に酸化シリコン(SiO2)などを含み、半導体基板1の主面に形成された溝2a内に形成されている絶縁膜であって、例えばSTI構造を有する。なお、素子分離領域2の上面は半導体基板1の主面よりも高い領域に位置するものとするが、素子分離領域2の上面の高さの位置は、半導体基板1の主面と同等か、それよりも低い位置にあってもよい。

【0021】

半導体基板1の主面にはN型の不純物(例えばP(リン))が導入されたNウエル3が形成されており、半導体基板1の主面上には酸化シリコン膜からなるBOX(Buried Oxide)膜4を介して、主にSi(シリコン)を含むSOI膜5が形成されている。BOX膜4の膜厚は例えば10nmであり、SOI膜5の膜厚は例えば10nmである。

【0022】

本実施の形態の半導体装置では、素子分離領域2により挟まれた一つの活性領域内に、半導体基板1の主面を覆うBOX膜4およびSOI膜5が形成されたSOI領域と、半導体基板1の主面がBOX膜4およびSOI膜5から露出しているバルクシリコン領域とが互いに隣接して配置されている。つまり、BOX膜4およびSOI膜5からなる積層膜の少なくとも一方の端部は素子分離領域2に接しておらず、また、SOI膜5の当該端部の近傍には素子分離領域2は形成されていない。つまり、SOI領域およびバルクシリコン領域とが同一の活性領域内に形成されており、それらの領域の境界部分の近傍の半導体基板1の主面には素子分離領域2が形成されていない。また、図示はしていないが、SOI膜5内には、Nウエル3と同様にN型の不純物(例えばP(リン))が導入されたN型のウエルが形成されている。

【0023】

なお、本願でいうSOI領域およびバルクシリコン領域の境界の近傍とは、SOI領域およびバルクシリコン領域の境界を含むSOI領域またはバルクシリコン領域もしくはそれら両方の領域を含む箇所を指すものとする。例えば、SOI領域およびバルクシリコン領域の境界近傍のバルクシリコン領域とは、バルクシリコン領域の一部の領域であって、前記境界に隣接する領域を指す。

【0024】

バルクシリコン領域に隣接するSOI膜5の端部は、BOX膜4の端部よりもバルクシリコン領域側に突き出ており、SOI膜5の当該端部の直下にはBOX膜4が形成されていない領域がある。つまり、SOI膜5およびBOX膜4からなる積層膜のバルクシリコン領域側の端部は、SOI膜5の方がBOX膜4よりもバルクシリコン領域側に伸びているひさし状の構造を有している。言い換えれば、ゲート電極9のゲート長方向において、BOX膜4の端部からゲート電極9までの距離は、SOI膜5の端部からゲート電極9までの距離よりも近い。また、ゲート電極9のゲート長方向において、BOX膜4の端部は、ゲート電極9側へ向かって、SOI膜5の端部よりも後退している。このひさし状の形状は、半導体基板1の主面上に形成した絶縁膜上に、パターニングされたSOI膜5を形成した後、ウェットエッチング法を用いて前記絶縁膜を一部除去し、半導体基板1の主面を露出させることで前記絶縁膜からなるBOX膜4を形成した際に、SOI膜5の端部の直下の前記絶縁膜が除去されることで形成されるものである。

【0025】

BOX膜4を形成するパターニング工程では、ウェットエッチングなどの等方性エッチングではなく、ドライエッチングなどの異方性エッチングを用いて前記ひさし状の形状が形成されることを防ぐことが考えられるが、ゲート電極を形成する前に行うエッチング工程でドライエッチング法を用いると、エッチングによる過剰なダメージが半導体基板1の主面などに蓄積されて半導体装置の信頼性が低下するため、BOX膜4のパターニング工程ではウェットエッチング法を用いる必要がある。

【0026】

なお、図1には、半導体基板1の主面に対して垂直な方向において、SOI膜5の前記端部と半導体基板1の主面との間にBOX膜4が形成されていない構造を示しているが、後述する図38に示すように、SOI膜5の前記端部と半導体基板1の主面との間には、BOX膜4が例えば半導体基板1の主面に接して形成されている場合が考えられる。ただしこの場合も、SOI膜5の前記端部の下面にはBOX膜4が接していない場合などが考えられ、少なくともSOI膜5およびBOX膜4からなる積層膜のバルクシリコン領域側の端部の側面には、BOX膜4が一部後退することで形成された窪みが存在する。

【0027】

図1に示すように、SOI領域では、SOI膜5の上面に接して、例えば酸化シリコン膜からなるゲート絶縁膜7が形成され、ゲート絶縁膜7上には例えばポリシリコン膜からなるゲート電極9が形成されている。ゲート電極9のゲート長方向において、ゲート電極9の横のSOI膜5の主面にはソース・ドレイン領域を構成するLDD層10が形成されている。LDD層10はSOI膜5内にP型の不純物(例えばB(ホウ素))を比較的低い濃度で導入することで形成された半導体領域である。ゲート電極9の直下のSOI膜5であってLDD層10により挟まれた領域は、低耐圧MOSFETの動作時にチャネル領域として機能する。

【0028】

ゲート電極9の両側の側壁には、例えば酸化シリコン膜および窒化シリコン膜の積層膜からなるサイドウォール11が形成されている。ここでは、ゲート電極9の側壁に接して形成された酸化シリコン膜と、ゲート電極9の側壁に前記酸化シリコン膜を介して形成された窒化シリコン膜とからなる前記積層膜によってサイドウォール11が形成されているものとするが、図では前記積層膜を一層の膜として示している。

【0029】

SOI領域において、ゲート電極9およびサイドウォール11から露出するSOI膜5の上面に接して、ゲート電極9の横にエピタキシャル層(せり上げ層、選択成長層)である拡散層12が形成(選択成長)されている。拡散層12は低耐圧MOSFETのソース・ドレイン領域を構成する半導体層であり、主にSi(シリコン)を含む。拡散層12はゲート電極9の両側にサイドウォール11を介して配置されており、拡散層12はゲート電極9を挟むようにゲート電極9のゲート長方向の両側に配置されている。拡散層12には、LDD層10に打ち込まれた不純物と同じ導電型の不純物が、LDD層10よりも高い濃度で注入されている。

【0030】

なお、拡散層12を形成するためにSOI膜5上のエピタキシャル層に打ち込んだ不純物は、前記エピタキシャル層だけでなくSOI膜5内にも注入されているものとするが、ここではSOI膜5上のエピタキシャル層を拡散層12として説明する。拡散層12は前記エピタキシャル層の上面から、LDD層10が形成されたSOI膜5の底部まで達して形成されているものとして考えてもよい。ただし、拡散層12を形成するために注入された不純物が、前記エピタキシャル層のみに注入されていてもよい。SOI領域に形成されたゲート電極9、LDD層10および拡散層12はPチャネル型の低耐圧MOSFETLpを構成している。

【0031】

同様に、バルクシリコン領域の半導体基板1の主面上には、半導体基板1の主面に接してエピタキシャル層が形成されており、当該エピタキシャル層にはN型の不純物(例えばP(リン))が高濃度で導入された拡散層13が形成されている。また、拡散層13の直下の半導体基板1の主面には、拡散層13を形成する際にバルクシリコン領域の前記エピタキシャル層に注入した不純物が前記エピタキシャル層を通過して注入されており、半導体基板1の主面に高い不純物濃度を有する半導体層13bが形成されている。拡散層13および半導体層13bには、Nウエル3に打ち込まれた不純物と同じ導電型の不純物が、Nウエル3よりも高い濃度で注入されている。バルクシリコン領域は活性領域内においてのみ素子分離領域2から露出しているため、バルクシリコン領域の拡散層13およびその上部のシリサイド層14は、一方の端部が素子分離領域2と隣接する位置で終端している。

【0032】

拡散層12、13およびゲート電極9のそれぞれの上面には、例えばNiSi(ニッケルシリサイド)からなるシリサイド層14が形成されている。

【0033】

ここで、SOI領域とバルクシリコン領域との境界の、BOX膜4およびSOI膜5からなる積層膜の端部が形成されている領域には、ゲート電極9と同様の構造のダミーゲート電極8が形成されている。ダミーゲート電極8は、BOX膜4から露出する半導体基板上の直上からSOI膜5の直上に亘って連続的に形成されている。半導体基板1の主面およびSOI膜5の表面とダミーゲート電極8との間には、例えば酸化シリコン膜からなる絶縁膜6が形成されている。つまり絶縁膜6は、SOI領域とバルクシリコン領域との境界近傍の半導体基板1の主面を覆い、SOI膜5の端部の底面、側面および上面を覆って形成されており、ダミーゲート電極8は絶縁膜6上に形成されている。絶縁膜6とゲート絶縁膜7とは同等の膜厚を有しており、同一の工程で形成された同層の絶縁膜により形成されている。

【0034】

図1では、絶縁膜6がBOX膜4の側壁の上部と下部に接しており、BOX膜4の側面の一部を露出している構造を示しているが、絶縁膜6は半導体基板1の主面、BOX膜4の側壁、SOI領域の底部、側壁および上面に亘って連続的に形成されていてもよい。また図1では、ひさし形状となっているSOI膜5の端部の直下に絶縁膜6を介してダミーゲート電極8の一部が形成されている構造を示しているが、BOX膜4および絶縁膜6の膜厚によっては、SOI膜5の端部の直下にダミーゲート電極8が形成されない場合もある。

【0035】

ダミーゲート電極8の側壁には、低耐圧MOSFETLpと同様にサイドウォール11が形成されており、ダミーゲート電極8の上面にはシリサイド層14が形成されている。SOI領域とバルクシリコン領域との境界近傍において、半導体基板1の主面とSOI膜5の端部との間には絶縁膜6およびダミーゲート電極8が形成されているため、半導体基板1とSOI膜5とは電気的に絶縁されている。また、SOI領域とバルクシリコン領域との境界近傍にはダミーゲート電極8が形成されているため、エピタキシャル層は形成されておらず、エピタキシャル層上のシリサイド層14も形成されていない。したがって、拡散層12上のシリサイド層14と、拡散層13上のシリサイド層14とは、ダミーゲート電極8およびダミーゲート電極8の側壁のサイドウォール11により分離されている。

【0036】

半導体基板1上の全面には、素子分離領域2、シリサイド層14およびサイドウォール11を覆うようにエッチストッパ膜15および層間絶縁膜16が半導体基板1の主面側から順に形成されている。エッチストッパ膜15は例えば窒化シリコン膜からなり、層間絶縁膜16は酸化シリコン膜からなる。エッチストッパ膜15は層間絶縁膜16よりも薄い膜厚で形成されており、層間絶縁膜16の上面はゲート電極9の上面よりも高い位置に均一な高さで形成されている。層間絶縁膜16およびエッチストッパ膜15を貫通し、シリサイド層14の上面を露出するコンタクトホールが複数形成されている。各コンタクトホール内には例えばW(タングステン)を主に含む接続部材であるコンタクトプラグ17が埋込まれており、コンタクトプラグ17の上面の高さは層間絶縁膜16の上面の高さとほぼ均一に揃えられている。

【0037】

コンタクトプラグ17は、ゲート電極、ソース・ドレイン領域または半導体基板などに所定の電位を供給するための接続部材である。図1には示していないが、ゲート電極9の上部にも、シリサイド層14を介してコンタクトプラグ17が形成されている。ただし、ダミーゲート電極8は半導体装置を構成する回路に寄与せず、他の配線などの導電体から絶縁された膜であるので、ダミーゲート電極8上のシリサイド層14にはコンタクトプラグ17は接続されていない。

【0038】

層間絶縁膜16上には、エッチストッパ膜18を介して層間絶縁膜19が形成されており、エッチストッパ膜18および層間絶縁膜19からなる積層膜には、コンタクトプラグ17の上面を露出する溝が複数形成されており、各溝内には配線20が埋込まれている。配線20は例えばCu(銅)を主に含み、コンタクトプラグ17を介してゲート電極、ソース・ドレイン領域または半導体基板などに電気的に接続されている。エッチストッパ膜は例えば窒化シリコン膜からなり、層間絶縁膜19は例えば酸化シリコン膜からなるものとする。

【0039】

上記のように、本実施の形態の半導体装置は、隣り合う素子分離領域2によって規定された一つの活性領域内に、SOI領域とバルクシリコン領域とが形成されている場合において、SOI領域とバルクシリコン領域との境界部分に絶縁膜6および絶縁膜6上のダミーゲート電極8を形成するものである。

【0040】

なお、図1では絶縁膜6をゲート絶縁膜7と同等の膜厚で形成しているが、絶縁膜6の膜厚はゲート絶縁膜7よりも厚くても良い。図2に、本実施の形態の半導体装置の変形例の断面図を示す。図2に示す半導体装置は、図1に示す半導体装置とほぼ同様の構造を有しているが、ダミーゲート電極8の直下の絶縁膜21の膜厚はSOI領域の低耐圧MOSFETLpのゲート絶縁膜7よりも厚い。ここでは、BOX膜4の膜厚を10nmとし、SOI膜5の膜厚を10nmとし、絶縁膜21の膜厚を5nmとしている。

【0041】

また、図1と異なり、図2の変形例の半導体装置では、バルクシリコン領域に低耐圧MOSFETLpよりも高い電圧で駆動するPチャネル型の高耐圧MOSFETHpが形成されている。高耐圧MOSFETHpは、バルクシリコン領域において半導体基板1上にゲート絶縁膜22を介して形成されたゲート電極23と、ゲート電極23の横の半導体基板1の主面に形成されたLDD層24と、LDD層24上のエピタキシャル層であって、LDD層24と同じ導電型の不純物がLDD層24よりも高濃度で導入された拡散層25とを有している。ゲート電極23の両側の側壁にはサイドウォール11が形成されており、拡散層25はサイドウォール11およびゲート電極23をゲート電極23のゲート長方向において挟むように配置されている。ここでは、LDD層24および拡散層25にはP型の不純物(例えばB(ホウ素))が導入されているものとする。LDD層24はNウエル3が形成された半導体基板1の主面に形成されており、ゲート電極23の直下のNウエル3であるチャネル領域を挟むように形成されている。図2に示す領域には、半導体層13b(図1参照)は形成されていない。

【0042】

拡散層25およびゲート電極23の上面にはシリサイド層14が形成されており、拡散層25およびゲート電極23は、層間絶縁膜16およびエッチストッパ膜15を貫通するコンタクトプラグ17を介して層間絶縁膜16上の配線20に電気的に接続されている。図示していない領域では、ゲート電極23も、シリサイド層14およびコンタクトプラグを介して層間絶縁膜16上の配線と電気的に接続されている。

【0043】

ここでは、高耐圧MOSFETHpは例えば本実施の形態の半導体装置に外部から電気信号を入力し、また電気信号を外部に出力する入出力(インプット/アウトプット:I/O)動作に用いられる高耐圧な電界効果トランジスタであるものとする。つまり、高耐圧MOSFETHpは低耐圧MOSFETLpよりも高耐圧な半導体素子であり、高耐圧MOSFETHpが形成されたバルクシリコン領域はI/O領域であるものとする。高耐圧MOSFETHpはゲート電極23のゲート長方向の幅(ゲート長)が低耐圧MOSFETLpのゲート長方向の幅(ゲート長)よりも長く、ゲート絶縁膜22はゲート絶縁膜7よりも半導体基板1の主面に対して垂直な方向の膜厚が厚く形成されている。

【0044】

図2に示す変形例の半導体装置では、SOI領域とバルクシリコン領域との間に形成された絶縁膜21がゲート絶縁膜22と同等の膜厚を有し、BOX膜4の膜厚の半分以上の膜厚を有しており、ひさし状のSOI膜5の端部の直下の窪みには、SOI膜5の底部および半導体基板1の主面に絶縁膜21が形成されている。したがって、前記窪み内は絶縁膜21が埋込まれているため、ダミーゲート電極8を構成するポリシリコン膜が形成される余地がない。このように、絶縁膜21の膜厚を厚くすればよりSOI膜5および半導体基板1間の絶縁性を高めることができる。特に、絶縁膜21がBOX膜4の膜厚の半分以上の膜厚を有していればひさし状のSOI膜5の端部の直下にはポリシリコン膜が形成されず、当該ポリシリコンの残渣が残らないため、後述するように、より効果的にSOI膜5と半導体基板1との間にリーク電流が流れることを防ぐことができる。

【0045】

なお、図2に示す変形例では、絶縁膜21はゲート絶縁膜22と同層の絶縁膜であり、ゲート絶縁膜22を形成した工程と同一の工程で絶縁膜21を形成しているものとする。図2では半導体基板1の主面に形成された絶縁膜21とSOI膜5の端部の表面に形成された絶縁膜21とが別々の膜として形成され、SOI膜5と半導体基板1との間で接触している構造を示しているが、絶縁膜21はSOI膜5の表面から半導体基板1の主面に亘って連続した層として形成されていてもよい。

【0046】

以下に、図37に示す比較例を用いて本実施の形態の半導体装置の効果について説明する。図37の断面図に示す比較例の半導体装置は、図1に示す本実施の形態の半導体装置とほぼ同様の構造を有しているが、ダミーゲート電極8、絶縁膜6およびダミーゲート電極8の側壁のサイドウォール11が形成されていない点で、図1に示す半導体装置と構造が異なる。なお、図37では図を見やすくするために拡散層、シリサイド層、エッチストッパ膜、層間絶縁膜、コンタクトプラグおよび配線などは図示していない。

【0047】

一つの活性領域上にSOI領域とバルクシリコン領域とが存在する場合、図37に示すように、BOX膜4およびSOI膜5の積層膜を形成すると、BOX膜4がウェットエッチングによりSOI領域側にエッチングされて後退するため、BOX膜4上のSOI膜5はバルクシリコン領域側に突き出したひさし状の形状となる。このように、前記積層膜の側面に窪みがある状態で半導体基板上にゲート電極を形成する目的でポリシリコン膜を形成した後に当該ポリシリコン膜をフォトリソグラフィ技術を用いたドライエッチング法によりパターニングすると、ひさし形状のSOI膜5の端部の直下にポリシリコン膜9pが残る虞がある。

【0048】

なお、ここではゲート電極9の下部のゲート絶縁膜7を形成する際に半導体基板1上に熱酸化法などにより形成された絶縁膜6bが、ポリシリコン膜9pおよびSOI膜5の間と、ポリシリコン膜9pおよび半導体基板1との間のそれぞれに形成されている。

【0049】

この場合、図1に示すようなダミーゲート電極8が形成されていないため、ゲート電極9を形成するためのドライエッチング工程またはその後の洗浄工程などでポリシリコン膜9pがBOX膜4から一部剥がれて浮いたような状態になることが予想され、また、ポリシリコン膜9pの存在に起因して半導体基板1上に残渣が残ることが予想される。このような残渣を残したまま完成した半導体装置では、ポリシリコン膜9pまたはポリシリコン膜9pの存在に起因して発生した残渣を介してSOI膜5と半導体基板1とが短絡(ショート)し、半導体装置が正常に動作しなくなる問題がある。

【0050】

また、前記残渣が形成されず、ひさし形状のSOI膜5と半導体基板1との間がポリシリコン膜9pおよび絶縁膜6bで埋込まれている場合であっても、ポリシリコン膜9pを介してSOI膜5および半導体基板1とが短絡する虞がある。すなわち、ゲート電極9の形成時のドライエッチング工程により一部が除去された絶縁膜6bがSOI膜5の端部の直下のSOI膜5および半導体基板1の表面に形成されていたとしても、絶縁膜6bの絶縁性は十分に保たれておらず、半導体装置の動作時にSOI膜5と半導体基板1との間で短絡が起きることが考えられる。

【0051】

図37に示すように、SOI膜5、絶縁膜6bおよびポリシリコン膜9pのバルクシリコン領域側の側壁にはサイドウォール11aが形成されているが、サイドウォール11aのような絶縁膜によりひさし形状のSOI膜5の側面が覆われていても、上述したような残渣に起因する短絡および絶縁膜6bの絶縁性の低下に起因する短絡が起こる虞がある。

【0052】

なお、ウェットエッチング法により加工されたBOX膜4の端部は、図38の比較例に示すように、SOI膜5の底面の端部に近い領域から除去され、ひさし状のSOI膜5の直下の半導体基板1の表面にはBOX膜4の一部が残るような形状となることが考えられる。図38は比較例として示す半導体装置の一部であって、図37に示すBOX膜4およびSOI膜5の積層膜の端部を拡大して示す断面図であり、ここでは前記積層膜と半導体基板1のみを示している。このようにひさし状の形状を有する前記積層膜は、SOI膜5の上部を含む半導体基板1上にポリシリコン膜からなるゲート電極を形成する工程で、図37に示すようにポリシリコン膜9pがひさし部分の下部に残ることとなり、これに起因して上述したような短絡現象が起こる。BOX膜4の端部が図38に示すような構造になる可能性があることは、図1に示す本実施の形態の半導体装置でも同様である。

【0053】

図38に示すBOX膜4の膜厚は10nmであり、SOI膜5の下部の絶縁膜をパターニングしてBOX膜4を形成する際は膜厚が10nmの前記絶縁膜を除去するウェットエッチングを行うため、SOI膜5の端部の直下のBOX膜4もSOI膜5の底面の端部から10nm程度の範囲が除去され、SOI膜5の端部がひさし状に突き出す形状となる。したがって、SOI膜5の底面に接するBOX膜4は、SOI膜5の底面の端部から10nm後退して形成される。

【0054】

また、上記したひさし部分に残る残渣による短絡の問題の他に、図39の比較例に示すように、SOI膜5とバルクシリコン領域である半導体基板1の主面が、素子分離領域2のような構造を隔てずに隣接することにより、SOI膜5および半導体基板1の表面のそれぞれの上部のエピタキシャル層上のシリサイド層14a同士が接触することに起因して短絡が起こる問題がある。図39は、比較例として示す半導体装置の断面図であり、図37と同様の構造を示しているが、図39では図37の構造に加えて、SOI膜5上のエピタキシャル層である拡散層12bと、半導体基板1上のエピタキシャル層である拡散層13aと、拡散層12bおよび13aのそれぞれの上部のシリサイド層14aと、サイドウォール11および11aとを示している。

【0055】

サイドウォール11はゲート電極9の側壁に形成された絶縁膜であり、サイドウォール11aはサイドウォール11を形成した際にBOX膜4およびSOI膜5からなる積層膜の側壁に形成された絶縁膜である。ここでは、BOX膜4とサイドウォール11aとの間のひさし部分の下部に絶縁膜6bおよびポリシリコン膜9pが形成されているものとする。

【0056】

図39に示すような半導体装置では、ゲート電極9、サイドウォール11および11aを形成した後にエピタキシャル成長法(選択成長法)によりSOI膜5の表面上およびバルクシリコン領域の半導体基板1の表面上にエピタキシャル層(選択成長層)を形成し、そのエピタキシャル層に不純物を注入することで、SOI膜5上に拡散層12bを形成し、半導体基板1上に拡散層13aを形成している。この場合、SOI領域に形成される拡散層12bとバルクシリコン領域に形成される拡散層13aが互いに近い領域に形成されるため、拡散層12b、13aのそれぞれの上部にシリサイド層14aを形成した場合、SOI領域およびバルクシリコン領域に形成されるシリサイド層14aが互いに接触し、またはそれらのシリサイド層14aが一体となって連続的に形成される虞がある。また、SOI領域およびバルクシリコン領域にエピタキシャル層を形成せず、SOI膜5および半導体基板1のそれぞれの上面に直接不純物を注入して拡散層を形成し、その表面にシリサイド層を形成した場合でも、SOI領域およびバルクシリコン領域に形成した前記シリサイド層が短絡する虞がある。

【0057】

このようにしてSOI領域およびバルクシリコン領域のシリサイド層14aが電気的に接続されると、SOI膜5と半導体基板1とが短絡することになるため、半導体装置が正常に動作しない問題が生じる。なお、この問題は前述したひさし状の構造が形成されているかどうかには関係なく生じるものであり、SOI膜5の直下であってBOX膜4の側壁にポリシリコン膜9pおよび絶縁膜6bが形成されておらず、SOI膜5およびBOX膜4の端部が揃っていても、シリサイド層14a同士が接触する問題は起こる。

【0058】

本来、SOI膜5は半導体基板1上にBOX4を隔てて形成されているため半導体基板1と絶縁されており、SOI領域とバルクシリコン領域との間には素子分離領域がなくてもよい。このため、SOI領域とバルクシリコン領域との境界に素子分離領域を形成することを省略することで、半導体装置の面積を低減することができる。

【0059】

しかし、図37および図39の2通りの比較例を用いて述べたように、BOX膜4のエッチングプロセスに起因して半導体基板1上に残渣などが残るとSOI膜5と半導体基板1とが短絡する虞があり、また、SOI膜5の表面および半導体基板1の上に形成されたそれぞれのエピタキシャル層上のシリサイド層14a同士が互いに接触して形成されることにより、SOI膜5と半導体基板1とが短絡する虞がある。

【0060】

そこで、本実施の形態の半導体装置では、図1に示すように、SOI領域とバルクシリコン領域との境界近傍の半導体基板上およびSOI膜5上に絶縁膜6を介してダミーゲート電極8を形成することにより、SOI膜5の端部の直下に形成された絶縁膜およびポリシリコン膜がエッチングまたは洗浄液などに晒されることを防いでいる。

【0061】

つまり、SOI領域とバルクシリコン領域との境界にダミーゲート電極8を形成する場合、ひさし状のSOI膜5の端部とその直下の半導体基板1との間に形成された絶縁膜6およびポリシリコン膜(ダミーゲート電極8)はSOI膜5の側壁に合わせてドライエッチされることはなく、ひさし状の形状のBOX膜4およびSOI膜5の積層膜の端部はダミーゲート電極8および絶縁膜6に覆われたまま半導体装置が完成する。したがって、ひさし状のSOI膜5の端部の直下に微量のポリシリコン膜が残ることにより半導体基板1上に残渣が発生し、前記残渣によってSOI膜5および半導体基板1が短絡することを防ぐことができる。

【0062】

また、図2に示す変形例の半導体装置では、絶縁膜21を高耐圧MOSFETHp用のゲート絶縁膜22と同一工程で形成した厚い膜とすることで、より効果的にSOI膜5と半導体基板1との短絡を防ぐことができる。

【0063】

また、本実施の形態の半導体装置では、ダミーゲート電極8およびその側壁のサイドウォール11を形成することにより、SOI領域およびバルクシリコン領域に形成されるシリサイド層14のそれぞれが近接して形成されることを防いでいる。

【0064】

つまり、ダミーゲート電極8およびその側壁のサイドウォール11を形成すると、サイドウォール11の表面にはシリサイド層は形成されないため、SOI領域の拡散層12およびその上部のシリサイド層14と、バルクシリコン領域の拡散層13およびその上部のシリサイド層14とを分離することができる。このため、SOI領域およびバルクシリコン領域のそれぞれのシリサイド層14が近接して短絡することを防ぐことができる。

【0065】

以上に述べたように、本実施の形態では、半導体装置の微細化などを目的として一つの活性領域内にSOI領域およびバルクシリコン領域を設けた場合に、SOI領域およびバルクシリコン領域の境界にダミーゲート電極を設けることにより、SOI膜および半導体基板が短絡することを防ぐことが可能となるため、半導体装置の信頼性を向上させることができる。また、これにより一つの活性領域内にSOI領域およびバルクシリコン領域を設けた場合に短絡が起こることを防ぎ、半導体素子の微細化の際に生じる前記短絡の問題を解消し、半導体装置の微細化により半導体装置の性能を向上することが可能となる。

【0066】

以下に、図3〜図18を用いて本実施の形態の半導体装置の製造方法を説明する。図3〜図18は本実施の形態の半導体装置の製造工程を示す断面図である。図3〜図18では、図の左側から右側にかけて順に半導体基板上部のSOI領域1Aおよびバルクシリコン領域1Bを示している。SOI領域1Aは半導体基板上に絶縁膜を介して半導体層が形成されるSOI構造を含む領域であり、ここではSOI領域1AにPチャネル型の低耐圧MOSFETを形成する工程について説明する。また、バルクシリコン領域1Bは前記SOI構造を構成する絶縁膜および半導体層から露出する半導体基板コンタクトプラグを接続する領域であり、または低耐圧MOSFETよりも高い電圧により駆動する高耐圧MOSFETを含むI/O部などであるものとする。低耐圧MOSFETは高耐圧MOSFETよりも小さい電流および電圧で駆動するトランジスタであり、半導体装置内のコア部においてスイッチングなどの用途に用いられるものである。なお、ここで言うコア部とは、上記したI/O部とは異なり、I/O部の素子よりも低い電流・電圧で駆動される素子により構成される回路などを含む領域である。

【0067】

まず、図3に示すように、例えば1〜10Ωcm程度の比抵抗を有するN型の単結晶シリコンなどからなる半導体基板(半導体ウエハ)1を準備する。次に、この半導体基板1を熱酸化してその表面に例えば厚さ11nm程度の絶縁膜2bを形成した後、その上層にCVD(Chemical Vapor Deposition)法などにより、例えば厚さ90nm程度の絶縁膜2cを形成(堆積)する。絶縁膜2bは酸化シリコンなどからなり、絶縁膜2cは窒化シリコン膜などからなる。その後、半導体基板1上の全面にフォトレジスト膜PR1を塗布する。

【0068】

次に、図4に示すように、投影露光装置を用いてフォトレジスト膜PR1を露光し、続いて現像を行った後に、フォトレジスト膜PR1の不要な部分を取り除き、半導体基板1上にフォトレジスト膜PR1からなるフォトレジストパターンを残す。ここでは、隣接するSOI領域1Aおよびバルクシリコン領域1Bが覆われるように前記フォトレジストパターンを残す。

【0069】

次に、図5に示すように、フォトレジスト膜PR1をエッチングマスクとして絶縁膜2c、絶縁膜2bおよび半導体基板1を順次ドライエッチングすることにより、素子分離形成予定領域の半導体基板1に、例えば深さ300nm程度の溝(素子分離用の溝)2aを形成した後、酸素プラズマなど用いたアッシング(灰化)を行うことでフォトレジスト膜PR1を除去する。溝2aは、素子分離用の溝であり、すなわち後述する素子分離領域2形成用の溝である。

【0070】

次に、図6に示すように、溝2aの内部(側壁および底部)を含む半導体基板1の主面上に、例えば厚み10nm程度の絶縁膜2dを形成する。それから、半導体基板1の主面上(すなわち絶縁膜2d上)に、溝2a内を埋めるように、絶縁膜2eをCVD法などにより形成(堆積)する。

【0071】

絶縁膜2dは、酸化シリコン膜または酸窒化シリコン膜からなる。絶縁膜2dが酸窒化シリコン膜の場合には、絶縁膜2d形成工程以降の熱処理によって溝2aの側壁が酸化することによる体積膨張を防止でき、半導体基板1に働く圧縮応力を低減できる効果がある。

【0072】

絶縁膜2eは、HDP−CVD(High Density Plasma CVD:高密度プラズマCVD)法により成膜された酸化シリコン膜、またはO3−TEOS酸化膜などである。なお、O3−TEOS酸化膜とは、O3(オゾン)およびTEOS(Tetraethoxysilane:テトラエトキシシラン、Tetra Ethyl Ortho Silicateともいう)を原料ガス(ソースガス)として用いて熱CVD法により形成した酸化シリコン膜である。

【0073】

続いて、半導体基板1を例えば1150℃程度で熱処理することにより、溝2aに埋込んだ絶縁膜2eを焼き締める。焼き締め前の状態では、O3−TEOS酸化膜よりもHDP−CVD法により成膜された酸化シリコン膜の方が緻密である。このため、絶縁膜2eがO3−TEOS酸化膜の場合、焼き締めによる絶縁膜2eの収縮により、半導体基板1に働く圧縮応力を低減できる効果がある。一方、絶縁膜2eがHDP−CVD法により成膜された酸化シリコン膜の場合には、絶縁膜2eがO3−TEOS酸化膜の場合に比べて、焼き締め時の絶縁膜2eの収縮が少ないため、後の工程で形成する素子分離領域2によって半導体基板1に働く圧縮応力が大きくなる。

【0074】

次に、図7に示すように、絶縁膜2eをCMP(Chemical Mechanical Polishing:化学的機械的研磨)法により研磨して絶縁膜2cを露出させ、熱リン酸などを用いたウエットエッチングにより絶縁膜2cを除去した後、フッ酸(HF)水溶液などを用いて溝2aの外部の絶縁膜2eおよび絶縁膜2bを除去し、溝2aの内部に絶縁膜2d、2eを残すことにより、絶縁膜2d、2eからなる素子分離領域(素子分離)2を形成する。

【0075】

前述したCMP法による研磨では、素子分離領域2の上面の高さは半導体基板1の主面の高さにまで後退せず、素子分離領域2の上面と絶縁膜2cの上面との高さが揃うことになる。その後に絶縁膜2c、2bを除去しているため、図7に示すように素子分離領域2の上面の高さは半導体基板1の主面の高さよりも高い状態となる。ただし、素子分離領域2を形成した時点で、素子分離領域2の上面の高さと半導体基板1の主面の高さとが同一の高さで揃っていても構わない。

【0076】

本実施の形態では、素子分離領域2は、STI(Shallow Trench Isolation)法により形成されるものとして説明したが、LOCOS(Local Oxidization of Silicon)法により形成しても構わない。後述するPチャネル型の低耐圧MOSFETLpは、素子分離領域2で規定された(囲まれた)活性領域内に形成される。SOI領域1Aおよびバルクシリコン領域1Bは前記活性領域内に含まれる。

【0077】

次に、図8に示すように、半導体基板1の主面から所定の深さに渡ってNウエル3を形成する。Nウエル3は、半導体基板1の主面に例えばホウ素(B)などのN型の不純物をイオン注入することなどによって形成することができる。なお、図8以降の図では、図を見やすくするために積層構造を有する素子分離領域2を一層の膜として示す。

【0078】

その後、半導体基板1の主面上に、絶縁膜4aおよび半導体層5aを順次形成する。絶縁膜4aは酸化シリコン膜などからなり、例えば熱酸化法、ウェット酸化法、またはCVD法などを用いて、素子分離領域2から露出している半導体基板1の主面に接して形成する。半導体層5aは例えばシリコン膜からなり、絶縁膜4a上および素子分離領域2上にCVD法などを用いて形成する。絶縁膜4aおよび半導体層5aの膜厚はそれぞれ例えば10nmとする。

【0079】

次に、図9に示すように、フォトリソグラフィ技術およびウェットエッチング法を用いて、半導体層5aをパターニングした後に絶縁膜4aをパターニングし、SOI領域1Aの半導体基板1の主面上に絶縁膜4aからなるBOX膜4および半導体層5aからなるSOI膜5を残し、バルクシリコン領域1Bの半導体基板1の主面を露出する。このとき、BOX膜4を形成するエッチング工程では、半導体基板1の主面がエッチング工程により受けるダメージを低減するためにドライエッチング法ではなくウェットエッチング法を用いる必要がある。

【0080】

BOX膜4の側面はSOI膜5の側面と平面視において重なるように揃うことが望ましいが、BOX膜4を形成するエッチング工程はSOI膜5をマスクとして行われ、ウェットエッチング法は等方性のあるエッチング方法であるため、膜厚が10nmの絶縁膜4aを除去する工程では、SOI領域1Aおよびバルクシリコン領域1Bの境界部分のSOI膜5の側面の直下からSOI領域1A方向に絶縁膜4aの側面が後退する。つまり、SOI膜5およびBOX膜4からなる積層膜のバルクシリコン領域1B側の端部は、SOI膜5の端部の方がBOX膜4の端部よりも突出し、BOX膜4が後退した領域が窪んだひさし状の構造となる。

【0081】

次に、図10に示すように、SOI領域1AのSOI膜5の表面およびバルクシリコン領域1Bの半導体基板の主面に酸化シリコン膜からなる絶縁膜6aを形成し、続いて半導体基板1の主面の全面上に、例えばCVD法を用いてポリシリコン膜8aを形成(堆積)する。絶縁膜6aは例えば熱酸化法またはウェット酸化法を用いて形成するため、前記ひさし状の構造を有し、露出しているSOI膜5の端部の上面、側面および底面に形成され、ひさし構造のSOI膜5の端部の直下に露出している半導体基板1の主面にも形成される。

【0082】

このとき、絶縁膜6aの膜厚はBOX膜4の膜厚の半分未満の厚さであり、BOX膜4が後退して形成された窪みには絶縁膜6aにより完全に埋込まれておらず、ポリシリコン膜8aが埋込まれている。ここでは、ひさし状の構造を有するSOI膜5の端部と半導体装置の間には、絶縁膜6a、ポリシリコン膜8aおよび絶縁膜6aが順に形成されるものとする。

【0083】

次に、図11に示すように、フォトリソグラフィ技術およびドライエッチング法を用いて、ポリシリコン膜8aおよび絶縁膜6aをパターニングし、SOI領域1AのSOI膜5の上面と、バルクシリコン領域1Bの半導体基板1の主面とを露出させる。これにより、SOI領域1AのSOI膜5上に絶縁膜6aからなるゲート絶縁膜7を介してポリシリコン膜8aからなるゲート電極9を形成する。また、同工程により、SOI領域1Aおよびバルクシリコン領域1Bの境界近傍のSOI膜5上および半導体基板1上に絶縁膜6aからなる絶縁膜6を介してポリシリコン膜8aからなるダミーゲート電極8を形成する。その後、ゲート電極9およびダミーゲート電極8を形成した際のドライエッチングにより発生したエッチング残渣などを除去するため、半導体基板1を薬液および純水などを用いて洗浄する。

【0084】

このとき、絶縁膜6およびその上のダミーゲート電極8はSOI領域1Aおよびバルクシリコン領域1Bの境界に跨って形成されるため、ひさし状の構造を有するBOX膜4およびSOI膜5からなる積層膜の端部は絶縁膜6およびダミーゲート電極8により覆われる。

【0085】

次に、図12に示すように、バルクシリコン領域1Bを覆い、SOI領域1Aを露出するフォトレジスト膜PR2を半導体基板1上に形成する。なお、フォトレジスト膜PR2はダミーゲート電極8の上面の一部を覆っているものとする。続いて、フォトレジスト膜PR2をマスクとして、ゲート電極9から露出しているSOI膜5にイオン注入法を用いてP型の不純物(例えばB(ホウ素))を注入する。これにより、ゲート電極9のゲート長方向における両側のSOI膜5内に、P型の不純物(例えばB(ホウ素))が比較的低濃度で導入された半導体層であるLDD層10を形成する。

【0086】

次に、図13に示すように、フォトレジスト膜PR2を除去した後、半導体基板1の主面の全面上に例えばCVD法を用いて窒化シリコン膜および酸化シリコン膜を順次形成する。続いて、ドライエッチング法を用いて前記酸化シリコン膜および前記窒化シリコン膜を順次除去して半導体基板1およびSOI膜5のそれぞれの上面を露出させることで、ゲート電極9およびダミーゲート電極8のそれぞれの側壁に前記酸化シリコン膜および前記窒化シリコン膜の積層膜からなるサイドウォール11を自己整合的に形成する。ダミーゲート電極8はSOI膜5の上面から半導体基板1の上面に亘って連続的に形成されているため、ダミーゲート電極8の一方の側壁のサイドウォール11は半導体基板1の上面に接し、もう一方の側壁のサイドウォール11はSOI膜5の上面に接して形成される。

【0087】

その後、ゲート電極9、ダミーゲート電極8およびサイドウォール11から露出している半導体基板1およびSOI膜5のそれぞれの上面に、エピタキシャル成長法(選択成長法)を用いてエピタキシャル層(選択成長層)12aを形成する。このとき、ひさし状の構造を有するBOX膜4およびSOI膜5からなる積層膜の端部は絶縁膜6、ダミーゲート電極8およびダミーゲート電極8の側壁のサイドウォール11により覆われているため、当該積層膜の端部の近傍にはエピタキシャル層12aは形成されない。

【0088】

次に、図14に示すように、フォトリソグラフィ技術およびイオン注入法を用いて、SOI領域1Aおよびバルクシリコン領域1Bの領域のエピタキシャル層12aに、P型の不純物(例えばB(ホウ素))およびN型の不純物(例えばP(リン))をそれぞれ打ち分ける。SOI領域1Aのゲート電極9の両側のエピタキシャル層12aは、P型の不純物(例えばB(ホウ素))が比較的高濃度で導入されることで拡散層12となる。また、バルクシリコン領域1Bのエピタキシャル層12aは、N型の不純物(例えばP(リン))が比較的高濃度で導入されることにより、拡散層13となる。これにより、SOI領域1Aには、ゲート電極9、LDD層10および拡散層12を含む低耐圧MOSFETLpが形成される。また、拡散層13の直下の半導体基板1の主面には、拡散層13を形成する際にバルクシリコン領域1Bの前記エピタキシャル層に注入した不純物が前記エピタキシャル層を通過して注入されており、半導体基板1の主面にNウエル3よりも高い不純物濃度を有する半導体層13bが形成されている。

【0089】

拡散層12はLDD層10よりも高い不純物濃度を有しており、拡散層12およびLDD層10は低耐圧MOSFETLpのソース・ドレイン領域を構成している。また、バルクシリコン領域1Bでは、Nウエル3上にNウエル3よりもN型の不純物の濃度が高い拡散層13が形成されている。拡散層13は半導体基板1に電位を供給するためのボディ端子として機能する半導体領域である。その後、イオン注入した不純物の拡散などを目的として半導体基板1を熱処理する。なお、拡散層12を形成するためのP型の不純物(例えばB(ホウ素))のイオン注入工程と、拡散層13を形成するためのN型の不純物(例えばP(リン))のイオン注入工程とは、どちらを先に行ってもよい。

【0090】

次に、図15に示すように、周知のサリサイド技術により拡散層12、13、ゲート電極9およびダミーゲート電極8のそれぞれの上面にシリサイド層14を形成する。このとき形成するシリサイド層14の部材は、NiSi(ニッケルシリサイド)またはCoSi(コバルトシリサイド)などとすることができる。シリサイド層14は、半導体基板1上に形成したNi(ニッケル)などを含む金属膜を、熱処理により下部の半導体層と反応させることで形成する。シリサイド層14を形成した際、シリサイド層14と拡散層12または13とからなる積層膜の厚さは、シリサイド層14を形成する前の拡散層12または13の厚さよりも厚くなる。このとき、ひさし状の構造を有するBOX膜4およびSOI膜5からなる積層膜の端部は絶縁膜6およびダミーゲート電極8により覆われており、ダミーゲート電極8はサイドウォール11に挟まれているため、当該積層膜の端部の近傍にはシリサイド層14は形成されない。したがって、シリサイド層14はSOI領域1Aおよびバルクシリコン領域1Bの境界においてダミーゲート電極8およびその側壁のサイドウォール11を隔てて分断され、拡散層12上のシリサイド層14と拡散層13上のシリサイド層14とが接触することはない。

【0091】

次に、図16に示すように、半導体基板1の主面上に、低耐圧MOSFETLp、ダミーゲート電極8およびシリサイド層14を覆うようにエッチストッパ膜15および層間絶縁膜16を順次形成する。エッチストッパ膜15は、例えば酸化シリコン膜の単体膜または薄い窒化シリコン膜からなり、その上の層間絶縁膜16は厚い酸化シリコン膜からなる。エッチストッパ膜15および層間絶縁膜16は例えばCVD法により形成し、その後、層間絶縁膜16の表面を、例えばCMP法を使用して平坦化する。

【0092】

次に、図17に示すように、層間絶縁膜16上に形成したフォトレジスト膜(図示しない)をエッチングマスクとして用いて、エッチストッパ膜15および層間絶縁膜16をドライエッチングすることにより、エッチストッパ膜15および層間絶縁膜16を貫通する複数のコンタクトホール(貫通孔)を形成する。前記複数のコンタクトホールは、拡散層12、13およびゲート電極9のそれぞれの上部のシリサイド層14に達する貫通孔である。ただし、後の工程で完成する半導体装置において、ダミーゲート電極8は電気的に機能しない膜なのでダミーゲート電極8の上部のシリサイド層14を露出するコンタクトホールを形成する必要はない。

【0093】

続いて、前記複数のコンタクトホール内に、タングステン(W)などからなる導電性のコンタクトプラグ(接続用導体部)17を形成する。コンタクトプラグ17を形成するには、例えば、コンタクトホールの底部および側壁を含む層間絶縁膜16上に、バリア導体膜(例えばチタン膜、窒化チタン膜、あるいはそれらの積層膜)を形成する。それから、前記バリア導体膜上にタングステン膜などからなる主導体膜を形成して前記コンタクトホールを埋込み、層間絶縁膜16上の不要な前記主導体膜および前記バリア導体膜をCMP法またはエッチバック法などによって除去することにより、コンタクトプラグ17を形成する。なお、図面の簡略化のために、図17ではコンタクトプラグ17を構成するバリア導体膜および主導体膜(タングステン膜)を一体化して示している。

【0094】

次に、図18に示すように、コンタクトプラグ17が埋込まれた層間絶縁膜16上に、エッチストッパ膜(エッチングストッパ用絶縁膜)18および配線形成用の層間絶縁膜19を順次形成する。エッチストッパ膜18は、層間絶縁膜19への溝加工の際にエッチングストッパとなる膜であり、層間絶縁膜19に対してエッチング選択性を有する材料を用い、例えば、エッチストッパ膜18を窒化シリコン膜とし、層間絶縁膜19を酸化シリコン膜とすることができる。

【0095】

その後、シングルダマシン法により第1層目の配線を形成する。まず、フォトレジスト膜(図示しない)をマスクとしたドライエッチングによって層間絶縁膜19およびエッチストッパ膜18の所定の領域にコンタクトプラグ17を露出する複数の配線溝を形成した後、半導体基板1の主面上に例えば窒化チタン膜、タンタル膜または窒化タンタル膜などからなるバリアメタル膜を形成する。続いて、CVD法またはスパッタリング法などによりバリアメタル膜上に銅のシード層を形成し、さらに電解めっき法などを用いてシード層上に銅めっき膜を形成し、前記銅めっき膜により前記配線溝の内部を埋込む。それから、配線溝以外の領域の銅めっき膜、シード層およびバリアメタル膜をCMP法により除去して、銅を主導電材料とする第1層目の配線20を形成する。なお、図面の簡略化のために、図18では、配線20を構成する銅めっき膜、シード層およびバリアメタル膜を一体化して示してある。

【0096】

SOI領域1Aの配線20は、コンタクトプラグ17を介して低耐圧MOSFETLpのソース・ドレイン領域およびゲート電極9に電気的に接続されている。バルクシリコン領域1Bの配線20は、コンタクトプラグ17、シリサイド層14および拡散層13を介して半導体基板1に電気的に接続されている。また、その後、デュアルダマシン法などにより配線20上に2層目以降の配線を形成することで本実施の形態の半導体装置が完成するが、ここでは2層目以降の配線の図示およびその製造工程の説明は省略する。また、配線20はダマシン配線に限定されず、配線用の導電体膜をパターニングして形成することもでき、その場合、配線20は例えばタングステン配線またはアルミニウム配線などとすることもできる。

【0097】

このように、隣り合う素子分離領域に挟まれた一つの活性領域内にSOI領域およびバルクシリコン領域が隣接して存在する半導体装置を製造する場合、図37および図38を用いて説明したように、SOI領域およびバルクシリコン領域の境界近傍においてダミーゲート電極8(図18参照)を形成せずにゲート電極9を形成すると、ひさし状のSOI膜5の端部の下の窪みにゲート電極9を形成するためのポリシリコン膜9pが残る。この状態で半導体装置の製造工程を続けると、ポリシリコン膜9pが残渣となって半導体基板1上に残り、当該残渣を介するなどしてSOI膜5と半導体基板1とが短絡する虞がある。

【0098】

図37のような構造は、図11を用いて説明したパターニング工程においてSOI領域およびバルクシリコン領域の境界近傍にダミーゲート電極8を形成せず、その他の領域(例えばSOI領域)にゲート電極をドライエッチング法により加工形成することで形成される。図37に示すようなポリシリコン膜9pに起因して残渣が発生すれば、SOI膜5および半導体基板1が残渣を介して短絡することなどが考えられ、完成した半導体装置が正常に動作しなくなる虞がある。

【0099】

また、図39を用いて説明したように、前記残渣による短絡などの不具合が起こらなかったとしても、SOI膜5と半導体基板1とがSOI領域とバルクシリコン領域との境界において素子分離領域のように幅が広い絶縁体を隔てず極近い領域で隣接する場合、半導体基板1の表面に形成されたエピタキシャル層である拡散層13aが、SOI膜5およびSOI膜5の表面に形成されたエピタキシャル層である拡散層12bに接近する。この場合、SOI膜5および拡散層12bと、拡散層13aとのそれぞれの表面に形成されたシリサイド層14a同士が接触し、または一体化して形成されることで、SOI膜5および半導体基板1が短絡し、完成した半導体装置が正常に動作しなくなる。

【0100】

このような短絡が起こることに起因して半導体装置の信頼性が低下することを防ぐため、本実施の形態の半導体装置の製造工程では、図11に示すように、SOI領域とバルクシリコン領域との境界近傍の半導体基板上およびSOI膜5上に絶縁膜6を介してダミーゲート電極8を形成することにより、SOI膜5の端部の直下に形成された絶縁膜およびポリシリコン膜がエッチングまたは洗浄液などに晒されることを防いでいる。

【0101】

これにより、ひさし状のSOI膜5の端部の直下に微量のポリシリコン膜が残ることに起因して半導体基板1上に残渣が発生し、前記残渣によってSOI膜5および半導体基板1が短絡することを防ぐことができる。

【0102】

また、本実施の形態の半導体装置の製造工程では、図16に示すように、ダミーゲート電極8およびその側壁のサイドウォール11を形成することにより、SOI領域およびバルクシリコン領域に形成されるシリサイド層14のそれぞれが近接して形成されることを防いでいる。

【0103】

つまり、ダミーゲート電極8およびその側壁のサイドウォール11を形成すると、サイドウォール11の表面にはシリサイド層は形成されないため、SOI領域の拡散層12およびその上部のシリサイド層14と、バルクシリコン領域の拡散層13およびその上部のシリサイド層14とを分離することができる。よって、SOI領域およびバルクシリコン領域のそれぞれのシリサイド層14が近接して短絡することを防ぐことができる。

【0104】

したがって、本実施の形態の半導体装置の製造工程では、半導体装置の微細化などを目的として一つの活性領域内にSOI領域およびバルクシリコン領域を設けた場合に、SOI領域およびバルクシリコン領域の境界にダミーゲート電極を設けることにより、SOI膜および半導体基板が短絡することを防ぐことが可能となるため、半導体装置の信頼性を向上させることができる。また、これにより一つの活性領域内にSOI領域およびバルクシリコン領域を設けた場合に短絡が起こることを防ぎ、半導体素子の微細化の際に生じる前記短絡の問題を解消することができるため、半導体装置の微細化により半導体装置の性能を向上することが可能となる。

【0105】

また、本実施の形態の半導体装置の製造方法の変形例として、ダミーゲート電極8の下面に接する絶縁膜の膜厚をゲート絶縁膜7よりも厚くして、より効果的にSOI膜5と半導体基板1との短絡を防ぐことが考えられる。この場合の半導体装置の製造工程を図3〜図9および図19〜図23を用いて説明する。図19〜図23は本実施の形態の半導体装置の製造工程の変形例を説明する断面図である。

【0106】

まず、図3〜図9を用いて説明した工程を行った後、半導体基板1上に厚さが異なる2種類の絶縁膜を半導体基板1の上面に形成する。つまり、図19に示すように、半導体基板1の主面の全面に熱酸化法、ウェット酸化法またはCVD法などを用いて、比較的膜厚が厚い絶縁膜21aを形成した後に、フォトリソグラフィ技術およびウェットエッチング法などを用いてSOI領域1Aの絶縁膜21aを除去し、バルクシリコン領域1Bには絶縁膜21aを残す。ただし、このときにSOI膜5のバルクシリコン領域1B側の端部に形成された絶縁膜21aは除去しない。なお、絶縁膜21aは熱酸化法、ウェット酸化法により形成されるため、形成時には半導体基板1上に露出する半導体基板1の上面およびSOI膜5の表面に形成される。したがって、SOI膜5のバルクシリコン領域1B側の端部では、SOI膜5の上面、側壁および底面に亘って絶縁膜21aが連続的に形成され、その下部では半導体基板1の主面にも絶縁膜21aが形成される。その後、例えば熱酸化法またはウェット酸化法などを用いて半導体基板1の主面を酸化し、絶縁膜21aから露出するSOI膜5の上面に、絶縁膜21aよりも膜厚が薄い絶縁膜6aを形成する。絶縁膜6a、21aは例えば酸化シリコンからなる膜である。

【0107】

ここではBOX膜4の膜厚を10nmとし、絶縁膜21aの膜厚を5nmとしており、また、SOI領域1Aおよびバルクシリコン領域1Bの境界近傍におけるSOI膜5およびBOX膜4からなる積層膜の端部のひさし構造では、SOI膜5と半導体基板1との間隔がBOX膜4の膜厚となっている。SOI膜5と半導体基板1との間のSOI膜5の底面および半導体基板1の上面に形成された絶縁膜21aは、それぞれBOX膜4の膜厚の値の半分以上の膜厚を有しているため、SOI膜5と半導体基板1との間には絶縁膜21aが完全に埋込まれている。

【0108】

次に、図20に示すように、半導体基板1の主面上の全面に例えばCVD法を用いてポリシリコン膜を形成(堆積)した後、フォトリソグラフィ技術およびドライエッチング法を用いて前記ポリシリコン膜およびその下部の絶縁膜6a、21aを加工(パターニング)することで、前記ポリシリコン膜からなるゲート電極9、ダミーゲート電極8およびゲート電極23を形成する。また、同一の工程により、絶縁膜6aからなるゲート絶縁膜7をゲート電極9とSOI膜5との間に形成し、絶縁膜21aからなる絶縁膜21を、ダミーゲート電極8とSOI膜5との間およびダミーゲート電極8と半導体基板1との間に形成し、絶縁膜21aからなるゲート絶縁膜22をバルクシリコン領域1Bのゲート電極23と半導体基板1との間に形成する。

【0109】

絶縁膜21およびゲート絶縁膜22は絶縁膜21aからなるため、絶縁膜6aからなるゲート絶縁膜7よりも厚い膜厚を有している。また、ゲート電極23はゲート電極9よりもゲート長が大きく、その下部のゲート絶縁膜22はゲート絶縁膜7よりもゲート幅方向における幅が広い。

【0110】

次に、図12を用いて説明した工程を行うことでSOI領域1AにLDD層10を形成した後、図21に示すように、SOI領域1Aをフォトレジスト膜(図示しない)で覆い、続いて、バルクシリコン領域1Bに露出する半導体基板1の主面に、ゲート電極23をマスクとしてP型の不純物(例えばB(ホウ素))をイオン注入法により注入することにより、ゲート電極23の横の半導体基板1の主面にLDD層24を形成する。なお、LDD層10およびLDD層24はどちらを先に形成してもよく、同一工程により形成してもよい。

【0111】

次に、図13を用いて説明したエピタキシャル層の製造工程を行った後、図22に示すように、ゲート電極9、22のそれぞれの横に形成されたエピタキシャル層にP型の不純物(例えばB(ホウ素))を高い濃度でイオン注入することにより、前記エピタキシャル層からなるP型の拡散層12、25をゲート電極9、22のそれぞれの横に形成する。なお、LDD層10、24を形成した工程と同様に、拡散層12および拡散層25を形成する際には、それぞれの拡散層を別のイオン注入工程により形成しても構わない。

【0112】

これにより、SOI領域1AにはLDD層10、拡散層12およびゲート電極9を含む低耐圧MOSFETLpが形成され、バルクシリコン領域1BにはLDD層24、拡散層25およびゲート電極23を含む高耐圧MOSFETHpが形成される。高耐圧MOSFETHpは低耐圧MOSFETLpよりも大きい膜厚を有するゲート絶縁膜22と、低耐圧MOSFETLpよりも大きいゲート長を有するゲート電極23を含んでいる。これは、高耐圧MOSFETHpが低耐圧MOSFETLpよりも高い電圧により駆動するトランジスタであるためである。ここでは、高耐圧MOSFETHpは半導体装置の外部に出力し、または半導体装置の外部から入力される電流を制御するI/O部において用いられる半導体素子とする。

【0113】

その後の工程は、図15〜図18を用いて説明した工程と同様の工程を行うことで、図23に示す半導体装置が完成する。このとき、バルクシリコン領域1Bでは、高耐圧MOSFETHpのソース・ドレイン領域を構成するLDD層24および拡散層25に所定の電位を供給するため、拡散層25の上面のシリサイド層14に達するコンタクトプラグ17およびその上部の配線20を形成する。また、図示しない領域では、ゲート電極23上のシリサイド層14に接続されるコンタクトプラグ17も形成する。なお、図18に示したような半導体基板1の電圧を制御する目的で形成されたコンタクトプラグ17および配線20は、図23に示していない他の領域に形成されているものとする。

【0114】

このようにして形成した本実施の形態の半導体装置は、絶縁膜21を高耐圧MOSFETHp用のゲート絶縁膜22と同一工程で形成した厚い膜とすることで、図18に示す構造の半導体装置より効果的にSOI膜5と半導体基板1との短絡を防ぐことを可能としている。特に、絶縁膜21の膜厚をBOX膜4の膜厚の2分の1以上の厚さとすることは、SOI膜5の一方の端部の直下のBOX膜4が後退した領域に絶縁膜21を完全に埋込み、当該SOI膜5の直下にポリシリコン膜が入り込むことを防ぐことができるため、SOI膜5と半導体基板1とが短絡することを防ぐ観点から好ましい。

【0115】

本実施の形態では、MOSFETのゲート電極の横にエピタキシャル層を形成し、当該エピタキシャル層をソース・ドレイン領域とする半導体層装置について説明したが、エピタキシャル層を形成せず、SOI膜またはバルクシリコン領域の半導体基板の主面に直接イオン注入を行ってLDD層よりも不純物濃度が高い拡散層を形成してもよい。この場合であっても、図39に示す構造と同様にSOI領域およびバルクシリコン領域の境界にダミーゲート電極を形成しなければ、前記拡散層が形成されたSOI膜および半導体基板の表面のシリサイド層同士が短絡する虞がある。これに対し、図1に示すようにダミーゲート電極8およびその両側のサイドウォール11を形成することにより、SOI領域およびバルクシリコン領域のそれぞれのシリサイド層14同士が電気的に接続されることを防ぐことができる。

【0116】

また、図24に示すように、本実施の半導体装置の変形例として、バルクシリコン領域において半導体基板1に電位を供給するコンタクトプラグ17aを、平面視においてダミーゲート電極8に重なるように形成した構造を示す。つまり、コンタクトプラグはダミーゲート電極8と、ダミーゲート電極8およびその側壁のサイドウォール11から露出するバルクシリコン領域1Bの半導体基板1の主面とに平面視において重なるように形成されている。言い換えれば、コンタクトプラグ17aはダミーゲート電極8の直上およびバルクシリコン領域1Bに亘って形成され、ダミーゲート電極8上のシリサイド層14およびバルクシリコン領域1Bのシリサイド層14に接続されるている。これにより、コンタクトプラグ17aがダミーゲート電極8と電気的に接続されても、ダミーゲート電極8自体は他の素子と絶縁されているため問題はない。コンタクトプラグ17aがダミーゲート電極8の直上に形成されておらず、ダミーゲート電極8の上部のシリサイド層14の側面とコンタクトプラグ17の側面とが接触するなどしていても同様である。

【0117】

また、図示は省略するが、図24と異なり、半導体基板1に電位を供給するコンタクトプラグ17aはダミーゲート電極8から離れて絶縁され、SOI領域の低耐圧MOSFETLpのダミーゲート電極8に近い方のソース・ドレイン領域に電位を供給するコンタクトプラグ17がダミーゲート電極8に接触し、電気的に接続されていても同様に問題はない。つまり、ダミーゲート電極8が半導体装置内の回路を構成せず、他の素子および配線などから絶縁されているため、ダミーゲート電極8の隣接するコンタクトプラグ17または17aのいずれか一方に接続されたとしても半導体装置の動作に影響はない。このため、ダミーゲート電極8の横の一方のコンタクトプラグとダミーゲート電極8との間の距離を十分に離して互いに接触しないようにする必要がなく、マージンを小さくすることが可能となるため、半導体装置の微細化が容易となる。

【0118】

(実施の形態2)

本実施の形態では、SOI領域にシリサイド層を形成する際に、バルクシリコン領域の半導体層上にシリサイド層が形成されることを防ぐことにより、SOI領域およびバルクシリコン領域のそれぞれのシリサイド層同士が接続することで短絡が起きることを防ぐことができる半導体装置について説明する。

【0119】

図39を用いて説明したように、SOI膜5と半導体基板1とは、SOI領域およびバルクシリコン領域のそれぞれのシリサイド層14a同士が電気的に接続されることにより短絡する問題がある。前記実施の形態では、SOI領域およびバルクシリコン領域の境界にダミーゲート電極を形成し、SOI領域およびバルクシリコン領域のシリサイド層を分離することにより前記短絡を防ぐことを記載したが、本実施の形態ではダミーゲート電極を形成せず、バルクシリコン領域にシリサイド層を形成しないことで前記短絡が起こることを防ぐ。なお、以下に示す図25および図26は、本実施の形態の半導体装置の製造工程を説明する断面図である。

【0120】

上述したような半導体装置を形成する方法としては、まず、図3〜図14を用いて説明した工程と同様の工程を行った後に、図25に示すように、例えば酸化シリコンからなるマスク材である絶縁膜26をバルクシリコン領域1Bの半導体基板1上に形成し、バルクシリコン領域の拡散層13を絶縁膜26により覆う。なお、本実施の形態ではダミーゲート電極は形成しないため、図11を用いて説明した工程ではゲート電極9およびゲート絶縁膜7のみを形成し、ダミーゲート電極8およびその下部の絶縁膜6は形成しない。したがって、図37に示す半導体装置と同様に、SOI膜5の端部の直下であってBOX膜4の側壁にはポリシリコン膜9pおよび絶縁膜6bが残っているものとする。また、図13のサイドウォール形成工程では、SOI膜5とその端部の直下のポリシリコン膜9pおよび絶縁膜6bとからなる積層膜の側壁に自己整合的にサイドウォール11aが形成されているものとする。

【0121】

絶縁膜26は、例えば図14の工程の後に、半導体基板1の主面の全面上にCVD法などを用いて酸化シリコン膜を形成し、続いてフォトリソグラフィ技術およびドライエッチング法を用いてバルクシリコン領域1B以外の領域の前記酸化シリコン膜を除去することで形成する。図25ではSOI領域1Aおよびバルクシリコン領域1Bの境界近傍の絶縁膜26の端部がサイドウォール11a上に位置するような構造を示しているが、絶縁膜26のSOI領域1A側の端部は、バルクシリコン領域1Bの拡散層13を覆い、SOI領域1Aの拡散層12を覆わない位置であれば、どの位置にあっても構わない。つまり、絶縁膜26の前記端部はサイドウォール11aの直上か、拡散層12から露出するSOI膜5の直上にあるものとする。

【0122】

次に、図15〜図18を用いて説明した工程と同等の工程を行うことで、図26に示す本実施の形態の半導体装置が完成する。つまり、図25に示す構造を形成した後、絶縁膜26によりバルクシリコン領域1Bを覆った状態で半導体基板1の主面の全面上に例えばNi(ニッケル)などからなる金属膜を形成した後に半導体基板1を複数回熱処理することにより、絶縁膜26から露出している拡散層12の表面にシリサイド層14を形成する。このとき、拡散層13は絶縁膜(マスク材)26に覆われており前記金属膜に接していないため、拡散層13の表面にはシリサイド層は形成されない。このように、絶縁膜などを用いて一部の半導体層の表面にシリサイド層が形成されないようにすることを、ここではシリサイドプロテクションと呼ぶ。

【0123】

その後、絶縁膜26を残した状態で、エッチストッパ膜15、層間絶縁膜16を形成した後に、SOI領域1Aのシリサイド層14に達するコンタクトプラグ17と、バルクシリコン領域1Bの拡散層13の上面に達し、半導体基板1に電位を供給するためのコンタクトプラグ17とを形成し、続いて配線20を形成する。バルクシリコン領域1Bにコンタクトプラグ17を形成する際は、絶縁膜26、エッチストッパ膜15および層間絶縁膜16を貫通するコンタクトホールを形成する。

【0124】

このようにして形成した半導体装置では、シリサイドプロテクションを行うことでバルクシリコン領域1Bの拡散層13の上面にシリサイド層が形成されないため、図39に示したようにSOI領域およびバルクシリコン領域のそれぞれのシリサイド層14a同士が接続されることによりSOI膜5と半導体基板1とが短絡することを防ぐことができる。

【0125】

これにより、半導体装置が正常に動かなくなることを防ぐことが可能となるため、半導体装置の信頼性を向上させることができる。

【0126】

なお、図25および図26ではバルクシリコン領域1Bの拡散層13を絶縁膜26で完全に覆い、拡散層13の上面にシリサイド層を一切形成しない場合について説明したが、絶縁膜26を形成する領域をSOI領域1Aおよびバルクシリコン領域1Bの境界近傍のみに限り、拡散層13の上面の一部にシリサイド層を形成してもよい。つまり、SOI領域1Aおよびバルクシリコン領域1Bのそれぞれに形成されたシリサイド層同士が、SOI領域1Aおよびバルクシリコン領域1Bの境界において互いに接続されることを防げば上記効果が得られるため、前記境界近傍のバルクシリコン領域にシリサイド層が形成されていなければ、バルクシリコン領域内の他の領域にシリサイド層が形成されていてもよい。この場合は図18と同様に、バルクシリコン領域1Bではコンタクトプラグ17をシリサイド層14を介して拡散層13および半導体基板1に電気的に接続すればよい。

【0127】

また、SOI領域1Aおよびバルクシリコン領域1Bの境界近傍のみに絶縁膜26を形成する場合には、図19〜図23を用いて説明した工程と同様の工程を行い、バルクシリコン領域1BにMOSFETを形成することも可能である。なお、このとき前記境界近傍には絶縁膜26を形成しているため、前記実施の形態1で説明したダミーゲート電極は形成しない。

【0128】

(実施の形態3)