半導体装置およびその製造方法

【課題】耐圧を確保しつつ、オン抵抗を下げることのできる半導体装置およびその製造方法を提供する。

【解決手段】高抵抗で第1導電型の第1ベース層12と、第1ベース層の裏面に設けられた第1導電型のドレイン層10と、第1ベース層の表面に形成された第2導電型の第2ベース層16と、第2ベース層の表面に形成された第1導電型のソース層18と、ソース層および第2ベース層の表面上に配置されたゲート絶縁膜20と、ゲート絶縁膜上に配置されたゲート電極22と、ゲート絶縁膜の下面からドレイン層に向かって延伸して配置された第1導電型の電流導通層14と、ドレイン層に設けられたドレイン電極28と、ソース層および第2ベース層に設けられたソース電極26とを備え、電流導通層の側面と第2ベース層の最接近部との距離W1と、第2ベース層とドレイン層との垂直方向の距離W2との関係が、W1>W2となるように構成した。

【解決手段】高抵抗で第1導電型の第1ベース層12と、第1ベース層の裏面に設けられた第1導電型のドレイン層10と、第1ベース層の表面に形成された第2導電型の第2ベース層16と、第2ベース層の表面に形成された第1導電型のソース層18と、ソース層および第2ベース層の表面上に配置されたゲート絶縁膜20と、ゲート絶縁膜上に配置されたゲート電極22と、ゲート絶縁膜の下面からドレイン層に向かって延伸して配置された第1導電型の電流導通層14と、ドレイン層に設けられたドレイン電極28と、ソース層および第2ベース層に設けられたソース電極26とを備え、電流導通層の側面と第2ベース層の最接近部との距離W1と、第2ベース層とドレイン層との垂直方向の距離W2との関係が、W1>W2となるように構成した。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置およびその製造方法に係り、特に耐圧を確保しつつ、オン抵抗を下げることのできる半導体装置およびその製造方法に関する。

【背景技術】

【0002】

近年、電子機器の低消費電力化、信頼性の向上等の観点から、半導体装置についてオン抵抗の低減が要望されている。

【0003】

例えば、ノート型パソコンや携帯電話等の携帯型通信機器の電源回路のスイッチング素子として用いられる半導体装置の一例としてのMOSFET(Metal Oxide Silicon Field Efect Transistor)は、内蔵電池によりできるだけ長時間にわたって駆動させるために、オン抵抗の低抵抗化が望まれている。例えば、オン抵抗の低減と過電流の低減とは、トレードオフの関係になっており、スイッチング素子としての高性能化には、オン抵抗の低減が必須であった。

【0004】

このような要望からオン抵抗を低減させる技術は種々提案されている(例えば、特許文献1参照。)。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2008−60152号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

ところで、プレーナ型MOSFETでは、高抵抗で比較的厚いエピタキシャル層のエピ抵抗と、プレーナ型構造に特有のJFET抵抗が、全オン抵抗の90%以上を占めている。

【0007】

ここで、エピ抵抗とは、エピタキシャル層を電子が流れるときの抵抗を言う。

【0008】

また、JFET抵抗は、接合型電界効果トランジスタ(JFET:Junction Field Effect Transistor) 抵抗の略であり、プレーナ型では隣接するセル間に寄生的にJFETが形成されて抵抗成分となる。

【0009】

JFET抵抗を下げるためには、JFET領域の不純物濃度を高くすれば良く、通常、ドリフト層(伝導層)よりも高い不純物濃度としている。

【0010】

しかしながら、不純物濃度を高くすると、空乏層が伸び難くなり、ドリフト層ではなく、JFET領域でアバランシェ降伏が起きて、耐圧が低下してしまう。このため、JFET抵抗を低減することにも限界があった。

【0011】

本発明の目的は、耐圧を確保しつつ、オン抵抗を下げることのできる半導体装置およびその製造方法を提供することにある。

【課題を解決するための手段】

【0012】

上記目的を達成するための本発明の一態様によれば、高抵抗で第1導電型の第1ベース層と、前記第1ベース層の裏面に設けられた第1導電型のドレイン層と、前記第1ベース層の表面に形成された第2導電型の第2ベース層と、前記第2ベース層の表面に形成された第1導電型のソース層と、前記ソース層および前記第2ベース層の表面上に配置されたゲート絶縁膜と、前記ゲート絶縁膜上に配置されたゲート電極と、前記ゲート絶縁膜の下面から前記ドレイン層に向かって延設された第1導電型の電流導通層と、前記ドレイン層に設けられたドレイン電極と、前記ソース層および前記第2ベース層に設けられたソース電極とを備え、前記電流導通層の側面と前記第2ベース層の最接近部との距離W1と、前記第2ベース層と前記ドレイン層との垂直方向の距離W2との関係が、W1>W2である半導体装置が提供される。

【0013】

本発明の他の態様によれば、高抵抗で第1導電型の第1ベース層と、前記第1ベース層の裏面に配置された電流導通層と、前記第1ベース層の裏面に配置された第1導電型のドレイン層と、前記第1ベース層の表面に配置された第2導電型の第2ベース層と、前記第2ベース層の表面に配置された第1導電型のソース層と、前記第1ベース層の表面に、前記第2ベース層の深さよりも浅く配置された第2導電型の第3ベース層と、前記第1ベース層の表面より、前記ソース層、前記第2ベース層を貫通して形成されたトレンチと、前記トレンチの底面および側壁面に配置されたゲート絶縁膜と、前記ゲート絶縁膜上に配置され、前記トレンチを充填するゲート電極と、前記ゲート電極を被覆して配置された層間絶縁膜と、前記ドレイン層に形成されたドレイン電極と、前記ソース層、前記第2ベース層に形成されたソース電極とを備え、前記電流導通層の上面と前記第3ベース層の下面との距離W1と、前記ドレイン層の上面と前記第2ベース層の下面との距離W2との関係が、W1>W2である半導体装置が提供される。

【0014】

本発明の他の態様によれば、高抵抗で第1導電型の第1ベース層を形成する工程と、前記第1ベース層の裏面に第1導電型のドレイン層を形成する工程と、前記第1ベース層の表面に第2導電型の第2ベース層を形成する工程と、前記第2ベース層の表面に第1導電型のソース層を形成する工程と、前記第1ベース層内または前記第1ベース層を貫通して前記ドレイン層に向かう電流導通層を形成する工程と、前記ソース層、前記第2ベース層および前記電流導通層の表面上にゲート絶縁膜を形成する工程と、前記ゲート絶縁膜上にゲート電極を形成する工程と、前記ドレイン層にドレイン電極を形成する工程と、前記ソース層および前記第2ベース層にソース電極を形成する工程とを有する半導体装置の製造方法が提供される。

【0015】

本発明の他の態様によれば、高抵抗で第1導電型の第1ベース層を形成する工程と、

前記第1ベース層の裏面に電流導通層を形成する工程と、前記第1ベース層の裏面に第1導電型のドレイン層を形成する工程と、前記第1ベース層の表面に第2導電型の第2ベース層を形成する工程と、前記第2ベース層の表面に第1導電型のソース層を形成する工程と、前記第1ベース層の表面に、前記第2ベース層の深さよりも浅く第2導電型の第3ベース層を形成する工程と、前記第1ベース層の表面より、前記ソース層、前記第2ベース層を貫通してトレンチを形成する工程と、前記トレンチの底面および側壁面にゲート絶縁膜を形成する工程と、前記ゲート絶縁膜上に、前記トレンチを充填するゲート電極を形成する工程と、前記ゲート電極を被覆して層間絶縁膜を形成する工程と、前記ドレイン層にドレイン電極を形成する工程と、前記ソース層、前記第2ベース層にソース電極を形成する工程とを有する半導体装置の製造方法が提供される。

【発明の効果】

【0016】

本発明によれば、耐圧を確保しつつ、オン抵抗を下げることのできる半導体装置およびその製造方法を提供することができる。

【図面の簡単な説明】

【0017】

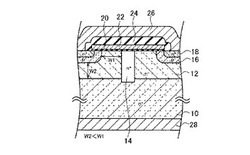

【図1】第1の実施の形態に係る半導体装置の模式的断面構造図。

【図2】第1の実施の形態に係る半導体装置の抵抗値の概念を示す模式的断面構造図。

【図3】第1の実施の形態に係る半導体装置の変形例を示す模式的断面構造図。

【図4】第1の実施の形態に係る半導体装置を並設した状態を示す模式的断面構造図。

【図5】第1の実施の形態に係る半導体装置の模式的鳥瞰図。

【図6】第1の実施の形態に係る半導体装置の製造方法の一工程を説明する模式的断面構造図。

【図7】第1の実施の形態に係る半導体装置の製造方法の一工程を説明する模式的断面構造図。

【図8】第1の実施の形態に係る半導体装置の製造方法の一工程を説明する模式的断面構造図。

【図9】第1の実施の形態に係る半導体装置の製造方法の一工程を説明する模式的断面構造図。

【図10】第1の実施形態に係る半導体装置における主要要素のストライプ状平面レイアウトを示す模式図。

【図11】図10のI−I線における模式的断面構造図。

【図12】第2の実施形態に係る半導体装置における主要要素のストライプ状平面レイアウトを示す模式図。

【図13】図12のII−II線における模式的断面構造図。

【図14】第1または第2の実施形態に係る半導体装置の四角形状平面パターン構成図。

【図15】第1または第2の実施形態に係る半導体装置の六角状平面パターン構成図。

【図16】第3の実施の形態に係る半導体装置であって、図17〜図18において、III−III線に沿う模式的断面構造図。

【図17】第3の実施の形態に係る半導体装置の格子状平面パターン構成図。

【図18】第3の実施の形態に係る半導体装置のストライプ状平面パターン構成図。

【図19】実施の形態に係る半導体装置を用いて構成した3相インバータの模式的回路構成図。

【発明を実施するための形態】

【0018】

次に、図面を参照して、本発明の実施の形態を説明する。以下において、同じブロックまたは要素には同じ符号を付して説明の重複を避け、説明を簡略にする。図面は模式的なものであり、現実のものとは異なることに留意すべきである。また、図面相互間においても互いの寸法の関係や比率が異なる部分が含まれていることはもちろんである。

【0019】

以下に示す実施の形態は、この発明の技術的思想を具体化するための装置や方法を例示するものであって、この発明の実施の形態は、各構成部品の配置などを下記のものに特定するものでない。この発明の実施の形態は、特許請求の範囲において、種々の変更を加えることができる。

【0020】

[第1の実施の形態]

(素子構造)

本発明の第1の実施の形態に係る半導体装置の模式的断面構造は、図1に示すように表される。また、第1の実施の形態に係る半導体装置を並設した状態を示す模式的断面構造図は図4に示すように表される。また、第1の実施の形態に係る半導体装置の模式的鳥瞰図は図5に示すように表される。

【0021】

第1の実施の形態に係る半導体装置は、図1、図4および図5に示すように、高抵抗でn型不純物をドープされた第1ベース層12と、第1ベース層12の裏面に設けられ、n型不純物をドープされたドレイン層10と、第1ベース層12の表面に形成され、p型不純物をドープされた第2ベース層16と、第2ベース層16の表面に形成され、n型不純物をドープされたソース層18と、ソース層18および第2ベース層16の表面上に配置されたゲート絶縁膜20と、ゲート絶縁膜20上に配置されたゲート電極22と、ゲート絶縁膜20の下面からドレイン層10に向かって延設され、n型不純物をドープされた電流導通層14と、ドレイン層10に設けられたドレイン電極28と、ソース層18および第2ベース層16に設けられたソース電極26とを備える。

【0022】

図1に示す半導体装置では、電流導通層14は、ゲート絶縁膜20の下面から第1ベース層12を貫通してドレイン層10まで達する深さに形成されている。

【0023】

そして、電流導通層14の側面と第2ベース層16の最接近部との距離W1と、第2ベース層16とドレイン層10との垂直方向の距離W2との関係が、W1>W2となるように構成されている。

【0024】

n型不純物としては、例えば、P、As、Sbなどを適用することができ、p型不純物は、例えば、B、Al、Gaなどを適用することができる。これらの不純物は、拡散技術若しくはイオン注入技術を用いて各層にドーピングすることができる。

【0025】

ゲート絶縁膜20としては、例えば、シリコン酸化膜、シリコン窒化膜、シリコン酸窒化膜、ハフニウム酸化膜、アルミナ膜、タンタル酸化膜などを適用することができる。

【0026】

ゲート電極22としては、例えば、ポリシリコンを適用することができ、ドレイン電極28とソース電極26には、例えば、アルミニウムを適用することができる。

【0027】

層間絶縁膜24としては、例えば、シリコン酸化膜、シリコン窒化膜、TEOS(テトラエトキシシラン)膜などを適用することができる。

【0028】

また、電流導通層14としては、n型不純物をドープされたシリコン、n型不純物をドープされたポリシリコンまたは金属(例えば、W等)の何れかで形成することができる。

【0029】

ここで、本実施の形態に係る半導体装置のオン抵抗について述べる前に、図2を参照して、比較対象としての半導体装置のオン抵抗について簡単に説明する。

【0030】

図2に示す半導体装置は、一般的な構造のプレーナ型MOSFETである。

【0031】

このプレーナ型MOSFETにおいて、ドレイン電極28とゲート電極22との間のオン抵抗R(on)は、ドレイン層10の抵抗R(n)と、エピ抵抗R(epi)と、JFET抵抗R(JFET)と、チャネル抵抗R(ch)と、ソース層18の抵抗R(n)と、電極の金属抵抗R(metal)との合成抵抗となる。

【0032】

即ち、R(on)=R(n)+R(epi)+R(JFET)+R(ch)+R(n)+R(metal)となる。

【0033】

これらの抵抗のうち、エピ抵抗R(epi)とJFET抵抗R(JFET)の比率が高く、全オン抵抗の90%以上を占めている。

【0034】

図2に示すプレーナ型MOSFETにおいて、JFET抵抗を下げるためには、JFET領域の不純物濃度を高くすれば良いが、不純物濃度を高くしすぎると、空乏層が伸び難くなって、JFET領域でアバランシェ降伏が発生し、耐圧が低下してしまうという不都合がある。このため、JFET抵抗を低減することには限界があった。

【0035】

これに対して、図1に示す第1の実施の形態に係る半導体装置では、ドレイン層10からの電流は電流導通層14を介して流れるため、図2に示す半導体装置におけるエピ抵抗R(epi)とJFET抵抗R(JFET)の抵抗成分の影響を受けなくなる。

【0036】

一方、第1の実施の形態に係る半導体装置は、ゲート電極22に近い部分に形成される蓄積層に生じるアキュムレーション抵抗R(acc) の影響を受けるようになる。

【0037】

即ち、第1の実施の形態に係る半導体装置におけるドレイン電極28とゲート電極22との間のオン抵抗R(on)は、ドレイン層10の抵抗R(n)と、電流導通層14の抵抗R(n)と、アキュムレーション抵抗R(acc)と、チャネル抵抗R(ch)と、ソース層18の抵抗R(n)と、電極の金属抵抗R(metal)との合成抵抗となる。

【0038】

即ち、R(on)=R(n)+R(n)+R(acc)+R(ch)+R(n)+R(metal)となる。

【0039】

このように、第1の実施の形態に係る半導体装置では、エピ抵抗R(epi)とJFET抵抗R(JFET)に代わって、アキュムレーション抵抗R(acc)の影響を受けるようになるが、アキュムレーション抵抗R(acc)の抵抗値は、エピ抵抗R(epi)およびJFET抵抗R(JFET)の抵抗値に比較して極めて小さいため、全体のオン抵抗を低減することができる。

【0040】

また、電流導通層14を設けたことにより、第2ベース層16とドレイン層10との間の耐圧が低下する懸念があるが、これを避けるために、電流導通層14の側面と第2ベース層16の最接近部との距離W1と、第2ベース層16とドレイン層10との垂直方向の距離W2との関係が、W1>W2となるようにしている。

【0041】

これにより、耐圧を確保しつつ、オン抵抗を下げることが可能となる。

【0042】

(変形例)

次に、図3を参照して、第1の実施の形態に係るプレーナ型半導体装置の変形例について説明する。

【0043】

なお、図1に示す半導体装置と同一の構成については同一符号を付して重複した説明は省略する。

【0044】

図3に示す変形例に係る半導体装置と、図1に示す半導体装置との相違点は、電流導通層14に代えて電流導通層14bを設けている点である。

【0045】

この電流導通層14bは、ゲート絶縁膜20の下面から第1ベース層12内に収まる深さに形成されている。

【0046】

また、電流導通層14bの側面と第2ベース層16の最接近部との距離W1と、第2ベース層16とドレイン層10との垂直方向の距離W2との関係が、W1>W2となるようにしている。

【0047】

これにより、図1に示す半導体装置と同様に、耐圧を確保しつつ、オン抵抗を下げることが可能となる。

【0048】

(製造方法)

第1の実施の形態に係る半導体装置の製造方法は、図1、図4および図5に示すように、高抵抗で第1導電型の第1ベース層12を形成する工程と、第1ベース層12の裏面に第1導電型のドレイン層10を形成する工程と、第1ベース層12の表面に第2導電型の第2ベース層16を形成する工程と、第2ベース層16の表面に第1導電型のソース層18を形成する工程と、第1ベース層12内または第1ベース層12を貫通してドレイン層10に向かう電流導通層14を形成する工程と、ソース層18、第2ベース層16および電流導通層14の表面上にゲート絶縁膜20を形成する工程と、ゲート絶縁膜20上にゲート電極22を形成する工程と、ドレイン層10にドレイン電極28を形成する工程と、ソース層18および第2ベース層16にソース電極26を形成する工程とを有する。

【0049】

(電流導通層の形成方法)

次に、図6〜図9を参照して、電流導通層14の形成方法について説明する。

【0050】

図6に示すように、第1ベース層12の裏面にn型不純物をドープされたドレイン層10を形成した後、図7に示すように異方性エッチング等によりトレンチ14aを形成する。

【0051】

なお、図7に示す例では、トレンチ14aは、第1ベース層12を貫通してドレイン層10に達する深さまで形成されているが、これに限らず、図3に示したように、トレンチ14aを第1ベース層12内に収まる深さに形成するようにしても良い。

【0052】

次いで、トレンチ14a内に、シリコン、ポリシリコンまたは金属(例えば、W等)を埋め込む。埋め込みには、例えば化学気相成長 (CVD:Chemical Vapor Deposition) などが適用される。

【0053】

また、電流導通層14がシリコンまたはポリシリコンで形成された場合には、n型不純物をドープする。

【0054】

そして、第1ベース層12の表面に第2導電型の第2ベース層16を形成し、第2ベース層16の表面に第1導電型のソース層18を形成し、ソース層18、第2ベース層16および電流導通層14の表面上にゲート絶縁膜20を形成し、ゲート絶縁膜20上にゲート電極22を形成すると図9に示す状態となる。

【0055】

この後、ドレイン層10にドレイン電極28を形成し、ソース層18および第2ベース層16にソース電極26を形成して、図1に示すような第1の実施の形態に係る半導体装置が作成される。

【0056】

図10は、第1実施形態に係る半導体装置における主要要素のストライプ状平面レイアウトを示す模式図である。

【0057】

また、図11は、図10のI−I線における模式的断面構造図である。図11では、エッチバック工程によって、電流導通層14の上面がエッチングされて、凹部形状に凹んでいる。この凹み形状に合わせて、ゲート絶縁膜20、ゲート電極22、層間絶縁膜24、ソース電極26が順次堆積形成される。

【0058】

[第2の実施の形態]

(素子構造)

図12は、第2実施形態に係る半導体装置における主要要素のストライプ状平面レイアウトを示す模式図である。

【0059】

また、図13は、図12のII−II線における模式的断面構造図である。

【0060】

なお、図1等に示す第1の実施形態に係る半導体装置と同一の構成については同一符号を付して重複した説明は省略する。

【0061】

図12、図13に示す第2の実施形態に係る半導体装置と、第1の実施形態に係る半導体装置との相違点は、ゲート電極22に代えて分割されたゲート電極22a、22bを形成し、電流導通層14の上方においては、ゲート絶縁膜20の上に層間絶縁膜24が形成されている点である。このように分割されたゲート電極22a・22bは、電気的には同電位とされるが、電流導通層14との間の寄生容量が減少するため、相対的にゲート・ドレイン間の寄生容量が低減化され、第1の実施の形態に比べて、高速動作を実現可能である。

【0062】

この構造によっても耐圧を確保しつつ、オン抵抗を下げることが可能である。

【0063】

(平面パターン)

図14には、第1または第2の実施の形態に係るプレーナ型半導体装置の四角形状平面パターン構成の例を示す。これにより、半導体装置が、互いに等間隔に配置される。

【0064】

また、図15には、第1または第2の実施の形態に係るプレーナ型半導体装置の六角状平面パターン構成の例を示す。これにより、半導体装置が、蜂の巣状のパターンとなるように互いに等間隔に配置される。

【0065】

[第3の実施の形態]

(素子構造)

次に、図16〜図18を参照して、第3の実施の形態に係るトレンチ型半導体装置について説明する。

【0066】

ここに、図16は、第3の実施の形態に係るトレンチ型半導体装置であって、図17〜図18において、III−III線に沿う模式的断面構造図、図17は、第3の実施の形態に係るトレンチ型半導体装置の格子状平面パターン構成図、図18は、第3の実施の形態に係るトレンチ型半導体装置のストライプ状平面パターン構成図である。

【0067】

第3の実施の形態に係る半導体装置は、図16に示すように、高抵抗で第1導電型の第1ベース層12と、第1ベース層12の裏面に配置された電流導通層14cと、第1ベース層12の裏面に配置された第1導電型のドレイン層10と、第1ベース層12の表面に配置された第2導電型の第2ベース層16と、第2ベース層16の表面に配置された第1導電型のソース層18と、第1ベース層12の表面に、第2ベース層16の深さよりも浅く配置された第2導電型の第3ベース層16aと、第1ベース層12の表面より、ソース層18、第2ベース層16を貫通して形成されたトレンチと、トレンチの底面および側壁面に配置されたゲート絶縁膜20と、ゲート絶縁膜20上に配置され、トレンチを充填するゲート電極22と、ゲート電極22を被覆して配置された層間絶縁膜5と、ドレイン層10に形成されたドレイン電極28と、ソース層18、第2ベース層16に形成されたソース電極6とを備える。ここで、電流導通層14cの上面と第3ベース層16aの下面との距離W3と、ドレイン層10の上面と第2ベース層16の下面との距離W4との関係が、W3>W4である。

【0068】

n型不純物としては、例えば、P、As、Sbなどを適用することができ、p型不純物は、例えば、B、Al、Gaなどを適用することができる。これらの不純物は、拡散技術若しくはイオン注入技術を用いて各層にドーピングすることができる。

【0069】

ゲート絶縁膜20としては、例えば、シリコン酸化膜、シリコン窒化膜、シリコン酸窒化膜、ハフニウム酸化膜、アルミナ膜、タンタル酸化膜などを適用することができる。

【0070】

ゲート電極22としては、例えば、ポリシリコンを適用することができ、ドレイン電極28とソース電極26には、例えば、アルミニウムを適用することができる。

【0071】

層間絶縁膜24としては、例えば、シリコン酸化膜、シリコン窒化膜、TEOS(テトラエトキシシラン)膜などを適用することができる。

【0072】

また、電流導通層14cとしては、n型不純物をドープされたシリコン、n型不純物をドープされたポリシリコンまたは金属(例えば、W等)の何れかで形成することができる。

【0073】

また、層間絶縁膜5は、LOCOS酸化膜により形成することができる。

【0074】

このような構成の第3の実施の形態に係る半導体装置によっても、耐圧を確保しつつ、オン抵抗を下げることが可能である。

【0075】

なお、図17に示すように、第3の実施の形態に係る半導体装置は、格子状に形成されていても良い。

【0076】

また、図18に示すように、第3の実施の形態に係る半導体装置は、ストライプ状に形成されていても良い。

【0077】

(製造方法)

第3の実施の形態に係る半導体装置の製造方法は、図16に示すように、高抵抗で第1導電型の第1ベース層12を形成する工程と、第1ベース層12の裏面に電流導通層14cを形成する工程と、第1ベース層12の裏面に第1導電型のドレイン層10を形成する工程と、第1ベース層12の表面に第2導電型の第2ベース層16を形成する工程と、第2ベース層16の表面に第1導電型のソース層18を形成する工程と、第1ベース層12の表面に、第2ベース層16の深さよりも浅く第2導電型の第3ベース層16aを形成する工程と、第1ベース層12の表面より、ソース層18、第2ベース層16を貫通してトレンチを形成する工程と、トレンチの底面および側壁面にゲート絶縁膜20を形成する工程と、ゲート絶縁膜20上に、トレンチを充填するゲート電極22を形成する工程と、ゲート電極22を被覆して層間絶縁膜5を形成する工程と、ドレイン層10にドレイン電極28を形成する工程と、ソース層18、第2ベース層16にソース電極6を形成する工程とを有する。

【0078】

なお、層間絶縁膜5は、LOCOS酸化膜により形成されるようにできる。

【0079】

(半導体装置の応用例)

本実施の形態に係る半導体装置を用いて構成した3相インバータの模式的回路構成は、図19に示すように、ゲートドライブ部50と、ゲートドライブ部50に接続されたパワーモジュール部52と、3相モータ部54とを備える。パワーモジュール部52は、3相モータ部54のU相、V相、W相に対応して、U、V、W相のインバータが接続されている。

【0080】

パワーモジュール部52は、コンデンサCが接続されたプラス端子(+)とマイナス端子(−)間に、インバータ構成のSiC・MOSFETQ1・Q2、Q3・Q4、およびQ5・Q6が接続されている。さらに、SiC・MOSFETQ1〜Q6のソース・ドレイン間には、ダイオードD1〜D6がそれぞれ逆並列に接続されている。

【0081】

[その他の実施の形態]

上記のように、実施の形態によって記載したが、この開示の一部をなす論述および図面は例示的なものであり、この発明を限定するものであると理解すべきではない。この開示から当業者には様々な代替実施の形態、実施例および運用技術が明らかとなろう。

【0082】

このように、本発明はここでは記載していない様々な実施の形態などを含む。

【0083】

例えば、本発明に係る半導体装置は、Siデバイスに限らずSiCデバイスにも適用することができ、耐圧を確保しつつ、オン抵抗を下げることができる。

【産業上の利用可能性】

【0084】

本発明の半導体装置は、高耐圧MOSFETを使用するブリッジ回路、LCDインバータ、モータ、自動車用HID(High Intensity Discharge lamp)ヘッドライト点灯装置などに適用可能である。

【符号の説明】

【0085】

5…層間絶縁膜

10…ドレイン層

12…第1ベース層

14、14b、14c…電流導通層

14a…トレンチ

16…第2ベース層

16a…第3ベース層

18…ソース層

20…ゲート絶縁膜

22、22a、22b…ゲート電極

24…層間絶縁膜

26…ソース電極

28…ドレイン電極

50…ゲートドライブ部

52…パワーモジュール部

54…三相モータ部

【技術分野】

【0001】

本発明は、半導体装置およびその製造方法に係り、特に耐圧を確保しつつ、オン抵抗を下げることのできる半導体装置およびその製造方法に関する。

【背景技術】

【0002】

近年、電子機器の低消費電力化、信頼性の向上等の観点から、半導体装置についてオン抵抗の低減が要望されている。

【0003】

例えば、ノート型パソコンや携帯電話等の携帯型通信機器の電源回路のスイッチング素子として用いられる半導体装置の一例としてのMOSFET(Metal Oxide Silicon Field Efect Transistor)は、内蔵電池によりできるだけ長時間にわたって駆動させるために、オン抵抗の低抵抗化が望まれている。例えば、オン抵抗の低減と過電流の低減とは、トレードオフの関係になっており、スイッチング素子としての高性能化には、オン抵抗の低減が必須であった。

【0004】

このような要望からオン抵抗を低減させる技術は種々提案されている(例えば、特許文献1参照。)。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2008−60152号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

ところで、プレーナ型MOSFETでは、高抵抗で比較的厚いエピタキシャル層のエピ抵抗と、プレーナ型構造に特有のJFET抵抗が、全オン抵抗の90%以上を占めている。

【0007】

ここで、エピ抵抗とは、エピタキシャル層を電子が流れるときの抵抗を言う。

【0008】

また、JFET抵抗は、接合型電界効果トランジスタ(JFET:Junction Field Effect Transistor) 抵抗の略であり、プレーナ型では隣接するセル間に寄生的にJFETが形成されて抵抗成分となる。

【0009】

JFET抵抗を下げるためには、JFET領域の不純物濃度を高くすれば良く、通常、ドリフト層(伝導層)よりも高い不純物濃度としている。

【0010】

しかしながら、不純物濃度を高くすると、空乏層が伸び難くなり、ドリフト層ではなく、JFET領域でアバランシェ降伏が起きて、耐圧が低下してしまう。このため、JFET抵抗を低減することにも限界があった。

【0011】

本発明の目的は、耐圧を確保しつつ、オン抵抗を下げることのできる半導体装置およびその製造方法を提供することにある。

【課題を解決するための手段】

【0012】

上記目的を達成するための本発明の一態様によれば、高抵抗で第1導電型の第1ベース層と、前記第1ベース層の裏面に設けられた第1導電型のドレイン層と、前記第1ベース層の表面に形成された第2導電型の第2ベース層と、前記第2ベース層の表面に形成された第1導電型のソース層と、前記ソース層および前記第2ベース層の表面上に配置されたゲート絶縁膜と、前記ゲート絶縁膜上に配置されたゲート電極と、前記ゲート絶縁膜の下面から前記ドレイン層に向かって延設された第1導電型の電流導通層と、前記ドレイン層に設けられたドレイン電極と、前記ソース層および前記第2ベース層に設けられたソース電極とを備え、前記電流導通層の側面と前記第2ベース層の最接近部との距離W1と、前記第2ベース層と前記ドレイン層との垂直方向の距離W2との関係が、W1>W2である半導体装置が提供される。

【0013】

本発明の他の態様によれば、高抵抗で第1導電型の第1ベース層と、前記第1ベース層の裏面に配置された電流導通層と、前記第1ベース層の裏面に配置された第1導電型のドレイン層と、前記第1ベース層の表面に配置された第2導電型の第2ベース層と、前記第2ベース層の表面に配置された第1導電型のソース層と、前記第1ベース層の表面に、前記第2ベース層の深さよりも浅く配置された第2導電型の第3ベース層と、前記第1ベース層の表面より、前記ソース層、前記第2ベース層を貫通して形成されたトレンチと、前記トレンチの底面および側壁面に配置されたゲート絶縁膜と、前記ゲート絶縁膜上に配置され、前記トレンチを充填するゲート電極と、前記ゲート電極を被覆して配置された層間絶縁膜と、前記ドレイン層に形成されたドレイン電極と、前記ソース層、前記第2ベース層に形成されたソース電極とを備え、前記電流導通層の上面と前記第3ベース層の下面との距離W1と、前記ドレイン層の上面と前記第2ベース層の下面との距離W2との関係が、W1>W2である半導体装置が提供される。

【0014】

本発明の他の態様によれば、高抵抗で第1導電型の第1ベース層を形成する工程と、前記第1ベース層の裏面に第1導電型のドレイン層を形成する工程と、前記第1ベース層の表面に第2導電型の第2ベース層を形成する工程と、前記第2ベース層の表面に第1導電型のソース層を形成する工程と、前記第1ベース層内または前記第1ベース層を貫通して前記ドレイン層に向かう電流導通層を形成する工程と、前記ソース層、前記第2ベース層および前記電流導通層の表面上にゲート絶縁膜を形成する工程と、前記ゲート絶縁膜上にゲート電極を形成する工程と、前記ドレイン層にドレイン電極を形成する工程と、前記ソース層および前記第2ベース層にソース電極を形成する工程とを有する半導体装置の製造方法が提供される。

【0015】

本発明の他の態様によれば、高抵抗で第1導電型の第1ベース層を形成する工程と、

前記第1ベース層の裏面に電流導通層を形成する工程と、前記第1ベース層の裏面に第1導電型のドレイン層を形成する工程と、前記第1ベース層の表面に第2導電型の第2ベース層を形成する工程と、前記第2ベース層の表面に第1導電型のソース層を形成する工程と、前記第1ベース層の表面に、前記第2ベース層の深さよりも浅く第2導電型の第3ベース層を形成する工程と、前記第1ベース層の表面より、前記ソース層、前記第2ベース層を貫通してトレンチを形成する工程と、前記トレンチの底面および側壁面にゲート絶縁膜を形成する工程と、前記ゲート絶縁膜上に、前記トレンチを充填するゲート電極を形成する工程と、前記ゲート電極を被覆して層間絶縁膜を形成する工程と、前記ドレイン層にドレイン電極を形成する工程と、前記ソース層、前記第2ベース層にソース電極を形成する工程とを有する半導体装置の製造方法が提供される。

【発明の効果】

【0016】

本発明によれば、耐圧を確保しつつ、オン抵抗を下げることのできる半導体装置およびその製造方法を提供することができる。

【図面の簡単な説明】

【0017】

【図1】第1の実施の形態に係る半導体装置の模式的断面構造図。

【図2】第1の実施の形態に係る半導体装置の抵抗値の概念を示す模式的断面構造図。

【図3】第1の実施の形態に係る半導体装置の変形例を示す模式的断面構造図。

【図4】第1の実施の形態に係る半導体装置を並設した状態を示す模式的断面構造図。

【図5】第1の実施の形態に係る半導体装置の模式的鳥瞰図。

【図6】第1の実施の形態に係る半導体装置の製造方法の一工程を説明する模式的断面構造図。

【図7】第1の実施の形態に係る半導体装置の製造方法の一工程を説明する模式的断面構造図。

【図8】第1の実施の形態に係る半導体装置の製造方法の一工程を説明する模式的断面構造図。

【図9】第1の実施の形態に係る半導体装置の製造方法の一工程を説明する模式的断面構造図。

【図10】第1の実施形態に係る半導体装置における主要要素のストライプ状平面レイアウトを示す模式図。

【図11】図10のI−I線における模式的断面構造図。

【図12】第2の実施形態に係る半導体装置における主要要素のストライプ状平面レイアウトを示す模式図。

【図13】図12のII−II線における模式的断面構造図。

【図14】第1または第2の実施形態に係る半導体装置の四角形状平面パターン構成図。

【図15】第1または第2の実施形態に係る半導体装置の六角状平面パターン構成図。

【図16】第3の実施の形態に係る半導体装置であって、図17〜図18において、III−III線に沿う模式的断面構造図。

【図17】第3の実施の形態に係る半導体装置の格子状平面パターン構成図。

【図18】第3の実施の形態に係る半導体装置のストライプ状平面パターン構成図。

【図19】実施の形態に係る半導体装置を用いて構成した3相インバータの模式的回路構成図。

【発明を実施するための形態】

【0018】

次に、図面を参照して、本発明の実施の形態を説明する。以下において、同じブロックまたは要素には同じ符号を付して説明の重複を避け、説明を簡略にする。図面は模式的なものであり、現実のものとは異なることに留意すべきである。また、図面相互間においても互いの寸法の関係や比率が異なる部分が含まれていることはもちろんである。

【0019】

以下に示す実施の形態は、この発明の技術的思想を具体化するための装置や方法を例示するものであって、この発明の実施の形態は、各構成部品の配置などを下記のものに特定するものでない。この発明の実施の形態は、特許請求の範囲において、種々の変更を加えることができる。

【0020】

[第1の実施の形態]

(素子構造)

本発明の第1の実施の形態に係る半導体装置の模式的断面構造は、図1に示すように表される。また、第1の実施の形態に係る半導体装置を並設した状態を示す模式的断面構造図は図4に示すように表される。また、第1の実施の形態に係る半導体装置の模式的鳥瞰図は図5に示すように表される。

【0021】

第1の実施の形態に係る半導体装置は、図1、図4および図5に示すように、高抵抗でn型不純物をドープされた第1ベース層12と、第1ベース層12の裏面に設けられ、n型不純物をドープされたドレイン層10と、第1ベース層12の表面に形成され、p型不純物をドープされた第2ベース層16と、第2ベース層16の表面に形成され、n型不純物をドープされたソース層18と、ソース層18および第2ベース層16の表面上に配置されたゲート絶縁膜20と、ゲート絶縁膜20上に配置されたゲート電極22と、ゲート絶縁膜20の下面からドレイン層10に向かって延設され、n型不純物をドープされた電流導通層14と、ドレイン層10に設けられたドレイン電極28と、ソース層18および第2ベース層16に設けられたソース電極26とを備える。

【0022】

図1に示す半導体装置では、電流導通層14は、ゲート絶縁膜20の下面から第1ベース層12を貫通してドレイン層10まで達する深さに形成されている。

【0023】

そして、電流導通層14の側面と第2ベース層16の最接近部との距離W1と、第2ベース層16とドレイン層10との垂直方向の距離W2との関係が、W1>W2となるように構成されている。

【0024】

n型不純物としては、例えば、P、As、Sbなどを適用することができ、p型不純物は、例えば、B、Al、Gaなどを適用することができる。これらの不純物は、拡散技術若しくはイオン注入技術を用いて各層にドーピングすることができる。

【0025】

ゲート絶縁膜20としては、例えば、シリコン酸化膜、シリコン窒化膜、シリコン酸窒化膜、ハフニウム酸化膜、アルミナ膜、タンタル酸化膜などを適用することができる。

【0026】

ゲート電極22としては、例えば、ポリシリコンを適用することができ、ドレイン電極28とソース電極26には、例えば、アルミニウムを適用することができる。

【0027】

層間絶縁膜24としては、例えば、シリコン酸化膜、シリコン窒化膜、TEOS(テトラエトキシシラン)膜などを適用することができる。

【0028】

また、電流導通層14としては、n型不純物をドープされたシリコン、n型不純物をドープされたポリシリコンまたは金属(例えば、W等)の何れかで形成することができる。

【0029】

ここで、本実施の形態に係る半導体装置のオン抵抗について述べる前に、図2を参照して、比較対象としての半導体装置のオン抵抗について簡単に説明する。

【0030】

図2に示す半導体装置は、一般的な構造のプレーナ型MOSFETである。

【0031】

このプレーナ型MOSFETにおいて、ドレイン電極28とゲート電極22との間のオン抵抗R(on)は、ドレイン層10の抵抗R(n)と、エピ抵抗R(epi)と、JFET抵抗R(JFET)と、チャネル抵抗R(ch)と、ソース層18の抵抗R(n)と、電極の金属抵抗R(metal)との合成抵抗となる。

【0032】

即ち、R(on)=R(n)+R(epi)+R(JFET)+R(ch)+R(n)+R(metal)となる。

【0033】

これらの抵抗のうち、エピ抵抗R(epi)とJFET抵抗R(JFET)の比率が高く、全オン抵抗の90%以上を占めている。

【0034】

図2に示すプレーナ型MOSFETにおいて、JFET抵抗を下げるためには、JFET領域の不純物濃度を高くすれば良いが、不純物濃度を高くしすぎると、空乏層が伸び難くなって、JFET領域でアバランシェ降伏が発生し、耐圧が低下してしまうという不都合がある。このため、JFET抵抗を低減することには限界があった。

【0035】

これに対して、図1に示す第1の実施の形態に係る半導体装置では、ドレイン層10からの電流は電流導通層14を介して流れるため、図2に示す半導体装置におけるエピ抵抗R(epi)とJFET抵抗R(JFET)の抵抗成分の影響を受けなくなる。

【0036】

一方、第1の実施の形態に係る半導体装置は、ゲート電極22に近い部分に形成される蓄積層に生じるアキュムレーション抵抗R(acc) の影響を受けるようになる。

【0037】

即ち、第1の実施の形態に係る半導体装置におけるドレイン電極28とゲート電極22との間のオン抵抗R(on)は、ドレイン層10の抵抗R(n)と、電流導通層14の抵抗R(n)と、アキュムレーション抵抗R(acc)と、チャネル抵抗R(ch)と、ソース層18の抵抗R(n)と、電極の金属抵抗R(metal)との合成抵抗となる。

【0038】

即ち、R(on)=R(n)+R(n)+R(acc)+R(ch)+R(n)+R(metal)となる。

【0039】

このように、第1の実施の形態に係る半導体装置では、エピ抵抗R(epi)とJFET抵抗R(JFET)に代わって、アキュムレーション抵抗R(acc)の影響を受けるようになるが、アキュムレーション抵抗R(acc)の抵抗値は、エピ抵抗R(epi)およびJFET抵抗R(JFET)の抵抗値に比較して極めて小さいため、全体のオン抵抗を低減することができる。

【0040】

また、電流導通層14を設けたことにより、第2ベース層16とドレイン層10との間の耐圧が低下する懸念があるが、これを避けるために、電流導通層14の側面と第2ベース層16の最接近部との距離W1と、第2ベース層16とドレイン層10との垂直方向の距離W2との関係が、W1>W2となるようにしている。

【0041】

これにより、耐圧を確保しつつ、オン抵抗を下げることが可能となる。

【0042】

(変形例)

次に、図3を参照して、第1の実施の形態に係るプレーナ型半導体装置の変形例について説明する。

【0043】

なお、図1に示す半導体装置と同一の構成については同一符号を付して重複した説明は省略する。

【0044】

図3に示す変形例に係る半導体装置と、図1に示す半導体装置との相違点は、電流導通層14に代えて電流導通層14bを設けている点である。

【0045】

この電流導通層14bは、ゲート絶縁膜20の下面から第1ベース層12内に収まる深さに形成されている。

【0046】

また、電流導通層14bの側面と第2ベース層16の最接近部との距離W1と、第2ベース層16とドレイン層10との垂直方向の距離W2との関係が、W1>W2となるようにしている。

【0047】

これにより、図1に示す半導体装置と同様に、耐圧を確保しつつ、オン抵抗を下げることが可能となる。

【0048】

(製造方法)

第1の実施の形態に係る半導体装置の製造方法は、図1、図4および図5に示すように、高抵抗で第1導電型の第1ベース層12を形成する工程と、第1ベース層12の裏面に第1導電型のドレイン層10を形成する工程と、第1ベース層12の表面に第2導電型の第2ベース層16を形成する工程と、第2ベース層16の表面に第1導電型のソース層18を形成する工程と、第1ベース層12内または第1ベース層12を貫通してドレイン層10に向かう電流導通層14を形成する工程と、ソース層18、第2ベース層16および電流導通層14の表面上にゲート絶縁膜20を形成する工程と、ゲート絶縁膜20上にゲート電極22を形成する工程と、ドレイン層10にドレイン電極28を形成する工程と、ソース層18および第2ベース層16にソース電極26を形成する工程とを有する。

【0049】

(電流導通層の形成方法)

次に、図6〜図9を参照して、電流導通層14の形成方法について説明する。

【0050】

図6に示すように、第1ベース層12の裏面にn型不純物をドープされたドレイン層10を形成した後、図7に示すように異方性エッチング等によりトレンチ14aを形成する。

【0051】

なお、図7に示す例では、トレンチ14aは、第1ベース層12を貫通してドレイン層10に達する深さまで形成されているが、これに限らず、図3に示したように、トレンチ14aを第1ベース層12内に収まる深さに形成するようにしても良い。

【0052】

次いで、トレンチ14a内に、シリコン、ポリシリコンまたは金属(例えば、W等)を埋め込む。埋め込みには、例えば化学気相成長 (CVD:Chemical Vapor Deposition) などが適用される。

【0053】

また、電流導通層14がシリコンまたはポリシリコンで形成された場合には、n型不純物をドープする。

【0054】

そして、第1ベース層12の表面に第2導電型の第2ベース層16を形成し、第2ベース層16の表面に第1導電型のソース層18を形成し、ソース層18、第2ベース層16および電流導通層14の表面上にゲート絶縁膜20を形成し、ゲート絶縁膜20上にゲート電極22を形成すると図9に示す状態となる。

【0055】

この後、ドレイン層10にドレイン電極28を形成し、ソース層18および第2ベース層16にソース電極26を形成して、図1に示すような第1の実施の形態に係る半導体装置が作成される。

【0056】

図10は、第1実施形態に係る半導体装置における主要要素のストライプ状平面レイアウトを示す模式図である。

【0057】

また、図11は、図10のI−I線における模式的断面構造図である。図11では、エッチバック工程によって、電流導通層14の上面がエッチングされて、凹部形状に凹んでいる。この凹み形状に合わせて、ゲート絶縁膜20、ゲート電極22、層間絶縁膜24、ソース電極26が順次堆積形成される。

【0058】

[第2の実施の形態]

(素子構造)

図12は、第2実施形態に係る半導体装置における主要要素のストライプ状平面レイアウトを示す模式図である。

【0059】

また、図13は、図12のII−II線における模式的断面構造図である。

【0060】

なお、図1等に示す第1の実施形態に係る半導体装置と同一の構成については同一符号を付して重複した説明は省略する。

【0061】

図12、図13に示す第2の実施形態に係る半導体装置と、第1の実施形態に係る半導体装置との相違点は、ゲート電極22に代えて分割されたゲート電極22a、22bを形成し、電流導通層14の上方においては、ゲート絶縁膜20の上に層間絶縁膜24が形成されている点である。このように分割されたゲート電極22a・22bは、電気的には同電位とされるが、電流導通層14との間の寄生容量が減少するため、相対的にゲート・ドレイン間の寄生容量が低減化され、第1の実施の形態に比べて、高速動作を実現可能である。

【0062】

この構造によっても耐圧を確保しつつ、オン抵抗を下げることが可能である。

【0063】

(平面パターン)

図14には、第1または第2の実施の形態に係るプレーナ型半導体装置の四角形状平面パターン構成の例を示す。これにより、半導体装置が、互いに等間隔に配置される。

【0064】

また、図15には、第1または第2の実施の形態に係るプレーナ型半導体装置の六角状平面パターン構成の例を示す。これにより、半導体装置が、蜂の巣状のパターンとなるように互いに等間隔に配置される。

【0065】

[第3の実施の形態]

(素子構造)

次に、図16〜図18を参照して、第3の実施の形態に係るトレンチ型半導体装置について説明する。

【0066】

ここに、図16は、第3の実施の形態に係るトレンチ型半導体装置であって、図17〜図18において、III−III線に沿う模式的断面構造図、図17は、第3の実施の形態に係るトレンチ型半導体装置の格子状平面パターン構成図、図18は、第3の実施の形態に係るトレンチ型半導体装置のストライプ状平面パターン構成図である。

【0067】

第3の実施の形態に係る半導体装置は、図16に示すように、高抵抗で第1導電型の第1ベース層12と、第1ベース層12の裏面に配置された電流導通層14cと、第1ベース層12の裏面に配置された第1導電型のドレイン層10と、第1ベース層12の表面に配置された第2導電型の第2ベース層16と、第2ベース層16の表面に配置された第1導電型のソース層18と、第1ベース層12の表面に、第2ベース層16の深さよりも浅く配置された第2導電型の第3ベース層16aと、第1ベース層12の表面より、ソース層18、第2ベース層16を貫通して形成されたトレンチと、トレンチの底面および側壁面に配置されたゲート絶縁膜20と、ゲート絶縁膜20上に配置され、トレンチを充填するゲート電極22と、ゲート電極22を被覆して配置された層間絶縁膜5と、ドレイン層10に形成されたドレイン電極28と、ソース層18、第2ベース層16に形成されたソース電極6とを備える。ここで、電流導通層14cの上面と第3ベース層16aの下面との距離W3と、ドレイン層10の上面と第2ベース層16の下面との距離W4との関係が、W3>W4である。

【0068】

n型不純物としては、例えば、P、As、Sbなどを適用することができ、p型不純物は、例えば、B、Al、Gaなどを適用することができる。これらの不純物は、拡散技術若しくはイオン注入技術を用いて各層にドーピングすることができる。

【0069】

ゲート絶縁膜20としては、例えば、シリコン酸化膜、シリコン窒化膜、シリコン酸窒化膜、ハフニウム酸化膜、アルミナ膜、タンタル酸化膜などを適用することができる。

【0070】

ゲート電極22としては、例えば、ポリシリコンを適用することができ、ドレイン電極28とソース電極26には、例えば、アルミニウムを適用することができる。

【0071】

層間絶縁膜24としては、例えば、シリコン酸化膜、シリコン窒化膜、TEOS(テトラエトキシシラン)膜などを適用することができる。

【0072】

また、電流導通層14cとしては、n型不純物をドープされたシリコン、n型不純物をドープされたポリシリコンまたは金属(例えば、W等)の何れかで形成することができる。

【0073】

また、層間絶縁膜5は、LOCOS酸化膜により形成することができる。

【0074】

このような構成の第3の実施の形態に係る半導体装置によっても、耐圧を確保しつつ、オン抵抗を下げることが可能である。

【0075】

なお、図17に示すように、第3の実施の形態に係る半導体装置は、格子状に形成されていても良い。

【0076】

また、図18に示すように、第3の実施の形態に係る半導体装置は、ストライプ状に形成されていても良い。

【0077】

(製造方法)

第3の実施の形態に係る半導体装置の製造方法は、図16に示すように、高抵抗で第1導電型の第1ベース層12を形成する工程と、第1ベース層12の裏面に電流導通層14cを形成する工程と、第1ベース層12の裏面に第1導電型のドレイン層10を形成する工程と、第1ベース層12の表面に第2導電型の第2ベース層16を形成する工程と、第2ベース層16の表面に第1導電型のソース層18を形成する工程と、第1ベース層12の表面に、第2ベース層16の深さよりも浅く第2導電型の第3ベース層16aを形成する工程と、第1ベース層12の表面より、ソース層18、第2ベース層16を貫通してトレンチを形成する工程と、トレンチの底面および側壁面にゲート絶縁膜20を形成する工程と、ゲート絶縁膜20上に、トレンチを充填するゲート電極22を形成する工程と、ゲート電極22を被覆して層間絶縁膜5を形成する工程と、ドレイン層10にドレイン電極28を形成する工程と、ソース層18、第2ベース層16にソース電極6を形成する工程とを有する。

【0078】

なお、層間絶縁膜5は、LOCOS酸化膜により形成されるようにできる。

【0079】

(半導体装置の応用例)

本実施の形態に係る半導体装置を用いて構成した3相インバータの模式的回路構成は、図19に示すように、ゲートドライブ部50と、ゲートドライブ部50に接続されたパワーモジュール部52と、3相モータ部54とを備える。パワーモジュール部52は、3相モータ部54のU相、V相、W相に対応して、U、V、W相のインバータが接続されている。

【0080】

パワーモジュール部52は、コンデンサCが接続されたプラス端子(+)とマイナス端子(−)間に、インバータ構成のSiC・MOSFETQ1・Q2、Q3・Q4、およびQ5・Q6が接続されている。さらに、SiC・MOSFETQ1〜Q6のソース・ドレイン間には、ダイオードD1〜D6がそれぞれ逆並列に接続されている。

【0081】

[その他の実施の形態]

上記のように、実施の形態によって記載したが、この開示の一部をなす論述および図面は例示的なものであり、この発明を限定するものであると理解すべきではない。この開示から当業者には様々な代替実施の形態、実施例および運用技術が明らかとなろう。

【0082】

このように、本発明はここでは記載していない様々な実施の形態などを含む。

【0083】

例えば、本発明に係る半導体装置は、Siデバイスに限らずSiCデバイスにも適用することができ、耐圧を確保しつつ、オン抵抗を下げることができる。

【産業上の利用可能性】

【0084】

本発明の半導体装置は、高耐圧MOSFETを使用するブリッジ回路、LCDインバータ、モータ、自動車用HID(High Intensity Discharge lamp)ヘッドライト点灯装置などに適用可能である。

【符号の説明】

【0085】

5…層間絶縁膜

10…ドレイン層

12…第1ベース層

14、14b、14c…電流導通層

14a…トレンチ

16…第2ベース層

16a…第3ベース層

18…ソース層

20…ゲート絶縁膜

22、22a、22b…ゲート電極

24…層間絶縁膜

26…ソース電極

28…ドレイン電極

50…ゲートドライブ部

52…パワーモジュール部

54…三相モータ部

【特許請求の範囲】

【請求項1】

高抵抗で第1導電型の第1ベース層と、

前記第1ベース層の裏面に配置された第1導電型のドレイン層と、

前記第1ベース層の表面に配置された第2導電型の第2ベース層と、

前記第2ベース層の表面に配置された第1導電型のソース層と、

前記ソース層および前記第2ベース層の表面上に配置されたゲート絶縁膜と、

前記ゲート絶縁膜上に配置されたゲート電極と、

前記ゲート絶縁膜の下面から前記ドレイン層に向かって延伸して配置された第1導電型の電流導通層と、

前記ドレイン層に配置されたドレイン電極と、

前記ソース層および前記第2ベース層に配置されたソース電極と

を備え、前記電流導通層の側面と前記第2ベース層の最接近部との距離W1と、前記第2ベース層と前記ドレイン層との垂直方向の距離W2との関係が、W1>W2であることを特徴とする半導体装置。

【請求項2】

前記電流導通層は、前記ゲート絶縁膜の下面から前記第1ベース層を貫通して前記ドレイン層まで達する深さに配置されたことを特徴とする請求項1に記載の半導体装置。

【請求項3】

前記電流導通層は、前記ゲート絶縁膜の下面から前記第1ベース層内に収まる深さに配置されたことを特徴とする請求項1に記載の半導体装置。

【請求項4】

前記電流導通層は、第1導電型のシリコン、第1導電型のポリシリコンまたは金属の何れかであることを特徴とする請求項1〜3の何れか1項に記載の半導体装置。

【請求項5】

前記ゲート絶縁膜は酸化シリコン、前記ゲート電極はポリシリコンで形成されることを特徴とする請求項1〜4の何れか1項に記載の半導体装置。

【請求項6】

前記距離W1は、40μm以上50μm以下であることを特徴とする請求項1〜5の何れか1項に記載の半導体装置。

【請求項7】

高抵抗で第1導電型の第1ベース層と、

前記第1ベース層の裏面に配置された電流導通層と、

前記第1ベース層の裏面に配置された第1導電型のドレイン層と、

前記第1ベース層の表面に配置された第2導電型の第2ベース層と、

前記第2ベース層の表面に配置された第1導電型のソース層と、

前記第1ベース層の表面に、前記第2ベース層の深さよりも浅く配置された第2導電型の第3ベース層と、

前記第1ベース層の表面より、前記ソース層、前記第2ベース層を貫通して形成されたトレンチと、

前記トレンチの底面および側壁面に配置されたゲート絶縁膜と、

前記ゲート絶縁膜上に配置され、前記トレンチを充填するゲート電極と、

前記ゲート電極を被覆して配置された層間絶縁膜と、

前記ドレイン層に配置されたドレイン電極と、

前記ソース層、前記第2ベース層に配置されたソース電極と

を備え、前記電流導通層の上面と前記第3ベース層の下面との距離W1と、前記ドレイン層の上面と前記第2ベース層の下面との距離W2との関係が、W1>W2であることを特徴とする半導体装置。

【請求項8】

前記層間絶縁膜は、LOCOS酸化膜により形成されたことを特徴とする請求項7記載の半導体装置。

【請求項9】

高抵抗で第1導電型の第1ベース層を形成する工程と、

前記第1ベース層の裏面に第1導電型のドレイン層を形成する工程と、

前記第1ベース層の表面に第2導電型の第2ベース層を形成する工程と、

前記第2ベース層の表面に第1導電型のソース層を形成する工程と、

前記第1ベース層内または前記第1ベース層を貫通して前記ドレイン層に向かう電流導通層を形成する工程と、

前記ソース層、前記第2ベース層および前記電流導通層の表面上にゲート絶縁膜を形成する工程と、

前記ゲート絶縁膜上にゲート電極を形成する工程と、

前記ドレイン層にドレイン電極を形成する工程と、

前記ソース層および前記第2ベース層にソース電極を形成する工程と

を有することを特徴とする半導体装置の製造方法。

【請求項10】

前記電流導通層を形成する工程は、

前記第1ベース層内または前記第1ベース層を貫通して前記ドレイン層まで達するトレンチを形成する工程と、

前記トレンチに第1導電型のシリコン、第1導電型のポリシリコンまたは金属の何れかを充填する工程と

を有することを特徴とする請求項9に記載の半導体装置の製造方法。

【請求項11】

高抵抗で第1導電型の第1ベース層を形成する工程と、

前記第1ベース層の裏面に電流導通層を形成する工程と、

前記第1ベース層の裏面に第1導電型のドレイン層を形成する工程と、

前記第1ベース層の表面に第2導電型の第2ベース層を形成する工程と、

前記第2ベース層の表面に第1導電型のソース層を形成する工程と、

前記第1ベース層の表面に、前記第2ベース層の深さよりも浅く第2導電型の第3ベース層を形成する工程と、

前記第1ベース層の表面より、前記ソース層、前記第2ベース層を貫通してトレンチを形成する工程と、

前記トレンチの底面および側壁面にゲート絶縁膜を形成する工程と、

前記ゲート絶縁膜上に、前記トレンチを充填するゲート電極を形成する工程と、

前記ゲート電極を被覆して層間絶縁膜を形成する工程と、

前記ドレイン層にドレイン電極を形成する工程と、

前記ソース層、前記第2ベース層にソース電極を形成する工程と

を有することを特徴とする半導体装置の製造方法。

【請求項12】

前記層間絶縁膜は、LOCOS酸化膜により形成されことを特徴とする請求項11に記載の半導体装置の製造方法。

【請求項1】

高抵抗で第1導電型の第1ベース層と、

前記第1ベース層の裏面に配置された第1導電型のドレイン層と、

前記第1ベース層の表面に配置された第2導電型の第2ベース層と、

前記第2ベース層の表面に配置された第1導電型のソース層と、

前記ソース層および前記第2ベース層の表面上に配置されたゲート絶縁膜と、

前記ゲート絶縁膜上に配置されたゲート電極と、

前記ゲート絶縁膜の下面から前記ドレイン層に向かって延伸して配置された第1導電型の電流導通層と、

前記ドレイン層に配置されたドレイン電極と、

前記ソース層および前記第2ベース層に配置されたソース電極と

を備え、前記電流導通層の側面と前記第2ベース層の最接近部との距離W1と、前記第2ベース層と前記ドレイン層との垂直方向の距離W2との関係が、W1>W2であることを特徴とする半導体装置。

【請求項2】

前記電流導通層は、前記ゲート絶縁膜の下面から前記第1ベース層を貫通して前記ドレイン層まで達する深さに配置されたことを特徴とする請求項1に記載の半導体装置。

【請求項3】

前記電流導通層は、前記ゲート絶縁膜の下面から前記第1ベース層内に収まる深さに配置されたことを特徴とする請求項1に記載の半導体装置。

【請求項4】

前記電流導通層は、第1導電型のシリコン、第1導電型のポリシリコンまたは金属の何れかであることを特徴とする請求項1〜3の何れか1項に記載の半導体装置。

【請求項5】

前記ゲート絶縁膜は酸化シリコン、前記ゲート電極はポリシリコンで形成されることを特徴とする請求項1〜4の何れか1項に記載の半導体装置。

【請求項6】

前記距離W1は、40μm以上50μm以下であることを特徴とする請求項1〜5の何れか1項に記載の半導体装置。

【請求項7】

高抵抗で第1導電型の第1ベース層と、

前記第1ベース層の裏面に配置された電流導通層と、

前記第1ベース層の裏面に配置された第1導電型のドレイン層と、

前記第1ベース層の表面に配置された第2導電型の第2ベース層と、

前記第2ベース層の表面に配置された第1導電型のソース層と、

前記第1ベース層の表面に、前記第2ベース層の深さよりも浅く配置された第2導電型の第3ベース層と、

前記第1ベース層の表面より、前記ソース層、前記第2ベース層を貫通して形成されたトレンチと、

前記トレンチの底面および側壁面に配置されたゲート絶縁膜と、

前記ゲート絶縁膜上に配置され、前記トレンチを充填するゲート電極と、

前記ゲート電極を被覆して配置された層間絶縁膜と、

前記ドレイン層に配置されたドレイン電極と、

前記ソース層、前記第2ベース層に配置されたソース電極と

を備え、前記電流導通層の上面と前記第3ベース層の下面との距離W1と、前記ドレイン層の上面と前記第2ベース層の下面との距離W2との関係が、W1>W2であることを特徴とする半導体装置。

【請求項8】

前記層間絶縁膜は、LOCOS酸化膜により形成されたことを特徴とする請求項7記載の半導体装置。

【請求項9】

高抵抗で第1導電型の第1ベース層を形成する工程と、

前記第1ベース層の裏面に第1導電型のドレイン層を形成する工程と、

前記第1ベース層の表面に第2導電型の第2ベース層を形成する工程と、

前記第2ベース層の表面に第1導電型のソース層を形成する工程と、

前記第1ベース層内または前記第1ベース層を貫通して前記ドレイン層に向かう電流導通層を形成する工程と、

前記ソース層、前記第2ベース層および前記電流導通層の表面上にゲート絶縁膜を形成する工程と、

前記ゲート絶縁膜上にゲート電極を形成する工程と、

前記ドレイン層にドレイン電極を形成する工程と、

前記ソース層および前記第2ベース層にソース電極を形成する工程と

を有することを特徴とする半導体装置の製造方法。

【請求項10】

前記電流導通層を形成する工程は、

前記第1ベース層内または前記第1ベース層を貫通して前記ドレイン層まで達するトレンチを形成する工程と、

前記トレンチに第1導電型のシリコン、第1導電型のポリシリコンまたは金属の何れかを充填する工程と

を有することを特徴とする請求項9に記載の半導体装置の製造方法。

【請求項11】

高抵抗で第1導電型の第1ベース層を形成する工程と、

前記第1ベース層の裏面に電流導通層を形成する工程と、

前記第1ベース層の裏面に第1導電型のドレイン層を形成する工程と、

前記第1ベース層の表面に第2導電型の第2ベース層を形成する工程と、

前記第2ベース層の表面に第1導電型のソース層を形成する工程と、

前記第1ベース層の表面に、前記第2ベース層の深さよりも浅く第2導電型の第3ベース層を形成する工程と、

前記第1ベース層の表面より、前記ソース層、前記第2ベース層を貫通してトレンチを形成する工程と、

前記トレンチの底面および側壁面にゲート絶縁膜を形成する工程と、

前記ゲート絶縁膜上に、前記トレンチを充填するゲート電極を形成する工程と、

前記ゲート電極を被覆して層間絶縁膜を形成する工程と、

前記ドレイン層にドレイン電極を形成する工程と、

前記ソース層、前記第2ベース層にソース電極を形成する工程と

を有することを特徴とする半導体装置の製造方法。

【請求項12】

前記層間絶縁膜は、LOCOS酸化膜により形成されことを特徴とする請求項11に記載の半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【公開番号】特開2013−98198(P2013−98198A)

【公開日】平成25年5月20日(2013.5.20)

【国際特許分類】

【出願番号】特願2011−236772(P2011−236772)

【出願日】平成23年10月28日(2011.10.28)

【出願人】(000116024)ローム株式会社 (3,539)

【公開日】平成25年5月20日(2013.5.20)

【国際特許分類】

【出願日】平成23年10月28日(2011.10.28)

【出願人】(000116024)ローム株式会社 (3,539)

[ Back to top ]