半導体装置およびその製造方法

【課題】 リセス巾およびリセス深さを制御性良く作製できる多段リセス構造とその製造方法を提供する。

【解決手段】 化合物半導体の導電層上に第1のリセスエッチングストッパー層5を設け、リセスエッチングストッパー層5上に第1の半導体層6を設け、さらに第1の半導体層6上に第2のリセスエッチングストッパー層7を設け、第2のリセスエッチングストッパー層7上に第2の半導体層8を設け、第1および第2の半導体層6,8の異方性エッチング液として、クエン酸水溶液と過酸化水素水の混合液からなるエッチング液を用いる。

【解決手段】 化合物半導体の導電層上に第1のリセスエッチングストッパー層5を設け、リセスエッチングストッパー層5上に第1の半導体層6を設け、さらに第1の半導体層6上に第2のリセスエッチングストッパー層7を設け、第2のリセスエッチングストッパー層7上に第2の半導体層8を設け、第1および第2の半導体層6,8の異方性エッチング液として、クエン酸水溶液と過酸化水素水の混合液からなるエッチング液を用いる。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】本発明は、化合物半導体装置及びその製造方法に関し、特に多段リセス構造を有する半導体装置およびその製造方法に関する。

【0002】

【従来の技術】ゲート耐圧の向上,ソース抵抗の低減,短チャネル効果抑制,表面効果の抑制などのため、HJFETでLDD構造を実現しようとしたとき、多段のリセス構造をとる必要があり、従来は、リセスエッチを2回の目合わせで個々に行っていた。また、特開平4−137737号公報にあるように多層マスクを用いて選択的にマスクをサイドエッチすることにより、横方向の制御性を向上させて2段リセス構造を実現していた。

【0003】

【発明が解決しようとする課題】しかしながら、2段リセスを2回の目合わせで行った場合、目合わせずれが問題となり、ゲートとn+領域との距離の制御や短縮が困難であった。また、特開平4−137737号公報にあるように多層マスクを用いて横方向の制御性を向上させたとしても、リセスエッチングの際に横方向にもエッチングが入ってしまい、短ゲート化やリセス巾の制御性に問題があった。

【0004】さらにリセスエッチングの際の深さ方向を考えたとき、1段目のリセス深さや2段目のリセス深さが、時間制御となり、再現性や制御性に問題があり、均一性が悪くなってしまうという問題があった。

【0005】本発明の目的は、リセス巾及びリセス深さを制御性良く作製できる半導体装置およびその製造方法を提供することにある。

【0006】

【課題を解決するための手段】前記目的を達成するため、本発明に係る半導体装置は、半導体多層構造を有する半導体装置であって、半導体多層構造は、化合物半導体の導電層上に第1のリセスエッチングストッパー層を設け、該リセスエッチングストッパー上に第1の半導体層を設け、該第1の半導体層上に第2のリセスエッチングストッパー層を設け、該第2のリセスエッチングストッパー層上に第2の半導体層を設けたものである。

【0007】また前記第1および第2の半導体層として、GaAs,InAs,AlxGa1-xAs(0≦x<1),AlyIn1-yAs(0≦y<1),InP,GaP,およびこれらの化合物から構成される化合物半導体を用いたものである。

【0008】また第1および第2のエッチングストッパー層として、AlAs、あるいはAlxGa1-xAsの組成より高いAl組成のAlzGa1-zAs(0<z≦1),AlyIn1-yAsより高いAl組成のAlwIn1-wAs(0<w≦1)を用いたものである。

【0009】また、(100)基板上に形成された半導体装置であり、半導体多層構造に設けられるゲートは、(011)に平行であり、リセスエッチング面は、(100)面と(111)面により構成されるものである。

【0010】また本発明に係る半導体装置の製造方法は、マスク形成工程と、パターニング工程と、第1の異方性エッチング工程と、第2の異方性エッチング工程とを含む、半導体多層構造を有する半導体装置の製造方法であって、半導体多層構造は、化合物半導体の導電層上に設けた第1のリセスエッチングストッパー層と、前記第1のリセスエッチングストッパー上に設けた第1の半導体層と、前記第1の半導体層上に設けた第2のリセスエッチングストッパー層と、前記第2のリセスエッチングストッパー層上に設けた第2の半導体層を有するものであり、マスク形成工程は、半導体多層構造上にエッチングレートの異なる第1のマスク層と第2のマスク層を設ける処理であり、パターニング工程は、第2のマスク層のパターニングを行い、これを用いて第1のマスク層のパターニングを行う処理であり、第1の異方性エッチング工程は、この第1および第2のマスク層を用いて第1の半導体層を第2のリセスエッチングストッパー層まで異方性エッチングする処理であり、第2の異方性エッチング工程は、開口部分のリセスエッチングストッパー層を除去し、さらに第1のマスク層の開口幅をサイドエッチングにより選択的に広げた後に、第1および第2のリセスエッチングストッパー層まで第2の半導体層および第1の半導体層の異方性エッチングを行う処理である。

【0011】また第1および第2の半導体層を異方性エッチングするエッチング液として、クエン酸水溶液と過酸化水素水の混合液からなるエッチング液を用いるものである。

【0012】

【作用】半導体多層構造上にエッチングレートの異なる第1のマスク層9と第2のマスク層10を設け(図1(b))、第2のマスク層10をパターニングし、そのパターニングされた第2のマスク層10を用いて第1のマスク層9のパターニングを行う。この第1および第2のマスク層9,10を用いて第2の半導体層8を第2のリセスエッチングストッパー層7まで異方性エッチングする。

【0013】第2のリセスエッチングストッパー層7まで異方性エッチングする際に、クエン酸水溶液と過酸化水素水の混合液からなるエッチング液を用いる。クエン酸系エッチング液は、GaAsなどの半導体層とAlAsなどのストッパー層を選択的にエッチングすることが可能であるばかりでなく、(111)B面のエッチング速度が極端に小さく抑えられるため、これを半導体多層構造のエッチングに用いれば、横方向はサイドエッチがほとんど入らず(111)Bで決まり、深さ方向はストッパー層7で決まるエッチングが可能となる。

【0014】上述したエッチング法を用いることにより、1段目の深さおよび開口幅は、第2のマスク層2の寸法とストッパー層7の位置で決まり、エッチング時間にほとんど依存しなくなる。

【0015】さらにゲートを(011)に平行にとることにより、開口形状は(111)B面で律速されるため、2段目の開口は、第2のマスク層9の寸法より細くすることが可能である(図2(e))。

【0016】その後、開口部分のリセスエッチングストッパー層7を除去し、さらに第1のマスク層9の開口巾をサイドエッチングにより選択的に広げた後に、第1および第2のリセスエッチングストッパー層5,7まで第2の半導体層8および第1の半導体層6の異方性エッチングを再度クエン酸系エッチング液で行う(図3(i))。

【0017】この際、第2の半導体層8はストッパー層7の存在により開口部分だけが削れるので、容易に2段リセス形状が作成できる。2段目の開口巾は最初の1段目のリセス巾ですでに決まっており、ゲートを(011)に平行にとることにより1段目のリセスエッチで細くなった開口巾は、2段目のエッチングでさらに細くなる。

【0018】第1の半導体層のキャリア濃度を第2の半導体層のキャリア濃度より小さくしておき、ゲート電極と第1の半導体層を短絡させ、第2の高濃度の半導体層と距離をとることにより、ゲートラグ等の表面の影響を回避しつつ、高いドレイン耐圧を得ることができる。しかもそれが容易に自己整合的に作製できる。横方向の2段目のリセス巾は、最初のマスク開口の巾と第1と第2の半導体層の厚さで決まり、エッチング深さ方向に関してもストッパー層の深さで決まる。1段目のリセス巾は第1のマスク層のサイドエッチ量で制御でき、その深さはストッパー層で決定される。このため、しきい値電圧Vtの制御性,均一性,再現性が向上する。また、ゲートを(011)に平行にとった場合、第1および第2の半導体層の厚さで制御される量だけマスク寸法からの短チャネル化を図れるので、デバイス特性の向上にもつながる。

【0019】

【発明の実施の形態】以下、本発明の実施形態をヘテロ接合形電界効果トランジスタを例にとり、図1〜図3を用いて説明する。

【0020】図1(a)に示すように半絶縁性GaAs基板1上に、たとえばMOCVD法により、基板側からi−GaAsバッファ層2を500nm,チャネル層3としてi−InGaAs層を15nm,n−AlGaAs層4を2×1018cm-3で33nm設け、第1のリセスエッチングストッパー層5としてn−AlAs層を2×1018cm-3で2nm設け、リセスエッチングストッパー層5上に第1の半導体層6として低濃度n−GaAs層を1×1018cm-3で150nm設ける。さらにn−GaAs層6上に第2のリセスエッチングストッパー層7としてn−AlAs層を2×1018cm-3で2nm設け、第2のリセスエッチングストッパー層7上に第2の半導体層8として高濃度n−GaAs層を4×1018cm-3で50nm設けることにより、本発明の半導体多層構造を作製する。

【0021】この化合物半導体多層構造を用いて、本発明の半導体装置の製造方法を説明する。該半導体多層構造上にエッチングレートの異なる第1のマスク層9としてSiO2層を50nm形成し、さらに第2のマスク層10としてフォトレジストを設ける(図1(b))。

【0022】次に第2のマスク層10であるフォトレジストのパターニングを行い(図1(c))、パターニングされた第2のマスク層10を用いて第1のマスク層9のSiO2のパターニングを行う(図1(d))。

【0023】この第1および第2のマスク層9,10を用いて第2の半導体層8のn−GaAs層を第2のリセスエッチングストッパー層7であるAlAsまで異方性エッチングを行なう。そのエッチングは、エッチング液として、クエン酸−水和物を同重量の水に溶かしたクエン酸水溶液と30%過酸化水素水を3:1で混合した混合液からなるエッチング液を用いて行う(図2(e))。

【0024】その後、開口部分のリセスエッチングストッパー層7のAlAs層を除去し、さらに第1のマスク層9であるSiO2の開口巾をバッファード弗酸により横方向にエッチングをして選択的に広げ、第1および第2のリセスエッチングストッパー層5および7のAlAs層まで第2の半導体層8としてのn−GaAs層および第1の半導体層6としてのn−GaAs層6の異方性エッチングを再度クエン酸系エッチング液で行う(図2の(f),(g),(h))。

【0025】さらに、エッチングストッパー層5および7のAlAs層の表面に出た部分を希塩酸で除去した後(図3(i))、第1のマスク層9であるフォトレジストを用いて、ゲート金属としてTi/Pt/Auを蒸着し、リフトオフ法によりゲート電極11の形成を行う(図3(j),(k))。これに通常の寸法でオーミック電極12を作製して半導体装置を完成させる。

【0026】クエン酸系エッチング液は、GaAsとalGaAsの選択エッチングが可能なうえ、低温では、(111)B面のエッチング速度が極端に小さく抑えられる。具体的には、リセスエッチングの1段目の開口巾および深さは、第1のマスク層のサイドエッチ後の開口寸法とストッパー層の位置で決まり、2段目の開口巾および深さは、第1のマスク層のサイドエッチ前の開口寸法とストッパー層の位置で決まる。このため、横方向にはマスクで規定される(111)B面で決まり、サイドエッチのほとんど入らないエッチングが可能となり、深さ方向ではストッパー層でエッチング深さは決定されるので、エッチング時間にほとんど依存せずにデバイスを作製できる。

【0027】開口形状は、横方向には(111)B面で律速されるため、ゲートを(011)に平行にとることにより、リセスエッチングの底の巾は最初のマスク開口巾より膜厚に応じて細くなる。

【0028】本発明の場合、最初のサイドエッチ前の第2のマスク層の開口巾より1段目のリセスエッチで細くなった開口巾は、2段目のエッチングでさらに電子供給層のAlGaAsの開口部分でさらに細くなる。

【0029】これにより、容易に短チャネル化を図れるので、デバイス特性の向上が図られる。本実施形態の場合、第2のマスク層の最初の開口巾が0.5μmのとき、横から0.14μmずつ傾斜した分だけ短ゲート化されるため、0.22μmのゲートが作製される。

【0030】このようにして作製した半導体装置は、ゲート電極11と低濃度の第1の半導体層6とを短絡あるいは距離を制御性良く縮められるため、ゲートラグ等の表面の影響を回避することができる。

【0031】ゲート電極11と高濃度の第2の半導体層8との距離は、第1のマスク層の選択エッチによる開口の広げ巾と層厚に依存し自己整合的に形成できるため、その距離を容易に制御することが可能となり、第2の半導体層8との距離と濃度を設計することにより、高いドレイン耐圧を保ちつつ、ソース抵抗を低減することができる。

【0032】リセスの作製工程において、サイドエッチが入らないため横方向の作製精度は向上し、エッチング深さ方向に関してもストッパー層で深さは決まるため、しきい値電圧Vtの制御性,均一性,再現性も向上する。プロセスがウェットプロセスのため装置が簡便であり、コスト的にも改善される。

【0033】本発明の実施形態では、ストッパー層としてAlAsを用いたが、GaAsとのエッチング選択比が得られる範囲の組成のAlGaAsでも構わない。エッチング液の組成に関しても本実施形態では3:1を用いたが、選択比や異方性が得られる範囲でこの限りではなく、バッファー液としてクエン酸アンモニウム等を加えても構わない。またマスク層としてフォトレジストとSiO2を用いたが、SiO2とSiONなど選択エッチ可能なマスク材料を利用しても構わない。材料系についても本実施形態はAlGaAs/InGaAs/GaAs系を例に取ったが、AlInAs/GaInAs系や、AlInAs/InGaAs/InGaP系等にも応用可能である。

【0034】

【発明の効果】以上説明したように本発明によれば、横方向にはマスクで規定される(111)B面で決まり、サイドエッチのほとんど入らないエッチングを行なうことができ、深さ方向ではストッパー層でエッチング深さは決定されるので、エッチング時間にほとんど依存せずにデバイスを作製できる。このため、しきい値電圧Vtの制御性,均一性,再現性をも向上するさせることができる。さらにプロセスがウェットプロセスのため、装置が簡便であり、コスト的にも改善することができる。

【0035】デバイス特性としても、半導体装置はゲート電極と低濃度半導体層とを短絡あるいは距離を制御性良く縮められるため、ゲートラグ等の表面の影響を回避することができる。

【0036】また、ゲート電極と高濃度の半導体層との距離は、マスク層の巾と層厚に依存し自己整合的に2段リセスが容易に制御性良く形成できるため、高いドレイン耐圧を保ちつつソース抵抗を低減することができる。

【0037】さらにゲートを(011)方向にとることにより、容易に短ゲート化を行えるため、デバイス特性を向上させることができる。

【図面の簡単な説明】

【図1】本発明の一実施形態に係る半導体装置の製造方法を製造工程順に示す断面図である。

【図2】本発明の一実施形態に係る半導体装置の製造方法を製造工程順に示す断面図である。

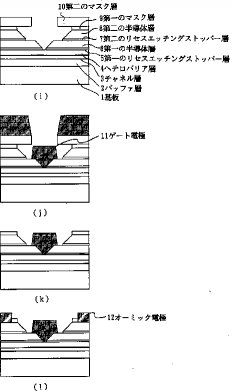

【図3】本発明の一実施形態に係る半導体装置の製造方法を製造工程順に示す断面図である。

【図4】従来の製造方法を製造工程順に示す断面図である。

【符号の説明】

1 基板

2 バッファ層

3 チャネル層

4 ヘテロバリア層

5 第1のリセスエッチングストッパー層

6 第1の半導体層

7 第2のリセスエッチングストッパー層

8 第2の半導体層

9 第1のマスク層

10 第2のマスク層

11 ゲート電極

12 オーミック電極

【0001】

【発明の属する技術分野】本発明は、化合物半導体装置及びその製造方法に関し、特に多段リセス構造を有する半導体装置およびその製造方法に関する。

【0002】

【従来の技術】ゲート耐圧の向上,ソース抵抗の低減,短チャネル効果抑制,表面効果の抑制などのため、HJFETでLDD構造を実現しようとしたとき、多段のリセス構造をとる必要があり、従来は、リセスエッチを2回の目合わせで個々に行っていた。また、特開平4−137737号公報にあるように多層マスクを用いて選択的にマスクをサイドエッチすることにより、横方向の制御性を向上させて2段リセス構造を実現していた。

【0003】

【発明が解決しようとする課題】しかしながら、2段リセスを2回の目合わせで行った場合、目合わせずれが問題となり、ゲートとn+領域との距離の制御や短縮が困難であった。また、特開平4−137737号公報にあるように多層マスクを用いて横方向の制御性を向上させたとしても、リセスエッチングの際に横方向にもエッチングが入ってしまい、短ゲート化やリセス巾の制御性に問題があった。

【0004】さらにリセスエッチングの際の深さ方向を考えたとき、1段目のリセス深さや2段目のリセス深さが、時間制御となり、再現性や制御性に問題があり、均一性が悪くなってしまうという問題があった。

【0005】本発明の目的は、リセス巾及びリセス深さを制御性良く作製できる半導体装置およびその製造方法を提供することにある。

【0006】

【課題を解決するための手段】前記目的を達成するため、本発明に係る半導体装置は、半導体多層構造を有する半導体装置であって、半導体多層構造は、化合物半導体の導電層上に第1のリセスエッチングストッパー層を設け、該リセスエッチングストッパー上に第1の半導体層を設け、該第1の半導体層上に第2のリセスエッチングストッパー層を設け、該第2のリセスエッチングストッパー層上に第2の半導体層を設けたものである。

【0007】また前記第1および第2の半導体層として、GaAs,InAs,AlxGa1-xAs(0≦x<1),AlyIn1-yAs(0≦y<1),InP,GaP,およびこれらの化合物から構成される化合物半導体を用いたものである。

【0008】また第1および第2のエッチングストッパー層として、AlAs、あるいはAlxGa1-xAsの組成より高いAl組成のAlzGa1-zAs(0<z≦1),AlyIn1-yAsより高いAl組成のAlwIn1-wAs(0<w≦1)を用いたものである。

【0009】また、(100)基板上に形成された半導体装置であり、半導体多層構造に設けられるゲートは、(011)に平行であり、リセスエッチング面は、(100)面と(111)面により構成されるものである。

【0010】また本発明に係る半導体装置の製造方法は、マスク形成工程と、パターニング工程と、第1の異方性エッチング工程と、第2の異方性エッチング工程とを含む、半導体多層構造を有する半導体装置の製造方法であって、半導体多層構造は、化合物半導体の導電層上に設けた第1のリセスエッチングストッパー層と、前記第1のリセスエッチングストッパー上に設けた第1の半導体層と、前記第1の半導体層上に設けた第2のリセスエッチングストッパー層と、前記第2のリセスエッチングストッパー層上に設けた第2の半導体層を有するものであり、マスク形成工程は、半導体多層構造上にエッチングレートの異なる第1のマスク層と第2のマスク層を設ける処理であり、パターニング工程は、第2のマスク層のパターニングを行い、これを用いて第1のマスク層のパターニングを行う処理であり、第1の異方性エッチング工程は、この第1および第2のマスク層を用いて第1の半導体層を第2のリセスエッチングストッパー層まで異方性エッチングする処理であり、第2の異方性エッチング工程は、開口部分のリセスエッチングストッパー層を除去し、さらに第1のマスク層の開口幅をサイドエッチングにより選択的に広げた後に、第1および第2のリセスエッチングストッパー層まで第2の半導体層および第1の半導体層の異方性エッチングを行う処理である。

【0011】また第1および第2の半導体層を異方性エッチングするエッチング液として、クエン酸水溶液と過酸化水素水の混合液からなるエッチング液を用いるものである。

【0012】

【作用】半導体多層構造上にエッチングレートの異なる第1のマスク層9と第2のマスク層10を設け(図1(b))、第2のマスク層10をパターニングし、そのパターニングされた第2のマスク層10を用いて第1のマスク層9のパターニングを行う。この第1および第2のマスク層9,10を用いて第2の半導体層8を第2のリセスエッチングストッパー層7まで異方性エッチングする。

【0013】第2のリセスエッチングストッパー層7まで異方性エッチングする際に、クエン酸水溶液と過酸化水素水の混合液からなるエッチング液を用いる。クエン酸系エッチング液は、GaAsなどの半導体層とAlAsなどのストッパー層を選択的にエッチングすることが可能であるばかりでなく、(111)B面のエッチング速度が極端に小さく抑えられるため、これを半導体多層構造のエッチングに用いれば、横方向はサイドエッチがほとんど入らず(111)Bで決まり、深さ方向はストッパー層7で決まるエッチングが可能となる。

【0014】上述したエッチング法を用いることにより、1段目の深さおよび開口幅は、第2のマスク層2の寸法とストッパー層7の位置で決まり、エッチング時間にほとんど依存しなくなる。

【0015】さらにゲートを(011)に平行にとることにより、開口形状は(111)B面で律速されるため、2段目の開口は、第2のマスク層9の寸法より細くすることが可能である(図2(e))。

【0016】その後、開口部分のリセスエッチングストッパー層7を除去し、さらに第1のマスク層9の開口巾をサイドエッチングにより選択的に広げた後に、第1および第2のリセスエッチングストッパー層5,7まで第2の半導体層8および第1の半導体層6の異方性エッチングを再度クエン酸系エッチング液で行う(図3(i))。

【0017】この際、第2の半導体層8はストッパー層7の存在により開口部分だけが削れるので、容易に2段リセス形状が作成できる。2段目の開口巾は最初の1段目のリセス巾ですでに決まっており、ゲートを(011)に平行にとることにより1段目のリセスエッチで細くなった開口巾は、2段目のエッチングでさらに細くなる。

【0018】第1の半導体層のキャリア濃度を第2の半導体層のキャリア濃度より小さくしておき、ゲート電極と第1の半導体層を短絡させ、第2の高濃度の半導体層と距離をとることにより、ゲートラグ等の表面の影響を回避しつつ、高いドレイン耐圧を得ることができる。しかもそれが容易に自己整合的に作製できる。横方向の2段目のリセス巾は、最初のマスク開口の巾と第1と第2の半導体層の厚さで決まり、エッチング深さ方向に関してもストッパー層の深さで決まる。1段目のリセス巾は第1のマスク層のサイドエッチ量で制御でき、その深さはストッパー層で決定される。このため、しきい値電圧Vtの制御性,均一性,再現性が向上する。また、ゲートを(011)に平行にとった場合、第1および第2の半導体層の厚さで制御される量だけマスク寸法からの短チャネル化を図れるので、デバイス特性の向上にもつながる。

【0019】

【発明の実施の形態】以下、本発明の実施形態をヘテロ接合形電界効果トランジスタを例にとり、図1〜図3を用いて説明する。

【0020】図1(a)に示すように半絶縁性GaAs基板1上に、たとえばMOCVD法により、基板側からi−GaAsバッファ層2を500nm,チャネル層3としてi−InGaAs層を15nm,n−AlGaAs層4を2×1018cm-3で33nm設け、第1のリセスエッチングストッパー層5としてn−AlAs層を2×1018cm-3で2nm設け、リセスエッチングストッパー層5上に第1の半導体層6として低濃度n−GaAs層を1×1018cm-3で150nm設ける。さらにn−GaAs層6上に第2のリセスエッチングストッパー層7としてn−AlAs層を2×1018cm-3で2nm設け、第2のリセスエッチングストッパー層7上に第2の半導体層8として高濃度n−GaAs層を4×1018cm-3で50nm設けることにより、本発明の半導体多層構造を作製する。

【0021】この化合物半導体多層構造を用いて、本発明の半導体装置の製造方法を説明する。該半導体多層構造上にエッチングレートの異なる第1のマスク層9としてSiO2層を50nm形成し、さらに第2のマスク層10としてフォトレジストを設ける(図1(b))。

【0022】次に第2のマスク層10であるフォトレジストのパターニングを行い(図1(c))、パターニングされた第2のマスク層10を用いて第1のマスク層9のSiO2のパターニングを行う(図1(d))。

【0023】この第1および第2のマスク層9,10を用いて第2の半導体層8のn−GaAs層を第2のリセスエッチングストッパー層7であるAlAsまで異方性エッチングを行なう。そのエッチングは、エッチング液として、クエン酸−水和物を同重量の水に溶かしたクエン酸水溶液と30%過酸化水素水を3:1で混合した混合液からなるエッチング液を用いて行う(図2(e))。

【0024】その後、開口部分のリセスエッチングストッパー層7のAlAs層を除去し、さらに第1のマスク層9であるSiO2の開口巾をバッファード弗酸により横方向にエッチングをして選択的に広げ、第1および第2のリセスエッチングストッパー層5および7のAlAs層まで第2の半導体層8としてのn−GaAs層および第1の半導体層6としてのn−GaAs層6の異方性エッチングを再度クエン酸系エッチング液で行う(図2の(f),(g),(h))。

【0025】さらに、エッチングストッパー層5および7のAlAs層の表面に出た部分を希塩酸で除去した後(図3(i))、第1のマスク層9であるフォトレジストを用いて、ゲート金属としてTi/Pt/Auを蒸着し、リフトオフ法によりゲート電極11の形成を行う(図3(j),(k))。これに通常の寸法でオーミック電極12を作製して半導体装置を完成させる。

【0026】クエン酸系エッチング液は、GaAsとalGaAsの選択エッチングが可能なうえ、低温では、(111)B面のエッチング速度が極端に小さく抑えられる。具体的には、リセスエッチングの1段目の開口巾および深さは、第1のマスク層のサイドエッチ後の開口寸法とストッパー層の位置で決まり、2段目の開口巾および深さは、第1のマスク層のサイドエッチ前の開口寸法とストッパー層の位置で決まる。このため、横方向にはマスクで規定される(111)B面で決まり、サイドエッチのほとんど入らないエッチングが可能となり、深さ方向ではストッパー層でエッチング深さは決定されるので、エッチング時間にほとんど依存せずにデバイスを作製できる。

【0027】開口形状は、横方向には(111)B面で律速されるため、ゲートを(011)に平行にとることにより、リセスエッチングの底の巾は最初のマスク開口巾より膜厚に応じて細くなる。

【0028】本発明の場合、最初のサイドエッチ前の第2のマスク層の開口巾より1段目のリセスエッチで細くなった開口巾は、2段目のエッチングでさらに電子供給層のAlGaAsの開口部分でさらに細くなる。

【0029】これにより、容易に短チャネル化を図れるので、デバイス特性の向上が図られる。本実施形態の場合、第2のマスク層の最初の開口巾が0.5μmのとき、横から0.14μmずつ傾斜した分だけ短ゲート化されるため、0.22μmのゲートが作製される。

【0030】このようにして作製した半導体装置は、ゲート電極11と低濃度の第1の半導体層6とを短絡あるいは距離を制御性良く縮められるため、ゲートラグ等の表面の影響を回避することができる。

【0031】ゲート電極11と高濃度の第2の半導体層8との距離は、第1のマスク層の選択エッチによる開口の広げ巾と層厚に依存し自己整合的に形成できるため、その距離を容易に制御することが可能となり、第2の半導体層8との距離と濃度を設計することにより、高いドレイン耐圧を保ちつつ、ソース抵抗を低減することができる。

【0032】リセスの作製工程において、サイドエッチが入らないため横方向の作製精度は向上し、エッチング深さ方向に関してもストッパー層で深さは決まるため、しきい値電圧Vtの制御性,均一性,再現性も向上する。プロセスがウェットプロセスのため装置が簡便であり、コスト的にも改善される。

【0033】本発明の実施形態では、ストッパー層としてAlAsを用いたが、GaAsとのエッチング選択比が得られる範囲の組成のAlGaAsでも構わない。エッチング液の組成に関しても本実施形態では3:1を用いたが、選択比や異方性が得られる範囲でこの限りではなく、バッファー液としてクエン酸アンモニウム等を加えても構わない。またマスク層としてフォトレジストとSiO2を用いたが、SiO2とSiONなど選択エッチ可能なマスク材料を利用しても構わない。材料系についても本実施形態はAlGaAs/InGaAs/GaAs系を例に取ったが、AlInAs/GaInAs系や、AlInAs/InGaAs/InGaP系等にも応用可能である。

【0034】

【発明の効果】以上説明したように本発明によれば、横方向にはマスクで規定される(111)B面で決まり、サイドエッチのほとんど入らないエッチングを行なうことができ、深さ方向ではストッパー層でエッチング深さは決定されるので、エッチング時間にほとんど依存せずにデバイスを作製できる。このため、しきい値電圧Vtの制御性,均一性,再現性をも向上するさせることができる。さらにプロセスがウェットプロセスのため、装置が簡便であり、コスト的にも改善することができる。

【0035】デバイス特性としても、半導体装置はゲート電極と低濃度半導体層とを短絡あるいは距離を制御性良く縮められるため、ゲートラグ等の表面の影響を回避することができる。

【0036】また、ゲート電極と高濃度の半導体層との距離は、マスク層の巾と層厚に依存し自己整合的に2段リセスが容易に制御性良く形成できるため、高いドレイン耐圧を保ちつつソース抵抗を低減することができる。

【0037】さらにゲートを(011)方向にとることにより、容易に短ゲート化を行えるため、デバイス特性を向上させることができる。

【図面の簡単な説明】

【図1】本発明の一実施形態に係る半導体装置の製造方法を製造工程順に示す断面図である。

【図2】本発明の一実施形態に係る半導体装置の製造方法を製造工程順に示す断面図である。

【図3】本発明の一実施形態に係る半導体装置の製造方法を製造工程順に示す断面図である。

【図4】従来の製造方法を製造工程順に示す断面図である。

【符号の説明】

1 基板

2 バッファ層

3 チャネル層

4 ヘテロバリア層

5 第1のリセスエッチングストッパー層

6 第1の半導体層

7 第2のリセスエッチングストッパー層

8 第2の半導体層

9 第1のマスク層

10 第2のマスク層

11 ゲート電極

12 オーミック電極

【特許請求の範囲】

【請求項1】 (100)基板上に形成された半導体多層構造を有する半導体装置であって、半導体多層構造は、化合物半導体の導電層上に第1のリセスエッチングストッパー層を設け、該リセスエッチングストッパー上に第1の半導体層を設け、該第1の半導体層上に第2のリセスエッチングストッパー層を設け、該第2のリセスエッチングストッパー層上に第2の半導体層を設けたものであり、当該半導体多層構造は前記第1の半導体層および前記第2の半導体層の(111)B面を側面とする2段のリセス形状を有し、下段のリセス底において前記化合物半導体の導電層に接するゲート電極が(011)方向に沿いかつ前記第2の半導体層とは間隙を持って前記第1の半導体層上に載置されてなる半導体装置。

【請求項2】 前記第1および第2の半導体層として、GaAs,InAs,AlxGa1-xAs(0≦x<1),AlyIn1-yAs(0≦y<1),InP,GaP,およびこれらの化合物から構成される化合物半導体を用いたものであることを特徴とする請求項1に記載の半導体装置。

【請求項3】 第1および第2のエッチングストッパー層として、AlAs、あるいはAlxGa1-xAsの組成より高いAl組成のAlzGa1-zAs(0<z≦1),AlyIn1-yAsより高いAl組成のAlwIn1-wAs(0<w≦1)を用いたものであることを特徴とする請求項1又は2に記載の半導体装置。

【請求項4】 マスク形成工程と、パターニング工程と、第1の異方性エッチング工程と、第2の異方性エッチング工程とを含む、(100)基板上に2段リセス形状の半導体多層構造を有する半導体装置の製造方法であって、半導体多層構造は、化合物半導体の導電層上に設けた第1のリセスエッチングストッパー層と、前記第1のリセスエッチングストッパー上に設けた第1の半導体層と、前記第1の半導体層上に設けた第2のリセスエッチングストッパー層と、前記第2のリセスエッチングストッパー層上に設けた第2の半導体層を有するものであり、マスク形成工程は、半導体多層構造上にエッチングレートの異なる第1のマスク層と第2のマスク層を設ける処理であり、パターニング工程は、第2のマスク層を(011)に平行なゲート形状にパターニングを行い、これを用いて第1のマスク層のパターニングを行う処理であり、第1の異方性エッチング工程は、前記第1および第2のマスク層を用いて第2の半導体層を第2のリセスエッチングストッパー層まで側面が(111)B面となるように異方性エッチングする処理であり、第2の異方性エッチング工程は、開口部分のリセスエッチングストッパー層を除去し、さらに第1のマスク層の開口幅をサイドエッチングにより選択的に広げた後に、第1および第2のリセスエッチングストッパー層まで第2の半導体層および第1の半導体層を側面が(111)B面となるように異方性エッチングを行う処理であることを特徴とする半導体装置の製造方法。

【請求項5】 前記第2の異方性エッチング工程に引き続き、前記第1および第2のエッチングストッパー層の表面露出部分を除去し、前記第2のマスク層を用いて自己整合的に前記化合物半導体の導電層に接続しかつ前記第2の半導体層とは間隙を持つゲート電極を形成する工程をさらに有する請求項4記載の半導体装置の製造方法。

【請求項6】第1または第2の半導体層を異方性エッチングする工程において、エッチング液としてクエン酸水溶液と過酸化水素水の混合液からなるエッチング液を用い、前記第1または第2のストッパー層に対して前記第1または第2の半導体層が選択的にエッチング可能であり、かつ(111)B面のエッチング速度が小さくなる条件でエッチングを行うことを特徴とする請求項4又は5に記載の半導体装置の製造方法。

【請求項1】 (100)基板上に形成された半導体多層構造を有する半導体装置であって、半導体多層構造は、化合物半導体の導電層上に第1のリセスエッチングストッパー層を設け、該リセスエッチングストッパー上に第1の半導体層を設け、該第1の半導体層上に第2のリセスエッチングストッパー層を設け、該第2のリセスエッチングストッパー層上に第2の半導体層を設けたものであり、当該半導体多層構造は前記第1の半導体層および前記第2の半導体層の(111)B面を側面とする2段のリセス形状を有し、下段のリセス底において前記化合物半導体の導電層に接するゲート電極が(011)方向に沿いかつ前記第2の半導体層とは間隙を持って前記第1の半導体層上に載置されてなる半導体装置。

【請求項2】 前記第1および第2の半導体層として、GaAs,InAs,AlxGa1-xAs(0≦x<1),AlyIn1-yAs(0≦y<1),InP,GaP,およびこれらの化合物から構成される化合物半導体を用いたものであることを特徴とする請求項1に記載の半導体装置。

【請求項3】 第1および第2のエッチングストッパー層として、AlAs、あるいはAlxGa1-xAsの組成より高いAl組成のAlzGa1-zAs(0<z≦1),AlyIn1-yAsより高いAl組成のAlwIn1-wAs(0<w≦1)を用いたものであることを特徴とする請求項1又は2に記載の半導体装置。

【請求項4】 マスク形成工程と、パターニング工程と、第1の異方性エッチング工程と、第2の異方性エッチング工程とを含む、(100)基板上に2段リセス形状の半導体多層構造を有する半導体装置の製造方法であって、半導体多層構造は、化合物半導体の導電層上に設けた第1のリセスエッチングストッパー層と、前記第1のリセスエッチングストッパー上に設けた第1の半導体層と、前記第1の半導体層上に設けた第2のリセスエッチングストッパー層と、前記第2のリセスエッチングストッパー層上に設けた第2の半導体層を有するものであり、マスク形成工程は、半導体多層構造上にエッチングレートの異なる第1のマスク層と第2のマスク層を設ける処理であり、パターニング工程は、第2のマスク層を(011)に平行なゲート形状にパターニングを行い、これを用いて第1のマスク層のパターニングを行う処理であり、第1の異方性エッチング工程は、前記第1および第2のマスク層を用いて第2の半導体層を第2のリセスエッチングストッパー層まで側面が(111)B面となるように異方性エッチングする処理であり、第2の異方性エッチング工程は、開口部分のリセスエッチングストッパー層を除去し、さらに第1のマスク層の開口幅をサイドエッチングにより選択的に広げた後に、第1および第2のリセスエッチングストッパー層まで第2の半導体層および第1の半導体層を側面が(111)B面となるように異方性エッチングを行う処理であることを特徴とする半導体装置の製造方法。

【請求項5】 前記第2の異方性エッチング工程に引き続き、前記第1および第2のエッチングストッパー層の表面露出部分を除去し、前記第2のマスク層を用いて自己整合的に前記化合物半導体の導電層に接続しかつ前記第2の半導体層とは間隙を持つゲート電極を形成する工程をさらに有する請求項4記載の半導体装置の製造方法。

【請求項6】第1または第2の半導体層を異方性エッチングする工程において、エッチング液としてクエン酸水溶液と過酸化水素水の混合液からなるエッチング液を用い、前記第1または第2のストッパー層に対して前記第1または第2の半導体層が選択的にエッチング可能であり、かつ(111)B面のエッチング速度が小さくなる条件でエッチングを行うことを特徴とする請求項4又は5に記載の半導体装置の製造方法。

【図4】

【図1】

【図2】

【図3】

【図1】

【図2】

【図3】

【公開番号】特開平11−354544

【公開日】平成11年(1999)12月24日

【国際特許分類】

【出願番号】特願平11−139383

【分割の表示】特願平8−139064の分割

【出願日】平成8年(1996)5月31日

【出願人】(000004237)日本電気株式会社 (19,353)

【公開日】平成11年(1999)12月24日

【国際特許分類】

【分割の表示】特願平8−139064の分割

【出願日】平成8年(1996)5月31日

【出願人】(000004237)日本電気株式会社 (19,353)

[ Back to top ]