半導体装置およびそれを備えた電子機器

【課題】小型化が可能な構成で、静電容量を正確に検出することができる半導体装置およびそれを備えた電子機器を提供する。

【解決手段】半導体装置1は、チップサイズパッケージ型半導体チップ2と、実装基板3と、検出対象物との間の静電容量を検出するための検出電極20と、検出電極20を取り囲むシールドとを含む。半導体チップ2は、内部回路8を構成する素子が作り込まれた半導体基板4と、半導体基板4の表面を封止する樹脂6と、樹脂6の表面から突出し、内部回路8に電気的に接続された突起電極7とを有する。実装基板3は、半導体チップ2の樹脂6の表面に対向して配置され、半導体チップ2がフリップチップ接合によって実装される実装面21を有する。検出電極20は、半導体チップ2または実装基板3に設けられており、シールドの少なくとも一部が実装基板3に設けられている。

【解決手段】半導体装置1は、チップサイズパッケージ型半導体チップ2と、実装基板3と、検出対象物との間の静電容量を検出するための検出電極20と、検出電極20を取り囲むシールドとを含む。半導体チップ2は、内部回路8を構成する素子が作り込まれた半導体基板4と、半導体基板4の表面を封止する樹脂6と、樹脂6の表面から突出し、内部回路8に電気的に接続された突起電極7とを有する。実装基板3は、半導体チップ2の樹脂6の表面に対向して配置され、半導体チップ2がフリップチップ接合によって実装される実装面21を有する。検出電極20は、半導体チップ2または実装基板3に設けられており、シールドの少なくとも一部が実装基板3に設けられている。

【発明の詳細な説明】

【技術分野】

【0001】

この発明は、検出対象物との間の静電容量を検出するための検出電極を備えた半導体装置およびこのような半導体装置を備えた電子機器に関する。

【背景技術】

【0002】

静電容量型近接センサは、検出電極と、信号処理のための処理回路とを含む。特許文献1には、検出電極と処理回路とを配線で接続した静電容量型近接センサが開示されている。検知対象物が検出電極に接近すると、検知対象物と検出電極との間にコンデンサが形成される。処理回路は、検出電極を一方の極板とするコンデンサの静電容量変化に基づいて、検知対象物の接近を検出し、検出信号を出力する。周囲からのノイズの影響を低減するために、検出電極と処理回路とを接続する配線は、信号線を取り囲むシールドを有するシールド配線で構成されている。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2006−32085号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

検出電極と処理回路とをシールド配線で接続する構造は複雑である。そのため、小型化が困難であり、小型の機器への実装が困難である。加えて、シールド配線を用いているとはいえ、配線の引き回しに起因する信号対ノイズ比(S/N比)の悪化の問題があるため、正確な検出が困難になるおそれがある。

そこで、この発明の目的は、小型化が可能な構成で、静電容量を正確に検出することができる半導体装置およびそれを備えた電子機器を提供することである。

【課題を解決するための手段】

【0005】

上記の目的を達成するための請求項1記載の発明に係る半導体装置は、内部回路を構成する素子が作り込まれた半導体基板と、前記半導体基板の表面を封止する樹脂と、前記樹脂の表面から突出し、前記内部回路に電気的に接続された突起電極とを有するチップサイズパッケージ型半導体チップと、前記半導体チップの前記樹脂の表面に対向して配置され、前記突起電極に電気的および機械的に接続されるランドを有し、前記半導体チップがフリップチップ接合によって実装される実装面を有する実装基板と、検出対象物との間の静電容量を検出するための検出電極と、前記検出電極を取り囲むシールドとを含む。そして、前記検出電極が前記半導体チップまたは前記実装基板に設けられており、前記シールドの少なくとも一部が前記実装基板に設けられている。

【0006】

この構成によれば、チップサイズパッケージ型半導体チップが実装基板の実装面にフリップチップ接合された構造によって、静電容量検出機能を有する半導体装置が構成されている。すなわち、半導体チップの半導体基板には内部回路を構成する素子が作り込まれており、その内部回路に電気的に接続された突起電極が、半導体基板の表面を封止する樹脂から突出している。その突起電極が実装基板のランドに電気的および機械的に接続されることによって、実装基板と半導体チップとが一体化されて、半導体装置が構成されている。半導体チップと実装基板との接続は、半導体チップ側の突起電極と実装基板側のランドとの接続によって達成されていて、それらの間に配線を必要としない。したがって、構造が簡単であり、かつ、容易に小型化を図ることができる。しかも、ボンディングワイヤによって半導体チップとリードフレームとを接続してモールド樹脂で封止する構成と比較すると、ボンディングワイヤまたはリードフレームの電位変化や、モールド樹脂の比誘電率の温度変化等に起因する誤検出を抑制することができる。したがって、静電容量の正確な検出が可能となる。

【0007】

さらに、静電容量を検出するための検出電極は、半導体チップまたは実装基板に設けられていて、検出電極を取り囲むシールドの少なくとも一部が実装基板に設けられている。したがって、半導体チップの内部回路によって静電容量検出のための信号処理回路を構成しておけば、信号処理回路と検出電極とシールドとを一体化することができ、検出電極および/またはシールドを保持するための別の部材を設ける必要がない。これによって、全体の構造が簡単になるから、容易に小型化を図ることができるうえ、ノイズの影響を受けにくく、したがって、静電容量の正確な検出が可能な半導体装置を提供することができる。

【0008】

請求項2に記載の発明は、前記検出電極が、前記実装基板の前記実装面に形成されている、請求項1に記載の半導体装置である。実装基板の実装面に検出電極を設けることによって、検出電極と半導体チップとの間の距離を最小にすることができるので、ノイズの影響を最小限にすることができる。具体的には、検出電極は、実装基板の実装面に形成されたランドパターンで構成されていてもよい。

【0009】

請求項3に記載の発明は、前記検出電極が、前記実装基板の前記実装面とは反対側の非実装面に形成されている、請求項1に記載の半導体装置である。この構成によれば、半導体チップが実装される実装面とは反対側の非実装面に検出電極が形成されているので、半導体チップとの接続のための制約を受けることなく検出電極を設計することができる。したがって、たとえば検出電極を大きな面積を有するように設計して、感度の向上を図ることができる。より具体的には、検出電極を半導体チップよりも大きな面積に形成して、より遠くの検出対象を検出できるようにすることができる。検出電極は、実装基板の非実装面に形成されたランドパターンで構成されていてもよい。

【0010】

請求項4に記載の発明は、前記検出電極が、前記半導体チップに設けられている、請求項1に記載の半導体装置である。この構成によれば、検出電極が半導体チップに設けられているので、内部回路と検出電極との間の配線長を一層短縮できるから、ノイズの影響をさらに抑制できる。

請求項5に記載の発明は、前記シールドは、前記実装基板に前記電極を取り囲むように形成されたシールドパターン膜を含む、請求項1〜4のいずれか一項に記載の半導体装置である。この構成によれば、電極を取り囲むように形成されたシールドパターン膜が実装基板に備えられている。これによって、実装基板を利用して(たとえば実装基板のランドパターンを利用して)シールドパターンを形成することができるので、構成を小型化および簡素化することができる。

【0011】

請求項6に記載の発明は、前記シールドパターン膜が前記実装面に形成されている、請求項5に記載の半導体装置である。この構成によれば、シールドパターン膜が実装面に形成されているので、とくに実装面に検出電極が形成される場合に、検出電極へのノイズの侵入を効果的に抑制することができる。

請求項7に記載の発明は、前記シールドパターン膜が、前記実装基板の前記実装面とは反対側の非実装面に形成されている、請求項5に記載の半導体装置である。この構成では、シールドパターンが非実装面に形成されているので、とくに非実装面に検出電極が形成される場合に、検出電極へのノイズの混入を効果的に抑制することができる。

【0012】

請求項8に記載の発明は、前記突起電極は、前記検出電極を取り囲むように配置され、前記シールドパターン膜に接続されたシールド用突起電極を含む、請求項5〜7のいずれか一項に記載の半導体装置である。この構成によれば、突起電極によっても検出電極がシールドされるので、さらに効果的にノイズの混入を抑制できる。複数個のシールド用突起電極が、検出電極を取り囲むように、間隔を開けて配列されていてもよい。隣り合うシールド用突起電極間の電位は、シールド用突起電極の電位、すなわち、シールドパターン膜の電位に等しくなるので、検出電極へのノイズの侵入を抑制できる。

【0013】

請求項9に記載の発明は、前記半導体チップは、前記半導体基板の表面に形成された配線層を含み、前記シールドは、前記配線層に形成されたシールド膜を含む、請求項1〜8のいずれか一項に記載の半導体装置である。この構成では、半導体チップの表面に配線層が形成されていて、この配線層にシールド膜が形成されている。これによって、半導体チップの配線層を利用してシールドを形成することができるので、構成を一層簡単にでき、かつ小型にすることができる。しかも、半導体チップ側から検出電極をシールドすることができるので、より効果的なノイズ対策が可能になる。

【0014】

請求項10に記載の発明は、前記検出電極が、複数の部分に分割されている、請求項1〜9のいずれか一項に記載の半導体装置である。この構成によれば、検出電極が複数の部分に分割されていることによって、各分割された部分に対して、異なる機能を与えることができる。これにより、より高機能な静電容量検出機能を提供することができる。たとえば、一対の検出電極の出力信号を用いてバックグラウンドノイズをキャンセルしたりする処理が可能になる。

【0015】

請求項11に記載の発明は、請求項1〜10のいずれか一項に記載の半導体装置と、前記半導体装置と接続された演算回路とを含む、電子機器である。半導体装置は、チップサイズパッケージ型半導体チップを実装基板にフリップチップ接合して構成された小型のものであるので、電子機器に対して容易に搭載することができ、当該電子機器に対して静電容量検出機能を提供することができる。たとえば、電子機器が、携帯型機器のように非常に小型のものであっても、精度の高い静電容量検出機能を提供できる。半導体装置が電子機器の演算回路に接続されていることによって、演算回路は、半導体装置による静電容量検出機能を利用した演算処理または制御処理を実行できる。

【0016】

請求項12に記載の発明は、前記電子機器が金属製の筐体を含む、請求項11に記載の電子機器である。半導体装置はシールドを備えており、しかも、半導体チップを実装基板にフリップチップ接合した構造のなかに検出電極およびシールドを備えている。そのため、金属製の筐体に起因するノイズを抑制することができるので、静電容量を正確に検出することができる。

【0017】

前記半導体装置に備えられる静電容量検出機能は、検出対象の接近により生じる静電容量変化を検出する静電容量型近接センサ機能であってもよい。

【図面の簡単な説明】

【0018】

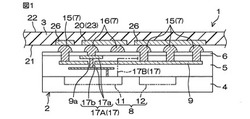

【図1】図1は、この発明の第1の実施形態に係る半導体装置の図解的な断面図である。

【図2】図2は前記半導体装置に備えられた実装基板の底面図である。

【図3】図3は、携帯型の電子機器の一例であるスマートフォンに対して前述の半導体装置を適用した構造を示す模式的な断面図である。

【図4】図4は、この発明の第2の実施形態に係る半導体装置の構成を説明するための図解的な断面図である。

【図5】図5は、図4に示された半導体装置の平面図である。

【図6】図6は、この発明の第3の実施形態に係る半導体装置の構成を説明するための模式的な断面図である。

【図7】図7は、図6に示された半導体装置に備えられた半導体チップの平面図である。

【図8】図8は、比較例に係る半導体装置の構成を示す模式的な断面図である。

【発明を実施するための形態】

【0019】

以下では、この発明の実施の形態を、添付図面を参照して詳細に説明する。

図1は、この発明の第1の実施形態に係る半導体装置の図解的な断面図である。また、図2は前記半導体装置に備えられた実装基板の底面図である。図1の断面図は、図2の線I-Iに対応している。半導体装置1は、半導体チップ2と、実装基板3と備えている。半導体チップ2は、半導体基板4と、その表面に形成された配線層5と、配線層5を封止する樹脂層6(たとえばポリイミド層)と、樹脂層6から突出した突起電極7とを備えている。半導体チップ2は、突起電極7を実装基板3の実装面に形成されたランドに接合させることによって、フリップチップ接合されている。図2には、突起電極7の配置を二点鎖線で示す。半導体基板4の内部には、複数の機能素子が形成されていて、それらは、内部回路8を形成している。内部回路8は、この実施形態では、信号処理回路11と照度センサ部12とを含む。配線層5は、配線を形成する金属膜(たとえばアルミニウムまたはアルミニウム合金からなる膜)と層間絶縁膜(たとえば酸化膜)とを含む、多層配線構造を有していてもよい。この多層配線構造を構成する金属膜の一部は、シールド膜9として利用されている。

【0020】

突起電極7は、樹脂層6から突出するように複数個形成されている。突起電極7は、半田ボールからなっていてもよい。複数の突起電極7は、シールド膜9に接続されたシールド用突起電極としての第1突起電極15と、信号処理回路11に接続された第2突起電極16とを含む。突起電極7は、さらに、半導体チップ2の内部回路に電源を供給したり、信号処理回路11の出力信号を取り出したりするための第3突起電極18を含んでいてもよい。図示は省略するが、実装基板3の実装面21には、突起電極18と接続されるランドが形成されている。

【0021】

シールド膜9には、開口9aが形成されている。配線層5には、シールド膜9から絶縁された状態で開口9aを貫通して信号処理回路11に至る信号経路17が設けられている。この信号経路17によって、第2突起電極16と信号処理回路11とが電気的に接続されている。信号経路17は、配線層5内の配線を構成する金属膜17aと、層間絶縁膜を貫通するビア17bとの組み合わせによって構成されていてもよい。信号経路17は、シールド膜9の下の部分では細く(具体的には、シールド膜9の上の部分よりも細く)形成されており、これにより、余分な(寄生)容量等が軽減されている。

【0022】

実装基板3は、たとえば、フレキシブルプリント配線基板からなり、半導体チップ2に対向する実装面21と、実装面21とは反対側の非実装面22とを備えている。実装面21には、検出対象物との間の静電容量を検出するための検出電極20が、ランドパターンを利用して形成されている。この実施形態では、検出電極20は、図2に示すように、第1検出電極23と、第2検出電極24とを含む。第1検出電極23は、第2検出電極24よりも大きく形成されている。第1検出電極23は、この実施形態では、平面視(実装基板3の主面(実装面21および非実装面22)を垂直に見下ろす平面視。以下同じ。)において矩形形状(たとえば0.8mm×1.2mm)を有しており、この第1検出電極23に対して、複数個の第2突起電極16が接合されている。より具体的には、第1検出電極23の矩形形状に対応する矩形パターンに配列された複数個(この実施形態では6個)の第2突起電極16が、第1検出電極23に接合されている。一方、第2検出電極24は、この実施形態においては、一つの第2突起電極16に対向するように小さな矩形形状(たとえば0.4mm×0.4mm)に形成されていて、この第2検出電極24に、一つの第2突起電極16が接合されている。

【0023】

第1検出電極23は、シールド膜9の開口9aを貫通するように配線層5に形成された信号経路17Aによって信号処理回路11に電気的に接続されている。第2検出電極54は、シールド膜9の別の開口(図示せず)を貫通するように配線層5に形成された別の信号経路17Bによって、信号処理回路11に接続されている。

実装基板3の実装面21には、さらに、ランドパターンを利用したシールドパターン膜26が形成されている。シールドパターン膜26は、検出電極20と同一の金属材料で形成された金属膜のパターンである。シールドパターン膜26は、帯状膜を、平面視において検出電極20を取り囲む環状を形成するように引き回して構成されている。この実施形態では、シールドパターン膜26が取り囲む領域内に、第1検出電極23および第2検出電極24が配置されており、さらに当該領域内に照度センサ部12のための検出窓25が配置されている。検出窓25は、実装基板3の実装面21および非実装面22の間を貫通した貫通窓である。半導体装置1には、平面視において、シールドパターン膜26に整合するパターンで、複数の第1突起電極15が、所定の間隔(たとえば0.4mm〜0.5mm)を空けて整列している。したがって、これらの第1突起電極15は、平面視において、検出電極20を取り囲む環状パターンを形成するように配列されている。これらの第1突起電極15は、シールドパターン膜26に接合されていて、シールドパターン膜26と同電位(より具体的にはグランド電位)とされている。

【0024】

半導体チップ2は、半導体基板4の表面に形成された配線層5の最表面を樹脂層6で封止したチップサイズパッケージ型の構成を有している。したがって、半導体チップ2は、それ自体の大きさが小さく、この小さな半導体チップ2をフリップチップ接合によって実装基板3に接合しているので、半導体装置1は、全体として、小型に構成することができる。さらに、実装基板3の実装面21に形成されたランドパターンを利用して検出電極20が形成されているので、検出電極20を保持するための別の部材を設ける必要がない。これによって、構成が簡単になっており、それに応じて、小型化が図られている。

【0025】

さらに、検出電極20に対するノイズの影響を排除するためのシールドが、実装基板3のランドパターンを利用したシールドパターン膜26と、半導体チップ2の配線層5に形成したシールド膜9と、シールド膜9とシールドパターン膜26とを電気的に接続する複数の第1突起電極15とで構成されている。したがって、シールドを構成するための特別の部材を必要としないので、構成が簡単になり、それに応じて小型化を図ることができる。

【0026】

さらにまた、信号処理回路11と検出電極20との間の電気的接続は、配線層5および第2突起電極16によって達成されており、長い配線ケーブルを用いていない。そのため、構成が簡単であり、かつ、信号経路に対するノイズの侵入を効果的に抑制することができる。これにより、簡単で、かつ小型の構成によって、静電容量を正確に検出することができる。

【0027】

より具体的には、検出電極20に対して検出対象が接近したときに、検出電極20と当該検出対象との間に形成されるコンデンサの容量が正確に検出される。さらに具体的には、検出対象が検出電極20に対して接近する前と、検出対象が検出電極20に接近した後との容量変化を、正確に検出することができる。これによって、静電容量型の近接センサを提供することができる。

【0028】

また、この実施形態では、検出電極20が、第1検出電極23と第2検出電極24とに分割されている。そこで、たとえば、第1および第2検出電極23,24の出力信号を用いてバックグラウンドノイズをキャンセルしたりする処理を信号処理回路11において行うことができる。これにより、静電容量を一層正確に検出できる。

図8に比較例を示すように、リードフレーム31の表面に半導体チップ32を搭載し、ボンディングワイヤ33によってリードフレーム31と半導体チップ32とを電気的に接続する構成の半導体装置が考えられる。リードフレーム31の一部、半導体チップ32およびボンディングワイヤ33は、モールド樹脂34によって封止されている。この構成において、半導体チップ32の表面の配線層を利用して検出電極35を形成することが考えられるかもしれない。しかし、この比較例に係る構成では、ボンディングワイヤ33およびリードフレーム31と検出電極35との間にそれぞれ容量が形成されるから、検出電極35が検出する容量は、ボンディングワイヤ33およびリードフレーム31の電位変化の影響を受ける。したがって、誤検出が生じるおそれがある。さらにまた、検出電極35が検出する容量は、モールド樹脂34の比誘電率の影響を受ける。ところが、モールド樹脂34の比誘電率は、温度に応じて変化するから、モールド樹脂34の温度が変化すれば、誤検出が生じるおそれがある。

【0029】

前述第1の実施形態の構成は、このような問題をも解決し、精度の高い静電容量検出機能を提供する。

図3は、携帯型の電子機器の一例であるスマートフォンに対して前述の半導体装置1を適用した構造を示す模式的な断面図である。スマートフォン40は、金属製の筐体41と、タッチパネル42と、半導体装置1と、演算処理部45(演算回路)とを備えている。筐体41においてタッチパネル42を指示している部分に開口41aが形成されており、この開口41aに半導体チップ2が配置されている。タッチパネル42には、光学窓43が設けられている。この光学窓43の背後に、検出電極20および照度センサ部12を対向させて、半導体装置1が配置されている。光学窓43に対応する部分においては、半導体チップ2の樹脂層6に開口が形成されている。半導体装置1を構成する実装基板3は、この例では、フレキシブルプリント配線基板からなる。この実装基板3は、たとえば、タッチパネル42との電気的接続のためのランドと、演算処理部45との電気的接続のためのランドと、タッチパネル42、演算処理部45および半導体装置1の間の電気的接続を担う配線パターンとを有している。

【0030】

筐体41が金属製であるので、検出電極20は、筐体41との間においても容量を形成する。しかし、半導体装置1は、信号処理回路11と検出電極20との間を極めて短い配線長で接続した構成を有しており、しかも、検出電極20の周囲に設けられたシールドを一体的に有している。これにより、金属製の筐体41による静電容量検出に対する影響を最小限にすることができる。よって、金属製の筐体41を有するスマートフォン40に搭載された場合であっても、半導体装置1は、すぐれた静電容量検出機能を提供することができる。しかも、半導体装置1は、それ自体が小型に構成されているので、小さな筐体41の内部に容易に収容することができる。これにより、筐体41の小型化や、筐体41に別の機能部品を収容することによる多機能化に寄与することができる。

【0031】

半導体装置1は、演算処理部45に対して、検出対象物が接近しているかどうかを表す信号を供給する。これに応じて、演算処理部45は、たとえば、タッチパネル42を背後から照明するためのバックライトをオン/オフ制御する。より具体的には、スマートフォン40の使用者がスマートフォン40を耳に押し当てたときに、半導体装置1は検出対象の接近を表す信号を演算処理部45に供給する。これに応答して、演算処理部45はバックライト消灯する。こうして、消費電力を低減することができる。半導体装置1が検出対象の接近を表す信号を出力おらず、かつ照度センサ部12が検出する照度が所定の消灯基準照度を超えていれば、演算処理部40は、バックライトを点灯してタッチパネル42を背後から照明する。バックライトの駆動電力は、照度センサ部12が検出する照度に応じて可変制御されてもよい。

【0032】

図4は、この発明の第2の実施形態に係る半導体装置の構成を説明するための図解的な断面図である。また、図5は、図4に示された半導体装置の平面図である。図4の断面図は、図5の線IV-IVに対応している。これらの図4および図5において、前述の図1および図2に示された各部に対応する部分には、同一の参照符を付して示す。

この半導体装置51においては、実装基板3の非実装面22に検出電極52が設けられている。さらに、非実装面22に、検出電極52を取り囲むようにシールドパターン膜56が設けられている。検出電極52およびシールドパターン膜56は、いずれも、実装基板3の非実装面22に形成されたランドパターンを利用して構成されている。信号処理回路11に接続された第2突起電極16は、実装基板3の実装面21に形成されたランド57に接続されている。ランド57と、検出電極52とは、実装基板3の実装面21および非実装面22の間を貫通する貫通ビア58によって、電気的に互いに接続されている。検出電極52は、第1検出電極53と、第2検出電極54とを含む。第1検出電極53は、第2検出電極54よりも大きな面積を有している。より具体的には、第1検出電極53は、ほぼ矩形形状を有しており、その一辺が中心に向かって帯状に切り欠かれている。この切り欠かれた領域に、帯状の第2検出電極54が配置されている。第2検出電極54の長手方向途中位置に照度センサ部12のための検出窓25が位置している。第1検出電極53は、貫通ビア58Aによって、ランド57に接続されており、さらに信号経路17Aを介して信号処理回路11に接続されている。第2検出電極54は、別の貫通ビア58Bによって、実装面21に形成された別のランドに接続されており、当該別のランドが、一つの第2突起電極16Bに接続されている。この第2突起電極16Bは、シールド膜9に形成された別の開口(図示せず)をシールド膜9から絶縁された状態で貫通する信号経路17Bを介して、信号処理回路11に接続されている。

【0033】

半導体チップ2内のシールド膜9に接続された第1突起電極15は、実装基板3の実装面21に形成されたランド59に接合されている。ランド59は、検出電極用のランド57の周囲を取り囲むように形成されていて、実装基板3を挟んでシールドパターン膜56と対向する位置まで延びて形成されている。ランド59は、実装基板3の実装面21および非実装面22の間を貫通する貫通ビア60によって、シールドパターン膜56に電気的に接続されている。シールドパターン膜56は、環状に形成された無端の帯状パターンに形成されている。このシールドパターン膜56に囲まれた領域には、検出電極52が配置されているほか、照度センサ部12のための検出窓25が配置されている。検出窓25は、実装基板3の実装面21および非実装面22の間を貫通して形成された貫通孔である。シールドパターン膜56に対応したランド59は、検出電極52を実装面21側から覆うパターンに形成されていて、非実装面22側からのノイズの侵入を抑制する。

【0034】

このように、この実施形態の構成によれば、検出電極52が実装基板3の非実装面22に形成されているので、検出電極52の設計に際して、半導体チップ2との電気的接続に伴う制限が少ない。そのため、検出電極52を、半導体チップ2よりも大きく形成することができる。これによって、検出感度を高めることができ、より遠くの検出対象の接近を検出できる。さらにまた、検出電極52の背後には、実装基板3の実装面21に配置したランド59が位置していて、このランド59が、シールド膜9に電気的に接続されている。それによって、検出電極52に対する実装面21側からのノイズの侵入を抑制することができる。こうして、静電容量検出精度をより一層高めることができる。

【0035】

また、この実施形態においても、検出電極52が、第1検出電極53と第2検出電極54とに分割されている。そこで、たとえば、第1および第2検出電極53,54の出力信号を用いてバックグラウンドノイズをキャンセルしたりする処理を信号処理回路11において行うことができる。これにより、静電容量を一層正確に検出できる。

図6は、この発明の第3の実施形態に係る半導体装置の構成を説明するための模式的な断面図である。また、図7は、図6に示された半導体装置の半導体チップ2の平面図である。図6の断面図は、図7の線VI-VIに対応している。これらの図6および図7において、前述の図1および図2に示された各部に対応する部分には、同一の参照符号を付して示す。

【0036】

この半導体装置71においては、半導体チップ2の配線層5内の金属膜(たとえばアルミニウム膜またはアルミニウム合金膜)によって検出電極72が形成されている。したがって、半導体チップ2には、検出電極のための突起電極は設けられていない。実装基板3の実装面21には、平面視において検出電極72を取り囲むように、ランドパターンを利用したシールドパターン膜73が形成されている。シールドパターン膜73は、突起電極15によって、半導体チップ2の配線層5に形成されたシールド膜9と電気的に接続されている。この実施形態では、検出電極72に対するシールドが、シールド膜9、突起電極15およびシールドパターン膜73によって構成されている。

【0037】

このような構成によっても、簡単でかつ小型の構成により、精度の高い静電容量検出が可能になる。

なお、検出電極72は、図6に示すように樹脂層6によって覆われていてもよいし、樹脂層6から露出していてもよい。また、配線層5に検出電極72を形成するのではなく、樹脂層6の表面に検出電極を形成してもよい。この場合の検出電極は、たとえば銅膜からなっていてもよい。

【0038】

以上、この発明のいくつかの実施形態について説明したが、この発明はさらに他の形態で実施することができる。たとえば、前述の実施形態では、シールドパターン膜26,56,73がいずれも無端状の環状である例を示したが、検出電極を取り囲むシールドパターン膜は、途中に僅かな切れ目があってもよい。その場合でも、その切れ目の部分の電位は、シールドパターン膜と等しくなるので、外部からのノイズを遮蔽できる。

【0039】

また、前述の実施形態においては、静電容量検出機能付きの半導体装置をスマートフォンに適用した例を説明したが、むろん、半導体装置の用途はこれに限られるわけではない。たとえば、テレビやディスプレイ等の電気機器のためのタッチスイッチとしても、この発明に係る半導体装置を利用することができる。

また、前述の第1および第2実施形態では、シールドパターン膜に囲まれた領域に照度センサ部12が配置されているが、シールドパターン膜に囲まれた領域の外側に照度センサ部12が配置されてもよい。

【0040】

さらに、前述の第1および第2の実施形態では、半導体チップに照度センサ部12が組み込まれた構成を示したが、照度センサ部12は省かれてもよい。また、照度センサ部以外の別の機能部分を半導体チップに搭載してもよい。また、前述の第1および第2実施形態では、照度センサ部12が半導体基板2内に形成されている例を示したが、配線層5内に照度センサ部が形成されていてもよい。

【0041】

また、前述の第1および第2の実施形態では、検出電極が2つの部分に分割されている例を示したが、むろん、検出電極が3つ以上の部分に分割されていてもよい。

その他、特許請求の範囲に記載された事項の範囲で種々の設計変更を施すことが可能である。

【符号の説明】

【0042】

1 半導体装置

2 半導体チップ

3 実装基板

4 半導体基板

5 配線層

6 樹脂層

7 突起電極

8 内部回路

9 シールド膜

11 信号処理回路

12 照度センサ部

15 第1突起電極

16,16B 第2突起電極

17,17A,17B 信号経路

20 検出電極

21 実装面

22 非実装面

23 第1検出電極

24 第2検出電極

25 検出窓

26 シールドパターン膜

40 スマートフォン

41 金属製の筐体

42 タッチパネル

43 光学窓

45 演算処理部

51 半導体装置

52 検出電極

53 第1検出電極

54 第2検出電極

56 シールドパターン膜

57 ランド

58,58A,58B 貫通ビア

59 ランド

60 貫通ビア

71 半導体装置

72 検出電極

73 シールドパターン膜

【技術分野】

【0001】

この発明は、検出対象物との間の静電容量を検出するための検出電極を備えた半導体装置およびこのような半導体装置を備えた電子機器に関する。

【背景技術】

【0002】

静電容量型近接センサは、検出電極と、信号処理のための処理回路とを含む。特許文献1には、検出電極と処理回路とを配線で接続した静電容量型近接センサが開示されている。検知対象物が検出電極に接近すると、検知対象物と検出電極との間にコンデンサが形成される。処理回路は、検出電極を一方の極板とするコンデンサの静電容量変化に基づいて、検知対象物の接近を検出し、検出信号を出力する。周囲からのノイズの影響を低減するために、検出電極と処理回路とを接続する配線は、信号線を取り囲むシールドを有するシールド配線で構成されている。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2006−32085号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

検出電極と処理回路とをシールド配線で接続する構造は複雑である。そのため、小型化が困難であり、小型の機器への実装が困難である。加えて、シールド配線を用いているとはいえ、配線の引き回しに起因する信号対ノイズ比(S/N比)の悪化の問題があるため、正確な検出が困難になるおそれがある。

そこで、この発明の目的は、小型化が可能な構成で、静電容量を正確に検出することができる半導体装置およびそれを備えた電子機器を提供することである。

【課題を解決するための手段】

【0005】

上記の目的を達成するための請求項1記載の発明に係る半導体装置は、内部回路を構成する素子が作り込まれた半導体基板と、前記半導体基板の表面を封止する樹脂と、前記樹脂の表面から突出し、前記内部回路に電気的に接続された突起電極とを有するチップサイズパッケージ型半導体チップと、前記半導体チップの前記樹脂の表面に対向して配置され、前記突起電極に電気的および機械的に接続されるランドを有し、前記半導体チップがフリップチップ接合によって実装される実装面を有する実装基板と、検出対象物との間の静電容量を検出するための検出電極と、前記検出電極を取り囲むシールドとを含む。そして、前記検出電極が前記半導体チップまたは前記実装基板に設けられており、前記シールドの少なくとも一部が前記実装基板に設けられている。

【0006】

この構成によれば、チップサイズパッケージ型半導体チップが実装基板の実装面にフリップチップ接合された構造によって、静電容量検出機能を有する半導体装置が構成されている。すなわち、半導体チップの半導体基板には内部回路を構成する素子が作り込まれており、その内部回路に電気的に接続された突起電極が、半導体基板の表面を封止する樹脂から突出している。その突起電極が実装基板のランドに電気的および機械的に接続されることによって、実装基板と半導体チップとが一体化されて、半導体装置が構成されている。半導体チップと実装基板との接続は、半導体チップ側の突起電極と実装基板側のランドとの接続によって達成されていて、それらの間に配線を必要としない。したがって、構造が簡単であり、かつ、容易に小型化を図ることができる。しかも、ボンディングワイヤによって半導体チップとリードフレームとを接続してモールド樹脂で封止する構成と比較すると、ボンディングワイヤまたはリードフレームの電位変化や、モールド樹脂の比誘電率の温度変化等に起因する誤検出を抑制することができる。したがって、静電容量の正確な検出が可能となる。

【0007】

さらに、静電容量を検出するための検出電極は、半導体チップまたは実装基板に設けられていて、検出電極を取り囲むシールドの少なくとも一部が実装基板に設けられている。したがって、半導体チップの内部回路によって静電容量検出のための信号処理回路を構成しておけば、信号処理回路と検出電極とシールドとを一体化することができ、検出電極および/またはシールドを保持するための別の部材を設ける必要がない。これによって、全体の構造が簡単になるから、容易に小型化を図ることができるうえ、ノイズの影響を受けにくく、したがって、静電容量の正確な検出が可能な半導体装置を提供することができる。

【0008】

請求項2に記載の発明は、前記検出電極が、前記実装基板の前記実装面に形成されている、請求項1に記載の半導体装置である。実装基板の実装面に検出電極を設けることによって、検出電極と半導体チップとの間の距離を最小にすることができるので、ノイズの影響を最小限にすることができる。具体的には、検出電極は、実装基板の実装面に形成されたランドパターンで構成されていてもよい。

【0009】

請求項3に記載の発明は、前記検出電極が、前記実装基板の前記実装面とは反対側の非実装面に形成されている、請求項1に記載の半導体装置である。この構成によれば、半導体チップが実装される実装面とは反対側の非実装面に検出電極が形成されているので、半導体チップとの接続のための制約を受けることなく検出電極を設計することができる。したがって、たとえば検出電極を大きな面積を有するように設計して、感度の向上を図ることができる。より具体的には、検出電極を半導体チップよりも大きな面積に形成して、より遠くの検出対象を検出できるようにすることができる。検出電極は、実装基板の非実装面に形成されたランドパターンで構成されていてもよい。

【0010】

請求項4に記載の発明は、前記検出電極が、前記半導体チップに設けられている、請求項1に記載の半導体装置である。この構成によれば、検出電極が半導体チップに設けられているので、内部回路と検出電極との間の配線長を一層短縮できるから、ノイズの影響をさらに抑制できる。

請求項5に記載の発明は、前記シールドは、前記実装基板に前記電極を取り囲むように形成されたシールドパターン膜を含む、請求項1〜4のいずれか一項に記載の半導体装置である。この構成によれば、電極を取り囲むように形成されたシールドパターン膜が実装基板に備えられている。これによって、実装基板を利用して(たとえば実装基板のランドパターンを利用して)シールドパターンを形成することができるので、構成を小型化および簡素化することができる。

【0011】

請求項6に記載の発明は、前記シールドパターン膜が前記実装面に形成されている、請求項5に記載の半導体装置である。この構成によれば、シールドパターン膜が実装面に形成されているので、とくに実装面に検出電極が形成される場合に、検出電極へのノイズの侵入を効果的に抑制することができる。

請求項7に記載の発明は、前記シールドパターン膜が、前記実装基板の前記実装面とは反対側の非実装面に形成されている、請求項5に記載の半導体装置である。この構成では、シールドパターンが非実装面に形成されているので、とくに非実装面に検出電極が形成される場合に、検出電極へのノイズの混入を効果的に抑制することができる。

【0012】

請求項8に記載の発明は、前記突起電極は、前記検出電極を取り囲むように配置され、前記シールドパターン膜に接続されたシールド用突起電極を含む、請求項5〜7のいずれか一項に記載の半導体装置である。この構成によれば、突起電極によっても検出電極がシールドされるので、さらに効果的にノイズの混入を抑制できる。複数個のシールド用突起電極が、検出電極を取り囲むように、間隔を開けて配列されていてもよい。隣り合うシールド用突起電極間の電位は、シールド用突起電極の電位、すなわち、シールドパターン膜の電位に等しくなるので、検出電極へのノイズの侵入を抑制できる。

【0013】

請求項9に記載の発明は、前記半導体チップは、前記半導体基板の表面に形成された配線層を含み、前記シールドは、前記配線層に形成されたシールド膜を含む、請求項1〜8のいずれか一項に記載の半導体装置である。この構成では、半導体チップの表面に配線層が形成されていて、この配線層にシールド膜が形成されている。これによって、半導体チップの配線層を利用してシールドを形成することができるので、構成を一層簡単にでき、かつ小型にすることができる。しかも、半導体チップ側から検出電極をシールドすることができるので、より効果的なノイズ対策が可能になる。

【0014】

請求項10に記載の発明は、前記検出電極が、複数の部分に分割されている、請求項1〜9のいずれか一項に記載の半導体装置である。この構成によれば、検出電極が複数の部分に分割されていることによって、各分割された部分に対して、異なる機能を与えることができる。これにより、より高機能な静電容量検出機能を提供することができる。たとえば、一対の検出電極の出力信号を用いてバックグラウンドノイズをキャンセルしたりする処理が可能になる。

【0015】

請求項11に記載の発明は、請求項1〜10のいずれか一項に記載の半導体装置と、前記半導体装置と接続された演算回路とを含む、電子機器である。半導体装置は、チップサイズパッケージ型半導体チップを実装基板にフリップチップ接合して構成された小型のものであるので、電子機器に対して容易に搭載することができ、当該電子機器に対して静電容量検出機能を提供することができる。たとえば、電子機器が、携帯型機器のように非常に小型のものであっても、精度の高い静電容量検出機能を提供できる。半導体装置が電子機器の演算回路に接続されていることによって、演算回路は、半導体装置による静電容量検出機能を利用した演算処理または制御処理を実行できる。

【0016】

請求項12に記載の発明は、前記電子機器が金属製の筐体を含む、請求項11に記載の電子機器である。半導体装置はシールドを備えており、しかも、半導体チップを実装基板にフリップチップ接合した構造のなかに検出電極およびシールドを備えている。そのため、金属製の筐体に起因するノイズを抑制することができるので、静電容量を正確に検出することができる。

【0017】

前記半導体装置に備えられる静電容量検出機能は、検出対象の接近により生じる静電容量変化を検出する静電容量型近接センサ機能であってもよい。

【図面の簡単な説明】

【0018】

【図1】図1は、この発明の第1の実施形態に係る半導体装置の図解的な断面図である。

【図2】図2は前記半導体装置に備えられた実装基板の底面図である。

【図3】図3は、携帯型の電子機器の一例であるスマートフォンに対して前述の半導体装置を適用した構造を示す模式的な断面図である。

【図4】図4は、この発明の第2の実施形態に係る半導体装置の構成を説明するための図解的な断面図である。

【図5】図5は、図4に示された半導体装置の平面図である。

【図6】図6は、この発明の第3の実施形態に係る半導体装置の構成を説明するための模式的な断面図である。

【図7】図7は、図6に示された半導体装置に備えられた半導体チップの平面図である。

【図8】図8は、比較例に係る半導体装置の構成を示す模式的な断面図である。

【発明を実施するための形態】

【0019】

以下では、この発明の実施の形態を、添付図面を参照して詳細に説明する。

図1は、この発明の第1の実施形態に係る半導体装置の図解的な断面図である。また、図2は前記半導体装置に備えられた実装基板の底面図である。図1の断面図は、図2の線I-Iに対応している。半導体装置1は、半導体チップ2と、実装基板3と備えている。半導体チップ2は、半導体基板4と、その表面に形成された配線層5と、配線層5を封止する樹脂層6(たとえばポリイミド層)と、樹脂層6から突出した突起電極7とを備えている。半導体チップ2は、突起電極7を実装基板3の実装面に形成されたランドに接合させることによって、フリップチップ接合されている。図2には、突起電極7の配置を二点鎖線で示す。半導体基板4の内部には、複数の機能素子が形成されていて、それらは、内部回路8を形成している。内部回路8は、この実施形態では、信号処理回路11と照度センサ部12とを含む。配線層5は、配線を形成する金属膜(たとえばアルミニウムまたはアルミニウム合金からなる膜)と層間絶縁膜(たとえば酸化膜)とを含む、多層配線構造を有していてもよい。この多層配線構造を構成する金属膜の一部は、シールド膜9として利用されている。

【0020】

突起電極7は、樹脂層6から突出するように複数個形成されている。突起電極7は、半田ボールからなっていてもよい。複数の突起電極7は、シールド膜9に接続されたシールド用突起電極としての第1突起電極15と、信号処理回路11に接続された第2突起電極16とを含む。突起電極7は、さらに、半導体チップ2の内部回路に電源を供給したり、信号処理回路11の出力信号を取り出したりするための第3突起電極18を含んでいてもよい。図示は省略するが、実装基板3の実装面21には、突起電極18と接続されるランドが形成されている。

【0021】

シールド膜9には、開口9aが形成されている。配線層5には、シールド膜9から絶縁された状態で開口9aを貫通して信号処理回路11に至る信号経路17が設けられている。この信号経路17によって、第2突起電極16と信号処理回路11とが電気的に接続されている。信号経路17は、配線層5内の配線を構成する金属膜17aと、層間絶縁膜を貫通するビア17bとの組み合わせによって構成されていてもよい。信号経路17は、シールド膜9の下の部分では細く(具体的には、シールド膜9の上の部分よりも細く)形成されており、これにより、余分な(寄生)容量等が軽減されている。

【0022】

実装基板3は、たとえば、フレキシブルプリント配線基板からなり、半導体チップ2に対向する実装面21と、実装面21とは反対側の非実装面22とを備えている。実装面21には、検出対象物との間の静電容量を検出するための検出電極20が、ランドパターンを利用して形成されている。この実施形態では、検出電極20は、図2に示すように、第1検出電極23と、第2検出電極24とを含む。第1検出電極23は、第2検出電極24よりも大きく形成されている。第1検出電極23は、この実施形態では、平面視(実装基板3の主面(実装面21および非実装面22)を垂直に見下ろす平面視。以下同じ。)において矩形形状(たとえば0.8mm×1.2mm)を有しており、この第1検出電極23に対して、複数個の第2突起電極16が接合されている。より具体的には、第1検出電極23の矩形形状に対応する矩形パターンに配列された複数個(この実施形態では6個)の第2突起電極16が、第1検出電極23に接合されている。一方、第2検出電極24は、この実施形態においては、一つの第2突起電極16に対向するように小さな矩形形状(たとえば0.4mm×0.4mm)に形成されていて、この第2検出電極24に、一つの第2突起電極16が接合されている。

【0023】

第1検出電極23は、シールド膜9の開口9aを貫通するように配線層5に形成された信号経路17Aによって信号処理回路11に電気的に接続されている。第2検出電極54は、シールド膜9の別の開口(図示せず)を貫通するように配線層5に形成された別の信号経路17Bによって、信号処理回路11に接続されている。

実装基板3の実装面21には、さらに、ランドパターンを利用したシールドパターン膜26が形成されている。シールドパターン膜26は、検出電極20と同一の金属材料で形成された金属膜のパターンである。シールドパターン膜26は、帯状膜を、平面視において検出電極20を取り囲む環状を形成するように引き回して構成されている。この実施形態では、シールドパターン膜26が取り囲む領域内に、第1検出電極23および第2検出電極24が配置されており、さらに当該領域内に照度センサ部12のための検出窓25が配置されている。検出窓25は、実装基板3の実装面21および非実装面22の間を貫通した貫通窓である。半導体装置1には、平面視において、シールドパターン膜26に整合するパターンで、複数の第1突起電極15が、所定の間隔(たとえば0.4mm〜0.5mm)を空けて整列している。したがって、これらの第1突起電極15は、平面視において、検出電極20を取り囲む環状パターンを形成するように配列されている。これらの第1突起電極15は、シールドパターン膜26に接合されていて、シールドパターン膜26と同電位(より具体的にはグランド電位)とされている。

【0024】

半導体チップ2は、半導体基板4の表面に形成された配線層5の最表面を樹脂層6で封止したチップサイズパッケージ型の構成を有している。したがって、半導体チップ2は、それ自体の大きさが小さく、この小さな半導体チップ2をフリップチップ接合によって実装基板3に接合しているので、半導体装置1は、全体として、小型に構成することができる。さらに、実装基板3の実装面21に形成されたランドパターンを利用して検出電極20が形成されているので、検出電極20を保持するための別の部材を設ける必要がない。これによって、構成が簡単になっており、それに応じて、小型化が図られている。

【0025】

さらに、検出電極20に対するノイズの影響を排除するためのシールドが、実装基板3のランドパターンを利用したシールドパターン膜26と、半導体チップ2の配線層5に形成したシールド膜9と、シールド膜9とシールドパターン膜26とを電気的に接続する複数の第1突起電極15とで構成されている。したがって、シールドを構成するための特別の部材を必要としないので、構成が簡単になり、それに応じて小型化を図ることができる。

【0026】

さらにまた、信号処理回路11と検出電極20との間の電気的接続は、配線層5および第2突起電極16によって達成されており、長い配線ケーブルを用いていない。そのため、構成が簡単であり、かつ、信号経路に対するノイズの侵入を効果的に抑制することができる。これにより、簡単で、かつ小型の構成によって、静電容量を正確に検出することができる。

【0027】

より具体的には、検出電極20に対して検出対象が接近したときに、検出電極20と当該検出対象との間に形成されるコンデンサの容量が正確に検出される。さらに具体的には、検出対象が検出電極20に対して接近する前と、検出対象が検出電極20に接近した後との容量変化を、正確に検出することができる。これによって、静電容量型の近接センサを提供することができる。

【0028】

また、この実施形態では、検出電極20が、第1検出電極23と第2検出電極24とに分割されている。そこで、たとえば、第1および第2検出電極23,24の出力信号を用いてバックグラウンドノイズをキャンセルしたりする処理を信号処理回路11において行うことができる。これにより、静電容量を一層正確に検出できる。

図8に比較例を示すように、リードフレーム31の表面に半導体チップ32を搭載し、ボンディングワイヤ33によってリードフレーム31と半導体チップ32とを電気的に接続する構成の半導体装置が考えられる。リードフレーム31の一部、半導体チップ32およびボンディングワイヤ33は、モールド樹脂34によって封止されている。この構成において、半導体チップ32の表面の配線層を利用して検出電極35を形成することが考えられるかもしれない。しかし、この比較例に係る構成では、ボンディングワイヤ33およびリードフレーム31と検出電極35との間にそれぞれ容量が形成されるから、検出電極35が検出する容量は、ボンディングワイヤ33およびリードフレーム31の電位変化の影響を受ける。したがって、誤検出が生じるおそれがある。さらにまた、検出電極35が検出する容量は、モールド樹脂34の比誘電率の影響を受ける。ところが、モールド樹脂34の比誘電率は、温度に応じて変化するから、モールド樹脂34の温度が変化すれば、誤検出が生じるおそれがある。

【0029】

前述第1の実施形態の構成は、このような問題をも解決し、精度の高い静電容量検出機能を提供する。

図3は、携帯型の電子機器の一例であるスマートフォンに対して前述の半導体装置1を適用した構造を示す模式的な断面図である。スマートフォン40は、金属製の筐体41と、タッチパネル42と、半導体装置1と、演算処理部45(演算回路)とを備えている。筐体41においてタッチパネル42を指示している部分に開口41aが形成されており、この開口41aに半導体チップ2が配置されている。タッチパネル42には、光学窓43が設けられている。この光学窓43の背後に、検出電極20および照度センサ部12を対向させて、半導体装置1が配置されている。光学窓43に対応する部分においては、半導体チップ2の樹脂層6に開口が形成されている。半導体装置1を構成する実装基板3は、この例では、フレキシブルプリント配線基板からなる。この実装基板3は、たとえば、タッチパネル42との電気的接続のためのランドと、演算処理部45との電気的接続のためのランドと、タッチパネル42、演算処理部45および半導体装置1の間の電気的接続を担う配線パターンとを有している。

【0030】

筐体41が金属製であるので、検出電極20は、筐体41との間においても容量を形成する。しかし、半導体装置1は、信号処理回路11と検出電極20との間を極めて短い配線長で接続した構成を有しており、しかも、検出電極20の周囲に設けられたシールドを一体的に有している。これにより、金属製の筐体41による静電容量検出に対する影響を最小限にすることができる。よって、金属製の筐体41を有するスマートフォン40に搭載された場合であっても、半導体装置1は、すぐれた静電容量検出機能を提供することができる。しかも、半導体装置1は、それ自体が小型に構成されているので、小さな筐体41の内部に容易に収容することができる。これにより、筐体41の小型化や、筐体41に別の機能部品を収容することによる多機能化に寄与することができる。

【0031】

半導体装置1は、演算処理部45に対して、検出対象物が接近しているかどうかを表す信号を供給する。これに応じて、演算処理部45は、たとえば、タッチパネル42を背後から照明するためのバックライトをオン/オフ制御する。より具体的には、スマートフォン40の使用者がスマートフォン40を耳に押し当てたときに、半導体装置1は検出対象の接近を表す信号を演算処理部45に供給する。これに応答して、演算処理部45はバックライト消灯する。こうして、消費電力を低減することができる。半導体装置1が検出対象の接近を表す信号を出力おらず、かつ照度センサ部12が検出する照度が所定の消灯基準照度を超えていれば、演算処理部40は、バックライトを点灯してタッチパネル42を背後から照明する。バックライトの駆動電力は、照度センサ部12が検出する照度に応じて可変制御されてもよい。

【0032】

図4は、この発明の第2の実施形態に係る半導体装置の構成を説明するための図解的な断面図である。また、図5は、図4に示された半導体装置の平面図である。図4の断面図は、図5の線IV-IVに対応している。これらの図4および図5において、前述の図1および図2に示された各部に対応する部分には、同一の参照符を付して示す。

この半導体装置51においては、実装基板3の非実装面22に検出電極52が設けられている。さらに、非実装面22に、検出電極52を取り囲むようにシールドパターン膜56が設けられている。検出電極52およびシールドパターン膜56は、いずれも、実装基板3の非実装面22に形成されたランドパターンを利用して構成されている。信号処理回路11に接続された第2突起電極16は、実装基板3の実装面21に形成されたランド57に接続されている。ランド57と、検出電極52とは、実装基板3の実装面21および非実装面22の間を貫通する貫通ビア58によって、電気的に互いに接続されている。検出電極52は、第1検出電極53と、第2検出電極54とを含む。第1検出電極53は、第2検出電極54よりも大きな面積を有している。より具体的には、第1検出電極53は、ほぼ矩形形状を有しており、その一辺が中心に向かって帯状に切り欠かれている。この切り欠かれた領域に、帯状の第2検出電極54が配置されている。第2検出電極54の長手方向途中位置に照度センサ部12のための検出窓25が位置している。第1検出電極53は、貫通ビア58Aによって、ランド57に接続されており、さらに信号経路17Aを介して信号処理回路11に接続されている。第2検出電極54は、別の貫通ビア58Bによって、実装面21に形成された別のランドに接続されており、当該別のランドが、一つの第2突起電極16Bに接続されている。この第2突起電極16Bは、シールド膜9に形成された別の開口(図示せず)をシールド膜9から絶縁された状態で貫通する信号経路17Bを介して、信号処理回路11に接続されている。

【0033】

半導体チップ2内のシールド膜9に接続された第1突起電極15は、実装基板3の実装面21に形成されたランド59に接合されている。ランド59は、検出電極用のランド57の周囲を取り囲むように形成されていて、実装基板3を挟んでシールドパターン膜56と対向する位置まで延びて形成されている。ランド59は、実装基板3の実装面21および非実装面22の間を貫通する貫通ビア60によって、シールドパターン膜56に電気的に接続されている。シールドパターン膜56は、環状に形成された無端の帯状パターンに形成されている。このシールドパターン膜56に囲まれた領域には、検出電極52が配置されているほか、照度センサ部12のための検出窓25が配置されている。検出窓25は、実装基板3の実装面21および非実装面22の間を貫通して形成された貫通孔である。シールドパターン膜56に対応したランド59は、検出電極52を実装面21側から覆うパターンに形成されていて、非実装面22側からのノイズの侵入を抑制する。

【0034】

このように、この実施形態の構成によれば、検出電極52が実装基板3の非実装面22に形成されているので、検出電極52の設計に際して、半導体チップ2との電気的接続に伴う制限が少ない。そのため、検出電極52を、半導体チップ2よりも大きく形成することができる。これによって、検出感度を高めることができ、より遠くの検出対象の接近を検出できる。さらにまた、検出電極52の背後には、実装基板3の実装面21に配置したランド59が位置していて、このランド59が、シールド膜9に電気的に接続されている。それによって、検出電極52に対する実装面21側からのノイズの侵入を抑制することができる。こうして、静電容量検出精度をより一層高めることができる。

【0035】

また、この実施形態においても、検出電極52が、第1検出電極53と第2検出電極54とに分割されている。そこで、たとえば、第1および第2検出電極53,54の出力信号を用いてバックグラウンドノイズをキャンセルしたりする処理を信号処理回路11において行うことができる。これにより、静電容量を一層正確に検出できる。

図6は、この発明の第3の実施形態に係る半導体装置の構成を説明するための模式的な断面図である。また、図7は、図6に示された半導体装置の半導体チップ2の平面図である。図6の断面図は、図7の線VI-VIに対応している。これらの図6および図7において、前述の図1および図2に示された各部に対応する部分には、同一の参照符号を付して示す。

【0036】

この半導体装置71においては、半導体チップ2の配線層5内の金属膜(たとえばアルミニウム膜またはアルミニウム合金膜)によって検出電極72が形成されている。したがって、半導体チップ2には、検出電極のための突起電極は設けられていない。実装基板3の実装面21には、平面視において検出電極72を取り囲むように、ランドパターンを利用したシールドパターン膜73が形成されている。シールドパターン膜73は、突起電極15によって、半導体チップ2の配線層5に形成されたシールド膜9と電気的に接続されている。この実施形態では、検出電極72に対するシールドが、シールド膜9、突起電極15およびシールドパターン膜73によって構成されている。

【0037】

このような構成によっても、簡単でかつ小型の構成により、精度の高い静電容量検出が可能になる。

なお、検出電極72は、図6に示すように樹脂層6によって覆われていてもよいし、樹脂層6から露出していてもよい。また、配線層5に検出電極72を形成するのではなく、樹脂層6の表面に検出電極を形成してもよい。この場合の検出電極は、たとえば銅膜からなっていてもよい。

【0038】

以上、この発明のいくつかの実施形態について説明したが、この発明はさらに他の形態で実施することができる。たとえば、前述の実施形態では、シールドパターン膜26,56,73がいずれも無端状の環状である例を示したが、検出電極を取り囲むシールドパターン膜は、途中に僅かな切れ目があってもよい。その場合でも、その切れ目の部分の電位は、シールドパターン膜と等しくなるので、外部からのノイズを遮蔽できる。

【0039】

また、前述の実施形態においては、静電容量検出機能付きの半導体装置をスマートフォンに適用した例を説明したが、むろん、半導体装置の用途はこれに限られるわけではない。たとえば、テレビやディスプレイ等の電気機器のためのタッチスイッチとしても、この発明に係る半導体装置を利用することができる。

また、前述の第1および第2実施形態では、シールドパターン膜に囲まれた領域に照度センサ部12が配置されているが、シールドパターン膜に囲まれた領域の外側に照度センサ部12が配置されてもよい。

【0040】

さらに、前述の第1および第2の実施形態では、半導体チップに照度センサ部12が組み込まれた構成を示したが、照度センサ部12は省かれてもよい。また、照度センサ部以外の別の機能部分を半導体チップに搭載してもよい。また、前述の第1および第2実施形態では、照度センサ部12が半導体基板2内に形成されている例を示したが、配線層5内に照度センサ部が形成されていてもよい。

【0041】

また、前述の第1および第2の実施形態では、検出電極が2つの部分に分割されている例を示したが、むろん、検出電極が3つ以上の部分に分割されていてもよい。

その他、特許請求の範囲に記載された事項の範囲で種々の設計変更を施すことが可能である。

【符号の説明】

【0042】

1 半導体装置

2 半導体チップ

3 実装基板

4 半導体基板

5 配線層

6 樹脂層

7 突起電極

8 内部回路

9 シールド膜

11 信号処理回路

12 照度センサ部

15 第1突起電極

16,16B 第2突起電極

17,17A,17B 信号経路

20 検出電極

21 実装面

22 非実装面

23 第1検出電極

24 第2検出電極

25 検出窓

26 シールドパターン膜

40 スマートフォン

41 金属製の筐体

42 タッチパネル

43 光学窓

45 演算処理部

51 半導体装置

52 検出電極

53 第1検出電極

54 第2検出電極

56 シールドパターン膜

57 ランド

58,58A,58B 貫通ビア

59 ランド

60 貫通ビア

71 半導体装置

72 検出電極

73 シールドパターン膜

【特許請求の範囲】

【請求項1】

内部回路を構成する素子が作り込まれた半導体基板と、前記半導体基板の表面を封止する樹脂と、前記樹脂の表面から突出し、前記内部回路に電気的に接続された突起電極とを有するチップサイズパッケージ型半導体チップと、

前記半導体チップの前記樹脂の表面に対向して配置され、前記突起電極に電気的および機械的に接続されるランドを有し、前記半導体チップがフリップチップ接合によって実装される実装面を有する実装基板と、

検出対象物との間の静電容量を検出するための検出電極と、

前記検出電極を取り囲むシールドとを含み、

前記検出電極が前記半導体チップまたは前記実装基板に設けられており、

前記シールドの少なくとも一部が前記実装基板に設けられている、半導体装置。

【請求項2】

前記検出電極が、前記実装基板の前記実装面に形成されている、請求項1に記載の半導体装置。

【請求項3】

前記検出電極が、前記実装基板の前記実装面とは反対側の非実装面に形成されている、請求項1に記載の半導体装置。

【請求項4】

前記検出電極が、前記半導体チップに設けられている、請求項1に記載の半導体装置。

【請求項5】

前記シールドは、前記実装基板に前記電極を取り囲むように形成されたシールドパターン膜を含む、請求項1〜4のいずれか一項に記載の半導体装置。

【請求項6】

前記シールドパターン膜が前記実装面に形成されている、請求項5に記載の半導体装置。

【請求項7】

前記シールドパターン膜が、前記実装基板の前記実装面とは反対側の非実装面に形成されている、請求項5に記載の半導体装置。

【請求項8】

前記突起電極は、前記検出電極を取り囲むように配置され、前記シールドパターン膜に接続されたシールド用突起電極を含む、請求項5〜7のいずれか一項に記載の半導体装置。

【請求項9】

前記半導体チップは、前記半導体基板の表面に形成された配線層を含み、

前記シールドは、前記配線層に形成されたシールド膜を含む、請求項1〜8のいずれか一項に記載の半導体装置。

【請求項10】

前記検出電極が、複数の部分に分割されている、請求項1〜9のいずれか一項に記載の半導体装置。

【請求項11】

請求項1〜10のいずれか一項に記載の半導体装置と、

前記半導体装置と接続された演算回路とを含む、電子機器。

【請求項12】

前記電子機器が金属製の筐体を含む、請求項11に記載の電子機器。

【請求項1】

内部回路を構成する素子が作り込まれた半導体基板と、前記半導体基板の表面を封止する樹脂と、前記樹脂の表面から突出し、前記内部回路に電気的に接続された突起電極とを有するチップサイズパッケージ型半導体チップと、

前記半導体チップの前記樹脂の表面に対向して配置され、前記突起電極に電気的および機械的に接続されるランドを有し、前記半導体チップがフリップチップ接合によって実装される実装面を有する実装基板と、

検出対象物との間の静電容量を検出するための検出電極と、

前記検出電極を取り囲むシールドとを含み、

前記検出電極が前記半導体チップまたは前記実装基板に設けられており、

前記シールドの少なくとも一部が前記実装基板に設けられている、半導体装置。

【請求項2】

前記検出電極が、前記実装基板の前記実装面に形成されている、請求項1に記載の半導体装置。

【請求項3】

前記検出電極が、前記実装基板の前記実装面とは反対側の非実装面に形成されている、請求項1に記載の半導体装置。

【請求項4】

前記検出電極が、前記半導体チップに設けられている、請求項1に記載の半導体装置。

【請求項5】

前記シールドは、前記実装基板に前記電極を取り囲むように形成されたシールドパターン膜を含む、請求項1〜4のいずれか一項に記載の半導体装置。

【請求項6】

前記シールドパターン膜が前記実装面に形成されている、請求項5に記載の半導体装置。

【請求項7】

前記シールドパターン膜が、前記実装基板の前記実装面とは反対側の非実装面に形成されている、請求項5に記載の半導体装置。

【請求項8】

前記突起電極は、前記検出電極を取り囲むように配置され、前記シールドパターン膜に接続されたシールド用突起電極を含む、請求項5〜7のいずれか一項に記載の半導体装置。

【請求項9】

前記半導体チップは、前記半導体基板の表面に形成された配線層を含み、

前記シールドは、前記配線層に形成されたシールド膜を含む、請求項1〜8のいずれか一項に記載の半導体装置。

【請求項10】

前記検出電極が、複数の部分に分割されている、請求項1〜9のいずれか一項に記載の半導体装置。

【請求項11】

請求項1〜10のいずれか一項に記載の半導体装置と、

前記半導体装置と接続された演算回路とを含む、電子機器。

【請求項12】

前記電子機器が金属製の筐体を含む、請求項11に記載の電子機器。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【公開番号】特開2013−105650(P2013−105650A)

【公開日】平成25年5月30日(2013.5.30)

【国際特許分類】

【出願番号】特願2011−249518(P2011−249518)

【出願日】平成23年11月15日(2011.11.15)

【出願人】(000116024)ローム株式会社 (3,539)

【Fターム(参考)】

【公開日】平成25年5月30日(2013.5.30)

【国際特許分類】

【出願日】平成23年11月15日(2011.11.15)

【出願人】(000116024)ローム株式会社 (3,539)

【Fターム(参考)】

[ Back to top ]