半導体装置および半導体システム

【課題】定電流のトリミングをより容易にすることが可能な半導体装置を提供する。

【解決手段】半導体装置の制御回路は、マルチプレクサに第2のデータをトリミングデータとして出力させる状態で、第2のデータを変化させることにより定電流を段階的に変化するように設定し、比較結果信号の論理が反転した時に対応する第2のデータを抽出し、この抽出した第2のデータを記憶回路に第1のデータとして記憶させる。

【解決手段】半導体装置の制御回路は、マルチプレクサに第2のデータをトリミングデータとして出力させる状態で、第2のデータを変化させることにより定電流を段階的に変化するように設定し、比較結果信号の論理が反転した時に対応する第2のデータを抽出し、この抽出した第2のデータを記憶回路に第1のデータとして記憶させる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、定電流をトリミングする半導体装置および半導体システムに関する。

【背景技術】

【0002】

従来、半導体装置においては歩留まり向上等のために、トリミングが採用される。このトリミングは、通常、ダイソータ時に各チップの値をテスタにて測定する。そして、得られた測定値が、ターゲット値から外れている場合、このターゲット値になる様に設定が行われる。

【0003】

近年、テストコスト削減のために、多数のチップを同時にダイソートすることが行われている。しかし、トリミングの補正値はチップ毎に異なる。このため、トリミング設定については、同時設定が困難となる。

【0004】

特に、電流の測定は時間が掛かるため、テスト時間の増大に繋がる。そこで、トリミングをBIST(Built−in Self−Test)の様な形で行うことが求められている。

【0005】

ここで、従来の半導体集積回路では、例えば、CPUとフラッシュメモリを有する半導体集積回路の外部の評価装置から期待値の電圧(Vref)を複数の半導体集積回路に並列的に与える。半導体集積回路の内部には、この期待値電圧と内部で発生する昇圧電圧とを比較する比較回路を内蔵する。CPUがその比較結果を参照しながら、昇圧電圧値を変更するデータレジスタの制御データを最適に設定していく。上記の比較回路やデータレジスタを内蔵CPUで制御し、トリミングを自己完結で行うため、複数の半導体集積回路に対する並列的なトリミングが容易であり、全体としてのテスト時間を短縮できる(例えば、特許文献1参照。)。

しかし、上記従来の半導体集積回路は、期待値の電圧(Vref)を用いたトリミングのBISTである。すなわち、期待値に対応する電流によるトリミングのBISTではない。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2002−318265号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

本発明は、定電流のトリミングをより容易にすることが可能な半導体装置を提供することを目的とする。

【課題を解決するための手段】

【0008】

本発明の一態様に係る半導体装置は、ターゲット電流が印加されるパッドと、前記パッドと接地との間に接続された第1のMOSトランジスタと、電源に一端が接続された第1の抵抗素子と、前記第1の抵抗素子の他端と前記接地との間に接続され、前記第1のMOSトランジスタに流れる前記ターゲット電流をカレントミラーした第1の電流が流れる第2のMOSトランジスタと、トリミングデータに対応した定電流を出力する定電流回路と、前記電源に一端が接続され、前記第1の抵抗素子と同じ抵抗値を有する第2の抵抗素子と、前記第2の抵抗素子の他端と前記接地との間に接続され、前記第2のMOSトランジスタと同じサイズを有し、前記定電流回路が出力する前記定電流に対応する第2の電流が流れる第3のMOSトランジスタと、前記第1の抵抗素子と前記第2のMOSトランジスタとの間の第1の電圧と、前記第2の抵抗素子と前記第3のMOSトランジスタとの間の第2の電圧とを比較し、前記第1の電圧と前記第2の電圧の大小関係に応じて論理が異なる比較結果信号を出力するコンパレータと、第1のデータを記憶する記憶回路と、前記比較結果信号が入力され、且つ、設定した第2のデータを出力する制御回路と、前記記憶回路に記憶された前記第1のデータが入力されるとともに前記制御回路から出力された第2のデータが入力され、前記制御回路か出力された選択信号に応じて選択した前記第1のデータまたは前記第2のデータの何れか一方を前記トリミングデータとして前記定電流回路に出力するマルチプレクサと、を備え、前記制御回路は、前記マルチプレクサが前記第2のデータを選択し前記トリミングデータとして出力する状態で、前記第2のデータを変化させることにより前記定電流を段階的に変化するように設定し、前記比較結果信号の論理が反転した時に対応する前記第2のデータを抽出し、抽出した前記第2のデータを前記記憶回路に前記第1のデータとして記憶させ、前記第2の電流の値は、設定された第2のデータに対応する定電流の値に、この設定された前記第2のデータに対応する前記定電流を次に設定される第2のデータに対応する定電流の値から引いた電流値差の2分の1を、加算した値であることを特徴とする。

【0009】

本発明の一態様に係る半導体システムは、ターゲット電流が印加されるパッドと、前記パッドと接地との間に接続された第1のMOSトランジスタと、電源に一端が接続された第1の抵抗素子と、前記第1の抵抗素子の他端と前記接地との間に接続され、前記第1のMOSトランジスタに流れる前記ターゲット電流をカレントミラーした第1の電流が流れる第2のMOSトランジスタと、トリミングデータに対応した定電流を出力する定電流回路と、前記電源に一端が接続され、前記第1の抵抗素子と同じ抵抗値を有する第2の抵抗素子と、前記第2の抵抗素子の他端と前記接地との間に接続され、前記第2のMOSトランジスタと同じサイズを有し、前記定電流回路が出力する前記定電流に対応する第2の電流が流れる第3のMOSトランジスタと、前記第1の抵抗素子と前記第2のMOSトランジスタとの間の第1の電圧と、前記第2の抵抗素子と前記第3のMOSトランジスタとの間の第2の電圧とを比較し、前記第1の電圧と前記第2の電圧の大小関係に応じて論理が異なる比較結果信号を出力するコンパレータと、第1のデータを記憶する記憶回路と、前記比較結果信号が入力され、且つ、設定した第2のデータを出力する制御回路と、前記記憶回路に記憶された前記第1のデータが入力されるとともに前記制御回路から出力された第2のデータが入力され、前記制御回路か出力された選択信号に応じて選択した前記第1のデータまたは前記第2のデータの何れか一方を前記トリミングデータとして前記定電流回路に出力するマルチプレクサと、を有し、前記制御回路は、前記マルチプレクサが前記第2のデータを選択し前記トリミングデータとして出力する状態で、前記第2のデータを変化させることにより前記定電流を段階的に変化するように設定し、前記比較結果信号の論理が反転した時に対応する前記第2のデータを抽出し、抽出した前記第2のデータを前記記憶回路に前記第1のデータとして記憶させ、前記第2の電流の値は、設定された第2のデータに対応する定電流の値に、この設定された前記第2のデータに対応する前記定電流を次に設定される第2のデータに対応する定電流の値から引いた電流値差の2分の1を、加算した値である複数の半導体装置と、前記ターゲット電流をそれぞれの前記半導体装置に順次印加して前記制御回路に前記第2のデータを抽出させ、全ての前記半導体装置の前記制御回路が抽出した前記第2のデータを前記記憶回路に前記第1のデータとして各々同時に記憶させた後、同時に全ての前記半導体装置の前記ベリファイ回路にベリファイさせるテスト装置と、を備えることを特徴とする。

【0010】

本発明の他の態様に係る半導体システムは、ターゲット電流が印加されるパッドと、前記パッドと接地との間に接続された第1のMOSトランジスタと、電源に一端が接続された第1の抵抗素子と、前記第1の抵抗素子の他端と前記接地との間に接続され、前記第1のMOSトランジスタに流れる前記ターゲット電流をカレントミラーした第1の電流が流れる第2のMOSトランジスタと、トリミングデータに対応した定電流を出力する定電流回路と、前記電源に一端が接続され、前記第1の抵抗素子と同じ抵抗値を有する第2の抵抗素子と、前記第2の抵抗素子の他端と前記接地との間に接続され、前記第2のMOSトランジスタと同じサイズを有し、前記定電流回路が出力する前記定電流に対応する第2の電流が流れる第3のMOSトランジスタと、前記第1の抵抗素子と前記第2のMOSトランジスタとの間の第1の電圧と、前記第2の抵抗素子と前記第3のMOSトランジスタとの間の第2の電圧とを比較し、前記第1の電圧と前記第2の電圧の大小関係に応じて論理が異なる比較結果信号を出力するコンパレータと、第1のデータを記憶する記憶回路と、前記比較結果信号が入力され、且つ、設定した第2のデータを出力する制御回路と、前記記憶回路に記憶された前記第1のデータが入力されるとともに前記制御回路から出力された第2のデータが入力され、前記制御回路か出力された選択信号に応じて選択した前記第1のデータまたは前記第2のデータの何れか一方を前記トリミングデータとして前記定電流回路に出力するマルチプレクサと、を有し、前記制御回路は、前記マルチプレクサが前記第2のデータを選択し前記トリミングデータとして出力する状態で、前記第2のデータを変化させることにより前記定電流を段階的に変化するように設定し、前記比較結果信号の論理が反転した時に対応する前記第2のデータを抽出し、抽出した前記第2のデータを前記記憶回路に前記第1のデータとして記憶させ、前記第2の電流の値は、設定された第2のデータに対応する定電流の値に、この設定された前記第2のデータに対応する前記定電流を次に設定される第2のデータに対応する定電流の値から引いた電流値差の2分の1を、加算した値である複数の半導体装置と、前記ターゲット電流をそれぞれの前記半導体装置に同時に印加し、全ての前記半導体装置の前記制御回路が抽出した前記第2のデータを前記記憶回路に前記第1のデータとして記憶させた後、同時に全ての前記半導体装置の前記ベリファイ回路にベリファイさせるテスト装置と、を備えることを特徴とする。

【発明の効果】

【0011】

本発明の一態様に係る半導体装置によれば、定電流のトリミングをより容易にすることができる。

【図面の簡単な説明】

【0012】

【図1】本発明の一態様である実施例1に係る半導体装置100を含む半導体システム1000の構成の一例を示す図である。

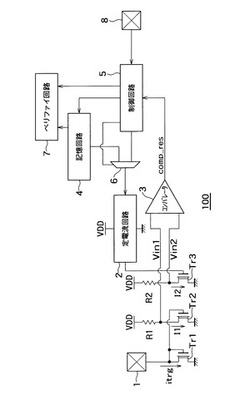

【図2】図1に示す半導体装置100の構成の一例を示す図である。

【図3】図2に示す半導体装置100のトリミングデータを生成する動作の一例を示すタイミングチャートである。

【図4】図2に示す半導体装置100のトリミングデータを生成する動作の他の例を示すタイミングチャートである。

【図5】図1に示す半導体システム1000が電流トリミングする場合のシーケンスの一例を示す図である。

【図6】図1に示す半導体システム1000が電流トリミングする場合のシーケンスの他の例を示す図である。

【発明を実施するための形態】

【0013】

以下、本発明を適用した各実施例について図面を参照しながら説明する。

【実施例1】

【0014】

図1は、本発明の一態様である実施例1に係る半導体装置100を含む半導体システム1000の構成の一例を示す図である。

【0015】

図1に示すように、半導体システム1000は、テスト装置1001と、基板1002とを備える。

【0016】

基板1002には、複数の半導体装置(チップ)100が配置されている。

【0017】

テスト装置1001は、半導体装置100にターゲット電流itrgを供給し、また、半導体装置100の動作を制御するための制御信号を半導体装置100に出力するようになっている。

【0018】

ここで、図2は、図1に示す半導体装置100の構成の一例を示す図である。

【0019】

図2に示すように、半導体装置100は、第1のパッド1と、定電流回路2と、コンパレータ3と、記憶回路4と、制御回路5と、マルチプレクサ6と、ベリファイ回路7と、第2のパッド8と、第1のMOSトランジスタTr1と、第2のMOSトランジスタTr2と、第3のMOSトランジスタTr3と、第1の抵抗素子R1と、第2の抵抗素子R2と、を備える。

【0020】

第1のパッド1は、テスト装置1001からターゲット電流itrgが印加されるようになっている。

【0021】

第1のMOSトランジスタTr1は、第1のパッド1と接地との間に接続されている。この第1のMOSトランジスタTr1は、ダイオード接続されている。

第1の抵抗素子R1は、電源VDDに一端が接続されている。

【0022】

第2のMOSトランジスタTr2は、第1の抵抗素子R1の他端と接地との間に接続され、第1のMOSトランジスタTr1のゲートにゲートが接続されている。すなわち、第1のMOSトランジスタTr1と第2のMOSトランジスタTr2とは、ミラー回路を構成する。

【0023】

これにより、この第2のMOSトランジスタTr2は、第1のMOSトランジスタTr2に流れるターゲット電流itrgをカレントミラーした第1の電流I1が流れるようになっている。

【0024】

ここでは、例えば、第1のMOSトランジスタTr1のサイズと第2のMOSトランジスタTr2のサイズとが等しく設定されている。この場合、ターゲット電流itrgと第1の電流I1とは、等しくなる。

【0025】

定電流回路2は、電源VDDと接地との間に接続されており、トリミングデータに対応した定電流Iregを出力するようになっている。

【0026】

第2の抵抗素子R2は、電源VDDに一端が接続されている。この第2の抵抗素子R2は、ここでは、例えば、第1の抵抗素子R1と同じ抵抗値を有する。

【0027】

第3のMOSトランジスタTr3は、第2の抵抗素子R2の他端と接地との間に接続されている。この第3のMOSトランジスタTr3は、第2のMOSトランジスタTr2と同じサイズを有する。この第3のMOSトランジスタTr3は、定電流回路2が出力する定電流Iregに対応する第2の電流I2が流れるようになっている。

【0028】

この第2の電流I2の値は、設定された第2のデータに対応する定電流Iregの値に、この設定された第2のデータに対応する定電流Iregを次に設定される第2のデータに対応する定電流Iregの値から引いた電流値差の2分の1を、加算した値である。

【0029】

コンパレータ3は、第1の抵抗素子R1と第2のMOSトランジスタTr2との間の第1の電圧Vin1と、第2の抵抗素子R2と第3のMOSトランジスタTr3との間の第2の電圧Vin2とを比較する。そして、コンパレータ3は、第1の電圧Vin1と第2の電圧Vin2の大小関係に応じて論理(レベル)が異なる比較結果信号comp_resを、出力するようになっている。

【0030】

ここで、第1の電圧Vin1は、第1の抵抗素子R1および第2のMOSトランジスタTr2に流れる第1の電流I1に応じた電圧降下により決定される。さらに、第2の電圧Vin2は、第2抵抗素子R2および第3のMOSトランジスタTr3に流れる第2の電流I2に応じた電圧降下により決定される。

【0031】

したがって、第1の電圧Vin1と第2の電圧Vin2とをコンパレータ3で比較することにより、第1の電流I1と第2の電流I2との大小関係を調べることができる。すなわち、第1の電流I1とターゲット電流itrgとの関係および第2の電流I2と定電流iregとの関係から、第1の電圧Vin1と第2の電圧Vin2とをコンパレータ3で比較することにより、ターゲット電流itrgと定電流iregとの大小関係を調べることができる。

【0032】

記憶回路4は、第1のデータ(ヒューズデータ)を記憶するようになっている。この記憶回路4は、例えば、ヒューズ素子や、NAND型フラッシュメモリ等の不揮発性メモリである。

【0033】

制御回路5は、比較結果信号comp_resがコンパレータ3から入力されるようになっている。また、制御回路5は、テスト装置1001から第2のパッド8を介して外部信号が入力されるようになっている。さらに、制御回路5は、設定した第2のデータをマルチプレクサ6に出力するようになっている。

【0034】

また、制御回路5は、マルチプレクサ6に選択信号を出力することにより、マルチプレクサ6に入力されたデータを切り換えて出力させるようになっている。

【0035】

また、制御回路5は、該外部信号に応じて、ベリファイ動作の指令をベリファイ回路7に出力するとともに、抽出された第2のデータをベリファイ回路7に出力するようになっている。

【0036】

マルチプレクサ6は、記憶回路4に記憶された第1のデータが入力されるとともに制御回路5から出力された第2のデータが入力されるようになっている。そして、マルチプレクサ6は、制御回路5から出力された選択信号に応じて選択した該第1のデータまたは該第2のデータの何れか一方を、該トリミングデータとして定電流回路2に出力するようになっている。

【0037】

ベリファイ回路7は、テスト装置1001から出力された該外部信号に応じて、記憶回路4に記憶された第1のデータを読み出す。そして、ベリファイ回路7は、読み出された第1のデータを制御回路5で抽出された第2のデータでベリファイし、このベリファイに応じたベリファイ信号を出力するようになっている。

【0038】

次に、以上のような構成を有する半導体システム1000の動作の一例について説明する。

【0039】

図3は、図2に示す半導体装置100のトリミングデータを生成する動作の一例を示すタイミングチャートである。

【0040】

トリミングデータを生成するために、制御回路5は、該選択信号によりマルチプレクサ6が第2のデータを選択しトリミングデータとして出力する状態にする。

【0041】

そして、制御回路5は、この状態で、第2のデータを変化(TAP0〜TAP3)させることにより、トリミングデータ(TAP0〜TAP3)を変化させて、定電流Iregを段階的に変化(ここでは増加)するように設定する。

【0042】

例えば、トリミングデータ(第2のデータ)TAP0、TAP1の時、コンパレータ3は、トリミングデータTAP0、TAP1に対応する第2の電流I2とターゲット電流itrgの比較を行う。このとき、第2の電流I2はターゲット電流itrgより小さいため、コンパレータ3から出力される比較結果信号comp_resは、“Low”レベルとなる。

【0043】

そして、トリミングデータ(第2のデータ)TAP2の時、コンパレータ3は、トリミングデータTAP2に対応する第2の電流I2とターゲット電流itrgの比較を行う。このとき、第2の電流I2はターゲット電流itrgより大きいため、コンパレータ3から出力される比較結果信号comp_resは、“High”レベルとなる。

【0044】

このとき、制御回路5は、第2のデータTAP2を抽出する。すなわち、制御回路5は、コンパレータ3から出力された比較結果信号comp_resの論理が反転した時に対応する第2のデータTAP2を抽出する。

【0045】

そして、制御回路5は、この抽出した第2のデータTAP2を記憶回路4に第1のデータ(最終的に調整されたトリミングデータ)として記憶させる。

【0046】

ここで、既述のように、第2の電流I2の値は、設定された第2のデータ(例えば、TAP0)に対応する定電流Iregの値に、この設定された第2のデータ(TAP0)に対応する該定電流Iregを次に設定される第2のデータ(TAP1)に対応する定電流Iregの値から引いた電流値差ΔIの2分の1を、加算した値である。他の第2のデータに対応する第2の電流I2も同様の関係である。

【0047】

したがって、図3に示すように、抽出された第2のデータTAP2に対応する定電流iregは、ターゲット電流itrgに一番近くなる。この抽出された第2のデータTAP2は、書き込みコマンドに応じて、制御回路5により、記憶回路4に第1のデータ(最終的に調整されたトリミングデータ)として記憶される。

【0048】

この図3に示す動作は、図1に示すテスト装置1001により、各半導体装置(チップ)100に対して実施される。

【0049】

なお、図3では、定電流Iregを段階的に増加するように設定しているが、定電流Iregを段階的に減少するように設定してもよい。

【0050】

また、図4は、図2に示す半導体装置100のトリミングデータを生成する動作の他の例を示すタイミングチャートである。

【0051】

トリミングデータで生成するために、制御回路5は、該選択信号によりマルチプレクサ6が第2のデータを選択しトリミングデータとして出力する状態にする。

【0052】

そして、制御回路5は、この状態で、第2のデータを変化(TAP0〜TAP3)させることにより、トリミングデータ(TAP0〜TAP3)を変化させて、定電流Iregを段階的に変化(ここでは増加)するように設定する。

【0053】

例えば、トリミングデータ(第2のデータ)TAP0の時、コンパレータ3は、トリミングデータTAP0に対応する第2の電流I2とターゲット電流itrgの比較を行う。このとき、第2の電流I2はターゲット電流itrgより小さいため、コンパレータ3から出力される比較結果信号comp_resは、“Low”レベルとなる。

【0054】

そして、トリミングデータ(第2のデータ)TAP1の時、コンパレータ3は、トリミングデータTAP1に対応する第2の電流I2とターゲット電流itrgの比較を行う。このとき、第2の電流I2はターゲット電流itrgより大きいため、コンパレータ3から出力される比較結果信号comp_resは、“High”レベルとなる。

【0055】

このとき、制御回路5は、第2のデータTAP1を抽出する。すなわち、制御回路5は、コンパレータ3から出力された比較結果信号comp_resの論理が反転した時に対応する第2のデータTAP1を抽出する。

【0056】

そして、制御回路5は、この抽出した第2のデータTAP1を記憶回路4に第1のデータとして記憶させる。

【0057】

ここで、既述のように、第2の電流I2の値は、設定された第2のデータ(例えば、TAP0)に対応する定電流Iregの値に、この設定された第2のデータ(TAP0)に対応する該定電流Iregを次に設定される第2のデータ(TAP1)に対応する定電流Iregの値から引いた電流値差ΔIの2分の1を、加算した値である。他の第2のデータに対応する第2の電流I2も同様の関係である。

【0058】

したがって、図4に示すように、抽出された第2のデータTAP2に対応する定電流iregは、ターゲット電流itrgに一番近くなる。この抽出された第2のデータTAP2は、書き込みコマンドに応じて、制御回路5により、記憶回路4に第1のデータ(最終的に調整されたトリミングデータ)として記憶される。

【0059】

この図4に示す動作は、図1に示すテスト装置1001により、各半導体装置(チップ)100に対して実施される。

【0060】

なお、図4では、定電流Iregを段階的に増加するように設定しているが、定電流Iregを段階的に減少するように設定してもよい。

【0061】

ここで、図5は、図1に示す半導体システム1000が電流トリミングする場合のシーケンスの一例を示す図である。

【0062】

既述のように、電流トリミングの場合、複数の半導体装置(チップ)100にテスト装置1001より同時にターゲット電流を流すことは難しい。この場合、トリミングデータを調整する動作は、半導体装置(チップ)100毎に順次実施する必要がある。

【0063】

しかし、本発明の場合、テスト装置1001からは全半導体装置(チップ)100に対し同一のターゲット電流を設定し、順次トリミングデータを抽出すればよい。

【0064】

これにより、テスト装置1001による測定動作が不要となる。その後、抽出したデータを一度に記憶装置に書き込み/ベリファイを実施することが可能になる。これにより、テスト時間の短縮が可能となる。

【0065】

例えば、図5に示すように、半導体システム1000のテスト装置1001は、ターゲット電流itrgをそれぞれの半導体装置(チップ)100に順次印加して制御回路5に第2のデータを抽出させる。そして、テスト装置1001は、該外部信号により、全ての半導体装置100の制御回路5が抽出した第2のデータを記憶回路4に第1のデータ(最終的に調整されたトリミングデータ)として各々同時に記憶させる。その後、テスト装置1001は、該外部信号により同時に全ての半導体装置100のベリファイ回路7にベリファイさせる。

【0066】

このように、測定単位内の全半導体装置(チップ)100のトリミングデータの生成が終了後は、記憶回路(ヒューズ素子)4への書き込み/データデータについて同時測定の実施が可能となり、テスト時間の短縮が可能となる。

【0067】

一方、仕様により、複数の半導体装置(チップ)100にテスト装置1001より同時にターゲット電流を流すことができる場合がある。この場合、トリミングデータを調整する動作は、半導体装置(チップ)100毎に同時に実施することができる。

【0068】

ここで、図6は、図1に示す半導体システム1000が電流トリミングする場合のシーケンスの他の例を示す図である。

【0069】

図6に示すように、半導体システム1000のテスト装置1001は、ターゲット電流itrgをそれぞれの半導体装置(チップ)100に同時に印加して制御回路5に第2のデータを抽出させる。そして、テスト装置1001は、該外部信号により、全ての半導体装置100の制御回路5が抽出した第2のデータを記憶回路4に第1のデータとして各々同時に記憶させる。その後、テスト回路1001は、該外部信号により同時に全ての半導体装置100のベリファイ回路7にベリファイさせる。

【0070】

このように、測定単位内の全半導体装置(チップ)100のトリミングデータの生成が終了後は、記憶回路(ヒューズ素子)4への書き込み/データデータについて同時測定の実施が可能となり、テスト時間の短縮が可能となる。

【0071】

以上のように、本実施例に係る半導体装置によれば、定電流のトリミングをより容易にすることができる。

【符号の説明】

【0072】

1 第1のパッド、2 定電流回路、3 コンパレータ、4 記憶回路、5 制御回路、6 マルチプレクサ、7 ベリファイ回路、8 第2のパッド、Tr1 第1のMOSトランジスタ、Tr2 第2のMOSトランジスタ、Tr3 第3のMOSトランジスタ、R1 第1の抵抗素子、R2 第2の抵抗素子、100 半導体装置、1000 半導体システム、1001 テスト装置、1002 基板

【技術分野】

【0001】

本発明は、定電流をトリミングする半導体装置および半導体システムに関する。

【背景技術】

【0002】

従来、半導体装置においては歩留まり向上等のために、トリミングが採用される。このトリミングは、通常、ダイソータ時に各チップの値をテスタにて測定する。そして、得られた測定値が、ターゲット値から外れている場合、このターゲット値になる様に設定が行われる。

【0003】

近年、テストコスト削減のために、多数のチップを同時にダイソートすることが行われている。しかし、トリミングの補正値はチップ毎に異なる。このため、トリミング設定については、同時設定が困難となる。

【0004】

特に、電流の測定は時間が掛かるため、テスト時間の増大に繋がる。そこで、トリミングをBIST(Built−in Self−Test)の様な形で行うことが求められている。

【0005】

ここで、従来の半導体集積回路では、例えば、CPUとフラッシュメモリを有する半導体集積回路の外部の評価装置から期待値の電圧(Vref)を複数の半導体集積回路に並列的に与える。半導体集積回路の内部には、この期待値電圧と内部で発生する昇圧電圧とを比較する比較回路を内蔵する。CPUがその比較結果を参照しながら、昇圧電圧値を変更するデータレジスタの制御データを最適に設定していく。上記の比較回路やデータレジスタを内蔵CPUで制御し、トリミングを自己完結で行うため、複数の半導体集積回路に対する並列的なトリミングが容易であり、全体としてのテスト時間を短縮できる(例えば、特許文献1参照。)。

しかし、上記従来の半導体集積回路は、期待値の電圧(Vref)を用いたトリミングのBISTである。すなわち、期待値に対応する電流によるトリミングのBISTではない。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2002−318265号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

本発明は、定電流のトリミングをより容易にすることが可能な半導体装置を提供することを目的とする。

【課題を解決するための手段】

【0008】

本発明の一態様に係る半導体装置は、ターゲット電流が印加されるパッドと、前記パッドと接地との間に接続された第1のMOSトランジスタと、電源に一端が接続された第1の抵抗素子と、前記第1の抵抗素子の他端と前記接地との間に接続され、前記第1のMOSトランジスタに流れる前記ターゲット電流をカレントミラーした第1の電流が流れる第2のMOSトランジスタと、トリミングデータに対応した定電流を出力する定電流回路と、前記電源に一端が接続され、前記第1の抵抗素子と同じ抵抗値を有する第2の抵抗素子と、前記第2の抵抗素子の他端と前記接地との間に接続され、前記第2のMOSトランジスタと同じサイズを有し、前記定電流回路が出力する前記定電流に対応する第2の電流が流れる第3のMOSトランジスタと、前記第1の抵抗素子と前記第2のMOSトランジスタとの間の第1の電圧と、前記第2の抵抗素子と前記第3のMOSトランジスタとの間の第2の電圧とを比較し、前記第1の電圧と前記第2の電圧の大小関係に応じて論理が異なる比較結果信号を出力するコンパレータと、第1のデータを記憶する記憶回路と、前記比較結果信号が入力され、且つ、設定した第2のデータを出力する制御回路と、前記記憶回路に記憶された前記第1のデータが入力されるとともに前記制御回路から出力された第2のデータが入力され、前記制御回路か出力された選択信号に応じて選択した前記第1のデータまたは前記第2のデータの何れか一方を前記トリミングデータとして前記定電流回路に出力するマルチプレクサと、を備え、前記制御回路は、前記マルチプレクサが前記第2のデータを選択し前記トリミングデータとして出力する状態で、前記第2のデータを変化させることにより前記定電流を段階的に変化するように設定し、前記比較結果信号の論理が反転した時に対応する前記第2のデータを抽出し、抽出した前記第2のデータを前記記憶回路に前記第1のデータとして記憶させ、前記第2の電流の値は、設定された第2のデータに対応する定電流の値に、この設定された前記第2のデータに対応する前記定電流を次に設定される第2のデータに対応する定電流の値から引いた電流値差の2分の1を、加算した値であることを特徴とする。

【0009】

本発明の一態様に係る半導体システムは、ターゲット電流が印加されるパッドと、前記パッドと接地との間に接続された第1のMOSトランジスタと、電源に一端が接続された第1の抵抗素子と、前記第1の抵抗素子の他端と前記接地との間に接続され、前記第1のMOSトランジスタに流れる前記ターゲット電流をカレントミラーした第1の電流が流れる第2のMOSトランジスタと、トリミングデータに対応した定電流を出力する定電流回路と、前記電源に一端が接続され、前記第1の抵抗素子と同じ抵抗値を有する第2の抵抗素子と、前記第2の抵抗素子の他端と前記接地との間に接続され、前記第2のMOSトランジスタと同じサイズを有し、前記定電流回路が出力する前記定電流に対応する第2の電流が流れる第3のMOSトランジスタと、前記第1の抵抗素子と前記第2のMOSトランジスタとの間の第1の電圧と、前記第2の抵抗素子と前記第3のMOSトランジスタとの間の第2の電圧とを比較し、前記第1の電圧と前記第2の電圧の大小関係に応じて論理が異なる比較結果信号を出力するコンパレータと、第1のデータを記憶する記憶回路と、前記比較結果信号が入力され、且つ、設定した第2のデータを出力する制御回路と、前記記憶回路に記憶された前記第1のデータが入力されるとともに前記制御回路から出力された第2のデータが入力され、前記制御回路か出力された選択信号に応じて選択した前記第1のデータまたは前記第2のデータの何れか一方を前記トリミングデータとして前記定電流回路に出力するマルチプレクサと、を有し、前記制御回路は、前記マルチプレクサが前記第2のデータを選択し前記トリミングデータとして出力する状態で、前記第2のデータを変化させることにより前記定電流を段階的に変化するように設定し、前記比較結果信号の論理が反転した時に対応する前記第2のデータを抽出し、抽出した前記第2のデータを前記記憶回路に前記第1のデータとして記憶させ、前記第2の電流の値は、設定された第2のデータに対応する定電流の値に、この設定された前記第2のデータに対応する前記定電流を次に設定される第2のデータに対応する定電流の値から引いた電流値差の2分の1を、加算した値である複数の半導体装置と、前記ターゲット電流をそれぞれの前記半導体装置に順次印加して前記制御回路に前記第2のデータを抽出させ、全ての前記半導体装置の前記制御回路が抽出した前記第2のデータを前記記憶回路に前記第1のデータとして各々同時に記憶させた後、同時に全ての前記半導体装置の前記ベリファイ回路にベリファイさせるテスト装置と、を備えることを特徴とする。

【0010】

本発明の他の態様に係る半導体システムは、ターゲット電流が印加されるパッドと、前記パッドと接地との間に接続された第1のMOSトランジスタと、電源に一端が接続された第1の抵抗素子と、前記第1の抵抗素子の他端と前記接地との間に接続され、前記第1のMOSトランジスタに流れる前記ターゲット電流をカレントミラーした第1の電流が流れる第2のMOSトランジスタと、トリミングデータに対応した定電流を出力する定電流回路と、前記電源に一端が接続され、前記第1の抵抗素子と同じ抵抗値を有する第2の抵抗素子と、前記第2の抵抗素子の他端と前記接地との間に接続され、前記第2のMOSトランジスタと同じサイズを有し、前記定電流回路が出力する前記定電流に対応する第2の電流が流れる第3のMOSトランジスタと、前記第1の抵抗素子と前記第2のMOSトランジスタとの間の第1の電圧と、前記第2の抵抗素子と前記第3のMOSトランジスタとの間の第2の電圧とを比較し、前記第1の電圧と前記第2の電圧の大小関係に応じて論理が異なる比較結果信号を出力するコンパレータと、第1のデータを記憶する記憶回路と、前記比較結果信号が入力され、且つ、設定した第2のデータを出力する制御回路と、前記記憶回路に記憶された前記第1のデータが入力されるとともに前記制御回路から出力された第2のデータが入力され、前記制御回路か出力された選択信号に応じて選択した前記第1のデータまたは前記第2のデータの何れか一方を前記トリミングデータとして前記定電流回路に出力するマルチプレクサと、を有し、前記制御回路は、前記マルチプレクサが前記第2のデータを選択し前記トリミングデータとして出力する状態で、前記第2のデータを変化させることにより前記定電流を段階的に変化するように設定し、前記比較結果信号の論理が反転した時に対応する前記第2のデータを抽出し、抽出した前記第2のデータを前記記憶回路に前記第1のデータとして記憶させ、前記第2の電流の値は、設定された第2のデータに対応する定電流の値に、この設定された前記第2のデータに対応する前記定電流を次に設定される第2のデータに対応する定電流の値から引いた電流値差の2分の1を、加算した値である複数の半導体装置と、前記ターゲット電流をそれぞれの前記半導体装置に同時に印加し、全ての前記半導体装置の前記制御回路が抽出した前記第2のデータを前記記憶回路に前記第1のデータとして記憶させた後、同時に全ての前記半導体装置の前記ベリファイ回路にベリファイさせるテスト装置と、を備えることを特徴とする。

【発明の効果】

【0011】

本発明の一態様に係る半導体装置によれば、定電流のトリミングをより容易にすることができる。

【図面の簡単な説明】

【0012】

【図1】本発明の一態様である実施例1に係る半導体装置100を含む半導体システム1000の構成の一例を示す図である。

【図2】図1に示す半導体装置100の構成の一例を示す図である。

【図3】図2に示す半導体装置100のトリミングデータを生成する動作の一例を示すタイミングチャートである。

【図4】図2に示す半導体装置100のトリミングデータを生成する動作の他の例を示すタイミングチャートである。

【図5】図1に示す半導体システム1000が電流トリミングする場合のシーケンスの一例を示す図である。

【図6】図1に示す半導体システム1000が電流トリミングする場合のシーケンスの他の例を示す図である。

【発明を実施するための形態】

【0013】

以下、本発明を適用した各実施例について図面を参照しながら説明する。

【実施例1】

【0014】

図1は、本発明の一態様である実施例1に係る半導体装置100を含む半導体システム1000の構成の一例を示す図である。

【0015】

図1に示すように、半導体システム1000は、テスト装置1001と、基板1002とを備える。

【0016】

基板1002には、複数の半導体装置(チップ)100が配置されている。

【0017】

テスト装置1001は、半導体装置100にターゲット電流itrgを供給し、また、半導体装置100の動作を制御するための制御信号を半導体装置100に出力するようになっている。

【0018】

ここで、図2は、図1に示す半導体装置100の構成の一例を示す図である。

【0019】

図2に示すように、半導体装置100は、第1のパッド1と、定電流回路2と、コンパレータ3と、記憶回路4と、制御回路5と、マルチプレクサ6と、ベリファイ回路7と、第2のパッド8と、第1のMOSトランジスタTr1と、第2のMOSトランジスタTr2と、第3のMOSトランジスタTr3と、第1の抵抗素子R1と、第2の抵抗素子R2と、を備える。

【0020】

第1のパッド1は、テスト装置1001からターゲット電流itrgが印加されるようになっている。

【0021】

第1のMOSトランジスタTr1は、第1のパッド1と接地との間に接続されている。この第1のMOSトランジスタTr1は、ダイオード接続されている。

第1の抵抗素子R1は、電源VDDに一端が接続されている。

【0022】

第2のMOSトランジスタTr2は、第1の抵抗素子R1の他端と接地との間に接続され、第1のMOSトランジスタTr1のゲートにゲートが接続されている。すなわち、第1のMOSトランジスタTr1と第2のMOSトランジスタTr2とは、ミラー回路を構成する。

【0023】

これにより、この第2のMOSトランジスタTr2は、第1のMOSトランジスタTr2に流れるターゲット電流itrgをカレントミラーした第1の電流I1が流れるようになっている。

【0024】

ここでは、例えば、第1のMOSトランジスタTr1のサイズと第2のMOSトランジスタTr2のサイズとが等しく設定されている。この場合、ターゲット電流itrgと第1の電流I1とは、等しくなる。

【0025】

定電流回路2は、電源VDDと接地との間に接続されており、トリミングデータに対応した定電流Iregを出力するようになっている。

【0026】

第2の抵抗素子R2は、電源VDDに一端が接続されている。この第2の抵抗素子R2は、ここでは、例えば、第1の抵抗素子R1と同じ抵抗値を有する。

【0027】

第3のMOSトランジスタTr3は、第2の抵抗素子R2の他端と接地との間に接続されている。この第3のMOSトランジスタTr3は、第2のMOSトランジスタTr2と同じサイズを有する。この第3のMOSトランジスタTr3は、定電流回路2が出力する定電流Iregに対応する第2の電流I2が流れるようになっている。

【0028】

この第2の電流I2の値は、設定された第2のデータに対応する定電流Iregの値に、この設定された第2のデータに対応する定電流Iregを次に設定される第2のデータに対応する定電流Iregの値から引いた電流値差の2分の1を、加算した値である。

【0029】

コンパレータ3は、第1の抵抗素子R1と第2のMOSトランジスタTr2との間の第1の電圧Vin1と、第2の抵抗素子R2と第3のMOSトランジスタTr3との間の第2の電圧Vin2とを比較する。そして、コンパレータ3は、第1の電圧Vin1と第2の電圧Vin2の大小関係に応じて論理(レベル)が異なる比較結果信号comp_resを、出力するようになっている。

【0030】

ここで、第1の電圧Vin1は、第1の抵抗素子R1および第2のMOSトランジスタTr2に流れる第1の電流I1に応じた電圧降下により決定される。さらに、第2の電圧Vin2は、第2抵抗素子R2および第3のMOSトランジスタTr3に流れる第2の電流I2に応じた電圧降下により決定される。

【0031】

したがって、第1の電圧Vin1と第2の電圧Vin2とをコンパレータ3で比較することにより、第1の電流I1と第2の電流I2との大小関係を調べることができる。すなわち、第1の電流I1とターゲット電流itrgとの関係および第2の電流I2と定電流iregとの関係から、第1の電圧Vin1と第2の電圧Vin2とをコンパレータ3で比較することにより、ターゲット電流itrgと定電流iregとの大小関係を調べることができる。

【0032】

記憶回路4は、第1のデータ(ヒューズデータ)を記憶するようになっている。この記憶回路4は、例えば、ヒューズ素子や、NAND型フラッシュメモリ等の不揮発性メモリである。

【0033】

制御回路5は、比較結果信号comp_resがコンパレータ3から入力されるようになっている。また、制御回路5は、テスト装置1001から第2のパッド8を介して外部信号が入力されるようになっている。さらに、制御回路5は、設定した第2のデータをマルチプレクサ6に出力するようになっている。

【0034】

また、制御回路5は、マルチプレクサ6に選択信号を出力することにより、マルチプレクサ6に入力されたデータを切り換えて出力させるようになっている。

【0035】

また、制御回路5は、該外部信号に応じて、ベリファイ動作の指令をベリファイ回路7に出力するとともに、抽出された第2のデータをベリファイ回路7に出力するようになっている。

【0036】

マルチプレクサ6は、記憶回路4に記憶された第1のデータが入力されるとともに制御回路5から出力された第2のデータが入力されるようになっている。そして、マルチプレクサ6は、制御回路5から出力された選択信号に応じて選択した該第1のデータまたは該第2のデータの何れか一方を、該トリミングデータとして定電流回路2に出力するようになっている。

【0037】

ベリファイ回路7は、テスト装置1001から出力された該外部信号に応じて、記憶回路4に記憶された第1のデータを読み出す。そして、ベリファイ回路7は、読み出された第1のデータを制御回路5で抽出された第2のデータでベリファイし、このベリファイに応じたベリファイ信号を出力するようになっている。

【0038】

次に、以上のような構成を有する半導体システム1000の動作の一例について説明する。

【0039】

図3は、図2に示す半導体装置100のトリミングデータを生成する動作の一例を示すタイミングチャートである。

【0040】

トリミングデータを生成するために、制御回路5は、該選択信号によりマルチプレクサ6が第2のデータを選択しトリミングデータとして出力する状態にする。

【0041】

そして、制御回路5は、この状態で、第2のデータを変化(TAP0〜TAP3)させることにより、トリミングデータ(TAP0〜TAP3)を変化させて、定電流Iregを段階的に変化(ここでは増加)するように設定する。

【0042】

例えば、トリミングデータ(第2のデータ)TAP0、TAP1の時、コンパレータ3は、トリミングデータTAP0、TAP1に対応する第2の電流I2とターゲット電流itrgの比較を行う。このとき、第2の電流I2はターゲット電流itrgより小さいため、コンパレータ3から出力される比較結果信号comp_resは、“Low”レベルとなる。

【0043】

そして、トリミングデータ(第2のデータ)TAP2の時、コンパレータ3は、トリミングデータTAP2に対応する第2の電流I2とターゲット電流itrgの比較を行う。このとき、第2の電流I2はターゲット電流itrgより大きいため、コンパレータ3から出力される比較結果信号comp_resは、“High”レベルとなる。

【0044】

このとき、制御回路5は、第2のデータTAP2を抽出する。すなわち、制御回路5は、コンパレータ3から出力された比較結果信号comp_resの論理が反転した時に対応する第2のデータTAP2を抽出する。

【0045】

そして、制御回路5は、この抽出した第2のデータTAP2を記憶回路4に第1のデータ(最終的に調整されたトリミングデータ)として記憶させる。

【0046】

ここで、既述のように、第2の電流I2の値は、設定された第2のデータ(例えば、TAP0)に対応する定電流Iregの値に、この設定された第2のデータ(TAP0)に対応する該定電流Iregを次に設定される第2のデータ(TAP1)に対応する定電流Iregの値から引いた電流値差ΔIの2分の1を、加算した値である。他の第2のデータに対応する第2の電流I2も同様の関係である。

【0047】

したがって、図3に示すように、抽出された第2のデータTAP2に対応する定電流iregは、ターゲット電流itrgに一番近くなる。この抽出された第2のデータTAP2は、書き込みコマンドに応じて、制御回路5により、記憶回路4に第1のデータ(最終的に調整されたトリミングデータ)として記憶される。

【0048】

この図3に示す動作は、図1に示すテスト装置1001により、各半導体装置(チップ)100に対して実施される。

【0049】

なお、図3では、定電流Iregを段階的に増加するように設定しているが、定電流Iregを段階的に減少するように設定してもよい。

【0050】

また、図4は、図2に示す半導体装置100のトリミングデータを生成する動作の他の例を示すタイミングチャートである。

【0051】

トリミングデータで生成するために、制御回路5は、該選択信号によりマルチプレクサ6が第2のデータを選択しトリミングデータとして出力する状態にする。

【0052】

そして、制御回路5は、この状態で、第2のデータを変化(TAP0〜TAP3)させることにより、トリミングデータ(TAP0〜TAP3)を変化させて、定電流Iregを段階的に変化(ここでは増加)するように設定する。

【0053】

例えば、トリミングデータ(第2のデータ)TAP0の時、コンパレータ3は、トリミングデータTAP0に対応する第2の電流I2とターゲット電流itrgの比較を行う。このとき、第2の電流I2はターゲット電流itrgより小さいため、コンパレータ3から出力される比較結果信号comp_resは、“Low”レベルとなる。

【0054】

そして、トリミングデータ(第2のデータ)TAP1の時、コンパレータ3は、トリミングデータTAP1に対応する第2の電流I2とターゲット電流itrgの比較を行う。このとき、第2の電流I2はターゲット電流itrgより大きいため、コンパレータ3から出力される比較結果信号comp_resは、“High”レベルとなる。

【0055】

このとき、制御回路5は、第2のデータTAP1を抽出する。すなわち、制御回路5は、コンパレータ3から出力された比較結果信号comp_resの論理が反転した時に対応する第2のデータTAP1を抽出する。

【0056】

そして、制御回路5は、この抽出した第2のデータTAP1を記憶回路4に第1のデータとして記憶させる。

【0057】

ここで、既述のように、第2の電流I2の値は、設定された第2のデータ(例えば、TAP0)に対応する定電流Iregの値に、この設定された第2のデータ(TAP0)に対応する該定電流Iregを次に設定される第2のデータ(TAP1)に対応する定電流Iregの値から引いた電流値差ΔIの2分の1を、加算した値である。他の第2のデータに対応する第2の電流I2も同様の関係である。

【0058】

したがって、図4に示すように、抽出された第2のデータTAP2に対応する定電流iregは、ターゲット電流itrgに一番近くなる。この抽出された第2のデータTAP2は、書き込みコマンドに応じて、制御回路5により、記憶回路4に第1のデータ(最終的に調整されたトリミングデータ)として記憶される。

【0059】

この図4に示す動作は、図1に示すテスト装置1001により、各半導体装置(チップ)100に対して実施される。

【0060】

なお、図4では、定電流Iregを段階的に増加するように設定しているが、定電流Iregを段階的に減少するように設定してもよい。

【0061】

ここで、図5は、図1に示す半導体システム1000が電流トリミングする場合のシーケンスの一例を示す図である。

【0062】

既述のように、電流トリミングの場合、複数の半導体装置(チップ)100にテスト装置1001より同時にターゲット電流を流すことは難しい。この場合、トリミングデータを調整する動作は、半導体装置(チップ)100毎に順次実施する必要がある。

【0063】

しかし、本発明の場合、テスト装置1001からは全半導体装置(チップ)100に対し同一のターゲット電流を設定し、順次トリミングデータを抽出すればよい。

【0064】

これにより、テスト装置1001による測定動作が不要となる。その後、抽出したデータを一度に記憶装置に書き込み/ベリファイを実施することが可能になる。これにより、テスト時間の短縮が可能となる。

【0065】

例えば、図5に示すように、半導体システム1000のテスト装置1001は、ターゲット電流itrgをそれぞれの半導体装置(チップ)100に順次印加して制御回路5に第2のデータを抽出させる。そして、テスト装置1001は、該外部信号により、全ての半導体装置100の制御回路5が抽出した第2のデータを記憶回路4に第1のデータ(最終的に調整されたトリミングデータ)として各々同時に記憶させる。その後、テスト装置1001は、該外部信号により同時に全ての半導体装置100のベリファイ回路7にベリファイさせる。

【0066】

このように、測定単位内の全半導体装置(チップ)100のトリミングデータの生成が終了後は、記憶回路(ヒューズ素子)4への書き込み/データデータについて同時測定の実施が可能となり、テスト時間の短縮が可能となる。

【0067】

一方、仕様により、複数の半導体装置(チップ)100にテスト装置1001より同時にターゲット電流を流すことができる場合がある。この場合、トリミングデータを調整する動作は、半導体装置(チップ)100毎に同時に実施することができる。

【0068】

ここで、図6は、図1に示す半導体システム1000が電流トリミングする場合のシーケンスの他の例を示す図である。

【0069】

図6に示すように、半導体システム1000のテスト装置1001は、ターゲット電流itrgをそれぞれの半導体装置(チップ)100に同時に印加して制御回路5に第2のデータを抽出させる。そして、テスト装置1001は、該外部信号により、全ての半導体装置100の制御回路5が抽出した第2のデータを記憶回路4に第1のデータとして各々同時に記憶させる。その後、テスト回路1001は、該外部信号により同時に全ての半導体装置100のベリファイ回路7にベリファイさせる。

【0070】

このように、測定単位内の全半導体装置(チップ)100のトリミングデータの生成が終了後は、記憶回路(ヒューズ素子)4への書き込み/データデータについて同時測定の実施が可能となり、テスト時間の短縮が可能となる。

【0071】

以上のように、本実施例に係る半導体装置によれば、定電流のトリミングをより容易にすることができる。

【符号の説明】

【0072】

1 第1のパッド、2 定電流回路、3 コンパレータ、4 記憶回路、5 制御回路、6 マルチプレクサ、7 ベリファイ回路、8 第2のパッド、Tr1 第1のMOSトランジスタ、Tr2 第2のMOSトランジスタ、Tr3 第3のMOSトランジスタ、R1 第1の抵抗素子、R2 第2の抵抗素子、100 半導体装置、1000 半導体システム、1001 テスト装置、1002 基板

【特許請求の範囲】

【請求項1】

ターゲット電流が印加されるパッドと、

前記パッドと接地との間に接続された第1のMOSトランジスタと、

電源に一端が接続された第1の抵抗素子と、

前記第1の抵抗素子の他端と前記接地との間に接続され、前記第1のMOSトランジスタに流れる前記ターゲット電流をカレントミラーした第1の電流が流れる第2のMOSトランジスタと、

トリミングデータに対応した定電流を出力する定電流回路と、

前記電源に一端が接続され、前記第1の抵抗素子と同じ抵抗値を有する第2の抵抗素子と、

前記第2の抵抗素子の他端と前記接地との間に接続され、前記第2のMOSトランジスタと同じサイズを有し、前記定電流回路が出力する前記定電流に対応する第2の電流が流れる第3のMOSトランジスタと、

前記第1の抵抗素子と前記第2のMOSトランジスタとの間の第1の電圧と、前記第2の抵抗素子と前記第3のMOSトランジスタとの間の第2の電圧とを比較し、前記第1の電圧と前記第2の電圧の大小関係に応じて論理が異なる比較結果信号を出力するコンパレータと、

第1のデータを記憶する記憶回路と、

前記比較結果信号が入力され、且つ、設定した第2のデータを出力する制御回路と、

前記記憶回路に記憶された前記第1のデータが入力されるとともに前記制御回路から出力された第2のデータが入力され、前記制御回路か出力された選択信号に応じて選択した前記第1のデータまたは前記第2のデータの何れか一方を前記トリミングデータとして前記定電流回路に出力するマルチプレクサと、を備え、

前記制御回路は、前記マルチプレクサが前記第2のデータを選択し前記トリミングデータとして出力する状態で、前記第2のデータを変化させることにより前記定電流を段階的に変化するように設定し、前記比較結果信号の論理が反転した時に対応する前記第2のデータを抽出し、抽出した前記第2のデータを前記記憶回路に前記第1のデータとして記憶させ、

前記第2の電流の値は、設定された第2のデータに対応する定電流の値に、この設定された前記第2のデータに対応する前記定電流を次に設定される第2のデータに対応する定電流の値から引いた電流値差の2分の1を、加算した値である

ことを特徴とする半導体装置。

【請求項2】

前記第1のMOSトランジスタのサイズと前記第2のMOSトランジスタのサイズとが等しい

ことを特徴とする請求項1に記載の半導体装置。

【請求項3】

外部信号に応じて、前記記憶回路に記憶された前記第1のデータを読み出し、読み出された前記第1のデータを前記制御回路に抽出された前記第2のデータでベリファイし、このベリファイに応じたベリファイ信号を出力するベリファイ回路をさらに備える

ことを特徴とする請求項1または2に記載の半導体装置。

【請求項4】

ターゲット電流が印加されるパッドと、前記パッドと接地との間に接続された第1のMOSトランジスタと、電源に一端が接続された第1の抵抗素子と、前記第1の抵抗素子の他端と前記接地との間に接続され、前記第1のMOSトランジスタに流れる前記ターゲット電流をカレントミラーした第1の電流が流れる第2のMOSトランジスタと、トリミングデータに対応した定電流を出力する定電流回路と、前記電源に一端が接続され、前記第1の抵抗素子と同じ抵抗値を有する第2の抵抗素子と、前記第2の抵抗素子の他端と前記接地との間に接続され、前記第2のMOSトランジスタと同じサイズを有し、前記定電流回路が出力する前記定電流に対応する第2の電流が流れる第3のMOSトランジスタと、前記第1の抵抗素子と前記第2のMOSトランジスタとの間の第1の電圧と、前記第2の抵抗素子と前記第3のMOSトランジスタとの間の第2の電圧とを比較し、前記第1の電圧と前記第2の電圧の大小関係に応じて論理が異なる比較結果信号を出力するコンパレータと、第1のデータを記憶する記憶回路と、前記比較結果信号が入力され、且つ、設定した第2のデータを出力する制御回路と、前記記憶回路に記憶された前記第1のデータが入力されるとともに前記制御回路から出力された第2のデータが入力され、前記制御回路か出力された選択信号に応じて選択した前記第1のデータまたは前記第2のデータの何れか一方を前記トリミングデータとして前記定電流回路に出力するマルチプレクサと、を有し、前記制御回路は、前記マルチプレクサが前記第2のデータを選択し前記トリミングデータとして出力する状態で、前記第2のデータを変化させることにより前記定電流を段階的に変化するように設定し、前記比較結果信号の論理が反転した時に対応する前記第2のデータを抽出し、抽出した前記第2のデータを前記記憶回路に前記第1のデータとして記憶させ、前記第2の電流の値は、設定された第2のデータに対応する定電流の値に、この設定された前記第2のデータに対応する前記定電流を次に設定される第2のデータに対応する定電流の値から引いた電流値差の2分の1を、加算した値である複数の半導体装置と、

前記ターゲット電流をそれぞれの前記半導体装置に順次印加して前記制御回路に前記第2のデータを抽出させ、全ての前記半導体装置の前記制御回路が抽出した前記第2のデータを前記記憶回路に前記第1のデータとして各々同時に記憶させた後、同時に全ての前記半導体装置の前記ベリファイ回路にベリファイさせるテスト装置と、を備える

ことを特徴とする半導体システム。

【請求項5】

ターゲット電流が印加されるパッドと、前記パッドと接地との間に接続された第1のMOSトランジスタと、電源に一端が接続された第1の抵抗素子と、前記第1の抵抗素子の他端と前記接地との間に接続され、前記第1のMOSトランジスタに流れる前記ターゲット電流をカレントミラーした第1の電流が流れる第2のMOSトランジスタと、トリミングデータに対応した定電流を出力する定電流回路と、前記電源に一端が接続され、前記第1の抵抗素子と同じ抵抗値を有する第2の抵抗素子と、前記第2の抵抗素子の他端と前記接地との間に接続され、前記第2のMOSトランジスタと同じサイズを有し、前記定電流回路が出力する前記定電流に対応する第2の電流が流れる第3のMOSトランジスタと、前記第1の抵抗素子と前記第2のMOSトランジスタとの間の第1の電圧と、前記第2の抵抗素子と前記第3のMOSトランジスタとの間の第2の電圧とを比較し、前記第1の電圧と前記第2の電圧の大小関係に応じて論理が異なる比較結果信号を出力するコンパレータと、第1のデータを記憶する記憶回路と、前記比較結果信号が入力され、且つ、設定した第2のデータを出力する制御回路と、前記記憶回路に記憶された前記第1のデータが入力されるとともに前記制御回路から出力された第2のデータが入力され、前記制御回路か出力された選択信号に応じて選択した前記第1のデータまたは前記第2のデータの何れか一方を前記トリミングデータとして前記定電流回路に出力するマルチプレクサと、を有し、前記制御回路は、前記マルチプレクサが前記第2のデータを選択し前記トリミングデータとして出力する状態で、前記第2のデータを変化させることにより前記定電流を段階的に変化するように設定し、前記比較結果信号の論理が反転した時に対応する前記第2のデータを抽出し、抽出した前記第2のデータを前記記憶回路に前記第1のデータとして記憶させ、前記第2の電流の値は、設定された第2のデータに対応する定電流の値に、この設定された前記第2のデータに対応する前記定電流を次に設定される第2のデータに対応する定電流の値から引いた電流値差の2分の1を、加算した値である複数の半導体装置と、

前記ターゲット電流をそれぞれの前記半導体装置に同時に印加し、全ての前記半導体装置の前記制御回路が抽出した前記第2のデータを前記記憶回路に前記第1のデータとして記憶させた後、同時に全ての前記半導体装置の前記ベリファイ回路にベリファイさせるテスト装置と、を備える

ことを特徴とする半導体システム。

【請求項1】

ターゲット電流が印加されるパッドと、

前記パッドと接地との間に接続された第1のMOSトランジスタと、

電源に一端が接続された第1の抵抗素子と、

前記第1の抵抗素子の他端と前記接地との間に接続され、前記第1のMOSトランジスタに流れる前記ターゲット電流をカレントミラーした第1の電流が流れる第2のMOSトランジスタと、

トリミングデータに対応した定電流を出力する定電流回路と、

前記電源に一端が接続され、前記第1の抵抗素子と同じ抵抗値を有する第2の抵抗素子と、

前記第2の抵抗素子の他端と前記接地との間に接続され、前記第2のMOSトランジスタと同じサイズを有し、前記定電流回路が出力する前記定電流に対応する第2の電流が流れる第3のMOSトランジスタと、

前記第1の抵抗素子と前記第2のMOSトランジスタとの間の第1の電圧と、前記第2の抵抗素子と前記第3のMOSトランジスタとの間の第2の電圧とを比較し、前記第1の電圧と前記第2の電圧の大小関係に応じて論理が異なる比較結果信号を出力するコンパレータと、

第1のデータを記憶する記憶回路と、

前記比較結果信号が入力され、且つ、設定した第2のデータを出力する制御回路と、

前記記憶回路に記憶された前記第1のデータが入力されるとともに前記制御回路から出力された第2のデータが入力され、前記制御回路か出力された選択信号に応じて選択した前記第1のデータまたは前記第2のデータの何れか一方を前記トリミングデータとして前記定電流回路に出力するマルチプレクサと、を備え、

前記制御回路は、前記マルチプレクサが前記第2のデータを選択し前記トリミングデータとして出力する状態で、前記第2のデータを変化させることにより前記定電流を段階的に変化するように設定し、前記比較結果信号の論理が反転した時に対応する前記第2のデータを抽出し、抽出した前記第2のデータを前記記憶回路に前記第1のデータとして記憶させ、

前記第2の電流の値は、設定された第2のデータに対応する定電流の値に、この設定された前記第2のデータに対応する前記定電流を次に設定される第2のデータに対応する定電流の値から引いた電流値差の2分の1を、加算した値である

ことを特徴とする半導体装置。

【請求項2】

前記第1のMOSトランジスタのサイズと前記第2のMOSトランジスタのサイズとが等しい

ことを特徴とする請求項1に記載の半導体装置。

【請求項3】

外部信号に応じて、前記記憶回路に記憶された前記第1のデータを読み出し、読み出された前記第1のデータを前記制御回路に抽出された前記第2のデータでベリファイし、このベリファイに応じたベリファイ信号を出力するベリファイ回路をさらに備える

ことを特徴とする請求項1または2に記載の半導体装置。

【請求項4】

ターゲット電流が印加されるパッドと、前記パッドと接地との間に接続された第1のMOSトランジスタと、電源に一端が接続された第1の抵抗素子と、前記第1の抵抗素子の他端と前記接地との間に接続され、前記第1のMOSトランジスタに流れる前記ターゲット電流をカレントミラーした第1の電流が流れる第2のMOSトランジスタと、トリミングデータに対応した定電流を出力する定電流回路と、前記電源に一端が接続され、前記第1の抵抗素子と同じ抵抗値を有する第2の抵抗素子と、前記第2の抵抗素子の他端と前記接地との間に接続され、前記第2のMOSトランジスタと同じサイズを有し、前記定電流回路が出力する前記定電流に対応する第2の電流が流れる第3のMOSトランジスタと、前記第1の抵抗素子と前記第2のMOSトランジスタとの間の第1の電圧と、前記第2の抵抗素子と前記第3のMOSトランジスタとの間の第2の電圧とを比較し、前記第1の電圧と前記第2の電圧の大小関係に応じて論理が異なる比較結果信号を出力するコンパレータと、第1のデータを記憶する記憶回路と、前記比較結果信号が入力され、且つ、設定した第2のデータを出力する制御回路と、前記記憶回路に記憶された前記第1のデータが入力されるとともに前記制御回路から出力された第2のデータが入力され、前記制御回路か出力された選択信号に応じて選択した前記第1のデータまたは前記第2のデータの何れか一方を前記トリミングデータとして前記定電流回路に出力するマルチプレクサと、を有し、前記制御回路は、前記マルチプレクサが前記第2のデータを選択し前記トリミングデータとして出力する状態で、前記第2のデータを変化させることにより前記定電流を段階的に変化するように設定し、前記比較結果信号の論理が反転した時に対応する前記第2のデータを抽出し、抽出した前記第2のデータを前記記憶回路に前記第1のデータとして記憶させ、前記第2の電流の値は、設定された第2のデータに対応する定電流の値に、この設定された前記第2のデータに対応する前記定電流を次に設定される第2のデータに対応する定電流の値から引いた電流値差の2分の1を、加算した値である複数の半導体装置と、

前記ターゲット電流をそれぞれの前記半導体装置に順次印加して前記制御回路に前記第2のデータを抽出させ、全ての前記半導体装置の前記制御回路が抽出した前記第2のデータを前記記憶回路に前記第1のデータとして各々同時に記憶させた後、同時に全ての前記半導体装置の前記ベリファイ回路にベリファイさせるテスト装置と、を備える

ことを特徴とする半導体システム。

【請求項5】

ターゲット電流が印加されるパッドと、前記パッドと接地との間に接続された第1のMOSトランジスタと、電源に一端が接続された第1の抵抗素子と、前記第1の抵抗素子の他端と前記接地との間に接続され、前記第1のMOSトランジスタに流れる前記ターゲット電流をカレントミラーした第1の電流が流れる第2のMOSトランジスタと、トリミングデータに対応した定電流を出力する定電流回路と、前記電源に一端が接続され、前記第1の抵抗素子と同じ抵抗値を有する第2の抵抗素子と、前記第2の抵抗素子の他端と前記接地との間に接続され、前記第2のMOSトランジスタと同じサイズを有し、前記定電流回路が出力する前記定電流に対応する第2の電流が流れる第3のMOSトランジスタと、前記第1の抵抗素子と前記第2のMOSトランジスタとの間の第1の電圧と、前記第2の抵抗素子と前記第3のMOSトランジスタとの間の第2の電圧とを比較し、前記第1の電圧と前記第2の電圧の大小関係に応じて論理が異なる比較結果信号を出力するコンパレータと、第1のデータを記憶する記憶回路と、前記比較結果信号が入力され、且つ、設定した第2のデータを出力する制御回路と、前記記憶回路に記憶された前記第1のデータが入力されるとともに前記制御回路から出力された第2のデータが入力され、前記制御回路か出力された選択信号に応じて選択した前記第1のデータまたは前記第2のデータの何れか一方を前記トリミングデータとして前記定電流回路に出力するマルチプレクサと、を有し、前記制御回路は、前記マルチプレクサが前記第2のデータを選択し前記トリミングデータとして出力する状態で、前記第2のデータを変化させることにより前記定電流を段階的に変化するように設定し、前記比較結果信号の論理が反転した時に対応する前記第2のデータを抽出し、抽出した前記第2のデータを前記記憶回路に前記第1のデータとして記憶させ、前記第2の電流の値は、設定された第2のデータに対応する定電流の値に、この設定された前記第2のデータに対応する前記定電流を次に設定される第2のデータに対応する定電流の値から引いた電流値差の2分の1を、加算した値である複数の半導体装置と、

前記ターゲット電流をそれぞれの前記半導体装置に同時に印加し、全ての前記半導体装置の前記制御回路が抽出した前記第2のデータを前記記憶回路に前記第1のデータとして記憶させた後、同時に全ての前記半導体装置の前記ベリファイ回路にベリファイさせるテスト装置と、を備える

ことを特徴とする半導体システム。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図2】

【図3】

【図4】

【図5】

【図6】

【公開番号】特開2010−219370(P2010−219370A)

【公開日】平成22年9月30日(2010.9.30)

【国際特許分類】

【出願番号】特願2009−65590(P2009−65590)

【出願日】平成21年3月18日(2009.3.18)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

【公開日】平成22年9月30日(2010.9.30)

【国際特許分類】

【出願日】平成21年3月18日(2009.3.18)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

[ Back to top ]