半導体装置および半導体装置の製造方法

【課題】配線やビアの構成材料として銅を含む半導体装置の信頼性を高める。

【解決手段】半導体装置100は、半導体基板(不図示)と、その上に形成された第1の絶縁層102と、第1の絶縁層102上に形成され、銅を主成分として含むビア104(第1の金属膜108)と、第1の絶縁層102上に第1の金属膜108に接して設けられ、Ru、TaまたはTiを含む第4の層118a、Wを含む第5の層118b、およびRu、TaまたはTiを含む第6の層118cがこの順で形成された第2のバリアメタル膜118と、第2のバリアメタル膜118上に第6の層118cに接して設けられ、銅を主成分として含む第2の金属膜120とを含む。

【解決手段】半導体装置100は、半導体基板(不図示)と、その上に形成された第1の絶縁層102と、第1の絶縁層102上に形成され、銅を主成分として含むビア104(第1の金属膜108)と、第1の絶縁層102上に第1の金属膜108に接して設けられ、Ru、TaまたはTiを含む第4の層118a、Wを含む第5の層118b、およびRu、TaまたはTiを含む第6の層118cがこの順で形成された第2のバリアメタル膜118と、第2のバリアメタル膜118上に第6の層118cに接して設けられ、銅を主成分として含む第2の金属膜120とを含む。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置および半導体装置の製造方法に関する。

【背景技術】

【0002】

近年、半導体装置の高速化に対する要請から、配線材料として銅等の低抵抗材料が利用されるようになってきた。配線材料として銅を用いた場合、銅が絶縁層中に拡散するのを防ぐために、銅配線の周囲に拡散防止層(バリアメタル膜)が形成される。

【0003】

配線の微細化が進むと半導体装置においてバリアメタル膜が占める割合が多くなり、その材料・特性を適切に選択することが重要になる。配線間の抵抗を抑えるためには、バリアメタル膜を低抵抗材料で構成するとともに、できるだけバリアメタル膜の膜厚を薄くすることが好ましい。

【0004】

特許文献1には、タンタル材料、チタン材料、またはタングステン材料を拡散防止層に使用した構成が開示されている。また、当該文献には、拡散防止層上にRu、Re、Ni、Pd、Os、Ir、Ptからなる群から選択されるいずれか一種、またはこの金属を50%以上含有する合金から形成された接着層が形成された構成が開示されている。当該文献には、拡散防止層上に銅層を形成するために、化学蒸着法により液体形態の銅材料を使用すると、拡散防止層とその上に形成された銅層間の接着性が低下すると記載されている。これは、拡散防止層としてタンタル系合金、チタン系合金、タングステン系合金等を用いた場合、これらの金属が、層間に存在する炭素等の不純物と反応して炭化物を形成することが原因とされている。そのため、このような炭化物を形成しない金属を接着層に用いることにより、銅層との接着性が向上することが期待できる、とされている。

非特許文献1には、バリアメタル膜としてWNxCyを用いることにより、エレクトロマイグレーション耐性が向上することが記載されている。

【特許文献1】特表2005−513813号公報

【非特許文献1】S. Smith et. al., "The Application of ALD WNxCy As a Copper Diffusion Barrier", Proceedings of the IITC2003, p.135-137

【発明の開示】

【発明が解決しようとする課題】

【0005】

近年、銅配線のストレスマイグレーションの発生が問題となりつつある。銅を配線材料として用いた場合、ストレスマイグレーションにより、たとえば下層配線と上層のビアとの界面において、ボイド(空洞)が発生してしまうことがある。このようなボイドが形成されると、配線間の接続不良が引き起こされて半導体装置の歩留が低下したり、長期間の使用により半導体装置が不安定になるという問題が生じる。特許文献1に記載の技術では、このような問題を解決することができない。

【課題を解決するための手段】

【0006】

本発明によれば、

半導体基板と、

前記半導体基板上に形成された絶縁膜と、

前記絶縁膜上に形成され、銅を主成分として含む第1の金属膜と、

絶縁膜上に前記第1の金属膜に接して設けられ、Ru、TaまたはTiを含む第1の層、Wを含む第2の層、およびRu、TaまたはTiを含む第3の層がこの順で形成されたバリアメタル膜と、

前記バリアメタル膜上に前記第3の層に接して設けられ、銅を主成分として含む第2の金属膜と、

を含む半導体装置が提供される。

【0007】

バリアメタル膜の材料としてW系材料を用いることにより、非特許文献1に記載されたように、エレクトロマイグレーション耐性を向上させることができる。本発明によれば、バリアメタル膜をWを含む第2の層で構成するとともに、第2の層と第1の金属膜との間にRu、TaまたはTiを含む第1の層が設けられるので、第1の金属膜とバリアメタル膜の密着性を良好にすることができる。これにより、配線のエレクトロマイグレーション耐性を高めるとともに、ストレスマイグレーション耐性を高めることができる。

【0008】

また、配線材料として銅を用いるとともにバリアメタル膜の材料としてW系材料を用いると、配線を形成する際のCMP(化学的機械的研磨:chemical mechanical polishing)処理時に、腐食が生じるという課題がある。このような、腐食が発生すると、配線形成に不良が生じ、抵抗の上昇や歩留まりの低下という問題が起こる。本発明によれば、Wを含む第2の層の上にRu、TaまたはTiを含む第3の層が設けられるので、CMP処理時に第2の層が保護され、腐食が生じるのを防ぐことができる。これにより、配線形成の不良を防ぎ、抵抗の上昇や歩留まりの低下を防ぐことができる。

【0009】

本発明によれば、

半導体基板と、

前記半導体基板上に形成された絶縁膜と、

前記絶縁膜上に形成され、銅を主成分として含む第1の金属膜と、

絶縁膜上に前記第1の金属膜に接して設けられた第1の層、Wを含む第2の層および前記第2の層とは異なる材料により構成された第3の層がこの順で形成されたバリアメタル膜と、

前記バリアメタル膜上に前記第3の層に接して設けられ、銅を主成分として含む第2の金属膜と、

を含み、

前記第1の層は、前記第2の層を構成する材料よりも銅との密着性が高い材料により構成された半導体装置が提供される。

【0010】

これにより、配線のエレクトロマイグレーション耐性を高めるとともに、ストレスマイグレーション耐性を高めることができる。

【0011】

本発明の半導体装置において、前記第3の層は、前記第2の層を構成する材料よりも、銅との間の電極電位差が小さい材料により構成することができる。

【0012】

CMP処理時に腐食が生じる現象は、以下の理由が一因であると考えられる。CMP用研磨液に電解質が溶け込んでいる場合に、銅により構成された金属膜とW系材料により構成されたバリアメタル膜とが接した状態でCMP用研磨液にさらされると、両者の標準電極電位の差異により局部電池が形成される。そのため、両者に電流が流れガルバニック腐食が生じると考えられる。第2の金属膜とバリアメタル膜の第2の層との間に銅との電極電位差が小さい材料により構成された第3の層を設けることにより、ガルバニック腐食の生成を防ぐことができる。これにより、配線形成の不良を防ぎ、抵抗の上昇や歩留まりの低下を防ぐことができる。

【0013】

本発明によれば、

半導体基板上に形成された、銅を主成分として含む第1の金属膜上に、絶縁膜を形成する工程と、

前記絶縁膜に、前記第1の金属膜に達する凹部を形成する工程と、

前記凹部内に、Ru、TaまたはTiを含む第1の層、Wを含む第2の層、およびRu、TaまたはTiを含む第3の層をこの順で形成して前記凹部の一部を埋め込むバリアメタル膜を形成する工程と、

前記凹部を埋め込むように、前記バリアメタル膜上に銅を主成分として含む第2の金属膜を形成する工程と、

前記凹部外部に露出した前記第2の金属膜および前記バリアメタル膜をCMPにより除去する工程と、

を含む半導体装置の製造方法が提供される。

【0014】

これにより、半導体装置の信頼性を高めることができる。

【0015】

なお、以上の構成要素の任意の組合せ、本発明の表現を方法、装置の間で変換したものもまた、本発明の態様として有効である。

【発明の効果】

【0016】

本発明によれば、配線やビアの構成材料として銅を含む半導体装置の信頼性を高めることができる。

【発明を実施するための最良の形態】

【0017】

以下、本発明の実施の形態について、図面を用いて説明する。尚、すべての図面において、同様な構成要素には同様の符号を付し、適宜説明を省略する。

【0018】

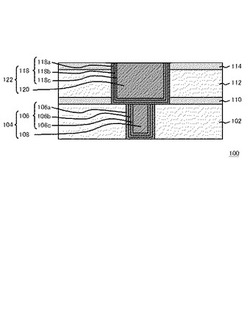

図1は、本実施の形態における半導体装置の構成の一部を示す断面図である。

半導体装置100は、半導体基板(不図示)、その上に形成された第1の絶縁層102、その上に形成されたエッチング阻止膜110、その上に形成された第2の絶縁層112およびその上に形成された保護絶縁膜114を含む。半導体装置100は、さらに、第1の絶縁層102に形成されたビア104およびビア104の上にビア104に接続して設けられた配線122を含む。ビア104は、第1の金属膜108およびその周囲に形成された第1のバリアメタル膜106を含む。配線122は、第2の金属膜120およびその周囲に形成された第2のバリアメタル膜118を含む。第1の金属膜108および第2の金属膜120は、銅を主成分として含む。ここで、第1の金属膜は、たとえばビア104とすることができる。この場合、第2の金属膜は、配線122とすることができる。また、第1の金属膜を配線、第2の金属膜をビアとすることもできる。

【0019】

本実施の形態において、第1のバリアメタル膜106および第2のバリアメタル膜118は、それぞれ3層構造を有する。第1のバリアメタル膜106は、第1の層106a、第1の層106aと異なる材料により構成された第2の層106bおよび第2の層106bと異なる材料により構成された第3の層106cがこの順で積層された構造を有する。第2のバリアメタル膜118は、第1の金属膜108に接続して設けられた第4の層118a、第4の層118aと異なる材料により構成された第5の層118bおよび第5の層118bと異なる材料により構成された第6の層118cがこの順で積層された構造を有する。

【0020】

第2の層106bおよび第5の層118bは、W(タングステン)を含む材料により構成することができる。第2の層106bおよび第5の層118bは、たとえば、W、WNまたはWNCにより構成することができる。第2の層106bおよび第5の層118bをWを含む材料により構成することにより、ビア104や配線122のエレクトロマイグレーション耐性を高めることができる。

【0021】

第1の層106aは、第2の層106bを構成する材料よりも銅との密着性が高い材料により構成することができる。第3の層106cは、第2の層106bを構成する材料よりも、銅との間でガルバニック腐食が生じにくい材料により構成することができる。

【0022】

第1の層106aおよび第3の層106cは、たとえば、Ru、TaまたはTiを含む材料により構成することができる。第1の層106aおよび第3の層106cは、たとえば、Ru、TaまたはTiの合金、窒化物、または窒炭化物により構成することができる。第1の層106aおよび第3の層106cは、同じ材料により構成することもでき、異なる材料により構成することもできる。

【0023】

また、第4の層118aおよび第6の層118cは、第1の層106aおよび第3の層106cと同様の材料により構成することができる。第2のバリアメタル膜118の構成例として、以下のようにすることができる。

(1)第4の層118a/第5の層118b/第6の層118c:Ta/WNC/Ta;

(2)第4の層118a/第5の層118b/第6の層118c:Ta/WNC/Ru;

(3)第4の層118a/第5の層118b/第6の層118c:Ru/WNC/Ru。これらは例示であり、種々の組合せとすることができる。

【0024】

第2の絶縁層112は、低誘電率膜により構成することができる。第2の絶縁層112は、たとえば、SiOCにより構成することができる。第1の絶縁層102は、シリコン酸化膜や第2の絶縁層112と同様の低誘電率膜により構成することができる。なお、ここでは図示していないが、第1の絶縁層102は、エッチング阻止膜や保護絶縁膜を含む構成とすることもできる。

【0025】

エッチング阻止膜110は、SiC、SiCN、SiOC、またはSiONにより構成することができる。保護絶縁膜114は、配線122を形成する際のCMP時に第2の絶縁層112を保護する機能を有する。保護絶縁膜114は、たとえば、シリコン酸化膜により構成することができる。

【0026】

次に、図1に示した半導体装置100の製造手順を説明する。図2および図3は、半導体装置100の製造手順を示す工程断面図である。

まず、半導体基板(不図示)上に第1の絶縁層102を形成する。つづいて、第1の絶縁層102にビアホールを形成し、ビアホール内に第1のバリアメタル膜106を形成する。次いで、ビアホール内に、第1のバリアメタル膜106上に第1の金属膜108を形成する。第1のバリアメタル膜106および第1の金属膜108の形成方法は、後述する第2のバリアメタル膜118および第2の金属膜120の形成方法と同様である。その後、ビアホール外部に露出した第1の金属膜108および第1のバリアメタル膜106をCMPにより除去してビア104を形成する。

【0027】

つづいて、ビア104上に、エッチング阻止膜110、第2の絶縁層112および保護絶縁膜114をCVD法により成膜する。これにより、図2(a)に示した構造が得られる。ここで、エッチング阻止膜110はSiCN、第2の絶縁層112はSiOC、保護絶縁膜114はSiO2により構成することができる。

【0028】

次いで、既知のリソグラフィ技術およびドライエッチングにより、保護絶縁膜114、第2の絶縁層112、およびエッチング阻止膜110に配線溝116を形成する(図2(b))。これにより、ビア104が露出される。

【0029】

その後、半導体基板の全面にALD(Atomic Layer Deposition)法またはPVD(Physical Vapor Deposition)法により、第4の層118a(膜厚約2〜10nm)を形成する。つづいて、第4の層118a上に、ALD法により第5の層118b(膜厚約2〜10nm)を形成する。次いで、第5の層118b上に、ALD法またはPVD法により、第6の層118c(膜厚約2〜10nm)を形成する(図2(c))。

【0030】

その後、第6の層118c上に、スパッタリング法等のPVD法により銅めっきのシード層として銅膜を約35nm〜75nm成膜する。これにより、配線溝116が部分的に埋め込まれる。つづいて、めっき法により銅膜を形成して第2の金属膜120を形成し、配線溝116を埋め込む(図3(a))。めっき法で形成される銅膜の膜厚は、約500nmとすることができる。

【0031】

つづいて、CMPにより配線溝116の外部に露出した第2の金属膜120および第2のバリアメタル膜118を除去する。これにより、配線122が形成される(図3(b))。

【0032】

本実施の形態において、W系材料で形成された第5の層118bの上部には第6の層118cが形成されている。そのため、CMP処理時にCMP用研磨液に電解質が溶け込んでいた場合でも、第5の層118bが第6の層118cにより保護されるため、ガルバニック腐食を防ぐことができる。このような観点からは、第6の層118cは、W系材料よりも銅との電極電位差が小さい材料により構成することが好ましい。第3の層106cも同様である。

【0033】

次いで、配線122上にキャップ絶縁膜124を形成する。キャップ絶縁膜124は、たとえばSiCNにより構成することができる。

【0034】

以上の処理を繰り返すことにより、多層配線構造を形成することができる。

【0035】

本実施の形態において、下層のビア104の第1の金属膜108は、第4の層118aが形成されている。これにより、ビア104の第1の金属膜108と第2のバリアメタル膜118との密着性を向上することができる。そのため、ビア104における銅の移動を固定することができ、配線形成後の熱処理時等にビア104と配線122との間にボイドが生じるのを防ぐことができる。このため、配線とビアとの間の断線の発生を防ぐことができ、半導体装置100の信頼性を向上させることができる。

【0036】

さらに、第2のバリアメタル膜118において、W系材料で形成された第5の層118bが第6の層118cにより保護されるため、CMP処理時にガルバニック腐食が発生するのを抑えることができる。これにより、半導体装置100の信頼性をさらに向上させることができる。

【0037】

以上、図面を参照して本発明の実施形態について述べたが、これらは本発明の例示であり、上記以外の様々な構成を採用することもできる。

【0038】

以上の実施の形態においては、シングルダマシン法で配線を形成する例を示したが、本発明はデュアルダマシン法で配線を形成する場合にも適用することができる。

【0039】

以上の実施の形態において、銅めっきのシード層をスパッタリング法等のPVD法により形成する手順を示したが、シード層は、CVD法等他の方法で形成することもできる。

【図面の簡単な説明】

【0040】

【図1】本発明の実施の形態における半導体装置の構成の一部を示す断面図である。

【図2】図1に示した半導体装置の製造手順を示す工程断面図である。

【図3】図1に示した半導体装置の製造手順を示す工程断面図である。

【符号の説明】

【0041】

100 半導体装置

102 第1の絶縁層

104 ビア

106 第1のバリアメタル膜

106a 第1の層

106b 第2の層

106c 第3の層

108 第1の金属膜

110 エッチング阻止膜

112 第2の絶縁層

114 保護絶縁膜

118 第2のバリアメタル膜

118a 第4の層

118b 第5の層

118c 第6の層

120 第2の金属膜

122 配線

124 キャップ絶縁膜

【技術分野】

【0001】

本発明は、半導体装置および半導体装置の製造方法に関する。

【背景技術】

【0002】

近年、半導体装置の高速化に対する要請から、配線材料として銅等の低抵抗材料が利用されるようになってきた。配線材料として銅を用いた場合、銅が絶縁層中に拡散するのを防ぐために、銅配線の周囲に拡散防止層(バリアメタル膜)が形成される。

【0003】

配線の微細化が進むと半導体装置においてバリアメタル膜が占める割合が多くなり、その材料・特性を適切に選択することが重要になる。配線間の抵抗を抑えるためには、バリアメタル膜を低抵抗材料で構成するとともに、できるだけバリアメタル膜の膜厚を薄くすることが好ましい。

【0004】

特許文献1には、タンタル材料、チタン材料、またはタングステン材料を拡散防止層に使用した構成が開示されている。また、当該文献には、拡散防止層上にRu、Re、Ni、Pd、Os、Ir、Ptからなる群から選択されるいずれか一種、またはこの金属を50%以上含有する合金から形成された接着層が形成された構成が開示されている。当該文献には、拡散防止層上に銅層を形成するために、化学蒸着法により液体形態の銅材料を使用すると、拡散防止層とその上に形成された銅層間の接着性が低下すると記載されている。これは、拡散防止層としてタンタル系合金、チタン系合金、タングステン系合金等を用いた場合、これらの金属が、層間に存在する炭素等の不純物と反応して炭化物を形成することが原因とされている。そのため、このような炭化物を形成しない金属を接着層に用いることにより、銅層との接着性が向上することが期待できる、とされている。

非特許文献1には、バリアメタル膜としてWNxCyを用いることにより、エレクトロマイグレーション耐性が向上することが記載されている。

【特許文献1】特表2005−513813号公報

【非特許文献1】S. Smith et. al., "The Application of ALD WNxCy As a Copper Diffusion Barrier", Proceedings of the IITC2003, p.135-137

【発明の開示】

【発明が解決しようとする課題】

【0005】

近年、銅配線のストレスマイグレーションの発生が問題となりつつある。銅を配線材料として用いた場合、ストレスマイグレーションにより、たとえば下層配線と上層のビアとの界面において、ボイド(空洞)が発生してしまうことがある。このようなボイドが形成されると、配線間の接続不良が引き起こされて半導体装置の歩留が低下したり、長期間の使用により半導体装置が不安定になるという問題が生じる。特許文献1に記載の技術では、このような問題を解決することができない。

【課題を解決するための手段】

【0006】

本発明によれば、

半導体基板と、

前記半導体基板上に形成された絶縁膜と、

前記絶縁膜上に形成され、銅を主成分として含む第1の金属膜と、

絶縁膜上に前記第1の金属膜に接して設けられ、Ru、TaまたはTiを含む第1の層、Wを含む第2の層、およびRu、TaまたはTiを含む第3の層がこの順で形成されたバリアメタル膜と、

前記バリアメタル膜上に前記第3の層に接して設けられ、銅を主成分として含む第2の金属膜と、

を含む半導体装置が提供される。

【0007】

バリアメタル膜の材料としてW系材料を用いることにより、非特許文献1に記載されたように、エレクトロマイグレーション耐性を向上させることができる。本発明によれば、バリアメタル膜をWを含む第2の層で構成するとともに、第2の層と第1の金属膜との間にRu、TaまたはTiを含む第1の層が設けられるので、第1の金属膜とバリアメタル膜の密着性を良好にすることができる。これにより、配線のエレクトロマイグレーション耐性を高めるとともに、ストレスマイグレーション耐性を高めることができる。

【0008】

また、配線材料として銅を用いるとともにバリアメタル膜の材料としてW系材料を用いると、配線を形成する際のCMP(化学的機械的研磨:chemical mechanical polishing)処理時に、腐食が生じるという課題がある。このような、腐食が発生すると、配線形成に不良が生じ、抵抗の上昇や歩留まりの低下という問題が起こる。本発明によれば、Wを含む第2の層の上にRu、TaまたはTiを含む第3の層が設けられるので、CMP処理時に第2の層が保護され、腐食が生じるのを防ぐことができる。これにより、配線形成の不良を防ぎ、抵抗の上昇や歩留まりの低下を防ぐことができる。

【0009】

本発明によれば、

半導体基板と、

前記半導体基板上に形成された絶縁膜と、

前記絶縁膜上に形成され、銅を主成分として含む第1の金属膜と、

絶縁膜上に前記第1の金属膜に接して設けられた第1の層、Wを含む第2の層および前記第2の層とは異なる材料により構成された第3の層がこの順で形成されたバリアメタル膜と、

前記バリアメタル膜上に前記第3の層に接して設けられ、銅を主成分として含む第2の金属膜と、

を含み、

前記第1の層は、前記第2の層を構成する材料よりも銅との密着性が高い材料により構成された半導体装置が提供される。

【0010】

これにより、配線のエレクトロマイグレーション耐性を高めるとともに、ストレスマイグレーション耐性を高めることができる。

【0011】

本発明の半導体装置において、前記第3の層は、前記第2の層を構成する材料よりも、銅との間の電極電位差が小さい材料により構成することができる。

【0012】

CMP処理時に腐食が生じる現象は、以下の理由が一因であると考えられる。CMP用研磨液に電解質が溶け込んでいる場合に、銅により構成された金属膜とW系材料により構成されたバリアメタル膜とが接した状態でCMP用研磨液にさらされると、両者の標準電極電位の差異により局部電池が形成される。そのため、両者に電流が流れガルバニック腐食が生じると考えられる。第2の金属膜とバリアメタル膜の第2の層との間に銅との電極電位差が小さい材料により構成された第3の層を設けることにより、ガルバニック腐食の生成を防ぐことができる。これにより、配線形成の不良を防ぎ、抵抗の上昇や歩留まりの低下を防ぐことができる。

【0013】

本発明によれば、

半導体基板上に形成された、銅を主成分として含む第1の金属膜上に、絶縁膜を形成する工程と、

前記絶縁膜に、前記第1の金属膜に達する凹部を形成する工程と、

前記凹部内に、Ru、TaまたはTiを含む第1の層、Wを含む第2の層、およびRu、TaまたはTiを含む第3の層をこの順で形成して前記凹部の一部を埋め込むバリアメタル膜を形成する工程と、

前記凹部を埋め込むように、前記バリアメタル膜上に銅を主成分として含む第2の金属膜を形成する工程と、

前記凹部外部に露出した前記第2の金属膜および前記バリアメタル膜をCMPにより除去する工程と、

を含む半導体装置の製造方法が提供される。

【0014】

これにより、半導体装置の信頼性を高めることができる。

【0015】

なお、以上の構成要素の任意の組合せ、本発明の表現を方法、装置の間で変換したものもまた、本発明の態様として有効である。

【発明の効果】

【0016】

本発明によれば、配線やビアの構成材料として銅を含む半導体装置の信頼性を高めることができる。

【発明を実施するための最良の形態】

【0017】

以下、本発明の実施の形態について、図面を用いて説明する。尚、すべての図面において、同様な構成要素には同様の符号を付し、適宜説明を省略する。

【0018】

図1は、本実施の形態における半導体装置の構成の一部を示す断面図である。

半導体装置100は、半導体基板(不図示)、その上に形成された第1の絶縁層102、その上に形成されたエッチング阻止膜110、その上に形成された第2の絶縁層112およびその上に形成された保護絶縁膜114を含む。半導体装置100は、さらに、第1の絶縁層102に形成されたビア104およびビア104の上にビア104に接続して設けられた配線122を含む。ビア104は、第1の金属膜108およびその周囲に形成された第1のバリアメタル膜106を含む。配線122は、第2の金属膜120およびその周囲に形成された第2のバリアメタル膜118を含む。第1の金属膜108および第2の金属膜120は、銅を主成分として含む。ここで、第1の金属膜は、たとえばビア104とすることができる。この場合、第2の金属膜は、配線122とすることができる。また、第1の金属膜を配線、第2の金属膜をビアとすることもできる。

【0019】

本実施の形態において、第1のバリアメタル膜106および第2のバリアメタル膜118は、それぞれ3層構造を有する。第1のバリアメタル膜106は、第1の層106a、第1の層106aと異なる材料により構成された第2の層106bおよび第2の層106bと異なる材料により構成された第3の層106cがこの順で積層された構造を有する。第2のバリアメタル膜118は、第1の金属膜108に接続して設けられた第4の層118a、第4の層118aと異なる材料により構成された第5の層118bおよび第5の層118bと異なる材料により構成された第6の層118cがこの順で積層された構造を有する。

【0020】

第2の層106bおよび第5の層118bは、W(タングステン)を含む材料により構成することができる。第2の層106bおよび第5の層118bは、たとえば、W、WNまたはWNCにより構成することができる。第2の層106bおよび第5の層118bをWを含む材料により構成することにより、ビア104や配線122のエレクトロマイグレーション耐性を高めることができる。

【0021】

第1の層106aは、第2の層106bを構成する材料よりも銅との密着性が高い材料により構成することができる。第3の層106cは、第2の層106bを構成する材料よりも、銅との間でガルバニック腐食が生じにくい材料により構成することができる。

【0022】

第1の層106aおよび第3の層106cは、たとえば、Ru、TaまたはTiを含む材料により構成することができる。第1の層106aおよび第3の層106cは、たとえば、Ru、TaまたはTiの合金、窒化物、または窒炭化物により構成することができる。第1の層106aおよび第3の層106cは、同じ材料により構成することもでき、異なる材料により構成することもできる。

【0023】

また、第4の層118aおよび第6の層118cは、第1の層106aおよび第3の層106cと同様の材料により構成することができる。第2のバリアメタル膜118の構成例として、以下のようにすることができる。

(1)第4の層118a/第5の層118b/第6の層118c:Ta/WNC/Ta;

(2)第4の層118a/第5の層118b/第6の層118c:Ta/WNC/Ru;

(3)第4の層118a/第5の層118b/第6の層118c:Ru/WNC/Ru。これらは例示であり、種々の組合せとすることができる。

【0024】

第2の絶縁層112は、低誘電率膜により構成することができる。第2の絶縁層112は、たとえば、SiOCにより構成することができる。第1の絶縁層102は、シリコン酸化膜や第2の絶縁層112と同様の低誘電率膜により構成することができる。なお、ここでは図示していないが、第1の絶縁層102は、エッチング阻止膜や保護絶縁膜を含む構成とすることもできる。

【0025】

エッチング阻止膜110は、SiC、SiCN、SiOC、またはSiONにより構成することができる。保護絶縁膜114は、配線122を形成する際のCMP時に第2の絶縁層112を保護する機能を有する。保護絶縁膜114は、たとえば、シリコン酸化膜により構成することができる。

【0026】

次に、図1に示した半導体装置100の製造手順を説明する。図2および図3は、半導体装置100の製造手順を示す工程断面図である。

まず、半導体基板(不図示)上に第1の絶縁層102を形成する。つづいて、第1の絶縁層102にビアホールを形成し、ビアホール内に第1のバリアメタル膜106を形成する。次いで、ビアホール内に、第1のバリアメタル膜106上に第1の金属膜108を形成する。第1のバリアメタル膜106および第1の金属膜108の形成方法は、後述する第2のバリアメタル膜118および第2の金属膜120の形成方法と同様である。その後、ビアホール外部に露出した第1の金属膜108および第1のバリアメタル膜106をCMPにより除去してビア104を形成する。

【0027】

つづいて、ビア104上に、エッチング阻止膜110、第2の絶縁層112および保護絶縁膜114をCVD法により成膜する。これにより、図2(a)に示した構造が得られる。ここで、エッチング阻止膜110はSiCN、第2の絶縁層112はSiOC、保護絶縁膜114はSiO2により構成することができる。

【0028】

次いで、既知のリソグラフィ技術およびドライエッチングにより、保護絶縁膜114、第2の絶縁層112、およびエッチング阻止膜110に配線溝116を形成する(図2(b))。これにより、ビア104が露出される。

【0029】

その後、半導体基板の全面にALD(Atomic Layer Deposition)法またはPVD(Physical Vapor Deposition)法により、第4の層118a(膜厚約2〜10nm)を形成する。つづいて、第4の層118a上に、ALD法により第5の層118b(膜厚約2〜10nm)を形成する。次いで、第5の層118b上に、ALD法またはPVD法により、第6の層118c(膜厚約2〜10nm)を形成する(図2(c))。

【0030】

その後、第6の層118c上に、スパッタリング法等のPVD法により銅めっきのシード層として銅膜を約35nm〜75nm成膜する。これにより、配線溝116が部分的に埋め込まれる。つづいて、めっき法により銅膜を形成して第2の金属膜120を形成し、配線溝116を埋め込む(図3(a))。めっき法で形成される銅膜の膜厚は、約500nmとすることができる。

【0031】

つづいて、CMPにより配線溝116の外部に露出した第2の金属膜120および第2のバリアメタル膜118を除去する。これにより、配線122が形成される(図3(b))。

【0032】

本実施の形態において、W系材料で形成された第5の層118bの上部には第6の層118cが形成されている。そのため、CMP処理時にCMP用研磨液に電解質が溶け込んでいた場合でも、第5の層118bが第6の層118cにより保護されるため、ガルバニック腐食を防ぐことができる。このような観点からは、第6の層118cは、W系材料よりも銅との電極電位差が小さい材料により構成することが好ましい。第3の層106cも同様である。

【0033】

次いで、配線122上にキャップ絶縁膜124を形成する。キャップ絶縁膜124は、たとえばSiCNにより構成することができる。

【0034】

以上の処理を繰り返すことにより、多層配線構造を形成することができる。

【0035】

本実施の形態において、下層のビア104の第1の金属膜108は、第4の層118aが形成されている。これにより、ビア104の第1の金属膜108と第2のバリアメタル膜118との密着性を向上することができる。そのため、ビア104における銅の移動を固定することができ、配線形成後の熱処理時等にビア104と配線122との間にボイドが生じるのを防ぐことができる。このため、配線とビアとの間の断線の発生を防ぐことができ、半導体装置100の信頼性を向上させることができる。

【0036】

さらに、第2のバリアメタル膜118において、W系材料で形成された第5の層118bが第6の層118cにより保護されるため、CMP処理時にガルバニック腐食が発生するのを抑えることができる。これにより、半導体装置100の信頼性をさらに向上させることができる。

【0037】

以上、図面を参照して本発明の実施形態について述べたが、これらは本発明の例示であり、上記以外の様々な構成を採用することもできる。

【0038】

以上の実施の形態においては、シングルダマシン法で配線を形成する例を示したが、本発明はデュアルダマシン法で配線を形成する場合にも適用することができる。

【0039】

以上の実施の形態において、銅めっきのシード層をスパッタリング法等のPVD法により形成する手順を示したが、シード層は、CVD法等他の方法で形成することもできる。

【図面の簡単な説明】

【0040】

【図1】本発明の実施の形態における半導体装置の構成の一部を示す断面図である。

【図2】図1に示した半導体装置の製造手順を示す工程断面図である。

【図3】図1に示した半導体装置の製造手順を示す工程断面図である。

【符号の説明】

【0041】

100 半導体装置

102 第1の絶縁層

104 ビア

106 第1のバリアメタル膜

106a 第1の層

106b 第2の層

106c 第3の層

108 第1の金属膜

110 エッチング阻止膜

112 第2の絶縁層

114 保護絶縁膜

118 第2のバリアメタル膜

118a 第4の層

118b 第5の層

118c 第6の層

120 第2の金属膜

122 配線

124 キャップ絶縁膜

【特許請求の範囲】

【請求項1】

半導体基板と、

前記半導体基板上に形成された絶縁膜と、

前記絶縁膜上に形成され、銅を主成分として含む第1の金属膜と、

前記絶縁膜上に前記第1の金属膜に接して設けられ、Ru、TaまたはTiを含む第1の層、Wを含む第2の層、およびRu、TaまたはTiを含む第3の層がこの順で形成されたバリアメタル膜と、

前記バリアメタル膜上に前記第3の層に接して設けられ、銅を主成分として含む第2の金属膜と、

を含む半導体装置。

【請求項2】

半導体基板と、

前記半導体基板上に形成された絶縁膜と、

前記絶縁膜上に形成され、銅を主成分として含む第1の金属膜と、

前記絶縁膜上に前記第1の金属膜に接して設けられた第1の層、Wを含む第2の層および前記第2の層とは異なる材料により構成された第3の層がこの順で形成されたバリアメタル膜と、

前記バリアメタル膜上に前記第3の層に接して設けられ、銅を主成分として含む第2の金属膜と、

を含み、

前記第1の層は、前記第2の層を構成する材料よりも銅との密着性が高い材料により構成された半導体装置。

【請求項3】

請求項2に記載の半導体装置において、

前記第1の層および前記第3の層は、ぞれぞれ、Ru、TaまたはTiを含む材料により構成された半導体装置。

【請求項4】

請求項1から3いずれかに記載の半導体装置において、

前記第2の層は、W、WNまたはWNCにより構成された半導体装置。

【請求項5】

半導体基板上に形成された、銅を主成分として含む第1の金属膜上に、絶縁膜を形成する工程と、

前記絶縁膜に、前記第1の金属膜に達する凹部を形成する工程と、

前記凹部内に、Ru、TaまたはTiを含む第1の層、Wを含む第2の層、およびRu、TaまたはTiを含む第3の層をこの順で形成して前記凹部の一部を埋め込むバリアメタル膜を形成する工程と、

前記凹部を埋め込むように、前記バリアメタル膜上に銅を主成分として含む第2の金属膜を形成する工程と、

前記凹部外部に露出した前記第2の金属膜および前記バリアメタル膜をCMPにより除去する工程と、

を含む半導体装置の製造方法。

【請求項6】

請求項5に記載の半導体装置の製造方法において、

前記CMPにより除去する工程において、電解質を含む研磨液を用いて前記第2の金属膜および前記バリアメタル膜を除去する半導体装置の製造方法。

【請求項7】

請求項5または6に記載の半導体装置の製造方法において、

前記第2の金属膜を形成する工程は、PVD法によりシード銅膜を形成する工程と、めっき法により銅膜を形成する工程と、を含む半導体装置の製造方法。

【請求項1】

半導体基板と、

前記半導体基板上に形成された絶縁膜と、

前記絶縁膜上に形成され、銅を主成分として含む第1の金属膜と、

前記絶縁膜上に前記第1の金属膜に接して設けられ、Ru、TaまたはTiを含む第1の層、Wを含む第2の層、およびRu、TaまたはTiを含む第3の層がこの順で形成されたバリアメタル膜と、

前記バリアメタル膜上に前記第3の層に接して設けられ、銅を主成分として含む第2の金属膜と、

を含む半導体装置。

【請求項2】

半導体基板と、

前記半導体基板上に形成された絶縁膜と、

前記絶縁膜上に形成され、銅を主成分として含む第1の金属膜と、

前記絶縁膜上に前記第1の金属膜に接して設けられた第1の層、Wを含む第2の層および前記第2の層とは異なる材料により構成された第3の層がこの順で形成されたバリアメタル膜と、

前記バリアメタル膜上に前記第3の層に接して設けられ、銅を主成分として含む第2の金属膜と、

を含み、

前記第1の層は、前記第2の層を構成する材料よりも銅との密着性が高い材料により構成された半導体装置。

【請求項3】

請求項2に記載の半導体装置において、

前記第1の層および前記第3の層は、ぞれぞれ、Ru、TaまたはTiを含む材料により構成された半導体装置。

【請求項4】

請求項1から3いずれかに記載の半導体装置において、

前記第2の層は、W、WNまたはWNCにより構成された半導体装置。

【請求項5】

半導体基板上に形成された、銅を主成分として含む第1の金属膜上に、絶縁膜を形成する工程と、

前記絶縁膜に、前記第1の金属膜に達する凹部を形成する工程と、

前記凹部内に、Ru、TaまたはTiを含む第1の層、Wを含む第2の層、およびRu、TaまたはTiを含む第3の層をこの順で形成して前記凹部の一部を埋め込むバリアメタル膜を形成する工程と、

前記凹部を埋め込むように、前記バリアメタル膜上に銅を主成分として含む第2の金属膜を形成する工程と、

前記凹部外部に露出した前記第2の金属膜および前記バリアメタル膜をCMPにより除去する工程と、

を含む半導体装置の製造方法。

【請求項6】

請求項5に記載の半導体装置の製造方法において、

前記CMPにより除去する工程において、電解質を含む研磨液を用いて前記第2の金属膜および前記バリアメタル膜を除去する半導体装置の製造方法。

【請求項7】

請求項5または6に記載の半導体装置の製造方法において、

前記第2の金属膜を形成する工程は、PVD法によりシード銅膜を形成する工程と、めっき法により銅膜を形成する工程と、を含む半導体装置の製造方法。

【図1】

【図2】

【図3】

【図2】

【図3】

【公開番号】特開2007−180313(P2007−180313A)

【公開日】平成19年7月12日(2007.7.12)

【国際特許分類】

【出願番号】特願2005−377862(P2005−377862)

【出願日】平成17年12月28日(2005.12.28)

【出願人】(302062931)NECエレクトロニクス株式会社 (8,021)

【出願人】(000227973)日本エー・エス・エム株式会社 (68)

【Fターム(参考)】

【公開日】平成19年7月12日(2007.7.12)

【国際特許分類】

【出願日】平成17年12月28日(2005.12.28)

【出願人】(302062931)NECエレクトロニクス株式会社 (8,021)

【出願人】(000227973)日本エー・エス・エム株式会社 (68)

【Fターム(参考)】

[ Back to top ]