半導体装置および半導体装置の製造方法

【課題】 リーク電流が十分に抑制可能な高誘電率絶縁膜20を有する半導体装置の製造方法を提供する。

【解決手段】 半導体領域19の上に高誘電率絶縁膜20をアトミックレイヤーデポジション法により成膜し、高誘電率絶縁膜20の上にアルミナ膜21をアトミックレイヤーデポジション法により成膜し、アルミナ膜21をアニールし、アルミナ膜21の上に導電層22を還元雰囲気下で成膜する。

【解決手段】 半導体領域19の上に高誘電率絶縁膜20をアトミックレイヤーデポジション法により成膜し、高誘電率絶縁膜20の上にアルミナ膜21をアトミックレイヤーデポジション法により成膜し、アルミナ膜21をアニールし、アルミナ膜21の上に導電層22を還元雰囲気下で成膜する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、高誘電率絶縁膜を有する半導体装置およびその半導体装置の製造方法に関する。

【背景技術】

【0002】

近年、大規模集積回路(LSI)の高密度化に伴い、ゲート絶縁膜とキャパシタ絶縁膜は薄膜化の一途をたどっている。薄膜化に伴うリーク電流の上昇を避けるため、3次元化などのように半導体装置の構造を変更することによる対策を図る一方、高誘電率絶縁膜を用いることで物理膜厚を増やしリーク電流の上昇を抑えることが試みられている(例えば、特許文献1参照。)。

【0003】

特に、EEPROMなどの不揮発性半導体記憶装置においては、電荷蓄積層と制御電極との間に形成するインターポリ絶縁膜に関して、例えば、シリコン酸化膜/シリコン窒化膜/シリコン酸化膜の三層積層膜(ONO膜)を用い、高誘電率化を図るとともに、インターポリ絶縁膜の面積を増大させるために3次元的な構造を適用することも試みられている。しかし、半導体記憶装置のメモリセル間の距離が縮小するにつれ、隣接するセル間の干渉が著しく増大してデバイス特性を劣化させるため、3次元的な構造による面積の増大は困難であった。

【0004】

このため、次世代の不揮発性半導体記憶装置の実現するために、インターポリ絶縁膜として、従来よりも高誘電率を有する絶縁膜を適用することが必要となる。高誘電率絶縁膜を適用した結果、インターポリ絶縁膜の面積を増大させずに容量を大きくできるので、3次元的な構造にする必要がなくなり、製造工程を簡略化できる。結果として、メモリセルは高性能化し、かつ、半導体記憶装置の製造方法は容易になり、高歩留まりな製造方法を実現することが可能となる。

【0005】

高誘電率絶縁膜としてはハフニウムアルミネート(HfAlO)などの複合酸化物が、膜厚の均一性や量産性、低ダメージなどの理由からアトミックレイヤーデポジション(ALD)法等の化学気相成長(CVD)法により形成されている。しかし、高誘電率絶縁膜をEEPROMのインターポリ絶縁膜に用いる場合は、印加される電界が高いためにリーク電流が十分に抑制できないという問題があった。

【特許文献1】特開2005−109231号公報

【発明の開示】

【発明が解決しようとする課題】

【0006】

本発明は、リーク電流が十分に抑制可能な高誘電率絶縁膜を有する半導体装置を提供する。また、本発明は、リーク電流が十分に抑制可能な高誘電率絶縁膜を有する半導体装置の製造方法を提供する。

【課題を解決するための手段】

【0007】

本願発明の一態様によれば、半導体領域と、半導体領域の上に設けられ、少なくともアルミニウム以外の金属元素を含む高誘電率絶縁膜と、高誘電率絶縁膜の上に設けられたアルミナ膜と、アルミナ膜の上に設けられた導電層とを有することを特徴とする半導体装置が提供される。

【0008】

本願発明の一態様によれば、半導体領域の上に高誘電率絶縁膜をアトミックレイヤーデポジション法により成膜し、高誘電率絶縁膜の上にアルミナ膜をアトミックレイヤーデポジション法により成膜し、アルミナ膜をアニールし、アルミナ膜の上に導電層を還元雰囲気下で成膜することを特徴とする半導体装置の製造方法が提供される。

【発明の効果】

【0009】

本発明の一態様に係る半導体装置およびその製造方法によれば、リーク電流が十分に抑制可能な高誘電率絶縁膜を有する半導体装置を提供できる。また、リーク電流が十分に抑制可能な高誘電率絶縁膜を有する半導体装置の製造方法を提供できる。

【発明を実施するための最良の形態】

【0010】

次に、図面を参照して、本発明の実施の形態について説明する。なお、以下では本発明の実施形態を図面に基づいて説明するが、図解のためだけであり、本発明はそれらの図面に限定されるものではない。以下の図面の記載において、同一又は類似の部分には同一又は類似の符号を付している。また、図面は模式的なものであり、厚みと平面寸法との関係、各層の厚みの比率等は現実のものとは異なることに留意すべきである。

【実施例1】

【0011】

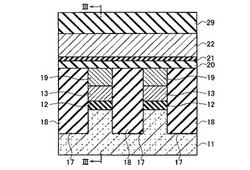

本発明の実施例1に係る半導体装置は、図1乃至図3に示すような、不揮発性半導体記憶装置1のNAND型電気的書き換え可能な不揮発性メモリ(EEPROM)である。実施例1は、不揮発性半導体記憶装置1の、電荷蓄積層13、19と制御電極22との間に形成するインターポリ絶縁膜20、21に高誘電率絶縁膜20を使用した場合である。不揮発性半導体記憶装置1は、半導体領域19と、半導体領域19の直上に設けられ、少なくともアルミニウム以外の金属元素を含む高誘電率絶縁膜20と、高誘電率絶縁膜20の上に設けられたアルミナ膜21と、アルミナ膜21の上に設けられた導電層22とを有する。このことにより、高誘電率絶縁膜20を経由して半導体領域19と導電層22の間を流れるリーク電流を低減することができる。

【0012】

不揮発性半導体記憶装置1は、半導体基板11を有している。半導体基板11には素子分離溝17が形成されている。素子分離溝17には素子分離絶縁膜18が埋め込まれている。素子分離絶縁膜18によって、複数の素子形成領域が区画され、分離されている。各素子形成領域では、半導体基板11の上に第1のゲート絶縁膜となる絶縁層12が設けられている。絶縁層12の上には浮遊ゲートになる導電層13、19が設けられている。導電層13、19は、導電膜13と導電膜19の積層構造をしている。導電膜13と19は、高濃度にドーピングされた半導体膜で構成されている。導電膜19の上には第2のゲート絶縁膜となる絶縁層20、21が設けられている。絶縁層20、21は、下層膜を高誘電率絶縁膜20とし、上層膜をアルミナ膜21とする積層構造をしている。高誘電率絶縁膜20には、アルミニウムを含む複合酸化物を用いることができる。このアルミニウムを含む複合酸化物としては、具体的には、ハフニウムアルミネート(HfAlO)、ジルコニウムアルミネート(ZrAlO)、ランタンアルミネート(LaAlO)等を用いることができる。アルミナ膜21の上には制御ゲートとなる導電層22が設けられている。導電層22の上にはパッシベーション膜となる絶縁層29が設けられている。絶縁層29は、ソース・ドレイン領域25の上にも配置されている。ソース・ドレイン領域25は、半導体基板11の表面を含むように半導体基板11内に設けられる。

【0013】

次に、実施例1の不揮発性半導体記憶装置1の製造方法について説明する。

【0014】

まず、図4と図5に示すように、p型シリコン(Si)基板11、もしくはn型シリコン基板中に形成したp型ウエル11の上に、第1の絶縁層12を1−15nm程度の厚さに形成する。第1の絶縁層12は、p型シリコン(Si)基板11の表面を酸化及び窒化する方法で形成する。第1の絶縁層12の上に化学気相成長(CVD)法によりドーピングされたポリシリコンを成膜することにより、第1の導電膜13を10−200nm程度の厚さに形成する。第1の導電膜13は浮遊ゲートであって電荷蓄積層となる。

【0015】

第1の導電膜13の上にCVD法によってシリコン窒化膜14を50−200nm程度の厚さに成膜する。さらに、シリコン窒化膜14の上にCVD法によってシリコン酸化膜15を50−400nm程度の厚さに形成する。シリコン酸化膜15の上にフォトレジストを塗布しレジスト膜を生成し、ホトリソグラフィ法にてパターニングしてレジストマスク16を形成する。

【0016】

レジストマスク16をマスクに用いて、シリコン窒化膜14をストッパーに用いて、シリコン酸化膜15を、反応性イオンエッチング(RIE)法にて、選択的にエッチングする。このシリコン酸化膜15のエッチング後にレジストマスク16を除去する。

【0017】

次いで、図6に示すように、シリコン酸化膜15をマスクとして、シリコン窒化膜14をRIE法にてエッチングし、続いて、第1の導電膜13、第1の絶縁層12及びシリコン基板11をRIE法にてエッチングして素子分離溝17を形成する。エッチング後に、エッチングにより形成された第1の導電膜13、第1の絶縁層12及びシリコン基板11の側面のダメージを除去するための高温後酸化工程を行う。

【0018】

シリコン酸化膜等の素子分離絶縁膜18をCVD法により200−1500nmの厚さに成膜し、素子分離絶縁膜18を素子分離溝17に埋め込む。素子分離絶縁膜18を窒素雰囲気又は酸素雰囲気での高温の熱処理を行い、素子分離絶縁膜18を高密度化する。ケミカルメカニカルポリッシング(CMP:Chemical Mechanical Polishing)法によって、シリコン窒化膜14をストッパーとして素子分離絶縁膜18の平坦化を行う。シリコン窒化膜14の上の素子分離絶縁膜18が除去される。シリコン酸化膜18、12と選択比をもってシリコン窒化膜14をエッチングすることが可能なホット燐酸(H2PO4)を用いて、シリコン窒化膜14を除去する。これにより、図6に示すような断面構造が得られる。

【0019】

実施例1では、素子分離溝17を形成するに際して、シリコン窒化膜14及びシリコン酸化膜15の積層膜をマスクとして用いているが、シリコン窒化膜14またはシリコン酸化膜15の膜厚及びRIE法の条件を適切にすれば、単層のシリコン窒化膜14、単層のシリコン酸化膜15、或いは他の単層・多層膜のいずれでもシリコン(Si)との選択比が取れる材料からなる膜であれば実施可能である。

【0020】

図7に示すように、シリコン窒化膜14の除去後に得られた溝内を埋め込むように第1の導電膜13の上に、段差被覆性に優れた成膜方法を用いて、第2の導電膜19を成膜する。第2の導電膜19としては、ドーピングされたポリシリコン膜を用いることができる。第1の導電膜13と第2の導電膜19とは積層され、第1の導電膜13と第2の導電膜19とで第1の導電層を構成する。次いで、CMP法により素子分離絶縁膜18をストッパーにして第2の導電膜19の平坦化を行う。素子分離絶縁膜18の上に堆積した第2の導電膜19は除去される。

【0021】

図8に示すように、平坦化した導電膜19と素子分離絶縁膜18の上にいわゆるシリコン酸化膜よりも高誘電率を有する高誘電率絶縁膜20を形成する。ここで、高誘電率絶縁膜20としては、シリコン酸化膜(SiO2膜)の比誘電率3.8−4よりも大きく、特に従来のONO膜で得られていた比誘電率5−5.5程度よりも大きい膜であることが望ましい。実施例1では高誘電率絶縁膜20としてハフニウム(Hf)とアルミニウム(Al)を含む複合酸化膜であるハフニウムアルミネート(HfAlO)膜を用いた。以下にHfAlO膜のALD法による形成方法の詳細を述べる。

【0022】

ここまで製造してきたシリコン基板11を、圧力が39.9Paに保持された真空チャンバ中に搬入し、シリコン基板11を基板温度290℃に加熱する。シリコン基板11にアルミニウム(Al)の原料ガスであるトリメチルアルミニウム(TMA:trimethylaluminum)と酸化剤であるオゾン(O3)を交互に流し供給することにより、アルミニウム原子層と酸素原子層からなるアルミニウム酸化膜(AlO膜)を形成できる。また、シリコン基板11にハフニウム(Hf)の原料ガスであるテトラキスエチルメチルアミノハフニウム(TEMAH:tetrakis-ethylmethylamino-hafunium)とオゾンを交互に流し供給することにより、ハフニウム原子層と酸素原子層からなるハフニウム酸化膜(HfO膜)を形成できる。このAlO膜とHfO膜を層状に積層させ、AlO膜とHfO膜をそれぞれ所望の層数繰り返すことにより必要とされるアルミニウムとハフニウムの組成比および膜厚のHfAlO膜を形成した。

【0023】

TMA、TEMAHのキャリアガスの流量はそれぞれ200sccm、500sccmであり、オゾンの流量は5slmであり、オゾンの濃度は250g/m3とした。また、原料ガスのシリコン基板11への供給時間はそれぞれ、TMAが1秒、TEMAH が2秒、オゾンが3秒であった。更にTMAとオゾンの交互の供給の間と、TEMAHとオゾンの交互の供給の間に、真空チャンバ内の雰囲気のパージのための窒素(N2)を5slmで2〜3秒間流した。

【0024】

具体的な交互の供給の回数としては、TEMAHとオゾンの交互供給を13回繰り返すごとにTMAとオゾンの交互供給を1回行うというシーケンスを15回繰り返した。このことにより、膜厚が20nmのHfAlO膜20を形成した。ここで、TEMAHとオゾンの交互供給の13回を増減することで、アルミニウムとハフニウムの組成比を変更することができる。また、シーケンスの繰り返しの15回を増減することで、HfAlO膜20の膜厚を増減することができる。

【0025】

その後、ポストデポジションアニール(PDA)として、500−1200℃の温度で、例えば、炉でのアニールにおいて10分以上2時間以内、ランプアニールにおいて1秒−30分以内、アニールを行う。この1回目のPDAにより、HfAlO膜20の高密度化を行い、膜質が改善される。なお、1回目のPDAは、後述する2回目のPDAにより省略することが可能である。ただ、1回目のPDAを行うことにより、HfAlO膜20が高密度化されているので後述するアルミナ膜21が2回目のPDAの際にHfAlO膜20中に拡散しにくくなる。このことにより、第2導電層22の成膜の際の露出面を、より薄いアルミナ膜21で、ハフニウム原子が露出しないようにアルミニウム原子で覆うことができる。

【0026】

実施例1では、1回目のPDAを省略したとすると、HfAlO膜20の形成の後に、アルミナ(Al2O3)膜21をHfAlO膜20の上に成膜する。以下にアルミナ膜のALD法による形成方法の詳細を述べる。

【0027】

シリコン基板11は真空チャンバ中に入れたまま、チャンバ内の圧力も39.9Paに保持し、シリコン基板11の基板温度も290℃に保持する。シリコン基板11にTMAとオゾンを交互に流し供給することにより、アルミニウム原子層と酸素原子層からなるアルミニウム酸化膜(AlO膜)を形成できる。このAlO膜を層状に積層させ、AlO膜を所望の層数繰り返すことにより必要とされる膜厚のアルミナ膜21をHfAlO膜20の直上に形成した。

【0028】

なお、1回目のPDAを省略したとすると、HfAlO膜20の形成に続けてアルミナ膜21を形成することになるので、第1の導電層19の上にハフニウムとアルミニウムを含む高誘電率絶縁膜20をALD法を用いて形成した後に、引き続きALD法をもちいて、アルミニウムの原料ガスTMAと酸化源のオゾンとの交互供給を行うことになる。HfAlO膜20とアルミナ膜21とでは、原料ガスのTMAが共通し、酸化源のオゾンも共通しているので、製造コストの上昇を最小限に抑えることができ、HfAlO膜20とアルミナ膜21に予期せぬ不純物が混入する等のダメージが発生しにくい。

【0029】

TMAのキャリアガスの流量は200sccmであり、オゾンの流量は5slmであり、オゾンの濃度は250g/m3とした。また、原料ガスのシリコン基板11への供給時間はそれぞれ、TMAが1秒、オゾンが3秒であった。更にTMAとオゾンの交互の供給の間に、真空チャンバ内の雰囲気のパージのための窒素(N2)を5slmで2〜3秒間流した。

【0030】

図12に示すように、TMAとオゾンの交互供給を10回繰り返すことにより、膜厚が0.8nmのアルミナ膜21を形成した。また、TMAとオゾンの交互供給の繰り返し回数のみを変更して、複数の不揮発性半導体記憶装置1を製造している。具体的には、繰り返し回数3回で膜厚が0.2nmの場合と、繰り返し回数5回で膜厚が0.4nmの場合と、繰り返し回数10回で膜厚が0.8nmの場合と、繰り返し回数15回で膜厚が1.2nmの場合と、繰り返し回数20回で膜厚が1.6nmの場合について、不揮発性半導体記憶装置1を製造している。また、比較例として、アルミナ膜21を省いただけの不揮発性半導体記憶装置も製造している。

【0031】

2回目のPDAとして、500−1200℃の温度で、例えば、炉でのアニールにおいて10分以上2時間以内、ランプアニールにおいて1秒−30分以内、アルミナ膜21のアニールを行う。この2回目のPDAにより、アルミナ膜21の高密度化を行い、膜質が改善される。また、1回目のPDAが省かれている場合は、この2回目のPDAにより、HfAlO膜20のアニールも行われ、HfAlO膜20は高密度化し、膜質が改善される。第2導電層22の成膜の際の露出面はアルミナ膜21で覆われているので、HfAlO膜20に起因するハフニウム原子が、第2導電層22の成膜の際の露出面に露出することはない。

【0032】

以上により、下層膜の高誘電率絶縁膜20と、上層膜のアルミナ膜21からなる積層構造を有しインターポリ絶縁膜となる第2の絶縁層が形成される。

【0033】

続いて図9に示すように、アルミナ膜21の上に制御ゲートとなる第2の導電層22を形成する。第2の導電層22は不揮発性半導体記憶装置1における制御電極となる。導電層22としては、例えば、ドーピングされたポリシリコン(POLY-Si)膜を用いることができる。ポリシリコン膜は、CVD法にて10−200nmの厚さに形成される。CVD法にてポリシリコン膜を形成する場合、原料ガスとしてシラン(SiH4)を用いるために、真空チャンバ内の雰囲気がシラン還元雰囲気になる。シラン還元雰囲気中の水素ラジカルは、不揮発性半導体記憶装置1の露出表面にハフニウムに結合した酸素原子があると、その酸素原子を抜き取る。HfAlO膜20が露出していると酸素原子が抜き取られてしまい、酸素欠損起因のリーク電流が発生しやすくなると考えられる。一方、シラン還元雰囲気中の水素ラジカルは、不揮発性半導体記憶装置1の露出表面にあるアルミニウムに結合した酸素原子を抜き取ることはできない。露出しているアルミナ膜21からは水素ラジカルは酸素原子を抜き取ることができず、このことにより、露出面からさらに深層にあるHfAlO膜20から水素ラジカルは酸素原子を抜き取ることができない。HfAlO膜20では、酸素欠損起因のリーク電流を低減することができる。

【0034】

HfAlO膜20の酸素欠損は、雰囲気が還元雰囲気になると生じるのであるから、第2の導電層22として、シランを原料ガスにポリシリコン膜を成膜する場合だけでなく、四塩化チタン(TiCl4)とアンモニア(NH3)を原料ガスとして窒化チタン(TiN)を成膜する場合などの他の原料ガス系についても酸素欠損起因のリーク電流を低減する効果がある。

【0035】

高誘電率絶縁膜20として、ハフニア(HfO)より比誘電率が低いにも関わらず、ハフニアではなくてハフニウムアルミネート(HfAlO)をもちいるのは、HfAlO膜の平面モフォロジーが良好だからである。HfO膜では薄膜になるとモフォロジが悪化し、HfO膜の上にアルミナ膜21を堆積しても、アルミナ膜21にピンホールなどが生じて膜厚の均一な水素ラジカルや酸素原子に対する拡散バリア膜を得ることが難しい。一方HfOにAlOを5%以上添加したHfAlO膜20は均一な膜厚の高誘電率絶縁膜を得ることが可能となり、HfAlO膜20の上に堆積したアルミナ膜も均一になり水素ラジカルや酸素原子の拡散バリア膜としての効果が有効となる。

【0036】

水素ラジカルや酸素原子に対する拡散バリア膜として、アルミナ膜21が好ましいのは、高誘電率絶縁膜20の形成と同様に、アルミナ膜21も酸化性雰囲気で成膜できるからである。拡散バリア膜としては窒化シリコン(SiN)膜などが考えられるが、SiN膜は還元性雰囲気で成膜されるので、形成時に高誘電率絶縁膜20にダメージを与えてしまう。アルミナ膜21は酸化性雰囲気で成膜が可能なため高誘電率絶縁膜20へのダメージを低減できる。また、アルミナ膜21のアルミニウムと酸素は高誘電率絶縁膜20の構成元素であるため、高誘電率絶縁膜20の形成時に同時に拡散バリア膜を形成できるというメリットもある。

【0037】

NAND型EEPROMのインターポリシリコン絶縁膜(IPD)にアルミナの拡散バリア膜21を伴ったHfAlO膜20を用いることによりフローティングゲート(FG)13、19の側壁酸化プロセス時に高誘電率絶縁膜20とポリシリコン電極13の界面のシリコン(Si)が酸化して酸化シリコン膜を形成して誘電率を下げることを抑制する効果がある。酸素はHfAlO膜20中を拡散しやすく、拡散した酸素がポリシリコン電極13を酸化して界面に酸化シリコン膜を形成する。しかし、HfAlO膜20とポリシリコン電極13の間にアルミナ膜21があると、アルミナ膜21が酸素のポリシリコン電極13への拡散を防ぐため酸化シリコン膜の形成を防ぐことができ、高い誘電率を有するIPDを最終的に得ることができる可能となる

図10と図11に示すように、第2の導電層22の上にレジスト膜24を塗布法により形成する。レジスト膜24をフォトリソグラフィ法により制御電極のパターンにパターニングしてレジストパターンを形成する。レジスト膜24をマスクに、RIE法により、第2の導電層22、アルミナ膜21、高誘電率絶縁膜20、第2の導電膜19、第1の導電膜13と第1の絶縁層12を選択エッチングする。第2の導電層22はアルミナ膜21をストッパーとして選択エッチングを行う。アルミナ膜21と高誘電率絶縁膜20は第2の導電膜19をストッパーとして選択エッチングを行う。第2の導電膜19と第1の導電膜13は第1の絶縁層12をストッパーとして選択エッチングを行う。第1の絶縁層12はシリコン基板11をストッパーとして選択エッチングを行う。エッチングされた第2の導電層22、アルミナ膜21、高誘電率絶縁膜20、第2の導電膜19、第1の導電膜13と第1の絶縁層12の積層構造は、ゲート構造と呼ばれる。このゲート構造に対して自己整合的に露出したシリコン基板11の表面から、イオン注入法によりn型不純物を導入する。レジスト膜24を除去する。注入した不純物を活性化する熱処理をして、ソース・ドレイン領域25をシリコン基板11内に形成する。以上で、ゲート構造とゲート構造の両側に配置されたソース・ドレイン領域25からなるメモリセルを複数個構成することができる。

【0038】

最後に、図1乃至図3に示すように、第2の導電層22、ソース・ドレイン領域25と素子分離絶縁膜18の上に、パッシベーション膜となる第3の絶縁層29をCVD法で形成する。第3の絶縁層29としては、シリコン酸化膜とシリコン窒化膜の積層膜を用いることができる。

【0039】

以上で、実施例1の不揮発性半導体記憶装置1の製造方法は終了する。

【0040】

上記の製造方法によって完成した不揮発性半導体記憶装置1のリーク電流を測定した。測定では、高誘電率絶縁膜20中の電界の強さが300MV/mになるように第1導電層13、19と第2導電層22の間に電圧を印加した場合に、高誘電率絶縁膜20を膜厚方向に流れるリーク電流の電流密度を測定した。

【0041】

測定結果は、図12に示すように、比較例のアルミナ膜21を省いただけの不揮発性半導体記憶装置におけるリーク電流の電流密度は、2×10−0A/m2であった。アルミナ膜21のTMAとオゾンの交互供給の繰り返し回数が3回で、アルミナ膜21の膜厚が0.2nmである不揮発性半導体記憶装置1におけるリーク電流の電流密度は、3×10−3A/m2であった。交互供給の繰り返し回数が5回で、膜厚が0.4nmである不揮発性半導体記憶装置1におけるリーク電流の電流密度は、1×10−3A/m2であった。交互供給の繰り返し回数が10回で、膜厚が0.8nmである不揮発性半導体記憶装置1におけるリーク電流の電流密度は、8×10−4A/m2であった。交互供給の繰り返し回数が15回で、膜厚が1.2nmである不揮発性半導体記憶装置1におけるリーク電流の電流密度は、2×10−3A/m2であった。交互供給の繰り返し回数が20回で、膜厚が1.6nmである不揮発性半導体記憶装置1におけるリーク電流の電流密度は、5×10−2A/m2であった。

【0042】

このように、アルミナ膜21を設けることにより、リーク電流の電流密度を40分の1以下に低減することができた。すなわち、アルミナ膜21のTMAとオゾンの交互供給の繰り返し回数を3回以上20回以下の範囲に設定するか、あるいは、アルミナ膜21の膜厚を0.2nm以上1.6nm以下の範囲に設定することにより、比較例に比べてリーク電流の電流密度を40分の1以下に低減することができた。

【0043】

さらに、アルミナ膜21のTMAとオゾンの交互供給の繰り返し回数を5回以上15回以下の範囲に設定するか、あるいは、アルミナ膜21の膜厚を0.4nm以上1.2nm以下の範囲に設定することにより、比較例に比べてリーク電流の電流密度を100分の1以下に低減することができた。

【0044】

特に、アルミナ膜21のTMAとオゾンの交互供給の繰り返し回数を10回に設定するか、あるいは、アルミナ膜21の膜厚を0.8nmに設定することにより、比較例に比べてリーク電流の電流密度を200分の1以下に低減することができた。

【0045】

また、実施例1では第2の導電層22としてポリシリコンについて述べたが、チタン(Ti)または窒化チタン(TiN)のような金属または金属窒化膜を第2の導電層22に用いる場合でも、リーク電流の電流密度を低減する効果があることを確認した。

【0046】

実施例1に示すようにインターポリ絶縁膜20、21に高誘電率絶縁膜であるHfAlO膜20を用いる際に、HfAlO膜20の上方の第2の導電層22のポリシリコン電極22とHfAlO膜20の間のみにアルミナ膜21を導入することによりリーク電流の低減を可能にしている。以下にその詳細を述べる

HfAlO膜20は比誘電率が10〜25の高誘電率絶縁膜でハフニウムの膜中の濃度を高めるほど比誘電率が大きくなる。このため、インターポリ絶縁膜として同じ容量の条件では、ハフニウムの膜中の濃度を高めることにより膜厚を厚くすることが可能となり、その結果としてリーク電流を低減することが可能となる。

【0047】

しかしながら、ハフニア(HfO2)の自由エネルギーは-253Kcal/molであり、アルミナ(Al2O3)の自由エネルギー-378Kcal/molより小さいことにも現れているように、ハフニアにおけるハフニウム原子と酸素原子との結合力は、アルミナにおけるアルミニウム原子と酸素原子との結合力より小さい。還元雰囲気において、ハフニウム原子と結合した酸素原子は、アルミニウム原子と結合した酸素原子より、還元雰囲気中に引き抜かれやすい。HfAlO膜20においては、還元雰囲気にさらされるとハフニウムの膜中の濃度が高くなるほど酸素欠損を生じやすくなる。そして、この酸素欠損はリーク電流を上昇させる原因になっている。このように、HfAlO膜において、高比誘電率化とリーク電流の低減化とはトレードオフの関係にある。HfAlO膜20を形成後にアルミナ膜21を形成することなくポリシリコン電極22を形成する場合、シラン還元雰囲気による酸素欠損起因のリーク電流は、ハフニウムのHfAlO膜20中の濃度の上昇と共に大きくなってしまう。これは、ハフニウムのHfAlO膜20中の濃度の上昇と共に、ハフニウム原子と結合する酸素原子のHfAlO膜20中の濃度が上昇しているからである。そこで、HfAlO膜20を形成後、ポリシリコン電極22を形成前にHfAlO膜20の上にアルミナ膜21を堆積することにより、露出表面がアルミニウム原子とアルミニウム原子と結合した酸素原子で覆われ、ハフニウム原子とハフニウム原子と結合した酸素原子は露出していないので、還元雰囲気下において酸素原子が抜き取られることはない。アルミナ膜21で覆われたHfAlO膜20は、シラン還元雰囲気下において、酸素欠損を生じることはなく、リーク電流の増加を抑制できる。

【0048】

なお、図12のアルミナ膜21の膜厚0.8nm、1.2nmと1.6nmの測定結果に現れているように、アルミナ膜21の比誘電率は8〜10とHfAlO膜20の比誘電率10〜25よりも小さいため、インターポリ絶縁膜20、21全体の容量はアルミナ膜21の膜厚を増加させると減少し、結果として同じ電界強度での測定では、アルミナ膜21の膜厚を増加させるとリーク電流が増加することになる。

【0049】

これらのデータより、リーク電流を低減するためにはアルミナ膜21は必要であるが、アルミナ膜が厚すぎるとリーク電流が増加してしまうことがわかる。したがって、リーク電流を効果的に低減するためには、最適な膜厚が存在する。図12より最適な膜厚は、0.2nm以上1.6nm以下の範囲であり、リーク電流を比較例の40分の1に低減することができる。さらに好ましくは、0.4nm以上1.2nm以下の範囲である。この範囲では、リーク電流を比較例の100分の1以下に低減することができる。なお、アルミナ膜21は、ALD法で成膜しているので、アルミニウムの原料ガスTMAと酸素源のオゾンとの交互供給の繰り返し回数は、膜厚に一対一に対応する。すなわち、最適な膜厚を最適な繰り返し回数で置き換えることができる。最適な繰り返し回数は、3回以上20回以下の範囲であり、さらに好ましくは、5回以上15回以下の範囲である。

【0050】

以上のように実施例1によれば、リーク電流が十分に抑制可能な高誘電率絶縁膜を有する半導体装置を提供できる。

【実施例2】

【0051】

本発明の実施例2に係る半導体装置も、図13に示すような、不揮発性半導体記憶装置1のNAND型EEPROMである。実施例2の不揮発性半導体記憶装置1では、インターポリ絶縁膜20、21に高誘電率絶縁膜20を使用するだけでなく、シリコン基板11と電荷蓄積層13、19との間に形成する第1の絶縁層12に高誘電率絶縁膜28を使用した場合である。

【0052】

不揮発性半導体記憶装置1は、シリコン基板である半導体領域11と、半導体領域11の上に設けられた高誘電率絶縁膜28と、高誘電率絶縁膜28の上に設けられたアルミナ膜27と、アルミナ膜27の上に設けられた導電層13、19とを有する。このことによっても、高誘電率絶縁膜28を経由して半導体領域11と導電層13、19の間を流れるリーク電流を低減することができる。

【0053】

実施例2の不揮発性半導体記憶装置1が、実施例1の不揮発性半導体記憶装置1と異なっている点は、第1の絶縁層12が、下層膜を高誘電率絶縁膜28とし、上層膜をアルミナ膜27とする積層構造をしている点である。高誘電率絶縁膜28には、アルミニウムを含む複合酸化物を用いることができる。このアルミニウムを含む複合酸化物としては、具体的には、ハフニウムアルミネート(HfAlO)、ジルコニウムアルミネート(ZrAlO)、ランタンアルミネート(LaAlO)等を用いることができる。

【0054】

次に、実施例2の不揮発性半導体記憶装置1の製造方法であるが、実施例1の製造方法とは、第1の絶縁層12の形成方法のみが異なる。実施例2の第1の絶縁層12の形成方法には、実施例1の高誘電率絶縁膜20とアルミナ膜21の形成方法をPDAの含めて適用して、高誘電率絶縁膜28とアルミナ膜27を形成する。そして、必要に応じて原料ガスとオゾンの交互供給の繰り返し回数を調整して所望の膜厚に設定している。

【0055】

そして、図12に示す結果と同様のリーク電流を低減する効果が第1の絶縁層12においても得られた。以上のように実施例2によっても、リーク電流が十分に抑制可能な高誘電率絶縁膜を有する半導体装置を提供できる。

【実施例3】

【0056】

本発明の実施例3に係る半導体装置も、図14に示すような、揮発性半導体記憶装置2のダイナミック・ランダム・アクセス・メモリ(DRAM)である。実施例3の揮発性半導体記憶装置2では、キャパシタ絶縁膜33、34に高誘電率絶縁膜33を使用し、さらに、選択トランジスタのゲート絶縁膜27、28に高誘電率絶縁膜28を使用している。

【0057】

揮発性半導体記憶装置2は、プレート電極領域である半導体領域31と、半導体領域31の上に設けられた高誘電率絶縁膜33と、高誘電率絶縁膜33の上に設けられたアルミナ膜34と、アルミナ膜34の上に設けられた蓄積電極である導電層36とを有する。このことにより、高誘電率絶縁膜33を経由して半導体領域31と導電層36の間を流れるリーク電流を低減することができる。

【0058】

また、揮発性半導体記憶装置2は、シリコン基板である半導体領域11と、半導体領域11の上に設けられた高誘電率絶縁膜28と、高誘電率絶縁膜28の上に設けられたアルミナ膜27と、アルミナ膜27の上に設けられた選択トランジスタのゲート電極となる導電層13とを有する。このことによっても、高誘電率絶縁膜28を経由して半導体領域11と導電層13の間を流れるリーク電流を低減することができる。

【0059】

揮発性半導体記憶装置2は、シリコン基板11、シリコン領域31、高誘電率絶縁膜33、アルミナ膜34、カラー酸化膜35、蓄積電極36、ソース・ドレイン領域25、高誘電率絶縁膜28、アルミナ膜27とゲート電極13を有している。揮発性半導体記憶装置2はディープトレンチ32を有し、高誘電率絶縁膜33とアルミナ膜34をキャパシタ絶縁膜とするキャパシタはディープトレンチ32に設けられる。また、揮発性半導体記憶装置2は選択トランジスタを有し、選択トランジスタは、ソース・ドレイン領域25、高誘電率絶縁膜28、アルミナ膜27とゲート電極13により構成される。選択トランジスタのソース・ドレイン領域25はキャパシタの電極である蓄積電極36に接続している。

【0060】

シリコン基板11には、p型の単結晶シリコン基板を用いることができる。シリコン基板11上にはディープトレンチ32が設けられている。

【0061】

シリコン領域31は、プレート電極として機能し、単結晶シリコンである。シリコン領域31の導電型は、シリコン基板11とは異なりn型である。シリコン領域31は、ディープトレンチ32の表面を含むように設けられている。キャパシタは、キャパシタ絶縁膜として機能する高誘電率絶縁膜33とアルミナ膜34を有し、さらに、キャパシタ絶縁膜33、34の両側にそれぞれ設けられるプレート電極31と蓄積電極36を有する。キャパシタ絶縁膜33、34は、下層膜を高誘電率絶縁膜33とし、上層膜をアルミナ膜34とする積層構造をしている。高誘電率絶縁膜33には、アルミニウムを含む複合酸化物を用いることができる。このアルミニウムを含む複合酸化物としては、具体的には、ハフニウムアルミネート(HfAlO)、ジルコニウムアルミネート(ZrAlO)、ランタンアルミネート(LaAlO)等を用いることができる。

【0062】

蓄積電極36は、アルミナ膜34の上に設けられ、ディープトレンチ32内に埋め込まれている。蓄積電極36は、n型の多結晶シリコンやポリシリコンでよい。

【0063】

カラー酸化膜35は、キャパシタ絶縁膜33、34の端面の上でディープトレンチ32内に設けられている。カラー酸化膜35は、シリコン領域31とソース・ドレイン領域25の間で寄生トランジスタがオンするのを防ぐ電気的素子分離膜として機能する。

【0064】

ソース・ドレイン領域25は、シリコン基板11の表面を含むシリコン基板11内に形成されている。ソース・ドレイン領域25は、不純物拡散層である。

【0065】

ゲート絶縁膜27、28は、シリコン基板11の上に形成されている。ゲート絶縁膜27、28は、下層膜を高誘電率絶縁膜28とし、上層膜をアルミナ膜27とする積層構造をしている。高誘電率絶縁膜28には、アルミニウムを含む複合酸化物を用いることができる。このアルミニウムを含む複合酸化物としては、具体的には、ハフニウムアルミネート(HfAlO)、ジルコニウムアルミネート(ZrAlO)、ランタンアルミネート(LaAlO)等を用いることができる。

【0066】

ゲート電極13は、ゲート絶縁膜27、28の上に形成されている。ゲート電極13は、n型の多結晶シリコンやポリシリコンでよい。

【0067】

実施例3の揮発性半導体記憶装置2は、基本的に従来の揮発性半導体記憶装置の製造方法と同じであるが、従来の製造方法とは、キャパシタ絶縁膜33、34の形成方法とゲート絶縁膜27、28の形成方法のみが異なる。ただ、これら実施例3のキャパシタ絶縁膜33、34の形成方法とゲート絶縁膜27、28の形成方法には、実施例1の高誘電率絶縁膜20とアルミナ膜21の形成方法をPDAも含めて適用して、高誘電率絶縁膜28、33とアルミナ膜27、34を形成する。そして、必要に応じて原料ガスとオゾンの交互供給の繰り返し回数を調整して所望の膜厚に設定している。

【0068】

揮発性半導体記憶装置2のキャパシタ絶縁膜33、34に高誘電率絶縁膜33を使用した場合にも、図12に示す結果と同様のリーク電流の低減を図ることが可能となり、揮発性半導体記憶装置2で良好なデバイス特性が得られた。

【0069】

揮発性半導体記憶装置2のゲート絶縁膜27、28に高誘電率絶縁膜28を使用した場合にも、図12に示す結果と同様のリーク電流の低減を図ることが可能となり、揮発性半導体記憶装置2で良好なデバイス特性が得られた。

【0070】

以上のように実施例3によっても、リーク電流が十分に抑制可能な高誘電率絶縁膜を有する半導体装置を提供できる。

【0071】

実施例1乃至3は、本発明を実施するにあたっての具体化の例を示したものに過ぎず、実施例1乃至3によって本発明の技術的範囲が限定的に解釈されてはならないものである。本発明は、その技術的思想、またはその主要な特徴から逸脱することなく、様々な形で実施することができる。すなわち、本発明の特許請求の範囲を逸脱しない範囲で、変更・改良や一部転用などが可能であり、これらすべて本発明の請求範囲内に包含されるものである。

【図面の簡単な説明】

【0072】

【図1】本発明の一実施形態に係る半導体装置の平面図である。

【図2】図1のII−II方向の断面図である。

【図3】図1のIII−III方向の断面図である。

【図4】本発明の一実施形態に係る半導体装置の製造途中の上面図である。

【図5】図4のV−V方向の断面図であり、本発明の一実施形態に係る半導体装置の製造途中の断面図(その1)である。

【図6】本発明の一実施形態に係る半導体装置の製造途中の断面図(その2)である。

【図7】本発明の一実施形態に係る半導体装置の製造途中の断面図(その3)である。

【図8】本発明の一実施形態に係る半導体装置の製造途中の断面図(その4)である。

【図9】本発明の一実施形態に係る半導体装置の製造途中の断面図(その5)である。

【図10】本発明の一実施形態に係る半導体装置の製造途中の断面図(その6)である。

【図11】図10のXI−XI方向の断面図であり、本発明の一実施形態に係る半導体装置の製造途中の断面図(その7)である。

【図12】本発明の一実施形態に係る半導体装置のインターポリ絶縁膜のリーク電流密度のアルミナ膜厚依存性を表すグラフである。

【図13】本発明の一実施形態に係る半導体装置の断面図である。

【図14】本発明の一実施形態に係る半導体装置の断面図である。

【符号の説明】

【0073】

1 不揮発性半導体記憶装置

2 揮発性半導体記憶装置

11 シリコン基板

12 第1絶縁層

13 第1導電層(第1導電膜)

14 シリコン窒化膜

15 シリコン酸化膜

16 レジストマスク

17 素子分離溝

18 素子分離絶縁膜

19 第1導電層(第2導電膜)

20 高誘電率絶縁膜(第2絶縁層)

21 アルミナ膜(第2絶縁層)

22 第2導電層

24 レジスト膜

25 ソース・ドレイン領域

27 高誘電率絶縁膜(第1絶縁層)

28 アルミナ膜(第1絶縁層)

29 第3絶縁層

31 プレート電極領域

32 トレンチ

33 高誘電率絶縁膜(キャパシタ絶縁層)

34 アルミナ膜(キャパシタ絶縁層)

35 カラー酸化膜

36 蓄積電極

【技術分野】

【0001】

本発明は、高誘電率絶縁膜を有する半導体装置およびその半導体装置の製造方法に関する。

【背景技術】

【0002】

近年、大規模集積回路(LSI)の高密度化に伴い、ゲート絶縁膜とキャパシタ絶縁膜は薄膜化の一途をたどっている。薄膜化に伴うリーク電流の上昇を避けるため、3次元化などのように半導体装置の構造を変更することによる対策を図る一方、高誘電率絶縁膜を用いることで物理膜厚を増やしリーク電流の上昇を抑えることが試みられている(例えば、特許文献1参照。)。

【0003】

特に、EEPROMなどの不揮発性半導体記憶装置においては、電荷蓄積層と制御電極との間に形成するインターポリ絶縁膜に関して、例えば、シリコン酸化膜/シリコン窒化膜/シリコン酸化膜の三層積層膜(ONO膜)を用い、高誘電率化を図るとともに、インターポリ絶縁膜の面積を増大させるために3次元的な構造を適用することも試みられている。しかし、半導体記憶装置のメモリセル間の距離が縮小するにつれ、隣接するセル間の干渉が著しく増大してデバイス特性を劣化させるため、3次元的な構造による面積の増大は困難であった。

【0004】

このため、次世代の不揮発性半導体記憶装置の実現するために、インターポリ絶縁膜として、従来よりも高誘電率を有する絶縁膜を適用することが必要となる。高誘電率絶縁膜を適用した結果、インターポリ絶縁膜の面積を増大させずに容量を大きくできるので、3次元的な構造にする必要がなくなり、製造工程を簡略化できる。結果として、メモリセルは高性能化し、かつ、半導体記憶装置の製造方法は容易になり、高歩留まりな製造方法を実現することが可能となる。

【0005】

高誘電率絶縁膜としてはハフニウムアルミネート(HfAlO)などの複合酸化物が、膜厚の均一性や量産性、低ダメージなどの理由からアトミックレイヤーデポジション(ALD)法等の化学気相成長(CVD)法により形成されている。しかし、高誘電率絶縁膜をEEPROMのインターポリ絶縁膜に用いる場合は、印加される電界が高いためにリーク電流が十分に抑制できないという問題があった。

【特許文献1】特開2005−109231号公報

【発明の開示】

【発明が解決しようとする課題】

【0006】

本発明は、リーク電流が十分に抑制可能な高誘電率絶縁膜を有する半導体装置を提供する。また、本発明は、リーク電流が十分に抑制可能な高誘電率絶縁膜を有する半導体装置の製造方法を提供する。

【課題を解決するための手段】

【0007】

本願発明の一態様によれば、半導体領域と、半導体領域の上に設けられ、少なくともアルミニウム以外の金属元素を含む高誘電率絶縁膜と、高誘電率絶縁膜の上に設けられたアルミナ膜と、アルミナ膜の上に設けられた導電層とを有することを特徴とする半導体装置が提供される。

【0008】

本願発明の一態様によれば、半導体領域の上に高誘電率絶縁膜をアトミックレイヤーデポジション法により成膜し、高誘電率絶縁膜の上にアルミナ膜をアトミックレイヤーデポジション法により成膜し、アルミナ膜をアニールし、アルミナ膜の上に導電層を還元雰囲気下で成膜することを特徴とする半導体装置の製造方法が提供される。

【発明の効果】

【0009】

本発明の一態様に係る半導体装置およびその製造方法によれば、リーク電流が十分に抑制可能な高誘電率絶縁膜を有する半導体装置を提供できる。また、リーク電流が十分に抑制可能な高誘電率絶縁膜を有する半導体装置の製造方法を提供できる。

【発明を実施するための最良の形態】

【0010】

次に、図面を参照して、本発明の実施の形態について説明する。なお、以下では本発明の実施形態を図面に基づいて説明するが、図解のためだけであり、本発明はそれらの図面に限定されるものではない。以下の図面の記載において、同一又は類似の部分には同一又は類似の符号を付している。また、図面は模式的なものであり、厚みと平面寸法との関係、各層の厚みの比率等は現実のものとは異なることに留意すべきである。

【実施例1】

【0011】

本発明の実施例1に係る半導体装置は、図1乃至図3に示すような、不揮発性半導体記憶装置1のNAND型電気的書き換え可能な不揮発性メモリ(EEPROM)である。実施例1は、不揮発性半導体記憶装置1の、電荷蓄積層13、19と制御電極22との間に形成するインターポリ絶縁膜20、21に高誘電率絶縁膜20を使用した場合である。不揮発性半導体記憶装置1は、半導体領域19と、半導体領域19の直上に設けられ、少なくともアルミニウム以外の金属元素を含む高誘電率絶縁膜20と、高誘電率絶縁膜20の上に設けられたアルミナ膜21と、アルミナ膜21の上に設けられた導電層22とを有する。このことにより、高誘電率絶縁膜20を経由して半導体領域19と導電層22の間を流れるリーク電流を低減することができる。

【0012】

不揮発性半導体記憶装置1は、半導体基板11を有している。半導体基板11には素子分離溝17が形成されている。素子分離溝17には素子分離絶縁膜18が埋め込まれている。素子分離絶縁膜18によって、複数の素子形成領域が区画され、分離されている。各素子形成領域では、半導体基板11の上に第1のゲート絶縁膜となる絶縁層12が設けられている。絶縁層12の上には浮遊ゲートになる導電層13、19が設けられている。導電層13、19は、導電膜13と導電膜19の積層構造をしている。導電膜13と19は、高濃度にドーピングされた半導体膜で構成されている。導電膜19の上には第2のゲート絶縁膜となる絶縁層20、21が設けられている。絶縁層20、21は、下層膜を高誘電率絶縁膜20とし、上層膜をアルミナ膜21とする積層構造をしている。高誘電率絶縁膜20には、アルミニウムを含む複合酸化物を用いることができる。このアルミニウムを含む複合酸化物としては、具体的には、ハフニウムアルミネート(HfAlO)、ジルコニウムアルミネート(ZrAlO)、ランタンアルミネート(LaAlO)等を用いることができる。アルミナ膜21の上には制御ゲートとなる導電層22が設けられている。導電層22の上にはパッシベーション膜となる絶縁層29が設けられている。絶縁層29は、ソース・ドレイン領域25の上にも配置されている。ソース・ドレイン領域25は、半導体基板11の表面を含むように半導体基板11内に設けられる。

【0013】

次に、実施例1の不揮発性半導体記憶装置1の製造方法について説明する。

【0014】

まず、図4と図5に示すように、p型シリコン(Si)基板11、もしくはn型シリコン基板中に形成したp型ウエル11の上に、第1の絶縁層12を1−15nm程度の厚さに形成する。第1の絶縁層12は、p型シリコン(Si)基板11の表面を酸化及び窒化する方法で形成する。第1の絶縁層12の上に化学気相成長(CVD)法によりドーピングされたポリシリコンを成膜することにより、第1の導電膜13を10−200nm程度の厚さに形成する。第1の導電膜13は浮遊ゲートであって電荷蓄積層となる。

【0015】

第1の導電膜13の上にCVD法によってシリコン窒化膜14を50−200nm程度の厚さに成膜する。さらに、シリコン窒化膜14の上にCVD法によってシリコン酸化膜15を50−400nm程度の厚さに形成する。シリコン酸化膜15の上にフォトレジストを塗布しレジスト膜を生成し、ホトリソグラフィ法にてパターニングしてレジストマスク16を形成する。

【0016】

レジストマスク16をマスクに用いて、シリコン窒化膜14をストッパーに用いて、シリコン酸化膜15を、反応性イオンエッチング(RIE)法にて、選択的にエッチングする。このシリコン酸化膜15のエッチング後にレジストマスク16を除去する。

【0017】

次いで、図6に示すように、シリコン酸化膜15をマスクとして、シリコン窒化膜14をRIE法にてエッチングし、続いて、第1の導電膜13、第1の絶縁層12及びシリコン基板11をRIE法にてエッチングして素子分離溝17を形成する。エッチング後に、エッチングにより形成された第1の導電膜13、第1の絶縁層12及びシリコン基板11の側面のダメージを除去するための高温後酸化工程を行う。

【0018】

シリコン酸化膜等の素子分離絶縁膜18をCVD法により200−1500nmの厚さに成膜し、素子分離絶縁膜18を素子分離溝17に埋め込む。素子分離絶縁膜18を窒素雰囲気又は酸素雰囲気での高温の熱処理を行い、素子分離絶縁膜18を高密度化する。ケミカルメカニカルポリッシング(CMP:Chemical Mechanical Polishing)法によって、シリコン窒化膜14をストッパーとして素子分離絶縁膜18の平坦化を行う。シリコン窒化膜14の上の素子分離絶縁膜18が除去される。シリコン酸化膜18、12と選択比をもってシリコン窒化膜14をエッチングすることが可能なホット燐酸(H2PO4)を用いて、シリコン窒化膜14を除去する。これにより、図6に示すような断面構造が得られる。

【0019】

実施例1では、素子分離溝17を形成するに際して、シリコン窒化膜14及びシリコン酸化膜15の積層膜をマスクとして用いているが、シリコン窒化膜14またはシリコン酸化膜15の膜厚及びRIE法の条件を適切にすれば、単層のシリコン窒化膜14、単層のシリコン酸化膜15、或いは他の単層・多層膜のいずれでもシリコン(Si)との選択比が取れる材料からなる膜であれば実施可能である。

【0020】

図7に示すように、シリコン窒化膜14の除去後に得られた溝内を埋め込むように第1の導電膜13の上に、段差被覆性に優れた成膜方法を用いて、第2の導電膜19を成膜する。第2の導電膜19としては、ドーピングされたポリシリコン膜を用いることができる。第1の導電膜13と第2の導電膜19とは積層され、第1の導電膜13と第2の導電膜19とで第1の導電層を構成する。次いで、CMP法により素子分離絶縁膜18をストッパーにして第2の導電膜19の平坦化を行う。素子分離絶縁膜18の上に堆積した第2の導電膜19は除去される。

【0021】

図8に示すように、平坦化した導電膜19と素子分離絶縁膜18の上にいわゆるシリコン酸化膜よりも高誘電率を有する高誘電率絶縁膜20を形成する。ここで、高誘電率絶縁膜20としては、シリコン酸化膜(SiO2膜)の比誘電率3.8−4よりも大きく、特に従来のONO膜で得られていた比誘電率5−5.5程度よりも大きい膜であることが望ましい。実施例1では高誘電率絶縁膜20としてハフニウム(Hf)とアルミニウム(Al)を含む複合酸化膜であるハフニウムアルミネート(HfAlO)膜を用いた。以下にHfAlO膜のALD法による形成方法の詳細を述べる。

【0022】

ここまで製造してきたシリコン基板11を、圧力が39.9Paに保持された真空チャンバ中に搬入し、シリコン基板11を基板温度290℃に加熱する。シリコン基板11にアルミニウム(Al)の原料ガスであるトリメチルアルミニウム(TMA:trimethylaluminum)と酸化剤であるオゾン(O3)を交互に流し供給することにより、アルミニウム原子層と酸素原子層からなるアルミニウム酸化膜(AlO膜)を形成できる。また、シリコン基板11にハフニウム(Hf)の原料ガスであるテトラキスエチルメチルアミノハフニウム(TEMAH:tetrakis-ethylmethylamino-hafunium)とオゾンを交互に流し供給することにより、ハフニウム原子層と酸素原子層からなるハフニウム酸化膜(HfO膜)を形成できる。このAlO膜とHfO膜を層状に積層させ、AlO膜とHfO膜をそれぞれ所望の層数繰り返すことにより必要とされるアルミニウムとハフニウムの組成比および膜厚のHfAlO膜を形成した。

【0023】

TMA、TEMAHのキャリアガスの流量はそれぞれ200sccm、500sccmであり、オゾンの流量は5slmであり、オゾンの濃度は250g/m3とした。また、原料ガスのシリコン基板11への供給時間はそれぞれ、TMAが1秒、TEMAH が2秒、オゾンが3秒であった。更にTMAとオゾンの交互の供給の間と、TEMAHとオゾンの交互の供給の間に、真空チャンバ内の雰囲気のパージのための窒素(N2)を5slmで2〜3秒間流した。

【0024】

具体的な交互の供給の回数としては、TEMAHとオゾンの交互供給を13回繰り返すごとにTMAとオゾンの交互供給を1回行うというシーケンスを15回繰り返した。このことにより、膜厚が20nmのHfAlO膜20を形成した。ここで、TEMAHとオゾンの交互供給の13回を増減することで、アルミニウムとハフニウムの組成比を変更することができる。また、シーケンスの繰り返しの15回を増減することで、HfAlO膜20の膜厚を増減することができる。

【0025】

その後、ポストデポジションアニール(PDA)として、500−1200℃の温度で、例えば、炉でのアニールにおいて10分以上2時間以内、ランプアニールにおいて1秒−30分以内、アニールを行う。この1回目のPDAにより、HfAlO膜20の高密度化を行い、膜質が改善される。なお、1回目のPDAは、後述する2回目のPDAにより省略することが可能である。ただ、1回目のPDAを行うことにより、HfAlO膜20が高密度化されているので後述するアルミナ膜21が2回目のPDAの際にHfAlO膜20中に拡散しにくくなる。このことにより、第2導電層22の成膜の際の露出面を、より薄いアルミナ膜21で、ハフニウム原子が露出しないようにアルミニウム原子で覆うことができる。

【0026】

実施例1では、1回目のPDAを省略したとすると、HfAlO膜20の形成の後に、アルミナ(Al2O3)膜21をHfAlO膜20の上に成膜する。以下にアルミナ膜のALD法による形成方法の詳細を述べる。

【0027】

シリコン基板11は真空チャンバ中に入れたまま、チャンバ内の圧力も39.9Paに保持し、シリコン基板11の基板温度も290℃に保持する。シリコン基板11にTMAとオゾンを交互に流し供給することにより、アルミニウム原子層と酸素原子層からなるアルミニウム酸化膜(AlO膜)を形成できる。このAlO膜を層状に積層させ、AlO膜を所望の層数繰り返すことにより必要とされる膜厚のアルミナ膜21をHfAlO膜20の直上に形成した。

【0028】

なお、1回目のPDAを省略したとすると、HfAlO膜20の形成に続けてアルミナ膜21を形成することになるので、第1の導電層19の上にハフニウムとアルミニウムを含む高誘電率絶縁膜20をALD法を用いて形成した後に、引き続きALD法をもちいて、アルミニウムの原料ガスTMAと酸化源のオゾンとの交互供給を行うことになる。HfAlO膜20とアルミナ膜21とでは、原料ガスのTMAが共通し、酸化源のオゾンも共通しているので、製造コストの上昇を最小限に抑えることができ、HfAlO膜20とアルミナ膜21に予期せぬ不純物が混入する等のダメージが発生しにくい。

【0029】

TMAのキャリアガスの流量は200sccmであり、オゾンの流量は5slmであり、オゾンの濃度は250g/m3とした。また、原料ガスのシリコン基板11への供給時間はそれぞれ、TMAが1秒、オゾンが3秒であった。更にTMAとオゾンの交互の供給の間に、真空チャンバ内の雰囲気のパージのための窒素(N2)を5slmで2〜3秒間流した。

【0030】

図12に示すように、TMAとオゾンの交互供給を10回繰り返すことにより、膜厚が0.8nmのアルミナ膜21を形成した。また、TMAとオゾンの交互供給の繰り返し回数のみを変更して、複数の不揮発性半導体記憶装置1を製造している。具体的には、繰り返し回数3回で膜厚が0.2nmの場合と、繰り返し回数5回で膜厚が0.4nmの場合と、繰り返し回数10回で膜厚が0.8nmの場合と、繰り返し回数15回で膜厚が1.2nmの場合と、繰り返し回数20回で膜厚が1.6nmの場合について、不揮発性半導体記憶装置1を製造している。また、比較例として、アルミナ膜21を省いただけの不揮発性半導体記憶装置も製造している。

【0031】

2回目のPDAとして、500−1200℃の温度で、例えば、炉でのアニールにおいて10分以上2時間以内、ランプアニールにおいて1秒−30分以内、アルミナ膜21のアニールを行う。この2回目のPDAにより、アルミナ膜21の高密度化を行い、膜質が改善される。また、1回目のPDAが省かれている場合は、この2回目のPDAにより、HfAlO膜20のアニールも行われ、HfAlO膜20は高密度化し、膜質が改善される。第2導電層22の成膜の際の露出面はアルミナ膜21で覆われているので、HfAlO膜20に起因するハフニウム原子が、第2導電層22の成膜の際の露出面に露出することはない。

【0032】

以上により、下層膜の高誘電率絶縁膜20と、上層膜のアルミナ膜21からなる積層構造を有しインターポリ絶縁膜となる第2の絶縁層が形成される。

【0033】

続いて図9に示すように、アルミナ膜21の上に制御ゲートとなる第2の導電層22を形成する。第2の導電層22は不揮発性半導体記憶装置1における制御電極となる。導電層22としては、例えば、ドーピングされたポリシリコン(POLY-Si)膜を用いることができる。ポリシリコン膜は、CVD法にて10−200nmの厚さに形成される。CVD法にてポリシリコン膜を形成する場合、原料ガスとしてシラン(SiH4)を用いるために、真空チャンバ内の雰囲気がシラン還元雰囲気になる。シラン還元雰囲気中の水素ラジカルは、不揮発性半導体記憶装置1の露出表面にハフニウムに結合した酸素原子があると、その酸素原子を抜き取る。HfAlO膜20が露出していると酸素原子が抜き取られてしまい、酸素欠損起因のリーク電流が発生しやすくなると考えられる。一方、シラン還元雰囲気中の水素ラジカルは、不揮発性半導体記憶装置1の露出表面にあるアルミニウムに結合した酸素原子を抜き取ることはできない。露出しているアルミナ膜21からは水素ラジカルは酸素原子を抜き取ることができず、このことにより、露出面からさらに深層にあるHfAlO膜20から水素ラジカルは酸素原子を抜き取ることができない。HfAlO膜20では、酸素欠損起因のリーク電流を低減することができる。

【0034】

HfAlO膜20の酸素欠損は、雰囲気が還元雰囲気になると生じるのであるから、第2の導電層22として、シランを原料ガスにポリシリコン膜を成膜する場合だけでなく、四塩化チタン(TiCl4)とアンモニア(NH3)を原料ガスとして窒化チタン(TiN)を成膜する場合などの他の原料ガス系についても酸素欠損起因のリーク電流を低減する効果がある。

【0035】

高誘電率絶縁膜20として、ハフニア(HfO)より比誘電率が低いにも関わらず、ハフニアではなくてハフニウムアルミネート(HfAlO)をもちいるのは、HfAlO膜の平面モフォロジーが良好だからである。HfO膜では薄膜になるとモフォロジが悪化し、HfO膜の上にアルミナ膜21を堆積しても、アルミナ膜21にピンホールなどが生じて膜厚の均一な水素ラジカルや酸素原子に対する拡散バリア膜を得ることが難しい。一方HfOにAlOを5%以上添加したHfAlO膜20は均一な膜厚の高誘電率絶縁膜を得ることが可能となり、HfAlO膜20の上に堆積したアルミナ膜も均一になり水素ラジカルや酸素原子の拡散バリア膜としての効果が有効となる。

【0036】

水素ラジカルや酸素原子に対する拡散バリア膜として、アルミナ膜21が好ましいのは、高誘電率絶縁膜20の形成と同様に、アルミナ膜21も酸化性雰囲気で成膜できるからである。拡散バリア膜としては窒化シリコン(SiN)膜などが考えられるが、SiN膜は還元性雰囲気で成膜されるので、形成時に高誘電率絶縁膜20にダメージを与えてしまう。アルミナ膜21は酸化性雰囲気で成膜が可能なため高誘電率絶縁膜20へのダメージを低減できる。また、アルミナ膜21のアルミニウムと酸素は高誘電率絶縁膜20の構成元素であるため、高誘電率絶縁膜20の形成時に同時に拡散バリア膜を形成できるというメリットもある。

【0037】

NAND型EEPROMのインターポリシリコン絶縁膜(IPD)にアルミナの拡散バリア膜21を伴ったHfAlO膜20を用いることによりフローティングゲート(FG)13、19の側壁酸化プロセス時に高誘電率絶縁膜20とポリシリコン電極13の界面のシリコン(Si)が酸化して酸化シリコン膜を形成して誘電率を下げることを抑制する効果がある。酸素はHfAlO膜20中を拡散しやすく、拡散した酸素がポリシリコン電極13を酸化して界面に酸化シリコン膜を形成する。しかし、HfAlO膜20とポリシリコン電極13の間にアルミナ膜21があると、アルミナ膜21が酸素のポリシリコン電極13への拡散を防ぐため酸化シリコン膜の形成を防ぐことができ、高い誘電率を有するIPDを最終的に得ることができる可能となる

図10と図11に示すように、第2の導電層22の上にレジスト膜24を塗布法により形成する。レジスト膜24をフォトリソグラフィ法により制御電極のパターンにパターニングしてレジストパターンを形成する。レジスト膜24をマスクに、RIE法により、第2の導電層22、アルミナ膜21、高誘電率絶縁膜20、第2の導電膜19、第1の導電膜13と第1の絶縁層12を選択エッチングする。第2の導電層22はアルミナ膜21をストッパーとして選択エッチングを行う。アルミナ膜21と高誘電率絶縁膜20は第2の導電膜19をストッパーとして選択エッチングを行う。第2の導電膜19と第1の導電膜13は第1の絶縁層12をストッパーとして選択エッチングを行う。第1の絶縁層12はシリコン基板11をストッパーとして選択エッチングを行う。エッチングされた第2の導電層22、アルミナ膜21、高誘電率絶縁膜20、第2の導電膜19、第1の導電膜13と第1の絶縁層12の積層構造は、ゲート構造と呼ばれる。このゲート構造に対して自己整合的に露出したシリコン基板11の表面から、イオン注入法によりn型不純物を導入する。レジスト膜24を除去する。注入した不純物を活性化する熱処理をして、ソース・ドレイン領域25をシリコン基板11内に形成する。以上で、ゲート構造とゲート構造の両側に配置されたソース・ドレイン領域25からなるメモリセルを複数個構成することができる。

【0038】

最後に、図1乃至図3に示すように、第2の導電層22、ソース・ドレイン領域25と素子分離絶縁膜18の上に、パッシベーション膜となる第3の絶縁層29をCVD法で形成する。第3の絶縁層29としては、シリコン酸化膜とシリコン窒化膜の積層膜を用いることができる。

【0039】

以上で、実施例1の不揮発性半導体記憶装置1の製造方法は終了する。

【0040】

上記の製造方法によって完成した不揮発性半導体記憶装置1のリーク電流を測定した。測定では、高誘電率絶縁膜20中の電界の強さが300MV/mになるように第1導電層13、19と第2導電層22の間に電圧を印加した場合に、高誘電率絶縁膜20を膜厚方向に流れるリーク電流の電流密度を測定した。

【0041】

測定結果は、図12に示すように、比較例のアルミナ膜21を省いただけの不揮発性半導体記憶装置におけるリーク電流の電流密度は、2×10−0A/m2であった。アルミナ膜21のTMAとオゾンの交互供給の繰り返し回数が3回で、アルミナ膜21の膜厚が0.2nmである不揮発性半導体記憶装置1におけるリーク電流の電流密度は、3×10−3A/m2であった。交互供給の繰り返し回数が5回で、膜厚が0.4nmである不揮発性半導体記憶装置1におけるリーク電流の電流密度は、1×10−3A/m2であった。交互供給の繰り返し回数が10回で、膜厚が0.8nmである不揮発性半導体記憶装置1におけるリーク電流の電流密度は、8×10−4A/m2であった。交互供給の繰り返し回数が15回で、膜厚が1.2nmである不揮発性半導体記憶装置1におけるリーク電流の電流密度は、2×10−3A/m2であった。交互供給の繰り返し回数が20回で、膜厚が1.6nmである不揮発性半導体記憶装置1におけるリーク電流の電流密度は、5×10−2A/m2であった。

【0042】

このように、アルミナ膜21を設けることにより、リーク電流の電流密度を40分の1以下に低減することができた。すなわち、アルミナ膜21のTMAとオゾンの交互供給の繰り返し回数を3回以上20回以下の範囲に設定するか、あるいは、アルミナ膜21の膜厚を0.2nm以上1.6nm以下の範囲に設定することにより、比較例に比べてリーク電流の電流密度を40分の1以下に低減することができた。

【0043】

さらに、アルミナ膜21のTMAとオゾンの交互供給の繰り返し回数を5回以上15回以下の範囲に設定するか、あるいは、アルミナ膜21の膜厚を0.4nm以上1.2nm以下の範囲に設定することにより、比較例に比べてリーク電流の電流密度を100分の1以下に低減することができた。

【0044】

特に、アルミナ膜21のTMAとオゾンの交互供給の繰り返し回数を10回に設定するか、あるいは、アルミナ膜21の膜厚を0.8nmに設定することにより、比較例に比べてリーク電流の電流密度を200分の1以下に低減することができた。

【0045】

また、実施例1では第2の導電層22としてポリシリコンについて述べたが、チタン(Ti)または窒化チタン(TiN)のような金属または金属窒化膜を第2の導電層22に用いる場合でも、リーク電流の電流密度を低減する効果があることを確認した。

【0046】

実施例1に示すようにインターポリ絶縁膜20、21に高誘電率絶縁膜であるHfAlO膜20を用いる際に、HfAlO膜20の上方の第2の導電層22のポリシリコン電極22とHfAlO膜20の間のみにアルミナ膜21を導入することによりリーク電流の低減を可能にしている。以下にその詳細を述べる

HfAlO膜20は比誘電率が10〜25の高誘電率絶縁膜でハフニウムの膜中の濃度を高めるほど比誘電率が大きくなる。このため、インターポリ絶縁膜として同じ容量の条件では、ハフニウムの膜中の濃度を高めることにより膜厚を厚くすることが可能となり、その結果としてリーク電流を低減することが可能となる。

【0047】

しかしながら、ハフニア(HfO2)の自由エネルギーは-253Kcal/molであり、アルミナ(Al2O3)の自由エネルギー-378Kcal/molより小さいことにも現れているように、ハフニアにおけるハフニウム原子と酸素原子との結合力は、アルミナにおけるアルミニウム原子と酸素原子との結合力より小さい。還元雰囲気において、ハフニウム原子と結合した酸素原子は、アルミニウム原子と結合した酸素原子より、還元雰囲気中に引き抜かれやすい。HfAlO膜20においては、還元雰囲気にさらされるとハフニウムの膜中の濃度が高くなるほど酸素欠損を生じやすくなる。そして、この酸素欠損はリーク電流を上昇させる原因になっている。このように、HfAlO膜において、高比誘電率化とリーク電流の低減化とはトレードオフの関係にある。HfAlO膜20を形成後にアルミナ膜21を形成することなくポリシリコン電極22を形成する場合、シラン還元雰囲気による酸素欠損起因のリーク電流は、ハフニウムのHfAlO膜20中の濃度の上昇と共に大きくなってしまう。これは、ハフニウムのHfAlO膜20中の濃度の上昇と共に、ハフニウム原子と結合する酸素原子のHfAlO膜20中の濃度が上昇しているからである。そこで、HfAlO膜20を形成後、ポリシリコン電極22を形成前にHfAlO膜20の上にアルミナ膜21を堆積することにより、露出表面がアルミニウム原子とアルミニウム原子と結合した酸素原子で覆われ、ハフニウム原子とハフニウム原子と結合した酸素原子は露出していないので、還元雰囲気下において酸素原子が抜き取られることはない。アルミナ膜21で覆われたHfAlO膜20は、シラン還元雰囲気下において、酸素欠損を生じることはなく、リーク電流の増加を抑制できる。

【0048】

なお、図12のアルミナ膜21の膜厚0.8nm、1.2nmと1.6nmの測定結果に現れているように、アルミナ膜21の比誘電率は8〜10とHfAlO膜20の比誘電率10〜25よりも小さいため、インターポリ絶縁膜20、21全体の容量はアルミナ膜21の膜厚を増加させると減少し、結果として同じ電界強度での測定では、アルミナ膜21の膜厚を増加させるとリーク電流が増加することになる。

【0049】

これらのデータより、リーク電流を低減するためにはアルミナ膜21は必要であるが、アルミナ膜が厚すぎるとリーク電流が増加してしまうことがわかる。したがって、リーク電流を効果的に低減するためには、最適な膜厚が存在する。図12より最適な膜厚は、0.2nm以上1.6nm以下の範囲であり、リーク電流を比較例の40分の1に低減することができる。さらに好ましくは、0.4nm以上1.2nm以下の範囲である。この範囲では、リーク電流を比較例の100分の1以下に低減することができる。なお、アルミナ膜21は、ALD法で成膜しているので、アルミニウムの原料ガスTMAと酸素源のオゾンとの交互供給の繰り返し回数は、膜厚に一対一に対応する。すなわち、最適な膜厚を最適な繰り返し回数で置き換えることができる。最適な繰り返し回数は、3回以上20回以下の範囲であり、さらに好ましくは、5回以上15回以下の範囲である。

【0050】

以上のように実施例1によれば、リーク電流が十分に抑制可能な高誘電率絶縁膜を有する半導体装置を提供できる。

【実施例2】

【0051】

本発明の実施例2に係る半導体装置も、図13に示すような、不揮発性半導体記憶装置1のNAND型EEPROMである。実施例2の不揮発性半導体記憶装置1では、インターポリ絶縁膜20、21に高誘電率絶縁膜20を使用するだけでなく、シリコン基板11と電荷蓄積層13、19との間に形成する第1の絶縁層12に高誘電率絶縁膜28を使用した場合である。

【0052】

不揮発性半導体記憶装置1は、シリコン基板である半導体領域11と、半導体領域11の上に設けられた高誘電率絶縁膜28と、高誘電率絶縁膜28の上に設けられたアルミナ膜27と、アルミナ膜27の上に設けられた導電層13、19とを有する。このことによっても、高誘電率絶縁膜28を経由して半導体領域11と導電層13、19の間を流れるリーク電流を低減することができる。

【0053】

実施例2の不揮発性半導体記憶装置1が、実施例1の不揮発性半導体記憶装置1と異なっている点は、第1の絶縁層12が、下層膜を高誘電率絶縁膜28とし、上層膜をアルミナ膜27とする積層構造をしている点である。高誘電率絶縁膜28には、アルミニウムを含む複合酸化物を用いることができる。このアルミニウムを含む複合酸化物としては、具体的には、ハフニウムアルミネート(HfAlO)、ジルコニウムアルミネート(ZrAlO)、ランタンアルミネート(LaAlO)等を用いることができる。

【0054】

次に、実施例2の不揮発性半導体記憶装置1の製造方法であるが、実施例1の製造方法とは、第1の絶縁層12の形成方法のみが異なる。実施例2の第1の絶縁層12の形成方法には、実施例1の高誘電率絶縁膜20とアルミナ膜21の形成方法をPDAの含めて適用して、高誘電率絶縁膜28とアルミナ膜27を形成する。そして、必要に応じて原料ガスとオゾンの交互供給の繰り返し回数を調整して所望の膜厚に設定している。

【0055】

そして、図12に示す結果と同様のリーク電流を低減する効果が第1の絶縁層12においても得られた。以上のように実施例2によっても、リーク電流が十分に抑制可能な高誘電率絶縁膜を有する半導体装置を提供できる。

【実施例3】

【0056】

本発明の実施例3に係る半導体装置も、図14に示すような、揮発性半導体記憶装置2のダイナミック・ランダム・アクセス・メモリ(DRAM)である。実施例3の揮発性半導体記憶装置2では、キャパシタ絶縁膜33、34に高誘電率絶縁膜33を使用し、さらに、選択トランジスタのゲート絶縁膜27、28に高誘電率絶縁膜28を使用している。

【0057】

揮発性半導体記憶装置2は、プレート電極領域である半導体領域31と、半導体領域31の上に設けられた高誘電率絶縁膜33と、高誘電率絶縁膜33の上に設けられたアルミナ膜34と、アルミナ膜34の上に設けられた蓄積電極である導電層36とを有する。このことにより、高誘電率絶縁膜33を経由して半導体領域31と導電層36の間を流れるリーク電流を低減することができる。

【0058】

また、揮発性半導体記憶装置2は、シリコン基板である半導体領域11と、半導体領域11の上に設けられた高誘電率絶縁膜28と、高誘電率絶縁膜28の上に設けられたアルミナ膜27と、アルミナ膜27の上に設けられた選択トランジスタのゲート電極となる導電層13とを有する。このことによっても、高誘電率絶縁膜28を経由して半導体領域11と導電層13の間を流れるリーク電流を低減することができる。

【0059】

揮発性半導体記憶装置2は、シリコン基板11、シリコン領域31、高誘電率絶縁膜33、アルミナ膜34、カラー酸化膜35、蓄積電極36、ソース・ドレイン領域25、高誘電率絶縁膜28、アルミナ膜27とゲート電極13を有している。揮発性半導体記憶装置2はディープトレンチ32を有し、高誘電率絶縁膜33とアルミナ膜34をキャパシタ絶縁膜とするキャパシタはディープトレンチ32に設けられる。また、揮発性半導体記憶装置2は選択トランジスタを有し、選択トランジスタは、ソース・ドレイン領域25、高誘電率絶縁膜28、アルミナ膜27とゲート電極13により構成される。選択トランジスタのソース・ドレイン領域25はキャパシタの電極である蓄積電極36に接続している。

【0060】

シリコン基板11には、p型の単結晶シリコン基板を用いることができる。シリコン基板11上にはディープトレンチ32が設けられている。

【0061】

シリコン領域31は、プレート電極として機能し、単結晶シリコンである。シリコン領域31の導電型は、シリコン基板11とは異なりn型である。シリコン領域31は、ディープトレンチ32の表面を含むように設けられている。キャパシタは、キャパシタ絶縁膜として機能する高誘電率絶縁膜33とアルミナ膜34を有し、さらに、キャパシタ絶縁膜33、34の両側にそれぞれ設けられるプレート電極31と蓄積電極36を有する。キャパシタ絶縁膜33、34は、下層膜を高誘電率絶縁膜33とし、上層膜をアルミナ膜34とする積層構造をしている。高誘電率絶縁膜33には、アルミニウムを含む複合酸化物を用いることができる。このアルミニウムを含む複合酸化物としては、具体的には、ハフニウムアルミネート(HfAlO)、ジルコニウムアルミネート(ZrAlO)、ランタンアルミネート(LaAlO)等を用いることができる。

【0062】

蓄積電極36は、アルミナ膜34の上に設けられ、ディープトレンチ32内に埋め込まれている。蓄積電極36は、n型の多結晶シリコンやポリシリコンでよい。

【0063】

カラー酸化膜35は、キャパシタ絶縁膜33、34の端面の上でディープトレンチ32内に設けられている。カラー酸化膜35は、シリコン領域31とソース・ドレイン領域25の間で寄生トランジスタがオンするのを防ぐ電気的素子分離膜として機能する。

【0064】

ソース・ドレイン領域25は、シリコン基板11の表面を含むシリコン基板11内に形成されている。ソース・ドレイン領域25は、不純物拡散層である。

【0065】

ゲート絶縁膜27、28は、シリコン基板11の上に形成されている。ゲート絶縁膜27、28は、下層膜を高誘電率絶縁膜28とし、上層膜をアルミナ膜27とする積層構造をしている。高誘電率絶縁膜28には、アルミニウムを含む複合酸化物を用いることができる。このアルミニウムを含む複合酸化物としては、具体的には、ハフニウムアルミネート(HfAlO)、ジルコニウムアルミネート(ZrAlO)、ランタンアルミネート(LaAlO)等を用いることができる。

【0066】

ゲート電極13は、ゲート絶縁膜27、28の上に形成されている。ゲート電極13は、n型の多結晶シリコンやポリシリコンでよい。

【0067】

実施例3の揮発性半導体記憶装置2は、基本的に従来の揮発性半導体記憶装置の製造方法と同じであるが、従来の製造方法とは、キャパシタ絶縁膜33、34の形成方法とゲート絶縁膜27、28の形成方法のみが異なる。ただ、これら実施例3のキャパシタ絶縁膜33、34の形成方法とゲート絶縁膜27、28の形成方法には、実施例1の高誘電率絶縁膜20とアルミナ膜21の形成方法をPDAも含めて適用して、高誘電率絶縁膜28、33とアルミナ膜27、34を形成する。そして、必要に応じて原料ガスとオゾンの交互供給の繰り返し回数を調整して所望の膜厚に設定している。

【0068】

揮発性半導体記憶装置2のキャパシタ絶縁膜33、34に高誘電率絶縁膜33を使用した場合にも、図12に示す結果と同様のリーク電流の低減を図ることが可能となり、揮発性半導体記憶装置2で良好なデバイス特性が得られた。

【0069】

揮発性半導体記憶装置2のゲート絶縁膜27、28に高誘電率絶縁膜28を使用した場合にも、図12に示す結果と同様のリーク電流の低減を図ることが可能となり、揮発性半導体記憶装置2で良好なデバイス特性が得られた。

【0070】

以上のように実施例3によっても、リーク電流が十分に抑制可能な高誘電率絶縁膜を有する半導体装置を提供できる。

【0071】

実施例1乃至3は、本発明を実施するにあたっての具体化の例を示したものに過ぎず、実施例1乃至3によって本発明の技術的範囲が限定的に解釈されてはならないものである。本発明は、その技術的思想、またはその主要な特徴から逸脱することなく、様々な形で実施することができる。すなわち、本発明の特許請求の範囲を逸脱しない範囲で、変更・改良や一部転用などが可能であり、これらすべて本発明の請求範囲内に包含されるものである。

【図面の簡単な説明】

【0072】

【図1】本発明の一実施形態に係る半導体装置の平面図である。

【図2】図1のII−II方向の断面図である。

【図3】図1のIII−III方向の断面図である。

【図4】本発明の一実施形態に係る半導体装置の製造途中の上面図である。

【図5】図4のV−V方向の断面図であり、本発明の一実施形態に係る半導体装置の製造途中の断面図(その1)である。

【図6】本発明の一実施形態に係る半導体装置の製造途中の断面図(その2)である。

【図7】本発明の一実施形態に係る半導体装置の製造途中の断面図(その3)である。

【図8】本発明の一実施形態に係る半導体装置の製造途中の断面図(その4)である。

【図9】本発明の一実施形態に係る半導体装置の製造途中の断面図(その5)である。

【図10】本発明の一実施形態に係る半導体装置の製造途中の断面図(その6)である。

【図11】図10のXI−XI方向の断面図であり、本発明の一実施形態に係る半導体装置の製造途中の断面図(その7)である。

【図12】本発明の一実施形態に係る半導体装置のインターポリ絶縁膜のリーク電流密度のアルミナ膜厚依存性を表すグラフである。

【図13】本発明の一実施形態に係る半導体装置の断面図である。

【図14】本発明の一実施形態に係る半導体装置の断面図である。

【符号の説明】

【0073】

1 不揮発性半導体記憶装置

2 揮発性半導体記憶装置

11 シリコン基板

12 第1絶縁層

13 第1導電層(第1導電膜)

14 シリコン窒化膜

15 シリコン酸化膜

16 レジストマスク

17 素子分離溝

18 素子分離絶縁膜

19 第1導電層(第2導電膜)

20 高誘電率絶縁膜(第2絶縁層)

21 アルミナ膜(第2絶縁層)

22 第2導電層

24 レジスト膜

25 ソース・ドレイン領域

27 高誘電率絶縁膜(第1絶縁層)

28 アルミナ膜(第1絶縁層)

29 第3絶縁層

31 プレート電極領域

32 トレンチ

33 高誘電率絶縁膜(キャパシタ絶縁層)

34 アルミナ膜(キャパシタ絶縁層)

35 カラー酸化膜

36 蓄積電極

【特許請求の範囲】

【請求項1】

半導体領域と、

前記半導体領域の上に設けられ、少なくともアルミニウム以外の金属元素を含む高誘電率絶縁膜と、

前記高誘電率絶縁膜の上に設けられたアルミナ膜と、

前記アルミナ膜の上に設けられた導電層とを有することを特徴とする半導体装置。

【請求項2】

前記高誘電率絶縁膜が、ハフニウムとアルミニウムを含む複合酸化膜であることを特徴とする請求項1に記載の半導体装置。

【請求項3】

前記アルミナ膜の膜厚が、0.2nm以上1.6nm以下であることを特徴とする請求項1または請求項2に記載の半導体装置。

【請求項4】

半導体領域の上に高誘電率絶縁膜をアトミックレイヤーデポジション法により成膜し、

前記高誘電率絶縁膜の上にアルミナ膜をアトミックレイヤーデポジション法により成膜し、

前記アルミナ膜をアニールし、

前記アルミナ膜の上に導電層を還元雰囲気下で成膜することを特徴とする半導体装置の製造方法。

【請求項5】

前記アルミナ膜の成膜では、アルミニウムソースガスと酸素源との交互供給の回数を3回以上20回以下とすることを特徴とする請求項4に記載の半導体装置の製造方法。

【請求項1】

半導体領域と、

前記半導体領域の上に設けられ、少なくともアルミニウム以外の金属元素を含む高誘電率絶縁膜と、

前記高誘電率絶縁膜の上に設けられたアルミナ膜と、

前記アルミナ膜の上に設けられた導電層とを有することを特徴とする半導体装置。

【請求項2】

前記高誘電率絶縁膜が、ハフニウムとアルミニウムを含む複合酸化膜であることを特徴とする請求項1に記載の半導体装置。

【請求項3】

前記アルミナ膜の膜厚が、0.2nm以上1.6nm以下であることを特徴とする請求項1または請求項2に記載の半導体装置。

【請求項4】

半導体領域の上に高誘電率絶縁膜をアトミックレイヤーデポジション法により成膜し、

前記高誘電率絶縁膜の上にアルミナ膜をアトミックレイヤーデポジション法により成膜し、

前記アルミナ膜をアニールし、

前記アルミナ膜の上に導電層を還元雰囲気下で成膜することを特徴とする半導体装置の製造方法。

【請求項5】

前記アルミナ膜の成膜では、アルミニウムソースガスと酸素源との交互供給の回数を3回以上20回以下とすることを特徴とする請求項4に記載の半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【公開番号】特開2007−88301(P2007−88301A)

【公開日】平成19年4月5日(2007.4.5)

【国際特許分類】

【出願番号】特願2005−276786(P2005−276786)

【出願日】平成17年9月22日(2005.9.22)

【出願人】(000003078)株式会社東芝 (54,554)

【出願人】(302052301)東芝ナノアナリシス株式会社 (7)

【Fターム(参考)】

【公開日】平成19年4月5日(2007.4.5)

【国際特許分類】

【出願日】平成17年9月22日(2005.9.22)

【出願人】(000003078)株式会社東芝 (54,554)

【出願人】(302052301)東芝ナノアナリシス株式会社 (7)

【Fターム(参考)】

[ Back to top ]