半導体装置および半導体装置の製造方法

【課題】絶縁膜の凹部内に形成された配線のバリアメタル膜の絶縁膜からの剥がれを防ぐ。

【解決手段】半導体装置100は、基板(不図示)上に形成され、太幅配線溝106が表面に形成された層間絶縁膜104と、層間絶縁膜104の太幅配線溝106を埋め込んで形成され、バリアメタル膜110および銅膜116により構成された太幅配線120とを含む。太幅配線溝106の底面には、角部に選択的に凹凸114が形成され、凹凸114上にバリアメタル膜110が形成されている。

【解決手段】半導体装置100は、基板(不図示)上に形成され、太幅配線溝106が表面に形成された層間絶縁膜104と、層間絶縁膜104の太幅配線溝106を埋め込んで形成され、バリアメタル膜110および銅膜116により構成された太幅配線120とを含む。太幅配線溝106の底面には、角部に選択的に凹凸114が形成され、凹凸114上にバリアメタル膜110が形成されている。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置および半導体装置の製造方法に関する。

【背景技術】

【0002】

近年における半導体装置の高集積化への要請から、配線、プラグ、パッド等の材料として、抵抗が低い銅が広く用いられるようになってきた。銅配線は、絶縁膜中に配線溝を形成し、当該配線溝内にバリアメタル膜を形成し、その上に銅膜を形成して配線溝を埋め込むことにより、形成される。しかし、バリアメタル膜が絶縁膜から剥がれたりすることにより、組み立て耐性が悪くなるという問題があった。

【0003】

特許文献1(特開2002−217195号公報)には、絶縁膜の表面に異なる幅を有する複数の溝が形成されており、各溝がバリアメタルと銅膜とからなる配線で埋め込まれた構成が記載されている。複数の溝のうち、幅が広い方の溝の底部には、たとえば複数の溝からなる凹凸が設けられている。これにより、広い溝と細い溝とのめっき時の析出速度の差を小さくすることができるとされている。

【特許文献1】特開2002−217195号公報

【発明の開示】

【発明が解決しようとする課題】

【0004】

しかし、特許文献1に記載の技術では、広い溝と細い溝とのめっき時の析出速度の差を小さくすることを目的としており、広い溝の底部全面に凹凸が形成されている一方、溝の角部には凹凸が形成されておらず、バリアメタル膜が絶縁膜から剥がれたりすることにより、組み立て耐性が悪くなるという問題を解決するという点では、依然として問題があった。

【課題を解決するための手段】

【0005】

本発明によれば、

基板と、

前記基板上に形成され、第1の凹部が表面に形成された絶縁膜と、

前記絶縁膜の第1の凹部を埋め込んで形成され、バリアメタル膜および銅膜により構成された第1の配線と、

を含み、

前記第1の凹部の底面には、角部に選択的に凹凸が形成され、当該凹凸上に前記バリアメタル膜が形成された半導体装置が提供される。

【0006】

本発明によれば、

基板上に形成された絶縁膜の表面に形成された第1の凹部に第1の配線を形成する工程を含み、

前記第1の配線を形成する工程は、

スパッタリング法により、前記第1の凹部内にバリアメタル膜を形成する第1の工程と、

エッチングにより、前記第1の凹部の底面の角部の前記バリアメタル膜および前記絶縁膜を削り、前記第1の凹部の底面の角部に凹凸を形成する第2の工程と、

前記第2の工程の後に、スパッタリング法により、前記第1の凹部内にバリアメタル膜を形成する第3の工程と、

前記第3の工程の後に、前記第1の凹部を埋め込むように銅を主成分として含む銅膜を形成する第4の工程と、

を含み、

前記第1の工程と前記第2の工程とを複数回行い、前記第1の凹部の底面の前記角部に選択的に前記凹凸を形成し、その後に前記第3の工程を行い、前記凹凸上に前記バリアメタル膜を形成する半導体装置の製造方法が提供される。

【0007】

本発明者の検討によれば、バリアメタル膜は、配線溝等の凹部の底面の角部で絶縁膜から剥がれやすいことが明らかになった。本発明の構成によれば、凹部の底面の角部に凹凸が選択的に形成される。そのため、凹部内に形成されるバリアメタル膜が、凹部内に食い込み、絶縁膜とバリアメタル膜との密着面積が大きくなり、これらの間の密着性を向上させることができる。これにより、絶縁膜の凹部内に形成された配線のバリアメタル膜の絶縁膜からの剥がれを防ぐことができる。

【0008】

なお、以上の構成要素の任意の組合せ、本発明の表現を方法、装置などの間で変換したものもまた、本発明の態様として有効である。

【発明の効果】

【0009】

本発明によれば、絶縁膜の凹部内に形成された配線のバリアメタル膜の絶縁膜からの剥がれを防ぐことができる。

【発明を実施するための最良の形態】

【0010】

以下、本発明の実施の形態について、図面を用いて説明する。尚、すべての図面において、同様な構成要素には同様の符号を付し、適宜説明を省略する。

【0011】

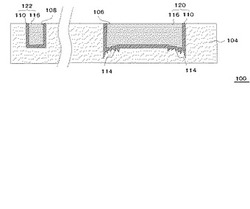

図1は、本実施の形態における半導体装置100の構成を示す断面図である。

半導体装置100は、シリコン基板等の半導体基板である基板(不図示)と、基板上に形成され、太幅配線溝106(第1の凹部)および細幅配線溝108(第2の凹部)が表面に形成された層間絶縁膜104(絶縁膜)と、層間絶縁膜104の太幅配線溝106を埋め込んで形成された太幅配線120(第1の配線)と、層間絶縁膜104の細幅配線溝108を埋め込んで形成された細幅配線122(第2の配線)とを含む。また、図示していないが、基板上には、トランジスタ等が形成されている。基板と層間絶縁膜104との間には、他の絶縁膜が形成されていてもよい。

【0012】

太幅配線120および細幅配線122は、バリアメタル膜110および銅膜116により構成される。バリアメタル膜110は、たとえばTi、W、Ta等の高融点金属を含む。好ましいバリアメタル膜110としては、たとえば、Ti、TiN、W、WN、Ta、TaN等が例示される。バリアメタル膜110としては、たとえばTaNおよびTaの積層構造等を用いることもできる。銅膜116は、銅を主成分として含むとともに銅とは異なる不純物金属を含んでもよい。

【0013】

本実施の形態において、太幅配線溝106は、たとえばアスペクト比が1以下とすることができる。太幅配線溝106の配線幅は、たとえば270nm以上720nm以下程度とすることができる。半導体装置100には、各層内のメタルの量を均一にして、強度を高めたり、上下の層との密着性を良好にするために、ダミー配線を設けた構成とすることができる。このようなダミー配線は、横方向および縦方向の幅が均一な太幅配線とすることができる。本実施の形態において、太幅配線120は、ダミー配線を含む構成とすることができ、ダミー配線の幅以上の配線幅を有する配線を太幅配線120とすることができる。一方、細幅配線122は、たとえばアスペクト比が3以上とすることができる。細幅配線溝108の配線幅は、たとえば90nm程度とすることができる。

【0014】

本実施の形態において、太幅配線溝106の底面には、角部に選択的に凹凸114が形成されている。ここで、凹凸114は、太幅配線溝106の底面の角部において、層間絶縁膜104中に食い込むように形成されている。このような構成により、太幅配線溝106内に形成されたバリアメタル膜110が、凹凸114の凹部に食い込み、層間絶縁膜104とバリアメタル膜110との密着面積が大きくなり、これらの間の密着性を向上させることができる。なお、凹凸114は、バリアメタル膜110の上面にも凹凸が反映される程度に大きく形成された構成とすることができる。これにより、バリアメタル膜110と銅膜116との間の密着性も向上させることができる。

【0015】

また、本実施の形態において、太幅配線溝106の底面の中央部は、略平坦に形成された構成とすることができる。このような構成により、太幅配線溝106の中央部では、バリアメタル膜110も略平坦に形成される。これにより、バリアメタル膜110上にめっき法で銅膜116を形成する際の銅膜116の面方位を均一にすることができる。たとえば、上記特許文献1に記載された技術では、広い溝の底部全面に凹凸が形成されている。そのため、広い溝内に銅膜をめっき法で形成する際に、溝底面の凹凸の影響を受け、めっき膜の面方位が不均一になり、SIV(stress-induced voiding)耐性が悪化するおそれがある。本実施の形態におれる半導体装置100によれば、太幅配線溝106の底面の角部に選択的に凹凸114が形成されるので、バリアメタル膜110と層間絶縁膜104との密着性を良好にできるとともに、SIV耐性も良好にすることができる。

【0016】

また、細幅配線溝108の底面の角部は、太幅配線溝106の底面の角部に比べて平坦に形成された構成とすることができる。細幅配線溝108の底面は、全体にわたって平坦な構成とすることができる。これにより、細幅配線122における抵抗ばらつきを低減することができる。細幅配線122においては、幅が狭いため、太幅配線120程バリアメタル膜110と層間絶縁膜104との間の剥がれは問題とならない。一方、細幅配線122では、少しの寸法の変化により、抵抗ばらつきが生じやすくなる。また、後述するように、細幅配線122を形成する際に、めっき法により配線溝内にめっき銅膜を形成する際、配線溝が狭くかつ底面の角部に凹凸があると、めっき銅膜を良好に埋め込めないおそれもある。本実施の形態において、太幅配線溝106においては、底面の角部に凹凸114が形成されるとともに、細幅配線溝108の底面は平坦に形成されるため、太幅配線120における剥がれの問題を解決できるとともに、細幅配線122の抵抗ばらつきを抑えることができる。

【0017】

層間絶縁膜104は、たとえば比誘電率がk=3.0以下の低誘電率膜とすることができる。層間絶縁膜104としては、たとえば、HSQ(ハイドロジェンシルセスキオキサン)、MSQ(メチルシルセスキオキサン)、またはMHSQ(メチル化ハイドロジェンシルセスキオキサン)等のポリオルガノシロキサン、ポリアリールエーテル(PAE)、ジビニルシロキサンビスベンゾシクロブテン(BCB)、またはSilk(登録商標)等の芳香族含有有機材料、SOG(spin on glass)、FOX(flowable oxide)、パリレン、サイトップ、またはベンゾシクロブテン(Benzocyclobutene:BCB)等の低誘電率材料を用いることができる。

【0018】

次に、本実施の形態における半導体装置100の製造手順を説明する。図2から図4は、半導体装置100の製造手順を示す工程断面図である。

本実施の形態において、半導体装置100の製造方法は、基板上に形成された層間絶縁膜104の表面に形成された太幅配線溝106に太幅配線120を形成する工程を含む。

太幅配線120(第1の配線)を形成する工程は、

スパッタリング法により、太幅配線溝106(第1の凹部)内にバリアメタル膜110を形成する第1の工程と、

エッチングにより、太幅配線溝106の底面の角部のバリアメタル膜110および層間絶縁膜104を削り、太幅配線溝106の底面の角部に凹凸を形成する第2の工程と、

第2の工程の後に、スパッタリング法により、太幅配線溝106内にバリアメタル膜110を形成する第3の工程と、

第3の工程の後に、太幅配線溝106を埋め込むように銅を主成分として含む銅膜116を形成する第4の工程と、を含む。ここで、第1の工程と第2の工程とを複数回行い、太幅配線溝106の底面の角部に選択的に凹凸114を形成し、その後に第3の工程を行い、凹凸114上の凹凸114表面にバリアメタル膜110を形成する工程を含む。

【0019】

また、太幅配線溝106に太幅配線120を形成する工程において、層間絶縁膜104の表面の太幅配線溝106と同層に形成され、太幅配線溝106よりも幅が狭い細幅配線溝108(第2の凹部)に細幅配線122(第2の配線)も形成する。ここで、第3の工程において、太幅配線溝106の底面の角部のバリアメタル膜110および層間絶縁膜104の方が、細幅配線溝108の底面の角部のバリアメタル膜110および層間絶縁膜104よりも多く削られ、細幅配線溝108の底面の角部は、太幅配線溝106の底面の角部に比べて平坦に形成される。

【0020】

以下、具体的に説明する。

まず、層間絶縁膜104に太幅配線溝106および細幅配線溝108を形成する(図2(a))。

【0021】

つづいて、層間絶縁膜104上全面にスパッタリング法により、バリアメタル膜110を形成する(図2(b))。

【0022】

つづいて、バリアメタル膜110をエッチングする。ここで、エッチングは、たとえばアルゴンイオンやヘリウムイオン等の不活性ガスイオンを用いて行うことができる。イオンの密度を低くするために、ガス圧を低くするとともに、高周波のプラズマ励起周波数のプラズマ励起パワーを低くすることができる。たとえば、ガス圧を0.3mTorr程度とし、高周波のプラズマ励起周波数(13.56MHz)のプラズマ励起パワーを100W程度とすることができる。

【0023】

本実施の形態において、エッチングガスとしては、アルゴンイオンを用いることができる。このとき、幅が広くアスペクト比が低い太幅配線溝106内には、アルゴンイオンが入り込み、エッチングレートが高くなる。とくに底面角部にイオンが集中し、太幅配線溝106の底面の角部で、層間絶縁膜104がエッチングされ、凹凸112が形成される。また、太幅配線溝106の底面の中央部でも、バリアメタル膜110が多少削られるが、均一に削られ、凹凸はほとんど形成されない。そのため、太幅配線溝106において、底面の角部で掘り込み量が深く、中央部に行くに従い、その掘り込み量が浅くなる構成とすることができる。これにより、太幅配線溝106の中央部では、バリアメタル膜110も略平坦に形成される。また、幅が狭くアスペクト比が高い細幅配線溝108内には、アルゴンイオンが入り込みにくいため、エッチングレートが低くなり、凹凸が形成されない(図2(c))。

【0024】

次いで、層間絶縁膜104上全面に再度スパッタリング法により、バリアメタル膜110を形成する(図3(a))。これにより、太幅配線溝106の角部の凹凸112がバリアメタル膜110で埋め込まれる。

【0025】

つづいて、バリアメタル膜110を再度エッチングする。ここで、エッチングの条件は、図2(c)を参照して説明したのと同様とすることができる。これにより、太幅配線溝106の角部では、層間絶縁膜104がさらにエッチングされ、凹凸112よりも凹凸の大きい凹凸114が形成される。一方、幅の狭い細幅配線溝108では、アルゴンイオンが入り込みにくいため、凹凸が形成されない(図3(b))。

【0026】

このように、バリアメタル膜110の形成とエッチングとを繰り返し複数回行い、徐々に凹凸114を形成することにより、太幅配線溝106の底面の角部に大きな凹凸114を形成するとともに、それ以外の箇所でバリアメタル膜110が剥がれたり、層間絶縁膜104がエッチングされるのを防ぐことができる。

【0027】

この後、層間絶縁膜104上全面に再度スパッタリング法により、バリアメタル膜110を形成する。これにより、太幅配線溝106の角部の凹凸114の凹部がバリアメタル膜110で埋め込まれ、凹凸114表面にバリアメタル膜110が形成される(図4(a))。また、このとき、太幅配線溝106底面の角部において、バリアメタル膜110の上面にも凹凸114が多少反映される。

【0028】

つづいて、バリアメタル膜110上全面に、スパッタリング法によりシード銅膜(不図示)を形成する。次いで、めっき法によりめっき銅膜を形成し、太幅配線溝106および細幅配線溝108内を銅膜116で埋め込む(図4(b))。つづいて、アニールを行う。アニールにより、太幅配線溝106および細幅配線溝108内の銅膜116の銅のグレインが成長する。これにより、銅膜116を低抵抗化することができる。この後、化学的機械的研磨(Chemical Mechanical Polishing:CMP)により、太幅配線溝106および細幅配線溝108外部に露出した銅膜116およびバリアメタル膜110を除去する。これにより、細幅配線溝108内に細幅配線122が、太幅配線溝106内に太幅配線120が形成される(図1)。

【0029】

図5は、本実施の形態における半導体装置の製造手順を示すフローチャートである。

まず、層間絶縁膜104に太幅配線溝106および細幅配線溝108等の配線溝を形成する(S100)。つづいて、層間絶縁膜上全面にスパッタリング法により、バリアメタル膜110を形成する(S102、第1の工程)。次いで、バリアメタル膜110をエッチングする(S104、第2の工程)。バリアメタル膜110の形成とエッチングを所定回数繰り返した後(ステップS106のYES)、スパッタリング法により、再度バリアメタル膜110を形成する(S108、第3の工程)。以上の図2から図4に示した例では、所定回数を2回としたが、より多い回数行うこともできる。その後、バリアメタル膜110上に銅膜116を形成し、太幅配線溝106および細幅配線溝108を銅膜116で埋め込む(S110、第4の工程)。

【0030】

次に、本実施の形態における半導体装置100の効果を説明する。

本実施の形態における半導体装置100によれば、太幅配線溝106の底面の角部において、凹凸114が選択的に層間絶縁膜104中に食い込むように形成されている。そのため、太幅配線120において、層間絶縁膜104とバリアメタル膜110との密着面積が大きくなり、これらの間の密着性を向上させることができる。一方、細幅配線溝108の底面には凹凸が形成されないため、細幅配線122において抵抗ばらつきを抑えることができる。また、細幅配線122を形成する際に、めっき法により細幅配線溝108内にめっき銅膜を形成する際にも、めっき銅膜を良好に埋め込ことができる。これにより、細幅配線122において配線抵抗を安定化できるとともに、同時に半導体装置100の組み立て耐性を向上させることができる。

【0031】

さらに、太幅配線溝106の底面の中央部は、略平坦に形成された構成とすることができる。これにより、太幅配線溝106の中央部では、バリアメタル膜110も略平坦に形成され、バリアメタル膜110上にめっき法で銅膜116を形成する際の銅膜116の面方位を均一にすることができる。そのため、太幅配線120のSIV耐性も良好にすることができる。

【0032】

なお、本実施の形態において、ダミー配線も太幅配線120により構成することができる。ダミー配線の底面の角部に凹凸を形成することにより、ダミー配線におけるバリアメタル膜110と層間絶縁膜104との密着性を良好にすることができ、半導体装置100の強度を高めることができる。

【0033】

以上、図面を参照して本発明の実施形態について述べたが、これらは本発明の例示であり、上記以外の様々な構成を採用することもできる。

【0034】

細幅配線122および太幅配線120は、シングルダマシン法またはデュアルダマシン法のいずれに適用してもよい。

【0035】

なお、以上の実施の形態で説明した凹凸114を形成する手順は、層間絶縁膜104が低誘電率膜により構成された層にのみ適用することができる。たとえば、半導体装置100の多層配線構造のうち、層間絶縁膜としてシリコン酸化膜が用いられているような層においては、従来の配線溝形成工程で配線溝を形成することができる。層間絶縁膜104として低誘電率膜を用いる層において、層間絶縁膜104とバリアメタル膜110との密着性が問題となりやすいためである。このように、層間絶縁膜の種類によって配線溝の形成手順を異ならせることにより、半導体装置100の製造時のスループットを高めることができるとともに、上記の組み立て耐性を向上させることができる等の効果を得ることができる。

【0036】

以上の実施の形態においては、太幅配線溝106の底面(太幅配線溝106の下方)および側面(太幅配線溝106と同層)に一層の層間絶縁膜104が形成された構成を例として示したが、太幅配線溝106の底面(太幅配線溝106の下方)と側面(太幅配線溝106と同層)とでは、異なる層の層間絶縁膜で構成することもできる。この場合も、層間絶縁膜は、低誘電率膜により構成することができる。

【図面の簡単な説明】

【0037】

【図1】本発明の実施の形態における半導体装置の構成を示す断面図である。

【図2】本発明の実施の形態における半導体装置の製造手順を示す工程断面図である。

【図3】本発明の実施の形態における半導体装置の製造手順を示す工程断面図である。

【図4】本発明の実施の形態における半導体装置の製造手順を示す工程断面図である。

【図5】本発明の実施の形態における半導体装置の製造手順を示すフローチャートである。

【符号の説明】

【0038】

100 半導体装置

104 層間絶縁膜

106 太幅配線溝

108 細幅配線溝

110 バリアメタル膜

112 凹凸

114 凹凸

116 銅膜

120 太幅配線

122 細幅配線

【技術分野】

【0001】

本発明は、半導体装置および半導体装置の製造方法に関する。

【背景技術】

【0002】

近年における半導体装置の高集積化への要請から、配線、プラグ、パッド等の材料として、抵抗が低い銅が広く用いられるようになってきた。銅配線は、絶縁膜中に配線溝を形成し、当該配線溝内にバリアメタル膜を形成し、その上に銅膜を形成して配線溝を埋め込むことにより、形成される。しかし、バリアメタル膜が絶縁膜から剥がれたりすることにより、組み立て耐性が悪くなるという問題があった。

【0003】

特許文献1(特開2002−217195号公報)には、絶縁膜の表面に異なる幅を有する複数の溝が形成されており、各溝がバリアメタルと銅膜とからなる配線で埋め込まれた構成が記載されている。複数の溝のうち、幅が広い方の溝の底部には、たとえば複数の溝からなる凹凸が設けられている。これにより、広い溝と細い溝とのめっき時の析出速度の差を小さくすることができるとされている。

【特許文献1】特開2002−217195号公報

【発明の開示】

【発明が解決しようとする課題】

【0004】

しかし、特許文献1に記載の技術では、広い溝と細い溝とのめっき時の析出速度の差を小さくすることを目的としており、広い溝の底部全面に凹凸が形成されている一方、溝の角部には凹凸が形成されておらず、バリアメタル膜が絶縁膜から剥がれたりすることにより、組み立て耐性が悪くなるという問題を解決するという点では、依然として問題があった。

【課題を解決するための手段】

【0005】

本発明によれば、

基板と、

前記基板上に形成され、第1の凹部が表面に形成された絶縁膜と、

前記絶縁膜の第1の凹部を埋め込んで形成され、バリアメタル膜および銅膜により構成された第1の配線と、

を含み、

前記第1の凹部の底面には、角部に選択的に凹凸が形成され、当該凹凸上に前記バリアメタル膜が形成された半導体装置が提供される。

【0006】

本発明によれば、

基板上に形成された絶縁膜の表面に形成された第1の凹部に第1の配線を形成する工程を含み、

前記第1の配線を形成する工程は、

スパッタリング法により、前記第1の凹部内にバリアメタル膜を形成する第1の工程と、

エッチングにより、前記第1の凹部の底面の角部の前記バリアメタル膜および前記絶縁膜を削り、前記第1の凹部の底面の角部に凹凸を形成する第2の工程と、

前記第2の工程の後に、スパッタリング法により、前記第1の凹部内にバリアメタル膜を形成する第3の工程と、

前記第3の工程の後に、前記第1の凹部を埋め込むように銅を主成分として含む銅膜を形成する第4の工程と、

を含み、

前記第1の工程と前記第2の工程とを複数回行い、前記第1の凹部の底面の前記角部に選択的に前記凹凸を形成し、その後に前記第3の工程を行い、前記凹凸上に前記バリアメタル膜を形成する半導体装置の製造方法が提供される。

【0007】

本発明者の検討によれば、バリアメタル膜は、配線溝等の凹部の底面の角部で絶縁膜から剥がれやすいことが明らかになった。本発明の構成によれば、凹部の底面の角部に凹凸が選択的に形成される。そのため、凹部内に形成されるバリアメタル膜が、凹部内に食い込み、絶縁膜とバリアメタル膜との密着面積が大きくなり、これらの間の密着性を向上させることができる。これにより、絶縁膜の凹部内に形成された配線のバリアメタル膜の絶縁膜からの剥がれを防ぐことができる。

【0008】

なお、以上の構成要素の任意の組合せ、本発明の表現を方法、装置などの間で変換したものもまた、本発明の態様として有効である。

【発明の効果】

【0009】

本発明によれば、絶縁膜の凹部内に形成された配線のバリアメタル膜の絶縁膜からの剥がれを防ぐことができる。

【発明を実施するための最良の形態】

【0010】

以下、本発明の実施の形態について、図面を用いて説明する。尚、すべての図面において、同様な構成要素には同様の符号を付し、適宜説明を省略する。

【0011】

図1は、本実施の形態における半導体装置100の構成を示す断面図である。

半導体装置100は、シリコン基板等の半導体基板である基板(不図示)と、基板上に形成され、太幅配線溝106(第1の凹部)および細幅配線溝108(第2の凹部)が表面に形成された層間絶縁膜104(絶縁膜)と、層間絶縁膜104の太幅配線溝106を埋め込んで形成された太幅配線120(第1の配線)と、層間絶縁膜104の細幅配線溝108を埋め込んで形成された細幅配線122(第2の配線)とを含む。また、図示していないが、基板上には、トランジスタ等が形成されている。基板と層間絶縁膜104との間には、他の絶縁膜が形成されていてもよい。

【0012】

太幅配線120および細幅配線122は、バリアメタル膜110および銅膜116により構成される。バリアメタル膜110は、たとえばTi、W、Ta等の高融点金属を含む。好ましいバリアメタル膜110としては、たとえば、Ti、TiN、W、WN、Ta、TaN等が例示される。バリアメタル膜110としては、たとえばTaNおよびTaの積層構造等を用いることもできる。銅膜116は、銅を主成分として含むとともに銅とは異なる不純物金属を含んでもよい。

【0013】

本実施の形態において、太幅配線溝106は、たとえばアスペクト比が1以下とすることができる。太幅配線溝106の配線幅は、たとえば270nm以上720nm以下程度とすることができる。半導体装置100には、各層内のメタルの量を均一にして、強度を高めたり、上下の層との密着性を良好にするために、ダミー配線を設けた構成とすることができる。このようなダミー配線は、横方向および縦方向の幅が均一な太幅配線とすることができる。本実施の形態において、太幅配線120は、ダミー配線を含む構成とすることができ、ダミー配線の幅以上の配線幅を有する配線を太幅配線120とすることができる。一方、細幅配線122は、たとえばアスペクト比が3以上とすることができる。細幅配線溝108の配線幅は、たとえば90nm程度とすることができる。

【0014】

本実施の形態において、太幅配線溝106の底面には、角部に選択的に凹凸114が形成されている。ここで、凹凸114は、太幅配線溝106の底面の角部において、層間絶縁膜104中に食い込むように形成されている。このような構成により、太幅配線溝106内に形成されたバリアメタル膜110が、凹凸114の凹部に食い込み、層間絶縁膜104とバリアメタル膜110との密着面積が大きくなり、これらの間の密着性を向上させることができる。なお、凹凸114は、バリアメタル膜110の上面にも凹凸が反映される程度に大きく形成された構成とすることができる。これにより、バリアメタル膜110と銅膜116との間の密着性も向上させることができる。

【0015】

また、本実施の形態において、太幅配線溝106の底面の中央部は、略平坦に形成された構成とすることができる。このような構成により、太幅配線溝106の中央部では、バリアメタル膜110も略平坦に形成される。これにより、バリアメタル膜110上にめっき法で銅膜116を形成する際の銅膜116の面方位を均一にすることができる。たとえば、上記特許文献1に記載された技術では、広い溝の底部全面に凹凸が形成されている。そのため、広い溝内に銅膜をめっき法で形成する際に、溝底面の凹凸の影響を受け、めっき膜の面方位が不均一になり、SIV(stress-induced voiding)耐性が悪化するおそれがある。本実施の形態におれる半導体装置100によれば、太幅配線溝106の底面の角部に選択的に凹凸114が形成されるので、バリアメタル膜110と層間絶縁膜104との密着性を良好にできるとともに、SIV耐性も良好にすることができる。

【0016】

また、細幅配線溝108の底面の角部は、太幅配線溝106の底面の角部に比べて平坦に形成された構成とすることができる。細幅配線溝108の底面は、全体にわたって平坦な構成とすることができる。これにより、細幅配線122における抵抗ばらつきを低減することができる。細幅配線122においては、幅が狭いため、太幅配線120程バリアメタル膜110と層間絶縁膜104との間の剥がれは問題とならない。一方、細幅配線122では、少しの寸法の変化により、抵抗ばらつきが生じやすくなる。また、後述するように、細幅配線122を形成する際に、めっき法により配線溝内にめっき銅膜を形成する際、配線溝が狭くかつ底面の角部に凹凸があると、めっき銅膜を良好に埋め込めないおそれもある。本実施の形態において、太幅配線溝106においては、底面の角部に凹凸114が形成されるとともに、細幅配線溝108の底面は平坦に形成されるため、太幅配線120における剥がれの問題を解決できるとともに、細幅配線122の抵抗ばらつきを抑えることができる。

【0017】

層間絶縁膜104は、たとえば比誘電率がk=3.0以下の低誘電率膜とすることができる。層間絶縁膜104としては、たとえば、HSQ(ハイドロジェンシルセスキオキサン)、MSQ(メチルシルセスキオキサン)、またはMHSQ(メチル化ハイドロジェンシルセスキオキサン)等のポリオルガノシロキサン、ポリアリールエーテル(PAE)、ジビニルシロキサンビスベンゾシクロブテン(BCB)、またはSilk(登録商標)等の芳香族含有有機材料、SOG(spin on glass)、FOX(flowable oxide)、パリレン、サイトップ、またはベンゾシクロブテン(Benzocyclobutene:BCB)等の低誘電率材料を用いることができる。

【0018】

次に、本実施の形態における半導体装置100の製造手順を説明する。図2から図4は、半導体装置100の製造手順を示す工程断面図である。

本実施の形態において、半導体装置100の製造方法は、基板上に形成された層間絶縁膜104の表面に形成された太幅配線溝106に太幅配線120を形成する工程を含む。

太幅配線120(第1の配線)を形成する工程は、

スパッタリング法により、太幅配線溝106(第1の凹部)内にバリアメタル膜110を形成する第1の工程と、

エッチングにより、太幅配線溝106の底面の角部のバリアメタル膜110および層間絶縁膜104を削り、太幅配線溝106の底面の角部に凹凸を形成する第2の工程と、

第2の工程の後に、スパッタリング法により、太幅配線溝106内にバリアメタル膜110を形成する第3の工程と、

第3の工程の後に、太幅配線溝106を埋め込むように銅を主成分として含む銅膜116を形成する第4の工程と、を含む。ここで、第1の工程と第2の工程とを複数回行い、太幅配線溝106の底面の角部に選択的に凹凸114を形成し、その後に第3の工程を行い、凹凸114上の凹凸114表面にバリアメタル膜110を形成する工程を含む。

【0019】

また、太幅配線溝106に太幅配線120を形成する工程において、層間絶縁膜104の表面の太幅配線溝106と同層に形成され、太幅配線溝106よりも幅が狭い細幅配線溝108(第2の凹部)に細幅配線122(第2の配線)も形成する。ここで、第3の工程において、太幅配線溝106の底面の角部のバリアメタル膜110および層間絶縁膜104の方が、細幅配線溝108の底面の角部のバリアメタル膜110および層間絶縁膜104よりも多く削られ、細幅配線溝108の底面の角部は、太幅配線溝106の底面の角部に比べて平坦に形成される。

【0020】

以下、具体的に説明する。

まず、層間絶縁膜104に太幅配線溝106および細幅配線溝108を形成する(図2(a))。

【0021】

つづいて、層間絶縁膜104上全面にスパッタリング法により、バリアメタル膜110を形成する(図2(b))。

【0022】

つづいて、バリアメタル膜110をエッチングする。ここで、エッチングは、たとえばアルゴンイオンやヘリウムイオン等の不活性ガスイオンを用いて行うことができる。イオンの密度を低くするために、ガス圧を低くするとともに、高周波のプラズマ励起周波数のプラズマ励起パワーを低くすることができる。たとえば、ガス圧を0.3mTorr程度とし、高周波のプラズマ励起周波数(13.56MHz)のプラズマ励起パワーを100W程度とすることができる。

【0023】

本実施の形態において、エッチングガスとしては、アルゴンイオンを用いることができる。このとき、幅が広くアスペクト比が低い太幅配線溝106内には、アルゴンイオンが入り込み、エッチングレートが高くなる。とくに底面角部にイオンが集中し、太幅配線溝106の底面の角部で、層間絶縁膜104がエッチングされ、凹凸112が形成される。また、太幅配線溝106の底面の中央部でも、バリアメタル膜110が多少削られるが、均一に削られ、凹凸はほとんど形成されない。そのため、太幅配線溝106において、底面の角部で掘り込み量が深く、中央部に行くに従い、その掘り込み量が浅くなる構成とすることができる。これにより、太幅配線溝106の中央部では、バリアメタル膜110も略平坦に形成される。また、幅が狭くアスペクト比が高い細幅配線溝108内には、アルゴンイオンが入り込みにくいため、エッチングレートが低くなり、凹凸が形成されない(図2(c))。

【0024】

次いで、層間絶縁膜104上全面に再度スパッタリング法により、バリアメタル膜110を形成する(図3(a))。これにより、太幅配線溝106の角部の凹凸112がバリアメタル膜110で埋め込まれる。

【0025】

つづいて、バリアメタル膜110を再度エッチングする。ここで、エッチングの条件は、図2(c)を参照して説明したのと同様とすることができる。これにより、太幅配線溝106の角部では、層間絶縁膜104がさらにエッチングされ、凹凸112よりも凹凸の大きい凹凸114が形成される。一方、幅の狭い細幅配線溝108では、アルゴンイオンが入り込みにくいため、凹凸が形成されない(図3(b))。

【0026】

このように、バリアメタル膜110の形成とエッチングとを繰り返し複数回行い、徐々に凹凸114を形成することにより、太幅配線溝106の底面の角部に大きな凹凸114を形成するとともに、それ以外の箇所でバリアメタル膜110が剥がれたり、層間絶縁膜104がエッチングされるのを防ぐことができる。

【0027】

この後、層間絶縁膜104上全面に再度スパッタリング法により、バリアメタル膜110を形成する。これにより、太幅配線溝106の角部の凹凸114の凹部がバリアメタル膜110で埋め込まれ、凹凸114表面にバリアメタル膜110が形成される(図4(a))。また、このとき、太幅配線溝106底面の角部において、バリアメタル膜110の上面にも凹凸114が多少反映される。

【0028】

つづいて、バリアメタル膜110上全面に、スパッタリング法によりシード銅膜(不図示)を形成する。次いで、めっき法によりめっき銅膜を形成し、太幅配線溝106および細幅配線溝108内を銅膜116で埋め込む(図4(b))。つづいて、アニールを行う。アニールにより、太幅配線溝106および細幅配線溝108内の銅膜116の銅のグレインが成長する。これにより、銅膜116を低抵抗化することができる。この後、化学的機械的研磨(Chemical Mechanical Polishing:CMP)により、太幅配線溝106および細幅配線溝108外部に露出した銅膜116およびバリアメタル膜110を除去する。これにより、細幅配線溝108内に細幅配線122が、太幅配線溝106内に太幅配線120が形成される(図1)。

【0029】

図5は、本実施の形態における半導体装置の製造手順を示すフローチャートである。

まず、層間絶縁膜104に太幅配線溝106および細幅配線溝108等の配線溝を形成する(S100)。つづいて、層間絶縁膜上全面にスパッタリング法により、バリアメタル膜110を形成する(S102、第1の工程)。次いで、バリアメタル膜110をエッチングする(S104、第2の工程)。バリアメタル膜110の形成とエッチングを所定回数繰り返した後(ステップS106のYES)、スパッタリング法により、再度バリアメタル膜110を形成する(S108、第3の工程)。以上の図2から図4に示した例では、所定回数を2回としたが、より多い回数行うこともできる。その後、バリアメタル膜110上に銅膜116を形成し、太幅配線溝106および細幅配線溝108を銅膜116で埋め込む(S110、第4の工程)。

【0030】

次に、本実施の形態における半導体装置100の効果を説明する。

本実施の形態における半導体装置100によれば、太幅配線溝106の底面の角部において、凹凸114が選択的に層間絶縁膜104中に食い込むように形成されている。そのため、太幅配線120において、層間絶縁膜104とバリアメタル膜110との密着面積が大きくなり、これらの間の密着性を向上させることができる。一方、細幅配線溝108の底面には凹凸が形成されないため、細幅配線122において抵抗ばらつきを抑えることができる。また、細幅配線122を形成する際に、めっき法により細幅配線溝108内にめっき銅膜を形成する際にも、めっき銅膜を良好に埋め込ことができる。これにより、細幅配線122において配線抵抗を安定化できるとともに、同時に半導体装置100の組み立て耐性を向上させることができる。

【0031】

さらに、太幅配線溝106の底面の中央部は、略平坦に形成された構成とすることができる。これにより、太幅配線溝106の中央部では、バリアメタル膜110も略平坦に形成され、バリアメタル膜110上にめっき法で銅膜116を形成する際の銅膜116の面方位を均一にすることができる。そのため、太幅配線120のSIV耐性も良好にすることができる。

【0032】

なお、本実施の形態において、ダミー配線も太幅配線120により構成することができる。ダミー配線の底面の角部に凹凸を形成することにより、ダミー配線におけるバリアメタル膜110と層間絶縁膜104との密着性を良好にすることができ、半導体装置100の強度を高めることができる。

【0033】

以上、図面を参照して本発明の実施形態について述べたが、これらは本発明の例示であり、上記以外の様々な構成を採用することもできる。

【0034】

細幅配線122および太幅配線120は、シングルダマシン法またはデュアルダマシン法のいずれに適用してもよい。

【0035】

なお、以上の実施の形態で説明した凹凸114を形成する手順は、層間絶縁膜104が低誘電率膜により構成された層にのみ適用することができる。たとえば、半導体装置100の多層配線構造のうち、層間絶縁膜としてシリコン酸化膜が用いられているような層においては、従来の配線溝形成工程で配線溝を形成することができる。層間絶縁膜104として低誘電率膜を用いる層において、層間絶縁膜104とバリアメタル膜110との密着性が問題となりやすいためである。このように、層間絶縁膜の種類によって配線溝の形成手順を異ならせることにより、半導体装置100の製造時のスループットを高めることができるとともに、上記の組み立て耐性を向上させることができる等の効果を得ることができる。

【0036】

以上の実施の形態においては、太幅配線溝106の底面(太幅配線溝106の下方)および側面(太幅配線溝106と同層)に一層の層間絶縁膜104が形成された構成を例として示したが、太幅配線溝106の底面(太幅配線溝106の下方)と側面(太幅配線溝106と同層)とでは、異なる層の層間絶縁膜で構成することもできる。この場合も、層間絶縁膜は、低誘電率膜により構成することができる。

【図面の簡単な説明】

【0037】

【図1】本発明の実施の形態における半導体装置の構成を示す断面図である。

【図2】本発明の実施の形態における半導体装置の製造手順を示す工程断面図である。

【図3】本発明の実施の形態における半導体装置の製造手順を示す工程断面図である。

【図4】本発明の実施の形態における半導体装置の製造手順を示す工程断面図である。

【図5】本発明の実施の形態における半導体装置の製造手順を示すフローチャートである。

【符号の説明】

【0038】

100 半導体装置

104 層間絶縁膜

106 太幅配線溝

108 細幅配線溝

110 バリアメタル膜

112 凹凸

114 凹凸

116 銅膜

120 太幅配線

122 細幅配線

【特許請求の範囲】

【請求項1】

基板と、

前記基板上に形成され、第1の凹部が表面に形成された絶縁膜と、

前記絶縁膜の第1の凹部を埋め込んで形成され、バリアメタル膜および銅膜により構成された第1の配線と、

を含み、

前記第1の凹部の底面には、角部に選択的に凹凸が形成され、当該凹凸上に前記バリアメタル膜が形成された半導体装置。

【請求項2】

請求項1に記載の半導体装置において、

前記絶縁膜の前記表面の前記第1の凹部と同層に形成され、前記第1の凹部よりも幅が狭い第2の凹部を埋め込んで形成され、バリアメタル膜および銅膜により構成された第2の配線をさらに含み、

前記第2の凹部の底面の角部は、前記第1の凹部の底面の角部に比べて平坦に形成された半導体装置。

【請求項3】

請求項1または2に記載の半導体装置において、

前記絶縁膜は、低誘電率膜であり、前記第1の凹部の底面の角部の凹凸は、前記絶縁膜に形成された半導体装置。

【請求項4】

請求項1から3いずれかに記載の半導体装置において、

前記第1の凹部の底面の中央部は、略平坦に形成された半導体装置。

【請求項5】

請求項1から4いずれかに記載の半導体装置において、

前記第1の配線は、ダミー配線を含む半導体装置。

【請求項6】

基板上に形成された絶縁膜の表面に形成された第1の凹部に第1の配線を形成する工程を含み、

前記第1の配線を形成する工程は、

スパッタリング法により、前記第1の凹部内にバリアメタル膜を形成する第1の工程と、

エッチングにより、前記第1の凹部の底面の角部の前記バリアメタル膜および前記絶縁膜を削り、前記第1の凹部の底面の角部に凹凸を形成する第2の工程と、

前記第2の工程の後に、スパッタリング法により、前記第1の凹部内にバリアメタル膜を形成する第3の工程と、

前記第3の工程の後に、前記第1の凹部を埋め込むように銅を主成分として含む銅膜を形成する第4の工程と、

を含み、

前記第1の工程と前記第2の工程とを複数回行い、前記第1の凹部の底面の前記角部に選択的に前記凹凸を形成し、その後に前記第3の工程を行い、前記凹凸上に前記バリアメタル膜を形成する半導体装置の製造方法。

【請求項7】

請求項6に記載の半導体装置の製造方法において、

前記第1の凹部に第1の配線を形成する工程において、前記絶縁膜の前記表面の前記第1の凹部と同層に形成され、前記第1の凹部よりも幅が狭い第2の凹部に第2の配線も形成し、

前記第3の工程において、前記第1の凹部の底面の角部の前記バリアメタル膜および前記絶縁膜の方が、前記第2の凹部の底面の角部の前記バリアメタル膜および前記絶縁膜よりも多く削られ、前記第2の凹部の底面の角部は、前記第1の凹部の底面の角部に比べて平坦に形成される半導体装置の製造方法。

【請求項1】

基板と、

前記基板上に形成され、第1の凹部が表面に形成された絶縁膜と、

前記絶縁膜の第1の凹部を埋め込んで形成され、バリアメタル膜および銅膜により構成された第1の配線と、

を含み、

前記第1の凹部の底面には、角部に選択的に凹凸が形成され、当該凹凸上に前記バリアメタル膜が形成された半導体装置。

【請求項2】

請求項1に記載の半導体装置において、

前記絶縁膜の前記表面の前記第1の凹部と同層に形成され、前記第1の凹部よりも幅が狭い第2の凹部を埋め込んで形成され、バリアメタル膜および銅膜により構成された第2の配線をさらに含み、

前記第2の凹部の底面の角部は、前記第1の凹部の底面の角部に比べて平坦に形成された半導体装置。

【請求項3】

請求項1または2に記載の半導体装置において、

前記絶縁膜は、低誘電率膜であり、前記第1の凹部の底面の角部の凹凸は、前記絶縁膜に形成された半導体装置。

【請求項4】

請求項1から3いずれかに記載の半導体装置において、

前記第1の凹部の底面の中央部は、略平坦に形成された半導体装置。

【請求項5】

請求項1から4いずれかに記載の半導体装置において、

前記第1の配線は、ダミー配線を含む半導体装置。

【請求項6】

基板上に形成された絶縁膜の表面に形成された第1の凹部に第1の配線を形成する工程を含み、

前記第1の配線を形成する工程は、

スパッタリング法により、前記第1の凹部内にバリアメタル膜を形成する第1の工程と、

エッチングにより、前記第1の凹部の底面の角部の前記バリアメタル膜および前記絶縁膜を削り、前記第1の凹部の底面の角部に凹凸を形成する第2の工程と、

前記第2の工程の後に、スパッタリング法により、前記第1の凹部内にバリアメタル膜を形成する第3の工程と、

前記第3の工程の後に、前記第1の凹部を埋め込むように銅を主成分として含む銅膜を形成する第4の工程と、

を含み、

前記第1の工程と前記第2の工程とを複数回行い、前記第1の凹部の底面の前記角部に選択的に前記凹凸を形成し、その後に前記第3の工程を行い、前記凹凸上に前記バリアメタル膜を形成する半導体装置の製造方法。

【請求項7】

請求項6に記載の半導体装置の製造方法において、

前記第1の凹部に第1の配線を形成する工程において、前記絶縁膜の前記表面の前記第1の凹部と同層に形成され、前記第1の凹部よりも幅が狭い第2の凹部に第2の配線も形成し、

前記第3の工程において、前記第1の凹部の底面の角部の前記バリアメタル膜および前記絶縁膜の方が、前記第2の凹部の底面の角部の前記バリアメタル膜および前記絶縁膜よりも多く削られ、前記第2の凹部の底面の角部は、前記第1の凹部の底面の角部に比べて平坦に形成される半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図2】

【図3】

【図4】

【図5】

【公開番号】特開2010−135432(P2010−135432A)

【公開日】平成22年6月17日(2010.6.17)

【国際特許分類】

【出願番号】特願2008−307920(P2008−307920)

【出願日】平成20年12月2日(2008.12.2)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

【公開日】平成22年6月17日(2010.6.17)

【国際特許分類】

【出願日】平成20年12月2日(2008.12.2)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

[ Back to top ]