半導体装置および半導体装置の製造方法

【課題】上面にストラップ配線が形成された絶縁膜と、この絶縁膜の下面に形成された配線と間で剥離が生じることが抑制された半導体装置および半導体装置の製造方法を提供する。

【解決手段】本発明に係る半導体装置は、半導体基板SSと、半導体基板SS上に形成され、周辺配線P1および配線L2が形成された配線層LL1,LL2と、配線層LL2に形成され、配線L3を含む配線層LL3と、配線層LL3上に形成され、磁気記憶素子MRを含む配線層LL4とを備え、配線L1,L2上に形成された拡散防止膜NF1,NF2は、SiCN膜またはSiC膜から形成され、配線L3上に形成された拡散防止膜NF3は、SiNから形成される。

【解決手段】本発明に係る半導体装置は、半導体基板SSと、半導体基板SS上に形成され、周辺配線P1および配線L2が形成された配線層LL1,LL2と、配線層LL2に形成され、配線L3を含む配線層LL3と、配線層LL3上に形成され、磁気記憶素子MRを含む配線層LL4とを備え、配線L1,L2上に形成された拡散防止膜NF1,NF2は、SiCN膜またはSiC膜から形成され、配線L3上に形成された拡散防止膜NF3は、SiNから形成される。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置および半導体装置の製造方法に関し、特に、磁気記憶素子を含む半導体装置およびその製造方法に関する発明である。

【背景技術】

【0002】

従来から磁気記憶素子を備えた半導体装置が提案されている。たとえば、特開2007−165505号公報に記載された半導体装置は、磁気トンネル素子と、磁気トンネル抵抗素子が形成された第1の層間絶縁膜と、上面に上記第1の層間絶縁膜が形成された第2の層間絶縁膜とを備える。

【0003】

さらに、この半導体装置は、第2の層間絶縁膜に形成された配線層と、この配線層および第2の層間絶縁膜上に形成された拡散防止膜と、前記拡散防止膜を貫通するコンタクト部と、拡散防止膜上に形成され、コンタクト部に接続されたストラップ配線とを備える。そして、このストラップ配線上に磁気トンネル素子が形成されている。

【0004】

特開2007−165505号公報には、上記のように構成された半導体装置の製造方法が記載されている。

【0005】

第2の層間絶縁膜に配線層を形成した後、拡散防止膜を第2の層間絶縁膜上に形成する。拡散防止膜に配線層に達する開口部を形成し、この開口部にW(タングステン)等を充填して、コンタクトを形成する。

【0006】

コンタクトを形成した後、たとえば、Ta膜等の金属膜を形成し、この金属膜上に強磁性体膜と、トンネル絶縁膜と、強磁性体膜とを含む積層体を形成する。その後、写真製版工程およびエッチング工程を経て、積層体および金属膜を加工することで、拡散防止膜上にストラップ配線を形成し、このストラップ配線上に磁気トンネル素子を形成する。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開2007−165505号公報

【発明の概要】

【発明が解決しようとする課題】

【0008】

特開2007−165505号公報に記載された半導体装置の製造方法において、上記上記積層体および、上面に積層体が形成された金属膜を加工して、ストラップ配線および磁気トンネル素子を形成するときには、まず、積層膜上にフォトレジストを形成し、このフォトレジストをパターニングする。

【0009】

そして、パターニングされたフォトレジストをマスクとすると共に、金属膜をストッパとして、積層体にドライエッチングを施す。これにより、磁気トンネル素子が金属膜上に形成される。その後、残留しているフォトレジストを除去するために、アッシングを施す。その後、金属膜にパターニングを施すことで、ストラップ配線が形成される。

【0010】

ここで、ストラップ配線となる金属膜は、積層体にドライエッチングを施す際には、100℃〜300℃程度のガス雰囲気中に曝され、さらに、アッシング処理を行うときにも、金属膜は、アッシングプラズマに曝されることになる。この際、金属膜が酸化や窒化され膨張する。その後、基板がプラズマエッチング処理装置から搬出され、次の処理装置に搬送される。この搬送中において、基板が冷却され、金属膜が収縮して、ウエハが反る。

【0011】

ここで、絶縁膜である拡散防止膜と、金属膜である配線層との密着性は低いため、金属膜が収縮し、ウエハが反ると、拡散防止膜と配線層との間で剥離が生じる。

【0012】

本発明は、上記のような課題に鑑みてなされたものであって、その目的は、上面にストラップ配線が形成された絶縁膜と、この絶縁膜の下面に形成された配線と間で剥離が生じることが抑制された半導体装置および半導体装置の製造方法を提供することである。

【課題を解決するための手段】

【0013】

本発明に係る半導体装置は、1つの局面では、主表面を有する半導体基板と、半導体基板の主表面上に形成され、第1銅配線を含む第1配線層と、第1配線層上に形成され、第2銅配線を含む第2配線層と、第2配線層上に形成され、磁気記憶素子を含む第3配線層と、第1銅配線の上面に接するように形成され、炭化珪素(SiC)膜または炭化窒化ケイ素(SiCN)膜で構成された絶縁膜と、第2銅配線の上面に接するように形成された第1窒化ケイ素(SiN)膜とを備える。上記第2銅配線に磁気記憶素子の書き換え電流が流され、第2銅配線は、銅から形成された配線本体と、配線本体の底面および側面を覆う積層金属膜とを含む。上記積層金属膜は、タンタル(Ta),チタン(Ti),ルテニウム(Ru),マンガン(Mn),マグネシウム(Mg),タングステン(W)の少なくとも1つを含む第1金属膜と、コバルト(Co),ニッケル(Ni),鉄(Fe)の少なくとも1つを含む第2金属膜との積層膜とされる。

【0014】

本発明に係る半導体装置は、他の局面では、主表面を有する半導体基板と、半導体基板の主表面上に形成され、第1銅配線を含む第1配線層と、第1配線層上に形成され、第2銅配線を含む第2配線層と、第2配線層上に形成され、磁気記憶素子を含む第3配線層とを備える。上記第1配線層は、第1銅配線の上面に接するように形成され、炭化珪素(SiC)膜又は炭化窒化ケイ素(SiCN)膜で構成された絶縁膜を含む。上記第2配線層は、第2銅配線の上面に接するように形成された第1窒化ケイ素(SiN)膜と、第2銅配線と間隔をあけて形成された第3銅配線とを含む。上記第3配線層は、第3銅配線の上部と接続される第1プラグと、第1プラグの上部および磁気記憶素子の下部とを接続する第1ストラップ配線とを含む。

【0015】

本発明に係る半導体装置の製造方法は、主表面を有する半導体基板を準備する工程と、

主表面上に第1配線層を形成する工程と、第1配線層のうち、最も上層に位置する第1配線層上に第2配線層を形成する工程と、第2配線層上に磁気記憶素子を含む第3配線層を形成する工程とを備える。上記第1配線層を形成する工程は、第1絶縁膜を形成する工程と、第1絶縁膜に第1銅配線を形成する工程と、第1銅配線の上面と接触する炭化珪素(SiC)膜又は炭化窒化ケイ素(SiCN)膜で構成された絶縁膜を形成する工程とを含む。上記第2配線層を形成する工程は、第1配線層上に第2絶縁膜を形成する工程と、第2絶縁膜に第2銅配線を形成する工程と、第2銅配線上に形成され、第2銅配線の上面と接触する第1窒化ケイ素(SiN)膜を形成する工程とを含む。上記第2銅配線を形成する工程は、第2絶縁膜に第1溝部を形成する工程と、第1溝部の側面および底面に、タンタル(Ta),チタン(Ti),ルテニウム(Ru),マンガン(Mn),マグネシウム(Mg),タングステン(W)の少なくとも1つを含む第1金属膜およびコバルト(Co),ニッケル(Ni),鉄(Fe)の少なくとも1つを含む第2金属膜の積層膜を形成する工程と、積層膜が形成された第1溝部内に銅から形成された配線本体を形成する工程とを有する。

【0016】

本発明に係る半導体の製造方法は、他の局面では、主表面を有する半導体基板を準備する工程と、 主表面上に第1配線層を形成する工程と、第1配線層上に第2配線層を形成する工程と、第2配線層上に磁気記憶素子を含む第3配線層を形成する工程とを備える。上記第1配線層を形成する工程は、第1絶縁膜を形成する工程と、第1絶縁膜に第1銅配線を形成する工程と、第1銅配線の上面に接するように炭化珪素(SiC)膜、又は炭化窒化ケイ素(SiCN)膜で構成された絶縁膜を形成する工程とを含む。上記第2配線層を形成する工程は、第2絶縁膜を形成する工程と、第2絶縁膜に第2銅配線および第3銅配線を形成する工程と、第2銅配線の上面と接触する第1窒化ケイ素(SiN)膜を形成する工程とを含む。上記第3配線層を形成する工程は、第3銅配線の上部に接続される第1プラグを形成する工程と、第1プラグの上部および磁気記憶素子の下部を接続する第1ストラップ配線を形成する工程とを含む。

【発明の効果】

【0017】

本発明に係る半導体装置および半導体装置の製造方法によれば、ストラップ配線の下面に形成された絶縁膜と、この絶縁膜の下面に形成された配線層とが剥離することを抑制することができる。

【図面の簡単な説明】

【0018】

【図1】本実施の形態1に係る半導体装置が搭載されたチップのレイアウトを模式的に示した平面図である。

【図2】MRAM100を模式的に示す模式図である。

【図3】ビット線BL、磁気記憶素子MRおよびディジット線DLの配置関係を模式的に示す平面図である。

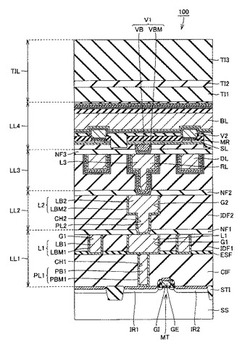

【図4】MRAM100の断面図である。

【図5】配線層LL3およびその周囲に位置する部分を拡大視した断面図である。

【図6】図5のVI−VI線における断面図である。

【図7】周辺回路200における断面図である。

【図8】MRAM100の配線層LL1製造工程の第1製造工程を示す断面図である。

【図9】図8に示す製造工程の次の工程を示す断面図である。

【図10】図9に示す製造工程の次の工程を示す断面図である。

【図11】図10に示す製造工程の次の工程を示す断面図である。

【図12】図11に示す製造工程の次の工程を示す断面図である。

【図13】図12に示す製造工程の次の工程を示す断面図である。

【図14】図13に示す製造工程の次の工程を示す断面図である。

【図15】図14に示す製造工程の次の工程を示す断面図である。

【図16】図15に示す製造工程の次の工程を示す断面図である。

【図17】図16に示す製造工程の次の工程を示す断面図である。

【図18】図17に示す製造工程の次の工程を示す断面図である。

【図19】図18に示す製造工程の次の工程を示す断面図である。

【図20】図19に示す製造工程の次の工程を示す断面図である。

【図21】配線L2が形成されたときにおけるMRAM100の一部を示す断面図であり、上記図5に示す断面に対応する断面図である。

【図22】配線L2が形成されたときのMRAM100の断面図であり、上記図6に示す断面に対応する断面である。

【図23】配線L2が形成されたときの周辺回路200の断面図であり、上記図7に示す断面に対応する断面図である。

【図24】図21に示す製造工程の次の工程を示す断面図である。

【図25】図22に示す製造工程の次の工程を示す断面図である。

【図26】図23に示す製造工程の後の工程を示す断面図である。

【図27】図24に示す製造工程の次の工程を示す断面図である。

【図28】図25に示す製造工程の次の工程を示す断面図である。

【図29】図26に示す製造工程の次の工程を示す断面図である。

【図30】図27に示す製造工程の次の工程を示す断面図である。

【図31】図28に示す製造工程の次の工程を示す断面図である。

【図32】図29に示す製造工程の次の工程を示す断面図である。

【図33】図30に示す製造工程の次の工程を示す断面図である。

【図34】図31に示す製造工程の次の工程を示す断面図である。

【図35】図32に示す製造工程の次の工程を示す断面図である。

【図36】図33に示す製造工程の次の工程を示す断面図である。

【図37】図34に示す製造工程の次の工程を示す断面図である。

【図38】図35に示す製造工程の次の工程を示す断面図である。

【図39】図36に示す製造工程の次の工程を示す断面図である。

【図40】図37に示す製造工程の次の工程を示す断面図である。

【図41】図38に示す製造工程の次の工程を示す断面図である。

【図42】図39に示す製造工程の次の工程を示す断面図である。

【図43】図40に示す製造工程の次の工程を示す断面図である。

【図44】図41に示す製造工程の次の工程を示す断面図である。

【図45】図42に示す製造工程の次の工程を示す断面図である。

【図46】図43に示す製造工程の次の工程を示す断面図である。

【図47】図44に示す製造工程の次の工程を示す断面図である。

【図48】図45に示す製造工程の次の工程を示す断面図である。

【図49】図46に示す製造工程の次の工程を示す断面図である。

【図50】図47に示す製造工程の次の工程を示す断面図である。

【図51】図48に示す製造工程の次の工程を示す断面図である。

【図52】図49に示す製造工程の次の工程を示す断面図である。

【図53】図50に示す製造工程の次の工程を示す断面図である。

【図54】図51に示す製造工程の次の工程を示す断面図である。

【図55】図52に示す製造工程の次の工程を示す断面図である。

【図56】図53に示す製造工程の次の工程を示す断面図である。

【図57】図54に示す製造工程の次の工程を示す断面図である。

【図58】図55に示す製造工程の次の工程を示す断面図である。

【図59】図56に示す製造工程の次の工程を示す断面図である。

【図60】図57に示す製造工程の次の工程を示す断面図である。

【図61】図58に示す製造工程の次の工程を示す断面図である。

【図62】図59に示す製造工程の次の工程を示す断面図である。

【図63】図60に示す製造工程の次の工程を示す断面図である。

【図64】図61に示す製造工程の次の工程を示す断面図である。

【図65】図62に示す製造工程の次の工程を示す断面図である。

【図66】図63に示す製造工程の次の工程を示す断面図である。

【図67】図64に示す製造工程の次の工程を示す断面図である。

【図68】図65に示す製造工程の次の工程を示す断面図である。

【図69】図66に示す製造工程の次の工程を示す断面図である。

【図70】図67に示す製造工程の次の工程を示す断面図である。

【図71】図68に示す製造工程の次の工程を示す断面図である。

【図72】図69に示す製造工程の次の工程を示す断面図である。

【図73】図70に示す製造工程の次の工程を示す断面図である。

【図74】図71に示す製造工程の次の工程を示す断面図である。

【図75】図72に示す製造工程の次の工程を示す断面図である。

【図76】図73に示す製造工程の次の工程を示す断面図である。

【図77】図74に示す製造工程の次の工程を示す断面図である。

【図78】図75に示す製造工程の次の工程を示す断面図である。

【図79】図76に示す製造工程の次の工程を示す断面図である。

【図80】図77に示す製造工程の次の工程を示す断面図である。

【図81】図78に示す製造工程の次の工程を示す断面図である。

【図82】図79に示す製造工程の次の工程を示す断面図である。

【図83】図80に示す製造工程の次の工程を示す断面図である。

【図84】図81に示す製造工程の次の工程を示す断面図である。

【図85】図82に示す製造工程の次の工程を示す断面図である。

【図86】図83に示す製造工程の次の工程を示す断面図である。

【図87】図84に示す製造工程の次の工程を示す断面図である。

【図88】図85に示す製造工程の次の工程を示す断面図である。

【図89】図86に示す製造工程の次の工程を示す断面図である。

【図90】図87に示す製造工程の次の工程を示す断面図である。

【図91】図88に示す製造工程の次の工程を示す断面図である。

【図92】図89に示す製造工程の次の工程を示す断面図である。

【図93】図5において、種類の異なる金属でストラップ配線SLを形成したMRAM100において、MRAM100の製造過程でディジット線DLおよび周辺配線P2等と、拡散防止膜NF3との間で剥がれが生じた個数(割合)を示すグラフである。

【図94】各種のストラップ配線SLを採用した場合に、磁気記憶素子MRをパターニングした後、半導体基板SSが冷却されることで、半導体基板SSに生じる反りを示すグラフである。

【図95】本発明の実施の形態2に係る半導体装置の周辺回路200の断面図である。

【図96】周辺配線P2の幅と、拡散防止膜NF2との間で生じる剥離の相関関係を示すグラフである。

【図97】本実施の形態2に係る半導体装置の製造工程の一部を示す断面図であり、上記図32に対応する工程を示す断面図である。

【図98】図97に示す製造工程後の製造工程を示す断面図である。

【図99】図98に示す製造工程後の製造工程を示す断面図である。

【図100】図99に示す製造工程後の製造工程を示す断面図である。

【図101】本実施の形態3に係る半導体装置の周辺回路200における断面図である。

【図102】本実施の形態3に係る半導体装置の周辺回路200の製造工程の一部を示す断面図である。

【図103】図102に示す製造工程の次の工程を示す断面図である。

【図104】図103に示す製造工程の次の工程を示す断面図である。

【図105】図104に示す製造工程の次の工程を示す断面図である。

【図106】図105に示す製造工程の次の工程を示す断面図である。

【図107】周辺回路200の変形例を示す断面図である。

【図108】図107に示す周辺回路200を製造する工程の一部を示す断面図である。

【図109】図108に示す製造工程の次の工程を示す断面図である。

【図110】図109に示す製造工程の次の工程を示す断面図である。

【図111】本実施の形態4に係る半導体装置に搭載されたMRAM100の断面図である。

【図112】本実施の形態4に係るMRAM100の製造工程の一部を示す断面図である。

【図113】図112に示す製造工程の次の工程を示す断面図である。

【図114】図113に示す製造工程の次の工程を示す断面図である。

【図115】図114に示す製造工程の次の工程を示す断面図である。

【図116】図115に示す製造工程の次の工程を示す断面図である。

【図117】図116に示す製造工程の次の工程を示す断面図である。

【図118】図117に示す製造工程の次の工程を示す断面図である。

【図119】図118に示す製造工程の次の工程を示す断面図である。

【図120】図119に示す製造工程の次の工程を示す断面図である。

【図121】図120に示す製造工程の次の工程を示す断面図である。

【発明を実施するための形態】

【0019】

図1から図110を用いて、本発明に係る実施の形態について説明する。なお、以下に説明する実施の形態において、個数、量などに言及する場合、特に記載がある場合を除き、本発明の範囲は必ずしもその個数、量などに限定されない。また、以下の実施の形態において、各々の構成要素は、特に記載がある場合を除き、本発明にとって必ずしも必須のものではない。また、以下に複数の実施の形態が存在する場合、特に記載がある場合を除き、各々の実施の形態の特徴部分を適宜組合わせることは、当初から予定されている。

【0020】

(実施の形態1)

図1は、本実施の形態1に係る半導体装置が搭載されたチップのレイアウトを模式的に示した平面図である。この図1を参照して、半導体チップ(半導体装置)SCは、半導体基板SSと、半導体基板SSの主表面上に形成されたMRAM100と、周辺回路200と、CPU300と、半導体基板SSの周縁部に形成された複数のパッド部Pとを備える。CPU300は、多種多様な演算処理を行う部分である。

【0021】

MRAM100は、情報を記憶、記憶された情報を読み出し、および情報を書き換えたりすることができるメモリであり、MRAM100は、不揮発性半導体記憶装置である。周辺回路200は、電源回路や、クロック回路やリセット回路等を含む。

【0022】

パッド部Pは、外部回路と、半導体チップSCとを接続するための入出力用の端子部である。

【0023】

図2は、MRAM100を模式的に示す模式図である。この図2を参照して、MRAM100は、複数の磁気記憶素子MRと、一方向に向けて延びる複数のディジット線DLと、このディジット線DLの上方に配置され、ディジット線DLと交差する方向に延びる複数のビット線BLとを含む。

【0024】

さらに、平面視したときにビット線BLとディジット線DLとの交差部分に磁気記憶素子MRが形成されている。

【0025】

図3は、ビット線BL、磁気記憶素子MRおよびディジット線DLの配置関係を模式的に示す平面図である。図4は、MRAM100の断面図である。

【0026】

この図3および図4において、ビット線BLとディジット線DLとの間に、磁気記憶素子MRが形成されており、磁気記憶素子MRの上端部は、ビアプラグV2によってビット線BLに接続されている。磁気記憶素子MRは、ストラップ配線SLの上面上に形成されており、ストラップ配線SLは、ビアプラグV1によって、読出用配線RLに接続されている。

【0027】

磁気記憶素子MRは、トンネル絶縁膜を介して、磁化の方向が固定された強磁性層から形成された固定層と、外部から加えられる磁界によって磁化方向が変化する強磁性層から形成されたフリー層とが対向するように配置されている。

【0028】

この磁気記憶素子MRは、フリー層の磁化方向によって、固定層とフリー層との間の電気抵抗が変化する。

【0029】

たとえば、固定層の磁化方向とフリー層の磁化方向とが同じ場合には、磁気記憶素子MRの抵抗値は低くなる。固定層の磁化方向とフリー層の磁化方向とが異なる場合には、磁気記憶素子MRの抵抗値は高くなる。そこで、抵抗値と、デジタル値の「0」および「1」とを関連付けることで、磁気記憶素子MRをメモリとして機能させる。

【0030】

図4を参照して、MRAM100は、主表面を有する半導体基板SSと、この半導体基板SSの主表面上に形成され、配線(第1配線)L1を含む配線層(第1配線層)LL1と、この配線層LL1の上面に形成され、配線(第1配線)L2を含む配線層(第1配線)LL2と、配線層LL2上に形成され配線L3(第2配線)を含む配線層(第2配線層)LL3と、配線層LL3上に形成された磁気記憶素子MRを含む配線層LL4とを備える。MRAM100は、配線層LL4上に形成された上部絶縁層TILをさらに備える。なお、配線層LL2と配線層LL3との膜厚は実質的に同一である。

【0031】

半導体基板SSの主表面上には、複数の素子分離領域STIが形成されている。配線層LL1は、半導体基板SSの主表面上に形成されたMOSトランジスタMTと、このMOSトランジスタMTに接続されたプラグPL1と、プラグPL1の上端部に接続された配線L1とを含む。さらに、配線層LL1はMOSトランジスタMTを覆うように形成されたコンタクト層間絶縁膜CIFと、コンタクト層間絶縁膜CIFの上面に形成されたエッチングストッパ膜ESFと、エッチングストッパ膜ESFの上面に形成された層間絶縁膜IDF1と、層間絶縁膜IDF1の上面に形成された拡散防止膜NF1とを含む。

【0032】

MOSトランジスタMTは、素子分離領域STIによって区画された活性領域上に形成されている。MOSトランジスタMTは、シリコン酸化膜などから形成されたゲート絶縁膜GIと、ゲート絶縁膜GI上に形成されたゲート電極GEと、不純物拡散層IR1および不純物拡散層IR2とを備える。

【0033】

ゲート電極GEは、ポリシリコン膜等から形成されており、ゲート電極GEの側面上には、シリコン酸化膜等から形成されたサイドウォールが形成されている。

【0034】

不純物拡散層IR1は、半導体基板SSの主表面のうち、ゲート電極GEと隣り合う位置に形成されており、不純物拡散層IR2は、ゲート電極GEに対して不純物拡散層IR1と反対側に形成されている。

【0035】

コンタクト層間絶縁膜CIFは、MOSトランジスタMTを覆うように形成されている。コンタクト層間絶縁膜CIFは、たとえば、オゾンTEOS(tetra-ethyl-ortho-silicate)膜等から形成されている。プラグPL1はコンタクト層間絶縁膜CIFを貫通するように形成されており、コンタクト層間絶縁膜CIFには、コンタクト層間絶縁膜CIFを貫通し、不純物拡散層IR1に達するコンタクトホールCH1が形成されている。プラグPL1は、コンタクトホールCH1の内周面上に形成されたコンタクト用バリアメタルPBM1と、コンタクト用バリアメタルPBM1上に形成され、コンタクトホールCH1内に充填されたプラグ本体部PB1とを含む。

【0036】

コンタクト用バリアメタルPBM1は、たとえば、チタン膜や窒化チタン膜等から形成されている。プラグ本体部PB1は、たとえば、タングステン(W)等から形成されている。

【0037】

エッチングストッパ膜ESFは、コンタクト層間絶縁膜CIFの上面に形成されており、エッチングストッパ膜ESFは、炭化窒化ケイ素膜(SiCN膜)、又は炭化珪素膜(SiC膜)から形成されている。層間絶縁膜IDF1は、エッチングストッパ膜ESFの上面上に形成されており、この層間絶縁膜IDF1は、たとえば、TEOS酸化膜などから形成されている。

【0038】

エッチングストッパ膜ESFおよび層間絶縁膜IDF1内に、複数の配線L1が形成されており、プラグPL1の上部は、1つの配線L1に接続されている。

【0039】

エッチングストッパ膜ESFおよび層間絶縁膜IDF1には、溝部G1が形成されている。配線L1は、溝部G1の内周面に形成されたバリアメタルLBM1と、このバリアメタルLBM1上に形成され、溝部G1内に充填された配線本体部LB1を含む。バリアメタルLBM1は、たとえば、チタン/窒化チタン膜等から形成され、それ以外でもタンタル(Ta),チタン(Ti),ルテニウム(Ru),マンガン(Mn),マグネシウム(Mg),タングステン(W)の少なくとも1つの元素を含む金属材料から形成されてもよい。配線本体部LB1は、銅(銅を主体とする金属材料を含む)から形成されている。バリアメタルLBM1は、配線L1の配線本体部LB1を形成する銅が、熱処理によって、半導体基板SSを構成するシリコンに拡散することを抑制する。これにより、MOSトランジスタMTの閾値の変動、耐圧不良等を抑制し、MOSトランジスタMTの特性劣化を抑制する。

【0040】

拡散防止膜NF1は、層間絶縁膜IDF1の上面および配線L1の上面上に形成されており、拡散防止膜NF1は、炭化窒化ケイ素膜(SiCN膜)、又は炭化珪素膜(SiC膜)から形成されている。

【0041】

エッチングストッパ膜ESFも、バリアメタルLBM1と同様に、配線L1を構成する銅原子が、コンタクト層間絶縁膜CIFおよび半導体基板SS内に拡散することを抑制する。

【0042】

上記のように形成された配線層LL1の上面には、配線層LL2が形成されている。配線層LL2は、拡散防止膜NF1の上面に形成された層間絶縁膜IDF2と、層間絶縁膜IDF2に形成されたプラグPL2および配線L2と、層間絶縁膜IDF2および配線L2の上面を覆うように形成された拡散防止膜NF2とを含む。拡散防止膜NF2は、炭化窒化ケイ素膜(SiCN膜)、又は炭化珪素膜(SiC膜)から形成されており、層間絶縁膜IDF2は、たとえば、TEOS膜、酸化シリコン膜、あるいは、SiOC膜、HSQ膜、MSQ膜、又はSiOF膜等から形成されている。

【0043】

プラグPL2は、配線L2の下面に達するように形成されており、プラグPL2の上端部には、配線L2が接続されている。プラグPL2および配線L2は、層間絶縁膜IDF2内に形成されたコンタクトホールCH2と、コンタクトホールCH2と連通する溝部G2内に形成されている。

【0044】

プラグPL2および配線L2は、コンタクトホールCH2および溝部G2の内周面に形成されたバリアメタルLBM2とバリアメタルLBM2上に形成され、溝部G2およびコンタクトホールCH2内に充填された配線本体部LB2とによって形成されている。

【0045】

バリアメタルLBM2は、バリアメタルLBM1と同様の金属材料から形成されており、配線本体部LB2も配線本体部LB1と同様に銅(銅を主体とする金属材料を含む)から形成されている。拡散防止膜NF2は、配線L2の上面を覆うように形成されており、拡散防止膜NF2は、拡散防止膜NF1と同様に、炭化窒化ケイ素膜(SiCN膜)、又は炭化珪素膜(SiC膜)から形成されている。

【0046】

この配線層LL2の上面には、配線層LL3が形成されている。この配線層LL3内には、ディジット線(第2配線)DLが形成されている。図5は、配線層LL3およびその周囲に位置する部分を拡大視した断面図である。図6は、図5のVI−VI線における断面図である。図7は、周辺回路200における断面図である。

【0047】

図5において、配線層LL3は、拡散防止膜NF2の上面上に形成された層間絶縁膜IDF3と、層間絶縁膜IDF3および拡散防止膜NF2を貫通するように形成された配線L3と、層間絶縁膜IDF3に形成されたディジット線DLと、配線L3およびディジット線DLの上面と接触するように層間絶縁膜IDF3の上面上に形成された拡散防止膜NF3とを含む。層間絶縁膜IDF3は層間絶縁膜IDF2と同一の材料にて形成される。

【0048】

ディジット線DLには、磁気記憶素子MRに書き込まれた情報を書き換える時に電流が供給される。そして、後述するビット線BL内にも、電流が供給される。ディジット線DL内を流れる電流によって磁界が発生し、後述するビット線BL内を流れる電流によっても磁界が発生する。この2つの磁界の構成磁場によって、磁気記憶素子MRに書き込まれた情報が書き換えられる。

【0049】

ディジット線DLは、層間絶縁膜IDF3に形成された溝部DG内に形成されている。ディジット線DLは、溝部DGの底面および内側面を覆う積層金属膜(被覆金属膜)と、この積層金属膜上に形成され、溝部DG内に充填された配線本体部DLBとを含む。

【0050】

積層金属膜は、溝部DGの底面および内側面を覆うように形成されたバリアメタル(第1金属膜)DB1と、バリアメタルDB1上に形成されたクラッド層(第2金属膜)DCLと、クラッド層DCL上に形成されたバリアメタルDB2とを含む。

【0051】

バリアメタルDB1およびバリアメタルDB2は、たとえば、タンタル(Ta),チタン(Ti),ルテニウム(Ru),マンガン(Mn),マグネシウム(Mg),タングステン(W)の少なくとも1つの元素を含む金属材料から形成される。具体的には、チタンや窒化チタンなどが採用される。

【0052】

クラッド層CLDは、高透磁率材料から形成されており、コバルト(Co),ニッケル(Ni),鉄(Fe)の少なくとも1つの元素を含む金属材料から形成される。さらに詳細には、クラッド層CLDは、NiFe(鉄ニッケル)、NiFeMo、CoNbZr(コバルトニオブジルコニウム)、CoFeNb、CoFeSiB、CoNbRu、CoNbZrMoCr、CoZrCrMoなどの合金、もしくはアモルファス合金を用いることが好ましい。配線本体部DLBは、銅(銅を主体として含む金属材料を含む)から形成されている。

【0053】

配線L3は、層間絶縁膜IDF3および拡散防止膜NF2を貫通する溝部G3およびコンタクトホールCH3内に形成されており、配線L3は、配線L2の上端部に接続されている。配線L3は、溝部G3およびコンタクトホールCH3の内周面に形成された積層金属膜と、この積層金属膜の上面に形成され、溝部G3およびコンタクトホールCH3内に充填された配線本体部LB3とを含む。

【0054】

積層金属膜(被覆金属膜)は、溝部G3およびコンタクトホールCH3の内周面に形成されたバリアメタルLBM3と、バリアメタルLBM3上に形成されたクラッド層CL1と、クラッド層CL1上に形成されたバリアメタルLBM4とを含む。バリアメタル(第1金属膜)LBM3およびバリアメタルLBM4は、たとえば、タンタル(Ta),チタン(Ti),ルテニウム(Ru),マンガン(Mn),マグネシウム(Mg),タングステン(W)の少なくとも1つを含む金属材料から形成される。具体的には、チタンや窒化チタンなどが採用される。

【0055】

クラッド層(第2金属膜)CL1としては、透磁率が高く残留磁化の非常に低い軟磁性体を用いることが好ましい。具体的には、クラッド層CL1は、コバルト(Co),ニッケル(Ni),鉄(Fe)の少なくとも1つを含む金属材料から形成される。さらに詳細には、クラッド層CLDは、NiFe(鉄ニッケル)、NiFeMo、CoNbZr(コバルトニオブジルコニウム)、CoFeNb、CoFeSiB、CoNbRu、CoNbZrMoCr、CoZrCrMoなどの合金、もしくはアモルファス合金を用いることが好ましい。配線本体部LB3は、銅(銅を主体とする金属材料を含む)から形成されている。

【0056】

図4において、配線L3、配線L2、配線L1およびプラグPL1は互いに接続され、MOSトランジスタMTの不純物拡散層IR1に接続されており、配線L3、配線L2、配線L1およびプラグPL1は、読出用配線RLとして機能する。拡散防止膜NF3は、ディジット線DLの上面から配線L3の上面に達するように形成され、ディジット線DLの上面および配線L3の上面は、拡散防止膜NF3によって覆われている。

【0057】

図7において、周辺回路200においても、配線層LL2に、層間絶縁膜IDF2と、層間絶縁膜IDF2内に形成された周辺配線P1と、周辺配線P1の上面および層間絶縁膜IDF2の上面を覆うように、拡散防止膜NF2が形成されている。層間絶縁膜IDF2には、溝部PG1が形成されており、この溝部PG1内に周辺配線P1が形成されている。

【0058】

周辺配線P1は、溝部PG1の側面および底面に形成されたバリアメタルPLM1と、このバリアメタルPLM1上に形成された配線本体部PLB1とを含む。バリアメタルPLM1は、図4に示すバリアメタルLBM2と同一の金属材料によって形成されており、配線本体部PLB1は、配線本体部LB2と同一の金属材料によって形成されている。

【0059】

周辺回路200においても、配線層LL3には、拡散防止膜NF2上に形成された層間絶縁膜IDF3が形成されており、層間絶縁膜IDF3の上面には、拡散防止膜NF3が形成されている。

【0060】

層間絶縁膜IDF3および拡散防止膜NF2を貫通するように周辺配線(第4配線)P2が形成されており、周辺配線P2は、周辺配線P1の上端部に接続されている。

【0061】

周辺配線P2は、拡散防止膜NF2および層間絶縁膜IDF3に形成されたコンタクトホールCH4およびこのコンタクトホールCH4と連通する溝部PG2に形成されている。

【0062】

周辺配線P2は、コンタクトホールCH4および溝部PG2の底面および側面に形成された積層金属膜(被覆金属膜)と、この積層金属膜の上面に形成された配線本体部PLB2とを含む。

【0063】

積層金属膜は、バリアメタルPLM2と、バリアメタルPLM2上に形成されたクラッド層PLC1と、クラッド層PLC1上に形成されたバリアメタルPLM3とを含む。

【0064】

バリアメタルPLM2は、図5に示すバリアメタルLBM3と同一の金属材料によって形成されている。クラッド層PLC1は、図5に示すクラッド層CL1と同一の金属材料によって形成されている。バリアメタルPLM3は、図5に示すバリアメタルLBM4と同一の金属材料によって形成されている。配線本体部PLB2も、図5に示す配線本体部LB3と同一の金属材料によって形成されている。

【0065】

そして、図5および図7に示すように、拡散防止膜NF3は、周辺配線P2、ディジット線DLおよび配線L3の上面と接触するように形成されている。ここで、配線本体部PLB2、配線本体部LB3および配線本体部DLBは、いずれも、銅(銅を主体とする金属材料を含む)から形成されており、拡散防止膜NF3は窒化ケイ素(SiN)膜から形成されている。具体的には、LT(Low Temperature)−SiN膜から形成されている。LT(Low Temperature)−SiN膜は、炭化窒化ケイ素膜(SiCN膜)及び炭化珪素膜(SiC膜)よりも硬度が高いため、配線本体部PLB2、配線本体部LB3および配線本体部DLBと、拡散防止膜NF3との剥離が抑制されている。

【0066】

図5において、MRAM100の配線層LL4は、拡散防止膜NF3上に形成された層間絶縁膜(第1層間絶縁膜)IDF4と、拡散防止膜NF3および層間絶縁膜IDF4を貫通するように形成され、配線(第3配線)L3の上部に接続されたビアプラグ(第1プラグ)V1と、ビアプラグV1の上部に接続され、層間絶縁膜IDF4の上面に形成されたストラップ配線SLとを含む。

【0067】

層間絶縁膜IDF4は、複数の厚肉部SPが、ビット線BLの延びる方向に間隔をあけて複数形成されており、厚肉部SP間には、薄肉部TPが形成されている。厚肉部SPは、拡散防止膜NF3の上面のうち、ディジット線DL上に位置する部分から配線L3の上方に位置する部分に亘って形成されている。層間絶縁膜IDF4のうち、厚肉部SPの上面に、ストラップ配線SLが形成されている。

【0068】

ストラップ配線SLは、層間絶縁膜IDF4の厚肉部SP上に形成された第1金属膜SL1と、第1金属膜SL1上に形成された第2金属膜SL2とを含む積層金属膜とされている。第1金属膜SL1は、チタン(Ti)膜から形成されており、第2金属膜SL2は、窒化チタン(TiN)膜から形成されている。

【0069】

層間絶縁膜IDF4および拡散防止膜NF3には、層間絶縁膜IDF4の上面から配線L3の上面に達するビアホールが形成されている。

【0070】

ビアプラグV1は、ビアホール内に位置するバリアメタルVBMと、タングステンや銅等の金属材料によって構成されたビア本体VBとを含む。ビアプラグV1の上面は、第1金属膜SL1に接触している。なお、バリアメタルVBMとしては、たとえば、チタン/窒化チタン膜等から形成され、それ以外でもタンタル(Ta),チタン(Ti),ルテニウム(Ru),マンガン(Mn),マグネシウム(Mg),タングステン(W)の少なくとも1つの元素を含む金属材料から形成されてもよい。

【0071】

ストラップ配線SLの第2金属膜SL2上には、磁気記憶素子MRが形成されている。磁気記憶素子MRは、第2金属膜SL2上に形成された磁化固定層MF1と、この磁化固定層MF1の上面に形成されたトンネル絶縁膜MIと、トンネル絶縁膜MIの上面に形成され磁化自由層MF2とを備えている。

【0072】

磁化固定層MF1は、磁化の方向が固定された層であり、外部磁場によって磁化されている方向が変化しないように構成されている。

【0073】

トンネル絶縁膜MIは、磁化固定層MF1と磁化自由層MF2とを分離する層であって、トンネル絶縁膜MIは、たとえば、酸化アルミニウム膜や酸化マグネシウム膜などの金属酸化物膜から形成されている。

【0074】

磁化自由層MF2は、外部磁場によって磁化方向が可変となるように構成された層であって、強磁性膜から構成されている。

【0075】

磁化固定層MF1および磁化自由層MF2は、たとえばニッケル、鉄および/またはコバルトを主成分とする強磁性材料などから形成されている。さらに、その強磁性材料の磁気特性向上と熱的安定性のため、それら強磁性材料にホウ素、窒素、シリコン、モリブデンなどの添加物が導入されてもよい。磁化固定層および磁化自由層として、ハーフメタルと呼ばれるNiMnSb、Co2Mn(Ge,Si)、Co2Fe(Al,Si)、(Zn,Mn)Fe2O4などが用いられてもよい。ハーフメタルでは一方のスピンバンドにエネルギギャップが存在するので、非常に大きな磁気効果を得ることができ、その結果、大きな信号出力を得ることができる。磁化固定層および磁化自由層の組合せの一例として、磁化固定層としてたとえば白金マンガン合金膜とコバルト鉄合金膜との積層構造が用いられ、磁化自由層としてニッケル鉄合金膜が用いられてもよい。

【0076】

磁気記憶素子MRの磁化自由層MF2上には、ビアプラグV2が形成されており、このビアプラグV2の上端部は、後述するビット線BLに接続されている。

【0077】

ストラップ配線SLの上面には、絶縁膜IF1が形成されている。絶縁膜IF1は、窒化ケイ素(SiN)膜から構成されている。絶縁膜IF1は、ストラップ配線SLの上面を覆うと共に、磁気記憶素子MRの側面およびビアプラグV2の側面の一部を覆うように形成されている。

【0078】

絶縁膜IF1は、上記のように、窒化ケイ素(SiN)膜から形成されており、拡散防止膜NF3と同一の絶縁膜から構成されている。その一方で、ディジット線DLよりも下層に位置する拡散防止膜NF2,NF1は、炭化窒化ケイ素膜(SiCN膜)又は炭化珪素膜(SiC膜)から構成されている。

【0079】

窒化ケイ素(SiN)膜は、炭化窒化ケイ素(SiCN)膜よりも低温で形成することができるため、ディジット線DLよりも上方に位置する拡散防止膜NF3や絶縁膜IF1等を低温で形成することで、ディジット線DLにヒロック(突起)が発生すること抑制することができる。絶縁膜IF1上には、層間絶縁膜IDF5が形成されている。層間絶縁膜IDF5は、たとえば、酸化シリコン膜から形成されている。

【0080】

図6に示すように、層間絶縁膜IDF5には、ビット線BLの延在方向に溝部BLGが形成されており、この溝部BLG内にビット線BLが形成されている。なお、ビアプラグV2の上端部は、この溝部BLG内に入り込むように突出している。

【0081】

ビット線BLは、バリアメタルBB3と、このバリアメタルBB3上に形成されたバリアメタルBB4と、クラッド層BC2と、ビット線本体部BLBとを含む。バリアメタルBB3は、溝部BLGの底面および側面を覆うように形成されており、バリアメタルBB3は、バリアメタルDB1等と同様の金属材料によって構成されている。たとえば、バリアメタルBB3は、タンタル(Ta),窒化タンタル(TaN)などの金属材料から構成されている。それ以外でもタンタル(Ta),チタン(Ti),ルテニウム(Ru),マンガン(Mn),マグネシウム(Mg),タングステン(W)の少なくとも1つの元素を含む金属材料から形成されてもよい。

【0082】

クラッド層BC2は、バリアメタルBB3の内側面上に形成されている。クラッド層BC2は、クラッド層DCLと同様の金属材料によって構成されている。たとえば、クラッド層BC2は、NiFe等から構成されている。なお、図5に示す断面では、クラッド層BC2は、紙面の奥側と手前側とに位置しており、この図5には図示されていない。

【0083】

図6において、バリアメタルBB4は、クラッド層BC2の側面上およびバリアメタルBB3の底面上に形成されており、バリアメタルBB4は、バリアメタルDB2と同一の金属材料によって構成されている。たとえば、バリアメタルBB4は、タンタル(Ta)や窒化タンタル(TaN)から構成されている。それ以外でもタンタル(Ta),チタン(Ti),ルテニウム(Ru),マンガン(Mn),マグネシウム(Mg),タングステン(W)の少なくとも1つの元素を含む金属材料から形成されてもよい。

【0084】

そして、ビット線本体部BLBは、バリアメタルBB4上に形成されており、溝部BLG内に充填されている。ビット線本体部BLBは、銅(銅を主体とする金属を含む)から構成されている。

【0085】

層間絶縁膜IDF5の上面上には、拡散防止膜NF4が形成されており、この拡散防止膜NF4は、ビット線本体部BLBの上面、バリアメタルBB4、クラッド層BC2、およびバリアメタルBB3の上面に接触するように形成されている。拡散防止膜NF4も、拡散防止膜NF3および絶縁膜IF1と同様に、窒化ケイ素(SiN)膜から構成されている。

【0086】

拡散防止膜NF4は、厚く形成された厚肉部と、厚肉部間に位置し、厚肉部よりも薄く形成された薄肉部とを含む。拡散防止膜NF4の厚肉部は、ビット線BLの上面に位置しており、拡散防止膜NF4の薄肉部は、ビット線BLの上面の間に位置する層間絶縁膜IDF5の上面に形成されている。拡散防止膜NF4の厚肉部上に、バリアメタルBB1と、クラッド層BC1と、バリアメタルBB2とが順次積層されて構成された積層金属膜(被覆金属膜)が形成されている。

【0087】

バリアメタルBB1およびバリアメタルBB2は、バリアメタルBB3およびバリアメタルBB4などと同一の金属材料によって形成されている。たとえば、タンタル(Ta)や窒化タンタル(TaN)から構成されている。それ以外でもタンタル(Ta),チタン(Ti),ルテニウム(Ru),マンガン(Mn),マグネシウム(Mg),タングステン(W)の少なくとも1つの元素を含む金属材料から形成されてもよい。クラッド層BC1もクラッド層BC2やクラッド層DCLなどと同一の金属材料から構成されている。

【0088】

このように、MRAM100の配線層LL4は、層間絶縁膜IDF4からバリアメタルBB2の間に位置する複数のレイヤから構成されており、配線層LL4内には、ビアプラグV1、ストラップ配線SL、磁気記憶素子MR、およびビット線BLなどが構成されている。

【0089】

図7において、周辺回路200の配線層LL4は、層間絶縁膜IDF3の上面に位置し、周辺配線P2の上面と接触する拡散防止膜NF3と、この拡散防止膜NF3上に形成された層間絶縁膜IDF4の薄肉部TPと、薄肉部TP上に形成された層間絶縁膜IDF5と、この層間絶縁膜IDF5の上面に形成された拡散防止膜NF4とを含む。配線層LL4は、拡散防止膜NF3、層間絶縁膜IDF4および層間絶縁膜IDF5を貫通するように形成された周辺配線P3を含む。

【0090】

周辺配線P3は、周辺配線P2の上端部に接続されており、周辺配線P3は、拡散防止膜NF3、層間絶縁膜IDF4および層間絶縁膜IDF5に形成されたコンタクトホールCH5および溝部PG3内に形成されている。

【0091】

周辺配線P3はコンタクトホールCH5および溝部PG3の内側面および底面に形成されたバリアメタルPLM4と、このバリアメタルPLM4の側面に形成されたクラッド層PLC2と、バリアメタルPLM4の底面およびクラッド層PLC2の側面上に形成されたバリアメタルPLM5と、配線本体部PLB3とを含む。

【0092】

バリアメタルPLM4は、図6に示すバリアメタルBB3と同一の金属材料によって形成されており、クラッド層PLC2は、図6に示すクラッド層BC2と同一の金属材料によって構成されている。さらに、バリアメタルPLM5は、バリアメタルBB4と同一の金属材料によって形成されている。

【0093】

さらに、配線本体部PLB3は図6に示すビット線本体部BLBと同一の金属材料によって形成されており、具体的には、銅(銅を主体とする金属材料)によって形成されている。拡散防止膜NF4は、窒化ケイ素(SiN)膜から形成されている。

【0094】

上記のように構成された配線層LL4の上面上には、上部絶縁層TILが積層されている。図5〜図7に示すように、上部絶縁層TILは、拡散防止膜NF5上に形成された

上層絶縁膜TI1と、上層絶縁膜TI1上に形成され上層絶縁膜TI2と、上層絶縁膜TI2の上面上に形成された上層絶縁膜TI3とを含む。

【0095】

上層絶縁膜TI1は、窒化ケイ素(SiN)膜から形成されており、上層絶縁膜TI2および上層絶縁膜TI3は、シリコン酸化膜から形成されている。図7において、周辺回路200には、上層絶縁膜TI1,TI2および上層絶縁膜TI3を貫通する外部コンタクトCTが形成されている。

【0096】

上記のように構成されたMRAM100の書き込みおよび読み出し動作について説明する。

【0097】

図5において、MRAM100の磁気記憶素子MRに書き込まれた情報を書き換えるときには、ビット線BLおよびディジット線DLに電流が流される。そして、ビット線BL内を流れる電流によって磁場が発生する。同様にディジット線DLに電流が流れることで、磁場が発生する。各磁場の合成磁場によって、磁気記憶素子MRの磁化自由層の磁化方向が変更される。これにより、磁気記憶素子MR内の情報の書き換えが完了する。

【0098】

この際、図6に示すように、ビット線BLのビット線本体部BLBの側面にはクラッド層BC2が形成され、ビット線BLの上方には、クラッド層BC1が形成されている。

【0099】

このように、ビット線本体部BLBの周囲に形成されたクラッド層は、ビット線本体部BLBの上面および側面を覆うよう配置される一方で、磁気記憶素子MRに向けて開口するように配置されている。

【0100】

各クラッド層は、高透磁率材料から形成されているため、ビット線BL内に電流が流れることで生じる磁束は、クラッド層内を優先的に流れる。この結果、磁束が、各クラッド層より外側に発散することが抑制され、磁気記憶素子MRに磁束が集中する。

【0101】

同様に、図5に示すように、ディジット線DLの配線本体部DLBの側面および底面は、クラッド層DCLによって覆われている。クラッド層DCLは、ディジット線DLの上方に位置する磁気記憶素子MRに向けて開口している。このため、ディジット線DL内を電流が流れることを生じる磁束は、磁気記憶素子MRに集中するように放射される。

【0102】

この結果、ビット線BLおよびディジット線DL内を電流が流れることで生じる合成磁界が強められ、ディジット線DLおよびビット線BLに供給される電流量を少なく抑えたとしても、磁気記憶素子MRの磁化自由層の磁化方向を変更することができる。この結果、MRAM100の消費電力を小さく抑えることができる。

【0103】

磁気記憶素子MRに書き込まれた情報を読み出すときには、図4に示すMOSトランジスタMTのゲート電極GEに所定の電圧が印加され、MOSトランジスタMTがON状態となる。

【0104】

そして、ビット線BLおよび不純物拡散層IR2に所定電圧が印加される。これにより、ビット線BL、磁気記憶素子MR、ストラップ配線SL、ビアプラグV1、読出用配線RL(配線L1〜L3およびプラグPL1)、不純物拡散層IR1および不純物拡散層IR2を通るように電流が流れる。磁気記憶素子MR内の磁化自由層の磁化方向によって、磁気記憶素子MRの抵抗値が変化するため、不純物拡散層IR2およびビット線BL間を流れる電流量から磁気記憶素子MRの抵抗値を検出することで、選択された磁気記憶素子MR内に書き込まれた情報を読み出すことができる。

【0105】

上記のように構成されたMRAM100および周辺回路200の製造方法について、図8から図92を用いて説明する。

【0106】

なお、図8から図20を用いて、MRAM100の配線層LL1の製造工程について説明し、その後、図21から図92を用いて、MRAM100および周辺回路200の配線層LL1〜上部絶縁層TILの製造工程について説明する。

【0107】

図8は、MRAM100の配線層LL1製造工程の第1製造工程を示す断面図である。この図8に示すように、主表面を有する半導体基板SSを準備する。その後、半導体基板SSの主表面上に素子分離領域STIを形成し、主表面上に活性領域を形成する。素子分離領域STIを形成した後、活性領域にイオン注入法などにより、不純物を活性領域内に導入し、図示されないウエル領域やチャネル領域を形成する。ウエル領域やチャネル領域を形成した後、半導体基板SSの主表面に、たとえば、熱酸化処理等を施して、シリコン酸化膜を主表面上に形成する。

【0108】

次に、図9において、半導体基板SSの主表面上に形成されたシリコン酸化膜上に、ポリシリコン膜をCVD(Chemical Vapor Deposition)法などで堆積し、このポリシリコン膜をパターニングする。これにより、半導体基板SSの主表面上にゲート絶縁膜GIが残留すると共に、このゲート絶縁膜GI上にゲート電極GEが形成される。

【0109】

次に、図10において、ゲート電極GEをマスクとして、半導体基板SSの主表面に所定の導電型の不純物を活性領域に導入する。その後、ゲート電極GEを覆うように、酸化シリコン膜および窒化シリコン膜を、CVD法により順次堆積する。そして、形成された酸化シリコン膜および窒化シリコン膜上に異方性エッチングを施すことで、ゲート電極GEの側面上にサイドウォールSWを形成する。

【0110】

サイドウォールSWを形成した後、ゲート電極GEおよびサイドウォールSWをマスクとして、不純物を活性領域に導入する。この2回の不純物の導入により、不純物拡散層IR1および不純物拡散層IR2が形成される。なお、不純物を導入した後には、不純物を拡散させるための熱処理が半導体基板SSに加えられる。

【0111】

次に、図11に示すように、各不純物領域を形成した後、ゲート電極GEの上面および不純物拡散層IR1および不純物拡散層IR2に、コバルトシリサイド膜を形成する。このようにして、半導体基板SSの主表面上にMOSトランジスタMTが形成される。

【0112】

次に図12に示すように、MOSトランジスタMTを形成した後に、MOSトランジスタMTを覆うようにコンタクト層間絶縁膜CIFを形成する。

【0113】

コンタクト層間絶縁膜CIFは、オゾンとTEOSとを原料に使用した熱CVD法により形成されるオゾンTEOS膜と、TEOSを原料に使用したプラズマCVD法により形成されるプラズマTEOS膜との積層膜から形成されている。

【0114】

コンタクト層間絶縁膜CIFに、写真製版処理およびエッチングを施して、コンタクトホールCH1をコンタクト層間絶縁膜CIFに形成する。コンタクトホールCH1を形成した後、スパッタリングなどでコンタクトホールCH1の内周面およびコンタクトホールCH1から露出するコバルトシリサイド膜上にバリアメタルを形成する。なお、バリアメタルとしては、チタン/窒化チタン膜等が採用される。バリアメタルを形成した後、タングステンなどを充填する。タングステン等の金属材料を充填した後、CMP(Chemical Mechanical Polishing)法で、コンタクト層間絶縁膜CIF上に位置するタングステンなどの金属材料と、バリアメタルを除去する。

【0115】

これにより、コンタクト用バリアメタルPBM1およびプラグ本体部PB1を含むプラグPL1が形成される。

【0116】

プラグPL1を形成した後、コンタクト層間絶縁膜CIFの表面に、プラズマ処理を施す。具体的には、アンモニアガスまたは、アンモニアガスおよび窒素ガスをチャンバ内に供給し、このチャンバ内に半導体基板SSを搬入する。その後、チャンバ内を400℃程度として、チャンバ内のガスをプラズマ化する。プラズマ化したガスによって、コンタクト層間絶縁膜CIFの表面にプラズマ処理を施す。

【0117】

次に、図13に示すように、コンタクト層間絶縁膜CIFおよびプラグPL1の上面にエッチングストッパ膜ESFをCVD法などにより形成する。エッチングストッパ膜ESFは、炭化窒化ケイ素膜(SiCN膜)、又は炭化珪素膜(SiC膜)が採用される。なお、エッチングストッパ膜ESFの成膜温度は、たとえば、450℃程度とされている。

【0118】

コンタクト層間絶縁膜CIFの上面には、プラズマ処理が施されているため、エッチングストッパ膜ESFとコンタクト層間絶縁膜CIFとの密着性の向上が図られている。

【0119】

その後、エッチングストッパ膜ESFの上面にCVD法などにより層間絶縁膜IDF1を形成する。層間絶縁膜IDF1としては、酸化シリコン膜や酸化シリコン膜よりも低誘電率である低誘電率膜が採用される。たとえば、TEOS膜、酸化シリコン膜、あるいは、SiOF膜等が採用される。

【0120】

次に、図14に示すように、フォトリソグラフィ技術およびエッチング技術を用いて、層間絶縁膜IDF1およびエッチングストッパ膜ESFにパターニングを施し、溝部G1を形成する。

【0121】

次に、図15に示すように、溝部G1の内周面および溝部G1から露出するプラグPL1の上端部に、スパッタリングなどで、バリアメタルBM0を形成する。バリアメタルBM0は、たとえば、タンタル(Ta)、チタン(Ti)、ルテニウム(Ru)、タングステン(W)、マンガン(Mn)およびこれらの窒化物や窒化珪化物、または、これらの積層膜から構成され、言い換えれば、バリアメタルBM0は、タンタル、チタン、ルテニウム、マンガンのいずれかの金属材料からなる金属材料膜、この金属材料とSi、N、O、Cのいずれかの元素との化合物膜のいずれかの膜から形成される。このバリアメタルBM0上に、電解めっき法などで、銅などの導電膜CF0を堆積する。導電膜CF0は、溝部G1内に埋め込まれる。

【0122】

導電膜CF0は、たとえば、銅(Cu)または銅合金(銅(Cu)とアルミニウム(Al)、マグネシウム(Mg)、チタン(Ti)、マンガン(Mn)、鉄(Fe)、亜鉛(Zn)、ジルコニウム(Zr)、ニオブ(Nb)、モリブデン(Mo)、ルテニウム(Ru)、パラジウム(Pd)、銀(Ag)、金(Au)、In(インジウム)、ランタノイド系金属、アクチノイド系金属などの合金)から形成される。

【0123】

次に、図16に示すように、CMP法などで、層間絶縁膜IDF1上の導電膜CF0およびバリアメタルBM0を除去する。これにより、配線本体部LB1およびバリアメタルLBM1を含む配線L1が形成される。

【0124】

配線L1が形成された層間絶縁膜IDF1に、上記コンタクト層間絶縁膜CIFの上面に施したプラズマ処理と同様のプラズマ処理を施す。

【0125】

次に、図17に示すように、層間絶縁膜IDF1および配線L1の上面上に、拡散防止膜NF1をCVD法により形成する。拡散防止膜NF1は、炭化窒化ケイ素膜(SiCN膜)、又は炭化珪素膜(SiC膜)が採用される。層間絶縁膜IDF1の上面には、プラズマ処理が施されているため、配線L1および層間絶縁膜IDF2と、拡散防止膜NF1との密着性の向上が図られている。なお、拡散防止膜NF1の成膜温度は、たとえば、450℃程度とされている。拡散防止膜NF1の上面に、CVD法などにより、層間絶縁膜IDF2を形成する。層間絶縁膜IDF2は、たとえば、TEOS膜、酸化シリコン膜、あるいは、SiOC膜、HSQ膜、MSQ膜、又はSiOF膜から構成されている。

【0126】

次に、図18に示すように、フォトリソグラフィ技術およびエッチング技術を使用することにより、層間絶縁膜IDF2および拡散防止膜NF1にパターニングを施して、コンタクトホールCH2および溝部G2を形成する。なお、配線L1の上面の一部は、コンタクトホールCH2から露出する。

【0127】

次に、図19に示すように、コンタクトホールCH2および溝部G2の表面上に、バリアメタルBM1をスパッタリングで形成する。その後、導電膜CF1を電解めっき法などで形成し、導電膜CF1をコンタクトホールCH2および溝部G2内に充填する。

【0128】

なお、バリアメタルBM1は、図15に示すバリアメタルBM0で採用可能な金属材料のうち、適当な金属材料が採用される。導電膜CF1も、図15に示す導電膜CF0として採用可能な金属材料のうち、適当な金属材料が採用される。

【0129】

次に、図20に示すように、CMP法により層間絶縁膜IDF2上に位置する導電膜CF1およびバリアメタルBM1が除去される。この結果、コンタクトホールCH2および溝部G2の内表面に形成されたバリアメタルLBM2と、コンタクトホールCH2および溝部G2内に充填された配線本体部LB2とを含む配線L2が形成される。

【0130】

このように、配線L2を形成した後、層間絶縁膜IDF2に、層間絶縁膜IDF1およびコンタクト層間絶縁膜CIFに施したプラズマ処理と同様のプラズマ処理を施す。

【0131】

このようにして、MRAM100の配線層LL1が形成される。そして、図21は、配線L2が形成されたときにおけるMRAM100の一部を示す断面図であり、上記図5に示す断面に対応する断面図である。図22は、配線L2が形成されたときのMRAM100の断面図であり、上記図6に示す断面に対応する断面である。図23は、配線L2が形成されたときの周辺回路200の断面図であり、上記図7に示す断面に対応する断面図である。

【0132】

図24から図26は、各々図21から図23に示す製造工程の後の工程を示す断面図である。

【0133】

図24および図26に示すように、層間絶縁膜IDF2の上面上に、炭化窒化ケイ素膜(SiCN膜)又は炭化珪素膜(SiC膜)から形成された拡散防止膜NF2をCVD法などで形成する。なお、拡散防止膜NF2の成膜温度は、たとえば、450℃程度とされている。次に、図27から図29に示すように、層間絶縁膜IDF3をCVD法により形成する。その後、フォトリソグラフィ技術およびエッチング技術を使用することにより、層間絶縁膜IDF3に溝部DG、溝部G3、コンタクトホールCH3、コンタクトホールCH4および溝部PG2を形成する。

【0134】

なお、図27に示すように、層間絶縁膜IDF3のうち、MRAM100となる部分に溝部DG、コンタクトホールCH3および溝部G3が形成され、図29に示すように、周辺回路200となる部分にコンタクトホールCH4および溝部PG2が形成される。

【0135】

次に、図30から図32に示すように、バリアメタルBM2と、クラッド層CL1と、バリアメタルBM3を順次積層する。

【0136】

なお、バリアメタルBM2およびバリアメタルBM3としては、タンタル(Ta),チタン(Ti),ルテニウム(Ru),マンガン(Mn),マグネシウム(Mg),タングステン(W)の少なくとも1つを含む金属材料から形成される。具体的には、チタンや窒化チタンなどが採用される。

【0137】

クラッド層CL1は、高透磁率材料から形成されており、コバルト(Co),ニッケル(Ni),鉄(Fe)の少なくとも1つを含む金属材料が採用され、さらに詳細には、クラッド層CL1は、NiFe(鉄ニッケル)、NiFeMo、CoNbZr(コバルトニオブジルコニウム)、CoFeNb、CoFeSiB、CoNbRu、CoNbZrMoCr、CoZrCrMoなどの合金、もしくはアモルファス合金を用いることが好ましい。

【0138】

次に、図33から図35に示すように、スパッタリングや電解めっき法などで、金属材料を塗布する。この金属材料としては、銅(銅を主体として含む金属材料を含む)から形成されている。具体的には、銅(Cu)または銅合金(銅(Cu)とアルミニウム(Al)、マグネシウム(Mg)、チタン(Ti)、マンガン(Mn)、鉄(Fe)、亜鉛(Zn)、ジルコニウム(Zr)、ニオブ(Nb)、モリブデン(Mo)、ルテニウム(Ru)、パラジウム(Pd)、銀(Ag)、金(Au)、In(インジウム)、ランタノイド系金属、アクチノイド系金属などの合金)等が採用される。

【0139】

そして、CMP法などで、層間絶縁膜IDF3上に位置する上記金属材料およびバリアメタルBM2、クラッド層CL1およびバリアメタルBM3を除去する。これにより、ディジット線DL、配線L3およびプラグPL2が形成される。

【0140】

そして、ディジット線DL、配線L3およびプラグPL2が形成された層間絶縁膜IDF3にプラズマ処理を施す。

【0141】

まず、半導体基板SSをチャンバ内に搬入し、窒素を含有する分子と窒素を含有しない不活性分子とからなる混合ガスをチャンバ内に導入する。このとき、窒素を含有する分子の流量よりも窒素を含有しない不活性分子の流量が多い条件で、混合ガスを導入し、混合ガスをプラズマ化してプラズマ処理を実施する。

【0142】

そして、層間絶縁膜IDF3の上面上に、LT(Low Temperature)−SiN膜をCVD法により形成する。たとえば、成膜温度は、275℃以下とされる。成膜温度を低く抑えることで、ディジット線DL、配線L3および周辺配線P2にヒロックが形成されることを抑制することができる。さらに、層間絶縁膜IDF3にプラズマ処理が施されているので、拡散防止膜NF3と層間絶縁膜IDF3との密着性の向上が図られている。

【0143】

次に、図36から図38に示すように、拡散防止膜NF3の上面上に、TEOS酸化膜等をCVD法などで堆積し、層間絶縁膜IDF4を形成する。

【0144】

次に、図39から図41に示すように、フォトリソグラフィおよびエッチングを施すことで、層間絶縁膜IDF4および拡散防止膜NF3にビアホールVH1を形成する。これにより、配線L3の上面が露出する。

【0145】

次に、図42から図44に示すように、層間絶縁膜IDF4の上面に、たとえば、チタン/窒化チタン膜などを成膜して、バリアメタルVBMを形成する。なお、バリアメタルVBMとしては、チタン/窒化チタン膜以外でもタンタル(Ta),チタン(Ti),ルテニウム(Ru),マンガン(Mn),マグネシウム(Mg),タングステン(W)の少なくとも1つの元素を含む金属材料を用いてもよい。そして、図45から図47に示すように、バリアメタルVBM上に、タングステンや銅などの金属材料を成膜して、導電膜CF2を形成する。

【0146】

次に、図48から図50に示すように、バリアメタルVBMおよび導電膜CF23にCMPを施して、バリアメタルVBMおよび導電膜CF2を平坦化する。これにより、ビアプラグV1が形成される。

【0147】

次に、図51から図53に示すように、ビアプラグV1の上端部上に、スパッタリングなどで導電膜CF3を形成する。導電膜CF3は、たとえば、チタン(Ti)から形成されている。この導電膜CF3の上面に、導電膜CF4を形成する。導電膜CF4は、窒化チタン(TiN)から構成されている。このように、層間絶縁膜IDF4およびビアプラグV1上に、チタン膜と、チタン上に形成された窒化チタン(TiN)膜との積層構造等を形成する。なお、導電膜CF3および導電膜CF4のいずれも、窒化チタン(TiN)から形成してもよい。このように層間絶縁膜IDF4上に設けられたビア本体VBやバリアメタルVBMを全て除去してからチタンで構成された導電膜CF3を形成した場合、導電膜CF3および導電膜CF3に形成される導電膜CF4の膜質や均一性が良くなる。

【0148】

次に、図54から図56に示すように、まず、導電膜CF4の上面に、磁化固定層MF1、トンネル絶縁膜MIおよび磁化自由層MF2を順次積層する。これにより、導電膜CF4の上面に、積層体LMRが形成される。そして、積層体LMRの磁化自由層MF2の上面に導電膜CF5を形成する。導電膜CF5としては、たとえば、タンタル膜やルテニウム膜等が採用される。

【0149】

次に、図57から図59に示すように、導電膜CF5の上面に、シリコン酸化膜HDPをCVD法などで堆積する。そして、シリコン酸化膜HDPの上面にマスクパターンMP1を形成する。

【0150】

その後、図60から図62に示すように、シリコン酸化膜HDPおよび導電膜CF5にエッチングを施すことで、マスクパターンMP2,MP3が形成される。そして、マスクパターンMP2,MP3を用いて、積層体LMRにプラズマドライエッチングを施す。これにより、図63から図65に示すように、導電膜CF4の上面のうち、MRAM100が形成される領域に、磁気記憶素子MRが形成されると共に、磁気記憶素子MRの上面に、ビアプラグV2が形成される。なお、図65に示すように、周辺回路200となる部分においては、積層体LMRおよびマスクパターンMP3は完全に除去される。そして、アッシング処理を施すことで、ビアプラグV2の上面に残留するマスクパターンMP2を除去する。

【0151】

プラズマドライエッチングを施すときには、半導体基板SSは、チャンバ内に搬入され、半導体基板SSは高温の雰囲気に曝される。このため、導電膜CF4は100℃〜300℃程度のガス雰囲気中に暴露される。同様に、導電膜CF4は、上記アッシング工程において、アッシングプラズマに曝されることになる。

【0152】

ここで、導電膜CF3および導電膜CF4の積層構造は、窒化チタン(TiN)あるいはチタン(Ti)上に窒化チタン(TiN)を形成した2層構造から形成されている。窒化チタン(TiN)は、タンタル(Ta)や窒化タンタル(TaN)などよりも酸化および窒化され難いため、導電膜CF4が上記エッチング工程およびアッシング工程において膨張することが抑制されている。

【0153】

さらに、導電膜CF4および導電膜CF4の直下の導電膜CF3において、上層(導電膜CF4)の窒化チタン(TiN)は、下層(導電膜CF3)のチタン(Ti)よりも酸化および窒化され難いため、下層(Ti)を上層(TiN)で覆うことで、下層(Ti)が酸化および窒化されることが抑制されている。なお、チタン(Ti)は、タンタル(Ta)や窒化タンタル(TaN)よりも酸化および窒化され易い材料である。

【0154】

これにより、導電膜CF4および導電膜CF3は上記エッチング工程およびアッシング工程により導電膜CF4および導電膜CF3が膨張することが抑制されている。

【0155】

エッチング工程およびアッシング工程が終了すると、半導体基板SSはチャンバから搬出され、次の処理装置に搬送される。この搬送過程において、半導体基板SSは冷却されることになるが、上述のように、導電膜CF4および導電膜CF3の膨張は小さく抑えられているため、搬送過程において、導電膜CF4および導電膜CF3が冷却したとしても、導電膜CF4および導電膜CF3内に内部応力が残留することを抑制することができる。

【0156】

半導体基板SSに生じる反りを小さく抑えることができ、拡散防止膜NF3と、配線L3、ディジット線DLおよび周辺配線P2の上面と、拡散防止膜NF3とので剥離などが生じることを抑制することができる。

【0157】

次に、図66から図68に示すように、LT(Low Temperature)−SiNから形成された絶縁膜IF1をたとえば、CVD法により形成する。

【0158】

絶縁膜IF1の成膜温度は、275℃以下とされ、磁気記憶素子MRの磁気特性に影響を与えない温度で成膜することができる。

【0159】

さらに、絶縁膜IF1を低温で形成することで、ディジット線DLなどの上面にヒロックが形成されることを抑制することができる。

【0160】

次に、図69から図71に示すように、絶縁膜IF1にパターニングを施す。パターニングが施された絶縁膜IF1をマスクとして、導電膜CF4をエッチングする。これにより、ストラップ配線SLが形成される。

【0161】

この際、層間絶縁膜IDF4もエッチングされ、厚肉部SPと薄肉部TPとが形成される。そして、厚肉部SP内にビアプラグV1が形成され、厚肉部SPの上面上に、ストラップ配線SLが形成される。そして、ストラップ配線SLの上面に磁気記憶素子MRが形成される。

【0162】

なお、薄肉部TPは、拡散防止膜NF3の上面のうち、厚肉部SPの間に位置する部分と、周辺回路200となる領域に形成される。

【0163】

次に、図72から図74に示すように、絶縁膜IF1を覆うように、シリコン酸化膜等から形成された層間絶縁膜IDF5を、たとえば、CVD法などで形成する。そして、層間絶縁膜IDF5にパターニングを施して、コンタクトホールCH5を形成する。これにより、コンタクトホールCH5の底面において、拡散防止膜NF3の上面が露出する。

【0164】

さらに、図75から図77に示すように、層間絶縁膜IDF5にパターニングを施して、溝部BLGと溝部PG3とを形成する。これにより、溝部G1内で絶縁膜IF1が露出する。

【0165】

そして、溝部BLG内に露出する絶縁膜IF1と、コンタクトホールCH5から露出する拡散防止膜NF3をエッチングする。絶縁膜IF1と、コンタクトホールCH5は、いずれも、窒化ケイ素(SiN)膜から形成されているため、溝部BLG内の絶縁膜IF1およびコンタクトホールCH5の底に位置する拡散防止膜NF3を同一の工程で除去することができる。

【0166】

これにより、ビアプラグV2の上端部と、周辺配線P3の上面の一部とが露出する。

次に、図78から図80において、バリアメタルBM4およびクラッド層CL2をスパッタリング等で順次形成する。

【0167】

その後、クラッド層CL2にエッチングを施すことで、溝部BLG、溝部PG3、コンタクトホールCH5の底部と、層間絶縁膜IDF5の上面に形成されたクラッド層CL2を除去する。これにより、溝部BLG、溝部PG3およびコンタクトホールCH5の側面にクラッド層CL2が残留する。そして、バリアメタルBM5をスパッタリングで形成する。

【0168】

次に、層間絶縁膜IDF5の上面上に電解めっき法やスパッタリング等で、バリアメタルBM5上に銅または銅を主体とする金属膜を堆積する。

【0169】

次に、図81から図83に示すように、CMP法で、上記の金属膜を平坦化することで、溝部G1内に埋め込まれたビット線本体部BLBが形成されると共に、コンタクトホールCH5および溝部PG3内に埋め込まれた配線本体部PLB3が形成される。

【0170】

その後、層間絶縁膜IDF5の上面に位置するバリアメタルBM5およびバリアメタルBM4をCMP法で除去することで、バリアメタルBB3、クラッド層BC2、バリアメタルBB4が溝部BLG内に形成されると共に、バリアメタルPLM4、クラッド層PLC2およびバリアメタルPLM5が、溝部PG3およびコンタクトホールCH5の内周面に形成される。

【0171】

これにより、ビット線BLおよび周辺配線P3が形成されると共に、各側面にクラッド層が形成される。

【0172】

次に、図84から図86に示すように、層間絶縁膜IDF5の上面上に、LT(Low Temperature)−SiN膜等の拡散防止膜NF4を、たとえば、CVD法などで形成する。

【0173】

拡散防止膜NF4の成膜温度は、たとえば、275℃以下とすることができ、既に形成されている磁気記憶素子MRの磁化特性への影響が小さく抑えられている。

【0174】

さらに、LT(Low Temperature)−SiN膜を採用することで、拡散防止膜NF4の成膜温度を低く抑えることで、ビット線BLや周辺配線P3にヒロックが形成されることを抑制することができる。

【0175】

拡散防止膜NF4を形成した後に、バリアメタルBM6、クラッド層CL3およびバリアメタルBM7を、スパッタリング等で順次積層する。

【0176】

次に、図87から図89に示すように、バリアメタルBM7の上面上に、LT(Low Temperature)−SiN膜から形成された拡散防止膜NF5を形成する。なお、拡散防止膜NF5の成膜温度も、275℃以下とされており、ビット線BLにヒロックが形成されることを抑制することができる。そして、この拡散防止膜NF5にパターニングを施す。

【0177】

次に、図90から図92に示すように、パターニングが施された拡散防止膜NF5をマスクとして、バリアメタルBM7、クラッド層CL3およびバリアメタルBM6にパターニングを施す。これにより、ビット線BLの上方に位置するバリアメタルBB1、クラッド層BC1およびバリアメタルBB2が形成される。

【0178】

その後、図5〜図7に示すように、上層絶縁膜TI1を拡散防止膜NF5を覆うように拡散防止膜NF4の上面に形成する。上層絶縁膜TI1も、LT(Low Temperature)−SiN膜が採用されており、275℃以下程度の低温で成膜することができる。これにより、磁気記憶素子MRの磁化特性に影響を与えることが抑制されており、さらに、ビット線BLおよび周辺配線P3にヒロックが形成されることが抑制されている。

【0179】

そして、上層絶縁膜TI1の上面上に、上層絶縁膜TI2,TI3を順次積層する。なお、周辺回路200となる領域においては、拡散防止膜NF4、上層絶縁膜TI1,TI2,TI3にパターニングを施すとともに、金属膜を充填することで、外部コンタクトCTを形成する。このようにして、本実施の形態に係るMRAM100および周辺回路200を形成することができる。

【0180】

上述のように、本実施の形態に係る半導体装置のMRAM100および周辺回路200においては、図4に示す配線層LL1および配線層LL2に形成された配線(第1配線)L1,L2の上面と接するように形成された拡散防止膜NF1,NF2は、炭化窒化ケイ素(SiCN)膜、又は炭化珪素膜(SiC膜)から形成されている。その一方で、書き換え電流が流されるディジット線DLや、このディジット線DLと同一の配線層LL3に形成された配線L3および周辺配線P2の上面と接触する拡散防止膜(第1窒化ケイ素(SiN)膜)NF3は、LT(Low Temperature)−SiN膜によって形成されている。このため、拡散防止膜NF3を形成する過程において、ディジット線DLや周辺配線P2などにヒロックが形成されることを抑制することができると共に、ディジット線DLや周辺配線P2から銅元素が周囲に拡散することを抑制することができる。さらに、図5に示すように、ディジット線DLの底面および側面を覆うように、コバルト(Co),ニッケル(Ni),鉄(Fe)の少なくとも1つの元素を含むクラッド層(第2金属膜)DCLが形成されているため、書き換え動作のときに要する書き換え電流の省電力化を図ることができる。

【0181】

特に、クラッド層DCLの外周面および内周面には、タンタル(Ta),チタン(Ti),ルテニウム(Ru),マンガン(Mn),マグネシウム(Mg),タングステン(W)の少なくとも1つの元素を含むバリアメタル(第1金属膜)DB1,DB2が形成されており、クラッド層DCL内の金属元素やディジット線DLの銅元素が拡散することを抑制することができ、MOSトランジスタMTの特性変動を抑制することができる。

【0182】

さらに、MRAM100は、配線層(第2配線層)LL3内に設けられ、ディジット線DLから間隔をあけて形成された配線(第3配線)L3と、配線層(第3配線層)LL4内に設けられ、配線L3の上部と接続されたストラップ配線(第1ストラップ配線)SLと、拡散防止膜(第1窒化ケイ素(SiN)膜)NF3上に形成された層間絶縁膜(層間絶縁膜)IDF4とをさらに備える。

【0183】

そして、ストラップ配線SLは、チタン(Ti)を含む金属材料から形成することで、MRAM100の製造過程において、ストラップ配線SLが酸化および窒化されることを抑制することができる。

【0184】

なお、本実施の形態においては、チタン(Ti)から形成された第1金属膜SL1と、第1金属膜SL1上に位置し、窒化チタン(TiN)から形成された第2金属膜SL2とから構成している。このように、ストラップ配線SLを積層体から形成することで、ストラップ配線SLの酸化および窒化を抑制することができる。なお、ストラップ配線SLを第2金属膜SL2のみで形成してもよい。

【0185】

図93は、図5において、種類の異なる金属でストラップ配線SLを形成したMRAM100において、MRAM100の製造過程でディジット線DLおよび周辺配線P2等と、拡散防止膜NF3との間で剥がれが生じた個数(割合)を示すグラフである。

【0186】

この図93に示すグラフにおいて、「TaNストラップ」とは、ストラップ配線SLを窒化タンタル(TaN)で形成したMRAM100を示す。「TiNストラップ」とは、ストラップ配線SLを窒化チタン(TiN)で形成したMRAM100を示す。

【0187】

そして、このグラフは、積層体LMRをエッチングして磁気記憶素子MRを形成した後、アッシング処理施し、その後、ウエハを室温で冷却したときに、各MRAM100において、ディジット線DLや周辺配線P3と、拡散防止膜NF3との間で剥がれが生じた個数(割合)を示す。

【0188】

この図93のグラフに示すように、ストラップ配線SLを窒化チタン(TiN)で形成した方が、ストラップ配線SLを窒化タンタル(TaN)で形成したとき場合よりも、剥がれが生じる割合が遥かに小さいことが分かる。

【0189】

これは、窒化チタン(TiN)は、窒化タンタル(TaN)よりも酸化および窒化され難いため、積層体LMRをエッチングする工程やアッシング工程において、ストラップ配線SLが膨張することを抑制することができるためである。

【0190】

図94は、各種のストラップ配線SLを採用した場合に、磁気記憶素子MRをパターニングした後、半導体基板SSが冷却されることで、半導体基板SSに生じる反りを示すグラフである。

【0191】

この図94に示すグラフにおいて、「TaN=35nm」とは、ストラップ配線SLを、35nmの窒化タンタル(TaN)膜で構成したMRAM100を意味する。「TiN=35nm」とは、ストラップ配線SLを35nmの窒化チタン(TiN)で形成したMRAM100を意味する。さらに、「TiN/Ti=23/12nm」とは、ストラップ配線SLを、12nmのチタン(Ti)膜と、このチタン(Ti)膜上に形成された23nmの窒化チタン(TiN)膜との積層膜としたMRAM100を意味する。

【0192】

このグラフは、上記3つのMRAM100において、積層体LMRにエッチングを施して磁気記憶素子MRを形成し、さらに、アッシング処理を施した後、ウエハを冷却したときに、ウエハに生じる反り量を測定した結果を示す。

【0193】

なお、上記3つのMRAM100において、ストラップ配線SL以外の構成は、互いに実質的に同一となるように形成されている。

【0194】

いずれのMRAM100においても、ウエハ(半導体基板SS)の反り量が20μm以上となると、ストラップ配線SLや周辺配線P3と、拡散防止膜NF3との間で剥がれが生じる。

【0195】

そして、グラフに示されるように、ストラップ配線SLを窒化タンタル(TaN)で形成したMRAM100においては、ウエハの反り量は、約38μm程度であることが分かる。ストラップ配線SLを窒化チタン(TiN)で形成したときには、約18μm程度の反りがウエハに生じることが分かる。ストラップ配線SLをチタン(Ti)と、窒化チタン(TiN)との積層膜で形成したMRAM100においては、ウエハに約8μmの反りが生じることが分かる。

【0196】

すなわち、ストラップ配線SLをチタン(Ti)と、窒化チタン(TiN)との積層膜で構成したMRAM100が、ウエハに生じる反り量が最も小さいことが分かる。次に、窒化チタン(TiN)でストラップ配線SLを形成したMRAM100が、ウエハに生じる反り量が小さくなることが分かる。

【0197】

そして、ストラップ配線SLをチタン(Ti)と窒化チタン(TiN)との積層膜で形成したMRAM100と、ストラップ配線SLをチタン(Ti)で形成したMRAM100とにおいては、ウエハの反り量が20μmより小さいことが分かる。

【0198】

したがって、ストラップ配線SLをチタン(Ti)または、チタン(Ti)と窒化チタン(TiN)との積層膜から形成することで、ディジット線DLや周辺配線P3と、拡散防止膜NF3との間で剥離が生じる確率を大きく下げることができることが分かる。

【0199】

なお、上記図93および図94を用いて、本実施の形態に係るMRAM100のディジット線DLに基づく効果について説明したが、さらに、本実施の形態においては、下記のような効果を得ることができる。

【0200】

本実施の形態に係る半導体装置のMRAM100は、ストラップ配線SL上に形成され、磁気記憶素子MRの側面を少なくとも覆うように形成され、LT(Low Temperature)−SiN膜から形成された絶縁膜(第2窒化ケイ素(SiN)膜)IF1を含む。このように、磁気記憶素子MR上に形成される絶縁膜を低温で形成可能なLT(Low Temperature)−SiN膜を採用することで、磁気記憶素子MRの磁気特性が変動することを抑制することができるとともに、ディジット線DLにヒロックが形成されることを抑制することができる。

【0201】

さらに、本実施の形態に係る半導体装置のMRAM100は、配線層LL4内に形成され、磁気記憶素子MR上に形成され、磁気記憶素子MRの上端部に接続されたビット線BLと、このビット線BLの上面と接触し、LT(Low Temperature)−SiN膜によって形成された拡散防止膜(第3窒化ケイ素(SiN)膜)NF4とをさらに備える。このように、ビット線BL上に形成される絶縁膜を低温で形成可能なLT(Low Temperature)−SiN膜とすることで、製造過程においてビット線BLにヒロックが形成されることを抑制することができる。特に、炭化窒化ケイ素(SiCN)膜又は炭化珪素膜(SiC膜)の成膜温度は、450℃程度である一方で、窒化ケイ素(SiN)膜は、275℃以下に抑えることができ、ヒロック対策および磁気記憶素子MRの磁化特性の変動の抑制を効果的に図ることができる。一方窒化珪素膜よりも炭化窒化珪素膜や炭化珪素膜は誘電率が低く、デバイス動作の高速化を図ることができる。

【0202】

(実施の形態2)

図95から図100を用いて、MRAM100および周辺回路200を含む半導体装置について説明する。なお、図95から図100に示す構成のうち、上記図1から図92に示す構成と同一または相当する構成については、同一の符号を付してその説明を省略する場合がある。

【0203】

図95は、本発明の実施の形態2に係る半導体装置の周辺回路200の断面図である。この図95に示す例においては、周辺配線P2は、複数の分割配線DP2を含む。各分割配線DP2は間隔をあけて配置されており、各分割配線DP2は、周辺配線P3および周辺配線P1に接続されている。周辺配線P2を複数の分割配線DP2で構成することで、分割配線DP2の幅Wを小さく抑えることができる。たとえば、分割配線DP2の最大幅は、ディジット線DL、配線L1、配線L2、配線L3、周辺配線P1および周辺配線P3の最大幅よりも小さく抑えられている。なお、本実施の形態2に係る半導体装置および上記実施の形態1に係る半導体装置において、配線層LL1および配線層LL2の厚さと、配線層LL3の厚さとは、実質的に同一となるように形成されている。

【0204】

特に、配線層LL1および配線層LL2(第1配線層)に形成された配線L1、配線L2および周辺配線P1の最大幅よりも小さくなるように形成されている。

【0205】

周辺配線P2は、半導体装置の製造過程において、第1金属膜SL1および第2金属膜SL2に内部応力が生じた際に、拡散防止膜NF3との界面において剥離が生じ易い。特に、周辺配線P2の幅(周辺配線P2の延在方向に対して垂直な方向な断面における幅)と、剥離の発生確率との関係については、一定の関係が発明者等の鋭意努力の結果、配線の幅が4μmよりも大きい場合には、剥離が生じるとの結果が見出されているが、詳細については後述する。

【0206】

配線層LL1および配線層LL2内に位置する配線L1、配線L2および周辺配線P1は、周辺配線P2よりも上記第1金属膜SL1および第2金属膜SL2から離れている。

【0207】

このため、仮に、第1金属膜SL1および第2金属膜SL2が製造過程で酸化や窒化され、膨張した後に、冷却され収縮したしても、配線L1および拡散防止膜NF1の間と、配線L2および拡散防止膜NF2の間とに、剥離は生じにくい。

【0208】

そこで、周辺配線P2を複数の分割配線DP2で構成し、各分割配線DP2の幅を配線層LL1および配線層LL2に形成された配線の幅よりも小さくすることで、分割配線DP2と拡散防止膜NF3との間で剥離が生じることを抑制することができる。

【0209】

図96は、周辺配線P2の幅と、拡散防止膜NF3との間で生じる剥離の相関関係を示すグラフである。この図96において、MRAM100および周辺回路200において、剥離が生じた部分の累積度数を示す。横軸は、拡散防止膜NF3との間で剥離が生じた配線の幅を示す。この図96において、配線幅が4μm以下の部分では、剥離が生じていないことが分かる。そこで、分割配線DP2の最大幅を4μm以下とするのが好ましいことが分かる。なお、同様の理由からディジット線DLおよび配線L3の最大幅も、4μm以下とするのが好ましいことが分かる。

【0210】

この図96に示すグラフにおいて、実線で囲まれた領域において、剥離が発生する頻度が落ちているのは、MRAM100および周辺回路200において、配線の幅が20μm以上となる部分が少ないためである。なお、図95に示す例においては、周辺配線P2を複数の分割配線DP2で構成することで、各分割配線DP2の幅を小さく抑えるように形成しているが、図7に示す周辺配線P2の最大幅を、配線層LL1および配線層LL2(第1配線層)に形成された配線L1、配線L2および周辺配線P1の最大幅よりも小さくなるように形成してもよい。この場合には、周辺配線P2の最大幅を4μmより小さくする。

【0211】

図97を用いて、本実施の形態2に係る半導体装置の製造方法について、図97から図 を用いて説明する。

【0212】

図97は、本実施の形態2に係る半導体装置の製造工程の一部を示す断面図であり、上記図32に対応する工程を示す断面図である。この図97に示すように、層間絶縁膜IDF3に複数の溝部DPGを形成する。その後、バリアメタルBM2、クラッド層CL1およびバリアメタルBM3を順次積層する。

【0213】

次に、図98に示すように、電解めっき法やスパッタリングにより、銅(銅を主体とする金属を含む)を堆積する。これにより、各溝部DPG内に銅が充填される。その後、この銅膜をCMP法により平坦化すると共に、層間絶縁膜IDF4上に位置する銅膜を除去する。さらに、層間絶縁膜IDF4上に位置するバリアメタルBM2、クラッド層CL1およびバリアメタルBM3を除去する。そして、窒化ケイ素(SiN)膜の拡散防止膜NF3を形成する。なお、この図97に示す工程は、上記図35に示す工程に対応する。

【0214】

この図98に示された製造工程後においては、上記実施の形態1に係る製造工程と実質的に同一の処理が施される。

【0215】

そして、図99に示すように、層間絶縁膜IDF5の上面上に、溝部PG3を形成する。その後、バリアメタルBM4およびクラッド層CL2を順次積層する。その後、クラッド層CL2にエッチングを施し、溝部PG2の底面および層間絶縁膜IDF5の上面上に位置するクラッド層CL2を除去する。その後、バリアメタルBM5を堆積する。なお、この図99に示す工程は、上記図80に示す工程に対応する。

【0216】

次に図100に示すように、銅をスパッタリングや電解めっき法により、層間絶縁膜IDF5上に形成する。これにより、溝部PG3内に銅が充填される。その後、層間絶縁膜IDF5上に位置する銅およびバリアメタルBM4およびバリアメタルBM5を除去する。そして、窒化ケイ素(SiN)から形成された拡散防止膜NF4を形成する。なお、この図100に示す工程は、上記図83に対応する工程である。

【0217】

そして、上記実施の形態1において説明した処理と実質的に同一の処理を施すことで、本実施の形態2に係る半導体装置を製造することができる。

【0218】

なお、本実施の形態2に係る半導体装置の製造方法によれば、周辺配線P2は、幅が小さい複数の分割配線DP2によって構成されているため、積層体LMRをパターニングすることで、ウエハに反りが生じたとしても、分割配線DP2と拡散防止膜NF3との間で剥離が生じることを抑制することができる。

【0219】

(実施の形態3)

図101から図110を用いて、本発明の実施の形態3に係る半導体装置およびその製造方法にいついて説明する。なお、図101から図110に示す構成のうち、上記図1から図100に示す構成と同一または相当する構成については、同一の符号を付してその説明を省略する場合がある。

【0220】

図101は、本実施の形態3に係る半導体装置の周辺回路200における断面図である。なお、図101の断面位置は、上記図7に示す断面位置とは異なる位置における断面図である。

【0221】

図101を参照して、周辺配線P2の上面には、複数のダミープラグDPLが形成されている。ダミープラグDPL間の幅W2は、4μmより小さくなるように配置されている。なお、この図101に示す例においては、ダミープラグDPLは、3つ形成されているが、その個数は3つに限られず、適宜変更されることは言うまでもない。

【0222】

ダミープラグDPLは、拡散防止膜NF3および層間絶縁膜IDF4を貫通するように形成された穴部DPHに形成されている。ダミープラグDPLは、穴部DPHの内周面および底部に亘って形成されたバリアメタルVBMと、このバリアメタルVBM上に形成され、穴部DPH内に充填された導電膜CF2とによって構成されている。

【0223】

この図101に示す例においては、ダミープラグDPLの上端部は、層間絶縁膜IDF5に接触するように形成されている。周辺配線P2の上面に複数のダミープラグDPLを形成することで、拡散防止膜NF3と周辺配線P2との密着性が高められている。

【0224】

これにより、この図101に示す周辺回路200を製造する過程において、拡散防止膜NF3と周辺配線P3との間で剥離が生じることを抑制することができる。

【0225】

ここで、図102から図110を用いて、本実施の形態3に係る半導体装置の製造方法について説明する。

【0226】

図102は、本実施の形態3に係る半導体装置の周辺回路200の製造工程の一部を示す断面図である。なお、この図102に示す製造工程は、実施の形態1に係る製造工程のうち、図50に示す製造工程に対応する。

【0227】

ここで、図102に示すように、拡散防止膜NF3および層間絶縁膜IDF4に穴部DPHを形成し、その後、バリアメタルVBMを形成する。バリアメタルVBMを形成した後、スパッタリング等で銅等の金属膜を堆積する。これにより、穴部DPH内に金属膜が充填される。この堆積された金属膜をCMP法などで平坦化する。これにより、層間絶縁膜IDF4上に位置する銅等の金属膜が除去される。

【0228】

次に、図103に示すように、層間絶縁膜IDF4の上面に、導電膜CF3を形成し、この導電膜CF3の上面に導電膜CF4を形成する。なお、図103に示す製造工程は、上記実施の形態1の図53に示す製造工程に対応する。次に、図104に示すように、磁化固定層MF1、トンネル絶縁膜MI、磁化自由層MF2、導電膜CF5およびシリコン酸化膜HDPを順次積層する。なお、この図104に示す製造工程は、上記実施の形態1の図59に対応する工程である。

【0229】

次に、図105に示すように、本実施の形態3に係る周辺回路200が位置する部分のいては、導電膜CF4の上面に形成されたシリコン酸化膜HDP、導電膜CF5、積層体LMRは順次除去される。その後、導電膜CF4の上面上に絶縁膜IF1を形成する。なお、この図105に示す工程は、上記図68に示す工程に対応する。次に、図106に示すように、層間絶縁膜IDF4上に位置する絶縁膜IF1、導電膜CF4および導電膜CF3を順次除去する。さらに、層間絶縁膜IDF4もエッチングされ、薄膜化される。これにより、ダミープラグDPLが、周辺配線P2の上面上に形成される。

【0230】

その後、上記実施の形態1に係る製造工程と同様の製造工程を経ることで、図101に示す周辺回路200を得ることができる。

【0231】

図107は、周辺回路200の変形例を示す断面図である。この図107示す例においては、ダミープラグDPLは、層間絶縁膜IDF4の厚肉部SPおよび拡散防止膜NF3を貫通する穴部DPHに形成されている。

【0232】

そして、ダミープラグDPLの上端部は、ダミー上層配線DTLに接続されている。なお、このダミー上層配線DTLは、導電膜CF3および導電膜CF4の積層膜によって形成されている。ダミー上層配線DTLの導電膜CF3および導電膜CF4は、図5に示すストラップ配線SLの第1金属膜SL1および第2金属膜SL2と同一のレイヤーに形成されているが、ダミー上層配線DTLは、ストラップ配線SLおよび磁気記憶素子MRに電気的に接続されていない。このように、ダミープラグDPLの上端部を導電膜(金属膜)に接続してもよい。

【0233】

図108は、図107に示す周辺回路200を製造する工程の一部を示す断面図である。この図108に示す工程は、上記実施の形態1の図68に示す製造工程に対応する工程を示す図である。この図108に示すように、導電膜CF4の上面上に窒化ケイ素(SiN)から形成された絶縁膜IF1を形成する。

【0234】

次に、図109に示すように、絶縁膜IF1にパターニングを施して、絶縁膜IF1のうち、ダミープラグDPLが位置する部分の上方に位置する部分を残留させる。

【0235】

次に、図110に示すように、パターニングが施された絶縁膜IF1をマスクとして、導電膜CF4および導電膜CF3をパターニングする。これにより、ダミープラグDPLの上部に接続された導電膜CF4および導電膜CF3が残留する。

【0236】

その後、上記実施の形態1に係る半導体装置の製造工程と実質的に同一の工程を経ることで、図17に示された周辺回路200を含む半導体装置が製造される。

【0237】

(実施の形態4)

図111から図121を用いて、本実施の形態4に係る半導体装置について説明する。なお、図111から図120に示す構成のうち、上記図1から図110に示す構成と同一または相当する構成については、同一の符号を付してその説明を省略する。図111は、本実施の形態4に係る半導体装置に搭載されたMRAM100の断面図である。この図111に示すように、本実施の形態4に係るMRAM100も、配線層LL4には、拡散防止膜NF3および層間絶縁膜IDF4内に形成されたビアプラグV1と、このビアプラグV1に接続されたストラップ配線SLと、ストラップ配線SLの上面に形成された磁気記憶素子MRとを備える。

【0238】

ビアプラグV1は、拡散防止膜NF3および層間絶縁膜IDF4を貫通するように形成されたビアホールVH1に形成されている。ビアプラグV1は、ビアホールVH1の内周面および層間絶縁膜IDF4の上面に形成された第1金属膜SL1と、第1金属膜SL1上に形成され、ビアホールVH1内に充填されたビア本体VBと備える。

【0239】

ストラップ配線SLは、上記第1金属膜SL1およびこの第1金属膜SL1の上面に形成された第2金属膜SL2とを備える。このように、第1金属膜SL1は、ビアプラグV1の一部を構成すると共に、ストラップ配線SLの一部を構成する。なお、本実施の形態4においても、第1金属膜SL1は、チタン(Ti)膜から形成されており、第2金属膜SL2は、窒化チタン(TiN)膜から形成されている。

【0240】

第1金属膜SL1が、ビアプラグV1およびストラップ配線SLの構成を兼用することで、半導体装置の製造工程を簡略化することができる。そこで、図112から図120を用いて、本実施の形態4に係る半導体装置の製造方法について説明する。

【0241】

図112は、本実施の形態4に係るMRAM100の製造工程の一部を示す断面図である。なお、この図112に示す工程は、上記図39に示す製造工程に対応する工程である。この図112に示すように、フォトリソグラフィおよびエッチングを施すことで、層間絶縁膜IDF4にビアホールVH1を形成する。

【0242】

次に、図113に示すように、層間絶縁膜IDF4の上面およびビアホールVH1の内周面を覆うように導電膜CF3を、スパッタリングにより形成する。なお、導電膜CF3には、チタン(Ti)が採用される。図114に示すように、導電膜CF3の上面に導電膜CF2をスパッタリングで形成する。導電膜CF2は、タングステンや銅などの金属材料が採用される。

【0243】

次に、図115に示すように、導電膜CF2および導電膜CF3にCMPを施す。これにより、導電膜CF3の上面が露出し、導電膜CF3は、層間絶縁膜IDF4の上面に残留する。導電膜CF2は、ビアホールVH1内に残留する。

【0244】

次に、図116に示すように、導電膜CF2の上面に導電膜CF4を形成する。導電膜CF4には、窒化チタン(TiN)が採用される。次に、図117に示すように、導電膜CF3の上面上に積層体LMRおよび導電膜CF5を形成する。

【0245】

その後、図118に示すように、導電膜CF5の上面上にシリコン酸化膜HDPおよびマスクパターンMP1を形成し、図119に示すように、導電膜CF5をパターニングして、ビアプラグV1および磁気記憶素子MRを形成する。次に、図120に示すように、LT(Low Temperature)−SiNから形成された絶縁膜IF1をたとえば、CVD法により形成する。次に、絶縁膜IF1をパターニングして、マスクを形成する。この絶縁膜IF1のマスクを用いて、図121に示すように導電膜CF4および導電膜CF3をパターニングして、ストラップ配線SLを形成する。

【0246】

このように、ストラップ配線SLの一部を構成する第1金属膜SL1は、ビアプラグV1を形成するときに予め形成されており、製造工程の簡略化が図られている。そして、上記実施の形態1に示す製造工程を同様の製造工程を経ることで、本実施の形態4に係る半導体装置を製造することができる。

【0247】

以上のように本発明の実施の形態について説明を行なったが、今回開示された実施の形態はすべての点で例示であって制限的なものではないと考えられるべきである。本発明の範囲は特許請求の範囲によって示され、特許請求の範囲と均等の意味および範囲内でのすべての変更が含まれることが意図される。さらに、上記数値などは、例示であり、上記数値および範囲にかぎられない。

【産業上の利用可能性】

【0248】

本発明は、半導体装置および半導体装置の製造方法に適用でき、特に、磁気記憶素子を含む半導体装置およびその製造方法に好適である。

【符号の説明】

【0249】

100 MRAM、200 周辺回路、BB1,BB2,BB3,BB4 バリアメタル、BC1 クラッド層、BC2 クラッド層、BL ビット線、BLB ビット線本体部、BLG 溝部、BM0,BM1,BM2,BM3,BM4,BM5,BM6,BM7 バリアメタル、CF0,CF1,CF2,CF3,CF4,CF5 導電膜、CH1,CH2,CH3,CH4,CH5 コンタクトホール、CIF コンタクト層間絶縁膜、CL1,CL2,CL3,CLD クラッド層、CNF 拡散防止膜、CT 外部コンタクト、DB1,DB2 バリアメタル、DCL クラッド層、DG 溝部、DL ディジット線、DLB 配線本体部、DP2 分割配線、DPG 溝部、DPH 穴部、DPL ダミープラグ、DTL ダミー上層配線、G1,G2,G3 溝部、GE ゲート電極、GI ゲート絶縁膜、HDP シリコン酸化膜、IDF1,IDF2,IDF3,IDF4,IDF5 層間絶縁膜、IF1 絶縁膜、IR1,IR2 不純物拡散層、L1,L2,L3 配線、LB1,LB2,LB3 配線本体部、LBM1,LBM2,LBM3,LBM4 バリアメタル、LL1,LL2,LL3,LL4 配線層、LMR 積層体、MF1 磁化固定層、MF2 磁化自由層、MI トンネル絶縁膜、MP2,MP3 マスクパターン、MR 磁気記憶素子、MT トランジスタ、NF1,NF2,NF3,NF4,NF5 拡散防止膜、P パッド部、P1,P2,P3 周辺配線、PB1 プラグ本体部、PBM1 コンタクト用バリアメタル、RL 読出用配線、SC 半導体チップ、SL ストラップ配線、SL1 金属膜、SL2 金属膜、SP 厚肉部、SS 半導体基板、STI 素子分離領域。

【技術分野】

【0001】

本発明は、半導体装置および半導体装置の製造方法に関し、特に、磁気記憶素子を含む半導体装置およびその製造方法に関する発明である。

【背景技術】

【0002】

従来から磁気記憶素子を備えた半導体装置が提案されている。たとえば、特開2007−165505号公報に記載された半導体装置は、磁気トンネル素子と、磁気トンネル抵抗素子が形成された第1の層間絶縁膜と、上面に上記第1の層間絶縁膜が形成された第2の層間絶縁膜とを備える。

【0003】

さらに、この半導体装置は、第2の層間絶縁膜に形成された配線層と、この配線層および第2の層間絶縁膜上に形成された拡散防止膜と、前記拡散防止膜を貫通するコンタクト部と、拡散防止膜上に形成され、コンタクト部に接続されたストラップ配線とを備える。そして、このストラップ配線上に磁気トンネル素子が形成されている。

【0004】

特開2007−165505号公報には、上記のように構成された半導体装置の製造方法が記載されている。

【0005】

第2の層間絶縁膜に配線層を形成した後、拡散防止膜を第2の層間絶縁膜上に形成する。拡散防止膜に配線層に達する開口部を形成し、この開口部にW(タングステン)等を充填して、コンタクトを形成する。

【0006】

コンタクトを形成した後、たとえば、Ta膜等の金属膜を形成し、この金属膜上に強磁性体膜と、トンネル絶縁膜と、強磁性体膜とを含む積層体を形成する。その後、写真製版工程およびエッチング工程を経て、積層体および金属膜を加工することで、拡散防止膜上にストラップ配線を形成し、このストラップ配線上に磁気トンネル素子を形成する。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開2007−165505号公報

【発明の概要】

【発明が解決しようとする課題】

【0008】

特開2007−165505号公報に記載された半導体装置の製造方法において、上記上記積層体および、上面に積層体が形成された金属膜を加工して、ストラップ配線および磁気トンネル素子を形成するときには、まず、積層膜上にフォトレジストを形成し、このフォトレジストをパターニングする。

【0009】

そして、パターニングされたフォトレジストをマスクとすると共に、金属膜をストッパとして、積層体にドライエッチングを施す。これにより、磁気トンネル素子が金属膜上に形成される。その後、残留しているフォトレジストを除去するために、アッシングを施す。その後、金属膜にパターニングを施すことで、ストラップ配線が形成される。

【0010】

ここで、ストラップ配線となる金属膜は、積層体にドライエッチングを施す際には、100℃〜300℃程度のガス雰囲気中に曝され、さらに、アッシング処理を行うときにも、金属膜は、アッシングプラズマに曝されることになる。この際、金属膜が酸化や窒化され膨張する。その後、基板がプラズマエッチング処理装置から搬出され、次の処理装置に搬送される。この搬送中において、基板が冷却され、金属膜が収縮して、ウエハが反る。

【0011】

ここで、絶縁膜である拡散防止膜と、金属膜である配線層との密着性は低いため、金属膜が収縮し、ウエハが反ると、拡散防止膜と配線層との間で剥離が生じる。

【0012】

本発明は、上記のような課題に鑑みてなされたものであって、その目的は、上面にストラップ配線が形成された絶縁膜と、この絶縁膜の下面に形成された配線と間で剥離が生じることが抑制された半導体装置および半導体装置の製造方法を提供することである。

【課題を解決するための手段】

【0013】

本発明に係る半導体装置は、1つの局面では、主表面を有する半導体基板と、半導体基板の主表面上に形成され、第1銅配線を含む第1配線層と、第1配線層上に形成され、第2銅配線を含む第2配線層と、第2配線層上に形成され、磁気記憶素子を含む第3配線層と、第1銅配線の上面に接するように形成され、炭化珪素(SiC)膜または炭化窒化ケイ素(SiCN)膜で構成された絶縁膜と、第2銅配線の上面に接するように形成された第1窒化ケイ素(SiN)膜とを備える。上記第2銅配線に磁気記憶素子の書き換え電流が流され、第2銅配線は、銅から形成された配線本体と、配線本体の底面および側面を覆う積層金属膜とを含む。上記積層金属膜は、タンタル(Ta),チタン(Ti),ルテニウム(Ru),マンガン(Mn),マグネシウム(Mg),タングステン(W)の少なくとも1つを含む第1金属膜と、コバルト(Co),ニッケル(Ni),鉄(Fe)の少なくとも1つを含む第2金属膜との積層膜とされる。

【0014】

本発明に係る半導体装置は、他の局面では、主表面を有する半導体基板と、半導体基板の主表面上に形成され、第1銅配線を含む第1配線層と、第1配線層上に形成され、第2銅配線を含む第2配線層と、第2配線層上に形成され、磁気記憶素子を含む第3配線層とを備える。上記第1配線層は、第1銅配線の上面に接するように形成され、炭化珪素(SiC)膜又は炭化窒化ケイ素(SiCN)膜で構成された絶縁膜を含む。上記第2配線層は、第2銅配線の上面に接するように形成された第1窒化ケイ素(SiN)膜と、第2銅配線と間隔をあけて形成された第3銅配線とを含む。上記第3配線層は、第3銅配線の上部と接続される第1プラグと、第1プラグの上部および磁気記憶素子の下部とを接続する第1ストラップ配線とを含む。

【0015】

本発明に係る半導体装置の製造方法は、主表面を有する半導体基板を準備する工程と、

主表面上に第1配線層を形成する工程と、第1配線層のうち、最も上層に位置する第1配線層上に第2配線層を形成する工程と、第2配線層上に磁気記憶素子を含む第3配線層を形成する工程とを備える。上記第1配線層を形成する工程は、第1絶縁膜を形成する工程と、第1絶縁膜に第1銅配線を形成する工程と、第1銅配線の上面と接触する炭化珪素(SiC)膜又は炭化窒化ケイ素(SiCN)膜で構成された絶縁膜を形成する工程とを含む。上記第2配線層を形成する工程は、第1配線層上に第2絶縁膜を形成する工程と、第2絶縁膜に第2銅配線を形成する工程と、第2銅配線上に形成され、第2銅配線の上面と接触する第1窒化ケイ素(SiN)膜を形成する工程とを含む。上記第2銅配線を形成する工程は、第2絶縁膜に第1溝部を形成する工程と、第1溝部の側面および底面に、タンタル(Ta),チタン(Ti),ルテニウム(Ru),マンガン(Mn),マグネシウム(Mg),タングステン(W)の少なくとも1つを含む第1金属膜およびコバルト(Co),ニッケル(Ni),鉄(Fe)の少なくとも1つを含む第2金属膜の積層膜を形成する工程と、積層膜が形成された第1溝部内に銅から形成された配線本体を形成する工程とを有する。

【0016】

本発明に係る半導体の製造方法は、他の局面では、主表面を有する半導体基板を準備する工程と、 主表面上に第1配線層を形成する工程と、第1配線層上に第2配線層を形成する工程と、第2配線層上に磁気記憶素子を含む第3配線層を形成する工程とを備える。上記第1配線層を形成する工程は、第1絶縁膜を形成する工程と、第1絶縁膜に第1銅配線を形成する工程と、第1銅配線の上面に接するように炭化珪素(SiC)膜、又は炭化窒化ケイ素(SiCN)膜で構成された絶縁膜を形成する工程とを含む。上記第2配線層を形成する工程は、第2絶縁膜を形成する工程と、第2絶縁膜に第2銅配線および第3銅配線を形成する工程と、第2銅配線の上面と接触する第1窒化ケイ素(SiN)膜を形成する工程とを含む。上記第3配線層を形成する工程は、第3銅配線の上部に接続される第1プラグを形成する工程と、第1プラグの上部および磁気記憶素子の下部を接続する第1ストラップ配線を形成する工程とを含む。

【発明の効果】

【0017】

本発明に係る半導体装置および半導体装置の製造方法によれば、ストラップ配線の下面に形成された絶縁膜と、この絶縁膜の下面に形成された配線層とが剥離することを抑制することができる。

【図面の簡単な説明】

【0018】

【図1】本実施の形態1に係る半導体装置が搭載されたチップのレイアウトを模式的に示した平面図である。

【図2】MRAM100を模式的に示す模式図である。

【図3】ビット線BL、磁気記憶素子MRおよびディジット線DLの配置関係を模式的に示す平面図である。

【図4】MRAM100の断面図である。

【図5】配線層LL3およびその周囲に位置する部分を拡大視した断面図である。

【図6】図5のVI−VI線における断面図である。

【図7】周辺回路200における断面図である。

【図8】MRAM100の配線層LL1製造工程の第1製造工程を示す断面図である。

【図9】図8に示す製造工程の次の工程を示す断面図である。

【図10】図9に示す製造工程の次の工程を示す断面図である。

【図11】図10に示す製造工程の次の工程を示す断面図である。

【図12】図11に示す製造工程の次の工程を示す断面図である。

【図13】図12に示す製造工程の次の工程を示す断面図である。

【図14】図13に示す製造工程の次の工程を示す断面図である。

【図15】図14に示す製造工程の次の工程を示す断面図である。

【図16】図15に示す製造工程の次の工程を示す断面図である。

【図17】図16に示す製造工程の次の工程を示す断面図である。

【図18】図17に示す製造工程の次の工程を示す断面図である。

【図19】図18に示す製造工程の次の工程を示す断面図である。

【図20】図19に示す製造工程の次の工程を示す断面図である。

【図21】配線L2が形成されたときにおけるMRAM100の一部を示す断面図であり、上記図5に示す断面に対応する断面図である。

【図22】配線L2が形成されたときのMRAM100の断面図であり、上記図6に示す断面に対応する断面である。

【図23】配線L2が形成されたときの周辺回路200の断面図であり、上記図7に示す断面に対応する断面図である。

【図24】図21に示す製造工程の次の工程を示す断面図である。

【図25】図22に示す製造工程の次の工程を示す断面図である。

【図26】図23に示す製造工程の後の工程を示す断面図である。

【図27】図24に示す製造工程の次の工程を示す断面図である。

【図28】図25に示す製造工程の次の工程を示す断面図である。

【図29】図26に示す製造工程の次の工程を示す断面図である。

【図30】図27に示す製造工程の次の工程を示す断面図である。

【図31】図28に示す製造工程の次の工程を示す断面図である。

【図32】図29に示す製造工程の次の工程を示す断面図である。

【図33】図30に示す製造工程の次の工程を示す断面図である。

【図34】図31に示す製造工程の次の工程を示す断面図である。

【図35】図32に示す製造工程の次の工程を示す断面図である。

【図36】図33に示す製造工程の次の工程を示す断面図である。

【図37】図34に示す製造工程の次の工程を示す断面図である。

【図38】図35に示す製造工程の次の工程を示す断面図である。

【図39】図36に示す製造工程の次の工程を示す断面図である。

【図40】図37に示す製造工程の次の工程を示す断面図である。

【図41】図38に示す製造工程の次の工程を示す断面図である。

【図42】図39に示す製造工程の次の工程を示す断面図である。

【図43】図40に示す製造工程の次の工程を示す断面図である。

【図44】図41に示す製造工程の次の工程を示す断面図である。

【図45】図42に示す製造工程の次の工程を示す断面図である。

【図46】図43に示す製造工程の次の工程を示す断面図である。

【図47】図44に示す製造工程の次の工程を示す断面図である。

【図48】図45に示す製造工程の次の工程を示す断面図である。

【図49】図46に示す製造工程の次の工程を示す断面図である。

【図50】図47に示す製造工程の次の工程を示す断面図である。

【図51】図48に示す製造工程の次の工程を示す断面図である。

【図52】図49に示す製造工程の次の工程を示す断面図である。

【図53】図50に示す製造工程の次の工程を示す断面図である。

【図54】図51に示す製造工程の次の工程を示す断面図である。

【図55】図52に示す製造工程の次の工程を示す断面図である。

【図56】図53に示す製造工程の次の工程を示す断面図である。

【図57】図54に示す製造工程の次の工程を示す断面図である。

【図58】図55に示す製造工程の次の工程を示す断面図である。

【図59】図56に示す製造工程の次の工程を示す断面図である。

【図60】図57に示す製造工程の次の工程を示す断面図である。

【図61】図58に示す製造工程の次の工程を示す断面図である。

【図62】図59に示す製造工程の次の工程を示す断面図である。

【図63】図60に示す製造工程の次の工程を示す断面図である。

【図64】図61に示す製造工程の次の工程を示す断面図である。

【図65】図62に示す製造工程の次の工程を示す断面図である。

【図66】図63に示す製造工程の次の工程を示す断面図である。

【図67】図64に示す製造工程の次の工程を示す断面図である。

【図68】図65に示す製造工程の次の工程を示す断面図である。

【図69】図66に示す製造工程の次の工程を示す断面図である。

【図70】図67に示す製造工程の次の工程を示す断面図である。

【図71】図68に示す製造工程の次の工程を示す断面図である。

【図72】図69に示す製造工程の次の工程を示す断面図である。

【図73】図70に示す製造工程の次の工程を示す断面図である。

【図74】図71に示す製造工程の次の工程を示す断面図である。

【図75】図72に示す製造工程の次の工程を示す断面図である。

【図76】図73に示す製造工程の次の工程を示す断面図である。

【図77】図74に示す製造工程の次の工程を示す断面図である。

【図78】図75に示す製造工程の次の工程を示す断面図である。

【図79】図76に示す製造工程の次の工程を示す断面図である。

【図80】図77に示す製造工程の次の工程を示す断面図である。

【図81】図78に示す製造工程の次の工程を示す断面図である。

【図82】図79に示す製造工程の次の工程を示す断面図である。

【図83】図80に示す製造工程の次の工程を示す断面図である。

【図84】図81に示す製造工程の次の工程を示す断面図である。

【図85】図82に示す製造工程の次の工程を示す断面図である。

【図86】図83に示す製造工程の次の工程を示す断面図である。

【図87】図84に示す製造工程の次の工程を示す断面図である。

【図88】図85に示す製造工程の次の工程を示す断面図である。

【図89】図86に示す製造工程の次の工程を示す断面図である。

【図90】図87に示す製造工程の次の工程を示す断面図である。

【図91】図88に示す製造工程の次の工程を示す断面図である。

【図92】図89に示す製造工程の次の工程を示す断面図である。

【図93】図5において、種類の異なる金属でストラップ配線SLを形成したMRAM100において、MRAM100の製造過程でディジット線DLおよび周辺配線P2等と、拡散防止膜NF3との間で剥がれが生じた個数(割合)を示すグラフである。

【図94】各種のストラップ配線SLを採用した場合に、磁気記憶素子MRをパターニングした後、半導体基板SSが冷却されることで、半導体基板SSに生じる反りを示すグラフである。

【図95】本発明の実施の形態2に係る半導体装置の周辺回路200の断面図である。

【図96】周辺配線P2の幅と、拡散防止膜NF2との間で生じる剥離の相関関係を示すグラフである。

【図97】本実施の形態2に係る半導体装置の製造工程の一部を示す断面図であり、上記図32に対応する工程を示す断面図である。

【図98】図97に示す製造工程後の製造工程を示す断面図である。

【図99】図98に示す製造工程後の製造工程を示す断面図である。

【図100】図99に示す製造工程後の製造工程を示す断面図である。

【図101】本実施の形態3に係る半導体装置の周辺回路200における断面図である。

【図102】本実施の形態3に係る半導体装置の周辺回路200の製造工程の一部を示す断面図である。

【図103】図102に示す製造工程の次の工程を示す断面図である。

【図104】図103に示す製造工程の次の工程を示す断面図である。

【図105】図104に示す製造工程の次の工程を示す断面図である。

【図106】図105に示す製造工程の次の工程を示す断面図である。

【図107】周辺回路200の変形例を示す断面図である。

【図108】図107に示す周辺回路200を製造する工程の一部を示す断面図である。

【図109】図108に示す製造工程の次の工程を示す断面図である。

【図110】図109に示す製造工程の次の工程を示す断面図である。

【図111】本実施の形態4に係る半導体装置に搭載されたMRAM100の断面図である。

【図112】本実施の形態4に係るMRAM100の製造工程の一部を示す断面図である。

【図113】図112に示す製造工程の次の工程を示す断面図である。

【図114】図113に示す製造工程の次の工程を示す断面図である。

【図115】図114に示す製造工程の次の工程を示す断面図である。

【図116】図115に示す製造工程の次の工程を示す断面図である。

【図117】図116に示す製造工程の次の工程を示す断面図である。

【図118】図117に示す製造工程の次の工程を示す断面図である。

【図119】図118に示す製造工程の次の工程を示す断面図である。

【図120】図119に示す製造工程の次の工程を示す断面図である。

【図121】図120に示す製造工程の次の工程を示す断面図である。

【発明を実施するための形態】

【0019】

図1から図110を用いて、本発明に係る実施の形態について説明する。なお、以下に説明する実施の形態において、個数、量などに言及する場合、特に記載がある場合を除き、本発明の範囲は必ずしもその個数、量などに限定されない。また、以下の実施の形態において、各々の構成要素は、特に記載がある場合を除き、本発明にとって必ずしも必須のものではない。また、以下に複数の実施の形態が存在する場合、特に記載がある場合を除き、各々の実施の形態の特徴部分を適宜組合わせることは、当初から予定されている。

【0020】

(実施の形態1)

図1は、本実施の形態1に係る半導体装置が搭載されたチップのレイアウトを模式的に示した平面図である。この図1を参照して、半導体チップ(半導体装置)SCは、半導体基板SSと、半導体基板SSの主表面上に形成されたMRAM100と、周辺回路200と、CPU300と、半導体基板SSの周縁部に形成された複数のパッド部Pとを備える。CPU300は、多種多様な演算処理を行う部分である。

【0021】

MRAM100は、情報を記憶、記憶された情報を読み出し、および情報を書き換えたりすることができるメモリであり、MRAM100は、不揮発性半導体記憶装置である。周辺回路200は、電源回路や、クロック回路やリセット回路等を含む。

【0022】

パッド部Pは、外部回路と、半導体チップSCとを接続するための入出力用の端子部である。

【0023】

図2は、MRAM100を模式的に示す模式図である。この図2を参照して、MRAM100は、複数の磁気記憶素子MRと、一方向に向けて延びる複数のディジット線DLと、このディジット線DLの上方に配置され、ディジット線DLと交差する方向に延びる複数のビット線BLとを含む。

【0024】

さらに、平面視したときにビット線BLとディジット線DLとの交差部分に磁気記憶素子MRが形成されている。

【0025】

図3は、ビット線BL、磁気記憶素子MRおよびディジット線DLの配置関係を模式的に示す平面図である。図4は、MRAM100の断面図である。

【0026】

この図3および図4において、ビット線BLとディジット線DLとの間に、磁気記憶素子MRが形成されており、磁気記憶素子MRの上端部は、ビアプラグV2によってビット線BLに接続されている。磁気記憶素子MRは、ストラップ配線SLの上面上に形成されており、ストラップ配線SLは、ビアプラグV1によって、読出用配線RLに接続されている。

【0027】

磁気記憶素子MRは、トンネル絶縁膜を介して、磁化の方向が固定された強磁性層から形成された固定層と、外部から加えられる磁界によって磁化方向が変化する強磁性層から形成されたフリー層とが対向するように配置されている。

【0028】

この磁気記憶素子MRは、フリー層の磁化方向によって、固定層とフリー層との間の電気抵抗が変化する。

【0029】

たとえば、固定層の磁化方向とフリー層の磁化方向とが同じ場合には、磁気記憶素子MRの抵抗値は低くなる。固定層の磁化方向とフリー層の磁化方向とが異なる場合には、磁気記憶素子MRの抵抗値は高くなる。そこで、抵抗値と、デジタル値の「0」および「1」とを関連付けることで、磁気記憶素子MRをメモリとして機能させる。

【0030】

図4を参照して、MRAM100は、主表面を有する半導体基板SSと、この半導体基板SSの主表面上に形成され、配線(第1配線)L1を含む配線層(第1配線層)LL1と、この配線層LL1の上面に形成され、配線(第1配線)L2を含む配線層(第1配線)LL2と、配線層LL2上に形成され配線L3(第2配線)を含む配線層(第2配線層)LL3と、配線層LL3上に形成された磁気記憶素子MRを含む配線層LL4とを備える。MRAM100は、配線層LL4上に形成された上部絶縁層TILをさらに備える。なお、配線層LL2と配線層LL3との膜厚は実質的に同一である。

【0031】

半導体基板SSの主表面上には、複数の素子分離領域STIが形成されている。配線層LL1は、半導体基板SSの主表面上に形成されたMOSトランジスタMTと、このMOSトランジスタMTに接続されたプラグPL1と、プラグPL1の上端部に接続された配線L1とを含む。さらに、配線層LL1はMOSトランジスタMTを覆うように形成されたコンタクト層間絶縁膜CIFと、コンタクト層間絶縁膜CIFの上面に形成されたエッチングストッパ膜ESFと、エッチングストッパ膜ESFの上面に形成された層間絶縁膜IDF1と、層間絶縁膜IDF1の上面に形成された拡散防止膜NF1とを含む。

【0032】

MOSトランジスタMTは、素子分離領域STIによって区画された活性領域上に形成されている。MOSトランジスタMTは、シリコン酸化膜などから形成されたゲート絶縁膜GIと、ゲート絶縁膜GI上に形成されたゲート電極GEと、不純物拡散層IR1および不純物拡散層IR2とを備える。

【0033】

ゲート電極GEは、ポリシリコン膜等から形成されており、ゲート電極GEの側面上には、シリコン酸化膜等から形成されたサイドウォールが形成されている。

【0034】

不純物拡散層IR1は、半導体基板SSの主表面のうち、ゲート電極GEと隣り合う位置に形成されており、不純物拡散層IR2は、ゲート電極GEに対して不純物拡散層IR1と反対側に形成されている。

【0035】

コンタクト層間絶縁膜CIFは、MOSトランジスタMTを覆うように形成されている。コンタクト層間絶縁膜CIFは、たとえば、オゾンTEOS(tetra-ethyl-ortho-silicate)膜等から形成されている。プラグPL1はコンタクト層間絶縁膜CIFを貫通するように形成されており、コンタクト層間絶縁膜CIFには、コンタクト層間絶縁膜CIFを貫通し、不純物拡散層IR1に達するコンタクトホールCH1が形成されている。プラグPL1は、コンタクトホールCH1の内周面上に形成されたコンタクト用バリアメタルPBM1と、コンタクト用バリアメタルPBM1上に形成され、コンタクトホールCH1内に充填されたプラグ本体部PB1とを含む。

【0036】

コンタクト用バリアメタルPBM1は、たとえば、チタン膜や窒化チタン膜等から形成されている。プラグ本体部PB1は、たとえば、タングステン(W)等から形成されている。

【0037】

エッチングストッパ膜ESFは、コンタクト層間絶縁膜CIFの上面に形成されており、エッチングストッパ膜ESFは、炭化窒化ケイ素膜(SiCN膜)、又は炭化珪素膜(SiC膜)から形成されている。層間絶縁膜IDF1は、エッチングストッパ膜ESFの上面上に形成されており、この層間絶縁膜IDF1は、たとえば、TEOS酸化膜などから形成されている。

【0038】

エッチングストッパ膜ESFおよび層間絶縁膜IDF1内に、複数の配線L1が形成されており、プラグPL1の上部は、1つの配線L1に接続されている。

【0039】

エッチングストッパ膜ESFおよび層間絶縁膜IDF1には、溝部G1が形成されている。配線L1は、溝部G1の内周面に形成されたバリアメタルLBM1と、このバリアメタルLBM1上に形成され、溝部G1内に充填された配線本体部LB1を含む。バリアメタルLBM1は、たとえば、チタン/窒化チタン膜等から形成され、それ以外でもタンタル(Ta),チタン(Ti),ルテニウム(Ru),マンガン(Mn),マグネシウム(Mg),タングステン(W)の少なくとも1つの元素を含む金属材料から形成されてもよい。配線本体部LB1は、銅(銅を主体とする金属材料を含む)から形成されている。バリアメタルLBM1は、配線L1の配線本体部LB1を形成する銅が、熱処理によって、半導体基板SSを構成するシリコンに拡散することを抑制する。これにより、MOSトランジスタMTの閾値の変動、耐圧不良等を抑制し、MOSトランジスタMTの特性劣化を抑制する。

【0040】

拡散防止膜NF1は、層間絶縁膜IDF1の上面および配線L1の上面上に形成されており、拡散防止膜NF1は、炭化窒化ケイ素膜(SiCN膜)、又は炭化珪素膜(SiC膜)から形成されている。

【0041】

エッチングストッパ膜ESFも、バリアメタルLBM1と同様に、配線L1を構成する銅原子が、コンタクト層間絶縁膜CIFおよび半導体基板SS内に拡散することを抑制する。

【0042】

上記のように形成された配線層LL1の上面には、配線層LL2が形成されている。配線層LL2は、拡散防止膜NF1の上面に形成された層間絶縁膜IDF2と、層間絶縁膜IDF2に形成されたプラグPL2および配線L2と、層間絶縁膜IDF2および配線L2の上面を覆うように形成された拡散防止膜NF2とを含む。拡散防止膜NF2は、炭化窒化ケイ素膜(SiCN膜)、又は炭化珪素膜(SiC膜)から形成されており、層間絶縁膜IDF2は、たとえば、TEOS膜、酸化シリコン膜、あるいは、SiOC膜、HSQ膜、MSQ膜、又はSiOF膜等から形成されている。

【0043】

プラグPL2は、配線L2の下面に達するように形成されており、プラグPL2の上端部には、配線L2が接続されている。プラグPL2および配線L2は、層間絶縁膜IDF2内に形成されたコンタクトホールCH2と、コンタクトホールCH2と連通する溝部G2内に形成されている。

【0044】

プラグPL2および配線L2は、コンタクトホールCH2および溝部G2の内周面に形成されたバリアメタルLBM2とバリアメタルLBM2上に形成され、溝部G2およびコンタクトホールCH2内に充填された配線本体部LB2とによって形成されている。

【0045】

バリアメタルLBM2は、バリアメタルLBM1と同様の金属材料から形成されており、配線本体部LB2も配線本体部LB1と同様に銅(銅を主体とする金属材料を含む)から形成されている。拡散防止膜NF2は、配線L2の上面を覆うように形成されており、拡散防止膜NF2は、拡散防止膜NF1と同様に、炭化窒化ケイ素膜(SiCN膜)、又は炭化珪素膜(SiC膜)から形成されている。

【0046】

この配線層LL2の上面には、配線層LL3が形成されている。この配線層LL3内には、ディジット線(第2配線)DLが形成されている。図5は、配線層LL3およびその周囲に位置する部分を拡大視した断面図である。図6は、図5のVI−VI線における断面図である。図7は、周辺回路200における断面図である。

【0047】

図5において、配線層LL3は、拡散防止膜NF2の上面上に形成された層間絶縁膜IDF3と、層間絶縁膜IDF3および拡散防止膜NF2を貫通するように形成された配線L3と、層間絶縁膜IDF3に形成されたディジット線DLと、配線L3およびディジット線DLの上面と接触するように層間絶縁膜IDF3の上面上に形成された拡散防止膜NF3とを含む。層間絶縁膜IDF3は層間絶縁膜IDF2と同一の材料にて形成される。

【0048】

ディジット線DLには、磁気記憶素子MRに書き込まれた情報を書き換える時に電流が供給される。そして、後述するビット線BL内にも、電流が供給される。ディジット線DL内を流れる電流によって磁界が発生し、後述するビット線BL内を流れる電流によっても磁界が発生する。この2つの磁界の構成磁場によって、磁気記憶素子MRに書き込まれた情報が書き換えられる。

【0049】

ディジット線DLは、層間絶縁膜IDF3に形成された溝部DG内に形成されている。ディジット線DLは、溝部DGの底面および内側面を覆う積層金属膜(被覆金属膜)と、この積層金属膜上に形成され、溝部DG内に充填された配線本体部DLBとを含む。

【0050】

積層金属膜は、溝部DGの底面および内側面を覆うように形成されたバリアメタル(第1金属膜)DB1と、バリアメタルDB1上に形成されたクラッド層(第2金属膜)DCLと、クラッド層DCL上に形成されたバリアメタルDB2とを含む。

【0051】

バリアメタルDB1およびバリアメタルDB2は、たとえば、タンタル(Ta),チタン(Ti),ルテニウム(Ru),マンガン(Mn),マグネシウム(Mg),タングステン(W)の少なくとも1つの元素を含む金属材料から形成される。具体的には、チタンや窒化チタンなどが採用される。

【0052】

クラッド層CLDは、高透磁率材料から形成されており、コバルト(Co),ニッケル(Ni),鉄(Fe)の少なくとも1つの元素を含む金属材料から形成される。さらに詳細には、クラッド層CLDは、NiFe(鉄ニッケル)、NiFeMo、CoNbZr(コバルトニオブジルコニウム)、CoFeNb、CoFeSiB、CoNbRu、CoNbZrMoCr、CoZrCrMoなどの合金、もしくはアモルファス合金を用いることが好ましい。配線本体部DLBは、銅(銅を主体として含む金属材料を含む)から形成されている。

【0053】

配線L3は、層間絶縁膜IDF3および拡散防止膜NF2を貫通する溝部G3およびコンタクトホールCH3内に形成されており、配線L3は、配線L2の上端部に接続されている。配線L3は、溝部G3およびコンタクトホールCH3の内周面に形成された積層金属膜と、この積層金属膜の上面に形成され、溝部G3およびコンタクトホールCH3内に充填された配線本体部LB3とを含む。

【0054】

積層金属膜(被覆金属膜)は、溝部G3およびコンタクトホールCH3の内周面に形成されたバリアメタルLBM3と、バリアメタルLBM3上に形成されたクラッド層CL1と、クラッド層CL1上に形成されたバリアメタルLBM4とを含む。バリアメタル(第1金属膜)LBM3およびバリアメタルLBM4は、たとえば、タンタル(Ta),チタン(Ti),ルテニウム(Ru),マンガン(Mn),マグネシウム(Mg),タングステン(W)の少なくとも1つを含む金属材料から形成される。具体的には、チタンや窒化チタンなどが採用される。

【0055】

クラッド層(第2金属膜)CL1としては、透磁率が高く残留磁化の非常に低い軟磁性体を用いることが好ましい。具体的には、クラッド層CL1は、コバルト(Co),ニッケル(Ni),鉄(Fe)の少なくとも1つを含む金属材料から形成される。さらに詳細には、クラッド層CLDは、NiFe(鉄ニッケル)、NiFeMo、CoNbZr(コバルトニオブジルコニウム)、CoFeNb、CoFeSiB、CoNbRu、CoNbZrMoCr、CoZrCrMoなどの合金、もしくはアモルファス合金を用いることが好ましい。配線本体部LB3は、銅(銅を主体とする金属材料を含む)から形成されている。

【0056】

図4において、配線L3、配線L2、配線L1およびプラグPL1は互いに接続され、MOSトランジスタMTの不純物拡散層IR1に接続されており、配線L3、配線L2、配線L1およびプラグPL1は、読出用配線RLとして機能する。拡散防止膜NF3は、ディジット線DLの上面から配線L3の上面に達するように形成され、ディジット線DLの上面および配線L3の上面は、拡散防止膜NF3によって覆われている。

【0057】

図7において、周辺回路200においても、配線層LL2に、層間絶縁膜IDF2と、層間絶縁膜IDF2内に形成された周辺配線P1と、周辺配線P1の上面および層間絶縁膜IDF2の上面を覆うように、拡散防止膜NF2が形成されている。層間絶縁膜IDF2には、溝部PG1が形成されており、この溝部PG1内に周辺配線P1が形成されている。

【0058】

周辺配線P1は、溝部PG1の側面および底面に形成されたバリアメタルPLM1と、このバリアメタルPLM1上に形成された配線本体部PLB1とを含む。バリアメタルPLM1は、図4に示すバリアメタルLBM2と同一の金属材料によって形成されており、配線本体部PLB1は、配線本体部LB2と同一の金属材料によって形成されている。

【0059】

周辺回路200においても、配線層LL3には、拡散防止膜NF2上に形成された層間絶縁膜IDF3が形成されており、層間絶縁膜IDF3の上面には、拡散防止膜NF3が形成されている。

【0060】

層間絶縁膜IDF3および拡散防止膜NF2を貫通するように周辺配線(第4配線)P2が形成されており、周辺配線P2は、周辺配線P1の上端部に接続されている。

【0061】

周辺配線P2は、拡散防止膜NF2および層間絶縁膜IDF3に形成されたコンタクトホールCH4およびこのコンタクトホールCH4と連通する溝部PG2に形成されている。

【0062】

周辺配線P2は、コンタクトホールCH4および溝部PG2の底面および側面に形成された積層金属膜(被覆金属膜)と、この積層金属膜の上面に形成された配線本体部PLB2とを含む。

【0063】

積層金属膜は、バリアメタルPLM2と、バリアメタルPLM2上に形成されたクラッド層PLC1と、クラッド層PLC1上に形成されたバリアメタルPLM3とを含む。

【0064】

バリアメタルPLM2は、図5に示すバリアメタルLBM3と同一の金属材料によって形成されている。クラッド層PLC1は、図5に示すクラッド層CL1と同一の金属材料によって形成されている。バリアメタルPLM3は、図5に示すバリアメタルLBM4と同一の金属材料によって形成されている。配線本体部PLB2も、図5に示す配線本体部LB3と同一の金属材料によって形成されている。

【0065】

そして、図5および図7に示すように、拡散防止膜NF3は、周辺配線P2、ディジット線DLおよび配線L3の上面と接触するように形成されている。ここで、配線本体部PLB2、配線本体部LB3および配線本体部DLBは、いずれも、銅(銅を主体とする金属材料を含む)から形成されており、拡散防止膜NF3は窒化ケイ素(SiN)膜から形成されている。具体的には、LT(Low Temperature)−SiN膜から形成されている。LT(Low Temperature)−SiN膜は、炭化窒化ケイ素膜(SiCN膜)及び炭化珪素膜(SiC膜)よりも硬度が高いため、配線本体部PLB2、配線本体部LB3および配線本体部DLBと、拡散防止膜NF3との剥離が抑制されている。

【0066】

図5において、MRAM100の配線層LL4は、拡散防止膜NF3上に形成された層間絶縁膜(第1層間絶縁膜)IDF4と、拡散防止膜NF3および層間絶縁膜IDF4を貫通するように形成され、配線(第3配線)L3の上部に接続されたビアプラグ(第1プラグ)V1と、ビアプラグV1の上部に接続され、層間絶縁膜IDF4の上面に形成されたストラップ配線SLとを含む。

【0067】

層間絶縁膜IDF4は、複数の厚肉部SPが、ビット線BLの延びる方向に間隔をあけて複数形成されており、厚肉部SP間には、薄肉部TPが形成されている。厚肉部SPは、拡散防止膜NF3の上面のうち、ディジット線DL上に位置する部分から配線L3の上方に位置する部分に亘って形成されている。層間絶縁膜IDF4のうち、厚肉部SPの上面に、ストラップ配線SLが形成されている。

【0068】

ストラップ配線SLは、層間絶縁膜IDF4の厚肉部SP上に形成された第1金属膜SL1と、第1金属膜SL1上に形成された第2金属膜SL2とを含む積層金属膜とされている。第1金属膜SL1は、チタン(Ti)膜から形成されており、第2金属膜SL2は、窒化チタン(TiN)膜から形成されている。

【0069】

層間絶縁膜IDF4および拡散防止膜NF3には、層間絶縁膜IDF4の上面から配線L3の上面に達するビアホールが形成されている。

【0070】

ビアプラグV1は、ビアホール内に位置するバリアメタルVBMと、タングステンや銅等の金属材料によって構成されたビア本体VBとを含む。ビアプラグV1の上面は、第1金属膜SL1に接触している。なお、バリアメタルVBMとしては、たとえば、チタン/窒化チタン膜等から形成され、それ以外でもタンタル(Ta),チタン(Ti),ルテニウム(Ru),マンガン(Mn),マグネシウム(Mg),タングステン(W)の少なくとも1つの元素を含む金属材料から形成されてもよい。

【0071】

ストラップ配線SLの第2金属膜SL2上には、磁気記憶素子MRが形成されている。磁気記憶素子MRは、第2金属膜SL2上に形成された磁化固定層MF1と、この磁化固定層MF1の上面に形成されたトンネル絶縁膜MIと、トンネル絶縁膜MIの上面に形成され磁化自由層MF2とを備えている。

【0072】

磁化固定層MF1は、磁化の方向が固定された層であり、外部磁場によって磁化されている方向が変化しないように構成されている。

【0073】

トンネル絶縁膜MIは、磁化固定層MF1と磁化自由層MF2とを分離する層であって、トンネル絶縁膜MIは、たとえば、酸化アルミニウム膜や酸化マグネシウム膜などの金属酸化物膜から形成されている。

【0074】

磁化自由層MF2は、外部磁場によって磁化方向が可変となるように構成された層であって、強磁性膜から構成されている。

【0075】

磁化固定層MF1および磁化自由層MF2は、たとえばニッケル、鉄および/またはコバルトを主成分とする強磁性材料などから形成されている。さらに、その強磁性材料の磁気特性向上と熱的安定性のため、それら強磁性材料にホウ素、窒素、シリコン、モリブデンなどの添加物が導入されてもよい。磁化固定層および磁化自由層として、ハーフメタルと呼ばれるNiMnSb、Co2Mn(Ge,Si)、Co2Fe(Al,Si)、(Zn,Mn)Fe2O4などが用いられてもよい。ハーフメタルでは一方のスピンバンドにエネルギギャップが存在するので、非常に大きな磁気効果を得ることができ、その結果、大きな信号出力を得ることができる。磁化固定層および磁化自由層の組合せの一例として、磁化固定層としてたとえば白金マンガン合金膜とコバルト鉄合金膜との積層構造が用いられ、磁化自由層としてニッケル鉄合金膜が用いられてもよい。

【0076】

磁気記憶素子MRの磁化自由層MF2上には、ビアプラグV2が形成されており、このビアプラグV2の上端部は、後述するビット線BLに接続されている。

【0077】

ストラップ配線SLの上面には、絶縁膜IF1が形成されている。絶縁膜IF1は、窒化ケイ素(SiN)膜から構成されている。絶縁膜IF1は、ストラップ配線SLの上面を覆うと共に、磁気記憶素子MRの側面およびビアプラグV2の側面の一部を覆うように形成されている。

【0078】

絶縁膜IF1は、上記のように、窒化ケイ素(SiN)膜から形成されており、拡散防止膜NF3と同一の絶縁膜から構成されている。その一方で、ディジット線DLよりも下層に位置する拡散防止膜NF2,NF1は、炭化窒化ケイ素膜(SiCN膜)又は炭化珪素膜(SiC膜)から構成されている。

【0079】

窒化ケイ素(SiN)膜は、炭化窒化ケイ素(SiCN)膜よりも低温で形成することができるため、ディジット線DLよりも上方に位置する拡散防止膜NF3や絶縁膜IF1等を低温で形成することで、ディジット線DLにヒロック(突起)が発生すること抑制することができる。絶縁膜IF1上には、層間絶縁膜IDF5が形成されている。層間絶縁膜IDF5は、たとえば、酸化シリコン膜から形成されている。

【0080】

図6に示すように、層間絶縁膜IDF5には、ビット線BLの延在方向に溝部BLGが形成されており、この溝部BLG内にビット線BLが形成されている。なお、ビアプラグV2の上端部は、この溝部BLG内に入り込むように突出している。

【0081】

ビット線BLは、バリアメタルBB3と、このバリアメタルBB3上に形成されたバリアメタルBB4と、クラッド層BC2と、ビット線本体部BLBとを含む。バリアメタルBB3は、溝部BLGの底面および側面を覆うように形成されており、バリアメタルBB3は、バリアメタルDB1等と同様の金属材料によって構成されている。たとえば、バリアメタルBB3は、タンタル(Ta),窒化タンタル(TaN)などの金属材料から構成されている。それ以外でもタンタル(Ta),チタン(Ti),ルテニウム(Ru),マンガン(Mn),マグネシウム(Mg),タングステン(W)の少なくとも1つの元素を含む金属材料から形成されてもよい。

【0082】

クラッド層BC2は、バリアメタルBB3の内側面上に形成されている。クラッド層BC2は、クラッド層DCLと同様の金属材料によって構成されている。たとえば、クラッド層BC2は、NiFe等から構成されている。なお、図5に示す断面では、クラッド層BC2は、紙面の奥側と手前側とに位置しており、この図5には図示されていない。

【0083】

図6において、バリアメタルBB4は、クラッド層BC2の側面上およびバリアメタルBB3の底面上に形成されており、バリアメタルBB4は、バリアメタルDB2と同一の金属材料によって構成されている。たとえば、バリアメタルBB4は、タンタル(Ta)や窒化タンタル(TaN)から構成されている。それ以外でもタンタル(Ta),チタン(Ti),ルテニウム(Ru),マンガン(Mn),マグネシウム(Mg),タングステン(W)の少なくとも1つの元素を含む金属材料から形成されてもよい。

【0084】

そして、ビット線本体部BLBは、バリアメタルBB4上に形成されており、溝部BLG内に充填されている。ビット線本体部BLBは、銅(銅を主体とする金属を含む)から構成されている。

【0085】

層間絶縁膜IDF5の上面上には、拡散防止膜NF4が形成されており、この拡散防止膜NF4は、ビット線本体部BLBの上面、バリアメタルBB4、クラッド層BC2、およびバリアメタルBB3の上面に接触するように形成されている。拡散防止膜NF4も、拡散防止膜NF3および絶縁膜IF1と同様に、窒化ケイ素(SiN)膜から構成されている。

【0086】

拡散防止膜NF4は、厚く形成された厚肉部と、厚肉部間に位置し、厚肉部よりも薄く形成された薄肉部とを含む。拡散防止膜NF4の厚肉部は、ビット線BLの上面に位置しており、拡散防止膜NF4の薄肉部は、ビット線BLの上面の間に位置する層間絶縁膜IDF5の上面に形成されている。拡散防止膜NF4の厚肉部上に、バリアメタルBB1と、クラッド層BC1と、バリアメタルBB2とが順次積層されて構成された積層金属膜(被覆金属膜)が形成されている。

【0087】

バリアメタルBB1およびバリアメタルBB2は、バリアメタルBB3およびバリアメタルBB4などと同一の金属材料によって形成されている。たとえば、タンタル(Ta)や窒化タンタル(TaN)から構成されている。それ以外でもタンタル(Ta),チタン(Ti),ルテニウム(Ru),マンガン(Mn),マグネシウム(Mg),タングステン(W)の少なくとも1つの元素を含む金属材料から形成されてもよい。クラッド層BC1もクラッド層BC2やクラッド層DCLなどと同一の金属材料から構成されている。

【0088】

このように、MRAM100の配線層LL4は、層間絶縁膜IDF4からバリアメタルBB2の間に位置する複数のレイヤから構成されており、配線層LL4内には、ビアプラグV1、ストラップ配線SL、磁気記憶素子MR、およびビット線BLなどが構成されている。

【0089】

図7において、周辺回路200の配線層LL4は、層間絶縁膜IDF3の上面に位置し、周辺配線P2の上面と接触する拡散防止膜NF3と、この拡散防止膜NF3上に形成された層間絶縁膜IDF4の薄肉部TPと、薄肉部TP上に形成された層間絶縁膜IDF5と、この層間絶縁膜IDF5の上面に形成された拡散防止膜NF4とを含む。配線層LL4は、拡散防止膜NF3、層間絶縁膜IDF4および層間絶縁膜IDF5を貫通するように形成された周辺配線P3を含む。

【0090】

周辺配線P3は、周辺配線P2の上端部に接続されており、周辺配線P3は、拡散防止膜NF3、層間絶縁膜IDF4および層間絶縁膜IDF5に形成されたコンタクトホールCH5および溝部PG3内に形成されている。

【0091】

周辺配線P3はコンタクトホールCH5および溝部PG3の内側面および底面に形成されたバリアメタルPLM4と、このバリアメタルPLM4の側面に形成されたクラッド層PLC2と、バリアメタルPLM4の底面およびクラッド層PLC2の側面上に形成されたバリアメタルPLM5と、配線本体部PLB3とを含む。

【0092】

バリアメタルPLM4は、図6に示すバリアメタルBB3と同一の金属材料によって形成されており、クラッド層PLC2は、図6に示すクラッド層BC2と同一の金属材料によって構成されている。さらに、バリアメタルPLM5は、バリアメタルBB4と同一の金属材料によって形成されている。

【0093】

さらに、配線本体部PLB3は図6に示すビット線本体部BLBと同一の金属材料によって形成されており、具体的には、銅(銅を主体とする金属材料)によって形成されている。拡散防止膜NF4は、窒化ケイ素(SiN)膜から形成されている。

【0094】

上記のように構成された配線層LL4の上面上には、上部絶縁層TILが積層されている。図5〜図7に示すように、上部絶縁層TILは、拡散防止膜NF5上に形成された

上層絶縁膜TI1と、上層絶縁膜TI1上に形成され上層絶縁膜TI2と、上層絶縁膜TI2の上面上に形成された上層絶縁膜TI3とを含む。

【0095】

上層絶縁膜TI1は、窒化ケイ素(SiN)膜から形成されており、上層絶縁膜TI2および上層絶縁膜TI3は、シリコン酸化膜から形成されている。図7において、周辺回路200には、上層絶縁膜TI1,TI2および上層絶縁膜TI3を貫通する外部コンタクトCTが形成されている。

【0096】

上記のように構成されたMRAM100の書き込みおよび読み出し動作について説明する。

【0097】

図5において、MRAM100の磁気記憶素子MRに書き込まれた情報を書き換えるときには、ビット線BLおよびディジット線DLに電流が流される。そして、ビット線BL内を流れる電流によって磁場が発生する。同様にディジット線DLに電流が流れることで、磁場が発生する。各磁場の合成磁場によって、磁気記憶素子MRの磁化自由層の磁化方向が変更される。これにより、磁気記憶素子MR内の情報の書き換えが完了する。

【0098】

この際、図6に示すように、ビット線BLのビット線本体部BLBの側面にはクラッド層BC2が形成され、ビット線BLの上方には、クラッド層BC1が形成されている。

【0099】

このように、ビット線本体部BLBの周囲に形成されたクラッド層は、ビット線本体部BLBの上面および側面を覆うよう配置される一方で、磁気記憶素子MRに向けて開口するように配置されている。

【0100】

各クラッド層は、高透磁率材料から形成されているため、ビット線BL内に電流が流れることで生じる磁束は、クラッド層内を優先的に流れる。この結果、磁束が、各クラッド層より外側に発散することが抑制され、磁気記憶素子MRに磁束が集中する。

【0101】

同様に、図5に示すように、ディジット線DLの配線本体部DLBの側面および底面は、クラッド層DCLによって覆われている。クラッド層DCLは、ディジット線DLの上方に位置する磁気記憶素子MRに向けて開口している。このため、ディジット線DL内を電流が流れることを生じる磁束は、磁気記憶素子MRに集中するように放射される。

【0102】

この結果、ビット線BLおよびディジット線DL内を電流が流れることで生じる合成磁界が強められ、ディジット線DLおよびビット線BLに供給される電流量を少なく抑えたとしても、磁気記憶素子MRの磁化自由層の磁化方向を変更することができる。この結果、MRAM100の消費電力を小さく抑えることができる。

【0103】

磁気記憶素子MRに書き込まれた情報を読み出すときには、図4に示すMOSトランジスタMTのゲート電極GEに所定の電圧が印加され、MOSトランジスタMTがON状態となる。

【0104】

そして、ビット線BLおよび不純物拡散層IR2に所定電圧が印加される。これにより、ビット線BL、磁気記憶素子MR、ストラップ配線SL、ビアプラグV1、読出用配線RL(配線L1〜L3およびプラグPL1)、不純物拡散層IR1および不純物拡散層IR2を通るように電流が流れる。磁気記憶素子MR内の磁化自由層の磁化方向によって、磁気記憶素子MRの抵抗値が変化するため、不純物拡散層IR2およびビット線BL間を流れる電流量から磁気記憶素子MRの抵抗値を検出することで、選択された磁気記憶素子MR内に書き込まれた情報を読み出すことができる。

【0105】

上記のように構成されたMRAM100および周辺回路200の製造方法について、図8から図92を用いて説明する。

【0106】

なお、図8から図20を用いて、MRAM100の配線層LL1の製造工程について説明し、その後、図21から図92を用いて、MRAM100および周辺回路200の配線層LL1〜上部絶縁層TILの製造工程について説明する。

【0107】

図8は、MRAM100の配線層LL1製造工程の第1製造工程を示す断面図である。この図8に示すように、主表面を有する半導体基板SSを準備する。その後、半導体基板SSの主表面上に素子分離領域STIを形成し、主表面上に活性領域を形成する。素子分離領域STIを形成した後、活性領域にイオン注入法などにより、不純物を活性領域内に導入し、図示されないウエル領域やチャネル領域を形成する。ウエル領域やチャネル領域を形成した後、半導体基板SSの主表面に、たとえば、熱酸化処理等を施して、シリコン酸化膜を主表面上に形成する。

【0108】

次に、図9において、半導体基板SSの主表面上に形成されたシリコン酸化膜上に、ポリシリコン膜をCVD(Chemical Vapor Deposition)法などで堆積し、このポリシリコン膜をパターニングする。これにより、半導体基板SSの主表面上にゲート絶縁膜GIが残留すると共に、このゲート絶縁膜GI上にゲート電極GEが形成される。

【0109】

次に、図10において、ゲート電極GEをマスクとして、半導体基板SSの主表面に所定の導電型の不純物を活性領域に導入する。その後、ゲート電極GEを覆うように、酸化シリコン膜および窒化シリコン膜を、CVD法により順次堆積する。そして、形成された酸化シリコン膜および窒化シリコン膜上に異方性エッチングを施すことで、ゲート電極GEの側面上にサイドウォールSWを形成する。

【0110】

サイドウォールSWを形成した後、ゲート電極GEおよびサイドウォールSWをマスクとして、不純物を活性領域に導入する。この2回の不純物の導入により、不純物拡散層IR1および不純物拡散層IR2が形成される。なお、不純物を導入した後には、不純物を拡散させるための熱処理が半導体基板SSに加えられる。

【0111】

次に、図11に示すように、各不純物領域を形成した後、ゲート電極GEの上面および不純物拡散層IR1および不純物拡散層IR2に、コバルトシリサイド膜を形成する。このようにして、半導体基板SSの主表面上にMOSトランジスタMTが形成される。

【0112】

次に図12に示すように、MOSトランジスタMTを形成した後に、MOSトランジスタMTを覆うようにコンタクト層間絶縁膜CIFを形成する。

【0113】

コンタクト層間絶縁膜CIFは、オゾンとTEOSとを原料に使用した熱CVD法により形成されるオゾンTEOS膜と、TEOSを原料に使用したプラズマCVD法により形成されるプラズマTEOS膜との積層膜から形成されている。

【0114】

コンタクト層間絶縁膜CIFに、写真製版処理およびエッチングを施して、コンタクトホールCH1をコンタクト層間絶縁膜CIFに形成する。コンタクトホールCH1を形成した後、スパッタリングなどでコンタクトホールCH1の内周面およびコンタクトホールCH1から露出するコバルトシリサイド膜上にバリアメタルを形成する。なお、バリアメタルとしては、チタン/窒化チタン膜等が採用される。バリアメタルを形成した後、タングステンなどを充填する。タングステン等の金属材料を充填した後、CMP(Chemical Mechanical Polishing)法で、コンタクト層間絶縁膜CIF上に位置するタングステンなどの金属材料と、バリアメタルを除去する。

【0115】

これにより、コンタクト用バリアメタルPBM1およびプラグ本体部PB1を含むプラグPL1が形成される。

【0116】

プラグPL1を形成した後、コンタクト層間絶縁膜CIFの表面に、プラズマ処理を施す。具体的には、アンモニアガスまたは、アンモニアガスおよび窒素ガスをチャンバ内に供給し、このチャンバ内に半導体基板SSを搬入する。その後、チャンバ内を400℃程度として、チャンバ内のガスをプラズマ化する。プラズマ化したガスによって、コンタクト層間絶縁膜CIFの表面にプラズマ処理を施す。

【0117】

次に、図13に示すように、コンタクト層間絶縁膜CIFおよびプラグPL1の上面にエッチングストッパ膜ESFをCVD法などにより形成する。エッチングストッパ膜ESFは、炭化窒化ケイ素膜(SiCN膜)、又は炭化珪素膜(SiC膜)が採用される。なお、エッチングストッパ膜ESFの成膜温度は、たとえば、450℃程度とされている。

【0118】

コンタクト層間絶縁膜CIFの上面には、プラズマ処理が施されているため、エッチングストッパ膜ESFとコンタクト層間絶縁膜CIFとの密着性の向上が図られている。

【0119】

その後、エッチングストッパ膜ESFの上面にCVD法などにより層間絶縁膜IDF1を形成する。層間絶縁膜IDF1としては、酸化シリコン膜や酸化シリコン膜よりも低誘電率である低誘電率膜が採用される。たとえば、TEOS膜、酸化シリコン膜、あるいは、SiOF膜等が採用される。

【0120】

次に、図14に示すように、フォトリソグラフィ技術およびエッチング技術を用いて、層間絶縁膜IDF1およびエッチングストッパ膜ESFにパターニングを施し、溝部G1を形成する。

【0121】

次に、図15に示すように、溝部G1の内周面および溝部G1から露出するプラグPL1の上端部に、スパッタリングなどで、バリアメタルBM0を形成する。バリアメタルBM0は、たとえば、タンタル(Ta)、チタン(Ti)、ルテニウム(Ru)、タングステン(W)、マンガン(Mn)およびこれらの窒化物や窒化珪化物、または、これらの積層膜から構成され、言い換えれば、バリアメタルBM0は、タンタル、チタン、ルテニウム、マンガンのいずれかの金属材料からなる金属材料膜、この金属材料とSi、N、O、Cのいずれかの元素との化合物膜のいずれかの膜から形成される。このバリアメタルBM0上に、電解めっき法などで、銅などの導電膜CF0を堆積する。導電膜CF0は、溝部G1内に埋め込まれる。

【0122】

導電膜CF0は、たとえば、銅(Cu)または銅合金(銅(Cu)とアルミニウム(Al)、マグネシウム(Mg)、チタン(Ti)、マンガン(Mn)、鉄(Fe)、亜鉛(Zn)、ジルコニウム(Zr)、ニオブ(Nb)、モリブデン(Mo)、ルテニウム(Ru)、パラジウム(Pd)、銀(Ag)、金(Au)、In(インジウム)、ランタノイド系金属、アクチノイド系金属などの合金)から形成される。

【0123】

次に、図16に示すように、CMP法などで、層間絶縁膜IDF1上の導電膜CF0およびバリアメタルBM0を除去する。これにより、配線本体部LB1およびバリアメタルLBM1を含む配線L1が形成される。

【0124】

配線L1が形成された層間絶縁膜IDF1に、上記コンタクト層間絶縁膜CIFの上面に施したプラズマ処理と同様のプラズマ処理を施す。

【0125】

次に、図17に示すように、層間絶縁膜IDF1および配線L1の上面上に、拡散防止膜NF1をCVD法により形成する。拡散防止膜NF1は、炭化窒化ケイ素膜(SiCN膜)、又は炭化珪素膜(SiC膜)が採用される。層間絶縁膜IDF1の上面には、プラズマ処理が施されているため、配線L1および層間絶縁膜IDF2と、拡散防止膜NF1との密着性の向上が図られている。なお、拡散防止膜NF1の成膜温度は、たとえば、450℃程度とされている。拡散防止膜NF1の上面に、CVD法などにより、層間絶縁膜IDF2を形成する。層間絶縁膜IDF2は、たとえば、TEOS膜、酸化シリコン膜、あるいは、SiOC膜、HSQ膜、MSQ膜、又はSiOF膜から構成されている。

【0126】

次に、図18に示すように、フォトリソグラフィ技術およびエッチング技術を使用することにより、層間絶縁膜IDF2および拡散防止膜NF1にパターニングを施して、コンタクトホールCH2および溝部G2を形成する。なお、配線L1の上面の一部は、コンタクトホールCH2から露出する。

【0127】

次に、図19に示すように、コンタクトホールCH2および溝部G2の表面上に、バリアメタルBM1をスパッタリングで形成する。その後、導電膜CF1を電解めっき法などで形成し、導電膜CF1をコンタクトホールCH2および溝部G2内に充填する。

【0128】

なお、バリアメタルBM1は、図15に示すバリアメタルBM0で採用可能な金属材料のうち、適当な金属材料が採用される。導電膜CF1も、図15に示す導電膜CF0として採用可能な金属材料のうち、適当な金属材料が採用される。

【0129】

次に、図20に示すように、CMP法により層間絶縁膜IDF2上に位置する導電膜CF1およびバリアメタルBM1が除去される。この結果、コンタクトホールCH2および溝部G2の内表面に形成されたバリアメタルLBM2と、コンタクトホールCH2および溝部G2内に充填された配線本体部LB2とを含む配線L2が形成される。

【0130】

このように、配線L2を形成した後、層間絶縁膜IDF2に、層間絶縁膜IDF1およびコンタクト層間絶縁膜CIFに施したプラズマ処理と同様のプラズマ処理を施す。

【0131】

このようにして、MRAM100の配線層LL1が形成される。そして、図21は、配線L2が形成されたときにおけるMRAM100の一部を示す断面図であり、上記図5に示す断面に対応する断面図である。図22は、配線L2が形成されたときのMRAM100の断面図であり、上記図6に示す断面に対応する断面である。図23は、配線L2が形成されたときの周辺回路200の断面図であり、上記図7に示す断面に対応する断面図である。

【0132】

図24から図26は、各々図21から図23に示す製造工程の後の工程を示す断面図である。

【0133】

図24および図26に示すように、層間絶縁膜IDF2の上面上に、炭化窒化ケイ素膜(SiCN膜)又は炭化珪素膜(SiC膜)から形成された拡散防止膜NF2をCVD法などで形成する。なお、拡散防止膜NF2の成膜温度は、たとえば、450℃程度とされている。次に、図27から図29に示すように、層間絶縁膜IDF3をCVD法により形成する。その後、フォトリソグラフィ技術およびエッチング技術を使用することにより、層間絶縁膜IDF3に溝部DG、溝部G3、コンタクトホールCH3、コンタクトホールCH4および溝部PG2を形成する。

【0134】

なお、図27に示すように、層間絶縁膜IDF3のうち、MRAM100となる部分に溝部DG、コンタクトホールCH3および溝部G3が形成され、図29に示すように、周辺回路200となる部分にコンタクトホールCH4および溝部PG2が形成される。

【0135】

次に、図30から図32に示すように、バリアメタルBM2と、クラッド層CL1と、バリアメタルBM3を順次積層する。

【0136】

なお、バリアメタルBM2およびバリアメタルBM3としては、タンタル(Ta),チタン(Ti),ルテニウム(Ru),マンガン(Mn),マグネシウム(Mg),タングステン(W)の少なくとも1つを含む金属材料から形成される。具体的には、チタンや窒化チタンなどが採用される。

【0137】

クラッド層CL1は、高透磁率材料から形成されており、コバルト(Co),ニッケル(Ni),鉄(Fe)の少なくとも1つを含む金属材料が採用され、さらに詳細には、クラッド層CL1は、NiFe(鉄ニッケル)、NiFeMo、CoNbZr(コバルトニオブジルコニウム)、CoFeNb、CoFeSiB、CoNbRu、CoNbZrMoCr、CoZrCrMoなどの合金、もしくはアモルファス合金を用いることが好ましい。

【0138】

次に、図33から図35に示すように、スパッタリングや電解めっき法などで、金属材料を塗布する。この金属材料としては、銅(銅を主体として含む金属材料を含む)から形成されている。具体的には、銅(Cu)または銅合金(銅(Cu)とアルミニウム(Al)、マグネシウム(Mg)、チタン(Ti)、マンガン(Mn)、鉄(Fe)、亜鉛(Zn)、ジルコニウム(Zr)、ニオブ(Nb)、モリブデン(Mo)、ルテニウム(Ru)、パラジウム(Pd)、銀(Ag)、金(Au)、In(インジウム)、ランタノイド系金属、アクチノイド系金属などの合金)等が採用される。

【0139】

そして、CMP法などで、層間絶縁膜IDF3上に位置する上記金属材料およびバリアメタルBM2、クラッド層CL1およびバリアメタルBM3を除去する。これにより、ディジット線DL、配線L3およびプラグPL2が形成される。

【0140】

そして、ディジット線DL、配線L3およびプラグPL2が形成された層間絶縁膜IDF3にプラズマ処理を施す。

【0141】

まず、半導体基板SSをチャンバ内に搬入し、窒素を含有する分子と窒素を含有しない不活性分子とからなる混合ガスをチャンバ内に導入する。このとき、窒素を含有する分子の流量よりも窒素を含有しない不活性分子の流量が多い条件で、混合ガスを導入し、混合ガスをプラズマ化してプラズマ処理を実施する。

【0142】

そして、層間絶縁膜IDF3の上面上に、LT(Low Temperature)−SiN膜をCVD法により形成する。たとえば、成膜温度は、275℃以下とされる。成膜温度を低く抑えることで、ディジット線DL、配線L3および周辺配線P2にヒロックが形成されることを抑制することができる。さらに、層間絶縁膜IDF3にプラズマ処理が施されているので、拡散防止膜NF3と層間絶縁膜IDF3との密着性の向上が図られている。

【0143】

次に、図36から図38に示すように、拡散防止膜NF3の上面上に、TEOS酸化膜等をCVD法などで堆積し、層間絶縁膜IDF4を形成する。

【0144】

次に、図39から図41に示すように、フォトリソグラフィおよびエッチングを施すことで、層間絶縁膜IDF4および拡散防止膜NF3にビアホールVH1を形成する。これにより、配線L3の上面が露出する。

【0145】

次に、図42から図44に示すように、層間絶縁膜IDF4の上面に、たとえば、チタン/窒化チタン膜などを成膜して、バリアメタルVBMを形成する。なお、バリアメタルVBMとしては、チタン/窒化チタン膜以外でもタンタル(Ta),チタン(Ti),ルテニウム(Ru),マンガン(Mn),マグネシウム(Mg),タングステン(W)の少なくとも1つの元素を含む金属材料を用いてもよい。そして、図45から図47に示すように、バリアメタルVBM上に、タングステンや銅などの金属材料を成膜して、導電膜CF2を形成する。

【0146】

次に、図48から図50に示すように、バリアメタルVBMおよび導電膜CF23にCMPを施して、バリアメタルVBMおよび導電膜CF2を平坦化する。これにより、ビアプラグV1が形成される。

【0147】

次に、図51から図53に示すように、ビアプラグV1の上端部上に、スパッタリングなどで導電膜CF3を形成する。導電膜CF3は、たとえば、チタン(Ti)から形成されている。この導電膜CF3の上面に、導電膜CF4を形成する。導電膜CF4は、窒化チタン(TiN)から構成されている。このように、層間絶縁膜IDF4およびビアプラグV1上に、チタン膜と、チタン上に形成された窒化チタン(TiN)膜との積層構造等を形成する。なお、導電膜CF3および導電膜CF4のいずれも、窒化チタン(TiN)から形成してもよい。このように層間絶縁膜IDF4上に設けられたビア本体VBやバリアメタルVBMを全て除去してからチタンで構成された導電膜CF3を形成した場合、導電膜CF3および導電膜CF3に形成される導電膜CF4の膜質や均一性が良くなる。

【0148】

次に、図54から図56に示すように、まず、導電膜CF4の上面に、磁化固定層MF1、トンネル絶縁膜MIおよび磁化自由層MF2を順次積層する。これにより、導電膜CF4の上面に、積層体LMRが形成される。そして、積層体LMRの磁化自由層MF2の上面に導電膜CF5を形成する。導電膜CF5としては、たとえば、タンタル膜やルテニウム膜等が採用される。

【0149】

次に、図57から図59に示すように、導電膜CF5の上面に、シリコン酸化膜HDPをCVD法などで堆積する。そして、シリコン酸化膜HDPの上面にマスクパターンMP1を形成する。

【0150】

その後、図60から図62に示すように、シリコン酸化膜HDPおよび導電膜CF5にエッチングを施すことで、マスクパターンMP2,MP3が形成される。そして、マスクパターンMP2,MP3を用いて、積層体LMRにプラズマドライエッチングを施す。これにより、図63から図65に示すように、導電膜CF4の上面のうち、MRAM100が形成される領域に、磁気記憶素子MRが形成されると共に、磁気記憶素子MRの上面に、ビアプラグV2が形成される。なお、図65に示すように、周辺回路200となる部分においては、積層体LMRおよびマスクパターンMP3は完全に除去される。そして、アッシング処理を施すことで、ビアプラグV2の上面に残留するマスクパターンMP2を除去する。

【0151】