半導体装置および半導体装置の製造方法

【課題】実効誘電率が低く、かつ信頼性の高いバリア絶縁膜を有する半導体装置を提供することができる。

【解決手段】半導体装置100は、層間絶縁膜10と、層間絶縁膜10中に設けられた配線20と、層間絶縁膜10上および配線20上に設けられたSiN膜30と、を備え、FTIRによって測定したSiN膜30のSi−N結合のピーク位置が845cm−1以上860cm−1以下である。これにより、配線金属の拡散を防ぐためのバリア絶縁膜である窒化シリコン膜において、リーク電流を抑制することができる

【解決手段】半導体装置100は、層間絶縁膜10と、層間絶縁膜10中に設けられた配線20と、層間絶縁膜10上および配線20上に設けられたSiN膜30と、を備え、FTIRによって測定したSiN膜30のSi−N結合のピーク位置が845cm−1以上860cm−1以下である。これにより、配線金属の拡散を防ぐためのバリア絶縁膜である窒化シリコン膜において、リーク電流を抑制することができる

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置および半導体装置の製造方法に関する。

【背景技術】

【0002】

配線の微細化に伴い、実効誘電率の低下が望まれている。特に、配線金属の拡散を防止するためのバリア絶縁膜の誘電率は他に比べて相対的に高く、このためバリア絶縁膜の低誘電率化が求められている。バリア絶縁膜の低誘電率化は、例えばバリア絶縁膜を、有機成分の組成比が高いC−rich SiCN、C−rich SiC、C−rich SiCOによって構成することが検討されている。他にも、例えば特許文献1に記載されるように、バリア絶縁膜を薄膜化することが挙げられる。

【0003】

特許文献1に記載の技術は、積層構造を有するバリア絶縁膜において、その一部を膜密度が高い高密度膜によって構成するというものである。また、積層構造を有するバリア絶縁膜において、その一部を窒化シリコン膜によって構成するということも開示されている。これらにより、外部からの水分の浸透を防ぎつつ、バリア絶縁膜を薄膜化して実効誘電率の低下を図ることができると記載されている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2009−182000号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

特許文献1によれば、バリア絶縁膜は、透水性に対する防止能の高い窒化シリコン膜を有している。このため、バリア絶縁膜を厚くせずとも、水分の浸透を防止することができる。よって、外部からの水分の浸透を防ぎつつ、実効誘電率の低下を図ることができると記載されている。しかし、本発明者は、このバリア絶縁膜を構成する窒化シリコン膜において、リーク電流が大きいという問題点を見いだした。このため、実効誘電率が低く、かつ信頼性の高いバリア絶縁膜を有する半導体装置が求められている。

【課題を解決するための手段】

【0006】

本発明によれば、層間絶縁膜と、

前記層間絶縁膜中に設けられた配線と、

前記層間絶縁膜上および前記配線上に設けられたSiN膜と、

を備え、

FTIR(赤外分光法)によって測定した前記SiN膜のSi−N結合のピーク位置が845cm−1以上860cm−1以下である半導体装置が提供される。

【0007】

本発明者らは、バリア絶縁膜を構成する窒化シリコン膜が有するSi−H結合やダングリングボンドに起因して、窒化シリコン膜においてリーク電流が発生していることを見いだした。本発明によれば、FTIRによって測定したSiN膜のSi−H結合のピーク位置が845cm−1以上860cm−1以下であり、これはSi−H結合やダングリングボンドが低減されていることを示している。このように、本発明に係るSiN膜は、Si−H結合やダングリングボンドの数が少ないため、窒化シリコン膜におけるリーク電流を抑制することができる。従って、実効誘電率が低く、かつ信頼性の高いバリア絶縁膜を有する半導体装置を提供することができる。

【0008】

本発明によれば、第1の層間絶縁膜と、前記第1の層間絶縁膜中に設けられた配線と、前記第1の層間絶縁膜上および前記配線上に設けられたSiN膜と、を備え、XPS(X線光電子分光)によって測定した前記SiN膜の組成比N/Siが0.9以上4/3以下である半導体装置が提供される。

【0009】

本発明によれば、第1の層間絶縁膜と、前記第1の層間絶縁膜中に設けられた配線と、前記第1の層間絶縁膜上および前記配線上に設けられたSiN膜と、を備え、前記SiN膜中における、ダングリングボンドに起因したスピン密度が1E17spins/cm3以下である半導体装置が提供される。

【0010】

本発明によれば、層間絶縁膜中に配線を設ける工程と、前記層間絶縁膜上および前記配線上に、SiN膜を形成する工程と、前記SiN膜に対し、窒化増強処理を行う工程と、を備える半導体装置の製造方法が提供される。

【発明の効果】

【0011】

本発明によれば、実効誘電率が低く、かつ信頼性の高いバリア絶縁膜を有する半導体装置を提供することができる。

【図面の簡単な説明】

【0012】

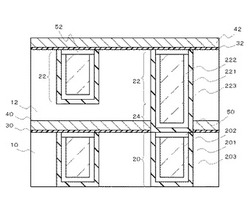

【図1】本実施形態に係る半導体装置を示す断面図である。

【図2】図1に示す半導体装置の製造方法を示す断面図である。

【図3】図1に示す半導体装置の製造方法を示す断面図である。

【図4】図1に示す半導体装置の製造方法を示す断面図である。

【図5】図1に示す半導体装置の製造方法を示す断面図である。

【図6】図1に示す半導体装置の製造方法を示す断面図である。

【図7】図1に示す半導体装置の製造方法を示す断面図である。

【図8】図1に示す半導体装置の製造方法を示す断面図である。

【図9】図1に示す多層配線構造を基板上に形成した場合を示す断面図である。

【図10】実施例1に係る半導体装置のXPSによる酸素1sのデプスプロファイルを示すグラフである。

【図11】実施例2に係る半導体装置のTOF−SIMSによるデプスプロファイルを示すグラフである。

【図12】実施例4に係るSiN膜の電流密度−電圧特性を示すグラフである。

【図13】実施例4に係るSiN膜のFTIRによって測定されたSi−N結合のピーク位置を示すグラフである。

【図14】実施例5に係るSiN膜のFTIRによって測定されたSi−N結合のピーク位置を示すグラフである。

【発明を実施するための形態】

【0013】

以下、本発明の実施の形態について、図面を用いて説明する。尚、すべての図面において、同様な構成要素には同様の符号を付し、適宜説明を省略する。

【0014】

図1は、本実施形態に係る半導体装置100を示す断面図である。また、図9は、図1に示す多層配線構造を基板上に形成した場合を示す断面図である。半導体装置100は、層間絶縁膜10と、配線20と、SiN膜30と、を備えている。FTIRによって測定したSiN膜30のSi−N結合のピーク位置が845cm−1以上860cm−1以下である。配線20は、層間絶縁膜10中に設けられている。SiN膜30は、層間絶縁膜10上および配線20上に設けられている。以下、半導体装置100の構成について、詳細に説明する。

【0015】

図9に示すように、半導体装置100は、トランジスタ70が設けられたシリコン基板80と、シリコン基板80上に設けられた多層配線層により構成される。多層配線層を構成する層間絶縁膜10は、シリコン基板80上に設けられている。層間絶縁膜10は、例えばSiCOH、Porous SiCOH、HSQ、Porous HSQ、MSQ、Porous MSQ、有機ポリマー、またはPorous 有機ポリマー等により構成されるLow−k膜からなる。層間絶縁膜10の膜厚は、例えば100〜180nmである。

【0016】

図1に示すように、配線20は、層間絶縁膜10の開口内に設けられたシード膜201、めっき膜202、およびバリアメタル膜203からなる。バリアメタル膜203は、例えば層間絶縁膜10の開口内に、TaN膜、Ta膜を順に積層して形成される。TaN膜の膜厚は、例えば2〜6nmである。また、Ta膜の膜厚は、例えば2〜6nmである。また、バリアメタル膜203は、Ta、Ti、またはCo等の単層膜や、これらを組み合わせた積層膜によって構成されていてもよい。

【0017】

シード膜201は、例えばCuと、添加金属材料であるAl、Mn、Ti、Sn、Mg、Si、またはZrからなる。この場合、シード膜201は、例えば添加金属材料を0.1〜1at%含有する。Mnを添加金属材料として用いた場合、Alを用いた場合と比較して、抵抗の上昇率が低い割に配線の信頼性の向上を図ることができる。さらに、シード膜201は、Pure Cuによって構成されていてもよい。めっき膜202は、シード膜201をシードとしためっき法によって形成され、例えばCuめっきを適用する。また、図1に示すように、配線20が添加金属材料を含む合金によって構成される場合、配線20は、SiN膜30と接する面において、添加金属材料が偏析してなる添加金属偏析層50をさらに有する。

【0018】

SiN膜30は、配線20を構成する金属材料の拡散を防止するバリア絶縁膜として働く。SiN膜30の膜厚は、1〜4nmであることが好ましい。SiN膜30の膜厚が5nmを超えると、後述する窒化増強処理時における窒化プラズマ等が膜中に十分に到達できず、膜中のSi−H結合やダングリングボンドが多く存在してしまい、良質なSiN膜ができない。

【0019】

FTIRによって測定したSiN膜30のSi−N結合のピーク位置が845cm−1以上860cm−1以下である。また、SiN膜30の膜組成は、0.9≦N/Si≦4/3である。これらは、SiN膜30中のSi−H結合やダングリングボンドが少ないことを示している。SiN膜の膜組成は、N/Si≧1であることが好ましい。この場合、SiN膜におけるリーク電流の十分な低減を実現することができる。

【0020】

図1に示すように、半導体装置100は、SiN膜30上に設けられたエッチングストッパ膜40と、エッチングストッパ膜40上に設けられた層間絶縁膜12と、をさらに備えている。エッチングストッパ膜40は、層間絶縁膜12をエッチングする条件において層間絶縁膜12よりもエッチングレートが遅く、このため層間絶縁膜12をエッチングする工程におけるエッチングストッパ膜として機能する。エッチングストッパ膜40は、例えば、SiCN(SiCNH)、SiCO(SiCOH)、SiCNO(SiCNOH)、SiC(SiCH)、SiB(SiBH)、SiBN(SiBHN)、SiBC(SiBCH)、SiBCN(SiBCNH)、C−rich SiCN(SiCNH)、C−rich SiCO(SiCOH)、C−rich SiCNO(SiCNOH)、C−rich SiC(SiCH)、C−rich SiBC(SiBCH)、およびC−rich SiBCN(SiBCHN)の少なくとも一つにより構成されるLow−k膜からなる。Low−k膜とは、SiO2によりも低い誘電率を有する膜をいう。エッチングストッパ膜40の比誘電率は、例えば4以下である。また、エッチングストッパ膜40の膜厚は、例えば20〜50nmである。

【0021】

層間絶縁膜12は、層間絶縁膜10と同様の材料によって構成することができる。層間絶縁膜12の膜厚は、例えば150〜200nmである。図1に示すように、層間絶縁膜12中には、配線22とビア24とが設けられている。配線22およびビア24は、配線20と同様に、シード膜221、めっき膜222、およびバリアメタル膜223によって構成されている。ビア24は、SiN膜30およびエッチングストッパ膜40を貫通して、配線20と接続するように設けられている。配線22は、ビア24を介して配線20と接続している。シード膜221、シード膜201と同様の材料によって構成することができる。また、めっき膜222についても、めっき膜202と同様の材料によって構成することができる。層間絶縁膜12上および配線22上には、SiN膜32と、エッチングストッパ膜42とが、この順に積層されて設けられている。エッチングストッパ膜42は、エッチングストッパ膜40と同様の材料によって構成することができる。また、配線22が添加金属材料を含む合金によって構成される場合、配線22は、SiN膜32と接する面において、添加金属材料が偏析してなる添加金属偏析層52を有する。

【0022】

次に、半導体装置100の製造方法について説明する。半導体装置100の製造方法は、層間絶縁膜10中に配線20を設ける工程と、層間絶縁膜10上および配線20上に、SiN膜30を設ける工程と、SiN膜30に対し、窒化増強処理を行う工程と、を備えている。以下、図1〜図9を用いて、半導体装置100の製造方法について詳細に説明する。

【0023】

図2〜図8は、図1に示す半導体装置100の製造方法を示す断面図である。まず、図2に示すように、トランジスタ70を含んだシリコン基板80上(図9参照)に、層間絶縁膜10を形成する。次に、層間絶縁膜10をエッチングして、配線20を形成するための開口を形成する。そして、この開口の底面および側面に、バリアメタル膜203を形成する。次いで、バリアメタル膜203上に、シード膜201を形成する。シード膜201の形成は、例えばCuに0.1〜1at%のAlを添加し、これをスパッタリングによってバリアメタル膜203上に付着させることで形成する。次いで、シード膜201をシードとしためっき法によって、めっき膜202を形成する。そして、配線20の表面をCMP(化学機械研磨)によって平坦化する。これにより、配線20が形成される。配線20は、例えばデュアルダマシン法によって形成される。

【0024】

次いで、層間絶縁膜10上および配線20上に、SiN膜30を形成する。SiN膜30は、SiH4ガスおよびNH3ガスを用いたプラズマCVDにより形成される。このプラズマCVDによるSiN膜30の形成は、例えば平行平板型プラズマCVDを用いて、以下の条件によって行われる。

温度:300〜370℃

ガス流量:SiH4=50〜700sccm、N2=0〜40,000ccm、NH3=50〜700sccm

RF周波数:13.56MHz

RFパワー:50〜250W

圧力:1〜5Torr

時間:1〜10s

【0025】

次いで、SiN膜30に対し、窒化増強処理を行う。窒化増強処理とは、図3に示すように、例えばN2、NH3の少なくとも一つを用いたプラズマCVDによる窒化プラズマ処理である。窒化プラズマ処理は、例えば平行平板型プラズマCVDを用いて、以下の条件によって行われる。

温度:300〜370℃

ガス流量:N2=0〜50,000ccm、NH3=300〜1,500sccm

RF周波数:13.56MHz

RFパワー:250〜1000W

圧力:1〜5Torr

時間:5〜30s

【0026】

図3に示す窒化プラズマ処理におけるプラズマCVDのパワーは、SiN膜30を形成する工程におけるプラズマCVDのパワーよりも高い。これにより、Si−H結合が少なく、かつダングリングボンドの少ないSiN膜30を形成することができる。なお、窒化増強処理は、窒素含有ガス雰囲気下でのEB処理またはUV処理により行ってもよい。

【0027】

FTIRによって測定した、窒化増強処理後のSiN膜におけるSi−N結合のピークは、窒化増強処理を実施しないものと比較して増加する。これは、Si−H結合やダングリングボンドが減少していることを示している。SiN膜のSi−N結合のピークは、窒化増強処理を行うことによって、845cm−1以上860cm−1以下となる。また、Si−H結合のピーク位置は、窒化増強処理を行っていないものと比較して減少していることも確認される。

なお、FTIR分析は、Si基板上に100nmのSiN膜を成膜して以下の条件において行った。SiN膜の成膜は、3nmの膜を33回繰り返し積層して行った。

測定器:Biorad社製 FTS40

測定条件:測定温度:室温

測定範囲 4000cm−1〜400cm−1のピークを測定した。

スキャン数 64回

バックグランドのSiの信号を削除した。

【0028】

また、XPSによって測定された窒化増強処理後のSiN膜30の膜組成は、0.9≦N/Si≦4/3である。ダングリングボンドがなく、リーク電流が抑制されたSiN膜30を実現するためには、N/Si≧1.0であることが好ましい。

XPSによる分析は、FTIRと同様にSi基板上にSiN膜を成膜して、以下の条件において行った。

測定器:Quantam2000

測定条件:測定方法:デプスプロファイル

スパッタ:Ar

スパッタレート:8.3nm/min

最表面以外の平均値を計算した。Si、N、Oを分析し、その中のN/Si比を計算した。また、後述する実施例に示すPCT前後のものは、酸素1sの周辺のデプスプロファイルを提示した。

【0029】

また、窒化増強処理によるダングリングボンドの減少は、ESR(電子スピン共鳴)によって測定されるスピン密度によっても確認することができる。SiN膜30の窒化増強処理後におけるダングリングボンド起因のスピン密度は、1E17spins/cm3以下である。これはESRによる検出限界以下の値である。

ESRによる分析は、FTIRと同様にSi基板上にSiN膜を成膜して、以下の条件において行った。

測定器:BRUKER社製 ESP350E

測定は、資料面を外部磁場方向に対し、垂直に設置した。

ESR分光法測定条件:測定温度 10K

中心磁場:3368G 付近

磁場掃引範囲:100G

G=2.004付近のSiN膜のダングリングボンド起因のシグナルから、スピン密度を計算した。

【0030】

窒化増強処理を行うことにより、SiN膜30は上面において窒素濃度が高くなり、下面へ向かうにつれて窒素濃度は低くなる。また、窒化増強処理においては、SiN膜30が緩衝材として機能する。これによって、層間絶縁膜10においては、上層に窒素が偏析する。これにより、層間絶縁膜10が過度に窒化されて誘電率が上昇してしまうことを抑制しつつ、TDDB(経時破壊)特性の向上を図ることができる。また、配線20においても、上層に窒素が偏析する。このため、配線20の表面が酸化することが抑制される。さらに、SiN膜30中の水素は、窒化プラズマ処理によって、配線20とバリアメタル膜203との界面付近に偏析する。これは、窒化プラズマ処理によってSiN膜30中のSi−H結合が切断され、水素がSiN膜30の下層に拡散したことに起因する。また、水素は窒素よりも軽元素で、かつ分子が小さいため、配線20とバリアメタル膜203の界面付近まで拡散するものと考えられる。

【0031】

次いで、図4に示すように、SiN膜30上にエッチングストッパ膜40を形成する。そして、エッチングストッパ膜40上に、層間絶縁膜12を形成する。さらに、層間絶縁膜12上に、ハードマスク60を形成する。ハードマスク60は、例えばSiO2によって構成される。図2〜図4に示す製造工程中において、配線20には、350〜400℃の熱履歴が加わる。このため、配線20が、添加金属材料を含む合金によって構成されている場合、添加金属材料が配線20の上面に偏析し、添加金属偏析層50が形成される。

【0032】

そして、図5に示すように、ハードマスク60をマスクとしたエッチングにより、層間絶縁膜12中に開口64を形成する。このとき、エッチングストッパ膜40においてエッチングはストップする。エッチングストッパ膜40は、層間絶縁膜12とのエッチング選択比の性能が10以上であればよい。例えばエッチングストッパ膜40がC−rich SiCN(O)であり、層間絶縁膜12がSiCOHである場合、エッチングストッパ膜40は、層間絶縁膜12とのエッチング選択比が20以上となる。また、エッチングストッパ膜40がC−rich SiCN(O)であり、層間絶縁膜12がPorous SiCOHである場合、層間絶縁膜12とのエッチング選択比は30以上となる。エッチングストッパ膜40下に位置するSiN膜30は、良好なバリア性能を有している。よって、エッチングストッパ膜40は、バリア性能を必要とせず、層間絶縁膜12とのエッチング選択比が得られればよいため、比誘電率が4以下のものを用いることができる。

【0033】

次いで、図6に示すように、ハードマスク60をマスクとしたエッチングにより、層間絶縁膜12中に開口62を形成する。このエッチングによって、開口64におけるエッチングストッパ膜40およびSiN膜30がエッチングされ、配線20の上面が露出する。次いで、図7に示すように、ハードマスク60を除去し、開口62内に、配線22を形成する。また、開口64内に、ビア24および配線22を形成する。配線22およびビア24を形成する工程については、配線20を形成する工程と同様であり、例えばデュアルダマシン法によって形成される。

【0034】

そして、図8に示すように、層間絶縁膜12上および配線22上に、SiN膜32およびエッチングストッパ膜42をこの順に積層する。図8に示す工程については、SiN膜30およびエッチングストッパ膜40を形成する工程と同様である。その後、図4〜図8の工程を繰り返すことによって、多層配線構造を有する半導体装置100を形成する。

【0035】

次に、本実施形態の効果を説明する。本発明者は、特許文献1に記載の技術において、バリア絶縁膜を構成するSiN膜が有するSi−H結合やダングリングボンドに起因して、SiN膜においてリーク電流が発生していることを見いだした。本実施形態によれば、FTIRによって測定したSiN膜30のSi−H結合のピーク位置が845cm−1以上860cm−1以下であり、これはSi−H結合やダングリングボンドが低減されていることを示している。このように、本実施形態に係るSiN膜30は、Si−H結合やダングリングボンドの数が少ないため、SiN膜におけるリーク電流を抑制することができる。

【0036】

また、本実施形態によれば、XPSによって測定したSiN膜30の組成比N/Siが0.9以上4/3以下である。さらに、SiN膜30中における、ダングリングボンドに起因したスピン密度が1E17spins/cm3以下である。これらについても、上記と同様に、SiN膜におけるSi−H結合やダングリングボンドが低減されていることを示している。このように、本実施形態に係るSiN膜30は、Si−H結合やダングリングボンドの数が少ないため、SiN膜におけるリーク電流を抑制することができる。

【0037】

SiN膜におけるリーク電流は、SiN膜が5nm以下の薄膜である場合に特に顕著となる。これは、SiN膜を成膜する工程においてプラズマがかかる時間が短時間となってしまうため、良好な膜質が得られないことに起因する。本実施形態によれば、SiN膜30の成膜後、窒化プラズマ処理を施している。このため、良好な膜質を有するSiN膜30を実現することができる。よって、SiN膜におけるリーク電流を抑制することができる。

【0038】

特許文献1に記載の技術では、層間絶縁膜間に設けられたSiCN膜、SiCO膜からなるバリア絶縁膜を有する。そして、SiCN膜の比誘電率は4.8であり、SiCO膜の比誘電率は4.5である。一方で、本実施形態によれば、SiN膜30に対して窒化増強処理を行うことによりSi−H結合やダングリングボンドが低減され、バリア性能の高い膜が実現される。このため、SiN膜30上に形成されるエッチングストッパ膜40は、バリア性能を必要としない。よって、エッチングストッパ膜40の比誘電率を4以下とすることができる。このように、層間絶縁膜間に設けられた絶縁膜の実効誘電率の低減を図ることができる。

【0039】

バリア絶縁膜が水分を吸湿することによって、半導体装置のEM(エレクトロマイグレーション)特性およびSIV(ストレス起因ボイディング)耐性は劣化する。これは、バリア絶縁膜を透過した水分によって、配線の表面が酸化されることや、バリア絶縁膜自体がストレスを受けることに起因する。また、配線の表面が酸化されると、配線の金属材料はイオン化されやすくなるため、金属イオンが配線間電界において移動しやすくなり、TDDB特性の劣化を引き起こしてしまう。一方で、これらの劣化を抑制するためにバリア絶縁膜を厚く形成すると、実効誘電率の上昇を引き起こす。本実施形態によれば、バリア絶縁膜として透水性の低いSiN膜30を用いている。よって、配線20や層間絶縁膜10の吸湿を防ぐことができる。これにより、配線20の表面が、水分によって酸化されてしまうことを抑制することができる。また、バリア絶縁膜であるSiN膜30自体のストレスを安定させることができる。よって、EM特性やTDDM特性の劣化を抑制しつつ、バリア絶縁膜の薄膜化を図ることができる。

【0040】

また、配線が添加金属材料を含む合金によって構成されている場合、添加金属材料が配線表面に偏析して添加金属偏析層が酸化されることにより、配線自体の酸化を抑制することができる。しかし、バリア絶縁膜が水分を吸湿することに伴い、配線中のグレイン界面に酸素が侵入する。侵入した酸素は、添加金属材料の移動を妨げるため、添加金属偏析層の形成が抑制されてしまう。本実施形態によれば、バリア絶縁膜としてSiN膜30を用いているため、バリア絶縁膜の吸湿を防止し、酸素の侵入を抑制することができる。よって、添加金属偏析層50の形成が安定したものとなる。よって、EM特性、SIV特性の劣化が抑制され、半導体装置の信頼性を向上させることが可能となる。

【0041】

また、SiN膜30に対して窒化増強処理を行うことにより、ダングリングボンドが低減された高密度な膜を実現することができる。このため、SiN膜の透水性を低減することができ、これにより配線20への水分の侵入を抑制できる。このため、配線中のグレイン界面に酸素が侵入することが抑制され、添加金属偏析層50の形成をさらに安定したものとすることができる。よって、EM特性、SIV特性の劣化が抑制され、半導体装置の信頼性を向上させることが可能となる。

【0042】

また、窒化増強処理を行う場合において、SiN膜30は緩衝材として機能する。このため、層間絶縁膜10においては、上層のみに窒素が偏析する。これにより、層間絶縁膜が過度に窒化されて誘電率が上昇することや、層間絶縁膜にダメージを与えることを抑制しつつ、TDDB特性の向上を図ることができる。また、配線20においても、上層のみに窒素が偏析する。このため、配線の表面が酸化することを抑制することができる。従って、半導体装置の信頼性を向上させることが可能となる。

【0043】

上記のように、本実施形態によれば、実効誘電率が低く、かつ信頼性の高いバリア絶縁膜を有する半導体装置を提供することができる。

【0044】

(実施例1)

図10は、実施例1に係る半導体装置のXPSによる酸素1sのデプスプロファイルを示すグラフである。実施例1としては、SiCN膜(図中左)と、窒化プラズマ処理を行ったSiN膜を3nm×33回積層してなる積層膜(図中右)のそれぞれについて、PCT(高圧高湿試験)を行い、PCT前後の膜質の変化をXSPによるデプスプロファイルによって比較した。SiCN膜は、100nmの膜厚を有するブランケット膜である。また、SiN膜を含む積層膜の膜厚は、100nmである。PCTの測定条件は、温度:125℃、湿度:100%、気圧:110kPa、時間:24時間である。

【0045】

図10では、各深さにおいてPCT前後のプロファイルが示されている。図10の左図中に示される各深さにおけるプロファイルのうち、円で囲った部分においては、ピークが見られる方がPCT後のプロファイルであり、ピークが見られない方がPCT前のプロファイルを示している。図10の左図に示すように、SiCN膜の場合は、PCT後、膜中におけるH−O結合のピークが見られるようになり、SiCN膜中の酸素が増加していることが分かる。一方で、図10の右図中においては、左図と同様に円で囲った部分におけるPCT前後のプロファイルはほぼ等しい。図10の右図に示すように、窒化プラズマ処理を行ったSiN膜を含む積層膜の場合は、PCT後、膜中においてH−O結合のピークは見られない。よって、積層膜中の酸素が増加していないことが分かる。このように、窒化プラズマ処理を行ったSiN膜を含む積層膜は、多湿の雰囲気においても膜質が安定しており、ストレスの変化が少ない膜であることが分かる。

【0046】

(実施例2)

図11は、実施例2に係る半導体装置のTOF−SIMSによるデプスプロファイルを示すグラフである。実施例2として、Cuアロイシード膜、Pure Cuめっき膜によって構成される配線上に、バリア絶縁膜およびエッチングストッパ膜を積層した構造に対し、PCTを行い、PCT前後の酸素に由来した信号強度(O-intensity)の変化をTOF−SIMSによるデプスプロファイルによって比較した。なお、PCTの測定条件は、実施例1と同様である。

【0047】

図11中の左図は、エッチングストッパ膜およびバリア絶縁膜として、Crich SiCN膜およびSiCN膜をそれぞれ使用した。Crich SiCN膜の膜厚は35nmであり、SiCN膜の膜厚は10nmである。左図中の上方に位置するグラフがPCT後のプロファイルであり、下方に位置するグラフがPCT前のプロファイルを示している。

図11中の右図は、エッチングストッパ膜およびバリア絶縁膜として、Crich SiCN膜およびSiN膜をそれぞれ使用した。Crich SiCN膜の膜厚は42nmであり、SiN膜の膜厚は3nmである。また、SiN膜は、成膜後に窒化プラズマ処理を施している。右図中の上方に位置するグラフがPCT後のプロファイルであり、下方に位置するグラフがPCT前のプロファイルを示している。

【0048】

図11の左図に示すように、バリア絶縁膜がSiCN膜の場合、バリア絶縁膜とCu配線との界面において、酸素に由来した信号強度が増加していることが分かる。一方で、図11の右図に示すように、バリア絶縁膜が窒化プラズマ処理を施したSiN膜の場合、バリア絶縁膜とCu配線との界面において、酸素に由来した信号強度は増加していない。このように、窒化プラズマ処理を行ったSiN膜をバリア絶縁膜とした場合、バリア絶縁膜の透水性が低減され、配線への酸素濃度の侵入を抑制できることが分かる。

【0049】

(実施例3)

実施例3として、実施例2に用いた二つの構造について、EM特性、TDDB特性、およびSIV特性を測定した。

EM特性については、バリア絶縁膜が窒化プラズマ処理を施したSiN膜の場合、バリア絶縁膜がSiCN膜の場合と比べて、MTTF(Mean Time To Failure)における寿命が5倍改善した。

TDDB特性については、バリア絶縁膜が窒化プラズマ処理を施したSiN膜の場合、バリア絶縁膜がSiCN膜の場合と比べて、MTTFにおける寿命が50倍改善した。

SiV特性については、66nm〜3μmの上層配線および下層配線間における不良を、175℃にホールドした条件において測定した。バリア絶縁膜がSiCN膜である場合、不良が発生した。一方で、バリア絶縁膜が窒化プラズマ処理を施したSiN膜である場合、1000時間経過後においても不良が発生しなかった。

【0050】

(実施例4)

実施例4としては、SiN膜を3nm×33回積層してなる積層膜に対し窒化プラズマ処理を行った場合と窒化プラズマ処理を行っていない場合とにおいて、SiN膜における電流密度−電圧特性、およびFTIRによるSi−N結合のピーク位置を測定した。

【0051】

図12は、実施例4に係るSiN膜の電流密度−電圧特性を示すグラフである。図12に示すように、窒化プラズマ処理を行っていない場合と比較して、窒化プラズマ処理を行った場合は、SiN膜におけるリーク電流を低減されている。窒化プラズマ処理を行った場合、窒化プラズマ処理を行っていない場合と比較して、3MV/cmでは、2桁のリーク電流が抑制された。

【0052】

図13は、実施例4に係るSiN膜のFTIRによって測定されたSi−N結合のピーク位置を示すグラフである。図13に示すように、窒化プラズマ処理を行っていない場合、Si−N結合のピーク位置は840cm−1である。これに対し、窒化プラズマ処理を行った場合、Si−N結合のピーク位置は856cm−1である。この結果から、窒化プラズマ処理を行うことにより、Si−H結合およびダングリングボンドが減少したことがわかる。理想のSi3N4では860cm−1と想定されるため、窒化プラズマ処理によって良質な膜となっていることが推定される。SiN膜をESR分析すると、窒化プラズマ処理を行っていない場合、ダングリングボンドに起因したスピン密度は5.8E17spins/cm3であった。これに対し、窒化プラズマ処理を行った場合、ダングリングボンドに起因したスピン密度は、検出限界である1E17spins/cm3以下であった。

【0053】

(実施例5)

図14は、実施例5に係るSiN膜のFTIRによって測定されたSi−N結合のピーク位置を示すグラフである。実施例5としては、窒化プラズマ処理を行ったSiN膜の膜厚が3〜5nmである場合のSi−N結合のピーク位置を測定した。図14に示すように、SiN膜の膜厚が増加するにつれ、Si−N結合のピークを示す波数は減少している。SiN膜の膜厚が3nmで850cm−1、3.5nmで846cm−1、4nmで845cm−1、5nmで838cm−1であった。これは、膜厚が増加するにつれ、SiN膜中のSi−H結合やダングリングボンドが増加していることを示している。デバイス的に許容されるのは4nm以下であり、この場合のSi−N結合のピーク位置は845cm−1と対応する。

【0054】

このように、本発明によれば、信頼性の高い半導体装置を提供することができることが分かる。

【0055】

以上、図面を参照して本発明の実施形態について述べたが、これらは本発明の例示であり、上記以外の様々な構成を採用することもできる。

【符号の説明】

【0056】

10、12 層間絶縁膜

20、22 配線

24 ビア

201、221 シード膜

202、222 めっき膜

203、223 バリアメタル膜

30、32 SiN膜

40、42 エッチングストッパ膜

50、52 添加金属偏析層

60 ハードマスク

62、64 開口

70 トランジスタ

80 シリコン基板

100 半導体装置

【技術分野】

【0001】

本発明は、半導体装置および半導体装置の製造方法に関する。

【背景技術】

【0002】

配線の微細化に伴い、実効誘電率の低下が望まれている。特に、配線金属の拡散を防止するためのバリア絶縁膜の誘電率は他に比べて相対的に高く、このためバリア絶縁膜の低誘電率化が求められている。バリア絶縁膜の低誘電率化は、例えばバリア絶縁膜を、有機成分の組成比が高いC−rich SiCN、C−rich SiC、C−rich SiCOによって構成することが検討されている。他にも、例えば特許文献1に記載されるように、バリア絶縁膜を薄膜化することが挙げられる。

【0003】

特許文献1に記載の技術は、積層構造を有するバリア絶縁膜において、その一部を膜密度が高い高密度膜によって構成するというものである。また、積層構造を有するバリア絶縁膜において、その一部を窒化シリコン膜によって構成するということも開示されている。これらにより、外部からの水分の浸透を防ぎつつ、バリア絶縁膜を薄膜化して実効誘電率の低下を図ることができると記載されている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2009−182000号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

特許文献1によれば、バリア絶縁膜は、透水性に対する防止能の高い窒化シリコン膜を有している。このため、バリア絶縁膜を厚くせずとも、水分の浸透を防止することができる。よって、外部からの水分の浸透を防ぎつつ、実効誘電率の低下を図ることができると記載されている。しかし、本発明者は、このバリア絶縁膜を構成する窒化シリコン膜において、リーク電流が大きいという問題点を見いだした。このため、実効誘電率が低く、かつ信頼性の高いバリア絶縁膜を有する半導体装置が求められている。

【課題を解決するための手段】

【0006】

本発明によれば、層間絶縁膜と、

前記層間絶縁膜中に設けられた配線と、

前記層間絶縁膜上および前記配線上に設けられたSiN膜と、

を備え、

FTIR(赤外分光法)によって測定した前記SiN膜のSi−N結合のピーク位置が845cm−1以上860cm−1以下である半導体装置が提供される。

【0007】

本発明者らは、バリア絶縁膜を構成する窒化シリコン膜が有するSi−H結合やダングリングボンドに起因して、窒化シリコン膜においてリーク電流が発生していることを見いだした。本発明によれば、FTIRによって測定したSiN膜のSi−H結合のピーク位置が845cm−1以上860cm−1以下であり、これはSi−H結合やダングリングボンドが低減されていることを示している。このように、本発明に係るSiN膜は、Si−H結合やダングリングボンドの数が少ないため、窒化シリコン膜におけるリーク電流を抑制することができる。従って、実効誘電率が低く、かつ信頼性の高いバリア絶縁膜を有する半導体装置を提供することができる。

【0008】

本発明によれば、第1の層間絶縁膜と、前記第1の層間絶縁膜中に設けられた配線と、前記第1の層間絶縁膜上および前記配線上に設けられたSiN膜と、を備え、XPS(X線光電子分光)によって測定した前記SiN膜の組成比N/Siが0.9以上4/3以下である半導体装置が提供される。

【0009】

本発明によれば、第1の層間絶縁膜と、前記第1の層間絶縁膜中に設けられた配線と、前記第1の層間絶縁膜上および前記配線上に設けられたSiN膜と、を備え、前記SiN膜中における、ダングリングボンドに起因したスピン密度が1E17spins/cm3以下である半導体装置が提供される。

【0010】

本発明によれば、層間絶縁膜中に配線を設ける工程と、前記層間絶縁膜上および前記配線上に、SiN膜を形成する工程と、前記SiN膜に対し、窒化増強処理を行う工程と、を備える半導体装置の製造方法が提供される。

【発明の効果】

【0011】

本発明によれば、実効誘電率が低く、かつ信頼性の高いバリア絶縁膜を有する半導体装置を提供することができる。

【図面の簡単な説明】

【0012】

【図1】本実施形態に係る半導体装置を示す断面図である。

【図2】図1に示す半導体装置の製造方法を示す断面図である。

【図3】図1に示す半導体装置の製造方法を示す断面図である。

【図4】図1に示す半導体装置の製造方法を示す断面図である。

【図5】図1に示す半導体装置の製造方法を示す断面図である。

【図6】図1に示す半導体装置の製造方法を示す断面図である。

【図7】図1に示す半導体装置の製造方法を示す断面図である。

【図8】図1に示す半導体装置の製造方法を示す断面図である。

【図9】図1に示す多層配線構造を基板上に形成した場合を示す断面図である。

【図10】実施例1に係る半導体装置のXPSによる酸素1sのデプスプロファイルを示すグラフである。

【図11】実施例2に係る半導体装置のTOF−SIMSによるデプスプロファイルを示すグラフである。

【図12】実施例4に係るSiN膜の電流密度−電圧特性を示すグラフである。

【図13】実施例4に係るSiN膜のFTIRによって測定されたSi−N結合のピーク位置を示すグラフである。

【図14】実施例5に係るSiN膜のFTIRによって測定されたSi−N結合のピーク位置を示すグラフである。

【発明を実施するための形態】

【0013】

以下、本発明の実施の形態について、図面を用いて説明する。尚、すべての図面において、同様な構成要素には同様の符号を付し、適宜説明を省略する。

【0014】

図1は、本実施形態に係る半導体装置100を示す断面図である。また、図9は、図1に示す多層配線構造を基板上に形成した場合を示す断面図である。半導体装置100は、層間絶縁膜10と、配線20と、SiN膜30と、を備えている。FTIRによって測定したSiN膜30のSi−N結合のピーク位置が845cm−1以上860cm−1以下である。配線20は、層間絶縁膜10中に設けられている。SiN膜30は、層間絶縁膜10上および配線20上に設けられている。以下、半導体装置100の構成について、詳細に説明する。

【0015】

図9に示すように、半導体装置100は、トランジスタ70が設けられたシリコン基板80と、シリコン基板80上に設けられた多層配線層により構成される。多層配線層を構成する層間絶縁膜10は、シリコン基板80上に設けられている。層間絶縁膜10は、例えばSiCOH、Porous SiCOH、HSQ、Porous HSQ、MSQ、Porous MSQ、有機ポリマー、またはPorous 有機ポリマー等により構成されるLow−k膜からなる。層間絶縁膜10の膜厚は、例えば100〜180nmである。

【0016】

図1に示すように、配線20は、層間絶縁膜10の開口内に設けられたシード膜201、めっき膜202、およびバリアメタル膜203からなる。バリアメタル膜203は、例えば層間絶縁膜10の開口内に、TaN膜、Ta膜を順に積層して形成される。TaN膜の膜厚は、例えば2〜6nmである。また、Ta膜の膜厚は、例えば2〜6nmである。また、バリアメタル膜203は、Ta、Ti、またはCo等の単層膜や、これらを組み合わせた積層膜によって構成されていてもよい。

【0017】

シード膜201は、例えばCuと、添加金属材料であるAl、Mn、Ti、Sn、Mg、Si、またはZrからなる。この場合、シード膜201は、例えば添加金属材料を0.1〜1at%含有する。Mnを添加金属材料として用いた場合、Alを用いた場合と比較して、抵抗の上昇率が低い割に配線の信頼性の向上を図ることができる。さらに、シード膜201は、Pure Cuによって構成されていてもよい。めっき膜202は、シード膜201をシードとしためっき法によって形成され、例えばCuめっきを適用する。また、図1に示すように、配線20が添加金属材料を含む合金によって構成される場合、配線20は、SiN膜30と接する面において、添加金属材料が偏析してなる添加金属偏析層50をさらに有する。

【0018】

SiN膜30は、配線20を構成する金属材料の拡散を防止するバリア絶縁膜として働く。SiN膜30の膜厚は、1〜4nmであることが好ましい。SiN膜30の膜厚が5nmを超えると、後述する窒化増強処理時における窒化プラズマ等が膜中に十分に到達できず、膜中のSi−H結合やダングリングボンドが多く存在してしまい、良質なSiN膜ができない。

【0019】

FTIRによって測定したSiN膜30のSi−N結合のピーク位置が845cm−1以上860cm−1以下である。また、SiN膜30の膜組成は、0.9≦N/Si≦4/3である。これらは、SiN膜30中のSi−H結合やダングリングボンドが少ないことを示している。SiN膜の膜組成は、N/Si≧1であることが好ましい。この場合、SiN膜におけるリーク電流の十分な低減を実現することができる。

【0020】

図1に示すように、半導体装置100は、SiN膜30上に設けられたエッチングストッパ膜40と、エッチングストッパ膜40上に設けられた層間絶縁膜12と、をさらに備えている。エッチングストッパ膜40は、層間絶縁膜12をエッチングする条件において層間絶縁膜12よりもエッチングレートが遅く、このため層間絶縁膜12をエッチングする工程におけるエッチングストッパ膜として機能する。エッチングストッパ膜40は、例えば、SiCN(SiCNH)、SiCO(SiCOH)、SiCNO(SiCNOH)、SiC(SiCH)、SiB(SiBH)、SiBN(SiBHN)、SiBC(SiBCH)、SiBCN(SiBCNH)、C−rich SiCN(SiCNH)、C−rich SiCO(SiCOH)、C−rich SiCNO(SiCNOH)、C−rich SiC(SiCH)、C−rich SiBC(SiBCH)、およびC−rich SiBCN(SiBCHN)の少なくとも一つにより構成されるLow−k膜からなる。Low−k膜とは、SiO2によりも低い誘電率を有する膜をいう。エッチングストッパ膜40の比誘電率は、例えば4以下である。また、エッチングストッパ膜40の膜厚は、例えば20〜50nmである。

【0021】

層間絶縁膜12は、層間絶縁膜10と同様の材料によって構成することができる。層間絶縁膜12の膜厚は、例えば150〜200nmである。図1に示すように、層間絶縁膜12中には、配線22とビア24とが設けられている。配線22およびビア24は、配線20と同様に、シード膜221、めっき膜222、およびバリアメタル膜223によって構成されている。ビア24は、SiN膜30およびエッチングストッパ膜40を貫通して、配線20と接続するように設けられている。配線22は、ビア24を介して配線20と接続している。シード膜221、シード膜201と同様の材料によって構成することができる。また、めっき膜222についても、めっき膜202と同様の材料によって構成することができる。層間絶縁膜12上および配線22上には、SiN膜32と、エッチングストッパ膜42とが、この順に積層されて設けられている。エッチングストッパ膜42は、エッチングストッパ膜40と同様の材料によって構成することができる。また、配線22が添加金属材料を含む合金によって構成される場合、配線22は、SiN膜32と接する面において、添加金属材料が偏析してなる添加金属偏析層52を有する。

【0022】

次に、半導体装置100の製造方法について説明する。半導体装置100の製造方法は、層間絶縁膜10中に配線20を設ける工程と、層間絶縁膜10上および配線20上に、SiN膜30を設ける工程と、SiN膜30に対し、窒化増強処理を行う工程と、を備えている。以下、図1〜図9を用いて、半導体装置100の製造方法について詳細に説明する。

【0023】

図2〜図8は、図1に示す半導体装置100の製造方法を示す断面図である。まず、図2に示すように、トランジスタ70を含んだシリコン基板80上(図9参照)に、層間絶縁膜10を形成する。次に、層間絶縁膜10をエッチングして、配線20を形成するための開口を形成する。そして、この開口の底面および側面に、バリアメタル膜203を形成する。次いで、バリアメタル膜203上に、シード膜201を形成する。シード膜201の形成は、例えばCuに0.1〜1at%のAlを添加し、これをスパッタリングによってバリアメタル膜203上に付着させることで形成する。次いで、シード膜201をシードとしためっき法によって、めっき膜202を形成する。そして、配線20の表面をCMP(化学機械研磨)によって平坦化する。これにより、配線20が形成される。配線20は、例えばデュアルダマシン法によって形成される。

【0024】

次いで、層間絶縁膜10上および配線20上に、SiN膜30を形成する。SiN膜30は、SiH4ガスおよびNH3ガスを用いたプラズマCVDにより形成される。このプラズマCVDによるSiN膜30の形成は、例えば平行平板型プラズマCVDを用いて、以下の条件によって行われる。

温度:300〜370℃

ガス流量:SiH4=50〜700sccm、N2=0〜40,000ccm、NH3=50〜700sccm

RF周波数:13.56MHz

RFパワー:50〜250W

圧力:1〜5Torr

時間:1〜10s

【0025】

次いで、SiN膜30に対し、窒化増強処理を行う。窒化増強処理とは、図3に示すように、例えばN2、NH3の少なくとも一つを用いたプラズマCVDによる窒化プラズマ処理である。窒化プラズマ処理は、例えば平行平板型プラズマCVDを用いて、以下の条件によって行われる。

温度:300〜370℃

ガス流量:N2=0〜50,000ccm、NH3=300〜1,500sccm

RF周波数:13.56MHz

RFパワー:250〜1000W

圧力:1〜5Torr

時間:5〜30s

【0026】

図3に示す窒化プラズマ処理におけるプラズマCVDのパワーは、SiN膜30を形成する工程におけるプラズマCVDのパワーよりも高い。これにより、Si−H結合が少なく、かつダングリングボンドの少ないSiN膜30を形成することができる。なお、窒化増強処理は、窒素含有ガス雰囲気下でのEB処理またはUV処理により行ってもよい。

【0027】

FTIRによって測定した、窒化増強処理後のSiN膜におけるSi−N結合のピークは、窒化増強処理を実施しないものと比較して増加する。これは、Si−H結合やダングリングボンドが減少していることを示している。SiN膜のSi−N結合のピークは、窒化増強処理を行うことによって、845cm−1以上860cm−1以下となる。また、Si−H結合のピーク位置は、窒化増強処理を行っていないものと比較して減少していることも確認される。

なお、FTIR分析は、Si基板上に100nmのSiN膜を成膜して以下の条件において行った。SiN膜の成膜は、3nmの膜を33回繰り返し積層して行った。

測定器:Biorad社製 FTS40

測定条件:測定温度:室温

測定範囲 4000cm−1〜400cm−1のピークを測定した。

スキャン数 64回

バックグランドのSiの信号を削除した。

【0028】

また、XPSによって測定された窒化増強処理後のSiN膜30の膜組成は、0.9≦N/Si≦4/3である。ダングリングボンドがなく、リーク電流が抑制されたSiN膜30を実現するためには、N/Si≧1.0であることが好ましい。

XPSによる分析は、FTIRと同様にSi基板上にSiN膜を成膜して、以下の条件において行った。

測定器:Quantam2000

測定条件:測定方法:デプスプロファイル

スパッタ:Ar

スパッタレート:8.3nm/min

最表面以外の平均値を計算した。Si、N、Oを分析し、その中のN/Si比を計算した。また、後述する実施例に示すPCT前後のものは、酸素1sの周辺のデプスプロファイルを提示した。

【0029】

また、窒化増強処理によるダングリングボンドの減少は、ESR(電子スピン共鳴)によって測定されるスピン密度によっても確認することができる。SiN膜30の窒化増強処理後におけるダングリングボンド起因のスピン密度は、1E17spins/cm3以下である。これはESRによる検出限界以下の値である。

ESRによる分析は、FTIRと同様にSi基板上にSiN膜を成膜して、以下の条件において行った。

測定器:BRUKER社製 ESP350E

測定は、資料面を外部磁場方向に対し、垂直に設置した。

ESR分光法測定条件:測定温度 10K

中心磁場:3368G 付近

磁場掃引範囲:100G

G=2.004付近のSiN膜のダングリングボンド起因のシグナルから、スピン密度を計算した。

【0030】

窒化増強処理を行うことにより、SiN膜30は上面において窒素濃度が高くなり、下面へ向かうにつれて窒素濃度は低くなる。また、窒化増強処理においては、SiN膜30が緩衝材として機能する。これによって、層間絶縁膜10においては、上層に窒素が偏析する。これにより、層間絶縁膜10が過度に窒化されて誘電率が上昇してしまうことを抑制しつつ、TDDB(経時破壊)特性の向上を図ることができる。また、配線20においても、上層に窒素が偏析する。このため、配線20の表面が酸化することが抑制される。さらに、SiN膜30中の水素は、窒化プラズマ処理によって、配線20とバリアメタル膜203との界面付近に偏析する。これは、窒化プラズマ処理によってSiN膜30中のSi−H結合が切断され、水素がSiN膜30の下層に拡散したことに起因する。また、水素は窒素よりも軽元素で、かつ分子が小さいため、配線20とバリアメタル膜203の界面付近まで拡散するものと考えられる。

【0031】

次いで、図4に示すように、SiN膜30上にエッチングストッパ膜40を形成する。そして、エッチングストッパ膜40上に、層間絶縁膜12を形成する。さらに、層間絶縁膜12上に、ハードマスク60を形成する。ハードマスク60は、例えばSiO2によって構成される。図2〜図4に示す製造工程中において、配線20には、350〜400℃の熱履歴が加わる。このため、配線20が、添加金属材料を含む合金によって構成されている場合、添加金属材料が配線20の上面に偏析し、添加金属偏析層50が形成される。

【0032】

そして、図5に示すように、ハードマスク60をマスクとしたエッチングにより、層間絶縁膜12中に開口64を形成する。このとき、エッチングストッパ膜40においてエッチングはストップする。エッチングストッパ膜40は、層間絶縁膜12とのエッチング選択比の性能が10以上であればよい。例えばエッチングストッパ膜40がC−rich SiCN(O)であり、層間絶縁膜12がSiCOHである場合、エッチングストッパ膜40は、層間絶縁膜12とのエッチング選択比が20以上となる。また、エッチングストッパ膜40がC−rich SiCN(O)であり、層間絶縁膜12がPorous SiCOHである場合、層間絶縁膜12とのエッチング選択比は30以上となる。エッチングストッパ膜40下に位置するSiN膜30は、良好なバリア性能を有している。よって、エッチングストッパ膜40は、バリア性能を必要とせず、層間絶縁膜12とのエッチング選択比が得られればよいため、比誘電率が4以下のものを用いることができる。

【0033】

次いで、図6に示すように、ハードマスク60をマスクとしたエッチングにより、層間絶縁膜12中に開口62を形成する。このエッチングによって、開口64におけるエッチングストッパ膜40およびSiN膜30がエッチングされ、配線20の上面が露出する。次いで、図7に示すように、ハードマスク60を除去し、開口62内に、配線22を形成する。また、開口64内に、ビア24および配線22を形成する。配線22およびビア24を形成する工程については、配線20を形成する工程と同様であり、例えばデュアルダマシン法によって形成される。

【0034】

そして、図8に示すように、層間絶縁膜12上および配線22上に、SiN膜32およびエッチングストッパ膜42をこの順に積層する。図8に示す工程については、SiN膜30およびエッチングストッパ膜40を形成する工程と同様である。その後、図4〜図8の工程を繰り返すことによって、多層配線構造を有する半導体装置100を形成する。

【0035】

次に、本実施形態の効果を説明する。本発明者は、特許文献1に記載の技術において、バリア絶縁膜を構成するSiN膜が有するSi−H結合やダングリングボンドに起因して、SiN膜においてリーク電流が発生していることを見いだした。本実施形態によれば、FTIRによって測定したSiN膜30のSi−H結合のピーク位置が845cm−1以上860cm−1以下であり、これはSi−H結合やダングリングボンドが低減されていることを示している。このように、本実施形態に係るSiN膜30は、Si−H結合やダングリングボンドの数が少ないため、SiN膜におけるリーク電流を抑制することができる。

【0036】

また、本実施形態によれば、XPSによって測定したSiN膜30の組成比N/Siが0.9以上4/3以下である。さらに、SiN膜30中における、ダングリングボンドに起因したスピン密度が1E17spins/cm3以下である。これらについても、上記と同様に、SiN膜におけるSi−H結合やダングリングボンドが低減されていることを示している。このように、本実施形態に係るSiN膜30は、Si−H結合やダングリングボンドの数が少ないため、SiN膜におけるリーク電流を抑制することができる。

【0037】

SiN膜におけるリーク電流は、SiN膜が5nm以下の薄膜である場合に特に顕著となる。これは、SiN膜を成膜する工程においてプラズマがかかる時間が短時間となってしまうため、良好な膜質が得られないことに起因する。本実施形態によれば、SiN膜30の成膜後、窒化プラズマ処理を施している。このため、良好な膜質を有するSiN膜30を実現することができる。よって、SiN膜におけるリーク電流を抑制することができる。

【0038】

特許文献1に記載の技術では、層間絶縁膜間に設けられたSiCN膜、SiCO膜からなるバリア絶縁膜を有する。そして、SiCN膜の比誘電率は4.8であり、SiCO膜の比誘電率は4.5である。一方で、本実施形態によれば、SiN膜30に対して窒化増強処理を行うことによりSi−H結合やダングリングボンドが低減され、バリア性能の高い膜が実現される。このため、SiN膜30上に形成されるエッチングストッパ膜40は、バリア性能を必要としない。よって、エッチングストッパ膜40の比誘電率を4以下とすることができる。このように、層間絶縁膜間に設けられた絶縁膜の実効誘電率の低減を図ることができる。

【0039】

バリア絶縁膜が水分を吸湿することによって、半導体装置のEM(エレクトロマイグレーション)特性およびSIV(ストレス起因ボイディング)耐性は劣化する。これは、バリア絶縁膜を透過した水分によって、配線の表面が酸化されることや、バリア絶縁膜自体がストレスを受けることに起因する。また、配線の表面が酸化されると、配線の金属材料はイオン化されやすくなるため、金属イオンが配線間電界において移動しやすくなり、TDDB特性の劣化を引き起こしてしまう。一方で、これらの劣化を抑制するためにバリア絶縁膜を厚く形成すると、実効誘電率の上昇を引き起こす。本実施形態によれば、バリア絶縁膜として透水性の低いSiN膜30を用いている。よって、配線20や層間絶縁膜10の吸湿を防ぐことができる。これにより、配線20の表面が、水分によって酸化されてしまうことを抑制することができる。また、バリア絶縁膜であるSiN膜30自体のストレスを安定させることができる。よって、EM特性やTDDM特性の劣化を抑制しつつ、バリア絶縁膜の薄膜化を図ることができる。

【0040】

また、配線が添加金属材料を含む合金によって構成されている場合、添加金属材料が配線表面に偏析して添加金属偏析層が酸化されることにより、配線自体の酸化を抑制することができる。しかし、バリア絶縁膜が水分を吸湿することに伴い、配線中のグレイン界面に酸素が侵入する。侵入した酸素は、添加金属材料の移動を妨げるため、添加金属偏析層の形成が抑制されてしまう。本実施形態によれば、バリア絶縁膜としてSiN膜30を用いているため、バリア絶縁膜の吸湿を防止し、酸素の侵入を抑制することができる。よって、添加金属偏析層50の形成が安定したものとなる。よって、EM特性、SIV特性の劣化が抑制され、半導体装置の信頼性を向上させることが可能となる。

【0041】

また、SiN膜30に対して窒化増強処理を行うことにより、ダングリングボンドが低減された高密度な膜を実現することができる。このため、SiN膜の透水性を低減することができ、これにより配線20への水分の侵入を抑制できる。このため、配線中のグレイン界面に酸素が侵入することが抑制され、添加金属偏析層50の形成をさらに安定したものとすることができる。よって、EM特性、SIV特性の劣化が抑制され、半導体装置の信頼性を向上させることが可能となる。

【0042】

また、窒化増強処理を行う場合において、SiN膜30は緩衝材として機能する。このため、層間絶縁膜10においては、上層のみに窒素が偏析する。これにより、層間絶縁膜が過度に窒化されて誘電率が上昇することや、層間絶縁膜にダメージを与えることを抑制しつつ、TDDB特性の向上を図ることができる。また、配線20においても、上層のみに窒素が偏析する。このため、配線の表面が酸化することを抑制することができる。従って、半導体装置の信頼性を向上させることが可能となる。

【0043】

上記のように、本実施形態によれば、実効誘電率が低く、かつ信頼性の高いバリア絶縁膜を有する半導体装置を提供することができる。

【0044】

(実施例1)

図10は、実施例1に係る半導体装置のXPSによる酸素1sのデプスプロファイルを示すグラフである。実施例1としては、SiCN膜(図中左)と、窒化プラズマ処理を行ったSiN膜を3nm×33回積層してなる積層膜(図中右)のそれぞれについて、PCT(高圧高湿試験)を行い、PCT前後の膜質の変化をXSPによるデプスプロファイルによって比較した。SiCN膜は、100nmの膜厚を有するブランケット膜である。また、SiN膜を含む積層膜の膜厚は、100nmである。PCTの測定条件は、温度:125℃、湿度:100%、気圧:110kPa、時間:24時間である。

【0045】

図10では、各深さにおいてPCT前後のプロファイルが示されている。図10の左図中に示される各深さにおけるプロファイルのうち、円で囲った部分においては、ピークが見られる方がPCT後のプロファイルであり、ピークが見られない方がPCT前のプロファイルを示している。図10の左図に示すように、SiCN膜の場合は、PCT後、膜中におけるH−O結合のピークが見られるようになり、SiCN膜中の酸素が増加していることが分かる。一方で、図10の右図中においては、左図と同様に円で囲った部分におけるPCT前後のプロファイルはほぼ等しい。図10の右図に示すように、窒化プラズマ処理を行ったSiN膜を含む積層膜の場合は、PCT後、膜中においてH−O結合のピークは見られない。よって、積層膜中の酸素が増加していないことが分かる。このように、窒化プラズマ処理を行ったSiN膜を含む積層膜は、多湿の雰囲気においても膜質が安定しており、ストレスの変化が少ない膜であることが分かる。

【0046】

(実施例2)

図11は、実施例2に係る半導体装置のTOF−SIMSによるデプスプロファイルを示すグラフである。実施例2として、Cuアロイシード膜、Pure Cuめっき膜によって構成される配線上に、バリア絶縁膜およびエッチングストッパ膜を積層した構造に対し、PCTを行い、PCT前後の酸素に由来した信号強度(O-intensity)の変化をTOF−SIMSによるデプスプロファイルによって比較した。なお、PCTの測定条件は、実施例1と同様である。

【0047】

図11中の左図は、エッチングストッパ膜およびバリア絶縁膜として、Crich SiCN膜およびSiCN膜をそれぞれ使用した。Crich SiCN膜の膜厚は35nmであり、SiCN膜の膜厚は10nmである。左図中の上方に位置するグラフがPCT後のプロファイルであり、下方に位置するグラフがPCT前のプロファイルを示している。

図11中の右図は、エッチングストッパ膜およびバリア絶縁膜として、Crich SiCN膜およびSiN膜をそれぞれ使用した。Crich SiCN膜の膜厚は42nmであり、SiN膜の膜厚は3nmである。また、SiN膜は、成膜後に窒化プラズマ処理を施している。右図中の上方に位置するグラフがPCT後のプロファイルであり、下方に位置するグラフがPCT前のプロファイルを示している。

【0048】

図11の左図に示すように、バリア絶縁膜がSiCN膜の場合、バリア絶縁膜とCu配線との界面において、酸素に由来した信号強度が増加していることが分かる。一方で、図11の右図に示すように、バリア絶縁膜が窒化プラズマ処理を施したSiN膜の場合、バリア絶縁膜とCu配線との界面において、酸素に由来した信号強度は増加していない。このように、窒化プラズマ処理を行ったSiN膜をバリア絶縁膜とした場合、バリア絶縁膜の透水性が低減され、配線への酸素濃度の侵入を抑制できることが分かる。

【0049】

(実施例3)

実施例3として、実施例2に用いた二つの構造について、EM特性、TDDB特性、およびSIV特性を測定した。

EM特性については、バリア絶縁膜が窒化プラズマ処理を施したSiN膜の場合、バリア絶縁膜がSiCN膜の場合と比べて、MTTF(Mean Time To Failure)における寿命が5倍改善した。

TDDB特性については、バリア絶縁膜が窒化プラズマ処理を施したSiN膜の場合、バリア絶縁膜がSiCN膜の場合と比べて、MTTFにおける寿命が50倍改善した。

SiV特性については、66nm〜3μmの上層配線および下層配線間における不良を、175℃にホールドした条件において測定した。バリア絶縁膜がSiCN膜である場合、不良が発生した。一方で、バリア絶縁膜が窒化プラズマ処理を施したSiN膜である場合、1000時間経過後においても不良が発生しなかった。

【0050】

(実施例4)

実施例4としては、SiN膜を3nm×33回積層してなる積層膜に対し窒化プラズマ処理を行った場合と窒化プラズマ処理を行っていない場合とにおいて、SiN膜における電流密度−電圧特性、およびFTIRによるSi−N結合のピーク位置を測定した。

【0051】

図12は、実施例4に係るSiN膜の電流密度−電圧特性を示すグラフである。図12に示すように、窒化プラズマ処理を行っていない場合と比較して、窒化プラズマ処理を行った場合は、SiN膜におけるリーク電流を低減されている。窒化プラズマ処理を行った場合、窒化プラズマ処理を行っていない場合と比較して、3MV/cmでは、2桁のリーク電流が抑制された。

【0052】

図13は、実施例4に係るSiN膜のFTIRによって測定されたSi−N結合のピーク位置を示すグラフである。図13に示すように、窒化プラズマ処理を行っていない場合、Si−N結合のピーク位置は840cm−1である。これに対し、窒化プラズマ処理を行った場合、Si−N結合のピーク位置は856cm−1である。この結果から、窒化プラズマ処理を行うことにより、Si−H結合およびダングリングボンドが減少したことがわかる。理想のSi3N4では860cm−1と想定されるため、窒化プラズマ処理によって良質な膜となっていることが推定される。SiN膜をESR分析すると、窒化プラズマ処理を行っていない場合、ダングリングボンドに起因したスピン密度は5.8E17spins/cm3であった。これに対し、窒化プラズマ処理を行った場合、ダングリングボンドに起因したスピン密度は、検出限界である1E17spins/cm3以下であった。

【0053】

(実施例5)

図14は、実施例5に係るSiN膜のFTIRによって測定されたSi−N結合のピーク位置を示すグラフである。実施例5としては、窒化プラズマ処理を行ったSiN膜の膜厚が3〜5nmである場合のSi−N結合のピーク位置を測定した。図14に示すように、SiN膜の膜厚が増加するにつれ、Si−N結合のピークを示す波数は減少している。SiN膜の膜厚が3nmで850cm−1、3.5nmで846cm−1、4nmで845cm−1、5nmで838cm−1であった。これは、膜厚が増加するにつれ、SiN膜中のSi−H結合やダングリングボンドが増加していることを示している。デバイス的に許容されるのは4nm以下であり、この場合のSi−N結合のピーク位置は845cm−1と対応する。

【0054】

このように、本発明によれば、信頼性の高い半導体装置を提供することができることが分かる。

【0055】

以上、図面を参照して本発明の実施形態について述べたが、これらは本発明の例示であり、上記以外の様々な構成を採用することもできる。

【符号の説明】

【0056】

10、12 層間絶縁膜

20、22 配線

24 ビア

201、221 シード膜

202、222 めっき膜

203、223 バリアメタル膜

30、32 SiN膜

40、42 エッチングストッパ膜

50、52 添加金属偏析層

60 ハードマスク

62、64 開口

70 トランジスタ

80 シリコン基板

100 半導体装置

【特許請求の範囲】

【請求項1】

第1の層間絶縁膜と、

前記第1の層間絶縁膜中に設けられた配線と、

前記第1の層間絶縁膜上および前記配線上に設けられたSiN膜と、

を備え、

FTIRによって測定した前記SiN膜のSi−N結合のピーク位置が845cm−1以上860cm−1以下である半導体装置。

【請求項2】

第1の層間絶縁膜と、

前記第1の層間絶縁膜中に設けられた配線と、

前記第1の層間絶縁膜上および前記配線上に設けられたSiN膜と、

を備え、

XPSによって測定した前記SiN膜の組成比N/Siが0.9以上4/3以下である半導体装置。

【請求項3】

第1の層間絶縁膜と、

前記第1の層間絶縁膜中に設けられた配線と、

前記第1の層間絶縁膜上および前記配線上に設けられたSiN膜と、

を備え、

前記SiN膜中における、ダングリングボンドに起因したスピン密度が1E17spins/cm3以下である半導体装置。

【請求項4】

請求項1ないし3いずれか1項に記載の半導体装置において、

前記配線は、

Cuと、添加金属材料であるAl、Mn、Ti、Sn、Mg、Si、またはZrからなり、

前記SiN膜と接する面において、前記添加金属材料が偏析してなる添加金属偏析層を有する半導体装置。

【請求項5】

請求項1ないし4いずれか1項に記載の半導体装置において、

前記SiN膜の膜厚は、1nm以上4nm以下である半導体装置。

【請求項6】

請求項1ないし5いずれか1項に記載の半導体装置において、

前記SiN膜は、上面において他の部分よりも窒素濃度が高い半導体装置。

【請求項7】

請求項1ないし6いずれか1項に記載の半導体装置において、

前記配線は、

側面および下面をバリアメタル膜によって覆われており、

前記バリアメタル膜との界面において、他の部分よりも水素濃度が高い半導体装置。

【請求項8】

請求項1ないし7いずれか1項に記載の半導体装置において、

前記SiN膜上に設けられたエッチングストッパ膜と、

前記エッチングストッパ膜上に設けられた第2の層間絶縁膜と、

をさらに備え、

前記エッチングストッパ膜は、前記第2の層間絶縁膜をエッチングする条件において前記第2の層間絶縁膜よりもエッチングレートが遅い半導体装置。

【請求項9】

請求項8に記載の半導体装置において、

前記エッチングストッパ膜は、SiCN(SiCNH)、SiCO(SiCOH)、SiCNO(SiCNOH)、SiC(SiCH)、SiB(SiBH)、SiBN(SiBHN)、SiBC(SiBCH)、SiBCN(SiBCNH)、C−rich SiCN(SiCNH)、C−rich SiCO(SiCOH)、C−rich SiCNO(SiCNOH)、C−rich SiC(SiCH)、C−rich SiBC(SiBCH)、およびC−rich SiBCN(SiBCHN)の少なくとも一つによって構成される半導体装置。

【請求項10】

請求項8または9に記載の半導体装置において、

前記エッチングストッパ膜の比誘電率が4以下である半導体装置。

【請求項11】

層間絶縁膜中に配線を設ける工程と、

前記第1の層間絶縁膜上および前記配線上に、SiN膜を形成する工程と、

前記SiN膜に対し、窒化増強処理を行う工程と、

を備える半導体装置の製造方法。

【請求項12】

請求項11に記載の半導体装置の製造方法において、

前記配線は、Cuと、添加金属材料であるAl、Mn、Ti、Sn、Mg、Si、またはZrからなり、

前記窒化増強処理を行う工程によって、前記配線のうち前記SiN膜と接する面に、前記添加金属材料が偏析してなる添加金属偏析層が形成される半導体装置の製造方法。

【請求項13】

請求項11または12に記載の半導体装置の製造方法において、

前記窒化増強処理は、プラズマCVDである半導体装置の製造方法。

【請求項14】

請求項13に記載の半導体装置の製造方法において、

前記SiN膜を形成する工程は、プラズマCVDによって行われ、

前記窒化増強処理を行う工程におけるプラズマCVDのパワーは、前記SiN膜を形成する工程におけるプラズマCVDのパワーよりも高い半導体装置の製造方法。

【請求項15】

請求項11または12に記載の半導体装置の製造方法において、

前記窒化増強処理は、窒素含有ガス雰囲気下における、EB処理またはUV処理である半導体装置の製造方法。

【請求項16】

請求項11ないし15いずれか1項に記載の半導体装置の製造方法において、

前記窒化増強処理を行う工程の後において、

前記SiN膜上にエッチングストッパ膜を形成する工程と、

前記エッチングストッパ膜上に第2の層間絶縁膜を形成する工程と、

をさらに備え、

前記エッチングストッパ膜は、前記第2の層間絶縁膜をエッチングする条件において前記第2の層間絶縁膜よりもエッチングレートが遅い半導体装置の製造方法。

【請求項1】

第1の層間絶縁膜と、

前記第1の層間絶縁膜中に設けられた配線と、

前記第1の層間絶縁膜上および前記配線上に設けられたSiN膜と、

を備え、

FTIRによって測定した前記SiN膜のSi−N結合のピーク位置が845cm−1以上860cm−1以下である半導体装置。

【請求項2】

第1の層間絶縁膜と、

前記第1の層間絶縁膜中に設けられた配線と、

前記第1の層間絶縁膜上および前記配線上に設けられたSiN膜と、

を備え、

XPSによって測定した前記SiN膜の組成比N/Siが0.9以上4/3以下である半導体装置。

【請求項3】

第1の層間絶縁膜と、

前記第1の層間絶縁膜中に設けられた配線と、

前記第1の層間絶縁膜上および前記配線上に設けられたSiN膜と、

を備え、

前記SiN膜中における、ダングリングボンドに起因したスピン密度が1E17spins/cm3以下である半導体装置。

【請求項4】

請求項1ないし3いずれか1項に記載の半導体装置において、

前記配線は、

Cuと、添加金属材料であるAl、Mn、Ti、Sn、Mg、Si、またはZrからなり、

前記SiN膜と接する面において、前記添加金属材料が偏析してなる添加金属偏析層を有する半導体装置。

【請求項5】

請求項1ないし4いずれか1項に記載の半導体装置において、

前記SiN膜の膜厚は、1nm以上4nm以下である半導体装置。

【請求項6】

請求項1ないし5いずれか1項に記載の半導体装置において、

前記SiN膜は、上面において他の部分よりも窒素濃度が高い半導体装置。

【請求項7】

請求項1ないし6いずれか1項に記載の半導体装置において、

前記配線は、

側面および下面をバリアメタル膜によって覆われており、

前記バリアメタル膜との界面において、他の部分よりも水素濃度が高い半導体装置。

【請求項8】

請求項1ないし7いずれか1項に記載の半導体装置において、

前記SiN膜上に設けられたエッチングストッパ膜と、

前記エッチングストッパ膜上に設けられた第2の層間絶縁膜と、

をさらに備え、

前記エッチングストッパ膜は、前記第2の層間絶縁膜をエッチングする条件において前記第2の層間絶縁膜よりもエッチングレートが遅い半導体装置。

【請求項9】

請求項8に記載の半導体装置において、

前記エッチングストッパ膜は、SiCN(SiCNH)、SiCO(SiCOH)、SiCNO(SiCNOH)、SiC(SiCH)、SiB(SiBH)、SiBN(SiBHN)、SiBC(SiBCH)、SiBCN(SiBCNH)、C−rich SiCN(SiCNH)、C−rich SiCO(SiCOH)、C−rich SiCNO(SiCNOH)、C−rich SiC(SiCH)、C−rich SiBC(SiBCH)、およびC−rich SiBCN(SiBCHN)の少なくとも一つによって構成される半導体装置。

【請求項10】

請求項8または9に記載の半導体装置において、

前記エッチングストッパ膜の比誘電率が4以下である半導体装置。

【請求項11】

層間絶縁膜中に配線を設ける工程と、

前記第1の層間絶縁膜上および前記配線上に、SiN膜を形成する工程と、

前記SiN膜に対し、窒化増強処理を行う工程と、

を備える半導体装置の製造方法。

【請求項12】

請求項11に記載の半導体装置の製造方法において、

前記配線は、Cuと、添加金属材料であるAl、Mn、Ti、Sn、Mg、Si、またはZrからなり、

前記窒化増強処理を行う工程によって、前記配線のうち前記SiN膜と接する面に、前記添加金属材料が偏析してなる添加金属偏析層が形成される半導体装置の製造方法。

【請求項13】

請求項11または12に記載の半導体装置の製造方法において、

前記窒化増強処理は、プラズマCVDである半導体装置の製造方法。

【請求項14】

請求項13に記載の半導体装置の製造方法において、

前記SiN膜を形成する工程は、プラズマCVDによって行われ、

前記窒化増強処理を行う工程におけるプラズマCVDのパワーは、前記SiN膜を形成する工程におけるプラズマCVDのパワーよりも高い半導体装置の製造方法。

【請求項15】

請求項11または12に記載の半導体装置の製造方法において、

前記窒化増強処理は、窒素含有ガス雰囲気下における、EB処理またはUV処理である半導体装置の製造方法。

【請求項16】

請求項11ないし15いずれか1項に記載の半導体装置の製造方法において、

前記窒化増強処理を行う工程の後において、

前記SiN膜上にエッチングストッパ膜を形成する工程と、

前記エッチングストッパ膜上に第2の層間絶縁膜を形成する工程と、

をさらに備え、

前記エッチングストッパ膜は、前記第2の層間絶縁膜をエッチングする条件において前記第2の層間絶縁膜よりもエッチングレートが遅い半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【公開番号】特開2012−146909(P2012−146909A)

【公開日】平成24年8月2日(2012.8.2)

【国際特許分類】

【出願番号】特願2011−5834(P2011−5834)

【出願日】平成23年1月14日(2011.1.14)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

【公開日】平成24年8月2日(2012.8.2)

【国際特許分類】

【出願日】平成23年1月14日(2011.1.14)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

[ Back to top ]