半導体装置および半導体装置の製造方法

【課題】半導体基板の転移を防止しつつ、絶縁膜の埋め込み性を確保するとともに、エッチング耐性を向上させる。

【解決手段】シリコン含有無機ポリマー膜8にアルカリ金属元素またはアルカリ土類金属元素を含有させ、塗布法などの方法にてトレンチ6内に埋め込まれるようにしてシリコン含有無機ポリマー膜8をライナー膜7上に形成し、水蒸気を含む雰囲気中でシリコン含有無機ポリマー膜8の酸化処理を行うことにより、シリコン含有無機ポリマー膜8をシリコン酸化膜9に変化させる。

【解決手段】シリコン含有無機ポリマー膜8にアルカリ金属元素またはアルカリ土類金属元素を含有させ、塗布法などの方法にてトレンチ6内に埋め込まれるようにしてシリコン含有無機ポリマー膜8をライナー膜7上に形成し、水蒸気を含む雰囲気中でシリコン含有無機ポリマー膜8の酸化処理を行うことにより、シリコン含有無機ポリマー膜8をシリコン酸化膜9に変化させる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明の実施形態は半導体装置および半導体装置の製造方法に関する。

【背景技術】

【0002】

半導体集積回路の微細化に伴って、CVD法では絶縁膜の埋め込みが困難になっている。絶縁膜の埋め込み性を確保するために、塗布法にてポリシラザンを埋め込む方法が検討されている。ポリシラザンは−SiH2−NH−の基本構造を有するポリマーで、水蒸気雰囲気でアニールすることによってシリコン酸化膜に転換できる。水蒸気温度は高い方が二酸化ケイ素の性質に近くなるが、Si側壁が同時に酸化され易くなり、Siの転移を引き起すことがある。水蒸気温度を低くすると、Si側壁の酸化は抑制されるが、エッチング液によるエッチング速度が速くなり、所望の形状を得ることが難しくなる。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2006−291107号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

本発明の一つの実施形態の目的は、半導体基板の転移を防止しつつ、絶縁膜の埋め込み性を確保するとともに、エッチング耐性を向上させることが可能な半導体装置および半導体装置の製造方法を提供することである。

【課題を解決するための手段】

【0005】

実施形態の半導体装置によれば、半導体基板と、トレンチと、シリコン酸化膜とが設けられている。トレンチは、前記半導体基板の素子分離領域に形成されている。シリコン酸化膜は、アルカリ金属元素またはアルカリ土類金属元素を含有し、前記トレンチに埋め込まれている。

【図面の簡単な説明】

【0006】

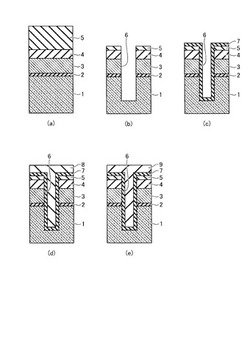

【図1】図1(a)〜図1(e)は、第1実施形態に係る半導体装置の製造方法を示す断面図である。

【図2】図2(a)〜図2(e)は、第1実施形態に係る半導体装置の製造方法を示す断面図である。

【図3】図3は、実施形態に係る半導体装置に適用されるアルカリ金属元素およびアルカリ土類金属元素の活性化エネルギーを示す図である。

【図4】図4(a)は、アルカリ金属元素およびアルカリ土類金属元素の1価イオンの活性化エネルギーと拡散係数との関係を示す図、図4(b)は、アルカリ金属元素およびアルカリ土類金属元素の中性原子の活性化エネルギーと拡散係数との関係を示す図である。

【図5】図5(a)〜図5(e)は、第2実施形態に係る半導体装置の製造方法を示す断面図である。

【図6】図6(a)〜図6(e)は、第3実施形態に係る半導体装置の製造方法を示す断面図である。

【図7】図7(a)〜図7(c)は、第4実施形態に係る半導体装置の製造方法を示す断面図である。

【発明を実施するための形態】

【0007】

以下、実施形態に係る半導体装置について図面を参照しながら説明する。なお、これらの実施形態により本発明が限定されるものではない。

【0008】

(第1実施形態)

図1(a)〜図1(e)および図2(a)〜図2(e)は、第1実施形態に係る半導体装置の製造方法を示す断面図である。なお、第1実施形態では、半導体装置としてNANDメモリを例にとる。

図1(a)において、熱酸化などの方法にて半導体基板1上にゲート絶縁膜2を形成する。なお、半導体基板1の材料は、例えば、Si、Ge、SiGe、SiC、SiSn、PbS、GaAs、InP、InGaAsP、GaP、GaNまたはZnSeなどを用いることができる。ゲート絶縁膜2としては、シリコン酸化膜を用いるようにしてもよいし、高誘電体膜を用いるようにしてもよい。また、ゲート絶縁膜2の膜厚は、例えば、8nm程度に設定することができる。

【0009】

次に、CVDなどの方法にてゲート絶縁膜2上に浮遊ゲート電極膜3を形成する。なお、浮遊ゲート電極膜3としては、多結晶シリコン膜を用いるようにしてもよいし、WSiまたはCoSiなどの合金膜を用いるようにしてもよい。また、浮遊ゲート電極膜3の膜厚は、例えば、100〜200nmの範囲内に設定することができる。

【0010】

次に、減圧CVDなどの方法にて浮遊ゲート電極膜3上にCMPストッパ膜4を形成する。なお、CMPストッパ膜4としては、シリコン窒化膜を用いるようにしてもよいし、多結晶シリコン膜を用いるようにしてもよい。また、CMPストッパ膜4の膜厚は、例えば、100〜200nmの範囲内に設定することができる。

【0011】

次に、LPCVDなどの方法にて上にハードマスク5を形成する。なお、ハードマスク5としては、例えば、TEOS膜を用いることができる。また、ハードマスク5の膜厚は、例えば、300nm程度に設定することができる。

【0012】

次に、図1(b)に示すように、フォトリソグラフィー技術およびドライエッチング技術を用いることにより、ハードマスク5、CMPストッパ膜4、浮遊ゲート電極膜3およびゲート絶縁膜2を貫通して半導体基板1内に達するトレンチ6を素子分離領域に形成する。この時、ハードマスク5は薄膜化され、CMPストッパ膜4上にハードマスク5が薄く残される。なお、このトレンチ6は、NANDメモリにおけるSTI(Shallow Trench Isolation)として用いることができる。また、トレンチ6の幅は10〜100nm程度の範囲内、トレンチ6の深さは200〜500nm程度の範囲内に設定することができる。

【0013】

次に、図1(c)に示すように、CVDなどの方法にてトレンチ6の側壁が覆われるようにしてハードマスク5上にライナー膜7を形成する。なお、ライナー膜7としては、例えば、TEOS膜またはHTO膜を用いることができ、アルカリ金属元素およびアルカリ土類金属元素を含有しないようにすることができる。また、ライナー膜7の膜厚は、1〜20nm程度の範囲内に設定することができる。また、ライナー膜7は省略するようにしてもよい。

【0014】

次に、図1(d)に示すように、塗布法などの方法にてトレンチ6内に埋め込まれるようにしてシリコン含有無機ポリマー膜8をライナー膜7上に形成する。この時、シリコン含有無機ポリマー膜8には、アルカリ金属元素またはアルカリ土類金属元素を含有させる。このアルカリ金属元素またはアルカリ土類金属元素は、K、Rb、Cs、MgおよびSrから選択されることが好ましく、特に、Csが最も好ましい。これらの元素は1種類だけ使用してもよいし、複数の元素を組み合わせて使用するようにしてもよい。また、このアルカリ金属元素またはアルカリ土類金属元素の濃度は、半導体基板1上に成膜した酸化物の表面濃度として、1010atoms/cm2以上に設定することが好ましい。

【0015】

また、シリコン含有無機ポリマー膜8は、Si−O結合またはSi−N結合を基本構造とする高分子から構成することができる。例えば、シリコン含有無機ポリマー膜8としては、例えば、ペルヒドロポリシラザン(PHPS)膜またはハイドロジェンシルセスキオキサン(HSQ)膜を用いることができる。

メチル基など有機物を官能基として有するシリコン含有ポリマー膜(有機SOG)をPHPS膜やHSQ膜の代わりに用いると、有機物が400℃から600℃程度の温度において分解を始めるので、これより高温の製造工程が入る部分には使用することが出来ない。特にSTIにおいては有機SOG中の炭素が固定電荷として働き、半導体デバイスの閾値に悪影響を及ぼす。それに対して、シリコン含有無機ポリマー膜(無機SOG)では、そのような影響を低減することが出来る。

また、有機SOGは電気的な耐圧が低く、5MV/cm程度である。10〜20MV/cm程度の高電界がかかるような箇所(例えば、NANDメモリのSTIなど)には有機SOGは使用できず、有機SOGよりも電気的な耐圧が高い無機SOGが使用される。

【0016】

ここで、シリコン含有無機ポリマー膜8にアルカリ金属元素またはアルカリ土類金属元素を含有させる方法としては、アルカリ金属元素またはアルカリ土類金属元素から構成される塩類をシリコン含有無機ポリマー溶液に添加してからライナー膜7上に塗布することができる。この時、シリコン含有無機ポリマー溶液中のアルカリ金属元素またはアルカリ土類金属元素の濃度は、Si基板上に成膜したときの表面濃度として1010atoms/cm2以上に設定することが好ましい。そして、シリコン含有無機ポリマー溶液を塗布した後、熱処理を行うことで溶媒を揮発させ、シリコン含有無機ポリマー膜8を形成することができる。なお、この熱処理は、例えば、ホットプレート上で80〜300℃程度の範囲内で数十秒間行うことができる。また、アルカリ金属元素またはアルカリ土類金属元素の添加剤としては、アルカリ金属元素またはアルカリ土類金属元素の硝酸塩、硫酸塩、炭酸塩、酸化物、塩化物、臭化物、弗化物、ヨウ化物、水酸化物などを挙げることができる。

【0017】

次に、図1(e)に示すように、水蒸気を含む雰囲気中でシリコン含有無機ポリマー膜8の酸化処理を行うことにより、シリコン含有無機ポリマー膜8をシリコン酸化膜9に変化させる。なお、酸化処理は、230℃以上かつ900℃以下の温度で行うことが好ましい。ここで、酸化処理の温度を230℃以上に設定することにより、シリコン酸化膜9を緻密化させることができる。このため、フッ酸などのエッチング液によるエッチング速度を遅くすることができ、所望の形状を得やすくすることができる。また、酸化処理の温度を900℃以下に設定することにより、半導体基板1の側壁の酸化を抑制することができ、半導体基板1の転移を抑制することができる。また、酸化炉内の雰囲気および温度を安定化させるために、酸化処理は、5分以上行うことが好ましい。ただし、過剰に長時間の酸化が行われると、半導体基板1の側壁が厚く酸化されるため、酸化処理に時間は、60分以下に設定することが好ましい。

【0018】

ここで、シリコン含有無機ポリマー膜8にアルカリ金属元素またはアルカリ土類金属元素を含有させることで、シリコン含有無機ポリマー膜8をシリコン酸化膜9に転換させる反応を促進させることができる。このため、シリコン含有無機ポリマー膜8の酸化処理の温度を低下させつつ、シリコン酸化膜9の元素濃度や密度などの膜質を二酸化ケイ素に近づけることができ、半導体基板1の転移を防止しつつ、トレンチ6でのシリコン酸化膜9の埋め込み性を確保するとともに、エッチング耐性を向上させることが可能となる。

【0019】

また、トレンチ6とシリコン酸化膜9との間にライナー膜7を設けることにより、シリコン含有無機ポリマー膜8にアルカリ金属元素またはアルカリ土類金属元素が含有されている場合においても、アルカリ金属元素またはアルカリ土類金属元素が半導体基板1およびゲート絶縁膜2に拡散するのを抑制することができる。このため、アルカリ金属元素またはアルカリ土類金属元素が半導体基板1およびゲート絶縁膜2で固定電荷として作用するのを抑制することができ、シリコン酸化膜9を用いたデバイスの信頼性の低下を抑制することができる。

【0020】

次に、図2(a)に示すように、CMPなどの方法にてCMPストッパ膜4が露出するまでシリコン酸化膜9、ライナー膜7およびハードマスク5を薄膜化することにより、トレンチ6の周辺のシリコン酸化膜9、ライナー膜7およびハードマスク5を除去する。

【0021】

なお、このCMPを行う前または後に不活性雰囲気中でシリコン酸化膜9の熱処理を行うようにしてもよい。この熱処理は、700℃以上かつ1100℃以下の温度で行うことが好ましい。ここで、熱処理の温度を700℃以上に設定することにより、シリコン酸化膜9を十分に緻密化させることができる。また、熱処理の温度を1100℃以下に設定することにより、デバイスによってはイオン注入で既に形成されたチャネル層の拡散深さが増大するのを抑制することができる。この熱処理によってシリコン酸化膜9から水分が除去され、シリコン酸化膜9を緻密化させることが可能となり、デバイスの電機特性を向上させることができる。

【0022】

次に、図2(b)に示すように、フッ化物を用いたドライエッチングまたは希フッ酸を用いたウェットエッチングにてシリコン酸化膜9およびライナー膜7の上部を除去することにより、CMPストッパ膜4に対して段差10を形成する。

【0023】

次に、図2(c)に示すように、リン酸溶液を用いたウェットエッチングにてCMPストッパ膜4を除去し、浮遊ゲート電極膜3を露出させる。

【0024】

次に、図2(d)に示すように、フッ化物を用いたドライエッチングまたは希フッ酸を用いたウェットエッチングにてシリコン酸化膜9およびライナー膜7の上部を除去することにより、浮遊ゲート電極膜3に対して段差11を形成する。この時、シリコン酸化膜9およびライナー膜7はゲート絶縁膜2上に突出させることが好ましい。

【0025】

ここで、アルカリ金属元素またはアルカリ土類金属元素をシリコン含有無機ポリマー膜8に含有させることにより、シリコン含有無機ポリマー膜8からシリコン酸化膜9への転換速度を向上させることができ、元素組成や密度などの膜質が二酸化ケイ素に近づく。そのため、シリコン酸化膜9のエッチング速度をライナー膜7のエッチング速度と同等にすることができる。このため、シリコン酸化膜9およびライナー膜7の上部を除去する際にライナー膜7に対してシリコン酸化膜9が過度にエッチングされるのを防止することができ、ライナー膜7とシリコン酸化膜9との高さを揃えることができる。なお、ライナー膜7とシリコン酸化膜9との高さの差は10nm以下にすることが好ましい。

【0026】

次に、図2(e)に示すように、CVDなどの方法にて段差11の側壁が覆われるようにして浮遊ゲート電極膜3、ライナー膜7およびシリコン酸化膜9上に電極間絶縁膜12を形成する。なお、電極間絶縁膜12としては、例えば、ONO(シリコン酸化膜/シリコン窒化膜/シリコン酸化膜)膜を用いることができる。また、電極間絶縁膜12の膜厚は、例えば、20nm程度に設定することができる。

【0027】

次に、CVDなどの方法にて電極間絶縁膜12上に制御ゲート電極膜13を形成する。なお、制御ゲート電極膜13としては、例えば、多結晶シリコン膜およびタングステン膜を用いることができる。また、制御ゲート電極膜12の膜厚は、例えば、50nm程度に設定することができる。

【0028】

図3は、実施形態に係る半導体装置に適用されるアルカリ金属元素およびアルカリ土類金属元素の活性化エネルギーを示す図である。なお、Ea(M+)およびEa(M0)はそれぞれ1価イオンおよび中性原子がシリコン格子中を移動する際の活性化エネルギー(計算値)である。また、活性化エネルギーEa(M+)、Ea(M0)それぞれについて、1.5eV以上の元素を薄いハッチ、2.0eV以上の元素を濃いハッチで示した。

図3において、アルカリ金属元素では、原子半径やイオン半径が大きくなるにしたがって活性化エネルギーEaが大きくなり、拡散するのに大きなエネルギーを必要とする。アルカリ土類金属元素に関しては、活性化エネルギーEa(M0)はアルカリ金属よりも全体的に大きいが、活性化エネルギーEa(M+)が小さい傾向にあることが分かる。

【0029】

図4(a)は、アルカリ金属元素およびアルカリ土類金属元素の1価イオンの活性化エネルギーと拡散係数との関係を示す図、図4(b)は、アルカリ金属元素およびアルカリ土類金属元素の中性原子の活性化エネルギーと拡散係数との関係を示す図である。なお、ここでは活性化エネルギーと、シリコン原子中およびシリコン酸化膜中の拡散係数(計算値)の関係を示した。

図4において、活性化エネルギーEa(M+)、Ea(M0)が小さくなるに従って、拡散係数が大きくなることが分かる。拡散しにくい元素は、活性化エネルギーEa(M+)、Ea(M0)がともに1.5eV以上、安全を見ると2.0eV以上である。活性化エネルギーEa(M+)、Ea(M0)の両者が1.5eV以上の元素はK、Rb、Cs、Mg、Srの5元素である。特に、CsはEa(M+)とEa(M0)両者共に2.5eV程度もあり、非常に拡散しにくい元素である。

【0030】

アルカリ金属元素やアルカリ土類金属元素は、ゾルゲル法などによるガラスの製造において、反応を促進させる触媒として利用されている。また、これらの元素は、ガラス転移温度を低下させて低温での流動性を高めることができる。これらの元素を、シリコン酸化物薄膜作成のための薬液に添加することで、薄膜形成を促進することが可能となるとともに、流動性を高めることができ、熱処理過程で生じるシリコン酸化膜9の収縮や応力が原因となって生じるSi基板の結晶転移を減少させることができる。

【0031】

また、アルカリ金属元素またはアルカリ土類金属元素を含む塗布液は酸化物へ転換する反応を促進させることができ、無機SOG膜の元素組成や密度などの膜質をCVD酸化膜の膜質に近づけることができる。このため、無機SOG膜をCVD酸化膜と同程度のエッチング速度にすることができ、ライナー膜7とシリコン酸化膜9との高さを揃えることができる。

【0032】

(第2実施形態)

図5(a)〜図5(e)は、第2実施形態に係る半導体装置の製造方法を示す断面図である。なお、第2実施形態では、半導体装置としてフィン型トランジスタを例にとる。

図5(a)において、CVDなどの方法にて半導体基板21上にCMPストッパ膜23を形成する。なお、半導体基板21上にCMPストッパ膜23を形成する前に、酸素雰囲気中で半導体基板21を熱処理することにより、半導体基板21上に酸化膜を形成するようにしてもよい。また、CMPストッパ膜23は、例えば、100〜200nm程度に設定することができる。

【0033】

そして、フォトリソグラフィー技術およびドライエッチング技術を用いてCMPストッパ膜23を貫通して半導体基板21内に達するトレンチを形成することにより、半導体基板21上にフィン22を形成する。なお、フィン22の高さは、100〜300nmの範囲内に設定することができる。フィン22の幅は、50nm以下に設定することができる。

【0034】

次に、図5(b)に示すように、CVDなどの方法にてフィン22およびCMPストッパ膜23が覆われるようにして半導体基板21上にライナー膜24を形成する。なお、ライナー膜24としては、例えば、TEOS膜またはHTO膜を用いることができ、アルカリ金属元素およびアルカリ土類金属元素を含有しないようにすることができる。また、ライナー膜24の膜厚は、2〜30nm程度の範囲内に設定することができる。また、ライナー膜24は省略してもよい。

【0035】

次に、塗布法などの方法にてフィン22の周囲が平坦化されるようにしてシリコン含有無機ポリマー膜25をライナー膜24上に形成する。この時、シリコン含有無機ポリマー膜24には、アルカリ金属元素またはアルカリ土類金属元素を含有させる。このシリコン含有無機ポリマー膜24は、シリコン含有無機ポリマー膜7と同様に構成することができる。

【0036】

次に、図5(c)に示すように、水蒸気を含む雰囲気中でシリコン含有無機ポリマー膜25の酸化処理を行うことにより、シリコン含有無機ポリマー膜25をシリコン酸化膜26に変化させる。この酸化処理は、図1(e)の酸化処理と同様に行うことができる。

【0037】

次に、図5(d)に示すように、CMPなどの方法にてCMPストッパ膜23が露出するまでシリコン酸化膜26およびライナー膜24を薄膜化することにより、フィン22上のシリコン酸化膜26およびライナー膜24を除去する。

【0038】

次に、図5(e)に示すように、フッ化物を用いたドライエッチングまたは希フッ酸を用いたウェットエッチングにてシリコン酸化膜26およびライナー膜24の上部を除去することにより、シリコン酸化膜26およびライナー膜24上にフィン22の一部を突出させる。そして、ゲート絶縁膜を介してフィン22の側壁にゲート電極を形成することにより、ダブルゲート型トランジスタを形成することができる。

【0039】

ここで、シリコン含有無機ポリマー膜25にアルカリ金属元素またはアルカリ土類金属元素を含有させることで、シリコン含有無機ポリマー膜25をシリコン酸化膜26に転換させる反応を促進させることができる。このため、シリコン含有無機ポリマー膜25の酸化処理の温度を低下させつつ、シリコン酸化膜26の元素濃度や密度などの膜質をライナー膜24に近づけることができ、半導体基板21の転移を防止しつつ、フィン22間でのシリコン酸化膜26の埋め込み性を確保するとともに、エッチング耐性を向上させることが可能となる。

【0040】

(第3実施形態)

図6(a)〜図6(e)は、第3実施形態に係る半導体装置の製造方法を示す断面図である。なお、第3実施形態では、半導体装置としてPMD(Pre Metal Dielectric)を例にとる。

図6(a)において、半導体基板31上にゲート絶縁膜34を介してゲート電極35を形成した後、ゲート電極35の両側に配置されるようにして半導体基板31に不純物拡散層32、33を形成する。次に、CVDなどの方法にて半導体基板31上に層間絶縁膜36を形成する。なお、層間絶縁膜36としては、シリコン酸化膜を用いることができる。

【0041】

次に、図6(b)に示すように、塗布法などの方法にてゲート電極35の周囲が平坦化されるようにしてシリコン含有無機ポリマー膜37を層間絶縁膜36上に形成する。この時、シリコン含有無機ポリマー膜37には、アルカリ金属元素またはアルカリ土類金属元素を含有させる。このシリコン含有無機ポリマー膜37は、シリコン含有無機ポリマー膜7と同様に構成することができる。

【0042】

次に、図6(c)に示すように、水蒸気を含む雰囲気中でシリコン含有無機ポリマー膜37の酸化処理を行うことにより、シリコン含有無機ポリマー膜37をシリコン酸化膜38に変化させる。この酸化処理は、図1(e)の酸化処理と同様に行うことができる。

【0043】

次に、CVDなどの方法にてシリコン酸化膜38上にCMPストッパ膜39を形成する。なお、CMPストッパ膜39としては、シリコン窒化膜を用いるようにしてもよいし、多結晶シリコン膜を用いるようにしてもよい。また、CMPストッパ膜39の膜厚は、例えば、100〜200nmの範囲内に設定することができる。

【0044】

次に、図6(d)に示すように、フォトリソグラフィー技術およびドライエッチング技術を用いることにより、不純物拡散層32、33を露出させる開口部40をCMPストッパ膜39、シリコン酸化膜38および層間絶縁膜36に形成する。

【0045】

次に、図6(e)に示すように、開口部40に埋め込まれるようにして不純物拡散層32、33に接続された配線41をCMPストッパ膜39上に形成する。そして、CVDなどの方法にて配線41上に層間絶縁膜42を形成する。なお、配線41としては、AlまたはCuなどの金属を用いることができる。層間絶縁膜42としては、シリコン酸化膜を用いることができる。

【0046】

ここで、シリコン含有無機ポリマー膜37にアルカリ金属元素またはアルカリ土類金属元素を含有させることで、シリコン含有無機ポリマー膜37をシリコン酸化膜38に転換させる反応を促進させることができる。このため、シリコン含有無機ポリマー膜37の酸化処理の温度を低下させつつ、シリコン酸化膜38の元素濃度や密度などの膜質を二酸化ケイ素に近づけることができ、半導体基板31の転移を防止しつつ、シリコン酸化膜38のエッチング耐性を向上させることが可能となる。

【0047】

(第4実施形態)

図7(a)〜図7(c)は、第4実施形態に係る半導体装置の製造方法を示す断面図である。なお、第4実施形態では、半導体装置としてIMD(Inter Metal Dielectric)を例にとる。

図7(a)において、層間絶縁膜51に配線52を埋め込んだ後、CVDなどの方法にて層間絶縁膜51上に保護膜53を形成する。なお、層間絶縁膜51としては、シリコン酸化膜を用いることができる。保護膜53としては、シリコン窒化膜を用いることができる。次に、塗布法などの方法にてシリコン含有無機ポリマー膜54を保護膜53上に形成する。この時、シリコン含有無機ポリマー膜54には、アルカリ金属元素またはアルカリ土類金属元素を含有させる。このシリコン含有無機ポリマー膜54は、シリコン含有無機ポリマー膜7と同様に構成することができる。

【0048】

次に、図7(b)に示すように、水蒸気を含む雰囲気中でシリコン含有無機ポリマー膜54の酸化処理を行うことにより、シリコン含有無機ポリマー膜54をシリコン酸化膜55に変化させる。この酸化処理は、図1(e)の酸化処理と同様に行うことができる。そして、フォトリソグラフィー技術およびドライエッチング技術を用いることにより、配線52を露出させる開口部56をシリコン酸化膜55および保護膜53に形成する。

【0049】

次に、図7(c)に示すように、配線52に接続された配線57を開口部56に埋め込む。

【0050】

ここで、シリコン含有無機ポリマー膜54にアルカリ金属元素またはアルカリ土類金属元素を含有させることで、シリコン含有無機ポリマー膜54をシリコン酸化膜55に転換させる反応を促進させることができ、シリコン酸化膜55のエッチング耐性を向上させることが可能となる。

【0051】

本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

【符号の説明】

【0052】

1、21、31 半導体基板、2、34 ゲート絶縁膜、3 浮遊ゲート電極膜、4、23、39 CMPストッパ膜、5 ハードマスク、6 トレンチ、7、24 ライナー膜、8、25、37、54 シリコン含有無機ポリマー膜、9、26、38、55 シリコン酸化膜、10、11 段差、12 電極間絶縁膜、13 制御ゲート電極膜、22 フィン、32、33 不純物拡散層、35 ゲート電極、36、42、51 層間絶縁膜、40、56 開口部、41、52、57 配線、53 保護膜

【技術分野】

【0001】

本発明の実施形態は半導体装置および半導体装置の製造方法に関する。

【背景技術】

【0002】

半導体集積回路の微細化に伴って、CVD法では絶縁膜の埋め込みが困難になっている。絶縁膜の埋め込み性を確保するために、塗布法にてポリシラザンを埋め込む方法が検討されている。ポリシラザンは−SiH2−NH−の基本構造を有するポリマーで、水蒸気雰囲気でアニールすることによってシリコン酸化膜に転換できる。水蒸気温度は高い方が二酸化ケイ素の性質に近くなるが、Si側壁が同時に酸化され易くなり、Siの転移を引き起すことがある。水蒸気温度を低くすると、Si側壁の酸化は抑制されるが、エッチング液によるエッチング速度が速くなり、所望の形状を得ることが難しくなる。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2006−291107号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

本発明の一つの実施形態の目的は、半導体基板の転移を防止しつつ、絶縁膜の埋め込み性を確保するとともに、エッチング耐性を向上させることが可能な半導体装置および半導体装置の製造方法を提供することである。

【課題を解決するための手段】

【0005】

実施形態の半導体装置によれば、半導体基板と、トレンチと、シリコン酸化膜とが設けられている。トレンチは、前記半導体基板の素子分離領域に形成されている。シリコン酸化膜は、アルカリ金属元素またはアルカリ土類金属元素を含有し、前記トレンチに埋め込まれている。

【図面の簡単な説明】

【0006】

【図1】図1(a)〜図1(e)は、第1実施形態に係る半導体装置の製造方法を示す断面図である。

【図2】図2(a)〜図2(e)は、第1実施形態に係る半導体装置の製造方法を示す断面図である。

【図3】図3は、実施形態に係る半導体装置に適用されるアルカリ金属元素およびアルカリ土類金属元素の活性化エネルギーを示す図である。

【図4】図4(a)は、アルカリ金属元素およびアルカリ土類金属元素の1価イオンの活性化エネルギーと拡散係数との関係を示す図、図4(b)は、アルカリ金属元素およびアルカリ土類金属元素の中性原子の活性化エネルギーと拡散係数との関係を示す図である。

【図5】図5(a)〜図5(e)は、第2実施形態に係る半導体装置の製造方法を示す断面図である。

【図6】図6(a)〜図6(e)は、第3実施形態に係る半導体装置の製造方法を示す断面図である。

【図7】図7(a)〜図7(c)は、第4実施形態に係る半導体装置の製造方法を示す断面図である。

【発明を実施するための形態】

【0007】

以下、実施形態に係る半導体装置について図面を参照しながら説明する。なお、これらの実施形態により本発明が限定されるものではない。

【0008】

(第1実施形態)

図1(a)〜図1(e)および図2(a)〜図2(e)は、第1実施形態に係る半導体装置の製造方法を示す断面図である。なお、第1実施形態では、半導体装置としてNANDメモリを例にとる。

図1(a)において、熱酸化などの方法にて半導体基板1上にゲート絶縁膜2を形成する。なお、半導体基板1の材料は、例えば、Si、Ge、SiGe、SiC、SiSn、PbS、GaAs、InP、InGaAsP、GaP、GaNまたはZnSeなどを用いることができる。ゲート絶縁膜2としては、シリコン酸化膜を用いるようにしてもよいし、高誘電体膜を用いるようにしてもよい。また、ゲート絶縁膜2の膜厚は、例えば、8nm程度に設定することができる。

【0009】

次に、CVDなどの方法にてゲート絶縁膜2上に浮遊ゲート電極膜3を形成する。なお、浮遊ゲート電極膜3としては、多結晶シリコン膜を用いるようにしてもよいし、WSiまたはCoSiなどの合金膜を用いるようにしてもよい。また、浮遊ゲート電極膜3の膜厚は、例えば、100〜200nmの範囲内に設定することができる。

【0010】

次に、減圧CVDなどの方法にて浮遊ゲート電極膜3上にCMPストッパ膜4を形成する。なお、CMPストッパ膜4としては、シリコン窒化膜を用いるようにしてもよいし、多結晶シリコン膜を用いるようにしてもよい。また、CMPストッパ膜4の膜厚は、例えば、100〜200nmの範囲内に設定することができる。

【0011】

次に、LPCVDなどの方法にて上にハードマスク5を形成する。なお、ハードマスク5としては、例えば、TEOS膜を用いることができる。また、ハードマスク5の膜厚は、例えば、300nm程度に設定することができる。

【0012】

次に、図1(b)に示すように、フォトリソグラフィー技術およびドライエッチング技術を用いることにより、ハードマスク5、CMPストッパ膜4、浮遊ゲート電極膜3およびゲート絶縁膜2を貫通して半導体基板1内に達するトレンチ6を素子分離領域に形成する。この時、ハードマスク5は薄膜化され、CMPストッパ膜4上にハードマスク5が薄く残される。なお、このトレンチ6は、NANDメモリにおけるSTI(Shallow Trench Isolation)として用いることができる。また、トレンチ6の幅は10〜100nm程度の範囲内、トレンチ6の深さは200〜500nm程度の範囲内に設定することができる。

【0013】

次に、図1(c)に示すように、CVDなどの方法にてトレンチ6の側壁が覆われるようにしてハードマスク5上にライナー膜7を形成する。なお、ライナー膜7としては、例えば、TEOS膜またはHTO膜を用いることができ、アルカリ金属元素およびアルカリ土類金属元素を含有しないようにすることができる。また、ライナー膜7の膜厚は、1〜20nm程度の範囲内に設定することができる。また、ライナー膜7は省略するようにしてもよい。

【0014】

次に、図1(d)に示すように、塗布法などの方法にてトレンチ6内に埋め込まれるようにしてシリコン含有無機ポリマー膜8をライナー膜7上に形成する。この時、シリコン含有無機ポリマー膜8には、アルカリ金属元素またはアルカリ土類金属元素を含有させる。このアルカリ金属元素またはアルカリ土類金属元素は、K、Rb、Cs、MgおよびSrから選択されることが好ましく、特に、Csが最も好ましい。これらの元素は1種類だけ使用してもよいし、複数の元素を組み合わせて使用するようにしてもよい。また、このアルカリ金属元素またはアルカリ土類金属元素の濃度は、半導体基板1上に成膜した酸化物の表面濃度として、1010atoms/cm2以上に設定することが好ましい。

【0015】

また、シリコン含有無機ポリマー膜8は、Si−O結合またはSi−N結合を基本構造とする高分子から構成することができる。例えば、シリコン含有無機ポリマー膜8としては、例えば、ペルヒドロポリシラザン(PHPS)膜またはハイドロジェンシルセスキオキサン(HSQ)膜を用いることができる。

メチル基など有機物を官能基として有するシリコン含有ポリマー膜(有機SOG)をPHPS膜やHSQ膜の代わりに用いると、有機物が400℃から600℃程度の温度において分解を始めるので、これより高温の製造工程が入る部分には使用することが出来ない。特にSTIにおいては有機SOG中の炭素が固定電荷として働き、半導体デバイスの閾値に悪影響を及ぼす。それに対して、シリコン含有無機ポリマー膜(無機SOG)では、そのような影響を低減することが出来る。

また、有機SOGは電気的な耐圧が低く、5MV/cm程度である。10〜20MV/cm程度の高電界がかかるような箇所(例えば、NANDメモリのSTIなど)には有機SOGは使用できず、有機SOGよりも電気的な耐圧が高い無機SOGが使用される。

【0016】

ここで、シリコン含有無機ポリマー膜8にアルカリ金属元素またはアルカリ土類金属元素を含有させる方法としては、アルカリ金属元素またはアルカリ土類金属元素から構成される塩類をシリコン含有無機ポリマー溶液に添加してからライナー膜7上に塗布することができる。この時、シリコン含有無機ポリマー溶液中のアルカリ金属元素またはアルカリ土類金属元素の濃度は、Si基板上に成膜したときの表面濃度として1010atoms/cm2以上に設定することが好ましい。そして、シリコン含有無機ポリマー溶液を塗布した後、熱処理を行うことで溶媒を揮発させ、シリコン含有無機ポリマー膜8を形成することができる。なお、この熱処理は、例えば、ホットプレート上で80〜300℃程度の範囲内で数十秒間行うことができる。また、アルカリ金属元素またはアルカリ土類金属元素の添加剤としては、アルカリ金属元素またはアルカリ土類金属元素の硝酸塩、硫酸塩、炭酸塩、酸化物、塩化物、臭化物、弗化物、ヨウ化物、水酸化物などを挙げることができる。

【0017】

次に、図1(e)に示すように、水蒸気を含む雰囲気中でシリコン含有無機ポリマー膜8の酸化処理を行うことにより、シリコン含有無機ポリマー膜8をシリコン酸化膜9に変化させる。なお、酸化処理は、230℃以上かつ900℃以下の温度で行うことが好ましい。ここで、酸化処理の温度を230℃以上に設定することにより、シリコン酸化膜9を緻密化させることができる。このため、フッ酸などのエッチング液によるエッチング速度を遅くすることができ、所望の形状を得やすくすることができる。また、酸化処理の温度を900℃以下に設定することにより、半導体基板1の側壁の酸化を抑制することができ、半導体基板1の転移を抑制することができる。また、酸化炉内の雰囲気および温度を安定化させるために、酸化処理は、5分以上行うことが好ましい。ただし、過剰に長時間の酸化が行われると、半導体基板1の側壁が厚く酸化されるため、酸化処理に時間は、60分以下に設定することが好ましい。

【0018】

ここで、シリコン含有無機ポリマー膜8にアルカリ金属元素またはアルカリ土類金属元素を含有させることで、シリコン含有無機ポリマー膜8をシリコン酸化膜9に転換させる反応を促進させることができる。このため、シリコン含有無機ポリマー膜8の酸化処理の温度を低下させつつ、シリコン酸化膜9の元素濃度や密度などの膜質を二酸化ケイ素に近づけることができ、半導体基板1の転移を防止しつつ、トレンチ6でのシリコン酸化膜9の埋め込み性を確保するとともに、エッチング耐性を向上させることが可能となる。

【0019】

また、トレンチ6とシリコン酸化膜9との間にライナー膜7を設けることにより、シリコン含有無機ポリマー膜8にアルカリ金属元素またはアルカリ土類金属元素が含有されている場合においても、アルカリ金属元素またはアルカリ土類金属元素が半導体基板1およびゲート絶縁膜2に拡散するのを抑制することができる。このため、アルカリ金属元素またはアルカリ土類金属元素が半導体基板1およびゲート絶縁膜2で固定電荷として作用するのを抑制することができ、シリコン酸化膜9を用いたデバイスの信頼性の低下を抑制することができる。

【0020】

次に、図2(a)に示すように、CMPなどの方法にてCMPストッパ膜4が露出するまでシリコン酸化膜9、ライナー膜7およびハードマスク5を薄膜化することにより、トレンチ6の周辺のシリコン酸化膜9、ライナー膜7およびハードマスク5を除去する。

【0021】

なお、このCMPを行う前または後に不活性雰囲気中でシリコン酸化膜9の熱処理を行うようにしてもよい。この熱処理は、700℃以上かつ1100℃以下の温度で行うことが好ましい。ここで、熱処理の温度を700℃以上に設定することにより、シリコン酸化膜9を十分に緻密化させることができる。また、熱処理の温度を1100℃以下に設定することにより、デバイスによってはイオン注入で既に形成されたチャネル層の拡散深さが増大するのを抑制することができる。この熱処理によってシリコン酸化膜9から水分が除去され、シリコン酸化膜9を緻密化させることが可能となり、デバイスの電機特性を向上させることができる。

【0022】

次に、図2(b)に示すように、フッ化物を用いたドライエッチングまたは希フッ酸を用いたウェットエッチングにてシリコン酸化膜9およびライナー膜7の上部を除去することにより、CMPストッパ膜4に対して段差10を形成する。

【0023】

次に、図2(c)に示すように、リン酸溶液を用いたウェットエッチングにてCMPストッパ膜4を除去し、浮遊ゲート電極膜3を露出させる。

【0024】

次に、図2(d)に示すように、フッ化物を用いたドライエッチングまたは希フッ酸を用いたウェットエッチングにてシリコン酸化膜9およびライナー膜7の上部を除去することにより、浮遊ゲート電極膜3に対して段差11を形成する。この時、シリコン酸化膜9およびライナー膜7はゲート絶縁膜2上に突出させることが好ましい。

【0025】

ここで、アルカリ金属元素またはアルカリ土類金属元素をシリコン含有無機ポリマー膜8に含有させることにより、シリコン含有無機ポリマー膜8からシリコン酸化膜9への転換速度を向上させることができ、元素組成や密度などの膜質が二酸化ケイ素に近づく。そのため、シリコン酸化膜9のエッチング速度をライナー膜7のエッチング速度と同等にすることができる。このため、シリコン酸化膜9およびライナー膜7の上部を除去する際にライナー膜7に対してシリコン酸化膜9が過度にエッチングされるのを防止することができ、ライナー膜7とシリコン酸化膜9との高さを揃えることができる。なお、ライナー膜7とシリコン酸化膜9との高さの差は10nm以下にすることが好ましい。

【0026】

次に、図2(e)に示すように、CVDなどの方法にて段差11の側壁が覆われるようにして浮遊ゲート電極膜3、ライナー膜7およびシリコン酸化膜9上に電極間絶縁膜12を形成する。なお、電極間絶縁膜12としては、例えば、ONO(シリコン酸化膜/シリコン窒化膜/シリコン酸化膜)膜を用いることができる。また、電極間絶縁膜12の膜厚は、例えば、20nm程度に設定することができる。

【0027】

次に、CVDなどの方法にて電極間絶縁膜12上に制御ゲート電極膜13を形成する。なお、制御ゲート電極膜13としては、例えば、多結晶シリコン膜およびタングステン膜を用いることができる。また、制御ゲート電極膜12の膜厚は、例えば、50nm程度に設定することができる。

【0028】

図3は、実施形態に係る半導体装置に適用されるアルカリ金属元素およびアルカリ土類金属元素の活性化エネルギーを示す図である。なお、Ea(M+)およびEa(M0)はそれぞれ1価イオンおよび中性原子がシリコン格子中を移動する際の活性化エネルギー(計算値)である。また、活性化エネルギーEa(M+)、Ea(M0)それぞれについて、1.5eV以上の元素を薄いハッチ、2.0eV以上の元素を濃いハッチで示した。

図3において、アルカリ金属元素では、原子半径やイオン半径が大きくなるにしたがって活性化エネルギーEaが大きくなり、拡散するのに大きなエネルギーを必要とする。アルカリ土類金属元素に関しては、活性化エネルギーEa(M0)はアルカリ金属よりも全体的に大きいが、活性化エネルギーEa(M+)が小さい傾向にあることが分かる。

【0029】

図4(a)は、アルカリ金属元素およびアルカリ土類金属元素の1価イオンの活性化エネルギーと拡散係数との関係を示す図、図4(b)は、アルカリ金属元素およびアルカリ土類金属元素の中性原子の活性化エネルギーと拡散係数との関係を示す図である。なお、ここでは活性化エネルギーと、シリコン原子中およびシリコン酸化膜中の拡散係数(計算値)の関係を示した。

図4において、活性化エネルギーEa(M+)、Ea(M0)が小さくなるに従って、拡散係数が大きくなることが分かる。拡散しにくい元素は、活性化エネルギーEa(M+)、Ea(M0)がともに1.5eV以上、安全を見ると2.0eV以上である。活性化エネルギーEa(M+)、Ea(M0)の両者が1.5eV以上の元素はK、Rb、Cs、Mg、Srの5元素である。特に、CsはEa(M+)とEa(M0)両者共に2.5eV程度もあり、非常に拡散しにくい元素である。

【0030】

アルカリ金属元素やアルカリ土類金属元素は、ゾルゲル法などによるガラスの製造において、反応を促進させる触媒として利用されている。また、これらの元素は、ガラス転移温度を低下させて低温での流動性を高めることができる。これらの元素を、シリコン酸化物薄膜作成のための薬液に添加することで、薄膜形成を促進することが可能となるとともに、流動性を高めることができ、熱処理過程で生じるシリコン酸化膜9の収縮や応力が原因となって生じるSi基板の結晶転移を減少させることができる。

【0031】

また、アルカリ金属元素またはアルカリ土類金属元素を含む塗布液は酸化物へ転換する反応を促進させることができ、無機SOG膜の元素組成や密度などの膜質をCVD酸化膜の膜質に近づけることができる。このため、無機SOG膜をCVD酸化膜と同程度のエッチング速度にすることができ、ライナー膜7とシリコン酸化膜9との高さを揃えることができる。

【0032】

(第2実施形態)

図5(a)〜図5(e)は、第2実施形態に係る半導体装置の製造方法を示す断面図である。なお、第2実施形態では、半導体装置としてフィン型トランジスタを例にとる。

図5(a)において、CVDなどの方法にて半導体基板21上にCMPストッパ膜23を形成する。なお、半導体基板21上にCMPストッパ膜23を形成する前に、酸素雰囲気中で半導体基板21を熱処理することにより、半導体基板21上に酸化膜を形成するようにしてもよい。また、CMPストッパ膜23は、例えば、100〜200nm程度に設定することができる。

【0033】

そして、フォトリソグラフィー技術およびドライエッチング技術を用いてCMPストッパ膜23を貫通して半導体基板21内に達するトレンチを形成することにより、半導体基板21上にフィン22を形成する。なお、フィン22の高さは、100〜300nmの範囲内に設定することができる。フィン22の幅は、50nm以下に設定することができる。

【0034】

次に、図5(b)に示すように、CVDなどの方法にてフィン22およびCMPストッパ膜23が覆われるようにして半導体基板21上にライナー膜24を形成する。なお、ライナー膜24としては、例えば、TEOS膜またはHTO膜を用いることができ、アルカリ金属元素およびアルカリ土類金属元素を含有しないようにすることができる。また、ライナー膜24の膜厚は、2〜30nm程度の範囲内に設定することができる。また、ライナー膜24は省略してもよい。

【0035】

次に、塗布法などの方法にてフィン22の周囲が平坦化されるようにしてシリコン含有無機ポリマー膜25をライナー膜24上に形成する。この時、シリコン含有無機ポリマー膜24には、アルカリ金属元素またはアルカリ土類金属元素を含有させる。このシリコン含有無機ポリマー膜24は、シリコン含有無機ポリマー膜7と同様に構成することができる。

【0036】

次に、図5(c)に示すように、水蒸気を含む雰囲気中でシリコン含有無機ポリマー膜25の酸化処理を行うことにより、シリコン含有無機ポリマー膜25をシリコン酸化膜26に変化させる。この酸化処理は、図1(e)の酸化処理と同様に行うことができる。

【0037】

次に、図5(d)に示すように、CMPなどの方法にてCMPストッパ膜23が露出するまでシリコン酸化膜26およびライナー膜24を薄膜化することにより、フィン22上のシリコン酸化膜26およびライナー膜24を除去する。

【0038】

次に、図5(e)に示すように、フッ化物を用いたドライエッチングまたは希フッ酸を用いたウェットエッチングにてシリコン酸化膜26およびライナー膜24の上部を除去することにより、シリコン酸化膜26およびライナー膜24上にフィン22の一部を突出させる。そして、ゲート絶縁膜を介してフィン22の側壁にゲート電極を形成することにより、ダブルゲート型トランジスタを形成することができる。

【0039】

ここで、シリコン含有無機ポリマー膜25にアルカリ金属元素またはアルカリ土類金属元素を含有させることで、シリコン含有無機ポリマー膜25をシリコン酸化膜26に転換させる反応を促進させることができる。このため、シリコン含有無機ポリマー膜25の酸化処理の温度を低下させつつ、シリコン酸化膜26の元素濃度や密度などの膜質をライナー膜24に近づけることができ、半導体基板21の転移を防止しつつ、フィン22間でのシリコン酸化膜26の埋め込み性を確保するとともに、エッチング耐性を向上させることが可能となる。

【0040】

(第3実施形態)

図6(a)〜図6(e)は、第3実施形態に係る半導体装置の製造方法を示す断面図である。なお、第3実施形態では、半導体装置としてPMD(Pre Metal Dielectric)を例にとる。

図6(a)において、半導体基板31上にゲート絶縁膜34を介してゲート電極35を形成した後、ゲート電極35の両側に配置されるようにして半導体基板31に不純物拡散層32、33を形成する。次に、CVDなどの方法にて半導体基板31上に層間絶縁膜36を形成する。なお、層間絶縁膜36としては、シリコン酸化膜を用いることができる。

【0041】

次に、図6(b)に示すように、塗布法などの方法にてゲート電極35の周囲が平坦化されるようにしてシリコン含有無機ポリマー膜37を層間絶縁膜36上に形成する。この時、シリコン含有無機ポリマー膜37には、アルカリ金属元素またはアルカリ土類金属元素を含有させる。このシリコン含有無機ポリマー膜37は、シリコン含有無機ポリマー膜7と同様に構成することができる。

【0042】

次に、図6(c)に示すように、水蒸気を含む雰囲気中でシリコン含有無機ポリマー膜37の酸化処理を行うことにより、シリコン含有無機ポリマー膜37をシリコン酸化膜38に変化させる。この酸化処理は、図1(e)の酸化処理と同様に行うことができる。

【0043】

次に、CVDなどの方法にてシリコン酸化膜38上にCMPストッパ膜39を形成する。なお、CMPストッパ膜39としては、シリコン窒化膜を用いるようにしてもよいし、多結晶シリコン膜を用いるようにしてもよい。また、CMPストッパ膜39の膜厚は、例えば、100〜200nmの範囲内に設定することができる。

【0044】

次に、図6(d)に示すように、フォトリソグラフィー技術およびドライエッチング技術を用いることにより、不純物拡散層32、33を露出させる開口部40をCMPストッパ膜39、シリコン酸化膜38および層間絶縁膜36に形成する。

【0045】

次に、図6(e)に示すように、開口部40に埋め込まれるようにして不純物拡散層32、33に接続された配線41をCMPストッパ膜39上に形成する。そして、CVDなどの方法にて配線41上に層間絶縁膜42を形成する。なお、配線41としては、AlまたはCuなどの金属を用いることができる。層間絶縁膜42としては、シリコン酸化膜を用いることができる。

【0046】

ここで、シリコン含有無機ポリマー膜37にアルカリ金属元素またはアルカリ土類金属元素を含有させることで、シリコン含有無機ポリマー膜37をシリコン酸化膜38に転換させる反応を促進させることができる。このため、シリコン含有無機ポリマー膜37の酸化処理の温度を低下させつつ、シリコン酸化膜38の元素濃度や密度などの膜質を二酸化ケイ素に近づけることができ、半導体基板31の転移を防止しつつ、シリコン酸化膜38のエッチング耐性を向上させることが可能となる。

【0047】

(第4実施形態)

図7(a)〜図7(c)は、第4実施形態に係る半導体装置の製造方法を示す断面図である。なお、第4実施形態では、半導体装置としてIMD(Inter Metal Dielectric)を例にとる。

図7(a)において、層間絶縁膜51に配線52を埋め込んだ後、CVDなどの方法にて層間絶縁膜51上に保護膜53を形成する。なお、層間絶縁膜51としては、シリコン酸化膜を用いることができる。保護膜53としては、シリコン窒化膜を用いることができる。次に、塗布法などの方法にてシリコン含有無機ポリマー膜54を保護膜53上に形成する。この時、シリコン含有無機ポリマー膜54には、アルカリ金属元素またはアルカリ土類金属元素を含有させる。このシリコン含有無機ポリマー膜54は、シリコン含有無機ポリマー膜7と同様に構成することができる。

【0048】

次に、図7(b)に示すように、水蒸気を含む雰囲気中でシリコン含有無機ポリマー膜54の酸化処理を行うことにより、シリコン含有無機ポリマー膜54をシリコン酸化膜55に変化させる。この酸化処理は、図1(e)の酸化処理と同様に行うことができる。そして、フォトリソグラフィー技術およびドライエッチング技術を用いることにより、配線52を露出させる開口部56をシリコン酸化膜55および保護膜53に形成する。

【0049】

次に、図7(c)に示すように、配線52に接続された配線57を開口部56に埋め込む。

【0050】

ここで、シリコン含有無機ポリマー膜54にアルカリ金属元素またはアルカリ土類金属元素を含有させることで、シリコン含有無機ポリマー膜54をシリコン酸化膜55に転換させる反応を促進させることができ、シリコン酸化膜55のエッチング耐性を向上させることが可能となる。

【0051】

本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

【符号の説明】

【0052】

1、21、31 半導体基板、2、34 ゲート絶縁膜、3 浮遊ゲート電極膜、4、23、39 CMPストッパ膜、5 ハードマスク、6 トレンチ、7、24 ライナー膜、8、25、37、54 シリコン含有無機ポリマー膜、9、26、38、55 シリコン酸化膜、10、11 段差、12 電極間絶縁膜、13 制御ゲート電極膜、22 フィン、32、33 不純物拡散層、35 ゲート電極、36、42、51 層間絶縁膜、40、56 開口部、41、52、57 配線、53 保護膜

【特許請求の範囲】

【請求項1】

半導体基板と、

前記半導体基板の素子分離領域に形成されたトレンチと、

前記トレンチに埋め込まれ、アルカリ金属元素またはアルカリ土類金属元素を含有するシリコン酸化膜とを備えることを特徴とする半導体装置。

【請求項2】

前記トレンチと前記シリコン酸化膜との間に形成され、アルカリ金属元素およびアルカリ土類金属元素を含有しないライナー膜をさらに備えることを特徴とする請求項1に記載の半導体装置。

【請求項3】

前記アルカリ金属元素またはアルカリ土類金属元素は、K、Rb、Cs、MgおよびSrから選択されることを特徴とする請求項1または2に記載の半導体装置。

【請求項4】

半導体基板にトレンチを形成する工程と、

アルカリ金属元素またはアルカリ土類金属元素を含有するシリコン含有無機ポリマー膜を前記トレンチに埋め込む工程と、

前記シリコン含有無機ポリマー膜の熱処理にて前記シリコン含有無機ポリマー膜をシリコン酸化膜に変化させる工程とを備えることを特徴とする半導体装置の製造方法。

【請求項5】

前記シリコン含有無機ポリマー膜は、Si−O結合またはSi−N結合を基本構造とする高分子からなることを特徴とする請求項4に記載の半導体装置の製造方法。

【請求項1】

半導体基板と、

前記半導体基板の素子分離領域に形成されたトレンチと、

前記トレンチに埋め込まれ、アルカリ金属元素またはアルカリ土類金属元素を含有するシリコン酸化膜とを備えることを特徴とする半導体装置。

【請求項2】

前記トレンチと前記シリコン酸化膜との間に形成され、アルカリ金属元素およびアルカリ土類金属元素を含有しないライナー膜をさらに備えることを特徴とする請求項1に記載の半導体装置。

【請求項3】

前記アルカリ金属元素またはアルカリ土類金属元素は、K、Rb、Cs、MgおよびSrから選択されることを特徴とする請求項1または2に記載の半導体装置。

【請求項4】

半導体基板にトレンチを形成する工程と、

アルカリ金属元素またはアルカリ土類金属元素を含有するシリコン含有無機ポリマー膜を前記トレンチに埋め込む工程と、

前記シリコン含有無機ポリマー膜の熱処理にて前記シリコン含有無機ポリマー膜をシリコン酸化膜に変化させる工程とを備えることを特徴とする半導体装置の製造方法。

【請求項5】

前記シリコン含有無機ポリマー膜は、Si−O結合またはSi−N結合を基本構造とする高分子からなることを特徴とする請求項4に記載の半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【公開番号】特開2012−235059(P2012−235059A)

【公開日】平成24年11月29日(2012.11.29)

【国際特許分類】

【出願番号】特願2011−104407(P2011−104407)

【出願日】平成23年5月9日(2011.5.9)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

【公開日】平成24年11月29日(2012.11.29)

【国際特許分類】

【出願日】平成23年5月9日(2011.5.9)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

[ Back to top ]