半導体装置および半導体装置の製造方法

【課題】本発明は、半導体装置の小型化に対応できる半導体装置を提供する。

【解決手段】一面から他面11bに貫通して設けられた開口部12と、外部電極28に接続された配線19と、一端が配線19に接続されて他端が開口部12内に露出されたインナーリード7とを有する基板17と、基板17の一面に搭載された半導体チップ16とを備え、半導体チップ16が、開口部12から露出するように配置された同電位の2以上の電極パッド5を含む電極パッド群15を有し、同電位の2以上の電極パッド5が、インナーリード7の1つと接続されている半導体装置10とする。

【解決手段】一面から他面11bに貫通して設けられた開口部12と、外部電極28に接続された配線19と、一端が配線19に接続されて他端が開口部12内に露出されたインナーリード7とを有する基板17と、基板17の一面に搭載された半導体チップ16とを備え、半導体チップ16が、開口部12から露出するように配置された同電位の2以上の電極パッド5を含む電極パッド群15を有し、同電位の2以上の電極パッド5が、インナーリード7の1つと接続されている半導体装置10とする。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置および半導体装置の製造方法に関する。

【背景技術】

【0002】

従来の半導体装置の一例として、例えば、BGA(Ball Grid Array)型やCSP(Chip Size Package)型などの半導体パッケージがある。このような半導体パッケージは、基板上に半導体チップを実装し、この半導体チップと基板との間をワイヤーボンディング等で接続した構造を有している。

【0003】

BGA型の半導体装置としては、半導体チップがチップパッドを有し、パッケージ基板がチップパッドを外方に臨ませる開口部を有し、パッケージ基板に配置されたパッケージ配線の一端にボンディングパッドが設けられ、他端に半田ボールが設けられ、チップパッドとボンディングパッドとが、ボンディングワイヤーを介して電気的に接続されているものがある(例えば、特許文献1参照)。

【0004】

また、従来の半導体装置として、例えば、特許文献2には、半導体ペレットの一主面には複数個の電極パッドが整列されているとともに、この電極パッド群列から離間した位置にも電極パッドが配置されており、TABテープのテープ本体にはメインボンディングホールが開設されているとともに、このメインボンディングホールの脇にはサブボンディングホールが開設されており、前記テープ本体に敷設された複数本のインナリードの先端部が前記メインボンディングホールおよび前記サブボンディングホールにおいて前記電極パッドのそれぞれにギャングボンディングされているものが記載されている。

【0005】

また、従来の半導体装置として、例えば、特許文献3には、TABを用いて積層された半導体チップからなり、半導体チップと電気的に接続されたTABの複数のフィルムリードがリードフレームの接続パッド上に並列に接続されている半導体集積回路装置が記載されている。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2008−198841号公報

【特許文献2】特開2003−059980号公報

【特許文献3】特開平06−268152号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

しかしながら、従来の半導体装置では、パッケージ基板上でのパッケージ配線の引き回しが困難となったり、遠回りの配線となったりしてしまう場合があり、広い配線スペースを確保しなければならず、半導体装置の小型化に対応しにくかった。

具体的には、例えば、特許文献1に記載の技術では、半田ボール数の制約に加え、パッケージ配線を構成する配線層が1層のみであることにより、半田ボール間に配置されるパッケージ配線数が制約されるため、パッケージ基板上でのパッケージ配線の引き回しが困難となったり、遠回りの配線となったりしやすく、問題となっていた。

【課題を解決するための手段】

【0008】

本発明者は、上記課題を解決するために鋭意検討を重ねた。

その結果、一端が配線に接続されて他端が開口部内に露出されたインナーリードを有する基板を備え、開口部から露出するように配置された半導体チップの複数の電極パッドのうち、同電位の2以上の電極パッドがインナーリードの1つと接続されているものとすることで、電極パッドの数に対する基板に配置された配線の数を少なくすることができ、基板上での配線の配置の自由度を向上させることが可能となり、半導体装置の小型化に適した半導体装置が得られることを見出し、本発明の半導体装置および半導体装置の製造方法を想到した。

【0009】

本発明の半導体装置は、一面から他面に貫通して設けられた開口部と、外部電極に接続された配線と、一端が前記配線に接続されて他端が前記開口部内に露出されたインナーリードとを有する基板と、前記基板の一面に搭載された半導体チップとを備え、前記半導体チップが、前記開口部から露出するように配置された同電位の2以上の電極パッドを含む電極パッド群を有し、前記同電位の2以上の電極パッドが、前記インナーリードの1つと接続されていることを特徴とする。

【発明の効果】

【0010】

本発明の半導体装置は、一面から他面に貫通して設けられた開口部と、外部電極に接続された配線と、一端が前記配線に接続されて他端が前記開口部内に露出されたインナーリードとを有する基板と、前記基板の一面に搭載された半導体チップとを備え、前記半導体チップが、前記開口部から露出するように配置された同電位の2以上の電極パッドを含む電極パッド群を有し、前記同電位の2以上の電極パッドが、前記インナーリードの1つと接続されているものであるので、電極パッドの数に対する基板に配置された配線の数を少なくすることができる。その結果、基板上での配線の配置の自由度を向上させることができ、半導体装置の小型化に適したものとなる。

【図面の簡単な説明】

【0011】

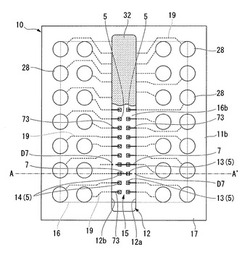

【図1】図1は、本発明の半導体装置の一例である第1の実施形態の半導体装置を説明するための図であり、半導体装置を下面側から見た平面図である。

【図2】図2は、本発明の半導体装置の一例である第1の実施形態の半導体装置を説明するための図であり、図1のA−A’線に対応する断面図である。

【図3A】図3Aは、本発明の半導体装置の製造方法の一例として第1の実施形態の半導体装置の製造方法を説明するための図であり、図1のA−A’線に対応する断面図である。

【図3B】図3Bは、本発明の半導体装置の製造方法の一例として第1の実施形態の半導体装置の製造方法を説明するための図であり、図1のA−A’線に対応する断面図である。

【図3C】図3Cは、本発明の半導体装置の製造方法の一例として第1の実施形態の半導体装置の製造方法を説明するための図であり、図1のA−A’線に対応する断面図である。

【図3D】図3Dは、本発明の半導体装置の製造方法の一例として第1の実施形態の半導体装置の製造方法を説明するための図であり、図1のA−A’線に対応する断面図である。

【図3E】図3Eは、本発明の半導体装置の製造方法の一例として第1の実施形態の半導体装置の製造方法を説明するための図であり、図1のA−A’線に対応する断面図である。

【図3F】図3Fは、本発明の半導体装置の製造方法の一例として第1の実施形態の半導体装置の製造方法を説明するための図であり、図1のA−A’線に対応する断面図である。

【図4A】図4Aは、図3Cに示される工程を説明するための図であり、図1のA−A’線に対応する断面図である。

【図4B】図4Bは、図3Cに示される工程を説明するための図であり、図1のA−A’線に対応する断面図である。

【図4C】図4Cは、図3Cに示される工程を説明するための図であり、図1のA−A’線に対応する断面図である。

【図5】図5は、本発明の半導体装置の他の例である第2の実施形態の半導体装置を説明するための図であり、半導体装置の一部を下面側から見た拡大平面図である。

【図6】図6は、本発明の半導体装置の他の例である第3の実施形態の半導体装置を説明するための図であり、半導体装置の一部を下面側から見た拡大平面図である。

【図7】図7は、本発明の半導体装置の他の例である第4の実施形態の半導体装置を説明するための図であり、半導体装置の一部を下面側から見た拡大平面図である。

【発明を実施するための形態】

【0012】

以下、図面を参照して本発明を適用した実施形態について詳細に説明する。尚、本発明

は以下の実施形態に限定されるものではなく、以下の説明で用いる図面は、本発明の実施

形態の構成を説明するためのものであり、図示される各部の大きさや厚さや寸法等は、実

際の半導体装置の寸法関係とは異なる場合がある。

【0013】

(第1の実施形態)

図1および図2は、本発明の半導体装置の一例である第1の実施形態の半導体装置を説明するための図である。図1は、半導体装置を下面側から見た平面図であり、図2は、図1のA−A’線に対応する断面図である。

本実施形態の半導体装置10は、BGA型の半導体装置であり、図2に示すように、配線基板17(基板)と半導体チップ16とを備えている。

【0014】

配線基板17は、例えば、フィルム状の平面視略矩形のポリイミド基材からなる絶縁基板11を備えたフレキシブル配線基板である。なお、絶縁基板11は、ポリイミド基材からなるものに限定されず、例えば、ガラスエポキシ基板などであってもよい。

絶縁基板11の半導体チップ16側の面(図2においては上面)には、Cu等の導電材料からなる複数の配線19が所定の形状で形成されている。

【0015】

また、配線基板17は、開口部12により開口部12の第1側壁12a側と第2側壁12b側の2つの領域に区画されている。配線基板17の他面11b(図2においては下面)の第1側壁12a側と第2側壁12b側のそれぞれの領域には、図1に示すように、所定の間隔で、外部電極である半田ボール28が格子状に配置されている。半田ボール28は、図2に示すように、各配線19の一端が絶縁基板11に形成された孔部により配線基板17の他面11bに露出されてなるランド(外部接続端子)29に電気的に接続されている。このことにより、各配線19と半田ボール28とが電気的に接続されている。

【0016】

また、配線基板17は、図1および図2に示すように、一面11aから他面11bに貫通して設けられた平面視略矩形の開口部12を有している。開口部12は、平面視で配線基板17の中央部に設けられ、第1側壁12aと第1側壁12aに対向する第2側壁12bとを有している。

【0017】

また、配線基板17は、複数の複接続インナーリード7(インナーリード)と、複数の単接続インナーリード73と、複数のダミーリードD7とを有するインナーリードを有している。複接続インナーリード7および単接続インナーリード73は、Au、Cu等の導電材料からなる平面視直線状のものであり、一端が配線19に接続されて他端が開口部12内に露出されているものである。各ダミーリードD7は、複接続インナーリード7と同じ導電材料からなる平面視直線状のものであり、他の導電部材と絶縁されている。また、各ダミーリードD7は、図1および図2に示すように、それぞれ開口部12内において複接続インナーリード7に対向して配置され、複接続インナーリード7と同じ層に配線19の延在方向に沿って形成されている。

本実施形態においては、図1に示すように、開口部12内に露出されている複接続インナーリード7に、後述する同電位の2以上の電極パッド5が接続され、開口部12内に露出されている単接続インナーリード73に、1つの電極パッド5が接続されている。

【0018】

また、図2に示すように、配線基板17の一面11aには、DAF(Die Attached Film)、或いはエラストマ(弾性体)等からなる接着部材31を介して、半導体チップ16が搭載されている。接着部材31は、配線基板17の配線19の形成されている領域を覆い、開口部12を除く領域に設けられている。

半導体チップ16は、略矩形の板状であり、半導体チップ16の図1および図2における下面16b(一面)には、例えばメモリ回路(不図示)と、半導体チップ16を外部と電気的に接続するための複数の電極パッド5からなる電極パッド群15とが形成されている。

半導体チップ16の下面16bにおいて、電極パッド群15を構成する電極パッド5の形成されている領域を除く領域には、図示しないパッシベーション膜が形成されており、メモリ回路の形成された面が保護されている。

【0019】

図1および図2に示すように、半導体チップ16は、電極パッド群15の設けられている側(下面16b側)を配線基板17に向けて配置されている。また、半導体チップ16は、図1および図2に示すように、配線基板17の開口部12から電極パッド群15が露出するように、配置されている。本実施形態においては、電極パッド群15は、図1および図2に示すように、半導体チップ16の中央部に2列に並んで配置された複数の電極パッド5からなるものとされている。

【0020】

より詳細には、図1に示すように、電極パッド群15は、開口部12の第1側壁12aに沿って第1側壁12aに近接して配置された複数の第1電極パッド5からなる第1電極パッド13の列と、第2側壁12bに沿って第2側壁12bに近接して配置された複数の第1電極パッド5からなる第2電極パッド14の列の2列からなるものとされている。

また、図1および図2に示す半導体装置10では、電極パッド群15が、同電位の2以上の電極パッド5を含むものとされている。なお、電極パッド群15に含まれる電極パッド5のうち、同電位である電極パッド5の数は、2以上であればよく、特に限定されない。

【0021】

本実施形態においては、図1および図2に示すように、同電位の2つの電極パッド5である図1において下から3つめに配置された第1電極パッド13と、その第1電極パッド13に隣接して配置された第2電極パッド14とが、複接続インナーリード7の1つと接続されている。また、同電位の2つの電極パッド5である図1において下から4つめに配置された第1電極パッド13と、その第1電極パッド13に隣接して配置された第2電極パッド14とが、複接続インナーリード7の1つと接続されている。

【0022】

図1および図2に示す半導体装置10において、各複接続インナーリード7に接続されている同電位の第1電極パッド13および第2電極パッド14は、電源またはグランドとされている。なお、複接続インナーリード7によって接続されている電極パッド5は、電源またはグランドとされていることが好ましいが、複接続インナーリード7によって接続できるように同電位とされていればよく、電源またはグランドでなくてもよい。

【0023】

また、図1に示すように、複接続インナーリード7の端部に配置された電極パッド5は、複接続インナーリード7に接続された他の電極パッド5と比較して、複接続インナーリード7に接続された配線19との距離が遠いものとなっている。

例えば、図1において下から3つめに配置された第1電極パッド13は、図1において下から3つめに配置された第2電極パッド14と比較して、複接続インナーリード7に接続された配線19との距離が遠いものとなっている。

また、図1において下から4つめに配置された第2電極パッド14は、図1において下から4つめに配置された第1電極パッド13と比較して、複接続インナーリード7に接続された配線19との距離が遠いものとなっている。

【0024】

また、図1に示す電極パッド5のうち、複接続インナーリード7に接続されていない電極パッド5は、それぞれ最も距離の近い対応する単接続インナーリード73に電気的に接続されている。

そして、図1および図2に示すように、複接続インナーリード7および単接続インナーリード73と、電極パッド5とが接続されていることにより、配線基板17に設けられた半田ボール28と半導体チップ16とが電気的に接続されている。

【0025】

また、図1および図2に示す半導体装置10では、開口部12内および開口部12近傍に封止樹脂からなる封止体32が形成されることにより、複接続インナーリード7および単接続インナーリード73が、封止樹脂に封止されている。このことにより、図1および図2に示す半導体装置10では、複接続インナーリード7および単接続インナーリード73を用いた半導体チップ16と配線基板17との接続部位が、外界から保護されるようになっている。

【0026】

また、半導体チップ16の配線基板17と対向していない領域は、封止樹脂からなる封止体33によって被覆されている。図1および図2に示す半導体装置10では、封止体33が形成されていることにより、半導体チップ16が外界から保護されるようになっている。

なお、封止体32、33に用いられる封止樹脂としては、例えばエポキシ樹脂等の熱硬化性樹脂などを用いることができる。

【0027】

「製造方法」

図3A〜図3Fは、本発明の半導体装置の製造方法の一例として第1の実施形態の半導体装置の製造方法を説明するための図であり、図1のA−A’線に対応する断面図である。また、図4A〜図4Cは、図3Cに示される工程を説明するための図であり、図1のA−A’線に対応する断面図である。なお、図3A〜図3Fおよび図4A〜図4Cにおいて、第1の実施の形態の半導体装置10と同一構成部分には同一の符号を付す。

【0028】

図1および図2に示す半導体装置10を製造するには、まず、配線基板17となる基板を用意し、図3Aに示すように、マトリクス状に配置された各製品形成部43に一面11aから他面11bに貫通して設けられた開口部12と、それぞれ1つの外部電極(図1および図2に示す半田ボール28)に接続される複数の配線19と、一端が配線19に接続されて他端が絶縁され、後の工程で切断されることにより複接続インナーリード7とダミーリードD7とに分離される複数のインナーリード材料A7と、後の工程で切断されることにより、一端が配線19に接続されて他端が開口部12内に露出された2つの単接続インナーリード73(図3Aには不図示、図1参照)に分離される複数のリード材料(不図示)とを有する配線母基板41(配線基板17)を形成する。

【0029】

本実施形態において用いられる配線母基板41は、MAP(Mold Array Process)方式で処理されるものであり、複数の製品形成部43がマトリクス状に配置されている。配線母基板41のそれぞれの製品形成部43には、図3Aに示すように接着部材31が搭載されている。

なお、各製品形成部43は、その後の工程で配線母基板41を切断分離することにより、図1および図2に示す半導体装置10の配線基板17となる部位である。したがって、配線母基板41の隣接する製品形成部43間には、ダイシングラインが配置されている。

【0030】

また、図3Aに示すように、インナーリード材料A7と単接続インナーリード73となるリード材料とは、両端部が配線基板17と一体化された所定の形状で、配線母基板41の製品形成部43にそれぞれ設けられた開口部12内に跨って延在するように形成されている。

また、本実施形態では、配線母基板41(配線基板17)を形成する工程において、図3Aに示すように、配線母基板41(配線基板17)に、各配線19の一端が絶縁基板11に形成された孔部により他面11bに露出されてなるランド29を形成する。

【0031】

次に、図3Bに示すように、配線母基板41の製品形成部43のそれぞれ(配線基板17)の一面11aに、同電位の2以上の電極パッド5を含む電極パッド群15(図1参照)を有する半導体チップ16を搭載し、電極パッド群15が開口部12から露出するように配置する。半導体チップ16は、DAFなどの接着部材31を介して、半導体チップ16の電極パッド群15を配線基板17側に向けて接着固定する。

【0032】

なお、図3Bには、複数の第1電極パッド5のうち、図1のA−A’線に対応する断面に配置された第1電極パッド13と第2電極パッド14が記載されている。配線母基板41に半導体チップ16が搭載されることにより、開口部12内において、各インナーリード材料A7(複接続インナーリード7)、および各単接続インナーリード73となるリード材料が、それぞれ接続される電極パッド5に対向配置される。

【0033】

次に、図3Cに示すように、インナーリード材料A7(複接続インナーリード7)および単接続インナーリード73となるリード材料と、電極パッド5とを接続する。この時、同電位の2以上の電極パッド5を、複接続インナーリード7(インナーリード)の一つと接続する(接続工程)。

本実施形態では、図4Aに示すように、接続工程を行う前に、開口部12内で、インナーリード材料A7(複接続インナーリード7)、および単接続インナーリード73となるリード材料を切断する。このことによりインナーリード材料A7は、複接続インナーリード7とダミーリードD7とに分離され、リード材料は、2つの単接続インナーリード73に分離される。

【0034】

インナーリード材料A7および単接続インナーリード73となるリード材料を切断する方法としては、例えば、図4Aおよび図4Bに示すように、インナーリードボンディング装置のボンディングツール70を用いて電極パッド5に接続する前に、ボンディングツール70を用いてインナーリード材料A7または単接続インナーリード73となるリード材料を切断する方法を用いることができる。この場合、インナーリード材料A7または単接続インナーリード73となるリード材料を切断した後、複接続インナーリード7または単接続インナーリード73を電極パッド5に接続する作業をスムーズに行うことができ、効率よく製造でき、好ましい。

また、インナーリード材料A7(複接続インナーリード7)および単接続インナーリード73となるリード材料の予め決められた位置には、接続工程を行う前に、例えばノッチ部などの図示しない切断容易部を設けることが好ましい。この場合、インナーリード材料A7および単接続インナーリード73となるリード材料を切断する際に、所定の位置で容易に効率よく高精度で切断できる。

【0035】

次に、接続工程を行う。接続工程は、図3Cに示すように、半導体チップ16の配線基板17側の面が上側になるように配置して行うことが好ましい。また、接続工程において、電極パッド5と、複接続インナーリード7または単接続インナーリード73とを接続する方法としては、例えば、図4A〜図4Cに示すインナーリードボンディング装置のボンディングツール70を用いて、超音波熱圧着する方法などを用いることができる。

【0036】

ここでは、まず、図1において下から3つめに配置された第1電極パッド13および第2電極パッド14と複接続インナーリード7との接続について説明する。なお、図1において下から4つめに配置された第1電極パッド13および第2電極パッド14と複接続インナーリード7との接続については、第1電極パッド13と複接続インナーリード7との接続と、第2電極パッド14と複接続インナーリード7との接続とを反対の順番で行うこと以外は同じであるので、説明を省略する。

【0037】

図1において下から3つめに配置された第1電極パッド13および第2電極パッド14と複接続インナーリード7とを接続する接続工程においては、同電位の2以上の電極パッド5(第1電極パッド13および第2電極パッド14)のうち、複接続インナーリード7に接続された配線19との距離が最も遠い電極パッド5(図3Cにおいては第1電極パッド13)が複接続インナーリード7の端部に配置されるように接続する。

【0038】

また、本実施形態の接続工程においては、図4Bおよび図4Cに示すように、同電位の2以上の電極パッド5のうち、複接続インナーリード7に接続された配線19との距離が近い電極パッド5(図3Cにおいては第2電極パッド14)から順に複接続インナーリード7に接続する。

具体的には、まず、図4Bに示すように、複接続インナーリード7と第2電極パッド14とを電気的に接続する。すなわち、電極パッド5に接続する複接続インナーリード7の切断に用いた図4Aに示すボンディングツール70を、図4Bに示すように、第2電極パッド14上の位置に移動させ、複接続インナーリード7のボンディング部位を第2の電極パッド14に超音波熱圧着により接続する。

【0039】

次に、図4Bに示すボンディングツール70を、図4Cに示すように、第1電極パッド13と第2電極パッド14のうち、配線19との距離(図1参照)が遠い第1電極パッド13上の位置に移動し、第1電極パッド13に、複接続インナーリード7の切断端部であるボンディング部位を超音波熱圧着により接続する。

このことにより、本実施形態においては、図1および図4Cに示すように、同電位の第1電極パッド13と第2電極パッド14のうち、配線19との距離が遠い電極パッド5である第1電極パッド13が複接続インナーリード7の端部に配置される。

【0040】

次に、複接続インナーリード7に接続されていない電極パッド5と単接続インナーリード73との接続について説明する。複接続インナーリード7に接続されていない電極パッド5と単接続インナーリード73とを接続する際には、単接続インナーリード73の切断に用いたボンディングツール70を、接続する電極パッド5上の位置に移動し、同電位の2以上の電極パッド5のうち、配線19との距離最もが遠い電極パッド5と複接続インナーリード7との接続と同様に、電極パッド5に、単接続インナーリード73の切断端部であるボンディング部位を超音波熱圧着により接続する。

【0041】

続いて、図3Dに示すように、開口部12内および開口部12近傍に封止樹脂からなる封止体32を形成して、複接続インナーリード7および単接続インナーリード73を封止するとともに、半導体チップ16の配線基板17と対向していない領域を覆うように、封止樹脂からなる封止体33を形成する。

封止体32および封止体33を形成する方法としては、特に限定されないが、例えば、以下に示す方法を用いることが好ましい。

【0042】

まず、トランスファーモールド装置の上型と下型からなる成型金型を用意し、配線母基板41を型閉めする。この時、製品形成領域43に形成された開口部12の長辺が、封止樹脂の注入方向に沿って配置されるように、配線母基板41を成型金型のキャビティ内に配置することが好ましい。このことにより、複接続インナーリード7および単接続インナーリード73が、成型金型内における封止樹脂の流動に支障を来たすことを防止でき、成型金型内における封止樹脂の流動をスムーズにすることができる。

【0043】

次に、成型金型に設けられているゲートから、成型金型のキャビティ内に溶融された封止樹脂を注入し、キャビティ内を封止樹脂で充填する。次いで、例えば180℃程度の所定温度で熱処理(キュア)することにより、封止樹脂を硬化させる。その後、成型金型から配線母基板41を取り出すことにより、図3Dに示すように封止体32および封止体33によって一括的に覆われた配線母基板41が得られる。

【0044】

その後、図3Eに示すように、各配線19の一端が露出されてなるランド29に電気的に接続された半田ボール28を形成する。半田ボール28を形成する際には、例えば、ランド29の配置に合わせて複数の吸着孔が形成されたボールマウントツールを用いる方法を用いることが好ましい。具体的には、ボールマウントツールの吸着孔に半田ボール28を保持し、保持された半田ボール28にフラックスを転写形成し、ランド29に一括搭載した後、所定温度でリフローすることにより、半田ボール28を固着する方法を用いることができる。

【0045】

その後、配線母基板41をダイシングブレードにより縦横のダイシングラインで切断し、製品形成部43毎に切断分離することで、各配線基板17に分断され、図1及び図2に示す半導体装置10が得られる。

なお、配線母基板41を切断する際には、図3Fに示すように、半導体チップ16を覆う封止体33にダイシングテープ48を接着し、ダイシングテープ48によって配線母基板41を支持させて切断することが好ましい。

【0046】

本実施形態の半導体装置10は、一面11aから他面11bに貫通して設けられた開口部12と、半田ボール28に接続された配線と、一端が配線19に接続されて他端が開口部12内に露出された複接続インナーリード7とを有する配線基板17と、配線基板17の一面に搭載され、開口部12から露出するように配置された同電位の2以上の電極パッド5を含む電極パッド群15を有する半導体チップ16とを備え、同電位の2以上の電極パッド5が、複接続インナーリード7の1つと接続されているものであるので、電極パッド5の数に対する配線基板17に配置された配線19の数を少なくすることができる。その結果、配線基板17上の配線スペースを確保することができ、配線基板17上での配線19の配置の自由度を向上させることができ、半導体装置10の小型化に適したものとなる。

【0047】

また、本実施形態の半導体装置10では、複接続インナーリード7の端部に配置された電極パッド5が、複接続インナーリード7に接続された他の電極パッド5と比較して、複接続インナーリード7に接続された配線19との距離が遠いものとなっているので、複接続インナーリード7の端部に接続された電極パッド5が、複接続インナーリード7に接続された他の電極パッドと比較して、配線19との距離が近い場合と比較して、複接続インナーリード7の長さを短くすることができ、複接続インナーリード7を配置するのに必要な平面積が少なくて済むとともに、容易に製造できる。

【0048】

また、本実施形態の半導体装置10は、配線基板17の配線19が、一層配線であるので、配線19が多層配線である場合と比較して、容易に製造でき、半導体装置10の生産性を向上させることができるとともに、コストを低減することができる。

【0049】

また、本実施形態の半導体装置10は、開口部12が、第1側壁12aと第1側壁12aに対向する第2側壁12bとを有し、電極パッド群15が、第1側壁12aに沿って第1側壁に近接して配置された複数の第1電極パッド13と、第2側壁12aに沿って第2側壁12aに近接して配置された複数の第2電極パッド14とを有し、同電位の2以上の電極パッド5が、隣接する第1電極パッド13と第2電極パッド14とを含むものであり、複接続インナーリード7が平面視直線状であるので、複接続インナーリード7を配置するのに必要な平面積が少なくて済み、小型化に適したものとなるとともに、複接続インナーリード7と第1電極パッド13および第2電極パッド14との接続が容易で生産性に優れたものとなる。

【0050】

また、本実施形態の半導体装置10は、同電位の2以上の電極パッド5が、電源またはグランドとされているので、例えば、同電位の2以上の電極パッド5が、電源またはグランドでない場合と比較して、容易に同電位の2以上の電極パッド5を設けることができる。

また、本実施形態の半導体装置10では、配線19の一端が、配線基板17の他面11bに露出されているので、容易にランド29を形成することができ、ランド29に半田ボール28を形成することで、配線19と半田ボール28とを容易に接続できる。

【0051】

また、本実施形態の半導体装置10の製造方法では、複接続インナーリード7の一つと、同電位の2以上の電極パッド5とを接続する接続工程とを備えているので、電極パッド5の数に対する配線19の数を少なくすることができ、配線基板17上での配線19の配置の自由度を向上させることができる。

【0052】

また、本実施形態の半導体装置10の製造方法は、配線基板17を形成する工程において、開口部12内に跨って延在する複接続インナーリード7およびダミーリードD7となるインナーリード材料A7と、単接続インナーリード73となるリード材料とを形成し、接続工程を行う前に、開口部12内でインナーリード材料A7および単接続インナーリード73となるリード材料を切断する工程を含む方法であるので、半導体チップ16を搭載する際に、インナーリード材料A7(複接続インナーリード7)および単接続インナーリード73となるリード材料が補強材として機能するため、半導体チップ16を所定の位置に容易に高精度で搭載できるとともに、半導体チップ16を搭載する際の作業性を向上させることができる。

【0053】

また、本実施形態の半導体装置10の製造方法は、接続工程において、同電位の2以上の電極パッド5のうち、複接続インナーリード7に接続された配線19との距離が近い電極パッド5から順に複接続インナーリード7に接続する方法であるので、複接続インナーリード7に接続された配線19との距離が遠い電極パッド5から順に複接続インナーリード7に接続する場合と比較して、接続不良等が生じにくく、効率よく高精度で同電位の2以上の電極パッド5を複接続インナーリード7に接続できる。

【0054】

また、本実施形態の半導体装置10の製造方法では、配線母基板41を用い、半田ボール28を形成するまでの各工程を行った後、製品形成領域43毎に個片化するので、図1及び図2に示す半導体装置を個々に製造する場合と比較して、効率良く製造できる。

【0055】

(第2の実施形態)

図1および図2に示す第1実施形態においては、第1電極パッド13と第2電極パッド14とを含む同電位の2つの電極パッド5が、複接続インナーリード7の1つと接続されている場合を例に挙げて説明したが、本発明においては、例えば、同電位である3以上の電極パッドが、複接続インナーリードの1つと接続されていてもよい。

【0056】

図5は、本発明の半導体装置の他の例である第2の実施形態の半導体装置を説明するための図であり、半導体装置の一部を下面側から見た拡大平面図である。

図5に示す半導体装置20が、図1に示す半導体装置10と異なる点は、同電位の2以上の電極パッド5が、隣接する2つの第1電極パッド13a、13bと、1つの第2電極パッド14とからなる隣接する3つの電極パッド5である点と、複接続インナーリード7aが、平面視L字型である点のみである。

【0057】

したがって、図1に示す半導体装置10と同じ部材については同じ符号を付し、説明を省略する。また、図5に示す半導体装置20は、図1に示す半導体装置10と同様にして製造できる。すなわち、複接続インナーリード7aは、図1に示す半導体装置10を構成する複接続インナーリード7と同様に、配線基板17を形成する工程において、両端部と3つの電極パッド5のうち中央に接続される電極パッド5(図5における第1電極パッド13a)に接続される部分の近傍とが、配線基板17と一体化された所定の形状で、開口部12内に跨って延在するようにインナーリード材料を形成し、接続工程を行う前に、インナーリード材料を開口部12内で切断してダミーリードD7と分離する方法により形成されたものである。

【0058】

図5に示す半導体装置20は、図1に示す半導体装置10と同様に、同電位の2以上の電極パッド5が、複接続インナーリード7aの1つと接続されているものであるので、電極パッド5の数に対する配線19の数を少なくすることができ、図1に示す半導体装置10と同様の効果が得られる。

【0059】

(第3の実施形態)

図6は、本発明の半導体装置の他の例である第3の実施形態の半導体装置を説明するための図であり、半導体装置の一部を下面側から見た拡大平面図である。

図6に示す半導体装置30が、図1に示す半導体装置10と異なる点は、同電位の2以上の電極パッド5が、1つの第2電極パッド14と、その第2電極パッド14から2番目に近い第1電極パッド13とからなる2つの電極パッド5である点と、複接続インナーリード7bが、第1側壁12aおよび第2側壁12bに対して平面視で斜め方向に延在する屈曲部を有するものである点のみである。

【0060】

したがって、図1に示す半導体装置10と同じ部材については同じ符号を付し、説明を省略する。また、図6に示す半導体装置30は、図1に示す半導体装置10と同様にして製造できる。すなわち、複接続インナーリード7bは、図1に示す半導体装置10を構成する複接続インナーリード7と同様に、配線基板17を形成する工程において、両端部が配線基板17と一体化された所定の形状で、開口部12内に跨って延在するようにインナーリード材料を形成し、接続工程を行う前に、インナーリード材料を開口部12内で切断してダミーリードD7と分離する方法により形成されたものである。

【0061】

図6に示す半導体装置30は、図1に示す半導体装置10と同様に、同電位の2以上の電極パッド5が、複接続インナーリード7bの1つと接続されているものであるので、電極パッド5の数に対する配線19の数を少なくすることができ、図1に示す半導体装置10と同様の効果が得られる。

また、図6に示す半導体装置30は、複接続インナーリード7bが、第1側壁12aおよび第2側壁12bに対して平面視で斜め方向に延在する屈曲部を有するものであるので、同電位の2以上の電極パッド5が、1つの第2電極パッド14と、その第2電極パッド14から2番目に近い第1電極パッド13とからなる2つの電極パッド5である場合に、2つの電極パッド5が最短距離で接続された複接続インナーリード7bとなる。

【0062】

なお、図6に示す半導体装置30では、同電位の2以上の電極パッド5が、1つの第2電極パッド14と、その第2電極パッド14から2番目に近い第1電極パッド13とからなる2つの電極パッド5である場合を例に挙げて説明したが、同電位の2以上の電極パッド5は、屈曲部を有する複接続インナーリードによって接続できればよく、例えば、1つの電極パッドと、その電極パッドから3番目や4番目に近い電極パッドであってもよい。

【0063】

(第4の実施形態)

図7は、本発明の半導体装置の他の例である第4の実施形態の半導体装置を説明するための図であり、半導体装置の一部を下面側から見た拡大平面図である。

図7に示す半導体装置40が、図1に示す半導体装置10と異なる点は、同電位の2以上の電極パッド5が、隣接する2つの第1電極パッド13c、13dおよび隣接する2つの第2電極パッド14c、14dからなる互いに隣接する4つの電極パッド5である点と、複接続インナーリード7cが、隣接する2つの第1電極パッド13c、13dの少なくとも一部および隣接する2つの第2電極パッド14c、14dの少なくとも一部と平面視で重なっている帯状のものである点と、複接続インナーリード7cの幅および複接続インナーリード7cに接続された配線19aの幅が、隣接する2つの第1電極パッド13c、13d間の距離および隣接する2つの第2電極パッド14c、14d間の距離よりも長いものである点のみである。

【0064】

したがって、図1に示す半導体装置10と同じ部材については同じ符号を付し、説明を省略する。また、図7に示す半導体装置40は、図1に示す半導体装置10と同様にして製造できる。すなわち、複接続インナーリード7c、図1に示す半導体装置10を構成する複接続インナーリード7と同様に、配線基板17を形成する工程において、両端部が配線基板17と一体化された所定の形状で、開口部12内に跨って延在するようにインナーリード材料を形成し、接続工程を行う前に、インナーリード材料を開口部12内で切断してダミーリードD7と分離する方法により形成されたものである。

【0065】

図7に示す半導体装置40は、図1に示す半導体装置10と同様に、同電位の2以上の電極パッド5が、複接続インナーリード7cの1つと接続されているものであるので、電極パッド5の数に対する配線の数を少なくすることができ、図1に示す半導体装置10と同様の効果が得られる。

また、図7に示す半導体装置40は、複接続インナーリード7cの幅および複接続インナーリード7cに接続された配線19aの幅が、隣接する2つの第1電極パッド13c、13d間の距離および隣接する2つの第2電極パッド14c、14d間の距離よりも長いものであるので、例えば、電極パッド5の幅よりも配線の幅が狭い場合と比較して、電源の強化を図ることができる。

【0066】

なお、図7に示す半導体装置40では、同電位の2以上の電極パッド5が、隣接する2つの第1電極パッド13c、13dおよび隣接する2つの第2電極パッド14c、14dからなる互いに隣接する4つの電極パッド5である場合を例に挙げて説明したが、同電位の2以上の電極パッド5は、例えば、互いに隣接する5以上の電極パッド5とすることができ、この場合の複接続インナーリードの平面形状は、同電位の2以上の電極パッド5を構成する全ての電極パッド5の少なくとも一部に平面視で重なる形状とすることができる。

【0067】

以上、本発明者によってなされた発明を実施形態に基づき説明したが、本発明は上記の実施形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることは言うまでもない。

【0068】

例えば、上述した実施形態では、配線基板17に一つの半導体チップ16を搭載した半導体装置を例に挙げて説明したが、本発明は、半導体装置の大容量化および高機能化を可能とするために、配線基板17に複数の半導体チップを搭載した半導体装置に適用しても良い。

また、上述した実施形態では、配線基板17として絶縁基板11の一面11aにのみ配線19を有する1層配線のものを用いた半導体装置について説明したが、本発明は、半導体装置の大容量化および高機能化を可能とするために、配線基板として2層配線以上の配線を有する多層配線基板を用いた半導体装置に適用しても良い。

【0069】

また、上述した実施形態では、中央部に開口部12が配置された配線基板を備える半導体装置について説明したが、開口部の位置は中央部でなくてもよいし、配線基板として、開口部により完全に2つに分離されたものを用いてもよい。

また、上述した実施形態では、BGA型の半導体装置に適用した場合について説明したが、LGA(Land Grid Array)型の半導体装置にも適用しても良い。

【符号の説明】

【0070】

5…電極パッド、7、7a、7b、7c…複接続インナーリード(インナーリード)、10、20、30、40…半導体装置、11…絶縁基板、11a…一面、11b…他面、12…開口部、12a…第1側壁、12b…第2側壁、13、13a、13b、13c、13d…第1電極パッド、14、14c、14d…第2電極パッド、15…電極パッド群、16…半導体チップ、17…配線基板(基板)、19、19a…配線、28…半田ボール(外部電極)、29…ランド、31…接着部材、32、33…封止体、41…配線母基板、43…製品形成部、48…ダイシングテープ、70…ボンディングツール、73…単接続インナーリード。

【技術分野】

【0001】

本発明は、半導体装置および半導体装置の製造方法に関する。

【背景技術】

【0002】

従来の半導体装置の一例として、例えば、BGA(Ball Grid Array)型やCSP(Chip Size Package)型などの半導体パッケージがある。このような半導体パッケージは、基板上に半導体チップを実装し、この半導体チップと基板との間をワイヤーボンディング等で接続した構造を有している。

【0003】

BGA型の半導体装置としては、半導体チップがチップパッドを有し、パッケージ基板がチップパッドを外方に臨ませる開口部を有し、パッケージ基板に配置されたパッケージ配線の一端にボンディングパッドが設けられ、他端に半田ボールが設けられ、チップパッドとボンディングパッドとが、ボンディングワイヤーを介して電気的に接続されているものがある(例えば、特許文献1参照)。

【0004】

また、従来の半導体装置として、例えば、特許文献2には、半導体ペレットの一主面には複数個の電極パッドが整列されているとともに、この電極パッド群列から離間した位置にも電極パッドが配置されており、TABテープのテープ本体にはメインボンディングホールが開設されているとともに、このメインボンディングホールの脇にはサブボンディングホールが開設されており、前記テープ本体に敷設された複数本のインナリードの先端部が前記メインボンディングホールおよび前記サブボンディングホールにおいて前記電極パッドのそれぞれにギャングボンディングされているものが記載されている。

【0005】

また、従来の半導体装置として、例えば、特許文献3には、TABを用いて積層された半導体チップからなり、半導体チップと電気的に接続されたTABの複数のフィルムリードがリードフレームの接続パッド上に並列に接続されている半導体集積回路装置が記載されている。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2008−198841号公報

【特許文献2】特開2003−059980号公報

【特許文献3】特開平06−268152号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

しかしながら、従来の半導体装置では、パッケージ基板上でのパッケージ配線の引き回しが困難となったり、遠回りの配線となったりしてしまう場合があり、広い配線スペースを確保しなければならず、半導体装置の小型化に対応しにくかった。

具体的には、例えば、特許文献1に記載の技術では、半田ボール数の制約に加え、パッケージ配線を構成する配線層が1層のみであることにより、半田ボール間に配置されるパッケージ配線数が制約されるため、パッケージ基板上でのパッケージ配線の引き回しが困難となったり、遠回りの配線となったりしやすく、問題となっていた。

【課題を解決するための手段】

【0008】

本発明者は、上記課題を解決するために鋭意検討を重ねた。

その結果、一端が配線に接続されて他端が開口部内に露出されたインナーリードを有する基板を備え、開口部から露出するように配置された半導体チップの複数の電極パッドのうち、同電位の2以上の電極パッドがインナーリードの1つと接続されているものとすることで、電極パッドの数に対する基板に配置された配線の数を少なくすることができ、基板上での配線の配置の自由度を向上させることが可能となり、半導体装置の小型化に適した半導体装置が得られることを見出し、本発明の半導体装置および半導体装置の製造方法を想到した。

【0009】

本発明の半導体装置は、一面から他面に貫通して設けられた開口部と、外部電極に接続された配線と、一端が前記配線に接続されて他端が前記開口部内に露出されたインナーリードとを有する基板と、前記基板の一面に搭載された半導体チップとを備え、前記半導体チップが、前記開口部から露出するように配置された同電位の2以上の電極パッドを含む電極パッド群を有し、前記同電位の2以上の電極パッドが、前記インナーリードの1つと接続されていることを特徴とする。

【発明の効果】

【0010】

本発明の半導体装置は、一面から他面に貫通して設けられた開口部と、外部電極に接続された配線と、一端が前記配線に接続されて他端が前記開口部内に露出されたインナーリードとを有する基板と、前記基板の一面に搭載された半導体チップとを備え、前記半導体チップが、前記開口部から露出するように配置された同電位の2以上の電極パッドを含む電極パッド群を有し、前記同電位の2以上の電極パッドが、前記インナーリードの1つと接続されているものであるので、電極パッドの数に対する基板に配置された配線の数を少なくすることができる。その結果、基板上での配線の配置の自由度を向上させることができ、半導体装置の小型化に適したものとなる。

【図面の簡単な説明】

【0011】

【図1】図1は、本発明の半導体装置の一例である第1の実施形態の半導体装置を説明するための図であり、半導体装置を下面側から見た平面図である。

【図2】図2は、本発明の半導体装置の一例である第1の実施形態の半導体装置を説明するための図であり、図1のA−A’線に対応する断面図である。

【図3A】図3Aは、本発明の半導体装置の製造方法の一例として第1の実施形態の半導体装置の製造方法を説明するための図であり、図1のA−A’線に対応する断面図である。

【図3B】図3Bは、本発明の半導体装置の製造方法の一例として第1の実施形態の半導体装置の製造方法を説明するための図であり、図1のA−A’線に対応する断面図である。

【図3C】図3Cは、本発明の半導体装置の製造方法の一例として第1の実施形態の半導体装置の製造方法を説明するための図であり、図1のA−A’線に対応する断面図である。

【図3D】図3Dは、本発明の半導体装置の製造方法の一例として第1の実施形態の半導体装置の製造方法を説明するための図であり、図1のA−A’線に対応する断面図である。

【図3E】図3Eは、本発明の半導体装置の製造方法の一例として第1の実施形態の半導体装置の製造方法を説明するための図であり、図1のA−A’線に対応する断面図である。

【図3F】図3Fは、本発明の半導体装置の製造方法の一例として第1の実施形態の半導体装置の製造方法を説明するための図であり、図1のA−A’線に対応する断面図である。

【図4A】図4Aは、図3Cに示される工程を説明するための図であり、図1のA−A’線に対応する断面図である。

【図4B】図4Bは、図3Cに示される工程を説明するための図であり、図1のA−A’線に対応する断面図である。

【図4C】図4Cは、図3Cに示される工程を説明するための図であり、図1のA−A’線に対応する断面図である。

【図5】図5は、本発明の半導体装置の他の例である第2の実施形態の半導体装置を説明するための図であり、半導体装置の一部を下面側から見た拡大平面図である。

【図6】図6は、本発明の半導体装置の他の例である第3の実施形態の半導体装置を説明するための図であり、半導体装置の一部を下面側から見た拡大平面図である。

【図7】図7は、本発明の半導体装置の他の例である第4の実施形態の半導体装置を説明するための図であり、半導体装置の一部を下面側から見た拡大平面図である。

【発明を実施するための形態】

【0012】

以下、図面を参照して本発明を適用した実施形態について詳細に説明する。尚、本発明

は以下の実施形態に限定されるものではなく、以下の説明で用いる図面は、本発明の実施

形態の構成を説明するためのものであり、図示される各部の大きさや厚さや寸法等は、実

際の半導体装置の寸法関係とは異なる場合がある。

【0013】

(第1の実施形態)

図1および図2は、本発明の半導体装置の一例である第1の実施形態の半導体装置を説明するための図である。図1は、半導体装置を下面側から見た平面図であり、図2は、図1のA−A’線に対応する断面図である。

本実施形態の半導体装置10は、BGA型の半導体装置であり、図2に示すように、配線基板17(基板)と半導体チップ16とを備えている。

【0014】

配線基板17は、例えば、フィルム状の平面視略矩形のポリイミド基材からなる絶縁基板11を備えたフレキシブル配線基板である。なお、絶縁基板11は、ポリイミド基材からなるものに限定されず、例えば、ガラスエポキシ基板などであってもよい。

絶縁基板11の半導体チップ16側の面(図2においては上面)には、Cu等の導電材料からなる複数の配線19が所定の形状で形成されている。

【0015】

また、配線基板17は、開口部12により開口部12の第1側壁12a側と第2側壁12b側の2つの領域に区画されている。配線基板17の他面11b(図2においては下面)の第1側壁12a側と第2側壁12b側のそれぞれの領域には、図1に示すように、所定の間隔で、外部電極である半田ボール28が格子状に配置されている。半田ボール28は、図2に示すように、各配線19の一端が絶縁基板11に形成された孔部により配線基板17の他面11bに露出されてなるランド(外部接続端子)29に電気的に接続されている。このことにより、各配線19と半田ボール28とが電気的に接続されている。

【0016】

また、配線基板17は、図1および図2に示すように、一面11aから他面11bに貫通して設けられた平面視略矩形の開口部12を有している。開口部12は、平面視で配線基板17の中央部に設けられ、第1側壁12aと第1側壁12aに対向する第2側壁12bとを有している。

【0017】

また、配線基板17は、複数の複接続インナーリード7(インナーリード)と、複数の単接続インナーリード73と、複数のダミーリードD7とを有するインナーリードを有している。複接続インナーリード7および単接続インナーリード73は、Au、Cu等の導電材料からなる平面視直線状のものであり、一端が配線19に接続されて他端が開口部12内に露出されているものである。各ダミーリードD7は、複接続インナーリード7と同じ導電材料からなる平面視直線状のものであり、他の導電部材と絶縁されている。また、各ダミーリードD7は、図1および図2に示すように、それぞれ開口部12内において複接続インナーリード7に対向して配置され、複接続インナーリード7と同じ層に配線19の延在方向に沿って形成されている。

本実施形態においては、図1に示すように、開口部12内に露出されている複接続インナーリード7に、後述する同電位の2以上の電極パッド5が接続され、開口部12内に露出されている単接続インナーリード73に、1つの電極パッド5が接続されている。

【0018】

また、図2に示すように、配線基板17の一面11aには、DAF(Die Attached Film)、或いはエラストマ(弾性体)等からなる接着部材31を介して、半導体チップ16が搭載されている。接着部材31は、配線基板17の配線19の形成されている領域を覆い、開口部12を除く領域に設けられている。

半導体チップ16は、略矩形の板状であり、半導体チップ16の図1および図2における下面16b(一面)には、例えばメモリ回路(不図示)と、半導体チップ16を外部と電気的に接続するための複数の電極パッド5からなる電極パッド群15とが形成されている。

半導体チップ16の下面16bにおいて、電極パッド群15を構成する電極パッド5の形成されている領域を除く領域には、図示しないパッシベーション膜が形成されており、メモリ回路の形成された面が保護されている。

【0019】

図1および図2に示すように、半導体チップ16は、電極パッド群15の設けられている側(下面16b側)を配線基板17に向けて配置されている。また、半導体チップ16は、図1および図2に示すように、配線基板17の開口部12から電極パッド群15が露出するように、配置されている。本実施形態においては、電極パッド群15は、図1および図2に示すように、半導体チップ16の中央部に2列に並んで配置された複数の電極パッド5からなるものとされている。

【0020】

より詳細には、図1に示すように、電極パッド群15は、開口部12の第1側壁12aに沿って第1側壁12aに近接して配置された複数の第1電極パッド5からなる第1電極パッド13の列と、第2側壁12bに沿って第2側壁12bに近接して配置された複数の第1電極パッド5からなる第2電極パッド14の列の2列からなるものとされている。

また、図1および図2に示す半導体装置10では、電極パッド群15が、同電位の2以上の電極パッド5を含むものとされている。なお、電極パッド群15に含まれる電極パッド5のうち、同電位である電極パッド5の数は、2以上であればよく、特に限定されない。

【0021】

本実施形態においては、図1および図2に示すように、同電位の2つの電極パッド5である図1において下から3つめに配置された第1電極パッド13と、その第1電極パッド13に隣接して配置された第2電極パッド14とが、複接続インナーリード7の1つと接続されている。また、同電位の2つの電極パッド5である図1において下から4つめに配置された第1電極パッド13と、その第1電極パッド13に隣接して配置された第2電極パッド14とが、複接続インナーリード7の1つと接続されている。

【0022】

図1および図2に示す半導体装置10において、各複接続インナーリード7に接続されている同電位の第1電極パッド13および第2電極パッド14は、電源またはグランドとされている。なお、複接続インナーリード7によって接続されている電極パッド5は、電源またはグランドとされていることが好ましいが、複接続インナーリード7によって接続できるように同電位とされていればよく、電源またはグランドでなくてもよい。

【0023】

また、図1に示すように、複接続インナーリード7の端部に配置された電極パッド5は、複接続インナーリード7に接続された他の電極パッド5と比較して、複接続インナーリード7に接続された配線19との距離が遠いものとなっている。

例えば、図1において下から3つめに配置された第1電極パッド13は、図1において下から3つめに配置された第2電極パッド14と比較して、複接続インナーリード7に接続された配線19との距離が遠いものとなっている。

また、図1において下から4つめに配置された第2電極パッド14は、図1において下から4つめに配置された第1電極パッド13と比較して、複接続インナーリード7に接続された配線19との距離が遠いものとなっている。

【0024】

また、図1に示す電極パッド5のうち、複接続インナーリード7に接続されていない電極パッド5は、それぞれ最も距離の近い対応する単接続インナーリード73に電気的に接続されている。

そして、図1および図2に示すように、複接続インナーリード7および単接続インナーリード73と、電極パッド5とが接続されていることにより、配線基板17に設けられた半田ボール28と半導体チップ16とが電気的に接続されている。

【0025】

また、図1および図2に示す半導体装置10では、開口部12内および開口部12近傍に封止樹脂からなる封止体32が形成されることにより、複接続インナーリード7および単接続インナーリード73が、封止樹脂に封止されている。このことにより、図1および図2に示す半導体装置10では、複接続インナーリード7および単接続インナーリード73を用いた半導体チップ16と配線基板17との接続部位が、外界から保護されるようになっている。

【0026】

また、半導体チップ16の配線基板17と対向していない領域は、封止樹脂からなる封止体33によって被覆されている。図1および図2に示す半導体装置10では、封止体33が形成されていることにより、半導体チップ16が外界から保護されるようになっている。

なお、封止体32、33に用いられる封止樹脂としては、例えばエポキシ樹脂等の熱硬化性樹脂などを用いることができる。

【0027】

「製造方法」

図3A〜図3Fは、本発明の半導体装置の製造方法の一例として第1の実施形態の半導体装置の製造方法を説明するための図であり、図1のA−A’線に対応する断面図である。また、図4A〜図4Cは、図3Cに示される工程を説明するための図であり、図1のA−A’線に対応する断面図である。なお、図3A〜図3Fおよび図4A〜図4Cにおいて、第1の実施の形態の半導体装置10と同一構成部分には同一の符号を付す。

【0028】

図1および図2に示す半導体装置10を製造するには、まず、配線基板17となる基板を用意し、図3Aに示すように、マトリクス状に配置された各製品形成部43に一面11aから他面11bに貫通して設けられた開口部12と、それぞれ1つの外部電極(図1および図2に示す半田ボール28)に接続される複数の配線19と、一端が配線19に接続されて他端が絶縁され、後の工程で切断されることにより複接続インナーリード7とダミーリードD7とに分離される複数のインナーリード材料A7と、後の工程で切断されることにより、一端が配線19に接続されて他端が開口部12内に露出された2つの単接続インナーリード73(図3Aには不図示、図1参照)に分離される複数のリード材料(不図示)とを有する配線母基板41(配線基板17)を形成する。

【0029】

本実施形態において用いられる配線母基板41は、MAP(Mold Array Process)方式で処理されるものであり、複数の製品形成部43がマトリクス状に配置されている。配線母基板41のそれぞれの製品形成部43には、図3Aに示すように接着部材31が搭載されている。

なお、各製品形成部43は、その後の工程で配線母基板41を切断分離することにより、図1および図2に示す半導体装置10の配線基板17となる部位である。したがって、配線母基板41の隣接する製品形成部43間には、ダイシングラインが配置されている。

【0030】

また、図3Aに示すように、インナーリード材料A7と単接続インナーリード73となるリード材料とは、両端部が配線基板17と一体化された所定の形状で、配線母基板41の製品形成部43にそれぞれ設けられた開口部12内に跨って延在するように形成されている。

また、本実施形態では、配線母基板41(配線基板17)を形成する工程において、図3Aに示すように、配線母基板41(配線基板17)に、各配線19の一端が絶縁基板11に形成された孔部により他面11bに露出されてなるランド29を形成する。

【0031】

次に、図3Bに示すように、配線母基板41の製品形成部43のそれぞれ(配線基板17)の一面11aに、同電位の2以上の電極パッド5を含む電極パッド群15(図1参照)を有する半導体チップ16を搭載し、電極パッド群15が開口部12から露出するように配置する。半導体チップ16は、DAFなどの接着部材31を介して、半導体チップ16の電極パッド群15を配線基板17側に向けて接着固定する。

【0032】

なお、図3Bには、複数の第1電極パッド5のうち、図1のA−A’線に対応する断面に配置された第1電極パッド13と第2電極パッド14が記載されている。配線母基板41に半導体チップ16が搭載されることにより、開口部12内において、各インナーリード材料A7(複接続インナーリード7)、および各単接続インナーリード73となるリード材料が、それぞれ接続される電極パッド5に対向配置される。

【0033】

次に、図3Cに示すように、インナーリード材料A7(複接続インナーリード7)および単接続インナーリード73となるリード材料と、電極パッド5とを接続する。この時、同電位の2以上の電極パッド5を、複接続インナーリード7(インナーリード)の一つと接続する(接続工程)。

本実施形態では、図4Aに示すように、接続工程を行う前に、開口部12内で、インナーリード材料A7(複接続インナーリード7)、および単接続インナーリード73となるリード材料を切断する。このことによりインナーリード材料A7は、複接続インナーリード7とダミーリードD7とに分離され、リード材料は、2つの単接続インナーリード73に分離される。

【0034】

インナーリード材料A7および単接続インナーリード73となるリード材料を切断する方法としては、例えば、図4Aおよび図4Bに示すように、インナーリードボンディング装置のボンディングツール70を用いて電極パッド5に接続する前に、ボンディングツール70を用いてインナーリード材料A7または単接続インナーリード73となるリード材料を切断する方法を用いることができる。この場合、インナーリード材料A7または単接続インナーリード73となるリード材料を切断した後、複接続インナーリード7または単接続インナーリード73を電極パッド5に接続する作業をスムーズに行うことができ、効率よく製造でき、好ましい。

また、インナーリード材料A7(複接続インナーリード7)および単接続インナーリード73となるリード材料の予め決められた位置には、接続工程を行う前に、例えばノッチ部などの図示しない切断容易部を設けることが好ましい。この場合、インナーリード材料A7および単接続インナーリード73となるリード材料を切断する際に、所定の位置で容易に効率よく高精度で切断できる。

【0035】

次に、接続工程を行う。接続工程は、図3Cに示すように、半導体チップ16の配線基板17側の面が上側になるように配置して行うことが好ましい。また、接続工程において、電極パッド5と、複接続インナーリード7または単接続インナーリード73とを接続する方法としては、例えば、図4A〜図4Cに示すインナーリードボンディング装置のボンディングツール70を用いて、超音波熱圧着する方法などを用いることができる。

【0036】

ここでは、まず、図1において下から3つめに配置された第1電極パッド13および第2電極パッド14と複接続インナーリード7との接続について説明する。なお、図1において下から4つめに配置された第1電極パッド13および第2電極パッド14と複接続インナーリード7との接続については、第1電極パッド13と複接続インナーリード7との接続と、第2電極パッド14と複接続インナーリード7との接続とを反対の順番で行うこと以外は同じであるので、説明を省略する。

【0037】

図1において下から3つめに配置された第1電極パッド13および第2電極パッド14と複接続インナーリード7とを接続する接続工程においては、同電位の2以上の電極パッド5(第1電極パッド13および第2電極パッド14)のうち、複接続インナーリード7に接続された配線19との距離が最も遠い電極パッド5(図3Cにおいては第1電極パッド13)が複接続インナーリード7の端部に配置されるように接続する。

【0038】

また、本実施形態の接続工程においては、図4Bおよび図4Cに示すように、同電位の2以上の電極パッド5のうち、複接続インナーリード7に接続された配線19との距離が近い電極パッド5(図3Cにおいては第2電極パッド14)から順に複接続インナーリード7に接続する。

具体的には、まず、図4Bに示すように、複接続インナーリード7と第2電極パッド14とを電気的に接続する。すなわち、電極パッド5に接続する複接続インナーリード7の切断に用いた図4Aに示すボンディングツール70を、図4Bに示すように、第2電極パッド14上の位置に移動させ、複接続インナーリード7のボンディング部位を第2の電極パッド14に超音波熱圧着により接続する。

【0039】

次に、図4Bに示すボンディングツール70を、図4Cに示すように、第1電極パッド13と第2電極パッド14のうち、配線19との距離(図1参照)が遠い第1電極パッド13上の位置に移動し、第1電極パッド13に、複接続インナーリード7の切断端部であるボンディング部位を超音波熱圧着により接続する。

このことにより、本実施形態においては、図1および図4Cに示すように、同電位の第1電極パッド13と第2電極パッド14のうち、配線19との距離が遠い電極パッド5である第1電極パッド13が複接続インナーリード7の端部に配置される。

【0040】

次に、複接続インナーリード7に接続されていない電極パッド5と単接続インナーリード73との接続について説明する。複接続インナーリード7に接続されていない電極パッド5と単接続インナーリード73とを接続する際には、単接続インナーリード73の切断に用いたボンディングツール70を、接続する電極パッド5上の位置に移動し、同電位の2以上の電極パッド5のうち、配線19との距離最もが遠い電極パッド5と複接続インナーリード7との接続と同様に、電極パッド5に、単接続インナーリード73の切断端部であるボンディング部位を超音波熱圧着により接続する。

【0041】

続いて、図3Dに示すように、開口部12内および開口部12近傍に封止樹脂からなる封止体32を形成して、複接続インナーリード7および単接続インナーリード73を封止するとともに、半導体チップ16の配線基板17と対向していない領域を覆うように、封止樹脂からなる封止体33を形成する。

封止体32および封止体33を形成する方法としては、特に限定されないが、例えば、以下に示す方法を用いることが好ましい。

【0042】

まず、トランスファーモールド装置の上型と下型からなる成型金型を用意し、配線母基板41を型閉めする。この時、製品形成領域43に形成された開口部12の長辺が、封止樹脂の注入方向に沿って配置されるように、配線母基板41を成型金型のキャビティ内に配置することが好ましい。このことにより、複接続インナーリード7および単接続インナーリード73が、成型金型内における封止樹脂の流動に支障を来たすことを防止でき、成型金型内における封止樹脂の流動をスムーズにすることができる。

【0043】

次に、成型金型に設けられているゲートから、成型金型のキャビティ内に溶融された封止樹脂を注入し、キャビティ内を封止樹脂で充填する。次いで、例えば180℃程度の所定温度で熱処理(キュア)することにより、封止樹脂を硬化させる。その後、成型金型から配線母基板41を取り出すことにより、図3Dに示すように封止体32および封止体33によって一括的に覆われた配線母基板41が得られる。

【0044】

その後、図3Eに示すように、各配線19の一端が露出されてなるランド29に電気的に接続された半田ボール28を形成する。半田ボール28を形成する際には、例えば、ランド29の配置に合わせて複数の吸着孔が形成されたボールマウントツールを用いる方法を用いることが好ましい。具体的には、ボールマウントツールの吸着孔に半田ボール28を保持し、保持された半田ボール28にフラックスを転写形成し、ランド29に一括搭載した後、所定温度でリフローすることにより、半田ボール28を固着する方法を用いることができる。

【0045】

その後、配線母基板41をダイシングブレードにより縦横のダイシングラインで切断し、製品形成部43毎に切断分離することで、各配線基板17に分断され、図1及び図2に示す半導体装置10が得られる。

なお、配線母基板41を切断する際には、図3Fに示すように、半導体チップ16を覆う封止体33にダイシングテープ48を接着し、ダイシングテープ48によって配線母基板41を支持させて切断することが好ましい。

【0046】

本実施形態の半導体装置10は、一面11aから他面11bに貫通して設けられた開口部12と、半田ボール28に接続された配線と、一端が配線19に接続されて他端が開口部12内に露出された複接続インナーリード7とを有する配線基板17と、配線基板17の一面に搭載され、開口部12から露出するように配置された同電位の2以上の電極パッド5を含む電極パッド群15を有する半導体チップ16とを備え、同電位の2以上の電極パッド5が、複接続インナーリード7の1つと接続されているものであるので、電極パッド5の数に対する配線基板17に配置された配線19の数を少なくすることができる。その結果、配線基板17上の配線スペースを確保することができ、配線基板17上での配線19の配置の自由度を向上させることができ、半導体装置10の小型化に適したものとなる。

【0047】

また、本実施形態の半導体装置10では、複接続インナーリード7の端部に配置された電極パッド5が、複接続インナーリード7に接続された他の電極パッド5と比較して、複接続インナーリード7に接続された配線19との距離が遠いものとなっているので、複接続インナーリード7の端部に接続された電極パッド5が、複接続インナーリード7に接続された他の電極パッドと比較して、配線19との距離が近い場合と比較して、複接続インナーリード7の長さを短くすることができ、複接続インナーリード7を配置するのに必要な平面積が少なくて済むとともに、容易に製造できる。

【0048】

また、本実施形態の半導体装置10は、配線基板17の配線19が、一層配線であるので、配線19が多層配線である場合と比較して、容易に製造でき、半導体装置10の生産性を向上させることができるとともに、コストを低減することができる。

【0049】

また、本実施形態の半導体装置10は、開口部12が、第1側壁12aと第1側壁12aに対向する第2側壁12bとを有し、電極パッド群15が、第1側壁12aに沿って第1側壁に近接して配置された複数の第1電極パッド13と、第2側壁12aに沿って第2側壁12aに近接して配置された複数の第2電極パッド14とを有し、同電位の2以上の電極パッド5が、隣接する第1電極パッド13と第2電極パッド14とを含むものであり、複接続インナーリード7が平面視直線状であるので、複接続インナーリード7を配置するのに必要な平面積が少なくて済み、小型化に適したものとなるとともに、複接続インナーリード7と第1電極パッド13および第2電極パッド14との接続が容易で生産性に優れたものとなる。

【0050】

また、本実施形態の半導体装置10は、同電位の2以上の電極パッド5が、電源またはグランドとされているので、例えば、同電位の2以上の電極パッド5が、電源またはグランドでない場合と比較して、容易に同電位の2以上の電極パッド5を設けることができる。

また、本実施形態の半導体装置10では、配線19の一端が、配線基板17の他面11bに露出されているので、容易にランド29を形成することができ、ランド29に半田ボール28を形成することで、配線19と半田ボール28とを容易に接続できる。

【0051】

また、本実施形態の半導体装置10の製造方法では、複接続インナーリード7の一つと、同電位の2以上の電極パッド5とを接続する接続工程とを備えているので、電極パッド5の数に対する配線19の数を少なくすることができ、配線基板17上での配線19の配置の自由度を向上させることができる。

【0052】

また、本実施形態の半導体装置10の製造方法は、配線基板17を形成する工程において、開口部12内に跨って延在する複接続インナーリード7およびダミーリードD7となるインナーリード材料A7と、単接続インナーリード73となるリード材料とを形成し、接続工程を行う前に、開口部12内でインナーリード材料A7および単接続インナーリード73となるリード材料を切断する工程を含む方法であるので、半導体チップ16を搭載する際に、インナーリード材料A7(複接続インナーリード7)および単接続インナーリード73となるリード材料が補強材として機能するため、半導体チップ16を所定の位置に容易に高精度で搭載できるとともに、半導体チップ16を搭載する際の作業性を向上させることができる。

【0053】

また、本実施形態の半導体装置10の製造方法は、接続工程において、同電位の2以上の電極パッド5のうち、複接続インナーリード7に接続された配線19との距離が近い電極パッド5から順に複接続インナーリード7に接続する方法であるので、複接続インナーリード7に接続された配線19との距離が遠い電極パッド5から順に複接続インナーリード7に接続する場合と比較して、接続不良等が生じにくく、効率よく高精度で同電位の2以上の電極パッド5を複接続インナーリード7に接続できる。

【0054】

また、本実施形態の半導体装置10の製造方法では、配線母基板41を用い、半田ボール28を形成するまでの各工程を行った後、製品形成領域43毎に個片化するので、図1及び図2に示す半導体装置を個々に製造する場合と比較して、効率良く製造できる。

【0055】

(第2の実施形態)

図1および図2に示す第1実施形態においては、第1電極パッド13と第2電極パッド14とを含む同電位の2つの電極パッド5が、複接続インナーリード7の1つと接続されている場合を例に挙げて説明したが、本発明においては、例えば、同電位である3以上の電極パッドが、複接続インナーリードの1つと接続されていてもよい。

【0056】

図5は、本発明の半導体装置の他の例である第2の実施形態の半導体装置を説明するための図であり、半導体装置の一部を下面側から見た拡大平面図である。

図5に示す半導体装置20が、図1に示す半導体装置10と異なる点は、同電位の2以上の電極パッド5が、隣接する2つの第1電極パッド13a、13bと、1つの第2電極パッド14とからなる隣接する3つの電極パッド5である点と、複接続インナーリード7aが、平面視L字型である点のみである。

【0057】

したがって、図1に示す半導体装置10と同じ部材については同じ符号を付し、説明を省略する。また、図5に示す半導体装置20は、図1に示す半導体装置10と同様にして製造できる。すなわち、複接続インナーリード7aは、図1に示す半導体装置10を構成する複接続インナーリード7と同様に、配線基板17を形成する工程において、両端部と3つの電極パッド5のうち中央に接続される電極パッド5(図5における第1電極パッド13a)に接続される部分の近傍とが、配線基板17と一体化された所定の形状で、開口部12内に跨って延在するようにインナーリード材料を形成し、接続工程を行う前に、インナーリード材料を開口部12内で切断してダミーリードD7と分離する方法により形成されたものである。

【0058】

図5に示す半導体装置20は、図1に示す半導体装置10と同様に、同電位の2以上の電極パッド5が、複接続インナーリード7aの1つと接続されているものであるので、電極パッド5の数に対する配線19の数を少なくすることができ、図1に示す半導体装置10と同様の効果が得られる。

【0059】

(第3の実施形態)

図6は、本発明の半導体装置の他の例である第3の実施形態の半導体装置を説明するための図であり、半導体装置の一部を下面側から見た拡大平面図である。

図6に示す半導体装置30が、図1に示す半導体装置10と異なる点は、同電位の2以上の電極パッド5が、1つの第2電極パッド14と、その第2電極パッド14から2番目に近い第1電極パッド13とからなる2つの電極パッド5である点と、複接続インナーリード7bが、第1側壁12aおよび第2側壁12bに対して平面視で斜め方向に延在する屈曲部を有するものである点のみである。

【0060】

したがって、図1に示す半導体装置10と同じ部材については同じ符号を付し、説明を省略する。また、図6に示す半導体装置30は、図1に示す半導体装置10と同様にして製造できる。すなわち、複接続インナーリード7bは、図1に示す半導体装置10を構成する複接続インナーリード7と同様に、配線基板17を形成する工程において、両端部が配線基板17と一体化された所定の形状で、開口部12内に跨って延在するようにインナーリード材料を形成し、接続工程を行う前に、インナーリード材料を開口部12内で切断してダミーリードD7と分離する方法により形成されたものである。

【0061】

図6に示す半導体装置30は、図1に示す半導体装置10と同様に、同電位の2以上の電極パッド5が、複接続インナーリード7bの1つと接続されているものであるので、電極パッド5の数に対する配線19の数を少なくすることができ、図1に示す半導体装置10と同様の効果が得られる。

また、図6に示す半導体装置30は、複接続インナーリード7bが、第1側壁12aおよび第2側壁12bに対して平面視で斜め方向に延在する屈曲部を有するものであるので、同電位の2以上の電極パッド5が、1つの第2電極パッド14と、その第2電極パッド14から2番目に近い第1電極パッド13とからなる2つの電極パッド5である場合に、2つの電極パッド5が最短距離で接続された複接続インナーリード7bとなる。

【0062】

なお、図6に示す半導体装置30では、同電位の2以上の電極パッド5が、1つの第2電極パッド14と、その第2電極パッド14から2番目に近い第1電極パッド13とからなる2つの電極パッド5である場合を例に挙げて説明したが、同電位の2以上の電極パッド5は、屈曲部を有する複接続インナーリードによって接続できればよく、例えば、1つの電極パッドと、その電極パッドから3番目や4番目に近い電極パッドであってもよい。

【0063】

(第4の実施形態)

図7は、本発明の半導体装置の他の例である第4の実施形態の半導体装置を説明するための図であり、半導体装置の一部を下面側から見た拡大平面図である。

図7に示す半導体装置40が、図1に示す半導体装置10と異なる点は、同電位の2以上の電極パッド5が、隣接する2つの第1電極パッド13c、13dおよび隣接する2つの第2電極パッド14c、14dからなる互いに隣接する4つの電極パッド5である点と、複接続インナーリード7cが、隣接する2つの第1電極パッド13c、13dの少なくとも一部および隣接する2つの第2電極パッド14c、14dの少なくとも一部と平面視で重なっている帯状のものである点と、複接続インナーリード7cの幅および複接続インナーリード7cに接続された配線19aの幅が、隣接する2つの第1電極パッド13c、13d間の距離および隣接する2つの第2電極パッド14c、14d間の距離よりも長いものである点のみである。

【0064】

したがって、図1に示す半導体装置10と同じ部材については同じ符号を付し、説明を省略する。また、図7に示す半導体装置40は、図1に示す半導体装置10と同様にして製造できる。すなわち、複接続インナーリード7c、図1に示す半導体装置10を構成する複接続インナーリード7と同様に、配線基板17を形成する工程において、両端部が配線基板17と一体化された所定の形状で、開口部12内に跨って延在するようにインナーリード材料を形成し、接続工程を行う前に、インナーリード材料を開口部12内で切断してダミーリードD7と分離する方法により形成されたものである。

【0065】

図7に示す半導体装置40は、図1に示す半導体装置10と同様に、同電位の2以上の電極パッド5が、複接続インナーリード7cの1つと接続されているものであるので、電極パッド5の数に対する配線の数を少なくすることができ、図1に示す半導体装置10と同様の効果が得られる。

また、図7に示す半導体装置40は、複接続インナーリード7cの幅および複接続インナーリード7cに接続された配線19aの幅が、隣接する2つの第1電極パッド13c、13d間の距離および隣接する2つの第2電極パッド14c、14d間の距離よりも長いものであるので、例えば、電極パッド5の幅よりも配線の幅が狭い場合と比較して、電源の強化を図ることができる。

【0066】

なお、図7に示す半導体装置40では、同電位の2以上の電極パッド5が、隣接する2つの第1電極パッド13c、13dおよび隣接する2つの第2電極パッド14c、14dからなる互いに隣接する4つの電極パッド5である場合を例に挙げて説明したが、同電位の2以上の電極パッド5は、例えば、互いに隣接する5以上の電極パッド5とすることができ、この場合の複接続インナーリードの平面形状は、同電位の2以上の電極パッド5を構成する全ての電極パッド5の少なくとも一部に平面視で重なる形状とすることができる。

【0067】

以上、本発明者によってなされた発明を実施形態に基づき説明したが、本発明は上記の実施形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることは言うまでもない。

【0068】

例えば、上述した実施形態では、配線基板17に一つの半導体チップ16を搭載した半導体装置を例に挙げて説明したが、本発明は、半導体装置の大容量化および高機能化を可能とするために、配線基板17に複数の半導体チップを搭載した半導体装置に適用しても良い。

また、上述した実施形態では、配線基板17として絶縁基板11の一面11aにのみ配線19を有する1層配線のものを用いた半導体装置について説明したが、本発明は、半導体装置の大容量化および高機能化を可能とするために、配線基板として2層配線以上の配線を有する多層配線基板を用いた半導体装置に適用しても良い。

【0069】

また、上述した実施形態では、中央部に開口部12が配置された配線基板を備える半導体装置について説明したが、開口部の位置は中央部でなくてもよいし、配線基板として、開口部により完全に2つに分離されたものを用いてもよい。

また、上述した実施形態では、BGA型の半導体装置に適用した場合について説明したが、LGA(Land Grid Array)型の半導体装置にも適用しても良い。

【符号の説明】

【0070】

5…電極パッド、7、7a、7b、7c…複接続インナーリード(インナーリード)、10、20、30、40…半導体装置、11…絶縁基板、11a…一面、11b…他面、12…開口部、12a…第1側壁、12b…第2側壁、13、13a、13b、13c、13d…第1電極パッド、14、14c、14d…第2電極パッド、15…電極パッド群、16…半導体チップ、17…配線基板(基板)、19、19a…配線、28…半田ボール(外部電極)、29…ランド、31…接着部材、32、33…封止体、41…配線母基板、43…製品形成部、48…ダイシングテープ、70…ボンディングツール、73…単接続インナーリード。

【特許請求の範囲】

【請求項1】

一面から他面に貫通して設けられた開口部と、外部電極に接続された配線と、一端が前記配線に接続されて他端が前記開口部内に露出されたインナーリードとを有する基板と、

前記基板の一面に搭載された半導体チップとを備え、

前記半導体チップが、前記開口部から露出するように配置された同電位の2以上の電極パッドを含む電極パッド群を有し、

前記同電位の2以上の電極パッドが、前記インナーリードの1つと接続されていることを特徴とする半導体装置。

【請求項2】

前記インナーリードの端部に接続された電極パッドは、前記インナーリードに接続された他の電極パッドと比較して、前記インナーリードに接続された配線との距離が遠いことを特徴とする請求項1に記載の半導体装置。

【請求項3】

前記開口部が、第1側壁と前記第1側壁に対向する第2側壁とを有し、

前記電極パッド群が、前記第1側壁に沿って前記第1側壁に近接して配置された複数の第1電極パッドと、前記第2側壁に沿って前記第2側壁に近接して配置された複数の第2電極パッドとを有し、

前記同電位の2以上の電極パッドが、前記第1電極パッドと前記第2電極パッドとを含むことを特徴とする請求項1または請求項2のいずれか一項に記載の半導体装置。

【請求項4】

前記同電位の2以上の電極パッドが、隣接する前記第1電極パッドと前記第2電極パッドであることを特徴とする請求項3に記載の半導体装置。

【請求項5】

前記インナーリードが、平面視直線状であることを特徴とする請求項4に記載の半導体装置。

【請求項6】

前記インナーリードが、前記第1側壁および前記第2側壁に対して平面視で斜め方向に延在する屈曲部を有することを特徴とする請求項3に記載の半導体装置。

【請求項7】

前記同電位の2以上の電極パッドが、隣接する2つの前記第1電極パッドまたは隣接する2つの前記第2電極パッドを含むことを特徴とする請求項3に記載の半導体装置。

【請求項8】

前記インナーリードが、平面視L字型であることを特徴とする請求項7に記載の半導体装置。

【請求項9】

前記同電位の2以上の電極パッドが、隣接する2以上の前記第1電極パッドおよび隣接する2以上の前記第2電極パッドを含み、

前記インナーリードが、隣接する2以上の前記第1電極パッドの少なくとも一部および隣接する2以上の前記第2電極パッドの少なくとも一部と平面視で重なっている帯状のものであることを特徴とする請求項3に記載の半導体装置。

【請求項10】

一面から他面に貫通して設けられた開口部と、外部電極に接続される配線と、一端が前記配線に接続されて他端が前記開口部内に露出されたインナーリードとを有する基板を形成する工程と、

前記基板の一面に、同電位の2以上の電極パッドを含む電極パッド群を有する半導体チップを搭載し、前記電極パッド群を前記開口部から露出するように配置する工程と、

前記インナーリードの一つと、前記同電位の2以上の電極パッドとを接続する接続工程とを備えることを特徴とする半導体装置の製造方法。

【請求項11】

前記基板を形成する工程において、前記開口部内に跨って延在するインナーリードを形成し、

前記接続工程を行う前に、前記開口部内で前記インナーリードを切断する工程を含むことを特徴とする請求項10に記載の半導体装置の製造方法。

【請求項12】

前記接続工程において、前記同電位の2以上の電極パッドのうち、前記インナーリードに接続された配線との距離が最も遠い電極パッドが前記インナーリードの端部に配置されるように接続することを特徴とする請求項10または請求項11に記載の半導体装置の製造方法。

【請求項13】

前記接続工程において、前記同電位の2以上の電極パッドのうち、前記インナーリードに接続された配線との距離が近い電極パッドから順に前記インナーリードに接続することを特徴とする請求項10〜請求項12のいずれか一項に記載の半導体装置の製造方法。

【請求項1】

一面から他面に貫通して設けられた開口部と、外部電極に接続された配線と、一端が前記配線に接続されて他端が前記開口部内に露出されたインナーリードとを有する基板と、

前記基板の一面に搭載された半導体チップとを備え、

前記半導体チップが、前記開口部から露出するように配置された同電位の2以上の電極パッドを含む電極パッド群を有し、

前記同電位の2以上の電極パッドが、前記インナーリードの1つと接続されていることを特徴とする半導体装置。

【請求項2】

前記インナーリードの端部に接続された電極パッドは、前記インナーリードに接続された他の電極パッドと比較して、前記インナーリードに接続された配線との距離が遠いことを特徴とする請求項1に記載の半導体装置。

【請求項3】

前記開口部が、第1側壁と前記第1側壁に対向する第2側壁とを有し、

前記電極パッド群が、前記第1側壁に沿って前記第1側壁に近接して配置された複数の第1電極パッドと、前記第2側壁に沿って前記第2側壁に近接して配置された複数の第2電極パッドとを有し、

前記同電位の2以上の電極パッドが、前記第1電極パッドと前記第2電極パッドとを含むことを特徴とする請求項1または請求項2のいずれか一項に記載の半導体装置。

【請求項4】

前記同電位の2以上の電極パッドが、隣接する前記第1電極パッドと前記第2電極パッドであることを特徴とする請求項3に記載の半導体装置。

【請求項5】

前記インナーリードが、平面視直線状であることを特徴とする請求項4に記載の半導体装置。

【請求項6】

前記インナーリードが、前記第1側壁および前記第2側壁に対して平面視で斜め方向に延在する屈曲部を有することを特徴とする請求項3に記載の半導体装置。

【請求項7】

前記同電位の2以上の電極パッドが、隣接する2つの前記第1電極パッドまたは隣接する2つの前記第2電極パッドを含むことを特徴とする請求項3に記載の半導体装置。

【請求項8】

前記インナーリードが、平面視L字型であることを特徴とする請求項7に記載の半導体装置。

【請求項9】

前記同電位の2以上の電極パッドが、隣接する2以上の前記第1電極パッドおよび隣接する2以上の前記第2電極パッドを含み、

前記インナーリードが、隣接する2以上の前記第1電極パッドの少なくとも一部および隣接する2以上の前記第2電極パッドの少なくとも一部と平面視で重なっている帯状のものであることを特徴とする請求項3に記載の半導体装置。

【請求項10】

一面から他面に貫通して設けられた開口部と、外部電極に接続される配線と、一端が前記配線に接続されて他端が前記開口部内に露出されたインナーリードとを有する基板を形成する工程と、

前記基板の一面に、同電位の2以上の電極パッドを含む電極パッド群を有する半導体チップを搭載し、前記電極パッド群を前記開口部から露出するように配置する工程と、

前記インナーリードの一つと、前記同電位の2以上の電極パッドとを接続する接続工程とを備えることを特徴とする半導体装置の製造方法。

【請求項11】

前記基板を形成する工程において、前記開口部内に跨って延在するインナーリードを形成し、

前記接続工程を行う前に、前記開口部内で前記インナーリードを切断する工程を含むことを特徴とする請求項10に記載の半導体装置の製造方法。

【請求項12】

前記接続工程において、前記同電位の2以上の電極パッドのうち、前記インナーリードに接続された配線との距離が最も遠い電極パッドが前記インナーリードの端部に配置されるように接続することを特徴とする請求項10または請求項11に記載の半導体装置の製造方法。

【請求項13】

前記接続工程において、前記同電位の2以上の電極パッドのうち、前記インナーリードに接続された配線との距離が近い電極パッドから順に前記インナーリードに接続することを特徴とする請求項10〜請求項12のいずれか一項に記載の半導体装置の製造方法。

【図1】

【図2】

【図3A】

【図3B】

【図3C】

【図3D】

【図3E】

【図3F】

【図4A】

【図4B】

【図4C】

【図5】

【図6】

【図7】

【図2】

【図3A】

【図3B】

【図3C】

【図3D】

【図3E】

【図3F】

【図4A】

【図4B】

【図4C】

【図5】

【図6】

【図7】

【公開番号】特開2012−43888(P2012−43888A)

【公開日】平成24年3月1日(2012.3.1)

【国際特許分類】

【出願番号】特願2010−182334(P2010−182334)

【出願日】平成22年8月17日(2010.8.17)

【出願人】(500174247)エルピーダメモリ株式会社 (2,599)

【Fターム(参考)】

【公開日】平成24年3月1日(2012.3.1)

【国際特許分類】

【出願日】平成22年8月17日(2010.8.17)

【出願人】(500174247)エルピーダメモリ株式会社 (2,599)

【Fターム(参考)】

[ Back to top ]