半導体装置および半導体装置の製造方法

【課題】トンネルウィンドウやセレクトゲートの加工寸法のばらつき、およびセレクトゲートのアライメント精度を考慮する必要がなく、セルサイズを小さくすることができる半導体装置およびその製造方法を提供すること。

【解決手段】不揮発性メモリセル7を半導体基板2上に選択的に備える半導体装置1が製造される。この製造方法は、ゲート絶縁膜23上において不揮発性メモリセル7用のアクティブ領域5に、セレクトゲート19を選択的に形成する工程と、セレクトゲート19に対して自己整合的に導入することによってn型トンネル拡散層11を形成する工程と、ゲート絶縁膜23の一部セレクトゲート19に対して自己整合的に除去し、その後の熱酸化によりトンネルウィンドウ25を形成する工程とを含む。

【解決手段】不揮発性メモリセル7を半導体基板2上に選択的に備える半導体装置1が製造される。この製造方法は、ゲート絶縁膜23上において不揮発性メモリセル7用のアクティブ領域5に、セレクトゲート19を選択的に形成する工程と、セレクトゲート19に対して自己整合的に導入することによってn型トンネル拡散層11を形成する工程と、ゲート絶縁膜23の一部セレクトゲート19に対して自己整合的に除去し、その後の熱酸化によりトンネルウィンドウ25を形成する工程とを含む。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、トンネル拡散層を有する不揮発性メモリセルを備えた半導体装置およびその製造方法に関する。

【背景技術】

【0002】

FLOTOX(Floating Gate Tunnel Oxide)型EEPROM(Electrically Erasable and Programmable ROM)は、スタックド・ゲート型メモリセルトランジスタと、これに直列に接続された選択トランジスタとで不揮発性メモリセルを構成した半導体メモリである。

EEPROMは、半導体基板上に形成されたゲート絶縁膜において、データの書込み/消去時に電子の通り道となる部分に、その周囲のゲート絶縁膜に比べて薄く形成されたトンネルウィンドウを有している。このトンネルウィンドウ上にはフローティングゲートが形成されており、ゲート絶縁膜においてトンネルウィンドウから間隔を空けた部分にはセレクト(選択)ゲートが形成されている。そして、トンネルウィンドウ、フローティングゲートおよびセレクトゲートは、たとえば、特許文献1の方法により形成することができる。

【0003】

特許文献1の方法では、シリコンからなる基材(ウエハ)の表面に複数の素子形成領域を形成し、各素子形成領域を酸化することによりゲート酸化膜を形成する。次に、或る素子形成領域のゲート酸化膜を部分的にエッチングすることにより、厚さを減じたトンネル酸化膜を形成する。さらに基材の内部側に、イオン注入してチャネルを生成し、n−化した第1および第2のメモリセル拡散層を形成する。次に、ゲート酸化膜上にポリシリコン層を成長させる。そして、このポリシリコン層をレジストパターンでマスキングし、エッチングして所定パターンのポリシリコン層とする。これにより、残ったポリシリコン層からなるフローティングゲートおよびセレクトゲートが、ゲート酸化膜上に同時に形成される。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2011−71381号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

EEPROMにおいてセレクトゲートがトンネル酸化膜(トンネルウィンドウ)を覆うように形成されていると、データの書込み/消去時にセレクトゲートに高電圧(たとえば15V以上)が印加されるため、薄いトンネル酸化膜が破壊され、動作不良を引き起こすおそれがある。

そのため、従来は、トンネル酸化膜やセレクトゲートの加工寸法のばらつき、セレクトゲートを形成するときのトンネル酸化膜に対するアライメント精度等を考慮して、トンネル酸化膜とセレクトゲートとの間に比較的大きなマージンができるようにセルを設計していた。加工寸法のばらつきに関して、たとえば、トンネル酸化膜は、ゲート絶縁膜の一部をウエットエッチングし、それにより露出した半導体基板を再度熱酸化して形成するが、ウエットエッチングは等方性エッチングなので、開口のサイズが設計通りにすることが難しい。その結果、そのマージン分、セルサイズが大きくなり、チップコストが増加するという問題があった。

【0006】

そこで、本発明の目的は、トンネルウィンドウやセレクトゲートの加工寸法のばらつき、およびセレクトゲートのアライメント精度を考慮する必要がなく、セルサイズを小さくすることができる半導体装置およびその製造方法を提供することである。

【課題を解決するための手段】

【0007】

本発明の半導体装置は、不揮発性メモリセルを半導体基板上に選択的に備える半導体装置であって、前記半導体基板上に形成されたゲート絶縁膜と、前記ゲート絶縁膜上において前記不揮発性メモリセル用の領域に、選択的に形成されたセレクトゲートと、前記ゲート絶縁膜上において前記不揮発性メモリセル用の領域に、選択的に形成されたフローティングゲートと、前記半導体基板において前記フローティングゲートの一部に対向し、前記セレクトゲートに対して自己整合的に形成されたトンネル拡散層と、前記ゲート絶縁膜において前記フローティングゲートと前記トンネル拡散層との間の部分に前記セレクトゲートに対して自己整合的に形成され、前記ゲート絶縁膜の他の部分よりも薄くされたトンネルウィンドウとを含む(請求項1)。

【0008】

本発明の半導体装置は、不揮発性メモリセルを半導体基板上に選択的に備える半導体装置の製造方法であって、前記半導体基板上にゲート絶縁膜を形成する工程と、前記ゲート絶縁膜上において前記不揮発性メモリセル用の領域に、セレクトゲートを選択的に形成する工程と、前記半導体基板において前記不揮発性メモリセル用の領域に、不純物を前記セレクトゲートに対して自己整合的に導入することによってトンネル拡散層を形成する工程と、前記ゲート絶縁膜において前記トンネル拡散層上の部分を前記セレクトゲートに対して自己整合的に除去し、その後、露出した前記半導体基板を熱酸化することにより、前記ゲート絶縁膜の他の部分よりも薄くされたトンネルウィンドウを形成する工程と、前記トンネルウィンドウを挟んで前記トンネル拡散層に対向するように、前記ゲート絶縁膜上にフローティングゲートを選択的に形成する工程とを含む、本発明の半導体装置の製造方法(請求項5)により製造することができる。

【0009】

この方法によれば、トンネルウィンドウの形成に先立ってセレクトゲートを形成し、そのセレクトゲートに対して自己整合的(セルフアライン)にトンネル拡散層およびトンネルウィンドウを形成するので、トンネルウィンドウやセレクトゲートの加工寸法のばらつき、およびセレクトゲートのアライメント精度による影響を無視することができる。そのため、不揮発性メモリセルを設計するにあたり、トンネルウィンドウに対するセレクトゲートのマージンをなくして、セルサイズを小さくすることができる。

【0010】

また、本発明の半導体装置の製造方法では、前記トンネルウィンドウを形成する工程は、前記ゲート絶縁膜上に、前記セレクトゲートを被覆するようにレジスト膜を形成する工程と、前記レジスト膜において、前記トンネル拡散層を形成すべき領域を露出させる開口を形成する工程であって、前記開口の周縁が、前記セレクトゲートにおける前記トンネル拡散層を形成すべき領域側の端部に対して前記セレクトゲートの内側に後退した位置に画成されるように前記開口を形成する工程と、前記レジスト膜をマスクとして用いて前記ゲート絶縁膜の一部を除去する工程とを含むことが好ましい(請求項6)。

【0011】

この方法によれば、開口の周縁とセレクトゲートの端部との間にマージンができるように、周縁がセレクトゲートの内側に後退(セットバック)して画成されるように開口を形成する。これにより、レジスト膜を露光・現像する際に露光ずれが生じ、当該開口がセットバック位置よりもセレクトゲートの外側に前進した位置に形成されても、開口の周縁がセレクトゲートよりも外側に画成されて、セレクトゲートがレジスト膜で完全に覆われることを防止することができる。すなわち、レジスト膜の開口にセレクトゲートの一部を確実に露出させることができるので、効率よくトンネルウィンドウをセレクトゲートに対して自己整合的に形成することができる。

【0012】

また、本発明の半導体装置では、前記フローティングゲートは、前記セレクトゲートよりも薄いことが好ましい(請求項2)。

この構成の半導体装置は、前記フローティングゲートを形成する工程が、前記セレクトゲートを形成する工程とは別工程において、前記セレクトゲートよりも薄いフローティングゲートで形成する工程を含む、本発明の半導体装置の製造方法(請求項7)により製造することができる。

【0013】

この方法によれば、フローティングゲート上に層間絶縁膜を形成する際に、層間絶縁膜に発生する段差を小さくすることができる。

また、本発明の半導体装置は、前記半導体基板上に、ソース領域およびドレイン領域よりも深い領域まで広がり、前記ソース領域および前記ドレイン領域よりも低不純物濃度の低濃度層を有するMOSトランジスタを選択的にさらに備え、前記ゲート絶縁膜上において前記MOSトランジスタ用の領域に選択的に形成され、前記セレクトゲートと同じ厚さのMOSゲートを含むことが好ましい(請求項3)。そして、前記セレクトゲートおよび前記MOSゲートの厚さは、具体的には、5000Å〜6000Åであることが好ましい(請求項4)。

【0014】

この構成の半導体装置は、前記半導体基板上に、ソース領域およびドレイン領域よりも深い領域まで広がり、前記ソース領域および前記ドレイン領域よりも低不純物濃度の低濃度層を有するMOSトランジスタを選択的に形成する工程をさらに含み、前記MOSトランジスタを形成する工程は、前記セレクトゲートを形成する工程と同一工程で実行され、前記ゲート絶縁膜上において前記MOSトランジスタ用の領域に、前記セレクトゲートと同じ厚さのMOSゲートを選択的に形成する工程と、前記半導体基板において前記MOSトランジスタ用の領域に、前記MOSゲートの上から不純物を導入することによって前記低濃度層を形成する工程と、前記半導体基板において前記MOSトランジスタ用の領域に、前記MOSゲートの上から不純物を導入することによって、前記低濃度層内に前記ソース領域および前記ドレイン領域を形成する工程とを含む、本発明の半導体装置の製造方法(請求項8)により製造することができる。

【0015】

この方法により、MOSトランジスタ用の領域において、いわゆるDDD(Double Diffused Drain)構造を形成できる。MOSトランジスタを高耐圧仕様とする場合には、このDDD構造とするとよい。また、この方法によれば、MOSゲートの厚さをセレクトゲートの厚さとともに適当な大きさにすることにより、低濃度層、ソース領域およびドレイン領域を形成する際に、不純物がMOSゲートを突き抜けることを防止することができる。

【図面の簡単な説明】

【0016】

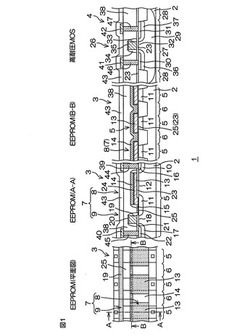

【図1】図1は、本発明の一実施形態に係る半導体装置の構成を説明するための模式図である。

【図2A】図2Aは、図1の半導体装置の製造工程の一部を説明するための模式図である。

【図2B】図2Bは、図2Aの次の工程を示す図である。

【図2C】図2Cは、図2Bの次の工程を示す図である。

【図2D】図2Dは、図2Cの次の工程を示す図である。

【図2E】図2Eは、図2Dの次の工程を示す図である。

【図2F】図2Fは、図2Eの次の工程を示す図である。

【図2G】図2Gは、図2Fの次の工程を示す図である。

【図2H】図2Hは、図2Gの次の工程を示す図である。

【図2I】図2Iは、図2Hの次の工程を示す図である。

【図2J】図2Jは、図2Iの次の工程を示す図である。

【図2K】図2Kは、図2Jの次の工程を示す図である。

【図2L】図2Lは、図2Kの次の工程を示す図である。

【図2M】図2Mは、図2Lの次の工程を示す図である。

【図2N】図2Nは、図2Mの次の工程を示す図である。

【発明を実施するための形態】

【0017】

以下では、本発明の実施の形態を、添付図面を参照して詳細に説明する。

図1は、本発明の一実施形態に係る半導体装置1の構成を説明するための模式図であって、紙面左から順に不揮発性メモリセル7の平面図、当該平面図のA−A断面、当該平面図のB−B断面および高耐圧DDD−MOSトランジスタ26の断面図をそれぞれ示している。

【0018】

半導体装置1は、たとえばシリコンからなるp型の半導体基板2と、この半導体基板2に設定されたメモリセル領域3と、このメモリセル領域3の周辺に配置された周辺回路領域4とを含む。なお、これらの領域3,4の配置形態は、適宜変更することができる。

メモリセル領域3には、互いに間隔を空けて配置(たとえば、行列状に配置)された複数のアクティブ領域5と、当該アクティブ領域5以外の部分に素子分離部6が設定されている。素子分離部6は、図1に示すように、半導体基板2の表面から比較的浅く掘り下がった溝に絶縁体が埋設されたSTI(Shallow Trench Isolation)構造を有するものであってもよいし、たとえば、LOCOS(Local Oxidation of Silicon)法により半導体基板2の表面に選択的に形成されたシリコン酸化膜であってもよい。

【0019】

素子分離部6により区画された複数のアクティブ領域5には、それぞれ不揮発性メモリセル7(EEPROM)が1つずつ設けられている。これにより、メモリセル領域3には、複数の不揮発性メモリセル7が行列状に配列されている。

各不揮発性メモリセル7は、スタックド・ゲート型のメモリセルトランジスタ8と、選択トランジスタ9とを直列接続した構成を有している。

【0020】

より具体的には、メモリセルトランジスタ8は、半導体基板2の表層部に間隔を開けて形成されたn型ソース領域10およびn型トンネル拡散層11と、これらの間のチャネル領域12に対向するように配置されたフローティングゲート13と、このフローティングゲート13に積層されたコントロールゲート14とを備えている。フローティングゲート13の厚さは、1000Å〜1500Åであり、コントロールゲート14の厚さは、1000Å〜1500Åである。

【0021】

フローティングゲート13は、各アクティブ領域5に1つずつ設けられている。一方、コントロールゲート14は、アクティブ領域5の長手方向に交差する方向(この実施形態では、直交方向)に延びるライン状に形成され、複数のアクティブ領域5に跨っていて、全てのフローティングゲート13を一括して覆っている。つまり、コントロールゲート14は、複数の不揮発性メモリセル7の共通の電極となっている。フローティングゲート13およびコントロールゲート14の両側面は、酸化シリコン等の絶縁物からなるサイドウォール15で一括して覆われている。

【0022】

n型ソース領域10の内方には、n型不純物を高濃度に拡散して形成したコンタクト領域16が形成されている。

n型トンネル拡散層11は、フローティングゲート13の一部に対向する領域に形成されており、また、メモリセルトランジスタ8のドレイン領域として機能する。

一方、選択トランジスタ9は、n型トンネル拡散層11をそのソース領域とし、これに対して所定間隔だけ隔てて半導体基板2に形成されたn型ドレイン領域17と、n型トンネル拡散層11とn型ドレイン領域17との間のチャネル領域18に対向するよう配置されたセレクトゲート19(選択ゲート)とを備えている。セレクトゲート19の厚さは、フローティングゲート13およびコントロールゲート14よりも厚く、5000Å〜6000Åである。

【0023】

セレクトゲート19は、アクティブ領域5の長手方向に交差する方向(この実施形態では、直交方向)に延びるライン状に形成され、複数のアクティブ領域5に跨っている。つまり、セレクトゲート19は、複数の不揮発性メモリセル7の共通の電極となっている。また、セレクトゲート19の上面には、後述するトンネルウィンドウ25と同じ厚さの薄膜状の絶縁膜20が形成されている。

【0024】

そして、この実施形態では、n型トンネル拡散層11は、セレクトゲート19に対して自己整合的に形成されている。

また、選択トランジスタ9のセレクトゲート19の両側面も、フローティングゲート13およびコントロールゲート14と同様に、酸化シリコン等の絶縁物からなるサイドウォール21で覆われている。

【0025】

また、選択トランジスタ9のn型ドレイン領域17には、n型不純物を高濃度に拡散して形成したコンタクト領域22が形成されている。

半導体基板2とフローティングゲート13およびセレクトゲート19との間には、たとえば酸化シリコンからなるゲート絶縁膜23が介在されている。また、フローティングゲート13とコントロールゲート14との間は、絶縁膜24によって絶縁されている。この絶縁膜24は、たとえば、窒化シリコン膜を一対の酸化シリコン膜で挟み込んだONO(酸化膜-窒化膜-酸化膜)構造の膜からなる。

【0026】

ゲート絶縁膜23において、n型トンネル拡散層11と、フローティングゲート13との間の部分には、たとえば、膜厚50Å〜100Åの薄膜部が形成されている。

この薄膜部は、n型トンネル拡散層11とフローティングゲート13との間で、FN(ファウラー・ノルドハイム)トンネリングによって電子を通過させるためのトンネルウィンドウ25である。この実施形態では、トンネルウィンドウ25もn型トンネル拡散層11と同様に、セレクトゲート19に対して自己整合的に形成されている。

【0027】

フローティングゲート13に対する電子の注入は、たとえば、ソースをオープンとするとともに、セレクトゲート19に高電圧を印加して選択トランジスタ9をオン状態として行われる。この状態で、コントロールゲート14に高電圧を印加し、ドレインをグランド電位とすると、n型トンネル拡散層11からトンネルウィンドウ25を介するFNトンネリングによって、フローティングゲート13に電子が注入される。

【0028】

フローティングゲート13からの電子の引き抜きは、たとえば、ソースをオープンとするとともに、セレクトゲート19に高電圧を印加して選択トランジスタ9をオン状態として行われる。この状態で、コントロールゲート14をグランド電位とし、ドレインに高電圧を印加すると、フローティングゲート13からトンネルウィンドウ25を介するFNトンネリングによって、n型トンネル拡散層11へと電子が引き抜かれる。

【0029】

フローティングゲート13に電子が注入されると、このフローティングゲート13が帯電している状態では、メモリセルトランジスタ8を導通させるためにコントロールゲート14に印加すべき閾値電圧が高くなる。そこで、コントロールゲート14に与えるべき読出電圧を、フローティングゲート13が非帯電状態(電子が引き抜かれた状態)のときにn型ソース領域10−n型トンネル拡散層11間を導通させることができ、かつ、フローティングゲート13が帯電状態(電子が注入された状態)のときにn型ソース領域10−n型トンネル拡散層11間が遮断状態に保持される値に設定しておく。そして、選択トランジスタ9のセレクトゲート19をハイレベルとし、ドレインをハイレベルとし、コントロールゲート14に前記読出電圧を印加する。このとき、ソース側に電流が流れるか否かを調べることにより、フローティングゲート13に電子が注入されているかどうかを区別できる。

【0030】

こうして、不揮発性メモリセル7に対する情報の書き込み、消去および読み出しの各動作を行うことができる。

周辺回路領域4は、たとえば、メモリセル領域3内の不揮発性メモリセル7に対して、選択的に、書き込み、読み出しおよび消去の各動作を行うためのデコーダ回路である。不揮発性メモリセル7は高耐圧仕様であるため、周辺回路領域4には、デコーダを構成する高耐圧仕様のMOSトランジスタ26が配置されている。この高耐圧仕様のMOSトランジスタはDDD構造を有している。

【0031】

DDD−MOSトランジスタ26は、メモリセル領域3と同様の素子分離部28により区画されたアクティブ領域27に形成されている。DDD−MOSトランジスタ26は、p型ウェル29と、p型ウェル29内の半導体基板2の表層領域に間隔を開けて形成されたn型ソース領域30およびn型ドレイン領域31を備えている。n型ソース領域30およびn型ドレイン領域31の間のチャネル領域32に対向するように、ゲート絶縁膜23を挟んでMOSゲート33が形成されている。MOSゲート33の厚さは、セレクトゲート19と同じ厚さ(5000Å〜6000Å)である。MOSゲート33の両側面は、酸化シリコン等の絶縁物からなるサイドウォール34で覆われている。また、MOSゲート33の上面には、トンネルウィンドウ25と同じ厚さの薄膜状の絶縁膜35が形成されている。

【0032】

n型ソース領域30およびn型ドレイン領域31は、サイドウォール34の直下から広がるn型低濃度層36,37内にそれぞれ形成されており、こうして、二重拡散ドレイン(DDD)構造が形成されている。n型低濃度層36,37は、ソース・ドレイン領域30,31よりも低濃度に形成され、かつ、これらよりも深く不純物イオンを注入して形成した領域である。n型低濃度層36,37は、MOSゲート33に対して自己整合的に形成されている。また、ソース・ドレイン領域30,31は、サイドウォール34に対して自己整合的に形成されている。n型低濃度層36,37は、n型ドレイン領域31の近傍における電界を緩和して、ホットエレクトロン効果を抑制する。

【0033】

半導体基板2上には、酸化シリコン等の絶縁物からなる層間絶縁膜38が積層されている。層間絶縁膜38により、セレクトゲート19、フローティングゲート13、コントロールゲート14およびMOSゲート33が一括して被覆されている。

層間絶縁膜38上には、アルミニウム等の導電材からなるソース電極39,41およびドレイン電極40,42が形成されており、さらにソース電極39,41およびドレイン電極40,42を被覆するように、窒化シリコン等の絶縁物からなる表面保護膜43が形成されている。層間絶縁膜38には、ソース電極39,41およびドレイン電極40,42と、コンタクト領域16,22およびソース・ドレイン領域30,31とをそれぞれ接続するためのコンタクトプラグ44〜47が埋設されている。

【0034】

図2A〜図2Nは、図1の半導体装置1の製造工程の一部を工程順に説明するための模式図である。

まず、図2Aに示すように、LOCOS法またはSTI法により、半導体基板2に素子分離部6,28が形成される。これにより、個々の不揮発性メモリセル7用のアクティブ領域5、個々のDDD−MOSトランジスタ26用のアクティブ領域27がそれぞれ確保される。次に、周辺回路領域4に選択的にB+(ボロン)を注入することにより、p型ウェル29が形成される。

【0035】

次に、図2Bに示すように、半導体基板2の表面を熱酸化することによって、たとえば、膜厚200Å〜400Åの酸化シリコン膜が形成され、これがゲート絶縁膜23となる。このゲート絶縁膜23は、DDD−MOSトランジスタ26のゲート絶縁膜23としてそのまま使用される。

次に、図2Cに示すように、セレクトゲート19およびMOSゲート33形成工程が行われる。すなわち、メモリセル領域3において、ゲート絶縁膜23上に選択トランジスタ9のセレクトゲート19が選択的に形成され、同時に、周辺回路領域4において、ゲート絶縁膜23上にDDD−MOSトランジスタ26のMOSゲート33が形成される。

【0036】

セレクトゲート19およびMOSゲート33の形成は、たとえば、導電化のための不純物(たとえばリン)を添加したポリシリコン膜を半導体基板2の全面に形成し、これをフォトリソグラフィでパターニングすることによって行える。すなわち、全面に形成されたポリシリコン膜上に、レジスト膜のパターンを形成する。このレジスト膜のパターンは、セレクトゲート19およびMOSゲート33を形成すべき領域を選択的に被覆し、その他の領域を露出させるパターンである。このレジスト膜をマスクとしてエッチングを行うことにより、導電化されたポリシリコン膜からなるセレクトゲート19およびMOSゲート33を同じ厚さで同時に形成することができる。

【0037】

次に、図2Dに示すように、n型トンネル拡散層11を形成するためのイオン注入(トンネル接合)が行われる。具体的には、半導体基板2上に所定のパターンのレジスト膜48が形成され、このレジスト膜48をマスクとして、n型不純物イオンが半導体基板2に注入される。

レジスト膜48は、不揮発性メモリセル7用のアクティブ領域5においてn型トンネル拡散層11を形成すべき領域に開口49を有している。この開口49は、その周縁50が、セレクトゲート19の幅方向(長手方向に直交する方向)においてセレクトゲート19のn型トンネル拡散層11を形成すべき領域側の端部51に対して、セレクトゲート19の内側に後退した位置(セレクトゲート19の上面上)に画成されるように形成される。

【0038】

これにより、レジスト膜48を露光・現像する際に露光ずれが生じ、当該開口49がセットバック位置よりもセレクトゲート19の外側に前進した位置に形成されても、開口49の周縁50がセレクトゲート19よりも外側に画成されて、セレクトゲート19がレジスト膜48で完全に覆われること(図2Dの破線48参照)を防止することができる。すなわち、レジスト膜48の開口49にセレクトゲート19の一部(上面および側面)を確実に露出させることができる。そのため、次の図2Eの工程で、ゲート絶縁膜23におけるトンネルウィンドウ25を形成すべき領域を除去するときに、当該領域をセレクトゲート19に対して確実に自己整合的に除去することができる。その結果、効率よくトンネルウィンドウ25をセレクトゲート19に対して自己整合的に形成することができる。

【0039】

そして、このようにセレクトゲート19の一部が露出した状態でイオンを注入するので、注入により半導体基板2に現れるn型トンネル拡散層11は、セレクトゲート19に対して自己整合的に形成される。また、たとえば、n型不純物イオンとしてAs+イオンまたはP+イオンが用いられ、そのドーズ量は1×1014〜1×1015/cm2とされ、その注入エネルギーは100keV〜200keVとされる。

【0040】

次の工程は、図2Eおよび図2Fに示すように、トンネルウィンドウ25の形成である。レジスト膜48を残した状態で、このレジスト膜48をマスクとしたウエットエッチングによって、開口49から露出するゲート絶縁膜23が、セレクトゲート19に対して自己整合的に除去される。レジスト膜48を除去した後、熱酸化法によって、電子をFNトンネリングさせることができる所定膜厚(50Å〜100Å)だけ酸化膜を成長させる。これにより、当該膜厚からなる薄膜のトンネルウィンドウ25が、セレクトゲート19に対して自己整合的に形成され、ゲート絶縁膜23も同じ膜厚だけ厚膜化される。トンネルウィンドウ25以外の領域における最終的なゲート絶縁膜23の膜厚は、たとえば、200Å〜300Åである。また、熱酸化の際に露出しているポリシリコンからなるセレクトゲート19およびMOSゲート33も熱酸化され、これらのゲートの表面(上面および側面)にトンネルウィンドウ25と同じ膜厚だけの絶縁膜20,35が同時に形成される。こうして、局所的な薄膜部(残余の部分よりも膜厚の小さい部分)であるトンネルウィンドウ25を有するゲート絶縁膜23が、メモリセル領域3および周辺回路領域4の半導体基板2表面に形成される。

【0041】

次に、図2G〜図2Iに示すように、フローティングゲート13およびコントロールゲート14形成工程が行われる。すなわち、メモリセル領域3において、ゲート絶縁膜23上に、セレクトゲート19とは間隔を開けて、フローティングゲート13、ONO構造の絶縁膜24およびコントロールゲート14の積層構造が形成される。フローティングゲート13は、n型トンネル拡散層11と重なり合う領域を有し、この領域において、トンネルウィンドウ25を挟んでn型トンネル拡散層11に対向するように形成される。

【0042】

フローティングゲート13およびコントロールゲート14の形成は、まず、図2Gに示すように、導電化のための不純物(たとえばリン)を添加したポリシリコン膜52を半導体基板2の全面に形成し、これをフォトリソグラフィでパターニングすることによって行える。すなわち、全面に形成されたポリシリコン膜52上に、レジスト膜53のパターンを形成する。このレジスト膜53のパターンは、互いに隣り合う不揮発性メモリセル7用のアクティブ領域5の間の領域を選択的に露出させ、その他の領域を被覆するパターンである。このレジスト膜53をマスクとしてエッチングを行うことにより、ポリシリコン膜52において隣り合う不揮発性メモリセル7用のアクティブ領域5の間にスペース54を形成することができる。また、ポリシリコン膜52は、セレクトゲート19の形成時に成膜したポリシリコン膜よりも薄くなるように成膜する。

【0043】

次に、図2Hに示すように、たとえば、CVD(化学的気相成長)法によって、半導体基板2の全面に絶縁膜が形成される。具体的には、まず、膜厚100Å程度の酸化シリコン膜が形成され、次いで、膜厚100Å程度の窒化シリコン膜が形成され、引き続き、膜厚100Å程度の酸化シリコン膜が形成される。こうして、酸化膜/窒化膜/酸化膜構造(ONO構造)の絶縁膜24が形成される。

【0044】

次の工程は、コントロールゲート14形成工程である。具体的には、導電化のための不純物(たとえばリン)を添加したポリシリコン膜55が半導体基板2の全面に形成される。

そして、図2Iに示すように、コントロールゲート14用のポリシリコン膜55、ONO構造の絶縁膜24およびフローティングゲート13用のポリシリコン膜52を一括でパターニングする。一括パターニングは、フォトリソグラフィによって行われる。すなわち、コントロールゲート14用のポリシリコン膜55上に、レジスト膜56を形成する。このレジスト膜56のパターンは、コントロールゲート14を形成すべき領域(フローティングゲート13はこの領域内に収まる)を選択的に被覆し、その他の領域を露出させるパターンである。このレジスト膜56をマスクとしてエッチングを行うことにより、フローティングゲート13、ONO構造の絶縁膜24およびコントロールゲート14の積層構造を一括して形成することができる。この際、セレクトゲート19およびMOSゲート33はレジスト膜56から露出しているが、これらのゲート19,33の表面はトンネルウィンドウ25と同時に形成された絶縁膜20,35に覆われているので、ポリシリコン膜52,55とのエッチング選択比を大きくすることによりエッチングされることを防止することができる。

【0045】

次の工程は、図2Jに示すように、n型ソース領域10、n型ドレイン領域17およびn型低濃度層36,37の形成である。すなわち、レジスト膜57をマスクとして、半導体基板2の表面に向けて選択的にn型不純物イオンが注入される。レジスト膜57は、不揮発性メモリセル7用のアクティブ領域5においてn型ソース領域10およびn型ドレイン領域17に対応する領域を露出させ、DDD−MOSトランジスタ26用のアクティブ領域27においてn型低濃度層36,37に対応する部分を露出させるパターンである。このレジスト膜57をマスクとしてn型不純物イオンを注入することによって、不揮発性メモリセル7用のアクティブ領域5にn型ソース領域10およびn型ドレイン領域17が形成され、DDD−MOSトランジスタ26用のアクティブ領域27では、MOSゲート33の両側にn型低濃度層36,37がそれぞれ形成される。たとえば、n型不純物イオンとしてAs+イオンまたはP+イオンが用いられ、そのドーズ量は1×1012〜1×1013/cm2とされ、その注入エネルギーは50keV〜100keVとされる。こうして、選択トランジスタ9のn型ソース領域10およびn型ドレイン領域17の形成のためのイオン注入と同工程で、DDD−MOSトランジスタ26のn型低濃度層36,37が形成される。この際、MOSゲート33をセレクトゲート19と同工程で比較的厚く形成したので、n型不純物がMOSゲート33を突き抜けることを防止することができる。

【0046】

レジスト膜57を剥離した後、図2Kに示すように、サイドウォール15,21,34形成工程が行われる。すなわち、たとえば、CVD法によって、半導体基板2の全面に酸化シリコン膜等の絶縁膜が形成された後、その絶縁膜がドライエッチングによってエッチバックされる。このエッチバックを、セレクトゲート19、コントロールゲート14およびMOSゲート33が露出するまで行うと、それらの各両側面にサイドウォール15,21,34が形成される。

【0047】

次に、図2Lに示すように、ソース−ドレイン注入工程が行われる。すなわち、レジスト膜58をマスクとして、半導体基板2の表面に向けて選択的にn型不純物イオンが注入される。レジスト膜58は、不揮発性メモリセル7用のアクティブ領域5においてn型ソース領域10およびn型ドレイン領域17の内方の一部を露出させ、DDD−MOSトランジスタ26用のアクティブ領域27において低濃度層36,37の内方の一部の領域(ソース・ドレイン領域30,31の対応領域)をそれぞれ露出させるパターンである。したがって、レジスト膜58をマスクとしてn型不純物イオンを注入することによって、不揮発性メモリセル7のコンタクト領域16,22が形成され、DDDトランジスタのソース・ドレイン領域30,31が形成される。たとえば、n型不純物イオンとしてAs+イオンが用いられ、そのドーズ量は、n型トンネル拡散層11のためのイオン注入(図2D)のときよりも多く、たとえば、1×1015〜1×1016/cm2とされる。または、注入エネルギーは、n型トンネル拡散層11のための注入(図2D)およびDDD注入(図2J)のときよりも小さく、たとえば、40keV〜70keVとされる。この際も、MOSゲート33をセレクトゲート19と同工程で比較的厚く形成したので、n型不純物がMOSゲート33を突き抜けることを防止することができる。

【0048】

この後は、レジスト膜58を剥離し、図2Mに示すように、全面を覆う層間絶縁膜38が形成され、当該層間絶縁膜38に、コンタクト領域16,22およびソース・ドレイン領域30,31をそれぞれ露出させる複数のコンタクトホール59〜62がレジスト膜63をマスクとしたエッチングにより形成され、図2Nに示すように、これらのコンタクトホール59〜62を介して各領域16,22,30,31にそれぞれ接触する複数のコンタクトプラグ44〜47および電極39〜42が形成される。

【0049】

なお、層間絶縁膜38は複数積層されてもよい。層間絶縁膜38を複数形成する場合でも、図2G〜図2Iの工程でフローティングゲート13およびコントロールゲート14を比較的薄く形成したので、層間絶縁膜38において、コントロールゲート14上に盛り上がった部分と他の部分との間に発生する段差を小さくすることができる。

そして、最上層の層間絶縁膜38上に、表面保護膜43が形成され、表面保護膜43に各電極をワイヤボンディング用のパッドとして露出させる開口(図示せず)が形成される。以上の工程を経て、図1の半導体装置1が得られる。

【0050】

以上のように、この実施形態によれば、トンネルウィンドウ25の形成(図2F)に先立ってセレクトゲート19を形成し(図2C)、そのセレクトゲート19に対して自己整合的(セルフアライン)にn型トンネル拡散層11およびトンネルウィンドウ25を形成するので、トンネルウィンドウ25やセレクトゲート19の加工寸法のばらつき、およびセレクトゲート19のアライメント精度による影響を無視することができる。そのため、不揮発性メモリセル7を設計するにあたり、トンネルウィンドウ25に対するセレクトゲート19のマージンをなくして、セルサイズを小さくすることができる。

【0051】

以上、本発明の一実施形態について説明したが、本発明は、さらに他の形態で実施することもできる。

たとえば、半導体装置1の各半導体部分の導電型を反転した構成が採用されてもよい。たとえば、半導体装置1において、p型の部分がn型であり、n型の部分がp型であってもよい。

【0052】

また、たとえば、前述の実施形態では、DDD−MOSトランジスタ26が半導体基板2上に形成される構成について説明したが、たとえば、半導体基板2上にLDD−MOSトランジスタ形成される構成に対しても本発明を適用することができる。また、前述の実施形態で示したドーズ量等の数値は一例であり、必要とされる仕様に応じて別の値が適用されてもよい。

【0053】

その他、特許請求の範囲に記載された事項の範囲で種々の設計変更を施すことが可能である。

【符号の説明】

【0054】

1 半導体装置

2 半導体基板

3 メモリセル領域

4 周辺回路領域

5 (不揮発性メモリセル用の)アクティブ領域

6 素子分離部

7 不揮発性メモリセル

8 メモリセルトランジスタ

9 選択トランジスタ

10 n型ソース領域

11 n型トンネル拡散層

12 チャネル領域

13 フローティングゲート

14 コントロールゲート

15 サイドウォール

16 (ソース)コンタクト領域

17 n型ドレイン領域

18 チャネル領域

19 セレクトゲート

20 (セレクトゲート上面の)絶縁膜

21 サイドウォール

22 (ドレイン)コンタクト領域

23 ゲート絶縁膜

24 (ONO構造の)絶縁膜

25 トンネルウィンドウ

26 DDD−MOSトランジスタ

27 (DDD−MOSトランジスタ用の)アクティブ領域

28 素子分離部

29 p型ウェル

30 n型ソース領域

31 n型ドレイン領域

32 チャネル領域

33 MOSゲート

34 サイドウォール

35 (MOSゲート上面の)絶縁膜

36 n型低濃度層

37 n型低濃度層

38 層間絶縁膜

39 (不揮発性メモリセル用の)ソース電極

40 (不揮発性メモリセル用の)ドレイン電極

41 (DDD−MOSトランジスタ用の)ソース電極

42 (DDD−MOSトランジスタ用の)ドレイン電極

43 表面保護膜

44 (ソース用)コンタクトプラグ

45 (ドレイン用)コンタクトプラグ

46 (ソース用)コンタクトプラグ

47 (ドレイン用)コンタクトプラグ

48 レジスト膜

49 (レジスト膜の)開口

50 (レジスト膜の)周縁

51 (セレクトゲートの)端部

52 ポリシリコン膜

53 レジスト膜

54 スペース

55 ポリシリコン膜

56 レジスト膜

57 レジスト膜

58 レジスト膜

59 コンタクトホール

60 コンタクトホール

61 コンタクトホール

62 コンタクトホール

63 レジスト膜

【技術分野】

【0001】

本発明は、トンネル拡散層を有する不揮発性メモリセルを備えた半導体装置およびその製造方法に関する。

【背景技術】

【0002】

FLOTOX(Floating Gate Tunnel Oxide)型EEPROM(Electrically Erasable and Programmable ROM)は、スタックド・ゲート型メモリセルトランジスタと、これに直列に接続された選択トランジスタとで不揮発性メモリセルを構成した半導体メモリである。

EEPROMは、半導体基板上に形成されたゲート絶縁膜において、データの書込み/消去時に電子の通り道となる部分に、その周囲のゲート絶縁膜に比べて薄く形成されたトンネルウィンドウを有している。このトンネルウィンドウ上にはフローティングゲートが形成されており、ゲート絶縁膜においてトンネルウィンドウから間隔を空けた部分にはセレクト(選択)ゲートが形成されている。そして、トンネルウィンドウ、フローティングゲートおよびセレクトゲートは、たとえば、特許文献1の方法により形成することができる。

【0003】

特許文献1の方法では、シリコンからなる基材(ウエハ)の表面に複数の素子形成領域を形成し、各素子形成領域を酸化することによりゲート酸化膜を形成する。次に、或る素子形成領域のゲート酸化膜を部分的にエッチングすることにより、厚さを減じたトンネル酸化膜を形成する。さらに基材の内部側に、イオン注入してチャネルを生成し、n−化した第1および第2のメモリセル拡散層を形成する。次に、ゲート酸化膜上にポリシリコン層を成長させる。そして、このポリシリコン層をレジストパターンでマスキングし、エッチングして所定パターンのポリシリコン層とする。これにより、残ったポリシリコン層からなるフローティングゲートおよびセレクトゲートが、ゲート酸化膜上に同時に形成される。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2011−71381号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

EEPROMにおいてセレクトゲートがトンネル酸化膜(トンネルウィンドウ)を覆うように形成されていると、データの書込み/消去時にセレクトゲートに高電圧(たとえば15V以上)が印加されるため、薄いトンネル酸化膜が破壊され、動作不良を引き起こすおそれがある。

そのため、従来は、トンネル酸化膜やセレクトゲートの加工寸法のばらつき、セレクトゲートを形成するときのトンネル酸化膜に対するアライメント精度等を考慮して、トンネル酸化膜とセレクトゲートとの間に比較的大きなマージンができるようにセルを設計していた。加工寸法のばらつきに関して、たとえば、トンネル酸化膜は、ゲート絶縁膜の一部をウエットエッチングし、それにより露出した半導体基板を再度熱酸化して形成するが、ウエットエッチングは等方性エッチングなので、開口のサイズが設計通りにすることが難しい。その結果、そのマージン分、セルサイズが大きくなり、チップコストが増加するという問題があった。

【0006】

そこで、本発明の目的は、トンネルウィンドウやセレクトゲートの加工寸法のばらつき、およびセレクトゲートのアライメント精度を考慮する必要がなく、セルサイズを小さくすることができる半導体装置およびその製造方法を提供することである。

【課題を解決するための手段】

【0007】

本発明の半導体装置は、不揮発性メモリセルを半導体基板上に選択的に備える半導体装置であって、前記半導体基板上に形成されたゲート絶縁膜と、前記ゲート絶縁膜上において前記不揮発性メモリセル用の領域に、選択的に形成されたセレクトゲートと、前記ゲート絶縁膜上において前記不揮発性メモリセル用の領域に、選択的に形成されたフローティングゲートと、前記半導体基板において前記フローティングゲートの一部に対向し、前記セレクトゲートに対して自己整合的に形成されたトンネル拡散層と、前記ゲート絶縁膜において前記フローティングゲートと前記トンネル拡散層との間の部分に前記セレクトゲートに対して自己整合的に形成され、前記ゲート絶縁膜の他の部分よりも薄くされたトンネルウィンドウとを含む(請求項1)。

【0008】

本発明の半導体装置は、不揮発性メモリセルを半導体基板上に選択的に備える半導体装置の製造方法であって、前記半導体基板上にゲート絶縁膜を形成する工程と、前記ゲート絶縁膜上において前記不揮発性メモリセル用の領域に、セレクトゲートを選択的に形成する工程と、前記半導体基板において前記不揮発性メモリセル用の領域に、不純物を前記セレクトゲートに対して自己整合的に導入することによってトンネル拡散層を形成する工程と、前記ゲート絶縁膜において前記トンネル拡散層上の部分を前記セレクトゲートに対して自己整合的に除去し、その後、露出した前記半導体基板を熱酸化することにより、前記ゲート絶縁膜の他の部分よりも薄くされたトンネルウィンドウを形成する工程と、前記トンネルウィンドウを挟んで前記トンネル拡散層に対向するように、前記ゲート絶縁膜上にフローティングゲートを選択的に形成する工程とを含む、本発明の半導体装置の製造方法(請求項5)により製造することができる。

【0009】

この方法によれば、トンネルウィンドウの形成に先立ってセレクトゲートを形成し、そのセレクトゲートに対して自己整合的(セルフアライン)にトンネル拡散層およびトンネルウィンドウを形成するので、トンネルウィンドウやセレクトゲートの加工寸法のばらつき、およびセレクトゲートのアライメント精度による影響を無視することができる。そのため、不揮発性メモリセルを設計するにあたり、トンネルウィンドウに対するセレクトゲートのマージンをなくして、セルサイズを小さくすることができる。

【0010】

また、本発明の半導体装置の製造方法では、前記トンネルウィンドウを形成する工程は、前記ゲート絶縁膜上に、前記セレクトゲートを被覆するようにレジスト膜を形成する工程と、前記レジスト膜において、前記トンネル拡散層を形成すべき領域を露出させる開口を形成する工程であって、前記開口の周縁が、前記セレクトゲートにおける前記トンネル拡散層を形成すべき領域側の端部に対して前記セレクトゲートの内側に後退した位置に画成されるように前記開口を形成する工程と、前記レジスト膜をマスクとして用いて前記ゲート絶縁膜の一部を除去する工程とを含むことが好ましい(請求項6)。

【0011】

この方法によれば、開口の周縁とセレクトゲートの端部との間にマージンができるように、周縁がセレクトゲートの内側に後退(セットバック)して画成されるように開口を形成する。これにより、レジスト膜を露光・現像する際に露光ずれが生じ、当該開口がセットバック位置よりもセレクトゲートの外側に前進した位置に形成されても、開口の周縁がセレクトゲートよりも外側に画成されて、セレクトゲートがレジスト膜で完全に覆われることを防止することができる。すなわち、レジスト膜の開口にセレクトゲートの一部を確実に露出させることができるので、効率よくトンネルウィンドウをセレクトゲートに対して自己整合的に形成することができる。

【0012】

また、本発明の半導体装置では、前記フローティングゲートは、前記セレクトゲートよりも薄いことが好ましい(請求項2)。

この構成の半導体装置は、前記フローティングゲートを形成する工程が、前記セレクトゲートを形成する工程とは別工程において、前記セレクトゲートよりも薄いフローティングゲートで形成する工程を含む、本発明の半導体装置の製造方法(請求項7)により製造することができる。

【0013】

この方法によれば、フローティングゲート上に層間絶縁膜を形成する際に、層間絶縁膜に発生する段差を小さくすることができる。

また、本発明の半導体装置は、前記半導体基板上に、ソース領域およびドレイン領域よりも深い領域まで広がり、前記ソース領域および前記ドレイン領域よりも低不純物濃度の低濃度層を有するMOSトランジスタを選択的にさらに備え、前記ゲート絶縁膜上において前記MOSトランジスタ用の領域に選択的に形成され、前記セレクトゲートと同じ厚さのMOSゲートを含むことが好ましい(請求項3)。そして、前記セレクトゲートおよび前記MOSゲートの厚さは、具体的には、5000Å〜6000Åであることが好ましい(請求項4)。

【0014】

この構成の半導体装置は、前記半導体基板上に、ソース領域およびドレイン領域よりも深い領域まで広がり、前記ソース領域および前記ドレイン領域よりも低不純物濃度の低濃度層を有するMOSトランジスタを選択的に形成する工程をさらに含み、前記MOSトランジスタを形成する工程は、前記セレクトゲートを形成する工程と同一工程で実行され、前記ゲート絶縁膜上において前記MOSトランジスタ用の領域に、前記セレクトゲートと同じ厚さのMOSゲートを選択的に形成する工程と、前記半導体基板において前記MOSトランジスタ用の領域に、前記MOSゲートの上から不純物を導入することによって前記低濃度層を形成する工程と、前記半導体基板において前記MOSトランジスタ用の領域に、前記MOSゲートの上から不純物を導入することによって、前記低濃度層内に前記ソース領域および前記ドレイン領域を形成する工程とを含む、本発明の半導体装置の製造方法(請求項8)により製造することができる。

【0015】

この方法により、MOSトランジスタ用の領域において、いわゆるDDD(Double Diffused Drain)構造を形成できる。MOSトランジスタを高耐圧仕様とする場合には、このDDD構造とするとよい。また、この方法によれば、MOSゲートの厚さをセレクトゲートの厚さとともに適当な大きさにすることにより、低濃度層、ソース領域およびドレイン領域を形成する際に、不純物がMOSゲートを突き抜けることを防止することができる。

【図面の簡単な説明】

【0016】

【図1】図1は、本発明の一実施形態に係る半導体装置の構成を説明するための模式図である。

【図2A】図2Aは、図1の半導体装置の製造工程の一部を説明するための模式図である。

【図2B】図2Bは、図2Aの次の工程を示す図である。

【図2C】図2Cは、図2Bの次の工程を示す図である。

【図2D】図2Dは、図2Cの次の工程を示す図である。

【図2E】図2Eは、図2Dの次の工程を示す図である。

【図2F】図2Fは、図2Eの次の工程を示す図である。

【図2G】図2Gは、図2Fの次の工程を示す図である。

【図2H】図2Hは、図2Gの次の工程を示す図である。

【図2I】図2Iは、図2Hの次の工程を示す図である。

【図2J】図2Jは、図2Iの次の工程を示す図である。

【図2K】図2Kは、図2Jの次の工程を示す図である。

【図2L】図2Lは、図2Kの次の工程を示す図である。

【図2M】図2Mは、図2Lの次の工程を示す図である。

【図2N】図2Nは、図2Mの次の工程を示す図である。

【発明を実施するための形態】

【0017】

以下では、本発明の実施の形態を、添付図面を参照して詳細に説明する。

図1は、本発明の一実施形態に係る半導体装置1の構成を説明するための模式図であって、紙面左から順に不揮発性メモリセル7の平面図、当該平面図のA−A断面、当該平面図のB−B断面および高耐圧DDD−MOSトランジスタ26の断面図をそれぞれ示している。

【0018】

半導体装置1は、たとえばシリコンからなるp型の半導体基板2と、この半導体基板2に設定されたメモリセル領域3と、このメモリセル領域3の周辺に配置された周辺回路領域4とを含む。なお、これらの領域3,4の配置形態は、適宜変更することができる。

メモリセル領域3には、互いに間隔を空けて配置(たとえば、行列状に配置)された複数のアクティブ領域5と、当該アクティブ領域5以外の部分に素子分離部6が設定されている。素子分離部6は、図1に示すように、半導体基板2の表面から比較的浅く掘り下がった溝に絶縁体が埋設されたSTI(Shallow Trench Isolation)構造を有するものであってもよいし、たとえば、LOCOS(Local Oxidation of Silicon)法により半導体基板2の表面に選択的に形成されたシリコン酸化膜であってもよい。

【0019】

素子分離部6により区画された複数のアクティブ領域5には、それぞれ不揮発性メモリセル7(EEPROM)が1つずつ設けられている。これにより、メモリセル領域3には、複数の不揮発性メモリセル7が行列状に配列されている。

各不揮発性メモリセル7は、スタックド・ゲート型のメモリセルトランジスタ8と、選択トランジスタ9とを直列接続した構成を有している。

【0020】

より具体的には、メモリセルトランジスタ8は、半導体基板2の表層部に間隔を開けて形成されたn型ソース領域10およびn型トンネル拡散層11と、これらの間のチャネル領域12に対向するように配置されたフローティングゲート13と、このフローティングゲート13に積層されたコントロールゲート14とを備えている。フローティングゲート13の厚さは、1000Å〜1500Åであり、コントロールゲート14の厚さは、1000Å〜1500Åである。

【0021】

フローティングゲート13は、各アクティブ領域5に1つずつ設けられている。一方、コントロールゲート14は、アクティブ領域5の長手方向に交差する方向(この実施形態では、直交方向)に延びるライン状に形成され、複数のアクティブ領域5に跨っていて、全てのフローティングゲート13を一括して覆っている。つまり、コントロールゲート14は、複数の不揮発性メモリセル7の共通の電極となっている。フローティングゲート13およびコントロールゲート14の両側面は、酸化シリコン等の絶縁物からなるサイドウォール15で一括して覆われている。

【0022】

n型ソース領域10の内方には、n型不純物を高濃度に拡散して形成したコンタクト領域16が形成されている。

n型トンネル拡散層11は、フローティングゲート13の一部に対向する領域に形成されており、また、メモリセルトランジスタ8のドレイン領域として機能する。

一方、選択トランジスタ9は、n型トンネル拡散層11をそのソース領域とし、これに対して所定間隔だけ隔てて半導体基板2に形成されたn型ドレイン領域17と、n型トンネル拡散層11とn型ドレイン領域17との間のチャネル領域18に対向するよう配置されたセレクトゲート19(選択ゲート)とを備えている。セレクトゲート19の厚さは、フローティングゲート13およびコントロールゲート14よりも厚く、5000Å〜6000Åである。

【0023】

セレクトゲート19は、アクティブ領域5の長手方向に交差する方向(この実施形態では、直交方向)に延びるライン状に形成され、複数のアクティブ領域5に跨っている。つまり、セレクトゲート19は、複数の不揮発性メモリセル7の共通の電極となっている。また、セレクトゲート19の上面には、後述するトンネルウィンドウ25と同じ厚さの薄膜状の絶縁膜20が形成されている。

【0024】

そして、この実施形態では、n型トンネル拡散層11は、セレクトゲート19に対して自己整合的に形成されている。

また、選択トランジスタ9のセレクトゲート19の両側面も、フローティングゲート13およびコントロールゲート14と同様に、酸化シリコン等の絶縁物からなるサイドウォール21で覆われている。

【0025】

また、選択トランジスタ9のn型ドレイン領域17には、n型不純物を高濃度に拡散して形成したコンタクト領域22が形成されている。

半導体基板2とフローティングゲート13およびセレクトゲート19との間には、たとえば酸化シリコンからなるゲート絶縁膜23が介在されている。また、フローティングゲート13とコントロールゲート14との間は、絶縁膜24によって絶縁されている。この絶縁膜24は、たとえば、窒化シリコン膜を一対の酸化シリコン膜で挟み込んだONO(酸化膜-窒化膜-酸化膜)構造の膜からなる。

【0026】

ゲート絶縁膜23において、n型トンネル拡散層11と、フローティングゲート13との間の部分には、たとえば、膜厚50Å〜100Åの薄膜部が形成されている。

この薄膜部は、n型トンネル拡散層11とフローティングゲート13との間で、FN(ファウラー・ノルドハイム)トンネリングによって電子を通過させるためのトンネルウィンドウ25である。この実施形態では、トンネルウィンドウ25もn型トンネル拡散層11と同様に、セレクトゲート19に対して自己整合的に形成されている。

【0027】

フローティングゲート13に対する電子の注入は、たとえば、ソースをオープンとするとともに、セレクトゲート19に高電圧を印加して選択トランジスタ9をオン状態として行われる。この状態で、コントロールゲート14に高電圧を印加し、ドレインをグランド電位とすると、n型トンネル拡散層11からトンネルウィンドウ25を介するFNトンネリングによって、フローティングゲート13に電子が注入される。

【0028】

フローティングゲート13からの電子の引き抜きは、たとえば、ソースをオープンとするとともに、セレクトゲート19に高電圧を印加して選択トランジスタ9をオン状態として行われる。この状態で、コントロールゲート14をグランド電位とし、ドレインに高電圧を印加すると、フローティングゲート13からトンネルウィンドウ25を介するFNトンネリングによって、n型トンネル拡散層11へと電子が引き抜かれる。

【0029】

フローティングゲート13に電子が注入されると、このフローティングゲート13が帯電している状態では、メモリセルトランジスタ8を導通させるためにコントロールゲート14に印加すべき閾値電圧が高くなる。そこで、コントロールゲート14に与えるべき読出電圧を、フローティングゲート13が非帯電状態(電子が引き抜かれた状態)のときにn型ソース領域10−n型トンネル拡散層11間を導通させることができ、かつ、フローティングゲート13が帯電状態(電子が注入された状態)のときにn型ソース領域10−n型トンネル拡散層11間が遮断状態に保持される値に設定しておく。そして、選択トランジスタ9のセレクトゲート19をハイレベルとし、ドレインをハイレベルとし、コントロールゲート14に前記読出電圧を印加する。このとき、ソース側に電流が流れるか否かを調べることにより、フローティングゲート13に電子が注入されているかどうかを区別できる。

【0030】

こうして、不揮発性メモリセル7に対する情報の書き込み、消去および読み出しの各動作を行うことができる。

周辺回路領域4は、たとえば、メモリセル領域3内の不揮発性メモリセル7に対して、選択的に、書き込み、読み出しおよび消去の各動作を行うためのデコーダ回路である。不揮発性メモリセル7は高耐圧仕様であるため、周辺回路領域4には、デコーダを構成する高耐圧仕様のMOSトランジスタ26が配置されている。この高耐圧仕様のMOSトランジスタはDDD構造を有している。

【0031】

DDD−MOSトランジスタ26は、メモリセル領域3と同様の素子分離部28により区画されたアクティブ領域27に形成されている。DDD−MOSトランジスタ26は、p型ウェル29と、p型ウェル29内の半導体基板2の表層領域に間隔を開けて形成されたn型ソース領域30およびn型ドレイン領域31を備えている。n型ソース領域30およびn型ドレイン領域31の間のチャネル領域32に対向するように、ゲート絶縁膜23を挟んでMOSゲート33が形成されている。MOSゲート33の厚さは、セレクトゲート19と同じ厚さ(5000Å〜6000Å)である。MOSゲート33の両側面は、酸化シリコン等の絶縁物からなるサイドウォール34で覆われている。また、MOSゲート33の上面には、トンネルウィンドウ25と同じ厚さの薄膜状の絶縁膜35が形成されている。

【0032】

n型ソース領域30およびn型ドレイン領域31は、サイドウォール34の直下から広がるn型低濃度層36,37内にそれぞれ形成されており、こうして、二重拡散ドレイン(DDD)構造が形成されている。n型低濃度層36,37は、ソース・ドレイン領域30,31よりも低濃度に形成され、かつ、これらよりも深く不純物イオンを注入して形成した領域である。n型低濃度層36,37は、MOSゲート33に対して自己整合的に形成されている。また、ソース・ドレイン領域30,31は、サイドウォール34に対して自己整合的に形成されている。n型低濃度層36,37は、n型ドレイン領域31の近傍における電界を緩和して、ホットエレクトロン効果を抑制する。

【0033】

半導体基板2上には、酸化シリコン等の絶縁物からなる層間絶縁膜38が積層されている。層間絶縁膜38により、セレクトゲート19、フローティングゲート13、コントロールゲート14およびMOSゲート33が一括して被覆されている。

層間絶縁膜38上には、アルミニウム等の導電材からなるソース電極39,41およびドレイン電極40,42が形成されており、さらにソース電極39,41およびドレイン電極40,42を被覆するように、窒化シリコン等の絶縁物からなる表面保護膜43が形成されている。層間絶縁膜38には、ソース電極39,41およびドレイン電極40,42と、コンタクト領域16,22およびソース・ドレイン領域30,31とをそれぞれ接続するためのコンタクトプラグ44〜47が埋設されている。

【0034】

図2A〜図2Nは、図1の半導体装置1の製造工程の一部を工程順に説明するための模式図である。

まず、図2Aに示すように、LOCOS法またはSTI法により、半導体基板2に素子分離部6,28が形成される。これにより、個々の不揮発性メモリセル7用のアクティブ領域5、個々のDDD−MOSトランジスタ26用のアクティブ領域27がそれぞれ確保される。次に、周辺回路領域4に選択的にB+(ボロン)を注入することにより、p型ウェル29が形成される。

【0035】

次に、図2Bに示すように、半導体基板2の表面を熱酸化することによって、たとえば、膜厚200Å〜400Åの酸化シリコン膜が形成され、これがゲート絶縁膜23となる。このゲート絶縁膜23は、DDD−MOSトランジスタ26のゲート絶縁膜23としてそのまま使用される。

次に、図2Cに示すように、セレクトゲート19およびMOSゲート33形成工程が行われる。すなわち、メモリセル領域3において、ゲート絶縁膜23上に選択トランジスタ9のセレクトゲート19が選択的に形成され、同時に、周辺回路領域4において、ゲート絶縁膜23上にDDD−MOSトランジスタ26のMOSゲート33が形成される。

【0036】

セレクトゲート19およびMOSゲート33の形成は、たとえば、導電化のための不純物(たとえばリン)を添加したポリシリコン膜を半導体基板2の全面に形成し、これをフォトリソグラフィでパターニングすることによって行える。すなわち、全面に形成されたポリシリコン膜上に、レジスト膜のパターンを形成する。このレジスト膜のパターンは、セレクトゲート19およびMOSゲート33を形成すべき領域を選択的に被覆し、その他の領域を露出させるパターンである。このレジスト膜をマスクとしてエッチングを行うことにより、導電化されたポリシリコン膜からなるセレクトゲート19およびMOSゲート33を同じ厚さで同時に形成することができる。

【0037】

次に、図2Dに示すように、n型トンネル拡散層11を形成するためのイオン注入(トンネル接合)が行われる。具体的には、半導体基板2上に所定のパターンのレジスト膜48が形成され、このレジスト膜48をマスクとして、n型不純物イオンが半導体基板2に注入される。

レジスト膜48は、不揮発性メモリセル7用のアクティブ領域5においてn型トンネル拡散層11を形成すべき領域に開口49を有している。この開口49は、その周縁50が、セレクトゲート19の幅方向(長手方向に直交する方向)においてセレクトゲート19のn型トンネル拡散層11を形成すべき領域側の端部51に対して、セレクトゲート19の内側に後退した位置(セレクトゲート19の上面上)に画成されるように形成される。

【0038】

これにより、レジスト膜48を露光・現像する際に露光ずれが生じ、当該開口49がセットバック位置よりもセレクトゲート19の外側に前進した位置に形成されても、開口49の周縁50がセレクトゲート19よりも外側に画成されて、セレクトゲート19がレジスト膜48で完全に覆われること(図2Dの破線48参照)を防止することができる。すなわち、レジスト膜48の開口49にセレクトゲート19の一部(上面および側面)を確実に露出させることができる。そのため、次の図2Eの工程で、ゲート絶縁膜23におけるトンネルウィンドウ25を形成すべき領域を除去するときに、当該領域をセレクトゲート19に対して確実に自己整合的に除去することができる。その結果、効率よくトンネルウィンドウ25をセレクトゲート19に対して自己整合的に形成することができる。

【0039】

そして、このようにセレクトゲート19の一部が露出した状態でイオンを注入するので、注入により半導体基板2に現れるn型トンネル拡散層11は、セレクトゲート19に対して自己整合的に形成される。また、たとえば、n型不純物イオンとしてAs+イオンまたはP+イオンが用いられ、そのドーズ量は1×1014〜1×1015/cm2とされ、その注入エネルギーは100keV〜200keVとされる。

【0040】

次の工程は、図2Eおよび図2Fに示すように、トンネルウィンドウ25の形成である。レジスト膜48を残した状態で、このレジスト膜48をマスクとしたウエットエッチングによって、開口49から露出するゲート絶縁膜23が、セレクトゲート19に対して自己整合的に除去される。レジスト膜48を除去した後、熱酸化法によって、電子をFNトンネリングさせることができる所定膜厚(50Å〜100Å)だけ酸化膜を成長させる。これにより、当該膜厚からなる薄膜のトンネルウィンドウ25が、セレクトゲート19に対して自己整合的に形成され、ゲート絶縁膜23も同じ膜厚だけ厚膜化される。トンネルウィンドウ25以外の領域における最終的なゲート絶縁膜23の膜厚は、たとえば、200Å〜300Åである。また、熱酸化の際に露出しているポリシリコンからなるセレクトゲート19およびMOSゲート33も熱酸化され、これらのゲートの表面(上面および側面)にトンネルウィンドウ25と同じ膜厚だけの絶縁膜20,35が同時に形成される。こうして、局所的な薄膜部(残余の部分よりも膜厚の小さい部分)であるトンネルウィンドウ25を有するゲート絶縁膜23が、メモリセル領域3および周辺回路領域4の半導体基板2表面に形成される。

【0041】

次に、図2G〜図2Iに示すように、フローティングゲート13およびコントロールゲート14形成工程が行われる。すなわち、メモリセル領域3において、ゲート絶縁膜23上に、セレクトゲート19とは間隔を開けて、フローティングゲート13、ONO構造の絶縁膜24およびコントロールゲート14の積層構造が形成される。フローティングゲート13は、n型トンネル拡散層11と重なり合う領域を有し、この領域において、トンネルウィンドウ25を挟んでn型トンネル拡散層11に対向するように形成される。

【0042】

フローティングゲート13およびコントロールゲート14の形成は、まず、図2Gに示すように、導電化のための不純物(たとえばリン)を添加したポリシリコン膜52を半導体基板2の全面に形成し、これをフォトリソグラフィでパターニングすることによって行える。すなわち、全面に形成されたポリシリコン膜52上に、レジスト膜53のパターンを形成する。このレジスト膜53のパターンは、互いに隣り合う不揮発性メモリセル7用のアクティブ領域5の間の領域を選択的に露出させ、その他の領域を被覆するパターンである。このレジスト膜53をマスクとしてエッチングを行うことにより、ポリシリコン膜52において隣り合う不揮発性メモリセル7用のアクティブ領域5の間にスペース54を形成することができる。また、ポリシリコン膜52は、セレクトゲート19の形成時に成膜したポリシリコン膜よりも薄くなるように成膜する。

【0043】

次に、図2Hに示すように、たとえば、CVD(化学的気相成長)法によって、半導体基板2の全面に絶縁膜が形成される。具体的には、まず、膜厚100Å程度の酸化シリコン膜が形成され、次いで、膜厚100Å程度の窒化シリコン膜が形成され、引き続き、膜厚100Å程度の酸化シリコン膜が形成される。こうして、酸化膜/窒化膜/酸化膜構造(ONO構造)の絶縁膜24が形成される。

【0044】

次の工程は、コントロールゲート14形成工程である。具体的には、導電化のための不純物(たとえばリン)を添加したポリシリコン膜55が半導体基板2の全面に形成される。

そして、図2Iに示すように、コントロールゲート14用のポリシリコン膜55、ONO構造の絶縁膜24およびフローティングゲート13用のポリシリコン膜52を一括でパターニングする。一括パターニングは、フォトリソグラフィによって行われる。すなわち、コントロールゲート14用のポリシリコン膜55上に、レジスト膜56を形成する。このレジスト膜56のパターンは、コントロールゲート14を形成すべき領域(フローティングゲート13はこの領域内に収まる)を選択的に被覆し、その他の領域を露出させるパターンである。このレジスト膜56をマスクとしてエッチングを行うことにより、フローティングゲート13、ONO構造の絶縁膜24およびコントロールゲート14の積層構造を一括して形成することができる。この際、セレクトゲート19およびMOSゲート33はレジスト膜56から露出しているが、これらのゲート19,33の表面はトンネルウィンドウ25と同時に形成された絶縁膜20,35に覆われているので、ポリシリコン膜52,55とのエッチング選択比を大きくすることによりエッチングされることを防止することができる。

【0045】

次の工程は、図2Jに示すように、n型ソース領域10、n型ドレイン領域17およびn型低濃度層36,37の形成である。すなわち、レジスト膜57をマスクとして、半導体基板2の表面に向けて選択的にn型不純物イオンが注入される。レジスト膜57は、不揮発性メモリセル7用のアクティブ領域5においてn型ソース領域10およびn型ドレイン領域17に対応する領域を露出させ、DDD−MOSトランジスタ26用のアクティブ領域27においてn型低濃度層36,37に対応する部分を露出させるパターンである。このレジスト膜57をマスクとしてn型不純物イオンを注入することによって、不揮発性メモリセル7用のアクティブ領域5にn型ソース領域10およびn型ドレイン領域17が形成され、DDD−MOSトランジスタ26用のアクティブ領域27では、MOSゲート33の両側にn型低濃度層36,37がそれぞれ形成される。たとえば、n型不純物イオンとしてAs+イオンまたはP+イオンが用いられ、そのドーズ量は1×1012〜1×1013/cm2とされ、その注入エネルギーは50keV〜100keVとされる。こうして、選択トランジスタ9のn型ソース領域10およびn型ドレイン領域17の形成のためのイオン注入と同工程で、DDD−MOSトランジスタ26のn型低濃度層36,37が形成される。この際、MOSゲート33をセレクトゲート19と同工程で比較的厚く形成したので、n型不純物がMOSゲート33を突き抜けることを防止することができる。

【0046】

レジスト膜57を剥離した後、図2Kに示すように、サイドウォール15,21,34形成工程が行われる。すなわち、たとえば、CVD法によって、半導体基板2の全面に酸化シリコン膜等の絶縁膜が形成された後、その絶縁膜がドライエッチングによってエッチバックされる。このエッチバックを、セレクトゲート19、コントロールゲート14およびMOSゲート33が露出するまで行うと、それらの各両側面にサイドウォール15,21,34が形成される。

【0047】

次に、図2Lに示すように、ソース−ドレイン注入工程が行われる。すなわち、レジスト膜58をマスクとして、半導体基板2の表面に向けて選択的にn型不純物イオンが注入される。レジスト膜58は、不揮発性メモリセル7用のアクティブ領域5においてn型ソース領域10およびn型ドレイン領域17の内方の一部を露出させ、DDD−MOSトランジスタ26用のアクティブ領域27において低濃度層36,37の内方の一部の領域(ソース・ドレイン領域30,31の対応領域)をそれぞれ露出させるパターンである。したがって、レジスト膜58をマスクとしてn型不純物イオンを注入することによって、不揮発性メモリセル7のコンタクト領域16,22が形成され、DDDトランジスタのソース・ドレイン領域30,31が形成される。たとえば、n型不純物イオンとしてAs+イオンが用いられ、そのドーズ量は、n型トンネル拡散層11のためのイオン注入(図2D)のときよりも多く、たとえば、1×1015〜1×1016/cm2とされる。または、注入エネルギーは、n型トンネル拡散層11のための注入(図2D)およびDDD注入(図2J)のときよりも小さく、たとえば、40keV〜70keVとされる。この際も、MOSゲート33をセレクトゲート19と同工程で比較的厚く形成したので、n型不純物がMOSゲート33を突き抜けることを防止することができる。

【0048】

この後は、レジスト膜58を剥離し、図2Mに示すように、全面を覆う層間絶縁膜38が形成され、当該層間絶縁膜38に、コンタクト領域16,22およびソース・ドレイン領域30,31をそれぞれ露出させる複数のコンタクトホール59〜62がレジスト膜63をマスクとしたエッチングにより形成され、図2Nに示すように、これらのコンタクトホール59〜62を介して各領域16,22,30,31にそれぞれ接触する複数のコンタクトプラグ44〜47および電極39〜42が形成される。

【0049】

なお、層間絶縁膜38は複数積層されてもよい。層間絶縁膜38を複数形成する場合でも、図2G〜図2Iの工程でフローティングゲート13およびコントロールゲート14を比較的薄く形成したので、層間絶縁膜38において、コントロールゲート14上に盛り上がった部分と他の部分との間に発生する段差を小さくすることができる。

そして、最上層の層間絶縁膜38上に、表面保護膜43が形成され、表面保護膜43に各電極をワイヤボンディング用のパッドとして露出させる開口(図示せず)が形成される。以上の工程を経て、図1の半導体装置1が得られる。

【0050】

以上のように、この実施形態によれば、トンネルウィンドウ25の形成(図2F)に先立ってセレクトゲート19を形成し(図2C)、そのセレクトゲート19に対して自己整合的(セルフアライン)にn型トンネル拡散層11およびトンネルウィンドウ25を形成するので、トンネルウィンドウ25やセレクトゲート19の加工寸法のばらつき、およびセレクトゲート19のアライメント精度による影響を無視することができる。そのため、不揮発性メモリセル7を設計するにあたり、トンネルウィンドウ25に対するセレクトゲート19のマージンをなくして、セルサイズを小さくすることができる。

【0051】

以上、本発明の一実施形態について説明したが、本発明は、さらに他の形態で実施することもできる。

たとえば、半導体装置1の各半導体部分の導電型を反転した構成が採用されてもよい。たとえば、半導体装置1において、p型の部分がn型であり、n型の部分がp型であってもよい。

【0052】

また、たとえば、前述の実施形態では、DDD−MOSトランジスタ26が半導体基板2上に形成される構成について説明したが、たとえば、半導体基板2上にLDD−MOSトランジスタ形成される構成に対しても本発明を適用することができる。また、前述の実施形態で示したドーズ量等の数値は一例であり、必要とされる仕様に応じて別の値が適用されてもよい。

【0053】

その他、特許請求の範囲に記載された事項の範囲で種々の設計変更を施すことが可能である。

【符号の説明】

【0054】

1 半導体装置

2 半導体基板

3 メモリセル領域

4 周辺回路領域

5 (不揮発性メモリセル用の)アクティブ領域

6 素子分離部

7 不揮発性メモリセル

8 メモリセルトランジスタ

9 選択トランジスタ

10 n型ソース領域

11 n型トンネル拡散層

12 チャネル領域

13 フローティングゲート

14 コントロールゲート

15 サイドウォール

16 (ソース)コンタクト領域

17 n型ドレイン領域

18 チャネル領域

19 セレクトゲート

20 (セレクトゲート上面の)絶縁膜

21 サイドウォール

22 (ドレイン)コンタクト領域

23 ゲート絶縁膜

24 (ONO構造の)絶縁膜

25 トンネルウィンドウ

26 DDD−MOSトランジスタ

27 (DDD−MOSトランジスタ用の)アクティブ領域

28 素子分離部

29 p型ウェル

30 n型ソース領域

31 n型ドレイン領域

32 チャネル領域

33 MOSゲート

34 サイドウォール

35 (MOSゲート上面の)絶縁膜

36 n型低濃度層

37 n型低濃度層

38 層間絶縁膜

39 (不揮発性メモリセル用の)ソース電極

40 (不揮発性メモリセル用の)ドレイン電極

41 (DDD−MOSトランジスタ用の)ソース電極

42 (DDD−MOSトランジスタ用の)ドレイン電極

43 表面保護膜

44 (ソース用)コンタクトプラグ

45 (ドレイン用)コンタクトプラグ

46 (ソース用)コンタクトプラグ

47 (ドレイン用)コンタクトプラグ

48 レジスト膜

49 (レジスト膜の)開口

50 (レジスト膜の)周縁

51 (セレクトゲートの)端部

52 ポリシリコン膜

53 レジスト膜

54 スペース

55 ポリシリコン膜

56 レジスト膜

57 レジスト膜

58 レジスト膜

59 コンタクトホール

60 コンタクトホール

61 コンタクトホール

62 コンタクトホール

63 レジスト膜

【特許請求の範囲】

【請求項1】

不揮発性メモリセルを半導体基板上に選択的に備える半導体装置であって、

前記半導体基板上に形成されたゲート絶縁膜と、

前記ゲート絶縁膜上において前記不揮発性メモリセル用の領域に、選択的に形成されたセレクトゲートと、

前記ゲート絶縁膜上において前記不揮発性メモリセル用の領域に、選択的に形成されたフローティングゲートと、

前記半導体基板において前記フローティングゲートの一部に対向し、前記セレクトゲートに対して自己整合的に形成されたトンネル拡散層と、

前記ゲート絶縁膜において前記フローティングゲートと前記トンネル拡散層との間の部分に前記セレクトゲートに対して自己整合的に形成され、前記ゲート絶縁膜の他の部分よりも薄くされたトンネルウィンドウとを含む、半導体装置。

【請求項2】

前記フローティングゲートは、前記セレクトゲートよりも薄い、請求項1に記載の半導体装置。

【請求項3】

前記半導体基板上に、ソース領域およびドレイン領域よりも深い領域まで広がり、前記ソース領域および前記ドレイン領域よりも低不純物濃度の低濃度層を有するMOSトランジスタを選択的にさらに備え、

前記ゲート絶縁膜上において前記MOSトランジスタ用の領域に選択的に形成され、前記セレクトゲートと同じ厚さのMOSゲートを含む、請求項1または2に記載の半導体装置。

【請求項4】

前記セレクトゲートおよび前記MOSゲートの厚さは、5000Å〜6000Åである、請求項3に記載の半導体装置。

【請求項5】

不揮発性メモリセルを半導体基板上に選択的に備える半導体装置の製造方法であって、

前記半導体基板上にゲート絶縁膜を形成する工程と、

前記ゲート絶縁膜上において前記不揮発性メモリセル用の領域に、セレクトゲートを選択的に形成する工程と、

前記半導体基板において前記不揮発性メモリセル用の領域に、不純物を前記セレクトゲートに対して自己整合的に導入することによってトンネル拡散層を形成する工程と、

前記ゲート絶縁膜において前記トンネル拡散層上の部分を前記セレクトゲートに対して自己整合的に除去し、その後、露出した前記半導体基板を熱酸化することにより、前記ゲート絶縁膜の他の部分よりも薄くされたトンネルウィンドウを形成する工程と、

前記トンネルウィンドウを挟んで前記トンネル拡散層に対向するように、前記ゲート絶縁膜上にフローティングゲートを選択的に形成する工程とを含む、半導体装置の製造方法。

【請求項6】

前記トンネルウィンドウを形成する工程は、

前記ゲート絶縁膜上に、前記セレクトゲートを被覆するようにレジスト膜を形成する工程と、

前記レジスト膜において、前記トンネル拡散層を形成すべき領域を露出させる開口を形成する工程であって、前記開口の周縁が、前記セレクトゲートにおける前記トンネル拡散層を形成すべき領域側の端部に対して前記セレクトゲートの内側に後退した位置に画成されるように前記開口を形成する工程と、

前記レジスト膜をマスクとして用いて前記ゲート絶縁膜の一部を除去する工程とを含む、請求項5に記載の半導体装置の製造方法。

【請求項7】

前記フローティングゲートを形成する工程は、前記セレクトゲートを形成する工程とは別工程において、前記セレクトゲートよりも薄いフローティングゲートで形成する工程を含む、請求項5または6に記載の半導体装置の製造方法。

【請求項8】

前記半導体基板上に、ソース領域およびドレイン領域よりも深い領域まで広がり、前記ソース領域および前記ドレイン領域よりも低不純物濃度の低濃度層を有するMOSトランジスタを選択的に形成する工程をさらに含み、

前記MOSトランジスタを形成する工程は、

前記セレクトゲートを形成する工程と同一工程で実行され、前記ゲート絶縁膜上において前記MOSトランジスタ用の領域に、前記セレクトゲートと同じ厚さのMOSゲートを選択的に形成する工程と、

前記半導体基板において前記MOSトランジスタ用の領域に、前記MOSゲートの上から不純物を導入することによって前記低濃度層を形成する工程と、

前記半導体基板において前記MOSトランジスタ用の領域に、前記MOSゲートの上から不純物を導入することによって、前記低濃度層内に前記ソース領域および前記ドレイン領域を形成する工程とを含む、請求項5〜7のいずれか一項に記載の半導体装置の製造方法。

【請求項1】

不揮発性メモリセルを半導体基板上に選択的に備える半導体装置であって、

前記半導体基板上に形成されたゲート絶縁膜と、

前記ゲート絶縁膜上において前記不揮発性メモリセル用の領域に、選択的に形成されたセレクトゲートと、

前記ゲート絶縁膜上において前記不揮発性メモリセル用の領域に、選択的に形成されたフローティングゲートと、

前記半導体基板において前記フローティングゲートの一部に対向し、前記セレクトゲートに対して自己整合的に形成されたトンネル拡散層と、

前記ゲート絶縁膜において前記フローティングゲートと前記トンネル拡散層との間の部分に前記セレクトゲートに対して自己整合的に形成され、前記ゲート絶縁膜の他の部分よりも薄くされたトンネルウィンドウとを含む、半導体装置。

【請求項2】

前記フローティングゲートは、前記セレクトゲートよりも薄い、請求項1に記載の半導体装置。

【請求項3】

前記半導体基板上に、ソース領域およびドレイン領域よりも深い領域まで広がり、前記ソース領域および前記ドレイン領域よりも低不純物濃度の低濃度層を有するMOSトランジスタを選択的にさらに備え、

前記ゲート絶縁膜上において前記MOSトランジスタ用の領域に選択的に形成され、前記セレクトゲートと同じ厚さのMOSゲートを含む、請求項1または2に記載の半導体装置。

【請求項4】

前記セレクトゲートおよび前記MOSゲートの厚さは、5000Å〜6000Åである、請求項3に記載の半導体装置。

【請求項5】

不揮発性メモリセルを半導体基板上に選択的に備える半導体装置の製造方法であって、

前記半導体基板上にゲート絶縁膜を形成する工程と、

前記ゲート絶縁膜上において前記不揮発性メモリセル用の領域に、セレクトゲートを選択的に形成する工程と、

前記半導体基板において前記不揮発性メモリセル用の領域に、不純物を前記セレクトゲートに対して自己整合的に導入することによってトンネル拡散層を形成する工程と、

前記ゲート絶縁膜において前記トンネル拡散層上の部分を前記セレクトゲートに対して自己整合的に除去し、その後、露出した前記半導体基板を熱酸化することにより、前記ゲート絶縁膜の他の部分よりも薄くされたトンネルウィンドウを形成する工程と、

前記トンネルウィンドウを挟んで前記トンネル拡散層に対向するように、前記ゲート絶縁膜上にフローティングゲートを選択的に形成する工程とを含む、半導体装置の製造方法。

【請求項6】

前記トンネルウィンドウを形成する工程は、

前記ゲート絶縁膜上に、前記セレクトゲートを被覆するようにレジスト膜を形成する工程と、

前記レジスト膜において、前記トンネル拡散層を形成すべき領域を露出させる開口を形成する工程であって、前記開口の周縁が、前記セレクトゲートにおける前記トンネル拡散層を形成すべき領域側の端部に対して前記セレクトゲートの内側に後退した位置に画成されるように前記開口を形成する工程と、

前記レジスト膜をマスクとして用いて前記ゲート絶縁膜の一部を除去する工程とを含む、請求項5に記載の半導体装置の製造方法。

【請求項7】

前記フローティングゲートを形成する工程は、前記セレクトゲートを形成する工程とは別工程において、前記セレクトゲートよりも薄いフローティングゲートで形成する工程を含む、請求項5または6に記載の半導体装置の製造方法。

【請求項8】

前記半導体基板上に、ソース領域およびドレイン領域よりも深い領域まで広がり、前記ソース領域および前記ドレイン領域よりも低不純物濃度の低濃度層を有するMOSトランジスタを選択的に形成する工程をさらに含み、

前記MOSトランジスタを形成する工程は、

前記セレクトゲートを形成する工程と同一工程で実行され、前記ゲート絶縁膜上において前記MOSトランジスタ用の領域に、前記セレクトゲートと同じ厚さのMOSゲートを選択的に形成する工程と、

前記半導体基板において前記MOSトランジスタ用の領域に、前記MOSゲートの上から不純物を導入することによって前記低濃度層を形成する工程と、

前記半導体基板において前記MOSトランジスタ用の領域に、前記MOSゲートの上から不純物を導入することによって、前記低濃度層内に前記ソース領域および前記ドレイン領域を形成する工程とを含む、請求項5〜7のいずれか一項に記載の半導体装置の製造方法。

【図1】

【図2A】

【図2B】

【図2C】

【図2D】

【図2E】

【図2F】

【図2G】

【図2H】

【図2I】

【図2J】

【図2K】

【図2L】

【図2M】

【図2N】

【図2A】

【図2B】

【図2C】

【図2D】

【図2E】

【図2F】

【図2G】

【図2H】

【図2I】

【図2J】

【図2K】

【図2L】

【図2M】

【図2N】

【公開番号】特開2013−115055(P2013−115055A)

【公開日】平成25年6月10日(2013.6.10)

【国際特許分類】

【出願番号】特願2011−256715(P2011−256715)

【出願日】平成23年11月24日(2011.11.24)

【出願人】(000116024)ローム株式会社 (3,539)

【Fターム(参考)】

【公開日】平成25年6月10日(2013.6.10)

【国際特許分類】

【出願日】平成23年11月24日(2011.11.24)

【出願人】(000116024)ローム株式会社 (3,539)

【Fターム(参考)】

[ Back to top ]