半導体装置および半導体装置の製造方法

【課題】フィンがバルク基板上に形成されたフィン型トランジスタにおいて、ソース/ドレインボトム領域での接合リーク電流の増大を抑制しつつ、ソース/ドレインとソース/ドレイン上に形成されたシリサイドとの接触抵抗を低減する。

【解決手段】フィン型半導体3の両端部に形成した高濃度不純物拡散層10からなるソース/ドレインの側面に、フィン型半導体3の上部の表面が露出するようにしてオフセットスペーサ7およびサイドウォールスペーサ8を形成し、フィン型半導体3の上部の高濃度不純物拡散層10の表面には、シリサイド層9を形成する。

【解決手段】フィン型半導体3の両端部に形成した高濃度不純物拡散層10からなるソース/ドレインの側面に、フィン型半導体3の上部の表面が露出するようにしてオフセットスペーサ7およびサイドウォールスペーサ8を形成し、フィン型半導体3の上部の高濃度不純物拡散層10の表面には、シリサイド層9を形成する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明の実施形態は半導体装置および半導体装置の製造方法に関する。

【背景技術】

【0002】

電界効果トランジスタでは、その微細化に伴って短チャネル効果が顕著になり、従来のシングルゲート型トランジスタでは短チャネル効果抑制のために高濃度のチャネル不純物が必要になってきている。しかし、チャネル不純物の高濃度化はチャネル中のキャリア移動度低下によるオン電流の減少、不純物ゆらぎによるしきい値電圧のばらつき増加、接合リーク電流増加などの問題を引き起こすことが知られており、微細化されたトランジスタの高性能化にはチャネル不純物の高濃度化によらない短チャネル効果抑制が必要である。

【0003】

チャネル不純物の高濃度化によらない短チャネル効果抑制を実現する方法として、チャネルに対してゲート電極を複数配置したマルチゲート型トランジスタが提案されている。マルチゲート型トランジスタは複数のゲート電極でチャネルポテンシャルを制御するため、チャネルポテンシャルに対するゲート電極の支配力をドレイン電極のそれよりも強くすることができ、チャネル不純物を高濃度にすることなく短チャネル効果が抑制できる。フィン型トランジスタはマルチゲート型トランジスタの一つであるが、フィンの高さを高くすることでチャネル幅が増加し、フットプリントを増大させることなくオン電流を増やせるため、たとえば高駆動電流が要求されるメモリのセルトランジスタなどに有効である。

【0004】

フィン型トランジスタにおいても平面型トランジスタ同様、ソース/ドレイン上にシリサイドを形成してその上にコンタクトを形成するのが一般的であるが、ソース/ドレインとシリサイドとの接触抵抗が寄生抵抗の主要成分であり、接触抵抗の低減が高性能化には重要である。この接触抵抗を低減するにはシリサイド材料のショットキー障壁高さを小さくする、ソース/ドレインとシリサイド界面の不純物濃度を上げる、ソース/ドレインとシリサイドとの接触面積を増やす、等が有効な方法である。

フィン型トランジスタではソース/ドレインとシリサイドとの接触面積を増やすために、ソース/ドレインのフィンをエピタキシャル成長で太くしてから表面をシリサイド化することが有効な技術として知られている。

【0005】

フィン型トランジスタにはバルク半導体基板上に形成されたタイプと、SOI(Silicon On Insulator)基板上に形成されたタイプとがあるが、半導体ウェハのコスト、平面型トランジスタとの混載、自己発熱の抑制、等の観点から前者が好ましい。

前者のタイプのフィン型トランジスタでは、ソース/ドレイン間のリーク電流防止のためフィンチャネルボトムにパンチスルーストッパが必要で、これによってソース/ドレインのボトムにPN接合が形成されるため、ソース/ドレイン上のシリサイドとこのPN接合が近づくと接合リーク電流が増加する。前述のようにフィン型トランジスタではフィン側面にシリサイドを形成することで、ソース/ドレインとシリサイドの接触面積を増やして、ソース/ドレインとシリサイドとの接触抵抗を低減できるが、シリサイドがソース/ドレインボトムのPN接合に接近して接合リーク電流を増加させないようにする必要がある。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2007−294757号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

本発明の一つの実施形態の目的は、フィンがバルク基板上に形成されたフィン型トランジスタにおいて、接合リーク電流の増大を抑制しつつ、ソース/ドレインとソース/ドレイン上のシリサイドとの接触抵抗を低減することが可能な半導体装置および半導体装置の製造方法を提供することである。

【課題を解決するための手段】

【0008】

実施形態の半導体装置によれば、フィン型半導体と、ゲート絶縁膜と、ゲート電極と、トップ層と、ソース/ドレインと、オフセットスペーサと、サイドウォールスペーサと、シリサイド層とが設けられている。ゲート電極は、前記フィン型半導体の側面にゲート絶縁膜を介して形成されている。トップ層は前記ゲート電極の上部に形成されている。ソース/ドレインは、前記フィン型半導体の両端部(前記ゲート電極と重ならない領域)に形成されている。オフセットスペーサおよびサイドウォールスペーサは、前記フィン型半導体の上部の表面が露出するようにして前記ゲート電極および前記ソース/ドレインの側面に形成されている。シリサイド層は、前記ソース/ドレイン表面に形成されている。

【図面の簡単な説明】

【0009】

【図1】図1(a)は、第1実施形態に係る半導体装置の概略構成を示す平面図、図1(b)は、図1(a)のA−A線で切断した半導体装置の概略構成を示す断面図、図1(c)は、図1(a)のB−B線で切断した半導体装置の概略構成を示す断面図である。

【図2】図2(a)〜図2(c)は、第2実施形態に係る半導体装置の製造方法を示す断面図である。

【図3】図3(a)〜図3(c)は、第2実施形態に係る半導体装置の製造方法を示す断面図である。

【図4】図4(a)〜図4(c)は、第2実施形態に係る半導体装置の製造方法を示す断面図である。

【図5】図5(a)〜図5(c)は、第2実施形態に係る半導体装置の製造方法を示す断面図である。

【図6】図6(a)〜図6(c)は、第2実施形態に係る半導体装置の製造方法を示す断面図である。

【図7】図7(a)〜図7(c)は、第2実施形態に係る半導体装置の製造方法を示す断面図である。

【図8】図8(a)〜図8(c)は、第2実施形態に係る半導体装置の製造方法を示す断面図である。

【図9】図9(a)〜図9(c)は、第2実施形態に係る半導体装置の製造方法を示す断面図である。

【図10】図10(a)〜図10(c)は、第2実施形態に係る半導体装置の製造方法を示す断面図である。

【図11】図11(a)〜図11(c)は、第2実施形態に係る半導体装置の製造方法を示す断面図である。

【図12】図12(a)〜図12(c)は、第2実施形態に係る半導体装置の製造方法を示す断面図である。

【図13】図13(a)〜図13(c)は、第2実施形態に係る半導体装置の製造方法を示す断面図である。

【図14】図14(a)〜図14(c)は、第2実施形態に係る半導体装置の製造方法を示す断面図である。

【図15】図15(a)〜図15(c)は、第2実施形態に係る半導体装置の製造方法を示す断面図である。

【図16】図16(a)〜図16(c)は、第2実施形態に係る半導体装置の製造方法を示す断面図である。

【図17】図17(a)〜図17(c)は、第2実施形態に係る半導体装置の製造方法を示す断面図である。

【図18】図18(a)〜図18(c)は、第2実施形態に係る半導体装置の製造方法を示す断面図である。

【図19】図19(a)〜図19(c)は、第2実施形態に係る半導体装置の製造方法を示す断面図である。

【図20】図20は、図1(c)のサイドウォールスペーサ8上のフィン突出量Efとオン電流Ionの関係を示す図である。

【発明を実施するための形態】

【0010】

以下、実施形態に係る半導体装置および半導体装置の製造方法について図面を参照しながら説明する。なお、これらの実施形態により本発明が限定されるものではない。

【0011】

(第1実施形態)

図1(a)は、第1実施形態に係る半導体装置の概略構成を示す平面図、図1(b)は、図1(a)のA−A線で切断した半導体装置の概略構成を示す断面図、図1(c)は、図1(a)のB−B線で切断した半導体装置の概略構成を示す断面図である。

【0012】

図1(a)〜図1(c)において、半導体基板1上にはフィン型半導体3が形成されている。なお、半導体基板1およびフィン型半導体3の材料は、例えば、Si、Ge、SiGe、GaAs、AlGaAs、InP、GaP、InGaAs、GaN、SiCなどから選択することができる。また、半導体基板1およびフィン型半導体3の材料は、互いに同じであってもよいし、互いに異なっていてもよい。

【0013】

そして、半導体基板1上には、フィン型半導体3の下部が埋め込まれるようにして埋め込み絶縁層2が形成されている。なお、埋め込み絶縁層2の構造としては、例えば、STI(Shallow Trench Isolation)構造を用いることができる。また、埋め込み絶縁層2の材料は、例えば、SiO2を用いることができる。

【0014】

そして、埋め込み絶縁層2上に突出したフィン型半導体3の側面には、ゲート絶縁膜6を介してゲート電極13が形成され、ゲート絶縁膜6を介してゲート電極13と対向する半導体3の内部にチャネル領域15が形成される。そして、フィン型半導体3の両端部には、高濃度不純物拡散層10からなるソース/ドレインが設けられている。なお、フィン型半導体3の高濃度不純物拡散層10は、N+型不純物拡散層とすることができる。また、フィン型半導体3のチャネル領域15では、チャネル領域15の不純物濃度のばらつきに起因する電界効果トランジスタの電気特性のばらつきや移動度の低下を抑制するために、チャネル領域15の不純物濃度を低減することが好ましい。チャネル領域15はノンドープであってもよい。チャネル領域15内の不純物濃度を十分に低減した場合でも短チャネル効果を抑制するため、フィン幅はゲート長よりも小さく、より具体的には2/3以下にすることが好ましい。なお、チャネル内の不純物濃度を十分低減することでフィン型トランジスタを完全空乏化デバイスとすることができる。

【0015】

ゲート電極13の材料は、例えば、多結晶シリコンを用いることができる。あるいは、ゲート電極13の材料は、例えば、W、Al、TaN、Ru、TiAlN、HfN、NiSi、MoおよびTiNなどから選択するようにしてもよい。また、ゲート絶縁膜6の材料は、例えば、SiO2、HfO、HfSiO、HfSiON、HfAlO、HfAlSiONおよびLa2O3などから選択することができる。

【0016】

また、フィン型半導体3の下部には、ゲート電極がフィン側面に存在しないためにソース/ドレイン間にリーク電流が流れるのを防止するためのパンチスルーストッパ層4が形成されている。なお、パンチスルーストッパ層4は、N+型不純物拡散層であるソース/ドレインに対して、P−型不純物拡散層とすることができる。

【0017】

フィン型半導体3上にはキャップ層5が形成され、キャップ層5およびゲート電極13上にはトップ層11の上部にハードマスク層12が形成されている。なお、キャップ層5およびハードマスク層12の材料は、例えば、Si3N4を用いることができる。トップ層11はキャップ層5で分断されたゲート電極13を接続して、フィン型トランジスタをダブルゲート動作させることができる。また、トップ層11をゲート電極13と接続された配線として用いることもできる。トップ層11の材料は、例えば、Wなどの高融点金属を用いることができる。

【0018】

フィン型半導体3の両端部において、フィン型半導体3の上部の表面が露出するようにしてオフセットスペーサ7およびサイドウォールスペーサ8が形成されている。なお、オフセットスペーサ7およびサイドウォールスペーサ8の材料は、例えば、Si3N4を用いることができる。そして、露出したフィン型半導体3の高濃度不純物拡散層10の表面には、シリサイド層9が形成されている。なお、シリサイド層9としては、例えば、WSi、MoSi、NiSiまたはNiPtSiなどを用いることができる。

【0019】

ここで、フィン型半導体3の上部の表面が露出するようにオフセットスペーサ7およびサイドウォールスペーサ8を形成することにより、シリサイド層9を高濃度不純物拡散層10とパンチスルーストッパ層4との接合面16から離間させることができる。このため、シリサイド層9に含まれる金属が前記接合面に拡散して接合リーク電流が増加することを抑制することができる。なお、接合リーク電流の増大を抑制するにはシリサイド層9と前記接合面16との距離が30nm以上であることが好ましい。

【0020】

(第2実施形態)

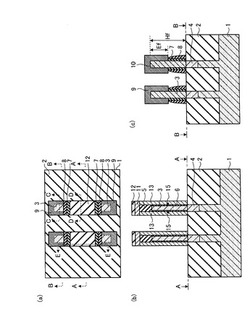

図2(a)〜図19(a)、図2(b)〜図19(b)および図2(c)〜図19(c)は、第2実施形態に係る半導体装置の製造方法を示す断面図である。なお、図2(a)〜図19(a)は、図1(a)のC−C線で切断した断面図、図2(b)〜図19(b)は、図1(a)のD−D線で切断した断面図、図2(c)〜図19(c)は、図1(a)のE−E線で切断した断面図である。

【0021】

図2(a)〜図2(c)において、CVDなどの方法にて半導体基板1上の全面にハードマスク材を成膜する。そして、フォトリソグラフィ技術およびエッチング技術にてハードマスク材をパターニングすることにより、半導体基板1上にキャップ層5を形成する。

【0022】

次に、図3(a)〜図3(c)に示すように、キャップ層5をマスクとして半導体基板1をエッチングすることにより、半導体基板1上にフィン型半導体3を形成する。

【0023】

次に、図4(a)〜図4(c)に示すように、CVDなどの方法にてフィン型半導体3が埋め込まれるように埋め込み絶縁層2を半導体基板1上に形成する。そして、CMPなどの方法にて埋め込み絶縁層2を平坦化する。この時、キャップ層5は、埋め込み絶縁層2のCMPのエッチストッパ膜として用いることができる。

【0024】

次に、図5(a)〜図5(c)に示すように、埋め込み絶縁層2のエッチバックを行うことにより、フィン型半導体3の下部が埋め込み絶縁層2にて埋め込まれるようにしてフィン型半導体3の上部を埋め込み絶縁層2から露出させる。

【0025】

次に、図6(a)〜図6(c)に示すように、イオン注入P1にてBやInなどのP型不純物を埋め込み絶縁層2に垂直に注入する。この時、注入されたP型不純物イオンは、埋め込み絶縁層2の表層である一定の確率で大角散乱が起こされ、そのP型不純物イオンがフィン型半導体3の下部にドープされて、フィン型半導体3の下部にパンチスルーストッパ層4を形成することができる。

【0026】

次に、図7(a)〜図7(c)に示すように、熱酸化またはCVDなどの方法にて埋め込み絶縁層2から突出したフィン型半導体3の側面にゲート絶縁膜6を形成する。

【0027】

次に、図8(a)〜図8(c)に示すように、CVDなどの方法にてフィン型半導体3が埋め込まれるようにゲート電極材13´を埋め込み絶縁層2上に形成する。そして、CMPなどの方法にてゲート電極材13´を平坦化する。この時、キャップ層5は、ゲート電極材13´のCMPのエッチストッパ膜として用いることができる。

【0028】

次に、図9(a)〜図9(c)に示すように、スパッタなどの方法にてキャップ層5およびゲート電極材13´上にトップ層11を形成する。

【0029】

次に、図10(a)〜図10(c)に示すように、CVDなどの方法にてトップ層11上にハードマスク材12´を形成する。

【0030】

次に、図11(a)〜図11(c)に示すように、フォトリソグラフィ技術およびエッチング技術にてハードマスク材12´をパターニングすることにより、トップ層11上にハードマスク層12を形成する。

【0031】

次に、図12(a)〜図12(c)に示すように、ハードマスク層12をマスクとしてトップ層11およびゲート電極材13´をエッチングすることにより、埋め込み絶縁層2上に突出したフィン型半導体3およびキャップ層5の側面にゲート電極13を形成する。

【0032】

次に、図13(a)〜図13(c)に示すように、CVDなどの方法にて埋め込み絶縁層2上に突出したフィン型半導体3の両端の側面およびゲート電極13の側面にオフセットスペーサ7を形成する。なお、埋め込み絶縁層2、キャップ層5およびハードマスク層12上のオフセットスペーサ7は、異方性エッチングにて除去することができる。

【0033】

次に、図14(a)〜図14(c)に示すように、イオン注入P2にてAs、PなどのN型不純物をフィン型半導体3の両端に斜めから注入することにより、フィン型半導体3の両端に高濃度不純物拡散層10を形成する。

【0034】

次に、図15(a)〜図15(c)に示すように、CVDなどの方法にて埋め込み絶縁層2上に突出したフィン型半導体3の両端の側面およびゲート電極13の側面に形成されたオフセットスペーサ7の外側にサイドウォールスペーサ8を形成する。なお、埋め込み絶縁層2、キャップ層5およびハードマスク層12上のサイドウォールスペーサ8は、異方性エッチングにて除去することができる。

【0035】

次に、図16(a)〜図16(c)に示すように、オフセットスペーサ7およびサイドウォールスペーサ8のエッチバックを行うことにより、フィン型半導体3の両端の上部の表面を露出させる。この時、キャップ層5およびハードマスク層12もエッチングされ、キャップ層5は除去することができる。また、ハードマスク層12はトップ層11上に一部が残るようにして、ゲート電極13およびトップ層11の側面がオフセットスペーサ7およびサイドウォールスペーサ8で完全に覆われたままにすることができる。

【0036】

ここで、ゲート電極13およびトップ層11の側面がオフセットスペーサ7およびサイドウォールスペーサ8で覆われたままにすることで、ゲート電極13およびトップ層11がソース/ドレイン上に形成されたコンタクトとショートすることを防ぐことができる。

【0037】

次に、図17(a)〜図17(c)に示すように、選択エピタキシャル成長にてフィン型半導体3の両端の上部の表面に半導体層14を形成する。なお、半導体層14の材料は、例えば、Si、Ge、SiGe、GaAs、AlGaAs、InP、GaP、InGaAs、GaN、SiCなどから選択することができる。

【0038】

次に、図18(a)〜図18(c)に示すように、イオン注入P3にてAs、PなどのN型不純物をフィン型半導体3の両端の上部に斜めから注入することにより、選択エピタキシャル成長で形成された半導体層14に高濃度の不純物をドーピングする。高濃度不純物拡散層10およびその上に形成された高濃度の不純物をドーピングされた半導体層14がソース/ドレインとなる。

【0039】

次に、図19(a)〜図19(c)に示すように、半導体層14の一部または全部をシリサイド化することにより、高濃度不純物拡散層10およびその上に形成された高濃度の不純物をドーピングされた半導体層14からなるソース/ドレインの表面にシリサイド層9を形成する。

【0040】

ここで、選択エピタキシャル成長にて高濃度不純物拡散層10上に半導体層14を形成してできたソース/ドレイン上にシリサイドを形成することにより、フィン型半導体3の幅が小さい場合においても、ソース/ドレイン領域のフィン型半導体3が完全にシリサイド化するのを防止することができる。これによりシリサイド層9とフィン型半導体3との接触面積を大きく保つことができ、ソース/ドレインとシリサイド層9の接触抵抗を低減することが可能となる。

【0041】

なお、上述した実施形態では、選択エピタキシャル成長にてフィン型半導体3の両端の上部に半導体層14を形成してから、フィン型半導体3の両端の上部にシリサイド層9を形成する方法について説明したが、オフセットスペーサおよびサイドウォールスペーサ8の上部にあるフィン型半導体3が完全にシリサイド化しない場合は、フィン型半導体3の両端の上部に半導体層14を形成することなく、フィン型半導体3の両端の上部にシリサイド層9を形成するようにしてもよい。

【0042】

図20は、図1(c)のオフセットスペーサ7およびサイドウォールスペーサ8上部のフィン突出量Efとオン電流Ionの関係を示す図である。

【0043】

図20において、オフセットスペーサ7およびサイドウォールスペーサ8上部のフィン突出量Efが増加すると、シリサイド層9とフィン型半導体3との接触面積が大きくなり、シリサイド層9とフィン型半導体3との接触抵抗が低減するため、オン電流Ionが増加する。

【0044】

一方、埋め込み絶縁層2上のフィン突出量Hfが一定の場合、オフセットスペーサ7およびサイドウォールスペーサ8上部のフィン突出量Efがオフセットスペーサ7およびサイドウォールスペーサ8の後退によって増加すると、シリサイド層9と高濃度不純物拡散層10の接合面16との距離が小さくなり、接合リーク電流が増加してオフ電流Ioffが増加する。

【0045】

ここで、シリサイド層9とPN接合面16との距離を保ちながら埋め込み絶縁層2上のフィン突出量Hfを増加させると、接合面16での接合リーク電流を増加させることなくフィン突出量Efの増加でソース/ドレインとシリサイド層9の接触抵抗が低減し、オン電流Ionを増加させることができる。

【0046】

なお、上述した実施形態では、フィン型半導体3をバルク基板上に形成する場合を例にとって説明したが、フィン型半導体3をSOI基板上に形成した構成に適用してもよい。また、上述した実施形態では、フィン型半導体3の両端部の側壁にオフセットスペーサ7を設ける方法について説明したが、オフセットスペーサ7は省略するようにしてもよい。

また、フィン型トランジスタとしてNチャネル型トランジスタについて説明したが、パンチスルーストッパおよびソースドレインの不純物のタイプを変えることで、Pチャネル型トランジスタに変えることができる。

【0047】

本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

【符号の説明】

【0048】

1 半導体基板、2 埋め込み絶縁層、3 フィン型半導体、4 パンチスルーストッパ層、5 キャップ層、6 ゲート絶縁膜、7 オフセットスペーサ、8 サイドウォールスペーサ、9 シリサイド層、10 高濃度不純物拡散層、11 トップ層、12 ハードマスク層、12 ´ ハードマスク材、13 ゲート電極、13´ ゲート電極材、14 半導体層、15 チャネル領域、16 PN接合面

【技術分野】

【0001】

本発明の実施形態は半導体装置および半導体装置の製造方法に関する。

【背景技術】

【0002】

電界効果トランジスタでは、その微細化に伴って短チャネル効果が顕著になり、従来のシングルゲート型トランジスタでは短チャネル効果抑制のために高濃度のチャネル不純物が必要になってきている。しかし、チャネル不純物の高濃度化はチャネル中のキャリア移動度低下によるオン電流の減少、不純物ゆらぎによるしきい値電圧のばらつき増加、接合リーク電流増加などの問題を引き起こすことが知られており、微細化されたトランジスタの高性能化にはチャネル不純物の高濃度化によらない短チャネル効果抑制が必要である。

【0003】

チャネル不純物の高濃度化によらない短チャネル効果抑制を実現する方法として、チャネルに対してゲート電極を複数配置したマルチゲート型トランジスタが提案されている。マルチゲート型トランジスタは複数のゲート電極でチャネルポテンシャルを制御するため、チャネルポテンシャルに対するゲート電極の支配力をドレイン電極のそれよりも強くすることができ、チャネル不純物を高濃度にすることなく短チャネル効果が抑制できる。フィン型トランジスタはマルチゲート型トランジスタの一つであるが、フィンの高さを高くすることでチャネル幅が増加し、フットプリントを増大させることなくオン電流を増やせるため、たとえば高駆動電流が要求されるメモリのセルトランジスタなどに有効である。

【0004】

フィン型トランジスタにおいても平面型トランジスタ同様、ソース/ドレイン上にシリサイドを形成してその上にコンタクトを形成するのが一般的であるが、ソース/ドレインとシリサイドとの接触抵抗が寄生抵抗の主要成分であり、接触抵抗の低減が高性能化には重要である。この接触抵抗を低減するにはシリサイド材料のショットキー障壁高さを小さくする、ソース/ドレインとシリサイド界面の不純物濃度を上げる、ソース/ドレインとシリサイドとの接触面積を増やす、等が有効な方法である。

フィン型トランジスタではソース/ドレインとシリサイドとの接触面積を増やすために、ソース/ドレインのフィンをエピタキシャル成長で太くしてから表面をシリサイド化することが有効な技術として知られている。

【0005】

フィン型トランジスタにはバルク半導体基板上に形成されたタイプと、SOI(Silicon On Insulator)基板上に形成されたタイプとがあるが、半導体ウェハのコスト、平面型トランジスタとの混載、自己発熱の抑制、等の観点から前者が好ましい。

前者のタイプのフィン型トランジスタでは、ソース/ドレイン間のリーク電流防止のためフィンチャネルボトムにパンチスルーストッパが必要で、これによってソース/ドレインのボトムにPN接合が形成されるため、ソース/ドレイン上のシリサイドとこのPN接合が近づくと接合リーク電流が増加する。前述のようにフィン型トランジスタではフィン側面にシリサイドを形成することで、ソース/ドレインとシリサイドの接触面積を増やして、ソース/ドレインとシリサイドとの接触抵抗を低減できるが、シリサイドがソース/ドレインボトムのPN接合に接近して接合リーク電流を増加させないようにする必要がある。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2007−294757号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

本発明の一つの実施形態の目的は、フィンがバルク基板上に形成されたフィン型トランジスタにおいて、接合リーク電流の増大を抑制しつつ、ソース/ドレインとソース/ドレイン上のシリサイドとの接触抵抗を低減することが可能な半導体装置および半導体装置の製造方法を提供することである。

【課題を解決するための手段】

【0008】

実施形態の半導体装置によれば、フィン型半導体と、ゲート絶縁膜と、ゲート電極と、トップ層と、ソース/ドレインと、オフセットスペーサと、サイドウォールスペーサと、シリサイド層とが設けられている。ゲート電極は、前記フィン型半導体の側面にゲート絶縁膜を介して形成されている。トップ層は前記ゲート電極の上部に形成されている。ソース/ドレインは、前記フィン型半導体の両端部(前記ゲート電極と重ならない領域)に形成されている。オフセットスペーサおよびサイドウォールスペーサは、前記フィン型半導体の上部の表面が露出するようにして前記ゲート電極および前記ソース/ドレインの側面に形成されている。シリサイド層は、前記ソース/ドレイン表面に形成されている。

【図面の簡単な説明】

【0009】

【図1】図1(a)は、第1実施形態に係る半導体装置の概略構成を示す平面図、図1(b)は、図1(a)のA−A線で切断した半導体装置の概略構成を示す断面図、図1(c)は、図1(a)のB−B線で切断した半導体装置の概略構成を示す断面図である。

【図2】図2(a)〜図2(c)は、第2実施形態に係る半導体装置の製造方法を示す断面図である。

【図3】図3(a)〜図3(c)は、第2実施形態に係る半導体装置の製造方法を示す断面図である。

【図4】図4(a)〜図4(c)は、第2実施形態に係る半導体装置の製造方法を示す断面図である。

【図5】図5(a)〜図5(c)は、第2実施形態に係る半導体装置の製造方法を示す断面図である。

【図6】図6(a)〜図6(c)は、第2実施形態に係る半導体装置の製造方法を示す断面図である。

【図7】図7(a)〜図7(c)は、第2実施形態に係る半導体装置の製造方法を示す断面図である。

【図8】図8(a)〜図8(c)は、第2実施形態に係る半導体装置の製造方法を示す断面図である。

【図9】図9(a)〜図9(c)は、第2実施形態に係る半導体装置の製造方法を示す断面図である。

【図10】図10(a)〜図10(c)は、第2実施形態に係る半導体装置の製造方法を示す断面図である。

【図11】図11(a)〜図11(c)は、第2実施形態に係る半導体装置の製造方法を示す断面図である。

【図12】図12(a)〜図12(c)は、第2実施形態に係る半導体装置の製造方法を示す断面図である。

【図13】図13(a)〜図13(c)は、第2実施形態に係る半導体装置の製造方法を示す断面図である。

【図14】図14(a)〜図14(c)は、第2実施形態に係る半導体装置の製造方法を示す断面図である。

【図15】図15(a)〜図15(c)は、第2実施形態に係る半導体装置の製造方法を示す断面図である。

【図16】図16(a)〜図16(c)は、第2実施形態に係る半導体装置の製造方法を示す断面図である。

【図17】図17(a)〜図17(c)は、第2実施形態に係る半導体装置の製造方法を示す断面図である。

【図18】図18(a)〜図18(c)は、第2実施形態に係る半導体装置の製造方法を示す断面図である。

【図19】図19(a)〜図19(c)は、第2実施形態に係る半導体装置の製造方法を示す断面図である。

【図20】図20は、図1(c)のサイドウォールスペーサ8上のフィン突出量Efとオン電流Ionの関係を示す図である。

【発明を実施するための形態】

【0010】

以下、実施形態に係る半導体装置および半導体装置の製造方法について図面を参照しながら説明する。なお、これらの実施形態により本発明が限定されるものではない。

【0011】

(第1実施形態)

図1(a)は、第1実施形態に係る半導体装置の概略構成を示す平面図、図1(b)は、図1(a)のA−A線で切断した半導体装置の概略構成を示す断面図、図1(c)は、図1(a)のB−B線で切断した半導体装置の概略構成を示す断面図である。

【0012】

図1(a)〜図1(c)において、半導体基板1上にはフィン型半導体3が形成されている。なお、半導体基板1およびフィン型半導体3の材料は、例えば、Si、Ge、SiGe、GaAs、AlGaAs、InP、GaP、InGaAs、GaN、SiCなどから選択することができる。また、半導体基板1およびフィン型半導体3の材料は、互いに同じであってもよいし、互いに異なっていてもよい。

【0013】

そして、半導体基板1上には、フィン型半導体3の下部が埋め込まれるようにして埋め込み絶縁層2が形成されている。なお、埋め込み絶縁層2の構造としては、例えば、STI(Shallow Trench Isolation)構造を用いることができる。また、埋め込み絶縁層2の材料は、例えば、SiO2を用いることができる。

【0014】

そして、埋め込み絶縁層2上に突出したフィン型半導体3の側面には、ゲート絶縁膜6を介してゲート電極13が形成され、ゲート絶縁膜6を介してゲート電極13と対向する半導体3の内部にチャネル領域15が形成される。そして、フィン型半導体3の両端部には、高濃度不純物拡散層10からなるソース/ドレインが設けられている。なお、フィン型半導体3の高濃度不純物拡散層10は、N+型不純物拡散層とすることができる。また、フィン型半導体3のチャネル領域15では、チャネル領域15の不純物濃度のばらつきに起因する電界効果トランジスタの電気特性のばらつきや移動度の低下を抑制するために、チャネル領域15の不純物濃度を低減することが好ましい。チャネル領域15はノンドープであってもよい。チャネル領域15内の不純物濃度を十分に低減した場合でも短チャネル効果を抑制するため、フィン幅はゲート長よりも小さく、より具体的には2/3以下にすることが好ましい。なお、チャネル内の不純物濃度を十分低減することでフィン型トランジスタを完全空乏化デバイスとすることができる。

【0015】

ゲート電極13の材料は、例えば、多結晶シリコンを用いることができる。あるいは、ゲート電極13の材料は、例えば、W、Al、TaN、Ru、TiAlN、HfN、NiSi、MoおよびTiNなどから選択するようにしてもよい。また、ゲート絶縁膜6の材料は、例えば、SiO2、HfO、HfSiO、HfSiON、HfAlO、HfAlSiONおよびLa2O3などから選択することができる。

【0016】

また、フィン型半導体3の下部には、ゲート電極がフィン側面に存在しないためにソース/ドレイン間にリーク電流が流れるのを防止するためのパンチスルーストッパ層4が形成されている。なお、パンチスルーストッパ層4は、N+型不純物拡散層であるソース/ドレインに対して、P−型不純物拡散層とすることができる。

【0017】

フィン型半導体3上にはキャップ層5が形成され、キャップ層5およびゲート電極13上にはトップ層11の上部にハードマスク層12が形成されている。なお、キャップ層5およびハードマスク層12の材料は、例えば、Si3N4を用いることができる。トップ層11はキャップ層5で分断されたゲート電極13を接続して、フィン型トランジスタをダブルゲート動作させることができる。また、トップ層11をゲート電極13と接続された配線として用いることもできる。トップ層11の材料は、例えば、Wなどの高融点金属を用いることができる。

【0018】

フィン型半導体3の両端部において、フィン型半導体3の上部の表面が露出するようにしてオフセットスペーサ7およびサイドウォールスペーサ8が形成されている。なお、オフセットスペーサ7およびサイドウォールスペーサ8の材料は、例えば、Si3N4を用いることができる。そして、露出したフィン型半導体3の高濃度不純物拡散層10の表面には、シリサイド層9が形成されている。なお、シリサイド層9としては、例えば、WSi、MoSi、NiSiまたはNiPtSiなどを用いることができる。

【0019】

ここで、フィン型半導体3の上部の表面が露出するようにオフセットスペーサ7およびサイドウォールスペーサ8を形成することにより、シリサイド層9を高濃度不純物拡散層10とパンチスルーストッパ層4との接合面16から離間させることができる。このため、シリサイド層9に含まれる金属が前記接合面に拡散して接合リーク電流が増加することを抑制することができる。なお、接合リーク電流の増大を抑制するにはシリサイド層9と前記接合面16との距離が30nm以上であることが好ましい。

【0020】

(第2実施形態)

図2(a)〜図19(a)、図2(b)〜図19(b)および図2(c)〜図19(c)は、第2実施形態に係る半導体装置の製造方法を示す断面図である。なお、図2(a)〜図19(a)は、図1(a)のC−C線で切断した断面図、図2(b)〜図19(b)は、図1(a)のD−D線で切断した断面図、図2(c)〜図19(c)は、図1(a)のE−E線で切断した断面図である。

【0021】

図2(a)〜図2(c)において、CVDなどの方法にて半導体基板1上の全面にハードマスク材を成膜する。そして、フォトリソグラフィ技術およびエッチング技術にてハードマスク材をパターニングすることにより、半導体基板1上にキャップ層5を形成する。

【0022】

次に、図3(a)〜図3(c)に示すように、キャップ層5をマスクとして半導体基板1をエッチングすることにより、半導体基板1上にフィン型半導体3を形成する。

【0023】

次に、図4(a)〜図4(c)に示すように、CVDなどの方法にてフィン型半導体3が埋め込まれるように埋め込み絶縁層2を半導体基板1上に形成する。そして、CMPなどの方法にて埋め込み絶縁層2を平坦化する。この時、キャップ層5は、埋め込み絶縁層2のCMPのエッチストッパ膜として用いることができる。

【0024】

次に、図5(a)〜図5(c)に示すように、埋め込み絶縁層2のエッチバックを行うことにより、フィン型半導体3の下部が埋め込み絶縁層2にて埋め込まれるようにしてフィン型半導体3の上部を埋め込み絶縁層2から露出させる。

【0025】

次に、図6(a)〜図6(c)に示すように、イオン注入P1にてBやInなどのP型不純物を埋め込み絶縁層2に垂直に注入する。この時、注入されたP型不純物イオンは、埋め込み絶縁層2の表層である一定の確率で大角散乱が起こされ、そのP型不純物イオンがフィン型半導体3の下部にドープされて、フィン型半導体3の下部にパンチスルーストッパ層4を形成することができる。

【0026】

次に、図7(a)〜図7(c)に示すように、熱酸化またはCVDなどの方法にて埋め込み絶縁層2から突出したフィン型半導体3の側面にゲート絶縁膜6を形成する。

【0027】

次に、図8(a)〜図8(c)に示すように、CVDなどの方法にてフィン型半導体3が埋め込まれるようにゲート電極材13´を埋め込み絶縁層2上に形成する。そして、CMPなどの方法にてゲート電極材13´を平坦化する。この時、キャップ層5は、ゲート電極材13´のCMPのエッチストッパ膜として用いることができる。

【0028】

次に、図9(a)〜図9(c)に示すように、スパッタなどの方法にてキャップ層5およびゲート電極材13´上にトップ層11を形成する。

【0029】

次に、図10(a)〜図10(c)に示すように、CVDなどの方法にてトップ層11上にハードマスク材12´を形成する。

【0030】

次に、図11(a)〜図11(c)に示すように、フォトリソグラフィ技術およびエッチング技術にてハードマスク材12´をパターニングすることにより、トップ層11上にハードマスク層12を形成する。

【0031】

次に、図12(a)〜図12(c)に示すように、ハードマスク層12をマスクとしてトップ層11およびゲート電極材13´をエッチングすることにより、埋め込み絶縁層2上に突出したフィン型半導体3およびキャップ層5の側面にゲート電極13を形成する。

【0032】

次に、図13(a)〜図13(c)に示すように、CVDなどの方法にて埋め込み絶縁層2上に突出したフィン型半導体3の両端の側面およびゲート電極13の側面にオフセットスペーサ7を形成する。なお、埋め込み絶縁層2、キャップ層5およびハードマスク層12上のオフセットスペーサ7は、異方性エッチングにて除去することができる。

【0033】

次に、図14(a)〜図14(c)に示すように、イオン注入P2にてAs、PなどのN型不純物をフィン型半導体3の両端に斜めから注入することにより、フィン型半導体3の両端に高濃度不純物拡散層10を形成する。

【0034】

次に、図15(a)〜図15(c)に示すように、CVDなどの方法にて埋め込み絶縁層2上に突出したフィン型半導体3の両端の側面およびゲート電極13の側面に形成されたオフセットスペーサ7の外側にサイドウォールスペーサ8を形成する。なお、埋め込み絶縁層2、キャップ層5およびハードマスク層12上のサイドウォールスペーサ8は、異方性エッチングにて除去することができる。

【0035】

次に、図16(a)〜図16(c)に示すように、オフセットスペーサ7およびサイドウォールスペーサ8のエッチバックを行うことにより、フィン型半導体3の両端の上部の表面を露出させる。この時、キャップ層5およびハードマスク層12もエッチングされ、キャップ層5は除去することができる。また、ハードマスク層12はトップ層11上に一部が残るようにして、ゲート電極13およびトップ層11の側面がオフセットスペーサ7およびサイドウォールスペーサ8で完全に覆われたままにすることができる。

【0036】

ここで、ゲート電極13およびトップ層11の側面がオフセットスペーサ7およびサイドウォールスペーサ8で覆われたままにすることで、ゲート電極13およびトップ層11がソース/ドレイン上に形成されたコンタクトとショートすることを防ぐことができる。

【0037】

次に、図17(a)〜図17(c)に示すように、選択エピタキシャル成長にてフィン型半導体3の両端の上部の表面に半導体層14を形成する。なお、半導体層14の材料は、例えば、Si、Ge、SiGe、GaAs、AlGaAs、InP、GaP、InGaAs、GaN、SiCなどから選択することができる。

【0038】

次に、図18(a)〜図18(c)に示すように、イオン注入P3にてAs、PなどのN型不純物をフィン型半導体3の両端の上部に斜めから注入することにより、選択エピタキシャル成長で形成された半導体層14に高濃度の不純物をドーピングする。高濃度不純物拡散層10およびその上に形成された高濃度の不純物をドーピングされた半導体層14がソース/ドレインとなる。

【0039】

次に、図19(a)〜図19(c)に示すように、半導体層14の一部または全部をシリサイド化することにより、高濃度不純物拡散層10およびその上に形成された高濃度の不純物をドーピングされた半導体層14からなるソース/ドレインの表面にシリサイド層9を形成する。

【0040】

ここで、選択エピタキシャル成長にて高濃度不純物拡散層10上に半導体層14を形成してできたソース/ドレイン上にシリサイドを形成することにより、フィン型半導体3の幅が小さい場合においても、ソース/ドレイン領域のフィン型半導体3が完全にシリサイド化するのを防止することができる。これによりシリサイド層9とフィン型半導体3との接触面積を大きく保つことができ、ソース/ドレインとシリサイド層9の接触抵抗を低減することが可能となる。

【0041】

なお、上述した実施形態では、選択エピタキシャル成長にてフィン型半導体3の両端の上部に半導体層14を形成してから、フィン型半導体3の両端の上部にシリサイド層9を形成する方法について説明したが、オフセットスペーサおよびサイドウォールスペーサ8の上部にあるフィン型半導体3が完全にシリサイド化しない場合は、フィン型半導体3の両端の上部に半導体層14を形成することなく、フィン型半導体3の両端の上部にシリサイド層9を形成するようにしてもよい。

【0042】

図20は、図1(c)のオフセットスペーサ7およびサイドウォールスペーサ8上部のフィン突出量Efとオン電流Ionの関係を示す図である。

【0043】

図20において、オフセットスペーサ7およびサイドウォールスペーサ8上部のフィン突出量Efが増加すると、シリサイド層9とフィン型半導体3との接触面積が大きくなり、シリサイド層9とフィン型半導体3との接触抵抗が低減するため、オン電流Ionが増加する。

【0044】

一方、埋め込み絶縁層2上のフィン突出量Hfが一定の場合、オフセットスペーサ7およびサイドウォールスペーサ8上部のフィン突出量Efがオフセットスペーサ7およびサイドウォールスペーサ8の後退によって増加すると、シリサイド層9と高濃度不純物拡散層10の接合面16との距離が小さくなり、接合リーク電流が増加してオフ電流Ioffが増加する。

【0045】

ここで、シリサイド層9とPN接合面16との距離を保ちながら埋め込み絶縁層2上のフィン突出量Hfを増加させると、接合面16での接合リーク電流を増加させることなくフィン突出量Efの増加でソース/ドレインとシリサイド層9の接触抵抗が低減し、オン電流Ionを増加させることができる。

【0046】

なお、上述した実施形態では、フィン型半導体3をバルク基板上に形成する場合を例にとって説明したが、フィン型半導体3をSOI基板上に形成した構成に適用してもよい。また、上述した実施形態では、フィン型半導体3の両端部の側壁にオフセットスペーサ7を設ける方法について説明したが、オフセットスペーサ7は省略するようにしてもよい。

また、フィン型トランジスタとしてNチャネル型トランジスタについて説明したが、パンチスルーストッパおよびソースドレインの不純物のタイプを変えることで、Pチャネル型トランジスタに変えることができる。

【0047】

本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

【符号の説明】

【0048】

1 半導体基板、2 埋め込み絶縁層、3 フィン型半導体、4 パンチスルーストッパ層、5 キャップ層、6 ゲート絶縁膜、7 オフセットスペーサ、8 サイドウォールスペーサ、9 シリサイド層、10 高濃度不純物拡散層、11 トップ層、12 ハードマスク層、12 ´ ハードマスク材、13 ゲート電極、13´ ゲート電極材、14 半導体層、15 チャネル領域、16 PN接合面

【特許請求の範囲】

【請求項1】

フィン型半導体と、

前記フィン型半導体の両端部が露出するようにして前記フィン型半導体の側面にゲート絶縁膜を介して形成されたゲート電極と、

前記フィン型半導体の両端部に形成されたソース/ドレインと、

前記フィン型半導体の上部の表面が露出するようにして前記ソース/ドレインの側面および前記ゲート電極の側面に形成されたオフセットスペーサおよびサイドウォールスペーサと、

前記フィン型半導体の上部の前記ソース/ドレインの表面に形成されたシリサイド層とを備えることを特徴とする半導体装置。

【請求項2】

前記フィン型半導体の下部を埋め込む埋め込み絶縁層と、

前記フィン型半導体の下部に形成されたパンチスルーストッパ層とをさらに備えることを特徴とする請求項1に記載の半導体装置。

【請求項3】

前記ソース/ドレインおよび前記パンチスルーストッパで形成される接合面と前記シリサイド層との距離が30nm以上であることを特徴とする請求項2に記載の半導体装置。

【請求項4】

半導体基板上にフィン型半導体を形成する工程と、

前記フィン型半導体表面にゲート絶縁膜を形成する工程と、

前記フィン型半導体の両端部が露出するようにして前記フィン型半導体の側面に前記ゲート絶縁膜を介してゲート電極を形成する工程と、

前記ゲート電極上にトップ層を形成する工程と、

前記フィン型半導体の両端部の側面および前記ゲート電極の側面にオフセットスペーサを形成する工程と、

前記フィン型半導体の両端部にソース/ドレインを形成する工程と、

前記フィン型半導体の両端部の側面および前記ゲート電極の側面の前記オフセットスペーサの外側にサイドウォールスペーサを形成する工程と

前記フィン型半導体の両端部に形成された前記オフセットスペーサおよび前記サイドウォールスペーサの上部を除去することにより、前記フィン型半導体の両端部の上部の表面を露出させる工程と、

前記フィンの両端部の上部の表面に半導体層を選択エピタキシャル成長させる工程と、

前記半導体層をシリサイド化することにより、前記フィンの両端部の上部の表面にシリサイド層を形成する工程とを備えることを特徴とする半導体装置の製造方法。

【請求項5】

前記ゲート電極および前記トップ層の上にハードマスクを形成する工程を備え、

前記フィン型半導体の両端部のオフセットスペーサおよびサイドウォールスペーサの上部を除去する時に、前記トップ層上の前記ハードマスクが残り、かつ前記オフセットスペーサおよびサイドウォールスペーサが前記ゲート電極の側面および前記トップ層の側面を完全に覆ったまま、前記ハードマスクが薄膜化されることを特徴とする請求項4に記載の半導体装置の製造方法。

【請求項1】

フィン型半導体と、

前記フィン型半導体の両端部が露出するようにして前記フィン型半導体の側面にゲート絶縁膜を介して形成されたゲート電極と、

前記フィン型半導体の両端部に形成されたソース/ドレインと、

前記フィン型半導体の上部の表面が露出するようにして前記ソース/ドレインの側面および前記ゲート電極の側面に形成されたオフセットスペーサおよびサイドウォールスペーサと、

前記フィン型半導体の上部の前記ソース/ドレインの表面に形成されたシリサイド層とを備えることを特徴とする半導体装置。

【請求項2】

前記フィン型半導体の下部を埋め込む埋め込み絶縁層と、

前記フィン型半導体の下部に形成されたパンチスルーストッパ層とをさらに備えることを特徴とする請求項1に記載の半導体装置。

【請求項3】

前記ソース/ドレインおよび前記パンチスルーストッパで形成される接合面と前記シリサイド層との距離が30nm以上であることを特徴とする請求項2に記載の半導体装置。

【請求項4】

半導体基板上にフィン型半導体を形成する工程と、

前記フィン型半導体表面にゲート絶縁膜を形成する工程と、

前記フィン型半導体の両端部が露出するようにして前記フィン型半導体の側面に前記ゲート絶縁膜を介してゲート電極を形成する工程と、

前記ゲート電極上にトップ層を形成する工程と、

前記フィン型半導体の両端部の側面および前記ゲート電極の側面にオフセットスペーサを形成する工程と、

前記フィン型半導体の両端部にソース/ドレインを形成する工程と、

前記フィン型半導体の両端部の側面および前記ゲート電極の側面の前記オフセットスペーサの外側にサイドウォールスペーサを形成する工程と

前記フィン型半導体の両端部に形成された前記オフセットスペーサおよび前記サイドウォールスペーサの上部を除去することにより、前記フィン型半導体の両端部の上部の表面を露出させる工程と、

前記フィンの両端部の上部の表面に半導体層を選択エピタキシャル成長させる工程と、

前記半導体層をシリサイド化することにより、前記フィンの両端部の上部の表面にシリサイド層を形成する工程とを備えることを特徴とする半導体装置の製造方法。

【請求項5】

前記ゲート電極および前記トップ層の上にハードマスクを形成する工程を備え、

前記フィン型半導体の両端部のオフセットスペーサおよびサイドウォールスペーサの上部を除去する時に、前記トップ層上の前記ハードマスクが残り、かつ前記オフセットスペーサおよびサイドウォールスペーサが前記ゲート電極の側面および前記トップ層の側面を完全に覆ったまま、前記ハードマスクが薄膜化されることを特徴とする請求項4に記載の半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【公開番号】特開2013−45901(P2013−45901A)

【公開日】平成25年3月4日(2013.3.4)

【国際特許分類】

【出願番号】特願2011−182828(P2011−182828)

【出願日】平成23年8月24日(2011.8.24)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

【公開日】平成25年3月4日(2013.3.4)

【国際特許分類】

【出願日】平成23年8月24日(2011.8.24)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

[ Back to top ]