半導体装置および半導体装置の製造方法

【課題】電界が局所的に集中することを抑制して、高耐圧化した半導体装置を提供する。

【解決手段】第1導電型の第1ドリフト領域140は、平面視でソース領域110から離間して設けられている。第1導電型の第2ドリフト領域150は、平面視で第1ドリフト領域140のうちソース領域110と反対側の領域に接している。第1導電型のドレイン領域120は、平面視で第1ドリフト領域140から離間しているとともに、平面視で第2ドリフト領域150のうち第1ドリフト領域140と反対側の領域に接している。チャネル領域130上には、ゲート絶縁層200およびゲート電極400が設けられている。第1フィールドプレート絶縁層300は、半導体基板100上に設けられ、少なくとも平面視で第1ドリフト領域140と第2ドリフト領域150の一部と重なるように設けられている。第1フィールドプレート電極420は、第1フィールドプレート絶縁層300上に接している。

【解決手段】第1導電型の第1ドリフト領域140は、平面視でソース領域110から離間して設けられている。第1導電型の第2ドリフト領域150は、平面視で第1ドリフト領域140のうちソース領域110と反対側の領域に接している。第1導電型のドレイン領域120は、平面視で第1ドリフト領域140から離間しているとともに、平面視で第2ドリフト領域150のうち第1ドリフト領域140と反対側の領域に接している。チャネル領域130上には、ゲート絶縁層200およびゲート電極400が設けられている。第1フィールドプレート絶縁層300は、半導体基板100上に設けられ、少なくとも平面視で第1ドリフト領域140と第2ドリフト領域150の一部と重なるように設けられている。第1フィールドプレート電極420は、第1フィールドプレート絶縁層300上に接している。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置および半導体装置の製造方法に関する。

【背景技術】

【0002】

近年、半導体装置を高耐圧化させるため、様々な構造の半導体装置が提案されている。

【0003】

特許文献1(特開2009−158821号公報)には、以下のような半導体装置が記載されている。P型半導体基板には、N型の第1ドリフト領域が形成されている。第2ドリフト領域は、第1ドリフト領域と連続するように形成され、第1ドリフト領域よりも底面の深さが深く形成されている。第2ドリフト領域のN型の不純物濃度は第1ドリフト領域よりも高い。また、N型のドレイン領域は、第2ドリフト領域に接触して形成されている。N型のソース領域は、第1ドリフト領域と離間して形成されている。これにより、半導体基板面と平行な方向の電界が両ドリフト領域によって二段階に緩和される。また、基板面に垂直な方向の電界を緩和する効果を高めることができるとされている。

【0004】

また、特許文献2(特開昭61−180483号公報)には、以下のような高耐圧MOS型半導体装置が記載されている。ゲートは、第1導電型の半導体基板の一主面上に、ゲート絶縁膜を介して形成されている。ソース領域は、第2導電型の高濃度領域であり、ゲートの一方の端部直下を含み、半導体基板の一主面に形成されている。第1ドリフト領域は、第2導電型で低濃度であり、ゲートの他方の端部直下を含み、半導体基板の一主面に形成されている。第2ドリフト領域は、第2導電型で中濃度領域であり、第1ドリフト領域に継続して、半導体基板の一主面に形成されている。フィールド(プレート)電極は、第1および第2ドリフト領域上にゲート絶縁膜よりも厚い層間絶縁膜を介して形成され、ソース領域に接続されている。これにより、半導体装置を高耐圧化することができ、またはオン抵抗が低下することによる高電流化することができるとされている。

【0005】

また、特許文献3(特開2006−202847号公報)には、以下のような半導体装置が記載されている。基板表面には、N+型ソース領域、チャネル領域およびN+型ドレイン領域が順に形成されている。ソース領域から基板の下方にかけて、縦型バイポーラトランジスタが形成されている。P型基板上には、縦型バイポーラトランジスタに接続するN+型の埋め込み層が形成されている。また、ドレイン領域とチャネル領域との間には、N−型のドリフト領域が形成されている。これにより、ドレイン端での電流集中を防止して静電放電に対する耐性に優れた半導体装置を得ることができるとされている。

【0006】

また、特許文献4(特開2007−027641号公報)には、以下のような半導体装置が記載されている。p型半導体基板上には、p型ボディ領域が形成されている。ボディ領域の表面領域には、n+型ソース領域が形成されている。半導体基板上には、n+型ドレイン領域が形成されている。ソース領域とドレイン領域との間には、n−型ドリフト領域が形成されている。ボディ領域上には、ゲート絶縁膜が形成されている。ドリフト領域上には、保護絶縁膜が形成されている。ゲート絶縁膜上および保護絶縁膜上の一部には、ゲート電極が形成されている。さらに、ゲート電極上、ソース領域上およびドレイン領域上には、シリサイド膜が形成されている。これにより、ゲート抵抗を充分に低抵抗化することができるとともに、高耐圧が得られるとされている。

【0007】

また、特許文献5(特開2009−164651号公報)には、以下のような半導体装置が記載されている。エピタキシャル・シリコン層上には、LOCOS膜を介して、ゲート電極が形成されている。LOCOS膜の左側には、P型の第1のドリフト層が形成されている。平面視でゲート電極を挟んでLOCOS膜の右側には、P+型のソース層が形成されている。第1のドリフト層よりも深い領域に、P型の第2のドリフト層が形成されている。第1および第2のドリフト層と接して、複数層からなるP型のドレイン層が形成されている。これにより、高いゲート耐圧およびソース・ドレイン耐圧を有するとともに、低いオン抵抗を有したトランジスタを得ることができるとされている。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特開2009−158821号公報

【特許文献2】特開昭61−180483号公報

【特許文献3】特開2006−202847号公報

【特許文献4】特開2007−027641号公報

【特許文献5】特開2009−164651号公報

【発明の概要】

【発明が解決しようとする課題】

【0009】

上記のように、ソース領域およびドレイン領域の間に設けられたドリフト領域や、ドリフト領域上に絶縁層を介して設けられたフィールドプレート電極を備える横型MOSFET(Metal Oxide Semiconductor Field Effect Transistor)が開示されている。しかし、発明者は、半導体装置の構成によっては、ドリフト領域中の電界強度が偏ってしまう可能性があることを見出した。

【課題を解決するための手段】

【0010】

本発明によれば、

半導体基板と、

前記半導体基板に設けられた第1導電型のソース領域と、

前記半導体基板に設けられ、平面視で前記ソース領域から離間して設けられた第1導電型の第1ドリフト領域と、

前記半導体基板のうち、平面視で前記ソース領域および前記第1ドリフト領域に挟まれた領域であるチャネル領域と、

前記半導体基板に設けられ、平面視で前記第1ドリフト領域のうち前記ソース領域と反対側の領域に接している第1導電型の第2ドリフト領域と、

前記半導体基板に設けられ、平面視で前記第1ドリフト領域から離間するとともに、平面視で前記第2ドリフト領域のうち前記第1ドリフト領域と反対側の領域に接しており、前記第1ドリフト領域および前記第2ドリフト領域よりも不純物濃度が高い第1導電型のドレイン領域と、

前記チャネル領域上に設けられたゲート絶縁層と、

前記ゲート絶縁層上に接し、平面視で前記チャネル領域と重なるように設けられたゲート電極と、

前記半導体基板上に設けられ、少なくとも平面視で前記第1ドリフト領域と前記第2ドリフト領域の一部と重なるように設けられ、前記ゲート絶縁層よりも厚い第1フィールドプレート絶縁層と、

前記第1フィールド絶縁層上に接し、平面視で前記第1ドリフト領域と前記第2ドリフト領域の一部と重なるように設けられた第1フィールドプレート電極と、

を備え、

前記第1ドリフト領域の深さをσ1、前記第1ドリフト領域の不純物濃度をN1、前記第2ドリフト領域の深さをσ2、前記第2ドリフト領域の不純物濃度をN2としたとき、下記式(1)を満たす半導体装置が提供される。

【0011】

【数1】

【0012】

(ただし、tOX*は前記ゲート絶縁層の電気的膜厚、tFP*は前記第1ドリフト領域と前記第2ドリフト領域との境界における前記第1フィールドプレート絶縁層の電気的膜厚である。なお、電気的膜厚は、誘電率と物理的膜厚との積である。)

【0013】

本発明によれば、

半導体基板に第1導電型の不純物を導入することにより、第1ドリフト領域を形成する第1ドリフト領域工程と

前記半導体基板に第1導電型の不純物を注入することにより、平面視で前記第1ドリフト領域に接するように、第2ドリフト領域を形成する第2ドリフト領域形成工程と、

前記半導体基板に第1導電型の不純物を注入することにより、平面視で前記第1ドリフト領域のうち前記第2ドリフト領域と反対側の領域から離間した位置に、ソース領域を形成する工程と、

前記半導体基板に前記第1ドリフト領域および前記第2ドリフト領域よりも高い不純物濃度で第1導電型の不純物を注入することにより、平面視で前記第1ドリフト領域から離間するとともに、平面視で前記第2ドリフト領域のうち前記第1ドリフト領域と反対側の領域に接するように、ドレイン領域を形成する工程と、

前記半導体基板上に、平面視で前記ソース領域および前記第1ドリフト領域に挟まれたチャネル領域に重なるようにゲート絶縁層を形成するゲート絶縁層形成工程と、

少なくとも平面視で前記第1ドリフト領域と前記第2ドリフト領域の一部と重なるように、前記ゲート絶縁層よりも厚く第1フィールドプレート絶縁層を形成する第1フィールドプレート絶縁層形成工程と、

前記ゲート絶縁層上に接するとともに、平面視で前記チャネル領域と重なるようにゲート電極を形成する工程と、

前記第1フィールドプレート絶縁層上に接し、平面視で前記第1ドリフト領域と前記第2ドリフト領域の一部と重なるように、第1フィールドプレート電極を形成する工程と、

を備え、

前記第1ドリフト領域形成工程、前記第2ドリフト領域形成工程、前記ゲート絶縁層形成工程および前記第1フィールドプレート絶縁層形成工程において、前記第1ドリフト領域の深さをσ1、前記第1ドリフト領域の不純物濃度をN1、前記第2ドリフト領域の深さをσ2、前記第2ドリフト領域の不純物濃度をN2としたとき、上記式(1)を満たすように、前記第1ドリフト領域、前記第2ドリフト領域、前記ゲート絶縁層および前記第1フィールドプレート絶縁層を形成する半導体装置の製造方法が提供される。

【0014】

本発明によれば、ソース領域およびドレイン領域の間には、第1ドリフト領域および第2ドリフト領域が設けられている。第1フィールドプレート電極は、第1フィールドプレート絶縁層上に接し、平面視で第1ドリフト領域と第2ドリフト領域の一部と重なるように設けられている。このとき、これらを構成する物性値は、上記式(1)を満たしている。これにより、半導体装置内の電界強度を偏りなく分布させることができる。また、ゲート電極および第1ドリフト領域の間、または第1ドリフト領域および第2ドリフト領域の間等における電界強度が大きくなることを抑制することができる。したがって、電界が局所的に集中することを抑制して、高耐圧化した半導体装置を提供することができる。

【発明の効果】

【0015】

本発明によれば、電界が局所的に集中することを抑制して、高耐圧化した半導体装置を提供することができる。

【図面の簡単な説明】

【0016】

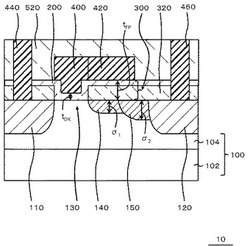

【図1】第1の実施形態に係る半導体装置の構成を示す断面図である。

【図2】第1の実施形態に係る半導体装置の構成を示す回路図である。

【図3】第1の実施形態に係る第1ドリフト領域の深さに対する電界強度の関係を示した図である。

【図4】第1の実施形態に係る半導体装置の構成を説明するための図である。

【図5】第1の実施形態に係る半導体装置の製造方法を説明するための断面図である。

【図6】第1の実施形態に係る半導体装置の製造方法を説明するための断面図である。

【図7】第1の実施形態に係る半導体装置の製造方法を説明するための断面図である。

【図8】第1の実施形態に係る半導体装置の製造方法を説明するための断面図である。

【図9】第1の実施形態に係る半導体装置の製造方法を説明するための断面図である。

【図10】比較例の半導体装置の構成を示す断面図である。

【図11】第1の実施形態の効果を説明するための図である。

【図12】第2の実施形態に係る半導体装置の構成を示す断面図である。

【図13】第3の実施形態に係る半導体装置の構成を示す断面図である。

【図14】第3の実施形態に係る半導体装置の製造方法を説明するための断面図である。

【図15】第3の実施形態に係る半導体装置の製造方法を説明するための断面図である。

【図16】第4の実施形態に係る半導体装置の構成を示す断面図である。

【図17】第4の実施形態に係る半導体装置の製造方法を説明するための断面図である。

【図18】第4の実施形態に係る半導体装置の製造方法を説明するための断面図である。

【図19】第4の実施形態に係る半導体装置の製造方法を説明するための断面図である。

【図20】第5の実施形態に係る半導体装置の構成を示す断面図である。

【図21】第6の実施形態に係る半導体装置の構成を示す断面図である。

【発明を実施するための形態】

【0017】

以下、本発明の実施の形態について、図面を用いて説明する。尚、すべての図面において、同様な構成要素には同様の符号を付し、適宜説明を省略する。

【0018】

(第1の実施形態)

図1〜図4を用い、第1の実施形態に係る半導体装置10について説明する。この半導体装置10は、以下の構成を備えている。第1導電型のソース領域110は、半導体基板100に設けられている。第1導電型の第1ドリフト領域140は、半導体基板100に設けられ、平面視でソース領域110から離間して設けられている。半導体基板100のうち、平面視でソース領域110および第1ドリフト領域140に挟まれた領域には、チャネル領域130が形成されている。第1導電型の第2ドリフト領域150は、半導体基板100に設けられ、平面視で第1ドリフト領域140のうちソース領域110と反対側の領域に接している。第1導電型のドレイン領域120は、半導体基板100に設けられ、平面視で第1ドリフト領域140から離間しているとともに、平面視で第2ドリフト領域150のうち第1ドリフト領域140と反対側の領域に接している。また、第1導電型のドレイン領域120は、第1ドリフト領域140および第2ドリフト領域150よりも不純物濃度が高い。チャネル領域130上には、ゲート絶縁層200が設けられている。ゲート電極400は、ゲート絶縁層200上に接し、平面視でチャネル領域130重なるように設けられている。第1フィールドプレート絶縁層300は、半導体基板100上に設けられ、少なくとも平面視で第1ドリフト領域140と第2ドリフト領域150の一部と重なるように設けられている。また、第1フィールドプレート絶縁層300は、ゲート絶縁層200よりも厚い。第1フィールドプレート電極420は、第1フィールドプレート絶縁層300上に接し、平面視で第1ドリフト領域140と第2ドリフト領域150の一部と重なるように設けられている。さらに、第1ドリフト領域140の深さをσ1、第1ドリフト領域140の不純物濃度をN1、第2ドリフト領域150の深さをσ2、第2ドリフト領域150の不純物濃度をN2としたとき、下記式(1)を満たす。

【0019】

【数1】

【0020】

ただし、tOX*はゲート絶縁層200の電気的膜厚、tFP*は第1ドリフト領域140と第2ドリフト領域150との境界における第1フィールドプレート絶縁層300の電気的膜厚である。なお、電気的膜厚は、誘電率と膜厚との積である。以下、詳細を説明する。

【0021】

まず、図1を用い、半導体装置10の全体構造について、説明する。図1は、第1の実施形態に係る半導体装置10の構成を示す断面図である。

【0022】

図1のように、半導体装置10は、横型MOSFETである。この半導体装置10は、たとえば、10V以上1000V未満の電圧が印加される電源用ICとして用いられる。具体的には、半導体装置10は、たとえば、コンピュータ、車載用電子機器、民生用電子機器または通信機器などの電源ICに用いられる。また、第1ドリフト領域140および第2ドリフト領域150の横方向の長さ、不純物濃度の構成によっては、1000V以上の高電圧が印加される、電力、輸送機器向け等の電力変換機にも用いることができる。

【0023】

第1の実施形態では、たとえば、半導体基板100の少なくとも主面側は、III族窒化物半導体からなるIII族窒化物半導体層104である。半導体基板100は、たとえば、下地基板102と、III族窒化物半導体からなるIII族窒化物半導体層104を備えている。III族窒化物半導体層104は、下地基板102の主面上に設けられている。下地基板102は、たとえば、Si基板、サファイア基板、SiC基板またはGaN基板(バルクGaN基板)である。好ましくは、下地基板102は、たとえば、Si基板である。これにより、Si系の半導体製造装置を流用することができる。

【0024】

下地基板102とIII族窒化物半導体層104との間には、バッファ層(不図示)が設けられていてもよい。バッファ層は、下地基板102とIII族窒化物半導体層104との格子定数の差に基づいて、適切な材料が用いられる。具体的には、バッファ層は、たとえば、AlGaN層、またはその積層構造である。

【0025】

III族窒化物半導体層104には、ソース領域110、チャネル領域130、第1ドリフト領域140、第2ドリフト領域150およびドレイン領域120が形成されている。これにより、横型MOSFETが形成されている。ここで、III族窒化物半導体は、Si系の半導体装置と比較して、高い耐圧性と、飽和ドリフト速度を有している。これにより、高耐圧で低損失なスイッチング素子を形成することができる。具体的には、III族窒化物半導体層104は、たとえば、GaN層である。また、III族窒化物半導体層104の面方位のうち、半導体基板100の法線方向の面方位は、たとえば(0001)(c−面)である。

【0026】

ここで、III族窒化物半導体層104にFETが形成されている場合、当該FETは、nチャネル型である。ただし、pチャネル型であってもよい。

【0027】

III族窒化物半導体層104は、たとえば、真性半導体である。言い換えれば、III族窒化物半導体層104のうち、ソース領域110およびドレイン領域130の間に位置する部分には、p型の不純物領域が形成されていない。また、少なくともチャネル領域130の不純物濃度は、たとえば、1×10−16atoms/cm3以下である。このような場合に、後述する半導体装置10の構成を備えていることにより、顕著に高耐圧化させることができる。

【0028】

また、ソース領域110、第1ドリフト領域140、第2ドリフト領域150およびドレイン領域120は、たとえば、n型である。すなわち、上記した「第1導電型」とは、たとえばn型である。当該n型の不純物は、たとえば、Siである。これにより、III族窒化物半導体層104において、容易にnチャネル型FETを形成することができる。

【0029】

なお、以下において、「半導体基板100に」とした場合には、特に断りのない限り、「半導体基板100のうちのIII族窒化物半導体層104に」であることを含んでいる。また、「第1導電型」は、n型であるとする。

【0030】

n型のソース領域110は、半導体基板100に設けられている。ここで、ソース領域110等の不純物が導入された領域は、たとえば、n型不純物をイオン注入することにより形成されている。また、ここでいう「ソース領域110」等の「不純物が導入された範囲」は、半導体基板100のうち不純物濃度が1×1016atoms/cm3以上である領域をいう。言い換えれば、「不純物が導入された範囲」は、半導体基板100の不純物濃度に対して、10倍以上高い濃度である領域をいう。なお、当該領域の不純物濃度が半導体基板100の不純物濃度に対して差が無い場合は、「不純物が導入された範囲」は最も不純物濃度が高い場所を頂点としたガウス分布であると仮定したときに頂点からσまで(ここでのσは標準偏差の意)の領域であってもよい。なお、上記した「不純物が導入された範囲」の定義は、「ソース領域110」、「第1ドリフト領域140」、「第2ドリフト領域150」および「ドレイン領域120」について適用される。また、当該定義は、不純物が導入された領域のうち、平面視での幅、半導体基板100の主面と垂直の方向における深さに対して適用される。

【0031】

n型の第1ドリフト領域140は、半導体基板100に設けられており、平面視でソース領域110から離間して設けられている。半導体基板100のうち平面視でソース領域110および第1ドリフト領域140に挟まれた領域には、チャネル領域130が形成されている。チャネル領域130の長さは、所望のオン抵抗、オフ抵抗またはドレイン・ソース間電流の大きさなどによって決定される。チャネル領域130の典型的な長さは、たとえば100nm以上10μm未満である。

【0032】

n型の第2ドリフト領域150は、半導体基板100に設けられ、平面視で第1ドリフト領域140のうちソース領域110と反対側の領域に接している。第2ドリフト領域150は、たとえば、第1ドリフト領域140よりも深く形成されている。なお、第1ドリフト領域140および第2ドリフト領域150における不純物濃度は、ソース領域110よりも低い。

【0033】

なお、第1ドリフト領域140および第2ドリフト領域150のうち、ソース領域110からドレイン領域120に向かう方向の長さについても、所望のオン抵抗、オフ抵抗またはドレイン・ソース間電流の大きさなどによって決定される。第1ドリフト領域140および第2ドリフト領域150のうち、ソース領域110からドレイン領域120に向かう方向の長さは、たとえば、100nm以上10μm未満である。

【0034】

n型のドレイン領域120は、半導体基板100に設けられ、平面視で第1ドリフト領域140から離間しているとともに、平面視で第2ドリフト領域150のうち第1ドリフト領域140と反対側の領域に接している。ここでいう「ドレイン領域120が平面視で第1ドリフト領域140から離間している」とは、ドレイン領域120が第1ドリフト領域140と接していないことを意味する。これにより、ゲート電極400と第1ドリフト領域140との間での電界集中を緩和することができる。

【0035】

また、ドレイン領域120は、第1ドリフト領域140および第2ドリフト領域150よりも不純物濃度が高い。ドレイン領域120と同様にして、ソース領域110も第1ドリフト領域140および第2ドリフト領域150よりも不純物濃度が高いことが好ましい。ソース領域110およびドレイン領域120の不純物濃度は、第1ドリフト領域140および第2ドリフト領域150よりも10倍以上高いことが好ましい。具体的には、ソース領域110およびドレイン領域120の不純物濃度が1×1020atoms/cm3以上であるとき、第1ドリフト領域140および第2ドリフト領域150の不純物濃度は1×1019atoms/cm3未満であることが好ましい。これにより、ソース・ドレイン間電圧によって電界が集中することを抑制することができる。

【0036】

なお、図1では、ドレイン領域120の深さが第2ドリフト領域150等よりも深い場合を示しているが、ドレイン領域120の深さは第2ドリフト領域150よりも浅くていもよい。

【0037】

ゲート絶縁層200は、チャネル領域130上に接して設けられている。ゲート絶縁層200は、たとえば、スパッタにより形成されたSiO2、SiN、Al2O3である。そのほか、ゲート絶縁層200は、Ta2O5などの高誘電率材料により形成されていてもよい。

【0038】

ゲート電極400は、ゲート絶縁層200上に接し、平面視でチャネル領域130に重なるように設けられている。

【0039】

第1フィールドプレート絶縁層300は、半導体基板100上に設けられ、少なくとも平面視で第1ドリフト領域140と第2ドリフト領域150の一部と重なるように設けられている。ここでいう「第1フィールドプレート絶縁層300」とは、後述する第1フィールドプレート電極420と半導体基板100の主面との間に設けられた絶縁層のことである。また、ここでいう「第1フィールドプレート絶縁層300」は、ゲート絶縁層200と独立に形成されている必要は無く、ゲート絶縁層200の一部を含んでいてもよい。第1の実施形態では、第1フィールドプレート絶縁層300は、下地絶縁層320の一部と、ゲート絶縁層200一部とを含んでいる。下地絶縁層320は、半導体基板100上に接して設けられており、平面視でチャネル領域130と重なる領域に開口部を有している。また、上述したゲート絶縁層200は、下地絶縁層320の開口部に露出したチャネル領域130上、および下地絶縁層320上に設けられている。これにより、第1フィールドプレート絶縁層300をゲート絶縁層200よりも厚くすることができる。なお、下地絶縁層320は、たとえば、CVD(Chemical Vapor Deposition)により形成された、SiO2、SiNなどである。

【0040】

第1フィールドプレート電極420は、第1フィールドプレート絶縁層300上に接し、平面視で第1ドリフト領域140と第2ドリフト領域150の一部と重なるように設けられている。言い換えれば、第1フィールドプレート電極420の一端は、平面視で第1ドリフト領域140および第2ドリフト領域150の境界よりもドレイン領域120側に位置している。また、第1フィールドプレート電極420は第1フィールドプレート絶縁層300上に設けられていることにより、第1フィールドプレート電極420の下面は、ゲート電極400の下面よりも半導体基板100の上面から離間している。

【0041】

第1の実施形態では、第1フィールドプレート電極420は、ゲート電極400に接続している。また、第1フィールドプレート電極420は、ゲート電極400と一体として形成されている。第1フィールドプレート電極420は、ゲート電極400と同じ材料により形成されている。なお、この場合では、ゲート電極400と第1フィールドプレート電極420との間に、界面は形成されていない。また、ゲート電極400、第1フィールドプレート電極420の材料は、たとえば、Alおよび/またはTiNなどである。このように、第1フィールドプレート電極420をゲート電極400と一体として形成することにより、製造工程を簡略化することができる。

【0042】

さらに、第1フィールドプレート電極420を覆うように、第1層間絶縁層520が設けられていてもよい。第1層間絶縁層520は、たとえば、SiO2、SiN、SiON、SiOC、SiOCH、SiCOHまたはSiOFなどである。

【0043】

ソース電極440は、平面視でソース領域110と重なるように設けられ、第1層間絶縁層520、ゲート絶縁層200および下地絶縁層320を貫通してソース領域110に接続している。また、ドレイン電極460は、平面視でドレイン領域120と重なるように設けられ、第1層間絶縁層520、ゲート絶縁層200および下地絶縁層320を貫通してドレイン領域120に接続している。また、ソース電極440、ドレイン電極460の材料は、たとえば、AlまたはTiNなどである。

【0044】

次に、図2を用い、第1の実施形態に係る半導体装置10の回路について説明する。図2は、第1の実施形態に係る半導体装置10の構成を示す回路図である。図2のように、第1の実施形態の半導体装置10は、たとえば、DC―DCコンバータである。この回路は、たとえば、降圧型のコンバータである。この半導体装置10は、たとえば、DC−DCコントローラIC800、2つのnチャネルFET11、インダクタ820およびコンデンサ840を備えている。2つのnチャネルFET11は、VINとGNDとの間に直列に接続されている。また、このnチャネルFET11は、たとえば、図1で示されたFETである。nチャネルFET11のゲート電圧は、DC−DCコントローラIC800によって制御されている。2つのnチャネルFET11の間からは、インダクタ820を介してVOUTが取り出される。なお、インダクタ820とVOUTとの間は、コンデンサ840を介してGNDに接続されている。また、DC−DCコントローラIC800は、たとえば、VINから入力されたDC信号をパルスに変換する。変換したパルスにより、nチャネルFET11は、インダクタ820にエネルギーを蓄え、次いでそのエネルギーをVOUTに放出するという動作を交互に繰り返す。第1の実施形態によれば、nチャネルFET11は、安定的にスイッチング機能を発揮することができる。

【0045】

次に、図3および図4を用い、第1の実施形態に係る半導体装置10の構成について、さらに詳細に説明する。図3は、第1の実施形態に係る第1ドリフト領域140の深さに対する電界強度の関係を示した図である。図4は、第1の実施形態に係る半導体装置10の構成を説明するための図である。

【0046】

図3は、ゲート電圧を0V、ドレイン・ソース間電圧を100Vとしたときの電界強度の第1ドリフト領域140の深さσ1の依存性についてシミュレーションした結果を示している。ゲート絶縁層200の厚さ(tOX)は50nm、第1ドリフト領域140と第2ドリフト領域150との境界における第1フィールドプレート絶縁層300の厚さ(tFP)は300nm、第2ドリフト領域150の不純物濃度(N2)は5×1018cm−2、第2ドリフト領域150の深さ(σ2)は15nm、第1ドリフト領域140の不純物濃度(N1)は2×1018cm−2であると仮定した。横軸は、第1ドリフト領域140の深さσ1(単位nm)である。また、縦軸は、電界強度(単位MV/cm)である。実線は、ゲート電極400および第1ドリフト領域140間の電界強度を示している。また、点線は、第1ドリフト領域140および第2ドリフト領域150間の電界強度を示している。

【0047】

図3のように、ゲート電極400および第1ドリフト領域140間の電界強度は、第1ドリフト領域140の深さσ1が大きくなるにつれて、大きくなる傾向にある。一方、第1ドリフト領域140および第2ドリフト領域150間の電界強度は、第1ドリフト領域140の深さσ1に対して下に凸の傾向を示す。第1ドリフト領域140の深さσ1が30nm以下の領域では、第1ドリフト領域140および第2ドリフト領域150間の電界強度は、第1ドリフト領域140の深さσ1が大きくなるにつれて、小さくなる傾向にある。

【0048】

ここで、ゲート電極400および第1ドリフト領域140間の電界強度と、第1ドリフト領域140および第2ドリフト領域150間の電界強度とが等しくなるときの第1ドリフト領域140の深さσ1をσ1cとする。第1ドリフト領域140の深さσ1がσ1cのとき、半導体装置10内の電界強度が最も均等(一様)に分布する。言い換えれば、このとき、半導体装置10内の電界強度の最大値を、最も小さくすることができる。

【0049】

また、第1ドリフト領域140および第2ドリフト領域150間の電界強度は、第1ドリフト領域140の深さσ1に対して、あまり大きく変わらない。反対に、ゲート電極400および第1ドリフト領域140間の電界強度は、第1ドリフト領域140の深さσ1に対して大きく依存している。したがって、第1ドリフト領域140の深さσ1をσ1cより小さくすることにより、半導体装置10内の電界強度を全体的に小さくすることができる。特に、第1ドリフト領域140の深さσ1をσ1cより小さくすることにより、ゲート電極400および第1ドリフト領域140間の電界強度を小さくすることができる。

【0050】

図4(a)は、様々な条件において、σ1cを算出した結果を示している。図4のように、発明者は、第1ドリフト領域140の深さをσ1、第1ドリフト領域140の不純物濃度をN1、第2ドリフト領域150の深さをσ2、第2ドリフト領域150の不純物濃度をN2としたとき、σ1cがσ2N2/N1に比例することを見出した。この比例定数をCσとしたとき、σ1cを下記式(2)で表すことができる。

【0051】

【数2】

【0052】

また、図4(b)は、ゲート絶縁層200の厚さをtOXとしたときの上記比例定数Cσのゲート絶縁層200の厚さtOX依存性を示している。図4のように、発明者は、比例定数Cσがゲート絶縁層200の厚さtOXの平方根に比例することを見出した。図中の実線は、比例定数Cσがゲート絶縁層200の厚さtOXの平方根に比例する関数をフィッティングしたものである。発明者は、半導体装置10における具体的なパラメータから、上記した関数を下記式(3)により表せることを見出した。ここで、ゲート絶縁層200の電気的膜厚をtOX*、第1ドリフト領域140と第2ドリフト領域150との境界における第1フィールドプレート絶縁層300の電気的膜厚をtFP*としたとき、比例定数Cσを以下の式(3)のように表すことができる。

【0053】

【数3】

【0054】

上記式(3)のうち、tOX*およびtFP*は、上述のように、それぞれゲート絶縁層200および第1フィールドプレート絶縁層300の電気的膜厚を示している。ここでいう「電気的膜厚」とは、絶縁膜の物理的膜厚と誘電率との積のことをいう。なお、「物理的膜厚」とは、対象となる層のうち断面視で下面から上面までの厚さのことをいう。

【0055】

したがって、ゲート絶縁層200の誘電率をεOX、ゲート絶縁層200の物理的膜厚をtOXとしたとき、ゲート絶縁層200の電気的膜厚tOX*を以下の式(4)のように表すことができる。

【0056】

【数4】

【0057】

また、第1フィールドプレート絶縁層300の誘電率をεFP*、ゲート絶縁層200の物理的膜厚をtFPとしたとき、第1フィールドプレート絶縁層300の電気的膜厚tFP*を以下の式(5)のように表すことができる。

【0058】

【数5】

【0059】

なお、第1フィールドプレート絶縁層300が複数の(たとえばN層の)絶縁層によって形成されている場合、それぞれの絶縁層の誘電率をεj、物理的膜厚をtj(1≦j≦N)としたとき、第1フィールドプレート絶縁層300の誘電率εFP*、ゲート絶縁層200の物理的膜厚tFPをそれぞれ以下の式(6)、式(7)のように表すことができる。

【0060】

【数6】

【0061】

【数7】

【0062】

第1の実施形態のように、第1フィールドプレート絶縁層300は、ゲート絶縁層200および下地絶縁層320が積層されることにより形成されている。この場合、ゲート絶縁層200の誘電率並びに厚さ、および下地絶縁層320の誘電率並びに厚さを、式(6)および式(7)に代入し、さらに式(5)を計算することにより、第1フィールドプレート絶縁層300の電気的膜厚tFP*を求めることができる。

【0063】

以上により、第1ドリフト領域140の深さσ1がσ1cより小さいとき、下記式(1)を満たす。

【0064】

【数8】

【0065】

上記式(1)を満たすことにより、ゲート電極400および第1ドリフト領域140の間、または第1ドリフト領域140および第2ドリフト領域150の間における電界強度が大きくなることを抑制することができる。

【0066】

ここで、第1ドリフト領域140の不純物濃度N1は、たとえば、第2ドリフト領域150の不純物濃度N2よりも小さい。このとき、第1ドリフト領域140、第2ドリフト領域150およびドレイン領域120の順で不純物濃度が高くなっている。このような構成とすることにより、イオン注入後の活性化工程によって、容易に不純物濃度が段階的に異なる不純物領域を形成することができる。また、N1<N2である場合、式(1)を満たすように不純物注入エネルギーなどの他のパラメータを調整することにより、第1ドリフト領域140の深さσ1が第2ドリフト領域150の深さσ2よりも大きい構成とすることができる。ただし、第1ドリフト領域140は、ドレイン領域120から離間している。これにより、半導体装置10中の電界強度を安定的に最小化して耐圧を維持するとともに、オン抵抗を可能な限り下げることができる。

【0067】

一方で、第1ドリフト領域140の不純物濃度N1は、たとえば、第2ドリフト領域150の不純物濃度N2よりも大きくてもよい。このとき、第1ドリフト領域140は、半導体基板100の表面付近に形成されていれば、式(1)を満たす範囲が広くなる。イオン注入などにより不純物領域の深さを制御することが困難な場合、N1>N2で且つ第1ドリフト領域140の深さσ1を浅くすることにより、容易に式(1)を満たす構成を形成することができる。この場合でも、半導体装置10中の電界強度を安定的に最小化して耐圧を維持するとともに、オン抵抗を可能な限り下げることができる。

【0068】

次に、図5〜図9を用い、第1の実施形態に係る半導体装置10の製造方法について説明する。図5〜図9は、第1の実施形態に係る半導体装置10の製造方法を説明するための断面図である。第1の実施形態に係る半導体装置10の製造方法は、以下の工程を備えている。まず、半導体基板100に、第1導電型の不純物を注入することにより、第1ドリフト領域140を形成する(第1ドリフト領域形成工程)。次いで、半導体基板100に、第1導電型の不純物を注入することにより、平面視で第1ドリフト領域140に接するように、第2ドリフト領域150を形成する(第2ドリフト領域形成工程)。次いで、半導体基板100に、第1導電型の不純物を注入することにより、平面視で第1ドリフト領域140のうち第2ドリフト領域150と反対側の領域から離間した位置に、ソース領域110を形成する。次いで、半導体基板100に、第1ドリフト領域140および第2ドリフト領域150よりも高い不純物濃度で第1導電型の不純物を注入することにより、平面視で第1ドリフト領域140から離間するとともに、平面視で第2ドリフト領域150のうち第1ドリフト領域140と反対側の領域に接するように、ドレイン領域120を形成する。次いで、半導体基板100上に、平面視でソース領域110および第1ドリフト領域140に挟まれたチャネル領域130に重なるようにゲート絶縁層200を形成する(ゲート絶縁層形成工程)。次いで、少なくとも平面視で第1ドリフト領域140と第2ドリフト領域150の一部と重なるように、ゲート絶縁層200よりも厚く、第1フィールドプレート絶縁層300を形成する(第1フィールドプレート絶縁層形成工程)。次いで、ゲート絶縁層200上に接するとともに、平面視でチャネル領域130と重なるように、ゲート電極400を形成する。次いで、第1フィールドプレート絶縁層300上に接し、平面視で第1ドリフト領域140と第2ドリフト領域150の一部と重なるように、第1フィールドプレート電極420を形成する。上記工程のうち、第1ドリフト領域形成工程、第2ドリフト領域形成工程、ゲート絶縁層形成工程および第1フィールドプレート絶縁層形成工程において、上述した式(1)を満たすように、第1ドリフト領域140、第2ドリフト領域150、ゲート絶縁層200および第1フィールドプレート絶縁層300を形成する。以下、詳細を説明する。

【0069】

図5(a)のように、まず、半導体基板100を準備する。図1で示したように、半導体基板100は、下地基板102の主面上にIII族窒化物半導体層104を備えている。ここでは、III族窒化物半導体層104は、たとえば、GaNである。次いで、半導体基板100上に、保護層240を形成する。ここでは、たとえば、半導体基板100の表面を酸化することにより保護層240を形成する。具体的には、保護層240は、たとえばGa2O3である。なお、保護層240をスパッタなどにより形成してもよい。

【0070】

次いで、図5(b)のように、保護層240上に、フォトレジスト層600を形成する。次いで、露光および現像により、平面視で第1ドリフト領域140の形成領域に、フォトレジスト層600に開口部(符号不図示)を形成する。次いで、イオン注入装置により、当該開口部に、第1導電型の不純物を注入する。このとき、第1ドリフト領域140の深さをσ1、第1ドリフト領域140の不純物濃度をN1が上記した式(1)を満たすように、不純物注入量、加速電圧等を調整する。これにより、第1ドリフト領域140を形成する(第1ドリフト領域形成工程)。ここでは、上述のように、n型の不純物として、Siを注入する。以下では、「第1導電型」が「n型」であり、「第1導電型の不純物」がn型の不純物であるSiであるとして説明する。次いで、たとえば、アッシングなどにより、フォトレジスト層600を除去する。

【0071】

次いで、図6(a)のように、保護層240上に、再度、フォトレジスト層600を形成する。次いで、露光および現像により、平面視で第1ドリフト領域140に接するように、フォトレジスト層600に開口部(符号不図示)を形成する。次いで、当該開口部に、n型の不純物としてSiを注入する。このとき、第2ドリフト領域150の深さをσ2、第2ドリフト領域150の不純物濃度をN2が上記した式(1)を満たすように、不純物注入量、加速電圧等を調整する。これにより、平面視で第1ドリフト領域140に接するように、第2ドリフト領域150を形成する(第2ドリフト領域形成工程)。次いで、たとえば、アッシングなどにより、フォトレジスト層600を除去する。

【0072】

次いで、図6(b)のように、保護層240上に、再度、フォトレジスト層600を形成する。次いで、露光および現像により、平面視で第1ドリフト領域140のうち第2ドリフト領域150と反対側の領域から離間した位置、および平面視で第1ドリフト領域140から離間するとともに平面視で第2ドリフト領域150のうち第1ドリフト領域140と反対側の領域に接するように、フォトレジスト層600に開口部(符号不図示)を形成する。すなわち、ソース領域110およびドレイン領域120の形成領域に、フォトレジスト層600に開口部を形成する。次いで、当該開口部に、n型の不純物としてSiを注入する。これにより、平面視で第1ドリフト領域140のうち第2ドリフト領域150と反対側の領域から離間するように、ソース領域110を形成する。また、平面視で第1ドリフト領域140から離間するとともに平面視で第2ドリフト領域150のうち第1ドリフト領域140と反対側の領域に接するように、ドレイン領域を形成する。

【0073】

このとき、第1ドリフト領域140および第2ドリフト領域150よりも高い不純物濃度で、ドレイン領域120を形成する。また、ドレイン領域120と同様にしてソース領域110も、第1ドリフト領域140および第2ドリフト領域150よりも高い濃度で形成することが好ましい。上述のように、ソース領域110およびドレイン領域120の不純物濃度を、第1ドリフト領域140および第2ドリフト領域150よりも10倍以上高くなるように形成することが好ましい。これにより、ソース・ドレイン間電圧によって電界が集中することを抑制することができる。

【0074】

以上の工程により、たとえば、チャネル領域130の長さが100nm以上10μm未満となるように、チャネル領域130を形成する。また、第1ドリフト領域140および第2ドリフト領域150のうち、ソース領域110からドレイン領域120に向かう方向の長さが100nm以上10μm未満となるように、第1ドリフト領域140および第2ドリフト領域150を形成する。

【0075】

次いで、たとえば、アッシングなどにより、フォトレジスト層600を除去する。さらに、プラズマエッチングまたはウエットエッチングにより、保護層240を除去する。

【0076】

ここで、たとえば、700℃以上1300℃未満でアニール処理を行うことにより、ソース領域110、第1ドリフト領域140、第2ドリフト領域150およびドレイン領域120に注入された不純物を活性化させる。これにより、注入されたイオンと結晶構成原子とを置換させることができる。また、イオン注入でダメージを受けた半導体基板100の結晶性を回復させることができる。なお、半導体基板100の主面が保護層240で覆われた状態でアニール処理を行ってもよい。これにより、半導体基板100の窒素が抜けることを抑制することができる。

【0077】

次いで、図7(a)のように、たとえば、CVDにより、半導体基板100上に、下地絶縁層320を形成する。下地絶縁層320として、たとえば、SiO2、SiNを成膜する。次いで、たとえば、RIE(Reactive Ion Etching)により、下地絶縁層320のうち、少なくとも平面視でチャネル領域130と重なる位置に、チャネル開口部210を形成する。

【0078】

次いで、図7(b)のように、たとえば、スパッタにより、チャネル開口部210に露出した半導体基板100上、および下地絶縁層320上に、ゲート絶縁層200を形成する。ゲート絶縁層200をスパッタにより形成することにより、膜質の良いゲート絶縁層200を形成することができる。ゲート絶縁層200として、たとえば、SiO2、SiN、Al2O3を成膜する。このようにして、平面視でチャネル領域130に重なるように、ゲート絶縁層200を形成する(ゲート絶縁層形成工程)。また、下地絶縁層320およびゲート絶縁層200を積層することにより、第1フィールドプレート絶縁層300を形成する。このようにして、少なくとも平面視で第1ドリフト領域140と第2ドリフト領域150の一部と重なるように、第1フィールドプレート絶縁層300を形成する(第1フィールドプレート絶縁層形成工程)。この場合、第1フィールドプレート絶縁層形成工程はゲート絶縁層形成工程を含んでいる。また、第1フィールドプレート絶縁層300は、下地絶縁層320の一部およびゲート絶縁層200の一部を含んでいる。

【0079】

ここで、以上のゲート絶縁層形成工程および第1フィールドプレート絶縁層形成工程において、ゲート絶縁層200の厚さtOX、ゲート絶縁層200の誘電率εOX、第1フィールドプレート絶縁層300の誘電率εFP、第1ドリフト領域140と第2ドリフト領域150との境界における第1フィールドプレート絶縁層300の厚さtFPが上述した式(1)を満たすように、成膜材料、成膜条件等を調整する。なお、第1フィールドプレート絶縁層300はゲート絶縁層200および下地絶縁層320が積層されることにより形成されているため、εFPおよびtFPは、ゲート絶縁層200の厚さtOX、ゲート絶縁層200の誘電率εOX、下地絶縁層320の誘電率εUL、および下地絶縁層320の厚さtULから上述した式(4)により算出する。

【0080】

また、ゲート絶縁層200として用いられる材料が高温に強くない材料(たとえばAl2O3)である場合、ゲート絶縁層形成工程を、下地絶縁層320を形成する工程よりも後に行う方が好ましい。この場合、下地絶縁層320を形成する前にゲート絶縁層形成工程を行った場合、ゲート絶縁層200の膜質が劣化する可能性がある。したがって、ゲート絶縁層形成工程を、下地絶縁層320を形成する工程よりも後に行うことにより、ゲート絶縁層200の膜質が劣化することを抑制することができる。

【0081】

次いで、図8(a)のように、スパッタにより、ゲート絶縁層200上に金属膜を形成する。たとえば、金属膜として、Alおよび/またはTiNを成膜する。次いで、当該金属膜上にフォトレジスト層(不図示)を形成する。露光および現像により、平面視でチャネル領域130と重なる位置、および平面視で第1ドリフト領域140並びに第2ドリフト領域の一部と重なる位置に残存するように、フォトレジスト層をパターニングする。このフォトレジスト層600をマスクとして、プラズマエッチングまたはウエットエッチングにより、金属膜をエッチングする。次いで、たとえば、アッシングによりフォトレジスト層を除去する。以上により、ゲート絶縁層200上に接するとともに、平面視でチャネル領域130と重なるように、ゲート電極400を形成する。また、第1フィールドプレート絶縁層300上に接し、平面視で第1ドリフト領域140と第2ドリフト領域150の一部と重なるように、第1フィールドプレート電極420を形成する。また、第1フィールドプレート電極420をゲート電極400と接続するように形成する。この場合では、第1フィールドプレート電極420を、たとえば、ゲート電極400と一体として形成する。これにより、製造工程を簡略化することができる。

【0082】

次いで、図8(b)のように、たとえば、CVDにより、ゲート絶縁層200、ゲート電極400および第1フィールドプレート電極420上に、第1層間絶縁層520を形成する。第1層間絶縁層520として、たとえば、SiO2、SiN、SiON、SiOC、SiOCH、SiCOHまたはSiOFを成膜する。

【0083】

次いで、図9(a)のように、RIEにより、平面視でソース領域110に重なる位置に、第1層間絶縁層520、ゲート絶縁層200および下地絶縁層320を貫通して半導体基板100の上面に接するソース開口部430を形成する。同時に、RIEにより、平面視でドレイン領域120に重なる位置に、第1層間絶縁層520、ゲート絶縁層200および下地絶縁層320を貫通して半導体基板100の上面に接するドレイン開口部450を形成する。

【0084】

次いで、図9(b)のように、たとえば、スパッタにより、ソース開口部430並びにドレイン開口部450の側面並びに底面、および第1層間絶縁層520上に、金属を形成する。これにより、ソース開口部430およびドレイン開口部450の内部に、金属を埋め込む。具体的には、スパッタにより、Alおよび/またはTiNなどを成膜する。次いで、CMP(Chemical Mechanical Polishing)により、第1層間絶縁層520上を平坦化する。これにより、ソース電極440のビアおよびドレイン電極460のビアを形成する。

【0085】

その後、ダマシン法により、第1層間絶縁層520上に、多層配線構造(不図示)を形成してもよい。また、多層配線構造の最上層に、電極パッド(不図示)を形成してもよい。

【0086】

以上により、第1の実施形態に係る半導体装置10を得ることができる。

【0087】

次に、図10および図11を用い、第1の実施形態の効果について説明する。図10は、比較例の半導体装置の構成を示す断面図である。また、図11は、第1の実施形態の効果を説明するための図である。

【0088】

図10(a)のように、比較例の半導体装置Aは、第1の実施形態に係る半導体装置10と異なり、第2ドリフト領域150および第1フィールドプレート電極420が設けられていない。他の構成は、第1の実施形態と同様である。

【0089】

図10(b)のように、比較例の半導体装置Bは、第1の実施形態に係る半導体装置10と異なり、第2ドリフト領域150が設けられていない。なお、第1フィールドプレート電極420は設けられている。他の構成は、第1の実施形態と同様である。

【0090】

図10(c)のように、比較例の半導体装置Cは、第1の実施形態に係る半導体装置10と異なり、第1ドリフト領域140が第2ドリフト領域150よりも深く形成されている。さらに、第1ドリフト領域140は、ドレイン領域120と接している。他の構成は、第1の実施形態と同様である。

【0091】

図11(a)は、ゲート電圧を0V、ドレイン・ソース間電圧を100Vとしたときの電界強度の分布を示している。横軸は、それぞれの半導体装置における平面視での位置である。また、縦軸は、電界強度(単位MV/cm)である。点線は、比較例の半導体装置Aを示している。破線は、比較例の半導体装置Bを示している。また、実線は、第1の実施形態に係る半導体装置10を示している。

【0092】

図11(a)のように、比較例の半導体装置Aは第1フィールドプレート電極420が設けられていないため、ゲート電極400および第1ドリフト領域140間の電界強度が局所的に大きくなっている。このような場合、ゲート電極400および第1ドリフト領域140間に電界が集中し、ゲート絶縁層200が絶縁破壊を起こす可能性がある。

【0093】

また、比較例の半導体装置Bは第1フィールドプレート電極420が設けられているため、ゲート電極400および第1ドリフト領域140間の電界強度は緩和されている。しかし、反対に、第1ドリフト領域140およびドレイン領域120間の電界強度が局所的に大きくなってしまっている。この原因は、第1フィールドプレート電極420が不純物濃度の高いドレイン領域120と近くなったことにより、電界が集中したと考えられる。

【0094】

一方、第1の実施形態に係る半導体装置10は、ゲート電極400および第1ドリフト領域140間の電界と、ゲート電極400および第1ドリフト領域140間の電界強度は、ともに緩和されている。当該半導体装置10内では、電界強度が一様に分布している。このように、第1の実施形態では、電界が局所的に集中することを抑制することができる。

【0095】

図11(b)は、ゲート電圧を0V、ドレイン・ソース間電圧を100Vとしたときの表面ポテンシャルの分布を示している。横軸は、それぞれの半導体装置における平面視での位置である。また、縦軸は、ポテンシャルエネルギー(単位eV)である。図中のそれぞれの半導体装置は、たとえば、以下のような構成である場合を示している。比較例の半導体装置Cのうち、第1ドリフト領域140の深さσ1は50nm、第2ドリフト領域150の深さσ2は15nmである。なお、上述のように、比較例の半導体装置Cにおいて、第1ドリフト領域140はドレイン領域120に接している。一方、第1の実施形態の半導体装置10のうち、第1ドリフト領域140の深さσ1は5nm、第2ドリフト領域150の深さσ2は15nmである。なお、上述のように、第1の実施形態に係る半導体装置10において、第1ドリフト領域140はドレイン領域120から離間している。

【0096】

図11(b)のように、比較例の半導体装置Cでは、第2ドリフト領域150から第1ドリフト領域140までの領域の電位がドレイン領域120の電位に近い値となっている。第1ドリフト領域140または第2ドリフト領域150がドレイン領域120と独立して形成されているにもかかわらず、ドレイン領域120が平面視で第1ドリフト領域140および第2ドリフト領域150を含むように一体として形成されていると同等となってしまっている。このような場合、ゲート電極400および第1ドリフト領域140間の電界強度が大きくなってしまう。

【0097】

一方、第1の実施形態に係る半導体装置10のうち、第1ドリフト領域140は、ドレイン領域120から離間して形成されている。これにより、第1ドリフト領域140からドレイン領域120までの領域において、緩やかな傾斜で電位が分布している。このような理由においても、第1の実施形態では、電界強度が偏ることがない。

【0098】

第1の実施形態によれば、ソース領域110およびドレイン領域120の間には、第1ドリフト領域140および第2ドリフト領域150が設けられている。第1フィールドプレート電極420は、第1フィールドプレート絶縁層300上に接し、平面視で第1ドリフト領域140と第2ドリフト領域150の一部と重なるように設けられている。このとき、これらを構成する物性値は、上記式(1)を満たしている。これにより、半導体装置10内の電界強度を偏りなく分布させることができる。また、ゲート電極400および第1ドリフト領域140の間、または第1ドリフト領域140および第2ドリフト領域150の間等における電界強度が大きくなることを抑制することができる。

【0099】

さらに、第1の実施形態によれば、第1導電型の不純物領域のみを形成することにより、半導体装置10を高耐圧化させることができる。ここで、たとえば、不純物領域を形成する半導体層がn型およびp型の両方の導電性を制御できる場合、たとえば、ソース領域110またはドレイン領域120の下方に、これらと逆の導電型のハロー領域(またはポケット領域とも呼ばれる)などを形成する場合がある。この場合、ハロー領域が設けられていることにより、ドレイン・ソース間のパンチスルーを抑制することができる。したがって、ソース領域110またはドレイン領域120の近傍に、これらと逆導電型の不純物領域を形成することによって、半導体装置10内の電界を緩和することが可能となる。しかし、導電制御が困難な半導体材料である場合、ソース領域110またはドレイン領域120と逆導電型の不純物領域を設けることは困難である可能性がある。そこで、第1導電型の不純物領域のみにより第1の実施形態のような構成を形成することにより、導電制御が困難な半導体材料であっても半導体装置10を安定的に高耐圧化させることができる。たとえば、上述のように、半導体基板100が、導電制御が困難なIII族窒化物半導体層104等を含む場合に特に有効である。

【0100】

以上により、第1の実施形態によれば、電界が局所的に集中することを抑制して、高耐圧化した半導体装置10を提供することができる。

【0101】

(第2の実施形態)

図12は、第2の実施形態に係る半導体装置10の構成を示す断面図である。第2の実施形態は、第1ドリフト領域140および第2ドリフト領域150に加え、ドリフト領域がさらに設けられている点を除いて、第1の実施形態と同様である。以下、詳細を説明する

【0102】

図12のように、n型の第3ドリフト領域160は、平面視で第2ドリフト領域150とドレイン領域120との間に設けられている。第3ドリフト領域160は、第2ドリフト領域150と接するとともに、ドレイン領域120とも接している。ここで、第3ドリフト領域160の不純物濃度は、たとえば、第1ドリフト領域140および第2ドリフト領域150よりも高い。一方で、第3ドリフト領域160の不純物濃度は、たとえば、ドレイン領域120よりも低い。

【0103】

また、第3ドリフト領域160の深さは、たとえば、第2ドリフト領域150よりも深い。これにより、第2ドリフト領域150は、ドレイン領域120から離間している。また、第2ドリフト領域150は、ドレイン領域120と接していない。

【0104】

第1フィールドプレート電極420は、たとえば、第1の実施形態と同様に、第1フィールドプレート絶縁層300上に接している。また、第1フィールドプレート電極420は、平面視で第1ドリフト領域140と第2ドリフト領域150の一部と重なるように設けられている。

【0105】

第2の実施形態に係る半導体装置10の製造方法は、以下の点を除いて、第1の実施形態と同様である。

【0106】

第2ドリフト領域150を形成する工程の後、ドレイン領域120を形成する工程の前に、第2ドリフト領域150のうち第1ドリフト領域140と反対側の領域に接するように、第3ドリフト領域160を形成する。このとき、第1ドリフト領域140および第2ドリフト領域150よりも高い不純物濃度で、且つ、ドレイン領域120よりも低い不純物濃度で、第3ドリフト領域160を形成する。次いで、平面視で第3ドリフト領域160のうち第2ドリフト領域と反対側の領域に接するように、ドレイン領域120を形成する。

【0107】

以降の工程は、第1の実施形態と同様である。

【0108】

第2の実施形態によれば、第1の実施形態と同様の効果を得ることができる。さらに、第2の実施形態によれば、平面視で第2ドリフト領域150とドレイン領域120との間には、さらにドリフト領域が設けられている。これにより、ゲート電極400およびドレイン領域120との間の電界を段階的に緩和することができる。したがって、さらに半導体装置10の耐圧を向上させることができる。

【0109】

以上、第2の実施形態では、第1フィールドプレート電極420は、平面視で第1ドリフト領域140、第2ドリフト領域150の一部と重なるように設けられている場合について説明した。または、第1フィールドプレート電極420は、平面視で第1ドリフト領域140、第2ドリフト領域150、および第3ドリフト領域160の一部と重なるように設けられていてもよい。この場合、第1フィールドプレート絶縁層300の厚さtFPは、第2ドリフト領域150と第3ドリフト領域160との境界における厚さであると置き換えて、半導体装置10は式(1)を満たす構成であればよい。

【0110】

(第3の実施形態)

図13は、第3の実施形態に係る半導体装置10の構成を示す断面図である。第3の実施形態は、以下の点を除いて、第1の実施形態と同様である。第1層間絶縁層520は、少なくともゲート電極400を覆うように設けられている。ソース電極440は、ソース領域110に接続している。また、第1フィールドプレート絶縁層300は、第1層間絶縁層520の一部を含んでいる。第1の実施形態における第1フィールドプレート電極420がゲート電極400に接続しているのに対して、第2の実施形態では第1フィールドプレート電極420がソース電極440に接続している。以下、詳細を説明する

【0111】

図13のように、第1の実施形態と同様にして、III族窒化物半導体層104には、ソース領域110、チャネル領域130、第1ドリフト領域140、第2ドリフト領域150およびドレイン領域120が形成されている。

【0112】

下地絶縁層320は、半導体基板100上に接して設けられており、平面視でチャネル領域130と重なる領域に開口部を有している。また、ゲート絶縁層200は、下地絶縁層320の開口部に露出したチャネル領域130上、および下地絶縁層320上に設けられている。ゲート電極400は、ゲート絶縁層200上に接し、平面視でチャネル領域130に重なるように設けられている。

【0113】

第3の実施形態では、第2フィールドプレート電極480は、ゲート電極400に接続している。第2フィールドプレート電極480は、平面視で第1ドリフト領域140の一部と重なるように設けられている。反対に、第2フィールドプレート電極480は、平面視で第2ドリフト領域150と重なっていない。言い換えれば、第2フィールドプレート電極480の一端は、平面視で第1ドリフト領域140および第2ドリフト領域150の境界よりもソース領域110側に位置している。また、第2フィールドプレート電極480は、ゲート電極400と一体として形成されていてもよい。

【0114】

第1層間絶縁層520は、たとえば、ゲート電極400および第2フィールドプレート電極480を覆うように設けられている。第1層間絶縁層520上に、さらに第2層間絶縁層540が設けられていてもよい。第2層間絶縁層540は、たとえば、第1層間絶縁層520よりも高密度の材料に形成されていてもよい。これにより、第2層間絶縁層540は、第1層間絶縁層520に対してエッチング選択性を有するエッチングストッパ層として機能させることができる。第2層間絶縁層540の材料は、たとえば、SiCN、SiC、SiON,SiCO、SiCONまたはSiNなどである。

【0115】

ここで「第1フィールドプレート絶縁層300」は、上述のように、第1フィールドプレート電極420と半導体基板100の主面との間に設けられた絶縁層である。第2の実施形態では、第1フィールドプレート絶縁層300は、第1層間絶縁層520の一部を含んでいる。ここでは、さらに、第1フィールドプレート絶縁層300は、第2層間絶縁層540の一部を含んでいる。したがって、第1フィールドプレート絶縁層300は、下地絶縁層320の一部、ゲート絶縁層200の一部、第1層間絶縁層520の一部および第2層間絶縁層540の一部を含んでいる。

【0116】

ソース電極440は、平面視でソース領域110と重なるように設けられている。また、ソース電極440は、下地絶縁層320、ゲート絶縁層200、第1層間絶縁層520および第2層間絶縁層540を貫通して、ソース領域110に接続している。

【0117】

第1フィールドプレート電極420は、第1フィールドプレート絶縁層300のうち、第2層間絶縁層540上に接している。また、第1フィールドプレート電極420は、平面視で第1ドリフト領域140と第2ドリフト領域150の一部と重なるように設けられている。また、第1フィールドプレート電極420はソース電極440に接続している。また、第1フィールドプレート電極420は、ソース電極440と一体として形成されている。第1フィールドプレート電極420は、ソース電極440と同じ材料により形成されている。また、ソース電極440、第1フィールドプレート電極420の材料は、たとえば、Alおよび/またはTiNなどである。このように、第1フィールドプレート電極420をソース電極440と一体として形成することにより、製造工程を簡略化することができる。

【0118】

さらに、当該半導体装置10のうち、それぞれの構成は、上述の式(1)を満たすように形成されている。なお、上述のように、第1フィールドプレート絶縁層300は、下地絶縁層320、ゲート絶縁層200、第1層間絶縁層520および第2層間絶縁層540が積層されることにより形成されている。したがって、第1フィールドプレート絶縁層300の電気的膜厚tFP*は、式(5)、式(6)および式(7)から下地絶縁層320、ゲート絶縁層200、第1層間絶縁層520および第2層間絶縁層540の誘電率と物理的膜厚との積の総和により求めることができる。

【0119】

次に、図14および図15を用い、第3の実施形態に係る半導体装置10の製造方法について説明する。図14および図15は、第1の実施形態に係る半導体装置10の製造方法を説明するための断面図である。第3の実施形態に係る半導体装置10の製造方法は、第1フィールドプレート電極420をソース電極440に接続する点を除いて、第1の実施形態と同様である。以下、詳細を説明する。

【0120】

第1の実施形態と同様にして、図7(b)までの工程を行う。半導体基板100には、ソース領域110、チャネル領域130、第1ドリフト領域140、第2ドリフト領域150およびドレイン領域120が形成されている。さらに、半導体基板100上には、下地絶縁層320が形成されている。また、チャネル130上および下地絶縁層320上には、ゲート絶縁層200が形成されている。

【0121】

図14(a)のように、スパッタにより、ゲート絶縁層200上に金属膜を形成する。たとえば、金属膜として、Alおよび/またはTiNを成膜する。次いで、当該金属膜上にフォトレジスト層(不図示)を形成する。露光および現像により、平面視でチャネル領域130と重なる位置、および平面視で第1ドリフト領域140の一部と重なる位置に残存するように、フォトレジスト層をパターニングする。このフォトレジスト層をマスクとして、プラズマエッチングまたはウエットエッチングにより、金属膜をエッチングする。次いで、たとえば、アッシングによりフォトレジスト層を除去する。以上により、ゲート絶縁層200上に接するとともに、平面視でチャネル領域130と重なるように、ゲート電極400を形成する。また、ゲート電極400に接続するとともに、平面視で第1ドリフト領域140の一部と重なるように、第2フィールドプレート電極480を形成する。この場合のように、第2フィールドプレート電極480を、たとえばゲート電極400と一体として形成する。これにより、製造工程を簡略化することができる。

【0122】

次いで、図14(b)のように、たとえば、CVDにより、ゲート絶縁層200、ゲート電極400および第2フィールドプレート電極480上に、第1層間絶縁層520を形成する。さらに、ここでは、第1層間絶縁層520上に、たとえば、第1層間絶縁層520よりも高密度の材料からなる第2層間絶縁層540を形成する。第2層間絶縁層540として、たとえば、SiCN、SiC、SiON,SiCO、SiCONまたはSiNを成膜する。

【0123】

次いで、図15(a)のように、RIEにより、平面視でソース領域110に重なる位置に、第2層間絶縁層540、第1層間絶縁層520、ゲート絶縁層200および下地絶縁層320を貫通して半導体基板100の上面に接するソース開口部430を形成する。同時に、RIEにより、平面視でドレイン領域120に重なる位置に、第2層間絶縁層540、第1層間絶縁層520、ゲート絶縁層200および下地絶縁層320を貫通して半導体基板100の上面に接するドレイン開口部450を形成する。

【0124】

次いで、図15(b)のように、ソース開口部430並びにドレイン開口部450の側面並びに底面、および第2層間絶縁層540上に、たとえば、スパッタにより、金属を形成する。これにより、ソース開口部430およびドレイン開口部450の内部に、金属を埋め込む。具体的には、スパッタにより、Alおよび/またはTiNなどを成膜する。次いで、CMPにより、第2層間絶縁層540上の金属を平坦化する。次いで、当該金属上にフォトレジスト層(不図示)を形成する。露光および現像により、平面視でソース領域110と重なる位置、および平面視で第1ドリフト領域140および第2ドリフト領域150の一部と重なる位置に残存するように、フォトレジスト層をパターニングする。このフォトレジスト層をマスクとして、プラズマエッチングまたはウエットエッチングにより、金属をエッチングする。次いで、たとえば、アッシングによりフォトレジスト層を除去する。以上により、ソース開口部430に金属を埋め込むことにより、ソース領域110に接続するように、ソース電極440を形成する。また、第1フィールドプレート絶縁層300上に接し、平面視で第1ドリフト領域140と第2ドリフト領域150の一部と重なるように、第1フィールドプレート電極420を形成する。また、第1フィールドプレート電極420をソース電極440と接続するように形成する。この場合では、第1フィールドプレート電極420を、たとえば、ソース電極440と一体として形成する。これにより、製造工程を簡略化することができる。

【0125】

以降の工程は、第1の実施形態と同様である。

【0126】

第3の実施形態によれば、第1フィールドプレート電極420がソース電極440に接続している。この場合でも第1の実施形態と同様の効果を得ることができる。さらに第3の実施形態によれば、フィールドプレート電極が複数設けられている。ここでは、たとえば、ゲート電極400に接続する第2フィールドプレート電極480、ソース電極440に接続する第1フィールドプレート電極420が設けられている。これにより、さらに効率的に、半導体装置10内の電界集中を緩和することができる。

【0127】

以上、第3の実施形態では、フィールドプレート電極が二つ設けられている場合について説明したが、フィールドプレート電極はさらに多段に設けられていてもよい。また、さらに、第2の実施形態のように、第3ドリフト領域160等の複数のドリフト領域が設けられていてもよい。

【0128】

また、第3の実施形態では、第2フィールドプレート電極480が設けられている場合について説明したが、第2フィールドプレート電極480は無くてもよい。その場合、下地絶縁層320は無くてもよい。この場合でも、第4の実施形態と同様の効果を得ることができる。

【0129】

(第4の実施形態)

図16は、第4の実施形態に係る半導体装置10の構成を示す断面図である。第4の実施形態は、第1フィールドプレート電極420が第2フィールドプレート電極480上に接している点を除いて、第1の実施形態、または第3の実施形態の一部と同様である。

【0130】

図16のように、第1の実施形態と同様にして、III族窒化物半導体層104には、ソース領域110、チャネル領域130、第1ドリフト領域140、第2ドリフト領域150およびドレイン領域120が形成されている。

【0131】

下地絶縁層320は、半導体基板100上に接して設けられており、平面視でチャネル領域130と重なる領域に開口部を有している。また、ゲート絶縁層200は、下地絶縁層320の開口部に露出したチャネル領域130上、および下地絶縁層320上に設けられている。ゲート電極400は、ゲート絶縁層200上に接し、平面視でチャネル領域130に重なるように設けられている。

【0132】

また、第2フィールドプレート電極480は、第2の実施形態と同様に、ゲート電極400に接続している。第2フィールドプレート電極480は、平面視で第1ドリフト領域140の一部と重なるように設けられている。

【0133】

第1層間絶縁層520は、半導体基板100上に設けられ、ゲート電極400および第2フィールドプレート電極480の上面と同一面を形成するように設けられている。

【0134】

第1フィールドプレート絶縁層300は、第1層間絶縁層520の一部を含んでいる。第4の実施形態では、第1フィールドプレート絶縁層300は、下地絶縁層320、ゲート絶縁層200および第1層間絶縁層520が積層されることにより形成されている。

【0135】

第1フィールドプレート電極420は、第1フィールドプレート絶縁層300のうち、第1層間絶縁層520上および第2フィールドプレート電極480上に接している。なお、第1フィールドプレート電極420は、平面視で第1ドリフト領域140と第2ドリフト領域150の一部と重なるように設けられている。この場合では、第1フィールドプレート電極420は、ゲート電極400と異なる材料で形成されていてもよい。

【0136】

さらに、当該半導体装置10のうち、それぞれの構成は、上述の式(1)を満たすように形成されている。第1フィールドプレート絶縁層300の電気的膜厚tFP*は、式(5)、式(6)および式(7)から下地絶縁層320、ゲート絶縁層200および第1層間絶縁層520の誘電率と物理的膜厚との積の総和により求めることができる。

【0137】

次に、図17〜図19を用い、第4の実施形態に係る半導体装置10の製造方法について説明する。図17〜図19は、第4の実施形態に係る半導体装置10の製造方法を説明するための断面図である。第4の実施形態に係る半導体装置10の製造方法は、第1フィールドプレート電極420を第2フィールドプレート電極480上に接するように形成する点を除いて、第1の実施形態または第2の実施形態の一部と同様である。以下、詳細を説明する。

【0138】

第2の実施形態と同様にして、図14(a)までの工程を行う。ゲート絶縁層200上には、平面視でチャネル領域130と重なるように、ゲート電極400が形成されている。また、ゲート電極400に接続するとともに、平面視で第1ドリフト領域140の一部と重なるように、第2フィールドプレート電極480が形成されている。

【0139】

次いで、図17(a)のように、たとえば、CVDにより、ゲート絶縁層200、ゲート電極400および第2フィールドプレート電極480上に、第1層間絶縁層520を形成する。

【0140】

次いで、図17(b)のように、CMPにより、ゲート電極400および第2フィールドプレート電極480の上面と同一面を形成するように、第1層間絶縁層520を平坦化する(平坦化工程)。

【0141】

次いで、図18(a)のように、たとえば、スパッタにより、ゲート電極400および第2フィールドプレート電極480上に、金属膜を形成する。当該金属膜として、たとえば、Alおよび/またはTiNなどを成膜する。次いで、金属膜上にフォトレジスト層(不図示)を形成する。露光および現像により、平面視で少なくとも第1ドリフト領域140と第2ドリフト領域150の一部と重なる領域に残存するように、フォトレジスト層をパターニングする。次いで、たとえば、アッシングによりフォトレジスト層を除去する。以上により、第1フィールドプレート絶縁層300のうち、第1層間絶縁層520上および第2フィールドプレート電極480上に接するように、第1フィールドプレート電極420を形成する。また、少なくとも平面視で第1ドリフト領域140と第2ドリフト領域150の一部と重なるように、第1フィールドプレート電極420を形成する。

【0142】

次いで、図18(b)のように、たとえば、CVDにより、第1層間絶縁層520上、および第1フィールドプレート電極420上を覆うように、第2層間絶縁層540を形成する。

【0143】

次いで、図19(a)のように、RIEにより、平面視でソース領域110に重なる位置に、第2層間絶縁層540、第1層間絶縁層520、ゲート絶縁層200および下地絶縁層320を貫通して、半導体基板100の上面に接するソース開口部430を形成する。同時に、RIEにより、平面視でドレイン領域120に重なる位置に、第2層間絶縁層540、第1層間絶縁層520、ゲート絶縁層200および下地絶縁層320を貫通して、半導体基板100の上面に接するドレイン開口部450を形成する。

【0144】

次いで、図19(b)のように、たとえば、スパッタにより、ソース開口部430並びにドレイン開口部450の側面並びに底面および第2層間絶縁層540上に、金属を形成する。これにより、ソース開口部430およびドレイン開口部450の内部に、金属を埋め込む。具体的には、具体的には、スパッタにより、Alおよび/またはTiNなどを成膜する。

【0145】

以降の工程は第1の実施形態と同様である。

【0146】

第4の実施形態によれば、第1の実施形態と同様の効果を得ることができる。さらに、第4の実施形態によれば、第1フィールドプレート電極420がゲート電極400および第2フィールドプレート電極480上に接している。これにより、さらに効率的に、半導体装置10内の電界集中を緩和することができる。

【0147】

以上、第4の実施形態では、フィールドプレート電極が二つ設けられている場合について説明したが、フィールドプレート電極はさらに多段に積層して設けられていてもよい。また、さらに、第2の実施形態のように、第3ドリフト領域160等の複数のが設けられていてもよい。

【0148】

以上、第1から4の実施形態において、ソース電極440およびドレイン電極460をスパッタにより形成したが、これに限定されるものではない。ソース電極440およびドレイン電極460をダマシン法によってCuを埋め込むことにより形成してもよい。その他、ソース電極440およびドレイン電極460をCVDによってWを埋め込むことにより形成してもよい。

【0149】

(第5の実施形態)

図20は、第5の実施形態に係る半導体装置10の構成を示す断面図である。第5の実施形態は、半導体基板100がSi基板である点を除いて、第1の実施形態と同様である。

【0150】

図20のように、第5の実施形態のうち、断面視での構造は、第1の実施形態と同様である。

【0151】

第5の実施形態では、半導体基板100は、たとえば、Si基板である。第1の実施形態と異なり、半導体基板100に、材質の異なる半導体層は形成されていない。すなわち、半導体基板100の表面近傍に、直接、横型MOSFETが形成されている。

【0152】

また、第1導電型がn型であり、半導体装置10がnチャネルFETを含む場合は、半導体基板100は、たとえば、p型Si基板である。一方、第1導電型がp型であり、半導体装置10がpチャネルFETを含む場合は、半導体基板100はn型Si基板であってもよい。

【0153】

また、ソース領域110およびドレイン領域120の下方に、これらと逆の導電型のハロー領域(不図示)がさらに形成されていてもよい。

【0154】

ゲート電極400、ソース電極440およびドレイン電極460は、第1の実施形態と同様に、たとえば、スパッタにより、Alおよび/またはTiNなどによって形成されていてもよい。または、これらの電極は、ダマシン法によってCuを埋め込むことにより形成されていてもよい。また、これらの電極は、CVDによってWを埋め込むことにより形成してもよい。

【0155】

第5の実施形態によれば、第1の実施形態と同様の効果を得ることができる。さらに第5の実施形態によれば、半導体基板100はSi基板である。これにより、半導体基板100のコストを低減し、安価に半導体装置10を提供することができる。また、制御用ICを同一チップ上に作り込むことができる。これにより、より広い範囲の製品形態に半導体装置10を適用することができる。また、半導体基板100に含まれる欠陥を低減して、基板耐圧を向上させた半導体装置10を提供することができる。

【0156】

(第6の実施形態)

図21は、第6の実施形態に係る半導体装置10の構成を示す断面図である。第6の実施形態は、ゲート絶縁層200上に下地絶縁層320が設けられている点を除いて、第1の実施形態、または第5の実施形態と同様である。

【0157】

第6の実施形態では、半導体基板100は、たとえば、Si基板である。半導体基板100には、ソース領域110、チャネル領域130、第1ドリフト領域140、第2ドリフト領域150およびドレイン領域120が形成されている。

【0158】

ゲート絶縁層200は、半導体基板100に接して設けられている。下地絶縁層320は、ゲート絶縁層200上に設けられている。したがって、第1フィールドプレート絶縁層300は、ゲート絶縁層200および下地絶縁層320の順で積層されることにより形成されている。また、第1フィールドプレート電極420は、第1フィールドプレート絶縁層300のうち下地絶縁層320の上面に接して設けられている。

【0159】

また、ゲート絶縁層200は、下地絶縁層320に対してエッチング選択性を有する材料により形成されている。具体的には、下地絶縁層320がたとえばSiO2により形成されている場合に、ゲート絶縁層200はたとえばSiNにより形成されている。

【0160】

次に、第6の実施形態に係る半導体装置10の製造方法について概略を説明する。第6の実施形態に係る半導体装置10の製造方法は、以下の点を除いて、第1の実施形態と同様である。

【0161】

第1の実施形態と同様にして、図5(a)から図6(b)までを行う。このとき、保護層240は無くてもよい。次いで、保護層240を形成した場合はこれを除去する。または、保護層240がゲート絶縁層200であってもよい。

【0162】

次いで、半導体基板100上の全面にゲート絶縁層200を形成する。次いで、ゲート絶縁層200上に、下地絶縁層320を形成する。次いで、RIEにより、下地絶縁層320にチャネル開口部210を形成する。

【0163】

以降の工程は、第1の実施形態と同様である。

【0164】

第6の実施形態によれば、第1の実施形態または第5の実施形態と同様の効果を得ることができる。さらに第6の実施形態のように、半導体基板100の材質に応じて、ゲート絶縁層200を下地絶縁層320よりも先に形成することもできる。

【0165】

以上、第5および第6の実施形態において、半導体基板100がSi基板である場合を説明したが、この場合において第1〜第4の実施形態の構成を適用してもよい。

【0166】

以上、図面を参照して本発明の実施形態について述べたが、これらは本発明の例示であり、上記以外の様々な構成を採用することもできる。

【符号の説明】

【0167】

10 半導体装置

100 半導体基板

102 下地基板

104 III族窒化物半導体層

110 ソース領域

120 ドレイン領域

130 チャネル領域

140 第1ドリフト領域

150 第2ドリフト領域

160 第3ドリフト領域

200 ゲート絶縁層

210 チャネル開口部

240 保護層

300 第1フィールドプレート絶縁層

320 下地絶縁層

400 ゲート電極

420 第1フィールドプレート絶縁層

430 ソース開口部

440 ソース電極

450 ドレイン開口部

460 ドレイン電極

480 第2フィールドプレート絶縁層

520 第1層間絶縁層

540 第2層間絶縁層

600 フォトレジスト層

A 比較例

B 比較例

C 比較例

【技術分野】

【0001】

本発明は、半導体装置および半導体装置の製造方法に関する。

【背景技術】

【0002】

近年、半導体装置を高耐圧化させるため、様々な構造の半導体装置が提案されている。

【0003】

特許文献1(特開2009−158821号公報)には、以下のような半導体装置が記載されている。P型半導体基板には、N型の第1ドリフト領域が形成されている。第2ドリフト領域は、第1ドリフト領域と連続するように形成され、第1ドリフト領域よりも底面の深さが深く形成されている。第2ドリフト領域のN型の不純物濃度は第1ドリフト領域よりも高い。また、N型のドレイン領域は、第2ドリフト領域に接触して形成されている。N型のソース領域は、第1ドリフト領域と離間して形成されている。これにより、半導体基板面と平行な方向の電界が両ドリフト領域によって二段階に緩和される。また、基板面に垂直な方向の電界を緩和する効果を高めることができるとされている。

【0004】

また、特許文献2(特開昭61−180483号公報)には、以下のような高耐圧MOS型半導体装置が記載されている。ゲートは、第1導電型の半導体基板の一主面上に、ゲート絶縁膜を介して形成されている。ソース領域は、第2導電型の高濃度領域であり、ゲートの一方の端部直下を含み、半導体基板の一主面に形成されている。第1ドリフト領域は、第2導電型で低濃度であり、ゲートの他方の端部直下を含み、半導体基板の一主面に形成されている。第2ドリフト領域は、第2導電型で中濃度領域であり、第1ドリフト領域に継続して、半導体基板の一主面に形成されている。フィールド(プレート)電極は、第1および第2ドリフト領域上にゲート絶縁膜よりも厚い層間絶縁膜を介して形成され、ソース領域に接続されている。これにより、半導体装置を高耐圧化することができ、またはオン抵抗が低下することによる高電流化することができるとされている。

【0005】

また、特許文献3(特開2006−202847号公報)には、以下のような半導体装置が記載されている。基板表面には、N+型ソース領域、チャネル領域およびN+型ドレイン領域が順に形成されている。ソース領域から基板の下方にかけて、縦型バイポーラトランジスタが形成されている。P型基板上には、縦型バイポーラトランジスタに接続するN+型の埋め込み層が形成されている。また、ドレイン領域とチャネル領域との間には、N−型のドリフト領域が形成されている。これにより、ドレイン端での電流集中を防止して静電放電に対する耐性に優れた半導体装置を得ることができるとされている。

【0006】

また、特許文献4(特開2007−027641号公報)には、以下のような半導体装置が記載されている。p型半導体基板上には、p型ボディ領域が形成されている。ボディ領域の表面領域には、n+型ソース領域が形成されている。半導体基板上には、n+型ドレイン領域が形成されている。ソース領域とドレイン領域との間には、n−型ドリフト領域が形成されている。ボディ領域上には、ゲート絶縁膜が形成されている。ドリフト領域上には、保護絶縁膜が形成されている。ゲート絶縁膜上および保護絶縁膜上の一部には、ゲート電極が形成されている。さらに、ゲート電極上、ソース領域上およびドレイン領域上には、シリサイド膜が形成されている。これにより、ゲート抵抗を充分に低抵抗化することができるとともに、高耐圧が得られるとされている。

【0007】

また、特許文献5(特開2009−164651号公報)には、以下のような半導体装置が記載されている。エピタキシャル・シリコン層上には、LOCOS膜を介して、ゲート電極が形成されている。LOCOS膜の左側には、P型の第1のドリフト層が形成されている。平面視でゲート電極を挟んでLOCOS膜の右側には、P+型のソース層が形成されている。第1のドリフト層よりも深い領域に、P型の第2のドリフト層が形成されている。第1および第2のドリフト層と接して、複数層からなるP型のドレイン層が形成されている。これにより、高いゲート耐圧およびソース・ドレイン耐圧を有するとともに、低いオン抵抗を有したトランジスタを得ることができるとされている。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特開2009−158821号公報

【特許文献2】特開昭61−180483号公報

【特許文献3】特開2006−202847号公報

【特許文献4】特開2007−027641号公報

【特許文献5】特開2009−164651号公報

【発明の概要】

【発明が解決しようとする課題】

【0009】

上記のように、ソース領域およびドレイン領域の間に設けられたドリフト領域や、ドリフト領域上に絶縁層を介して設けられたフィールドプレート電極を備える横型MOSFET(Metal Oxide Semiconductor Field Effect Transistor)が開示されている。しかし、発明者は、半導体装置の構成によっては、ドリフト領域中の電界強度が偏ってしまう可能性があることを見出した。

【課題を解決するための手段】

【0010】

本発明によれば、

半導体基板と、

前記半導体基板に設けられた第1導電型のソース領域と、

前記半導体基板に設けられ、平面視で前記ソース領域から離間して設けられた第1導電型の第1ドリフト領域と、

前記半導体基板のうち、平面視で前記ソース領域および前記第1ドリフト領域に挟まれた領域であるチャネル領域と、

前記半導体基板に設けられ、平面視で前記第1ドリフト領域のうち前記ソース領域と反対側の領域に接している第1導電型の第2ドリフト領域と、

前記半導体基板に設けられ、平面視で前記第1ドリフト領域から離間するとともに、平面視で前記第2ドリフト領域のうち前記第1ドリフト領域と反対側の領域に接しており、前記第1ドリフト領域および前記第2ドリフト領域よりも不純物濃度が高い第1導電型のドレイン領域と、

前記チャネル領域上に設けられたゲート絶縁層と、

前記ゲート絶縁層上に接し、平面視で前記チャネル領域と重なるように設けられたゲート電極と、

前記半導体基板上に設けられ、少なくとも平面視で前記第1ドリフト領域と前記第2ドリフト領域の一部と重なるように設けられ、前記ゲート絶縁層よりも厚い第1フィールドプレート絶縁層と、

前記第1フィールド絶縁層上に接し、平面視で前記第1ドリフト領域と前記第2ドリフト領域の一部と重なるように設けられた第1フィールドプレート電極と、

を備え、

前記第1ドリフト領域の深さをσ1、前記第1ドリフト領域の不純物濃度をN1、前記第2ドリフト領域の深さをσ2、前記第2ドリフト領域の不純物濃度をN2としたとき、下記式(1)を満たす半導体装置が提供される。

【0011】

【数1】

【0012】

(ただし、tOX*は前記ゲート絶縁層の電気的膜厚、tFP*は前記第1ドリフト領域と前記第2ドリフト領域との境界における前記第1フィールドプレート絶縁層の電気的膜厚である。なお、電気的膜厚は、誘電率と物理的膜厚との積である。)

【0013】

本発明によれば、

半導体基板に第1導電型の不純物を導入することにより、第1ドリフト領域を形成する第1ドリフト領域工程と

前記半導体基板に第1導電型の不純物を注入することにより、平面視で前記第1ドリフト領域に接するように、第2ドリフト領域を形成する第2ドリフト領域形成工程と、

前記半導体基板に第1導電型の不純物を注入することにより、平面視で前記第1ドリフト領域のうち前記第2ドリフト領域と反対側の領域から離間した位置に、ソース領域を形成する工程と、

前記半導体基板に前記第1ドリフト領域および前記第2ドリフト領域よりも高い不純物濃度で第1導電型の不純物を注入することにより、平面視で前記第1ドリフト領域から離間するとともに、平面視で前記第2ドリフト領域のうち前記第1ドリフト領域と反対側の領域に接するように、ドレイン領域を形成する工程と、

前記半導体基板上に、平面視で前記ソース領域および前記第1ドリフト領域に挟まれたチャネル領域に重なるようにゲート絶縁層を形成するゲート絶縁層形成工程と、

少なくとも平面視で前記第1ドリフト領域と前記第2ドリフト領域の一部と重なるように、前記ゲート絶縁層よりも厚く第1フィールドプレート絶縁層を形成する第1フィールドプレート絶縁層形成工程と、

前記ゲート絶縁層上に接するとともに、平面視で前記チャネル領域と重なるようにゲート電極を形成する工程と、

前記第1フィールドプレート絶縁層上に接し、平面視で前記第1ドリフト領域と前記第2ドリフト領域の一部と重なるように、第1フィールドプレート電極を形成する工程と、

を備え、

前記第1ドリフト領域形成工程、前記第2ドリフト領域形成工程、前記ゲート絶縁層形成工程および前記第1フィールドプレート絶縁層形成工程において、前記第1ドリフト領域の深さをσ1、前記第1ドリフト領域の不純物濃度をN1、前記第2ドリフト領域の深さをσ2、前記第2ドリフト領域の不純物濃度をN2としたとき、上記式(1)を満たすように、前記第1ドリフト領域、前記第2ドリフト領域、前記ゲート絶縁層および前記第1フィールドプレート絶縁層を形成する半導体装置の製造方法が提供される。

【0014】

本発明によれば、ソース領域およびドレイン領域の間には、第1ドリフト領域および第2ドリフト領域が設けられている。第1フィールドプレート電極は、第1フィールドプレート絶縁層上に接し、平面視で第1ドリフト領域と第2ドリフト領域の一部と重なるように設けられている。このとき、これらを構成する物性値は、上記式(1)を満たしている。これにより、半導体装置内の電界強度を偏りなく分布させることができる。また、ゲート電極および第1ドリフト領域の間、または第1ドリフト領域および第2ドリフト領域の間等における電界強度が大きくなることを抑制することができる。したがって、電界が局所的に集中することを抑制して、高耐圧化した半導体装置を提供することができる。

【発明の効果】

【0015】

本発明によれば、電界が局所的に集中することを抑制して、高耐圧化した半導体装置を提供することができる。

【図面の簡単な説明】

【0016】

【図1】第1の実施形態に係る半導体装置の構成を示す断面図である。

【図2】第1の実施形態に係る半導体装置の構成を示す回路図である。

【図3】第1の実施形態に係る第1ドリフト領域の深さに対する電界強度の関係を示した図である。

【図4】第1の実施形態に係る半導体装置の構成を説明するための図である。

【図5】第1の実施形態に係る半導体装置の製造方法を説明するための断面図である。

【図6】第1の実施形態に係る半導体装置の製造方法を説明するための断面図である。

【図7】第1の実施形態に係る半導体装置の製造方法を説明するための断面図である。

【図8】第1の実施形態に係る半導体装置の製造方法を説明するための断面図である。

【図9】第1の実施形態に係る半導体装置の製造方法を説明するための断面図である。

【図10】比較例の半導体装置の構成を示す断面図である。

【図11】第1の実施形態の効果を説明するための図である。

【図12】第2の実施形態に係る半導体装置の構成を示す断面図である。

【図13】第3の実施形態に係る半導体装置の構成を示す断面図である。

【図14】第3の実施形態に係る半導体装置の製造方法を説明するための断面図である。

【図15】第3の実施形態に係る半導体装置の製造方法を説明するための断面図である。

【図16】第4の実施形態に係る半導体装置の構成を示す断面図である。

【図17】第4の実施形態に係る半導体装置の製造方法を説明するための断面図である。

【図18】第4の実施形態に係る半導体装置の製造方法を説明するための断面図である。

【図19】第4の実施形態に係る半導体装置の製造方法を説明するための断面図である。

【図20】第5の実施形態に係る半導体装置の構成を示す断面図である。

【図21】第6の実施形態に係る半導体装置の構成を示す断面図である。

【発明を実施するための形態】

【0017】

以下、本発明の実施の形態について、図面を用いて説明する。尚、すべての図面において、同様な構成要素には同様の符号を付し、適宜説明を省略する。

【0018】

(第1の実施形態)

図1〜図4を用い、第1の実施形態に係る半導体装置10について説明する。この半導体装置10は、以下の構成を備えている。第1導電型のソース領域110は、半導体基板100に設けられている。第1導電型の第1ドリフト領域140は、半導体基板100に設けられ、平面視でソース領域110から離間して設けられている。半導体基板100のうち、平面視でソース領域110および第1ドリフト領域140に挟まれた領域には、チャネル領域130が形成されている。第1導電型の第2ドリフト領域150は、半導体基板100に設けられ、平面視で第1ドリフト領域140のうちソース領域110と反対側の領域に接している。第1導電型のドレイン領域120は、半導体基板100に設けられ、平面視で第1ドリフト領域140から離間しているとともに、平面視で第2ドリフト領域150のうち第1ドリフト領域140と反対側の領域に接している。また、第1導電型のドレイン領域120は、第1ドリフト領域140および第2ドリフト領域150よりも不純物濃度が高い。チャネル領域130上には、ゲート絶縁層200が設けられている。ゲート電極400は、ゲート絶縁層200上に接し、平面視でチャネル領域130重なるように設けられている。第1フィールドプレート絶縁層300は、半導体基板100上に設けられ、少なくとも平面視で第1ドリフト領域140と第2ドリフト領域150の一部と重なるように設けられている。また、第1フィールドプレート絶縁層300は、ゲート絶縁層200よりも厚い。第1フィールドプレート電極420は、第1フィールドプレート絶縁層300上に接し、平面視で第1ドリフト領域140と第2ドリフト領域150の一部と重なるように設けられている。さらに、第1ドリフト領域140の深さをσ1、第1ドリフト領域140の不純物濃度をN1、第2ドリフト領域150の深さをσ2、第2ドリフト領域150の不純物濃度をN2としたとき、下記式(1)を満たす。

【0019】

【数1】

【0020】

ただし、tOX*はゲート絶縁層200の電気的膜厚、tFP*は第1ドリフト領域140と第2ドリフト領域150との境界における第1フィールドプレート絶縁層300の電気的膜厚である。なお、電気的膜厚は、誘電率と膜厚との積である。以下、詳細を説明する。

【0021】

まず、図1を用い、半導体装置10の全体構造について、説明する。図1は、第1の実施形態に係る半導体装置10の構成を示す断面図である。

【0022】

図1のように、半導体装置10は、横型MOSFETである。この半導体装置10は、たとえば、10V以上1000V未満の電圧が印加される電源用ICとして用いられる。具体的には、半導体装置10は、たとえば、コンピュータ、車載用電子機器、民生用電子機器または通信機器などの電源ICに用いられる。また、第1ドリフト領域140および第2ドリフト領域150の横方向の長さ、不純物濃度の構成によっては、1000V以上の高電圧が印加される、電力、輸送機器向け等の電力変換機にも用いることができる。

【0023】

第1の実施形態では、たとえば、半導体基板100の少なくとも主面側は、III族窒化物半導体からなるIII族窒化物半導体層104である。半導体基板100は、たとえば、下地基板102と、III族窒化物半導体からなるIII族窒化物半導体層104を備えている。III族窒化物半導体層104は、下地基板102の主面上に設けられている。下地基板102は、たとえば、Si基板、サファイア基板、SiC基板またはGaN基板(バルクGaN基板)である。好ましくは、下地基板102は、たとえば、Si基板である。これにより、Si系の半導体製造装置を流用することができる。

【0024】

下地基板102とIII族窒化物半導体層104との間には、バッファ層(不図示)が設けられていてもよい。バッファ層は、下地基板102とIII族窒化物半導体層104との格子定数の差に基づいて、適切な材料が用いられる。具体的には、バッファ層は、たとえば、AlGaN層、またはその積層構造である。

【0025】

III族窒化物半導体層104には、ソース領域110、チャネル領域130、第1ドリフト領域140、第2ドリフト領域150およびドレイン領域120が形成されている。これにより、横型MOSFETが形成されている。ここで、III族窒化物半導体は、Si系の半導体装置と比較して、高い耐圧性と、飽和ドリフト速度を有している。これにより、高耐圧で低損失なスイッチング素子を形成することができる。具体的には、III族窒化物半導体層104は、たとえば、GaN層である。また、III族窒化物半導体層104の面方位のうち、半導体基板100の法線方向の面方位は、たとえば(0001)(c−面)である。

【0026】

ここで、III族窒化物半導体層104にFETが形成されている場合、当該FETは、nチャネル型である。ただし、pチャネル型であってもよい。

【0027】

III族窒化物半導体層104は、たとえば、真性半導体である。言い換えれば、III族窒化物半導体層104のうち、ソース領域110およびドレイン領域130の間に位置する部分には、p型の不純物領域が形成されていない。また、少なくともチャネル領域130の不純物濃度は、たとえば、1×10−16atoms/cm3以下である。このような場合に、後述する半導体装置10の構成を備えていることにより、顕著に高耐圧化させることができる。

【0028】

また、ソース領域110、第1ドリフト領域140、第2ドリフト領域150およびドレイン領域120は、たとえば、n型である。すなわち、上記した「第1導電型」とは、たとえばn型である。当該n型の不純物は、たとえば、Siである。これにより、III族窒化物半導体層104において、容易にnチャネル型FETを形成することができる。

【0029】

なお、以下において、「半導体基板100に」とした場合には、特に断りのない限り、「半導体基板100のうちのIII族窒化物半導体層104に」であることを含んでいる。また、「第1導電型」は、n型であるとする。

【0030】

n型のソース領域110は、半導体基板100に設けられている。ここで、ソース領域110等の不純物が導入された領域は、たとえば、n型不純物をイオン注入することにより形成されている。また、ここでいう「ソース領域110」等の「不純物が導入された範囲」は、半導体基板100のうち不純物濃度が1×1016atoms/cm3以上である領域をいう。言い換えれば、「不純物が導入された範囲」は、半導体基板100の不純物濃度に対して、10倍以上高い濃度である領域をいう。なお、当該領域の不純物濃度が半導体基板100の不純物濃度に対して差が無い場合は、「不純物が導入された範囲」は最も不純物濃度が高い場所を頂点としたガウス分布であると仮定したときに頂点からσまで(ここでのσは標準偏差の意)の領域であってもよい。なお、上記した「不純物が導入された範囲」の定義は、「ソース領域110」、「第1ドリフト領域140」、「第2ドリフト領域150」および「ドレイン領域120」について適用される。また、当該定義は、不純物が導入された領域のうち、平面視での幅、半導体基板100の主面と垂直の方向における深さに対して適用される。

【0031】

n型の第1ドリフト領域140は、半導体基板100に設けられており、平面視でソース領域110から離間して設けられている。半導体基板100のうち平面視でソース領域110および第1ドリフト領域140に挟まれた領域には、チャネル領域130が形成されている。チャネル領域130の長さは、所望のオン抵抗、オフ抵抗またはドレイン・ソース間電流の大きさなどによって決定される。チャネル領域130の典型的な長さは、たとえば100nm以上10μm未満である。

【0032】

n型の第2ドリフト領域150は、半導体基板100に設けられ、平面視で第1ドリフト領域140のうちソース領域110と反対側の領域に接している。第2ドリフト領域150は、たとえば、第1ドリフト領域140よりも深く形成されている。なお、第1ドリフト領域140および第2ドリフト領域150における不純物濃度は、ソース領域110よりも低い。

【0033】

なお、第1ドリフト領域140および第2ドリフト領域150のうち、ソース領域110からドレイン領域120に向かう方向の長さについても、所望のオン抵抗、オフ抵抗またはドレイン・ソース間電流の大きさなどによって決定される。第1ドリフト領域140および第2ドリフト領域150のうち、ソース領域110からドレイン領域120に向かう方向の長さは、たとえば、100nm以上10μm未満である。

【0034】

n型のドレイン領域120は、半導体基板100に設けられ、平面視で第1ドリフト領域140から離間しているとともに、平面視で第2ドリフト領域150のうち第1ドリフト領域140と反対側の領域に接している。ここでいう「ドレイン領域120が平面視で第1ドリフト領域140から離間している」とは、ドレイン領域120が第1ドリフト領域140と接していないことを意味する。これにより、ゲート電極400と第1ドリフト領域140との間での電界集中を緩和することができる。

【0035】

また、ドレイン領域120は、第1ドリフト領域140および第2ドリフト領域150よりも不純物濃度が高い。ドレイン領域120と同様にして、ソース領域110も第1ドリフト領域140および第2ドリフト領域150よりも不純物濃度が高いことが好ましい。ソース領域110およびドレイン領域120の不純物濃度は、第1ドリフト領域140および第2ドリフト領域150よりも10倍以上高いことが好ましい。具体的には、ソース領域110およびドレイン領域120の不純物濃度が1×1020atoms/cm3以上であるとき、第1ドリフト領域140および第2ドリフト領域150の不純物濃度は1×1019atoms/cm3未満であることが好ましい。これにより、ソース・ドレイン間電圧によって電界が集中することを抑制することができる。

【0036】

なお、図1では、ドレイン領域120の深さが第2ドリフト領域150等よりも深い場合を示しているが、ドレイン領域120の深さは第2ドリフト領域150よりも浅くていもよい。

【0037】

ゲート絶縁層200は、チャネル領域130上に接して設けられている。ゲート絶縁層200は、たとえば、スパッタにより形成されたSiO2、SiN、Al2O3である。そのほか、ゲート絶縁層200は、Ta2O5などの高誘電率材料により形成されていてもよい。

【0038】

ゲート電極400は、ゲート絶縁層200上に接し、平面視でチャネル領域130に重なるように設けられている。

【0039】

第1フィールドプレート絶縁層300は、半導体基板100上に設けられ、少なくとも平面視で第1ドリフト領域140と第2ドリフト領域150の一部と重なるように設けられている。ここでいう「第1フィールドプレート絶縁層300」とは、後述する第1フィールドプレート電極420と半導体基板100の主面との間に設けられた絶縁層のことである。また、ここでいう「第1フィールドプレート絶縁層300」は、ゲート絶縁層200と独立に形成されている必要は無く、ゲート絶縁層200の一部を含んでいてもよい。第1の実施形態では、第1フィールドプレート絶縁層300は、下地絶縁層320の一部と、ゲート絶縁層200一部とを含んでいる。下地絶縁層320は、半導体基板100上に接して設けられており、平面視でチャネル領域130と重なる領域に開口部を有している。また、上述したゲート絶縁層200は、下地絶縁層320の開口部に露出したチャネル領域130上、および下地絶縁層320上に設けられている。これにより、第1フィールドプレート絶縁層300をゲート絶縁層200よりも厚くすることができる。なお、下地絶縁層320は、たとえば、CVD(Chemical Vapor Deposition)により形成された、SiO2、SiNなどである。

【0040】

第1フィールドプレート電極420は、第1フィールドプレート絶縁層300上に接し、平面視で第1ドリフト領域140と第2ドリフト領域150の一部と重なるように設けられている。言い換えれば、第1フィールドプレート電極420の一端は、平面視で第1ドリフト領域140および第2ドリフト領域150の境界よりもドレイン領域120側に位置している。また、第1フィールドプレート電極420は第1フィールドプレート絶縁層300上に設けられていることにより、第1フィールドプレート電極420の下面は、ゲート電極400の下面よりも半導体基板100の上面から離間している。

【0041】

第1の実施形態では、第1フィールドプレート電極420は、ゲート電極400に接続している。また、第1フィールドプレート電極420は、ゲート電極400と一体として形成されている。第1フィールドプレート電極420は、ゲート電極400と同じ材料により形成されている。なお、この場合では、ゲート電極400と第1フィールドプレート電極420との間に、界面は形成されていない。また、ゲート電極400、第1フィールドプレート電極420の材料は、たとえば、Alおよび/またはTiNなどである。このように、第1フィールドプレート電極420をゲート電極400と一体として形成することにより、製造工程を簡略化することができる。

【0042】

さらに、第1フィールドプレート電極420を覆うように、第1層間絶縁層520が設けられていてもよい。第1層間絶縁層520は、たとえば、SiO2、SiN、SiON、SiOC、SiOCH、SiCOHまたはSiOFなどである。

【0043】

ソース電極440は、平面視でソース領域110と重なるように設けられ、第1層間絶縁層520、ゲート絶縁層200および下地絶縁層320を貫通してソース領域110に接続している。また、ドレイン電極460は、平面視でドレイン領域120と重なるように設けられ、第1層間絶縁層520、ゲート絶縁層200および下地絶縁層320を貫通してドレイン領域120に接続している。また、ソース電極440、ドレイン電極460の材料は、たとえば、AlまたはTiNなどである。

【0044】

次に、図2を用い、第1の実施形態に係る半導体装置10の回路について説明する。図2は、第1の実施形態に係る半導体装置10の構成を示す回路図である。図2のように、第1の実施形態の半導体装置10は、たとえば、DC―DCコンバータである。この回路は、たとえば、降圧型のコンバータである。この半導体装置10は、たとえば、DC−DCコントローラIC800、2つのnチャネルFET11、インダクタ820およびコンデンサ840を備えている。2つのnチャネルFET11は、VINとGNDとの間に直列に接続されている。また、このnチャネルFET11は、たとえば、図1で示されたFETである。nチャネルFET11のゲート電圧は、DC−DCコントローラIC800によって制御されている。2つのnチャネルFET11の間からは、インダクタ820を介してVOUTが取り出される。なお、インダクタ820とVOUTとの間は、コンデンサ840を介してGNDに接続されている。また、DC−DCコントローラIC800は、たとえば、VINから入力されたDC信号をパルスに変換する。変換したパルスにより、nチャネルFET11は、インダクタ820にエネルギーを蓄え、次いでそのエネルギーをVOUTに放出するという動作を交互に繰り返す。第1の実施形態によれば、nチャネルFET11は、安定的にスイッチング機能を発揮することができる。

【0045】

次に、図3および図4を用い、第1の実施形態に係る半導体装置10の構成について、さらに詳細に説明する。図3は、第1の実施形態に係る第1ドリフト領域140の深さに対する電界強度の関係を示した図である。図4は、第1の実施形態に係る半導体装置10の構成を説明するための図である。

【0046】

図3は、ゲート電圧を0V、ドレイン・ソース間電圧を100Vとしたときの電界強度の第1ドリフト領域140の深さσ1の依存性についてシミュレーションした結果を示している。ゲート絶縁層200の厚さ(tOX)は50nm、第1ドリフト領域140と第2ドリフト領域150との境界における第1フィールドプレート絶縁層300の厚さ(tFP)は300nm、第2ドリフト領域150の不純物濃度(N2)は5×1018cm−2、第2ドリフト領域150の深さ(σ2)は15nm、第1ドリフト領域140の不純物濃度(N1)は2×1018cm−2であると仮定した。横軸は、第1ドリフト領域140の深さσ1(単位nm)である。また、縦軸は、電界強度(単位MV/cm)である。実線は、ゲート電極400および第1ドリフト領域140間の電界強度を示している。また、点線は、第1ドリフト領域140および第2ドリフト領域150間の電界強度を示している。

【0047】

図3のように、ゲート電極400および第1ドリフト領域140間の電界強度は、第1ドリフト領域140の深さσ1が大きくなるにつれて、大きくなる傾向にある。一方、第1ドリフト領域140および第2ドリフト領域150間の電界強度は、第1ドリフト領域140の深さσ1に対して下に凸の傾向を示す。第1ドリフト領域140の深さσ1が30nm以下の領域では、第1ドリフト領域140および第2ドリフト領域150間の電界強度は、第1ドリフト領域140の深さσ1が大きくなるにつれて、小さくなる傾向にある。

【0048】

ここで、ゲート電極400および第1ドリフト領域140間の電界強度と、第1ドリフト領域140および第2ドリフト領域150間の電界強度とが等しくなるときの第1ドリフト領域140の深さσ1をσ1cとする。第1ドリフト領域140の深さσ1がσ1cのとき、半導体装置10内の電界強度が最も均等(一様)に分布する。言い換えれば、このとき、半導体装置10内の電界強度の最大値を、最も小さくすることができる。

【0049】

また、第1ドリフト領域140および第2ドリフト領域150間の電界強度は、第1ドリフト領域140の深さσ1に対して、あまり大きく変わらない。反対に、ゲート電極400および第1ドリフト領域140間の電界強度は、第1ドリフト領域140の深さσ1に対して大きく依存している。したがって、第1ドリフト領域140の深さσ1をσ1cより小さくすることにより、半導体装置10内の電界強度を全体的に小さくすることができる。特に、第1ドリフト領域140の深さσ1をσ1cより小さくすることにより、ゲート電極400および第1ドリフト領域140間の電界強度を小さくすることができる。

【0050】

図4(a)は、様々な条件において、σ1cを算出した結果を示している。図4のように、発明者は、第1ドリフト領域140の深さをσ1、第1ドリフト領域140の不純物濃度をN1、第2ドリフト領域150の深さをσ2、第2ドリフト領域150の不純物濃度をN2としたとき、σ1cがσ2N2/N1に比例することを見出した。この比例定数をCσとしたとき、σ1cを下記式(2)で表すことができる。

【0051】

【数2】

【0052】

また、図4(b)は、ゲート絶縁層200の厚さをtOXとしたときの上記比例定数Cσのゲート絶縁層200の厚さtOX依存性を示している。図4のように、発明者は、比例定数Cσがゲート絶縁層200の厚さtOXの平方根に比例することを見出した。図中の実線は、比例定数Cσがゲート絶縁層200の厚さtOXの平方根に比例する関数をフィッティングしたものである。発明者は、半導体装置10における具体的なパラメータから、上記した関数を下記式(3)により表せることを見出した。ここで、ゲート絶縁層200の電気的膜厚をtOX*、第1ドリフト領域140と第2ドリフト領域150との境界における第1フィールドプレート絶縁層300の電気的膜厚をtFP*としたとき、比例定数Cσを以下の式(3)のように表すことができる。

【0053】

【数3】

【0054】

上記式(3)のうち、tOX*およびtFP*は、上述のように、それぞれゲート絶縁層200および第1フィールドプレート絶縁層300の電気的膜厚を示している。ここでいう「電気的膜厚」とは、絶縁膜の物理的膜厚と誘電率との積のことをいう。なお、「物理的膜厚」とは、対象となる層のうち断面視で下面から上面までの厚さのことをいう。

【0055】

したがって、ゲート絶縁層200の誘電率をεOX、ゲート絶縁層200の物理的膜厚をtOXとしたとき、ゲート絶縁層200の電気的膜厚tOX*を以下の式(4)のように表すことができる。

【0056】

【数4】

【0057】

また、第1フィールドプレート絶縁層300の誘電率をεFP*、ゲート絶縁層200の物理的膜厚をtFPとしたとき、第1フィールドプレート絶縁層300の電気的膜厚tFP*を以下の式(5)のように表すことができる。

【0058】

【数5】

【0059】

なお、第1フィールドプレート絶縁層300が複数の(たとえばN層の)絶縁層によって形成されている場合、それぞれの絶縁層の誘電率をεj、物理的膜厚をtj(1≦j≦N)としたとき、第1フィールドプレート絶縁層300の誘電率εFP*、ゲート絶縁層200の物理的膜厚tFPをそれぞれ以下の式(6)、式(7)のように表すことができる。

【0060】

【数6】

【0061】

【数7】

【0062】

第1の実施形態のように、第1フィールドプレート絶縁層300は、ゲート絶縁層200および下地絶縁層320が積層されることにより形成されている。この場合、ゲート絶縁層200の誘電率並びに厚さ、および下地絶縁層320の誘電率並びに厚さを、式(6)および式(7)に代入し、さらに式(5)を計算することにより、第1フィールドプレート絶縁層300の電気的膜厚tFP*を求めることができる。

【0063】

以上により、第1ドリフト領域140の深さσ1がσ1cより小さいとき、下記式(1)を満たす。

【0064】

【数8】

【0065】

上記式(1)を満たすことにより、ゲート電極400および第1ドリフト領域140の間、または第1ドリフト領域140および第2ドリフト領域150の間における電界強度が大きくなることを抑制することができる。

【0066】

ここで、第1ドリフト領域140の不純物濃度N1は、たとえば、第2ドリフト領域150の不純物濃度N2よりも小さい。このとき、第1ドリフト領域140、第2ドリフト領域150およびドレイン領域120の順で不純物濃度が高くなっている。このような構成とすることにより、イオン注入後の活性化工程によって、容易に不純物濃度が段階的に異なる不純物領域を形成することができる。また、N1<N2である場合、式(1)を満たすように不純物注入エネルギーなどの他のパラメータを調整することにより、第1ドリフト領域140の深さσ1が第2ドリフト領域150の深さσ2よりも大きい構成とすることができる。ただし、第1ドリフト領域140は、ドレイン領域120から離間している。これにより、半導体装置10中の電界強度を安定的に最小化して耐圧を維持するとともに、オン抵抗を可能な限り下げることができる。

【0067】

一方で、第1ドリフト領域140の不純物濃度N1は、たとえば、第2ドリフト領域150の不純物濃度N2よりも大きくてもよい。このとき、第1ドリフト領域140は、半導体基板100の表面付近に形成されていれば、式(1)を満たす範囲が広くなる。イオン注入などにより不純物領域の深さを制御することが困難な場合、N1>N2で且つ第1ドリフト領域140の深さσ1を浅くすることにより、容易に式(1)を満たす構成を形成することができる。この場合でも、半導体装置10中の電界強度を安定的に最小化して耐圧を維持するとともに、オン抵抗を可能な限り下げることができる。

【0068】

次に、図5〜図9を用い、第1の実施形態に係る半導体装置10の製造方法について説明する。図5〜図9は、第1の実施形態に係る半導体装置10の製造方法を説明するための断面図である。第1の実施形態に係る半導体装置10の製造方法は、以下の工程を備えている。まず、半導体基板100に、第1導電型の不純物を注入することにより、第1ドリフト領域140を形成する(第1ドリフト領域形成工程)。次いで、半導体基板100に、第1導電型の不純物を注入することにより、平面視で第1ドリフト領域140に接するように、第2ドリフト領域150を形成する(第2ドリフト領域形成工程)。次いで、半導体基板100に、第1導電型の不純物を注入することにより、平面視で第1ドリフト領域140のうち第2ドリフト領域150と反対側の領域から離間した位置に、ソース領域110を形成する。次いで、半導体基板100に、第1ドリフト領域140および第2ドリフト領域150よりも高い不純物濃度で第1導電型の不純物を注入することにより、平面視で第1ドリフト領域140から離間するとともに、平面視で第2ドリフト領域150のうち第1ドリフト領域140と反対側の領域に接するように、ドレイン領域120を形成する。次いで、半導体基板100上に、平面視でソース領域110および第1ドリフト領域140に挟まれたチャネル領域130に重なるようにゲート絶縁層200を形成する(ゲート絶縁層形成工程)。次いで、少なくとも平面視で第1ドリフト領域140と第2ドリフト領域150の一部と重なるように、ゲート絶縁層200よりも厚く、第1フィールドプレート絶縁層300を形成する(第1フィールドプレート絶縁層形成工程)。次いで、ゲート絶縁層200上に接するとともに、平面視でチャネル領域130と重なるように、ゲート電極400を形成する。次いで、第1フィールドプレート絶縁層300上に接し、平面視で第1ドリフト領域140と第2ドリフト領域150の一部と重なるように、第1フィールドプレート電極420を形成する。上記工程のうち、第1ドリフト領域形成工程、第2ドリフト領域形成工程、ゲート絶縁層形成工程および第1フィールドプレート絶縁層形成工程において、上述した式(1)を満たすように、第1ドリフト領域140、第2ドリフト領域150、ゲート絶縁層200および第1フィールドプレート絶縁層300を形成する。以下、詳細を説明する。

【0069】

図5(a)のように、まず、半導体基板100を準備する。図1で示したように、半導体基板100は、下地基板102の主面上にIII族窒化物半導体層104を備えている。ここでは、III族窒化物半導体層104は、たとえば、GaNである。次いで、半導体基板100上に、保護層240を形成する。ここでは、たとえば、半導体基板100の表面を酸化することにより保護層240を形成する。具体的には、保護層240は、たとえばGa2O3である。なお、保護層240をスパッタなどにより形成してもよい。

【0070】

次いで、図5(b)のように、保護層240上に、フォトレジスト層600を形成する。次いで、露光および現像により、平面視で第1ドリフト領域140の形成領域に、フォトレジスト層600に開口部(符号不図示)を形成する。次いで、イオン注入装置により、当該開口部に、第1導電型の不純物を注入する。このとき、第1ドリフト領域140の深さをσ1、第1ドリフト領域140の不純物濃度をN1が上記した式(1)を満たすように、不純物注入量、加速電圧等を調整する。これにより、第1ドリフト領域140を形成する(第1ドリフト領域形成工程)。ここでは、上述のように、n型の不純物として、Siを注入する。以下では、「第1導電型」が「n型」であり、「第1導電型の不純物」がn型の不純物であるSiであるとして説明する。次いで、たとえば、アッシングなどにより、フォトレジスト層600を除去する。

【0071】

次いで、図6(a)のように、保護層240上に、再度、フォトレジスト層600を形成する。次いで、露光および現像により、平面視で第1ドリフト領域140に接するように、フォトレジスト層600に開口部(符号不図示)を形成する。次いで、当該開口部に、n型の不純物としてSiを注入する。このとき、第2ドリフト領域150の深さをσ2、第2ドリフト領域150の不純物濃度をN2が上記した式(1)を満たすように、不純物注入量、加速電圧等を調整する。これにより、平面視で第1ドリフト領域140に接するように、第2ドリフト領域150を形成する(第2ドリフト領域形成工程)。次いで、たとえば、アッシングなどにより、フォトレジスト層600を除去する。

【0072】

次いで、図6(b)のように、保護層240上に、再度、フォトレジスト層600を形成する。次いで、露光および現像により、平面視で第1ドリフト領域140のうち第2ドリフト領域150と反対側の領域から離間した位置、および平面視で第1ドリフト領域140から離間するとともに平面視で第2ドリフト領域150のうち第1ドリフト領域140と反対側の領域に接するように、フォトレジスト層600に開口部(符号不図示)を形成する。すなわち、ソース領域110およびドレイン領域120の形成領域に、フォトレジスト層600に開口部を形成する。次いで、当該開口部に、n型の不純物としてSiを注入する。これにより、平面視で第1ドリフト領域140のうち第2ドリフト領域150と反対側の領域から離間するように、ソース領域110を形成する。また、平面視で第1ドリフト領域140から離間するとともに平面視で第2ドリフト領域150のうち第1ドリフト領域140と反対側の領域に接するように、ドレイン領域を形成する。

【0073】

このとき、第1ドリフト領域140および第2ドリフト領域150よりも高い不純物濃度で、ドレイン領域120を形成する。また、ドレイン領域120と同様にしてソース領域110も、第1ドリフト領域140および第2ドリフト領域150よりも高い濃度で形成することが好ましい。上述のように、ソース領域110およびドレイン領域120の不純物濃度を、第1ドリフト領域140および第2ドリフト領域150よりも10倍以上高くなるように形成することが好ましい。これにより、ソース・ドレイン間電圧によって電界が集中することを抑制することができる。

【0074】

以上の工程により、たとえば、チャネル領域130の長さが100nm以上10μm未満となるように、チャネル領域130を形成する。また、第1ドリフト領域140および第2ドリフト領域150のうち、ソース領域110からドレイン領域120に向かう方向の長さが100nm以上10μm未満となるように、第1ドリフト領域140および第2ドリフト領域150を形成する。

【0075】

次いで、たとえば、アッシングなどにより、フォトレジスト層600を除去する。さらに、プラズマエッチングまたはウエットエッチングにより、保護層240を除去する。

【0076】

ここで、たとえば、700℃以上1300℃未満でアニール処理を行うことにより、ソース領域110、第1ドリフト領域140、第2ドリフト領域150およびドレイン領域120に注入された不純物を活性化させる。これにより、注入されたイオンと結晶構成原子とを置換させることができる。また、イオン注入でダメージを受けた半導体基板100の結晶性を回復させることができる。なお、半導体基板100の主面が保護層240で覆われた状態でアニール処理を行ってもよい。これにより、半導体基板100の窒素が抜けることを抑制することができる。

【0077】

次いで、図7(a)のように、たとえば、CVDにより、半導体基板100上に、下地絶縁層320を形成する。下地絶縁層320として、たとえば、SiO2、SiNを成膜する。次いで、たとえば、RIE(Reactive Ion Etching)により、下地絶縁層320のうち、少なくとも平面視でチャネル領域130と重なる位置に、チャネル開口部210を形成する。

【0078】

次いで、図7(b)のように、たとえば、スパッタにより、チャネル開口部210に露出した半導体基板100上、および下地絶縁層320上に、ゲート絶縁層200を形成する。ゲート絶縁層200をスパッタにより形成することにより、膜質の良いゲート絶縁層200を形成することができる。ゲート絶縁層200として、たとえば、SiO2、SiN、Al2O3を成膜する。このようにして、平面視でチャネル領域130に重なるように、ゲート絶縁層200を形成する(ゲート絶縁層形成工程)。また、下地絶縁層320およびゲート絶縁層200を積層することにより、第1フィールドプレート絶縁層300を形成する。このようにして、少なくとも平面視で第1ドリフト領域140と第2ドリフト領域150の一部と重なるように、第1フィールドプレート絶縁層300を形成する(第1フィールドプレート絶縁層形成工程)。この場合、第1フィールドプレート絶縁層形成工程はゲート絶縁層形成工程を含んでいる。また、第1フィールドプレート絶縁層300は、下地絶縁層320の一部およびゲート絶縁層200の一部を含んでいる。

【0079】

ここで、以上のゲート絶縁層形成工程および第1フィールドプレート絶縁層形成工程において、ゲート絶縁層200の厚さtOX、ゲート絶縁層200の誘電率εOX、第1フィールドプレート絶縁層300の誘電率εFP、第1ドリフト領域140と第2ドリフト領域150との境界における第1フィールドプレート絶縁層300の厚さtFPが上述した式(1)を満たすように、成膜材料、成膜条件等を調整する。なお、第1フィールドプレート絶縁層300はゲート絶縁層200および下地絶縁層320が積層されることにより形成されているため、εFPおよびtFPは、ゲート絶縁層200の厚さtOX、ゲート絶縁層200の誘電率εOX、下地絶縁層320の誘電率εUL、および下地絶縁層320の厚さtULから上述した式(4)により算出する。

【0080】

また、ゲート絶縁層200として用いられる材料が高温に強くない材料(たとえばAl2O3)である場合、ゲート絶縁層形成工程を、下地絶縁層320を形成する工程よりも後に行う方が好ましい。この場合、下地絶縁層320を形成する前にゲート絶縁層形成工程を行った場合、ゲート絶縁層200の膜質が劣化する可能性がある。したがって、ゲート絶縁層形成工程を、下地絶縁層320を形成する工程よりも後に行うことにより、ゲート絶縁層200の膜質が劣化することを抑制することができる。

【0081】

次いで、図8(a)のように、スパッタにより、ゲート絶縁層200上に金属膜を形成する。たとえば、金属膜として、Alおよび/またはTiNを成膜する。次いで、当該金属膜上にフォトレジスト層(不図示)を形成する。露光および現像により、平面視でチャネル領域130と重なる位置、および平面視で第1ドリフト領域140並びに第2ドリフト領域の一部と重なる位置に残存するように、フォトレジスト層をパターニングする。このフォトレジスト層600をマスクとして、プラズマエッチングまたはウエットエッチングにより、金属膜をエッチングする。次いで、たとえば、アッシングによりフォトレジスト層を除去する。以上により、ゲート絶縁層200上に接するとともに、平面視でチャネル領域130と重なるように、ゲート電極400を形成する。また、第1フィールドプレート絶縁層300上に接し、平面視で第1ドリフト領域140と第2ドリフト領域150の一部と重なるように、第1フィールドプレート電極420を形成する。また、第1フィールドプレート電極420をゲート電極400と接続するように形成する。この場合では、第1フィールドプレート電極420を、たとえば、ゲート電極400と一体として形成する。これにより、製造工程を簡略化することができる。

【0082】

次いで、図8(b)のように、たとえば、CVDにより、ゲート絶縁層200、ゲート電極400および第1フィールドプレート電極420上に、第1層間絶縁層520を形成する。第1層間絶縁層520として、たとえば、SiO2、SiN、SiON、SiOC、SiOCH、SiCOHまたはSiOFを成膜する。

【0083】

次いで、図9(a)のように、RIEにより、平面視でソース領域110に重なる位置に、第1層間絶縁層520、ゲート絶縁層200および下地絶縁層320を貫通して半導体基板100の上面に接するソース開口部430を形成する。同時に、RIEにより、平面視でドレイン領域120に重なる位置に、第1層間絶縁層520、ゲート絶縁層200および下地絶縁層320を貫通して半導体基板100の上面に接するドレイン開口部450を形成する。

【0084】

次いで、図9(b)のように、たとえば、スパッタにより、ソース開口部430並びにドレイン開口部450の側面並びに底面、および第1層間絶縁層520上に、金属を形成する。これにより、ソース開口部430およびドレイン開口部450の内部に、金属を埋め込む。具体的には、スパッタにより、Alおよび/またはTiNなどを成膜する。次いで、CMP(Chemical Mechanical Polishing)により、第1層間絶縁層520上を平坦化する。これにより、ソース電極440のビアおよびドレイン電極460のビアを形成する。

【0085】

その後、ダマシン法により、第1層間絶縁層520上に、多層配線構造(不図示)を形成してもよい。また、多層配線構造の最上層に、電極パッド(不図示)を形成してもよい。

【0086】

以上により、第1の実施形態に係る半導体装置10を得ることができる。

【0087】

次に、図10および図11を用い、第1の実施形態の効果について説明する。図10は、比較例の半導体装置の構成を示す断面図である。また、図11は、第1の実施形態の効果を説明するための図である。

【0088】

図10(a)のように、比較例の半導体装置Aは、第1の実施形態に係る半導体装置10と異なり、第2ドリフト領域150および第1フィールドプレート電極420が設けられていない。他の構成は、第1の実施形態と同様である。

【0089】

図10(b)のように、比較例の半導体装置Bは、第1の実施形態に係る半導体装置10と異なり、第2ドリフト領域150が設けられていない。なお、第1フィールドプレート電極420は設けられている。他の構成は、第1の実施形態と同様である。

【0090】

図10(c)のように、比較例の半導体装置Cは、第1の実施形態に係る半導体装置10と異なり、第1ドリフト領域140が第2ドリフト領域150よりも深く形成されている。さらに、第1ドリフト領域140は、ドレイン領域120と接している。他の構成は、第1の実施形態と同様である。

【0091】

図11(a)は、ゲート電圧を0V、ドレイン・ソース間電圧を100Vとしたときの電界強度の分布を示している。横軸は、それぞれの半導体装置における平面視での位置である。また、縦軸は、電界強度(単位MV/cm)である。点線は、比較例の半導体装置Aを示している。破線は、比較例の半導体装置Bを示している。また、実線は、第1の実施形態に係る半導体装置10を示している。

【0092】

図11(a)のように、比較例の半導体装置Aは第1フィールドプレート電極420が設けられていないため、ゲート電極400および第1ドリフト領域140間の電界強度が局所的に大きくなっている。このような場合、ゲート電極400および第1ドリフト領域140間に電界が集中し、ゲート絶縁層200が絶縁破壊を起こす可能性がある。

【0093】

また、比較例の半導体装置Bは第1フィールドプレート電極420が設けられているため、ゲート電極400および第1ドリフト領域140間の電界強度は緩和されている。しかし、反対に、第1ドリフト領域140およびドレイン領域120間の電界強度が局所的に大きくなってしまっている。この原因は、第1フィールドプレート電極420が不純物濃度の高いドレイン領域120と近くなったことにより、電界が集中したと考えられる。

【0094】

一方、第1の実施形態に係る半導体装置10は、ゲート電極400および第1ドリフト領域140間の電界と、ゲート電極400および第1ドリフト領域140間の電界強度は、ともに緩和されている。当該半導体装置10内では、電界強度が一様に分布している。このように、第1の実施形態では、電界が局所的に集中することを抑制することができる。

【0095】

図11(b)は、ゲート電圧を0V、ドレイン・ソース間電圧を100Vとしたときの表面ポテンシャルの分布を示している。横軸は、それぞれの半導体装置における平面視での位置である。また、縦軸は、ポテンシャルエネルギー(単位eV)である。図中のそれぞれの半導体装置は、たとえば、以下のような構成である場合を示している。比較例の半導体装置Cのうち、第1ドリフト領域140の深さσ1は50nm、第2ドリフト領域150の深さσ2は15nmである。なお、上述のように、比較例の半導体装置Cにおいて、第1ドリフト領域140はドレイン領域120に接している。一方、第1の実施形態の半導体装置10のうち、第1ドリフト領域140の深さσ1は5nm、第2ドリフト領域150の深さσ2は15nmである。なお、上述のように、第1の実施形態に係る半導体装置10において、第1ドリフト領域140はドレイン領域120から離間している。

【0096】

図11(b)のように、比較例の半導体装置Cでは、第2ドリフト領域150から第1ドリフト領域140までの領域の電位がドレイン領域120の電位に近い値となっている。第1ドリフト領域140または第2ドリフト領域150がドレイン領域120と独立して形成されているにもかかわらず、ドレイン領域120が平面視で第1ドリフト領域140および第2ドリフト領域150を含むように一体として形成されていると同等となってしまっている。このような場合、ゲート電極400および第1ドリフト領域140間の電界強度が大きくなってしまう。

【0097】

一方、第1の実施形態に係る半導体装置10のうち、第1ドリフト領域140は、ドレイン領域120から離間して形成されている。これにより、第1ドリフト領域140からドレイン領域120までの領域において、緩やかな傾斜で電位が分布している。このような理由においても、第1の実施形態では、電界強度が偏ることがない。

【0098】

第1の実施形態によれば、ソース領域110およびドレイン領域120の間には、第1ドリフト領域140および第2ドリフト領域150が設けられている。第1フィールドプレート電極420は、第1フィールドプレート絶縁層300上に接し、平面視で第1ドリフト領域140と第2ドリフト領域150の一部と重なるように設けられている。このとき、これらを構成する物性値は、上記式(1)を満たしている。これにより、半導体装置10内の電界強度を偏りなく分布させることができる。また、ゲート電極400および第1ドリフト領域140の間、または第1ドリフト領域140および第2ドリフト領域150の間等における電界強度が大きくなることを抑制することができる。

【0099】

さらに、第1の実施形態によれば、第1導電型の不純物領域のみを形成することにより、半導体装置10を高耐圧化させることができる。ここで、たとえば、不純物領域を形成する半導体層がn型およびp型の両方の導電性を制御できる場合、たとえば、ソース領域110またはドレイン領域120の下方に、これらと逆の導電型のハロー領域(またはポケット領域とも呼ばれる)などを形成する場合がある。この場合、ハロー領域が設けられていることにより、ドレイン・ソース間のパンチスルーを抑制することができる。したがって、ソース領域110またはドレイン領域120の近傍に、これらと逆導電型の不純物領域を形成することによって、半導体装置10内の電界を緩和することが可能となる。しかし、導電制御が困難な半導体材料である場合、ソース領域110またはドレイン領域120と逆導電型の不純物領域を設けることは困難である可能性がある。そこで、第1導電型の不純物領域のみにより第1の実施形態のような構成を形成することにより、導電制御が困難な半導体材料であっても半導体装置10を安定的に高耐圧化させることができる。たとえば、上述のように、半導体基板100が、導電制御が困難なIII族窒化物半導体層104等を含む場合に特に有効である。

【0100】

以上により、第1の実施形態によれば、電界が局所的に集中することを抑制して、高耐圧化した半導体装置10を提供することができる。

【0101】

(第2の実施形態)

図12は、第2の実施形態に係る半導体装置10の構成を示す断面図である。第2の実施形態は、第1ドリフト領域140および第2ドリフト領域150に加え、ドリフト領域がさらに設けられている点を除いて、第1の実施形態と同様である。以下、詳細を説明する

【0102】

図12のように、n型の第3ドリフト領域160は、平面視で第2ドリフト領域150とドレイン領域120との間に設けられている。第3ドリフト領域160は、第2ドリフト領域150と接するとともに、ドレイン領域120とも接している。ここで、第3ドリフト領域160の不純物濃度は、たとえば、第1ドリフト領域140および第2ドリフト領域150よりも高い。一方で、第3ドリフト領域160の不純物濃度は、たとえば、ドレイン領域120よりも低い。

【0103】

また、第3ドリフト領域160の深さは、たとえば、第2ドリフト領域150よりも深い。これにより、第2ドリフト領域150は、ドレイン領域120から離間している。また、第2ドリフト領域150は、ドレイン領域120と接していない。

【0104】

第1フィールドプレート電極420は、たとえば、第1の実施形態と同様に、第1フィールドプレート絶縁層300上に接している。また、第1フィールドプレート電極420は、平面視で第1ドリフト領域140と第2ドリフト領域150の一部と重なるように設けられている。

【0105】

第2の実施形態に係る半導体装置10の製造方法は、以下の点を除いて、第1の実施形態と同様である。

【0106】

第2ドリフト領域150を形成する工程の後、ドレイン領域120を形成する工程の前に、第2ドリフト領域150のうち第1ドリフト領域140と反対側の領域に接するように、第3ドリフト領域160を形成する。このとき、第1ドリフト領域140および第2ドリフト領域150よりも高い不純物濃度で、且つ、ドレイン領域120よりも低い不純物濃度で、第3ドリフト領域160を形成する。次いで、平面視で第3ドリフト領域160のうち第2ドリフト領域と反対側の領域に接するように、ドレイン領域120を形成する。

【0107】

以降の工程は、第1の実施形態と同様である。

【0108】

第2の実施形態によれば、第1の実施形態と同様の効果を得ることができる。さらに、第2の実施形態によれば、平面視で第2ドリフト領域150とドレイン領域120との間には、さらにドリフト領域が設けられている。これにより、ゲート電極400およびドレイン領域120との間の電界を段階的に緩和することができる。したがって、さらに半導体装置10の耐圧を向上させることができる。

【0109】

以上、第2の実施形態では、第1フィールドプレート電極420は、平面視で第1ドリフト領域140、第2ドリフト領域150の一部と重なるように設けられている場合について説明した。または、第1フィールドプレート電極420は、平面視で第1ドリフト領域140、第2ドリフト領域150、および第3ドリフト領域160の一部と重なるように設けられていてもよい。この場合、第1フィールドプレート絶縁層300の厚さtFPは、第2ドリフト領域150と第3ドリフト領域160との境界における厚さであると置き換えて、半導体装置10は式(1)を満たす構成であればよい。

【0110】

(第3の実施形態)

図13は、第3の実施形態に係る半導体装置10の構成を示す断面図である。第3の実施形態は、以下の点を除いて、第1の実施形態と同様である。第1層間絶縁層520は、少なくともゲート電極400を覆うように設けられている。ソース電極440は、ソース領域110に接続している。また、第1フィールドプレート絶縁層300は、第1層間絶縁層520の一部を含んでいる。第1の実施形態における第1フィールドプレート電極420がゲート電極400に接続しているのに対して、第2の実施形態では第1フィールドプレート電極420がソース電極440に接続している。以下、詳細を説明する

【0111】

図13のように、第1の実施形態と同様にして、III族窒化物半導体層104には、ソース領域110、チャネル領域130、第1ドリフト領域140、第2ドリフト領域150およびドレイン領域120が形成されている。

【0112】

下地絶縁層320は、半導体基板100上に接して設けられており、平面視でチャネル領域130と重なる領域に開口部を有している。また、ゲート絶縁層200は、下地絶縁層320の開口部に露出したチャネル領域130上、および下地絶縁層320上に設けられている。ゲート電極400は、ゲート絶縁層200上に接し、平面視でチャネル領域130に重なるように設けられている。

【0113】

第3の実施形態では、第2フィールドプレート電極480は、ゲート電極400に接続している。第2フィールドプレート電極480は、平面視で第1ドリフト領域140の一部と重なるように設けられている。反対に、第2フィールドプレート電極480は、平面視で第2ドリフト領域150と重なっていない。言い換えれば、第2フィールドプレート電極480の一端は、平面視で第1ドリフト領域140および第2ドリフト領域150の境界よりもソース領域110側に位置している。また、第2フィールドプレート電極480は、ゲート電極400と一体として形成されていてもよい。

【0114】

第1層間絶縁層520は、たとえば、ゲート電極400および第2フィールドプレート電極480を覆うように設けられている。第1層間絶縁層520上に、さらに第2層間絶縁層540が設けられていてもよい。第2層間絶縁層540は、たとえば、第1層間絶縁層520よりも高密度の材料に形成されていてもよい。これにより、第2層間絶縁層540は、第1層間絶縁層520に対してエッチング選択性を有するエッチングストッパ層として機能させることができる。第2層間絶縁層540の材料は、たとえば、SiCN、SiC、SiON,SiCO、SiCONまたはSiNなどである。

【0115】

ここで「第1フィールドプレート絶縁層300」は、上述のように、第1フィールドプレート電極420と半導体基板100の主面との間に設けられた絶縁層である。第2の実施形態では、第1フィールドプレート絶縁層300は、第1層間絶縁層520の一部を含んでいる。ここでは、さらに、第1フィールドプレート絶縁層300は、第2層間絶縁層540の一部を含んでいる。したがって、第1フィールドプレート絶縁層300は、下地絶縁層320の一部、ゲート絶縁層200の一部、第1層間絶縁層520の一部および第2層間絶縁層540の一部を含んでいる。

【0116】

ソース電極440は、平面視でソース領域110と重なるように設けられている。また、ソース電極440は、下地絶縁層320、ゲート絶縁層200、第1層間絶縁層520および第2層間絶縁層540を貫通して、ソース領域110に接続している。

【0117】

第1フィールドプレート電極420は、第1フィールドプレート絶縁層300のうち、第2層間絶縁層540上に接している。また、第1フィールドプレート電極420は、平面視で第1ドリフト領域140と第2ドリフト領域150の一部と重なるように設けられている。また、第1フィールドプレート電極420はソース電極440に接続している。また、第1フィールドプレート電極420は、ソース電極440と一体として形成されている。第1フィールドプレート電極420は、ソース電極440と同じ材料により形成されている。また、ソース電極440、第1フィールドプレート電極420の材料は、たとえば、Alおよび/またはTiNなどである。このように、第1フィールドプレート電極420をソース電極440と一体として形成することにより、製造工程を簡略化することができる。

【0118】

さらに、当該半導体装置10のうち、それぞれの構成は、上述の式(1)を満たすように形成されている。なお、上述のように、第1フィールドプレート絶縁層300は、下地絶縁層320、ゲート絶縁層200、第1層間絶縁層520および第2層間絶縁層540が積層されることにより形成されている。したがって、第1フィールドプレート絶縁層300の電気的膜厚tFP*は、式(5)、式(6)および式(7)から下地絶縁層320、ゲート絶縁層200、第1層間絶縁層520および第2層間絶縁層540の誘電率と物理的膜厚との積の総和により求めることができる。

【0119】

次に、図14および図15を用い、第3の実施形態に係る半導体装置10の製造方法について説明する。図14および図15は、第1の実施形態に係る半導体装置10の製造方法を説明するための断面図である。第3の実施形態に係る半導体装置10の製造方法は、第1フィールドプレート電極420をソース電極440に接続する点を除いて、第1の実施形態と同様である。以下、詳細を説明する。

【0120】

第1の実施形態と同様にして、図7(b)までの工程を行う。半導体基板100には、ソース領域110、チャネル領域130、第1ドリフト領域140、第2ドリフト領域150およびドレイン領域120が形成されている。さらに、半導体基板100上には、下地絶縁層320が形成されている。また、チャネル130上および下地絶縁層320上には、ゲート絶縁層200が形成されている。

【0121】

図14(a)のように、スパッタにより、ゲート絶縁層200上に金属膜を形成する。たとえば、金属膜として、Alおよび/またはTiNを成膜する。次いで、当該金属膜上にフォトレジスト層(不図示)を形成する。露光および現像により、平面視でチャネル領域130と重なる位置、および平面視で第1ドリフト領域140の一部と重なる位置に残存するように、フォトレジスト層をパターニングする。このフォトレジスト層をマスクとして、プラズマエッチングまたはウエットエッチングにより、金属膜をエッチングする。次いで、たとえば、アッシングによりフォトレジスト層を除去する。以上により、ゲート絶縁層200上に接するとともに、平面視でチャネル領域130と重なるように、ゲート電極400を形成する。また、ゲート電極400に接続するとともに、平面視で第1ドリフト領域140の一部と重なるように、第2フィールドプレート電極480を形成する。この場合のように、第2フィールドプレート電極480を、たとえばゲート電極400と一体として形成する。これにより、製造工程を簡略化することができる。

【0122】

次いで、図14(b)のように、たとえば、CVDにより、ゲート絶縁層200、ゲート電極400および第2フィールドプレート電極480上に、第1層間絶縁層520を形成する。さらに、ここでは、第1層間絶縁層520上に、たとえば、第1層間絶縁層520よりも高密度の材料からなる第2層間絶縁層540を形成する。第2層間絶縁層540として、たとえば、SiCN、SiC、SiON,SiCO、SiCONまたはSiNを成膜する。

【0123】

次いで、図15(a)のように、RIEにより、平面視でソース領域110に重なる位置に、第2層間絶縁層540、第1層間絶縁層520、ゲート絶縁層200および下地絶縁層320を貫通して半導体基板100の上面に接するソース開口部430を形成する。同時に、RIEにより、平面視でドレイン領域120に重なる位置に、第2層間絶縁層540、第1層間絶縁層520、ゲート絶縁層200および下地絶縁層320を貫通して半導体基板100の上面に接するドレイン開口部450を形成する。

【0124】

次いで、図15(b)のように、ソース開口部430並びにドレイン開口部450の側面並びに底面、および第2層間絶縁層540上に、たとえば、スパッタにより、金属を形成する。これにより、ソース開口部430およびドレイン開口部450の内部に、金属を埋め込む。具体的には、スパッタにより、Alおよび/またはTiNなどを成膜する。次いで、CMPにより、第2層間絶縁層540上の金属を平坦化する。次いで、当該金属上にフォトレジスト層(不図示)を形成する。露光および現像により、平面視でソース領域110と重なる位置、および平面視で第1ドリフト領域140および第2ドリフト領域150の一部と重なる位置に残存するように、フォトレジスト層をパターニングする。このフォトレジスト層をマスクとして、プラズマエッチングまたはウエットエッチングにより、金属をエッチングする。次いで、たとえば、アッシングによりフォトレジスト層を除去する。以上により、ソース開口部430に金属を埋め込むことにより、ソース領域110に接続するように、ソース電極440を形成する。また、第1フィールドプレート絶縁層300上に接し、平面視で第1ドリフト領域140と第2ドリフト領域150の一部と重なるように、第1フィールドプレート電極420を形成する。また、第1フィールドプレート電極420をソース電極440と接続するように形成する。この場合では、第1フィールドプレート電極420を、たとえば、ソース電極440と一体として形成する。これにより、製造工程を簡略化することができる。

【0125】

以降の工程は、第1の実施形態と同様である。

【0126】

第3の実施形態によれば、第1フィールドプレート電極420がソース電極440に接続している。この場合でも第1の実施形態と同様の効果を得ることができる。さらに第3の実施形態によれば、フィールドプレート電極が複数設けられている。ここでは、たとえば、ゲート電極400に接続する第2フィールドプレート電極480、ソース電極440に接続する第1フィールドプレート電極420が設けられている。これにより、さらに効率的に、半導体装置10内の電界集中を緩和することができる。

【0127】

以上、第3の実施形態では、フィールドプレート電極が二つ設けられている場合について説明したが、フィールドプレート電極はさらに多段に設けられていてもよい。また、さらに、第2の実施形態のように、第3ドリフト領域160等の複数のドリフト領域が設けられていてもよい。

【0128】

また、第3の実施形態では、第2フィールドプレート電極480が設けられている場合について説明したが、第2フィールドプレート電極480は無くてもよい。その場合、下地絶縁層320は無くてもよい。この場合でも、第4の実施形態と同様の効果を得ることができる。

【0129】

(第4の実施形態)

図16は、第4の実施形態に係る半導体装置10の構成を示す断面図である。第4の実施形態は、第1フィールドプレート電極420が第2フィールドプレート電極480上に接している点を除いて、第1の実施形態、または第3の実施形態の一部と同様である。

【0130】

図16のように、第1の実施形態と同様にして、III族窒化物半導体層104には、ソース領域110、チャネル領域130、第1ドリフト領域140、第2ドリフト領域150およびドレイン領域120が形成されている。

【0131】

下地絶縁層320は、半導体基板100上に接して設けられており、平面視でチャネル領域130と重なる領域に開口部を有している。また、ゲート絶縁層200は、下地絶縁層320の開口部に露出したチャネル領域130上、および下地絶縁層320上に設けられている。ゲート電極400は、ゲート絶縁層200上に接し、平面視でチャネル領域130に重なるように設けられている。

【0132】

また、第2フィールドプレート電極480は、第2の実施形態と同様に、ゲート電極400に接続している。第2フィールドプレート電極480は、平面視で第1ドリフト領域140の一部と重なるように設けられている。

【0133】

第1層間絶縁層520は、半導体基板100上に設けられ、ゲート電極400および第2フィールドプレート電極480の上面と同一面を形成するように設けられている。

【0134】

第1フィールドプレート絶縁層300は、第1層間絶縁層520の一部を含んでいる。第4の実施形態では、第1フィールドプレート絶縁層300は、下地絶縁層320、ゲート絶縁層200および第1層間絶縁層520が積層されることにより形成されている。

【0135】

第1フィールドプレート電極420は、第1フィールドプレート絶縁層300のうち、第1層間絶縁層520上および第2フィールドプレート電極480上に接している。なお、第1フィールドプレート電極420は、平面視で第1ドリフト領域140と第2ドリフト領域150の一部と重なるように設けられている。この場合では、第1フィールドプレート電極420は、ゲート電極400と異なる材料で形成されていてもよい。

【0136】

さらに、当該半導体装置10のうち、それぞれの構成は、上述の式(1)を満たすように形成されている。第1フィールドプレート絶縁層300の電気的膜厚tFP*は、式(5)、式(6)および式(7)から下地絶縁層320、ゲート絶縁層200および第1層間絶縁層520の誘電率と物理的膜厚との積の総和により求めることができる。

【0137】

次に、図17〜図19を用い、第4の実施形態に係る半導体装置10の製造方法について説明する。図17〜図19は、第4の実施形態に係る半導体装置10の製造方法を説明するための断面図である。第4の実施形態に係る半導体装置10の製造方法は、第1フィールドプレート電極420を第2フィールドプレート電極480上に接するように形成する点を除いて、第1の実施形態または第2の実施形態の一部と同様である。以下、詳細を説明する。

【0138】

第2の実施形態と同様にして、図14(a)までの工程を行う。ゲート絶縁層200上には、平面視でチャネル領域130と重なるように、ゲート電極400が形成されている。また、ゲート電極400に接続するとともに、平面視で第1ドリフト領域140の一部と重なるように、第2フィールドプレート電極480が形成されている。

【0139】

次いで、図17(a)のように、たとえば、CVDにより、ゲート絶縁層200、ゲート電極400および第2フィールドプレート電極480上に、第1層間絶縁層520を形成する。

【0140】

次いで、図17(b)のように、CMPにより、ゲート電極400および第2フィールドプレート電極480の上面と同一面を形成するように、第1層間絶縁層520を平坦化する(平坦化工程)。

【0141】

次いで、図18(a)のように、たとえば、スパッタにより、ゲート電極400および第2フィールドプレート電極480上に、金属膜を形成する。当該金属膜として、たとえば、Alおよび/またはTiNなどを成膜する。次いで、金属膜上にフォトレジスト層(不図示)を形成する。露光および現像により、平面視で少なくとも第1ドリフト領域140と第2ドリフト領域150の一部と重なる領域に残存するように、フォトレジスト層をパターニングする。次いで、たとえば、アッシングによりフォトレジスト層を除去する。以上により、第1フィールドプレート絶縁層300のうち、第1層間絶縁層520上および第2フィールドプレート電極480上に接するように、第1フィールドプレート電極420を形成する。また、少なくとも平面視で第1ドリフト領域140と第2ドリフト領域150の一部と重なるように、第1フィールドプレート電極420を形成する。

【0142】

次いで、図18(b)のように、たとえば、CVDにより、第1層間絶縁層520上、および第1フィールドプレート電極420上を覆うように、第2層間絶縁層540を形成する。

【0143】

次いで、図19(a)のように、RIEにより、平面視でソース領域110に重なる位置に、第2層間絶縁層540、第1層間絶縁層520、ゲート絶縁層200および下地絶縁層320を貫通して、半導体基板100の上面に接するソース開口部430を形成する。同時に、RIEにより、平面視でドレイン領域120に重なる位置に、第2層間絶縁層540、第1層間絶縁層520、ゲート絶縁層200および下地絶縁層320を貫通して、半導体基板100の上面に接するドレイン開口部450を形成する。

【0144】

次いで、図19(b)のように、たとえば、スパッタにより、ソース開口部430並びにドレイン開口部450の側面並びに底面および第2層間絶縁層540上に、金属を形成する。これにより、ソース開口部430およびドレイン開口部450の内部に、金属を埋め込む。具体的には、具体的には、スパッタにより、Alおよび/またはTiNなどを成膜する。

【0145】

以降の工程は第1の実施形態と同様である。

【0146】

第4の実施形態によれば、第1の実施形態と同様の効果を得ることができる。さらに、第4の実施形態によれば、第1フィールドプレート電極420がゲート電極400および第2フィールドプレート電極480上に接している。これにより、さらに効率的に、半導体装置10内の電界集中を緩和することができる。

【0147】

以上、第4の実施形態では、フィールドプレート電極が二つ設けられている場合について説明したが、フィールドプレート電極はさらに多段に積層して設けられていてもよい。また、さらに、第2の実施形態のように、第3ドリフト領域160等の複数のが設けられていてもよい。

【0148】

以上、第1から4の実施形態において、ソース電極440およびドレイン電極460をスパッタにより形成したが、これに限定されるものではない。ソース電極440およびドレイン電極460をダマシン法によってCuを埋め込むことにより形成してもよい。その他、ソース電極440およびドレイン電極460をCVDによってWを埋め込むことにより形成してもよい。

【0149】

(第5の実施形態)

図20は、第5の実施形態に係る半導体装置10の構成を示す断面図である。第5の実施形態は、半導体基板100がSi基板である点を除いて、第1の実施形態と同様である。

【0150】

図20のように、第5の実施形態のうち、断面視での構造は、第1の実施形態と同様である。

【0151】

第5の実施形態では、半導体基板100は、たとえば、Si基板である。第1の実施形態と異なり、半導体基板100に、材質の異なる半導体層は形成されていない。すなわち、半導体基板100の表面近傍に、直接、横型MOSFETが形成されている。

【0152】

また、第1導電型がn型であり、半導体装置10がnチャネルFETを含む場合は、半導体基板100は、たとえば、p型Si基板である。一方、第1導電型がp型であり、半導体装置10がpチャネルFETを含む場合は、半導体基板100はn型Si基板であってもよい。

【0153】

また、ソース領域110およびドレイン領域120の下方に、これらと逆の導電型のハロー領域(不図示)がさらに形成されていてもよい。

【0154】

ゲート電極400、ソース電極440およびドレイン電極460は、第1の実施形態と同様に、たとえば、スパッタにより、Alおよび/またはTiNなどによって形成されていてもよい。または、これらの電極は、ダマシン法によってCuを埋め込むことにより形成されていてもよい。また、これらの電極は、CVDによってWを埋め込むことにより形成してもよい。

【0155】

第5の実施形態によれば、第1の実施形態と同様の効果を得ることができる。さらに第5の実施形態によれば、半導体基板100はSi基板である。これにより、半導体基板100のコストを低減し、安価に半導体装置10を提供することができる。また、制御用ICを同一チップ上に作り込むことができる。これにより、より広い範囲の製品形態に半導体装置10を適用することができる。また、半導体基板100に含まれる欠陥を低減して、基板耐圧を向上させた半導体装置10を提供することができる。

【0156】

(第6の実施形態)

図21は、第6の実施形態に係る半導体装置10の構成を示す断面図である。第6の実施形態は、ゲート絶縁層200上に下地絶縁層320が設けられている点を除いて、第1の実施形態、または第5の実施形態と同様である。

【0157】

第6の実施形態では、半導体基板100は、たとえば、Si基板である。半導体基板100には、ソース領域110、チャネル領域130、第1ドリフト領域140、第2ドリフト領域150およびドレイン領域120が形成されている。

【0158】

ゲート絶縁層200は、半導体基板100に接して設けられている。下地絶縁層320は、ゲート絶縁層200上に設けられている。したがって、第1フィールドプレート絶縁層300は、ゲート絶縁層200および下地絶縁層320の順で積層されることにより形成されている。また、第1フィールドプレート電極420は、第1フィールドプレート絶縁層300のうち下地絶縁層320の上面に接して設けられている。

【0159】

また、ゲート絶縁層200は、下地絶縁層320に対してエッチング選択性を有する材料により形成されている。具体的には、下地絶縁層320がたとえばSiO2により形成されている場合に、ゲート絶縁層200はたとえばSiNにより形成されている。

【0160】

次に、第6の実施形態に係る半導体装置10の製造方法について概略を説明する。第6の実施形態に係る半導体装置10の製造方法は、以下の点を除いて、第1の実施形態と同様である。

【0161】

第1の実施形態と同様にして、図5(a)から図6(b)までを行う。このとき、保護層240は無くてもよい。次いで、保護層240を形成した場合はこれを除去する。または、保護層240がゲート絶縁層200であってもよい。

【0162】

次いで、半導体基板100上の全面にゲート絶縁層200を形成する。次いで、ゲート絶縁層200上に、下地絶縁層320を形成する。次いで、RIEにより、下地絶縁層320にチャネル開口部210を形成する。

【0163】

以降の工程は、第1の実施形態と同様である。

【0164】

第6の実施形態によれば、第1の実施形態または第5の実施形態と同様の効果を得ることができる。さらに第6の実施形態のように、半導体基板100の材質に応じて、ゲート絶縁層200を下地絶縁層320よりも先に形成することもできる。

【0165】

以上、第5および第6の実施形態において、半導体基板100がSi基板である場合を説明したが、この場合において第1〜第4の実施形態の構成を適用してもよい。

【0166】

以上、図面を参照して本発明の実施形態について述べたが、これらは本発明の例示であり、上記以外の様々な構成を採用することもできる。

【符号の説明】

【0167】

10 半導体装置

100 半導体基板

102 下地基板

104 III族窒化物半導体層

110 ソース領域

120 ドレイン領域

130 チャネル領域

140 第1ドリフト領域

150 第2ドリフト領域

160 第3ドリフト領域

200 ゲート絶縁層

210 チャネル開口部

240 保護層

300 第1フィールドプレート絶縁層

320 下地絶縁層

400 ゲート電極

420 第1フィールドプレート絶縁層

430 ソース開口部

440 ソース電極

450 ドレイン開口部

460 ドレイン電極

480 第2フィールドプレート絶縁層

520 第1層間絶縁層

540 第2層間絶縁層

600 フォトレジスト層

A 比較例

B 比較例

C 比較例

【特許請求の範囲】

【請求項1】

半導体基板と、

前記半導体基板に設けられた第1導電型のソース領域と、

前記半導体基板に設けられ、平面視で前記ソース領域から離間して設けられた第1導電型の第1ドリフト領域と、

前記半導体基板のうち、平面視で前記ソース領域および前記第1ドリフト領域に挟まれた領域であるチャネル領域と、

前記半導体基板に設けられ、平面視で前記第1ドリフト領域のうち前記ソース領域と反対側の領域に接している第1導電型の第2ドリフト領域と、

前記半導体基板に設けられ、平面視で前記第1ドリフト領域から離間するとともに、平面視で前記第2ドリフト領域のうち前記第1ドリフト領域と反対側の領域に接しており、前記第1ドリフト領域および前記第2ドリフト領域よりも不純物濃度が高い第1導電型のドレイン領域と、

前記チャネル領域上に設けられたゲート絶縁層と、

前記ゲート絶縁層上に接し、平面視で前記チャネル領域と重なるように設けられたゲート電極と、

前記半導体基板上に設けられ、少なくとも平面視で前記第1ドリフト領域と前記第2ドリフト領域の一部と重なるように設けられ、前記ゲート絶縁層よりも厚い第1フィールドプレート絶縁層と、

前記第1フィールド絶縁層上に接し、平面視で前記第1ドリフト領域と前記第2ドリフト領域の一部と重なるように設けられた第1フィールドプレート電極と、

を備え、

前記第1ドリフト領域の深さをσ1、前記第1ドリフト領域の不純物濃度をN1、前記第2ドリフト領域の深さをσ2、前記第2ドリフト領域の不純物濃度をN2としたとき、下記式(1)を満たす半導体装置。

【数1】

(ただし、tOX*は前記ゲート絶縁層の電気的膜厚、tFP*は前記第1ドリフト領域と前記第2ドリフト領域との境界における前記第1フィールドプレート絶縁層の電気的膜厚である。なお、電気的膜厚は、誘電率と物理的膜厚との積である。)

【請求項2】

請求項1に記載の半導体装置において、

前記半導体基板は、主面側にIII族窒化物半導体層を備え、

前記ソース領域、前記チャネル領域、前記第1ドリフト領域、前記第2ドリフト領域および前記ドレイン領域は、当該III族窒化物半導体層に形成されている半導体装置。

【請求項3】

請求項2に記載の半導体装置において、

前記チャネル領域の不純物濃度は、1×10−16atoms/cm3以下である半導体装置。

【請求項4】

請求項2または3に記載の半導体装置において、

前記III族窒化物半導体層は、真性半導体である半導体装置。

【請求項5】

請求項2〜4のいずれか一項に記載の半導体装置において、

前記ソース領域、前記第1ドリフト領域、前記第2ドリフト領域および前記ドレイン領域は、n型であり、

当該n型の不純物は、Siである半導体装置。

【請求項6】

請求項5に記載の半導体装置において、

前記III族窒化物半導体層のうち、前記ソース領域および前記ドレイン領域の間に位置する部分には、p型の不純物領域が形成されていない半導体装置。

【請求項7】

請求項2〜6のいずれか一項に記載の半導体装置において、

前記半導体基板のうち、前記III族窒化物半導体層は、下地基板上に設けられ、

当該下地基板は、Si基板、サファイア基板、SiC基板またはGaN基板である半導体装置。

【請求項8】

請求項1に記載の半導体装置において、

前記半導体基板は、Si基板である半導体装置。

【請求項9】

請求項1〜8のいずれか一項に記載の半導体装置において、

N1<N2である半導体装置。

【請求項10】

請求項1〜8のいずれか一項に記載の半導体装置において、

N1>N2である半導体装置。

【請求項11】

請求項1〜10のいずれか一項に記載の半導体装置において、

前記第1フィールドプレート電極は、前記ゲート電極に接続し、前記ゲート電極と一体として形成されている半導体装置。

【請求項12】

請求項1〜10のいずれか一項に記載の半導体装置において、

少なくとも前記ゲート電極を覆うように設けられた第1層間絶縁層と、

前記ソース領域に接続するソース電極をさらに備え、

前記第1フィールドプレート絶縁層は、前記第1層間絶縁層の一部を含み、

前記第1フィールドプレート電極は前記ソース電極に接続している半導体装置。

【請求項13】

請求項12に記載の半導体装置において、

前記ゲート電極に接続するとともに、平面視で前記第1ドリフト領域の一部と重なるように設けられた第2フィールドプレート電極をさらに備え、

前記第1層間絶縁層は、少なくとも前記ゲート電極および前記第2フィールドプレート電極を覆うように設けられている半導体装置。

【請求項14】

請求項1〜10のいずれか一項に記載の半導体装置において、

前記ゲート電極に接続するとともに、平面視で前記第1ドリフト領域の一部と重なるように設けられた第2フィールドプレート電極と、

前記半導体基板上に設けられ、前記ゲート電極および前記第2フィールドプレート電極の上面と同一面を形成するように設けられた第1層間絶縁層と、

をさらに備え、

前記第1フィールドプレート絶縁層は、前記第1層間絶縁層の一部を含み、

前記第1フィールドプレート電極は、前記第1フィールドプレート絶縁層のうち、前記第1層間絶縁層上および前記第2フィールドプレート電極上に接している半導体装置。

【請求項15】

請求項1〜14に記載の半導体装置において、

前記半導体基板上に接し、平面視で前記チャネル領域と重なる領域に開口部を有する下地絶縁層をさらに備え、

前記ゲート絶縁層は、前記開口部に露出した前記半導体基板上、および前記下地絶縁層上に接して設けられ、

前記第1フィールドプレート絶縁層は、前記下地絶縁層の一部および前記ゲート絶縁層の一部を含む半導体装置。

【請求項16】