半導体装置および半導体装置の駆動方法

【課題】省電力化かつ高速での書き込み処理が可能なメモリの多値化に適した半導体装置およびベリファイ処理を提供する。

【解決手段】半導体装置に用いるメモリセルを、酸化物半導体を用いたトランジスタと酸化物半導体以外の材料を用いたトランジスタをそれぞれ有する構成とし、書き込み回路を用いてデータバッファのデータをメモリセルに書き込む前に、予め各々のメモリセルの有するしきい値ばらつきを調べ、データバッファのデータに対して当該しきい値ばらつきを補正したデータが各々のメモリセルに書き込む。

【解決手段】半導体装置に用いるメモリセルを、酸化物半導体を用いたトランジスタと酸化物半導体以外の材料を用いたトランジスタをそれぞれ有する構成とし、書き込み回路を用いてデータバッファのデータをメモリセルに書き込む前に、予め各々のメモリセルの有するしきい値ばらつきを調べ、データバッファのデータに対して当該しきい値ばらつきを補正したデータが各々のメモリセルに書き込む。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体素子を利用した半導体装置およびその駆動方法に関するものである。

【背景技術】

【0002】

半導体素子を利用した記憶装置は、電力の供給がなくなると記憶内容が失われる揮発性のものと、電力の供給がなくなっても記憶内容は保持される不揮発性のものとに大別される。

【0003】

揮発性記憶装置の代表的な例としては、DRAM(Dynamic Random Access Memory)がある。DRAMは、記憶素子を構成するトランジスタを選択してキャパシタに電荷を蓄積することで、情報を記憶する。

【0004】

上述の原理から、DRAMでは、情報を読み出すとキャパシタの電荷は失われるため、情報の読み出しの度に、再度の書き込み動作が必要となる。また、記憶素子を構成するトランジスタにおいてはオフ状態でのソースとドレイン間のリーク電流(オフ電流)等によって、トランジスタが選択されていない状況でも電荷が流出、または流入するため、データの保持期間が短い。このため、所定の周期で再度の書き込み動作(リフレッシュ動作)が必要であり、消費電力を十分に低減することは困難である。また、電力の供給がなくなると記憶内容が失われるため、長期間の記憶の保持には、磁性材料や光学材料を利用した別の記憶装置が必要となる。

【0005】

揮発性記憶装置の別の例としてはSRAM(Static Random Access Memory)がある。SRAMは、フリップフロップなどの回路を用いて記憶内容を保持するため、リフレッシュ動作が不要であり、この点においてはDRAMより有利である。しかし、フリップフロップなどの回路を用いているため、記憶容量あたりの単価が高くなるという問題がある。また、電力の供給がなくなると記憶内容が失われるという点については、DRAMと変わるところはない。

【0006】

不揮発性記憶装置の代表例としては、フラッシュメモリがある。フラッシュメモリは、トランジスタのゲート電極とチャネル形成領域との間にフローティングゲートを有し、当該フローティングゲートに電荷を保持させることで記憶を行うため、データの保持期間は極めて長く(半永久的)、揮発性記憶装置で必要なリフレッシュ動作が不要であるという利点を有している(例えば、特許文献1参照)。

【0007】

しかし、書き込みの際に生じるトンネル電流によって記憶素子を構成するゲート絶縁層が劣化するため、所定回数の書き込みによって記憶素子が機能しなくなるという問題が生じる。この問題の影響を緩和するために、例えば、各記憶素子の書き込み回数を均一化する手法が採られるが、これを実現するためには、複雑な周辺回路が必要になってしまう。そして、このような手法を採用しても、根本的な寿命の問題が解消するわけではない。つまり、フラッシュメモリは、情報の書き換え頻度が高い用途には不向きである。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特開昭57−105889号公報

【発明の概要】

【発明が解決しようとする課題】

【0009】

フラッシュメモリでは通常、誤ったデータがメモリセルに書き込まれないように、メモリセルに書き込んだデータを一度読み出して正誤判定を行い、書き込みデータと読み出しデータが異なっていた場合は、書き込み電圧を変更して再度データを書き込むベリファイ処理という機能がある。

【0010】

ベリファイ処理は通常、m行×n列のメモリセルにデータを書き込む場合、図3(A)に示すフロー図のように、まず、いずれか1行のメモリセルに対してデータ(メモリセルに保持させたいデータ)の書き込み処理を行い、書き込み後にメモリセルから読み出し(ベリファイ読み出し)を行い、1行全てのメモリセルに正常にデータが書き込めたか否かを判定し、正常にデータが書き込めていないメモリセルが1つでも存在する場合には、該当するメモリセルの書き込みデータ電位を変更したうえで、再度1行全てのメモリセルにデータの書き込みを行う。この処理を繰り返して最終的に1行全てのメモリセルに正常にデータが書き込まれた時点で書き込み処理が終了となる。

【0011】

このため、ベリファイ処理およびデータの書き込みを複数回行う必要があり、特にそれぞれのメモリセルのしきい値電圧のばらつきが大きい場合は、読み込み処理および書き込み処理の回数が非常に多くなる。また、メモリセルを構成するトランジスタにシリコン等の半導体材料を用いる場合、トランジスタはフローティングゲートを有する構造に形成されるが、書き込み処理を行う毎にメモリセルのデータを消去する必要がある。

【0012】

上述の問題に加え、メモリセルを構成するトランジスタのしきい値電圧にばらつきがあると、当該トランジスタのしきい値電圧のばらつきに起因して、複数のメモリセルそれぞれを動作するために必要な電位(メモリセルのしきい値電圧ともいう)にもばらつきが生じる。メモリセルの動作電圧を決定する際、このメモリセルのしきい値電圧のばらつきを考慮しないと、動作エラーが生じるおそれがあった。そのため複数のメモリセルそれぞれの動作電圧は、メモリセルのしきい値電圧のばらつきを考慮して幅をもたせて設定される。そのためメモリセルの動作電圧の低減には限界があった。

【0013】

また、メモリセルを多値化する場合にも動作電圧は増大するので、動作電圧を増大させず、かつ、メモリセルの面積を増大させずに記憶容量を増大することは難しかった。

【0014】

上記の問題を鑑み、本明細書では、省電力化かつ高速での書き込み処理が可能な半導体装置およびその駆動方法を提供することを目的の一とする。さらには、メモリセルの多値化に適した半導体装置およびその駆動方法を提供することを目的の一とする。

【課題を解決するための手段】

【0015】

上記問題を解決するため、オフ電流の低いトランジスタを含むメモリセルを備えた半導体装置の構成とした。なお、オフ電流の低いトランジスタとは、バンドギャップの広い半導体(例えばバンドギャップが2eV以上、好ましくは3eV以上の半導体)、具体的には酸化物半導体を用いて構成される。

【0016】

オフ電流の低いトランジスタの一例としては、例えば半導体層として酸化物半導体を用いたトランジスタを挙げることができる。酸化物半導体はバンドギャップが3.0eV以上であり、シリコンのバンドギャップ(1.1eV)と比較して非常に大きい。

【0017】

トランジスタのオフ抵抗(トランジスタがオフ状態の時における、ソースとドレイン間の抵抗をいう。)は、チャネルが形成される半導体層における熱的に励起するキャリアの濃度に反比例する。ドナーやアクセプタによるキャリアが全く存在しない状態(真性半導体)であっても、シリコンの場合にはバンドギャップが1.1eVであるため、室温(300K)での熱励起キャリアの濃度は1×1011cm−3程度である。

【0018】

一方、例えばバンドギャップが3.2eVの半導体(酸化物半導体を想定。)の場合では熱励起キャリアの濃度は1×10−7cm−3程度となる。電子移動度が同じ場合、抵抗率は、キャリア濃度に反比例するので、バンドギャップ3.2eVの半導体の抵抗率は、シリコンより18桁も大きい。

【0019】

このようなバンドギャップの広い酸化物半導体を半導体層に適用したトランジスタ(OSトランジスタ)は、極めて低いオフ電流を実現できる。

【0020】

酸化物半導体は、このワイドギャップ半導体の一種であり、少なくともIn、Ga、Sn及びZnから選ばれた一種以上の元素を含有するもの、例えば、In−Sn−Ga−Zn−O系酸化物半導体、In−Ga−Zn−O系酸化物半導体、In−Sn−Zn−O系酸化物半導体などを用いることが好ましい。

【0021】

前述の酸化物半導体を用いて形成した酸化物半導体膜は、単結晶、多結晶(ポリクリスタルともいう。)または非晶質などの状態をとる。なお、好ましくは、酸化物半導体膜は、CAAC−OS(C Axis Aligned Crystalline Oxide Semiconductor)膜とする。CAAC−OSの構造等についての具体的な内容は、実施の形態6にて詳細を説明する。

【0022】

また、ベリファイ機能を図3(B)に示すフロー図のように、まず、いずれか1行のメモリセルに対して任意の電位(以下、基準電位と略記する)の書き込み処理を行い、各々のメモリセルにおいて、メモリセルの有するしきい値電圧ばらつきを、基準電位を用いて導出して、メモリセルに書き込むデータ(メモリセルに保持させたいデータ)に対してしきい値電圧ばらつきの補正を行い、その後、1行全てのメモリセルにしきい値電圧ばらつきの補正されたデータを書き込むフローとした。

【0023】

開示する発明の一態様は、ビット線からの電位の入力制御およびビット線への電位の出力制御を行う第1のトランジスタと、ワード線の電位に基づいてビット線への電位の出力制御を行い、ゲート電極に加わる電位に基づいて第1の電位または第2の電位を出力する第2のトランジスタと、ゲート電極に加わるワード線からの電位を調整する容量素子と、を備えるメモリセルと、メモリセルに書き込むデータを保持するデータバッファと、基準電位および各々が異なる複数の書き込みデータ電位を生成する電位生成回路と、周期が一定のコントロール信号を出力するコントロール信号生成回路と、複数の書き込みデータ電位のうちのいずれか一または基準電位をメモリセルに書き込む書き込み回路と、メモリセルの書き込みデータ電位を読み出す読み出し回路と、第1の電位または第2の電位の入力に基づいてコントロール信号の出力制御を行うスイッチング素子を有し、第1のトランジスタは、チャネル領域に酸化物半導体を用い、第2のトランジスタは、チャネル領域にシリコン、ゲルマニウム、シリコンゲルマニウム、炭化シリコンまたはガリウム砒素のいずれかを用い、第2のトランジスタは、ゲート電極に加わる電位がしきい値に達するまで第1の電位を出力し、ゲート電極に加わる電位がしきい値に達した時点で第2の電位を出力し、ワード線は、コントロール信号の出力に基づいて電気信号が変化し、書き込み回路は、データバッファからのデータ入力前において基準電位をメモリセルに書き込み、データバッファからのデータ入力後においてコントロール信号の入力に基づいて複数の書き込みデータ電位のうちのいずれか一を選択し、スイッチング素子がオフ状態になった時点で選択されている書き込みデータ電位をメモリセルに書き込み、スイッチング素子は、第1の電位が入力されている期間において書き込み回路へのコントロール信号の出力を許容し、第2の電位が入力された時点で書き込み回路へのコントロール信号の出力を遮断する半導体装置。

【0024】

なお、本明細書において、「半導体層としてシリコン、ゲルマニウム、シリコンゲルマニウム、炭化シリコン、ガリウム砒素または有機半導体材料のいずれかを用いたトランジスタ」のことを、文章の簡略化および理解の容易を図るために「酸化物半導体以外の材料を用いたトランジスタ」と略記することがある。

【0025】

上記構成において、コントロール信号生成回路は、基準電位がメモリセルに書き込まれた後から、スイッチング素子からのコントロール信号の出力が停止するまでの間、コントロール信号を生成する。つまり、これ以外の期間においては、コントロール信号の周期が一定でない、または、コントロール信号の生成が停止していてもよい。

【0026】

上記構成において、電位生成回路で生成される複数の書き込みデータ電位の大きさはそれぞれ異なっている。電位生成回路で生成される大きさの異なる複数の書き込みデータ電位のそれぞれが、複数の第1の信号線のいずれかに供給され、書き込み回路に供給される。電位生成回路で生成される複数の書き込みデータ電位には、同じデータを書き込む複数の電位が含まれている。

【0027】

上記構成において、複数のメモリセルのそれぞれにおいて、第1のトランジスタのソースまたはドレインの一方は、第2のトランジスタのゲートに電気的に接続されている。

【0028】

上記構成において、書き込み回路は複数のメモリセルがそれぞれ有する第1のトランジスタのソースまたはドレインの他方に電気的に接続され、読み出し回路は複数のメモリセルがそれぞれ有する第2のトランジスタのソースまたはドレインの一方に電気的に接続されている。

【0029】

上記構成において、複数のメモリセルのしきい値電圧は、ばらつき(分布幅)を有する場合がある。その場合、しきい値電圧が最小(Vth_min)であるメモリセルとしきい値電圧が最大(Vth_max)であるメモリセルとでは、メモリセルに書き込まれる電位が異なる場合がある。

【0030】

しきい値電圧が最小(Vth_min)であるメモリセルへの書き込みデータ電位として決定される電位は、電位生成回路にて生成される複数の書き込みデータ電位のなかで、同じデータを書き込む複数の書き込みデータ電位のうち最小の電位の大きさであることが好ましい。また、しきい値電圧が最大(Vth_max)であるメモリセルへの書き込みデータ電位として決定される電位は、電位生成回路にて生成される複数の書き込みデータ電位のなかで、同じデータを書き込む複数の書き込みデータ電位のうち最大の電位の大きさであることが好ましい。

【0031】

逆に言うと、電位生成回路にて生成される複数の書き込みデータ電位のなかで、同じデータを書き込む複数の書き込みデータ電位のうち最小の電位は、しきい値電圧が最小(Vth_min)であるメモリセルへの書き込みデータ電位として決定される電位の大きさであることが好ましい。また、電位生成回路にて生成される複数の書き込みデータ電位のなかで、同じデータを書き込む複数の書き込みデータ電位のうち最大の電位は、しきい値電圧が最大(Vth_max)であるメモリセルへの書き込みデータ電位として決定される電位の大きさであることが好ましい。

【0032】

上記構成において、第2のトランジスタは、シリコン、ゲルマニウム、シリコンゲルマニウム、炭化シリコン、ガリウム砒素または有機半導体材料のいずれかを含む基板に設けられたチャネル形成領域を有することが好ましい。

【0033】

なお、前述の基板は、単結晶半導体基板またはSOI基板とすることが好ましい。また、前述の基板の半導体材料はシリコンであることが好ましい。また、酸化物半導体は、In、Ga、Sn及びZnから選ばれた一種以上の元素を含んでなる酸化物半導体材料を有することが好ましい。

【0034】

なお、上記において、酸化物半導体を用いてトランジスタを構成する場合を示したが、開示する発明はこれに限定されない。酸化物半導体と同等のオフ電流特性が実現できる材料、例えば、炭化シリコンをはじめとするワイドギャップ材料(より具体的には、例えば、エネルギーギャップEgが3eVより大きい半導体材料)などを適用しても良い。

【0035】

また、開示する発明の一態様は、チャネル領域に酸化物半導体を用いた第1のトランジスタおよびチャネル領域にシリコン、ゲルマニウム、シリコンゲルマニウム、炭化シリコン、ガリウム砒素または有機半導体材料のいずれかを用いた第2のトランジスタをそれぞれ有し、第1のトランジスタのソースまたはドレインの一方が、第2のトランジスタのゲートに電気的に接続されている複数のメモリセルと、データバッファ、書き込み回路、読み出し回路、コントロール信号生成回路およびスイッチング素子を有する駆動回路と、基準電位および複数の書き込みデータ電位を生成する電位生成回路を備え、コントロール信号生成回路で生成されたコントロール信号がスイッチング素子に一定の周期で断続的に出力される半導体装置において、第2のトランジスタのゲート電極に基準電位を加え、第1のトランジスタをオフ状態とすることにより電位生成回路の基準電位を複数のメモリセルに書き込んだ後、データバッファに保持されたデータを書き込み回路に入力して、電位生成回路で生成される複数の書き込みデータ電位のうちいずれか一の電位をメモリセルへの書き込みデータ電位として選択し、基準電位が複数のメモリセルに書き込まれた後に、コントロール信号の生成に基づいて、第2のトランジスタのためのワード線の電気信号が変化することで、第2のトランジスタのゲート電極に加わる電位が変化する動作、および、スイッチング素子を介して入力されるコントロール信号の入力に基づいて、書き込み回路にて選択されている書き込みデータ電位が一の電位とは別の電位に変化する動作を繰り返し行い、第2のトランジスタのゲート電極に加わる電位が第2のトランジスタのしきい値電圧に達した時点でスイッチング素子が停止し、第2のトランジスタのゲート電極に加わる電位の変化、および、書き込み回路にて選択される書き込みデータ電位の変化が停止し、スイッチング素子の停止時点において、書き込み回路にて選択されている書き込みデータ電位が、メモリセルに書き込まれる半導体装置の駆動方法である。

【発明の効果】

【0036】

開示する発明に係る半導体装置では、酸化物半導体を用いたトランジスタのオフ電流が極めて小さいため、これを用いることにより長期にわたり記憶内容を保持することが可能である。つまり、リフレッシュ動作が不要となるか、または、リフレッシュ動作の頻度を極めて低くすることが可能となるため、消費電力を十分に低減することができる。また、電力の供給がない場合であっても、長期にわたって記憶内容を保持することが可能である。

【0037】

また、開示する発明に係る半導体装置では、メモリセルを構成するトランジスタのしきい値電圧にばらつきがあっても、書き込み後の複数のメモリセルのしきい値電圧のばらつき(分布幅)を小さくすることができ、半導体装置の動作電圧を低減することができる。または、動作電圧を増大させずかつメモリセルの面積を増大させずに、メモリを多値化することができ、半導体装置の単位面積あたりの記憶容量を増大することができる。または、書き込み、保持、読み出し等の動作を確実に行い、かつ、書き込みを高速化させて行える半導体装置を提供することができる。

【0038】

また、開示する発明に係る半導体装置では、情報の書き込みに高い電圧を必要とせず、素子の劣化の問題もない。例えば、従来の不揮発性メモリのように、フローティングゲートへの電子の注入や、フローティングゲートからの電子の引き抜きを行う必要がないため、ゲート絶縁層の劣化といった問題が全く生じない。すなわち、開示する発明に係る半導体装置では、従来の不揮発性メモリで問題となっている書き換え可能回数に制限はなく、信頼性が飛躍的に向上する。さらに、トランジスタのオン状態、オフ状態によって、情報の書き込みが行われるため、高速な動作も容易に実現しうる。また、情報を消去するための動作が不要であるというメリットもある。

【0039】

また、酸化物半導体以外の材料を用いたトランジスタは、十分な高速動作が可能であるため、これを、酸化物半導体を用いたトランジスタと組み合わせて用いることにより、半導体装置の動作(例えば、情報の読み出し動作)の高速性を十分に確保することができる。また、酸化物半導体以外の材料を用いたトランジスタにより、高速動作が要求される各種回路(論理回路、駆動回路など)を好適に実現することが可能である。

【0040】

また、開示する発明に係る半導体装置では、あらかじめ基準電位をメモリセルへの書き込み、ベリファイ処理を行うことで書き込みデータ電位を決定し、その後所望のデータを書き込むことで書き込み処理を高速化することができる。

【図面の簡単な説明】

【0041】

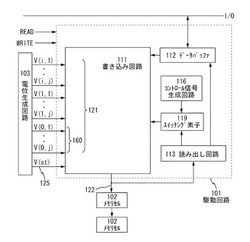

【図1】半導体装置のブロック図。

【図2】ベリファイ処理を説明する図。

【図3】本発明および従来のベリファイ処理のフローチャート。

【図4】半導体装置が有するメモリセルのしきい値電圧の分布を示す図。

【図5】半導体装置の回路図。

【図6】半導体装置が有するデータバッファの回路図。

【図7】半導体装置が有する電位生成回路の回路図。

【図8】半導体装置が有する電位生成回路の回路図。

【図9】半導体装置が有する書き込み回路の回路図。

【図10】半導体装置が有する書き込み回路の回路図。

【図11】半導体装置が有するメモリセルの回路図。

【図12】半導体装置が有する読み出し回路の回路図。

【図13】半導体装置が有する書き込みのタイミングチャート。

【図14】半導体装置が有する読み出しのタイミングチャート。

【図15】半導体装置が有するメモリセルの回路図。

【図16】半導体装置の回路図。

【図17】半導体装置が有するメモリセルの断面図および平面図。

【図18】半導体装置の作製工程を示す断面図。

【図19】半導体装置の作製工程を示す断面図。

【図20】半導体装置の作製工程を示す断面図。

【図21】半導体装置の作製工程を示す断面図。

【図22】半導体装置の作製工程を示す断面図。

【図23】半導体装置を用いた電子機器。

【図24】酸化物材料の構造を説明する図。

【図25】酸化物材料の構造を説明する図。

【図26】酸化物材料の構造を説明する図。

【図27】酸化物半導体を用いたトランジスタの特性を示す図。

【図28】酸化物半導体を用いたトランジスタの特性評価用回路図。

【図29】酸化物半導体を用いたトランジスタの特性評価用タイミングチャート。

【図30】酸化物半導体を用いたトランジスタの特性を示す図。

【図31】酸化物半導体を用いたトランジスタの特性を示す図。

【図32】酸化物半導体を用いたトランジスタの特性を示す図。

【発明を実施するための形態】

【0042】

開示する発明の実施の形態の一例について、図面を用いて以下に説明する。但し、本発明は以下の説明に限定されず、本発明の趣旨およびその範囲から逸脱することなくその形態および詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。

【0043】

なお、図面等において示す各構成の、位置、大きさ、範囲などは、理解の簡単のため、実際の位置、大きさ、範囲などを表していない場合がある。このため、開示する発明は、必ずしも、図面等に開示された位置、大きさ、範囲などに限定されない。

【0044】

なお、本明細書等における「第1」、「第2」、「第3」などの序数詞は、構成要素の混同を避けるために付すものであり、数的に限定するものではないことを付記する。

【0045】

(実施の形態1)

本実施の形態では、開示する発明の一態様に係る半導体装置の構成および動作について、図1乃至図4を参照して説明する。

【0046】

<半導体装置の構成についての説明>

図1は、メモリセルを有する半導体装置のブロック図の一例である。

【0047】

半導体装置は、駆動回路101と、複数のメモリセル102と、電位生成回路103と、を有する。また、半導体装置は、入出力信号(I/O)を与える配線(データ入出力線ともいう)、読み出し信号(READ)を与える配線、書き込み信号(WRITE)を与える配線を有する。

【0048】

駆動回路101は、書き込み回路111と、データバッファ112と、読み出し回路113と、コントロール信号生成回路116およびスイッチング素子119と、を有し、複数のメモリセル102を駆動する機能を備える。駆動回路101は、複数のメモリセル102の各列に設けられている。

【0049】

複数のメモリセル102はそれぞれ、酸化物半導体を用いた第1のトランジスタ(図2でのOSトランジスタ201に相当する)と、酸化物半導体以外の材料を用いた第2のトランジスタ(図2でのトランジスタ203に相当する)を有する。なお、複数のメモリセル102のそれぞれにおいて、酸化物半導体を用いた第1のトランジスタ(図2でのOSトランジスタ201に相当する)のソースまたはドレインの一方は、酸化物半導体以外の材料を用いた第2のトランジスタ(図2でのトランジスタ203に相当する)のゲートに電気的に接続されている構成とすることができる。なお、本明細書等に記載されている「酸化物半導体を用いたトランジスタ」とは、少なくともチャネル形成領域に酸化物半導体が用いられているトランジスタの事を表しており、また、「酸化物半導体以外の材料を用いたトランジスタ」とは、少なくともチャネル形成領域に酸化物半導体以外の半導体材料が用いられているトランジスタの事を表している。

【0050】

また、複数のメモリセル102のそれぞれにおいて、酸化物半導体以外の材料を用いた第1のトランジスタ(図2でのOSトランジスタ201に相当する)は、半導体材料を含む基板に設けられたチャネル形成領域を有することが好ましい。

【0051】

電位生成回路103は、i×j(iは2以上の整数、jは2以上の整数)本の書き込みデータ電位供給線(図1の第1の信号線121に相当する)および、1本の基準電位供給線(図1の第3の信号線125に相当する)に電気的に接続している。第1の信号線121である書込みデータ電位供給線は、複数の書き込みデータ電位を書き込み回路111に供給する。第3の信号線125である基準電位供給線は、基準電位V(st)を書き込み回路111に供給する。基準電位V(st)は酸化物半導体以外の材料を用いた第2のトランジスタがオン状態とならない電位であればどの電位でもよい。なお、iはメモリセル102に格納することができるデータ(値)の数であり、jは1つのデータに対して書き込むことのできる電位の種類となる。例えば、図1の範囲160で示される書き込みデータ電位供給線は、データ”0”を出力するために用いる配線であり、j種類の異なる電位を供給するためのj本の配線を有している。

【0052】

なお、電位生成回路103から書き込みデータ電位供給線である第1の信号線121に供給される複数の書き込みデータ電位(V(0,1)〜V(i,j))は、それぞれ異なる大きさである。

【0053】

書き込み回路111は、メモリセル102、データバッファ112、スイッチング素子119に電気的に接続されており、データバッファ112に保持されたデータが書き込み回路111に入力される前の状態において、電位生成回路103で生成される基準電位V(st)を、複数のメモリセル102のそれぞれに書き込む機能を有する。また、データバッファ112に保持されたデータが書き込み回路111に入力された後の状態において、書き込み回路111はデータバッファ112から入力されたデータ、および、スイッチング素子119を介してコントロール信号生成回路116から入力されるコントロール信号に基づいて、電位生成回路103で生成される複数の書き込みデータ電位のうちのいずれか一の電位(例えば、V(1,1))を選択する機能を有する。また、スイッチング素子119がオフ状態となった時点で選択されている書き込みデータ電位をメモリセルに書き込む機能を有する。

【0054】

データバッファ112は、書き込み回路111および読み出し回路113に電気的に接続されており、複数のメモリセル102のそれぞれに書き込むデータを保持する機能および、読み出し回路113により読み出したデータを保持する、または保持されたデータを外部(I/O線)に出力する機能を有する。

【0055】

読み出し回路113は、ビット線である第2の信号線122を介して複数のメモリセル102のそれぞれに電気的に接続されており、メモリセル102に書き込まれたデータを読み出す機能を有する。また、読み出し回路113は、メモリセル102から入力される電位信号(第1の電位または第2の電位)に基づいて、コントロール信号生成回路116にて生成されるコントロール信号を、書き込み回路111に入力するか否かの信号をスイッチング素子119に出力する機能を有する。また読み出し回路113は読み出したデータをデータバッファ112に出力する機能を有する。

【0056】

なお、第2の信号線122は、複数のメモリセル102がそれぞれ有する酸化物半導体を用いた第1のトランジスタ(図2でのOSトランジスタ201に相当する)のソースまたはドレインの他方に電気的に接続されている構成とすることができる。

【0057】

コントロール信号生成回路116は、スイッチング素子119と電気的に接続されており、周期が一定のコントロール信号を生成する機能を有する。また、コントロール信号生成回路116は、複数のメモリセル102のワード線WL(図示しない)の電位の変化と同期してコントロール信号を生成する機能を有する。なお、コントロール信号は、メモリセル102に基準電位V(st)が書き込まれた後から、スイッチング素子119からのコントロール信号の出力が停止するまでの期間において生成されればよく、それ以外の期間においては、周期が一定でない、または生成されない構成であってもよい。

【0058】

スイッチング素子119は、書き込み回路111、読み出し回路113およびコントロール信号生成回路116に電気的に接続されており、読み出し回路113からの電位信号(第1の電位または第2の電位)に応じて、コントロール信号生成回路116から入力されるコントロール信号を、書き込み回路111に出力するまたは停止する機能を有する。

【0059】

<半導体装置の動作についての説明>

まず、データバッファ112に保持されたデータが書き込み回路111に入力される前の状態において、電位生成回路103で生成された基準電位V(st)が、複数のメモリセル102に書き込まれる。該処理が行われると、データバッファ112に保持されているデータが書き込み回路111に入力され、電位生成回路103で生成された複数の書き込みデータ電位のうち、データバッファ112より入力されたデータに対応したいずれか一の電位が選択される。その後、メモリセル102に書き込まれた基準電位V(st)を用いてベリファイ処理が行われる。

【0060】

本実施の形態で行われるベリファイ処理を具体的に説明するため、複数のメモリセル102の1つで行われる動作について図2を用いて説明する。なお、図3は、ベリファイ処理を説明する簡単なフローチャートである。なお、本実施の形態等において、トランジスタ203はpチャネル型トランジスタとして説明を行うが、勿論これに限定されるものではない。

【0061】

図2に示すメモリセル102は、図1の第2の信号線122であるビット線BL(1)と酸化物半導体を用いた第1のトランジスタ(第2のトランジスタとの区別を容易にするため、以下では「OSトランジスタ」と略記する)であるOSトランジスタ201のドレイン電極が電気的に接続され、OSトランジスタ201のゲート電極とワード線WL_OS(1)が電気的に接続され、OSトランジスタ201のソース電極と酸化物半導体以外の材料を用いたトランジスタ203のゲート電極は、容量素子204の電極の一方と電気的に接続され、容量素子204の電極の他方はワード線WL(1)に電気的に接続される。また、ビット線BL(1)とトランジスタ203のドレイン電極が電気的に接続され、トランジスタ203のソース電極と信号線VSLが電気的に接続されて、1つのメモリセル102が構成される。なお、本明細書中の図面において、OSトランジスタは、オフ電流が極めて低いことを表現するために図2のOSトランジスタ201のように、一部を点線とした符号を用いる。なお、ここでは、OSトランジスタ201をnチャネル型のトランジスタ、トランジスタ203をpチャネル型のトランジスタとして、以下説明を行うが、勿論これに限定されることはない。

【0062】

ここで、OSトランジスタが有する「極めて低いオフ電流」を説明するため、以下に、高純度化された酸化物半導体を用いたトランジスタのオフ電流を求めた結果について説明する。

【0063】

<OSトランジスタのオフ電流測定>

まず、高純度化された酸化物半導体を用いたトランジスタのオフ電流が十分に小さいことを考慮して、チャネル幅Wが1mと十分に大きいトランジスタを用意してオフ電流の測定を行った。チャネル幅Wが1mのトランジスタのオフ電流を測定した結果を図27に示す。図27において、横軸はゲート電圧VG、縦軸はドレイン電流IDである。ドレイン電圧VDが+1Vまたは+10Vの場合、ゲート電圧VGが−5Vから−20Vの範囲では、トランジスタのオフ電流は、検出限界である1×10−12A以下であることがわかった。また、トランジスタのオフ電流(ここでは、単位チャネル幅(1μm)あたりの値)は1aA/μm(1×10−18A/μm)以下となることがわかった。

【0064】

次に、高純度化された酸化物半導体を用いたトランジスタのオフ電流をさらに正確に求めた結果について説明する。上述したように、高純度化された酸化物半導体を用いたトランジスタのオフ電流は、測定器の検出限界である1×10−12A以下であることがわかった。そこで、特性評価用素子を作製し、より正確なオフ電流の値(上記測定における測定器の検出限界以下の値)を求めた結果について説明する。

【0065】

はじめに、電流測定方法に用いた特性評価用素子について、図28を参照して説明する。

【0066】

図28に示す特性評価用素子は、測定系3300が3つ並列に接続されている。測定系3300は、容量素子3302、トランジスタ3304、トランジスタ3305、トランジスタ3306、トランジスタ3308を有する。トランジスタ3304、トランジスタ3305、トランジスタ3306、トランジスタ3308には、高純度化された酸化物半導体を用いたトランジスタを適用した。

【0067】

測定系3300において、トランジスタ3304のソース端子およびドレイン端子の一方と、容量素子3302の端子の一方と、トランジスタ3305のソース端子およびドレイン端子の一方は、電源(V2を与える電源)に電気的に接続されている。また、トランジスタ3304のソース端子およびドレイン端子の他方と、トランジスタ3308のソース端子およびドレイン端子の一方と、容量素子3302の端子の他方と、トランジスタ3305のゲート端子とは、電気的に接続されている。また、トランジスタ3308のソース端子およびドレイン端子の他方と、トランジスタ3306のソース端子およびドレイン端子の一方と、トランジスタ3306のゲート端子は、電源(V1を与える電源)に電気的に接続されている。また、トランジスタ3305のソース端子およびドレイン端子の他方と、トランジスタ3306のソース端子およびドレイン端子の他方とは、電気的に接続され、出力端子となっている。

【0068】

なお、トランジスタ3304のゲート端子には、トランジスタ3304のオン状態と、オフ状態を制御する電位Vext_b2が供給され、トランジスタ3308のゲート端子には、トランジスタ3308のオン状態と、オフ状態を制御する電位Vext_b1が供給される。また、出力端子からは電位Voutが出力される。

【0069】

次に、上記の特性評価用素子を用いた電流測定方法について説明する。

【0070】

まず、オフ電流を測定するために電位差を付与する初期期間の概略について説明する。初期期間においては、トランジスタ3308のゲート端子に、トランジスタ3308をオン状態とする電位Vext_b1を入力して、トランジスタ3304のソース端子またはドレイン端子の他方と電気的に接続されるノード(つまり、トランジスタ3308のソース端子およびドレイン端子の一方、容量素子3302の端子の他方、およびトランジスタ3305のゲート端子に電気的に接続されるノード)であるノードAに電位V1を与える。ここで、電位V1は、例えば高電位とする。また、トランジスタ3304はオフ状態としておく。

【0071】

その後、トランジスタ3308のゲート端子に、トランジスタ3308をオフ状態とする電位Vext_b1を入力して、トランジスタ3308をオフ状態とする。トランジスタ3308をオフ状態とした後に、電位V1を低電位とする。ここでも、トランジスタ3304はオフ状態としておく。また、電位V2は電位V1と同じ電位とする。以上により、初期期間が終了する。初期期間が終了した状態では、ノードAとトランジスタ3304のソース端子及びドレイン端子の一方との間に電位差が生じ、また、ノードAとトランジスタ3308のソース端子及びドレイン端子の他方との間に電位差が生じることになるため、トランジスタ3304およびトランジスタ3308には僅かに電荷が流れる。つまり、オフ電流が発生する。

【0072】

次に、オフ電流の測定期間の概略について説明する。測定期間においては、トランジスタ3304のソース端子またはドレイン端子の一方の端子の電位(つまりV2)、および、トランジスタ3308のソース端子またはドレイン端子の他方の端子の電位(つまりV1)は低電位に固定しておく。一方で、測定期間中は、上記ノードAの電位は固定しない(フローティング状態とする)。これにより、トランジスタ3304に電荷が流れ、時間の経過と共にノードAに保持される電荷量が変動する。そして、ノードAに保持される電荷量の変動に伴って、ノードAの電位が変動する。つまり、出力端子の出力電位Voutも変動する。

【0073】

上記電位差を付与する初期期間、および、その後の測定期間における各電位の関係の詳細(タイミングチャート)を図29に示す。

【0074】

初期期間において、まず、電位Vext_b2を、トランジスタ3304がオン状態となるような電位(高電位)とする。これによって、ノードAの電位はV2すなわち低電位(VSS)となる。なお、ノードAに低電位(VSS)を与えるのは必須ではない。その後、電位Vext_b2を、トランジスタ3304がオフ状態となるような電位(低電位)として、トランジスタ3304をオフ状態とする。そして、次に、電位Vext_b1を、トランジスタ3308がオン状態となるような電位(高電位)とする。これによって、ノードAの電位はV1、すなわち高電位(VDD)となる。その後、Vext_b1を、トランジスタ3308がオフ状態となるような電位とする。これによって、ノードAがフローティング状態となり、初期期間が終了する。

【0075】

その後の測定期間においては、電位V1および電位V2を、ノードAに電荷が流れ込み、またはノードAから電荷が流れ出すような電位とする。ここでは、電位V1および電位V2を低電位(VSS)とする。ただし、出力電位Voutを測定するタイミングにおいては、出力回路を動作させる必要が生じるため、一時的にV1を高電位(VDD)とすることがある。なお、V1を高電位(VDD)とする期間は、測定に影響を与えない程度の短期間とする。

【0076】

上述のようにして電位差を与え、測定期間が開始されると、時間の経過と共にノードAに保持される電荷量が変動し、これに従ってノードAの電位が変動する。これは、トランジスタ3305のゲート端子の電位が変動することを意味するから、時間の経過と共に、出力端子の出力電位Voutの電位も変化することとなる。

【0077】

得られた出力電位Voutから、オフ電流を算出する方法について、以下に説明する。

【0078】

オフ電流の算出に先だって、ノードAの電位VAと、出力電位Voutとの関係を求めておく。これにより、出力電位VoutからノードAの電位VAを求めることができる。上述の関係から、ノードAの電位VAは、出力電位Voutの関数として以下の式(1)のように表すことができる。

【0079】

【数1】

【0080】

また、ノードAの電荷QAは、ノードAの電位VA、ノードAに接続される容量CA、定数(const)を用いて、以下の式(2)のように表される。ここで、ノードAに接続される容量CAは、容量素子3302の容量と他の容量の和である。

【0081】

【数2】

【0082】

ノードAの電流IAは、ノードAに流れ込む電荷(またはノードAから流れ出る電荷)の時間微分であるから、ノードAの電流IAは以下の式(3)のように表される。

【0083】

【数3】

【0084】

このように、ノードAに接続される容量CAと、出力端子の出力電位Voutから、ノードAの電流IAを求めることができる。

【0085】

以上に示す方法により、オフ状態においてトランジスタのソースとドレイン間を流れるリーク電流(オフ電流)を測定することができる。

【0086】

本実施の形態では、チャネル長L=10μm、チャネル幅W=50μmの、高純度化した酸化物半導体を用いてトランジスタ3304、トランジスタ3305、トランジスタ3306、トランジスタ3308を作製した。また、並列された各測定系3300において、容量素子3302の各容量値を、100fF、1pF、3pFとした。

【0087】

なお、本実施の形態に係る測定では、VDD=5V、VSS=0Vとした。また、測定期間においては、電位V1を原則としてVSSとし、10secから300secの範囲ごとに、100msecの期間だけVDDとしてVoutを測定した。また、素子に流れる電流Iの算出に用いられるΔtは、約30000secとした。

【0088】

図30に、上記電流測定に係る経過時間Timeと、出力電位Voutとの関係を示す。図30より、時間の経過にしたがって、電位が変化している様子が確認できる。

【0089】

図31には、上記電流測定によって算出された室温(25℃)におけるオフ電流を示す。なお、図31は、ソース−ドレイン電圧Vと、オフ電流Iとの関係を表すものである。図31から、ソース−ドレイン電圧が4Vの条件において、オフ電流は約40zA/μmであることが分かった。また、ソース−ドレイン電圧が3.1Vの条件において、オフ電流は10zA/μm以下であることが分かった。なお、1zAは10−21Aを表す。

【0090】

さらに、上記電流測定によって算出された85℃の温度環境下におけるオフ電流について図32に示す。図32は、85℃の温度環境下におけるソース−ドレイン電圧Vと、オフ電流Iとの関係を表すものである。図32から、ソース−ドレイン電圧が3.1Vの条件において、オフ電流は100zA/μm以下であることが分かった。

【0091】

以上のように、高純度化された酸化物半導体を用いたトランジスタでは、オフ電流が十分に小さくなることが確認された。

【0092】

書き込み回路111に基準電位V(st)が供給されると、第2の信号線122であるビット線BL(1)には基準電位V(st)が印加される。同時に、ワード線WL(1)の電位が高電位VH(例えば5V)から低電位VL(例えば0V)に減少する。その後、ワード線WL_OS(1)の電位が高電位VH(例えば5V)まで上昇する。ワード線WL_OS(1)の電位が高電位VH(例えば5V)まで上昇すると、OSトランジスタ201のゲート電極に高電位VHが印加され、OSトランジスタ201がオン状態となる。そして、メモリセル102のフローティングノード202は、ビット線BL(1)に印加された基準電位V(st)と同等の電位となる電荷が蓄えられる。そして、ワード線WL_OS(1)が低電位VL(例えば0V)となり、OSトランジスタ201がオフ状態となる。その後、ワード線WL(1)に印加される電位が低電位VL(例えば0V)から高電位VH(例えば5V)に上昇し、同時に書き込み信号線WRITEの電位が低電位VLに減少して、書き込み回路111は第2の信号線122であるビット線BL(1)から電気的に切断され、ビット線BL(1)はフローティングとなる。OSトランジスタ201は、オフ電流が極めて小さいという特徴を有しているため、フローティングノード202に蓄えられた電荷の保持が容易になり、また保持された情報の読み出しが容易になる。

【0093】

その後、ベリファイ処理が行われるため、第2の信号線122であるビット線BL(1)は低電位VL(例えば0V)にプリチャージされ、かつフローティングとなる。また、ワード線WL_OS(1)は低電位VLのままであり、信号線VSLは高電位VH(例えば5V)まで上昇する。ビット線BL(1)が低電位VLの期間は、読み出し回路113に第1の電位(本実施の形態では、低電位VL(例えば0V))が入力され、読み出し回路113からスイッチング素子119に対しても第1の電位が出力される。

【0094】

スイッチング素子119は、第1の電位(本実施の形態では、低電位VL(例えば0V))が入力されている期間においてショートとなり、コントロール信号生成回路116と書き込み回路111が電気的に接続され、コントロール信号生成回路116で生成されるコントロール信号が書き込み回路111に入力される。なお、コントロール信号生成回路116でのコントロール信号の生成に基づいて、ワード線WL(1)の電位が変化する。

【0095】

例えば、フローティングノード202に基準電位V(st)として1Vが書き込まれ、ワード線WL(1)に5Vが印加され、信号線VSLに5Vが印加される場合、フローティングノード202の電位はフローティングノード202に書き込まれた基準電位V(st)(1V)と、ワード線WL(1)の電位(5V)との容量結合により6Vと見なせる。また、信号線VSLには高電位として5Vが印加されているため、トランジスタ203のVgsは1Vとなる。

【0096】

トランジスタ203のしきい値電位が仮に−1.3Vであるとすると、Vgsが1Vの状態ではトランジスタ203はオフ状態であり、ビット線BL(1)の電位は第1の電位(低電位VL(例えば0V))のままとなる。そして、読み出し回路113に第1の電位(低電位VL(例えば0V))が読み出され、スイッチング素子119にも第1の電位(低電位VL(例えば0V))が入力される。

【0097】

スイッチング素子119に第1の電位(低電位VL(例えば0V))が入力されている期間は、コントロール信号生成回路116で生成されたコントロール信号が、書き込み回路111に入力され、コントロール信号の入力に基づいて書き込み回路111にて選択されている書き込みデータ電位が変化する。例えば、データバッファ112からのデータ入力により、書き込み回路111にてV(1,4)の書き込みデータ電位が選択されている場合、書き込み回路111にコントロール信号が1回入力されると、V(1,3)の書き込みデータ電位が選択される、つまり、コントロール信号の入力に基づいて、選択される書き込みデータ電位供給線(第1の信号線121に相当)が変化する。

【0098】

また、コントロール信号の生成に基づいて(生成と同期して)、スイッチング素子119が停止するまで(オープンとなるまで、または絶縁状態となるまで)、ワード線WL(1)の電位が徐々に変化する。なお、ワード線WL(1)の電位変化量は、基準電位V(st)の電位およびメモリセル102の実際のしきい値Vthのばらつき幅によって決まる。

【0099】

例えば、基準電位V(st)が1.0V、トランジスタ203の設計しきい値電圧が−1.0V、実際のしきい値電圧が−1.3V、ワード線WL(1)の電位が5V、信号線VSLの電位が5Vの場合、ワード線WL(1)の1度目の電位変化量は、トランジスタ203がオン状態となる(つまり、Vgsが設計しきい値電圧である−1.0V以下になる)のに必要なだけ、つまり2V減少する。この時、トランジスタ203のVgsは容量結合によって見かけ上、Vgsの設計しきい値電圧である−1.0Vとなるが、トランジスタ203の実際のしきい値電圧は−1.3Vであるため、トランジスタ203はオフ状態のままである。

【0100】

このため、第2の信号線122であるビット線BL(1)から読み出し回路113に対して第1の電位(本実施の形態では、低電位VL(例えば0V))が出力され、読み出し回路113からスイッチング素子119に対しても第1の電位が出力される。そして、スイッチング素子119に第1の電位(低電位VL(例えば0V))が入力されている期間は、コントロール信号生成回路116で生成されたコントロール信号が、書き込み回路111に入力されるため、コントロール信号の生成に基づいて(生成と同期して)、ワード線WL(1)には2度目の電位変化が生じる。

【0101】

2度目以降の電位変化量は、メモリセル102の実際のしきい値電圧Vthのばらつき幅よりも小さくなるよう設計者が設定した任意の電位を用いることができる。任意の電位としては、メモリセルのしきい値電圧Vthのばらつき幅の1/2以下の電位とすることが望ましい。電位生成回路103において、1つのデータに対して書き込むことのできる電位の種類が5種類である場合、5種類の電位として上述の任意の電位ずつ変化させた電位を用いることが好ましい。例えば、2度目以降の電位減少により減少する電位を0.1Vに設定した場合、5種類の電位は1.0V,0.9V,0.8V,0.7V,0.6Vまたは、1.0V,1.1V,1.2V,1.3V,1.4Vというように設定すればよい。

【0102】

上述のように、ワード線WL(1)の2度目以降の電位変化量を0.1Vと設定すると、4度目の電位減少後にトランジスタ203のVgsが−1.3Vとなり、トランジスタ203がオン状態となる。これにより、ビット線BL(1)と信号線VSLが電気的に接続され、ビット線BL(1)の電位は信号線VSLの電位(5V)と等しくなり、読み出し回路113に第2の電位(本実施の形態では、高電位VH(5V))が読み出され、スイッチング素子119にも第2の電位(本実施の形態では高電位VH(5V))が入力されて、スイッチング素子119は停止し(オープンとなる、または絶縁状態となる)、コントロール信号生成回路116と書き込み回路111は電気的に切断される。

【0103】

書き込み回路111は、スイッチング素子119が停止するまでの期間においてコントロール信号が入力され、コントロール信号の入力に応じて、選択される書き込みデータ電位が変動する。

【0104】

例えば、データバッファ112からデータが入力された直後において、書き込みデータ電位としてV(3,5)が選択されている場合において、コントロール信号生成回路116で生成されたコントロール信号が4回入力された場合、「入力されたパルス信号数−1」だけ移動した第1の信号線121の電位、つまり、複数の書き込み電位のうちの1つであるV(3,2)が書き込みデータ電位として選択される。これにより、書き込み回路111にて選択されている書き込みデータ電位は、メモリセルのしきい値電圧ばらつき分の電位が補正された電位となる。

【0105】

なお、上述ではメモリセル102の1つについての動作のみを説明したが、同じ行の他の複数のメモリセル102においても、同様の処理が同時に行われる。そして1行全てのメモリセルにおいて上述の処理が終了した時点で書き込み信号線WRITEの電位が高電位VHとなり、書き込み回路111は第2の信号線122であるビット線BL(1)と電気的に接続され、各々のメモリセル102のしきい値電圧ばらつき分の電位を補正した書き込みデータ電位が、複数のメモリセル102に書き込まれる。

【0106】

このように、本実施の形態に記載の半導体装置およびベリファイ処理を用いることにより、2回の書き込み(基準電位V(st)をメモリセルに書き込む、および、しきい値電圧ばらつき分の電位が補正された書き込みデータ電位をメモリセルに書き込む)と1回のベリファイ読み出しで、複数のメモリセル102に各々のメモリセルのしきい値電圧ばらつき分を補正した書き込みデータ電位を書き込むことができるため、従来のメモリセルのしきい値電圧Vthのばらつきをより小さくすることができ、かつ書き込み動作の高速化が可能となる。なお、図2のメモリセルを構成する2つのトランジスタを両方とも、酸化物半導体以外の材料を用いたトランジスタにより構成した場合、フローティングノード202に蓄えられた電荷が時間と共に抜けてしまうためリフレッシュ動作を行う必要がある、という問題が生じる。しかし、図2のように、酸化物半導体を用いたトランジスタのソースまたはドレインの一方を、酸化物半導体以外の材料を用いたトランジスタのゲートに電気的に接続した構造とすることにより、当該問題を解決することができる。したがって、本実施の形態に記載されるように、メモリセル102を構成するトランジスタの1つに酸化物半導体を用いたトランジスタを使用する事は、本明細書に記載の技術的特徴を体現する上で、重要な要素であるといえる。

【0107】

したがって、本実施の形態に記載の半導体装置およびベリファイ処理を用いることにより、従来のメモリセルと比較して、書き込み処理およびベリファイ処理を大幅に削減することが可能となり、半導体装置の高速動作、消費電力低減に寄与できる。

【0108】

上記、本実施の形態に記載の半導体装置を用いたベリファイ処理において、メモリセル102を構成するトランジスタのしきい値電圧のばらつきなどに起因して、複数のメモリセル102それぞれを動作するために必要な電位(メモリセルのしきい値電圧ともいう)は、ばらつき(分布幅)を有する場合がある。

【0109】

複数のメモリセル102のしきい値電圧がばらつき(分布幅)を有する場合に、複数のメモリセル102にデータ”1”を書き込む手順の一例を図4(A)に示す。なお、電位生成回路103で生成される複数の書き込みデータ電位(V(0,1)〜V(i,j))のうち、電位V(1,1)からV(1,j)がデータ”1”を書き込む電位である。

【0110】

図4(A)は、メモリセル数Nを横軸にとり、メモリセル102のしきい値電圧Vthを縦軸にとり、複数のメモリセル102のしきい値電圧Vthの分布を示したグラフである。図4(A)には、書き込み前(データ”0”)と書き込み後(データ”1”)のしきい値電圧Vthの分布を示している。書き込み前(データ”0”)のしきい値電圧Vthの分布から延びる矢印の先に書き込み後(データ”1”)のしきい値電圧Vthの分布を示す。また、書き込みに用いた電位の大きさを矢印の横に示している。

【0111】

図4(A)に示すように、電位生成回路103で生成される複数の書き込みデータ電位(V(0,1)〜V(i,j))のうち第1の電位(ここではV(1,1))を書き込みデータ電位として用いてメモリセル102のしきい値電圧Vthが最も低い第1の範囲のメモリセルに書き込みを行う。すると、書き込み前(データ”0”)のしきい値電圧Vthの分布から書き込み後(データ”1”)のしきい値電圧Vthの分布に変化する。

【0112】

また、図4(A)に示すように、電位生成回路103で生成される複数の書き込みデータ電位(V(0,1)〜V(i,j))のうち前記第1の電位とは別の電位である第2の電位(ここではV(1,2))を書き込みデータ電位として用いてメモリセル102のしきい値電圧Vthが前記第1の範囲より1つ高い第2の範囲のメモリセルに書き込みを行う。すると、書き込み前(データ”0”)のしきい値電圧Vthの分布から書き込み後(データ”1”)のしきい値電圧Vthの分布に変化する。

【0113】

また、図4(A)に示すように、電位生成回路103で生成される複数の書き込みデータ電位(V(0,1)〜V(i,j))のうち前記第2の電位とは別の電位である第3の電位(ここではV(1,3))を書き込みデータ電位として用いてメモリセル102のしきい値電圧Vthが前記第2の範囲より1つ高い第3の範囲のメモリセルに書き込みを行う。すると、書き込み前(データ”0”)のしきい値電圧Vthの分布から書き込み後(データ”1”)のしきい値電圧Vthの分布に変化する。

【0114】

また、図4(A)に示すように、電位生成回路103で生成される複数の書き込みデータ電位(V(0,1)〜V(i,j))のうち前記第3の電位とは別の電位である第4の電位(ここではV(1,4))を書き込みデータ電位として用いてメモリセル102のしきい値電圧Vthが前記第3の範囲より1つ高い第4の範囲のメモリセルに書き込みを行う。すると、書き込み前(データ”0”)のしきい値電圧Vthの分布から書き込み後(データ”1”)のしきい値電圧Vthの分布に変化する。

【0115】

また、図4(A)に示すように、電位生成回路103で生成される複数の書き込みデータ電位(V(0,1)〜V(i,j))のうち前記第4の電位とは別の電位である第5の電位(ここではV(1,5))を書き込みデータ電位として用いてメモリセル102のしきい値電圧Vthが前記第4の範囲より1つ高い第5の範囲のメモリセルに書き込みを行う。すると、書き込み前(データ”0”)のしきい値電圧Vthの分布から書き込み後(データ”1”)のしきい値電圧Vthの分布に変化する。

【0116】

また、図4(A)に示すように、電位生成回路103で生成される複数の書き込みデータ電位(V(0,1)〜V(i,j))のうち前記第5の電位とは別の電位である第6の電位(ここではV(1,6))を書き込みデータ電位として用いてメモリセル102のしきい値電圧Vthが前記第5の範囲より1つ高い第6の範囲のメモリセルに書き込みを行う。すると、書き込み前(データ”0”)のしきい値電圧Vthの分布から書き込み後(データ”1”)のしきい値電圧Vthの分布に変化する。

【0117】

このように電位生成回路103で生成されるデータ”1”を書き込む複数の書き込みデータ電位(V(0,1)〜V(i,j))のうち、メモリセルのしきい値電圧Vthの大小に合わせて、書き込み後のメモリセルのしきい値電圧Vthが定められた範囲に収まる電位を選択することで、書き込み後(データ”1”)のしきい値電圧Vthの分布の幅を小さくすることができる。

【0118】

上記では、メモリセル102が有するデータが”0”、”1”の2値である例を説明したが、メモリセル102が有するデータが3値以上(多値)である場合にも上記構成を適用することができる。書き込み前のしきい値電圧Vthのばらつき(分布幅)よりも書き込み後のしきい値電圧Vthのばらつき(分布幅)を小さくすることができるので、メモリセルを多値化する場合にも有利である。例えば図4(B)に示すように、書き込み前(データ”0”)のしきい値電圧Vthのばらつき(分布幅)よりも書き込み後(データ”1”、”2”および”3”)のしきい値電圧Vthのばらつき(分布幅)を小さくすることができる。その結果、動作電圧を増大させず、かつ、メモリセルの面積を増大させずに記憶容量を増大することができる。

【0119】

書き込み後のしきい値電圧Vthのばらつき(分布幅)は、同じデータを書き込む複数の電位のうち隣り合う電位間の電位幅程度に抑えることが可能となる。同じデータを書き込む複数の電位を狭い間隔で生成することで、書き込み後のメモリセルのしきい値電圧Vthのばらつき(分布幅)を小さくすることが可能である。

【0120】

図4(A)に示したように、複数のメモリセル102のしきい値電圧は、ばらつき(分布幅)を有する場合、しきい値電圧が最小(Vth_min)であるメモリセルとしきい値電圧が最大(Vth_max)であるメモリセルとでは、同じデータを書き込む場合であっても、書き込みデータ電位として決定される電位が異なる場合がある。

【0121】

例えば、しきい値電圧が最小(Vth_min)であるメモリセル102へデータ”1”を書き込む書き込みデータ電位として決定される電位は、図4(A)に示すように電位V(1,1)となり、しきい値電圧が最大(Vth_max)であるメモリセル102へデータ”1”を書き込む書き込みデータ電位として決定される電位は、図4(A)に示すように電位V(1,6)となる。

【0122】

本実施の形態に係る半導体装置では、メモリセル102を構成するトランジスタのしきい値電圧にばらつきがあっても、書き込み後の複数のメモリセル102のしきい値電圧のばらつき(分布幅)を小さくすることができ、半導体装置の動作電圧を低減することができる。または、動作電圧を増大させずかつメモリセルの面積を増大させずに、メモリを多値化することができ、半導体装置の単位面積あたりの記憶容量を増大することができる。または、書き込み、保持、読み出し等の動作を確実に行える半導体装置を提供することができる。

【0123】

以上、本実施の形態に示す構成、方法などは、他の実施の形態に示す構成、方法などと適宜組み合わせて用いることができる。

【0124】

(実施の形態2)

本実施の形態では、開示する発明の一態様に係る半導体装置の回路構成および動作について、図5乃至図12を参照して説明する。

【0125】

<駆動回路の説明>

図5は半導体装置のブロック図である。

【0126】

駆動回路401は、データバッファ412、書き込み回路411、読み出し回路413、コントロール信号生成回路416およびスイッチング素子419で構成されており、データの書き込み、読み出し、ベリファイ処理を行なう機能を有する。また、駆動回路401は各列に設けられている。

【0127】

電位生成回路403は、i×j(iは2以上の整数、jは2以上の整数)本の書き込みデータ電位供給線(図1の第1の信号線121に相当する)に電気的に接続しており、それぞれの書き込みデータ電位供給線が駆動回路401の書き込み回路411(1)〜(n)に電気的に接続され、複数の書き込みデータ電位を書き込み回路411(1)〜(n)に供給する。なお、iはメモリセル402に格納することができるデータ(値)の数であり、jは1つのデータに対して書き込むことのできる電圧の種類なる。また、nは列の数であり、1以上の整数となる。

【0128】

メモリセル402は、m行×n列で構成されており、各行毎にビット線BL(1)〜(n)(図1の第2の信号線122に相当する)を介して駆動回路401(1)〜(n)と電気的に接続されている。メモリセル402は、書き込みが実行された場合にビット線BL(1)〜(n)に供給された電位を記憶し、読み出しが実行されたときに記憶しているデータをビット線BL(1)〜(n)に出力する。なお、図5では、書き込み用の信号線と読み出し用の信号線とをビット線BL(1)〜(n)で兼用する例を示したが、書き込み用の信号線と読み出し用の信号線とを別々に設けてもよい。なお、mは行の数であり、1以上の整数となる。

【0129】

データバッファ412(1)〜(n)は、書き込み回路411(1)〜(n)、読み出し回路413(1)〜(n)にそれぞれ電気的に接続されている。また、データバッファ412(1)〜(n)は、データ入出力線I/O(1)〜(k)(kは2以上の整数)、アドレス選択信号線CA(1)〜(n)、書き込みデータ転送信号線TW、読み出しデータ転送信号線TRにそれぞれ電気的に接続されている。データバッファ412(1)〜(n)は、書き込みを行なう場合にアドレス選択信号線CA(1)〜(n)によって選択されたデータバッファ412とデータ入出力線I/O(1)〜(k)を電気的に接続することで、データ入出力線I/O(1)〜(k)から入力されたデータをデータバッファ412(1)〜(n)のいずれかに保持する。そして、書き込みデータ転送信号線TWから書き込みデータ転送信号が入力されると、データバッファ412(1)〜(n)に保持していたデータを書き込み回路411(1)〜(n)に出力する。また、読み出しを行なう場合に読み出しデータ転送信号線TRより読み出しデータ転送信号が入力されると、読み出し回路413(1)〜(n)から出力されたデータがデータバッファ412(1)〜(n)に保持される。そして、アドレス選択信号線CA(1)〜(n)によって選択されたデータバッファ412(1)〜(n)のいずれかがデータ入出力線I/O(1)〜(k)と電気的に接続され、データバッファ412(1)〜(n)に保持されているデータがデータ入出力線I/O(1)〜(k)に出力される。なお、kは書き込みデータの情報量を示す1以上の整数で、1つのメモリセルに4値までのデータを格納できる場合をk=2、1つのメモリセルに8値までのデータを格納できる場合をk=3とすることができる。

【0130】

書き込み回路411(1)〜(n)は、書き込みデータ電位供給線を介して電位生成回路403に電気的に接続されている。また、書き込み回路411(1)〜(n)は、データバッファ412(1)〜(n)、読み出し回路413(1)〜(n)、メモリセル402(1,1)〜(m,n)にそれぞれ電気的に接続されている。また、書き込み回路411(1)〜(n)には、信号線SP、信号線RST、信号線SW、信号線CLK、書き込み信号線WRITE、読み出し信号線READが電気的に接続されている。書き込み回路411(1)〜(n)は、読み出し回路413から入力された信号VE(1)〜(n)に応じて書き込みデータ電位供給線の1本を選択してビット線BL(1)〜(n)と電気的に接続する機能を有する。

【0131】

読み出し回路413(1)〜(n)は、データバッファ412(1)〜(n)、メモリセル402(1,1)〜(m,n)、書き込み回路411(1)〜(n)に電気的に接続されている。また、読み出し回路413(1)〜(n)には、信号線PRE、信号線TRD、信号線CLK、信号線RST2、読み出し信号線READが電気的に接続されている。読み出し回路413(1)〜(n)は、読み出し信号線READから読み出し信号が入力されると、メモリセル402(1,1)〜(m,n)のいずれか1行分のデータを読み出す。また、信号線TRDにパルスが入力されると、読み出したデータをデータバッファ412(1)〜(n)にそれぞれ出力し、また、ベリファイ処理が行われると、読み出したデータをスイッチング素子419(1)〜(n)にそれぞれ出力する。

【0132】

コントロール信号生成回路416(1)〜(n)は、スイッチング素子419(1)〜(n)と電気的に接続されており、周期が一定のコントロール信号を生成する機能を有する。また、複数のメモリセル102のワード線WL(1)〜(m)(図11参照)の電位の変化と同期してコントロール信号を生成する機能を有する。

【0133】

スイッチング素子419(1)〜(n)は、コントロール信号生成回路416(1)〜(n)、書き込み回路411(1)〜(n)、読み出し回路413(1)〜(n)に電気的に接続されている。スイッチング素子419(1)〜(n)は、読み出し回路413(1)〜(n)からの信号に応じて、コントロール信号生成回路416(1)〜(n)から入力されるコントロール信号を、書き込み回路411(1)〜(n)に出力する、または停止する機能を有する。

【0134】

デコーダ404は、アドレス信号線CAddr及び、駆動回路401のデータバッファ412(1)〜(n)に電気的に接続されており、アドレス信号CAddrに応じてデータの書き込み、読み出しを行なう駆動回路401を選択する。

【0135】

データバッファ412、電位生成回路403、書き込み回路411、メモリセル402、読み出し回路413の具体的な回路や動作については以下に説明する。なお、コントロール信号生成回路416およびスイッチング素子419についての構造や動作の詳細説明はここでは行わないが、既知の技術を用いればよい。

【0136】

<データバッファの説明>

図6は、図5のデータバッファ412の回路の一例を示している。データ入出力線I/O(1)〜(k)は、それぞれトランジスタ502の各ドレイン電極と電気的に接続され、アドレス選択信号線CA(x)(xは1以上n以下の整数)は、トランジスタ502のゲート電極と電気的に接続され、トランジスタ502の各ソース電極はラッチ回路501(x,1)〜(x,k)の一端とそれぞれが電気的に接続されている。また、ラッチ回路501(x,1)〜(x,k)のもう一端はトランジスタ503及び504の各ドレイン電極にそれぞれ電気的に接続され、トランジスタ503の各ゲート電極は書き込みデータ転送信号線TWと電気的に接続され、トランジスタ503の各ソース電極は信号線WDA(x,1)〜(x,k)と電気的に接続され、トランジスタ504の各ゲート電極は読み出しデータ転送信号線TRと電気的に接続され、トランジスタ504の各ソース電極は信号線RDA(x,1)〜(x,k)と電気的に接続される。

【0137】

データバッファ412の書き込みデータの入力動作について説明する。まず、データ入出力線I/O(1)〜(k)より任意の書き込みデータが順次送られる。そのタイミングと同期してアドレス選択信号線CA(x)に高電位VH(例えば5V)が印加されトランジスタ502がオン状態となり、ラッチ回路501(x,1)〜(x,k)にデータ入出力線I/O(1)〜(k)の情報が保持される。その後、高電位VHが印加されていたアドレス選択信号線CA(x)は低電位VL(例えば0V)が印加され、トランジスタ502はオフ状態となる。前記の手順で1〜n列全てのラッチ回路501にデータを保持、または書き込みに必要な列のラッチ回路501にデータを保持する。次に、書き込みデータ転送信号線TWに高電位VHが印加されてトランジスタ503がオン状態となり、ラッチ回路501(x,1)〜(x,k)に保持されていた任意のデータが、信号線WDA(1,1)〜(n,k)にそれぞれ伝達される。

【0138】

次にデータバッファ412の読み出しデータの出力動作について説明する。データの読み出しが行われると信号線RDA(x,1)〜(x,k)から読み出しデータが入力される。そのとき、信号線TWは低電位VLとなっており、信号線TRが低電位VLから高電位VHに上昇する。そして、信号線RDA(x,1)〜(x,k)とラッチ回路501(x,1)〜(x,k)がそれぞれ電気的に接続され、ラッチ回路501(x,1)〜(x,k)に読み出しデータが保持される。そして、信号線TRが高電位VHから低電位VLに減少する。ラッチ回路501(x,1)〜(x,k)に1行分のデータが保持された後、アドレス選択信号線CA(x)に高電位VHが印加されトランジスタ502がオン状態となりラッチ回路501(x,1)〜(x,k)とデータ入出力線I/O(1)〜(k)が電気的に接続され、ラッチ回路501(x,1)〜(x,k)に保持されたデータがデータ入出力線I/O(1)〜(k)に順次出力される。

【0139】

データバッファ412は図6の回路以外でも公知の回路を用いることができる。そのため、図6の回路に限定されることはない。

【0140】

<電位生成回路の説明>

図7は図5の電位生成回路の一例を示している。電位生成回路403は、メモリセル402のビット線BL(n)に印加するための電位を生成する機能を有する。

【0141】

はじめに電位生成回路403の構成について、図7を参照して説明する。電位生成回路403は、電源電位Vdd(例えば5V)と抵抗601の一方が電気的に接続され、抵抗601の他方と抵抗611の一方は電気的に接続され、抵抗611の他方と抵抗621の一方は電気的に接続され、抵抗621の他方は接地され(または低電位が与えられ)、抵抗601と抵抗611間にボルテージフォロア602の入力端、抵抗601と抵抗611間にボルテージフォロア612の入力端が電気的に接続される。また、ボルテージフォロア602及び612の出力端と接地電位(または低電位)の間には、それぞれ抵抗603および抵抗605、ならびに抵抗613および抵抗615が電気的に接続され、ボルテージフォロア602の出力端と、抵抗603および抵抗605の間には、ボルテージフォロア604およびボルテージフォロア606が電気的に接続されている。また、ボルテージフォロア612の出力端と、抵抗613および抵抗615の間には、ボルテージフォロア614およびボルテージフォロア616が電気的に接続されている。

【0142】

次に、電位生成回路403の動作について説明する。電源電位Vddが供給されるとボルテージフォロア602、612の入力端には、抵抗601、611、621の抵抗の総和に対して電源電位Vddからそれぞれのボルテージフォロアまでに電気的に接続されている抵抗の比だけ電圧降下した電位が入力される。そして、ボルテージフォロア602および612の出力電位もボルテージフォロア602および612の入力電位と同一の電位となる。ボルテージフォロア602および612の出力電位は、それぞれボルテージフォロア604、および614に入力され、ボルテージフォロア604、および614の出力電位はそれぞれ、ボルテージフォロア604、および614の入力電位と等しい電位がV(0,j)およびV(i,j)として書き込みデータ電位供給線に出力される。一方、ボルテージフォロア602および612の出力端と接地電位(または低電位)の間には抵抗603、605および613、615が電気的に直列接続され、抵抗603と抵抗605の間にはボルテージフォロア606の入力端が電気的に接続されている。そのため、ボルテージフォロア606の入力端には、抵抗603および抵抗605の抵抗の総和に対してボルテージフォロア602の出力端からボルテージフォロア606までに電気的に接続されている抵抗の比だけ電圧降下した電位が入力される。そして、ボルテージフォロア606の出力端にはボルテージフォロア606の入力電位と等しい電位がV(i,1)として書き込みデータ電位供給線に出力される。同様の構成で、ボルテージフォロア616の出力端にもボルテージフォロア616の入力電位と等しい電位がV(0,1)として書き込みデータ電位供給線に出力される。

【0143】

なお、図7ではデータ”0”(メモリセル102に書き込む電位が0V)を書き込むのにV(0,1)〜V(0,j)のj本の書き込みデータ電位供給線を用いているが、図8に示すように、データ”0”の書き込みデータ電位供給線の数を1本とすることができる。これにより、書き込みデータ電位供給線の数が減少するため、配線を減らせる分、メモリセル102の占有面積を大きくすることができる。また、データ”i”(メモリセル102に書き込む電位が最大)を書き込む場合にのみ書き込みデータ電位供給線を1本とすることで、前記と同様の効果を得ることができる。さらに、データ”0”とデータ”i”を書き込む場合に書き込みデータ電位供給線を1本とすることで、電位生成回路103が有する書き込みデータ電位供給線の数を(i−2)×j+2本とすることもでき、配線を減らせる分、メモリセル102の占有面積をより大きくすることができる。

【0144】

電位生成回路103は図7および図8の回路以外でも公知の回路を用いることができる。そのため、図7および図8の回路に限定されることはない。

【0145】

<書き込み回路の説明>

図9は、図5の書き込み回路の一例を示している。書き込み回路411は複数の書き込みデータ電位供給線のうち1本をビット線(BL)と電気的に接続し、ビット線(BL)に書き込みデータ電位を供給する機能を有する。また、図13には書き込み動作時のタイミングチャートを示す。

【0146】

図5に示すデータバッファ412(x)と電気的に接続される信号線WDA(x,1)〜(x,k)は、デコーダ701(x)の入力端と電気的に接続され、デコーダ701(x)の各出力端は、トランジスタ702の各ソース電極と電気的に接続され、トランジスタ702および703の各ゲート電極は、インバータ704の出力端と電気的に接続され、トランジスタ703のソース電極は接地される。インバータ704の入力端は、信号線SPと電気的に接続され、トランジスタ702および703の各ドレイン電極はシフトレジスタ708(x,0)〜(x,i)のいずれかに電気的に接続される。また、信号線RSTは、シフトレジスタ708(x,0)〜(x,i)とそれぞれ電気的に接続され、スイッチング素子419であるトランジスタ706のソース電極はコントロール信号生成回路(図9ではCTRLと記載)と電気的に接続され、トランジスタ706のゲート電極は信号線VE(x)と電気的に接続され、トランジスタ706のドレイン電極はトランジスタ705のソース電極と電気的に接続され、トランジスタ705のゲート電極はインバータ707の出力端と電気的に接続され、インバータ707の入力端は信号線READと電気的に接続され、トランジスタ705のドレイン電極はシフトレジスタ708(x,0)〜(x,i)の各入力端と電気的に接続される。また、シフトレジスタ708(x,0)の各出力端はトランジスタ720(1)〜720(j)の各ゲート電極とそれぞれ電気的に接続され、シフトレジスタ708(x,1)の各出力端はトランジスタ730(1)〜730(j)の各ゲート電極とそれぞれ電気的に接続され、シフトレジスタ708(x,i)の各出力端はトランジスタ730(1)〜730(j)の各ゲート電極とそれぞれ電気的に接続される。またトランジスタ709のドレイン電極は基準電位供給線V(st)と電気的に接続され、トランジスタ709のゲート電極は信号線SWと電気的に接続される。また、各トランジスタ720(1)〜720(j)、730(1)〜730(j)、740(1)〜740(j)のドレイン電極は書き込みデータ電位供給線とそれぞれ電気的に接続され、トランジスタ720(1)〜720(j)、730(1)〜730(j)、740(1)〜740(j)のソース電極は、トランジスタ715のドレイン電極に電気的に接続され、トランジスタ715のゲート電極は書き込み信号線WRITEと電気的に接続され、トランジスタ715のソース電極はビット線BL(x)と電気的に接続される。

【0147】

なお、各々のデータについて電位の種類が1種類でよい場合については、図10のように、電位の種類が1種類でよいデータ(ここではデータ”0”)について1本の書き込みデータ電位供給線および1つのスイッチング素子(720(1))を設けシフトレジスタ708(x,0)を用いない構造としてもよい。

【0148】

次に、書き込み回路411の動作について図9を用いて説明する。はじめに信号線SPの出力端は低電位VLが印加されており、トランジスタ702はオフ状態となり、トランジスタ703がオン状態となる。そのため、シフトレジスタ708(x,0)〜(x,i)のスタートパルスには接地電位が入力され、シフトレジスタ708(x,0)〜(x,i)の各出力端にはそれぞれ低電位VL(例えば0V)が出力され、トランジスタ720(1)〜740(j)はそれぞれオフ状態となっている。そして、信号線RSTに高電位VHが印加され、シフトレジスタ708(x,0)〜(x,i)がリセット状態となり、その後、信号線RSTは低電位VLとなる。そして、信号線SWが高電位VHとなりトランジスタ709がオン状態となって信号線WBL(x)の電位は基準電位V(st)と等しくなり、信号線WRITEに高電位VHが印加され、トランジスタ715がオン状態となって第2の信号線122であるビット線BL(x)の電位もV(st)となり、メモリセルへの書き込みが行われる。

【0149】

メモリセルに基準電位V(st)の書き込みが終了すると、書き込みデータ転送信号線TWに高電位VHが印加され、データバッファ412(1)〜(n)(図5参照)に保持されていた書き込みデータが信号線WDA(1,1)〜(n,k)を通して書き込み回路411(1)〜(n)に入力される。書き込み回路411(1)〜(n)に入力された書き込みデータはデコーダ701(x)に入力される。デコーダ701(x)は書き込みデータに対応する出力端のみ高電位を出力するため、トランジスタ702のいずれかのソース電極には高電位が印加される状態となる。

【0150】

デコーダ701(x)からの書き込みデータが出力されると信号線SPに高電位VHが印加されて、トランジスタ703がオフ状態となり、トランジスタ702がオン状態となる。そして、デコーダ701(x)の出力結果がシフトレジスタ708(x,0)〜(x,i)に入力される。なお、シフトレジスタ708(x,0)〜(x,i)のうちいずれか一つのシフトレジスタには高電位VH、他のシフトレジスタには低電位VLが入力される。シフトレジスタ708(x,0)〜(x,i)にデコーダ701(x)の出力結果が入力されると、高電位VHが入力されたシフトレジスタ708のみ動作を始める。シフトレジスタ708が動作すると、出力の最下位の信号線に高電位VHが印加され、それ以外の信号線には低電位VLが印加される。動作しているシフトレジスタ708の最下位の信号線に高電位VHが印加されると、シフトレジスタ708の出力端と電気的に接続されている複数のトランジスタのうち一つのトランジスタのゲート電極にも高電位が印加される。そしてトランジスタ720(1)〜740(j)のうちいずれかのゲート電極に高電位VHが印加され、信号線WBLと書き込みデータ電位供給線のいずれかが電気的に接続され、信号線WBLは書き込みデータに等しい書き込みデータ電位V(0,1)〜V(i,j)のいずれかが供給される。

【0151】

信号線WBL(x)に書き込みデータ電位が供給された後、信号線SPに低電位VLが印加されてトランジスタ702の各ゲート電極およびトランジスタ703の各ゲート電極には高電位VHが印加され、トランジスタ702はそれぞれオフ状態となり、デコーダ701(x)の出力端とシフトレジスタ708(x,0)〜(x,i)の入力端は絶縁状態(非導通状態ともいう)となる。一方でトランジスタ703がオン状態となるためシフトレジスタ708(x,0)〜(x,i)には接地電位が入力されるが、動作しているシフトレジスタ708の出力端は動作開始時の状態を維持する。

【0152】

信号線WBL(x)に書き込みデータ電位が供給された後に、ベリファイ処理が行われ、各々のメモリセル102のしきい値ばらつき分の電位が補正された電位を、1行の複数のメモリセル102に書き込む(詳細は、実施の形態1を参照)。そして、他の行についても同様の処理を行う。

【0153】

上述のように、デコーダ701(x)からのデータを書き込む前に、複数のメモリセル102に予め基準電位V(st)を書き込み、ベリファイ処理を行うことで、メモリセルのしきい値Vthのばらつきが補正された電位をメモリセルに書き込むことができ、データ書き込み後のメモリセルのしきい値Vthのばらつきを小さくすることができる。

【0154】

<メモリセルの説明>

図11は、図5のメモリセル402(1,1)〜(m,n)を示している。また、図13は書き込み動作時のタイミングチャートを示しており、図14には読み出し動作時のタイミングチャートを示す。

【0155】

はじめに、メモリセル402の構成について説明する。メモリセル402(1,1)は、ビット線BL(1)とOSトランジスタ801のドレイン電極が電気的に接続され、OSトランジスタ801のゲート電極とワード線WL_OS(1)が電気的に接続され、OSトランジスタ801のソース電極とトランジスタ803のゲート電極は、容量素子804の電極の一方と電気的に接続され、容量素子804の電極の他方はワード線WL(1)に接続される。また、ビット線BL(1)とトランジスタ803のドレイン電極が電気的に接続され、トランジスタ803のソース電極と信号線VSLが電気的に接続されて、1つのメモリセル402が構成される。

【0156】

次に書き込み動作について説明する。メモリセル402にデータが書き込まれるときは、図9の書き込み信号線WRITEの電位が高電位VHまで上昇し、ビット線BL(1)〜(n)には書き込みデータ電位が印加される。書き込み信号線WRITEの電位が高電位VHに上昇すると同時に、ワード線WL(1)〜(m)のうち書き込み対象となる1行のワード線の電位も高電位VHから低電位VLに減少にする。その後、ワード線WL_OS(1)〜(m)のうち書き込み対象となる1行のワード線の電位も高電位VHまで上昇する。例えば、ワード線WL_OS(1)の電位が高電位VHまで上昇すると、OSトランジスタ801のゲート電極及びワード線WL_OS(1)と電気的に接続される1行目の全てのOSトランジスタのゲート電極に高電位VHが印加され、各OSトランジスタがオン状態となる。そして、メモリセル402のフローティングノード802は、ビット線BL(1)に印加された書き込みデータ電位と同等の電位となる電荷が蓄えられる。そして、ワード線WL_OS(1)が低電位VLとなり、ワード線WL_OS(1)とOSトランジスタのゲート電極が電気的に接続される1行目のOSトランジスタ全てがオフ状態となる。その後、ワード線WL(1)に印加される電位が低電位VLから高電位VHに上昇し、同時に信号線WRITEの電位も高電位VHから低電位VLに減少する。OSトランジスタ801は、オフ電流が極めて小さいという特徴を有しているため、フローティングノード802に蓄えられた電荷の保持が容易になり、また保持された情報の読み出しが容易になる。

【0157】

<読み出し回路の説明>

図12は、図5の読み出し回路の一例を示している。読み出し回路413はメモリセル402に書き込まれた情報を読み出す機能を有する。また、図14には読み出し動作時のタイミングチャートを示す。

【0158】

読み出し回路413においてトランジスタ901のソース電極には、低電位VBLが印加され、トランジスタ901のゲート電極は、信号線PREと電気的に接続され、トランジスタ901のドレイン電極とトランジスタ902のソース電極とインバータ903の入力端は信号線VE(x)と電気的に接続され、インバータ903の出力端はトランジスタ904の各ゲート電極と電気的に接続される。また、トランジスタ902のゲート電極は、読み出し信号線READと電気的に接続され、トランジスタ902のドレイン電極は、ビット線BL(x)と電気的に接続される。そして、トランジスタ904の各ドレイン電極は信号線C(x,1)〜(x,k)とそれぞれ電気的に接続され、信号線C(x,1)〜(x,k)はカウンタ907(x)の出力端と電気的に接続され、カウンタ907(x)の入力端は、信号線CLK及び信号線RST2がそれぞれ電気的に接続される。さらに、トランジスタ904の各ソース電極は、ラッチ回路908(x,1)〜(x,k)の各入力端とそれぞれ対となって電気的に接続され、ラッチ回路908(x,1)〜(x,k)の各出力端は、トランジスタ905の各ドレイン電極とそれぞれ対となって電気的に接続され、トランジスタ905の各ゲート電極は、信号線TRDとそれぞれ電気的に接続され、トランジスタ905の各ソース電極とトランジスタ906の各ドレイン電極は、信号線RDA(x,1)〜(x,k)とそれぞれ対となって電気的に接続され、トランジスタ906の各ゲート電極は信号線TRDの反転信号が出力される信号線(図中では、TRDの上部にラインを引いて表現。)とそれぞれ電気的に接続され、トランジスタ906の各ソース電極は接地される(または低電位が与えられる)。

【0159】

次に、読み出し回路413の動作について、図14を参照して説明する。読み出しまたはベリファイ処理が行なわれると、信号線PREが高電位VHとなりトランジスタ901がオン状態となり、次に読み出し信号線READが高電位VHとなってトランジスタ902がオン状態となる。そして、ビット線BL(x)は低電位VBLと等しくなる。このとき、トランジスタ904のゲート電極には高電位VHが印加され、トランジスタ904はオン状態となる。読み出し信号線READが高電位VHになると同時に、信号線RST2にもパルスが印加され、カウンタ907(x)はリセット状態となり、信号線C(x,1)〜C(x,k)はそれぞれ低電位VLが出力される。信号線RST2が低電位VLになると同時に信号線PREも低電位となり、ビット線BL(x)は低電位かつフローティングとなる。

【0160】

ビット線BL(x)がフローティング状態になった後、メモリセルのワード線WL(y)(yは1以上m以下の整数)の電位は段階的に減少する。ワード線WL(y)の電位が減少すると、フローティングノード802に書き込まれていたデータによってトランジスタ803がオン状態になりビット線BL(x)の電位は高電位VHとなる。

【0161】

カウンタ907(x)は信号線CLKが立ち上がるごとに、出力信号C(x,1)〜C(x,k)の値を大きくする。なお、ワード線WL(y)の電位は、図14に示すように、信号線CLKの立ち上がりに同期して段階的に減少する。ラッチ回路908(1)〜(k)には、トランジスタ904がオン状態である限り出力信号C(x,1)〜C(x,k)と同等の電位がそれぞれのラッチ回路に記憶されるが、メモリセルのデータが読み出されビット線BL(x)が高電位となると、トランジスタ904のゲート電極にはそれぞれ低電位VLが印加されるためトランジスタ904はオフ状態となる。そしてラッチ回路908(1)〜(k)は、トランジスタ904がオフ状態となる前の信号線C(x,1)〜C(x,k)のデータを保持する。そして、ラッチ回路908(1)〜(k)に保持されたデータは読み出しデータと決定される。

【0162】

ワード線WL(y)が段階的に減少して低電位VLとなると、メモリセルのデータ”0”〜”i”のうちのいずれかのデータが読み出せたことになり、図9のラッチ回路908(1)〜(k)には、読み出したデータが保持される。そして信号線TRDが高電位VHとなり、トランジスタ905がそれぞれオン状態、トランジスタ906がそれぞれオフ状態になる。そして信号線RDA(x,1)〜RDA(x,k)は、ラッチ回路908(1)〜(k)とそれぞれ同じ電位が出力される。なお、信号線TRDが低電位の間はトランジスタ905がオフ状態、トランジスタ906がオン状態となり、信号線RDA(x,1)〜RDA(x,k)には接地電位(または低電位)が出力される。また、信号線RDA(x,1)〜RDA(x,k)に読み出したデータを出力した後、信号線TRDは低電位VLとなり信号線RDA(x,1)〜RDA(x,k)には接地電位(または低電位)が出力される。

【0163】

以上、本実施の形態に示す構成、方法などは、他の実施の形態に示す構成、方法などと適宜組み合わせて用いることができる。

【0164】

(実施の形態3)

本実施の形態では、開示する発明の一態様に係る半導体装置が有するメモリセルの回路構成およびその動作について、図15を参照して説明する。

【0165】

<メモリセルの基本構成>

図15(A−1)に示すメモリセルにおいて、第1の配線(1st Line)とトランジスタ1600のソース電極(またはドレイン電極)とは、電気的に接続され、第2の配線(2nd Line)とトランジスタ1600のドレイン電極(またはソース電極)とは、電気的に接続されている。また、第3の配線(3rd Line)とトランジスタ1602のソース電極(またはドレイン電極)とは、電気的に接続され、第4の配線(4th Line)と、トランジスタ1602のゲート電極とは、電気的に接続されている。そして、トランジスタ1600のゲート電極と、トランジスタ1602のドレイン電極(またはソース電極)は、容量素子1604の電極の一方と電気的に接続され、第5の配線(5th Line)と、容量素子1604の電極の他方は電気的に接続されている。

【0166】

ここで、トランジスタ1602には、例えば、酸化物半導体を用いたトランジスタが適用される。酸化物半導体を用いたトランジスタは、オフ電流が極めて小さいという特徴を有している。このため、トランジスタ1602をオフ状態とすることで、トランジスタ1600のゲート電極の電位を極めて長時間にわたって保持することが可能である。そして、容量素子1604を有することにより、トランジスタ1600のゲート電極に与えられた電荷の保持が容易になり、また、保持された情報の読み出しが容易になる。

【0167】

トランジスタ1600については、酸化物半導体以外の材料を用いたトランジスタが適用される。情報の読み出し速度を向上させるという観点からは、例えば、単結晶シリコンを用いたトランジスタなど、スイッチング速度の高いトランジスタを適用するのが好適である。

【0168】

また、図15(B)に示すように、容量素子1604を設けない構成とすることも可能である。

【0169】

図15(A−1)に示すメモリセルでは、トランジスタ1600のゲート電極の電位が保持可能という特徴を生かすことで、次のように、情報の書き込み、保持、読み出しが可能である。

【0170】

はじめに、情報の書き込みおよび保持について説明する。まず、第4の配線の電位を、トランジスタ1602がオン状態となる電位にして、トランジスタ1602をオン状態とする。これにより、第3の配線の電位が、トランジスタ1600のゲート電極、および容量素子1604に与えられる。すなわち、トランジスタ1600のゲート電極には、所定の電荷が与えられる(書き込み)。ここでは、異なる二つの電位を与える電荷(以下、低電位を与える電荷を電荷QL、高電位を与える電荷を電荷QHという)のいずれかが与えられるものとする。なお、異なる三つまたはそれ以上の電位を与える電荷を適用して、記憶容量を向上させても良い。その後、第4の配線の電位を、トランジスタ1602がオフ状態となる電位にして、トランジスタ1602をオフ状態とすることにより、トランジスタ1600のゲート電極に与えられた電荷が保持される(保持)。

【0171】

トランジスタ1602のオフ電流は極めて小さいから、トランジスタ1600のゲート電極の電荷は長時間にわたって保持される。

【0172】

次に、情報の読み出しについて説明する。第1の配線に所定の電位(定電位)を与えた状態で、第5の配線に適切な電位(読み出し電位)を与えると、トランジスタ1600のゲート電極に保持された電荷量に応じて、第2の配線は異なる電位をとる。一般に、トランジスタ1600をnチャネル型とすると、トランジスタ1600のゲート電極にQHが与えられている場合の見かけのしきい値Vth_Hは、トランジスタ1600のゲート電極にQLが与えられている場合の見かけのしきい値Vth_Lより低くなるためである。ここで、見かけのしきい値とは、トランジスタ1600を「オン状態」とするために必要な第5の配線の電位をいうものとする。したがって、第5の配線の電位をVth_HとVth_Lの間の電位V0とすることにより、トランジスタ1600のゲート電極に与えられた電荷を判別できる。例えば、書き込みにおいてQHが与えられた場合には、第5の配線の電位がV0(>Vth_H)となれば、トランジスタ1600は「オン状態」となる。QLが与えられた場合には、第5の配線の電位がV0(<Vth_L)となっても、トランジスタ1600は「オフ状態」のままである。このため、第2の配線の電位を見ることで、保持されている情報を読み出すことができる。

【0173】

しかしながら、メモリセルを構成するトランジスタ(例えば、トランジスタ1600)のしきい値電圧にばらつきがあると、当該トランジスタのしきい値電圧のばらつきに起因して、複数のメモリセルそれぞれを動作するために必要な電位(メモリセルのしきい値電圧ともいう)にもばらつきが生じる。例えば、トランジスタ1600のしきい値電圧にばらつきがあると、情報を読み出す際のメモリセルのしきい値電圧にもばらつきが生じる。そのため複数のメモリセルそれぞれの動作電圧は、メモリセルのしきい値電圧のばらつきを考慮して幅をもたせて設定される。そのためメモリセルの動作電圧の低減には限界があった。

【0174】

開示する発明の一態様に係る半導体装置では、実施の形態1において図1乃至図5に示したように、書き込みデータ電位が順次別の電位に変更され、書き込み、読み出し、ベリファイが行われ、複数のメモリセルの書き込みデータ電位が決定される。これにより、書き込み後の半導体装置のメモリセルのしきい値電圧のばらつき(分布幅)を小さくし、動作電圧を低減する、または記憶容量を増大する、または書き込み、保持、読み出し等の動作を確実に行え、かつ書き込みを高速化させて行える半導体装置およびその駆動方法を提供することができる。

【0175】

なお、メモリセルをアレイ状に複数配置して用いる場合には、所望のメモリセルの情報のみを読み出せることが必要になる。このように、所定のメモリセルの情報を読み出し、それ以外のメモリセルの情報を読み出さない場合には、読み出しの対象ではないメモリセルの第5の配線に対して、ゲート電極の状態にかかわらずトランジスタ1600が「オフ状態」となるような電位、つまり、Vth_Hより小さい電位を与えればよい。または、ゲート電極の状態にかかわらずトランジスタ1600が「オン状態」となるような電位、つまり、Vth_Lより大きい電位を第5の配線に与えればよい。

【0176】

次に、情報の書き換え(再度の書き込みともいう)について説明する。情報の書き換えは、上記情報の書き込みおよび保持と同様に行われる。つまり、第4の配線の電位を、トランジスタ1602がオン状態となる電位にして、トランジスタ1602をオン状態とする。これにより、第3の配線の電位(新たな情報に係る電位)が、トランジスタ1600のゲート電極および容量素子1604に与えられる。その後、第4の配線の電位を、トランジスタ1602がオフ状態となる電位にして、トランジスタ1602をオフ状態とすることにより、トランジスタ1600のゲート電極は、新たな情報に係る電荷が与えられた状態となる。

【0177】

このように、開示する発明に係る半導体装置が有するメモリセルは、再度の情報の書き込みによって直接的に情報を書き換えることが可能である。このためフラッシュメモリなどにおいて必要とされる高電圧を用いてのフローティングゲートからの電荷の引き抜きが不要であり、消去動作に起因する動作速度の低下を抑制することができる。つまり、メモリセルを有する半導体装置の高速動作が実現される。

【0178】

なお、図15(A−1)および図15(B)に示す第3の配線は、実施の形態1において図1に示す第2の信号線122に相当する。図15(A−1)および図15(B)に示す第2の配線は、実施の形態1において図1に示す第3の信号線125に相当する。

【0179】

なお、トランジスタ1602のドレイン電極(またはソース電極)は、トランジスタ1600のゲート電極と電気的に接続されることにより、不揮発性メモリ素子として用いられるフローティングゲート型トランジスタのフローティングゲートと同等の作用を奏する。以下において、トランジスタ1602のドレイン電極(またはソース電極)とトランジスタ1600のゲート電極が電気的に接続される部位をノードFGと呼ぶ場合がある。トランジスタ1602がオフの場合、当該ノードFGは絶縁体中に埋設されたと見ることができ、ノードFGには電荷が保持される。酸化物半導体を用いたトランジスタ1602のオフ電流は、シリコン半導体で形成されるトランジスタの10万分の1以下であるため、トランジスタ1602のリークによる、ノードFGに蓄積された電荷の消失を無視することが可能である。つまり、酸化物半導体を用いたトランジスタ1602により、電力の供給が無くても情報の保持が可能な不揮発性の記憶装置を実現することが可能である。

【0180】

例えば、トランジスタ1602の室温(25℃)でのオフ電流が10zA(1zA(ゼプトアンペア)は1×10−21A)以下であり、容量素子1604の容量値が10fF程度である場合には、少なくとも104秒以上のデータ保持が可能である。なお、当該保持時間が、トランジスタ特性や容量値によって変動することはいうまでもない。

【0181】

また、開示する発明の半導体装置が有するメモリセルにおいては、従来のフローティングゲート型トランジスタにおいて指摘されているゲート絶縁膜(トンネル絶縁膜)の劣化という問題が存在しない。つまり、従来問題とされていた、電子をフローティングゲートに注入する際のゲート絶縁膜の劣化という問題を解消することができる。これは、原理的な書き込み回数の制限が存在しないことを意味するものである。また、従来のフローティングゲート型トランジスタにおいて書き込みや消去の際に必要であった高電圧も不要である。

【0182】

図15(A−1)に示すメモリセルは、当該メモリセルを構成するトランジスタなどの要素が抵抗および容量を含むものとして、図15(A−2)のように考えることが可能である。つまり、図15(A−2)では、トランジスタ1600および容量素子1604が、それぞれ、抵抗および容量を含んで構成されると考えていることになる。R1およびC1は、それぞれ、容量素子1604の抵抗値および容量値であり、抵抗値R1は、容量素子1604を構成する絶縁層による抵抗値に相当する。また、R2およびC2は、それぞれ、トランジスタ1600の抵抗値および容量値であり、抵抗値R2はトランジスタ1600がオン状態の時のゲート絶縁層による抵抗値に相当し、容量値C2はいわゆるゲート容量(ゲート電極と、ソース電極またはドレイン電極との間に形成される容量、及び、ゲート電極とチャネル形成領域との間に形成される容量)の容量値に相当する。

【0183】

トランジスタ1602がオフ状態にある場合のソース電極とドレイン電極の間の抵抗値(実効抵抗とも呼ぶ)をROSとすると、トランジスタ1602のゲートリーク電流が十分に小さい条件において、R1およびR2が、R1≧ROS(R1はROS以上)、R2≧ROS(R2はROS以上)を満たす場合には、電荷の保持期間(情報の保持期間ということもできる)は、主としてトランジスタ1602のオフ電流によって決定されることになる。

【0184】

逆に、当該条件を満たさない場合には、トランジスタ1602のオフ電流が十分に小さくとも、保持期間を十分に確保することが困難になる。トランジスタ1602のオフ電流以外のリーク電流(例えば、トランジスタ1600におけるソース電極とゲート電極の間において生じるリーク電流等)が大きいためである。このことから、本実施の形態において開示するメモリセルは、R1≧ROS、およびR2≧ROSの関係を満たすものであることが望ましいといえる。

【0185】

一方で、C1とC2は、C1≧C2(C1はC2以上)の関係を満たすことが望ましい。C1を大きくすることで、第5の配線によってノードFGの電位を制御する際に、第5の配線の電位を効率よくノードFGに与えることができるようになり、第5の配線に与える電位間(例えば、読み出しの電位と、非読み出しの電位)の電位差を低く抑えることができるためである。

【0186】

このように、上述の関係を満たすことで、より好適なメモリセルを有する半導体装置を実現することが可能である。なお、R1およびR2は、トランジスタ1600のゲート絶縁層や容量素子1604の絶縁層によって制御される。C1およびC2についても同様である。よって、ゲート絶縁層の材料や厚さなどを適宜設定し、上述の関係を満たすようにすることが望ましい。

【0187】

本実施の形態で示す半導体装置においては、ノードFGが、フラッシュメモリ等のフローティングゲート型トランジスタのフローティングゲートと同等の作用をするが、本実施の形態のノードFGは、フラッシュメモリ等のフローティングゲートと本質的に異なる特徴を有している。

【0188】

フラッシュメモリでは、コントロールゲートに印加される電位が高いため、その電位が、隣接するセルのフローティングゲートに影響を与えないように、セルとセルとの間隔をある程度保つ必要が生じる。このことは、半導体装置の高集積化を阻害する要因の一つである。そして、当該要因は、高電界をかけてトンネル電流を発生させるというフラッシュメモリの根本的な原理に起因するものである。

【0189】

一方、本実施の形態に係る半導体装置が有するメモリセルは、酸化物半導体を用いたトランジスタのスイッチングによって動作し、上述のようなトンネル電流による電荷注入の原理を用いない。すなわち、フラッシュメモリのような、電荷を注入するための高電界が不要である。これにより、隣接セルに対する、コントロールゲートによる高電界の影響を考慮する必要がないため、高集積化が容易になる。

【0190】

また、高電界が不要であり、大型の周辺回路(昇圧回路など)が不要である点も、フラッシュメモリに対するアドバンテージである。例えば、本実施の形態に係るメモリセルに印加される電圧(メモリセルの各端子に同時に印加される電位の最大のものと最小のものの差)の最大値は、2段階(1ビット)の情報を書き込む場合、一つのメモリセルにおいて、5V以下、好ましくは3V以下とすることができる。

【0191】

さらに、容量素子1604を構成する絶縁層の比誘電率εr1と、トランジスタ1600を構成する絶縁層の比誘電率εr2とを異ならせる場合には、容量素子1604を構成する絶縁層の面積S1と、トランジスタ1600においてゲート容量を構成する絶縁層の面積S2とが、2・S2≧S1(2・S2はS1以上)(望ましくはS2≧S1(S2はS1以上))を満たしつつ、C1≧C2(C1はC2以上)を実現することが容易である。すなわち、容量素子1604を構成する絶縁層の面積を小さくしつつ、C1≧C2を実現することが容易である。具体的には、例えば、容量素子1604を構成する絶縁層においては、酸化ハフニウムなどのhigh−k材料でなる膜、または酸化ハフニウムなどのhigh−k材料でなる膜と酸化物半導体でなる膜との積層構造を採用してεr1を10以上、好ましくは15以上とし、ゲート容量を構成する絶縁層においては、酸化シリコンを採用して、εr2=3〜4とすることができる。

【0192】

このような構成を併せて用いることで、開示する発明に係る半導体装置が有するメモリセルの、より一層の高集積化が可能である。

【0193】

なお、半導体装置が有するメモリセルの記憶容量を大きくするためには、高集積化以外に、多値化の手法を採ることもできる。例えば、メモリセルの一に3段階以上の情報を書き込む構成とすることで、2段階(1ビット)の情報を書き込む場合と比較して記憶容量を増大させることができる。例えば、上述のような、低電位を与える電荷QL、高電位を与える電荷QHに加え、他の電位を与える電荷Qをトランジスタ1600のゲート電極に与えることで、多値化を実現することができる。

【0194】

本実施の形態に示す半導体装置では、酸化物半導体を用いたトランジスタ1602はオフ電流が極めて小さいため、これを用いることにより極めて長期にわたり記憶内容を保持することが可能である。つまり、リフレッシュ動作が不要となるか、または、リフレッシュ動作の頻度を極めて低くすることが可能となるため、消費電力を十分に低減することができる。また、電力の供給がない場合(ただし、電位は固定されていることが望ましい)であっても、長期にわたって記憶内容を保持することが可能である。

【0195】

また、開示する発明に係る半導体装置では、メモリセルを構成するトランジスタのしきい値電圧にばらつきがあっても、書き込み後の複数のメモリセルのしきい値電圧のばらつき(分布幅)を小さくすることができ、半導体装置の動作電圧を低減することができる。または、動作電圧を増大させずかつメモリセルの面積を増大させずに、メモリセルを多値化することができ、半導体装置の単位面積あたりの記憶容量を増大することができる。または、書き込み、保持、読み出し等の動作を確実に行える半導体装置を提供することができる。

【0196】

また、本実施の形態に示す半導体装置では、情報の書き込みに高い電圧を必要とせず、素子の劣化の問題もない。例えば、従来の不揮発性メモリのように、フローティングゲートへの電子の注入や、フローティングゲートからの電子の引き抜きを行う必要がないため、ゲート絶縁層の劣化といった問題が全く生じない。すなわち、開示する発明に係る半導体装置では、従来の不揮発性メモリで問題となっている書き換え可能回数に制限はなく、信頼性が飛躍的に向上する。さらに、トランジスタのオン状態、オフ状態によって、情報の書き込みが行われるため、高速な動作も容易に実現しうる。

【0197】

また、酸化物半導体以外の材料を用いたトランジスタは、十分な高速動作が可能であるため、これを、酸化物半導体を用いたトランジスタと組み合わせて用いることにより、半導体装置の動作(例えば、情報の読み出し動作)の高速性を十分に確保することができる。また、酸化物半導体以外の材料を用いたトランジスタにより、高速動作が要求される各種回路(論理回路、駆動回路など)を好適に実現することが可能である。

【0198】

このように、酸化物半導体以外の材料を用いたトランジスタ(より広義には、十分な高速動作が可能なトランジスタ)と、酸化物半導体を用いたトランジスタ(より広義には、十分にオフ電流が小さいトランジスタ)とを一体に備えることで、これまでにない特徴を有する半導体装置を実現することができる。

【0199】

以上、本実施の形態に示す構成、方法などは、他の実施の形態に示す構成、方法などと適宜組み合わせて用いることができる。

【0200】

(実施の形態4)

本実施の形態では、開示する発明の一態様に係る半導体装置の応用例について、図16を用いて説明する。ここでは、記憶装置の一例について説明する。

【0201】

図16(A)、図16(B)および図16(C)は、図15(A−1)に示す半導体装置(以下、メモリセルとも記載する。)を複数用いて形成される、記憶装置として用いることができる半導体装置の回路図である。図16(A)および図16(B)は、メモリセルが直列に接続された、いわゆるNAND型の半導体装置の回路図であり、図16(C)は、メモリセルが並列に接続された、いわゆるNOR型の半導体装置の回路図である。

【0202】

図16(A)に示す半導体装置は、ソース線SL、ビット線BL、第1信号線S1、m本の第2信号線S2、m本のワード線WL、m個のメモリセルを有する。図16(A)では、ソース線SLおよびビット線BLを1本ずつ有する構成となっているが、これに限られることなく、ソース線SLおよびビット線BLを複数本有する構成としてもよい。

【0203】

各メモリセル(代表として、メモリセル1750(i)を考える。ここで、iは1以上m以下の整数)において、トランジスタ1700(i)のゲート電極と、トランジスタ1710(i)のドレイン電極(またはソース電極)と、容量素子1720(i)の電極の一方とは、電気的に接続されている。また、第1信号線S1とトランジスタ1710(i)のソース電極(またはドレイン電極)とは、電気的に接続され、第2信号線S2(i)と、トランジスタ1710(i)のゲート電極とは、電気的に接続されている。そして、ワード線WL(i)と、容量素子1720(i)の電極の他方は電気的に接続されている。

【0204】

また、メモリセル1750(i)が有するトランジスタ1700(i)のソース電極は、隣接するメモリセル1750(i−1)が有するトランジスタ1700(i−1)のドレイン電極と電気的に接続され、メモリセル1750(i)が有するトランジスタ1700(i)のドレイン電極は、隣接するメモリセル1750(i+1)が有するトランジスタ1700(i+1)のソース電極と電気的に接続される。ただし、直列に接続されたm個のメモリセルのうち、メモリセル1750(1)が有するトランジスタ1700(1)のドレイン電極は、ビット線BLと電気的に接続される。また、直列に接続されたm個のメモリセルのうち、メモリセル1750(m)が有するトランジスタ1700(m)のソース電極は、ソース線SLと電気的に接続される。

【0205】

メモリセル1750(1)が有するトランジスタ1700(1)は、選択トランジスタを介してビット線BLと電気的に接続されていてもよい(図示せず)。この場合、選択トランジスタのゲート電極には、選択線G(1)が接続される。また、メモリセル1750(m)が有するトランジスタ1700(m)も、選択トランジスタを介してソース線SLと電気的に接続されていてもよい(図示せず)。この場合、選択トランジスタのゲート電極には、選択線G(2)が接続される。

【0206】

図16(A)に示す半導体装置では、行ごとの書き込み動作および読み出し動作を行う。書き込み動作は次のように行われる。書き込みを行う行(例えば第i行)の第2信号線S2(i)にトランジスタ1710(i)がオン状態となる電位を与え、書き込みを行う行のトランジスタ1710(i)をオン状態にする。これにより、指定した行のトランジスタ1700(i)のゲート電極に第1信号線S1(i)の電位が与えられ、該ゲート電極に所定の電荷が与えられる。このようにして、指定した行のメモリセルにデータを書き込むことができる。

【0207】

また、読み出し動作は次のように行われる。読み出しを行う行(例えば、第i行)以外のワード線WLに、トランジスタ1700(i)のゲート電極に与えられた電荷によらず、読み出しを行う行以外のトランジスタ1700がオン状態となるような電位を与え、読み出しを行う行以外のトランジスタ1700をオン状態とする。それから、読み出しを行う行のワード線WL(i)に、トランジスタ1700(i)のゲート電極が有する電荷がどのデータに対応するかによって、トランジスタ1700(i)のオン状態またはオフ状態が選択されるような電位(読み出し電位)を与える。また、ソース線SLに定電位を与え、ビット線BLに接続されている読み出し回路(図示しない)を動作状態とする。ここで、ソース線SL−ビット線BL間の複数のトランジスタ1700(1)〜1700(m)のうち、読み出しを行う行のトランジスタ1700(i)を除いてオン状態となっているため、ソース線SL−ビット線BL間のコンダクタンスの大小は、読み出しを行う行のトランジスタ1700(i)の状態(オン状態またはオフ状態)によって決定される。読み出しを行う行のトランジスタ1700(i)のゲート電極が有する電荷がどのデータに対応するかによって、トランジスタの状態(オン状態またはオフ状態)は異なるから、それに応じて、ビット線BLの電位は異なる値をとることになる。ビット線BLの電位を読み出し回路によって読み出すことで、指定した行のメモリセルから情報を読み出すことができる。

【0208】

しかしながら、メモリセルを構成するトランジスタ(例えば、トランジスタ1700(i))のしきい値電圧にばらつきがあると、当該トランジスタのしきい値電圧のばらつきに起因して、複数のメモリセルそれぞれを動作するために必要な電位(メモリセルのしきい値電圧ともいう)にもばらつきが生じる。例えば、トランジスタ1700(i)のしきい値電圧にばらつきがあると、情報を読み出す際のメモリセルのしきい値電圧にもばらつきが生じる。そのため複数のメモリセルそれぞれの動作電圧は、メモリセルのしきい値電圧のばらつきを考慮して幅をもたせて設定される。そのためメモリセルの動作電圧の低減には限界があった。

【0209】

開示する発明の一態様に係る半導体装置では、実施の形態1において図1乃至図5に示したように、書き込みデータ電位が順次別の電位に変更され、書き込み、読み出し、ベリファイ処理が行われ、複数のメモリセルの書き込みデータ電位が決定される。これにより、書き込み後の半導体装置のメモリセルのしきい値電圧のばらつき(分布幅)を小さくし、動作電圧を低減する、または記憶容量を増大する、または書き込み、保持、読み出し等の動作を確実に行える半導体装置およびその駆動方法を提供することができる。

【0210】

なお、図16(A)に示す第1信号線S1は、実施の形態1において図1に示す第2の信号線122に相当する。図16(A)に示すビット線BLは、実施の形態1において図1に示す第3の信号線125に相当する。

【0211】

図16(B)に示す半導体装置は、図16(A)と一部構成が異なる半導体装置である。

【0212】

図16(B)に示す半導体装置と図16(A)に示す半導体装置との相違点の一として、図16(B)に示す半導体装置では、ビット線BLと、メモリセル1750(1)が有するトランジスタ1700(1)のドレイン電極とが、選択トランジスタ1730を介して電気的に接続されている点が挙げられる。選択トランジスタ1730はゲート電極において、選択トランジスタ1730のオンオフを切り替えるための選択線G(1)と電気的に接続されている。

【0213】

また、図16(B)に示す半導体装置と図16(A)に示す半導体装置との相違点の一として、図16(A)に示す半導体装置においては、各メモリセルのトランジスタ1710はソース電極(またはドレイン電極)が第1信号線S1に接続されているのに対して、図16(B)に示す半導体装置においては、各メモリセルのトランジスタ1710は直列に接続されている点が挙げられる。つまり、メモリセル1750(i)が有するトランジスタ1710(i)のソース電極は、隣接するメモリセル1750(i−1)が有するトランジスタ1710(i−1)のドレイン電極と電気的に接続され、メモリセル1750(i)が有するトランジスタ1710(i)のドレイン電極は、隣接するメモリセル1750(i+1)が有するトランジスタ1710(i+1)のソース電極と電気的に接続される。ただし、直列に接続されたm個のメモリセルのうち、メモリセル1750(1)が有するトランジスタ1710(1)のソース電極は、第1信号線S1と電気的に接続される。また、直列に接続された各メモリセルにおいて、トランジスタ1710(i)のドレイン電極(またはソース電極)は、図16(A)に示す半導体装置と同様に、トランジスタ1700(i)のゲート電極と、容量素子1720(i)の電極の一方と電気的に接続される。

【0214】

図16(B)に示す半導体装置の他の部分の構成については、図16(A)に示す半導体装置と同様なので、詳細については上述の記載を参照することができる。

【0215】

なお、図16(B)に示す半導体装置において、第1信号線S1とビット線BLは別々に設けられているが、開示する発明はこれに限られるものではなく、第1信号線S1とビット線BLを同一の配線とする構成としても良い。

【0216】

図16(B)に示す半導体装置でも、行ごとの書き込み動作および読み出し動作を行う。書き込み動作は次のように行われる。

【0217】

書き込み動作は、行ごとに第1行から第m行まで順番に行われる。第i行(i=1〜m)の書き込みを行う場合には、書き込みを行う行(第i行)の第2信号線S2(i)にトランジスタ1710(i)がオン状態となる電位を与え、書き込みを行う行のトランジスタ1710(i)をオン状態にする。ここで、トランジスタ1710(i)と第1信号線S1との間にトランジスタ1710(1)からトランジスタ1710(i−1)が存在する場合には、書き込みを行う行までのトランジスタ1710(1)から1710(i−1)もオン状態として、書き込みを行う行のメモリセル1750(i)に第1信号線S1の電位が与えられるようにする。これにより、指定した行のトランジスタ1700(i)のゲート電極に第1信号線S1(i)の電位が与えられ、該ゲート電極に所定の電荷が与えられる。それから、第2信号線S2(i)の電位をGNDに固定すると、トランジスタ1700(i)のゲート電極に蓄積された電荷が保持される。このようにして、指定した行(第i行)のメモリセルにデータを書き込むことができる。

【0218】

なお、図16(B)に示す半導体装置では、各メモリセル1750を構成するトランジスタ1710を直列に接続するため、任意の行のデータのみを書き換えることは困難である。そのため、駆動方法として、複数行の一括消去動作を設けることが好ましい。例えば、第1行から第m行までをブロックとして、ブロック毎の消去を行うことが好ましい。所定のブロックのデータを書き換える場合には、まず当該ブロックのデータを消去して、第1行から第m行まで順番にデータを書き込むとよい。なお、直前に書き込んだ行のデータを書き換える場合には、消去動作は不要である。

【0219】

また、読み出し動作は次のように行われる。まず、選択線G1に電位を与えることにより、選択トランジスタをオンにする。なお、選択線G1に接続される選択トランジスタと、選択線G2に接続される選択トランジスタがある場合には、2つのトランジスタをオン状態とする。また、読み出しを行う行(例えば、第i行)以外のワード線WLに、トランジスタ1700(i)のゲート電極に与えられた電位によらず、読み出しを行う行以外のトランジスタ1700がオン状態となるような電位を与え、読み出しを行う行以外のトランジスタ1700をオン状態とする。それから、読み出しを行う行のワード線WL(i)に、トランジスタ1700(i)のゲート電極が有する電荷がどのデータに対応するかによって、トランジスタ1700(i)のオン状態またはオフ状態が選択されるような電位(読み出し電位)を与える。また、ソース線SLに定電位を与え、ビット線BLに接続されている読み出し回路(図示しない)を動作状態とする。ここで、ソース線SL−ビット線BL間の複数のトランジスタ1700(1)〜1700(m)のうち、読み出しを行う行のトランジスタ1700(i)を除いてオン状態となっているため、ソース線SL−ビット線BL間のコンダクタンスの大小は、読み出しを行う行のトランジスタ1700(i)の状態(オン状態またはオフ状態)によって決定される。読み出しを行う行のトランジスタ1700(i)のゲート電極が有する電荷がどのデータに対応するかによって、トランジスタの状態(オン状態またはオフ状態)は異なるから、それに応じて、ビット線BLの電位は異なる値をとることになる。ビット線の電位を読み出し回路によって読み出すことで、指定した行のメモリセルから情報を読み出すことができる。

【0220】

図16(B)に示す半導体装置においても、実施の形態1において図1乃至図5に示したように、書き込みデータ電位が順次別の電位に変更され、書き込み、読み出し、ベリファイ処理が行われ、複数のメモリセルの書き込みデータ電位が決定される。これにより、書き込み後の半導体装置のメモリセルのしきい値電圧のばらつき(分布幅)を小さくし、動作電圧を低減する、または記憶容量を増大する、または書き込み、保持、読み出し等の動作を確実に行える半導体装置およびその駆動方法を提供することができる。

【0221】

なお、図16(B)に示す第1信号線S1は、実施の形態1において図1に示す第2の信号線122に相当する。図16(B)に示すビット線BLは、実施の形態1において図1に示す第3の信号線125に相当する。

【0222】

図16(C)に示す半導体装置は、ソース線SL、ビット線BLおよび第1信号線S1をそれぞれn本有し、第2信号線S2およびワード線WLをそれぞれm本有し、複数のメモリセル1750(1,1)〜1750(m,n)を有する。

【0223】

各メモリセル(代表として、メモリセル1750(i,j)を考える。ここで、iは1以上m以下の整数、jは1以上n以下の整数)は、トランジスタ1700(i,j)のゲート電極と、トランジスタ1710(i,j)のドレイン電極(またはソース電極)と、容量素子1720(i,j)の電極の一方とは、電気的に接続されている。また、ソース線SL(j)とトランジスタ1700(i,j)のソース電極とは、電気的に接続され、ビット線BL(j)とトランジスタ1700(i,j)のドレイン電極とは、電気的に接続されている。また、第1信号線S1(j)とトランジスタ1710(i,j)のソース電極(またはドレイン電極)とは、電気的に接続され、第2信号線S2(i)と、トランジスタ1710(i,j)のゲート電極とは、電気的に接続されている。そして、ワード線WL(i)と、容量素子1720(i,j)の電極の他方は電気的に接続されている。

【0224】

図16(C)に示す半導体装置では、行ごとの書き込み動作および読み出し動作を行う。書き込み動作は、上述の図16(A)に示す半導体装置と同様の方法で行われる。読み出し動作は次のように行われる。まず、読み出しを行う行(例えば、第i行のメモリセル(i,1)〜(i,n))以外のワード線WLに、トランジスタ1700(i,1)〜(i,n)のゲート電極に与えられた電荷がどのデータに対応するかによらず、読み出しを行う行以外のトランジスタ1700がオフ状態となるような電位を与え、読み出しを行う行以外のトランジスタ1700をオフ状態とする。それから、読み出しを行う行のワード線WL(i)に、トランジスタ1700(i,1)〜(i,n)のゲート電極が有する電荷がどのデータに対応するかによってトランジスタ1700(i,1)〜(i,n)のオン状態またはオフ状態が選択されるような電位(読み出し電位)を与える。また、ソース線SL(j)に定電位を与え、ビット線BL(j)に接続されている読み出し回路(図示しない)を動作状態とする。ここで、ソース線SL(j)−ビット線BL(j)間のコンダクタンスの大小は、読み出しを行う行のトランジスタ1700(i,1)〜(i,n)の状態(オン状態またはオフ状態)によって決定される。つまり、読み出しを行う行のトランジスタ1700(i,1)〜(i,n)のゲート電極が有する電荷がどのデータに対応するかによって、ビット線BL(j)の電位は異なる値をとることになる。ビット線BL(j)の電位を読み出し回路によって読み出すことで、指定した行のメモリセルから情報を読み出すことができる。

【0225】

図16(C)に示す半導体装置においても、図1乃至図5に示したように、書き込みデータ電位が順次別の電位に変更され、書き込み、読み出し、ベリファイ処理が行われ、複数のメモリセルの書き込みデータ電位が決定される。これにより、書き込み後の半導体装置のメモリセルのしきい値電圧のばらつき(分布幅)を小さくし、動作電圧を低減する、または記憶容量を増大する、または書き込み、保持、読み出し等の動作を確実に行える半導体装置およびその駆動方法を提供することができる。

【0226】

なお、図16(C)に示す第1信号線S1は、図1に示す第2の信号線122に相当する。図16(C)に示すビット線BLは、図1に示す第3の信号線125に相当する。

【0227】

なお、上記においては、各メモリセル1750に保持させる情報量を1ビットとしたが、本実施の形態に示す半導体装置の構成はこれに限られない。書き込み時に各トランジスタ1700のゲート電極に与える電位を3種類以上用意して、各メモリセル1750が保持する情報量を増加させても良い。例えば、書き込み時に各トランジスタ1700のゲート電極にあたえる電位を4種類とする場合には、各メモリセルに2ビットの情報を保持させることができる。

【0228】

図16において、第1信号線S1とビット線BLは、兼用してもよい。第1信号線S1とビット線BLを兼用することにより、配線数を低減することができる。また、図16(C)において、ソース線SLは共通化してもよい。

【0229】

開示する発明に係る半導体装置では、メモリセルを構成するトランジスタのしきい値電圧にばらつきがあっても、書き込み後の複数のメモリセルのしきい値電圧のばらつき(分布幅)を小さくすることができ、半導体装置の動作電圧を低減することができる。または、動作電圧を増大させずかつメモリセルの面積を増大させずに、メモリセルを多値化することができ、半導体装置の単位面積あたりの記憶容量を増大することができる。または、書き込み、保持、読み出し等の動作を確実に行える半導体装置を提供することができる。

【0230】

以上、本実施の形態に示す構成、方法などは、他の実施の形態に示す構成、方法などと適宜組み合わせて用いることができる。

【0231】

(実施の形態5)

本実施の形態では、開示する発明の一態様に係る半導体装置が有するメモリセルの構成およびその作製方法について、図17乃至図21、図22を参照して説明する。

【0232】

<メモリセルの断面構成及び平面図>

図17は、半導体装置が有するメモリセルの構成の一例である。図17(A)には半導体装置が有するメモリセルの断面を、図17(B)には半導体装置が有するメモリセルの平面を、それぞれ示す。図17(A)において、A1−A2は、トランジスタのチャネル長方向に垂直な断面図であり、B1−B2は、トランジスタのチャネル長方向に平行な断面図である。図17に示す半導体装置は、下部に第1の半導体材料を用いたトランジスタ1860を有し、上部に第2の半導体材料を用いたトランジスタ1862を有する。また、図17に示す半導体装置は、トランジスタ1860とトランジスタ1862と容量素子1864とを、一つずつ有する構成として示しているが、それぞれ複数有する構成も含む。

【0233】

ここで、第1の半導体材料と第2の半導体材料とは異なる材料とすることが望ましい。例えば、第1の半導体材料を酸化物半導体以外の半導体材料とし、第2の半導体材料を酸化物半導体とすることができる。酸化物半導体以外の半導体材料としては、例えば、シリコン、ゲルマニウム、シリコンゲルマニウム、炭化シリコン、またはガリウムヒ素等を用いることができ、単結晶半導体を用いることが好ましい。他に、有機半導体材料などを用いてもよい。このような半導体材料を用いたトランジスタは、高速動作が容易である。一方で、酸化物半導体を用いたトランジスタは、オフ電流が非常に小さいという特性により長時間の電荷保持を可能とする。

【0234】

トランジスタ1860およびトランジスタ1862は、nチャネル型トランジスタ、pチャネル型トランジスタのいずれも用いることができる。ここでは、トランジスタ1860およびトランジスタ1862は、いずれもnチャネル型トランジスタとして説明する。また、本発明の一態様において、技術的な本質は、情報を保持するために酸化物半導体のようなオフ電流を十分に低減することが可能な半導体材料をトランジスタ1862に用いる点にあるから、半導体装置に用いられる材料や半導体装置の構造など、半導体装置の具体的な構成をここで示すものに限定する必要はない。

【0235】

トランジスタ1860は、半導体材料(例えば、シリコンなど)を含む基板1800に設けられたチャネル形成領域1816と、チャネル形成領域1816を挟むように設けられた不純物領域1820(ソース領域またはドレイン領域とも記す)と、不純物領域1820に接する金属化合物領域1824と、チャネル形成領域1816上に設けられたゲート絶縁層1808と、ゲート絶縁層1808上に設けられたゲート電極1810と、を有する。なお、図17において、明示的にはソース電極やドレイン電極を有しない場合があるが、便宜上、このような状態を含めてトランジスタと呼ぶ場合がある。また、この場合、トランジスタの接続関係を説明するために、ソース領域やドレイン領域を含めてソース電極やドレイン電極と表現することがある。つまり、本明細書において、ソース電極との記載には、ソース領域が含まれうる。

【0236】

トランジスタ1860の金属化合物領域1824の一部には、電極1826が接続されている。ここで、電極1826は、トランジスタ1860のソース電極やドレイン電極として機能する。また、基板1800上にはトランジスタ1860を囲むように素子分離絶縁層1806が設けられており、トランジスタ1860上に絶縁層1828が設けられている。なお、高集積化を実現するためには、図17に示すように、トランジスタ1860がサイドウォール絶縁層を有しない構成とすることが望ましい。一方で、トランジスタ1860の特性を重視する場合には、ゲート電極1810の側面にサイドウォール絶縁層を設け、そのサイドウォール絶縁層と重畳する領域に形成された不純物濃度が異なる領域を含めて不純物領域1820を設けても良い。

【0237】

トランジスタ1862は、絶縁層1828などの上に設けられた酸化物半導体層1844と、酸化物半導体層1844と電気的に接続されているソース電極またはドレイン電極1842a、およびソース電極またはドレイン電極1842bと、酸化物半導体層1844、ソース電極またはドレイン電極1842a、およびソース電極またはドレイン電極1842b、を覆うゲート絶縁層1846と、ゲート絶縁層1846上に酸化物半導体層1844と重畳するように設けられたゲート電極1848aと、を有する。

【0238】

ここで、トランジスタ1862に用いられる酸化物半導体層1844は水素などの不純物が十分に除去されることにより、または、十分な酸素が供給されることにより、高純度化されたものであることが望ましい。例えば、酸化物半導体層1844の水素濃度は5×1019atoms/cm3以下、望ましくは5×1018atoms/cm3以下、より望ましくは5×1017atoms/cm3以下とする。なお、上述の酸化物半導体層1844中の水素濃度は、二次イオン質量分析法(SIMS:Secondary Ion Mass Spectrometry)で測定されるものである。このように、水素濃度が十分に低減されて高純度化され、十分な酸素の供給により酸素欠乏に起因するエネルギーギャップ中の欠陥準位が低減された酸化物半導体層1844では、キャリア濃度が1×1012/cm3未満、望ましくは、1×1011/cm3未満、より望ましくは1.45×1010/cm3未満となる。例えば、室温(25℃)でのオフ電流(ここでは、単位チャネル幅(1μm)あたりの値)は100zA(1zA(ゼプトアンペア)は1×10−21A)以下、望ましくは10zA以下となる。このように、i型化(真性化)または実質的にi型化された酸化物半導体層1844を用いることで、極めて優れたオフ電流特性のトランジスタ1862を得ることができる。

【0239】

なお、トランジスタ1862では、微細化に起因して素子間に生じるリークを抑制するために、島状に加工された酸化物半導体層を用いているが、島状に加工されていない酸化物半導体層を採用しても良い。酸化物半導体層を島状に加工しない場合には、加工の際のエッチングによる酸化物半導体層の汚染を防止できる。

【0240】

容量素子1864は、ソース電極またはドレイン電極1842a、ゲート絶縁層1846、および導電層1848b、とで構成される。すなわち、ソース電極またはドレイン電極1842aは、容量素子1864の一方の電極として機能し、導電層1848bは、容量素子1864の他方の電極として機能することになる。このような構成とすることにより、十分な容量を確保することができる。また、酸化物半導体層1844とゲート絶縁層1846とを積層させる場合には、ソース電極またはドレイン電極1842aと、導電層1848bとの絶縁性を十分に確保することができる。さらに、容量が不要の場合は、容量素子1864を設けない構成とすることもできる。

【0241】

なお、トランジスタ1862および容量素子1864において、ソース電極またはドレイン電極1842a、およびソース電極またはドレイン電極1842bの端部は、テーパー形状であることが好ましい。ソース電極またはドレイン電極1842a、ソース電極またはドレイン電極1842bの端部をテーパー形状とすることにより、ゲート絶縁層1846の被覆性を向上させ、段切れを防止することができる。ここで、テーパー角は、例えば、30°以上60°以下とする。なお、テーパー角とは、テーパー形状を有する層(例えば、ソース電極またはドレイン電極1842a)を、その断面(基板の表面と直交する面)に垂直な方向から観察した際に、当該層の側面と底面がなす傾斜角を示す。

【0242】

トランジスタ1862および容量素子1864の上には絶縁層1850および絶縁層1852が設けられている。そして、ゲート絶縁層1846、絶縁層1850、絶縁層1852などに形成された開口には、電極1854が設けられ、絶縁層1852上には、電極1854と接続する配線1856が形成される。なお、図17では電極1826および電極1854を用いて、金属化合物領域1824、ソース電極またはドレイン電極1842b、および配線1856を接続しているが、本発明の一態様はこれに限定されない。例えば、ソース電極またはドレイン電極1842bを直接、金属化合物領域1824に接触させても良い。または、配線1856を直接、ソース電極またはソース電極またはドレイン電極1842bに接触させても良い。

【0243】

また、図17において、金属化合物領域1824とソース電極またはドレイン電極1842bを接続する電極1826と、ソース電極またはドレイン電極1842bと配線1856を接続する電極1854とは重畳して配置されている。つまり、トランジスタ1860のソース電極やドレイン電極として機能する電極1826と、トランジスタ1862のソース電極またはドレイン電極1842bと、が接する領域は、トランジスタ1862のソース電極またはドレイン電極1842bと、メモリセルの一と他のメモリセルとを接続する電極1854と、が接する領域と重なっている。このような平面レイアウトを採用することにより、コンタクト領域に起因する素子面積の増大を抑制することができる。つまり、半導体装置の集積度を高めることができる。

【0244】

また、図17において、トランジスタ1860と、トランジスタ1862とは、少なくとも一部が重畳するように設けられている。また、トランジスタ1862や容量素子1864が、トランジスタ1860と重畳するように設けられている。例えば、容量素子1864の導電層1848bは、トランジスタ1860のゲート電極1810と少なくとも一部が重畳して設けられている。このような、平面レイアウトを採用することにより、高集積化を図ることができる。例えば、最小加工寸法をFとして、メモリセルの占める面積を15F2〜25F2とすることが可能である。

【0245】

<半導体装置が有するメモリセルの作製方法>

次に、上記半導体装置が有するメモリセルの作製方法の一例について説明する。以下では、はじめに下部のトランジスタ1860の作製方法について図18および図19を参照して説明し、その後、上部のトランジスタ1862および容量素子1864の作製方法について図20および図21を参照して説明する。

【0246】

<下部のトランジスタの作製方法>

下部のトランジスタ1860の作製方法について、図18および図19を参照して説明する。

【0247】

まず、半導体材料を含む基板1800を用意する。半導体材料を含む基板としては、シリコンや炭化シリコンなどの単結晶半導体基板、多結晶半導体基板、シリコンゲルマニウムなどの化合物半導体基板、SOI基板などを適用することができる。ここでは、半導体材料を含む基板1800として、単結晶シリコン基板を用いる場合の一例について示すものとする。なお、一般に「SOI基板」は、絶縁表面上にシリコン半導体層が設けられた構成の基板をいうが、本明細書等においては、絶縁表面上にシリコン以外の材料からなる半導体層が設けられた構成の基板も含むものとする。つまり、「SOI基板」が有する半導体層は、シリコン半導体層に限定されない。また、SOI基板には、ガラス基板などの絶縁基板上に絶縁層を介して半導体層が設けられた構成のものが含まれるものとする。

【0248】

半導体材料を含む基板1800として、シリコンなどの単結晶半導体基板を用いる場合には、半導体装置の読み出し動作を高速化することができるため好適である。

【0249】

基板1800上には、素子分離絶縁層を形成するためのマスクとなる保護層1802を形成する(図18(A)参照)。保護層1802としては、例えば、酸化シリコンや窒化シリコン、酸窒化シリコンなどを材料とする絶縁層を用いることができる。なお、この工程の前後において、トランジスタのしきい値電圧を制御するために、n型の導電性を付与する不純物元素やp型の導電性を付与する不純物元素を基板1800に添加してもよい。半導体がシリコンの場合、n型の導電性を付与する不純物元素としては、例えば、リンや砒素などを用いることができる。また、p型の導電性を付与する不純物元素としては、例えば、硼素、アルミニウム、ガリウムなどを用いることができる。

【0250】

次に、上記の保護層1802をマスクとしてエッチングを行い、保護層1802に覆われていない領域(露出している領域)の、基板1800の一部を除去する。これにより他の半導体領域と分離された半導体領域1804が形成される(図18(B)参照)。当該エッチングには、ドライエッチングを用いるのが好適であるが、ウェットエッチングを用いても良い。エッチングガスやエッチング液については被エッチング材料に応じて適宜選択することができる。

【0251】

次に、半導体領域1804を覆うように絶縁層を形成し、半導体領域1804に重畳する領域の絶縁層を選択的に除去することで、素子分離絶縁層1806を形成する(図18(C)参照)。当該絶縁層は、酸化シリコンや窒化シリコン、酸窒化シリコンなどを用いて形成される。絶縁層の除去方法としては、CMP(化学的機械的研磨)などの研磨処理やエッチング処理などがあるが、そのいずれを用いても良い。なお、半導体領域1804の形成後、または、素子分離絶縁層1806の形成後には、上記保護層1802を除去する。

【0252】

ここで、CMP処理とは、被加工物の表面を基準にし、それにならって表面を化学的・機械的な複合作用により平坦化する手法である。より具体的には、研磨ステージの上に研磨布を貼り付け、被加工物と研磨布との間にスラリー(研磨剤)を供給しながら研磨ステージと被加工物とを各々回転または揺動させて、被研磨物の表面を、スラリーと被研磨物表面との間での化学反応と、研磨布と被研磨物との機械的研磨の作用により、被加工物の表面を研磨する方法である。

【0253】

なお、素子分離絶縁層1806の形成方法として、絶縁層を選択的に除去する方法の他、酸素を打ち込むことにより絶縁性の領域を形成する方法などを用いることもできる。

【0254】

次に、半導体領域1804の表面に絶縁層を形成し、当該絶縁層上に導電材料を含む層を形成する。

【0255】

絶縁層は後のゲート絶縁層となるものであり、例えば、半導体領域1804表面の熱処理(熱酸化処理や熱窒化処理など)によって形成することができる。熱処理に代えて、高密度プラズマ処理を適用しても良い。高密度プラズマ処理は、例えば、He、Ar、Kr、Xeなどの希ガス、酸素、酸化窒素、アンモニア、窒素、水素などのうちいずれかの混合ガスを用いて行うことができる。もちろん、CVD法やスパッタリング法等を用いて絶縁層を形成しても良い。当該絶縁層は、酸化シリコン、酸窒化シリコン、窒化シリコン、酸化ハフニウム、酸化アルミニウム、酸化タンタル、酸化イットリウム、ハフニウムシリケート(HfSixOy(x>0、y>0))、窒素が添加されたハフニウムシリケート(HfSixOy(x>0、y>0))、窒素が添加されたハフニウムアルミネート(HfAlxOy(x>0、y>0))等を含む単層構造または積層構造とすることが望ましい。また、絶縁層の厚さは、例えば、1nm以上100nm以下、好ましくは10nm以上50nm以下とすることができる。

【0256】

導電材料を含む層は、アルミニウムや銅、チタン、タンタル、タングステン等の金属材料を用いて形成することができる。また、多結晶シリコンなどの半導体材料を用いて、導電材料を含む層を形成しても良い。形成方法も特に限定されず、蒸着法、CVD法、スパッタリング法、スピンコート法などの各種成膜方法を用いることができる。なお、本実施の形態では、導電材料を含む層を、金属材料を用いて形成する場合の一例について示すものとする。

【0257】

その後、絶縁層および導電材料を含む層を選択的にエッチングして、ゲート絶縁層1808、ゲート電極1810を形成する(図18(C)参照)。

【0258】

次に、半導体領域1804にリン(P)やヒ素(As)などを添加して、チャネル形成領域1816および不純物領域1820を形成する(図18(D)参照)。なお、ここではn型トランジスタを形成するためにリンやヒ素を添加しているが、p型トランジスタを形成する場合には、硼素(B)やアルミニウム(Al)などの不純物元素を添加すればよい。ここで、添加する不純物の濃度は適宜設定することができるが、半導体素子が高度に微細化される場合には、その濃度を高くすることが望ましい。

【0259】

なお、ゲート電極1810の周囲にサイドウォール絶縁層を形成して、不純物元素が異なる濃度で添加された不純物領域を形成しても良い。

【0260】

次に、ゲート電極1810、不純物領域1820等を覆うように金属層1822を形成する(図19(A)参照)。当該金属層1822は、真空蒸着法やスパッタリング法、スピンコート法などの各種成膜方法を用いて形成することができる。金属層1822は、半導体領域1804を構成する半導体材料と反応することによって低抵抗な金属化合物となる金属材料を用いて形成することが望ましい。このような金属材料としては、例えば、チタン、タンタル、タングステン、ニッケル、コバルト、白金等がある。

【0261】

次に、熱処理を施して、上記金属層1822と半導体材料とを反応させる。これにより、不純物領域1820に接する金属化合物領域1824が形成される(図19(A)参照)。なお、ゲート電極1810として多結晶シリコンなどを用いる場合には、ゲート電極1810の金属層1822と接触する部分にも、金属化合物領域が形成されることになる。

【0262】

上記熱処理としては、例えば、フラッシュランプの照射による熱処理を用いることができる。もちろん、その他の熱処理方法を用いても良いが、金属化合物の形成に係る化学反応の制御性を向上させるためには、ごく短時間の熱処理を実現できる方法を用いることが望ましい。なお、上記の金属化合物領域は、金属材料と半導体材料との反応により形成されるものであり、十分に導電性が高められた領域である。当該金属化合物領域を形成することで、電気抵抗を十分に低減し、素子特性を向上させることができる。なお、金属化合物領域1824を形成した後には、金属層1822は除去する。

【0263】

次に、金属化合物領域1824の一部と接する領域に、電極1826を形成する(図19(B)参照)。電極1826は、例えば、導電材料を含む層を形成した後に、当該層を選択的にエッチングすることで形成される。導電材料を含む層は、アルミニウムや銅、チタン、タンタル、タングステン等の金属材料を用いて形成することができる。また、多結晶シリコンなどの半導体材料を用いて、導電材料を含む層を形成しても良い。形成方法も特に限定されず、蒸着法、CVD法、スパッタリング法、スピンコート法などの各種成膜方法を用いることができる。

【0264】

次に、上述の工程により形成された各構成を覆うように、絶縁層1828を形成する(図19(C)参照)。絶縁層1828は、酸化シリコン、酸窒化シリコン、窒化シリコン、酸化アルミニウム等の無機絶縁材料を含む材料を用いて形成することができる。特に、絶縁層1828に誘電率の低い(low−k)材料を用いることで、各種電極や配線の重なりに起因する容量を十分に低減することが可能になるため好ましい。なお、絶縁層1828には、これらの材料を用いた多孔性の絶縁層を適用しても良い。多孔性の絶縁層では、密度の高い絶縁層と比較して誘電率が低下するため、電極や配線に起因する容量をさらに低減することが可能である。また、絶縁層1828は、ポリイミド、アクリル等の有機絶縁材料を用いて形成することも可能である。なお、ここでは、絶縁層1828の単層構造としているが、本発明の一態様はこれに限定されない。2層以上の積層構造としても良い。3層構造とする場合には、例えば、酸化窒化シリコン層と、窒化酸化シリコン層と、酸化シリコン層の積層構造とすることができる。

【0265】

なお、電極1826は、絶縁層1828を形成した後に、絶縁層1828に金属化合物領域1824にまで達する開口を形成し、当該開口を埋め込むように形成することも可能である。

【0266】

この場合、例えば、開口を含む領域にPVD法によりチタン膜を薄く形成し、CVD法により窒化チタン膜を薄く形成した後に、開口に埋め込むようにタングステン膜を形成する方法を適用することができる。ここで、PVD法により形成されるチタン膜は、被形成面の酸化膜(自然酸化膜など)を還元し、下部電極など(ここでは金属化合物領域1824)との接触抵抗を低減させる機能を有する。また、その後に形成される窒化チタン膜は、導電性材料の拡散を抑制するバリア機能を備える。また、チタンや窒化チタンなどによるバリア膜を形成した後に、メッキ法により銅膜を形成してもよい。

【0267】

以上により、半導体材料を含む基板1800を用いたトランジスタ1860が形成される(図19(C)参照)。このようなトランジスタ1860は、高速動作が可能であるという特徴を有する。このため、当該トランジスタを読み出し用のトランジスタとして用いることで、情報の読み出しを高速に行うことができる。

【0268】

その後、トランジスタ1862および容量素子1864の形成前の処理として、絶縁層1828にCMP処理を施して、ゲート電極1810および電極1826の上面を露出させる(図19(D)参照)。ゲート電極1810および電極1826の上面を露出させる処理としては、CMP処理の他にエッチング処理などを適用することも可能であるが、トランジスタ1862の特性を向上させるために、絶縁層1828の表面は可能な限り平坦にしておくことが望ましく、絶縁層1828の平均面荒さ(Ra)は0.1nm以上0.5nm未満であることが好ましい。酸化物半導体膜が結晶性である場合に結晶方位を揃えることができるためである。

【0269】

なお、ここで、平均面粗さ(Ra)とは、JISB0601:2001(ISO4287:1997)で定義されている中心線平均粗さ(Ra)を、測定面に対して適用できるよう三次元に拡張したものをいう。平均面粗さ(Ra)は、基準面から指定面までの偏差の絶対値を平均した値で表現される。

【0270】

なお、絶縁層1828を平坦化させるためには、CMP処理に代えてドライエッチングなどを行ってもよい。ここで、エッチングガスとしては、塩素、塩化ボロン、塩化シリコンまたは四塩化炭素などの塩素系ガス、四フッ化炭素、フッ化硫黄またはフッ化窒素などのフッ素系ガスなどを用いればよい。

【0271】

また、絶縁層1828を平坦化させるためには、CMP処理に代えてプラズマ処理などを行ってもよい。ここで、プラズマ処理には希ガスを用いればよい。このプラズマ処理により、被処理面に不活性ガスのイオンが照射され、スパッタリング効果により被処理面の微細な凹凸が平坦化される。このようなプラズマ処理は逆スパッタとも呼ばれる。

【0272】

なお、絶縁層1828を平坦化するためには、前記処理の一種以上を適用すればよい。例えば、逆スパッタのみを行ってもよいし、CMP処理を行った後にドライエッチングを行ってもよい。ただし、酸化物半導体膜の被形成面である絶縁層1828に水を混入させないためには、ドライエッチングまたは逆スパッタを用いることが好ましい。特に、第2の加熱処理を行った後に平坦化処理を行う場合にはドライエッチングまたは逆スパッタを用いることが好ましい。CMP処理では絶縁層1828を研磨する際にスラリー等の溶液を使用するため、処理後には十分な洗浄処理および乾燥処理を行うことが好ましい。

【0273】

なお、上記の各工程の前後には、さらに電極や配線、半導体層、絶縁層などを形成する工程を含んでいても良い。例えば、配線の構造として、絶縁層および導電層の積層構造でなる多層配線構造を採用して、高度に集積化した半導体装置を実現することも可能である。

【0274】

<上部のトランジスタの作製方法>

次に、上部のトランジスタ1862および容量素子1864の作製方法について、図20および図21を参照して説明する。

【0275】

まず、ゲート電極1810、電極1826、絶縁層1828などの上に酸化物半導体膜を形成し、当該酸化物半導体膜を加工して、酸化物半導体層1844を形成する(図20(A)参照)。なお、酸化物半導体膜を形成する前に、ゲート電極1810、電極1826、絶縁層1828の上に、下地として機能する絶縁層を設けても良い。当該絶縁層は、スパッタリング法をはじめとするPVD法やプラズマCVD法などのCVD法などを用いて形成することができる。

【0276】

酸化物半導体膜に用いる材料としては、少なくともIn、Ga、Sn及びZnから選ばれた一種以上の元素を含有する。例えば、四元系金属の酸化物であるIn−Sn−Ga−Zn−O系酸化物半導体や、三元系金属の酸化物であるIn−Ga−Zn−O系酸化物半導体、In−Sn−Zn−O系酸化物半導体、In−Al−Zn−O系酸化物半導体、Sn−Ga−Zn−O系酸化物半導体、Al−Ga−Zn−O系酸化物半導体、Sn−Al−Zn−O系酸化物半導体や、二元系金属の酸化物であるIn−Zn−O系酸化物半導体、Sn−Zn−O系酸化物半導体、Al−Zn−O系酸化物半導体、Zn−Mg−O系酸化物半導体、Sn−Mg−O系酸化物半導体、In−Mg−O系酸化物半導体や、In−Ga−O系酸化物半導体、一元系金属の酸化物であるIn−O系酸化物半導体、Sn−O系酸化物半導体、Zn−O系酸化物半導体などを用いることができる。また、上記酸化物半導体にInとGaとSnとZn以外の元素、例えばSiO2を含ませてもよい。

【0277】

例えば、In−Ga−Zn−O系酸化物半導体とは、インジウム(In)、ガリウム(Ga)、亜鉛(Zn)を有する酸化物半導体、という意味であり、その組成比は問わない。

【0278】

また、酸化物半導体膜は、化学式InMO3(ZnO)m(m>0)で表記される薄膜を用いることができる。ここで、Mは、Zn、Ga、Al、Mn及びCoから選ばれた一または複数の金属元素を示す。例えばMとして、Ga、Ga及びAl、Ga及びMn、またはGa及びCoなどがある。

【0279】

また、酸化物半導体膜の厚さは、3nm以上30nm以下とするのが望ましい。酸化物半導体膜を厚くしすぎると(例えば、膜厚を50nm以上)、トランジスタがノーマリーオンとなってしまうおそれがあるためである。

【0280】

酸化物半導体膜は、水素、水、水酸基又は水素化物などの不純物が混入しにくい方法で作製するのが望ましい。例えば、スパッタリング法などを用いて作製することができる。

【0281】

本実施の形態では、スパッタリング法を用いてIn−Ga−Zn−O系の酸化物半導体膜を形成する場合について説明するが、前述の酸化物半導体膜をスパッタリング法以外を用いて形成しても良い。

【0282】

なお、In−Ga−Zn−O系の酸化物ターゲットとしては、In2O3:Ga2O3:ZnO=1:x:y(xは0以上、yは0.5以上5以下)の組成式で表されるものを用いるのが好適である。例えば、In2O3:Ga2O3:ZnO=1:1:2[mol数比]の組成比を有するターゲットなどを用いることができる。また、In2O3:Ga2O3:ZnO=1:1:1[mol数比]の組成比を有するターゲットや、In2O3:Ga2O3:ZnO=1:1:4[mol数比]の組成比を有するターゲットの組成比を有するターゲットを用いることもできる。

【0283】

また、酸化物半導体としてIn−Zn−O系の材料を用いる場合、用いるターゲットの組成比は、原子数比で、In:Zn=50:1〜1:2(モル数比に換算するとIn2O3:ZnO=25:1〜1:4)、好ましくはIn:Zn=20:1〜1:1(モル数比に換算するとIn2O3:ZnO=10:1〜1:2)、さらに好ましくはIn:Zn=15:1〜1.5:1(モル数比に換算するとIn2O3:ZnO=15:2〜3:4)とする。例えば、In−Zn−O系酸化物半導体の形成に用いるターゲットは、原子数比がIn:Zn:O=X:Y:Zのとき、Z>1.5X+Yとする。

【0284】

また、In−Sn−Zn−O系の材料膜の成膜に用いる酸化物半導体のターゲットの組成比は、In:Sn:Znが原子数比で、1:2:2、2:1:3、1:1:1、或いは20:45:35などを用いることができる。

【0285】

なお、ターゲット中の金属酸化物の相対密度は80%以上、好ましくは95%以上、さらに好ましくは99.9%以上である。相対密度の高いターゲットを用いることにより、緻密な構造の酸化物半導体膜を成膜することが可能である。

【0286】

酸化物半導体膜をスパッタリング法により成膜する際には、例えば、減圧状態に保持された処理室内に被処理物を保持し、被処理物の温度が100℃以上550℃未満、好ましくは200℃以上400℃以下となるように被処理物を熱する。または、酸化物半導体膜の成膜の際の被処理物の温度は、室温としてもよい。そして、処理室内の水分を除去しつつ、水素や水などが除去されたスパッタガスを導入し、上記ターゲットを用いて酸化物半導体膜を成膜する。被処理物を熱しながら酸化物半導体膜を成膜することにより、酸化物半導体膜に含まれる水素や水などの不純物を低減することができる。また、スパッタによる損傷を軽減することができる。処理室内の水分を除去するためには、吸着型の真空ポンプを用いることが好ましい。例えば、クライオポンプ、イオンポンプ、チタンサブリメーションポンプなどを用いることができる。また、ターボポンプにコールドトラップを加えたものを用いてもよい。クライオポンプなどを用いて排気することで、処理室から水分などの不純物を除去することができるため、酸化物半導体膜中の不純物濃度を低減できる。

【0287】

酸化物半導体膜を、スパッタリング法を用いて成膜する場合には、例えば、被処理物とターゲットの間との距離が170mm、圧力が0.4Pa、直流(DC)電力が0.5kW、雰囲気が酸素(酸素100%)雰囲気、またはアルゴン(アルゴン100%)雰囲気、または酸素とアルゴンの混合雰囲気、といった条件を適用することができる。なお、パルス直流(DC)電源を用いると、パーティクル(成膜時に形成される粉状の物質など)を低減でき、膜厚分布も均一となるため好ましい。酸化物半導体膜の厚さは、1nm以上50nm以下、好ましくは1nm以上30nm以下、より好ましくは1nm以上10nm以下とする。このような厚さの酸化物半導体膜を用いることで、微細化に伴う短チャネル効果を抑制することが可能である。ただし、適用する酸化物半導体材料や、半導体装置の用途などにより適切な厚さは異なるから、その厚さは、用いる材料や用途などに応じて選択することもできる。

【0288】

なお、酸化物半導体膜をスパッタリング法により成膜する前には、アルゴンガスを導入してプラズマを発生させる逆スパッタを行い、成膜表面(例えば絶縁層1828の表面)の付着物を除去するのが好ましい。ここで、逆スパッタとは、通常のスパッタリング法においては、スパッタターゲットにイオンを衝突させるところを、逆に、処理表面にイオンを衝突させることによってその表面を改質する方法のことをいう。処理表面にイオンを衝突させる方法としては、アルゴン雰囲気下で処理表面側に高周波電圧を印加して、被処理物付近にプラズマを生成する方法などがある。なお、アルゴン雰囲気に代えて窒素、ヘリウム、酸素などによる雰囲気を適用してもよい。

【0289】

また、酸化物半導体層の加工は、所望の形状のマスクを酸化物半導体層上に形成した後、当該酸化物半導体層をエッチングすることによって行うことができる。上述のマスクは、フォトリソグラフィなどの方法を用いて形成することができる。または、インクジェット法などの方法を用いてマスクを形成しても良い。なお、酸化物半導体層のエッチングは、ドライエッチングでもウェットエッチングでもよい。もちろん、これらを組み合わせて用いてもよい。

【0290】

なお、酸化物半導体層のエッチングは、ドライエッチングでもウェットエッチングでもよく、両方を用いてもよい。ドライエッチングに用いるエッチングガスとしては、塩素を含むガス(塩素系ガス、例えば塩素(Cl2)、三塩化硼素(BCl3)、四塩化珪素(SiCl4)、四塩化炭素(CCl4)など)が好ましい。また、フッ素を含むガス(フッ素系ガス、例えば四弗化炭素(CF4)、六弗化硫黄(SF6)、三弗化窒素(NF3)、トリフルオロメタン(CHF3)など)、臭化水素(HBr)、酸素(O2)、これらのガスにヘリウム(He)やアルゴン(Ar)などの希ガスを添加したガス、などを用いることができる。

【0291】

ドライエッチング法としては、平行平板型RIE(Reactive Ion Etching)法や、ICP(Inductively Coupled Plasma:誘導結合型プラズマ)エッチング法を用いることができる。所望の形状にエッチングできるように、エッチング条件(コイル型の電極に印加される電力量、基板側の電極に印加される電力量、基板側の電極温度等)を適宜調節する。

【0292】

ウェットエッチングに用いるエッチング液として、燐酸と酢酸と硝酸を混ぜた溶液、クエン酸やシュウ酸などの有機酸を用いることができる。本実施の形態では、ITO−07N(関東化学社製)を用いる。

【0293】

上述のように成膜された酸化物半導体層1844は、非単結晶構造をとる場合がある。ここで、非単結晶構造とは、非晶質構造、微結晶(マイクロクリスタル、ナノクリスタルなど)構造、多結晶構造、非晶質中に微結晶や多結晶が含まれる構造、非晶質構造の表面に微結晶や多結晶が形成された構造などをいう。

【0294】

なお、前述の方法により形成された酸化物半導体層1844には、不純物としての水分又は水素(水酸基を含む)が含まれていることがある。水分又は水素はドナー準位を形成しやすいため、酸化物半導体にとっては不純物である。そこで、酸化物半導体膜中の水分又は水素などの不純物を低減(脱水化または脱水素化)するために、酸化物半導体膜に対して、減圧雰囲気下、窒素や希ガスなどの不活性ガス雰囲気下、酸素ガス雰囲気下、などにおいて、脱水化または脱水素化の加熱処理(以下、第1の加熱処理と略記する)を行ってもよい。

【0295】

酸化物半導体層1844に第1の加熱処理を行うことで、酸化物半導体層1844中の水分又は水素を脱離させることができる。具体的には、250℃以上750℃以下、好ましくは400℃以上基板の歪み点未満の温度で加熱処理を行えば良い。例えば、500℃、3分間以上6分間以下程度で行えばよい。加熱処理にRTA法を用いれば、短時間に脱水化または脱水素化が行えるため、ガラス基板の歪点を超える温度でも処理することができる。

【0296】

加熱処理装置は電気炉に限られず、抵抗発熱体などの発熱体からの熱伝導又は熱輻射によって、被処理物を加熱する装置を備えていてもよい。例えば、GRTA(Gas Rapid Thermal Anneal)装置、LRTA(Lamp Rapid Thermal Anneal)装置等のRTA(Rapid Thermal Anneal)装置を用いることができる。LRTA装置は、ハロゲンランプ、メタルハライドランプ、キセノンアークランプ、カーボンアークランプ、高圧ナトリウムランプ、高圧水銀ランプなどのランプから発する光(電磁波)の輻射により、被処理物を加熱する装置である。GRTA装置は、高温のガスを用いて加熱処理を行う装置である。気体には、アルゴンなどの希ガス、又は窒素のような、加熱処理によって被処理物と反応しない不活性気体が用いられる。

【0297】

第1の加熱処理においては、窒素、又はヘリウム、ネオン、アルゴン等の希ガスに、水分又は水素などが含まれないことが好ましい。又は、加熱処理装置に導入する窒素、又はヘリウム、ネオン、アルゴン等の希ガスの純度を、6N(99.9999%)以上、好ましくは7N(99.99999%)以上、(即ち不純物濃度を1ppm以下、好ましくは0.1ppm以下)とすることが好ましい。

【0298】

また、第1の加熱処理を行った酸化物半導体層1844に、第2の加熱処理を行ってもよい。第2の加熱処理は、酸化性雰囲気にて加熱処理することにより酸化物半導体層1844中に酸素を供給して、第1の加熱処理の際に酸化物半導体層1844中に生じた酸素欠損を補う目的がある。このため、第2の加熱処理は加酸素化処理ということもできる。第2の加熱処理は、例えば200℃以上基板の歪み点未満で行えばよい。好ましくは、250℃以上450℃以下とする。処理時間は3分〜24時間とする。処理時間を長くするほど非晶質領域に対して結晶領域の割合の多い酸化物半導体層1844を形成することができるが、24時間を超える熱処理は生産性の低下を招くため好ましくない。

【0299】

酸化性雰囲気とは酸化性ガスを含む雰囲気である。酸化性ガスとは、酸素、オゾンまたは亜酸化窒素などであって、水、水素などが含まれないことが好ましい。例えば、熱処理装置に導入する酸素、オゾン、亜酸化窒素の純度を、8N(99.999999%)以上、好ましくは9N(99.9999999%)以上(即ち、不純物濃度が1ppm以下、好ましくは0.1ppm未満)とする。酸化性雰囲気は、酸化性ガスを不活性ガスと混合して用いてもよい。その場合、酸化性ガスが少なくとも10ppm以上含まれるものとする。また、不活性雰囲気とは、窒素、希ガス(ヘリウム、ネオン、アルゴン、クリプトン、キセノン)などの不活性ガスを主成分とする雰囲気である。具体的には、酸化性ガスなどの反応性ガスが10ppm未満とする。

【0300】

なお、第2の加熱処理に用いる熱処理装置およびガス種は、第1の加熱処理と同じ物を用いることができる。また、脱水化または脱水素化の加熱処理である第1の加熱処理と、加酸素化の加熱処理である第2の加熱処理は連続して行うことが好ましい。連続して行うことで、半導体装置の生産性を向上させることができる。

【0301】

酸化物半導体膜は、単結晶、多結晶(ポリクリスタルともいう。)または非晶質などの状態をとる。好ましくは、酸化物半導体膜は、CAAC−OS(C Axis Aligned Crystalline Oxide Semiconductor)膜とする。よって、当該トランジスタは、信頼性が高い。

【0302】

CAAC―OS膜は、酸化物半導体膜を成膜する際に被処理物を加熱しながら成膜することにより得ることができる。例えば、基板温度を150℃以上450℃以下とすればよく、好ましくは、基板温度を200℃以上350℃以下とすればよい。また、成膜時の雰囲気は酸化性雰囲気、不活性雰囲気または減圧雰囲気で行えばよく、より好ましくは酸素雰囲気で行えばよい。さらに好ましくは100%酸素雰囲気で行うことが好ましい。酸素雰囲気で成膜処理を行うことにより、成膜される酸化物半導体膜の結晶性が向上する。なお、CAAC―OS膜の具体的な内容については、実施の形態6にて記載する。

【0303】

次に、酸化物半導体層1844などの上に、ソース電極およびドレイン電極(これと同じ層で形成される配線を含む)を形成するための導電層を形成し、当該導電層を加工して、ソース電極またはドレイン電極1842a、ソース電極またはドレイン電極1842bを形成する(図20(B)参照)。

【0304】

導電層は、PVD法や、CVD法を用いて形成することができる。また、導電層の材料としては、アルミニウム、クロム、銅、タンタル、チタン、モリブデン、タングステンから選ばれた元素や、上述した元素を成分とする合金等を用いることができる。マンガン、マグネシウム、ジルコニウム、ベリリウム、ネオジム、スカンジウムのいずれか、またはこれらを複数組み合わせた材料を用いてもよい。

【0305】

導電層は、単層構造であっても良いし、2層以上の積層構造としてもよい。例えば、チタン膜や窒化チタン膜の単層構造、シリコンを含むアルミニウム膜の単層構造、アルミニウム膜上にチタン膜が積層された2層構造、窒化チタン膜上にチタン膜が積層された2層構造、チタン膜とアルミニウム膜とチタン膜とが積層された3層構造などが挙げられる。なお、導電層を、チタン膜や窒化チタン膜の単層構造とする場合には、テーパー形状を有するソース電極またはドレイン電極1842a、およびソース電極またはドレイン電極1842bへの加工が容易であるというメリットがある。

【0306】

また、導電層は、導電性の金属酸化物を用いて形成しても良い。導電性の金属酸化物としては酸化インジウム(In2O3)、酸化スズ(SnO2)、酸化亜鉛(ZnO)、インジウム錫酸化物(In2O3−SnO2、ITOと略記する場合がある)、インジウム亜鉛酸化物(In2O3−ZnO)、または、これらの金属酸化物材料にシリコン若しくは酸化シリコンを含有させたものを用いることができる。

【0307】

導電層のエッチングは、形成されるソース電極またはドレイン電極1842a、およびソース電極またはドレイン電極1842bの端部が、テーパー形状となるように行うことが好ましい。ここで、テーパー角は、例えば、30°以上60°以下であることが好ましい。ソース電極またはドレイン電極1842a、ソース電極またはドレイン電極1842bの端部をテーパー形状となるようにエッチングすることにより、後に形成されるゲート絶縁層1846の被覆性を向上し、段切れを防止することができる。

【0308】

上部のトランジスタのチャネル長(L)は、ソース電極またはドレイン電極1842a、およびソース電極またはドレイン電極1842bの下端部の間隔によって決定される。なお、チャネル長(L)が25nm未満のトランジスタを形成する場合に用いるマスク形成の露光を行う際には、数nm〜数10nmと波長の短い超紫外線(Extreme Ultraviolet)を用いるのが望ましい。超紫外線による露光は、解像度が高く焦点深度も大きい。従って、後に形成されるトランジスタのチャネル長(L)を、10nm以上1000nm(1μm)以下とすることも可能であり、回路の動作速度を高めることが可能である。また、微細化によって、半導体装置の消費電力を低減することも可能である。

【0309】

次に、ソース電極またはドレイン電極1842a、1842bを覆い、かつ、酸化物半導体層1844の一部と接するように、ゲート絶縁層1846を形成する(図20(C)参照)。

【0310】

ゲート絶縁層1846は、CVD法やスパッタリング法等を用いて形成することができる。また、ゲート絶縁層1846は、酸化シリコン、窒化シリコン、酸窒化シリコンなどの材料を用いて形成する。また、ゲート絶縁層1846は、13族元素および酸素を含む材料を用いて形成することもできる。13族元素および酸素を含む材料としては、例えば、酸化ガリウム、酸化アルミニウム、酸化アルミニウムガリウムなどを用いることができる。さらに、酸化タンタル、酸化ハフニウム、酸化イットリウム、ハフニウムシリケート(HfSixOy(x>0、y>0))、窒素が添加されたハフニウムシリケート(HfSixOy(x>0、y>0))、窒素が添加されたハフニウムアルミネート(HfAlxOy(x>0、y>0))、などを含むように形成してもよい。ゲート絶縁層1846は、単層構造としても良いし、上記の材料を組み合わせて積層構造としても良い。また、その厚さは特に限定されないが、半導体装置を微細化する場合には、トランジスタの動作を確保するために薄くするのが望ましい。例えば、酸化シリコンを用いる場合には、1nm以上100nm以下、好ましくは10nm以上50nm以下とすることができる。

【0311】

ゲート絶縁層1846は、水素、水などの不純物を混入させない方法を用いて成膜することが好ましい。ゲート絶縁層1846に水素、水などの不純物が含まれると、後に形成される酸化物半導体膜に水素、水などの不純物の浸入や、水素、水などの不純物による酸化物半導体膜中の酸素の引き抜き、などによって酸化物半導体膜のバックチャネルが低抵抗化(n型化)してしまい、寄生チャネルが形成されるおそれがあるためである。よって、ゲート絶縁層1846はできるだけ水素、水などの不純物が含まれないように作製することが好ましい。例えば、スパッタリング法によって成膜するのが好ましい。成膜する際に用いるスパッタガスとしては、水素、水などの不純物が除去された高純度ガスを用いることが好ましい。

【0312】

なお、酸化物半導体層1844に用いられる酸化物半導体材料には、13族元素を含むものが多い。このため、13族元素および酸素を含む材料を用いて、酸化物半導体層1844と接するゲート絶縁層1846を形成する場合には、酸化物半導体層1844との界面の状態を良好に保つことができる。これは、13族元素および酸素を含む材料と、酸化物半導体材料との相性が良いことによる。例えば、酸化物半導体層1844と酸化ガリウムを用いたゲート絶縁層1846を接して設けることにより、酸化物半導体層1844とゲート絶縁層1846との界面における水素のパイルアップを低減することができる。また、ゲート絶縁層1846として、酸化アルミニウムを用いる場合は、水を透過させにくいという特性を有しているため、当該材料を用いることは、酸化物半導体層1844の水の浸入防止という点においても好ましい。

【0313】

上述のように、ゲート絶縁層を薄くすると、トンネル効果などに起因するゲートリークが問題となる。ゲートリークの問題を解消するには、ゲート絶縁層1846に、酸化ハフニウム、酸化タンタル、酸化イットリウム、ハフニウムシリケート(HfSixOy(x>0、y>0))、窒素が添加されたハフニウムシリケート(HfSixOy(x>0、y>0))、窒素が添加されたハフニウムアルミネート(HfAlxOy(x>0、y>0))、などの高誘電率(high−k)材料を用いると良い。high−k材料をゲート絶縁層1846に用いることで、電気的特性を確保しつつ、ゲートリークを抑制するために膜厚を大きくすることが可能になる。なお、high−k材料を含む膜と、酸化シリコン、窒化シリコン、酸化窒化シリコン、窒化酸化シリコン、酸化アルミニウムなどのいずれかを含む膜との積層構造としてもよい。

【0314】

また、ゲート絶縁層1846は、酸素を化学量論的組成比よりも多く含むことが好ましい。例えば、ゲート絶縁層1846として酸化ガリウムを用いた場合、化学量論的組成比はGa2O3+α(0<α<1)と表すことができる。また、酸化アルミニウムを用いた場合は、Al2O3+α(0<α<1)と表すことができる。さらに、酸化ガリウムアルミニウムを用いた場合は、GaxAl2−xO3+α(0<x<2、0<α<1)と表すことができる。

【0315】

なお、酸化物半導体膜の成膜後、酸化物半導体層1844の形成後、またはゲート絶縁層1846の形成後のいずれかにおいて、酸素ドープ処理を行ってもよい。酸素ドープとは、酸素(少なくとも、酸素ラジカル、酸素原子、酸素イオン、のいずれかを含む)をバルクに添加することをいう。なお、当該「バルク」の用語は、酸素を、薄膜表面のみでなく薄膜内部に添加することを明確にする趣旨で用いている。また、「酸素ドープ」には、プラズマ化した酸素をバルクに添加する「酸素プラズマドープ」が含まれる。酸素ドープ処理を行うことにより、酸化物半導体層1844やゲート絶縁膜に含まれる酸素を、化学量論的組成比より多くすることができる。

【0316】

酸素ドープ処理は、ICP(Inductively Coupled Plasma:誘導結合型プラズマ)方式を用いて、マイクロ波(例えば、周波数2.45GHz)により励起された酸素プラズマを用いて行うことが好ましい。

【0317】

ゲート絶縁層1846の形成後には、不活性ガス雰囲気下、または酸素雰囲気下で第3の加熱処理を行うことが望ましい。第3の加熱処理の温度は、200℃以上450℃以下、好ましくは250℃以上350℃以下とすることが望ましい。例えば、窒素雰囲気下で250℃、1時間の熱処理を行えばよい。第3の加熱処理を行うことによって、トランジスタの電気的特性のばらつきを軽減することができる。また、酸化物半導体層1844に接する膜、例えばゲート絶縁層1846が酸素を含む場合、酸化物半導体層1844に酸素を供給し、該酸化物半導体層1844の酸素欠損を補填して、i型(真性半導体)またはi型に限りなく近い酸化物半導体層を形成することもできる。なお、酸化物半導体層1844に接して酸素を含む下地膜などがある場合は、下地膜側からも酸素欠損を補填することができる。

【0318】