半導体装置および半導体装置ユニット

【課題】半導体パッケージをより小型とすることができる半導体装置を提供すること。

【解決手段】回路素子の少なくとも一部が形成された半導体基板3と、半導体基板3の表面に配置された1または複数の表面電極41a,41bと、半導体基板3の裏面に配置され、上記回路素子と導通している裏面電極42と、を備え、表面電極41a,41bが上記回路素子と導通している、半導体装置A1であって、上記表面の側に配置されており、かつ、半導体基板3、表面電極41a,41bおよび裏面電極42を支持している支持基板1と、表面電極41a,41bと導通しているとともに半導体基板3を貫通している導電部51a,51bと、をさらに備える。

【解決手段】回路素子の少なくとも一部が形成された半導体基板3と、半導体基板3の表面に配置された1または複数の表面電極41a,41bと、半導体基板3の裏面に配置され、上記回路素子と導通している裏面電極42と、を備え、表面電極41a,41bが上記回路素子と導通している、半導体装置A1であって、上記表面の側に配置されており、かつ、半導体基板3、表面電極41a,41bおよび裏面電極42を支持している支持基板1と、表面電極41a,41bと導通しているとともに半導体基板3を貫通している導電部51a,51bと、をさらに備える。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置および半導体装置ユニットに関する。

【背景技術】

【0002】

ダイオードやトランジスタなどの半導体装置は、たとえばリードや基板に搭載された、いわゆるパッケージの形態として用いられる。近年、携帯機器を中心として電子機器の小型化が進んでいる。そのため、半導体装置が実装された半導体パッケージの小型化が望まれている。

【0003】

従来、半導体パッケージとして特許文献1に示されたものが知られている。図17に示すように、この半導体パッケージは、半導体装置9Aと、モールド樹脂97を備えている。半導体装置9Aは、半導体チップ93、ベース電極941、エミッタ電極942、コレクタ電極943、リード9d1,9d2、Auバンプ981,982およびボンディングワイヤ9wを備えている。半導体チップ93は、バイポーラトランジスタを構成している。ベース電極941およびエミッタ電極942は、半導体チップ93の図下面に配置されている。コレクタ電極943は、半導体チップ93の図上面に配置されている。ベース電極941は、バンプ981を介して、図示しないリードと電気的に接続している。エミッタ電極942は、バンプ982を介して、リード9d1と電気的に接続している。コレクタ電極943は、ボンディングワイヤ9wにより、リード9d2と電気的に接続している。モールド樹脂97は、半導体装置9Aの上記の各構成部品を覆っている。

【0004】

半導体装置9Aにおいては、ボンディングワイヤ9wを備えていることから、モールド樹脂97を、ボンディングワイヤ9wを十分に覆うことのできる大きさとする必要がある。そのため、半導体装置9Aを備えた半導体パッケージの小型化を図ることが困難となっていた。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2001−60598号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

本発明は、上記した事情のもとで考え出されたものであって、半導体パッケージをより小型とすることができる半導体装置を提供することを主たる課題とする。

【課題を解決するための手段】

【0007】

本発明の第1の側面によって提供される半導体装置は、回路素子の少なくとも一部が形成された半導体基板と、上記半導体基板の表面に配置された1または複数の表面電極と、上記半導体基板の裏面に配置され、上記回路素子と導通している裏面電極と、を備え、1以上の上記表面電極が上記回路素子と導通している、半導体装置であって、上記表面の側に配置されており、かつ、上記半導体基板、上記表面電極および上記裏面電極を支持している支持基板と、上記表面電極と導通しているとともに、上記半導体基板の表面の側および上記半導体基板の裏面の側において露出している導電部と、をさらに備えることを特徴としている。

【0008】

本発明の好ましい実施の形態においては、上記導電部は上記半導体基板を貫通している。このような構成によれば、上記回路素子を外部端子と接続するためにワイヤボンディングを施す必要がなくなる。そのため、上記半導体装置を実装する半導体パッケージに、ボンディングワイヤのパッドを設ける必要がなくなる。これにより、上記半導体パッケージの小型化を図ることが可能となる。

【0009】

本発明の好ましい実施の形態においては、上記導電部が延びる方向に沿って、上記導電部を貫通する絶縁部が形成されている。

【0010】

本発明の好ましい実施の形態においては、上記半導体基板は、上記導電部が延びる方向に沿って形成された貫通孔と、この貫通孔の内面に形成された絶縁膜と、を備えており、この絶縁膜は上記導電部を被膜している。

【0011】

本発明の好ましい実施の形態においては、上記裏面の側には、上記導電部と導通している外部接続電極が配置され、上記裏面電極は、上記半導体基板の裏面と接触しており、上記裏面電極と上記裏面との接触部分のうち通電する部分の面積である通電面積が、上記外部接続電極の面積より大きい。

【0012】

本発明の好ましい実施の形態においては、上記裏面の側には、上記外部接続電極と導通しているバンプが配置され、このバンプと上記導電部とが、上記半導体基板の面内方向において重ならないように配置されている。

【0013】

本発明の好ましい実施の形態においては、上記半導体基板の裏面の側から上記半導体基板の表面に向かって延出しているとともに上記表面電極または上記裏面電極と導通している延出電極と、上記延出電極と接しているバンプと、をさらに備えている。このような構成によれば、上記半導体装置が上記半導体装置の幅方向に大きくなることを抑制しつつ、上記バンプが接触している電極と上記バンプとの接触面積を、大きくできる。そのため、上記バンプが接触している電極と上記バンプとの接触抵抗の値を、小さくできる。

【0014】

本発明の好ましい実施の形態においては、上記半導体基板の裏面の側に配置され、かつ、上記延出電極と接しているとともに、上記バンプと接している外部接続電極をさらに備えている。このような構成によれば、上記バンプが接触する電極と上記バンプとの接触面積を、さらに大きくすることができる。そのため、上記バンプが接触する電極と上記バンプとの接触抵抗の値を、さらに小さくできる。

【0015】

本発明の好ましい実施の形態においては、上記導電部は、上記半導体基板を貫通しており、上記延出電極は、上記半導体装置の側面に形成され、かつ、上記導電部と異なるものとされている。

【0016】

本発明の好ましい実施の形態においては、上記導電部が延びる方向に沿って、上記導電部を貫通する絶縁部が形成されている。

【0017】

本発明の好ましい実施の形態においては、上記延出電極は、上記半導体装置の側面に形成され、かつ、上記導電部とされている。このような構成によれば、上記導電部と異なる上記延出電極を形成する必要がない。すなわち、上記半導体装置の上記回路素子が構成されている部分から、上記半導体装置の幅方向において、上記導電部より遠い位置に、上記延出電極を形成する必要がない。そのため、幅方向の大きさがより小さい上記半導体装置を提供できる。

【0018】

本発明の好ましい実施の形態においては、上記回路素子は、トランジスタであり、このトランジスタと接続される3つの電極のうちの2つが、上記表面電極とされ、これらの3つの電極のうちの他の1つが、上記裏面電極とされている。

【0019】

本発明の第2の側面によって提供される半導体装置ユニットは、本発明の第1の側面にかかる2つの半導体装置を備え、これら2つの半導体装置の一方である第1の半導体装置の上記表面電極と、これら2つの半導体装置の他方である第2の半導体装置における上記裏面電極とが、対向するように、上記第1および第2の半導体装置が積層されており、上記第1の半導体装置の上記支持基板上に固定されているとともに、上記第2の半導体装置の上記導電部または上記裏面電極と導通しているボンディングリボンを備えている。

【0020】

このような構成によれば、上記第2の半導体装置の上記導電部または上記裏面電極を、上記半導体装置ユニットの外部と導通させるためのワイヤボンディングを施す必要がない。そのため、上記第1の半導体装置の上に上記第2の半導体装置を積層させた場合でも、上記第1の半導体装置の上記支持基板の面方向の大きさを大きくする必要がない。

【0021】

本発明の好ましい実施の形態においては、上記第2の半導体装置は、請求項6に記載の半導体装置であり、上記ボンディングリボンは、上記第2の半導体装置の上記バンプと接合されており、かつ、上記第1の半導体装置の上記支持基板上に固定されている。

【0022】

本発明の好ましい実施の形態においては、上記第1の半導体装置の上記支持基板を貫通している追加の導電部をさらに備え、この追加の導電部は、上記第1の半導体装置の上記表面電極と、上記第2の半導体装置の上記導電部または上記裏面電極であって、上記ボンディングリボンと導通しているものとは異なるものと、いずれとも導通している。このような構成によれば、上記第1の半導体装置の上記表面電極と、上記第2の半導体装置の上記導電部または上記裏面電極とが、上記追加の導電部により、直接、導通させられる。そのため、上記追加の導電部と導通している、上記第2の半導体装置の上記導電部または上記裏面電極を、上記半導体装置ユニットの外部と、上記ボンディングリボンなどを用いて導通させる必要がなくなる。これにより、上記半導体装置ユニットに設ける上記ボンディングリボンの個数を減少させうる。

【0023】

本発明の好ましい実施の形態においては、上記第2の半導体装置の上記支持基板の平面視において、上記第2の半導体装置の上記支持基板は、上記第1の半導体装置の上記支持基板からはみ出る部分を有する。

【0024】

本発明の第3の側面によって提供される半導体装置ユニットは、本発明の第1の側面にかかる2つの半導体装置を備え、これら2つの半導体装置の一方である第1の半導体装置と、これら2つの半導体装置の他方である第2の半導体装置とが積層されており、上記第1および第2の半導体装置が、同一の中間基板を、上記第1の半導体装置の上記支持基板および上記第2の半導体装置の上記支持基板として共有している。

【0025】

このような構成によれば、上記第1の半導体装置の上記支持基板および上記第2の半導体装置の上記支持基板を、別個に設ける必要がない。そのため、上記第1および第2の半導体装置を単に積層させた場合と比較して、上記第1または第2の半導体装置の厚さ方向における上記半導体装置ユニットの大きさを、小さくできる。これにより、上記半導体装置ユニットのコンパクト化が図れる。

【0026】

本発明の好ましい実施の形態においては、上記中間基板は、絶縁性を有し、上記中間基板は、上記第1の半導体装置の上記表面電極または上記裏面電極と、上記第2の半導体装置の上記表面電極または上記裏面電極と、いずれとも導通する、上記中間基板を貫通する導電部を備えている。このような構成によれば、上記第2の半導体装置の上記表面電極または上記裏面電極を上記半導体装置ユニットの外部と導通させるために設ける必要があるワイヤの本数を、少なくできる。

【0027】

本発明のその他の特徴および利点は、添付図面を参照して以下に行う詳細な説明によって、より明らかとなろう。

【図面の簡単な説明】

【0028】

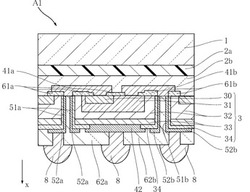

【図1】本発明の第1実施形態にかかる半導体装置の要部断面図を概念的に示したものである。

【図2】図1に示した半導体装置の要部上面図を示したものである。

【図3】図1に示した半導体装置の要部底面図を示したものである。

【図4】図1に示した半導体装置の製造方法の工程を示した図である。

【図5】図4に続く工程を示す図である。

【図6】図5に続く工程を示す図である。

【図7】図6に続く工程を示す図である。

【図8】図7に続く工程を示す図である。

【図9】図8に続く工程を示す図である。

【図10】本発明の第2実施形態にかかる半導体装置の要部断面図を概念的に示したものである。

【図11】図10に示した半導体装置の製造方法の一工程を示した図である。

【図12】本発明の第3実施形態にかかる半導体装置の要部断面図を概念的に示したものである。

【図13a】本発明の第4実施形態にかかる半導体装置ユニットの斜視図である。

【図13b】図13aに示した半導体装置ユニットの断面図を概念的に示したものである。

【図14】本発明の第4実施形態にかかる半導体装置ユニットの他の一例の斜視図である。

【図15】本発明の第5実施形態にかかる半導体装置ユニットの断面図を概念的に示したものである。

【図16】図15に示した半導体装置ユニットの製造方法の一工程を示した図である。

【図17】従来の半導体装置を示す要部断面図である。

【発明を実施するための形態】

【0029】

以下、本発明の好ましい実施の形態につき、図面を参照して具体的に説明する。

【0030】

図1〜9を用いて、本発明の第1実施形態について説明する。

【0031】

図1は本発明の第1実施形態にかかる半導体装置A1を概念的に示した要部断面図である。本実施形態では半導体装置A1として、バイポーラトランジスタを示している。半導体装置A1は、支持基板1、接着部2a、保護絶縁膜2b、半導体基板3、表面電極41a,41b、裏面電極42、導電部51a,51b、外部接続電極52a,52b、絶縁部61a,61b,62a,62b、および、バンプ8を備えている。表面電極41aがエミッタ電極であり、表面電極41bがベース電極であり、裏面電極42がコレクタ電極である。

【0032】

支持基板1は、樹脂からなる接着部2a、および、保護絶縁膜2bを介して、半導体基板3、表面電極41a,41b、裏面電極42a、絶縁部61a,61b、と連結している。これにより、支持基板1は、半導体基板3、表面電極41a,41b、裏面電極42、絶縁部61a,61b,62a,62b、および、バンプ8を、支持している。支持基板1の厚さは500μm程度とされている。支持基板1はガラス製である。支持基板1として、放熱性のよい金属を用いてもよい。

【0033】

半導体基板3は、n型半導体層30、p型半導体層31、n型半導体層32、n型半導体層33および絶縁部34を備えている。これらの半導体層により、半導体基板3には、トランジスタが形成されている。本発明でいう回路素子は、本実施形態では、バイポーラトランジスタである。半導体基板3の厚さは、たとえば100μm以下であり、30μmや40μmであることが好ましい。p型半導体層31のx方向における大きさは、たとえば、5〜30μmである。絶縁部34は、半導体基板3に形成されたx方向に延びる貫通孔の内面に、形成されている。絶縁部34は、本発明でいう絶縁膜である。

【0034】

表面電極41a,41bは、半導体基板3の図中上面(本発明でいう半導体基板の表面)に配置されている。表面電極41aは、n型半導体層30および導電部51aと導通している。表面電極41aは、絶縁部61aにより、p型半導体層31およびn型半導体層32と絶縁されている。同様に、表面電極41bは、p型半導体層31および導電部51bと導通している。表面電極41bは、絶縁部61bにより、n型半導体層32と絶縁されている。また、表面電極41a,41bは、たとえばSiNなどからなる保護絶縁膜2bにより覆われ、保護されている。なお、製造工程を削減するため、保護絶縁膜2bを形成せず、表面電極41a,41b上に直接、接着部2aを形成してもよい。

【0035】

裏面電極42は、半導体基板3の図中下面(本発明でいう半導体基板の裏面)に配置されている。裏面電極42は、n型半導体層33と導通している。

【0036】

導電部51a,51bは、x方向に沿って、半導体基板3を貫通するように形成されている。また、導電部51a,51bは、半導体基板3の表面の側および半導体基板3の裏面の側において露出しているともいえる。導電部51a,51bは、円筒状である。なお、導電部51a,51bの形状は、x方向視において、円形である必要はない。たとえば、方形状でもよい。また、導電部51a,51bは、円錐筒状であってもよい。導電部51a,51bの周囲には、絶縁部34が形成されている。絶縁部34は、導電部51aとn型半導体層32,33とを絶縁している。同様に、絶縁部34は、導電部51bとn型半導体層32,33とを絶縁している。絶縁部62a,62bが、導電部51a,51bの内側にそれぞれ形成されている。絶縁部62a,62bは、導電部51a,51bが延びる方向(本実施形態ではx方向)に沿って、導電部51a,51b、をそれぞれ貫通している。さらに、絶縁部62a,62bは、導電部51a,51bと裏面電極42とを絶縁している。

【0037】

外部接続電極52a,52bは、半導体基板3の裏面に配置されている。外部接続電極52aは導電部51aと、外部接続電極52bは導電部51bと、それぞれ導通している。

【0038】

バンプ8は、本実施形態に係る半導体装置A1が外部端子と電気的に接続可能とするために形成されている。バンプ8は、裏面電極42ないし外部接続電極52a,52bと導通している。また、バンプ8は、半導体装置A1が取り付けられる半導体パッケージ(図示略)の配線基板などに接続されている。

【0039】

図2には、図1に示した半導体装置A1の要部上面図を示している。図3には、本実施形態にかかる半導体装置A1の要部底面図を示している。図2では、図1に示した支持基板1、接着部2a、保護絶縁膜2b、表面電極41a,41b、絶縁部61a,61bを、理解の便宜上省略している。同様に、図3では、図1に示した絶縁部62a,62bを省略している。図2,3において、導電部51a’は、図1に示した導電部51aに対応する。同様に、導電部51b’は導電部51bに対応する。図3において、裏面電極42’は、図1に示した裏面電極42に対応する。同様に、外部接続電極52a’,52b’は、外部接続電極52a,52bにそれぞれ対応する。また、バンプ8’は、バンプ8に対応する。

【0040】

図2に表されているように本実施形態では、従来の半導体装置においてワイヤボンディングパッドが形成されていた領域に、導電部51a’,51b’が形成されている。図1で示したように、導電部51a’は、エミッタ電極である表面電極41aに導通している。そのため、導電部51a’は、ベース電極である表面電極41bと導通している導電部51b’と比較して、より大きい電流を流す必要がある。このため、図2および図3によく表われているように、導電部51a’は3つ、導電部51b’は1つ、形成されている。もちろん、導電部51a’,51b’の個数の組み合わせは、これに限られない。

【0041】

図3によく表れているように、裏面電極42’の面積は、外部接続電極52a’、または外部接続電極52b’の面積と比較して大きい。また、バンプ8’は、導電部51a’または51b’と重ならないように配置されている。

【0042】

図4〜図9を用いて、半導体装置A1の製造方法について説明する。

【0043】

まず、図4に示すように、公知の方法により、半導体基板3を作成する。そして、この半導体基板3に、絶縁部61a,61b、および、表面電極41a,41bを形成する。次に、表面電極41a,41b、または、絶縁部61a,61bの図中上部に、保護絶縁膜2b、接着部2aを形成する。

【0044】

次に、図5に示すように、接着部2aの図中上部に、支持基板1を接合する。次に、図6に示すように、半導体基板3におけるn型半導体層33の図中下方を研削する。このとき、n型半導体層33の厚さは、500〜800μmとなっている。支持基板1がなければ、以下で述べる導電部51a,51bの形成の際に半導体基板3が折れ曲がったりすることを防ぐために、半導体基板3の厚さは100μm以上である必要がある。しかしながら、本実施形態に係る半導体装置A1は支持基板1を備えている。そのため、半導体基板3の厚さが100μm以下、たとえば30μmと薄いものであっても、導電部51a,51bの形成の際に半導体基板3が折れ曲がったりすることはない。

【0045】

次に、図7に示すように、半導体基板3の図中下部から孔を形成する。そして、この孔の内面およびn型半導体層33の図中下面に、たとえば酸化処理によってSiO2からな

る絶縁部34を形成する。次に、図8に示すように、絶縁部34の表面に、導電部51a,51bを形成する。その後、外部接続電極52a,52bおよび裏面電極42を形成する。次に、図9に示すように、絶縁部62a,62bを形成する。その後、図1に示したバンプ8を形成し、半導体装置A1が完成する。

【0046】

次に、半導体装置A1の作用について説明する。

【0047】

本実施形態によれば、半導体装置A1を外部端子と接続するためのワイヤボンディングを施す必要がなくなる。そのため、ボンディングワイヤを樹脂で覆うことが不要となる。また、半導体装置A1は支持基板1を備えているため、従来の半導体装置に比べて、n型半導体層33をより薄くすることができる。これにより、半導体基板3をより薄くすることができる。その結果、半導体装置A1を実装する半導体パッケージの厚さをより小さくすることが可能となる。また、n型半導体層33が薄くなることから、半導体装置A1の低抵抗化が望める。

【0048】

また、ワイヤボンディングを施すことが不要となることから、半導体装置A1を実装する半導体パッケージにボンディングワイヤを接続するためのパッドを設ける必要がなくなる。そのため、半導体装置A1の平面視において、半導体装置A1を実装する半導体パッケージの小型化を図ることが可能となる。

【0049】

導電部51a,51bの内側にはそれぞれ、絶縁部62a,62bが充填されている。そのため、導電部51a,51bを形成するために用いる導電材料を、より少なくできる。その結果半導体装置A1の製造コストの減少を図ることが可能となる。

【0050】

図3に示したように、裏面電極42’の面積は、外部接続電極52a’、または外部接続電極52b’の面積と比較して大きい。そのため、たとえ外部接続電極52a’や外部接続電極52b’を形成したとしても、これらの外部接続電極を形成しない場合と比較して、裏面電極42’とn型半導体層33との接触面積を大幅に減少させる必要はない。その結果、半導体装置A1において、裏面電極42とn型半導体層33との接触抵抗を低いまま維持しうる。

【0051】

半導体装置A1において発生した熱が、表面電極41a,41b、導電部51a,51b、外部接続電極52a,52bそしてバンプ8と伝導する。その後、この熱は、半導体パッケージに伝導され、外部に放出される。つまり、本実施形態では、半導体装置A1で発生した熱を、容易に外部に放出することが可能となっている。

【0052】

バンプ8は、外部接続電極52a,52bを介して、導電部51a,51bと導通している。そのため、バンプ8の形成位置は、導電部51aの位置に拘束されない。すなわち、半導体装置A1を実装する半導体パッケージの形状等に応じて、バンプ8の形成位置を自在に決定できる。

【0053】

図10〜16は、本発明の他の実施形態を示している。なお、これらの図において、上記実施形態と同一または類似の要素には、上記実施形態と同一の符号を付している。

【0054】

図10,11を用いて、本発明の第2実施形態について説明する。

【0055】

図10は本発明の第2実施形態にかかる半導体装置A2を示した断面図である。半導体装置A2は、半導体装置A1の基本的な構成に加えて、延出電極53a,53b、外部接続電極54a,54b、バンプ8a,8bを備えている。半導体装置A2は、ほぼ左右対称であるから、以下では、半導体装置A2の図中左側に形成された、延出電極53a、外部接続電極54a、バンプ8aについて、説明する。以下の説明は、半導体装置A2の図中右側に形成された、延出電極53b、外部接続電極54b、バンプ8b、についても同様に適用できる。

【0056】

延出電極53aは、半導体装置A2の側面(図中左方の面)に形成されている。延出電極53aは、半導体基板3の裏面から半導体基板3の表面に向かって延びている。延出電極53aは、半導体基板3の表面まで達しており、表面電極41aと接している。これにより、延出電極53aは表面電極41aと導通している。

【0057】

外部接続電極54aは、半導体基板3の図中下面に配置されている。外部接続電極54aは、その左端において、延出電極53aと接している。また、外部接続電極54aは、その右端において、導電部51aとも接している。

【0058】

図10に表れているように、バンプ8aは、外部接続電極54aの図中右端の近傍から延出電極53aの図中上端の近傍にわたって、外部接続電極54aおよび延出電極53aと接している。バンプ8aは、半導体装置A2が外部端子と電気的に接続可能とするために形成されている。

【0059】

図11を用いて、半導体装置A2の製造方法について説明する。

【0060】

半導体装置A2の製造は、第1実施形態において述べた方法とほぼ同様に行う。そのため、以下では、半導体装置A1の製造方法と異なる工程について主に述べる。まず、図4,5に示した工程を実行し、図6に示されたものを製造する。次に、図7に示したように、半導体基板3に2つの孔を設ける。さらに半導体装置A2の製造においては、半導体基板3に、別の孔を形成する。この孔は、図11で示した孔hである。次に、図11に示すように、孔hの内部に、延出電極53a,53bなどを形成する。その後、外部接続電極54a,54bなどを形成するなどして、図11に示したものを得る。図11は、図8と比べて、孔h、延出電極53a,53bの有無などにおいて異なる。

【0061】

次に、図11に示されたものを、孔hで分断されるように線Lに沿って切断する。その後、図10で示した絶縁部62a,62bおよびバンプ8a,8b,8cを形成する。これにより、半導体装置A2が完成する。

【0062】

次に、半導体装置A2の作用について説明する。

【0063】

このような構成によれば、半導体装置A2が半導体装置A2の幅方向に大きくなることを抑制しつつ、たとえば外部接続電極54aおよび延出電極53aとバンプ8aとの接触面積を、大きくできる。そのため、外部接続電極54aおよび延出電極53aとバンプ8aとの接触抵抗の値を、小さくできる。また、上記接触面積が大きくなっていることから、外部接続電極54aおよび延出電極53aと、バンプ8aとを、強固に接合することが可能となっている。

【0064】

なお、図においては、延出電極53a,53bが真上方向に延びている。もちろん、本発明にかかる延出電極が延びる方向はこれに限られない。たとえば、図斜め上方向に延出電極53a,53bが延びていてもよい。また、外部接続電極54a,54bの形成は必ずしも必要はない。

【0065】

さらに、延出電極53aは、半導体基板3の表面まで達していなくてもよい。このとき、延出電極53aを、外部接続電極54aおよび導電部51aを介して、表面電極41aと導通させるとよい。

【0066】

図12を用いて、本発明の第3実施形態について説明する。

【0067】

本実施形態では、延出電極53aが導電部51aとされている。同様に、延出電極53bが導電部51bとされている。延出電極53a,53bは、半導体装置A3の側面(図における左側または右側)に形成されている。半導体装置A3は、半導体装置A2と同様に製造できる。

【0068】

このような構成によれば、導電部51aや導電部51bと異なる延出電極を形成する必要がない。すなわち、導電部51aや導電部51bより外側に、延出電極を形成する必要がない。これにより、幅方向において小さい半導体装置A3を提供できる。

【0069】

図13a,13bを用いて、本発明の第4実施形態について説明する。

【0070】

図13aは、本発明の第4実施形態にかかる半導体装置ユニットの斜視図である。同図に示された半導体装置ユニットB1は、第1実施形態で示した半導体装置A1が積層されている。図13bは、図13aに示した半導体装置ユニットの断面図を概念的に示したものである。図13bでは、図13aで示した半導体装置ユニットB1の半導体装置A1のうち、下から2つの半導体装置A1a,A1bを示している。

【0071】

図13a,13bに表れているように、半導体装置ユニットB1は、半導体装置A1aおよび半導体装置A1bが積層されている。半導体装置A1aは、本発明にかかる第1の半導体装置に相当する。半導体装置A1bは、本発明にかかる第2の半導体装置に相当する。図13bに表れているように、半導体装置ユニットB1において、半導体装置A1aの表面電極41a,41bと、半導体装置A1bの裏面電極42とが、対向している。

【0072】

半導体装置ユニットB1は、ボンディングリボンw1、および、導電部55を備えている。

【0073】

図13a,13bに表れているように、ボンディングリボンw1は、薄い帯状の導電体である。ボンディングリボンw1は、たとえばアルミニウムから構成されている。図示していないが、ボンディングリボンw1は、半導体装置ユニットB1の外部の電極などと導通している。図13bに表れているように、ボンディングリボンw1は、半導体装置A1aの支持基板1上の固定されている。ボンディングリボンw1は、バンプ8aと接合している。これにより、ボンディングリボンw1は、半導体装置A1bの導電部51aと導通している。

【0074】

導電部55は、半導体装置A1aの支持基板1に形成され、この支持基板1を貫通している。導電部55は、本発明でいう追加の導電部に相当する。導電部55は、半導体装置A1aの表面電極41bと導通している。導電部55は、半導体装置A1bのバンプ8bと、電極dを介して導通している。これにより、導電部55は、半導体装置A1bの導電部51bと導通しているといえる。半導体装置A1bのバンプ8bは、ボンディングリボンw1と導通している半導体装置A1bのバンプ8aとは異なるものである。また、半導体装置A1bのバンプ8cには、ボンディングリボンw2が接続されている。

【0075】

このような構成によれば、半導体装置A1bのバンプ8a,8b,8cを、半導体装置ユニットB1の外部と導通させるためのワイヤボンディングを施す必要がない。そのため、半導体装置A1aの上に半導体装置A1bを積層させた場合でも、ワイヤボンディングのためのパッドを設ける必要がなく、半導体装置A1aの支持基板1の面方向の大きさを大きくする必要がない。その結果、半導体装置ユニットB1を実装するために必要な、半導体パッケージにおけるスペースを小さくすることができる。特に、半導体装置ユニットB1を、ディスクリート部品として用いる場合に好適である。

【0076】

また上述した構成によれば、半導体装置A1bのバンプ8aの形成する位置を適宜移動させることにより、半導体装置A1aの支持基板1上におけるボンディングリボンw1を形成する位置を、自在に決定できる。

【0077】

半導体装置A1aの表面電極41bと、半導体装置A1bのバンプ8bとが、導電部55により、直接、導通させられる。そのため、半導体装置A1bのバンプ8bを、半導体装置ユニットB1の外部と、ボンディングリボンw1などを用いて導通させる必要がなくなる。これにより、半導体装置ユニットB1に設けるボンディングリボンw1の個数を少なくすることが可能となっている。

【0078】

半導体装置ユニットB1において、半導体装置A1bと半導体装置A1cとの間にも、ボンディングリボンw1,w2が設けられている。半導体装置A1bと半導体装置A1cとの関係は、上述した半導体装置A1aと半導体装置A1bとの関係と同様である。

【0079】

また、本実施形態では、本発明にかかる第1および第2の半導体装置が同一の回路素子であるバイポーラトランジスタを構成するものを示した。だが、本発明にかかる半導体装置ユニットは、本発明にかかる第1の半導体装置と第2の半導体装置とが異なる回路素子を構成していてもよい。また、第2実施形態にかかる半導体装置A2と半導体装置A1とが積層されたものであってもよい。

【0080】

また、半導体装置A1bの支持基板1の平面視において、半導体装置A1bの支持基板1は、半導体装置A1aの支持基板1からはみ出る部分を有していてもよい。たとえば、図14で示すように、半導体装置ユニットB1’における半導体装置A1の幅方向の大きさを、半導体装置ユニットB1’の上部にいくにつれて序々に大きくしてもよい。このような構成によれば、ボンディングリボンw1どうし、ならびに、ボンディングリボンw2どうしの干渉を抑制することができる。

【0081】

図15,16を用いて、本発明の第5実施形態について説明する。

【0082】

図15は、本発明の第5実施形態にかかる半導体装置ユニットの断面図を概念的に示したものである。

【0083】

同図に示された半導体装置ユニットB2は、第1実施形態で示した半導体装置A1が2つ積層した構成とされている。半導体装置ユニットB2における半導体装置A1のうち、図中下方に示されたものが、半導体装置A1dである。一方、半導体装置ユニットB2における半導体装置A1のうち、図中上方に示されたものが、半導体装置A1eである。半導体装置A1dは、本発明にかかる第1の半導体装置に相当する。半導体装置A1eは、本発明にかかる第2の半導体装置に相当する。

【0084】

図15に表れているように、半導体装置ユニットB2において、半導体装置A1dと半導体装置A1eとが、同一の中間基板mbを、半導体装置A1dの支持基板1および半導体装置A1eの支持基板1として共有している。

【0085】

中間基板mbは、絶縁性を有し、導電部56を備えている。導電部56は、中間基板mbを貫通している。導電部56は、半導体装置A1dの表面電極41bと導通している。また、導電部56は、半導体装置A1eの表面電極41aとも導通している。導電部56の形成は、かならずしも必要ではない。

【0086】

半導体装置A1dのバンプ8a,8b,8cは、第1実施形態で述べたのと同様に、半導体装置ユニットB2が取り付けられるパッケージ(図示略)の配線基板などに接続される。一方、半導体装置A1eのバンプ8a,8b,8cには、たとえば半導体装置ユニットB2の外部と接続するためのボンディングワイヤが接続される。

【0087】

次に、半導体装置ユニットB2の製造方法について説明する。

【0088】

まず、第1実施形態で説明した方法と同様の方法により、半導体装置A1dを製造する。このとき、半導体装置A1dの支持基板1を貼り付ける際に既に導電部56が形成された支持基板1を用いる。

【0089】

次に、図16に示すように、図4で示したものと同一のものを、半導体装置A1dの支持基板1の表面に接合する。次に、半導体装置A1eとなるもののn型半導体層33を研削するなど、第1実施形態で説明した方法と同様の方法を用いることで、半導体装置ユニットB2を得る。

【0090】

次に、半導体装置ユニットB2の作用について説明する。

【0091】

このような構成によれば、半導体装置A1dおよびA1eの支持基板1を、個別に設ける必要がない。そのため、半導体装置A1d,A1eを単に積層させた場合と比較して、x方向における半導体装置ユニットB2の大きさを、小さくできる。これにより、半導体装置ユニットB2のコンパクト化を図ることができる。

【0092】

また、半導体装置A1eの表面電極41a,41bや裏面電極42を半導体装置ユニットB2の外部と導通させるために設ける必要があるワイヤの本数を、少なくできる。

【0093】

また、本実施形態でも、本発明にかかる第1および第2の半導体装置が同一の回路素子であるバイポーラトランジスタを構成するものを示した。だが、本発明にかかる半導体装置ユニットは、本発明にかかる第1の半導体装置と第2の半導体装置とが異なる回路素子を構成していてもよい。

【0094】

本発明の範囲は、上述した実施形態に限定されるものではない。本発明に係る半導体装置の各部の具体的な構成は、種々に設計変更自在である。たとえば、本発明でいう回路素子は、バイポーラトランジスタに限定されず、MOSFETなどでもよい。また、pn接合ダイオードやショットキー接合ダイオードなどでもよい。ショットキー接合ダイオードが形成されている場合、本発明にかかる半導体基板に回路素子の一部が形成されているといえる。

【0095】

上記半導体装置の厚さ方向視において、上記導電部を格子状に配置したり、千鳥配置にしたりしても良い。このような構成によれば、上記厚さ方向視において、同一領域内に形成できる上記導電部の数を多くすることができる。これにより、上記導電部全体の内部抵抗を小さくすることができる。また、上記表面電極と上記導電部との接触抵抗をより小さくできる。

【符号の説明】

【0096】

A1,A2,A3,A1a,A1b,A1c,A1d,A1e 半導体装置

B1,B1’,B2 半導体装置ユニット

1 支持基板

mb 中間基板

2a 接着部

2b 保護絶縁膜

3 半導体基板

30,32,33 n型半導体層

31 p型半導体層

34,61a,61b,62a,62b 絶縁部

41a,41b 表面電極

42 裏面電極

51a,51b,51a’,51b’,55,56 導電部

52a,52b,52a’,52b’,54a,54b 外部接続電極

53a,53b 延出電極

8,8’,8a,8b,8c バンプ

d 電極

h 孔

x 方向

【技術分野】

【0001】

本発明は、半導体装置および半導体装置ユニットに関する。

【背景技術】

【0002】

ダイオードやトランジスタなどの半導体装置は、たとえばリードや基板に搭載された、いわゆるパッケージの形態として用いられる。近年、携帯機器を中心として電子機器の小型化が進んでいる。そのため、半導体装置が実装された半導体パッケージの小型化が望まれている。

【0003】

従来、半導体パッケージとして特許文献1に示されたものが知られている。図17に示すように、この半導体パッケージは、半導体装置9Aと、モールド樹脂97を備えている。半導体装置9Aは、半導体チップ93、ベース電極941、エミッタ電極942、コレクタ電極943、リード9d1,9d2、Auバンプ981,982およびボンディングワイヤ9wを備えている。半導体チップ93は、バイポーラトランジスタを構成している。ベース電極941およびエミッタ電極942は、半導体チップ93の図下面に配置されている。コレクタ電極943は、半導体チップ93の図上面に配置されている。ベース電極941は、バンプ981を介して、図示しないリードと電気的に接続している。エミッタ電極942は、バンプ982を介して、リード9d1と電気的に接続している。コレクタ電極943は、ボンディングワイヤ9wにより、リード9d2と電気的に接続している。モールド樹脂97は、半導体装置9Aの上記の各構成部品を覆っている。

【0004】

半導体装置9Aにおいては、ボンディングワイヤ9wを備えていることから、モールド樹脂97を、ボンディングワイヤ9wを十分に覆うことのできる大きさとする必要がある。そのため、半導体装置9Aを備えた半導体パッケージの小型化を図ることが困難となっていた。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2001−60598号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

本発明は、上記した事情のもとで考え出されたものであって、半導体パッケージをより小型とすることができる半導体装置を提供することを主たる課題とする。

【課題を解決するための手段】

【0007】

本発明の第1の側面によって提供される半導体装置は、回路素子の少なくとも一部が形成された半導体基板と、上記半導体基板の表面に配置された1または複数の表面電極と、上記半導体基板の裏面に配置され、上記回路素子と導通している裏面電極と、を備え、1以上の上記表面電極が上記回路素子と導通している、半導体装置であって、上記表面の側に配置されており、かつ、上記半導体基板、上記表面電極および上記裏面電極を支持している支持基板と、上記表面電極と導通しているとともに、上記半導体基板の表面の側および上記半導体基板の裏面の側において露出している導電部と、をさらに備えることを特徴としている。

【0008】

本発明の好ましい実施の形態においては、上記導電部は上記半導体基板を貫通している。このような構成によれば、上記回路素子を外部端子と接続するためにワイヤボンディングを施す必要がなくなる。そのため、上記半導体装置を実装する半導体パッケージに、ボンディングワイヤのパッドを設ける必要がなくなる。これにより、上記半導体パッケージの小型化を図ることが可能となる。

【0009】

本発明の好ましい実施の形態においては、上記導電部が延びる方向に沿って、上記導電部を貫通する絶縁部が形成されている。

【0010】

本発明の好ましい実施の形態においては、上記半導体基板は、上記導電部が延びる方向に沿って形成された貫通孔と、この貫通孔の内面に形成された絶縁膜と、を備えており、この絶縁膜は上記導電部を被膜している。

【0011】

本発明の好ましい実施の形態においては、上記裏面の側には、上記導電部と導通している外部接続電極が配置され、上記裏面電極は、上記半導体基板の裏面と接触しており、上記裏面電極と上記裏面との接触部分のうち通電する部分の面積である通電面積が、上記外部接続電極の面積より大きい。

【0012】

本発明の好ましい実施の形態においては、上記裏面の側には、上記外部接続電極と導通しているバンプが配置され、このバンプと上記導電部とが、上記半導体基板の面内方向において重ならないように配置されている。

【0013】

本発明の好ましい実施の形態においては、上記半導体基板の裏面の側から上記半導体基板の表面に向かって延出しているとともに上記表面電極または上記裏面電極と導通している延出電極と、上記延出電極と接しているバンプと、をさらに備えている。このような構成によれば、上記半導体装置が上記半導体装置の幅方向に大きくなることを抑制しつつ、上記バンプが接触している電極と上記バンプとの接触面積を、大きくできる。そのため、上記バンプが接触している電極と上記バンプとの接触抵抗の値を、小さくできる。

【0014】

本発明の好ましい実施の形態においては、上記半導体基板の裏面の側に配置され、かつ、上記延出電極と接しているとともに、上記バンプと接している外部接続電極をさらに備えている。このような構成によれば、上記バンプが接触する電極と上記バンプとの接触面積を、さらに大きくすることができる。そのため、上記バンプが接触する電極と上記バンプとの接触抵抗の値を、さらに小さくできる。

【0015】

本発明の好ましい実施の形態においては、上記導電部は、上記半導体基板を貫通しており、上記延出電極は、上記半導体装置の側面に形成され、かつ、上記導電部と異なるものとされている。

【0016】

本発明の好ましい実施の形態においては、上記導電部が延びる方向に沿って、上記導電部を貫通する絶縁部が形成されている。

【0017】

本発明の好ましい実施の形態においては、上記延出電極は、上記半導体装置の側面に形成され、かつ、上記導電部とされている。このような構成によれば、上記導電部と異なる上記延出電極を形成する必要がない。すなわち、上記半導体装置の上記回路素子が構成されている部分から、上記半導体装置の幅方向において、上記導電部より遠い位置に、上記延出電極を形成する必要がない。そのため、幅方向の大きさがより小さい上記半導体装置を提供できる。

【0018】

本発明の好ましい実施の形態においては、上記回路素子は、トランジスタであり、このトランジスタと接続される3つの電極のうちの2つが、上記表面電極とされ、これらの3つの電極のうちの他の1つが、上記裏面電極とされている。

【0019】

本発明の第2の側面によって提供される半導体装置ユニットは、本発明の第1の側面にかかる2つの半導体装置を備え、これら2つの半導体装置の一方である第1の半導体装置の上記表面電極と、これら2つの半導体装置の他方である第2の半導体装置における上記裏面電極とが、対向するように、上記第1および第2の半導体装置が積層されており、上記第1の半導体装置の上記支持基板上に固定されているとともに、上記第2の半導体装置の上記導電部または上記裏面電極と導通しているボンディングリボンを備えている。

【0020】

このような構成によれば、上記第2の半導体装置の上記導電部または上記裏面電極を、上記半導体装置ユニットの外部と導通させるためのワイヤボンディングを施す必要がない。そのため、上記第1の半導体装置の上に上記第2の半導体装置を積層させた場合でも、上記第1の半導体装置の上記支持基板の面方向の大きさを大きくする必要がない。

【0021】

本発明の好ましい実施の形態においては、上記第2の半導体装置は、請求項6に記載の半導体装置であり、上記ボンディングリボンは、上記第2の半導体装置の上記バンプと接合されており、かつ、上記第1の半導体装置の上記支持基板上に固定されている。

【0022】

本発明の好ましい実施の形態においては、上記第1の半導体装置の上記支持基板を貫通している追加の導電部をさらに備え、この追加の導電部は、上記第1の半導体装置の上記表面電極と、上記第2の半導体装置の上記導電部または上記裏面電極であって、上記ボンディングリボンと導通しているものとは異なるものと、いずれとも導通している。このような構成によれば、上記第1の半導体装置の上記表面電極と、上記第2の半導体装置の上記導電部または上記裏面電極とが、上記追加の導電部により、直接、導通させられる。そのため、上記追加の導電部と導通している、上記第2の半導体装置の上記導電部または上記裏面電極を、上記半導体装置ユニットの外部と、上記ボンディングリボンなどを用いて導通させる必要がなくなる。これにより、上記半導体装置ユニットに設ける上記ボンディングリボンの個数を減少させうる。

【0023】

本発明の好ましい実施の形態においては、上記第2の半導体装置の上記支持基板の平面視において、上記第2の半導体装置の上記支持基板は、上記第1の半導体装置の上記支持基板からはみ出る部分を有する。

【0024】

本発明の第3の側面によって提供される半導体装置ユニットは、本発明の第1の側面にかかる2つの半導体装置を備え、これら2つの半導体装置の一方である第1の半導体装置と、これら2つの半導体装置の他方である第2の半導体装置とが積層されており、上記第1および第2の半導体装置が、同一の中間基板を、上記第1の半導体装置の上記支持基板および上記第2の半導体装置の上記支持基板として共有している。

【0025】

このような構成によれば、上記第1の半導体装置の上記支持基板および上記第2の半導体装置の上記支持基板を、別個に設ける必要がない。そのため、上記第1および第2の半導体装置を単に積層させた場合と比較して、上記第1または第2の半導体装置の厚さ方向における上記半導体装置ユニットの大きさを、小さくできる。これにより、上記半導体装置ユニットのコンパクト化が図れる。

【0026】

本発明の好ましい実施の形態においては、上記中間基板は、絶縁性を有し、上記中間基板は、上記第1の半導体装置の上記表面電極または上記裏面電極と、上記第2の半導体装置の上記表面電極または上記裏面電極と、いずれとも導通する、上記中間基板を貫通する導電部を備えている。このような構成によれば、上記第2の半導体装置の上記表面電極または上記裏面電極を上記半導体装置ユニットの外部と導通させるために設ける必要があるワイヤの本数を、少なくできる。

【0027】

本発明のその他の特徴および利点は、添付図面を参照して以下に行う詳細な説明によって、より明らかとなろう。

【図面の簡単な説明】

【0028】

【図1】本発明の第1実施形態にかかる半導体装置の要部断面図を概念的に示したものである。

【図2】図1に示した半導体装置の要部上面図を示したものである。

【図3】図1に示した半導体装置の要部底面図を示したものである。

【図4】図1に示した半導体装置の製造方法の工程を示した図である。

【図5】図4に続く工程を示す図である。

【図6】図5に続く工程を示す図である。

【図7】図6に続く工程を示す図である。

【図8】図7に続く工程を示す図である。

【図9】図8に続く工程を示す図である。

【図10】本発明の第2実施形態にかかる半導体装置の要部断面図を概念的に示したものである。

【図11】図10に示した半導体装置の製造方法の一工程を示した図である。

【図12】本発明の第3実施形態にかかる半導体装置の要部断面図を概念的に示したものである。

【図13a】本発明の第4実施形態にかかる半導体装置ユニットの斜視図である。

【図13b】図13aに示した半導体装置ユニットの断面図を概念的に示したものである。

【図14】本発明の第4実施形態にかかる半導体装置ユニットの他の一例の斜視図である。

【図15】本発明の第5実施形態にかかる半導体装置ユニットの断面図を概念的に示したものである。

【図16】図15に示した半導体装置ユニットの製造方法の一工程を示した図である。

【図17】従来の半導体装置を示す要部断面図である。

【発明を実施するための形態】

【0029】

以下、本発明の好ましい実施の形態につき、図面を参照して具体的に説明する。

【0030】

図1〜9を用いて、本発明の第1実施形態について説明する。

【0031】

図1は本発明の第1実施形態にかかる半導体装置A1を概念的に示した要部断面図である。本実施形態では半導体装置A1として、バイポーラトランジスタを示している。半導体装置A1は、支持基板1、接着部2a、保護絶縁膜2b、半導体基板3、表面電極41a,41b、裏面電極42、導電部51a,51b、外部接続電極52a,52b、絶縁部61a,61b,62a,62b、および、バンプ8を備えている。表面電極41aがエミッタ電極であり、表面電極41bがベース電極であり、裏面電極42がコレクタ電極である。

【0032】

支持基板1は、樹脂からなる接着部2a、および、保護絶縁膜2bを介して、半導体基板3、表面電極41a,41b、裏面電極42a、絶縁部61a,61b、と連結している。これにより、支持基板1は、半導体基板3、表面電極41a,41b、裏面電極42、絶縁部61a,61b,62a,62b、および、バンプ8を、支持している。支持基板1の厚さは500μm程度とされている。支持基板1はガラス製である。支持基板1として、放熱性のよい金属を用いてもよい。

【0033】

半導体基板3は、n型半導体層30、p型半導体層31、n型半導体層32、n型半導体層33および絶縁部34を備えている。これらの半導体層により、半導体基板3には、トランジスタが形成されている。本発明でいう回路素子は、本実施形態では、バイポーラトランジスタである。半導体基板3の厚さは、たとえば100μm以下であり、30μmや40μmであることが好ましい。p型半導体層31のx方向における大きさは、たとえば、5〜30μmである。絶縁部34は、半導体基板3に形成されたx方向に延びる貫通孔の内面に、形成されている。絶縁部34は、本発明でいう絶縁膜である。

【0034】

表面電極41a,41bは、半導体基板3の図中上面(本発明でいう半導体基板の表面)に配置されている。表面電極41aは、n型半導体層30および導電部51aと導通している。表面電極41aは、絶縁部61aにより、p型半導体層31およびn型半導体層32と絶縁されている。同様に、表面電極41bは、p型半導体層31および導電部51bと導通している。表面電極41bは、絶縁部61bにより、n型半導体層32と絶縁されている。また、表面電極41a,41bは、たとえばSiNなどからなる保護絶縁膜2bにより覆われ、保護されている。なお、製造工程を削減するため、保護絶縁膜2bを形成せず、表面電極41a,41b上に直接、接着部2aを形成してもよい。

【0035】

裏面電極42は、半導体基板3の図中下面(本発明でいう半導体基板の裏面)に配置されている。裏面電極42は、n型半導体層33と導通している。

【0036】

導電部51a,51bは、x方向に沿って、半導体基板3を貫通するように形成されている。また、導電部51a,51bは、半導体基板3の表面の側および半導体基板3の裏面の側において露出しているともいえる。導電部51a,51bは、円筒状である。なお、導電部51a,51bの形状は、x方向視において、円形である必要はない。たとえば、方形状でもよい。また、導電部51a,51bは、円錐筒状であってもよい。導電部51a,51bの周囲には、絶縁部34が形成されている。絶縁部34は、導電部51aとn型半導体層32,33とを絶縁している。同様に、絶縁部34は、導電部51bとn型半導体層32,33とを絶縁している。絶縁部62a,62bが、導電部51a,51bの内側にそれぞれ形成されている。絶縁部62a,62bは、導電部51a,51bが延びる方向(本実施形態ではx方向)に沿って、導電部51a,51b、をそれぞれ貫通している。さらに、絶縁部62a,62bは、導電部51a,51bと裏面電極42とを絶縁している。

【0037】

外部接続電極52a,52bは、半導体基板3の裏面に配置されている。外部接続電極52aは導電部51aと、外部接続電極52bは導電部51bと、それぞれ導通している。

【0038】

バンプ8は、本実施形態に係る半導体装置A1が外部端子と電気的に接続可能とするために形成されている。バンプ8は、裏面電極42ないし外部接続電極52a,52bと導通している。また、バンプ8は、半導体装置A1が取り付けられる半導体パッケージ(図示略)の配線基板などに接続されている。

【0039】

図2には、図1に示した半導体装置A1の要部上面図を示している。図3には、本実施形態にかかる半導体装置A1の要部底面図を示している。図2では、図1に示した支持基板1、接着部2a、保護絶縁膜2b、表面電極41a,41b、絶縁部61a,61bを、理解の便宜上省略している。同様に、図3では、図1に示した絶縁部62a,62bを省略している。図2,3において、導電部51a’は、図1に示した導電部51aに対応する。同様に、導電部51b’は導電部51bに対応する。図3において、裏面電極42’は、図1に示した裏面電極42に対応する。同様に、外部接続電極52a’,52b’は、外部接続電極52a,52bにそれぞれ対応する。また、バンプ8’は、バンプ8に対応する。

【0040】

図2に表されているように本実施形態では、従来の半導体装置においてワイヤボンディングパッドが形成されていた領域に、導電部51a’,51b’が形成されている。図1で示したように、導電部51a’は、エミッタ電極である表面電極41aに導通している。そのため、導電部51a’は、ベース電極である表面電極41bと導通している導電部51b’と比較して、より大きい電流を流す必要がある。このため、図2および図3によく表われているように、導電部51a’は3つ、導電部51b’は1つ、形成されている。もちろん、導電部51a’,51b’の個数の組み合わせは、これに限られない。

【0041】

図3によく表れているように、裏面電極42’の面積は、外部接続電極52a’、または外部接続電極52b’の面積と比較して大きい。また、バンプ8’は、導電部51a’または51b’と重ならないように配置されている。

【0042】

図4〜図9を用いて、半導体装置A1の製造方法について説明する。

【0043】

まず、図4に示すように、公知の方法により、半導体基板3を作成する。そして、この半導体基板3に、絶縁部61a,61b、および、表面電極41a,41bを形成する。次に、表面電極41a,41b、または、絶縁部61a,61bの図中上部に、保護絶縁膜2b、接着部2aを形成する。

【0044】

次に、図5に示すように、接着部2aの図中上部に、支持基板1を接合する。次に、図6に示すように、半導体基板3におけるn型半導体層33の図中下方を研削する。このとき、n型半導体層33の厚さは、500〜800μmとなっている。支持基板1がなければ、以下で述べる導電部51a,51bの形成の際に半導体基板3が折れ曲がったりすることを防ぐために、半導体基板3の厚さは100μm以上である必要がある。しかしながら、本実施形態に係る半導体装置A1は支持基板1を備えている。そのため、半導体基板3の厚さが100μm以下、たとえば30μmと薄いものであっても、導電部51a,51bの形成の際に半導体基板3が折れ曲がったりすることはない。

【0045】

次に、図7に示すように、半導体基板3の図中下部から孔を形成する。そして、この孔の内面およびn型半導体層33の図中下面に、たとえば酸化処理によってSiO2からな

る絶縁部34を形成する。次に、図8に示すように、絶縁部34の表面に、導電部51a,51bを形成する。その後、外部接続電極52a,52bおよび裏面電極42を形成する。次に、図9に示すように、絶縁部62a,62bを形成する。その後、図1に示したバンプ8を形成し、半導体装置A1が完成する。

【0046】

次に、半導体装置A1の作用について説明する。

【0047】

本実施形態によれば、半導体装置A1を外部端子と接続するためのワイヤボンディングを施す必要がなくなる。そのため、ボンディングワイヤを樹脂で覆うことが不要となる。また、半導体装置A1は支持基板1を備えているため、従来の半導体装置に比べて、n型半導体層33をより薄くすることができる。これにより、半導体基板3をより薄くすることができる。その結果、半導体装置A1を実装する半導体パッケージの厚さをより小さくすることが可能となる。また、n型半導体層33が薄くなることから、半導体装置A1の低抵抗化が望める。

【0048】

また、ワイヤボンディングを施すことが不要となることから、半導体装置A1を実装する半導体パッケージにボンディングワイヤを接続するためのパッドを設ける必要がなくなる。そのため、半導体装置A1の平面視において、半導体装置A1を実装する半導体パッケージの小型化を図ることが可能となる。

【0049】

導電部51a,51bの内側にはそれぞれ、絶縁部62a,62bが充填されている。そのため、導電部51a,51bを形成するために用いる導電材料を、より少なくできる。その結果半導体装置A1の製造コストの減少を図ることが可能となる。

【0050】

図3に示したように、裏面電極42’の面積は、外部接続電極52a’、または外部接続電極52b’の面積と比較して大きい。そのため、たとえ外部接続電極52a’や外部接続電極52b’を形成したとしても、これらの外部接続電極を形成しない場合と比較して、裏面電極42’とn型半導体層33との接触面積を大幅に減少させる必要はない。その結果、半導体装置A1において、裏面電極42とn型半導体層33との接触抵抗を低いまま維持しうる。

【0051】

半導体装置A1において発生した熱が、表面電極41a,41b、導電部51a,51b、外部接続電極52a,52bそしてバンプ8と伝導する。その後、この熱は、半導体パッケージに伝導され、外部に放出される。つまり、本実施形態では、半導体装置A1で発生した熱を、容易に外部に放出することが可能となっている。

【0052】

バンプ8は、外部接続電極52a,52bを介して、導電部51a,51bと導通している。そのため、バンプ8の形成位置は、導電部51aの位置に拘束されない。すなわち、半導体装置A1を実装する半導体パッケージの形状等に応じて、バンプ8の形成位置を自在に決定できる。

【0053】

図10〜16は、本発明の他の実施形態を示している。なお、これらの図において、上記実施形態と同一または類似の要素には、上記実施形態と同一の符号を付している。

【0054】

図10,11を用いて、本発明の第2実施形態について説明する。

【0055】

図10は本発明の第2実施形態にかかる半導体装置A2を示した断面図である。半導体装置A2は、半導体装置A1の基本的な構成に加えて、延出電極53a,53b、外部接続電極54a,54b、バンプ8a,8bを備えている。半導体装置A2は、ほぼ左右対称であるから、以下では、半導体装置A2の図中左側に形成された、延出電極53a、外部接続電極54a、バンプ8aについて、説明する。以下の説明は、半導体装置A2の図中右側に形成された、延出電極53b、外部接続電極54b、バンプ8b、についても同様に適用できる。

【0056】

延出電極53aは、半導体装置A2の側面(図中左方の面)に形成されている。延出電極53aは、半導体基板3の裏面から半導体基板3の表面に向かって延びている。延出電極53aは、半導体基板3の表面まで達しており、表面電極41aと接している。これにより、延出電極53aは表面電極41aと導通している。

【0057】

外部接続電極54aは、半導体基板3の図中下面に配置されている。外部接続電極54aは、その左端において、延出電極53aと接している。また、外部接続電極54aは、その右端において、導電部51aとも接している。

【0058】

図10に表れているように、バンプ8aは、外部接続電極54aの図中右端の近傍から延出電極53aの図中上端の近傍にわたって、外部接続電極54aおよび延出電極53aと接している。バンプ8aは、半導体装置A2が外部端子と電気的に接続可能とするために形成されている。

【0059】

図11を用いて、半導体装置A2の製造方法について説明する。

【0060】

半導体装置A2の製造は、第1実施形態において述べた方法とほぼ同様に行う。そのため、以下では、半導体装置A1の製造方法と異なる工程について主に述べる。まず、図4,5に示した工程を実行し、図6に示されたものを製造する。次に、図7に示したように、半導体基板3に2つの孔を設ける。さらに半導体装置A2の製造においては、半導体基板3に、別の孔を形成する。この孔は、図11で示した孔hである。次に、図11に示すように、孔hの内部に、延出電極53a,53bなどを形成する。その後、外部接続電極54a,54bなどを形成するなどして、図11に示したものを得る。図11は、図8と比べて、孔h、延出電極53a,53bの有無などにおいて異なる。

【0061】

次に、図11に示されたものを、孔hで分断されるように線Lに沿って切断する。その後、図10で示した絶縁部62a,62bおよびバンプ8a,8b,8cを形成する。これにより、半導体装置A2が完成する。

【0062】

次に、半導体装置A2の作用について説明する。

【0063】

このような構成によれば、半導体装置A2が半導体装置A2の幅方向に大きくなることを抑制しつつ、たとえば外部接続電極54aおよび延出電極53aとバンプ8aとの接触面積を、大きくできる。そのため、外部接続電極54aおよび延出電極53aとバンプ8aとの接触抵抗の値を、小さくできる。また、上記接触面積が大きくなっていることから、外部接続電極54aおよび延出電極53aと、バンプ8aとを、強固に接合することが可能となっている。

【0064】

なお、図においては、延出電極53a,53bが真上方向に延びている。もちろん、本発明にかかる延出電極が延びる方向はこれに限られない。たとえば、図斜め上方向に延出電極53a,53bが延びていてもよい。また、外部接続電極54a,54bの形成は必ずしも必要はない。

【0065】

さらに、延出電極53aは、半導体基板3の表面まで達していなくてもよい。このとき、延出電極53aを、外部接続電極54aおよび導電部51aを介して、表面電極41aと導通させるとよい。

【0066】

図12を用いて、本発明の第3実施形態について説明する。

【0067】

本実施形態では、延出電極53aが導電部51aとされている。同様に、延出電極53bが導電部51bとされている。延出電極53a,53bは、半導体装置A3の側面(図における左側または右側)に形成されている。半導体装置A3は、半導体装置A2と同様に製造できる。

【0068】

このような構成によれば、導電部51aや導電部51bと異なる延出電極を形成する必要がない。すなわち、導電部51aや導電部51bより外側に、延出電極を形成する必要がない。これにより、幅方向において小さい半導体装置A3を提供できる。

【0069】

図13a,13bを用いて、本発明の第4実施形態について説明する。

【0070】

図13aは、本発明の第4実施形態にかかる半導体装置ユニットの斜視図である。同図に示された半導体装置ユニットB1は、第1実施形態で示した半導体装置A1が積層されている。図13bは、図13aに示した半導体装置ユニットの断面図を概念的に示したものである。図13bでは、図13aで示した半導体装置ユニットB1の半導体装置A1のうち、下から2つの半導体装置A1a,A1bを示している。

【0071】

図13a,13bに表れているように、半導体装置ユニットB1は、半導体装置A1aおよび半導体装置A1bが積層されている。半導体装置A1aは、本発明にかかる第1の半導体装置に相当する。半導体装置A1bは、本発明にかかる第2の半導体装置に相当する。図13bに表れているように、半導体装置ユニットB1において、半導体装置A1aの表面電極41a,41bと、半導体装置A1bの裏面電極42とが、対向している。

【0072】

半導体装置ユニットB1は、ボンディングリボンw1、および、導電部55を備えている。

【0073】

図13a,13bに表れているように、ボンディングリボンw1は、薄い帯状の導電体である。ボンディングリボンw1は、たとえばアルミニウムから構成されている。図示していないが、ボンディングリボンw1は、半導体装置ユニットB1の外部の電極などと導通している。図13bに表れているように、ボンディングリボンw1は、半導体装置A1aの支持基板1上の固定されている。ボンディングリボンw1は、バンプ8aと接合している。これにより、ボンディングリボンw1は、半導体装置A1bの導電部51aと導通している。

【0074】

導電部55は、半導体装置A1aの支持基板1に形成され、この支持基板1を貫通している。導電部55は、本発明でいう追加の導電部に相当する。導電部55は、半導体装置A1aの表面電極41bと導通している。導電部55は、半導体装置A1bのバンプ8bと、電極dを介して導通している。これにより、導電部55は、半導体装置A1bの導電部51bと導通しているといえる。半導体装置A1bのバンプ8bは、ボンディングリボンw1と導通している半導体装置A1bのバンプ8aとは異なるものである。また、半導体装置A1bのバンプ8cには、ボンディングリボンw2が接続されている。

【0075】

このような構成によれば、半導体装置A1bのバンプ8a,8b,8cを、半導体装置ユニットB1の外部と導通させるためのワイヤボンディングを施す必要がない。そのため、半導体装置A1aの上に半導体装置A1bを積層させた場合でも、ワイヤボンディングのためのパッドを設ける必要がなく、半導体装置A1aの支持基板1の面方向の大きさを大きくする必要がない。その結果、半導体装置ユニットB1を実装するために必要な、半導体パッケージにおけるスペースを小さくすることができる。特に、半導体装置ユニットB1を、ディスクリート部品として用いる場合に好適である。

【0076】

また上述した構成によれば、半導体装置A1bのバンプ8aの形成する位置を適宜移動させることにより、半導体装置A1aの支持基板1上におけるボンディングリボンw1を形成する位置を、自在に決定できる。

【0077】

半導体装置A1aの表面電極41bと、半導体装置A1bのバンプ8bとが、導電部55により、直接、導通させられる。そのため、半導体装置A1bのバンプ8bを、半導体装置ユニットB1の外部と、ボンディングリボンw1などを用いて導通させる必要がなくなる。これにより、半導体装置ユニットB1に設けるボンディングリボンw1の個数を少なくすることが可能となっている。

【0078】

半導体装置ユニットB1において、半導体装置A1bと半導体装置A1cとの間にも、ボンディングリボンw1,w2が設けられている。半導体装置A1bと半導体装置A1cとの関係は、上述した半導体装置A1aと半導体装置A1bとの関係と同様である。

【0079】

また、本実施形態では、本発明にかかる第1および第2の半導体装置が同一の回路素子であるバイポーラトランジスタを構成するものを示した。だが、本発明にかかる半導体装置ユニットは、本発明にかかる第1の半導体装置と第2の半導体装置とが異なる回路素子を構成していてもよい。また、第2実施形態にかかる半導体装置A2と半導体装置A1とが積層されたものであってもよい。

【0080】

また、半導体装置A1bの支持基板1の平面視において、半導体装置A1bの支持基板1は、半導体装置A1aの支持基板1からはみ出る部分を有していてもよい。たとえば、図14で示すように、半導体装置ユニットB1’における半導体装置A1の幅方向の大きさを、半導体装置ユニットB1’の上部にいくにつれて序々に大きくしてもよい。このような構成によれば、ボンディングリボンw1どうし、ならびに、ボンディングリボンw2どうしの干渉を抑制することができる。

【0081】

図15,16を用いて、本発明の第5実施形態について説明する。

【0082】

図15は、本発明の第5実施形態にかかる半導体装置ユニットの断面図を概念的に示したものである。

【0083】

同図に示された半導体装置ユニットB2は、第1実施形態で示した半導体装置A1が2つ積層した構成とされている。半導体装置ユニットB2における半導体装置A1のうち、図中下方に示されたものが、半導体装置A1dである。一方、半導体装置ユニットB2における半導体装置A1のうち、図中上方に示されたものが、半導体装置A1eである。半導体装置A1dは、本発明にかかる第1の半導体装置に相当する。半導体装置A1eは、本発明にかかる第2の半導体装置に相当する。

【0084】

図15に表れているように、半導体装置ユニットB2において、半導体装置A1dと半導体装置A1eとが、同一の中間基板mbを、半導体装置A1dの支持基板1および半導体装置A1eの支持基板1として共有している。

【0085】

中間基板mbは、絶縁性を有し、導電部56を備えている。導電部56は、中間基板mbを貫通している。導電部56は、半導体装置A1dの表面電極41bと導通している。また、導電部56は、半導体装置A1eの表面電極41aとも導通している。導電部56の形成は、かならずしも必要ではない。

【0086】

半導体装置A1dのバンプ8a,8b,8cは、第1実施形態で述べたのと同様に、半導体装置ユニットB2が取り付けられるパッケージ(図示略)の配線基板などに接続される。一方、半導体装置A1eのバンプ8a,8b,8cには、たとえば半導体装置ユニットB2の外部と接続するためのボンディングワイヤが接続される。

【0087】

次に、半導体装置ユニットB2の製造方法について説明する。

【0088】

まず、第1実施形態で説明した方法と同様の方法により、半導体装置A1dを製造する。このとき、半導体装置A1dの支持基板1を貼り付ける際に既に導電部56が形成された支持基板1を用いる。

【0089】

次に、図16に示すように、図4で示したものと同一のものを、半導体装置A1dの支持基板1の表面に接合する。次に、半導体装置A1eとなるもののn型半導体層33を研削するなど、第1実施形態で説明した方法と同様の方法を用いることで、半導体装置ユニットB2を得る。

【0090】

次に、半導体装置ユニットB2の作用について説明する。

【0091】

このような構成によれば、半導体装置A1dおよびA1eの支持基板1を、個別に設ける必要がない。そのため、半導体装置A1d,A1eを単に積層させた場合と比較して、x方向における半導体装置ユニットB2の大きさを、小さくできる。これにより、半導体装置ユニットB2のコンパクト化を図ることができる。

【0092】

また、半導体装置A1eの表面電極41a,41bや裏面電極42を半導体装置ユニットB2の外部と導通させるために設ける必要があるワイヤの本数を、少なくできる。

【0093】

また、本実施形態でも、本発明にかかる第1および第2の半導体装置が同一の回路素子であるバイポーラトランジスタを構成するものを示した。だが、本発明にかかる半導体装置ユニットは、本発明にかかる第1の半導体装置と第2の半導体装置とが異なる回路素子を構成していてもよい。

【0094】

本発明の範囲は、上述した実施形態に限定されるものではない。本発明に係る半導体装置の各部の具体的な構成は、種々に設計変更自在である。たとえば、本発明でいう回路素子は、バイポーラトランジスタに限定されず、MOSFETなどでもよい。また、pn接合ダイオードやショットキー接合ダイオードなどでもよい。ショットキー接合ダイオードが形成されている場合、本発明にかかる半導体基板に回路素子の一部が形成されているといえる。

【0095】

上記半導体装置の厚さ方向視において、上記導電部を格子状に配置したり、千鳥配置にしたりしても良い。このような構成によれば、上記厚さ方向視において、同一領域内に形成できる上記導電部の数を多くすることができる。これにより、上記導電部全体の内部抵抗を小さくすることができる。また、上記表面電極と上記導電部との接触抵抗をより小さくできる。

【符号の説明】

【0096】

A1,A2,A3,A1a,A1b,A1c,A1d,A1e 半導体装置

B1,B1’,B2 半導体装置ユニット

1 支持基板

mb 中間基板

2a 接着部

2b 保護絶縁膜

3 半導体基板

30,32,33 n型半導体層

31 p型半導体層

34,61a,61b,62a,62b 絶縁部

41a,41b 表面電極

42 裏面電極

51a,51b,51a’,51b’,55,56 導電部

52a,52b,52a’,52b’,54a,54b 外部接続電極

53a,53b 延出電極

8,8’,8a,8b,8c バンプ

d 電極

h 孔

x 方向

【特許請求の範囲】

【請求項1】

回路素子の少なくとも一部が形成された半導体基板と、

上記半導体基板の表面に配置された1または複数の表面電極と、

上記半導体基板の裏面に配置され、上記回路素子と導通している裏面電極と、

を備え、

1以上の上記表面電極が上記回路素子と導通している、半導体装置であって、

上記表面の側に配置されており、かつ、上記半導体基板、上記表面電極および上記裏面電極を支持している支持基板と、

上記表面電極と導通しているとともに、上記半導体基板の表面の側および上記半導体基板の裏面の側において露出している導電部と、

をさらに備えることを特徴とする、半導体装置。

【請求項2】

上記導電部は上記半導体基板を貫通している、請求項1に記載の半導体装置。

【請求項3】

上記導電部が延びる方向に沿って、上記導電部を貫通する絶縁部が形成されている、請求項2に記載の半導体装置。

【請求項4】

上記半導体基板は、上記導電部が延びる方向に沿って形成された貫通孔と、この貫通孔の内面に形成された絶縁膜と、を備えており、

この絶縁膜は上記導電部を被膜している、請求項2または3に記載の半導体装置。

【請求項5】

上記裏面の側には、上記導電部と導通している外部接続電極が配置され、

上記裏面電極は、上記半導体基板の裏面と接触しており、

上記裏面電極と上記裏面との接触部分のうち通電する部分の面積である通電面積が、上記外部接続電極の面積より大きい、請求項2ないし4のいずれかに記載の半導体装置。

【請求項6】

上記裏面の側には、上記外部接続電極と導通しているバンプが配置され、

このバンプと上記導電部とが、上記半導体基板の面内方向において重ならないように配置されている、請求項5に記載の半導体装置。

【請求項7】

上記半導体基板の裏面の側から上記半導体基板の表面に向かって延出しているとともに上記表面電極または上記裏面電極と導通している延出電極と、

上記延出電極と接しているバンプと、

をさらに備えている、請求項1に記載の半導体装置。

【請求項8】

上記半導体基板の裏面の側に配置され、かつ、上記延出電極と接しているとともに、上記バンプと接している外部接続電極をさらに備えている、請求項7に記載の半導体装置。

【請求項9】

上記導電部は、上記半導体基板を貫通しており、

上記延出電極は、上記半導体装置の側面に形成され、かつ、上記導電部と異なるものとされている、請求項7または8に記載の半導体装置。

【請求項10】

上記導電部が延びる方向に沿って、上記導電部を貫通する絶縁部が形成されている、請求項9に記載の半導体装置。

【請求項11】

上記延出電極は、上記半導体装置の側面に形成され、かつ、上記導電部とされている、請求項7または8に記載の半導体装置。

【請求項12】

上記回路素子は、トランジスタであり、

このトランジスタと接続される3つの電極のうちの2つが、上記表面電極とされ、

これらの3つの電極のうちの他の1つが上記裏面電極とされている、請求項1ないし11のいずれかに記載の半導体装置。

【請求項13】

請求項1ないし12のいずれかに記載の2つの半導体装置を備え、

これら2つの半導体装置の一方である第1の半導体装置の上記表面電極と、これら2つの半導体装置の他方である第2の半導体装置における上記裏面電極とが、対向するように、上記第1および第2の半導体装置が積層されており、

上記第1の半導体装置の上記支持基板上に固定されているとともに、上記第2の半導体装置の上記導電部または上記裏面電極と導通しているボンディングリボンを備えている、半導体装置ユニット。

【請求項14】

上記第2の半導体装置は、請求項6に記載の半導体装置であり、

上記ボンディングリボンは、上記第2の半導体装置の上記バンプと接合されており、かつ、上記第1の半導体装置の上記支持基板上に固定されている、請求項13に記載の半導体装置ユニット。

【請求項15】

上記第1の半導体装置の上記支持基板を貫通している追加の導電部をさらに備え、

この追加の導電部は、

上記第1の半導体装置の上記表面電極と、

上記第2の半導体装置の上記導電部または上記裏面電極であって、上記ボンディングリボンと導通しているものとは異なるものと、

いずれとも導通している、請求項13または14に記載の半導体装置ユニット。

【請求項16】

上記第2の半導体装置の上記支持基板の平面視において、上記第2の半導体装置の上記支持基板は、上記第1の半導体装置の上記支持基板からはみ出る部分を有する、請求項13ないし15のいずれかに記載の半導体装置ユニット。

【請求項17】

請求項1ないし12のいずれかに記載の2つの半導体装置を備え、

これら2つの半導体装置の一方である第1の半導体装置と、これら2つの半導体装置の他方である第2の半導体装置とが積層されており、

上記第1および第2の半導体装置が、同一の中間基板を、上記第1の半導体装置の上記支持基板および上記第2の半導体装置の上記支持基板として共有している、半導体装置ユニット。

【請求項18】

上記中間基板は、絶縁性を有し、

上記中間基板は、上記第1の半導体装置の上記表面電極または上記裏面電極と、上記第2の半導体装置の上記表面電極または上記裏面電極と、いずれとも導通する、上記中間基板を貫通する導電部を備えている、請求項17に記載の半導体装置ユニット。

【請求項1】

回路素子の少なくとも一部が形成された半導体基板と、

上記半導体基板の表面に配置された1または複数の表面電極と、

上記半導体基板の裏面に配置され、上記回路素子と導通している裏面電極と、

を備え、

1以上の上記表面電極が上記回路素子と導通している、半導体装置であって、

上記表面の側に配置されており、かつ、上記半導体基板、上記表面電極および上記裏面電極を支持している支持基板と、

上記表面電極と導通しているとともに、上記半導体基板の表面の側および上記半導体基板の裏面の側において露出している導電部と、

をさらに備えることを特徴とする、半導体装置。

【請求項2】

上記導電部は上記半導体基板を貫通している、請求項1に記載の半導体装置。

【請求項3】

上記導電部が延びる方向に沿って、上記導電部を貫通する絶縁部が形成されている、請求項2に記載の半導体装置。

【請求項4】

上記半導体基板は、上記導電部が延びる方向に沿って形成された貫通孔と、この貫通孔の内面に形成された絶縁膜と、を備えており、

この絶縁膜は上記導電部を被膜している、請求項2または3に記載の半導体装置。

【請求項5】

上記裏面の側には、上記導電部と導通している外部接続電極が配置され、

上記裏面電極は、上記半導体基板の裏面と接触しており、

上記裏面電極と上記裏面との接触部分のうち通電する部分の面積である通電面積が、上記外部接続電極の面積より大きい、請求項2ないし4のいずれかに記載の半導体装置。

【請求項6】

上記裏面の側には、上記外部接続電極と導通しているバンプが配置され、

このバンプと上記導電部とが、上記半導体基板の面内方向において重ならないように配置されている、請求項5に記載の半導体装置。

【請求項7】

上記半導体基板の裏面の側から上記半導体基板の表面に向かって延出しているとともに上記表面電極または上記裏面電極と導通している延出電極と、

上記延出電極と接しているバンプと、

をさらに備えている、請求項1に記載の半導体装置。

【請求項8】

上記半導体基板の裏面の側に配置され、かつ、上記延出電極と接しているとともに、上記バンプと接している外部接続電極をさらに備えている、請求項7に記載の半導体装置。

【請求項9】

上記導電部は、上記半導体基板を貫通しており、

上記延出電極は、上記半導体装置の側面に形成され、かつ、上記導電部と異なるものとされている、請求項7または8に記載の半導体装置。

【請求項10】

上記導電部が延びる方向に沿って、上記導電部を貫通する絶縁部が形成されている、請求項9に記載の半導体装置。

【請求項11】

上記延出電極は、上記半導体装置の側面に形成され、かつ、上記導電部とされている、請求項7または8に記載の半導体装置。

【請求項12】

上記回路素子は、トランジスタであり、

このトランジスタと接続される3つの電極のうちの2つが、上記表面電極とされ、

これらの3つの電極のうちの他の1つが上記裏面電極とされている、請求項1ないし11のいずれかに記載の半導体装置。

【請求項13】

請求項1ないし12のいずれかに記載の2つの半導体装置を備え、

これら2つの半導体装置の一方である第1の半導体装置の上記表面電極と、これら2つの半導体装置の他方である第2の半導体装置における上記裏面電極とが、対向するように、上記第1および第2の半導体装置が積層されており、

上記第1の半導体装置の上記支持基板上に固定されているとともに、上記第2の半導体装置の上記導電部または上記裏面電極と導通しているボンディングリボンを備えている、半導体装置ユニット。

【請求項14】

上記第2の半導体装置は、請求項6に記載の半導体装置であり、

上記ボンディングリボンは、上記第2の半導体装置の上記バンプと接合されており、かつ、上記第1の半導体装置の上記支持基板上に固定されている、請求項13に記載の半導体装置ユニット。

【請求項15】

上記第1の半導体装置の上記支持基板を貫通している追加の導電部をさらに備え、

この追加の導電部は、

上記第1の半導体装置の上記表面電極と、

上記第2の半導体装置の上記導電部または上記裏面電極であって、上記ボンディングリボンと導通しているものとは異なるものと、

いずれとも導通している、請求項13または14に記載の半導体装置ユニット。

【請求項16】

上記第2の半導体装置の上記支持基板の平面視において、上記第2の半導体装置の上記支持基板は、上記第1の半導体装置の上記支持基板からはみ出る部分を有する、請求項13ないし15のいずれかに記載の半導体装置ユニット。

【請求項17】

請求項1ないし12のいずれかに記載の2つの半導体装置を備え、

これら2つの半導体装置の一方である第1の半導体装置と、これら2つの半導体装置の他方である第2の半導体装置とが積層されており、

上記第1および第2の半導体装置が、同一の中間基板を、上記第1の半導体装置の上記支持基板および上記第2の半導体装置の上記支持基板として共有している、半導体装置ユニット。

【請求項18】

上記中間基板は、絶縁性を有し、

上記中間基板は、上記第1の半導体装置の上記表面電極または上記裏面電極と、上記第2の半導体装置の上記表面電極または上記裏面電極と、いずれとも導通する、上記中間基板を貫通する導電部を備えている、請求項17に記載の半導体装置ユニット。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13a】

【図13b】

【図14】

【図15】

【図16】

【図17】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13a】

【図13b】

【図14】

【図15】

【図16】

【図17】

【公開番号】特開2013−77850(P2013−77850A)

【公開日】平成25年4月25日(2013.4.25)

【国際特許分類】

【出願番号】特願2013−15538(P2013−15538)

【出願日】平成25年1月30日(2013.1.30)

【分割の表示】特願2008−237548(P2008−237548)の分割

【原出願日】平成20年9月17日(2008.9.17)

【出願人】(000116024)ローム株式会社 (3,539)

【公開日】平成25年4月25日(2013.4.25)

【国際特許分類】

【出願日】平成25年1月30日(2013.1.30)

【分割の表示】特願2008−237548(P2008−237548)の分割

【原出願日】平成20年9月17日(2008.9.17)

【出願人】(000116024)ローム株式会社 (3,539)

[ Back to top ]