半導体装置およびDC−DCコンバータ

【課題】半導体装置のソース領域とドレイン領域との間のオン抵抗を低減させる。

【解決手段】第1導電型のソース領域と第1導電型のドレイン領域とが表面に選択的に形成された第2導電型のベース層と、前記ベース層内に設けられ、前記ソース領域から前記ドレイン領域の方向に延在する素子分離層と、前記素子分離層の上側に設けられ、前記ソース領域と前記ドレイン領域との間の電流経路を制御する制御電極と、前記ベース層の上側の少なくとも一部または前記素子分離層内の少なくとも一部に配置され、前記素子分離層の比誘電率よりも高い比誘電率を有する高誘電体層と、前記ソース領域に接続された第1の主電極と、前記ドレイン領域に接続された第2の主電極と、を備えたことを特徴とする半導体装置が提供される。

【解決手段】第1導電型のソース領域と第1導電型のドレイン領域とが表面に選択的に形成された第2導電型のベース層と、前記ベース層内に設けられ、前記ソース領域から前記ドレイン領域の方向に延在する素子分離層と、前記素子分離層の上側に設けられ、前記ソース領域と前記ドレイン領域との間の電流経路を制御する制御電極と、前記ベース層の上側の少なくとも一部または前記素子分離層内の少なくとも一部に配置され、前記素子分離層の比誘電率よりも高い比誘電率を有する高誘電体層と、前記ソース領域に接続された第1の主電極と、前記ドレイン領域に接続された第2の主電極と、を備えたことを特徴とする半導体装置が提供される。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置およびDC−DCコンバータに関する。

【背景技術】

【0002】

近年、微細プロセスによるデバイスとパワーデバイスとを集積し、複雑なシステムとパワーデバイスとを集積化する流れがある。パワーデバイスと組み合わせる場合でも、微細プロセスの条件を大きく変更しないことが求められる。例えば、熱工程等は、微細なCMOSデバイスの特性に影響を与えるため、なるべく変更しないことが望ましい。特に、最近の微細プロセスでは、PN接合を基板表面から浅く形成する都合上、熱履歴は少ないほどよい。

【0003】

最近、上述した微細プロセスにおいて、プロセスを追加せずに、厚いゲート酸化膜を形成する技術が報告されている(例えば、非特許文献1参照)。

そのデバイス構造は、素子分離層であるSTI(Shallow Trench Isolation)がストライプ状に形成され、そのSTI上にゲート電極が配置されるというものである。すなわち、半導体層上にはゲートを配置されない構造である。

【0004】

STI上に配置されたゲート電極と、STIとSTIとの間のPウェル領域と、が平面的に距離をもつことで、ゲート電極とPウェル領域との間に厚いゲート酸化膜が形成される。これにより、耐圧が高いゲート酸化膜が設けられる。しかしながら、パワーデバイスの単位面積あたりのオン抵抗の低減については、未だ改善されていないのが実情である。

【先行技術文献】

【非特許文献】

【0005】

【非特許文献1】J.Sonsky,G.Doornnbos,A.Heringa,M.van Duuren,J.Perez-Gonzalez,“Towards universal and voltage-scalable high gate and drain-voltage MOSFETs in CMOS",Proceedings of ISPSD 2009 IEEE,P.315-318

【発明の概要】

【発明が解決しようとする課題】

【0006】

本発明の目的は、ソース領域とドレイン領域との間の単位面積あたりのオン抵抗をより低減させた半導体装置およびこの半導体装置を組み込んだDC−DCコンバータを提供することにある。

【課題を解決するための手段】

【0007】

本発明の一態様によれば、第1導電型のソース領域と第1導電型のドレイン領域とが表面に選択的に形成された第2導電型のベース層と、前記ベース層内に設けられ、前記ソース領域から前記ドレイン領域の方向に延在する素子分離層と、前記素子分離層の上側に設けられ、前記ソース領域と前記ドレイン領域との間の電流経路を制御する制御電極と、前記ベース層の上側の少なくとも一部または前記素子分離層内の少なくとも一部に配置され、前記素子分離層の比誘電率よりも高い比誘電率を有する高誘電体層と、前記ソース領域に接続された第1の主電極と、前記ドレイン領域に接続された第2の主電極と、を備えたことを特徴とする半導体装置が提供される。

【0008】

また、本発明の一態様によれば、ハイサイド用のスイッチング素子と、前記ハイサイド用のスイッチング素子に直列に接続されたローサイド用のスイッチング素子と、前記ハイサイド用のスイッチング素子と前記ローサイド用のスイッチング素子とを制御するドライバ回路用の上述した半導体装置と、前記ハイサイド用のスイッチング素子と前記ローサイド用のスイッチング素子との間に、一端側が接続されたインダクタと、前記インダクタの他端側に接続されたコンデンサと、を備えたことを特徴とするDC−DCコンバータが提供される。

【発明の効果】

【0009】

本発明によれば、ソース領域とドレイン領域との間の単位面積あたりのオン抵抗をより低減させた半導体装置およびこの半導体装置を組み込んだDC−DCコンバータが実現する。

【図面の簡単な説明】

【0010】

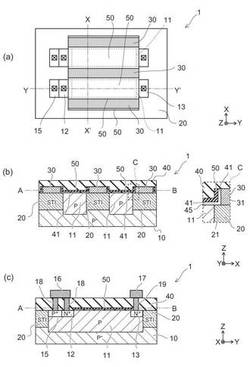

【図1】本実施の形態に係る半導体装置を示し、(a)は、(b)および(c)のA−Bの水平面で切断して上からみた半導体装置の要部横断面図、(b)は、(a)のX−X’断面図、(c)は、(a)のY−Y’断面図である。

【図2】半導体装置およびこれを用いたDC−DCの要部回路図を示し、(a)は、DC−DCコンバータの要部回路図、(b)は、半導体装置およびこれを制御する制御回路の要部回路図、(c)は、制御回路の要部回路である。

【図3】半導体装置の動作を説明するための図を示し、(a)は、本実施の形態に係る半導体装置のX−X’断面図、(b)は、比較例に係る半導体装置のX−X’断面図およびY−Y’断面図である。

【図4】CMOSおよび半導体装置の製造過程における要部断面図を示し、(α)は、CMOS中のスイッチング素子の製造過程における要部断面図、(β)は、半導体装置の製造過程におけるX−X’断面図、(γ)は、半導体装置の製造過程におけるY−Y’断面図であり、(a)は、素子分離層の形成工程図、(b)は、ベース層の形成工程図、(c)は、ゲート酸化膜、ゲート電極およびLDD(Lightly Doped Drain)領域の形成工程図である。

【図5】CMOSおよび半導体装置の製造過程における要部断面図を示し、(α)は、CMOS中のスイッチング素子の製造過程における要部断面図、(β)は、半導体装置の製造過程におけるX−X’断面図、(γ)は、半導体装置の製造過程におけるY−Y’断面図であり、(a)および(b)は、側壁保護膜の形成工程図である。

【図6】CMOSおよび半導体装置の製造過程における要部断面図を示し、(α)は、CMOS中のスイッチング素子の製造過程における要部断面図、(β)は、半導体装置の製造過程におけるX−X’断面図、(γ)は、半導体装置の製造過程におけるY−Y’断面図であり、(a)は、側壁保護膜の形成工程図、(b)は、ソース領域およびドレイン領域の形成工程図である。

【図7】本実施の形態の第1および第2の変形例の半導体装置を示し、(a)は、第1の変形例の半導体装置の要部断面図、(b)は、第2の変形例の半導体装置の要部断面図である。

【図8】本実施の形態の第3および第4の変形例の半導体装置を示し、(a)は、第3の変形例の半導体装置の要部断面図、(b)は、第4変形例の半導体装置の要部断面図である。

【図9】本実施の形態の第5の変形例の半導体装置を示し、(a)は、(b)のA−Bの水平面で切断して上からみた第5の変形例の半導体装置の要部横断面図、(b)は、(a)のY−Y’断面図である。

【図10】本実施の形態の第6の変形例の半導体装置を示し、(a)は、(b)のA−Bの水平面で切断して上からみた第6の変形例の半導体装置の要部横断面図、(b)は、(a)のY−Y’断面図である。

【図11】本実施の形態の第7の変形例の半導体装置を示し、(a)は、(b)および(c)のA−Bの水平面で切断して上からみた第7の変形例の半導体装置の要部横断面図、(b)は、(a)のX−X’断面図、(c)は、(a)のY−Y’断面図である。

【図12】本実施の形態の第8の変形例の半導体装置を示し、(a)は、(b)のA−Bの水平面で切断して上からみた第8の変形例の半導体装置の要部横断面図、(b)は、(a)のY−Y’断面図である。

【発明を実施するための形態】

【0011】

以下、本発明に係る半導体装置の実施の形態について、図面を参照して説明する。

図1は、本実施の形態に係る半導体装置を示し、(a)は、(b)および(c)のA−Bの水平面で切断して上からみた半導体装置の要部横断面図であり、(b)は、(a)のX−X’断面図であり、(c)は、(a)のY−Y’断面図である。ただし、図1(a)からは、図1(b)および図1(c)に示す層間絶縁膜40が取り除かれている。

【0012】

半導体装置1は、例えば、ケイ素(Si)等を主たる成分としている。半導体装置1は、第2導電型としてのP−型の半導体層10と、このP−型の半導体層10上に選択的に形成されたP型のベース層11と、ベース層11内に選択的に設けられた素子分離層20(以下、STI20)と、を備える。また、ベース層11上には、第1導電型としてのN+型のソース領域12が選択的に設けられ、このソース領域12から離間して、ベース層11上には、N+型のドレイン領域13が選択的に設けられている。ベース層11上では、P+型のコンタクト領域15がソース領域12に隣接している。半導体装置1は、Nチャネル型のMOSである。なお、ベース層11については、第2の導電型のウェル層と称する場合もある。

【0013】

素子分離層であるSTI20は、絶縁体であり、例えば、酸化ケイ素(SiO2)を主たる成分としている。STI20は、ベース層11内に設けられている。STI20は、ソース領域12からドレイン領域13の方向(図中のY方向)にストライプ状に延在している。また、STI20は、STI20が延在する方向とは略垂直な方向(図中のX方向)に周期的に配列されている。これにより、隣接するSTI20間のベース層11は、STI20と略平行に延在する。そして、制御電極としてのゲート電極30がSTI20の上側に設けられ、ソース領域12とドレイン領域13との間の電流経路を制御する。図1では、3本のゲート電極30を例示しているが、その数についてはこの数に限定されない。ゲート電極30の数に応じて、その両側にベース層11、ソース領域12、ドレイン領域13等が配置される。

【0014】

また、図1(b)の右横には、図1(b)のC部分が示されている。ゲート電極30の側壁31は、STI20の側壁21と面一ではなく、STI20の内側に位置している。さらに、半導体装置1では、隣接するゲート電極30間のベース層11の上側の少なくとも一部に高誘電体層50が設けられている。図1では、ベース層11の上側の全面に高誘電体層50が設けられた状態が示されている。

【0015】

例えば、ベース層11の上側の全面に高誘電体層50が設けられた場合、高誘電体層50は、ベース層11の上側に設けられたほか、ゲート電極30の側壁31にまで延在している。すなわち、高誘電体層50は、ゲート電極30の側壁31と、STI20間のベース層11に近接するように配置されている。なお、高誘電体層50は、図中のY方向に延在している。また、高誘電体層50とベース層11との間には、酸化膜41、酸化膜45が形成されている。高誘電体層50とゲート電極30との間には、酸化膜41が形成されている。そして、半導体装置1では、ビア間や配線間(図示しない)の絶縁を保つために、層間絶縁膜40がベース層11の上側およびゲート電極30の上側に設けられている。

【0016】

層間絶縁膜40、酸化膜41および酸化膜45の材質は、例えば、酸化ケイ素(SiO2)である。これにより、ゲート電極30とベース層11との間には、STI20、酸化膜41、酸化膜45および層間絶縁膜40が存在することになり、ゲート電極30とベース層11との間には、厚い酸化膜が介在する。この厚い酸化膜を、半導体装置1のゲート酸化膜とすると、半導体装置1は、高耐圧のゲート酸化膜を備える。なお、酸化ケイ素(SiO2)の比誘電率は、例えば、3.9程度である。

【0017】

また、高誘電体層50の材質としては、後述する容量結合を促進させるために、STI20、層間絶縁膜40もしくは酸化膜41の比誘電率よりも高い材質が選択される。例えば、高誘電体層50の材質としては、窒化ケイ素(Si3N4)が該当する。窒化ケイ素(Si3N4)の比誘電率は、7.5程度である。このほか、高誘電体層50の材質としては、酸化ハフニウム(HfO2)等を用いてもよい。このような比誘電率が高い高誘電体層50が配置されることにより、半導体装置1のオン状態では、高誘電体層50による容量結合が促進されて、ゲート電極30に面したベース層11の表面の一部または側壁の一部に高濃度の電荷が誘起される。この現象については、半導体装置1の動作を説明する際に、再度詳細に説明する。

【0018】

また、上述したドレイン領域13、ソース領域12およびコンタクト領域15は、ベース層11の長手方向の端部に選択的に設けられている。そして、第1の主電極としてのソース電極16は、ビア18を介してソース領域12およびコンタクト領域15に電気的に接続されている。第2の主電極としてのドレイン電極17は、ビア19を介してドレイン領域13に電気的に接続されている。また、複数のゲート電極30は、共通のゲート配線(図示しない)に接続されている。複数のソース電極16は、並列状に接続されている(図示しない)。複数のドレイン電極17は、並列状に接続されている(図示しない)。これにより、それぞれのベース層11内に流れる電流が合流して、半導体装置1に大電流を通電させることができる。このように、半導体装置1は、パワーMOSとして機能する。また、半導体装置1のオン・オフは、例えば、半導体装置1と同じ基板上に形成された微細なCMOS(Complementary Metal Oxide Semiconductor)により制御される。

【0019】

次に、半導体装置1をドライバ回路とするDC−DCコンバータと、半導体装置1を駆動する制御回路について説明する。

図2は、半導体装置およびこれを用いたDC−DCコンバータの要部回路図を示し、(a)は、DC−DCコンバータの要部回路図であり、(b)は、半導体装置およびこれを制御する制御回路の要部回路図であり、(c)は、制御回路の要部回路である。

【0020】

図2(a)に示すDC−DCコンバータ200は、降圧型のDC−DCコンバータであり、ドライバ回路300と、ハイサイド用のスイッチング素子102と、ローサイド用のスイッチング素子103と、インダクタ104と、コンデンサ105と、を備えている。ドライバ回路300は、ハイサイド用のスイッチング素子102と、ローサイド用のスイッチング素子103とのオン、オフを制御する。

【0021】

スイッチング素子102とスイッチング素子103とは直列に接続されている。スイッチング素子102のドレイン102dとスイッチング素子103のドレイン103dとの間の接続点(ノード)106には、例えば、コイル等のインダクタ104の一端側が接続している。インダクタ104の他端側には、コンデンサ105を介して基準電位(例えば、接地電位GND)が供給される。スイッチング素子103のソース103sは、基準電位(GND)に接続され、ソース103sにも基準電位が供給される。また、インダクタ104の他端側は、出力端子107に接続している。そして、スイッチング素子102のソース102sと、基準電位(GND)との間に設けられた電源110により、スイッチング素子102のソース102sには、入力電圧Vinが入力され、出力端子107からは入力電圧Vinが変換された出力電圧Voutが出力される。

【0022】

図2(b)に示すように、ドライバ回路300には、半導体装置1が組み込まれている。例えば、スイッチング素子である半導体装置1には、Pチャネル型のスイッチング素子109が直列に接続されている。半導体装置1のドレイン電極17とスイッチング素子109のドレイン電極109dとの間の接続点108は、スイッチング素子102、103のゲート電極30に接続されている。

【0023】

さらに、図2(c)に示すように、半導体装置1のゲート電極30は、制御回路であるCMOS60に接続されている。CMOS60からの制御信号により、半導体装置1のオン・オフが制御される。

【0024】

CMOS60は、Pチャネル型のMOSで構成されるスイッチング素子60pと、Nチャネル型のMOSで構成されるスイッチング素子60nとから構成される。CMOS60は、さらにCMOS60とは別の制御回路70、71により制御されている。半導体装置1を含むドライバ回路300とCMOS60とは、同じ半導体層10上に設けられている。なお、半導体装置1については、後述する半導体装置2〜7に置き換えることができる。また、このようなドライバ回路300およびCMOS60は、DC−DCコンバータのほか、例えば、モータドライバ回路等にも組み込むことができる(図示しない)。

【0025】

次に、半導体装置1の作用効果について説明する。

図3は、半導体装置の動作を説明するための図を示し、(a)は、本実施の形態に係る半導体装置のX−X’断面図、(b)は、比較例に係る半導体装置のX−X’断面図およびY−Y’断面図である。半導体装置1と半導体装置100とは、半導体装置100に、上述した高誘電体層50が設けられていない点で異なっている。なお、図3の向きは、図1(b)の向きに対応している。

【0026】

最初に、半導体装置100により、半導体装置の動作について説明する。

まず、ゲート電極30とソース電極16との間に、閾値電圧以下の電圧を印加し、ソース電極16とドレイン電極17との間に所定の電圧を印加する。この際、ゲート電極30とドレイン電極17との間にも電圧が印加され、STI20とベース層11との界面からも空乏層が伸び、空乏層が電界を緩和することにより半導体装置100は、高耐圧を維持する。

そして、半導体装置100のゲート電極30に閾値電圧より大きい正バイアスを印加し、ゲート電極30に面したベース層11の表面82の一部または側壁83の一部に反転層81を生じさせることで半導体装置100をオンさせる。これにより、ソース電極16とドレイン電極17との間に電流が流れる。

【0027】

この場合、半導体装置100においては、反転層81がベース層11の表面82もしくは側壁83に沿って主に形成される。上述した非特許文献1によれば、ソース領域12とドレイン領域13の間に流れる電流分布は、ベース層11の表面82の反転層81で58%であり、ベース層11の側壁83の反転層81で39%であるとされている。すなわち、半導体装置100においては、ベース層11の表面82に流れる電流とベース層11の側壁83に流れる電流が主に通電に寄与する。

【0028】

半導体装置1についても同様にオンさせると、反転層80がベース層11の表面82もしくは側壁83に沿って主に形成して、ソース領域12とドレイン領域13との間が通電する。ただし、半導体装置1では、ベース層11の上側に高誘電体層50が配置されたために、反転層80内に誘起される電荷密度は、半導体装置100に比べ大きくなる。これは、半導体装置1では、高誘電体層50の配置により容量結合がより促進され、ベース層11の表面82もしくは側壁83で電荷が著しく誘起されるためである。例えば、図3では、反転層80、81内に生成する電荷密度の大小を濃淡で表し、濃淡が濃いほど、電荷密度が大きいことを表示している。

この高誘電体層50は、ゲート電極30の側壁31側にも形成されているので、反転層80内の電荷密度は、ゲート電極30の近傍ほど高くなる。

【0029】

ここで、高誘電体層50の材質を窒化ケイ素(Si3N4)とすると、高誘電体層50の比誘電率は、STI20の材質である酸化ケイ素(SiO2)に比べおよそ2倍程度になっている。従って、高誘電体層50がゲート電極30とベース層11との間に介在する場合は、ベース層11の反転層80内に誘起される電荷密度は増加する。その結果、半導体装置1のソース領域12とドレイン領域13との間のオン抵抗(以下、単にオン抵抗と称する)は、半導体装置100のオン抵抗に比べ低減する。

【0030】

また、高誘電体層50については、ベース層11の上側の少なくとも一部に配置されている場合でも容量結合を促進させることができるので、半導体装置1では、ベース層11の上側の少なくとも一部に高誘電体層50が設けられていればよい。特に、電界の強さはゲート電極30からの距離に反比例することから、ゲート電極30の近傍に発生する電荷が主にオン抵抗の低減に寄与する。従って、高誘電体層50は、ゲート電極30の近傍に存在することが望ましい。

【0031】

なお、比較例の半導体装置100では、高誘電体層50が設けられていない。従って、半導体装置100をオンさせると、電界がゲート電極30の端部において局部的に集中し易い。その結果、反転層81内の電荷密度が半導体装置1に比べて小さくなり、単位面積あたりのオン抵抗が半導体装置1よりも大きくなる。この半導体装置100で、所望のオン抵抗を得るには、チャネル幅を広くする方法もあるが、この方法では、素子サイズの増大を招いてしまう。従って、半導体装置1のように、高誘電体層50が設けられた構造が好ましい。

【0032】

次に、半導体装置1の製造方法について説明する。

図4〜図6は、半導体装置の製造過程を説明する要部断面図である。図4〜図6中の(α)には、制御回路として組み込まれるCMOSの中、一例として、Nチャネル型のスイッチング素子60nの製造工程についても併せて表示されている。半導体装置1の製造工程については、上述したX−X’断面が(β)に、Y−Y’断面が(γ)に示されている。

【0033】

まず、図4は、CMOSおよび半導体装置の製造過程における要部断面図であり、(α)は、CMOS中のスイッチング素子の製造過程における要部断面図であり、(β)は、半導体装置の製造過程におけるX−X’断面図であり、(γ)は、半導体装置の製造過程におけるY−Y’断面図である。さらに、(a)は、素子分離層の形成工程図であり、(b)は、ベース層の形成工程図であり、(c)は、ゲート酸化膜、ゲート電極およびLDD(Lightly Doped Drain)領域の形成工程図である。

【0034】

図4(a)に示すように、P−型の半導体層10内に、埋め込み法によりSTI20を形成する。次いで、半導体層10上およびSTI20上に、イオンプレーティング注入で使用されるバッファ酸化膜47を形成する。バッファ酸化膜47は、熱酸化法、低圧CVD法によって形成する。バッファ酸化膜47の材質としては、酸化ケイ素(SiO2)等が選択される。次に、図4(b)に示すように、隣接するSTI20間にウェル状のベース層11を形成する。その後、バッファ酸化膜47を除去し、スイッチング素子60nのゲート酸化膜となる酸化膜45を形成する。酸化膜45は、熱酸化法、低圧CVD法等により形成する。酸化膜45の材質としては、酸化ケイ素(SiO2)、酸窒化ケイ素(SiON)、窒化ケイ素(Si3N4)、酸化タンタル(Ta2O5)等が選択される。

【0035】

次に、図4(c)に示すように、酸化膜45を介して、柱状のゲート電極30、65を形成する。ゲート電極30、65のパターニングは、光リソグラフィ法、X線リソグラフィ法、電子ビームリソグラフィ法、反応性イオンエッチング(RIE)法等により行われる。ゲート電極30、65の材質は、例えば、ポリシリコン、タングステン(W)である。ゲート電極30、65の材質がタングステン(W)の場合は、窒化チタン(TiN)、窒化タングステン(WN)のバリア層を設けてもよい。なお、CMOSのNチャネル型のスイッチング素子60nの形成領域(α)には、イオン注入法によりベース層11に選択的にN−領域(Lightly Doped Drain領域)61を形成する。

【0036】

次に、図5は、CMOSおよび半導体装置の製造過程における要部断面図を示し、(α)は、CMOS中のスイッチング素子の製造過程における要部断面図、(β)は、半導体装置の製造過程におけるX−X’断面図、(γ)は、半導体装置の製造過程におけるY−Y’断面図であり、(a)および(b)は、側壁保護膜の形成工程図である。

図5(a)に示すように、酸化膜45およびゲート電極30、65の周辺に、低圧CVD法により、酸化ケイ素(SiO2)等の酸化膜41、窒化ケイ素(Si3N4)等の窒化膜50aを順に形成する。次に、図5(b)に示すように、半導体装置1の形成領域(β)、(γ)に、レジスト62をパターニングする。例えば、光リソグラフィ法等により、半導体装置1の形成領域のベース層11に選択的にレジスト62を形成する。この際、ゲート電極30側壁近傍の酸化膜41、窒化膜50aは表出させる。また、半導体装置1のソース領域12、ドレイン領域13およびコンタクト領域15を形成する領域は表出させる。

【0037】

次に、図6は、CMOSおよび半導体装置の製造過程における要部断面図を示し、(α)は、CMOS中のスイッチング素子の製造過程における要部断面図、(β)は、半導体装置の製造過程におけるX−X’断面図、(γ)は、半導体装置の製造過程におけるY−Y’断面図であり、(a)は、側壁保護膜の形成工程図、(b)は、ソース領域およびドレイン領域の形成工程図である。図6(a)に示すように、異方性のエッチング(例えば、RIE等)を酸化膜41、窒化膜50aに施す。続いて、上述したレジスト62を除去する。これにより、ゲート電極65の側壁には、この側壁がマスクとなって酸化膜41、窒化膜50aが残り、これらの酸化膜、窒化膜を含む側壁保護膜66が形成される。一方、半導体装置1の形成領域(β)、(γ)においては、STI20間のベース層11上の窒化膜50aが残されて、上述した高誘電体層50が形成される。

【0038】

次に、CMOSのNチャネル型のスイッチング素子60nの形成領域(α)においては、N−領域61に隣接するように、N+型のソース領域63およびドレイン領域64をイオン注入法により形成する。また、半導体装置1の形成領域(β)、(γ)においては、ソース領域12、ドレイン領域13およびコンタクト領域15をイオン注入法により形成する。この状態を、図6(b)に示す。そして、この後においては、それぞれの素子に関し、ソース領域12、63、ドレイン領域13、64およびコンタクト領域15上の酸化膜45を取り除き、ソース電極をソース領域に接続させ、ドレイン電極をドレイン領域に接続させる(図示しない)。このような方法によって、半導体装置1並びにCMOSが形成される。

【0039】

この製造工程では、CMOSと半導体装置1とが並行して形成される。従って、高誘電体層50に関しては、側壁保護膜66と同時に形成することができる。これにより、高誘電体層50のみを専用に形成するという工程は要さない。従って、CMOSがノード65nm程度の微細構造を有する場合、CMOS形成プロセスに半導体装置1を混載しても、大きなプロセス変更を伴なわない。その結果、CMOS側の熱履歴を変更することなく、半導体装置1を製造することができる。

【0040】

次に、本実施の形態に係る半導体装置の変形例について説明する。以下の説明では、同じ部材には同じ符号を付し、詳細な説明を適宜省略する。

図7は、本実施の形態の第1および第2の変形例の半導体装置を示し、(a)は、第1の変形例の半導体装置の要部断面図、(b)は、第2の変形例の半導体装置の要部断面図である。図7には、ベース層11が延在する方向とは、略垂直に切断した半導体装置2の要部断面が示されている。また、図7(a)の右横には、図7(a)のD部分が示されている。

【0041】

図7(a)に示す第1の変形例である半導体装置2Aでは、STI20内の少なくとも一部に高誘電体層51が設けられている。

例えば、図7(a)には、STI20の側壁21および底面22に沿うように、高誘電体層51が設けられた状態が示されている。高誘電体層51とベース層11との間には、酸化膜23が介在している。酸化膜23の材質は、STI20の材質と同じである。また、高誘電体層51の材質は、上述した高誘電体層50の材質と同じである。高誘電体層51は、ベース層11に近接し、STI20の側壁21および底面22に沿って、図中のY方向に延在している。

【0042】

このような構造の半導体装置2Aをオンさせると、反転層80がベース層11の表面82もしくは側壁83に沿って主に形成される。特に、半導体装置2Aでは、STI20の側壁21および底面22に沿うように、高誘電体層51が配置されたために、ベース層11の側壁83において著しく電荷が誘起される。従って、半導体装置2Aの単位面積あたりのオン抵抗は、半導体装置100より低減する。

【0043】

また、図7(b)に、第2の変形例である半導体装置2Bを示す。

半導体装置2Bにおいては、高誘電体層51がSTI20の側壁21のみに沿うように配置されている。このような場合でも、上述した容量結合が促進されて、電荷密度の高い反転層80を形成することができる。すなわち、高誘電体層51は、STI20内の少なくとも一部に設けられていればよい。

【0044】

特に、STI20は、隣接する素子の分離層である必要がある。従って、STI20の底面22に面するベース層11に反転層を誘起しすぎると、隣接する素子同士が反転層を通して電気的に接続される場合がある。この場合、STI20は、隣接する素子を電気的に分離をすることができなくなる。従って、半導体装置2Bでは、高誘電体層51を側壁21のみに沿って形成し、隣接する素子同士の分離を確実なものにしている。さらに、半導体装置2Bの単位面積あたりのオン抵抗は半導体装置100よりも低減する。

【0045】

図8は、本実施の形態の第3および第4の変形例の半導体装置を示し、(a)は、第3の変形例の半導体装置の要部断面図、(b)は、第4変形例の半導体装置の要部断面図である。図8には、ベース層11が延在する方向とは、略垂直に切断した半導体装置3の要部断面が示されている。

【0046】

図8(a)に示す第3の変形例である半導体装置3Aでは、ベース層11の上側の少なくとも一部に高誘電体層50が設けられ、さらに、STI20内の少なくとも一部に高誘電体層51が設けられている。

【0047】

このような構造の半導体装置3Aをオンさせると、ベース層11の表面82もしくは側壁83に沿って主に反転層80が形成される。半導体装置3Aでは、ベース層11の上側に高誘電体層50が配置されたほか、STI20の側壁21および底面22に沿うように、高誘電体層51が配置されたために、半導体装置1、2A、2Bよりもベース層11の表面82および側壁83で電荷が著しく誘起される。従って、半導体装置3Aの単位面積あたりのオン抵抗は、半導体装置1、2A、2Bより低減する。

【0048】

また、図8(b)に、第4の変形例である半導体装置3Bを示す。

高誘電体層51については、STI20内の少なくとも一部に配置されている場合でも、上述した容量結合を促進させることができる。従って、半導体装置3Bでは、高誘電体層51をSTI20の側壁21のみに沿って配置している。その結果、隣接する素子同士を確実に電気的に分離させることができる。さらに、半導体装置3Bの単位面積あたりのオン抵抗は、半導体装置1、2A、2Bより低減する。

【0049】

図9は、本実施の形態の第5の変形例の半導体装置を示し、(a)は、(b)のA−Bの水平面で切断して上からみた第5の変形例の半導体装置の要部横断面図、(b)は、(a)のY−Y’断面図である。ただし、図9(a)からは、層間絶縁膜40が取り除かれている。

【0050】

第5の変形例である半導体装置4では、高誘電体層50が設けられたほか、ベース層11とドレイン領域13との間に、N型のドリフト層14が設けられている。高誘電体層50は、ドリフト層14上およびドリフト層14とゲート電極30との間に設けられている。そして、ドリフト層14に並列して設けられたゲート電極30bの幅を、ベース層11に並列して設けられたゲート電極30aの幅よりも細くしている。ゲート電極30の幅とは、X方向にゲート電極30を切断した場合の幅をいう。

【0051】

半導体装置4の動作について説明する。

まず、ゲート電極30に印加する電圧を閾値以下の電圧にする。ソース領域12とドレイン領域13との間には、所定の電圧を印加する。この場合、ドリフト層14には、ベース層11とドリフト層14との界面から空乏層が伸びる。この際、ベース層11の表面82もしくは側壁83には反転層は形成されない。

【0052】

ここで、ドリフト層14においては、トランジスタの通電経路となるために低抵抗であることが望ましい。これを実現するために、ドリフト層14の不純物濃度を単純に高くする方法がある。しかし、単純にドリフト層14の不純物濃度を高くすると、空乏層がドリフト層14内で伸び難くなり、高耐圧を維持できなくなる場合がある。

【0053】

そこで、ゲート電極30bをドリフト層14に並列に配置する。ゲート電極30bとドリフト層14との間にも電界が印加されるため、ドリフト層14には、ドリフト層14とSTI20との界面からも空乏層が伸びる。これらの空乏層が重なって、半導体装置4においては、空乏層がドリフト層14内で満遍なく伸び得る。その結果、ドレイン領域13とソース領域12との間の電界の強さを緩和しやすくなり、ドリフト層14の不純物濃度を高くすることができる。このように、ドレイン領域13とソース領域12との間の耐圧を維持しながら、オン抵抗を低減することができる。

【0054】

半導体装置4では、ドリフト層14の不純物濃度を高くしつつ、ドリフト層14に並列して配置されるゲート電極30bの幅をゲート電極30aよりも細くしている。このような構造であれば、ドリフト層14の不純物濃度を高くしても、ゲート電極30bとドリフト層14との間に、所定の電圧が印加されるので、空乏化がドリフト層14内で伸び易くなる。

【0055】

また、半導体装置4では、ゲート電極30bの幅をゲート電極30aよりも細くしているので、ゲート電極30bとドリフト層14との間の距離が離れ、ゲート電極30bとドリフト層14との間の電界の強さを調節することができる。これにより、ゲート電極30とドリフト層14との間でアバランシェ降伏が起きにくく、半導体装置4は高耐圧を維持する。

【0056】

そして、ゲート電極30に印加する電圧を閾値以上の電圧にすると、ベース層11の表面82もしくは側壁83には、上述した反転層80が形成される。これにより、ソース領域12とドレイン領域13との間に電流が流れる。さらに、半導体装置4では、ドリフト層14がN型であるために、ドリフト層14の表面84もしくは側壁85には蓄積層が形成される。蓄積層が形成されると、ドリフト層14内において、より自由キャリアが増加する。従って、半導体装置4のオン抵抗は、半導体装置1〜3よりもさらに低減する。

【0057】

図10は、本実施の形態の第6の変形例の半導体装置を示し、(a)は、(b)のA−Bの水平面で切断して上からみた第6の変形例の半導体装置の要部横断面図、(b)は、(a)のY−Y’断面図である。ただし、図10(a)からは、層間絶縁膜40が取り除かれている。

【0058】

第6の変形例である半導体装置5では、ベース層11の上側に高誘電体層50が配置されている。ただし、ドリフト層14上およびドリフト層14とゲート電極30bとの間には、高誘電体層50が設けられていない。

このような構造であれば、ゲート電極30とドレイン領域13との間の容量の中、ドリフト層14に並列するゲート電極30bとドレイン領域13との間の容量分がより小さくなる。このため、ゲート電極30とドレイン領域13との間の容量が低減する。従って半導体装置5では、半導体装置4よりもミラー容量を下げることができ、より高速のスイッチング動作が実現する。

【0059】

図11は、本実施の形態の第7の変形例の半導体装置を示し、(a)は、(b)および(c)のA−Bの水平面で切断して上からみた第7の変形例の半導体装置の要部横断面図、(b)は、(a)のX−X’断面図、(c)は、(a)のY−Y’断面図である。ただし、図11(a)からは、層間絶縁膜40が取り除かれている。

【0060】

第7の変形例である半導体装置6では、ベース層11の上側に高誘電体層50が配置されている。ただし、ドリフト層14上には、高誘電体層50が設けられていない。また、半導体装置6では、高誘電体層50のほか、STI20内の少なくとも一部に高誘電体層51が設けられている。

このような構造であれば、半導体装置6のゲート電極30とドレイン領域13との間の容量の中、ドリフト層14に並列するゲート電極30bとドレイン領域13との間の容量分がより小さくなる。このため、半導体装置6では、半導体装置4よりも高速のスイッチング動作が実現する。また、半導体装置6では、STI20内の少なくとも一部に高誘電体層51が設けられているので、反転層80内の電荷密度が高まり、半導体装置5よりもオン抵抗を低減させることができる。

【0061】

図12は、本実施の形態の第8の変形例の半導体装置を示し、(a)は、(b)のA−Bの水平面で切断して上からみた第8の変形例の半導体装置の要部横断面図、(b)は、(a)のY−Y’断面図である。ただし、図12(a)からは、層間絶縁膜40が取り除かれている。

【0062】

第8の変形例である半導体装置7では、高誘電体層50が設けられたほか、ゲート電極30bの部分をゲート電極30aから分離させた構造を有する。ゲート電極30aから電気的に独立した部分を、電極32としている。電極32は、ドリフト層14に並列に配置されている。そして、ゲート電極30aは、共通のライン90で接続されている。電極32は、共通のライン91を通じてソース電極16に接続され、ソース領域12に電気的に接続されている。また、ドレイン領域13は、ドレイン電極17を通じ、共通のライン92で接続されている。

【0063】

この半導体装置7では、ソース電極16とドレイン電極17との間に所定の電圧を印加しても、ゲート電極30aの電圧が閾値以下ならば、ソース電極16とドレイン電極17との間は通電しない。ゲート電極30aの電圧が閾値以上になると、ソース電極16とドレイン電極17との間は通電する。しかし、電極32がソース電極16に導通しているために、ドリフト層14に蓄積層は形成され難い。

【0064】

しかしながら、ゲート電極とドレイン電極17との間の容量は、ゲート電極30aとドレイン電極17との間の容量のみになり、半導体装置4〜6よりもさらに容量が低減する。このため、半導体装置7では、半導体装置4〜6よりもよりミラー容量を下げることができ、より高速のスイッチング動作が実現する。

【0065】

以上、具体例を参照しつつ本発明の実施の形態について説明した。しかし、本発明はこれらの具体例に限定されるものではない。すなわち、これら具体例に、当業者が適宜設計変更を加えたものも、本発明の特徴を備えている限り、本発明の範囲に包含される。例えば、前述した各具体例が備える各要素およびその配置、材料、条件、形状、サイズなどは、例示したものに限定されるわけではなく適宜変更することができる。

【0066】

また、本実施の形態では、第1導電型をN型とし、第2導電型をP型とした場合について説明したが、第1導電型をP型とし、第2導電型をN型とする構造についても実施の形態に含まれ、同様の効果を得る。その他、本発明はその要旨を逸脱しない範囲で種々変形して実施できる。

【0067】

また、前述した各実施の形態が備える各要素は、技術的に可能な限りにおいて複合させることができ、これらを組み合わせたものも本発明の特徴を含む限り本発明の範囲に包含される。

その他、本発明の思想の範疇において、当業者であれば、各種の変更例及び修正例に想到し得るものであり、それら変更例及び修正例についても本発明の範囲に属するものと了解される。

【符号の説明】

【0068】

1、2A、2B、3A、3B、4、5、6、7、100 半導体装置

10 半導体層

11 ベース層

12 ソース領域

13 ドレイン領域

14 ドリフト層

16 ソース電極

17 ドレイン電極

18、19 ビア

20 STI(素子分離層)

30、30a、30b ゲート電極

50、51 高誘電体層

60 CMOS

60n、60p スイッチング素子

70、71 制御回路

102、103、109 スイッチング素子

104 インダクタ

105 コンデンサ

106 接続点(スイッチノード)

200 DC−DCコンバータ

300 ドライバ回路

【技術分野】

【0001】

本発明は、半導体装置およびDC−DCコンバータに関する。

【背景技術】

【0002】

近年、微細プロセスによるデバイスとパワーデバイスとを集積し、複雑なシステムとパワーデバイスとを集積化する流れがある。パワーデバイスと組み合わせる場合でも、微細プロセスの条件を大きく変更しないことが求められる。例えば、熱工程等は、微細なCMOSデバイスの特性に影響を与えるため、なるべく変更しないことが望ましい。特に、最近の微細プロセスでは、PN接合を基板表面から浅く形成する都合上、熱履歴は少ないほどよい。

【0003】

最近、上述した微細プロセスにおいて、プロセスを追加せずに、厚いゲート酸化膜を形成する技術が報告されている(例えば、非特許文献1参照)。

そのデバイス構造は、素子分離層であるSTI(Shallow Trench Isolation)がストライプ状に形成され、そのSTI上にゲート電極が配置されるというものである。すなわち、半導体層上にはゲートを配置されない構造である。

【0004】

STI上に配置されたゲート電極と、STIとSTIとの間のPウェル領域と、が平面的に距離をもつことで、ゲート電極とPウェル領域との間に厚いゲート酸化膜が形成される。これにより、耐圧が高いゲート酸化膜が設けられる。しかしながら、パワーデバイスの単位面積あたりのオン抵抗の低減については、未だ改善されていないのが実情である。

【先行技術文献】

【非特許文献】

【0005】

【非特許文献1】J.Sonsky,G.Doornnbos,A.Heringa,M.van Duuren,J.Perez-Gonzalez,“Towards universal and voltage-scalable high gate and drain-voltage MOSFETs in CMOS",Proceedings of ISPSD 2009 IEEE,P.315-318

【発明の概要】

【発明が解決しようとする課題】

【0006】

本発明の目的は、ソース領域とドレイン領域との間の単位面積あたりのオン抵抗をより低減させた半導体装置およびこの半導体装置を組み込んだDC−DCコンバータを提供することにある。

【課題を解決するための手段】

【0007】

本発明の一態様によれば、第1導電型のソース領域と第1導電型のドレイン領域とが表面に選択的に形成された第2導電型のベース層と、前記ベース層内に設けられ、前記ソース領域から前記ドレイン領域の方向に延在する素子分離層と、前記素子分離層の上側に設けられ、前記ソース領域と前記ドレイン領域との間の電流経路を制御する制御電極と、前記ベース層の上側の少なくとも一部または前記素子分離層内の少なくとも一部に配置され、前記素子分離層の比誘電率よりも高い比誘電率を有する高誘電体層と、前記ソース領域に接続された第1の主電極と、前記ドレイン領域に接続された第2の主電極と、を備えたことを特徴とする半導体装置が提供される。

【0008】

また、本発明の一態様によれば、ハイサイド用のスイッチング素子と、前記ハイサイド用のスイッチング素子に直列に接続されたローサイド用のスイッチング素子と、前記ハイサイド用のスイッチング素子と前記ローサイド用のスイッチング素子とを制御するドライバ回路用の上述した半導体装置と、前記ハイサイド用のスイッチング素子と前記ローサイド用のスイッチング素子との間に、一端側が接続されたインダクタと、前記インダクタの他端側に接続されたコンデンサと、を備えたことを特徴とするDC−DCコンバータが提供される。

【発明の効果】

【0009】

本発明によれば、ソース領域とドレイン領域との間の単位面積あたりのオン抵抗をより低減させた半導体装置およびこの半導体装置を組み込んだDC−DCコンバータが実現する。

【図面の簡単な説明】

【0010】

【図1】本実施の形態に係る半導体装置を示し、(a)は、(b)および(c)のA−Bの水平面で切断して上からみた半導体装置の要部横断面図、(b)は、(a)のX−X’断面図、(c)は、(a)のY−Y’断面図である。

【図2】半導体装置およびこれを用いたDC−DCの要部回路図を示し、(a)は、DC−DCコンバータの要部回路図、(b)は、半導体装置およびこれを制御する制御回路の要部回路図、(c)は、制御回路の要部回路である。

【図3】半導体装置の動作を説明するための図を示し、(a)は、本実施の形態に係る半導体装置のX−X’断面図、(b)は、比較例に係る半導体装置のX−X’断面図およびY−Y’断面図である。

【図4】CMOSおよび半導体装置の製造過程における要部断面図を示し、(α)は、CMOS中のスイッチング素子の製造過程における要部断面図、(β)は、半導体装置の製造過程におけるX−X’断面図、(γ)は、半導体装置の製造過程におけるY−Y’断面図であり、(a)は、素子分離層の形成工程図、(b)は、ベース層の形成工程図、(c)は、ゲート酸化膜、ゲート電極およびLDD(Lightly Doped Drain)領域の形成工程図である。

【図5】CMOSおよび半導体装置の製造過程における要部断面図を示し、(α)は、CMOS中のスイッチング素子の製造過程における要部断面図、(β)は、半導体装置の製造過程におけるX−X’断面図、(γ)は、半導体装置の製造過程におけるY−Y’断面図であり、(a)および(b)は、側壁保護膜の形成工程図である。

【図6】CMOSおよび半導体装置の製造過程における要部断面図を示し、(α)は、CMOS中のスイッチング素子の製造過程における要部断面図、(β)は、半導体装置の製造過程におけるX−X’断面図、(γ)は、半導体装置の製造過程におけるY−Y’断面図であり、(a)は、側壁保護膜の形成工程図、(b)は、ソース領域およびドレイン領域の形成工程図である。

【図7】本実施の形態の第1および第2の変形例の半導体装置を示し、(a)は、第1の変形例の半導体装置の要部断面図、(b)は、第2の変形例の半導体装置の要部断面図である。

【図8】本実施の形態の第3および第4の変形例の半導体装置を示し、(a)は、第3の変形例の半導体装置の要部断面図、(b)は、第4変形例の半導体装置の要部断面図である。

【図9】本実施の形態の第5の変形例の半導体装置を示し、(a)は、(b)のA−Bの水平面で切断して上からみた第5の変形例の半導体装置の要部横断面図、(b)は、(a)のY−Y’断面図である。

【図10】本実施の形態の第6の変形例の半導体装置を示し、(a)は、(b)のA−Bの水平面で切断して上からみた第6の変形例の半導体装置の要部横断面図、(b)は、(a)のY−Y’断面図である。

【図11】本実施の形態の第7の変形例の半導体装置を示し、(a)は、(b)および(c)のA−Bの水平面で切断して上からみた第7の変形例の半導体装置の要部横断面図、(b)は、(a)のX−X’断面図、(c)は、(a)のY−Y’断面図である。

【図12】本実施の形態の第8の変形例の半導体装置を示し、(a)は、(b)のA−Bの水平面で切断して上からみた第8の変形例の半導体装置の要部横断面図、(b)は、(a)のY−Y’断面図である。

【発明を実施するための形態】

【0011】

以下、本発明に係る半導体装置の実施の形態について、図面を参照して説明する。

図1は、本実施の形態に係る半導体装置を示し、(a)は、(b)および(c)のA−Bの水平面で切断して上からみた半導体装置の要部横断面図であり、(b)は、(a)のX−X’断面図であり、(c)は、(a)のY−Y’断面図である。ただし、図1(a)からは、図1(b)および図1(c)に示す層間絶縁膜40が取り除かれている。

【0012】

半導体装置1は、例えば、ケイ素(Si)等を主たる成分としている。半導体装置1は、第2導電型としてのP−型の半導体層10と、このP−型の半導体層10上に選択的に形成されたP型のベース層11と、ベース層11内に選択的に設けられた素子分離層20(以下、STI20)と、を備える。また、ベース層11上には、第1導電型としてのN+型のソース領域12が選択的に設けられ、このソース領域12から離間して、ベース層11上には、N+型のドレイン領域13が選択的に設けられている。ベース層11上では、P+型のコンタクト領域15がソース領域12に隣接している。半導体装置1は、Nチャネル型のMOSである。なお、ベース層11については、第2の導電型のウェル層と称する場合もある。

【0013】

素子分離層であるSTI20は、絶縁体であり、例えば、酸化ケイ素(SiO2)を主たる成分としている。STI20は、ベース層11内に設けられている。STI20は、ソース領域12からドレイン領域13の方向(図中のY方向)にストライプ状に延在している。また、STI20は、STI20が延在する方向とは略垂直な方向(図中のX方向)に周期的に配列されている。これにより、隣接するSTI20間のベース層11は、STI20と略平行に延在する。そして、制御電極としてのゲート電極30がSTI20の上側に設けられ、ソース領域12とドレイン領域13との間の電流経路を制御する。図1では、3本のゲート電極30を例示しているが、その数についてはこの数に限定されない。ゲート電極30の数に応じて、その両側にベース層11、ソース領域12、ドレイン領域13等が配置される。

【0014】

また、図1(b)の右横には、図1(b)のC部分が示されている。ゲート電極30の側壁31は、STI20の側壁21と面一ではなく、STI20の内側に位置している。さらに、半導体装置1では、隣接するゲート電極30間のベース層11の上側の少なくとも一部に高誘電体層50が設けられている。図1では、ベース層11の上側の全面に高誘電体層50が設けられた状態が示されている。

【0015】

例えば、ベース層11の上側の全面に高誘電体層50が設けられた場合、高誘電体層50は、ベース層11の上側に設けられたほか、ゲート電極30の側壁31にまで延在している。すなわち、高誘電体層50は、ゲート電極30の側壁31と、STI20間のベース層11に近接するように配置されている。なお、高誘電体層50は、図中のY方向に延在している。また、高誘電体層50とベース層11との間には、酸化膜41、酸化膜45が形成されている。高誘電体層50とゲート電極30との間には、酸化膜41が形成されている。そして、半導体装置1では、ビア間や配線間(図示しない)の絶縁を保つために、層間絶縁膜40がベース層11の上側およびゲート電極30の上側に設けられている。

【0016】

層間絶縁膜40、酸化膜41および酸化膜45の材質は、例えば、酸化ケイ素(SiO2)である。これにより、ゲート電極30とベース層11との間には、STI20、酸化膜41、酸化膜45および層間絶縁膜40が存在することになり、ゲート電極30とベース層11との間には、厚い酸化膜が介在する。この厚い酸化膜を、半導体装置1のゲート酸化膜とすると、半導体装置1は、高耐圧のゲート酸化膜を備える。なお、酸化ケイ素(SiO2)の比誘電率は、例えば、3.9程度である。

【0017】

また、高誘電体層50の材質としては、後述する容量結合を促進させるために、STI20、層間絶縁膜40もしくは酸化膜41の比誘電率よりも高い材質が選択される。例えば、高誘電体層50の材質としては、窒化ケイ素(Si3N4)が該当する。窒化ケイ素(Si3N4)の比誘電率は、7.5程度である。このほか、高誘電体層50の材質としては、酸化ハフニウム(HfO2)等を用いてもよい。このような比誘電率が高い高誘電体層50が配置されることにより、半導体装置1のオン状態では、高誘電体層50による容量結合が促進されて、ゲート電極30に面したベース層11の表面の一部または側壁の一部に高濃度の電荷が誘起される。この現象については、半導体装置1の動作を説明する際に、再度詳細に説明する。

【0018】

また、上述したドレイン領域13、ソース領域12およびコンタクト領域15は、ベース層11の長手方向の端部に選択的に設けられている。そして、第1の主電極としてのソース電極16は、ビア18を介してソース領域12およびコンタクト領域15に電気的に接続されている。第2の主電極としてのドレイン電極17は、ビア19を介してドレイン領域13に電気的に接続されている。また、複数のゲート電極30は、共通のゲート配線(図示しない)に接続されている。複数のソース電極16は、並列状に接続されている(図示しない)。複数のドレイン電極17は、並列状に接続されている(図示しない)。これにより、それぞれのベース層11内に流れる電流が合流して、半導体装置1に大電流を通電させることができる。このように、半導体装置1は、パワーMOSとして機能する。また、半導体装置1のオン・オフは、例えば、半導体装置1と同じ基板上に形成された微細なCMOS(Complementary Metal Oxide Semiconductor)により制御される。

【0019】

次に、半導体装置1をドライバ回路とするDC−DCコンバータと、半導体装置1を駆動する制御回路について説明する。

図2は、半導体装置およびこれを用いたDC−DCコンバータの要部回路図を示し、(a)は、DC−DCコンバータの要部回路図であり、(b)は、半導体装置およびこれを制御する制御回路の要部回路図であり、(c)は、制御回路の要部回路である。

【0020】

図2(a)に示すDC−DCコンバータ200は、降圧型のDC−DCコンバータであり、ドライバ回路300と、ハイサイド用のスイッチング素子102と、ローサイド用のスイッチング素子103と、インダクタ104と、コンデンサ105と、を備えている。ドライバ回路300は、ハイサイド用のスイッチング素子102と、ローサイド用のスイッチング素子103とのオン、オフを制御する。

【0021】

スイッチング素子102とスイッチング素子103とは直列に接続されている。スイッチング素子102のドレイン102dとスイッチング素子103のドレイン103dとの間の接続点(ノード)106には、例えば、コイル等のインダクタ104の一端側が接続している。インダクタ104の他端側には、コンデンサ105を介して基準電位(例えば、接地電位GND)が供給される。スイッチング素子103のソース103sは、基準電位(GND)に接続され、ソース103sにも基準電位が供給される。また、インダクタ104の他端側は、出力端子107に接続している。そして、スイッチング素子102のソース102sと、基準電位(GND)との間に設けられた電源110により、スイッチング素子102のソース102sには、入力電圧Vinが入力され、出力端子107からは入力電圧Vinが変換された出力電圧Voutが出力される。

【0022】

図2(b)に示すように、ドライバ回路300には、半導体装置1が組み込まれている。例えば、スイッチング素子である半導体装置1には、Pチャネル型のスイッチング素子109が直列に接続されている。半導体装置1のドレイン電極17とスイッチング素子109のドレイン電極109dとの間の接続点108は、スイッチング素子102、103のゲート電極30に接続されている。

【0023】

さらに、図2(c)に示すように、半導体装置1のゲート電極30は、制御回路であるCMOS60に接続されている。CMOS60からの制御信号により、半導体装置1のオン・オフが制御される。

【0024】

CMOS60は、Pチャネル型のMOSで構成されるスイッチング素子60pと、Nチャネル型のMOSで構成されるスイッチング素子60nとから構成される。CMOS60は、さらにCMOS60とは別の制御回路70、71により制御されている。半導体装置1を含むドライバ回路300とCMOS60とは、同じ半導体層10上に設けられている。なお、半導体装置1については、後述する半導体装置2〜7に置き換えることができる。また、このようなドライバ回路300およびCMOS60は、DC−DCコンバータのほか、例えば、モータドライバ回路等にも組み込むことができる(図示しない)。

【0025】

次に、半導体装置1の作用効果について説明する。

図3は、半導体装置の動作を説明するための図を示し、(a)は、本実施の形態に係る半導体装置のX−X’断面図、(b)は、比較例に係る半導体装置のX−X’断面図およびY−Y’断面図である。半導体装置1と半導体装置100とは、半導体装置100に、上述した高誘電体層50が設けられていない点で異なっている。なお、図3の向きは、図1(b)の向きに対応している。

【0026】

最初に、半導体装置100により、半導体装置の動作について説明する。

まず、ゲート電極30とソース電極16との間に、閾値電圧以下の電圧を印加し、ソース電極16とドレイン電極17との間に所定の電圧を印加する。この際、ゲート電極30とドレイン電極17との間にも電圧が印加され、STI20とベース層11との界面からも空乏層が伸び、空乏層が電界を緩和することにより半導体装置100は、高耐圧を維持する。

そして、半導体装置100のゲート電極30に閾値電圧より大きい正バイアスを印加し、ゲート電極30に面したベース層11の表面82の一部または側壁83の一部に反転層81を生じさせることで半導体装置100をオンさせる。これにより、ソース電極16とドレイン電極17との間に電流が流れる。

【0027】

この場合、半導体装置100においては、反転層81がベース層11の表面82もしくは側壁83に沿って主に形成される。上述した非特許文献1によれば、ソース領域12とドレイン領域13の間に流れる電流分布は、ベース層11の表面82の反転層81で58%であり、ベース層11の側壁83の反転層81で39%であるとされている。すなわち、半導体装置100においては、ベース層11の表面82に流れる電流とベース層11の側壁83に流れる電流が主に通電に寄与する。

【0028】

半導体装置1についても同様にオンさせると、反転層80がベース層11の表面82もしくは側壁83に沿って主に形成して、ソース領域12とドレイン領域13との間が通電する。ただし、半導体装置1では、ベース層11の上側に高誘電体層50が配置されたために、反転層80内に誘起される電荷密度は、半導体装置100に比べ大きくなる。これは、半導体装置1では、高誘電体層50の配置により容量結合がより促進され、ベース層11の表面82もしくは側壁83で電荷が著しく誘起されるためである。例えば、図3では、反転層80、81内に生成する電荷密度の大小を濃淡で表し、濃淡が濃いほど、電荷密度が大きいことを表示している。

この高誘電体層50は、ゲート電極30の側壁31側にも形成されているので、反転層80内の電荷密度は、ゲート電極30の近傍ほど高くなる。

【0029】

ここで、高誘電体層50の材質を窒化ケイ素(Si3N4)とすると、高誘電体層50の比誘電率は、STI20の材質である酸化ケイ素(SiO2)に比べおよそ2倍程度になっている。従って、高誘電体層50がゲート電極30とベース層11との間に介在する場合は、ベース層11の反転層80内に誘起される電荷密度は増加する。その結果、半導体装置1のソース領域12とドレイン領域13との間のオン抵抗(以下、単にオン抵抗と称する)は、半導体装置100のオン抵抗に比べ低減する。

【0030】

また、高誘電体層50については、ベース層11の上側の少なくとも一部に配置されている場合でも容量結合を促進させることができるので、半導体装置1では、ベース層11の上側の少なくとも一部に高誘電体層50が設けられていればよい。特に、電界の強さはゲート電極30からの距離に反比例することから、ゲート電極30の近傍に発生する電荷が主にオン抵抗の低減に寄与する。従って、高誘電体層50は、ゲート電極30の近傍に存在することが望ましい。

【0031】

なお、比較例の半導体装置100では、高誘電体層50が設けられていない。従って、半導体装置100をオンさせると、電界がゲート電極30の端部において局部的に集中し易い。その結果、反転層81内の電荷密度が半導体装置1に比べて小さくなり、単位面積あたりのオン抵抗が半導体装置1よりも大きくなる。この半導体装置100で、所望のオン抵抗を得るには、チャネル幅を広くする方法もあるが、この方法では、素子サイズの増大を招いてしまう。従って、半導体装置1のように、高誘電体層50が設けられた構造が好ましい。

【0032】

次に、半導体装置1の製造方法について説明する。

図4〜図6は、半導体装置の製造過程を説明する要部断面図である。図4〜図6中の(α)には、制御回路として組み込まれるCMOSの中、一例として、Nチャネル型のスイッチング素子60nの製造工程についても併せて表示されている。半導体装置1の製造工程については、上述したX−X’断面が(β)に、Y−Y’断面が(γ)に示されている。

【0033】

まず、図4は、CMOSおよび半導体装置の製造過程における要部断面図であり、(α)は、CMOS中のスイッチング素子の製造過程における要部断面図であり、(β)は、半導体装置の製造過程におけるX−X’断面図であり、(γ)は、半導体装置の製造過程におけるY−Y’断面図である。さらに、(a)は、素子分離層の形成工程図であり、(b)は、ベース層の形成工程図であり、(c)は、ゲート酸化膜、ゲート電極およびLDD(Lightly Doped Drain)領域の形成工程図である。

【0034】

図4(a)に示すように、P−型の半導体層10内に、埋め込み法によりSTI20を形成する。次いで、半導体層10上およびSTI20上に、イオンプレーティング注入で使用されるバッファ酸化膜47を形成する。バッファ酸化膜47は、熱酸化法、低圧CVD法によって形成する。バッファ酸化膜47の材質としては、酸化ケイ素(SiO2)等が選択される。次に、図4(b)に示すように、隣接するSTI20間にウェル状のベース層11を形成する。その後、バッファ酸化膜47を除去し、スイッチング素子60nのゲート酸化膜となる酸化膜45を形成する。酸化膜45は、熱酸化法、低圧CVD法等により形成する。酸化膜45の材質としては、酸化ケイ素(SiO2)、酸窒化ケイ素(SiON)、窒化ケイ素(Si3N4)、酸化タンタル(Ta2O5)等が選択される。

【0035】

次に、図4(c)に示すように、酸化膜45を介して、柱状のゲート電極30、65を形成する。ゲート電極30、65のパターニングは、光リソグラフィ法、X線リソグラフィ法、電子ビームリソグラフィ法、反応性イオンエッチング(RIE)法等により行われる。ゲート電極30、65の材質は、例えば、ポリシリコン、タングステン(W)である。ゲート電極30、65の材質がタングステン(W)の場合は、窒化チタン(TiN)、窒化タングステン(WN)のバリア層を設けてもよい。なお、CMOSのNチャネル型のスイッチング素子60nの形成領域(α)には、イオン注入法によりベース層11に選択的にN−領域(Lightly Doped Drain領域)61を形成する。

【0036】

次に、図5は、CMOSおよび半導体装置の製造過程における要部断面図を示し、(α)は、CMOS中のスイッチング素子の製造過程における要部断面図、(β)は、半導体装置の製造過程におけるX−X’断面図、(γ)は、半導体装置の製造過程におけるY−Y’断面図であり、(a)および(b)は、側壁保護膜の形成工程図である。

図5(a)に示すように、酸化膜45およびゲート電極30、65の周辺に、低圧CVD法により、酸化ケイ素(SiO2)等の酸化膜41、窒化ケイ素(Si3N4)等の窒化膜50aを順に形成する。次に、図5(b)に示すように、半導体装置1の形成領域(β)、(γ)に、レジスト62をパターニングする。例えば、光リソグラフィ法等により、半導体装置1の形成領域のベース層11に選択的にレジスト62を形成する。この際、ゲート電極30側壁近傍の酸化膜41、窒化膜50aは表出させる。また、半導体装置1のソース領域12、ドレイン領域13およびコンタクト領域15を形成する領域は表出させる。

【0037】

次に、図6は、CMOSおよび半導体装置の製造過程における要部断面図を示し、(α)は、CMOS中のスイッチング素子の製造過程における要部断面図、(β)は、半導体装置の製造過程におけるX−X’断面図、(γ)は、半導体装置の製造過程におけるY−Y’断面図であり、(a)は、側壁保護膜の形成工程図、(b)は、ソース領域およびドレイン領域の形成工程図である。図6(a)に示すように、異方性のエッチング(例えば、RIE等)を酸化膜41、窒化膜50aに施す。続いて、上述したレジスト62を除去する。これにより、ゲート電極65の側壁には、この側壁がマスクとなって酸化膜41、窒化膜50aが残り、これらの酸化膜、窒化膜を含む側壁保護膜66が形成される。一方、半導体装置1の形成領域(β)、(γ)においては、STI20間のベース層11上の窒化膜50aが残されて、上述した高誘電体層50が形成される。

【0038】

次に、CMOSのNチャネル型のスイッチング素子60nの形成領域(α)においては、N−領域61に隣接するように、N+型のソース領域63およびドレイン領域64をイオン注入法により形成する。また、半導体装置1の形成領域(β)、(γ)においては、ソース領域12、ドレイン領域13およびコンタクト領域15をイオン注入法により形成する。この状態を、図6(b)に示す。そして、この後においては、それぞれの素子に関し、ソース領域12、63、ドレイン領域13、64およびコンタクト領域15上の酸化膜45を取り除き、ソース電極をソース領域に接続させ、ドレイン電極をドレイン領域に接続させる(図示しない)。このような方法によって、半導体装置1並びにCMOSが形成される。

【0039】

この製造工程では、CMOSと半導体装置1とが並行して形成される。従って、高誘電体層50に関しては、側壁保護膜66と同時に形成することができる。これにより、高誘電体層50のみを専用に形成するという工程は要さない。従って、CMOSがノード65nm程度の微細構造を有する場合、CMOS形成プロセスに半導体装置1を混載しても、大きなプロセス変更を伴なわない。その結果、CMOS側の熱履歴を変更することなく、半導体装置1を製造することができる。

【0040】

次に、本実施の形態に係る半導体装置の変形例について説明する。以下の説明では、同じ部材には同じ符号を付し、詳細な説明を適宜省略する。

図7は、本実施の形態の第1および第2の変形例の半導体装置を示し、(a)は、第1の変形例の半導体装置の要部断面図、(b)は、第2の変形例の半導体装置の要部断面図である。図7には、ベース層11が延在する方向とは、略垂直に切断した半導体装置2の要部断面が示されている。また、図7(a)の右横には、図7(a)のD部分が示されている。

【0041】

図7(a)に示す第1の変形例である半導体装置2Aでは、STI20内の少なくとも一部に高誘電体層51が設けられている。

例えば、図7(a)には、STI20の側壁21および底面22に沿うように、高誘電体層51が設けられた状態が示されている。高誘電体層51とベース層11との間には、酸化膜23が介在している。酸化膜23の材質は、STI20の材質と同じである。また、高誘電体層51の材質は、上述した高誘電体層50の材質と同じである。高誘電体層51は、ベース層11に近接し、STI20の側壁21および底面22に沿って、図中のY方向に延在している。

【0042】

このような構造の半導体装置2Aをオンさせると、反転層80がベース層11の表面82もしくは側壁83に沿って主に形成される。特に、半導体装置2Aでは、STI20の側壁21および底面22に沿うように、高誘電体層51が配置されたために、ベース層11の側壁83において著しく電荷が誘起される。従って、半導体装置2Aの単位面積あたりのオン抵抗は、半導体装置100より低減する。

【0043】

また、図7(b)に、第2の変形例である半導体装置2Bを示す。

半導体装置2Bにおいては、高誘電体層51がSTI20の側壁21のみに沿うように配置されている。このような場合でも、上述した容量結合が促進されて、電荷密度の高い反転層80を形成することができる。すなわち、高誘電体層51は、STI20内の少なくとも一部に設けられていればよい。

【0044】

特に、STI20は、隣接する素子の分離層である必要がある。従って、STI20の底面22に面するベース層11に反転層を誘起しすぎると、隣接する素子同士が反転層を通して電気的に接続される場合がある。この場合、STI20は、隣接する素子を電気的に分離をすることができなくなる。従って、半導体装置2Bでは、高誘電体層51を側壁21のみに沿って形成し、隣接する素子同士の分離を確実なものにしている。さらに、半導体装置2Bの単位面積あたりのオン抵抗は半導体装置100よりも低減する。

【0045】

図8は、本実施の形態の第3および第4の変形例の半導体装置を示し、(a)は、第3の変形例の半導体装置の要部断面図、(b)は、第4変形例の半導体装置の要部断面図である。図8には、ベース層11が延在する方向とは、略垂直に切断した半導体装置3の要部断面が示されている。

【0046】

図8(a)に示す第3の変形例である半導体装置3Aでは、ベース層11の上側の少なくとも一部に高誘電体層50が設けられ、さらに、STI20内の少なくとも一部に高誘電体層51が設けられている。

【0047】

このような構造の半導体装置3Aをオンさせると、ベース層11の表面82もしくは側壁83に沿って主に反転層80が形成される。半導体装置3Aでは、ベース層11の上側に高誘電体層50が配置されたほか、STI20の側壁21および底面22に沿うように、高誘電体層51が配置されたために、半導体装置1、2A、2Bよりもベース層11の表面82および側壁83で電荷が著しく誘起される。従って、半導体装置3Aの単位面積あたりのオン抵抗は、半導体装置1、2A、2Bより低減する。

【0048】

また、図8(b)に、第4の変形例である半導体装置3Bを示す。

高誘電体層51については、STI20内の少なくとも一部に配置されている場合でも、上述した容量結合を促進させることができる。従って、半導体装置3Bでは、高誘電体層51をSTI20の側壁21のみに沿って配置している。その結果、隣接する素子同士を確実に電気的に分離させることができる。さらに、半導体装置3Bの単位面積あたりのオン抵抗は、半導体装置1、2A、2Bより低減する。

【0049】

図9は、本実施の形態の第5の変形例の半導体装置を示し、(a)は、(b)のA−Bの水平面で切断して上からみた第5の変形例の半導体装置の要部横断面図、(b)は、(a)のY−Y’断面図である。ただし、図9(a)からは、層間絶縁膜40が取り除かれている。

【0050】

第5の変形例である半導体装置4では、高誘電体層50が設けられたほか、ベース層11とドレイン領域13との間に、N型のドリフト層14が設けられている。高誘電体層50は、ドリフト層14上およびドリフト層14とゲート電極30との間に設けられている。そして、ドリフト層14に並列して設けられたゲート電極30bの幅を、ベース層11に並列して設けられたゲート電極30aの幅よりも細くしている。ゲート電極30の幅とは、X方向にゲート電極30を切断した場合の幅をいう。

【0051】

半導体装置4の動作について説明する。

まず、ゲート電極30に印加する電圧を閾値以下の電圧にする。ソース領域12とドレイン領域13との間には、所定の電圧を印加する。この場合、ドリフト層14には、ベース層11とドリフト層14との界面から空乏層が伸びる。この際、ベース層11の表面82もしくは側壁83には反転層は形成されない。

【0052】

ここで、ドリフト層14においては、トランジスタの通電経路となるために低抵抗であることが望ましい。これを実現するために、ドリフト層14の不純物濃度を単純に高くする方法がある。しかし、単純にドリフト層14の不純物濃度を高くすると、空乏層がドリフト層14内で伸び難くなり、高耐圧を維持できなくなる場合がある。

【0053】

そこで、ゲート電極30bをドリフト層14に並列に配置する。ゲート電極30bとドリフト層14との間にも電界が印加されるため、ドリフト層14には、ドリフト層14とSTI20との界面からも空乏層が伸びる。これらの空乏層が重なって、半導体装置4においては、空乏層がドリフト層14内で満遍なく伸び得る。その結果、ドレイン領域13とソース領域12との間の電界の強さを緩和しやすくなり、ドリフト層14の不純物濃度を高くすることができる。このように、ドレイン領域13とソース領域12との間の耐圧を維持しながら、オン抵抗を低減することができる。

【0054】

半導体装置4では、ドリフト層14の不純物濃度を高くしつつ、ドリフト層14に並列して配置されるゲート電極30bの幅をゲート電極30aよりも細くしている。このような構造であれば、ドリフト層14の不純物濃度を高くしても、ゲート電極30bとドリフト層14との間に、所定の電圧が印加されるので、空乏化がドリフト層14内で伸び易くなる。

【0055】

また、半導体装置4では、ゲート電極30bの幅をゲート電極30aよりも細くしているので、ゲート電極30bとドリフト層14との間の距離が離れ、ゲート電極30bとドリフト層14との間の電界の強さを調節することができる。これにより、ゲート電極30とドリフト層14との間でアバランシェ降伏が起きにくく、半導体装置4は高耐圧を維持する。

【0056】

そして、ゲート電極30に印加する電圧を閾値以上の電圧にすると、ベース層11の表面82もしくは側壁83には、上述した反転層80が形成される。これにより、ソース領域12とドレイン領域13との間に電流が流れる。さらに、半導体装置4では、ドリフト層14がN型であるために、ドリフト層14の表面84もしくは側壁85には蓄積層が形成される。蓄積層が形成されると、ドリフト層14内において、より自由キャリアが増加する。従って、半導体装置4のオン抵抗は、半導体装置1〜3よりもさらに低減する。

【0057】

図10は、本実施の形態の第6の変形例の半導体装置を示し、(a)は、(b)のA−Bの水平面で切断して上からみた第6の変形例の半導体装置の要部横断面図、(b)は、(a)のY−Y’断面図である。ただし、図10(a)からは、層間絶縁膜40が取り除かれている。

【0058】

第6の変形例である半導体装置5では、ベース層11の上側に高誘電体層50が配置されている。ただし、ドリフト層14上およびドリフト層14とゲート電極30bとの間には、高誘電体層50が設けられていない。

このような構造であれば、ゲート電極30とドレイン領域13との間の容量の中、ドリフト層14に並列するゲート電極30bとドレイン領域13との間の容量分がより小さくなる。このため、ゲート電極30とドレイン領域13との間の容量が低減する。従って半導体装置5では、半導体装置4よりもミラー容量を下げることができ、より高速のスイッチング動作が実現する。

【0059】

図11は、本実施の形態の第7の変形例の半導体装置を示し、(a)は、(b)および(c)のA−Bの水平面で切断して上からみた第7の変形例の半導体装置の要部横断面図、(b)は、(a)のX−X’断面図、(c)は、(a)のY−Y’断面図である。ただし、図11(a)からは、層間絶縁膜40が取り除かれている。

【0060】

第7の変形例である半導体装置6では、ベース層11の上側に高誘電体層50が配置されている。ただし、ドリフト層14上には、高誘電体層50が設けられていない。また、半導体装置6では、高誘電体層50のほか、STI20内の少なくとも一部に高誘電体層51が設けられている。

このような構造であれば、半導体装置6のゲート電極30とドレイン領域13との間の容量の中、ドリフト層14に並列するゲート電極30bとドレイン領域13との間の容量分がより小さくなる。このため、半導体装置6では、半導体装置4よりも高速のスイッチング動作が実現する。また、半導体装置6では、STI20内の少なくとも一部に高誘電体層51が設けられているので、反転層80内の電荷密度が高まり、半導体装置5よりもオン抵抗を低減させることができる。

【0061】

図12は、本実施の形態の第8の変形例の半導体装置を示し、(a)は、(b)のA−Bの水平面で切断して上からみた第8の変形例の半導体装置の要部横断面図、(b)は、(a)のY−Y’断面図である。ただし、図12(a)からは、層間絶縁膜40が取り除かれている。

【0062】

第8の変形例である半導体装置7では、高誘電体層50が設けられたほか、ゲート電極30bの部分をゲート電極30aから分離させた構造を有する。ゲート電極30aから電気的に独立した部分を、電極32としている。電極32は、ドリフト層14に並列に配置されている。そして、ゲート電極30aは、共通のライン90で接続されている。電極32は、共通のライン91を通じてソース電極16に接続され、ソース領域12に電気的に接続されている。また、ドレイン領域13は、ドレイン電極17を通じ、共通のライン92で接続されている。

【0063】

この半導体装置7では、ソース電極16とドレイン電極17との間に所定の電圧を印加しても、ゲート電極30aの電圧が閾値以下ならば、ソース電極16とドレイン電極17との間は通電しない。ゲート電極30aの電圧が閾値以上になると、ソース電極16とドレイン電極17との間は通電する。しかし、電極32がソース電極16に導通しているために、ドリフト層14に蓄積層は形成され難い。

【0064】

しかしながら、ゲート電極とドレイン電極17との間の容量は、ゲート電極30aとドレイン電極17との間の容量のみになり、半導体装置4〜6よりもさらに容量が低減する。このため、半導体装置7では、半導体装置4〜6よりもよりミラー容量を下げることができ、より高速のスイッチング動作が実現する。

【0065】

以上、具体例を参照しつつ本発明の実施の形態について説明した。しかし、本発明はこれらの具体例に限定されるものではない。すなわち、これら具体例に、当業者が適宜設計変更を加えたものも、本発明の特徴を備えている限り、本発明の範囲に包含される。例えば、前述した各具体例が備える各要素およびその配置、材料、条件、形状、サイズなどは、例示したものに限定されるわけではなく適宜変更することができる。

【0066】

また、本実施の形態では、第1導電型をN型とし、第2導電型をP型とした場合について説明したが、第1導電型をP型とし、第2導電型をN型とする構造についても実施の形態に含まれ、同様の効果を得る。その他、本発明はその要旨を逸脱しない範囲で種々変形して実施できる。

【0067】

また、前述した各実施の形態が備える各要素は、技術的に可能な限りにおいて複合させることができ、これらを組み合わせたものも本発明の特徴を含む限り本発明の範囲に包含される。

その他、本発明の思想の範疇において、当業者であれば、各種の変更例及び修正例に想到し得るものであり、それら変更例及び修正例についても本発明の範囲に属するものと了解される。

【符号の説明】

【0068】

1、2A、2B、3A、3B、4、5、6、7、100 半導体装置

10 半導体層

11 ベース層

12 ソース領域

13 ドレイン領域

14 ドリフト層

16 ソース電極

17 ドレイン電極

18、19 ビア

20 STI(素子分離層)

30、30a、30b ゲート電極

50、51 高誘電体層

60 CMOS

60n、60p スイッチング素子

70、71 制御回路

102、103、109 スイッチング素子

104 インダクタ

105 コンデンサ

106 接続点(スイッチノード)

200 DC−DCコンバータ

300 ドライバ回路

【特許請求の範囲】

【請求項1】

第1導電型のソース領域と第1導電型のドレイン領域とが表面に選択的に形成された第2導電型のベース層と、

前記ベース層内に設けられ、前記ソース領域から前記ドレイン領域の方向に延在する素子分離層と、

前記素子分離層の上側に設けられ、前記ソース領域と前記ドレイン領域との間の電流経路を制御する制御電極と、

前記ベース層の上側の少なくとも一部または前記素子分離層内の少なくとも一部に配置され、前記素子分離層の比誘電率よりも高い比誘電率を有する高誘電体層と、

前記ソース領域に接続された第1の主電極と、

前記ドレイン領域に接続された第2の主電極と、

を備えたことを特徴とする半導体装置。

【請求項2】

前記高誘電体層は、前記ベース層の上側の少なくとも一部および前記素子分離層内の少なくとも一部に配置されたことを特徴とする請求項1記載の半導体装置。

【請求項3】

前記高誘電体層は、前記ベース層の上から前記制御電極の側壁にまで延在していることを特徴とする請求項1または2に記載の半導体装置。

【請求項4】

前記ベース層と前記ドレイン領域との間に設けられた第1導電型のドリフト層をさらに備えたことを特徴とする請求項1から3のいずれか1つに記載の半導体装置。

【請求項5】

前記ドリフト層に並列する前記制御電極の幅は、前記半導体層に並列する前記制御電極の幅よりも狭いことを特徴とする請求項4記載の半導体装置。

【請求項6】

前記高誘電体層は、前記ドリフト層の上側には設けられていないことを特徴とする請求項4または5に記載の半導体装置。

【請求項7】

前記ドリフト層に並列する前記制御電極の部分は、前記ベース層に並列する前記制御電極から分離され、

前記部分は、前記第1の主電極と電気的に接続されていることを特徴とする請求項4〜6のいずれか1つに記載の半導体装置。

【請求項8】

ハイサイド用のスイッチング素子と、

前記ハイサイド用のスイッチング素子に直列に接続されたローサイド用のスイッチング素子と、

前記ハイサイド用のスイッチング素子と前記ローサイド用のスイッチング素子とを制御するドライバ回路用の請求項1〜6のいずれか1つに記載された半導体装置と、

前記ハイサイド用のスイッチング素子と前記ローサイド用のスイッチング素子との間に、一端側が接続されたインダクタと、

前記インダクタの他端側に接続されたコンデンサと、

を備えたことを特徴とするDC−DCコンバータ。

【請求項1】

第1導電型のソース領域と第1導電型のドレイン領域とが表面に選択的に形成された第2導電型のベース層と、

前記ベース層内に設けられ、前記ソース領域から前記ドレイン領域の方向に延在する素子分離層と、

前記素子分離層の上側に設けられ、前記ソース領域と前記ドレイン領域との間の電流経路を制御する制御電極と、

前記ベース層の上側の少なくとも一部または前記素子分離層内の少なくとも一部に配置され、前記素子分離層の比誘電率よりも高い比誘電率を有する高誘電体層と、

前記ソース領域に接続された第1の主電極と、

前記ドレイン領域に接続された第2の主電極と、

を備えたことを特徴とする半導体装置。

【請求項2】

前記高誘電体層は、前記ベース層の上側の少なくとも一部および前記素子分離層内の少なくとも一部に配置されたことを特徴とする請求項1記載の半導体装置。

【請求項3】

前記高誘電体層は、前記ベース層の上から前記制御電極の側壁にまで延在していることを特徴とする請求項1または2に記載の半導体装置。

【請求項4】

前記ベース層と前記ドレイン領域との間に設けられた第1導電型のドリフト層をさらに備えたことを特徴とする請求項1から3のいずれか1つに記載の半導体装置。

【請求項5】

前記ドリフト層に並列する前記制御電極の幅は、前記半導体層に並列する前記制御電極の幅よりも狭いことを特徴とする請求項4記載の半導体装置。

【請求項6】

前記高誘電体層は、前記ドリフト層の上側には設けられていないことを特徴とする請求項4または5に記載の半導体装置。

【請求項7】

前記ドリフト層に並列する前記制御電極の部分は、前記ベース層に並列する前記制御電極から分離され、

前記部分は、前記第1の主電極と電気的に接続されていることを特徴とする請求項4〜6のいずれか1つに記載の半導体装置。

【請求項8】

ハイサイド用のスイッチング素子と、

前記ハイサイド用のスイッチング素子に直列に接続されたローサイド用のスイッチング素子と、

前記ハイサイド用のスイッチング素子と前記ローサイド用のスイッチング素子とを制御するドライバ回路用の請求項1〜6のいずれか1つに記載された半導体装置と、

前記ハイサイド用のスイッチング素子と前記ローサイド用のスイッチング素子との間に、一端側が接続されたインダクタと、

前記インダクタの他端側に接続されたコンデンサと、

を備えたことを特徴とするDC−DCコンバータ。

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図1】

【図9】

【図10】

【図11】

【図12】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図1】

【図9】

【図10】

【図11】

【図12】

【公開番号】特開2011−114126(P2011−114126A)

【公開日】平成23年6月9日(2011.6.9)

【国際特許分類】

【出願番号】特願2009−268618(P2009−268618)

【出願日】平成21年11月26日(2009.11.26)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

【公開日】平成23年6月9日(2011.6.9)

【国際特許分類】

【出願日】平成21年11月26日(2009.11.26)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

[ Back to top ]