半導体装置とその製造方法

【課題】 キャパシタ直下の導電性プラグが埋め込まれるホールの加工精度を高めることが可能な半導体装置とその製造方法を提供すること。

【解決手段】 第1絶縁膜11の第1、第2ホール11a、11b内に第1、第2導電性プラグ32a、32bを形成する工程と、酸化防止絶縁膜14に第1開口14aを形成する工程と、第1開口14a内に補助導電性プラグ36aを形成する工程と、補助導電性プラグ36a上にキャパシタQを形成する工程と、キャパシタQを覆う第2絶縁膜41に第3、第4ホール41a、41bを形成する工程と、第4ホール41bの下の酸化防止絶縁膜14に第2開口14bを形成する工程と、第3ホール41a内に第3導電性プラグ47aを形成する工程と、第3ホール41a内に第4導電性プラグ47bを形成する工程とを有する半導体装置の製造方法による。

【解決手段】 第1絶縁膜11の第1、第2ホール11a、11b内に第1、第2導電性プラグ32a、32bを形成する工程と、酸化防止絶縁膜14に第1開口14aを形成する工程と、第1開口14a内に補助導電性プラグ36aを形成する工程と、補助導電性プラグ36a上にキャパシタQを形成する工程と、キャパシタQを覆う第2絶縁膜41に第3、第4ホール41a、41bを形成する工程と、第4ホール41bの下の酸化防止絶縁膜14に第2開口14bを形成する工程と、第3ホール41a内に第3導電性プラグ47aを形成する工程と、第3ホール41a内に第4導電性プラグ47bを形成する工程とを有する半導体装置の製造方法による。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置とその製造方法に関する。

【背景技術】

【0002】

電源を切っても情報を記憶することができる不揮発性メモリとして、フラッシュメモリや強誘電体メモリが知られている。

【0003】

このうち、フラッシュメモリは、絶縁ゲート型電界効果トランジスタ(IGFET)のゲート絶縁膜中に埋め込んだフローティングゲートを有し、記憶情報を表す電荷をこのフローティングゲートに蓄積することによって情報を記憶する。しかし、このようなフラッシュメモリでは、情報の書き込みや消去の際に、ゲート絶縁膜にトンネル電流を流す必要があり、比較的高い電圧が必要であるという欠点がある。

【0004】

これに対し、強誘電体メモリは、FeRAM(Ferroelectric Random Access Memory)とも呼ばれ、強誘電体キャパシタが備える強誘電体膜のヒステリシス特性を利用して情報を記憶する。その強誘電体膜は、キャパシタの上部電極と下部電極の間に印加される電圧に応じて分極を生じ、その電圧を取り去っても自発分極が残留する。印加電圧の極性を反転すると、この自発分極も反転し、その自発分極の向きを「1」と「0」に対応させることで、強誘電体膜に情報が書き込まれる。この書き込みに必要な電圧はフラッシュメモリにおけるよりも低く、また、フラッシュメモリよりも高速で書き込みができるという利点がFeARMにはある。

【0005】

FeRAMは、その構造によりスタック型とプレーナ型とに大別される。後者のプレーナ型では、半導体基板に形成されたMOSトランジスタとキャパシタ下部電極とが、キャパシタの上方の金属配線を介して電気的に接続され、キャパシタの平面形状が大きくなり易い傾向がある。

【0006】

これに対し、スタック型のFeRAMでは、MOSトランジスタのソース/ドレイン領域に繋がる導電性プラグの直上にキャパシタ下部電極が形成され、その導電性プラグを介して下部電極とMOSトランジスタとが電気的に接続される。このような構造によれば、プレーナ型と比較してキャパシタの平面形状を小さくすることができ、今後求められるFeRAMの微細化に有利となる。

【0007】

そのような微細化が可能となるには、キャパシタ直下の導電性プラグが埋め込まれる開口を精度良く形成する必要があるので、その開口の加工精度をいかにして高めるかが微細化を進めるための重要な要素となる。

【0008】

なお、上記したスタック型のFeRAMについては、下記の特許文献1、2にその一例が開示されている。

【特許文献1】特開2001−358311号公報

【特許文献2】特開2003−68993号公報

【発明の開示】

【発明が解決しようとする課題】

【0009】

本発明の目的は、キャパシタ直下の導電性プラグが埋め込まれる開口の加工精度を高めることが可能な半導体装置とその製造方法を提供することにある。

【課題を解決するための手段】

【0010】

本発明の一観点によれば、半導体基板と、前記半導体基板の表層に間隔をおいて形成された第1、第2不純物拡散領域と、前記半導体基板上に形成され、前記第1、第2不純物拡散領域のそれぞれの上に第1、第2ホールを備えた第1絶縁膜と、前記第1、第2ホール内にそれぞれ形成され、前記第1、第2不純物拡散領域のそれぞれと電気的に接続された第1、第2導電性プラグと、前記第1絶縁膜の上に形成され、前記第1、第2導電性プラグのそれぞれの上に第1、第2開口を備えた酸化防止絶縁膜と、前記第1開口内に形成された補助導電性プラグと、前記補助導電性プラグ上、及び前記第1開口の周囲の前記酸化防止絶縁膜上に、下部電極、キャパシタ誘電体膜、及び上部電極を順に形成してなるキャパシタと、前記キャパシタを覆うと共に、前記上部電極の上に第3ホールを備え、且つ前記第2開口の上に第4ホールを備えた第2絶縁膜と、前記第3ホール内に形成され、前記上部電極と電気的に接続された第3導電性プラグと、前記第4ホール内と前記第2開口内とに形成され、前記第2導電性プラグと電気的に接続された第4導電性プラグと、を有する半導体装置が提供される。

【0011】

また、本発明の別の観点によれば、半導体基板の表層に互いに間隔をおいて第1、第2不純物拡散領域を形成する工程と、前記半導体基板上に第1絶縁膜を形成する工程と、前記第1絶縁膜をパターニングして、前記第1、第2不純物拡散領域上の該第1絶縁膜にそれぞれ第1、第2ホールを形成する工程と、前記第1、第2ホール内に、前記第1、第2不純物拡散領域のそれぞれと電気的に接続される第1、第2導電性プラグを形成する工程と、前記第1絶縁膜上と前記第1、第2導電性プラグ上とに酸化防止絶縁膜を形成する工程と、前記酸化防止絶縁膜をパターニングして、前記第1導電性プラグの上の該酸化防止絶縁膜に第1開口を形成する工程と、前記酸化防止絶縁膜上と前記第1開口内とに導電膜を形成する工程と、前記導電膜を研磨することにより、前記酸化防止絶縁膜上から該導電膜を除去すると共に、前記第1開口内に前記導電膜を補助導電性プラグとして残す工程と、前記補助導電性プラグ上、及び前記第1開口の周囲の前記酸化防止絶縁膜上に、下部電極、キャパシタ誘電体膜、及び上部電極を順に積層してキャパシタを形成する工程と、前記キャパシタを覆う第2絶縁膜を形成する工程と、前記第2絶縁膜をパターニングすることにより、前記上部電極と前記第2ホールのそれぞれの上の前記第2絶縁膜に第3、第4ホールを形成すると共に、前記第4ホールの下の前記酸化防止絶縁膜に第2開口を形成する工程と、前記第3ホール内に、前記上部電極と電気的に接続される第3導電性プラグを形成する工程と、前記第4ホール内と前記第2開口内とに、前記第2導電性プラグと電気的に接続される第4導電性プラグを形成する工程と、を有する半導体装置の製造方法が提供される。

【0012】

本発明によれば、酸化防止絶縁膜の第1開口内に補助導電性プラグを形成し、この補助導電性プラグとその下の第1導電性プラグにより、キャパシタの下部電極を第1不純物拡散領域に電気的に接続する。その第1開口は、酸化防止絶縁膜のみをパターニングして形成されるので、例えば酸化防止絶縁膜とその下の第1絶縁膜を一括してコンタクトホールを形成する場合と比較して、パターニングにおけるエッチング量を少なくすることができる。これにより、エッチングマスクとして使用されるレジストパターンがエッチングによって膜減りし難くなり、補助導電性プラグが形成される第1開口を精度良く形成することが可能となる。

【0013】

また、酸化防止絶縁膜に上記の第1開口を形成する工程において、該第1開口から間隔がおかれた部分の酸化防止絶縁膜にアライメント用開口を形成してもよい。その場合、第1開口内に導電膜を形成する工程においてアライメント用開口内にも導電膜を形成し、該導電膜を研磨する工程においてアライメント用開口内に導電膜をアライメントマークとして残す。

【0014】

このアライメントマーク用開口は酸化防止絶縁膜に形成されるので、その深さが上記の第1開口と同様に浅くなり、アライメント用開口を埋め込むのに必要な導電膜の厚さを薄くすることができる。従って、導電膜を研磨する工程において、研磨残を残さないためのオーバー研磨量を少なくすることができるので、過剰な研磨によって第1開口内の補助導電性プラグの上面にリセスが発生したり、酸化防止絶縁膜にディッシングが発生したりするのを防止できる。

【0015】

これにより、平坦性が良好に保たれた補助導電性プラグ上にキャパシタの下部電極が形成されるので、下地の凹凸によって下部電極の配向性が低下するのを抑止でき、配向性が良好に保たれた下部電極によりその上のキャパシタ誘電体膜の配向を高めることが可能となる。

【0016】

更に、上記のように酸化防止絶縁膜にディッシングが発生せず、酸素の透過を防止するのに必要な酸化防止絶縁膜の厚さを維持することができるので、酸化防止絶縁膜の下の第2導電性プラグを酸化雰囲気から確実に保護することができ、第2導電性プラグにコンタクト不良が発生するのを防ぐことができる。

【0017】

また、上記のアライメント用開口を完全に埋める厚さに導電膜を形成することで、研磨によりその導電膜をアライメント用開口内に残して得られるアライメントマークの上面に大きな凹部が形成されない。これにより、アライメントマーク上に形成される下部電極用導電膜に膜厚が薄い部分が形成されないので、酸素雰囲気中でキャパシタ誘電体膜に対してアニールを施しても、下部電極用導電膜によって酸素がブロックされ、酸素によってアライメントマークが酸化して飛散するのを防止することができる。

【発明の効果】

【0018】

本発明によれば、補助導電性プラグが埋め込まれる第1開口が酸化防止絶縁膜に形成されるため、パターニングによりその第1開口を形成する際のエッチング量を少なくすることができ、パターニング時のエッチングマスクがエッチングによって膜減りするのが防止され、第1開口の加工精度を高めることが可能となる。

【0019】

更に、上記の第1開口と同時に酸化防止絶縁膜にアライメントマーク用開口を形成する場合でも、アライメント用開口を埋め込むのに必要な導電膜の厚さを薄くできるので、その導電膜に対するオーバー研磨量を低減できる。これにより、補助導電性プラグと酸化防止絶縁膜のそれぞれの上面の平坦性が向上するので、キャパシタの下部電極の配向性を高めることができると共に、酸化防止絶縁膜の下の第2導電性プラグを酸化雰囲気から確実に保護することができる。

【発明を実施するための最良の形態】

【0020】

以下に、本発明の実施の形態について、添付図面を参照しながら詳細に説明する。

【0021】

(1)予備的事項の説明

本実施形態の説明に先立ち、本発明の予備的事項について説明する。

【0022】

図1〜図6は、仮想的な半導体装置の製造途中の断面図である。なお、これらの図では、強誘電体キャパシタが形成されるセル領域Iと、スクライブ領域等の周辺領域IIとを併記してある。

【0023】

この半導体装置は、スタック型のFeRAMであり、以下のようにして作成される。

【0024】

最初に、図1(a)に示す断面構造を得るまでの工程について説明する。

【0025】

まず、n型又はp型のシリコン(半導体)基板1表面に、トランジスタの活性領域を画定するSTI(Shallow Trench Isolation)用の溝を形成し、その中に酸化シリコン等の絶縁膜を埋め込んで素子分離絶縁膜2とする。なお、素子分離構造はSTIに限られず、LOCOS(Local Oxidation of Silicon)法で素子分離絶縁膜2を形成してもよい。

【0026】

次いで、シリコン基板1の活性領域にp型不純物を導入してpウェル3を形成した後、その活性領域の表面を熱酸化することにより、ゲート絶縁膜4となる熱酸化膜を形成する。

【0027】

続いて、シリコン基板1の上側全面に非晶質又は多結晶のシリコン膜を形成し、これらの膜をフォトリソグラフィによりパターニングして二つのゲート電極5を形成する。

【0028】

pウェル3上には、上記の2つのゲート電極5が間隔をおいて平行に配置され、それらのゲート電極5はワード線の一部を構成する。

【0029】

次いで、ゲート電極5をマスクにするイオン注入により、ゲート電極5の横のシリコン基板1にn型不純物を導入し、第1、第2ソース/ドレインエクステンション6a、6bを形成する。

【0030】

その後に、シリコン基板20の上側全面に絶縁膜を形成し、その絶縁膜をエッチバックしてゲート電極5の横に絶縁性サイドウォール7を形成する。その絶縁膜として、例えばCVD法により酸化シリコン膜を形成する。

【0031】

続いて、絶縁性サイドウォール7とゲート電極5をマスクにしながら、シリコン基板1にn型不純物を再びイオン注入することにより、二つのゲート電極5の側方のシリコン基板1の表層に、互いに間隔がおかれた第1、第2ソース/ドレイン領域(第1、第2不純物拡散領域)8a、8bを形成する。

【0032】

ここまでの工程により、シリコン基板1の活性領域には、ゲート絶縁膜4、ゲート電極5、及び第1、第2ソース/ドレイン領域8a、8bによって構成される第1、第2MOSトランジスタTR1、TR2が形成されたことになる。

【0033】

次に、シリコン基板1の上側全面に、スパッタ法によりコバルト層等の高融点金属層を形成した後、この高融点金属層を加熱してシリコンと反応させ、シリコン基板1上に高融点金属シリサイド層9を形成する。その高融点金属シリサイド層9はゲート電極5の表層部分にも形成され、それによりゲート電極5が低抵抗化されることになる。

【0034】

その後、素子分離絶縁膜2の上等で未反応となっている高融点金属層をウエットエッチングして除去する。

【0035】

続いて、プラズマCVD法により、シリコン基板1の上側全面に窒化シリコン(SiN)膜を厚さ約80nmに形成し、それをカバー絶縁膜10とする。次いで、このカバー絶縁膜10の上に、TEOSガスを使用するプラズマCVD法により第1絶縁膜11として酸化シリコン膜を厚さ約11000nmに形成する。

【0036】

次いで、図1(b)に示すように、上記の第1絶縁膜11の上面をCMP(Chemical Mechanical Polishing)法により研磨して平坦化する。このCMPの結果、第1絶縁膜11の厚さは、シリコン基板20の平坦面上で約800nmとなる。

【0037】

そして、図1(c)に示すように、フォトリソグラフィによりカバー絶縁膜10と第1絶縁膜11とをパターニングして、二つのゲート電極5の間の第2ソース/ドレイン領域8bの上に第1コンタクトホール11cを形成する。

【0038】

次に、図2(a)に示すように、第2ソース/ドレイン領域8bと電気的に接続される第1コンタクトプラグ13cを第1コンタクトホール11c内に形成する。その第1コンタクトプラグ13cは、タングステンで主に構成されるが、タングステンは非常に酸化され易く、プロセス中で酸化されるとコンタクト不良を引き起こす。

【0039】

そこで、次の工程では、図2(b)に示すように、第1コンタクトプラグ13cを酸化雰囲気から保護するための酸化防止絶縁膜14として、プラズマCVD法により酸窒化シリコン(SiON)膜を厚さ約130nmに形成する。

【0040】

その後に、プラズマCVD法により酸化防止絶縁膜14上に酸化シリコン膜を厚さ約200nmに形成し、その酸化シリコン膜を絶縁性密着膜15とする。

【0041】

続いて、図2(c)に示すように、絶縁性密着膜15上にフォトレジストを塗布し、それを露光、現像することにより第1レジストパターン16を形成する。その第1レジストパターン16は、セル領域Iにおいて第1ソース/ドレイン領域8a上にホール形状の第1窓16aを有すると共に、周辺領域IIにおいて幅の広い第2窓16bを有する。

【0042】

そして、これら第1、第2窓16a、16bを通じてカバー絶縁膜10、第1絶縁膜11、酸化防止絶縁膜14、及び絶縁性密着膜15をRIE(Reactive Ion Etching)でエッチングすることにより、セル領域Iにおけるこれらの絶縁膜に第2コンタクトホール11dを形成すると共に、周辺領域IIにアライメントマーク用開口11eを形成する。

【0043】

これらのうち、開口11eは、後述のキャパシタを形成するためのフォトリソグラフィの際、露光装置(不図示)とシリコン基板1との位置合わせを行うのに使用される。

【0044】

ここで、第2コンタクトホール11dは、酸化防止絶縁膜14と絶縁性密着膜15の厚さにより、その深さが既述の第1コンタクトホール11cよりも深くなる。そのため、このエッチング工程におけるエッチング量は第1コンタクトホール11cのそれよりも多くなり、RIEのエッチング雰囲気中に第1レジストパターン16が長時間曝される。その結果、図示のように、エッチングの最中に第1レジストパターン16が膜減りし、エッチングが終了する頃にはエッチングマスクとなる第1レジストパターン16の残厚が極めて薄くなるので、上記のように深い第2コンタクトホール11dを精度良く形成するのは難しい。このような問題は、第1レジストパターン16の膜厚を薄くする必要のある微細な直径の第2コンタクトホール11dを形成する場合に特に顕著に見られる。

【0045】

その後に、第1レジストパターン16は除去される。

【0046】

次いで、図3(a)に示すように、スパッタ法によりシリコン基板1の上側全面にバリアメタル膜17としてチタン膜と窒化チタン膜とをこの順に形成する。なお、窒化チタン膜についてはCVD法で形成してもよい。そのバリアメタル膜17は、上記した第2コンタクトホール11dと開口11eのそれぞれの内面にも形成される。

【0047】

次に、図3(b)に示すように、上記のバリアメタル膜17上にタングステン膜18を形成し、そのタングステン膜18で第2コンタクトホール11dを完全に埋め込む。

【0048】

タングステン膜18は、アライメントマーク用の開口11e内にも形成されるが、本来はその厚さは第2コンタクトホール11dを埋める程度で十分なため、この例では第2コンタクトホール11dを埋めるのに必要な最低限の厚さでタングステン膜18を形成する。このようにすると、第2コンタクトホール11dよりも幅が広い開口11eは、図示のようにタングステン膜18によって完全には埋め込まれないことになる。

【0049】

その後に、図3(c)に示すように、絶縁性密着膜15上の余分なバリアメタル膜17とタングステン膜18とをCMP法により研磨して除去し、これらの膜を第2コンタクトホール11dと開口11e内にのみ残す。このようにして第2コンタクトホール11d内に残されたバリアメタル膜17とタングステン膜18は第2コンタクトプラグ19として使用され、周辺領域IIの開口11e内に残されたこれらの膜はアライメントマーク20とされる。

【0050】

次いで、図4(a)に示すように、スパッタ法によりイリジウム膜を約50〜200nmの厚さ、例えば100nmに形成し、それを下部電極用導電膜21とする。

【0051】

更に、MOCVD(Metal Organic CVD)法により、下部電極用導電膜21上に強誘電体膜22としてPZT(Lead Zirconate Titanate: PbZrTiO3)膜を厚さ約50〜150nm、例えば100nmに形成する。

【0052】

その後、この強誘電体膜22上にスパッタ法により酸化イリジウム(IrO2)膜を50〜200nm、例えば100nmの厚さに形成し、それを上部電極用導電膜23とする。

【0053】

このようにして積層された下部電極用導電膜21、強誘電体膜22、及び上部電極用導電膜23は、後でパターニングされてそれぞれキャパシタ下部電極、キャパシタ誘電体膜、及びキャパシタ上部電極とされる。

【0054】

次に、図4(b)に示すように、上部電極用導電膜23上に第1マスク材料層25としてスパッタ法により窒化チタン膜を厚さ約200nmに形成した後、更にその上にCVD法により酸化シリコン膜を約600nmの厚さに形成し、それを第2マスク材料層26とする。

【0055】

その後に、第2マスク材料層26上にフォトレジスト27を塗布する。

【0056】

次に、図5(a)に示す断面構造を得るまでの工程について説明する。

【0057】

まず、不図示のステッパ等の露光装置内にシリコン基板1を入れる。そして、アライメント用開口11eに起因して第2マスク材料層26の表面に形成される凹部を光学的に検出し、露光装置とシリコン基板1との位置合わせを行う。続いて、この露光装置内でフォトレジスト27を露光した後に、それを現像することで、セル領域Iにおいてキャパシタ平面形状を有するキャパシタ用レジストパターン27aを形成する。また、そのキャパシタ用レジストパターン27aは、周辺領域Iにおいて、アライメントマーク用の開口11eを上方から覆う。

【0058】

次に、図5(b)に示す断面構造を得るまでの工程について説明する。

【0059】

まず、キャパシタ用レジストパターン27aをマスクにして第2マスク材料膜26をエッチングすることによりハードマスク26aを形成する。

【0060】

そして、キャパシタ用レジストパターン27aを除去した後に、ハードマスク26aをマスクにして第1ハードマスク層25をエッチングし、その第1マスク材料層25をハードマスク26aの下にのみ残す。

【0061】

続いて、図6(a)に示すように、ハードマスク26aをエッチングマスクにしながら、下部電極用導電膜21、強誘電体膜22、及び上部電極用導電膜23を一括してエッチングする。これにより、第2コンタクトプラグ19上には、下部電極21a、キャパシタ誘電体膜22a、及び上部電極23aをこの順に積層してなるキャパシタQが形成されたことになる。

【0062】

なお、周辺領域IIでは、下部電極用導電膜21、強誘電体膜22、及び上部電極用導電膜23はエッチングされず、ハードマスク26aの下に残存する。

【0063】

続いて、図6(b)に示すように、ハードマスク26aと第1マスク材料層25とをウエットエッチングとドライエッチングにより除去する。

【0064】

その後に、キャパシタQを形成する際のエッチングやスパッタによってキャパシタ誘電体膜22aが受けたダメージを回復させるため、酸素雰囲気中でキャパシタQをアニールする。そのようなアニールは、回復アニールとも呼ばれる。

【0065】

ところで、上記の例では、コンタクトプラグ19を構成するタングステン膜18は、第2コンタクトホール11dを埋め込む最低限の厚さで形成されているため、第2コンタクトホール11dよりも幅が広い開口11eに対するタングステン膜18の埋め込みは不完全となっている。そのため、図6(b)に示されるように、開口11eには、キャパシタQの下部電極21aを構成する下部電極用導電膜21が残っており、上記の回復アニールの際の酸素がその下部電極用導電膜21に到達する。

【0066】

しかし、下部電極用導電膜21は、カバレッジの悪いスパッタ法によって形成されているので、その膜厚が開口11e内において不均一となっており、図示のような薄厚部21bが下部電極用導電膜21に発生し、その薄厚部21bからタングステン膜18に上記の酸素が侵入することになる。こうなると、他の金属に比べて非常に酸化され易いタングステン膜18が薄厚部21bの近くで酸化し、下部電極用導電膜21によって密閉された空間において酸化されたタングステンが膨張して、その膨張により下部電極用導電膜21、強誘電体膜22、及び上部電極用導電膜23のいずれかよりなる膜25が周囲に飛散する。その膜25は、デバイス不良を引き起こすと共に、後の工程で行われるフォトリソグラフィ工程におけるパターン不良の原因となるので、好ましくない。

【0067】

このような膜25の剥離を発生させないためには、周辺領域IIにおいて、タングステン膜18によって開口11eを完全に埋め込むことで、周辺領域IIに下部電極用導電膜21を残さないようにすることが考えられる。

【0068】

図7、図8は、このようにタングステン膜18で開口11eを完全に埋め込む場合の仮想的なFeRAMの製造途中の断面図である。なお、図7、図8において、図1〜図6で説明した要素にはこれらの図と同じ符号を付し、以下ではその説明を省略する。

【0069】

まず、上記で説明した図1(a)〜図3(a)の工程を行った後、図7(a)に示すように、バリアメタル膜17上にタングステン膜18を形成し、そのタングステン膜18で第2コンタクトホール11dと開口11eの両方を完全に埋め込む。このように、第2コンタクトホール11dだけでなく、それよりも幅の広い開口11eも埋め込むために、タングステン膜18の厚さは、上記の例(図3(b)参照)よりもかなり厚く、例えばシリコン基板1の平坦面上で約900nm程度の厚さにする必要がある。

【0070】

その後に、図7(b)に示すように、絶縁性密着層15上の余分なバリアメタル膜17とタングステン膜18とをCMP法により研磨して除去することにより、第2コンタクトホール11dと開口11eの中に残されたこれらの膜をそれぞれ第2コンタクトプラグ19、アライメントマーク20とする。

【0071】

ところで、そのCMPでは、第2コンタクトホール11dと開口11e以外にタングステン膜18とバリアメタル膜17を残さないために、これらの膜の合計膜厚よりも研磨量が多くなるようなオーバー研磨が施される。特に、この例のように研磨対象となるタングステン膜18が厚いほどCMP後に膜が残り易いので、上記のオーバー研磨の量は、タングステン膜18を薄くする先の例(図3(c)参照)よりも多く設定される。

【0072】

その結果、図7(b)に示されるように、絶縁性密着膜15や酸化防止絶縁膜14が不必要に研磨され、第1コンタクトプラグ13cの上のこれらの膜にディッシング(膜減り)が発生すると共に、第2コンタクトプラグ19も過剰に研磨されてその上面にリセス(窪み)が発生する。

【0073】

この後は、既述の図4(a)〜図6(b)の工程を行うことで、図8に示すようなキャパシタQを第2コンタクトプラグ19上に形成する。

【0074】

この例では、周辺領域IIの開口11eがタングステンよりなるアライメントマーク20によって完全に埋め込まれており、その上に下部電極用導電膜21が均一な厚さで形成されている。従って、酸素雰囲気中でキャパシタQに対して回復アニールを施しても、下部電極用導電膜21によって酸素の透過が阻止されるので、図6(b)のような膜25が発生せず、剥離した膜25に起因するパターン不良等の問題は回避できる。

【0075】

しかし、図7(b)で説明したように、タングステン膜18に対するCMP時のオーバー研磨量を多くしたことで、第1コンタクトプラグ13c上の酸化防止絶縁膜14にディッシングが発生する。これにより、キャパシタQの回復アニール時に、タングステンを主に構成される第1コンタクトプラグ13cを酸化防止絶縁膜14で酸素雰囲気から保護するのが難しくなり、第1コンタクトプラグ13cが酸化してコンタクト不良を引き起こす恐れが新たに発生する。

【0076】

しかも、上記のCMPにより、キャパシタQの直下の第2コンタクトプラグ19の上面にリセスが形成し、その上面の平坦性が低下する。このリセスに起因する平坦性の低下により下部電極21aにおけるイリジウムの配向性が低下する。キャパシタ誘電体膜22aの配向は、下部電極21aの配向に大きく依存するので、このように下部電極21aの配向性が低下すると、キャパシタ誘電体膜22aの配向性も低下し、ひいてはキャパシタ誘電体膜22aの強誘電体特性が劣化する。

【0077】

本願発明者はこのような問題点に鑑み、以下に説明するような本発明の実施の形態に想到した。

【0078】

(2)第1実施形態

図9〜図18は、本発明の第1実施形態に係る半導体装置の製造途中の断面図である。なお、これらの図において、図1〜図8で説明したのと同じ要素にはこれらの図と同じ符号を付し、以下ではその説明を省略する。

【0079】

この半導体装置はスタック型のFeRAMであり、以下のようにして作成される。

【0080】

まず、予備的事項で説明した図1(a)、(b)の工程を行った後に、図9(a)に示すように、第1絶縁膜11の上にフォトレジストを塗布し、それを露光、現像して第2レジストパターン30を形成する。

【0081】

図示のように、第1、第2ソース/ドレイン領域8a、8bの上方の第2レジストパターン30には、ホール形状の第1、第2窓30a、30bがそれぞれ形成される。

【0082】

続いて、図9(b)に示すように、周波数が13.56MHzでパワーが1kW〜2.5kWの高周波電力をエッチング雰囲気に印加すると共に、C4F8、Ar、及びO2の混合ガスをエッチングガスとして使用するRIEにより、上記の第1、第2窓30a、30bを通じて第1絶縁膜11とカバー絶縁膜10とをエッチングして、第1、第2ソース/ドレイン領域8a、8bのそれぞれの上に第1、第2ホール11a、11bを形成する。なお、上記のエッチング雰囲気の圧力は特に限定されないが、本実施形態では2〜7Paとする。

【0083】

このエッチングが終了後、第2レジストパターン30は除去される。

【0084】

次に、図9(c)に示す断面構造を得るまでの工程について説明する。

【0085】

まず、第1絶縁膜11の上面と、第1、第2ホール11a、11bの内面とに、スパッタ法によりチタン膜を厚さ約30nmに形成する。更に、このチタン膜の上に、四塩化チタンガス(TiCl4)を反応ガスとして使用するCVD法により、厚さが約20nmの窒化チタン膜を形成し、この窒化チタン膜と上記のチタン膜とを第1バリアメタル膜31とする。

【0086】

その後に、六フッ化タングステンガスを使用するCVD法を用いて、この第1バリアメタル膜31上にタングステン膜32を形成し、このタングステン膜32により第1、第2ホール11a、11bを完全に埋め込む。

【0087】

続いて、図10(a)に示すように、第1絶縁膜11が研磨ストッパとなるようなスラリー(研磨剤)、例えばCabot Microelectronics Corporation製のW2000を使用するCMP法により、第1絶縁膜11上の余分な第1バリアメタル膜31とタングステン膜32とを研磨して除去し、これらの膜を第1、第2ホール11a、11b内に第1、第2導電性プラグ32a、32bとして残す。

【0088】

このように、第1、第2導電性プラグ32a、32bは同じプロセスによって形成されるので、それらの上面の高さは同じになる。また、第1、第2ソース/ドレイン領域8a、8bは、それぞれ第1、第2導電性プラグ32a、32bと電気的に接続される。

【0089】

次いで、図10(b)に示すように、シラン(SiH4)とN2Oとを反応ガスとするプラズマCVD法により、第1、第2導電性プラグ32a、32bと第1絶縁膜11のそれぞれの上面に酸窒化シリコン膜を形成し、それを酸化防止絶縁膜14とする。その酸化防止絶縁膜14は、第1絶縁膜11よりも薄い厚さ、例えば約130nmの厚さに形成するのが好ましい。

【0090】

酸化防止絶縁膜14を構成する酸窒化シリコンは、他の絶縁膜に比べ、酸素の透過防止性に優れている。そのため、二つのゲート電極5の間に形成された酸化し易いタングステンで主に構成される第2導電性プラグ32bは、この酸化防止絶縁膜14によって酸化雰囲気から保護され、プロセス中に異常酸化してコンタクト不良を起こすのが防止される。

【0091】

このように酸素の透過を防止する機能を有する絶縁膜としては、上記の酸窒化シリコン膜の他に窒化シリコン(SiN)膜とアルミナ(Al2O3)膜があり、これらの膜を単層で酸化防止絶縁膜14として形成してもよい。その場合、窒化シリコン膜は、シランとアンモニアとを反応ガスとするプラズマCVD法によって形成される。また、アルミナ膜はスパッタ法によって形成される。

【0092】

その後に、上記の酸化防止絶縁膜14上に、絶縁性密着膜15として酸化シリコン膜を約200nmに形成する。この酸化シリコン膜の成膜方法は特に限定されないが、本実施形態ではTEOSガスを用いるプラズマCVD法によりこの酸化シリコン膜を形成する。

【0093】

続いて、図10(c)に示すように、絶縁性密着膜15上にフォトレジストを塗布し、それを露光、現像して第3レジストパターン33を形成する。この第3レジストパターン33は、第2導電性プラグ32aの上方にホール形状の第3窓33aを有すると共に、この第3窓33aよりも幅が広い第4窓33bを周辺領域IIに有する。

【0094】

その後に、図11(a)に示すように、上記の第3、第4窓33a、33bを通じてその下の絶縁性密着膜15と酸化防止絶縁膜14とをエッチングすることにより、各窓33a、33bの下の酸化防止絶縁膜14にそれぞれ第1開口14aとアライメントマーク用開口14cとを形成する。

【0095】

このときのエッチング条件は特に限定されないが、本実施形態では、C4F8、Ar、及びO2の混合ガスをエッチングガスとして使用するRIEを採用する。

【0096】

また、これにより形成された第1開口14aの深さは、酸化防止絶縁膜14と絶縁性密着膜15の合計膜厚に等しく約330nmとなるが、この値は第1、第2ホール11a、11bの深さ(約900nm)よりも浅く、この工程におけるエッチング量は図2(b)のそれよりも格段に少ない。よって、エッチングによる第3レジストパターン33の膜減りが図2(b)の場合よりも低減され、エッチング終了後にも第3レジストパターン33が厚く残存するので、第1開口14aを精度良く形成することができる。

【0097】

その後に、第3レジストパターン33は除去される。

【0098】

次に、図11(b)に示すように、絶縁性密着膜15の上面と各開口14a、14cの内面とに、第2バリアメタル膜35として窒化チタン膜を約50nmの厚さに形成する。

【0099】

ここで、既述のように、第1開口14aの深さが約330nmと浅いので、カバレッジに優れた高価なCVD法で第2バリアメタル膜35を形成する必要は無く、安価なスパッタ法により第2バリアメタル膜35を形成することができる。但し、第2バリアメタル膜35の成膜方法はスパッタ法に限定されず、CVD法で第2バリアメタル膜35を形成してもよい。

その後に、六フッ化タングステンガスを用いるCVD法により、この第2バリアメタル膜35の上に導電膜36としてタングステン膜を形成し、この導電膜36で上記の各開口14a、14cを完全に埋め込む。

【0100】

上記のようにアライメント用開口14cの深さが非常に浅いので、それを埋め込むのに必要な導電膜36の厚さは、図7(a)で説明したタングステン膜18の厚さよりも薄くて済み、本実施形態では絶縁性密着膜15の平坦面上で例えば約300nmとされる。

【0101】

続いて、図11(c)に示すように、絶縁性密着膜15を研磨ストッパにしながら、その絶縁性密着膜15上の余分な第2バリアメタル膜35と導電膜36とをCMP法により研磨して除去し、これらの膜を第1開口14aとアライメントマーク用開口14cの中にのみ残す。そのCMPにおけるスラリーとして、例えばCabot Microelectronics Corporation製のW2000を採用する。

【0102】

そして、このようにして残された第2バリアメタル膜35と導電膜36は、第1開口14a内において、第1導電性プラグ32aと電気的に接続される補助導電性プラグ36aとされると共に、アライメントマーク用開口14c内においてアライメントマーク36cとされる。

【0103】

ところで、このCMPにおいては、開口14a、14c以外の絶縁性密着膜15上に導電膜36や第2バリアメタル膜35を残さないために、研磨量をこれらの膜の合計の厚さよりも多くするオーバー研磨が行われる。

【0104】

但し、研磨の対象となる導電膜36の厚さが上記のように薄いので、絶縁性密着膜15上に研磨残を残さないためのオーバー研磨量を図7(b)の場合よりも少なくすることができ、過剰な研磨をしなくて済む。よって、上記のようにCMPを行っても、補助導電性プラグ36aの上面にリセスが発生したり、酸化防止絶縁膜14や絶縁性密着膜15にディッシングが発生したりすることが防止され、CMPを終了した後の絶縁性密着膜15と補助導電性プラグ36aの各上面の平坦性を極めて良好にすることができる。

【0105】

次に、図12(a)に示す断面構造を得るまでの工程について説明する。

【0106】

まず、スパッタ法により、補助導電性プラグ36aと絶縁性密着膜15のそれぞれの上に下部電極用導電膜21として配向性金属膜を形成する。配向性金属膜としては、例えばイリジウム膜がある。本実施形態では、そのうちのイリジウム膜を50〜200nmの厚さ、より好ましくは100nmの厚さに形成する。

【0107】

上記したように、絶縁性密着膜15と補助導電性プラグ36aの各上面の平坦性が良いので、下部電極用導電膜21の配向性が下地の凹凸によって低下するのが防がれ、その配向性を良好に保つことができる。

【0108】

次いで、強誘電体膜22として、PZT膜をMOCVD法により下部電極用導電膜21上に50〜150nmの厚さ、より好ましくは100nmの厚さに形成する。なお、強誘電体膜22の成膜方法としては、MOCVD法の他に、スパッタ法やゾル・ゲル法もある。更に、強誘電体膜22の材料は上記のPZTに限定されず、SrBi2Ta2O9、SrBi2(Ta, Nb)2O9等のBi層状構造化合物や、PZTにランタンをドープしたPLZT、或いはその他の金属酸化物強誘電体で強誘電体膜22を構成してもよい。

【0109】

その強誘電体膜22の配向性は、下地の下部電極用導電膜21の配向性に大きく依存するが、上記のように下部電極用導電膜21の配向性が良好なので、この強誘電体膜22の配向も高められる。

【0110】

その後に、強誘電体膜22の上に、スパッタ法により酸化イリジウム(IrO2)膜を50〜200nmの厚さ、より好ましくは100nmの厚さに形成し、それを上部電極用導電膜23とする。

【0111】

続いて、図12(b)に示すように、上部電極用導電膜23上に第1マスク材料層25としてスパッタ法により窒化チタン膜を厚さ約200nmに形成した後、更にその上にCVD法により酸化シリコン膜を約600nmの厚さに形成し、それを第2マスク材料層26とする。

【0112】

その後に、マスク材料層26上にフォトレジスト27を塗布する。

【0113】

ところで、補助導電性プラグ36aよりも幅が広いアライメントマーク36cの上面は、図11(c)のCMP工程におけるオーバー研磨によって、その周囲の絶縁性密着膜15の上面よりも若干低くなっている。その結果、図12(b)の工程を終了した後では、アライメントマーク36cに起因する浅い凹部(不図示)が周辺領域IIのマスク材料層26に形成されている。その凹部の深さは、典型的には約50〜100nm程度と浅い。

【0114】

このような凹部を利用することにより、次の図13(a)の工程では、まずステッパ等の露光装置(不図示)内にシリコン基板1を入れ、アライメントマーク36c上の上記の凹部を光学的に検出することで、露光装置とシリコン基板1との位置合わせを自動的に行う。

【0115】

次いで、露光装置内でフォトレジスト27を露光した後に、フォトレジスト27を現像することにより、図13(a)に示されるようなキャパシタ用レジストパターン27aを形成する。そのキャパシタ用レジストパターン27aは、セル領域I上においてキャパシタ平面形状を有すると共に、周辺領域IIにおいてアライメントマーク36cを覆う。

【0116】

次に、図13(b)に示す断面構造を得るまでの工程について説明する。

【0117】

まず、キャパシタ用レジストパターン27aをエッチングマスクに使用しながら第2マスク材料層26をエッチングしてハードマスク26aを形成する。

【0118】

そして、キャパシタ用レジストパターン27aを除去した後、上記のハードマスク26aをマスクにして第1マスク材料層25をエッチングすることにより、ハードマスク26aの下にのみ第1マスク材料層25を残す。

【0119】

続いて、図14(a)に示すように、ハロゲンガスを含むエッチングガスを用いて、ハードマスク26aで覆われていない部分の下部電極用導電膜21、強誘電体膜22、及び上部電極用導電膜23を一括してドライエッチングする。これにより、セル領域Iには、補助導電性プラグ36aと電気的に接続された下部電極21a、キャパシタ誘電体膜22a、及び上部電極23aを順に積層してなるキャパシタQが形成されたことになる。

【0120】

そのキャパシタQを構成する下部電極21aは、絶縁性密着膜15によって膜剥がれが防止される。更に、絶縁性密着膜15は、非晶質の酸化シリコンよりなるため、結晶性のある膜のように下部電極21aの配向を乱してしまうことが無く、下部電極21aの配向を良好に保つようにも機能する。

【0121】

その後に、ハードマスク26aと第1マスク材料層25とをウエットエッチングとドライエッチングにより除去する。

【0122】

次いで、図14(b)に示すように、上記した図14(a)のエッチング工程等でキャパシタ誘電体膜22aが受けたダメージを回復させるため、不図示のファーネス内にシリコン基板1を入れ、酸素雰囲気中で基板温度を550℃とする一回目の回復アニールをキャパシタ誘電体膜22aに対して約40分間行う。

【0123】

ここで、アライメント用開口14c内にアライメントマーク36cが略完全に埋め込まれているので、アライメントマーク36c上の下部電極用導電膜21には、図6(b)に示したような薄厚部21bが形成されていない。従って、このように酸素雰囲気中で回復アニールを行っても、下部電極用導電膜21で酸素をブロックすることができ、アライメントマーク36cが酸化するのを防ぐことができる。

【0124】

次に、図15(a)に示す断面構造を得るまでの工程について説明する。

【0125】

まず、水素等の還元性雰囲気からキャパシタ誘電体膜22aを保護するために、キャパシタ保護絶縁膜40として水素ブロック性に優れたアルミナ膜をシリコン基板1の上側全面に約50nmの厚さに形成する。

【0126】

そのキャパシタ保護絶縁膜40の成膜方法は特に限定されない。但し、カバレッジ特性に優れたALD(Atomic Layer Deposition)法でキャパシタ保護絶縁膜40を形成すれば、キャパシタQの側面にキャパシタ保護絶縁膜40をカバレッジ良く形成することができるので、隣接するキャパシタQの間隔を狭めることができ、FeRAMの微細化を推し進めることができる。

【0127】

次いで、シランを反応ガスとして使用するHDPCVD(High Density Plasma CVD)法を用いて、キャパシタ保護絶縁膜40上に第2絶縁膜41を形成し、隣接する二つのキャパシタQの間の空間をその第2絶縁膜41で埋め込む。その第2絶縁膜41の厚さは特に限定されないが、本実施形態ではシリコン基板1の平坦面上で約700nmとする。

【0128】

その後に、TEOSガスを用いるプラズマCVD法により、第2絶縁膜41上に犠牲絶縁膜42として酸化シリコン膜を形成する。この第2絶縁膜41の厚さは、シリコン基板1の平坦面上で例えば800nmである。

【0129】

続いて、図15(b)に示すように、CMP法により犠牲絶縁膜42と第2絶縁膜41の上面を研磨して平坦化した後、第2絶縁膜41上にフォトレジストを塗布し、それを露光、現像することにより、上部電極23a上にホール形状の第5窓43aを備えた第4レジストパターン43を形成する。

【0130】

そして、図16(a)に示すように、上記の第5窓43aを通じて第2絶縁膜41とキャパシタ保護絶縁膜40とをエッチングして、これらの絶縁膜40、41に上部電極23aに至る深さの第3ホール41aを形成する。このエッチングは、C4F8、Ar、及びO2の混合ガスをエッチングガスとして使用する平行平板型プラズマエッチング装置で行われ、エッチング時の圧力は2〜7Paとされる。また、周波数が13.56MHzでパワーが1kW〜2.5kWの高周波電力がそのエッチング装置の上部電極に印加され、それにより上記のエッチングガスがプラズマ化される。

【0131】

そして、第4レジストパターン43を除去した後に、ここまでの工程でキャパシタ誘電体膜22aが受けたダメージを回復させるため、不図示のファーネス内にシリコン基板1を入れ、酸素雰囲気中で基板温度を550℃とする二回目の回復アニールを約40分間行う。

【0132】

次に、図16(b)に示すように、第2絶縁膜41上にフォトレジストを再び塗布して、そのフォトレジストを露光、現像し、第5レジストパターン45を形成する。その現像により、第2導電性プラグ36b上の第5レジストパターン45には、ホール形状の第6窓45aが形成される。

【0133】

その後に、図17(a)に示すように、第5レジストパターン45の第6窓45aを通じて第2絶縁膜41、キャパシタ保護絶縁膜40、絶縁性密着膜15、及び酸化防止絶縁膜14をエッチングする。これにより、第2絶縁膜41に第4ホール41bが形成されると共に、その第4ホール41bの下の酸化防止絶縁膜14に第2開口14bが形成される。このようなエッチングは、例えばC4F8、Ar、O2、及びCOの混合ガスをエッチングガスとする平行平板プラズマエッチング装置で行われる。

【0134】

なお、このエッチングでは、圧力が2〜7Paに設定されると共に、周波数が13.56MHzでパワーが1kW〜2.5kWの高周波電力がエッチング装置の上部電極に印加される。

【0135】

このように、上部電極23a上の浅い第3ホール41aとは別に、第2ソース/ドレイン領域8b上の深い第4ホール41bを形成することで、浅い第3ホール41aの下の上部電極23aがエッチング雰囲気に長時間曝されるのを防ぐことができ、その下のキャパシタ誘電体膜22aが劣化するのを抑制することが可能となる。

【0136】

更に、第2ソース/ドレイン領域8b上の第2導電性プラグ36bは、本工程が終了するまで、酸化防止絶縁膜14によって覆われているので、第2導電性プラグ36bを構成するタングステンが酸化してコンタクト不良を起こすのが防止される。

【0137】

その後に、図17(b)に示すように、第5レジストパターン45を除去する。

【0138】

次に、図18(a)に示す断面構造を得るまでの工程について説明する。

【0139】

まず、第2絶縁膜41の上面と、第3、第4ホール41a、41bのそれぞれの内面に、スパッタ法によりバリアメタル膜として窒化チタン膜を約50nmの厚さに形成する。そして、このバリアメタル膜の上に、第3、第4ホール41a、41bを埋め込むのに十分な厚さ、例えば第2絶縁膜41の平坦面上での厚さが300nmとなるタングステン膜を形成する。

【0140】

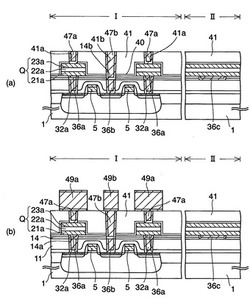

その後に、第2絶縁膜41上の余分なバリアメタル膜とタングステン膜とをCMP法により研磨して除去し、これらの膜を第3、第4ホール41a、41b内にそれぞれ第3、第4導電性プラグ47a、47bとして残す。

【0141】

これらの導電性プラグのうち、第3導電性プラグ47aは上部電極23aと電気的に接続される。そして、第4導電性プラグ47bは、第2導電性プラグ36bと電気的に接続され、その第2導電性プラグ36bと共にビット線の一部を構成する。

【0142】

次に、図18(b)に示す断面構造を得るまでの工程について説明する。

【0143】

まず、第2絶縁膜41と第3、第4導電性プラグ47a、47bのそれぞれの上面に、スパッタ法により金属積層膜を形成する。その金属積層膜は、例えば、厚さ約50nmの窒化チタン膜、厚さ約360nmのアルミニウム膜、及び厚さ約70nmの窒化チタン膜をこの順に積層してなる。

【0144】

その後に、フォトリソグラフィによりこの金属積層膜をパターニングして、第3、第4導電性プラグ47a、47bのそれぞれと電気的に接続される一層目金属配線49aとビット線用金属パッド49bとを形成する。

【0145】

この後は、一層目金属配線49aと金属パッド49bの上に第3絶縁膜を形成する工程に移るが、その詳細については省略する。

【0146】

ここまでの工程により、本実施形態に係る半導体装置の基本構造が完成した。

【0147】

以上説明した半導体装置の製造方法によれば、図18(b)に示したように、キャパシタQの直下の導電性プラグを、第1導電性プラグ12aと補助導電性プラグ36aとに分割する。

【0148】

その補助導電性プラグ36aが埋め込まれる第1開口14aは、第1絶縁膜11よりも薄い酸化防止絶縁膜14に形成されるので、図11(a)の工程で第1開口14aを形成する際のエッチング量は少なくて済む。そのため、エッチングによる第3レジストパターン33の膜減りを低減することができ、第3レジストパターン33をマスクにしたエッチングで第1開口14aを精度良く形成することができる。

【0149】

更に、本実施形態では、上記の第1開口14aと同じプロセスにより、酸化防止絶縁膜14にアライメントマーク用開口14cを形成するので、このアライメントマーク用開口14cの深さも第1開口14aと同様に浅くすることができる。その結果、図11(b)に示したように、アライメントマーク14cを完全に埋め込むのに必要な導電膜36の膜厚を、図7(a)に示したタングステン膜18よりも薄くすることができ、図11(c)のCMP工程におけるタングステン膜18のオーバー研磨量を少なくすることができる。従って、このCMP工程では、補助導電性プラグ36aの上面にリセスが殆ど発生しないと共に、酸化防止絶縁膜14と絶縁性密着膜15のディッシングも抑制することができる。

【0150】

これらにより、本実施形態では、上面が平坦な補助導電性プラグ36a上に下部電極21aが形成されるので、下地の凹凸に起因する配向性の劣化が下部電極21aに発生し難くなり、良好な配向性を持った下部電極21aによりその上のキャパシタ誘電体膜22aの配向性を高めることができ、キャパシタ誘電体膜22aの強誘電体特性が向上された高品位なFeRAMを提供することが可能になる。

【0151】

しかも、上記のように酸化防止絶縁膜14にディッシングが発生しないので、プロセス中常に酸化防止絶縁膜14の酸素透過防止能力を維持することができ、ビット線の一部を構成する第2導電性プラグ36bが酸化してコンタクト不良を引き起こすのを防ぐことができる。

【0152】

なお、上記では、図17(a)を用いて説明したように、第4ホール41bと第2開口14bとを同時に形成し、その後にキャパシタ誘電体膜22aに対して二回目の回復アニールを行ったが、本発明はこれに限定されない。

【0153】

例えば、図17(a)の工程において、酸化防止絶縁膜14をエッチングストッパ膜にしながら第4ホール41bを形成し、第2導電性プラグ36bが酸化防止絶縁膜14で覆われた状態で上記の回復アニールを行ってもよい。その場合は、回復アニールを終了した後に、第4ホール41b下の酸化防止絶縁膜14をエッチングすることにより第2開口14bを形成する。

【0154】

(3)第2実施形態

上記した第1実施形態では、図11(b)、(c)で説明したように、第2バリアメタル膜35と導電膜36との積層膜で補助導電性プラグ36aを構成した。これに対し、本実施形態では、導電膜36のみで補助導電性プラグ36aを構成する。

【0155】

図19(a)〜図19(c)は、本発明の第2実施形態に係る半導体装置の製造途中の断面図である。なお、これらの図において、第1実施形態で説明した要素には第1実施形態と同じ符号を付し、以下ではその説明を省略する。

【0156】

本実施形態に係る半導体装置を作成するには、まず、第1実施形態で説明した図9(a)〜図11(a)の工程を行う。

【0157】

その後、図19(a)に示すように、絶縁性密着膜15の上面と各開口14a、14cのそれぞれの中に単層の導電膜36を形成し、その導電膜36で各開口14a、14cを完全に埋め込む。

【0158】

その導電膜36の構成材料は特に限定されないが、本実施形態では、窒化チタン膜と窒化チタンアルミニウム膜のいずれかの単層膜をスパッタ法により導電膜36として形成する。導電膜36としてスパッタ法により窒化チタンアルミニウム膜を形成する場合は、例えば、チタンを5%含むアルミニウムターゲットを用い、且つ、窒素とアルゴンとの混合ガスをスパッタガスとして使用することで、ターゲット中のチタンを気相中で窒化して窒化チタンアルミニウム膜を得る。

【0159】

次いで、図19(b)に示すように、絶縁性密着膜15を研磨ストッパとして使用しながら、その絶縁性密着膜15上の余分な導電膜36をCMP法により研磨して除去する。そのCMPでは、スラリーとして例えばCabot Microelectronics Corporation製のW2000が採用される。

【0160】

これにより、第1開口14aに導電膜36が補助導電性プラグ36aとして残されると共に、アライメント用開口14c内の導電膜36がアライメントマーク36cとされる。

【0161】

その後は、第1実施形態で説明した図12(a)〜図18(b)の工程を行うことで、図19(c)に示すように、キャパシタQを備えた半導体装置を完成させる。

【0162】

上記した本実施形態によれば、補助導電性プラグ36aが、タングステンよりも酸化し難い窒化チタン膜や窒化チタンアルミニウム膜の単層膜で構成されるので、補助導電性プラグ36aにタングステンを採用する第1実施形態と比較してプラグ36aの耐熱性が向上し、アニール等の熱プロセスを行う場合でも補助導電性プラグ36aのコンタクト特性を安定化させることが可能となる。

【0163】

以下に、本発明の特徴を付記する。

【0164】

(付記1) 半導体基板と、

前記半導体基板の表層に間隔をおいて形成された第1、第2不純物拡散領域と、

前記半導体基板上に形成され、前記第1、第2不純物拡散領域のそれぞれの上に第1、第2ホールを備えた第1絶縁膜と、

前記第1、第2ホール内にそれぞれ形成され、前記第1、第2不純物拡散領域のそれぞれと電気的に接続された第1、第2導電性プラグと、

前記第1絶縁膜の上に形成され、前記第1、第2導電性プラグのそれぞれの上に第1、第2開口を備えた酸化防止絶縁膜と、

前記第1開口内に形成された補助導電性プラグと、

前記補助導電性プラグ上、及び前記第1開口の周囲の前記酸化防止絶縁膜上に、下部電極、キャパシタ誘電体膜、及び上部電極を順に形成してなるキャパシタと、

前記キャパシタを覆うと共に、前記上部電極の上に第3ホールを備え、且つ前記第2開口の上に第4ホールを備えた第2絶縁膜と、

前記第3ホール内に形成され、前記上部電極と電気的に接続された第3導電性プラグと、

前記第4ホール内と前記第2開口内とに形成され、前記第2導電性プラグと電気的に接続された第4導電性プラグと、

を有することを特徴とする半導体装置。

【0165】

(付記2) 前記下部電極は配向性金属膜で構成されることを特徴とする付記1に記載の半導体装置。

【0166】

(付記3) 前記配向性金属膜は、イリジウムで構成されることを特徴とする付記2に記載の半導体装置。

【0167】

(付記4) 前記酸化防止絶縁膜は、前記第1絶縁膜よりも薄いことを特徴とする付記1に記載の半導体装置。

【0168】

(付記5) 前記第1導電性プラグと前記第2導電性プラグのそれぞれの上面の高さは同じ高さであることを特徴とする付記1に記載の半導体装置。

【0169】

(付記6) 前記補助導電性プラグは、バリアメタル膜とタングステン膜との積層膜、窒化チタン膜の単層膜、及び窒化チタンアルミニウム膜の単層膜のいずれかで構成されることを特徴とする付記1に記載の半導体装置の製造方法。

【0170】

(付記7) 前記酸化防止絶縁膜は、酸窒化シリコン膜、窒化シリコン膜、及びアルミナ膜のいずれかであることを特徴とする付記1に記載の半導体装置。

【0171】

(付記8) 前記酸化防止絶縁膜上に絶縁性密着膜が形成され、該絶縁性密着膜上に前記下部電極と前記第2絶縁膜とが形成されたことを特徴とする付記1に記載の半導体装置。

【0172】

(付記9) 前記第2導電性プラグと前記4導電性プラグは、ビット線の一部を構成することを特徴とする付記1に記載の半導体装置。

【0173】

(付記10) 前記第1、第2不純物拡散領域の間の前記半導体基板上に形成されたゲート絶縁膜と、

前記ゲート絶縁膜上に形成され、ワード線の一部を構成するゲート電極とを有することを特徴とする付記1に記載の半導体装置。

【0174】

(付記11) 半導体基板の表層に互いに間隔をおいて第1、第2不純物拡散領域を形成する工程と、

前記半導体基板上に第1絶縁膜を形成する工程と、

前記第1絶縁膜をパターニングして、前記第1、第2不純物拡散領域上の該第1絶縁膜にそれぞれ第1、第2ホールを形成する工程と、

前記第1、第2ホール内に、前記第1、第2不純物拡散領域のそれぞれと電気的に接続される第1、第2導電性プラグを形成する工程と、

前記第1絶縁膜上と前記第1、第2導電性プラグ上とに酸化防止絶縁膜を形成する工程と、

前記酸化防止絶縁膜をパターニングして、前記第1導電性プラグの上の該酸化防止絶縁膜に第1開口を形成する工程と、

前記酸化防止絶縁膜上と前記第1開口内とに導電膜を形成する工程と、

前記導電膜を研磨することにより、前記酸化防止絶縁膜上から該導電膜を除去すると共に、前記第1開口内に前記導電膜を補助導電性プラグとして残す工程と、

前記補助導電性プラグ上、及び前記第1開口の周囲の前記酸化防止絶縁膜上に、下部電極、キャパシタ誘電体膜、及び上部電極を順に積層してキャパシタを形成する工程と、

前記キャパシタを覆う第2絶縁膜を形成する工程と、

前記第2絶縁膜をパターニングすることにより、前記上部電極と前記第2ホールのそれぞれの上の前記第2絶縁膜に第3、第4ホールを形成すると共に、前記第4ホールの下の前記酸化防止絶縁膜に第2開口を形成する工程と、

前記第3ホール内に、前記上部電極と電気的に接続される第3導電性プラグを形成する工程と、

前記第4ホール内と前記第2開口内とに、前記第2導電性プラグと電気的に接続される第4導電性プラグを形成する工程と、

を有することを特徴とする半導体装置の製造方法。

【0175】

(付記12) 前記酸化防止絶縁膜を形成する工程において、前記第1絶縁膜よりも薄い厚さに前記酸化防止絶縁膜を形成することを特徴とする付記11に記載の半導体装置の製造方法。

【0176】

(付記13) 前記導電膜を形成する工程において、バリアメタル膜とタングステン膜との積層膜、窒化チタン膜の単層膜、及び窒化チタンアルミニウム膜の単層膜のいずれかを前記導電膜として形成することを特徴とする付記11に記載の半導体装置の製造方法。

【0177】

(付記14) 酸化防止絶縁膜を形成する工程において、酸窒化シリコン膜、窒化シリコン膜、及びアルミナ膜のいずれかを前記酸化防止絶縁膜として形成することを特徴とする付記11に記載の半導体装置の製造方法。

【0178】

(付記15) 前記酸化防止絶縁膜を形成した後に、該酸化防止絶縁膜上に絶縁性密着膜を形成する工程を有し、

前記絶縁性密着膜上に、前記下部電極と前記第2絶縁膜とを形成することを特徴とする付記11に記載の半導体装置の製造方法。

【0179】

(付記16) 前記第4ホールを形成した後に、酸素雰囲気中において前記キャパシタ誘電体膜をアニールし、その後に前記第2開口を形成することを特徴とする付記11に記載の半導体装置の製造方法。

【図面の簡単な説明】

【0180】

【図1】図1(a)〜(c)は、仮想的な半導体装置の製造途中の断面図(その1)である。

【図2】図2(a)〜(c)は、仮想的な半導体装置の製造途中の断面図(その2)である。

【図3】図3(a)〜(c)は、仮想的な半導体装置の製造途中の断面図(その3)である。

【図4】図4(a)、(b)は、仮想的な半導体装置の製造途中の断面図(その4)である。

【図5】図5(a)、(b)は、仮想的な半導体装置の製造途中の断面図(その5)である。

【図6】図6(a)、(b)は、仮想的な半導体装置の製造途中の断面図(その6)である。

【図7】図7(a)、(b)は、アライメント用開口をタングステン膜で完全に埋め込む場合の仮想的な半導体装置の製造途中の断面図(その1)である。

【図8】図8は、アライメント用開口をタングステン膜で完全に埋め込む場合の仮想的な半導体装置の製造途中の断面図(その2)である。

【図9】図9(a)〜(c)は、本発明の第1実施形態に係る半導体装置の製造途中の断面図(その1)である。

【図10】図10(a)〜(c)は、本発明の第1実施形態に係る半導体装置の製造途中の断面図(その2)である。

【図11】図11(a)〜(c)は、本発明の第1実施形態に係る半導体装置の製造途中の断面図(その3)である。

【図12】図12(a)、(b)は、本発明の第1実施形態に係る半導体装置の製造途中の断面図(その4)である。

【図13】図13(a)、(b)は、本発明の第1実施形態に係る半導体装置の製造途中の断面図(その5)である。

【図14】図14(a)、(b)は、本発明の第1実施形態に係る半導体装置の製造途中の断面図(その6)である。

【図15】図15(a)、(b)は、本発明の第1実施形態に係る半導体装置の製造途中の断面図(その7)である。

【図16】図16(a)、(b)は、本発明の第1実施形態に係る半導体装置の製造途中の断面図(その8)である。

【図17】図17(a)、(b)は、本発明の第1実施形態に係る半導体装置の製造途中の断面図(その9)である。

【図18】図18(a)、(b)は、本発明の第1実施形態に係る半導体装置の製造途中の断面図(その10)である。

【図19】図19(a)〜(c)は、本発明の第2実施形態に係る半導体装置の製造途中の断面図である。

【符号の説明】

【0181】

1…シリコン基板、2…素子分離絶縁膜、3…pウェル、4…ゲート絶縁膜、5…ゲート電極、6a、6b…第1、第2ソース/ドレインエクステンション、7…絶縁性サイドウォール、8a、8b…第1、第2ソース/ドレイン領域、9…高融点金属シリサイド層、10…カバー絶縁膜、11…第1絶縁膜、11a、11b…第1、第2ホール、11c…第1コンタクトホール、11e…アライメントマーク用開口、13c…第1コンタクトプラグ、14…酸化防止絶縁膜、15…絶縁性密着膜、16…第1レジストパターン、17…バリアメタル膜、18…タングステン膜、19…第2コンタクトプラグ、20…アライメントマーク、21…下部電極用導電膜、21a…下部電極、22…強誘電体膜、22a…キャパシタ誘電体膜、23…上部電極用導電膜、23a…上部電極、25…第1マスク材料層、26…第2マスク材料層、26a…ハードマスク、27…フォトレジスト、27a…キャパシタ用レジストパターン、30…第2レジストパターン、30a、30b…第1、第2窓、31…第1バリアメタル膜、32…タングステン膜、32a、32b…第1、第2導電性プラグ、14a、14b…第1、第2開口、14c…アライメントマーク用開口、33…第3レジストパターン、33a…第3窓、33b…第4窓、35…第2バリアメタル膜、36…導電膜、36a…補助導電性プラグ、36c…アライメントマーク、40…キャパシタ保護絶縁膜、41…第2絶縁膜、41a…第3ホール、42…犠牲絶縁膜、43…第4レジストパターン、43a…第5窓、45…第5レジストパターン、45a…第6窓、47a、47b…第3、第4導電性プラグ、49a…一層目金属配線、49b…ビット線用金属パッド。

【技術分野】

【0001】

本発明は、半導体装置とその製造方法に関する。

【背景技術】

【0002】

電源を切っても情報を記憶することができる不揮発性メモリとして、フラッシュメモリや強誘電体メモリが知られている。

【0003】

このうち、フラッシュメモリは、絶縁ゲート型電界効果トランジスタ(IGFET)のゲート絶縁膜中に埋め込んだフローティングゲートを有し、記憶情報を表す電荷をこのフローティングゲートに蓄積することによって情報を記憶する。しかし、このようなフラッシュメモリでは、情報の書き込みや消去の際に、ゲート絶縁膜にトンネル電流を流す必要があり、比較的高い電圧が必要であるという欠点がある。

【0004】

これに対し、強誘電体メモリは、FeRAM(Ferroelectric Random Access Memory)とも呼ばれ、強誘電体キャパシタが備える強誘電体膜のヒステリシス特性を利用して情報を記憶する。その強誘電体膜は、キャパシタの上部電極と下部電極の間に印加される電圧に応じて分極を生じ、その電圧を取り去っても自発分極が残留する。印加電圧の極性を反転すると、この自発分極も反転し、その自発分極の向きを「1」と「0」に対応させることで、強誘電体膜に情報が書き込まれる。この書き込みに必要な電圧はフラッシュメモリにおけるよりも低く、また、フラッシュメモリよりも高速で書き込みができるという利点がFeARMにはある。

【0005】

FeRAMは、その構造によりスタック型とプレーナ型とに大別される。後者のプレーナ型では、半導体基板に形成されたMOSトランジスタとキャパシタ下部電極とが、キャパシタの上方の金属配線を介して電気的に接続され、キャパシタの平面形状が大きくなり易い傾向がある。

【0006】

これに対し、スタック型のFeRAMでは、MOSトランジスタのソース/ドレイン領域に繋がる導電性プラグの直上にキャパシタ下部電極が形成され、その導電性プラグを介して下部電極とMOSトランジスタとが電気的に接続される。このような構造によれば、プレーナ型と比較してキャパシタの平面形状を小さくすることができ、今後求められるFeRAMの微細化に有利となる。

【0007】

そのような微細化が可能となるには、キャパシタ直下の導電性プラグが埋め込まれる開口を精度良く形成する必要があるので、その開口の加工精度をいかにして高めるかが微細化を進めるための重要な要素となる。

【0008】

なお、上記したスタック型のFeRAMについては、下記の特許文献1、2にその一例が開示されている。

【特許文献1】特開2001−358311号公報

【特許文献2】特開2003−68993号公報

【発明の開示】

【発明が解決しようとする課題】

【0009】

本発明の目的は、キャパシタ直下の導電性プラグが埋め込まれる開口の加工精度を高めることが可能な半導体装置とその製造方法を提供することにある。

【課題を解決するための手段】

【0010】

本発明の一観点によれば、半導体基板と、前記半導体基板の表層に間隔をおいて形成された第1、第2不純物拡散領域と、前記半導体基板上に形成され、前記第1、第2不純物拡散領域のそれぞれの上に第1、第2ホールを備えた第1絶縁膜と、前記第1、第2ホール内にそれぞれ形成され、前記第1、第2不純物拡散領域のそれぞれと電気的に接続された第1、第2導電性プラグと、前記第1絶縁膜の上に形成され、前記第1、第2導電性プラグのそれぞれの上に第1、第2開口を備えた酸化防止絶縁膜と、前記第1開口内に形成された補助導電性プラグと、前記補助導電性プラグ上、及び前記第1開口の周囲の前記酸化防止絶縁膜上に、下部電極、キャパシタ誘電体膜、及び上部電極を順に形成してなるキャパシタと、前記キャパシタを覆うと共に、前記上部電極の上に第3ホールを備え、且つ前記第2開口の上に第4ホールを備えた第2絶縁膜と、前記第3ホール内に形成され、前記上部電極と電気的に接続された第3導電性プラグと、前記第4ホール内と前記第2開口内とに形成され、前記第2導電性プラグと電気的に接続された第4導電性プラグと、を有する半導体装置が提供される。

【0011】

また、本発明の別の観点によれば、半導体基板の表層に互いに間隔をおいて第1、第2不純物拡散領域を形成する工程と、前記半導体基板上に第1絶縁膜を形成する工程と、前記第1絶縁膜をパターニングして、前記第1、第2不純物拡散領域上の該第1絶縁膜にそれぞれ第1、第2ホールを形成する工程と、前記第1、第2ホール内に、前記第1、第2不純物拡散領域のそれぞれと電気的に接続される第1、第2導電性プラグを形成する工程と、前記第1絶縁膜上と前記第1、第2導電性プラグ上とに酸化防止絶縁膜を形成する工程と、前記酸化防止絶縁膜をパターニングして、前記第1導電性プラグの上の該酸化防止絶縁膜に第1開口を形成する工程と、前記酸化防止絶縁膜上と前記第1開口内とに導電膜を形成する工程と、前記導電膜を研磨することにより、前記酸化防止絶縁膜上から該導電膜を除去すると共に、前記第1開口内に前記導電膜を補助導電性プラグとして残す工程と、前記補助導電性プラグ上、及び前記第1開口の周囲の前記酸化防止絶縁膜上に、下部電極、キャパシタ誘電体膜、及び上部電極を順に積層してキャパシタを形成する工程と、前記キャパシタを覆う第2絶縁膜を形成する工程と、前記第2絶縁膜をパターニングすることにより、前記上部電極と前記第2ホールのそれぞれの上の前記第2絶縁膜に第3、第4ホールを形成すると共に、前記第4ホールの下の前記酸化防止絶縁膜に第2開口を形成する工程と、前記第3ホール内に、前記上部電極と電気的に接続される第3導電性プラグを形成する工程と、前記第4ホール内と前記第2開口内とに、前記第2導電性プラグと電気的に接続される第4導電性プラグを形成する工程と、を有する半導体装置の製造方法が提供される。

【0012】

本発明によれば、酸化防止絶縁膜の第1開口内に補助導電性プラグを形成し、この補助導電性プラグとその下の第1導電性プラグにより、キャパシタの下部電極を第1不純物拡散領域に電気的に接続する。その第1開口は、酸化防止絶縁膜のみをパターニングして形成されるので、例えば酸化防止絶縁膜とその下の第1絶縁膜を一括してコンタクトホールを形成する場合と比較して、パターニングにおけるエッチング量を少なくすることができる。これにより、エッチングマスクとして使用されるレジストパターンがエッチングによって膜減りし難くなり、補助導電性プラグが形成される第1開口を精度良く形成することが可能となる。

【0013】

また、酸化防止絶縁膜に上記の第1開口を形成する工程において、該第1開口から間隔がおかれた部分の酸化防止絶縁膜にアライメント用開口を形成してもよい。その場合、第1開口内に導電膜を形成する工程においてアライメント用開口内にも導電膜を形成し、該導電膜を研磨する工程においてアライメント用開口内に導電膜をアライメントマークとして残す。

【0014】

このアライメントマーク用開口は酸化防止絶縁膜に形成されるので、その深さが上記の第1開口と同様に浅くなり、アライメント用開口を埋め込むのに必要な導電膜の厚さを薄くすることができる。従って、導電膜を研磨する工程において、研磨残を残さないためのオーバー研磨量を少なくすることができるので、過剰な研磨によって第1開口内の補助導電性プラグの上面にリセスが発生したり、酸化防止絶縁膜にディッシングが発生したりするのを防止できる。

【0015】

これにより、平坦性が良好に保たれた補助導電性プラグ上にキャパシタの下部電極が形成されるので、下地の凹凸によって下部電極の配向性が低下するのを抑止でき、配向性が良好に保たれた下部電極によりその上のキャパシタ誘電体膜の配向を高めることが可能となる。

【0016】

更に、上記のように酸化防止絶縁膜にディッシングが発生せず、酸素の透過を防止するのに必要な酸化防止絶縁膜の厚さを維持することができるので、酸化防止絶縁膜の下の第2導電性プラグを酸化雰囲気から確実に保護することができ、第2導電性プラグにコンタクト不良が発生するのを防ぐことができる。

【0017】

また、上記のアライメント用開口を完全に埋める厚さに導電膜を形成することで、研磨によりその導電膜をアライメント用開口内に残して得られるアライメントマークの上面に大きな凹部が形成されない。これにより、アライメントマーク上に形成される下部電極用導電膜に膜厚が薄い部分が形成されないので、酸素雰囲気中でキャパシタ誘電体膜に対してアニールを施しても、下部電極用導電膜によって酸素がブロックされ、酸素によってアライメントマークが酸化して飛散するのを防止することができる。

【発明の効果】

【0018】

本発明によれば、補助導電性プラグが埋め込まれる第1開口が酸化防止絶縁膜に形成されるため、パターニングによりその第1開口を形成する際のエッチング量を少なくすることができ、パターニング時のエッチングマスクがエッチングによって膜減りするのが防止され、第1開口の加工精度を高めることが可能となる。

【0019】

更に、上記の第1開口と同時に酸化防止絶縁膜にアライメントマーク用開口を形成する場合でも、アライメント用開口を埋め込むのに必要な導電膜の厚さを薄くできるので、その導電膜に対するオーバー研磨量を低減できる。これにより、補助導電性プラグと酸化防止絶縁膜のそれぞれの上面の平坦性が向上するので、キャパシタの下部電極の配向性を高めることができると共に、酸化防止絶縁膜の下の第2導電性プラグを酸化雰囲気から確実に保護することができる。

【発明を実施するための最良の形態】

【0020】

以下に、本発明の実施の形態について、添付図面を参照しながら詳細に説明する。

【0021】

(1)予備的事項の説明

本実施形態の説明に先立ち、本発明の予備的事項について説明する。

【0022】

図1〜図6は、仮想的な半導体装置の製造途中の断面図である。なお、これらの図では、強誘電体キャパシタが形成されるセル領域Iと、スクライブ領域等の周辺領域IIとを併記してある。

【0023】

この半導体装置は、スタック型のFeRAMであり、以下のようにして作成される。

【0024】

最初に、図1(a)に示す断面構造を得るまでの工程について説明する。

【0025】

まず、n型又はp型のシリコン(半導体)基板1表面に、トランジスタの活性領域を画定するSTI(Shallow Trench Isolation)用の溝を形成し、その中に酸化シリコン等の絶縁膜を埋め込んで素子分離絶縁膜2とする。なお、素子分離構造はSTIに限られず、LOCOS(Local Oxidation of Silicon)法で素子分離絶縁膜2を形成してもよい。

【0026】

次いで、シリコン基板1の活性領域にp型不純物を導入してpウェル3を形成した後、その活性領域の表面を熱酸化することにより、ゲート絶縁膜4となる熱酸化膜を形成する。

【0027】

続いて、シリコン基板1の上側全面に非晶質又は多結晶のシリコン膜を形成し、これらの膜をフォトリソグラフィによりパターニングして二つのゲート電極5を形成する。

【0028】

pウェル3上には、上記の2つのゲート電極5が間隔をおいて平行に配置され、それらのゲート電極5はワード線の一部を構成する。

【0029】

次いで、ゲート電極5をマスクにするイオン注入により、ゲート電極5の横のシリコン基板1にn型不純物を導入し、第1、第2ソース/ドレインエクステンション6a、6bを形成する。

【0030】

その後に、シリコン基板20の上側全面に絶縁膜を形成し、その絶縁膜をエッチバックしてゲート電極5の横に絶縁性サイドウォール7を形成する。その絶縁膜として、例えばCVD法により酸化シリコン膜を形成する。

【0031】

続いて、絶縁性サイドウォール7とゲート電極5をマスクにしながら、シリコン基板1にn型不純物を再びイオン注入することにより、二つのゲート電極5の側方のシリコン基板1の表層に、互いに間隔がおかれた第1、第2ソース/ドレイン領域(第1、第2不純物拡散領域)8a、8bを形成する。

【0032】

ここまでの工程により、シリコン基板1の活性領域には、ゲート絶縁膜4、ゲート電極5、及び第1、第2ソース/ドレイン領域8a、8bによって構成される第1、第2MOSトランジスタTR1、TR2が形成されたことになる。

【0033】

次に、シリコン基板1の上側全面に、スパッタ法によりコバルト層等の高融点金属層を形成した後、この高融点金属層を加熱してシリコンと反応させ、シリコン基板1上に高融点金属シリサイド層9を形成する。その高融点金属シリサイド層9はゲート電極5の表層部分にも形成され、それによりゲート電極5が低抵抗化されることになる。

【0034】

その後、素子分離絶縁膜2の上等で未反応となっている高融点金属層をウエットエッチングして除去する。

【0035】

続いて、プラズマCVD法により、シリコン基板1の上側全面に窒化シリコン(SiN)膜を厚さ約80nmに形成し、それをカバー絶縁膜10とする。次いで、このカバー絶縁膜10の上に、TEOSガスを使用するプラズマCVD法により第1絶縁膜11として酸化シリコン膜を厚さ約11000nmに形成する。

【0036】

次いで、図1(b)に示すように、上記の第1絶縁膜11の上面をCMP(Chemical Mechanical Polishing)法により研磨して平坦化する。このCMPの結果、第1絶縁膜11の厚さは、シリコン基板20の平坦面上で約800nmとなる。

【0037】

そして、図1(c)に示すように、フォトリソグラフィによりカバー絶縁膜10と第1絶縁膜11とをパターニングして、二つのゲート電極5の間の第2ソース/ドレイン領域8bの上に第1コンタクトホール11cを形成する。

【0038】

次に、図2(a)に示すように、第2ソース/ドレイン領域8bと電気的に接続される第1コンタクトプラグ13cを第1コンタクトホール11c内に形成する。その第1コンタクトプラグ13cは、タングステンで主に構成されるが、タングステンは非常に酸化され易く、プロセス中で酸化されるとコンタクト不良を引き起こす。

【0039】

そこで、次の工程では、図2(b)に示すように、第1コンタクトプラグ13cを酸化雰囲気から保護するための酸化防止絶縁膜14として、プラズマCVD法により酸窒化シリコン(SiON)膜を厚さ約130nmに形成する。

【0040】

その後に、プラズマCVD法により酸化防止絶縁膜14上に酸化シリコン膜を厚さ約200nmに形成し、その酸化シリコン膜を絶縁性密着膜15とする。

【0041】

続いて、図2(c)に示すように、絶縁性密着膜15上にフォトレジストを塗布し、それを露光、現像することにより第1レジストパターン16を形成する。その第1レジストパターン16は、セル領域Iにおいて第1ソース/ドレイン領域8a上にホール形状の第1窓16aを有すると共に、周辺領域IIにおいて幅の広い第2窓16bを有する。

【0042】

そして、これら第1、第2窓16a、16bを通じてカバー絶縁膜10、第1絶縁膜11、酸化防止絶縁膜14、及び絶縁性密着膜15をRIE(Reactive Ion Etching)でエッチングすることにより、セル領域Iにおけるこれらの絶縁膜に第2コンタクトホール11dを形成すると共に、周辺領域IIにアライメントマーク用開口11eを形成する。

【0043】

これらのうち、開口11eは、後述のキャパシタを形成するためのフォトリソグラフィの際、露光装置(不図示)とシリコン基板1との位置合わせを行うのに使用される。

【0044】

ここで、第2コンタクトホール11dは、酸化防止絶縁膜14と絶縁性密着膜15の厚さにより、その深さが既述の第1コンタクトホール11cよりも深くなる。そのため、このエッチング工程におけるエッチング量は第1コンタクトホール11cのそれよりも多くなり、RIEのエッチング雰囲気中に第1レジストパターン16が長時間曝される。その結果、図示のように、エッチングの最中に第1レジストパターン16が膜減りし、エッチングが終了する頃にはエッチングマスクとなる第1レジストパターン16の残厚が極めて薄くなるので、上記のように深い第2コンタクトホール11dを精度良く形成するのは難しい。このような問題は、第1レジストパターン16の膜厚を薄くする必要のある微細な直径の第2コンタクトホール11dを形成する場合に特に顕著に見られる。

【0045】

その後に、第1レジストパターン16は除去される。

【0046】

次いで、図3(a)に示すように、スパッタ法によりシリコン基板1の上側全面にバリアメタル膜17としてチタン膜と窒化チタン膜とをこの順に形成する。なお、窒化チタン膜についてはCVD法で形成してもよい。そのバリアメタル膜17は、上記した第2コンタクトホール11dと開口11eのそれぞれの内面にも形成される。

【0047】

次に、図3(b)に示すように、上記のバリアメタル膜17上にタングステン膜18を形成し、そのタングステン膜18で第2コンタクトホール11dを完全に埋め込む。

【0048】

タングステン膜18は、アライメントマーク用の開口11e内にも形成されるが、本来はその厚さは第2コンタクトホール11dを埋める程度で十分なため、この例では第2コンタクトホール11dを埋めるのに必要な最低限の厚さでタングステン膜18を形成する。このようにすると、第2コンタクトホール11dよりも幅が広い開口11eは、図示のようにタングステン膜18によって完全には埋め込まれないことになる。

【0049】

その後に、図3(c)に示すように、絶縁性密着膜15上の余分なバリアメタル膜17とタングステン膜18とをCMP法により研磨して除去し、これらの膜を第2コンタクトホール11dと開口11e内にのみ残す。このようにして第2コンタクトホール11d内に残されたバリアメタル膜17とタングステン膜18は第2コンタクトプラグ19として使用され、周辺領域IIの開口11e内に残されたこれらの膜はアライメントマーク20とされる。

【0050】

次いで、図4(a)に示すように、スパッタ法によりイリジウム膜を約50〜200nmの厚さ、例えば100nmに形成し、それを下部電極用導電膜21とする。

【0051】

更に、MOCVD(Metal Organic CVD)法により、下部電極用導電膜21上に強誘電体膜22としてPZT(Lead Zirconate Titanate: PbZrTiO3)膜を厚さ約50〜150nm、例えば100nmに形成する。

【0052】

その後、この強誘電体膜22上にスパッタ法により酸化イリジウム(IrO2)膜を50〜200nm、例えば100nmの厚さに形成し、それを上部電極用導電膜23とする。

【0053】

このようにして積層された下部電極用導電膜21、強誘電体膜22、及び上部電極用導電膜23は、後でパターニングされてそれぞれキャパシタ下部電極、キャパシタ誘電体膜、及びキャパシタ上部電極とされる。

【0054】

次に、図4(b)に示すように、上部電極用導電膜23上に第1マスク材料層25としてスパッタ法により窒化チタン膜を厚さ約200nmに形成した後、更にその上にCVD法により酸化シリコン膜を約600nmの厚さに形成し、それを第2マスク材料層26とする。

【0055】

その後に、第2マスク材料層26上にフォトレジスト27を塗布する。

【0056】

次に、図5(a)に示す断面構造を得るまでの工程について説明する。

【0057】

まず、不図示のステッパ等の露光装置内にシリコン基板1を入れる。そして、アライメント用開口11eに起因して第2マスク材料層26の表面に形成される凹部を光学的に検出し、露光装置とシリコン基板1との位置合わせを行う。続いて、この露光装置内でフォトレジスト27を露光した後に、それを現像することで、セル領域Iにおいてキャパシタ平面形状を有するキャパシタ用レジストパターン27aを形成する。また、そのキャパシタ用レジストパターン27aは、周辺領域Iにおいて、アライメントマーク用の開口11eを上方から覆う。

【0058】

次に、図5(b)に示す断面構造を得るまでの工程について説明する。

【0059】

まず、キャパシタ用レジストパターン27aをマスクにして第2マスク材料膜26をエッチングすることによりハードマスク26aを形成する。

【0060】

そして、キャパシタ用レジストパターン27aを除去した後に、ハードマスク26aをマスクにして第1ハードマスク層25をエッチングし、その第1マスク材料層25をハードマスク26aの下にのみ残す。

【0061】

続いて、図6(a)に示すように、ハードマスク26aをエッチングマスクにしながら、下部電極用導電膜21、強誘電体膜22、及び上部電極用導電膜23を一括してエッチングする。これにより、第2コンタクトプラグ19上には、下部電極21a、キャパシタ誘電体膜22a、及び上部電極23aをこの順に積層してなるキャパシタQが形成されたことになる。

【0062】

なお、周辺領域IIでは、下部電極用導電膜21、強誘電体膜22、及び上部電極用導電膜23はエッチングされず、ハードマスク26aの下に残存する。

【0063】

続いて、図6(b)に示すように、ハードマスク26aと第1マスク材料層25とをウエットエッチングとドライエッチングにより除去する。

【0064】

その後に、キャパシタQを形成する際のエッチングやスパッタによってキャパシタ誘電体膜22aが受けたダメージを回復させるため、酸素雰囲気中でキャパシタQをアニールする。そのようなアニールは、回復アニールとも呼ばれる。

【0065】

ところで、上記の例では、コンタクトプラグ19を構成するタングステン膜18は、第2コンタクトホール11dを埋め込む最低限の厚さで形成されているため、第2コンタクトホール11dよりも幅が広い開口11eに対するタングステン膜18の埋め込みは不完全となっている。そのため、図6(b)に示されるように、開口11eには、キャパシタQの下部電極21aを構成する下部電極用導電膜21が残っており、上記の回復アニールの際の酸素がその下部電極用導電膜21に到達する。

【0066】

しかし、下部電極用導電膜21は、カバレッジの悪いスパッタ法によって形成されているので、その膜厚が開口11e内において不均一となっており、図示のような薄厚部21bが下部電極用導電膜21に発生し、その薄厚部21bからタングステン膜18に上記の酸素が侵入することになる。こうなると、他の金属に比べて非常に酸化され易いタングステン膜18が薄厚部21bの近くで酸化し、下部電極用導電膜21によって密閉された空間において酸化されたタングステンが膨張して、その膨張により下部電極用導電膜21、強誘電体膜22、及び上部電極用導電膜23のいずれかよりなる膜25が周囲に飛散する。その膜25は、デバイス不良を引き起こすと共に、後の工程で行われるフォトリソグラフィ工程におけるパターン不良の原因となるので、好ましくない。

【0067】

このような膜25の剥離を発生させないためには、周辺領域IIにおいて、タングステン膜18によって開口11eを完全に埋め込むことで、周辺領域IIに下部電極用導電膜21を残さないようにすることが考えられる。

【0068】

図7、図8は、このようにタングステン膜18で開口11eを完全に埋め込む場合の仮想的なFeRAMの製造途中の断面図である。なお、図7、図8において、図1〜図6で説明した要素にはこれらの図と同じ符号を付し、以下ではその説明を省略する。

【0069】

まず、上記で説明した図1(a)〜図3(a)の工程を行った後、図7(a)に示すように、バリアメタル膜17上にタングステン膜18を形成し、そのタングステン膜18で第2コンタクトホール11dと開口11eの両方を完全に埋め込む。このように、第2コンタクトホール11dだけでなく、それよりも幅の広い開口11eも埋め込むために、タングステン膜18の厚さは、上記の例(図3(b)参照)よりもかなり厚く、例えばシリコン基板1の平坦面上で約900nm程度の厚さにする必要がある。

【0070】

その後に、図7(b)に示すように、絶縁性密着層15上の余分なバリアメタル膜17とタングステン膜18とをCMP法により研磨して除去することにより、第2コンタクトホール11dと開口11eの中に残されたこれらの膜をそれぞれ第2コンタクトプラグ19、アライメントマーク20とする。

【0071】

ところで、そのCMPでは、第2コンタクトホール11dと開口11e以外にタングステン膜18とバリアメタル膜17を残さないために、これらの膜の合計膜厚よりも研磨量が多くなるようなオーバー研磨が施される。特に、この例のように研磨対象となるタングステン膜18が厚いほどCMP後に膜が残り易いので、上記のオーバー研磨の量は、タングステン膜18を薄くする先の例(図3(c)参照)よりも多く設定される。

【0072】

その結果、図7(b)に示されるように、絶縁性密着膜15や酸化防止絶縁膜14が不必要に研磨され、第1コンタクトプラグ13cの上のこれらの膜にディッシング(膜減り)が発生すると共に、第2コンタクトプラグ19も過剰に研磨されてその上面にリセス(窪み)が発生する。

【0073】

この後は、既述の図4(a)〜図6(b)の工程を行うことで、図8に示すようなキャパシタQを第2コンタクトプラグ19上に形成する。

【0074】

この例では、周辺領域IIの開口11eがタングステンよりなるアライメントマーク20によって完全に埋め込まれており、その上に下部電極用導電膜21が均一な厚さで形成されている。従って、酸素雰囲気中でキャパシタQに対して回復アニールを施しても、下部電極用導電膜21によって酸素の透過が阻止されるので、図6(b)のような膜25が発生せず、剥離した膜25に起因するパターン不良等の問題は回避できる。

【0075】

しかし、図7(b)で説明したように、タングステン膜18に対するCMP時のオーバー研磨量を多くしたことで、第1コンタクトプラグ13c上の酸化防止絶縁膜14にディッシングが発生する。これにより、キャパシタQの回復アニール時に、タングステンを主に構成される第1コンタクトプラグ13cを酸化防止絶縁膜14で酸素雰囲気から保護するのが難しくなり、第1コンタクトプラグ13cが酸化してコンタクト不良を引き起こす恐れが新たに発生する。

【0076】

しかも、上記のCMPにより、キャパシタQの直下の第2コンタクトプラグ19の上面にリセスが形成し、その上面の平坦性が低下する。このリセスに起因する平坦性の低下により下部電極21aにおけるイリジウムの配向性が低下する。キャパシタ誘電体膜22aの配向は、下部電極21aの配向に大きく依存するので、このように下部電極21aの配向性が低下すると、キャパシタ誘電体膜22aの配向性も低下し、ひいてはキャパシタ誘電体膜22aの強誘電体特性が劣化する。

【0077】

本願発明者はこのような問題点に鑑み、以下に説明するような本発明の実施の形態に想到した。

【0078】

(2)第1実施形態

図9〜図18は、本発明の第1実施形態に係る半導体装置の製造途中の断面図である。なお、これらの図において、図1〜図8で説明したのと同じ要素にはこれらの図と同じ符号を付し、以下ではその説明を省略する。

【0079】

この半導体装置はスタック型のFeRAMであり、以下のようにして作成される。

【0080】

まず、予備的事項で説明した図1(a)、(b)の工程を行った後に、図9(a)に示すように、第1絶縁膜11の上にフォトレジストを塗布し、それを露光、現像して第2レジストパターン30を形成する。

【0081】

図示のように、第1、第2ソース/ドレイン領域8a、8bの上方の第2レジストパターン30には、ホール形状の第1、第2窓30a、30bがそれぞれ形成される。

【0082】

続いて、図9(b)に示すように、周波数が13.56MHzでパワーが1kW〜2.5kWの高周波電力をエッチング雰囲気に印加すると共に、C4F8、Ar、及びO2の混合ガスをエッチングガスとして使用するRIEにより、上記の第1、第2窓30a、30bを通じて第1絶縁膜11とカバー絶縁膜10とをエッチングして、第1、第2ソース/ドレイン領域8a、8bのそれぞれの上に第1、第2ホール11a、11bを形成する。なお、上記のエッチング雰囲気の圧力は特に限定されないが、本実施形態では2〜7Paとする。

【0083】

このエッチングが終了後、第2レジストパターン30は除去される。

【0084】

次に、図9(c)に示す断面構造を得るまでの工程について説明する。

【0085】

まず、第1絶縁膜11の上面と、第1、第2ホール11a、11bの内面とに、スパッタ法によりチタン膜を厚さ約30nmに形成する。更に、このチタン膜の上に、四塩化チタンガス(TiCl4)を反応ガスとして使用するCVD法により、厚さが約20nmの窒化チタン膜を形成し、この窒化チタン膜と上記のチタン膜とを第1バリアメタル膜31とする。

【0086】

その後に、六フッ化タングステンガスを使用するCVD法を用いて、この第1バリアメタル膜31上にタングステン膜32を形成し、このタングステン膜32により第1、第2ホール11a、11bを完全に埋め込む。

【0087】

続いて、図10(a)に示すように、第1絶縁膜11が研磨ストッパとなるようなスラリー(研磨剤)、例えばCabot Microelectronics Corporation製のW2000を使用するCMP法により、第1絶縁膜11上の余分な第1バリアメタル膜31とタングステン膜32とを研磨して除去し、これらの膜を第1、第2ホール11a、11b内に第1、第2導電性プラグ32a、32bとして残す。

【0088】

このように、第1、第2導電性プラグ32a、32bは同じプロセスによって形成されるので、それらの上面の高さは同じになる。また、第1、第2ソース/ドレイン領域8a、8bは、それぞれ第1、第2導電性プラグ32a、32bと電気的に接続される。

【0089】

次いで、図10(b)に示すように、シラン(SiH4)とN2Oとを反応ガスとするプラズマCVD法により、第1、第2導電性プラグ32a、32bと第1絶縁膜11のそれぞれの上面に酸窒化シリコン膜を形成し、それを酸化防止絶縁膜14とする。その酸化防止絶縁膜14は、第1絶縁膜11よりも薄い厚さ、例えば約130nmの厚さに形成するのが好ましい。

【0090】

酸化防止絶縁膜14を構成する酸窒化シリコンは、他の絶縁膜に比べ、酸素の透過防止性に優れている。そのため、二つのゲート電極5の間に形成された酸化し易いタングステンで主に構成される第2導電性プラグ32bは、この酸化防止絶縁膜14によって酸化雰囲気から保護され、プロセス中に異常酸化してコンタクト不良を起こすのが防止される。

【0091】

このように酸素の透過を防止する機能を有する絶縁膜としては、上記の酸窒化シリコン膜の他に窒化シリコン(SiN)膜とアルミナ(Al2O3)膜があり、これらの膜を単層で酸化防止絶縁膜14として形成してもよい。その場合、窒化シリコン膜は、シランとアンモニアとを反応ガスとするプラズマCVD法によって形成される。また、アルミナ膜はスパッタ法によって形成される。

【0092】

その後に、上記の酸化防止絶縁膜14上に、絶縁性密着膜15として酸化シリコン膜を約200nmに形成する。この酸化シリコン膜の成膜方法は特に限定されないが、本実施形態ではTEOSガスを用いるプラズマCVD法によりこの酸化シリコン膜を形成する。

【0093】

続いて、図10(c)に示すように、絶縁性密着膜15上にフォトレジストを塗布し、それを露光、現像して第3レジストパターン33を形成する。この第3レジストパターン33は、第2導電性プラグ32aの上方にホール形状の第3窓33aを有すると共に、この第3窓33aよりも幅が広い第4窓33bを周辺領域IIに有する。

【0094】

その後に、図11(a)に示すように、上記の第3、第4窓33a、33bを通じてその下の絶縁性密着膜15と酸化防止絶縁膜14とをエッチングすることにより、各窓33a、33bの下の酸化防止絶縁膜14にそれぞれ第1開口14aとアライメントマーク用開口14cとを形成する。

【0095】

このときのエッチング条件は特に限定されないが、本実施形態では、C4F8、Ar、及びO2の混合ガスをエッチングガスとして使用するRIEを採用する。

【0096】

また、これにより形成された第1開口14aの深さは、酸化防止絶縁膜14と絶縁性密着膜15の合計膜厚に等しく約330nmとなるが、この値は第1、第2ホール11a、11bの深さ(約900nm)よりも浅く、この工程におけるエッチング量は図2(b)のそれよりも格段に少ない。よって、エッチングによる第3レジストパターン33の膜減りが図2(b)の場合よりも低減され、エッチング終了後にも第3レジストパターン33が厚く残存するので、第1開口14aを精度良く形成することができる。

【0097】

その後に、第3レジストパターン33は除去される。

【0098】

次に、図11(b)に示すように、絶縁性密着膜15の上面と各開口14a、14cの内面とに、第2バリアメタル膜35として窒化チタン膜を約50nmの厚さに形成する。

【0099】

ここで、既述のように、第1開口14aの深さが約330nmと浅いので、カバレッジに優れた高価なCVD法で第2バリアメタル膜35を形成する必要は無く、安価なスパッタ法により第2バリアメタル膜35を形成することができる。但し、第2バリアメタル膜35の成膜方法はスパッタ法に限定されず、CVD法で第2バリアメタル膜35を形成してもよい。

その後に、六フッ化タングステンガスを用いるCVD法により、この第2バリアメタル膜35の上に導電膜36としてタングステン膜を形成し、この導電膜36で上記の各開口14a、14cを完全に埋め込む。

【0100】

上記のようにアライメント用開口14cの深さが非常に浅いので、それを埋め込むのに必要な導電膜36の厚さは、図7(a)で説明したタングステン膜18の厚さよりも薄くて済み、本実施形態では絶縁性密着膜15の平坦面上で例えば約300nmとされる。

【0101】

続いて、図11(c)に示すように、絶縁性密着膜15を研磨ストッパにしながら、その絶縁性密着膜15上の余分な第2バリアメタル膜35と導電膜36とをCMP法により研磨して除去し、これらの膜を第1開口14aとアライメントマーク用開口14cの中にのみ残す。そのCMPにおけるスラリーとして、例えばCabot Microelectronics Corporation製のW2000を採用する。

【0102】

そして、このようにして残された第2バリアメタル膜35と導電膜36は、第1開口14a内において、第1導電性プラグ32aと電気的に接続される補助導電性プラグ36aとされると共に、アライメントマーク用開口14c内においてアライメントマーク36cとされる。

【0103】

ところで、このCMPにおいては、開口14a、14c以外の絶縁性密着膜15上に導電膜36や第2バリアメタル膜35を残さないために、研磨量をこれらの膜の合計の厚さよりも多くするオーバー研磨が行われる。

【0104】

但し、研磨の対象となる導電膜36の厚さが上記のように薄いので、絶縁性密着膜15上に研磨残を残さないためのオーバー研磨量を図7(b)の場合よりも少なくすることができ、過剰な研磨をしなくて済む。よって、上記のようにCMPを行っても、補助導電性プラグ36aの上面にリセスが発生したり、酸化防止絶縁膜14や絶縁性密着膜15にディッシングが発生したりすることが防止され、CMPを終了した後の絶縁性密着膜15と補助導電性プラグ36aの各上面の平坦性を極めて良好にすることができる。

【0105】

次に、図12(a)に示す断面構造を得るまでの工程について説明する。

【0106】

まず、スパッタ法により、補助導電性プラグ36aと絶縁性密着膜15のそれぞれの上に下部電極用導電膜21として配向性金属膜を形成する。配向性金属膜としては、例えばイリジウム膜がある。本実施形態では、そのうちのイリジウム膜を50〜200nmの厚さ、より好ましくは100nmの厚さに形成する。

【0107】

上記したように、絶縁性密着膜15と補助導電性プラグ36aの各上面の平坦性が良いので、下部電極用導電膜21の配向性が下地の凹凸によって低下するのが防がれ、その配向性を良好に保つことができる。

【0108】

次いで、強誘電体膜22として、PZT膜をMOCVD法により下部電極用導電膜21上に50〜150nmの厚さ、より好ましくは100nmの厚さに形成する。なお、強誘電体膜22の成膜方法としては、MOCVD法の他に、スパッタ法やゾル・ゲル法もある。更に、強誘電体膜22の材料は上記のPZTに限定されず、SrBi2Ta2O9、SrBi2(Ta, Nb)2O9等のBi層状構造化合物や、PZTにランタンをドープしたPLZT、或いはその他の金属酸化物強誘電体で強誘電体膜22を構成してもよい。

【0109】

その強誘電体膜22の配向性は、下地の下部電極用導電膜21の配向性に大きく依存するが、上記のように下部電極用導電膜21の配向性が良好なので、この強誘電体膜22の配向も高められる。

【0110】

その後に、強誘電体膜22の上に、スパッタ法により酸化イリジウム(IrO2)膜を50〜200nmの厚さ、より好ましくは100nmの厚さに形成し、それを上部電極用導電膜23とする。

【0111】

続いて、図12(b)に示すように、上部電極用導電膜23上に第1マスク材料層25としてスパッタ法により窒化チタン膜を厚さ約200nmに形成した後、更にその上にCVD法により酸化シリコン膜を約600nmの厚さに形成し、それを第2マスク材料層26とする。

【0112】

その後に、マスク材料層26上にフォトレジスト27を塗布する。

【0113】

ところで、補助導電性プラグ36aよりも幅が広いアライメントマーク36cの上面は、図11(c)のCMP工程におけるオーバー研磨によって、その周囲の絶縁性密着膜15の上面よりも若干低くなっている。その結果、図12(b)の工程を終了した後では、アライメントマーク36cに起因する浅い凹部(不図示)が周辺領域IIのマスク材料層26に形成されている。その凹部の深さは、典型的には約50〜100nm程度と浅い。

【0114】

このような凹部を利用することにより、次の図13(a)の工程では、まずステッパ等の露光装置(不図示)内にシリコン基板1を入れ、アライメントマーク36c上の上記の凹部を光学的に検出することで、露光装置とシリコン基板1との位置合わせを自動的に行う。

【0115】

次いで、露光装置内でフォトレジスト27を露光した後に、フォトレジスト27を現像することにより、図13(a)に示されるようなキャパシタ用レジストパターン27aを形成する。そのキャパシタ用レジストパターン27aは、セル領域I上においてキャパシタ平面形状を有すると共に、周辺領域IIにおいてアライメントマーク36cを覆う。

【0116】

次に、図13(b)に示す断面構造を得るまでの工程について説明する。

【0117】

まず、キャパシタ用レジストパターン27aをエッチングマスクに使用しながら第2マスク材料層26をエッチングしてハードマスク26aを形成する。

【0118】

そして、キャパシタ用レジストパターン27aを除去した後、上記のハードマスク26aをマスクにして第1マスク材料層25をエッチングすることにより、ハードマスク26aの下にのみ第1マスク材料層25を残す。

【0119】

続いて、図14(a)に示すように、ハロゲンガスを含むエッチングガスを用いて、ハードマスク26aで覆われていない部分の下部電極用導電膜21、強誘電体膜22、及び上部電極用導電膜23を一括してドライエッチングする。これにより、セル領域Iには、補助導電性プラグ36aと電気的に接続された下部電極21a、キャパシタ誘電体膜22a、及び上部電極23aを順に積層してなるキャパシタQが形成されたことになる。

【0120】

そのキャパシタQを構成する下部電極21aは、絶縁性密着膜15によって膜剥がれが防止される。更に、絶縁性密着膜15は、非晶質の酸化シリコンよりなるため、結晶性のある膜のように下部電極21aの配向を乱してしまうことが無く、下部電極21aの配向を良好に保つようにも機能する。

【0121】

その後に、ハードマスク26aと第1マスク材料層25とをウエットエッチングとドライエッチングにより除去する。

【0122】

次いで、図14(b)に示すように、上記した図14(a)のエッチング工程等でキャパシタ誘電体膜22aが受けたダメージを回復させるため、不図示のファーネス内にシリコン基板1を入れ、酸素雰囲気中で基板温度を550℃とする一回目の回復アニールをキャパシタ誘電体膜22aに対して約40分間行う。

【0123】

ここで、アライメント用開口14c内にアライメントマーク36cが略完全に埋め込まれているので、アライメントマーク36c上の下部電極用導電膜21には、図6(b)に示したような薄厚部21bが形成されていない。従って、このように酸素雰囲気中で回復アニールを行っても、下部電極用導電膜21で酸素をブロックすることができ、アライメントマーク36cが酸化するのを防ぐことができる。

【0124】

次に、図15(a)に示す断面構造を得るまでの工程について説明する。

【0125】

まず、水素等の還元性雰囲気からキャパシタ誘電体膜22aを保護するために、キャパシタ保護絶縁膜40として水素ブロック性に優れたアルミナ膜をシリコン基板1の上側全面に約50nmの厚さに形成する。

【0126】

そのキャパシタ保護絶縁膜40の成膜方法は特に限定されない。但し、カバレッジ特性に優れたALD(Atomic Layer Deposition)法でキャパシタ保護絶縁膜40を形成すれば、キャパシタQの側面にキャパシタ保護絶縁膜40をカバレッジ良く形成することができるので、隣接するキャパシタQの間隔を狭めることができ、FeRAMの微細化を推し進めることができる。

【0127】

次いで、シランを反応ガスとして使用するHDPCVD(High Density Plasma CVD)法を用いて、キャパシタ保護絶縁膜40上に第2絶縁膜41を形成し、隣接する二つのキャパシタQの間の空間をその第2絶縁膜41で埋め込む。その第2絶縁膜41の厚さは特に限定されないが、本実施形態ではシリコン基板1の平坦面上で約700nmとする。

【0128】

その後に、TEOSガスを用いるプラズマCVD法により、第2絶縁膜41上に犠牲絶縁膜42として酸化シリコン膜を形成する。この第2絶縁膜41の厚さは、シリコン基板1の平坦面上で例えば800nmである。

【0129】

続いて、図15(b)に示すように、CMP法により犠牲絶縁膜42と第2絶縁膜41の上面を研磨して平坦化した後、第2絶縁膜41上にフォトレジストを塗布し、それを露光、現像することにより、上部電極23a上にホール形状の第5窓43aを備えた第4レジストパターン43を形成する。

【0130】

そして、図16(a)に示すように、上記の第5窓43aを通じて第2絶縁膜41とキャパシタ保護絶縁膜40とをエッチングして、これらの絶縁膜40、41に上部電極23aに至る深さの第3ホール41aを形成する。このエッチングは、C4F8、Ar、及びO2の混合ガスをエッチングガスとして使用する平行平板型プラズマエッチング装置で行われ、エッチング時の圧力は2〜7Paとされる。また、周波数が13.56MHzでパワーが1kW〜2.5kWの高周波電力がそのエッチング装置の上部電極に印加され、それにより上記のエッチングガスがプラズマ化される。

【0131】

そして、第4レジストパターン43を除去した後に、ここまでの工程でキャパシタ誘電体膜22aが受けたダメージを回復させるため、不図示のファーネス内にシリコン基板1を入れ、酸素雰囲気中で基板温度を550℃とする二回目の回復アニールを約40分間行う。

【0132】

次に、図16(b)に示すように、第2絶縁膜41上にフォトレジストを再び塗布して、そのフォトレジストを露光、現像し、第5レジストパターン45を形成する。その現像により、第2導電性プラグ36b上の第5レジストパターン45には、ホール形状の第6窓45aが形成される。

【0133】

その後に、図17(a)に示すように、第5レジストパターン45の第6窓45aを通じて第2絶縁膜41、キャパシタ保護絶縁膜40、絶縁性密着膜15、及び酸化防止絶縁膜14をエッチングする。これにより、第2絶縁膜41に第4ホール41bが形成されると共に、その第4ホール41bの下の酸化防止絶縁膜14に第2開口14bが形成される。このようなエッチングは、例えばC4F8、Ar、O2、及びCOの混合ガスをエッチングガスとする平行平板プラズマエッチング装置で行われる。

【0134】

なお、このエッチングでは、圧力が2〜7Paに設定されると共に、周波数が13.56MHzでパワーが1kW〜2.5kWの高周波電力がエッチング装置の上部電極に印加される。

【0135】

このように、上部電極23a上の浅い第3ホール41aとは別に、第2ソース/ドレイン領域8b上の深い第4ホール41bを形成することで、浅い第3ホール41aの下の上部電極23aがエッチング雰囲気に長時間曝されるのを防ぐことができ、その下のキャパシタ誘電体膜22aが劣化するのを抑制することが可能となる。

【0136】

更に、第2ソース/ドレイン領域8b上の第2導電性プラグ36bは、本工程が終了するまで、酸化防止絶縁膜14によって覆われているので、第2導電性プラグ36bを構成するタングステンが酸化してコンタクト不良を起こすのが防止される。

【0137】

その後に、図17(b)に示すように、第5レジストパターン45を除去する。

【0138】

次に、図18(a)に示す断面構造を得るまでの工程について説明する。

【0139】

まず、第2絶縁膜41の上面と、第3、第4ホール41a、41bのそれぞれの内面に、スパッタ法によりバリアメタル膜として窒化チタン膜を約50nmの厚さに形成する。そして、このバリアメタル膜の上に、第3、第4ホール41a、41bを埋め込むのに十分な厚さ、例えば第2絶縁膜41の平坦面上での厚さが300nmとなるタングステン膜を形成する。

【0140】

その後に、第2絶縁膜41上の余分なバリアメタル膜とタングステン膜とをCMP法により研磨して除去し、これらの膜を第3、第4ホール41a、41b内にそれぞれ第3、第4導電性プラグ47a、47bとして残す。

【0141】

これらの導電性プラグのうち、第3導電性プラグ47aは上部電極23aと電気的に接続される。そして、第4導電性プラグ47bは、第2導電性プラグ36bと電気的に接続され、その第2導電性プラグ36bと共にビット線の一部を構成する。

【0142】

次に、図18(b)に示す断面構造を得るまでの工程について説明する。

【0143】

まず、第2絶縁膜41と第3、第4導電性プラグ47a、47bのそれぞれの上面に、スパッタ法により金属積層膜を形成する。その金属積層膜は、例えば、厚さ約50nmの窒化チタン膜、厚さ約360nmのアルミニウム膜、及び厚さ約70nmの窒化チタン膜をこの順に積層してなる。

【0144】

その後に、フォトリソグラフィによりこの金属積層膜をパターニングして、第3、第4導電性プラグ47a、47bのそれぞれと電気的に接続される一層目金属配線49aとビット線用金属パッド49bとを形成する。

【0145】

この後は、一層目金属配線49aと金属パッド49bの上に第3絶縁膜を形成する工程に移るが、その詳細については省略する。

【0146】

ここまでの工程により、本実施形態に係る半導体装置の基本構造が完成した。

【0147】

以上説明した半導体装置の製造方法によれば、図18(b)に示したように、キャパシタQの直下の導電性プラグを、第1導電性プラグ12aと補助導電性プラグ36aとに分割する。

【0148】

その補助導電性プラグ36aが埋め込まれる第1開口14aは、第1絶縁膜11よりも薄い酸化防止絶縁膜14に形成されるので、図11(a)の工程で第1開口14aを形成する際のエッチング量は少なくて済む。そのため、エッチングによる第3レジストパターン33の膜減りを低減することができ、第3レジストパターン33をマスクにしたエッチングで第1開口14aを精度良く形成することができる。

【0149】

更に、本実施形態では、上記の第1開口14aと同じプロセスにより、酸化防止絶縁膜14にアライメントマーク用開口14cを形成するので、このアライメントマーク用開口14cの深さも第1開口14aと同様に浅くすることができる。その結果、図11(b)に示したように、アライメントマーク14cを完全に埋め込むのに必要な導電膜36の膜厚を、図7(a)に示したタングステン膜18よりも薄くすることができ、図11(c)のCMP工程におけるタングステン膜18のオーバー研磨量を少なくすることができる。従って、このCMP工程では、補助導電性プラグ36aの上面にリセスが殆ど発生しないと共に、酸化防止絶縁膜14と絶縁性密着膜15のディッシングも抑制することができる。

【0150】

これらにより、本実施形態では、上面が平坦な補助導電性プラグ36a上に下部電極21aが形成されるので、下地の凹凸に起因する配向性の劣化が下部電極21aに発生し難くなり、良好な配向性を持った下部電極21aによりその上のキャパシタ誘電体膜22aの配向性を高めることができ、キャパシタ誘電体膜22aの強誘電体特性が向上された高品位なFeRAMを提供することが可能になる。

【0151】

しかも、上記のように酸化防止絶縁膜14にディッシングが発生しないので、プロセス中常に酸化防止絶縁膜14の酸素透過防止能力を維持することができ、ビット線の一部を構成する第2導電性プラグ36bが酸化してコンタクト不良を引き起こすのを防ぐことができる。

【0152】

なお、上記では、図17(a)を用いて説明したように、第4ホール41bと第2開口14bとを同時に形成し、その後にキャパシタ誘電体膜22aに対して二回目の回復アニールを行ったが、本発明はこれに限定されない。

【0153】

例えば、図17(a)の工程において、酸化防止絶縁膜14をエッチングストッパ膜にしながら第4ホール41bを形成し、第2導電性プラグ36bが酸化防止絶縁膜14で覆われた状態で上記の回復アニールを行ってもよい。その場合は、回復アニールを終了した後に、第4ホール41b下の酸化防止絶縁膜14をエッチングすることにより第2開口14bを形成する。

【0154】

(3)第2実施形態

上記した第1実施形態では、図11(b)、(c)で説明したように、第2バリアメタル膜35と導電膜36との積層膜で補助導電性プラグ36aを構成した。これに対し、本実施形態では、導電膜36のみで補助導電性プラグ36aを構成する。

【0155】

図19(a)〜図19(c)は、本発明の第2実施形態に係る半導体装置の製造途中の断面図である。なお、これらの図において、第1実施形態で説明した要素には第1実施形態と同じ符号を付し、以下ではその説明を省略する。

【0156】

本実施形態に係る半導体装置を作成するには、まず、第1実施形態で説明した図9(a)〜図11(a)の工程を行う。

【0157】

その後、図19(a)に示すように、絶縁性密着膜15の上面と各開口14a、14cのそれぞれの中に単層の導電膜36を形成し、その導電膜36で各開口14a、14cを完全に埋め込む。

【0158】

その導電膜36の構成材料は特に限定されないが、本実施形態では、窒化チタン膜と窒化チタンアルミニウム膜のいずれかの単層膜をスパッタ法により導電膜36として形成する。導電膜36としてスパッタ法により窒化チタンアルミニウム膜を形成する場合は、例えば、チタンを5%含むアルミニウムターゲットを用い、且つ、窒素とアルゴンとの混合ガスをスパッタガスとして使用することで、ターゲット中のチタンを気相中で窒化して窒化チタンアルミニウム膜を得る。

【0159】

次いで、図19(b)に示すように、絶縁性密着膜15を研磨ストッパとして使用しながら、その絶縁性密着膜15上の余分な導電膜36をCMP法により研磨して除去する。そのCMPでは、スラリーとして例えばCabot Microelectronics Corporation製のW2000が採用される。

【0160】

これにより、第1開口14aに導電膜36が補助導電性プラグ36aとして残されると共に、アライメント用開口14c内の導電膜36がアライメントマーク36cとされる。

【0161】

その後は、第1実施形態で説明した図12(a)〜図18(b)の工程を行うことで、図19(c)に示すように、キャパシタQを備えた半導体装置を完成させる。

【0162】

上記した本実施形態によれば、補助導電性プラグ36aが、タングステンよりも酸化し難い窒化チタン膜や窒化チタンアルミニウム膜の単層膜で構成されるので、補助導電性プラグ36aにタングステンを採用する第1実施形態と比較してプラグ36aの耐熱性が向上し、アニール等の熱プロセスを行う場合でも補助導電性プラグ36aのコンタクト特性を安定化させることが可能となる。

【0163】

以下に、本発明の特徴を付記する。

【0164】

(付記1) 半導体基板と、

前記半導体基板の表層に間隔をおいて形成された第1、第2不純物拡散領域と、

前記半導体基板上に形成され、前記第1、第2不純物拡散領域のそれぞれの上に第1、第2ホールを備えた第1絶縁膜と、

前記第1、第2ホール内にそれぞれ形成され、前記第1、第2不純物拡散領域のそれぞれと電気的に接続された第1、第2導電性プラグと、

前記第1絶縁膜の上に形成され、前記第1、第2導電性プラグのそれぞれの上に第1、第2開口を備えた酸化防止絶縁膜と、

前記第1開口内に形成された補助導電性プラグと、

前記補助導電性プラグ上、及び前記第1開口の周囲の前記酸化防止絶縁膜上に、下部電極、キャパシタ誘電体膜、及び上部電極を順に形成してなるキャパシタと、

前記キャパシタを覆うと共に、前記上部電極の上に第3ホールを備え、且つ前記第2開口の上に第4ホールを備えた第2絶縁膜と、

前記第3ホール内に形成され、前記上部電極と電気的に接続された第3導電性プラグと、

前記第4ホール内と前記第2開口内とに形成され、前記第2導電性プラグと電気的に接続された第4導電性プラグと、

を有することを特徴とする半導体装置。

【0165】

(付記2) 前記下部電極は配向性金属膜で構成されることを特徴とする付記1に記載の半導体装置。

【0166】

(付記3) 前記配向性金属膜は、イリジウムで構成されることを特徴とする付記2に記載の半導体装置。

【0167】

(付記4) 前記酸化防止絶縁膜は、前記第1絶縁膜よりも薄いことを特徴とする付記1に記載の半導体装置。

【0168】

(付記5) 前記第1導電性プラグと前記第2導電性プラグのそれぞれの上面の高さは同じ高さであることを特徴とする付記1に記載の半導体装置。

【0169】

(付記6) 前記補助導電性プラグは、バリアメタル膜とタングステン膜との積層膜、窒化チタン膜の単層膜、及び窒化チタンアルミニウム膜の単層膜のいずれかで構成されることを特徴とする付記1に記載の半導体装置の製造方法。

【0170】

(付記7) 前記酸化防止絶縁膜は、酸窒化シリコン膜、窒化シリコン膜、及びアルミナ膜のいずれかであることを特徴とする付記1に記載の半導体装置。

【0171】

(付記8) 前記酸化防止絶縁膜上に絶縁性密着膜が形成され、該絶縁性密着膜上に前記下部電極と前記第2絶縁膜とが形成されたことを特徴とする付記1に記載の半導体装置。

【0172】

(付記9) 前記第2導電性プラグと前記4導電性プラグは、ビット線の一部を構成することを特徴とする付記1に記載の半導体装置。

【0173】

(付記10) 前記第1、第2不純物拡散領域の間の前記半導体基板上に形成されたゲート絶縁膜と、

前記ゲート絶縁膜上に形成され、ワード線の一部を構成するゲート電極とを有することを特徴とする付記1に記載の半導体装置。

【0174】

(付記11) 半導体基板の表層に互いに間隔をおいて第1、第2不純物拡散領域を形成する工程と、

前記半導体基板上に第1絶縁膜を形成する工程と、

前記第1絶縁膜をパターニングして、前記第1、第2不純物拡散領域上の該第1絶縁膜にそれぞれ第1、第2ホールを形成する工程と、

前記第1、第2ホール内に、前記第1、第2不純物拡散領域のそれぞれと電気的に接続される第1、第2導電性プラグを形成する工程と、

前記第1絶縁膜上と前記第1、第2導電性プラグ上とに酸化防止絶縁膜を形成する工程と、

前記酸化防止絶縁膜をパターニングして、前記第1導電性プラグの上の該酸化防止絶縁膜に第1開口を形成する工程と、

前記酸化防止絶縁膜上と前記第1開口内とに導電膜を形成する工程と、

前記導電膜を研磨することにより、前記酸化防止絶縁膜上から該導電膜を除去すると共に、前記第1開口内に前記導電膜を補助導電性プラグとして残す工程と、

前記補助導電性プラグ上、及び前記第1開口の周囲の前記酸化防止絶縁膜上に、下部電極、キャパシタ誘電体膜、及び上部電極を順に積層してキャパシタを形成する工程と、

前記キャパシタを覆う第2絶縁膜を形成する工程と、

前記第2絶縁膜をパターニングすることにより、前記上部電極と前記第2ホールのそれぞれの上の前記第2絶縁膜に第3、第4ホールを形成すると共に、前記第4ホールの下の前記酸化防止絶縁膜に第2開口を形成する工程と、

前記第3ホール内に、前記上部電極と電気的に接続される第3導電性プラグを形成する工程と、

前記第4ホール内と前記第2開口内とに、前記第2導電性プラグと電気的に接続される第4導電性プラグを形成する工程と、

を有することを特徴とする半導体装置の製造方法。

【0175】

(付記12) 前記酸化防止絶縁膜を形成する工程において、前記第1絶縁膜よりも薄い厚さに前記酸化防止絶縁膜を形成することを特徴とする付記11に記載の半導体装置の製造方法。

【0176】

(付記13) 前記導電膜を形成する工程において、バリアメタル膜とタングステン膜との積層膜、窒化チタン膜の単層膜、及び窒化チタンアルミニウム膜の単層膜のいずれかを前記導電膜として形成することを特徴とする付記11に記載の半導体装置の製造方法。

【0177】

(付記14) 酸化防止絶縁膜を形成する工程において、酸窒化シリコン膜、窒化シリコン膜、及びアルミナ膜のいずれかを前記酸化防止絶縁膜として形成することを特徴とする付記11に記載の半導体装置の製造方法。

【0178】

(付記15) 前記酸化防止絶縁膜を形成した後に、該酸化防止絶縁膜上に絶縁性密着膜を形成する工程を有し、

前記絶縁性密着膜上に、前記下部電極と前記第2絶縁膜とを形成することを特徴とする付記11に記載の半導体装置の製造方法。

【0179】

(付記16) 前記第4ホールを形成した後に、酸素雰囲気中において前記キャパシタ誘電体膜をアニールし、その後に前記第2開口を形成することを特徴とする付記11に記載の半導体装置の製造方法。

【図面の簡単な説明】

【0180】

【図1】図1(a)〜(c)は、仮想的な半導体装置の製造途中の断面図(その1)である。

【図2】図2(a)〜(c)は、仮想的な半導体装置の製造途中の断面図(その2)である。

【図3】図3(a)〜(c)は、仮想的な半導体装置の製造途中の断面図(その3)である。

【図4】図4(a)、(b)は、仮想的な半導体装置の製造途中の断面図(その4)である。

【図5】図5(a)、(b)は、仮想的な半導体装置の製造途中の断面図(その5)である。

【図6】図6(a)、(b)は、仮想的な半導体装置の製造途中の断面図(その6)である。

【図7】図7(a)、(b)は、アライメント用開口をタングステン膜で完全に埋め込む場合の仮想的な半導体装置の製造途中の断面図(その1)である。

【図8】図8は、アライメント用開口をタングステン膜で完全に埋め込む場合の仮想的な半導体装置の製造途中の断面図(その2)である。

【図9】図9(a)〜(c)は、本発明の第1実施形態に係る半導体装置の製造途中の断面図(その1)である。

【図10】図10(a)〜(c)は、本発明の第1実施形態に係る半導体装置の製造途中の断面図(その2)である。

【図11】図11(a)〜(c)は、本発明の第1実施形態に係る半導体装置の製造途中の断面図(その3)である。

【図12】図12(a)、(b)は、本発明の第1実施形態に係る半導体装置の製造途中の断面図(その4)である。

【図13】図13(a)、(b)は、本発明の第1実施形態に係る半導体装置の製造途中の断面図(その5)である。

【図14】図14(a)、(b)は、本発明の第1実施形態に係る半導体装置の製造途中の断面図(その6)である。

【図15】図15(a)、(b)は、本発明の第1実施形態に係る半導体装置の製造途中の断面図(その7)である。

【図16】図16(a)、(b)は、本発明の第1実施形態に係る半導体装置の製造途中の断面図(その8)である。

【図17】図17(a)、(b)は、本発明の第1実施形態に係る半導体装置の製造途中の断面図(その9)である。

【図18】図18(a)、(b)は、本発明の第1実施形態に係る半導体装置の製造途中の断面図(その10)である。

【図19】図19(a)〜(c)は、本発明の第2実施形態に係る半導体装置の製造途中の断面図である。

【符号の説明】

【0181】

1…シリコン基板、2…素子分離絶縁膜、3…pウェル、4…ゲート絶縁膜、5…ゲート電極、6a、6b…第1、第2ソース/ドレインエクステンション、7…絶縁性サイドウォール、8a、8b…第1、第2ソース/ドレイン領域、9…高融点金属シリサイド層、10…カバー絶縁膜、11…第1絶縁膜、11a、11b…第1、第2ホール、11c…第1コンタクトホール、11e…アライメントマーク用開口、13c…第1コンタクトプラグ、14…酸化防止絶縁膜、15…絶縁性密着膜、16…第1レジストパターン、17…バリアメタル膜、18…タングステン膜、19…第2コンタクトプラグ、20…アライメントマーク、21…下部電極用導電膜、21a…下部電極、22…強誘電体膜、22a…キャパシタ誘電体膜、23…上部電極用導電膜、23a…上部電極、25…第1マスク材料層、26…第2マスク材料層、26a…ハードマスク、27…フォトレジスト、27a…キャパシタ用レジストパターン、30…第2レジストパターン、30a、30b…第1、第2窓、31…第1バリアメタル膜、32…タングステン膜、32a、32b…第1、第2導電性プラグ、14a、14b…第1、第2開口、14c…アライメントマーク用開口、33…第3レジストパターン、33a…第3窓、33b…第4窓、35…第2バリアメタル膜、36…導電膜、36a…補助導電性プラグ、36c…アライメントマーク、40…キャパシタ保護絶縁膜、41…第2絶縁膜、41a…第3ホール、42…犠牲絶縁膜、43…第4レジストパターン、43a…第5窓、45…第5レジストパターン、45a…第6窓、47a、47b…第3、第4導電性プラグ、49a…一層目金属配線、49b…ビット線用金属パッド。

【特許請求の範囲】

【請求項1】

半導体基板と、

前記半導体基板の表層に間隔をおいて形成された第1、第2不純物拡散領域と、

前記半導体基板上に形成され、前記第1、第2不純物拡散領域のそれぞれの上に第1、第2ホールを備えた第1絶縁膜と、

前記第1、第2ホール内にそれぞれ形成され、前記第1、第2不純物拡散領域のそれぞれと電気的に接続された第1、第2導電性プラグと、

前記第1絶縁膜の上に形成され、前記第1、第2導電性プラグのそれぞれの上に第1、第2開口を備えた酸化防止絶縁膜と、

前記第1開口内に形成された補助導電性プラグと、

前記補助導電性プラグ上、及び前記第1開口の周囲の前記酸化防止絶縁膜上に、下部電極、キャパシタ誘電体膜、及び上部電極を順に形成してなるキャパシタと、

前記キャパシタを覆うと共に、前記上部電極の上に第3ホールを備え、且つ前記第2開口の上に第4ホールを備えた第2絶縁膜と、

前記第3ホール内に形成され、前記上部電極と電気的に接続された第3導電性プラグと、

前記第4ホール内と前記第2開口内とに形成され、前記第2導電性プラグと電気的に接続された第4導電性プラグと、

を有することを特徴とする半導体装置。

【請求項2】

前記下部電極は配向性金属膜で構成されることを特徴とする請求項1に記載の半導体装置。

【請求項3】

前記第1導電性プラグと前記第2導電性プラグのそれぞれの上面の高さは同じ高さであることを特徴とする請求項1に記載の半導体装置。

【請求項4】

前記補助導電性プラグは、バリアメタル膜とタングステン膜との積層膜、窒化チタン膜の単層膜、及び窒化チタンアルミニウム膜の単層膜のいずれかで構成されることを特徴とする請求項1に記載の半導体装置の製造方法。

【請求項5】

前記酸化防止絶縁膜は、酸窒化シリコン膜、窒化シリコン膜、及びアルミナ膜のいずれかであることを特徴とする請求項1に記載の半導体装置。

【請求項6】

前記第2導電性プラグと前記4導電性プラグは、ビット線の一部を構成することを特徴とする請求項1に記載の半導体装置。

【請求項7】

半導体基板の表層に互いに間隔をおいて第1、第2不純物拡散領域を形成する工程と、

前記半導体基板上に第1絶縁膜を形成する工程と、

前記第1絶縁膜をパターニングして、前記第1、第2不純物拡散領域上の該第1絶縁膜にそれぞれ第1、第2ホールを形成する工程と、

前記第1、第2ホール内に、前記第1、第2不純物拡散領域のそれぞれと電気的に接続される第1、第2導電性プラグを形成する工程と、

前記第1絶縁膜上と前記第1、第2導電性プラグ上とに酸化防止絶縁膜を形成する工程と、

前記酸化防止絶縁膜をパターニングして、前記第1導電性プラグの上の該酸化防止絶縁膜に第1開口を形成する工程と、

前記酸化防止絶縁膜上と前記第1開口内とに導電膜を形成する工程と、

前記導電膜を研磨することにより、前記酸化防止絶縁膜上から該導電膜を除去すると共に、前記第1開口内に前記導電膜を補助導電性プラグとして残す工程と、

前記補助導電性プラグ上、及び前記第1開口の周囲の前記酸化防止絶縁膜上に、下部電極、キャパシタ誘電体膜、及び上部電極を順に積層してキャパシタを形成する工程と、

前記キャパシタを覆う第2絶縁膜を形成する工程と、

前記第2絶縁膜をパターニングすることにより、前記上部電極と前記第2ホールのそれぞれの上の前記第2絶縁膜に第3、第4ホールを形成すると共に、前記第4ホールの下の前記酸化防止絶縁膜に第2開口を形成する工程と、

前記第3ホール内に、前記上部電極と電気的に接続される第3導電性プラグを形成する工程と、

前記第4ホール内と前記第2開口内とに、前記第2導電性プラグと電気的に接続される第4導電性プラグを形成する工程と、

を有することを特徴とする半導体装置の製造方法。

【請求項8】

前記導電膜を形成する工程において、バリアメタル膜とタングステン膜との積層膜、窒化チタン膜の単層膜、及び窒化チタンアルミニウム膜の単層膜のいずれかを前記導電膜として形成することを特徴とする請求項7に記載の半導体装置の製造方法。

【請求項9】

前記第4ホールを形成した後に、酸素雰囲気中において前記キャパシタ誘電体膜をアニールし、その後に前記第2開口を形成することを特徴とする請求項7に記載の半導体装置の製造方法。

【請求項1】

半導体基板と、

前記半導体基板の表層に間隔をおいて形成された第1、第2不純物拡散領域と、

前記半導体基板上に形成され、前記第1、第2不純物拡散領域のそれぞれの上に第1、第2ホールを備えた第1絶縁膜と、

前記第1、第2ホール内にそれぞれ形成され、前記第1、第2不純物拡散領域のそれぞれと電気的に接続された第1、第2導電性プラグと、

前記第1絶縁膜の上に形成され、前記第1、第2導電性プラグのそれぞれの上に第1、第2開口を備えた酸化防止絶縁膜と、

前記第1開口内に形成された補助導電性プラグと、

前記補助導電性プラグ上、及び前記第1開口の周囲の前記酸化防止絶縁膜上に、下部電極、キャパシタ誘電体膜、及び上部電極を順に形成してなるキャパシタと、

前記キャパシタを覆うと共に、前記上部電極の上に第3ホールを備え、且つ前記第2開口の上に第4ホールを備えた第2絶縁膜と、

前記第3ホール内に形成され、前記上部電極と電気的に接続された第3導電性プラグと、

前記第4ホール内と前記第2開口内とに形成され、前記第2導電性プラグと電気的に接続された第4導電性プラグと、

を有することを特徴とする半導体装置。

【請求項2】

前記下部電極は配向性金属膜で構成されることを特徴とする請求項1に記載の半導体装置。

【請求項3】

前記第1導電性プラグと前記第2導電性プラグのそれぞれの上面の高さは同じ高さであることを特徴とする請求項1に記載の半導体装置。

【請求項4】

前記補助導電性プラグは、バリアメタル膜とタングステン膜との積層膜、窒化チタン膜の単層膜、及び窒化チタンアルミニウム膜の単層膜のいずれかで構成されることを特徴とする請求項1に記載の半導体装置の製造方法。

【請求項5】

前記酸化防止絶縁膜は、酸窒化シリコン膜、窒化シリコン膜、及びアルミナ膜のいずれかであることを特徴とする請求項1に記載の半導体装置。

【請求項6】

前記第2導電性プラグと前記4導電性プラグは、ビット線の一部を構成することを特徴とする請求項1に記載の半導体装置。

【請求項7】

半導体基板の表層に互いに間隔をおいて第1、第2不純物拡散領域を形成する工程と、

前記半導体基板上に第1絶縁膜を形成する工程と、

前記第1絶縁膜をパターニングして、前記第1、第2不純物拡散領域上の該第1絶縁膜にそれぞれ第1、第2ホールを形成する工程と、

前記第1、第2ホール内に、前記第1、第2不純物拡散領域のそれぞれと電気的に接続される第1、第2導電性プラグを形成する工程と、

前記第1絶縁膜上と前記第1、第2導電性プラグ上とに酸化防止絶縁膜を形成する工程と、

前記酸化防止絶縁膜をパターニングして、前記第1導電性プラグの上の該酸化防止絶縁膜に第1開口を形成する工程と、

前記酸化防止絶縁膜上と前記第1開口内とに導電膜を形成する工程と、

前記導電膜を研磨することにより、前記酸化防止絶縁膜上から該導電膜を除去すると共に、前記第1開口内に前記導電膜を補助導電性プラグとして残す工程と、

前記補助導電性プラグ上、及び前記第1開口の周囲の前記酸化防止絶縁膜上に、下部電極、キャパシタ誘電体膜、及び上部電極を順に積層してキャパシタを形成する工程と、

前記キャパシタを覆う第2絶縁膜を形成する工程と、

前記第2絶縁膜をパターニングすることにより、前記上部電極と前記第2ホールのそれぞれの上の前記第2絶縁膜に第3、第4ホールを形成すると共に、前記第4ホールの下の前記酸化防止絶縁膜に第2開口を形成する工程と、

前記第3ホール内に、前記上部電極と電気的に接続される第3導電性プラグを形成する工程と、

前記第4ホール内と前記第2開口内とに、前記第2導電性プラグと電気的に接続される第4導電性プラグを形成する工程と、

を有することを特徴とする半導体装置の製造方法。

【請求項8】

前記導電膜を形成する工程において、バリアメタル膜とタングステン膜との積層膜、窒化チタン膜の単層膜、及び窒化チタンアルミニウム膜の単層膜のいずれかを前記導電膜として形成することを特徴とする請求項7に記載の半導体装置の製造方法。

【請求項9】

前記第4ホールを形成した後に、酸素雰囲気中において前記キャパシタ誘電体膜をアニールし、その後に前記第2開口を形成することを特徴とする請求項7に記載の半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【公開番号】特開2007−36126(P2007−36126A)

【公開日】平成19年2月8日(2007.2.8)

【国際特許分類】

【出願番号】特願2005−221010(P2005−221010)

【出願日】平成17年7月29日(2005.7.29)

【出願人】(000005223)富士通株式会社 (25,993)

【Fターム(参考)】

【公開日】平成19年2月8日(2007.2.8)

【国際特許分類】

【出願日】平成17年7月29日(2005.7.29)

【出願人】(000005223)富士通株式会社 (25,993)

【Fターム(参考)】

[ Back to top ]