半導体装置とその製造方法

【課題】半導体装置とその製造方法において、半導体部品と回路基板との位置合わせを容易にすること。

【解決手段】表面に複数の第1の電極22が形成された第1の回路基材20と、第1の回路基材20の上方に設けられ、第1の電極22の各々の上方に第1の貫通孔30aと第2の貫通孔30bとが形成された第2の回路基材30と、第2の回路基材30の上方に設けられた半導体パッケージ50と、第1の貫通孔30aと第2の貫通孔30b内に設けられ、第1の電極22と半導体パッケージ50とを接続する複数の第1のバンプ51とを有する半導体装置による。

【解決手段】表面に複数の第1の電極22が形成された第1の回路基材20と、第1の回路基材20の上方に設けられ、第1の電極22の各々の上方に第1の貫通孔30aと第2の貫通孔30bとが形成された第2の回路基材30と、第2の回路基材30の上方に設けられた半導体パッケージ50と、第1の貫通孔30aと第2の貫通孔30b内に設けられ、第1の電極22と半導体パッケージ50とを接続する複数の第1のバンプ51とを有する半導体装置による。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置とその製造方法に関する。

【背景技術】

【0002】

近年、電子機器の小型化に伴い、電子機器に搭載される半導体パッケージや半導体素子等の半導体部品の小型化が進んでいる。その半導体部品は、はんだバンプ等の接続端子を介して電子機器内の回路基材に搭載されるが、この電子機器の歩留まりを向上させるにはこれら回路基材と半導体部品との位置合わせ精度を高めるのが好ましい。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開平7−183333号公報

【特許文献2】特開2007−27305号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

半導体装置とその製造方法において、半導体部品と回路基板との位置合わせを容易にすることを目的とする。

【課題を解決するための手段】

【0005】

以下の開示の一観点によれば、表面に複数の第1の電極が形成された第1の回路基材と、前記第1の回路基材の上方に設けられ、前記複数の第1の電極の各々の上方に第1の貫通孔と第2の貫通孔とが形成された第2の回路基材と、前記第2の回路基材の上方に設けられ、表面に複数の第2の電極が形成された半導体部品と、前記第1の貫通孔内と前記第2の貫通孔内に設けられ、前記第1の電極と前記第2の電極とを接続する複数の第1のバンプとを有する半導体装置が提供される。

【0006】

また、その開示の他の観点によれば、表面に複数の第1の電極が形成された第1の回路基材の上方に、第1の貫通孔と第2の貫通孔とが形成された第2の回路基材を配する工程と、半導体部品の複数の第2の電極の各々の上に形成された複数の第1のバンプを前記第1の貫通孔と前記第2の貫通孔に通し、前記第1の回路基材の複数の前記第1の電極に前記複数の第1のバンプを当接させる工程と、前記第1のバンプを加熱して溶融させ、前記第1の電極に前記第1のバンプを接合させる工程とを有する半導体装置の製造方法が提供される。

【0007】

更に、その開示の別の観点によれば、第1の回路基材が備える複数の第1のバンプの各々に、第2の回路基材の複数の貫通孔の各々を嵌合させる工程と、前記回路基材の前記複数の貫通孔の各々に、半導体部品が備える複数の第2のバンプの各々を嵌合させる工程と、前記第1のバンプと前記第2のバンプの各々を加熱して溶融し、該第1のバンプと該第2のバンプの各々を介して前記第1の回路基材と前記半導体部品とを電気的かつ機械的に接続する工程とを有する半導体装置の製造方法が提供される。

【発明の効果】

【0008】

以下の開示によれば、第2の回路基材の第1の貫通孔と前記第2の貫通孔に半導体部品のバンプを通すので、これらの貫通孔により溶融したバンプの動きを規制することができ、第1の回路基材の電極とバンプとの間に位置ずれが発生するのを防止することができる。

【図面の簡単な説明】

【0009】

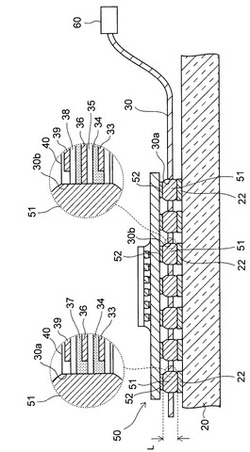

【図1】図1(a)、(b)は、インターポーザを利用した半導体装置の製造途中の断面図である。

【図2】図2は、第1実施形態に係る半導体装置の製造途中の断面図(その1)である。

【図3】図3は、第1実施形態に係る半導体装置の製造途中の断面図(その2)である。

【図4】図4は、第1実施形態に係る半導体装置の製造途中の断面図(その3)である。

【図5】図5は、第1実施形態に係る半導体装置の製造途中の断面図(その4)である。

【図6】図6は、第1実施形態に係る半導体装置の製造途中の断面図(その5)である。

【図7】図7は、第1実施形態に係る半導体装置の製造途中の断面図(その6)である。

【図8】図8は、第1実施形態で使用する第2の回路基材の拡大平面図である。

【図9】図9は、第2実施形態に係る半導体装置の製造途中の断面図(その1)である。

【図10】図10は、第2実施形態に係る半導体装置の製造途中の断面図(その2)である。

【図11】図11は、第2実施形態に係る半導体装置の製造途中の断面図(その3)である。

【図12】図12は、第2実施形態に係る半導体装置の製造途中の断面図(その4)である。

【図13】図13は、第3実施形態に係る半導体装置の製造途中の断面図(その1)である。

【図14】図14は、第3実施形態に係る半導体装置の製造途中の断面図(その2)である。

【図15】図15は、第3実施形態に係る半導体装置の製造途中の断面図(その3)である。

【図16】図16は、第4実施形態に係る半導体装置の製造途中の断面図(その1)である。

【図17】図17は、第4実施形態に係る半導体装置の製造途中の断面図(その2)である。

【図18】図18は、第4実施形態に係る半導体装置の製造途中の断面図(その3)である。

【図19】図19は、第5実施形態に係る半導体装置の断面図である。

【発明を実施するための形態】

【0010】

半導体パッケージ等の半導体部品を回路基材に実装する形態として、半導体部品と回路基板との間に配線を中継するためのインターポーザを設ける形態がある。

【0011】

各実施形態の説明に先立ち、そのようなインターポーザを利用した半導体装置の製造方法について説明する。

【0012】

図1(a)、(b)は、その半導体装置の製造途中の断面図である。

【0013】

まず、図1(a)に示すように、一方の主面上に第1の電極3が設けられた回路基材1を用意し、その回路基材1とインターポーザ4との位置合わせを行う。

【0014】

インターポーザ4は、ポリイミド等の可撓性基材に第2の電極6を形成してなり、その第2の電極6上には第1のはんだバンプ5が接合される。

【0015】

そして、第1のはんだバンプ5が第1の電極3に当接した状態で、その第1のはんだバンプ5をリフローすることにより、第1のはんだバンプ5を介して回路基材1とインターポーザ4とを機械的かつ電気的に接続する。

【0016】

次に、図1(b)に示すように、インターポーザ4の上に半導体パッケージ10を載置する。

【0017】

その半導体パッケージ10はパッケージ基材15を備えており、そのパッケージ基材15の二つの主面のうちインターポーザ4に対向する主面には第2のはんだバンプ8が設けられる。

【0018】

一方、パッケージ基材15の他方の主面上には第3の電極14が形成され、半導体素子13が第3のはんだバンプ12を介してその第3の電極14と接続されている。

【0019】

なお、半導体素子13とパッケージ基材15との間の隙間には、これらの接続信頼性を向上させるためのアンダーフィル樹脂19が充填される。

【0020】

そして、第2のはんだバンプ8と第2の電極6とが位置合わせされた状態で、この第2のはんだバンプ8をリフローすることにより、第2の電極6に第2のはんだバンプ8を接合する。

【0021】

以上により、この半導体装置の基本構造が完成したことになる。

【0022】

このような半導体装置の製造方法では、図1(b)のリフローの際、第2の電極6と第2のはんだバンプ8とが接合されるように、半導体パッケージ10とインターポーザ4とを位置合わせする必要がある。

【0023】

しかしながら、回路基材1、インターポーザ4、及び半導体パッケージ10は、材料の相違が原因で各々の熱膨張量が異なるので、図1(b)の工程で各はんだバンプ8をリフローする際に互いに異なる量で伸長してしまう。

【0024】

そのため、リフロー時に第2の電極6と第2のはんだバンプ8とが位置ずれを起こし、高精度な位置合わせが困難である。

【0025】

特に、インターポーザ4は、熱膨張率の大きなポリイミドを主にしてなるため、位置合わせの困難性を更に助長してしまう。

【0026】

しかも、この実装構造では、第1のはんだバンプ5と第2のはんだバンプ8の各々の高さと、インターポーザ4の厚さとを合わせた間隔Dだけ半導体パッケージ10が回路基材1から隔てられる。そのため、半導体パッケージ10から回路基材1への配線の引き回し距離が長くなり、RC遅延によって半導体パッケージ10の高速動作を妨げてしまう。

【0027】

このように、回路基材1と半導体パッケージ10との間に単にインターポーザ4を設けたのでは、位置合わせの困難性や信号処理速度の低下といった問題が生じることになる。

【0028】

このような問題に鑑み、本願発明者は以下に説明するような各実施形態に想到した。

【0029】

(第1実施形態)

図2〜図7は、本実施形態に係る半導体装置の製造途中の断面図である。

【0030】

この半導体装置を製造するには、まず、図2に示すように、実装基板等として供せられる第1の回路基材20を用意する。

【0031】

第1の回路基材20は、ガラスエポキシ樹脂等よりなり、その表面上には銅箔や銅めっき膜をパターニングしてなる複数の第1の電極22が形成される。

【0032】

なお、第1の回路基材20としては、複数の配線と絶縁層を積層してなる多層回路基板を使用してもよい。更に、第1の回路基材20の剛性も特に限定されず、可撓性のある回路基材やリジッドな回路基材のどちらも第1の回路基材20として採用し得る。

【0033】

また、このような第1の回路基材20と共に、図3に示すように、第1の貫通孔30aと第2の貫通孔30bが複数形成された第2の回路基材30を用意する。なお、この第2の回路基材30の端部に、信号を引き出すためのコネクタ60を設けてもよい。

【0034】

この第2の回路基材30は、点線円内に示すように、各層31〜40を積層してなる積層構造を有する。その積層構造は、下から順に、第1のカバーレイ31、第1の絶縁層32、第1のグランド配線33、第1の接着層34、第2の絶縁層35、信号配線36、第2の接着層37、第3の絶縁層38、第2のグランド配線39、第2のカバーレイ40を有する。

【0035】

このうち、第1〜第3の絶縁層32、35、38としては樹脂のみからなる可撓性の樹脂フィルムが用いられ、本実施形態ではポリイミドフィルムの一種である宇部興産株式会社製のユーピレックスを使用する。また、これらの絶縁層32、35、38の厚さは特に限定されないが、本実施形態では約15μmの厚さに各絶縁層を形成する。

【0036】

このように可撓性のある各絶縁層32、35、38を使用することで、第2の回路基材30自体も可撓性を呈するようになる。

【0037】

一方、第1及び第2の接着層34、37としては、絶縁性のある厚さ約15μmの京セラケミカル社製のTFA-860FBを使用する。

【0038】

更に、第1及び第2のグランド配線33、39と、信号配線36としては、厚さが約9μmの電解銅めっき膜を使用する。信号配線36は第2の絶縁層35の上面上に形成されており、その信号配線36と第2の絶縁層35とを覆うように第3の絶縁層38が形成される。

【0039】

本実施形態では、これら各層31〜40を張り合わせて厚さが約0.1mmの積層体を形成した後、ドリル加工によって直径が約0.7mmの第1の貫通孔30aと第2の貫通孔30bをその積層体に形成し、第2の回路基材30を作製する。

【0040】

このようにして形成された各貫通孔30a、30bのうち、第2の貫通孔30bにおいては、その内面30yに信号配線36が露出する。

【0041】

一方、第1の貫通孔30aにおいては、信号配線36は絶縁性の第2の接着層37によって、当該貫通孔30aの内面30xから隔離されている。

【0042】

図8は、この第2の回路基材30の拡大平面図である。

【0043】

図8に示されるように、第1のグランド配線33と第2のグランド配線39は、第2の回路基材30において、各貫通孔30a、30bを除く領域の全面に形成される。

【0044】

一方、信号配線36はライン状の平面形状を有しており、二本の信号配線36が対になって差動配線として機能する。差動配線においては、二本の信号配線36に位相が互いに逆の信号が供給され、ノイズ耐性の向上やデバイスの高速化に有利である。

【0045】

更に、これらグランド配線33、39と信号配線36は、ストリップ配線構造となっており、高周波信号の伝送に好適である。

【0046】

また、上記した第2の回路基材30と共に、図4に示すような半導体パッケージ50を用意する。

【0047】

その半導体パッケージ50は、いわゆるBGA(Ball Grid Array)型のパッケージであって、パッケージ基材53と半導体素子58とを備える。

【0048】

パッケージ基材53の両主面のうち、半導体素子58が搭載されていない側の主面には第2の電極52がグリッド状に複数設けられる。

【0049】

第2の電極52は、銅めっき膜等をパターニングしてなり、その表面には第1のはんだバンプ51が接合される。

【0050】

一方、半導体素子58が搭載されている側のパッケージ基材53の主面には銅めっき膜をパターニングしてなる第3の電極56が形成されており、その第3の電極56に突起電極57が接合される。

【0051】

突起電極57は、例えばはんだバンプであって、半導体素子58の不図示の電極にも接合される。

【0052】

そして、パッケージ基材53と半導体素子58の間の隙間には、これらの間の接続信頼性を高めるべくアンダーフィル樹脂59が充填される。

【0053】

続いて、図5に示すように、下から順に第1の回路基材20、第2の回路基材30、及び半導体パッケージ50を配する。そして、第1の電極パッド22の上方に各貫通孔30a、30bが位置するように、第1の回路基材20と第2の回路基材30との位置合わせを行う。

【0054】

同様に、第2の回路基材30と半導体パッケージ50との位置合わせを行い、各貫通孔30a、30bの上方に第1のはんだバンプ51が位置するようにする。

【0055】

次いで、図6に示すように、半導体パッケージ50が備える複数の第1のはんだバンプ51を第1の貫通孔30aと第2の貫通孔30bに通し、第1の回路基材20の表面に形成された複数の第1の電極22に各はんだバンプ51を当接させる。

【0056】

このとき、隣接する第1のはんだバンプ51同士の間隔や、はんだバンプ51の直径にばらつきがあることがあるので、そのばらつきを寛容できるように各貫通孔30a、30bの直径を第1のはんだバンプ51のそれよりも大きくしておくのが好ましい。

【0057】

例えば、第1のはんだバンプ51の直径が約0.6μmのときは、これよりも大きい約0.7μmの直径に各貫通孔30a、30bを形成するのが好ましい。

【0058】

次に、図7に示すように、第1のはんだバンプ51の融点よりも高い温度に当該はんだバンプ51をリフローして加熱することにより、はんだバンプ51を溶融させて第1の電極22に接合させる。

【0059】

このとき、各回路基材20、30と半導体パッケージ50は材料の相違に起因して互いに異なる量で熱膨張をする。

【0060】

但し、本実施形態では、第2の回路基材30の各貫通孔30a、30bが第1のはんだバンプ51を保持するように機能するので、上記の熱膨張量の相違に起因して各回路基材20、30や半導体パッケージ50が位置ずれするのを抑制できる。

【0061】

その後、第1のはんだバンプ51を冷却して固化することで、上記した第1の回路基材20、第2の回路基材30、及び半導体パッケージ50が第1のはんだバンプ51により互いに機械的且つ電気的に接続される。

【0062】

既述のように、各貫通孔30a、30bのうち、第1の貫通孔30aにおいては各配線33、36、39が当該貫通孔30aの内面に露出していない。よって、第1の貫通孔30a内の第1のはんだバンプ51は、第2の回路基材30の各配線33、36、39に接続されることはない。

【0063】

一方、第2の貫通孔30bにおいては、その内面に信号配線36が露出しているので、第1のはんだバンプ51はその信号配線36と電気的に接続され、半導体パッケージ50の所定の信号が第2の回路基材20に流されることになる。

【0064】

そして、その信号は、第2の回路基材20に接続されたコネクタ60を介して、他の電子部品等に入出力される。このように、この半導体装置においては、半導体パッケージ50の所定の信号とそれ以外の信号とを分離し、それらを第1の回路基材20と第2の回路基材30のそれぞれに分けて供給することができる。

【0065】

以上により、本実施形態に係る半導体装置の基本構造が完成したことになる。

【0066】

上記した本実施形態によれば、図7に示したように、第2の回路基材30に貫通孔30a、30bを設け、これらの貫通孔30a、30bに第1のはんだバンプ51を通すようにした。

【0067】

このようにすると、第1のはんだバンプ51をリフローするとき、第2の回路基材30の各貫通孔30a、30bが溶融した第1のはんだバンプ51を保持し、第1のはんだバンプ51の動きを規制するように機能する。そのため、材料の相違に起因してリフロー時の熱膨張量が各回路基材20、30と半導体パッケージ50の各々で異なる場合でも、第1のはんだバンプ51と各電極22、52との間に位置ずれが発生するのを防止できる。

【0068】

しかも、本実施形態では、図1(b)のように二段のはんだバンプ5、6を設けず、第1のはんだバンプ51の一段のみを利用して第1の回路基材20上に半導体パッケージ50を実装する。

【0069】

そのため、実装時に行うリフローの回数がはんだバンプ51に対する1回のみとなり、図1(a)、(b)のようにリフローを二回行う場合と比較して、リフロー時に第1のはんだバンプ51と各電極22、52とが位置ずれする危険性を更に低減できる。

【0070】

更に、このように第1のはんだバンプ51を1段のみ設けることで、図1(b)の例と比較して第1の回路基材20と半導体パッケージ50との間隔Lを狭めることができる。これにより、半導体パッケージ50から第1の回路基材20までの配線の引き回し距離を短くでき、RC遅延が抑制されて高速動作が可能な半導体装置を提供することができる。

【0071】

また、半導体パッケージ50の所定の信号については、第2の貫通孔30bから第2の回路基材30の信号配線36に流すようにした。既述のように、その信号配線36は二本が対となって差動配線として機能するので、上記の信号のノイズレベルを低い状態に維持しながら、デバイスの高速化を実現することができる。

【0072】

特に、信号配線36は、ポリイミドのように誘電率が均一な樹脂のみからなる第2の絶縁層35と第3の絶縁層38で挟まれているので、信号経路に沿う周囲の誘電率の変動が小さい。

【0073】

これに対し、熱硬化性樹脂をガラスクロスに含浸させてなるコンポジット材料を使用する回路基材では、ガラスクロスの誘電率が熱硬化性樹脂のそれよりも高いため、ガラスクロスの織目付近で信号配線の周囲の誘電率が変動する。よって、この場合は、差動信号配線の二つの信号配線間で信号の伝播時間に遅延が生じ、その遅延が許容範囲を超えると、半導体パッケージ50において当該信号の処理ができなくなる。

【0074】

本実施形態では、各絶縁層35、38や接着層34、37が樹脂のみからなり、ガラスクロスを使用していないので、ガラスクロスの織り目が原因で信号の伝播時間に遅延が生じるおそれがなく、半導体パッケージ50において信号を高速に処理することができる。

【0075】

(第2実施形態)

次に、第2実施形態について説明する。

【0076】

本実施形態では、第1実施形態と比較して半導体装置の微細化に有利な技術について説明する。

【0077】

図9〜図12は、本実施形態に係る半導体装置の製造途中の断面図である。なお、これらの図において第1実施形態で説明したのと同じ要素には第1実施形態で説明したのと同じ符号を付し、以下ではその説明を省略する。

【0078】

この半導体装置を製造するには、まず、図9に示すように、第1実施形態で説明した第2の回路基材30を用意する。

【0079】

但し、本実施形態では、その第2の回路基材30の二つの主面のうち、後述の第1の回路基材に対向する主面に予め複数の凹部30cを形成しておく。

【0080】

その凹部30cの形成方法は特に限定されない。例えば、炭酸ガスレーザの照射によって第2の回路基材30の所定部分を蒸散させて凹部30cを形成し得る。或いは、不図示のレジストパターンをマスクに用い、ウエットエッチングにより第2の回路基材30の所定部分を除去して凹部30cを形成してもよい。いずれの場合でも、信号配線36がレーザやウエットエッチングに対するストッパとして機能し、凹部30cは信号配線36よりも深く形成されることはない。

【0081】

次いで、図10に示すように、凹部30c内に第2のはんだバンプ61を設け、凹部30cの底面に露出している信号配線36の上にその第2のはんだバンプ61を接合する。

【0082】

その第2のはんだバンプ61の直径は特に限定されないが、第1実施形態で説明した第1のはんだバンプ51(図4参照)よりも小さい直径、例えば0.2mm〜0.4mm程度とするのが好ましい。

【0083】

また、第2のはんだバンプ61の材料も特に限定されず、第1のはんだバンプ51と同一の材料を使用し得る。

【0084】

次に、図11に示すように、半導体パッケージ50が備える複数の第1のはんだバンプ51を第1の貫通孔30aと第2の貫通孔30bに通し、第1の電極22にその第1のはんだバンプ51を当接させる。

【0085】

また、本実施形態では、第1の回路基板20の表面に複数の第3の電極23が形成されており、本工程ではそれらの第3の電極23に第2のはんだバンプ61を当接させる。

【0086】

その後、図12に示すように、各はんだバンプ51、61の融点よりも高い温度に当該はんだバンプ51、61をリフローして加熱することにより、各はんだバンプ51、61を溶融させてそれらを各電極22、23に接合させる。

【0087】

以上により、本実施形態に係る半導体装置の基本構造が完成したことになる。

【0088】

本実施形態によれば、第1のはんだバンプ51の他に、第2の回路基材30の凹部30cに第2のはんだバンプ61を設けたので、第1実施形態と比較して各はんだバンプ51、61の配置が高密度になる。

【0089】

そのため、第1の回路基材20の隣接する二つの第3の電極23同士の間隔Pを詰めることができ、半導体装置の微細化に寄与することが可能となる。

【0090】

更に、その第2のはんだバンプ61の直径を第1のはんだバンプ51のそれよりも小さくすることで、第3の電極23同士の間隔Pを更に小さくすることができ、半導体装置の一層の微細化を図ることができるようになる。

【0091】

しかも、第2のはんだバンプ61を設けたことで、信号配線36と第3の電極23との間隔Tが狭まるので、第1実施形態よりもRC遅延を効率的に抑えることができ、半導体装置の一層の高速化を図ることもできるようになる。

【0092】

(第3実施形態)

上記した第2実施形態では、図12に示したように、第2の回路基材30の二つの主面のうち、第1の回路基材20に対向する面側に第2のはんだバンプ61を設けることで、第1の回路基材20の第3の電極23同士の間隔Pを詰めるようにした。

【0093】

これに対し、本実施形態では、第2実施形態と比較して第2の回路基材30を上下逆にして用いることで、半導体パッケージ50の電極同士の間隔を詰めるようにする。

【0094】

図13〜図15は、本実施形態に係る半導体装置の製造途中の断面図である。なお、これらの図において、第2実施形態で説明したのと同じ要素には第2実施形態におけるのと同じ符号を付し、以下ではその説明を省略する。

【0095】

まず、図13に示すように、第2のはんだバンプ61を上側にして第2の回路基材30を用意する。

【0096】

第2実施形態で説明したように、各々の第2のはんだバンプ61は、凹部30cの底面に露出している信号配線36の上に接合される。また、各々の第2のはんだバンプ61の直径は、第1実施形態で説明した第1のはんだバンプ51(図4参照)よりも小さな0.2mm〜0.4mm程度の値を有する。

【0097】

次に、図14に示すように、半導体パッケージ50が備える複数の第1のはんだバンプ51を第1の貫通孔30aと第2の貫通孔30bに通し、第1の回路基材20の第1の電極22にその第1のはんだバンプ51を当接させる。

【0098】

ここで、本実施形態における半導体パッケージ50の表面には、第2の電極52の他に複数の第4の電極54が設けられる。

【0099】

本工程では、それら第4の電極54に上記の第2のはんだバンプ61を当接させる。

【0100】

次いで、図15に示すように、各はんだバンプ51、61の融点よりも高い温度に当該はんだバンプ51、61をリフローして加熱することにより、各はんだバンプ51、61を溶融させてそれらを第1の電極22と第4の電極54に接合させる。

【0101】

以上により、本実施形態に係る半導体装置の基本構造が完成したことになる。

【0102】

本実施形態によれば、第2実施形態と同様に、第1のはんだバンプ51の他に第2のはんだバンプ61を設けたので、第1実施形態と比較して各はんだバンプ51、61の配置が高密度になる。

【0103】

そして、そのように高密度に配された第2のはんだバンプ61を介して半導体パッケージ50と第2の回路基材30とを接続するので、半導体パッケージ50の第4の電極54の配置密度を第2のはんだバンプ61に合わせて高密度化できる。

【0104】

これにより、半導体パッケージ50の隣接する二つの第4の電極54同士の間隔Sを詰めることができ、半導体装置の微細化に寄与することが可能となる。

【0105】

(第4実施形態)

第1実施形態では、図5に示したように、第1の回路基材20に半導体パッケージ50を実装するに際し、半導体パッケージ50にのみ第1のはんだバンプ51を設け、第1の回路基材20にははんだバンプを設けなかった。

【0106】

これに対し、本実施形態では、以下のようにして第1の回路基材20と半導体パッケージ50の各々にはんだバンプを設ける。

【0107】

図16〜図18は、本実施形態に係る半導体装置の製造途中の断面図である。なお、これらの図において、第1実施形態で説明したのと同じ要素には第1実施形態におけるのと同じ符号を付し、以下ではその説明を省略する。

【0108】

この半導体装置を製造するには、まず、図16に示すように、第1の回路基材20、第2の回路基材30、及び半導体パッケージ50を用意する。

【0109】

このうち、半導体パッケージ50の第2の電極52には、第1実施形態と同様に複数の第1のはんだバンプ51が接合される。

【0110】

一方、第1の回路基材20の第1の電極22には、複数の第2のはんだバンプ70が接合される。

【0111】

また、第2の回路基材30には、第1実施形態と同様に第1の貫通孔30aと第2の貫通孔30bが形成される。それらの貫通孔30a、30bの直径D1は特に限定されないが、直径D1を各バンプ51、70の各々の直径D2よりも小さくするのが好ましい。

【0112】

本実施形態では、貫通孔30a、30bの直径D1を約0.4mmとし、各バンプ51、70の直径D2を約0.6mmとする。

【0113】

なお、第1のはんだバンプ51と第2のはんだバンプ70の直径は同じである必要はなく、異なる直径であってもよい。

【0114】

次に、図17に示すように、第1の回路基材20に向けて第2の回路基材30を下ろし、第2のはんだバンプ70の各々に貫通孔30a、30bを嵌合させる。

【0115】

このとき、上記のように各貫通孔30a、30bの直径D1を第2のはんだバンプ70の直径D2よりも小さくしたので、本工程では第2のはんだバンプ70が各貫通孔30a、30bを通り抜けず、第2の回路基材30がはんだバンプ70により係止された状態となる。

【0116】

その後に、第2の回路基材30に向けて半導体部品50を降ろし、各貫通孔30a、30bに第1のはんだバンプ51を嵌合させる。

【0117】

本実施形態では、このように貫通孔30a、30bに各バンプ51、70を嵌合させることで、各回路基板20、30や半導体パッケージ50の相互の位置が自己整合的に定まり、これらの位置合わせが容易になる。

【0118】

続いて、図18に示すように、各はんだバンプ51、70を加熱して溶融することにより柱状の接続媒体75を形成する。そして、その接続媒体75が冷えて固化することで、第1の回路基材20の第1の電極22と半導体部品50の第2の電極52とが電気的かつ機械的に接続される。

【0119】

また、第2の貫通孔30bの内面に露出していた信号配線36は上記の接続媒体75に接続され、これにより半導体パッケージ50の所定の信号は第2の回路基材30に流されることになる。

【0120】

一方、第1実施形態で説明したように、第1の貫通孔30aにおいては、その内面に信号配線36が露出していないので、信号配線36と接続媒体75とが接続されることはない。

【0121】

ここで、接続媒体75により貫通孔30a、30bを隙間なく充填するには、図17に示したように、溶融前の各はんだバンプ51、70が互いに離間することなく、各々の頂点が接しているのが好ましい。

【0122】

以上により、本実施形態に係る半導体装置の基本構造が完成したことになる。

【0123】

上記した本実施形態によれば、図17を参照して説明したように、第2の回路基材30の各貫通孔30a、30bに各はんだバンプ51、70を嵌合させる。これにより、各回路基材20、30と半導体パッケージ50の相互の位置を自動的に決定でき、これらの位置合わせを簡単に行うことができる。

【0124】

また、図18に示したように、各はんだバンプ51、70を溶融してなる接続媒体75は、各はんだバンプ51、70を上下方向に繋げたような形となり、幅Wよりも高さHの方が長い柱状となる。

【0125】

ここで、各回路基材20、30や半導体パッケージ50は、それらの材料の違いから互いに異なる熱膨張量を有する。そのような熱膨張量の相違が原因で接続媒体75には応力が加わることになるが、高さ方向に長い接続媒体75は自身が変形してその応力を吸収し易い特性があるため、応力が原因で接続媒体75と各電極22、51との間に接続不良が発生する危険性が減る。

【0126】

しかも、接続媒体75の形成前に、熱履歴等が原因で第1の回路基材20や半導体パッケージ50に反りが発生し、対向する電極22、52同士の間隔が場所により変動している場合でも、柱状の接続媒体75によりその間隔の変動を吸収できる。これにより、第1の回路基材20等の反りが原因で発生する回路基材20と半導体パッケージ50との接続不良を防止でき、半導体装置の信頼性を高めることが可能となる。

【0127】

更に、本実施形態では、各貫通孔30a、30bの直径D1を、上記のように各バンプ51、70の直径D2よりも小さくする。そのため、直径D1が直径D2よりも大きい場合と比較して、第2の回路基材30において信号配線36が占める領域を増やすことができる。

【0128】

(第5実施形態)

図19は、本実施形態に係る半導体装置の断面図である。なお、図19において第1実施形態でしたのと同じ要素には第1実施形態と同じ符号を付し、以下ではその説明を省略する。

【0129】

本実施形態では、図19に示すように、第2の回路基材30の上方に二つの半導体パッケージ50を並べて設けるようにする。

【0130】

このように第1の回路基材20の上に複数の半導体パッケージ50を搭載することで、半導体パッケージ50を一つだけ搭載する場合と比較して、半導体装置全体の高機能化を図ることが可能となる。

【0131】

しかも、第2の回路基材30は可撓性を有しているので、図13の点線Qのように第2の回路基材30が撓むことで、各半導体パッケージ50と各回路基材30、50との位置合わせに余裕を持たせることもできる。

【0132】

なお、この例では第1の回路基材20上に二つの半導体パッケージ50を搭載したが、半導体パッケージ50の個数はこれに限定されず、三以上の半導体パッケージ50を搭載するようにしてもよい。

【0133】

以上、各実施形態について詳細に説明したが、各実施形態は上記に限定されない。

【0134】

例えば、第1〜第5実施形態では第1の回路基材20に半導体パッケージ50を搭載したが、搭載可能な半導体部品は半導体パッケージ50に限定されず、半導体部品として半導体素子を第1の回路基材20に搭載してもよい。

【0135】

以上説明した各実施形態に関し、更に以下の付記を開示する。

【0136】

(付記1) 表面に複数の第1の電極が形成された第1の回路基材と、

前記第1の回路基材の上方に設けられ、前記複数の第1の電極の各々の上方に第1の貫通孔と第2の貫通孔とが形成された第2の回路基材と、

前記第2の回路基材の上方に設けられ、表面に複数の第2の電極が形成された半導体部品と、

前記第1の貫通孔内と前記第2の貫通孔内に設けられ、前記第1の電極と前記第2の電極とを接続する複数の第1のバンプと、

を有することを特徴とする半導体装置。

【0137】

(付記2) 前記第2の回路基材は配線を有し、

前記第1の貫通孔の内面が絶縁材料によって前記配線から隔離されたことを特徴とする付記1に記載の半導体装置。

【0138】

(付記3) 前記第2の回路基材は配線を有し、

前記第2の貫通孔の内面に前記配線が露出し、該配線が前記第1のバンプに接続されたことを特徴とする付記1に記載の半導体装置。

【0139】

(付記4) 前記第2の回路基材において前記配線が二本設けられ、二本の前記配線が対となって差動配線として機能することを特徴とする付記3に記載の半導体装置。

【0140】

(付記5) 前記第2の回路基材が、上面に前記配線が形成された樹脂からなる第1の絶縁層と、前記配線と前記第1の絶縁層とを覆う樹脂からなる第2の絶縁層とを有する付記4に記載の半導体装置。

【0141】

(付記6) 前記第1の回路基材の前記表面に形成された第3の電極と、

前記第2の回路基材に形成された配線とを更に有し、

前記第2の回路基材の二つの主面のうち、前記第1の回路基材に対向する主面に凹部が形成されたと共に、

前記第1のバンプよりも直径が小さい第2のバンプが前記凹部に設けられ、前記第1の回路基材の前記第3の電極と前記第2の回路基材の前記配線とが、前記第2のバンプにより接続されたことを特徴とする付記1〜5のいずれかに記載の半導体装置。

【0142】

(付記7) 前記半導体部品の前記表面に形成された第4の電極と、

前記回路基板に形成された配線とを更に有し、

前記第2の回路基材の二つの主面のうち、前記半導体部品に対向する主面に凹部が形成されたと共に、

前記第1のバンプよりも直径が小さい第2のバンプが前記凹部に設けられ、前記半導体部品の前記第4の電極と前記第2の回路基材の前記配線とが、前記第2のバンプにより接続されたことを特徴とする付記1〜5のいずれかに記載の半導体装置。

【0143】

(付記8) 前記第2の回路基材は可撓性を有することを特徴とする付記1〜7のいずれかに記載の半導体装置。

【0144】

(付記9) 前記第2の回路基材の縁にコネクタが設けられたことを特徴とする付記8に記載の半導体装置。

【0145】

(付記10) 前記第2の回路基板の上方に、前記半導体部品が並べて複数設けられたことを特徴とする付記8に記載の半導体装置。

【0146】

(付記11) 表面に複数の第1の電極が形成された第1の回路基材の上方に、第1の貫通孔と第2の貫通孔とが形成された第2の回路基材を配する工程と、

半導体部品の複数の第2の電極の各々の上に形成された複数の第1のバンプを前記第1の貫通孔と前記第2の貫通孔に通し、前記第1の回路基材の複数の前記第1の電極に前記複数の第1のバンプを当接させる工程と、

前記第1のバンプを加熱して溶融させ、前記第1の電極に前記第1のバンプを接合させる工程と、

を有することを特徴とする半導体装置の製造方法。

【0147】

(付記12) 前記第2の回路基材の二つの主面のうち、前記第1の回路基材に対向する主面に凹部を形成し、該凹部に前記第2の回路基材の配線を露出させる工程と、

前記凹部に、前記第1のバンプよりも直径が小さい第2のバンプを設け、前記配線と前記第2のバンプとを接続する工程とを更に有し、

前記複数の第1の電極に前記複数の第1のバンプを当接させる工程において、前記第1の回路基材の前記表面に形成された第3の電極に前記第2のバンプを当接させ、

前記第1の電極に前記第1のバンプを接合させる工程において、前記第3の電極に前記第2のバンプを接合させることを特徴とする付記11に記載の半導体装置の製造方法。

【0148】

(付記13) 前記第2の回路基材の二つの主面のうち、前記半導体部品に対向する主面に凹部を形成し、該凹部に前記第2の回路基材の配線を露出させる工程と、

前記凹部に、前記第1のバンプよりも直径が小さい第2のバンプを設け、前記配線と前記第2のバンプとを接続する工程とを更に有し、

前記複数の第1の電極に前記複数の第1のバンプを当接させる工程において、前記半導体部品の前記表面に形成された第4の電極に前記第2のバンプを当接させ、

前記第1の電極に前記第1のバンプを接合させる工程において、前記第4の電極に前記第2のバンプを接合させることを特徴とする付記11に記載の半導体装置の製造方法。

【0149】

(付記14) 第1の回路基材が備える複数の第1のバンプの各々に、第2の回路基材の複数の貫通孔の各々を嵌合させる工程と、

前記回路基材の前記複数の貫通孔の各々に、半導体部品が備える複数の第2のバンプの各々を嵌合させる工程と、

前記第1のバンプと前記第2のバンプの各々を加熱して溶融し、該第1のバンプと該第2のバンプの各々を介して前記第1の回路基材と前記半導体部品とを電気的かつ機械的に接続する工程と、

を有することを特徴とする半導体装置の製造方法。

【0150】

(付記15) 前記貫通孔の直径は、前記第1のバンプと前記第2のバンプの各々の直径よりも小さいことを特徴とする付記14に記載の半導体装置の製造方法。

【符号の説明】

【0151】

1…回路基材、3…第1の電極、4…インターポーザ、5…第1のはんだバンプ、6…第2のはんだバンプ、8…第2のはんだバンプ、10…半導体パッケージ、12…第3のはんだバンプ、13…半導体素子、14…第3の電極、15…パッケージ基材、19…アンダーフィル樹脂、20…第1の回路基材、22…第1の電極、23…第3の電極、30…第2の回路基材、30a…第1の貫通孔、30b…第2の貫通孔、30c…凹部、31…第1のカバーレイ、32…第1の絶縁層、33…第1のグランド配線、34…第1の接着層、35…第2の絶縁層、36…信号配線、37…第2の接着層、38…第3の絶縁層、39…第2のグランド配線、40…第2のカバーレイ、50…半導体パッケージ、51…第1のはんだバンプ、52…第2の電極、53…パッケージ基材、54…第4の電極、56…第3の電極、57…突起電極、58…半導体素子、59…アンダーフィル樹脂、61、70…第2のはんだバンプ、75…接続媒体。

【技術分野】

【0001】

本発明は、半導体装置とその製造方法に関する。

【背景技術】

【0002】

近年、電子機器の小型化に伴い、電子機器に搭載される半導体パッケージや半導体素子等の半導体部品の小型化が進んでいる。その半導体部品は、はんだバンプ等の接続端子を介して電子機器内の回路基材に搭載されるが、この電子機器の歩留まりを向上させるにはこれら回路基材と半導体部品との位置合わせ精度を高めるのが好ましい。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開平7−183333号公報

【特許文献2】特開2007−27305号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

半導体装置とその製造方法において、半導体部品と回路基板との位置合わせを容易にすることを目的とする。

【課題を解決するための手段】

【0005】

以下の開示の一観点によれば、表面に複数の第1の電極が形成された第1の回路基材と、前記第1の回路基材の上方に設けられ、前記複数の第1の電極の各々の上方に第1の貫通孔と第2の貫通孔とが形成された第2の回路基材と、前記第2の回路基材の上方に設けられ、表面に複数の第2の電極が形成された半導体部品と、前記第1の貫通孔内と前記第2の貫通孔内に設けられ、前記第1の電極と前記第2の電極とを接続する複数の第1のバンプとを有する半導体装置が提供される。

【0006】

また、その開示の他の観点によれば、表面に複数の第1の電極が形成された第1の回路基材の上方に、第1の貫通孔と第2の貫通孔とが形成された第2の回路基材を配する工程と、半導体部品の複数の第2の電極の各々の上に形成された複数の第1のバンプを前記第1の貫通孔と前記第2の貫通孔に通し、前記第1の回路基材の複数の前記第1の電極に前記複数の第1のバンプを当接させる工程と、前記第1のバンプを加熱して溶融させ、前記第1の電極に前記第1のバンプを接合させる工程とを有する半導体装置の製造方法が提供される。

【0007】

更に、その開示の別の観点によれば、第1の回路基材が備える複数の第1のバンプの各々に、第2の回路基材の複数の貫通孔の各々を嵌合させる工程と、前記回路基材の前記複数の貫通孔の各々に、半導体部品が備える複数の第2のバンプの各々を嵌合させる工程と、前記第1のバンプと前記第2のバンプの各々を加熱して溶融し、該第1のバンプと該第2のバンプの各々を介して前記第1の回路基材と前記半導体部品とを電気的かつ機械的に接続する工程とを有する半導体装置の製造方法が提供される。

【発明の効果】

【0008】

以下の開示によれば、第2の回路基材の第1の貫通孔と前記第2の貫通孔に半導体部品のバンプを通すので、これらの貫通孔により溶融したバンプの動きを規制することができ、第1の回路基材の電極とバンプとの間に位置ずれが発生するのを防止することができる。

【図面の簡単な説明】

【0009】

【図1】図1(a)、(b)は、インターポーザを利用した半導体装置の製造途中の断面図である。

【図2】図2は、第1実施形態に係る半導体装置の製造途中の断面図(その1)である。

【図3】図3は、第1実施形態に係る半導体装置の製造途中の断面図(その2)である。

【図4】図4は、第1実施形態に係る半導体装置の製造途中の断面図(その3)である。

【図5】図5は、第1実施形態に係る半導体装置の製造途中の断面図(その4)である。

【図6】図6は、第1実施形態に係る半導体装置の製造途中の断面図(その5)である。

【図7】図7は、第1実施形態に係る半導体装置の製造途中の断面図(その6)である。

【図8】図8は、第1実施形態で使用する第2の回路基材の拡大平面図である。

【図9】図9は、第2実施形態に係る半導体装置の製造途中の断面図(その1)である。

【図10】図10は、第2実施形態に係る半導体装置の製造途中の断面図(その2)である。

【図11】図11は、第2実施形態に係る半導体装置の製造途中の断面図(その3)である。

【図12】図12は、第2実施形態に係る半導体装置の製造途中の断面図(その4)である。

【図13】図13は、第3実施形態に係る半導体装置の製造途中の断面図(その1)である。

【図14】図14は、第3実施形態に係る半導体装置の製造途中の断面図(その2)である。

【図15】図15は、第3実施形態に係る半導体装置の製造途中の断面図(その3)である。

【図16】図16は、第4実施形態に係る半導体装置の製造途中の断面図(その1)である。

【図17】図17は、第4実施形態に係る半導体装置の製造途中の断面図(その2)である。

【図18】図18は、第4実施形態に係る半導体装置の製造途中の断面図(その3)である。

【図19】図19は、第5実施形態に係る半導体装置の断面図である。

【発明を実施するための形態】

【0010】

半導体パッケージ等の半導体部品を回路基材に実装する形態として、半導体部品と回路基板との間に配線を中継するためのインターポーザを設ける形態がある。

【0011】

各実施形態の説明に先立ち、そのようなインターポーザを利用した半導体装置の製造方法について説明する。

【0012】

図1(a)、(b)は、その半導体装置の製造途中の断面図である。

【0013】

まず、図1(a)に示すように、一方の主面上に第1の電極3が設けられた回路基材1を用意し、その回路基材1とインターポーザ4との位置合わせを行う。

【0014】

インターポーザ4は、ポリイミド等の可撓性基材に第2の電極6を形成してなり、その第2の電極6上には第1のはんだバンプ5が接合される。

【0015】

そして、第1のはんだバンプ5が第1の電極3に当接した状態で、その第1のはんだバンプ5をリフローすることにより、第1のはんだバンプ5を介して回路基材1とインターポーザ4とを機械的かつ電気的に接続する。

【0016】

次に、図1(b)に示すように、インターポーザ4の上に半導体パッケージ10を載置する。

【0017】

その半導体パッケージ10はパッケージ基材15を備えており、そのパッケージ基材15の二つの主面のうちインターポーザ4に対向する主面には第2のはんだバンプ8が設けられる。

【0018】

一方、パッケージ基材15の他方の主面上には第3の電極14が形成され、半導体素子13が第3のはんだバンプ12を介してその第3の電極14と接続されている。

【0019】

なお、半導体素子13とパッケージ基材15との間の隙間には、これらの接続信頼性を向上させるためのアンダーフィル樹脂19が充填される。

【0020】

そして、第2のはんだバンプ8と第2の電極6とが位置合わせされた状態で、この第2のはんだバンプ8をリフローすることにより、第2の電極6に第2のはんだバンプ8を接合する。

【0021】

以上により、この半導体装置の基本構造が完成したことになる。

【0022】

このような半導体装置の製造方法では、図1(b)のリフローの際、第2の電極6と第2のはんだバンプ8とが接合されるように、半導体パッケージ10とインターポーザ4とを位置合わせする必要がある。

【0023】

しかしながら、回路基材1、インターポーザ4、及び半導体パッケージ10は、材料の相違が原因で各々の熱膨張量が異なるので、図1(b)の工程で各はんだバンプ8をリフローする際に互いに異なる量で伸長してしまう。

【0024】

そのため、リフロー時に第2の電極6と第2のはんだバンプ8とが位置ずれを起こし、高精度な位置合わせが困難である。

【0025】

特に、インターポーザ4は、熱膨張率の大きなポリイミドを主にしてなるため、位置合わせの困難性を更に助長してしまう。

【0026】

しかも、この実装構造では、第1のはんだバンプ5と第2のはんだバンプ8の各々の高さと、インターポーザ4の厚さとを合わせた間隔Dだけ半導体パッケージ10が回路基材1から隔てられる。そのため、半導体パッケージ10から回路基材1への配線の引き回し距離が長くなり、RC遅延によって半導体パッケージ10の高速動作を妨げてしまう。

【0027】

このように、回路基材1と半導体パッケージ10との間に単にインターポーザ4を設けたのでは、位置合わせの困難性や信号処理速度の低下といった問題が生じることになる。

【0028】

このような問題に鑑み、本願発明者は以下に説明するような各実施形態に想到した。

【0029】

(第1実施形態)

図2〜図7は、本実施形態に係る半導体装置の製造途中の断面図である。

【0030】

この半導体装置を製造するには、まず、図2に示すように、実装基板等として供せられる第1の回路基材20を用意する。

【0031】

第1の回路基材20は、ガラスエポキシ樹脂等よりなり、その表面上には銅箔や銅めっき膜をパターニングしてなる複数の第1の電極22が形成される。

【0032】

なお、第1の回路基材20としては、複数の配線と絶縁層を積層してなる多層回路基板を使用してもよい。更に、第1の回路基材20の剛性も特に限定されず、可撓性のある回路基材やリジッドな回路基材のどちらも第1の回路基材20として採用し得る。

【0033】

また、このような第1の回路基材20と共に、図3に示すように、第1の貫通孔30aと第2の貫通孔30bが複数形成された第2の回路基材30を用意する。なお、この第2の回路基材30の端部に、信号を引き出すためのコネクタ60を設けてもよい。

【0034】

この第2の回路基材30は、点線円内に示すように、各層31〜40を積層してなる積層構造を有する。その積層構造は、下から順に、第1のカバーレイ31、第1の絶縁層32、第1のグランド配線33、第1の接着層34、第2の絶縁層35、信号配線36、第2の接着層37、第3の絶縁層38、第2のグランド配線39、第2のカバーレイ40を有する。

【0035】

このうち、第1〜第3の絶縁層32、35、38としては樹脂のみからなる可撓性の樹脂フィルムが用いられ、本実施形態ではポリイミドフィルムの一種である宇部興産株式会社製のユーピレックスを使用する。また、これらの絶縁層32、35、38の厚さは特に限定されないが、本実施形態では約15μmの厚さに各絶縁層を形成する。

【0036】

このように可撓性のある各絶縁層32、35、38を使用することで、第2の回路基材30自体も可撓性を呈するようになる。

【0037】

一方、第1及び第2の接着層34、37としては、絶縁性のある厚さ約15μmの京セラケミカル社製のTFA-860FBを使用する。

【0038】

更に、第1及び第2のグランド配線33、39と、信号配線36としては、厚さが約9μmの電解銅めっき膜を使用する。信号配線36は第2の絶縁層35の上面上に形成されており、その信号配線36と第2の絶縁層35とを覆うように第3の絶縁層38が形成される。

【0039】

本実施形態では、これら各層31〜40を張り合わせて厚さが約0.1mmの積層体を形成した後、ドリル加工によって直径が約0.7mmの第1の貫通孔30aと第2の貫通孔30bをその積層体に形成し、第2の回路基材30を作製する。

【0040】

このようにして形成された各貫通孔30a、30bのうち、第2の貫通孔30bにおいては、その内面30yに信号配線36が露出する。

【0041】

一方、第1の貫通孔30aにおいては、信号配線36は絶縁性の第2の接着層37によって、当該貫通孔30aの内面30xから隔離されている。

【0042】

図8は、この第2の回路基材30の拡大平面図である。

【0043】

図8に示されるように、第1のグランド配線33と第2のグランド配線39は、第2の回路基材30において、各貫通孔30a、30bを除く領域の全面に形成される。

【0044】

一方、信号配線36はライン状の平面形状を有しており、二本の信号配線36が対になって差動配線として機能する。差動配線においては、二本の信号配線36に位相が互いに逆の信号が供給され、ノイズ耐性の向上やデバイスの高速化に有利である。

【0045】

更に、これらグランド配線33、39と信号配線36は、ストリップ配線構造となっており、高周波信号の伝送に好適である。

【0046】

また、上記した第2の回路基材30と共に、図4に示すような半導体パッケージ50を用意する。

【0047】

その半導体パッケージ50は、いわゆるBGA(Ball Grid Array)型のパッケージであって、パッケージ基材53と半導体素子58とを備える。

【0048】

パッケージ基材53の両主面のうち、半導体素子58が搭載されていない側の主面には第2の電極52がグリッド状に複数設けられる。

【0049】

第2の電極52は、銅めっき膜等をパターニングしてなり、その表面には第1のはんだバンプ51が接合される。

【0050】

一方、半導体素子58が搭載されている側のパッケージ基材53の主面には銅めっき膜をパターニングしてなる第3の電極56が形成されており、その第3の電極56に突起電極57が接合される。

【0051】

突起電極57は、例えばはんだバンプであって、半導体素子58の不図示の電極にも接合される。

【0052】

そして、パッケージ基材53と半導体素子58の間の隙間には、これらの間の接続信頼性を高めるべくアンダーフィル樹脂59が充填される。

【0053】

続いて、図5に示すように、下から順に第1の回路基材20、第2の回路基材30、及び半導体パッケージ50を配する。そして、第1の電極パッド22の上方に各貫通孔30a、30bが位置するように、第1の回路基材20と第2の回路基材30との位置合わせを行う。

【0054】

同様に、第2の回路基材30と半導体パッケージ50との位置合わせを行い、各貫通孔30a、30bの上方に第1のはんだバンプ51が位置するようにする。

【0055】

次いで、図6に示すように、半導体パッケージ50が備える複数の第1のはんだバンプ51を第1の貫通孔30aと第2の貫通孔30bに通し、第1の回路基材20の表面に形成された複数の第1の電極22に各はんだバンプ51を当接させる。

【0056】

このとき、隣接する第1のはんだバンプ51同士の間隔や、はんだバンプ51の直径にばらつきがあることがあるので、そのばらつきを寛容できるように各貫通孔30a、30bの直径を第1のはんだバンプ51のそれよりも大きくしておくのが好ましい。

【0057】

例えば、第1のはんだバンプ51の直径が約0.6μmのときは、これよりも大きい約0.7μmの直径に各貫通孔30a、30bを形成するのが好ましい。

【0058】

次に、図7に示すように、第1のはんだバンプ51の融点よりも高い温度に当該はんだバンプ51をリフローして加熱することにより、はんだバンプ51を溶融させて第1の電極22に接合させる。

【0059】

このとき、各回路基材20、30と半導体パッケージ50は材料の相違に起因して互いに異なる量で熱膨張をする。

【0060】

但し、本実施形態では、第2の回路基材30の各貫通孔30a、30bが第1のはんだバンプ51を保持するように機能するので、上記の熱膨張量の相違に起因して各回路基材20、30や半導体パッケージ50が位置ずれするのを抑制できる。

【0061】

その後、第1のはんだバンプ51を冷却して固化することで、上記した第1の回路基材20、第2の回路基材30、及び半導体パッケージ50が第1のはんだバンプ51により互いに機械的且つ電気的に接続される。

【0062】

既述のように、各貫通孔30a、30bのうち、第1の貫通孔30aにおいては各配線33、36、39が当該貫通孔30aの内面に露出していない。よって、第1の貫通孔30a内の第1のはんだバンプ51は、第2の回路基材30の各配線33、36、39に接続されることはない。

【0063】

一方、第2の貫通孔30bにおいては、その内面に信号配線36が露出しているので、第1のはんだバンプ51はその信号配線36と電気的に接続され、半導体パッケージ50の所定の信号が第2の回路基材20に流されることになる。

【0064】

そして、その信号は、第2の回路基材20に接続されたコネクタ60を介して、他の電子部品等に入出力される。このように、この半導体装置においては、半導体パッケージ50の所定の信号とそれ以外の信号とを分離し、それらを第1の回路基材20と第2の回路基材30のそれぞれに分けて供給することができる。

【0065】

以上により、本実施形態に係る半導体装置の基本構造が完成したことになる。

【0066】

上記した本実施形態によれば、図7に示したように、第2の回路基材30に貫通孔30a、30bを設け、これらの貫通孔30a、30bに第1のはんだバンプ51を通すようにした。

【0067】

このようにすると、第1のはんだバンプ51をリフローするとき、第2の回路基材30の各貫通孔30a、30bが溶融した第1のはんだバンプ51を保持し、第1のはんだバンプ51の動きを規制するように機能する。そのため、材料の相違に起因してリフロー時の熱膨張量が各回路基材20、30と半導体パッケージ50の各々で異なる場合でも、第1のはんだバンプ51と各電極22、52との間に位置ずれが発生するのを防止できる。

【0068】

しかも、本実施形態では、図1(b)のように二段のはんだバンプ5、6を設けず、第1のはんだバンプ51の一段のみを利用して第1の回路基材20上に半導体パッケージ50を実装する。

【0069】

そのため、実装時に行うリフローの回数がはんだバンプ51に対する1回のみとなり、図1(a)、(b)のようにリフローを二回行う場合と比較して、リフロー時に第1のはんだバンプ51と各電極22、52とが位置ずれする危険性を更に低減できる。

【0070】

更に、このように第1のはんだバンプ51を1段のみ設けることで、図1(b)の例と比較して第1の回路基材20と半導体パッケージ50との間隔Lを狭めることができる。これにより、半導体パッケージ50から第1の回路基材20までの配線の引き回し距離を短くでき、RC遅延が抑制されて高速動作が可能な半導体装置を提供することができる。

【0071】

また、半導体パッケージ50の所定の信号については、第2の貫通孔30bから第2の回路基材30の信号配線36に流すようにした。既述のように、その信号配線36は二本が対となって差動配線として機能するので、上記の信号のノイズレベルを低い状態に維持しながら、デバイスの高速化を実現することができる。

【0072】

特に、信号配線36は、ポリイミドのように誘電率が均一な樹脂のみからなる第2の絶縁層35と第3の絶縁層38で挟まれているので、信号経路に沿う周囲の誘電率の変動が小さい。

【0073】

これに対し、熱硬化性樹脂をガラスクロスに含浸させてなるコンポジット材料を使用する回路基材では、ガラスクロスの誘電率が熱硬化性樹脂のそれよりも高いため、ガラスクロスの織目付近で信号配線の周囲の誘電率が変動する。よって、この場合は、差動信号配線の二つの信号配線間で信号の伝播時間に遅延が生じ、その遅延が許容範囲を超えると、半導体パッケージ50において当該信号の処理ができなくなる。

【0074】

本実施形態では、各絶縁層35、38や接着層34、37が樹脂のみからなり、ガラスクロスを使用していないので、ガラスクロスの織り目が原因で信号の伝播時間に遅延が生じるおそれがなく、半導体パッケージ50において信号を高速に処理することができる。

【0075】

(第2実施形態)

次に、第2実施形態について説明する。

【0076】

本実施形態では、第1実施形態と比較して半導体装置の微細化に有利な技術について説明する。

【0077】

図9〜図12は、本実施形態に係る半導体装置の製造途中の断面図である。なお、これらの図において第1実施形態で説明したのと同じ要素には第1実施形態で説明したのと同じ符号を付し、以下ではその説明を省略する。

【0078】

この半導体装置を製造するには、まず、図9に示すように、第1実施形態で説明した第2の回路基材30を用意する。

【0079】

但し、本実施形態では、その第2の回路基材30の二つの主面のうち、後述の第1の回路基材に対向する主面に予め複数の凹部30cを形成しておく。

【0080】

その凹部30cの形成方法は特に限定されない。例えば、炭酸ガスレーザの照射によって第2の回路基材30の所定部分を蒸散させて凹部30cを形成し得る。或いは、不図示のレジストパターンをマスクに用い、ウエットエッチングにより第2の回路基材30の所定部分を除去して凹部30cを形成してもよい。いずれの場合でも、信号配線36がレーザやウエットエッチングに対するストッパとして機能し、凹部30cは信号配線36よりも深く形成されることはない。

【0081】

次いで、図10に示すように、凹部30c内に第2のはんだバンプ61を設け、凹部30cの底面に露出している信号配線36の上にその第2のはんだバンプ61を接合する。

【0082】

その第2のはんだバンプ61の直径は特に限定されないが、第1実施形態で説明した第1のはんだバンプ51(図4参照)よりも小さい直径、例えば0.2mm〜0.4mm程度とするのが好ましい。

【0083】

また、第2のはんだバンプ61の材料も特に限定されず、第1のはんだバンプ51と同一の材料を使用し得る。

【0084】

次に、図11に示すように、半導体パッケージ50が備える複数の第1のはんだバンプ51を第1の貫通孔30aと第2の貫通孔30bに通し、第1の電極22にその第1のはんだバンプ51を当接させる。

【0085】

また、本実施形態では、第1の回路基板20の表面に複数の第3の電極23が形成されており、本工程ではそれらの第3の電極23に第2のはんだバンプ61を当接させる。

【0086】

その後、図12に示すように、各はんだバンプ51、61の融点よりも高い温度に当該はんだバンプ51、61をリフローして加熱することにより、各はんだバンプ51、61を溶融させてそれらを各電極22、23に接合させる。

【0087】

以上により、本実施形態に係る半導体装置の基本構造が完成したことになる。

【0088】

本実施形態によれば、第1のはんだバンプ51の他に、第2の回路基材30の凹部30cに第2のはんだバンプ61を設けたので、第1実施形態と比較して各はんだバンプ51、61の配置が高密度になる。

【0089】

そのため、第1の回路基材20の隣接する二つの第3の電極23同士の間隔Pを詰めることができ、半導体装置の微細化に寄与することが可能となる。

【0090】

更に、その第2のはんだバンプ61の直径を第1のはんだバンプ51のそれよりも小さくすることで、第3の電極23同士の間隔Pを更に小さくすることができ、半導体装置の一層の微細化を図ることができるようになる。

【0091】

しかも、第2のはんだバンプ61を設けたことで、信号配線36と第3の電極23との間隔Tが狭まるので、第1実施形態よりもRC遅延を効率的に抑えることができ、半導体装置の一層の高速化を図ることもできるようになる。

【0092】

(第3実施形態)

上記した第2実施形態では、図12に示したように、第2の回路基材30の二つの主面のうち、第1の回路基材20に対向する面側に第2のはんだバンプ61を設けることで、第1の回路基材20の第3の電極23同士の間隔Pを詰めるようにした。

【0093】

これに対し、本実施形態では、第2実施形態と比較して第2の回路基材30を上下逆にして用いることで、半導体パッケージ50の電極同士の間隔を詰めるようにする。

【0094】

図13〜図15は、本実施形態に係る半導体装置の製造途中の断面図である。なお、これらの図において、第2実施形態で説明したのと同じ要素には第2実施形態におけるのと同じ符号を付し、以下ではその説明を省略する。

【0095】

まず、図13に示すように、第2のはんだバンプ61を上側にして第2の回路基材30を用意する。

【0096】

第2実施形態で説明したように、各々の第2のはんだバンプ61は、凹部30cの底面に露出している信号配線36の上に接合される。また、各々の第2のはんだバンプ61の直径は、第1実施形態で説明した第1のはんだバンプ51(図4参照)よりも小さな0.2mm〜0.4mm程度の値を有する。

【0097】

次に、図14に示すように、半導体パッケージ50が備える複数の第1のはんだバンプ51を第1の貫通孔30aと第2の貫通孔30bに通し、第1の回路基材20の第1の電極22にその第1のはんだバンプ51を当接させる。

【0098】

ここで、本実施形態における半導体パッケージ50の表面には、第2の電極52の他に複数の第4の電極54が設けられる。

【0099】

本工程では、それら第4の電極54に上記の第2のはんだバンプ61を当接させる。

【0100】

次いで、図15に示すように、各はんだバンプ51、61の融点よりも高い温度に当該はんだバンプ51、61をリフローして加熱することにより、各はんだバンプ51、61を溶融させてそれらを第1の電極22と第4の電極54に接合させる。

【0101】

以上により、本実施形態に係る半導体装置の基本構造が完成したことになる。

【0102】

本実施形態によれば、第2実施形態と同様に、第1のはんだバンプ51の他に第2のはんだバンプ61を設けたので、第1実施形態と比較して各はんだバンプ51、61の配置が高密度になる。

【0103】

そして、そのように高密度に配された第2のはんだバンプ61を介して半導体パッケージ50と第2の回路基材30とを接続するので、半導体パッケージ50の第4の電極54の配置密度を第2のはんだバンプ61に合わせて高密度化できる。

【0104】

これにより、半導体パッケージ50の隣接する二つの第4の電極54同士の間隔Sを詰めることができ、半導体装置の微細化に寄与することが可能となる。

【0105】

(第4実施形態)

第1実施形態では、図5に示したように、第1の回路基材20に半導体パッケージ50を実装するに際し、半導体パッケージ50にのみ第1のはんだバンプ51を設け、第1の回路基材20にははんだバンプを設けなかった。

【0106】

これに対し、本実施形態では、以下のようにして第1の回路基材20と半導体パッケージ50の各々にはんだバンプを設ける。

【0107】

図16〜図18は、本実施形態に係る半導体装置の製造途中の断面図である。なお、これらの図において、第1実施形態で説明したのと同じ要素には第1実施形態におけるのと同じ符号を付し、以下ではその説明を省略する。

【0108】

この半導体装置を製造するには、まず、図16に示すように、第1の回路基材20、第2の回路基材30、及び半導体パッケージ50を用意する。

【0109】

このうち、半導体パッケージ50の第2の電極52には、第1実施形態と同様に複数の第1のはんだバンプ51が接合される。

【0110】

一方、第1の回路基材20の第1の電極22には、複数の第2のはんだバンプ70が接合される。

【0111】

また、第2の回路基材30には、第1実施形態と同様に第1の貫通孔30aと第2の貫通孔30bが形成される。それらの貫通孔30a、30bの直径D1は特に限定されないが、直径D1を各バンプ51、70の各々の直径D2よりも小さくするのが好ましい。

【0112】

本実施形態では、貫通孔30a、30bの直径D1を約0.4mmとし、各バンプ51、70の直径D2を約0.6mmとする。

【0113】

なお、第1のはんだバンプ51と第2のはんだバンプ70の直径は同じである必要はなく、異なる直径であってもよい。

【0114】

次に、図17に示すように、第1の回路基材20に向けて第2の回路基材30を下ろし、第2のはんだバンプ70の各々に貫通孔30a、30bを嵌合させる。

【0115】

このとき、上記のように各貫通孔30a、30bの直径D1を第2のはんだバンプ70の直径D2よりも小さくしたので、本工程では第2のはんだバンプ70が各貫通孔30a、30bを通り抜けず、第2の回路基材30がはんだバンプ70により係止された状態となる。

【0116】

その後に、第2の回路基材30に向けて半導体部品50を降ろし、各貫通孔30a、30bに第1のはんだバンプ51を嵌合させる。

【0117】

本実施形態では、このように貫通孔30a、30bに各バンプ51、70を嵌合させることで、各回路基板20、30や半導体パッケージ50の相互の位置が自己整合的に定まり、これらの位置合わせが容易になる。

【0118】

続いて、図18に示すように、各はんだバンプ51、70を加熱して溶融することにより柱状の接続媒体75を形成する。そして、その接続媒体75が冷えて固化することで、第1の回路基材20の第1の電極22と半導体部品50の第2の電極52とが電気的かつ機械的に接続される。

【0119】

また、第2の貫通孔30bの内面に露出していた信号配線36は上記の接続媒体75に接続され、これにより半導体パッケージ50の所定の信号は第2の回路基材30に流されることになる。

【0120】

一方、第1実施形態で説明したように、第1の貫通孔30aにおいては、その内面に信号配線36が露出していないので、信号配線36と接続媒体75とが接続されることはない。

【0121】

ここで、接続媒体75により貫通孔30a、30bを隙間なく充填するには、図17に示したように、溶融前の各はんだバンプ51、70が互いに離間することなく、各々の頂点が接しているのが好ましい。

【0122】

以上により、本実施形態に係る半導体装置の基本構造が完成したことになる。

【0123】

上記した本実施形態によれば、図17を参照して説明したように、第2の回路基材30の各貫通孔30a、30bに各はんだバンプ51、70を嵌合させる。これにより、各回路基材20、30と半導体パッケージ50の相互の位置を自動的に決定でき、これらの位置合わせを簡単に行うことができる。

【0124】

また、図18に示したように、各はんだバンプ51、70を溶融してなる接続媒体75は、各はんだバンプ51、70を上下方向に繋げたような形となり、幅Wよりも高さHの方が長い柱状となる。

【0125】

ここで、各回路基材20、30や半導体パッケージ50は、それらの材料の違いから互いに異なる熱膨張量を有する。そのような熱膨張量の相違が原因で接続媒体75には応力が加わることになるが、高さ方向に長い接続媒体75は自身が変形してその応力を吸収し易い特性があるため、応力が原因で接続媒体75と各電極22、51との間に接続不良が発生する危険性が減る。

【0126】

しかも、接続媒体75の形成前に、熱履歴等が原因で第1の回路基材20や半導体パッケージ50に反りが発生し、対向する電極22、52同士の間隔が場所により変動している場合でも、柱状の接続媒体75によりその間隔の変動を吸収できる。これにより、第1の回路基材20等の反りが原因で発生する回路基材20と半導体パッケージ50との接続不良を防止でき、半導体装置の信頼性を高めることが可能となる。

【0127】

更に、本実施形態では、各貫通孔30a、30bの直径D1を、上記のように各バンプ51、70の直径D2よりも小さくする。そのため、直径D1が直径D2よりも大きい場合と比較して、第2の回路基材30において信号配線36が占める領域を増やすことができる。

【0128】

(第5実施形態)

図19は、本実施形態に係る半導体装置の断面図である。なお、図19において第1実施形態でしたのと同じ要素には第1実施形態と同じ符号を付し、以下ではその説明を省略する。

【0129】

本実施形態では、図19に示すように、第2の回路基材30の上方に二つの半導体パッケージ50を並べて設けるようにする。

【0130】

このように第1の回路基材20の上に複数の半導体パッケージ50を搭載することで、半導体パッケージ50を一つだけ搭載する場合と比較して、半導体装置全体の高機能化を図ることが可能となる。

【0131】

しかも、第2の回路基材30は可撓性を有しているので、図13の点線Qのように第2の回路基材30が撓むことで、各半導体パッケージ50と各回路基材30、50との位置合わせに余裕を持たせることもできる。

【0132】

なお、この例では第1の回路基材20上に二つの半導体パッケージ50を搭載したが、半導体パッケージ50の個数はこれに限定されず、三以上の半導体パッケージ50を搭載するようにしてもよい。

【0133】

以上、各実施形態について詳細に説明したが、各実施形態は上記に限定されない。

【0134】

例えば、第1〜第5実施形態では第1の回路基材20に半導体パッケージ50を搭載したが、搭載可能な半導体部品は半導体パッケージ50に限定されず、半導体部品として半導体素子を第1の回路基材20に搭載してもよい。

【0135】

以上説明した各実施形態に関し、更に以下の付記を開示する。

【0136】

(付記1) 表面に複数の第1の電極が形成された第1の回路基材と、

前記第1の回路基材の上方に設けられ、前記複数の第1の電極の各々の上方に第1の貫通孔と第2の貫通孔とが形成された第2の回路基材と、

前記第2の回路基材の上方に設けられ、表面に複数の第2の電極が形成された半導体部品と、

前記第1の貫通孔内と前記第2の貫通孔内に設けられ、前記第1の電極と前記第2の電極とを接続する複数の第1のバンプと、

を有することを特徴とする半導体装置。

【0137】

(付記2) 前記第2の回路基材は配線を有し、

前記第1の貫通孔の内面が絶縁材料によって前記配線から隔離されたことを特徴とする付記1に記載の半導体装置。

【0138】

(付記3) 前記第2の回路基材は配線を有し、

前記第2の貫通孔の内面に前記配線が露出し、該配線が前記第1のバンプに接続されたことを特徴とする付記1に記載の半導体装置。

【0139】

(付記4) 前記第2の回路基材において前記配線が二本設けられ、二本の前記配線が対となって差動配線として機能することを特徴とする付記3に記載の半導体装置。

【0140】

(付記5) 前記第2の回路基材が、上面に前記配線が形成された樹脂からなる第1の絶縁層と、前記配線と前記第1の絶縁層とを覆う樹脂からなる第2の絶縁層とを有する付記4に記載の半導体装置。

【0141】

(付記6) 前記第1の回路基材の前記表面に形成された第3の電極と、

前記第2の回路基材に形成された配線とを更に有し、

前記第2の回路基材の二つの主面のうち、前記第1の回路基材に対向する主面に凹部が形成されたと共に、

前記第1のバンプよりも直径が小さい第2のバンプが前記凹部に設けられ、前記第1の回路基材の前記第3の電極と前記第2の回路基材の前記配線とが、前記第2のバンプにより接続されたことを特徴とする付記1〜5のいずれかに記載の半導体装置。

【0142】

(付記7) 前記半導体部品の前記表面に形成された第4の電極と、

前記回路基板に形成された配線とを更に有し、

前記第2の回路基材の二つの主面のうち、前記半導体部品に対向する主面に凹部が形成されたと共に、

前記第1のバンプよりも直径が小さい第2のバンプが前記凹部に設けられ、前記半導体部品の前記第4の電極と前記第2の回路基材の前記配線とが、前記第2のバンプにより接続されたことを特徴とする付記1〜5のいずれかに記載の半導体装置。

【0143】

(付記8) 前記第2の回路基材は可撓性を有することを特徴とする付記1〜7のいずれかに記載の半導体装置。

【0144】

(付記9) 前記第2の回路基材の縁にコネクタが設けられたことを特徴とする付記8に記載の半導体装置。

【0145】

(付記10) 前記第2の回路基板の上方に、前記半導体部品が並べて複数設けられたことを特徴とする付記8に記載の半導体装置。

【0146】

(付記11) 表面に複数の第1の電極が形成された第1の回路基材の上方に、第1の貫通孔と第2の貫通孔とが形成された第2の回路基材を配する工程と、

半導体部品の複数の第2の電極の各々の上に形成された複数の第1のバンプを前記第1の貫通孔と前記第2の貫通孔に通し、前記第1の回路基材の複数の前記第1の電極に前記複数の第1のバンプを当接させる工程と、

前記第1のバンプを加熱して溶融させ、前記第1の電極に前記第1のバンプを接合させる工程と、

を有することを特徴とする半導体装置の製造方法。

【0147】

(付記12) 前記第2の回路基材の二つの主面のうち、前記第1の回路基材に対向する主面に凹部を形成し、該凹部に前記第2の回路基材の配線を露出させる工程と、

前記凹部に、前記第1のバンプよりも直径が小さい第2のバンプを設け、前記配線と前記第2のバンプとを接続する工程とを更に有し、

前記複数の第1の電極に前記複数の第1のバンプを当接させる工程において、前記第1の回路基材の前記表面に形成された第3の電極に前記第2のバンプを当接させ、

前記第1の電極に前記第1のバンプを接合させる工程において、前記第3の電極に前記第2のバンプを接合させることを特徴とする付記11に記載の半導体装置の製造方法。

【0148】

(付記13) 前記第2の回路基材の二つの主面のうち、前記半導体部品に対向する主面に凹部を形成し、該凹部に前記第2の回路基材の配線を露出させる工程と、

前記凹部に、前記第1のバンプよりも直径が小さい第2のバンプを設け、前記配線と前記第2のバンプとを接続する工程とを更に有し、

前記複数の第1の電極に前記複数の第1のバンプを当接させる工程において、前記半導体部品の前記表面に形成された第4の電極に前記第2のバンプを当接させ、

前記第1の電極に前記第1のバンプを接合させる工程において、前記第4の電極に前記第2のバンプを接合させることを特徴とする付記11に記載の半導体装置の製造方法。

【0149】

(付記14) 第1の回路基材が備える複数の第1のバンプの各々に、第2の回路基材の複数の貫通孔の各々を嵌合させる工程と、

前記回路基材の前記複数の貫通孔の各々に、半導体部品が備える複数の第2のバンプの各々を嵌合させる工程と、

前記第1のバンプと前記第2のバンプの各々を加熱して溶融し、該第1のバンプと該第2のバンプの各々を介して前記第1の回路基材と前記半導体部品とを電気的かつ機械的に接続する工程と、

を有することを特徴とする半導体装置の製造方法。

【0150】

(付記15) 前記貫通孔の直径は、前記第1のバンプと前記第2のバンプの各々の直径よりも小さいことを特徴とする付記14に記載の半導体装置の製造方法。

【符号の説明】

【0151】

1…回路基材、3…第1の電極、4…インターポーザ、5…第1のはんだバンプ、6…第2のはんだバンプ、8…第2のはんだバンプ、10…半導体パッケージ、12…第3のはんだバンプ、13…半導体素子、14…第3の電極、15…パッケージ基材、19…アンダーフィル樹脂、20…第1の回路基材、22…第1の電極、23…第3の電極、30…第2の回路基材、30a…第1の貫通孔、30b…第2の貫通孔、30c…凹部、31…第1のカバーレイ、32…第1の絶縁層、33…第1のグランド配線、34…第1の接着層、35…第2の絶縁層、36…信号配線、37…第2の接着層、38…第3の絶縁層、39…第2のグランド配線、40…第2のカバーレイ、50…半導体パッケージ、51…第1のはんだバンプ、52…第2の電極、53…パッケージ基材、54…第4の電極、56…第3の電極、57…突起電極、58…半導体素子、59…アンダーフィル樹脂、61、70…第2のはんだバンプ、75…接続媒体。

【特許請求の範囲】

【請求項1】

表面に複数の第1の電極が形成された第1の回路基材と、

前記第1の回路基材の上方に設けられ、前記複数の第1の電極の各々の上方に第1の貫通孔と第2の貫通孔とが形成された第2の回路基材と、

前記第2の回路基材の上方に設けられ、表面に複数の第2の電極が形成された半導体部品と、

前記第1の貫通孔内と前記第2の貫通孔内に設けられ、前記第1の電極と前記第2の電極とを接続する複数の第1のバンプと、

を有することを特徴とする半導体装置。

【請求項2】

前記第2の回路基材は配線を有し、

前記第1の貫通孔の内面が絶縁材料によって前記配線から隔離されたことを特徴とする請求項1に記載の半導体装置。

【請求項3】

前記第2の回路基材は配線を有し、

前記第2の貫通孔の内面に前記配線が露出し、該配線が前記第1のバンプに接続されたことを特徴とする請求項1に記載の半導体装置。

【請求項4】

前記第2の回路基材において前記配線が二本設けられ、二本の前記配線が対となって差動配線として機能することを特徴とする請求項3に記載の半導体装置。

【請求項5】

前記第1の回路基材の前記表面に形成された第3の電極と、

前記第2の回路基材に形成された配線とを更に有し、

前記第2の回路基材の二つの主面のうち、前記第1の回路基材に対向する主面に凹部が形成されたと共に、

前記第1のバンプよりも直径が小さい第2のバンプが前記凹部に設けられ、前記第1の回路基材の前記第3の電極と前記第2の回路基材の前記配線とが、前記第2のバンプにより接続されたことを特徴とする請求項1〜4のいずれか1項に記載の半導体装置。

【請求項6】

前記半導体部品の前記表面に形成された第4の電極と、

前記回路基板に形成された配線とを更に有し、

前記第2の回路基材の二つの主面のうち、前記半導体部品に対向する主面に凹部が形成されたと共に、

前記第1のバンプよりも直径が小さい第2のバンプが前記凹部に設けられ、前記半導体部品の前記第4の電極と前記第2の回路基材の前記配線とが、前記第2のバンプにより接続されたことを特徴とする請求項1〜4のいずれか1項に記載の半導体装置。

【請求項7】

表面に複数の第1の電極が形成された第1の回路基材の上方に、第1の貫通孔と第2の貫通孔とが形成された第2の回路基材を配する工程と、

半導体部品の複数の第2の電極の各々の上に形成された複数の第1のバンプを前記第1の貫通孔と前記第2の貫通孔に通し、前記第1の回路基材の複数の前記第1の電極に前記複数の第1のバンプを当接させる工程と、

前記第1のバンプを加熱して溶融させ、前記第1の電極に前記第1のバンプを接合させる工程と、

を有することを特徴とする半導体装置の製造方法。

【請求項8】

前記第2の回路基材の二つの主面のうち、前記半導体部品に対向する主面に凹部を形成し、該凹部に前記第2の回路基材の配線を露出させる工程と、

前記凹部に、前記第1のバンプよりも直径が小さい第2のバンプを設け、前記配線と前記第2のバンプとを接続する工程とを更に有し、

前記複数の第1の電極に前記複数の第1のバンプを当接させる工程において、前記半導体部品の前記表面に形成された第4の電極に前記第2のバンプを当接させ、

前記第1の電極に前記第1のバンプを接合させる工程において、前記第4の電極に前記第2のバンプを接合させることを特徴とする請求項7に記載の半導体装置の製造方法。

【請求項9】

第1の回路基材が備える複数の第1のバンプの各々に、第2の回路基材の複数の貫通孔の各々を嵌合させる工程と、

前記回路基材の前記複数の貫通孔の各々に、半導体部品が備える複数の第2のバンプの各々を嵌合させる工程と、

前記第1のバンプと前記第2のバンプの各々を加熱して溶融し、該第1のバンプと該第2のバンプの各々を介して前記第1の回路基材と前記半導体部品とを電気的かつ機械的に接続する工程と、

を有することを特徴とする半導体装置の製造方法。

【請求項10】

前記貫通孔の直径は、前記第1のバンプと前記第2のバンプの各々の直径よりも小さいことを特徴とする請求項9に記載の半導体装置の製造方法。

【請求項1】

表面に複数の第1の電極が形成された第1の回路基材と、

前記第1の回路基材の上方に設けられ、前記複数の第1の電極の各々の上方に第1の貫通孔と第2の貫通孔とが形成された第2の回路基材と、

前記第2の回路基材の上方に設けられ、表面に複数の第2の電極が形成された半導体部品と、

前記第1の貫通孔内と前記第2の貫通孔内に設けられ、前記第1の電極と前記第2の電極とを接続する複数の第1のバンプと、

を有することを特徴とする半導体装置。

【請求項2】

前記第2の回路基材は配線を有し、

前記第1の貫通孔の内面が絶縁材料によって前記配線から隔離されたことを特徴とする請求項1に記載の半導体装置。

【請求項3】

前記第2の回路基材は配線を有し、

前記第2の貫通孔の内面に前記配線が露出し、該配線が前記第1のバンプに接続されたことを特徴とする請求項1に記載の半導体装置。

【請求項4】

前記第2の回路基材において前記配線が二本設けられ、二本の前記配線が対となって差動配線として機能することを特徴とする請求項3に記載の半導体装置。

【請求項5】

前記第1の回路基材の前記表面に形成された第3の電極と、

前記第2の回路基材に形成された配線とを更に有し、

前記第2の回路基材の二つの主面のうち、前記第1の回路基材に対向する主面に凹部が形成されたと共に、

前記第1のバンプよりも直径が小さい第2のバンプが前記凹部に設けられ、前記第1の回路基材の前記第3の電極と前記第2の回路基材の前記配線とが、前記第2のバンプにより接続されたことを特徴とする請求項1〜4のいずれか1項に記載の半導体装置。

【請求項6】

前記半導体部品の前記表面に形成された第4の電極と、

前記回路基板に形成された配線とを更に有し、

前記第2の回路基材の二つの主面のうち、前記半導体部品に対向する主面に凹部が形成されたと共に、

前記第1のバンプよりも直径が小さい第2のバンプが前記凹部に設けられ、前記半導体部品の前記第4の電極と前記第2の回路基材の前記配線とが、前記第2のバンプにより接続されたことを特徴とする請求項1〜4のいずれか1項に記載の半導体装置。

【請求項7】

表面に複数の第1の電極が形成された第1の回路基材の上方に、第1の貫通孔と第2の貫通孔とが形成された第2の回路基材を配する工程と、

半導体部品の複数の第2の電極の各々の上に形成された複数の第1のバンプを前記第1の貫通孔と前記第2の貫通孔に通し、前記第1の回路基材の複数の前記第1の電極に前記複数の第1のバンプを当接させる工程と、

前記第1のバンプを加熱して溶融させ、前記第1の電極に前記第1のバンプを接合させる工程と、

を有することを特徴とする半導体装置の製造方法。

【請求項8】

前記第2の回路基材の二つの主面のうち、前記半導体部品に対向する主面に凹部を形成し、該凹部に前記第2の回路基材の配線を露出させる工程と、

前記凹部に、前記第1のバンプよりも直径が小さい第2のバンプを設け、前記配線と前記第2のバンプとを接続する工程とを更に有し、

前記複数の第1の電極に前記複数の第1のバンプを当接させる工程において、前記半導体部品の前記表面に形成された第4の電極に前記第2のバンプを当接させ、

前記第1の電極に前記第1のバンプを接合させる工程において、前記第4の電極に前記第2のバンプを接合させることを特徴とする請求項7に記載の半導体装置の製造方法。

【請求項9】

第1の回路基材が備える複数の第1のバンプの各々に、第2の回路基材の複数の貫通孔の各々を嵌合させる工程と、

前記回路基材の前記複数の貫通孔の各々に、半導体部品が備える複数の第2のバンプの各々を嵌合させる工程と、

前記第1のバンプと前記第2のバンプの各々を加熱して溶融し、該第1のバンプと該第2のバンプの各々を介して前記第1の回路基材と前記半導体部品とを電気的かつ機械的に接続する工程と、

を有することを特徴とする半導体装置の製造方法。

【請求項10】

前記貫通孔の直径は、前記第1のバンプと前記第2のバンプの各々の直径よりも小さいことを特徴とする請求項9に記載の半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【公開番号】特開2011−103441(P2011−103441A)

【公開日】平成23年5月26日(2011.5.26)

【国際特許分類】

【出願番号】特願2010−190604(P2010−190604)

【出願日】平成22年8月27日(2010.8.27)

【出願人】(000005223)富士通株式会社 (25,993)

【Fターム(参考)】

【公開日】平成23年5月26日(2011.5.26)

【国際特許分類】

【出願日】平成22年8月27日(2010.8.27)

【出願人】(000005223)富士通株式会社 (25,993)

【Fターム(参考)】

[ Back to top ]