半導体装置とその製造方法

【課題】フリップチップ実装の際のアンダーフィル樹脂の流れ拡がりの問題を解決する。

【解決手段】半導体装置は、基板と、前記基板の主面上にフリップチップ状態で搭載された半導体素子と、前記基板の主面に於いて、前記半導体素子の少なくとも一つの縁部に沿って配設された第1の導電パタ―ンと、前記基板の主面上に於いて、前記第1の導電パタ―ンから離間し、かつ前記第1の導電パタ―ンに沿って配設された第2の導電パタ―ンと、前記基板の主面上に於いて、前記第1の導電パタ―ンと第2の導電パタ―ンとの間に橋絡状態をもって配置された受動素子と、前記基板と前記半導体素子との間に充填された樹脂とを有し、前記樹脂は、前記基板の主面に於いて、前記半導体素子と前記第1の導電パタ―ンと間に延在する。

【解決手段】半導体装置は、基板と、前記基板の主面上にフリップチップ状態で搭載された半導体素子と、前記基板の主面に於いて、前記半導体素子の少なくとも一つの縁部に沿って配設された第1の導電パタ―ンと、前記基板の主面上に於いて、前記第1の導電パタ―ンから離間し、かつ前記第1の導電パタ―ンに沿って配設された第2の導電パタ―ンと、前記基板の主面上に於いて、前記第1の導電パタ―ンと第2の導電パタ―ンとの間に橋絡状態をもって配置された受動素子と、前記基板と前記半導体素子との間に充填された樹脂とを有し、前記樹脂は、前記基板の主面に於いて、前記半導体素子と前記第1の導電パタ―ンと間に延在する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は半導体装置に係り、特に配線基板上に半導体素子をフリップチップ実装した半導体装置、およびその製造方法に関する。

【背景技術】

【0002】

フリップチップ実装は今日の半導体装置において広く使われている技術である。

【0003】

フリップチップ実装では、配線パタ―ンが形成された配線基板の主面上に半導体素子が、電極パッドが形成された面を前記主面に対向させて載置され、前記電極パッドを前記配線パタ―ンに半田バンプなどにより接続する。

【0004】

フリップチップ実装を行うことにより、半導体素子と配線基板との間の配線長が短縮され、寄生インピーダンス或いは寄生インダクタンスの効果を低減することができる。また半導体素子で生じた熱を、半田バンプを介して効率的に配線基板へと散逸させることができる。

【0005】

フリップチップ実装では、このように半導体素子を配線基板上に実装した後、前記半田バンプおよび配線パタ―ンを保護し、また半導体素子を機械的に支持するため、半導体素子と配線基板との間の隙間に、アンダーフィル樹脂が注入される。アンダーフィル樹脂の充填は、一般に毛細管現象を使って行われ、このため、このようなアンダーフィル樹脂としては、ボイドの巻き込み或いは未充填の問題が生じないように、流動性および濡れ性に優れた樹脂が使われる。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2006−140327号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

半導体素子を配線基板上に搭載し半導体装置を形成する際、当該半導体素子の電源回路のON,OFFに伴い雑音(ノイズ)が生ずるなどして電源電圧が変動することにより、当該半導体素子の動作が不安定なものとなることを防止する為に、前記半導体素子の近傍に於いて、電源線と接地線(グランド線)との間に容量素子が配置される。

【0008】

当該容量素子としては、例えば容量が100pF程度、外形寸法1.6×0.8mm角程のセラミックキャパシタが適用される。

【0009】

当該容量素子は、その形状から、チップ型容量素子と称される。

【0010】

例えば半導体素子中のトランジスタが一斉にONした場合などには、電源線に大きな負荷がかかり、電源電圧が低下し、一方これらのトランジスタが一斉にOFFした場合には、電源ラインに大きなサージが発生する。

【0011】

チップ型容量素子は、このような電源ラインの電圧変動を平滑化して、安定した電源電圧の供給を可能にする。

【0012】

また、前記半導体素子の周囲には、前記アンダーフィル樹脂が拡がり、流動性および濡れ性の良い樹脂ほど遠方まで拡がる傾向がある。

【0013】

そこで、従来、チップ型容量素子を配線基板上に配置する場合には、当該アンダーフィル樹脂の拡がりを避けて、半導体素子から離間して配置する必要があった。

【0014】

しかし、チップ型容量素子を半導体素子から離間して配置すると、その間の配線パタ―ンに起因する寄生インダクタンス或いは寄生キャパシタンスにより、半導体装置全体の電気特性が低下してしまう。

【0015】

また、チップ型容量素子を半導体素子から離間して配置することにより、配線基板の面積の増大を招き、半導体装置として小形化が困難となる。

【0016】

さらに、前記アンダーフィル樹脂として、流動性および濡れ性に優れた樹脂を用いた場合、空間に注入したアンダーフィル樹脂が流出してしまい、半導体素子を側方から支える樹脂フィレットの形成が不十分となる。

【0017】

従来の半導体装置10の構成を、図1A,図1Bに示す。図1Bは、図1Aに於ける線A−A’に沿った断面を示す。

【0018】

図1Aおよび図1Bを参照するに、配線基板11の上側主面11Aには半導体素子12がフリップチップ状態で搭載されている。

【0019】

そして、配線基板11と半導体素子12の間の空間に注入されたアンダーフィル樹脂13が、前記配線基板11の上側主面11Aに於いて、半導体素子12が占有する領域を超えて、距離L1にわたり拡がっている。

【0020】

そして前記配線基板11の主面には、半導体素子12の近傍に、当該半導体素子12の側縁から距離L1以上離れて、チップ型容量素子14が配置されている。

【0021】

一方、配線基板11の下側主面11Bには、外部接続のための電極パッド11bが形成されている。

【0022】

前記チップ型容量素子14が前記アンダーフィル樹脂13により覆われてしまうと、図1A,図1Bの半導体装置が前記配線基板11上の電極パッド11bへの半田バンプ(ボール)の形成工程或いは放熱部材の半田付け工程などの後工程で熱処理を受けた場合、図2Aに示すようにチップ型容量素子14下部の、前記配線基板11との間の隙間において溶融半田が矢印方向に飛び出して短絡を生ずるか、あるいは図2Bに示すようにアンダーフィル樹脂層13が途切れた部分で溶融半田が矢印のように飛び出して半田ボール15Xを形成してしまう。

【0023】

ただし図2A,図2Bは、前記チップ型容量素子14を切る線A−A’に沿った断面図の一部であり、前記チップ型容量素子14は、セラミックキャパシタ本体となるセラミック部材14Cとその両側に形成された電極14A,14Bを有しており、また前記配線基板11の上側主面11A上には、前記電極14A,14Bにそれぞれ対応して電極パッド11a1,11a2が形成されている。

【0024】

前記電極14Aは前記電極パッド11a1に半田15Aにより接続され、前記電極14Bは前記電極パッド11a2に半田15Bにより接続される。なお図1および図2A,図2B中、配線基板11中に形成される多層配線構造については図示を省略している。

【0025】

図2Aを参照するに、前記チップ型容量素子14と配線基板11の上側主面11Aとの間には隙間ないし空間が形成されているが、先にも述べたように前記配線基板11に熱処理が加えられると、前記半田15A,15Bは溶融して矢印で示すように飛び出し、その結果形成される半田延出部15a,15bが短絡を生じてしまう恐れがある。

【0026】

また図2Bの例では、前記アンダーフィル樹脂13が途切れた部分において溶融半田が飛び出し、半田ボール15Xが形成されている。このようにして形成された半田ボール15Xは、図2B中、矢印でしめしたように飛び出すことがある。

【0027】

図2Cは、このような半田ボールの実際の例を示す写真である。ただし図2Cは前記配線基板11の上側主面11Aを垂直に見下ろした図であり、アンダーフィル樹脂13が黒く示されている。

【0028】

図2Cを参照するに、アンダーフィル樹脂の外縁13Eが白く輝いており、溶融半田がアンダーフィル樹脂の外縁13Eまで飛び出している。また所々に半田ボール15Xが形成されている。

【0029】

このように図1A,図1Bの半導体装置では、チップ型容量素子14は前記アンダーフィル樹脂13の外縁よりも外側に配置する必要があり、このため半導体素子12の外縁から距離L1以上離れた位置に形成する必要があった。前記図1A,図1Bの半導体装置10の場合、この距離L1は、2mmあるいはそれ以上になる場合があった。

【0030】

しかし、このようにチップ型容量素子14を半導体素子12から遠く離れた位置に形成すると、先にも述べたように配線の寄生インダクタンスや寄生インピーダンスの効果により、半導体装置の電気特性が劣化してしまう問題が生じる。

【0031】

またチップ型容量素子14を半導体素子12から離間して配置することにより、配線基板11の面積が増大し、半導体装置のサイズが増大してしまう問題が生じる。

【0032】

さらに先にも説明したように、前記アンダーフィル樹脂13は、高い流動性により前記配線基板11と半導体素子12との間の隙間から流れ出してしまう恐れがあり、アンダーフィル樹脂13による前記半導体素子11側面の力学的な支持が不十分となる恐れがある。

【課題を解決するための手段】

【0033】

実施形態の一観点によれば、基板と、前記基板の主面上にフリップチップ状態で搭載された半導体素子と、前記基板の主面に於いて、前記半導体素子の少なくとも一つの縁部に沿って配設された第1の導電パタ―ンと、前記基板の主面上に於いて、前記第1の導電パタ―ンから離間し、かつ前記第1の導電パタ―ンに沿って配設された第2の導電パタ―ンと、前記基板の主面上に於いて、前記第1の導電パタ―ンと第2の導電パタ―ンとの間に橋絡状態をもって配置された受動素子と、前記基板と前記半導体素子との間に充填された樹脂とを有し、前記樹脂は、前記基板の主面に於いて、前記半導体素子と前記第1の導電パタ―ンと間に延在することを特徴とする半導体装置が提供される。

【0034】

実施形態の他の観点によれば、基板の主面上に於ける、半導体素子の実装領域の近傍に、第1の導電パタ―ン及び第2の導体パターンを形成する工程と、前記第1の導電パタ―ンと第2の導体パターンとの間に、受動素子を、橋絡状態をもって配置する工程と、前記実装領域に、半導体素子をフリップチップ実装する工程と、前記基板と前記半導体素子との間に樹脂を充填する工程とを含むことを特徴とする半導体装置の製造方法が提供される。

【0035】

実施形態のさらに他の観点によれば、基板の主面上に於ける、半導体素子の実装領域の近傍に、第1の導電パタ―ン及び第2の導体パターンを形成する工程と、前記第1の導電パタ―ンと第2の導体パターンとの間に、受動素子を、橋絡状態をもって配置する工程と、前記実装領域上に樹脂を塗布する工程と、前記実装領域に、半導体素子をフリップチップ実装する工程とを含むことを特徴とする半導体装置の製造方法が提供される。

【発明の効果】

【0036】

前記第1の導電パタ―ンはアンダーフィル樹脂のダムとして作用し、前記半導体素子と配線基板との間にアンダーフィル樹脂を充填する際に、アンダーフィル樹脂が前記第1の導電パタ―ンを超えて流出することがない。

【0037】

そこで、前記第1の導電パタ―ンを前記半導体素子が占有する領域に近接して配設することにより、前記受動素子を前記半導体素子に近接して配置することが可能となる。これにより、半導体装置の電気特性を安定化させることが可能となる。

【図面の簡単な説明】

【0038】

【図1A】従来の半導体装置を示す平面図である。

【図1B】図1A中、線A−A’に沿った断面図である。

【図2A】図1A,図1Bの半導体装置における問題点を説明する断面図である。

【図2B】図1A,図1Bの半導体装置における問題点を説明する断面図である。

【図2C】図1A,図1Bの半導体装置における問題点を説明する写真を示す図である。

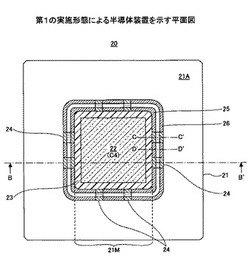

【図3A】第1の実施形態による半導体装置を示す平面図である。

【図3B】図3A中、線B−B’に沿った断面図である。

【図4A】図3A中、線C−C’に沿った拡大断面図である。

【図4B】図3A中、線D−D’に沿った拡大断面図である。

【図4C】図4A中、線d−d’に沿った断面図である。

【図5A】第1の実施形態による半導体装置の製造方法を説明する平面図(その1)である。

【図5B】第1の実施形態による半導体装置の製造方法を説明する断面図(その1)である。

【図6A】第1の実施形態による半導体装置の製造方法を説明する平面図(その2)である。

【図6B】第1の実施形態による半導体装置の製造方法を説明する断面図(その2)である。

【図7A】第1の実施形態による半導体装置の製造方法を説明する平面図(その3)である。

【図7B】第1の実施形態による半導体装置の製造方法を説明する断面図(その3)である。

【図8A】第1の実施形態による半導体装置の製造方法を説明する平面図(その4)である。

【図8B】第1の実施形態による半導体装置の製造方法を説明する断面図(その4)である。

【図9A】第1の実施形態による半導体装置の製造方法を説明する平面図(その5)である。

【図9B】第1の実施形態による半導体装置の製造方法を説明する断面図(その5)である。

【図10A】第1の実施形態による半導体装置の製造方法を説明する平面図(その6)である。

【図10B】第1の実施形態による半導体装置の製造方法を説明する断面図(その6)である。

【図11A】第1の実施形態における受動素子の実装の詳細を示す平面図である。

【図11B】図11A中、線F−F’に沿った断面を、半田リフロー前の状態で示す断面図である。

【図11C】図11A中、線F−F’に沿った断面を、半田リフロー後の状態で示す断面図である。

【図12】第1の実施形態の一変形例を示す拡大平面図である。

【図13A】第1の実施形態の一変形例を示す平面図である。

【図13B】第1の実施形態の一変形例を示す平面図である。

【図14A】第1の実施形態の一変形例を示す平面図である。

【図14B】図14Aで使われる多端子セラミックキャパシタを示す斜視図である。

【図14C】第1の実施形態の一変形例を示す平面図である。

【図15A】図10A,図10Bに引き続いて実行される半導体装置の製造工程を説明する断面図(その1)である。

【図15B】図10A,図10Bに引き続いて実行される半導体装置の製造工程を説明する断面図(その2)である。

【図15C】図10A,図10Bに引き続いて実行される半導体装置の製造工程を説明する断面図(その3)である。

【図16A】ダム作用が無い場合のアンダーフィル樹脂の濡れ拡がりの様子を示す写真である。

【図16B】ダム作用がある場合のアンダーフィル樹脂の濡れ拡がりの様子を示す写真である。

【図16C】図16B中、四角Aで囲んだ部分を詳細に示す拡大図である。

【図17】第1の実施形態の一変形例を示す断面図である。

【図18A】第1の実施形態の一変形例を示す平面図である。

【図18B】第1の実施形態の一変形例を示す平面図である。

【図18C】図18Aおよび図18B中、線G−G’に沿った断面図である。

【図18D】図18A中、線H−H’に沿った断面図である。

【図18E】図18B中、線I−I’に沿った断面図である。

【図19】第1の実施形態の一変形例を示す平面図である。

【図20A】第2の実施形態による半導体装置の製造方法を説明する平面図(その1)である。

【図20B】第2の実施形態による半導体装置の製造方法を説明する断面図(その1)である。

【図21A】第2の実施形態による半導体装置の製造方法を説明する平面図(その2)である。

【図21B】第2の実施形態による半導体装置の製造方法を説明する断面図(その2)である。

【図22A】第2の実施形態による半導体装置の製造方法を説明する平面図(その3)である。

【図22B】第2の実施形態による半導体装置の製造方法を説明する断面図(その3)である。

【図23A】第2の実施形態による半導体装置の製造方法を説明する平面図(その4)である。

【図23B】第2の実施形態による半導体装置の製造方法を説明する断面図(その4)である。

【図24A】第2の実施形態による半導体装置の製造方法を説明する平面図(その5)である。

【図24B】第2の実施形態による半導体装置の製造方法を説明する断面図(その5)である。

【図25A】第2の実施形態による半導体装置の製造方法を説明する平面図(その6)である。

【図25B】第2の実施形態による半導体装置の製造方法を説明する断面図(その6)である。

【図26A】第2の実施形態の一変形例による半導体装置を示す平面図である。

【図26B】図26A中、線K−K’に沿った断面図である。

【図26C】図26A中、線L−L’に沿った断面図である。

【図27】第3の実施形態による半導体装置を説明する平面図である。

【図28】第3の実施形態による半導体装置の比較例を示す平面図である。

【図29】第3の実施形態による半導体装置の別の比較例を示す平面図である。

【図30】第3の実施形態の一変形例を説明する平面図である。

【図31】第4の実施形態による半導体装置を説明する平面図である。

【図32】第5の実施形態による半導体装置を説明する平面図である。

【図33A】第6の実施形態による半導体装置を説明する平面図(その1)である。

【図33B】第6の実施形態による半導体装置を説明する平面図(その2)である。

【図34A】第6の実施形態の一変形例を説明する平面図(その1)である。

【図34B】第6の実施形態の一変形例を説明する平面図(その2)である。

【図35A】第6の実施形態の他の変形例を説明する平面図(その1)である。

【図35B】第6の実施形態の他の変形例を説明する平面図(その2)である。

【図36A】第6の実施形態のさらに他の変形例を説明する平面図(その1)である。

【図36B】第6の実施形態のさらに他の変形例を説明する平面図(その2)である。

【図37A】図36を、半導体素子およびアンダーフィル樹脂の一部まで含めて示す平面図である。

【図37B】図37A中、線M−M’に沿った断面図である。

【図37C】図37A中、線N−N’に沿った断面図である。

【図37D】図37A中、線O−O’に沿った断面図である。

【図37E】図37A中、線P−P’に沿った断面図である。

【図38】他の実施形態による半導体装置の例を示す平面図である。

【図39】他の実施形態による半導体装置の例を示す平面図である。

【図40A】さらに他の実施形態による半導体装置の例を示す断面図である。

【図40B】さらに他の実施形態による半導体装置の例を示す断面図である。

【図40C】さらに他の実施形態による半導体装置の例を示す断面図である。

【図40D】さらに他の実施形態による電子装置の例を示す断面図である。

【発明を実施するための形態】

【0039】

[第1の実施形態]

図3A,図3Bは、第1の実施形態によるシングルチップ構成の半導体装置20の構成を示す、それぞれ平面図および断面図である。ただし図3Bは、図3Aの中、線B−B’に沿った半導体装置20の断面を示す。

【0040】

図3Aおよび図3Bを参照するに、配線基板21の上側主面21Aには半導体素子22がフリップチップ状態で搭載されているが、前記上側主面21Aには、前記半導体素子22が占有する領域(C4)を含む領域21M(以下、実装領域と称する)を多重に囲繞して、例えば半田よりなる第1の導電パターン25が形成されており、さらにその外側に、前記第1の導体パタ―ン25を囲繞して、同じく例えば半田よりなる第2の導電パタ―ン26が形成されている。

【0041】

後で詳細に説明するように、前記第1の導体パタ―ン25は、前記配線基板21の主面と前記半導体素子22との間の隙間を充填するアンダーフィル樹脂23のダムとして作用し、前記アンダーフィル樹脂23は前記第1の導電パタ―ン25が画成する前記実装領域21Mの外側に拡がることがない。

【0042】

さらに本実施形態の半導体装置20では、前記半導体素子22を囲んで、前記第1の導電パタ―ン25と前記第2の導電パタ―ン26を架橋するように、多数のチップ型容量素子24が配置されている。

【0043】

また前記配線基板21の下側主面21Bには、外部接続用の電極パッド21bが多数形成されている。

【0044】

本実施形態の半導体装置20では、前記第1の導電パタ―ン25がアンダーフィル樹脂23のダムとして作用するため、前記第1の導電パタ―ン25を前記半導体素子21に近接して配置することにより、すなわち前記半導体素子22と第1の導電パタ―ン25との間の距離L2を、図1A,図1Bに示した例における距離L1よりも短く設定することにより(L2<L1)、前記アンダーフィル樹脂23の拡がりを、前記実装領域21M,すなわち前記半半導体素子22の占有領域C4の近傍に閉じ込めることが可能となり、前記アンダーフィル樹脂23が前記配線基板21と前記半導体素子22との間の隙間から流れ出してしまい、アンダーフィル樹脂23による半導体素子22側面の支持が不十分になる問題が回避される。

【0045】

また前記実装領域21Mのすぐ外側にチップ型容量素子24を配置することが可能となり、先に説明した寄生インダクタンスおよび寄生キャパシタンスの増加の問題、およびこれに起因する半導体装置20の電気特性の劣化の問題が回避される。

【0046】

さらに前記距離L2を短縮することにより、従来アンダーフィル樹脂により覆われていた配線基板21の表面に、チップ型容量素子以外にも様々な受動素子や能動素子を配置することが可能となり、基板面積の利用効率が向上する。

【0047】

また、図4Aは、図3Aに於ける線C−C’に沿った拡大断面図を、図4Bは、図3A中、線D−D’に沿った拡大断面図であり、半導体装置20のそれぞれの断面構造を示す。

【0048】

図4Aを参照するに、前記配線基板21中には、電源パタ―ン21V1とその下に電源パタ―ン21V2を含む内部配線21Vが形成されており、前記電源パタ―ン21V1と21V2の一方が図示しない電源端子に、また他方が同じく図示しない接地端子に接続されている。

【0049】

前記配線基板21の上側主面21Aには、前記半導体素子22が占有する領域C4に電極パッド21aが行列状に配置されており、前記電極パッド21aには、前記半導体素子22の回路面22Aに行列状に形成された半田バンプ22aが接続されている。さらに前記電源パタ―ン21V1からは対応する電極パッド21aにビアプラグ21v1が延在し、電源電圧あるいは接地電圧(グランド)が供給され、また前記電源パタ―ン21V2からは対応する電極パッド21aにビアプラグ21v2が延在し、前記電源パタ―ン21V1に電源電圧が供給されている場合には接地電圧(グランド)が、また前記電源パタ―ン21V1に接地電圧が供給されている場合には電源電圧が供給される。その際、下側の前記電源パタ―ン21V2から延在するビアプラグ21v2は、図4Cに示すように前記上側の電源パタ―ン21v1中に形成された開口部中を延在し、短絡が回避される。

【0050】

尚図4Cは、図4Aに於ける線D−D’に沿った断面を示している。

【0051】

前記図4Aでは、前記配線基板21の上側主面21A上に、前記導電パタ―ン25に対応して電極パッド25Aが、前記実装領域21Mを囲繞して形成されており、さらに前記電極パッド25Aの外側に前記導電パタ―ン26に対応して電極パッド26Aが、前記電極パッド25Aを囲繞するように形成されている。前記電極パッド25Aおよび前記導電パタ―ン25には、電源パタ―ン21V1およびビアプラグ21v1から電源電圧または接地電圧が供給され、前記電極パッド26Aおよび前記導電パタ―ン26には電源パタ―ン21V2およびビアプラグ21v2から接地電圧または電源電圧が供給される。

【0052】

また、図4Aに示す構成では、前記電極パッド25Aと電極パッド26Aとの間に、内部にキャパシタ電極24cおよびキャパシタ電極24dを合対向して有するセラミックキャパシタ本体24Cを有する二端子構成のチップ型容量素子24が、前記電極パッド25Aと電極パッド26Aとを架橋するように配置され、前記キャパシタ電極24cが、対応する電極パッド24Aを介して前記電極パッド25Aに、前記第1の導電パタ―ン25を構成する半田パタ―ンにより接続され、また前記キャパシタ電極24dが、対応する電極パッド24Bを介して前記電極パッド26Aに、前記第2の導電パタ―ン26を構成する半田パタ―ンにより接続されている。このようなチップ型容量素子24としては、例えば株式会社村田製作所より市販のLLLシリーズの製品などを使うことができる。

【0053】

一方、図4Bに示す構成にあっては、前記チップ型容量素子24は含まれておらず、前記電極パッド25A上に前記第1の導電パタ―ン25を構成する半田パタ―ンが、また前記電極パッド25B上に前記第2の導電パタ―ン26を構成する半田パタ―ンが、それぞれ形成されている。

【0054】

図4A,図4Bのいずれにおいても前記第1の導電パタ―ン25および第2の導電パタ―ン26を構成する半田パタ―ンは前記配線基板21の上側主面21Aから上方に盛り上がっており、特に内側の第1の導電パタ―ン25を構成する半田パタ―ンは、前記アンダーフィル樹脂23の拡がりを阻止するダムとして作用する。

【0055】

前記第1の導電パタ―ン25,第2の導電パタ―ン26に対応する半田パタ―ンの上方への盛り上がりの好ましい高さは、前記アンダーフィル樹脂23との濡れ性により多少変化するが、例えば前記アンダーフィル樹脂23としてエイブルスティック社のUF8802Fを使った場合、80μm程度あるいはそれ以上に設定しておくのが好ましく、100μmの高さがあれば、通常のアンダーフィル樹脂に対しては十分である。

【0056】

本実施形態によれば、アンダーフィル樹脂23の拡がりが前記第1の導電パタ―ン25で阻止されるため、チップ型容量素子24などの受動素子がアンダーフィル樹脂23で覆われる恐れがなく、前記配線基板21の下側主面21Bに半田バンプを形成する際などにおいて熱処理がなされる場合でも、これらの受動素子において溶融半田の飛び出しによる半田ボールの形成、或いはこのような半田ボールに起因する短絡の発生が回避される。

【0057】

前記図3A,図3Bに示す半導体装置20の製造方法を、図5A,図5B〜図10A,図10Bに示す。

【0058】

図5A,図5Bを参照するに、前記配線基板21上には前記半導体素子22の占有領域C4に、前記半導体素子22の回路面22A上の半田バンプ22aに対応して電極パッド21aが行列状に形成されており、また前記第1の導電パタ―ン25の形成位置に電極パッド25Aが、前記半導体素子22の占有領域C4を含む実装領域21Mを囲繞するように形成されている。また前記電極パッド25Aの外側で前記第2の導電パタ―ン26の形成位置に、前記電極パッド25Aを囲繞するように電極パッド26Aが形成されている。

【0059】

なお図6B、および図7B〜図10Bにおいて前記電極パッド21aは簡単のため連続した電極パターンを図示しているが、これらは図5Aに示すように行列状に配列された小さな電極パッドより構成されている。

【0060】

次に図6A,図6Bを参照するに、前記電極パッド25Aおよび26A上にクリーム半田パタ―ン25Bおよび26Bがそれぞれ印刷される。

【0061】

さらに図7A,図7Bを参照するに、前記クリーム半田パタ―ン25Bと26Bを架橋するように、チップ型容量素子24が配置され、前記クリーム半田パタ―ン25Bと26Bを溶融させることにより、前記チップ型容量素子24が所望の数だけ実装される。

【0062】

チップ型容量素子24の実装の詳細については、後述する。

【0063】

前記クリーム半田パタ―ン25Bおよび26Bの溶融により、前記配線基板21上には前記電極パッド25Aおよび26Aにそれぞれ対応して、第1の導電パタ―ン25および第2の導電パタ―ン26が、半田パタ―ンにより形成される。

【0064】

次に図8Aおよび図8Bを参照するに、前記配線基板21上に半導体素子22がフリップチップ実装され、前記半導体素子22の回路面22Aに形成されたそれぞれの半田バンプ22aが、前記配線基板21の対応する電極パッド21aと接続される。

【0065】

次に図9Aおよび9Bを参照するに、ディスペンサ31を使って前記アンダーフィル樹脂23が、前記配線基板21と半導体素子22との間の隙間に、毛細管現象を使って充填される。

【0066】

図9Aおよび図9Bに示す工程では、前記アンダーフィル樹脂23の充填は、前記ディスペンサ31の先端を、前記導電パタ―ン25の内側に配置させて実行される。

【0067】

このようにして充填されたアンダーフィル樹脂23は、硬化される。

【0068】

前記図10Aおよび図10Bに示す半導体装置20について、必要に応じて前記配線基板21の下側主面上のパッド電極21bに半田バンプを形成し、これを製品として顧客に引き渡すことができる。

【0069】

本実施形態によれば、前記ディスペンサ31により充填されたアンダーフィル樹脂23は、ダムとして作用する前記第1の導電パタ―ン25によりせき止められ、実装領域21M(図7A参照)の外側には流出しない。

【0070】

前記図7A,図7Bに示すチップ型容量素子24の実装プロセスを、図11A〜図11Cに示す。

【0071】

尚、図11Bおよび図11Cは、図11Aに於いて、線F−F’に沿った断面を示す。

【0072】

図11Bは、前記第1の導電パタ―ン25および第2の導電パタ―ン26を構成する半田パタ―ンが溶融する以前の状態を示し、図11Cは前記半田パタ―ンが溶融した後の状態を示している。なお図11Bおよび図11Cにおいて、前記セラミック本体24C中に形成されるキャパシタ電極24c,24dの図示は省略する。

【0073】

図11Aおよび図11Bを参照するに、前記チップ型容量素子24はその電極24A,24Bが前記第1の電極パターン25および第2の電極パターン26を構成するクリーム半田パタ―ン25Bおよび26Bにそれぞれコンタクトするように載置され、さらに前記半田パタ―ンを溶融させることにより、前記電極24Aおよび24Bを覆って溶融半田がはい上がり、図11Cに示すようにチップ型容量素子24が実装される。

【0074】

この様な半田パタ―ンの溶融の際、前記電極パッド25Aおよび26Aの幅や長さが異なっていると、溶融半田の表面張力の平衡がくずれ、チップ型容量素子24が立ち上がっていわゆるツームストン現象、あるいはマンハッタン現象と称される不良を生じる恐れがあるが、本実施形態では前記電極パッド25Aおよび26A、およびその上の第1の導電パタ―ン25および26が略対称に形成されており、このような実装不良は生じない。

【0075】

尚、図11Aでは、前記電極パッド25Aおよび25Bを図示するために、前記導電パタ―ン25および26の幅を電極パッド25Aおよび25Bの幅よりも小さく表示してあるが、これは表示上の都合であって、図11Bに示すように前記電極パッド25Aおよび26Aの表面は、それぞれクリーム半田25Bおよび26Bにより覆われている。

【0076】

このように本実施形態によれば、前記第1の導電パタ―ン25および第2の導電パタ―ン26を略等しく、すなわち対称的に形成することで、前記チップ型容量素子24など受動素子にツームストン現象が発生するのが防止・抑制され、半導体装置の製造歩留まりを向上させることができる。

【0077】

なお図11A〜図11Cに示す実施形態では、前記電極パッド25Aおよび26Aは、前記チップ型容量素子24の実装を任意の位置でできるように、十分な幅をもって形成されているが、本実施形態においては、図12に示すように、前記電極パッド25A,25Bの幅を前記チップ型容量素子24の形成位置25AW,26AWにおいてのみ増大させ、それ以外の領域ではダムとなる半田パタ―ンを形成可能な最小限の幅とすることも可能である。

【0078】

この場合、前記形成位置25AW,26AWでは前記第1および第2の導電パタ―ン25,26を構成する半田パタ―ンは、幅広の半田パタ―ン25W,26Wとなり、チップ型容量素子24は前記形成位置25AW,26AWに確実に半田付けされるが、互いに隣接する形成位置25AWどうし、あるいは互いに隣接する形成位置26AWどうしは、細い半田パタ―ン25あるいは26でのみ接続される。

【0079】

これにより、これら形成位置間におけるチップ型容量素子24の溶融半田の表面張力を介した干渉が低減され、二つのチップ型容量素子24を近接して配置した場合でも、ツームストン現象を抑制することができる。

【0080】

すなわち図12に示す構成により、多数のチップ型容量素子を半導体素子22の周辺に、近接して配置することができる。

【0081】

図13Aおよび図13Bは、本実施形態の一変形例による半導体装置20A,20Bをそれぞれ示している。

【0082】

前述の如く、本実施形態では前記配線基板21上にフリップチップ実装された半導体チップ22を二重に囲繞して、前記第1の導電パタ―ン25および第2の導電パタ―ン26が形成されており、チップ型容量素子24は、前記半導体素子22を囲んで、前記導体パターン25および導体パターン26との間を橋絡するように実装されている。

【0083】

そこで、図9Aおよび図9Bにおいてディスペンサ31を使って前記アンダーフィル樹脂23を充填する際、前記ディスペンサ31が既に実装されているチップ型容量素子24と干渉してしまうような場合に、本実施形態では前記チップ型容量素子を、ディスペンサ31と干渉しない位置に適宜配置することが可能である。

【0084】

例えば図13Aに示す半導体装置20Aの例では、ディスペンサ31は図中、前記半導体素子22の右縁に沿って矢印で示すように移動されるが、前記チップ型容量素子24のうち、チップ型容量素子241および242は、かかるディスペンサ31の移動範囲を避けて形成されており、ディスペンサ31とチップ型容量素子24との干渉は生じない。

【0085】

同様に図13Bに示す半導体装置20Bの例では、ディスペンサ31は図中、矢印で示すように前記半導体素子22の右縁から上縁に沿って、右上角部を回り込んで移動され、、前記チップ型容量素子243,244は、半導体素子22の上縁で左上角部近傍に、また前記チップ型容量素子245,246は、半導体素子22のおよび右縁で右下角部近傍にまとめて配置してある。

【0086】

すなわち本実施形態によれば、前記第1の導電パタ―ン25が前記実装領域を多重に囲繞するため、半導体素子周辺でのチップ型容量素子24などの受動素子の配置の自由度が増大し、前記半導体素子22の実装の際、アンダーフィル樹脂23の注入位置を避けて前記受動素子を配置することが可能で、これにより、アンダーフィル樹脂の注入に使われるディスペンサ31が前記受動素子と干渉する問題を回避することができる。

【0087】

これに対し、例えば前記半導体装置10では、ディスペンサがチップ型容量素子13と干渉する場合があり、ディスペンサを使ったアンダーフィル樹脂13の注入位置が限定されてしまう。

【0088】

なお、この様にチップ型容量素子を近接して配置した場合には、前記導電パタ―ン25と導電パタ―ン26を対称に形成しても、溶融半田の表面張力の干渉により、チップ型容量素子にツームストン現象が発生し易い。

【0089】

この様な場合には、先に図12に示したように一つのチップ型容量素子、例えばチップ型容量素子243とこれに隣接するチップ型容量素子、例えばチップ型容量素子244の間において前記導電パタ―ン25,26を構成する半田パタ―ンの幅を減少させることにより、溶融半田の干渉を低減させることができる。

【0090】

本実施形態の半導体装置20によれば、前記アンダーフィル樹脂23の拡がりが前記第1の導電パタ―ン25で阻止されるため、例えば図14Aに示すように、配線基板21のうち、従来流れ拡がったアンダーフィル樹脂で覆われてしまっていた領域に、図14Bに示す、セラミック本体34cの両側縁部に沿って端子34aと端子34bを交互に配列された多端子構成のチップ型容量素子34など、他の受動素子を配置したり、図14Cに示すように、DRAM35などの能動素子を配置したりすることが可能となる。

【0091】

これにより、配線基板表面の利用効率を向上させ、また半導体装置の機能をさらに向上させることができる。

【0092】

図14Aに示す多端子チップ型容量素子34の場合も、アンダーフィル樹脂23で覆われてしまうと、チップ型容量素子24の場合と同様に、先に図2A〜図2Cを用いて説明した問題が生じ、このような構成を実現するのは、実装基板21の寸法を増大させる以外には、困難であった。

【0093】

また図14Cに示すDRAM35の場合には、DRAMに耐熱制限があるため、最終工程で実装をせざるを得ないが、アンダーフィル樹脂が前記DRAM35の実装パッドを覆ってしまうと、このような実装は不可能となってしまう。

【0094】

すなわち、図14Cに示す構成も、実装基板21の寸法を増大させる以外には、従来実現が困難であった。

【0095】

これに対し本実施形態によれば、図14Aあるいは図14Cに示す構成を、配線基板21のサイズを増大させることなく、容易に実現することが可能となる。

【0096】

特に図14Cに示す構成では、配線基板21上に、半導体素子22と共にDRAMなどの記憶素子を実装することにより、小型のシステムインパッケージを構成することができる。

【0097】

前記図10A,図10Bに示す半導体装置20に対して、さらに施される加工処理を、図15A〜図15Cに示す。

【0098】

図15Aを参照するに、当該半導体装置20において、前記半導体素子22の背面、すなわち上面に、導電性接着剤よりなるチップ背面接着剤層36がディスペンサ37を使って塗布され、さらに図15Bに示すように前記配線基板21上に、例えばAlSiCなどの熱伝導性合金よりなる封止部材38が、前記半導体素子22の前記背面に前記接着剤層36により接合されるように配置されている。

【0099】

前記封止部材38は、その外周部に、前記配線基板21上において前記半導体素子22を収納する空間を画成するように形成された接合部38Aが、前記配線基板21の上側主面21Aに、接着剤層39により接着される。

【0100】

本実施形態による半導体装置20は、図15Aに示す状態で製品として顧客に引き渡される場合、或いは図15Bに示される状態で製品として顧客に引き渡される場合がある。

【0101】

また必要に応じて、図15Cに示すように、前記配線基板21の下側主面21Bに形成した外部接続用電極パッド21b(図3B参照)に半田バンプ21cを形成し、半導体装置20をこの状態で製品として顧客に引き渡すことも可能である。

【0102】

なお、一般に図15Bあるいは図15Cに示す配線基板21上に封止部材38を配設した半導体装置では、半導体素子22が発熱した場合、主として配線基板21の熱膨張係数と封止部材38の熱膨張係数の差により、配線基板21に反りが発生することがある。

【0103】

このような反りは、配線基板21の中心からの距離が増大するにつれて増大する傾向がある。

【0104】

配線基板21にこのような反りが発生してしまうと、半導体装置20を例えばマザーボード上に配置した場合、電気接続の信頼性が低下するなどの問題が生じる。

【0105】

これに対し、本実施形態では前記導電パタ―ン25のダム作用によりアンダーフィル樹脂23の配線基板21上における流れ拡がりが阻止されるため、図17に示すように、前記封止部材38を前記配線基板21の上側主面21Aに、前記配線基板21の外周21eから矢印で示すように内側に寄った位置において接合することが可能となり、半導体素子22が発熱した場合でも、熱による配線基板21の反りを緩和することができる。

【0106】

図16Aおよび図16Bは、それぞれ本実施例の導電パタ―ン25,26を設けなかった場合および設けた場合の、前記配線基板21の表面上におけるアンダーフィル樹脂23の拡がりの様子を示す写真である。

【0107】

ただし図16Aおよび図16Bに示す実施形態では、半導体素子22を実装せずにディスペンサを使い、図9A,図9Bに示す配線基板21のうち、半導体素子22により占有される領域C4にアンダーフィル樹脂23を形成している。

【0108】

前記アンダーフィル樹脂23として、エポキシ樹脂(例えばナガセケムテックス社の型番T693/UFR108F10)を用い、70℃の温度に於いて充填を行っている。

【0109】

図16Aおよび図16Bを参照するに、前記導電パタ―ン25,26を設けなかった場合には、アンダーフィル樹脂23は前記配線基板21上を、前記半導体素子22の占有領域C4を超えて拡がり、半導体素子22を囲んで配置されるチップ型容量素子24などの受動素子を覆ってしまう。

【0110】

これに対し、導電パタ―ン25,26を設けた場合には、アンダーフィル樹脂23は導電パタ―ン25により拡がりが阻止され、チップ型容量素子24などの受動素子がアンダーフィル樹脂23により覆われることはない。

【0111】

図16Cは、図16Bに於いて、矩形Aにより囲まれた部位を拡大して示す写真である。

【0112】

図16Cを参照するに、アンダーフィル樹脂23は導電パタ―ン25により拡がりが阻止されており、導電パタ―ン25は所期のダム作用を生じていることが確認される。

【0113】

なお前記アンダーフィル樹脂は、前記エポキシ樹脂に限定されるものではなく、表1〜表4に示す他の様々な樹脂を適用することができる。

【0114】

【表1】

【0115】

【表2】

【0116】

【表3】

【0117】

【表4】

【0118】

なお表1には、それぞれの樹脂の充填時、すなわち図9A,図9Bを用いて説明したディスペンサを使って充填する際の温度(ステージ温度)を、硬化条件と共に示している。

【0119】

前記第1の実施形態の一変形例による半導体装置20Cを図17に示す。

【0120】

図17を参照するに、本変形例は、先に図15Cに於いて示した構造に対応して、封止部材38の接合部38Aが、当該封止部材38の外縁38eから、矢印で示すように内側に寄った位置に形成されている。

【0121】

かかる構成では、前記接合部38Aは、前記配線基板21の外縁21eから内側に寄った位置に形成されている。

【0122】

このように配線基板21の外縁21eから内側に寄った位置において封止部材38を前記配線基板21に接合することにより、封止部材38と配線基板21の熱膨張係数差に起因する配線基板21の反りの問題を軽減することができる。

【0123】

このような構成は、前記導電パタ―ン25によりアンダーフィル樹脂23の拡がりが阻止される結果、チップ型容量素子24などの受動素子を半導体素子22の近傍に、すなわち実装領域22Mの直近に配置できるため、前記封止部材38の接合部38Aの接合のための領域を配線基板21の表面に確保でき、その結果、可能となったものである。

【0124】

図18A,図18Bは、本実施形態の半導体装置の他の変形例による半導体装置20D,20Eをそれぞれ示し、図18Cおよび図18Dは、それぞれ前記図18A中、線G−G’およびに線H−H’に沿った断面を、図18Eは、図18B中、線I−I’に沿った断面を示す。

【0125】

図18Aを参照するに、本変形例では前記導電パタ―ン25,26の一部が、前記チップ型容量素子24が設けられる部分において、半導体素子22の占有領域C4に向かって屈曲されており、その結果、チップ型容量素子24を、図18Cに示すように、前記半導体素子22の直近に配設することができる。

【0126】

これにより、本実施形態では、半導体素子22とチップ型容量素子24との間の距離を最短化することができ、これに伴い、半導体素子22とチップ型容量素子24との間の配線の寄生インダクタンス或いは寄生キャパシタンスを低減し、半導体装置の電気特性をさらに向上させることができる。

【0127】

なお図18Aに示す変形例では、前記導電パタ―ン25,26は、前記チップ型容量素子24の形成領域以外では、図18Dに示すように前記半導体素子22から離間して形成されている。

【0128】

このため先に図9A,図9Bで説明したアンダーフィル樹脂の充填工程においても、アンダーフィル樹脂23を、図18A中に矢印A〜Dで示した位置のいずれからでも、ディスペンサ31により注入することができる。

【0129】

図18Bに示す構成では、前記導電パタ―ン25,26が直角に屈曲されており、図18Aに示す構成と同様にアンダーフィル樹脂23を、図18A中に矢印A〜Dで示した位置のいずれからでも、ディスペンサ31により注入することが可能であるが、前記導電パタ―ン25,26が直角に屈曲されている結果、図18Eに示すように前記チップ型容量素子24の形成位置以外では、ディスペンサ31による注入位置選択の際の自由度が、図18Aの構成に比べて向上する。

【0130】

また図18A,18Bに示す変形例では、半導体素子22のうち、熱応力の集中が発生しやすい角部において、厚いアンダーフィル樹脂層23を形成することができ、半導体装置全体の機械的および電気的な安定性および信頼性が向上する。この観点からは、前記図18Aの構成の方が、前記半導体素子22の角部において半導体素子22を支持するアンダーフィル樹脂23の量を増大させることができ、より好ましい。

【0131】

また図18Aに示す構成では、前記導電パタ―ン25,26は屈曲しながらも、互いに平行な関係を維持するため、図18Aに示すように多数のチップ型容量素子24を任意の位置に配置することができる。

【0132】

図19は、本実施形態のさらなる変形例による半導体装置20Fを示す。

【0133】

本実施形態の変形例の如く、外側の導電パタ―ン26は、チップ型容量素子24の形成位置にのみ形成した不連続な形状に形成することもできる。

【0134】

[第2の実施形態]

第2の実施形態による半導体装置40の製造方法を、図20A,図20B〜図25A,図25Bに示す。尚、図20B〜図25Bは、線J−J’(図7B参照)に沿った断面図を示す。図中、先に説明した部分に対応する部分には同一の参照符号を付し、説明を省略する。

【0135】

図20A,図20B〜図25A,図25Bに示す工程は、先の図5A,図5B〜図7A,図7Bの工程と同じであり、図22Aおよび図22Bに示すように、前記配線基板21の上側主面21A上において、電極パッド21aの配列を囲む実装領域21M(図19A参照)を囲んで、第1の導電パタ―ン25および第2の導電パタ―ン26が、半田パタ―ンにより形成されている。

【0136】

また図22A,図22Bに示す状態では、前記導電パタ―ン25と導電パタ―ン26との間に、チップ型容量素子24が実装されている。

【0137】

本実施形態では、図23Aおよび図23Bに示すように、ディスペンサ31を使って前記配線基板21の上側主面21Aのうち、電極パッド21aの配列が形成されたチップ占有領域C4にアンダーフィル樹脂43が、必要量だけ滴下される。

【0138】

その後、図24Aおよび図24Bに示すように、半導体素子22が前記電極パッド21aに、フリップチップ実装される。このため前記アンダーフィル樹脂43には、例えばアジピン酸、コハク酸、無水グルタル酸などのフラックス成分(活性成分)が添加されており、前記半導体チッ22のバンプ電極22aとパッド電極21aの接合が促進される。前記アンダーフィル樹脂43の必要量は、前記半導体素子22が前記配線基板21の上側主面21A上にフリップチップ実装された場合に、前記アンダーフィル樹脂43が前記半導体素子22と前記上側主面21Aとの間の隙間を充填し、かつ、必要に応じて半導体素子22の側壁面を支持するフィレットが形成される量に設定される。

【0139】

本実施形態においても、導電パタ―ン25のダム作用により、アンダーフィル樹脂43が、当該導電パタ―ン25を乗り越えて外部に流出することはない。

【0140】

さらに図24Aおよび図24Bに示す状態で前記アンダーフィル樹脂43を硬化させることにより、図25Aおよび図25Bに示す半導体装置40が得られる。

【0141】

本実施形態によれば、アンダーフィル樹脂43は、前記図9Aおよび図9Bに示したように半導体素子22を実装してから注入する必要がないため、図26A〜図26Cの変形例に示すように、ダムとなる導電パタ―ン25を前記半導体チップ22の外周直近に、前記半導体素子22の外周に接するように形成してもよい。

【0142】

尚、図26Bおよび図26Cは、図26A中、線K−K’および線L−L’に沿った断面を示す。図中、先に説明した部分に対応する部分には同一の参照符号を付し、説明を省略する。

【0143】

このように前記導体パターン25を前記半導体素子22の外周直近に形成することにより、チップ型容量素子24を半導体素子22の直近に配置することができ、半導体素子22とチップ型容量素子24との間の配線の寄生インダクタンスや寄生キャパシタンスの効果をさらに低減することが可能となる。またこれに伴い、半導体装置40Aの電気特性をさらに向上させることができる。

【0144】

本実施形態においても、先の第1の実施形態の場合と同様に、図25Aおよび図25Bに示す半導体装置40、あるいは図26Aおよび図26Bに示す半導体装置40A上に、先に図15A〜図15Cに示す工程を施すことにより、封止部材38および半田バンプ21cを形成することができる。

【0145】

また本実施形態においても、先の実施形態と同様な様々な変形が可能である。

【0146】

[第3の実施形態]

前記各実施形態に於ける半導体装置の構成は、配線基板上におけるアンダーフィル樹脂の濡れ拡がりを抑制できるため、単一の配線基板上に多数の半導体素子を近接してフリップチップ実装するマルチチップモジュールに適用した場合に有効である。

【0147】

この様な第3の実施形態による半導体装置60の構成を、図27に示す。

【0148】

図27を参照するに、配線基板21上には、各々が、先の第1の実施形態による半導体装置20〜20F、あるいは第2の実施形態による半導体装置40,40Aのいずれかよりなり、単一の半導体素子22を含む複数の半導体装置要素61A〜61Dが、行列状に配置されている。

【0149】

図27に示される構成によれば、上下方向あるいは左右方向に隣接する一対の半導体チップ22の間にもチップ型容量素子24などの受動素子を配置することができ、マルチチップモジュール構成の半導体装置60に対し、優れた電気特性を保証することができる。

【0150】

これに対し、各々の半導体装置要素61A〜61Dが先に説明した導電パタ―ン25,26を有さない場合には、図28あるいは図29に示すようにアンダーフィル樹脂23が各々の半導体素子22から拡がってしまい、チップ型容量素子24などの受動素子は、前記配線基板21上に、前記複数の半導体素子を囲んで配置する外はなく、十分な個数のチップ型容量素子24を配置できないため、電気特性が不安定となり易い。

【0151】

なお図28,29では便宜上、図27に示す構成と同じ参照符号を使ってはいるが、これらの図面は本実施形態の半導体装置あるいはその変形例を示すものではない。

【0152】

図20は、図28に示す半導体装置60の一変形例によるマルチチップ構成の半導体装置60Aを示す平面図である。

【0153】

図60Aを参照するに、本変形例では外側の導電パタ―ン26が、上下および左右に隣接する半導体装置要素61A〜61Dの間で共用されており、これにより、配線基板21上における半導体装置要素61A〜61Dの占有面積を低減することができる。

【0154】

[第4の実施形態]

先の各実施形態で説明した半導体装置の構成は、複数の異なった電源電圧を使う場合に拡張することができる。

【0155】

このような第4の実施形態による半導体装置80を、図31に示す。

【0156】

図31に於いて、先に説明した部分に対応する部分には同一の参照符号を付し、説明を省略する。

【0157】

図31を参照するに、前記配線基板21上には、前記導電パタ―ン25を囲繞して、前記導電パタ―ン26に対応して導電パタ―ン261が形成されており、さらに前記導電パタ―ン261を囲繞してその外側に次の導電パタ―ン262が形成されており、前記導電パタ―ン262の外側にはこれを囲繞してさらに次の導電パタ―ン263が形成されており、前記導電パタ―ン263の外側にはこれを囲繞してさらに次の導電パタ―ン264が形成されている。

【0158】

このように、半導体装置80にあっては、導電パタ―ン261〜264が前記導電パタ―ン25を囲繞して同心的に形成されている。

【0159】

本第4の実施形態では、例えば前記導電パタ―ン25に第1の電源電圧(電源1)を供給する場合、導電パタ―ン261には接地電圧(グランド)が供給され、導電パタ―ン262には第2の電源電圧(電源2)が供給され、導電パタ―ン263には接地電圧(グランド)が供給され、導電パタ―ン264には第2の電源電圧(電源2)が供給されるように構成される。

【0160】

このような各導電パタ―ン25,261,262,263、264への電源電圧1,電源電圧2,電源電圧3および接地電圧の供給は、前記配線基板21中の配線パタ―ン21V(図4A,図4Bを参照)により行うことができる。

【0161】

あるいは前記導電パタ―ン25に接地電圧(グランド)を供給する場合には、導電パタ―ン261に第1の電源電圧(電源1)を供給し、導電パタ―ン262に接地電圧(グランド)を供給し、導電パタ―ン263に第2の電源電圧(電源2)を供給し、導電パタ―ン264に第接地電圧(グランド)を供給するように構成してもよい。

【0162】

この場合には、2種類の電源電圧を供給することになる。

【0163】

本実施形態でも前記チップ型容量素子24などの受動素子は、前記導電パタ―ン25と導電パタ―ン261の間、導電パタ―ン261と導電パタ―ン262の間、導電パタ―ン262と導電パタ―ン263の間、および導電パタ―ン263と導電パタ―ン264の間を架橋して設けられる。

【0164】

[第5の実施形態]

複数の電源電圧を使った第5の実施形態による半導体装置100を、図32に示す。

【0165】

半導体装置100は、前記半導体装置20の拡張に相当し、前記導電パタ―ン26の外側に、図14Bに示すと同様に、複数の多端子構成のセラミックキャパシタ34が、半導体素子22を挟んで図面上で左右に合対向して配置されている。

【0166】

本第5の実施形態では、先の半導体装置20の場合と同様に、前記導電パタ―ン25に電源電圧1(電源1)と接地電圧(グランド)の一方が供給され、前記パタ―ン26に前記電源電圧1(電源1)と接地電圧(グランド)の他方が供給されるが、前記セラミックキャパシタ34は、前記図14Bにおける端子34aおよび34bに電源電圧1(電源1)と接地電圧(グランド)をそれぞれ印加されるキャパシタ341と、前記端子34aおよび34bに電源電圧2(電源2)と接地電圧(グランド)をそれぞれ印加されるキャパシタ342と、前記端子34aおよび34bに電源電圧3(電源3)と接地電圧(グランド)をそれぞれ印加されるキャパシタ343と、を含み、これにより半導体装置100では、電源電圧1、電源電圧2、および電源電圧3のそれぞれに、デカップリングキャパシタが設けられ、安定化が図られることになる。

【0167】

また当該半導体装置100では、前記導電パタ―ン26の外側に、前記チップ型容量素子24と同様な二端子構成の複数のセラミックキャパシタ44が、半導体素子22を挟んで図面上で上下に合い対向して配置されている。前記複数のセラミックキャパシタ44はキャパシタ441,442,443を含み、キャパシタ441は電源電圧1(電源1)および接地電圧(グランド)を供給され、キャパシタ442は電源電圧1(電源2)および接地電圧(グランド)を供給され、キャパシタ443は電源電圧1(電源3)および接地電圧(グランド)を供給され、これにより半導体装置100では、電源電圧1、電源電圧2、および電源電圧3のさらなる安定化が図られることになる。

【0168】

[第6の実施形態]

複数の電源電圧(電源電圧1,電源電圧2)を適用した第6の実施形態による半導体装置の一部を図33A,図33Bに示す。

【0169】

図33Aは、チップ型容量素子が実装される前の状態を、図33Bはチップ型容量素子が実装された後の状態を示している。図中、先に説明した部分には同一の参照符号を付し、説明を省略する。

【0170】

図33Aを参照するに、本実施形態では、前記導体パターン25および導体パターン26のいずれもが接地電圧(グランド)に設定され、前記導体パターン25中には、前記配線基板21上に形成され電源電圧1(電源1)が供給される電極パッド45aを露出するカットアウト25a、および前記配線基板21上に形成され電源電圧2(電源2)が供給される電極パッド45bを露出するカットアウト25bが形成されている。同様に前記導体パターン26中には、前記配線基板21上に形成され電源電圧1(電源1)が供給される電極パッド46aを露出するカットアウト26a、および前記配線基板21上に形成され電源電圧2(電源2)が供給される電極パッド46bを露出するカットアウト26bが形成されている。なお本実施形態でも、図示はしないが、前記導体パターン25は半導体素子22下のアンダーフィル樹脂23の濡れ拡がりを阻止するダムを構成している。

【0171】

本実施形態では、前記導電パタ―ン25上のカットアウト25aと導電パタ―ン26上のカットアウト26aは、互い違いの関係に形成されており、これに伴い、電極パッド25aと電極パッド25bも、互い違いの関係に形成されている。また同様にカットアウト25bとカットアウト26bも互い違いの関係に形成されており、これに伴い電極パッド45bと電極パッド46bも互い違いの関係に形成されている。

【0172】

図33Bでは、前記配線基板21上に端子1〜8を有する多端子構成のセラミックキャパシタが、チップ型容量素子53A,53Bとして実装されている。より具体的には前記チップ型容量素子53Aが、その端子1と3をそれぞれ前記電極パッド45aに、端子6と8をそれぞれ前記電極パッド46aに、端子2,4を前記導体パターン25に、さらに端子5,7を前記導体パタ―ン26に、コンタクトさせて実装されている。また図33では前記キャパシタ53Bが、その端子1と3がそれぞれ前記電極パッド45aに、端子6と8がそれぞれ前記電極パッド46aに、端子2,4が前記導体パターン25に、さらに端子5,7が前記導体パタ―ン26にコンタクトするように実装されている。

【0173】

換言すると、図33A,図33Bに示す構成では、電極パッド45a,46aが、実装される多端子セラミックキャパシタ53Aの端子に対応した位置に形成されており、電極パッド45b,46bが、実装される多端子セラミックキャパシタ53Bの端子に対応した位置に形成されている。

【0174】

このような多端子チップ型容量素子53A,53Bとしては、例えば株式会社村田製作所からLLAシリーズとして市販のセラミックキャパシタを使うことができる。

【0175】

かかる構成により、電源電圧1の電源ラインにキャパシタ53Aが、また電源電圧2の電源ラインにキャパシタ53Bが挿入され、それぞれの電圧変動が、これらのキャパシタにより、独立に、かつ効果的に吸収される。

【0176】

なお、図33A,図33Bに示す構成において、電源電圧1と電源電圧2を一致させることにより、単一の電源電圧を用いた半導体装置を構成できる。

【0177】

図33A,図33Bに示す実施形態の一変形例を、図34A,図34Bに示す。

【0178】

図34Aを参照するに、前記電極パッド45a,45b,46a,46bに加えて、前記配線基板21上の導体パターン25と導体パターン26との間に、接地電圧が供給される電極パッド47aおよび前記電源電圧1(電源1)が供給される電極パッド47bが形成されている。また前記配線基板21上の導体パターン25と導体パターン26との間に、接地電圧が供給される電極パッド47cおよび前記電源電圧2(電源2)が供給される電極パッド47dが形成されている。

【0179】

なお本実施形態では、導電パタ―ン25上のカットアウト25aと導電パタ―ン26上のカットアウト26aは、互いに対称的な関係に形成されており、これに伴い、電極パッド45aと電極パッド46aも、互いに対称的な関係に形成されている。

同様に、導電パタ―ン25上のカットアウト25bと導電パタ―ン26上のカットアウト26bも、互いに対称的な関係に形成されており、これに伴い、電極パッド45bと電極パッド46bも、互いに対称的な関係に形成されている。

【0180】

図34Bは、前記図34Aに示す電源パッド45a,46a,45b,46b,47a,47b上に、端子1〜10を有する多端子セラミックキャパシタ53C,53Dがチップ型容量素子として実装された状態を示す。

【0181】

図34Bを参照するに、本変形例では前記チップ型容量素子53Cは、その端子1および3をそれぞれ前記電極パッド45aに、端子5および7をそれぞれ前記電極パッド46aに、端子2および4を前記導電パタ―ン25に、端子6および8を導電パタ―ン26に、端子9および10をそれぞれ電極パッド47aおよび47bにコンタクトさせて実装されている。また本変形例では前記チップ型容量素子53Dは、その端子1および3をそれぞれ前記電極パッド45bに、端子5および7をそれぞれ前記電極パッド46bに、端子2および4を前記導電パタ―ン25に、端子6および8を導電パタ―ン26に、端子9および10をそれぞれ電極パッド47cおよび47dにコンタクトさせて実装されている。換言すると、図34A,図34Bに示す構成では、電極パッド45a,46a,47a,47bが、実装される多端子セラミックキャパシタ53Cの端子に対応した位置に形成されており、電極パッド45b,46b,47c,47dが、実装される多端子セラミックキャパシタ53Dの端子に対応した位置に形成されている。

【0182】

かかる構成によっても、電源電圧1の電源ラインにチップ型容量素子53Cが、また電源電圧2の電源ラインにチップ型容量素子53Dが挿入され、それぞれの電圧変動が、これらのキャパシタにより、独立に、かつ効果的に吸収される。

【0183】

このようなチップ型容量素子55,56としては、例えば株式会社村田製作所よりLLMシリーズとして市販されているセラミックキャパシタを適用することができる。

【0184】

前記図33A,図33Bに示す実施形態の更なる変形例を図35A,図35Bに示す。

【0185】

図35Aを参照するに、本変形例では、前記電極パッド46a,46bの数が、それぞれ3個に増やされており、さらに前記配線基板21上の導体パターン25と導体パターン26との間に、チップ型容量素子53Eに対応して、接地電圧が供給される電極パッド48aおよび前記電源電圧1(電源1)が供給される電極パッド48bが、図面上で左右に並んで形成されている。同様に本変形例では、前記配線基板21上の導体パターン25と導体パターン26との間に、前記チップ型容量素子53Eに対応して、電源電圧1(電源1)が供給される電極パッド48cおよび接地電圧(グランド)が供給される電極パッド48dが、図面上で左右に並んで形成されている。

【0186】

さらに本変形例では、前記配線基板21上の導体パターン25と導体パターン26との間に、チップ型容量素子53Fに対応して、電源電圧2(電源2)が供給される電極パッド48eおよび接地電圧(グランド)が供給される電極パッド48fが、図面上で左右に並んで形成されており、また前記配線基板21上の導体パターン25と導体パターン26との間に、前記チップ型容量素子53Fに対応して、電源電圧2(電源2)が供給される電極パッド48gおよび前記接地電圧(グランド)が供給される電極パッド48hが、図面上で左右に並んで形成されている。

【0187】

本変形例では、図33Aおよび図33Bに示す実施形態と同様に、導体パターン25中に形成されるカットアウト25aと導体パターン26中に形成されるカットアウト26aが互い違いの関係に形成され、これに伴って電極パターン45aと電極パターン46aも、互い違いの関係に形成される。またカットアウト25bとカットアウト26bも互い違いの関係に形成され、これに伴って電極パターン45bと電極パターン46bも互い違いの関係に形成される。

【0188】

図35Bを参照するに、本変形例では前記チップ型容量素子53Eは、その端子1,3,5を前記導体パターン25にコンタクトさせ、端子2,4をそれぞれ前記電極パッド45aにコンタクトさせ、端子6,8,10をそれぞれ前記電極パッド46aにコンタクトさせ、端子7および9を前記導電パタ―ン26にコンタクトさせ、端子11および12をそれぞれ端子48a,48bにコンタクトさせ、端子13,14をそれぞれ端子48c、48dにコンタクトさせて実装されている。また本変形例では前記チップ型容量素子53Fは、その端子1,3,5を前記導体パターン25にコンタクトさせ、端子2,4をそれぞれ前記電極パッド45bにコンタクトさせ、端子6,8,10をそれぞれ前記電極パッド46bにコンタクトさせ、端子7および9を前記導電パタ―ン26にコンタクトさせ、端子11および12をそれぞれ端子48e,48fにコンタクトさせ、端子13,14をそれぞれ端子48g,48hにコンタクトさせて実装されている。

【0189】

換言すると、図35A,図35Bに示す構成では、電極パッド45a,46a,48a〜48dが、実装される多端子セラミックキャパシタ53Eの端子に対応した位置に形成されており、電極パッド45b,46b,48e〜48hが、実装される多端子セラミックキャパシタ53Fの端子に対応した位置に形成されている。

【0190】

かかる構成によれば、電源電圧1の電源ラインにチップ型容量素子53Eが、また電源電圧2の電源ラインにチップ型容量素子53Fが挿入され、それぞれの電圧変動が、これらのキャパシタにより、独立に、かつ効果的に吸収される。

【0191】

このようなチップ型容量素子53E,53Fとしては、前記村田製作所製のセラミックキャパシタを適用することができる。

【0192】

前記図33A,図33Bに示す実施形態の更なる変形例を、図36A,図36Bに示す。

【0193】

図36Aを参照するに、本変形例では、前記電極パッド45a,45a,46a,46bの数が、それぞれ3個に増やされており、さらに前記配線基板21上の導体パターン25と導体パターン26との間に、チップ型容量素子53Eに対応して、接地電圧が供給される電極パッド48aおよび前記電源電圧1(電源1)が供給される電極パッド48bが、図面上で左右に並んで形成されている。同様に本変形例では、前記配線基板21上の導体パターン25と導体パターン26との間に、前記チップ型容量素子53Eに対応して、電源電圧1(電源1)が供給される電極パッド48cおよび接地電圧(グランド)が供給される電極パッド48dが、図面上で左右に並んで形成されている。

【0194】

さらに本変形例では、前記配線基板21上の導体パターン25と導体パターン26との間に、チップ型容量素子53Fに対応して、電源電圧2(電源2)が供給される電極パッド48eおよび接地電圧(グランド)が供給される電極パッド48fが、図面上で左右に並んで形成されており、また前記配線基板21上の導体パターン25と導体パターン26との間に、前記チップ型容量素子53Fに対応して、電源電圧2(電源2)が供給される電極パッド48gおよび前記接地電圧(グランド)が供給される電極パッド48hが、図面上で左右に並んで形成されている。

【0195】

本変形例では、図33Aおよび図33Bに示す実施形態と同様に、導体パターン25中に形成されるカットアウト25aと導体パターン26中に形成されるカットアウト26aが互い違いの関係に形成され、これに伴って電極パターン45aと電極パターン46aも、互い違いの関係に形成される。またカットアウト25bとカットアウト26bも互い違いの関係に形成され、これに伴って電極パターン45bと電極パターン46bも互い違いの関係に形成される。

【0196】

図35Bを参照するに、本変形例では前記チップ型容量素子53Gは、その端子1,3,5を前記導体パターン25にコンタクトさせ、端子2,4,6をそれぞれ前記電極パッド45aにコンタクトさせ、端子7,9,11をそれぞれ前記電極パッド46aにコンタクトさせ、端子8,10,12を前記導電パタ―ン26にコンタクトさせ、端子13および14をそれぞれ端子48a,48bにコンタクトさせ、端子15,16をそれぞれ端子48c、48dにコンタクトさせて実装されている。また本変形例では前記チップ型容量素子53Hは、その端子1,3,5を前記導体パターン25にコンタクトさせ、端子2,4,6をそれぞれ前記電極パッド45bにコンタクトさせ、端子7,9,11をそれぞれ前記電極パッド46bにコンタクトさせ、端子8,10,12前記導電パタ―ン26にコンタクトさせ、端子13および14をそれぞれ端子48e,48fにコンタクトさせ、端子15,16をそれぞれ端子48g,48hにコンタクトさせて実装されている。換言すると、図36A,図36Bに示す構成では、電極パッド45a,46a,48a〜48dが、実装される多端子セラミックキャパシタ53Gの端子に対応した位置に形成されており、電極パッド45b,46b,48e〜48hが、実装される多端子セラミックキャパシタ53Hの端子に対応した位置に形成されている。

【0197】

かかる構成によれば、電源電圧1の電源ラインにチップ型容量素子53Gが、また電源電圧2の電源ラインにチップ型容量素子53Hが挿入され、それぞれの電圧変動が、これらのキャパシタにより、独立に、かつ効果的に吸収される。このようなチップ型容量素子53G,53Hとしては、例えば株式会社村田製作所よりLLKシリーズとして市販のセラミックキャパシタを使うことができる。

【0198】

図37Aは、前記図36Bの半導体装置を、半導体素子22およびアンダーフィル樹脂23の一部まで含めて示し、図37B〜図37Eは、それぞれ図37Aに示す線M−M’,線N−N’,線O−O’および線P−P’に沿った断面を示す。

【0199】

ただし図中、先に説明した部分に対応する部分には同一の参照符号を付し、説明を省略する。

【0200】

図37B〜図37Dを参照するに、本実施形態では前記配線基板21中に形成される内部配線21Vが、接地電圧(グランド)を供給される電源パタ―ン21V1と電源電圧1を供給される電源パタ―ン21V2の外に、前記電源パタ―ン21V2の下に、電源電圧2(電源2)を供給される電源パタ―ン21V3を含んでおり、前記電源パタ―ン21V3は、図37Dに示すビアプラグ21v3を介して、前記半導体素子22の電極パッド21aの一つに接続される。

【0201】

図37Bでは、前記キャパシタ53Gの端子4に対応する半田パタ―ンS4が電極パタ―ン45a上に形成されており、前記電極パタ―ン45aは前記電源パタ―ン21V2に接続されている。また先の各実施形態と同様に、本実施形態でも、導電パタ―ン25を構成する半田パタ―ンが電極パッド25A上に形成され、アンダーフィル樹脂23の濡れ拡がりを阻止するダムを構成している。また前記キャパシタ53Gの端子10に対応する半田パタ―ンS10が、前記導体パターン26を構成する半田パタ―ンに接続され融合している。

【0202】

一方、図37Cでは、導電パタ―ン25,26が先の各実施形態と同様に形成されており、導電パタ―ン25が前記アンダーフィル樹脂23の濡れ拡がりを阻止するダムを構成している。

【0203】

また図37Cでは、前記導電パタ―ン25,26の間に、前記キャパシタ53Gの端子15,16に対応する半田パタ―ンS15,S16が形成されており、前記半田パタ―ンS15は対応する電極パターン48cを介して電源パタ―ン21V1に接続されており、半田パタ―ンS16は、対応する電極パターン48dを介して電源パタ―ン21V2に接続されている。

【0204】

さらに図37Dに示す構成にあっては、導電パタ―ン25,26が先の各実施形態と同様に形成されており、導電パタ―ン25が、やはり前記アンダーフィル樹脂23の濡れ拡がりを阻止するダムを構成している。

【0205】

図37Dに示す構成にあっては、更に、前記導電パタ―ン25,26の間に、前記キャパシタ53Hの端子3および9に対応する半田パタ―ンS3,S9が形成されており、前記半田パタ―ンS3は、前記導電パタ―ン25を構成する半田パタ―ンに接続され融合しており、一方、前記半田パタ―ンS9は、対応する電極パターン46bを介して電源パタ―ン21V3に接続されている。

【0206】

図37Eに示す構成にあっては、導電パタ―ン25,26は見えないが、前記キャパシタ53Gの端子13に対応する半田パタ―ンS13が、電源電圧1(電源1)が供給される電源パタ―ン21V2に接続され、前記キャパシタ53Gの端子15に対応する半田パタ―ンS15が、接地電圧1(グランド)が供給される電源パタ―ン21V1に接続され、前記キャパシタ53Hの端子13に対応する半田パタ―ンS13が、電源電圧2(電源2)が供給される電源パタ―ン21V3に接続され、前記キャパシタ53Hの端子15に対応する半田パタ―ンS15が、接地電圧1(グランド)が供給される電源パタ―ン21V1に接続されている。

【0207】

以上、様々な実施形態について説明してきたが、本発明は更なる変形が可能である。

【0208】

例えば使用するアンダーフィル樹脂23の種類により、図38に示すように導体パタ―ン25,26を、それぞれ複数の、相互に分離した部材251〜254および261〜264より構成することができる。濡れ拡がり性の低い樹脂を前記アンダーフィル樹脂23として使う場合、あるいは導体パタ―ン25を構成する半田との濡れ性が低い樹脂を前記アンダーフィル樹脂23として使い場合には、図38に示す構成であっても、アンダーフィル樹脂の濡れ拡がりを抑制することが可能である。

【0209】

また半導体装置が、チップ型容量素子24が半導体素子22の一方の側、あるいは特定の側にのみ形成される場合には、図39に示すように導体パターン25,26を、チップ型容量素子24が形成される側のみに形成してもよい。

【0210】

さらに本発明は、前記シングルチップ構成あるいはマルチチップ構成の半導体装置、あるいはシステムインパッケージのみならず、図40Aおよび図40Bに示すように、前記配線基板21の代わりに別の半導体素子111を使い、その上に例えば図3A,図3Bの構成、あるいは図27の構成を形成し、チップオンチップ構成の半導体装置を形成することも可能である。

【0211】

更に前記各実施形態で説明した半導体装置を用い、図40Cに示すように、先の実施形態のいずれかの半導体装置上に、さらに別の半導体パッケージを実装したパッケージオンパッケージ構造の半導体装置を形成することも可能である。

【0212】

図40Cに示す例では、前記別の半導体パッケージは配線基板501とその上に実装され樹脂503で封止された半導体素子502を含み、前記半導体素子502は前記配線基板501にボンディングワイヤ504にて配線されている。図示の例では、別の半導体パッケージは、前記配線基板21上に、半田バンプ505により実装されている。

【0213】

さらに図40Dに示すように、先の各実施形態で説明した半導体装置において、配線基板21の代わりに実装基板(マザーボード)601を使い、ベアチップ実装の電子装置を構成することも可能である。

【0214】

以上、本発明を好ましい実施形態について説明したが、本発明はかかる特定の実施形態に限定されるものではなく、特許請求の範囲に記載した要旨内において様々な変形・変更が可能である。

(付記1)

基板と、

前記基板の主面上にフリップチップ状態で搭載された半導体素子と、

前記基板の主面のうち、前記半導体素子の少なくとも一の縁部に沿って配設された第1の導電パタ―ンと、

前記基板の主面上に於いて、前記第1の導電パタ―ンから離間し、かつ前記第1の導電パタ―ンに沿って配設された第2の導電パタ―ンと、

前記基板の主面上に於いて、前記第1の導電パタ―ンと第2の導電パタ―ンとの間の橋絡状態をもって配置された受動素子と、

前記基板と前記半導体チップとの間の空間を充填する樹脂層と、

を含み、

前記樹脂層は、前記基板の主面に於いて、前記半導体素子と前記第1の導電パタ―ンとの間に延在することを特徴とする半導体装置。

(付記2)

前記第1の導電パタ―ンは、前記半導体素子を囲繞していることを特徴とする付記1記載の半導体装置。

(付記3)

前記第2の導電パタ―ンは、前記第1の導電パタ―ンを囲繞していることを特徴とする付記1または2記載の半導体装置。

(付記4)

前記第2の導電パタ―ンは、前記第1の導電パタ―ンを全体として囲繞する複数の部材より構成されることを特徴とする付記1または2記載の半導体装置。

(付記5)

前記第1の導電パタ―ンは、前記半導体素子の外縁に一致して延在することを特徴とする付記1〜4のうち、いずれか一項記載の半導体装置。

(付記6)

前記第1の導電パタ―ンは、前記半導体素子に近接して延在する第1の部分と、前記半導体素子から離間して延在する第2の部分と、前記第1の部分と前記第2の部分を接続する屈曲部とを有し、前記第2の導体パターンは前記第1の導体パターンに平行して延在し、前記受動素子は、前記第1の導電パタ―ンの第1の部分に形成されることを特徴とする付記1〜4のうち、いずれか一項記載の半導体装置。

(付記7)

前記屈曲部では前記第1の導電パタ―ンは直角に屈曲することを特徴とする付記6記載の半導体装置。

(付記8)

前記屈曲部では前記第1の導電パタ―ンは、前記第1の部分から前記第2の部分へと漸移することを特徴とする付記6記載の半導体装置。

(付記9)

前記第1の導電パタ―ンは、前記半導体チップを全体として囲繞する複数の部材より構成されることを特徴とする付記1記載の半導体装置。

(付記10)

前記第1の導電パタ―ンと前記第2の導電パタ―ンの一方には電源電圧が供給され、他方には接地電圧が供給されることを特徴とする付記1〜9のうち、いずれか一項記載の半導体装置。

(付記11)

前記受動素子は、第1の端子と第2の端子を有する二端子素子であり、前記受動素子は、前記第1の端子が前記第1の導電パタ―ンに、前記第2の端子が前記第2の導電パタ―ンに接続された状態で実装されていることを特徴とする付記10記載の半導体装置。

(付記12)

前記第1の導電部材および前記第2の導電部材は、それぞれ前記第1の導電部材の他の部分および前記第2の導電部材の他の部分よりも幅広の第1の接続部および第2の接続部を含み、前記受動素子は、前記第1の端子を前記第1の接続部に、前記第2の端子を前記第2の接続部に接続して実装されていることを特徴とする付記11記載の半導体装置。

(付記13)

前記第1の導電パタ―ンと前記第2の導電パタ―ンの一方には第1の電源電圧が供給され、他方には接地電圧が供給され、さらに前記第2の導電部材の外側には、第3の電源電圧が供給される別の受動素子が配置されていることを特徴とする付記1〜9のうち、いずれか一項記載の半導体装置。

(付記14)

前記第1の導電パタ―ンと前記第2の導電パタ―ンのいずれにも接地電圧が供給され、前記第1の導電パタ―ンには、前記基板表面を露出する複数のカットアウトが、それぞれ、前記基板表面上に形成され電源電圧を供給される第1の電極パッドを露出するように形成されており、前記第2の導電パタ―ンには、前記基板表面を露出する複数のカットアウトが、それぞれ、前記基板表面上に形成され前記電源電圧を供給される第2の電極パッドを露出するように形成されており、前記基板上には、前記受動素子として、第1の側縁部に前記第1の導電パタ―ンに接続される複数の第1の接地端子と、前記第1の電極パッドに接続される複数の第1の電源端子とが交互に配列され、前記第1の側縁部に対向する第2の側縁部に、前記第2の導電パタ―ンに接続される複数の第2の接地端子と、前記第2の電極パッドに接続される複数の第2の電源端子が交互に配列された多端子キャパシタが、前記複数の第1の接地端子が前記第1の導電パタ―ンに接続され、前記複数の第1の電源端子が、対応する複数の前記第1の電極パッドに接続され、前記複数の第2の接地端子が前記第2の導電パタ―ンに接続され、前記複数の第2の電源端子が、対応する複数の前記第2の電極パッドに接続された状態で、実装されていることを特徴とする付記1〜9のうち、いずれか一項記載の半導体装置。

(付記15)

前記第1の導電パタ―ンと前記第2の導電パタ―ンのいずれにも接地電圧が供給され、前記第1の導電パタ―ンには、前記基板表面を露出する複数の第1のカットアウトが、それぞれ、前記基板表面上に形成され第1の電源電圧を供給される第1の電極パッドを露出するように形成されており、前記第2の導電パタ―ンには、前記基板表面を露出する複数の第2のカットアウトが、それぞれ、前記基板表面上に形成され前記第1の電源電圧を供給される第2の電極パッドを露出するように形成されており、

前記第1の導電パタ―ンには、前記基板表面を露出する複数の第3のカットアウトが、それぞれ、前記基板表面上に形成され第2の電源電圧を供給される第3の電極パッドを露出するように形成されており、前記第2の導電パタ―ンには、前記基板表面を露出する複数の第4のカットアウトが、それぞれ、前記基板表面上に形成され前記第2の電源電圧を供給される第4の電極パッドを露出するように形成されており、

前記基板上には、前記受動素子として、第1の側縁部に前記第1の導電パタ―ンに接続される複数の第1の接地端子と、前記第1の電極パッドに接続される複数の第1の電源端子とが交互に配列され、前記第1の側縁部に対向する第2の側縁部に、前記第2の導電パタ―ンに接続される複数の第2の接地端子と、前記第2の電極パッドに接続される複数の第2の電源端子が交互に配列された第1の多端子キャパシタが、前記複数の第1の接地端子が前記第1の導電パタ―ンに接続され、前記複数の第1の電源端子が、対応する複数の前記第1の電極パッドに接続され、前記複数の第2の接地端子が前記第2の導電パタ―ンに接続され、前記複数の第2の電源端子が、対応する複数の前記第2の電極パッドに接続された状態で、実装されており、

前記基板上にはさらに、前記受動素子として、第3の側縁部に前記第1の導電パタ―ンに接続される複数の第3の接地端子と、前記第3の電極パッドに接続される複数の第3の電源端子とが交互に配列され、前記第3の側縁部に対向する第4の側縁部に、前記第2の導電パタ―ンに接続される複数の第4の接地端子と、前記第2の電極パッドに接続される複数の第4の電源端子が交互に配列された第2の多端子キャパシタが、前記複数の第3の接地端子が前記第1の導電パタ―ンに接続され、前記複数の第3の電源端子が、対応する複数の前記第3の電極パッドに接続され、前記複数の第4の接地端子が前記第2の導電パタ―ンに接続され、前記複数の第4の電源端子が、対応する複数の前記第4の電極パッドに接続された状態で、実装されていることを特徴とする付記1〜9のうち、いずれか一項記載の半導体装置。

(付記16)

前記第2の導電パタ―ンの外側には、複数の導電パタ―ンが前記第2の導電パタ―ンを囲繞して同心的に形成されており、前記複数の導電パタ―ンには、接地電圧と電源電圧が交互に供給され、前記電源電圧は、各導電パタ―ンで異なっており、前記第2の導電パタ―ンおよび前記複数の導電パタ―ンには、任意の導電パタ―ンと、その外側に隣接する導電パタ―ンとの間に、受動素子が橋絡状態をもって配置されていることを特徴とする付記1〜9のうち、いずれか一項記載の半導体装置。

(付記17)

前記基板上には接合部を有する封止部材が、前記接合部を前記基板の主面に接合した状態で、また前記半導体チップの上主面に接合した状態で実装されており、前記接合部は、前記基板の外縁よりも内側に寄った位置において前記基板の主面に接合されることを特徴とする付記1〜16のうち、いずれか一項記載の半導体装置。

(付記18)

基板と、

前記基板の主面上にフリップチップ状態で搭載された複数の半導体素子と、

前記基板の主面のうち、前記複数の半導体素子の各々を囲繞して配設された第1の導電パタ―ンと、

前記基板の主面上、前記各々の半導体素子について、前記第1の導電パタ―ンから離間し、かつ前記第1の同導電素子を囲繞して配設された第2の導電パタ―ンと、

前記基板上、前記各々の半導体素子について、前記第1の導電パタ―ンと前記第2の導電パタ―ンとの間を架橋して配置された受動素子と、

前記各々の半導体チップについて、前記基板と当該半導体素子との間の空間を充填する樹脂層と、

を含み、

前記各々の半導体素子について、前記樹脂層は、前記基板の主面のうち、前記第1の導電パタ―ンが囲繞する領域に限定されることを特徴とする半導体装置。

(付記19)

基板の主面上に於ける、半導体素子の実装領域の近傍に、第1の導電パタ―ン及び第2の導体パターンを形成する工程と、

前記第1の導電パタ―ンと第2の導体パターンとの間に、受動素子を、橋絡状態をもって配置する工程と、

前記実装領域に、半導体素子をフリップチップ実装する工程と、

前記基板と前記半導体素子との間に樹脂を充填する工程と

を含むことを特徴とする半導体装置の製造方法。

(付記20)

基板の主面上に於ける、半導体素子の実装領域の近傍に、第1の導電パタ―ン及び第2の導体パターンを形成する工程と、

前記第1の導電パタ―ンと第2の導体パターンとの間に、受動素子を、橋絡状態をもって配置する工程と、

前記実装領域上に樹脂を塗布する工程と、

前記実装領域に、半導体素子をフリップチップ実装する工程と

を含むことを特徴とする半導体装置の製造方法。

【符号の説明】

【0215】

10,20,20A,20B,20C,20D,20E,20F,40,40A,60,80,100 半導体装置

11,21 配線基板

11A,21A 上側主面

11B,21B 下側主面

11a1,11a2,11b,21a,21b,25A,26A 電極パッド

12,22 半導体素子

13,23,43 アンダーフィル樹脂

14,24,241〜246,441〜443 受動素子

14A,14B 電極

14C,24C セラミックキャパシタ本体

15A,15B 半田

15a,15b 半田延出部

21M 実装領域

21V 内部配線

21V1,21V2,21V3 電源パタ―ン

21v1,21v2 ビアプラグ

21e 配線基板縁部

22a 半田バンプ

24A,24B,34a,34b,45a〜48a,45b〜48b,48c〜48h 電極

24c,24d キャパシタ電極

25 第1の導電パタ―ン

25a,25b,26a,26b カットアウト

26,261 第2の導電パタ―ン

262〜264 外側導電パタ―ン

25AW,26AW チップ型容量素子形成位置

25W,26W 幅広パタ―ン

31 ディスペンサ

34,341〜34353A,53B,53C,53D,53E,53Fm53G,53H 多端子キャパシタ

35 DRAM

36,39 接着剤

38 封止部材

38e 封止部材縁部

38A 接合部

61A〜61D 半導体装置要素

【技術分野】

【0001】

本発明は半導体装置に係り、特に配線基板上に半導体素子をフリップチップ実装した半導体装置、およびその製造方法に関する。

【背景技術】

【0002】

フリップチップ実装は今日の半導体装置において広く使われている技術である。

【0003】

フリップチップ実装では、配線パタ―ンが形成された配線基板の主面上に半導体素子が、電極パッドが形成された面を前記主面に対向させて載置され、前記電極パッドを前記配線パタ―ンに半田バンプなどにより接続する。

【0004】

フリップチップ実装を行うことにより、半導体素子と配線基板との間の配線長が短縮され、寄生インピーダンス或いは寄生インダクタンスの効果を低減することができる。また半導体素子で生じた熱を、半田バンプを介して効率的に配線基板へと散逸させることができる。

【0005】

フリップチップ実装では、このように半導体素子を配線基板上に実装した後、前記半田バンプおよび配線パタ―ンを保護し、また半導体素子を機械的に支持するため、半導体素子と配線基板との間の隙間に、アンダーフィル樹脂が注入される。アンダーフィル樹脂の充填は、一般に毛細管現象を使って行われ、このため、このようなアンダーフィル樹脂としては、ボイドの巻き込み或いは未充填の問題が生じないように、流動性および濡れ性に優れた樹脂が使われる。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2006−140327号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

半導体素子を配線基板上に搭載し半導体装置を形成する際、当該半導体素子の電源回路のON,OFFに伴い雑音(ノイズ)が生ずるなどして電源電圧が変動することにより、当該半導体素子の動作が不安定なものとなることを防止する為に、前記半導体素子の近傍に於いて、電源線と接地線(グランド線)との間に容量素子が配置される。

【0008】

当該容量素子としては、例えば容量が100pF程度、外形寸法1.6×0.8mm角程のセラミックキャパシタが適用される。

【0009】

当該容量素子は、その形状から、チップ型容量素子と称される。

【0010】

例えば半導体素子中のトランジスタが一斉にONした場合などには、電源線に大きな負荷がかかり、電源電圧が低下し、一方これらのトランジスタが一斉にOFFした場合には、電源ラインに大きなサージが発生する。

【0011】

チップ型容量素子は、このような電源ラインの電圧変動を平滑化して、安定した電源電圧の供給を可能にする。

【0012】

また、前記半導体素子の周囲には、前記アンダーフィル樹脂が拡がり、流動性および濡れ性の良い樹脂ほど遠方まで拡がる傾向がある。

【0013】

そこで、従来、チップ型容量素子を配線基板上に配置する場合には、当該アンダーフィル樹脂の拡がりを避けて、半導体素子から離間して配置する必要があった。

【0014】

しかし、チップ型容量素子を半導体素子から離間して配置すると、その間の配線パタ―ンに起因する寄生インダクタンス或いは寄生キャパシタンスにより、半導体装置全体の電気特性が低下してしまう。

【0015】

また、チップ型容量素子を半導体素子から離間して配置することにより、配線基板の面積の増大を招き、半導体装置として小形化が困難となる。

【0016】

さらに、前記アンダーフィル樹脂として、流動性および濡れ性に優れた樹脂を用いた場合、空間に注入したアンダーフィル樹脂が流出してしまい、半導体素子を側方から支える樹脂フィレットの形成が不十分となる。

【0017】

従来の半導体装置10の構成を、図1A,図1Bに示す。図1Bは、図1Aに於ける線A−A’に沿った断面を示す。

【0018】

図1Aおよび図1Bを参照するに、配線基板11の上側主面11Aには半導体素子12がフリップチップ状態で搭載されている。

【0019】

そして、配線基板11と半導体素子12の間の空間に注入されたアンダーフィル樹脂13が、前記配線基板11の上側主面11Aに於いて、半導体素子12が占有する領域を超えて、距離L1にわたり拡がっている。

【0020】

そして前記配線基板11の主面には、半導体素子12の近傍に、当該半導体素子12の側縁から距離L1以上離れて、チップ型容量素子14が配置されている。

【0021】

一方、配線基板11の下側主面11Bには、外部接続のための電極パッド11bが形成されている。

【0022】

前記チップ型容量素子14が前記アンダーフィル樹脂13により覆われてしまうと、図1A,図1Bの半導体装置が前記配線基板11上の電極パッド11bへの半田バンプ(ボール)の形成工程或いは放熱部材の半田付け工程などの後工程で熱処理を受けた場合、図2Aに示すようにチップ型容量素子14下部の、前記配線基板11との間の隙間において溶融半田が矢印方向に飛び出して短絡を生ずるか、あるいは図2Bに示すようにアンダーフィル樹脂層13が途切れた部分で溶融半田が矢印のように飛び出して半田ボール15Xを形成してしまう。

【0023】

ただし図2A,図2Bは、前記チップ型容量素子14を切る線A−A’に沿った断面図の一部であり、前記チップ型容量素子14は、セラミックキャパシタ本体となるセラミック部材14Cとその両側に形成された電極14A,14Bを有しており、また前記配線基板11の上側主面11A上には、前記電極14A,14Bにそれぞれ対応して電極パッド11a1,11a2が形成されている。

【0024】

前記電極14Aは前記電極パッド11a1に半田15Aにより接続され、前記電極14Bは前記電極パッド11a2に半田15Bにより接続される。なお図1および図2A,図2B中、配線基板11中に形成される多層配線構造については図示を省略している。

【0025】

図2Aを参照するに、前記チップ型容量素子14と配線基板11の上側主面11Aとの間には隙間ないし空間が形成されているが、先にも述べたように前記配線基板11に熱処理が加えられると、前記半田15A,15Bは溶融して矢印で示すように飛び出し、その結果形成される半田延出部15a,15bが短絡を生じてしまう恐れがある。

【0026】

また図2Bの例では、前記アンダーフィル樹脂13が途切れた部分において溶融半田が飛び出し、半田ボール15Xが形成されている。このようにして形成された半田ボール15Xは、図2B中、矢印でしめしたように飛び出すことがある。

【0027】

図2Cは、このような半田ボールの実際の例を示す写真である。ただし図2Cは前記配線基板11の上側主面11Aを垂直に見下ろした図であり、アンダーフィル樹脂13が黒く示されている。

【0028】

図2Cを参照するに、アンダーフィル樹脂の外縁13Eが白く輝いており、溶融半田がアンダーフィル樹脂の外縁13Eまで飛び出している。また所々に半田ボール15Xが形成されている。

【0029】

このように図1A,図1Bの半導体装置では、チップ型容量素子14は前記アンダーフィル樹脂13の外縁よりも外側に配置する必要があり、このため半導体素子12の外縁から距離L1以上離れた位置に形成する必要があった。前記図1A,図1Bの半導体装置10の場合、この距離L1は、2mmあるいはそれ以上になる場合があった。

【0030】

しかし、このようにチップ型容量素子14を半導体素子12から遠く離れた位置に形成すると、先にも述べたように配線の寄生インダクタンスや寄生インピーダンスの効果により、半導体装置の電気特性が劣化してしまう問題が生じる。

【0031】

またチップ型容量素子14を半導体素子12から離間して配置することにより、配線基板11の面積が増大し、半導体装置のサイズが増大してしまう問題が生じる。

【0032】

さらに先にも説明したように、前記アンダーフィル樹脂13は、高い流動性により前記配線基板11と半導体素子12との間の隙間から流れ出してしまう恐れがあり、アンダーフィル樹脂13による前記半導体素子11側面の力学的な支持が不十分となる恐れがある。

【課題を解決するための手段】

【0033】

実施形態の一観点によれば、基板と、前記基板の主面上にフリップチップ状態で搭載された半導体素子と、前記基板の主面に於いて、前記半導体素子の少なくとも一つの縁部に沿って配設された第1の導電パタ―ンと、前記基板の主面上に於いて、前記第1の導電パタ―ンから離間し、かつ前記第1の導電パタ―ンに沿って配設された第2の導電パタ―ンと、前記基板の主面上に於いて、前記第1の導電パタ―ンと第2の導電パタ―ンとの間に橋絡状態をもって配置された受動素子と、前記基板と前記半導体素子との間に充填された樹脂とを有し、前記樹脂は、前記基板の主面に於いて、前記半導体素子と前記第1の導電パタ―ンと間に延在することを特徴とする半導体装置が提供される。

【0034】

実施形態の他の観点によれば、基板の主面上に於ける、半導体素子の実装領域の近傍に、第1の導電パタ―ン及び第2の導体パターンを形成する工程と、前記第1の導電パタ―ンと第2の導体パターンとの間に、受動素子を、橋絡状態をもって配置する工程と、前記実装領域に、半導体素子をフリップチップ実装する工程と、前記基板と前記半導体素子との間に樹脂を充填する工程とを含むことを特徴とする半導体装置の製造方法が提供される。

【0035】

実施形態のさらに他の観点によれば、基板の主面上に於ける、半導体素子の実装領域の近傍に、第1の導電パタ―ン及び第2の導体パターンを形成する工程と、前記第1の導電パタ―ンと第2の導体パターンとの間に、受動素子を、橋絡状態をもって配置する工程と、前記実装領域上に樹脂を塗布する工程と、前記実装領域に、半導体素子をフリップチップ実装する工程とを含むことを特徴とする半導体装置の製造方法が提供される。

【発明の効果】

【0036】

前記第1の導電パタ―ンはアンダーフィル樹脂のダムとして作用し、前記半導体素子と配線基板との間にアンダーフィル樹脂を充填する際に、アンダーフィル樹脂が前記第1の導電パタ―ンを超えて流出することがない。

【0037】

そこで、前記第1の導電パタ―ンを前記半導体素子が占有する領域に近接して配設することにより、前記受動素子を前記半導体素子に近接して配置することが可能となる。これにより、半導体装置の電気特性を安定化させることが可能となる。

【図面の簡単な説明】

【0038】

【図1A】従来の半導体装置を示す平面図である。

【図1B】図1A中、線A−A’に沿った断面図である。

【図2A】図1A,図1Bの半導体装置における問題点を説明する断面図である。

【図2B】図1A,図1Bの半導体装置における問題点を説明する断面図である。

【図2C】図1A,図1Bの半導体装置における問題点を説明する写真を示す図である。

【図3A】第1の実施形態による半導体装置を示す平面図である。

【図3B】図3A中、線B−B’に沿った断面図である。

【図4A】図3A中、線C−C’に沿った拡大断面図である。

【図4B】図3A中、線D−D’に沿った拡大断面図である。

【図4C】図4A中、線d−d’に沿った断面図である。

【図5A】第1の実施形態による半導体装置の製造方法を説明する平面図(その1)である。

【図5B】第1の実施形態による半導体装置の製造方法を説明する断面図(その1)である。

【図6A】第1の実施形態による半導体装置の製造方法を説明する平面図(その2)である。

【図6B】第1の実施形態による半導体装置の製造方法を説明する断面図(その2)である。

【図7A】第1の実施形態による半導体装置の製造方法を説明する平面図(その3)である。

【図7B】第1の実施形態による半導体装置の製造方法を説明する断面図(その3)である。

【図8A】第1の実施形態による半導体装置の製造方法を説明する平面図(その4)である。

【図8B】第1の実施形態による半導体装置の製造方法を説明する断面図(その4)である。

【図9A】第1の実施形態による半導体装置の製造方法を説明する平面図(その5)である。

【図9B】第1の実施形態による半導体装置の製造方法を説明する断面図(その5)である。

【図10A】第1の実施形態による半導体装置の製造方法を説明する平面図(その6)である。

【図10B】第1の実施形態による半導体装置の製造方法を説明する断面図(その6)である。

【図11A】第1の実施形態における受動素子の実装の詳細を示す平面図である。

【図11B】図11A中、線F−F’に沿った断面を、半田リフロー前の状態で示す断面図である。

【図11C】図11A中、線F−F’に沿った断面を、半田リフロー後の状態で示す断面図である。

【図12】第1の実施形態の一変形例を示す拡大平面図である。

【図13A】第1の実施形態の一変形例を示す平面図である。

【図13B】第1の実施形態の一変形例を示す平面図である。

【図14A】第1の実施形態の一変形例を示す平面図である。

【図14B】図14Aで使われる多端子セラミックキャパシタを示す斜視図である。

【図14C】第1の実施形態の一変形例を示す平面図である。

【図15A】図10A,図10Bに引き続いて実行される半導体装置の製造工程を説明する断面図(その1)である。

【図15B】図10A,図10Bに引き続いて実行される半導体装置の製造工程を説明する断面図(その2)である。

【図15C】図10A,図10Bに引き続いて実行される半導体装置の製造工程を説明する断面図(その3)である。

【図16A】ダム作用が無い場合のアンダーフィル樹脂の濡れ拡がりの様子を示す写真である。

【図16B】ダム作用がある場合のアンダーフィル樹脂の濡れ拡がりの様子を示す写真である。

【図16C】図16B中、四角Aで囲んだ部分を詳細に示す拡大図である。

【図17】第1の実施形態の一変形例を示す断面図である。

【図18A】第1の実施形態の一変形例を示す平面図である。

【図18B】第1の実施形態の一変形例を示す平面図である。

【図18C】図18Aおよび図18B中、線G−G’に沿った断面図である。

【図18D】図18A中、線H−H’に沿った断面図である。

【図18E】図18B中、線I−I’に沿った断面図である。

【図19】第1の実施形態の一変形例を示す平面図である。

【図20A】第2の実施形態による半導体装置の製造方法を説明する平面図(その1)である。

【図20B】第2の実施形態による半導体装置の製造方法を説明する断面図(その1)である。

【図21A】第2の実施形態による半導体装置の製造方法を説明する平面図(その2)である。

【図21B】第2の実施形態による半導体装置の製造方法を説明する断面図(その2)である。

【図22A】第2の実施形態による半導体装置の製造方法を説明する平面図(その3)である。

【図22B】第2の実施形態による半導体装置の製造方法を説明する断面図(その3)である。

【図23A】第2の実施形態による半導体装置の製造方法を説明する平面図(その4)である。

【図23B】第2の実施形態による半導体装置の製造方法を説明する断面図(その4)である。

【図24A】第2の実施形態による半導体装置の製造方法を説明する平面図(その5)である。

【図24B】第2の実施形態による半導体装置の製造方法を説明する断面図(その5)である。

【図25A】第2の実施形態による半導体装置の製造方法を説明する平面図(その6)である。

【図25B】第2の実施形態による半導体装置の製造方法を説明する断面図(その6)である。

【図26A】第2の実施形態の一変形例による半導体装置を示す平面図である。

【図26B】図26A中、線K−K’に沿った断面図である。

【図26C】図26A中、線L−L’に沿った断面図である。

【図27】第3の実施形態による半導体装置を説明する平面図である。

【図28】第3の実施形態による半導体装置の比較例を示す平面図である。

【図29】第3の実施形態による半導体装置の別の比較例を示す平面図である。

【図30】第3の実施形態の一変形例を説明する平面図である。

【図31】第4の実施形態による半導体装置を説明する平面図である。

【図32】第5の実施形態による半導体装置を説明する平面図である。

【図33A】第6の実施形態による半導体装置を説明する平面図(その1)である。

【図33B】第6の実施形態による半導体装置を説明する平面図(その2)である。

【図34A】第6の実施形態の一変形例を説明する平面図(その1)である。

【図34B】第6の実施形態の一変形例を説明する平面図(その2)である。

【図35A】第6の実施形態の他の変形例を説明する平面図(その1)である。

【図35B】第6の実施形態の他の変形例を説明する平面図(その2)である。

【図36A】第6の実施形態のさらに他の変形例を説明する平面図(その1)である。

【図36B】第6の実施形態のさらに他の変形例を説明する平面図(その2)である。

【図37A】図36を、半導体素子およびアンダーフィル樹脂の一部まで含めて示す平面図である。

【図37B】図37A中、線M−M’に沿った断面図である。

【図37C】図37A中、線N−N’に沿った断面図である。

【図37D】図37A中、線O−O’に沿った断面図である。

【図37E】図37A中、線P−P’に沿った断面図である。

【図38】他の実施形態による半導体装置の例を示す平面図である。

【図39】他の実施形態による半導体装置の例を示す平面図である。

【図40A】さらに他の実施形態による半導体装置の例を示す断面図である。

【図40B】さらに他の実施形態による半導体装置の例を示す断面図である。

【図40C】さらに他の実施形態による半導体装置の例を示す断面図である。

【図40D】さらに他の実施形態による電子装置の例を示す断面図である。

【発明を実施するための形態】

【0039】

[第1の実施形態]

図3A,図3Bは、第1の実施形態によるシングルチップ構成の半導体装置20の構成を示す、それぞれ平面図および断面図である。ただし図3Bは、図3Aの中、線B−B’に沿った半導体装置20の断面を示す。

【0040】

図3Aおよび図3Bを参照するに、配線基板21の上側主面21Aには半導体素子22がフリップチップ状態で搭載されているが、前記上側主面21Aには、前記半導体素子22が占有する領域(C4)を含む領域21M(以下、実装領域と称する)を多重に囲繞して、例えば半田よりなる第1の導電パターン25が形成されており、さらにその外側に、前記第1の導体パタ―ン25を囲繞して、同じく例えば半田よりなる第2の導電パタ―ン26が形成されている。

【0041】

後で詳細に説明するように、前記第1の導体パタ―ン25は、前記配線基板21の主面と前記半導体素子22との間の隙間を充填するアンダーフィル樹脂23のダムとして作用し、前記アンダーフィル樹脂23は前記第1の導電パタ―ン25が画成する前記実装領域21Mの外側に拡がることがない。

【0042】

さらに本実施形態の半導体装置20では、前記半導体素子22を囲んで、前記第1の導電パタ―ン25と前記第2の導電パタ―ン26を架橋するように、多数のチップ型容量素子24が配置されている。

【0043】

また前記配線基板21の下側主面21Bには、外部接続用の電極パッド21bが多数形成されている。

【0044】

本実施形態の半導体装置20では、前記第1の導電パタ―ン25がアンダーフィル樹脂23のダムとして作用するため、前記第1の導電パタ―ン25を前記半導体素子21に近接して配置することにより、すなわち前記半導体素子22と第1の導電パタ―ン25との間の距離L2を、図1A,図1Bに示した例における距離L1よりも短く設定することにより(L2<L1)、前記アンダーフィル樹脂23の拡がりを、前記実装領域21M,すなわち前記半半導体素子22の占有領域C4の近傍に閉じ込めることが可能となり、前記アンダーフィル樹脂23が前記配線基板21と前記半導体素子22との間の隙間から流れ出してしまい、アンダーフィル樹脂23による半導体素子22側面の支持が不十分になる問題が回避される。

【0045】

また前記実装領域21Mのすぐ外側にチップ型容量素子24を配置することが可能となり、先に説明した寄生インダクタンスおよび寄生キャパシタンスの増加の問題、およびこれに起因する半導体装置20の電気特性の劣化の問題が回避される。

【0046】

さらに前記距離L2を短縮することにより、従来アンダーフィル樹脂により覆われていた配線基板21の表面に、チップ型容量素子以外にも様々な受動素子や能動素子を配置することが可能となり、基板面積の利用効率が向上する。

【0047】

また、図4Aは、図3Aに於ける線C−C’に沿った拡大断面図を、図4Bは、図3A中、線D−D’に沿った拡大断面図であり、半導体装置20のそれぞれの断面構造を示す。

【0048】

図4Aを参照するに、前記配線基板21中には、電源パタ―ン21V1とその下に電源パタ―ン21V2を含む内部配線21Vが形成されており、前記電源パタ―ン21V1と21V2の一方が図示しない電源端子に、また他方が同じく図示しない接地端子に接続されている。

【0049】

前記配線基板21の上側主面21Aには、前記半導体素子22が占有する領域C4に電極パッド21aが行列状に配置されており、前記電極パッド21aには、前記半導体素子22の回路面22Aに行列状に形成された半田バンプ22aが接続されている。さらに前記電源パタ―ン21V1からは対応する電極パッド21aにビアプラグ21v1が延在し、電源電圧あるいは接地電圧(グランド)が供給され、また前記電源パタ―ン21V2からは対応する電極パッド21aにビアプラグ21v2が延在し、前記電源パタ―ン21V1に電源電圧が供給されている場合には接地電圧(グランド)が、また前記電源パタ―ン21V1に接地電圧が供給されている場合には電源電圧が供給される。その際、下側の前記電源パタ―ン21V2から延在するビアプラグ21v2は、図4Cに示すように前記上側の電源パタ―ン21v1中に形成された開口部中を延在し、短絡が回避される。

【0050】

尚図4Cは、図4Aに於ける線D−D’に沿った断面を示している。

【0051】

前記図4Aでは、前記配線基板21の上側主面21A上に、前記導電パタ―ン25に対応して電極パッド25Aが、前記実装領域21Mを囲繞して形成されており、さらに前記電極パッド25Aの外側に前記導電パタ―ン26に対応して電極パッド26Aが、前記電極パッド25Aを囲繞するように形成されている。前記電極パッド25Aおよび前記導電パタ―ン25には、電源パタ―ン21V1およびビアプラグ21v1から電源電圧または接地電圧が供給され、前記電極パッド26Aおよび前記導電パタ―ン26には電源パタ―ン21V2およびビアプラグ21v2から接地電圧または電源電圧が供給される。

【0052】

また、図4Aに示す構成では、前記電極パッド25Aと電極パッド26Aとの間に、内部にキャパシタ電極24cおよびキャパシタ電極24dを合対向して有するセラミックキャパシタ本体24Cを有する二端子構成のチップ型容量素子24が、前記電極パッド25Aと電極パッド26Aとを架橋するように配置され、前記キャパシタ電極24cが、対応する電極パッド24Aを介して前記電極パッド25Aに、前記第1の導電パタ―ン25を構成する半田パタ―ンにより接続され、また前記キャパシタ電極24dが、対応する電極パッド24Bを介して前記電極パッド26Aに、前記第2の導電パタ―ン26を構成する半田パタ―ンにより接続されている。このようなチップ型容量素子24としては、例えば株式会社村田製作所より市販のLLLシリーズの製品などを使うことができる。

【0053】

一方、図4Bに示す構成にあっては、前記チップ型容量素子24は含まれておらず、前記電極パッド25A上に前記第1の導電パタ―ン25を構成する半田パタ―ンが、また前記電極パッド25B上に前記第2の導電パタ―ン26を構成する半田パタ―ンが、それぞれ形成されている。

【0054】

図4A,図4Bのいずれにおいても前記第1の導電パタ―ン25および第2の導電パタ―ン26を構成する半田パタ―ンは前記配線基板21の上側主面21Aから上方に盛り上がっており、特に内側の第1の導電パタ―ン25を構成する半田パタ―ンは、前記アンダーフィル樹脂23の拡がりを阻止するダムとして作用する。

【0055】

前記第1の導電パタ―ン25,第2の導電パタ―ン26に対応する半田パタ―ンの上方への盛り上がりの好ましい高さは、前記アンダーフィル樹脂23との濡れ性により多少変化するが、例えば前記アンダーフィル樹脂23としてエイブルスティック社のUF8802Fを使った場合、80μm程度あるいはそれ以上に設定しておくのが好ましく、100μmの高さがあれば、通常のアンダーフィル樹脂に対しては十分である。

【0056】

本実施形態によれば、アンダーフィル樹脂23の拡がりが前記第1の導電パタ―ン25で阻止されるため、チップ型容量素子24などの受動素子がアンダーフィル樹脂23で覆われる恐れがなく、前記配線基板21の下側主面21Bに半田バンプを形成する際などにおいて熱処理がなされる場合でも、これらの受動素子において溶融半田の飛び出しによる半田ボールの形成、或いはこのような半田ボールに起因する短絡の発生が回避される。

【0057】

前記図3A,図3Bに示す半導体装置20の製造方法を、図5A,図5B〜図10A,図10Bに示す。

【0058】

図5A,図5Bを参照するに、前記配線基板21上には前記半導体素子22の占有領域C4に、前記半導体素子22の回路面22A上の半田バンプ22aに対応して電極パッド21aが行列状に形成されており、また前記第1の導電パタ―ン25の形成位置に電極パッド25Aが、前記半導体素子22の占有領域C4を含む実装領域21Mを囲繞するように形成されている。また前記電極パッド25Aの外側で前記第2の導電パタ―ン26の形成位置に、前記電極パッド25Aを囲繞するように電極パッド26Aが形成されている。

【0059】

なお図6B、および図7B〜図10Bにおいて前記電極パッド21aは簡単のため連続した電極パターンを図示しているが、これらは図5Aに示すように行列状に配列された小さな電極パッドより構成されている。

【0060】

次に図6A,図6Bを参照するに、前記電極パッド25Aおよび26A上にクリーム半田パタ―ン25Bおよび26Bがそれぞれ印刷される。

【0061】

さらに図7A,図7Bを参照するに、前記クリーム半田パタ―ン25Bと26Bを架橋するように、チップ型容量素子24が配置され、前記クリーム半田パタ―ン25Bと26Bを溶融させることにより、前記チップ型容量素子24が所望の数だけ実装される。

【0062】

チップ型容量素子24の実装の詳細については、後述する。

【0063】

前記クリーム半田パタ―ン25Bおよび26Bの溶融により、前記配線基板21上には前記電極パッド25Aおよび26Aにそれぞれ対応して、第1の導電パタ―ン25および第2の導電パタ―ン26が、半田パタ―ンにより形成される。

【0064】

次に図8Aおよび図8Bを参照するに、前記配線基板21上に半導体素子22がフリップチップ実装され、前記半導体素子22の回路面22Aに形成されたそれぞれの半田バンプ22aが、前記配線基板21の対応する電極パッド21aと接続される。

【0065】

次に図9Aおよび9Bを参照するに、ディスペンサ31を使って前記アンダーフィル樹脂23が、前記配線基板21と半導体素子22との間の隙間に、毛細管現象を使って充填される。

【0066】

図9Aおよび図9Bに示す工程では、前記アンダーフィル樹脂23の充填は、前記ディスペンサ31の先端を、前記導電パタ―ン25の内側に配置させて実行される。

【0067】

このようにして充填されたアンダーフィル樹脂23は、硬化される。

【0068】

前記図10Aおよび図10Bに示す半導体装置20について、必要に応じて前記配線基板21の下側主面上のパッド電極21bに半田バンプを形成し、これを製品として顧客に引き渡すことができる。

【0069】

本実施形態によれば、前記ディスペンサ31により充填されたアンダーフィル樹脂23は、ダムとして作用する前記第1の導電パタ―ン25によりせき止められ、実装領域21M(図7A参照)の外側には流出しない。

【0070】

前記図7A,図7Bに示すチップ型容量素子24の実装プロセスを、図11A〜図11Cに示す。

【0071】

尚、図11Bおよび図11Cは、図11Aに於いて、線F−F’に沿った断面を示す。

【0072】

図11Bは、前記第1の導電パタ―ン25および第2の導電パタ―ン26を構成する半田パタ―ンが溶融する以前の状態を示し、図11Cは前記半田パタ―ンが溶融した後の状態を示している。なお図11Bおよび図11Cにおいて、前記セラミック本体24C中に形成されるキャパシタ電極24c,24dの図示は省略する。

【0073】

図11Aおよび図11Bを参照するに、前記チップ型容量素子24はその電極24A,24Bが前記第1の電極パターン25および第2の電極パターン26を構成するクリーム半田パタ―ン25Bおよび26Bにそれぞれコンタクトするように載置され、さらに前記半田パタ―ンを溶融させることにより、前記電極24Aおよび24Bを覆って溶融半田がはい上がり、図11Cに示すようにチップ型容量素子24が実装される。

【0074】

この様な半田パタ―ンの溶融の際、前記電極パッド25Aおよび26Aの幅や長さが異なっていると、溶融半田の表面張力の平衡がくずれ、チップ型容量素子24が立ち上がっていわゆるツームストン現象、あるいはマンハッタン現象と称される不良を生じる恐れがあるが、本実施形態では前記電極パッド25Aおよび26A、およびその上の第1の導電パタ―ン25および26が略対称に形成されており、このような実装不良は生じない。

【0075】

尚、図11Aでは、前記電極パッド25Aおよび25Bを図示するために、前記導電パタ―ン25および26の幅を電極パッド25Aおよび25Bの幅よりも小さく表示してあるが、これは表示上の都合であって、図11Bに示すように前記電極パッド25Aおよび26Aの表面は、それぞれクリーム半田25Bおよび26Bにより覆われている。

【0076】

このように本実施形態によれば、前記第1の導電パタ―ン25および第2の導電パタ―ン26を略等しく、すなわち対称的に形成することで、前記チップ型容量素子24など受動素子にツームストン現象が発生するのが防止・抑制され、半導体装置の製造歩留まりを向上させることができる。

【0077】

なお図11A〜図11Cに示す実施形態では、前記電極パッド25Aおよび26Aは、前記チップ型容量素子24の実装を任意の位置でできるように、十分な幅をもって形成されているが、本実施形態においては、図12に示すように、前記電極パッド25A,25Bの幅を前記チップ型容量素子24の形成位置25AW,26AWにおいてのみ増大させ、それ以外の領域ではダムとなる半田パタ―ンを形成可能な最小限の幅とすることも可能である。

【0078】

この場合、前記形成位置25AW,26AWでは前記第1および第2の導電パタ―ン25,26を構成する半田パタ―ンは、幅広の半田パタ―ン25W,26Wとなり、チップ型容量素子24は前記形成位置25AW,26AWに確実に半田付けされるが、互いに隣接する形成位置25AWどうし、あるいは互いに隣接する形成位置26AWどうしは、細い半田パタ―ン25あるいは26でのみ接続される。

【0079】

これにより、これら形成位置間におけるチップ型容量素子24の溶融半田の表面張力を介した干渉が低減され、二つのチップ型容量素子24を近接して配置した場合でも、ツームストン現象を抑制することができる。

【0080】

すなわち図12に示す構成により、多数のチップ型容量素子を半導体素子22の周辺に、近接して配置することができる。

【0081】

図13Aおよび図13Bは、本実施形態の一変形例による半導体装置20A,20Bをそれぞれ示している。

【0082】

前述の如く、本実施形態では前記配線基板21上にフリップチップ実装された半導体チップ22を二重に囲繞して、前記第1の導電パタ―ン25および第2の導電パタ―ン26が形成されており、チップ型容量素子24は、前記半導体素子22を囲んで、前記導体パターン25および導体パターン26との間を橋絡するように実装されている。

【0083】

そこで、図9Aおよび図9Bにおいてディスペンサ31を使って前記アンダーフィル樹脂23を充填する際、前記ディスペンサ31が既に実装されているチップ型容量素子24と干渉してしまうような場合に、本実施形態では前記チップ型容量素子を、ディスペンサ31と干渉しない位置に適宜配置することが可能である。

【0084】

例えば図13Aに示す半導体装置20Aの例では、ディスペンサ31は図中、前記半導体素子22の右縁に沿って矢印で示すように移動されるが、前記チップ型容量素子24のうち、チップ型容量素子241および242は、かかるディスペンサ31の移動範囲を避けて形成されており、ディスペンサ31とチップ型容量素子24との干渉は生じない。

【0085】

同様に図13Bに示す半導体装置20Bの例では、ディスペンサ31は図中、矢印で示すように前記半導体素子22の右縁から上縁に沿って、右上角部を回り込んで移動され、、前記チップ型容量素子243,244は、半導体素子22の上縁で左上角部近傍に、また前記チップ型容量素子245,246は、半導体素子22のおよび右縁で右下角部近傍にまとめて配置してある。

【0086】

すなわち本実施形態によれば、前記第1の導電パタ―ン25が前記実装領域を多重に囲繞するため、半導体素子周辺でのチップ型容量素子24などの受動素子の配置の自由度が増大し、前記半導体素子22の実装の際、アンダーフィル樹脂23の注入位置を避けて前記受動素子を配置することが可能で、これにより、アンダーフィル樹脂の注入に使われるディスペンサ31が前記受動素子と干渉する問題を回避することができる。

【0087】

これに対し、例えば前記半導体装置10では、ディスペンサがチップ型容量素子13と干渉する場合があり、ディスペンサを使ったアンダーフィル樹脂13の注入位置が限定されてしまう。

【0088】

なお、この様にチップ型容量素子を近接して配置した場合には、前記導電パタ―ン25と導電パタ―ン26を対称に形成しても、溶融半田の表面張力の干渉により、チップ型容量素子にツームストン現象が発生し易い。

【0089】

この様な場合には、先に図12に示したように一つのチップ型容量素子、例えばチップ型容量素子243とこれに隣接するチップ型容量素子、例えばチップ型容量素子244の間において前記導電パタ―ン25,26を構成する半田パタ―ンの幅を減少させることにより、溶融半田の干渉を低減させることができる。

【0090】

本実施形態の半導体装置20によれば、前記アンダーフィル樹脂23の拡がりが前記第1の導電パタ―ン25で阻止されるため、例えば図14Aに示すように、配線基板21のうち、従来流れ拡がったアンダーフィル樹脂で覆われてしまっていた領域に、図14Bに示す、セラミック本体34cの両側縁部に沿って端子34aと端子34bを交互に配列された多端子構成のチップ型容量素子34など、他の受動素子を配置したり、図14Cに示すように、DRAM35などの能動素子を配置したりすることが可能となる。

【0091】

これにより、配線基板表面の利用効率を向上させ、また半導体装置の機能をさらに向上させることができる。

【0092】

図14Aに示す多端子チップ型容量素子34の場合も、アンダーフィル樹脂23で覆われてしまうと、チップ型容量素子24の場合と同様に、先に図2A〜図2Cを用いて説明した問題が生じ、このような構成を実現するのは、実装基板21の寸法を増大させる以外には、困難であった。

【0093】

また図14Cに示すDRAM35の場合には、DRAMに耐熱制限があるため、最終工程で実装をせざるを得ないが、アンダーフィル樹脂が前記DRAM35の実装パッドを覆ってしまうと、このような実装は不可能となってしまう。

【0094】

すなわち、図14Cに示す構成も、実装基板21の寸法を増大させる以外には、従来実現が困難であった。

【0095】

これに対し本実施形態によれば、図14Aあるいは図14Cに示す構成を、配線基板21のサイズを増大させることなく、容易に実現することが可能となる。

【0096】

特に図14Cに示す構成では、配線基板21上に、半導体素子22と共にDRAMなどの記憶素子を実装することにより、小型のシステムインパッケージを構成することができる。

【0097】

前記図10A,図10Bに示す半導体装置20に対して、さらに施される加工処理を、図15A〜図15Cに示す。

【0098】

図15Aを参照するに、当該半導体装置20において、前記半導体素子22の背面、すなわち上面に、導電性接着剤よりなるチップ背面接着剤層36がディスペンサ37を使って塗布され、さらに図15Bに示すように前記配線基板21上に、例えばAlSiCなどの熱伝導性合金よりなる封止部材38が、前記半導体素子22の前記背面に前記接着剤層36により接合されるように配置されている。

【0099】

前記封止部材38は、その外周部に、前記配線基板21上において前記半導体素子22を収納する空間を画成するように形成された接合部38Aが、前記配線基板21の上側主面21Aに、接着剤層39により接着される。

【0100】

本実施形態による半導体装置20は、図15Aに示す状態で製品として顧客に引き渡される場合、或いは図15Bに示される状態で製品として顧客に引き渡される場合がある。

【0101】

また必要に応じて、図15Cに示すように、前記配線基板21の下側主面21Bに形成した外部接続用電極パッド21b(図3B参照)に半田バンプ21cを形成し、半導体装置20をこの状態で製品として顧客に引き渡すことも可能である。

【0102】

なお、一般に図15Bあるいは図15Cに示す配線基板21上に封止部材38を配設した半導体装置では、半導体素子22が発熱した場合、主として配線基板21の熱膨張係数と封止部材38の熱膨張係数の差により、配線基板21に反りが発生することがある。

【0103】

このような反りは、配線基板21の中心からの距離が増大するにつれて増大する傾向がある。

【0104】

配線基板21にこのような反りが発生してしまうと、半導体装置20を例えばマザーボード上に配置した場合、電気接続の信頼性が低下するなどの問題が生じる。

【0105】

これに対し、本実施形態では前記導電パタ―ン25のダム作用によりアンダーフィル樹脂23の配線基板21上における流れ拡がりが阻止されるため、図17に示すように、前記封止部材38を前記配線基板21の上側主面21Aに、前記配線基板21の外周21eから矢印で示すように内側に寄った位置において接合することが可能となり、半導体素子22が発熱した場合でも、熱による配線基板21の反りを緩和することができる。

【0106】

図16Aおよび図16Bは、それぞれ本実施例の導電パタ―ン25,26を設けなかった場合および設けた場合の、前記配線基板21の表面上におけるアンダーフィル樹脂23の拡がりの様子を示す写真である。

【0107】

ただし図16Aおよび図16Bに示す実施形態では、半導体素子22を実装せずにディスペンサを使い、図9A,図9Bに示す配線基板21のうち、半導体素子22により占有される領域C4にアンダーフィル樹脂23を形成している。

【0108】

前記アンダーフィル樹脂23として、エポキシ樹脂(例えばナガセケムテックス社の型番T693/UFR108F10)を用い、70℃の温度に於いて充填を行っている。

【0109】

図16Aおよび図16Bを参照するに、前記導電パタ―ン25,26を設けなかった場合には、アンダーフィル樹脂23は前記配線基板21上を、前記半導体素子22の占有領域C4を超えて拡がり、半導体素子22を囲んで配置されるチップ型容量素子24などの受動素子を覆ってしまう。

【0110】

これに対し、導電パタ―ン25,26を設けた場合には、アンダーフィル樹脂23は導電パタ―ン25により拡がりが阻止され、チップ型容量素子24などの受動素子がアンダーフィル樹脂23により覆われることはない。

【0111】

図16Cは、図16Bに於いて、矩形Aにより囲まれた部位を拡大して示す写真である。

【0112】

図16Cを参照するに、アンダーフィル樹脂23は導電パタ―ン25により拡がりが阻止されており、導電パタ―ン25は所期のダム作用を生じていることが確認される。

【0113】

なお前記アンダーフィル樹脂は、前記エポキシ樹脂に限定されるものではなく、表1〜表4に示す他の様々な樹脂を適用することができる。

【0114】

【表1】

【0115】

【表2】

【0116】

【表3】

【0117】

【表4】

【0118】

なお表1には、それぞれの樹脂の充填時、すなわち図9A,図9Bを用いて説明したディスペンサを使って充填する際の温度(ステージ温度)を、硬化条件と共に示している。

【0119】

前記第1の実施形態の一変形例による半導体装置20Cを図17に示す。

【0120】

図17を参照するに、本変形例は、先に図15Cに於いて示した構造に対応して、封止部材38の接合部38Aが、当該封止部材38の外縁38eから、矢印で示すように内側に寄った位置に形成されている。

【0121】

かかる構成では、前記接合部38Aは、前記配線基板21の外縁21eから内側に寄った位置に形成されている。

【0122】

このように配線基板21の外縁21eから内側に寄った位置において封止部材38を前記配線基板21に接合することにより、封止部材38と配線基板21の熱膨張係数差に起因する配線基板21の反りの問題を軽減することができる。

【0123】

このような構成は、前記導電パタ―ン25によりアンダーフィル樹脂23の拡がりが阻止される結果、チップ型容量素子24などの受動素子を半導体素子22の近傍に、すなわち実装領域22Mの直近に配置できるため、前記封止部材38の接合部38Aの接合のための領域を配線基板21の表面に確保でき、その結果、可能となったものである。

【0124】

図18A,図18Bは、本実施形態の半導体装置の他の変形例による半導体装置20D,20Eをそれぞれ示し、図18Cおよび図18Dは、それぞれ前記図18A中、線G−G’およびに線H−H’に沿った断面を、図18Eは、図18B中、線I−I’に沿った断面を示す。

【0125】

図18Aを参照するに、本変形例では前記導電パタ―ン25,26の一部が、前記チップ型容量素子24が設けられる部分において、半導体素子22の占有領域C4に向かって屈曲されており、その結果、チップ型容量素子24を、図18Cに示すように、前記半導体素子22の直近に配設することができる。

【0126】

これにより、本実施形態では、半導体素子22とチップ型容量素子24との間の距離を最短化することができ、これに伴い、半導体素子22とチップ型容量素子24との間の配線の寄生インダクタンス或いは寄生キャパシタンスを低減し、半導体装置の電気特性をさらに向上させることができる。

【0127】

なお図18Aに示す変形例では、前記導電パタ―ン25,26は、前記チップ型容量素子24の形成領域以外では、図18Dに示すように前記半導体素子22から離間して形成されている。

【0128】

このため先に図9A,図9Bで説明したアンダーフィル樹脂の充填工程においても、アンダーフィル樹脂23を、図18A中に矢印A〜Dで示した位置のいずれからでも、ディスペンサ31により注入することができる。

【0129】

図18Bに示す構成では、前記導電パタ―ン25,26が直角に屈曲されており、図18Aに示す構成と同様にアンダーフィル樹脂23を、図18A中に矢印A〜Dで示した位置のいずれからでも、ディスペンサ31により注入することが可能であるが、前記導電パタ―ン25,26が直角に屈曲されている結果、図18Eに示すように前記チップ型容量素子24の形成位置以外では、ディスペンサ31による注入位置選択の際の自由度が、図18Aの構成に比べて向上する。

【0130】

また図18A,18Bに示す変形例では、半導体素子22のうち、熱応力の集中が発生しやすい角部において、厚いアンダーフィル樹脂層23を形成することができ、半導体装置全体の機械的および電気的な安定性および信頼性が向上する。この観点からは、前記図18Aの構成の方が、前記半導体素子22の角部において半導体素子22を支持するアンダーフィル樹脂23の量を増大させることができ、より好ましい。

【0131】

また図18Aに示す構成では、前記導電パタ―ン25,26は屈曲しながらも、互いに平行な関係を維持するため、図18Aに示すように多数のチップ型容量素子24を任意の位置に配置することができる。

【0132】

図19は、本実施形態のさらなる変形例による半導体装置20Fを示す。

【0133】

本実施形態の変形例の如く、外側の導電パタ―ン26は、チップ型容量素子24の形成位置にのみ形成した不連続な形状に形成することもできる。

【0134】

[第2の実施形態]

第2の実施形態による半導体装置40の製造方法を、図20A,図20B〜図25A,図25Bに示す。尚、図20B〜図25Bは、線J−J’(図7B参照)に沿った断面図を示す。図中、先に説明した部分に対応する部分には同一の参照符号を付し、説明を省略する。

【0135】

図20A,図20B〜図25A,図25Bに示す工程は、先の図5A,図5B〜図7A,図7Bの工程と同じであり、図22Aおよび図22Bに示すように、前記配線基板21の上側主面21A上において、電極パッド21aの配列を囲む実装領域21M(図19A参照)を囲んで、第1の導電パタ―ン25および第2の導電パタ―ン26が、半田パタ―ンにより形成されている。

【0136】

また図22A,図22Bに示す状態では、前記導電パタ―ン25と導電パタ―ン26との間に、チップ型容量素子24が実装されている。

【0137】

本実施形態では、図23Aおよび図23Bに示すように、ディスペンサ31を使って前記配線基板21の上側主面21Aのうち、電極パッド21aの配列が形成されたチップ占有領域C4にアンダーフィル樹脂43が、必要量だけ滴下される。

【0138】

その後、図24Aおよび図24Bに示すように、半導体素子22が前記電極パッド21aに、フリップチップ実装される。このため前記アンダーフィル樹脂43には、例えばアジピン酸、コハク酸、無水グルタル酸などのフラックス成分(活性成分)が添加されており、前記半導体チッ22のバンプ電極22aとパッド電極21aの接合が促進される。前記アンダーフィル樹脂43の必要量は、前記半導体素子22が前記配線基板21の上側主面21A上にフリップチップ実装された場合に、前記アンダーフィル樹脂43が前記半導体素子22と前記上側主面21Aとの間の隙間を充填し、かつ、必要に応じて半導体素子22の側壁面を支持するフィレットが形成される量に設定される。

【0139】

本実施形態においても、導電パタ―ン25のダム作用により、アンダーフィル樹脂43が、当該導電パタ―ン25を乗り越えて外部に流出することはない。

【0140】

さらに図24Aおよび図24Bに示す状態で前記アンダーフィル樹脂43を硬化させることにより、図25Aおよび図25Bに示す半導体装置40が得られる。

【0141】

本実施形態によれば、アンダーフィル樹脂43は、前記図9Aおよび図9Bに示したように半導体素子22を実装してから注入する必要がないため、図26A〜図26Cの変形例に示すように、ダムとなる導電パタ―ン25を前記半導体チップ22の外周直近に、前記半導体素子22の外周に接するように形成してもよい。

【0142】

尚、図26Bおよび図26Cは、図26A中、線K−K’および線L−L’に沿った断面を示す。図中、先に説明した部分に対応する部分には同一の参照符号を付し、説明を省略する。

【0143】

このように前記導体パターン25を前記半導体素子22の外周直近に形成することにより、チップ型容量素子24を半導体素子22の直近に配置することができ、半導体素子22とチップ型容量素子24との間の配線の寄生インダクタンスや寄生キャパシタンスの効果をさらに低減することが可能となる。またこれに伴い、半導体装置40Aの電気特性をさらに向上させることができる。

【0144】

本実施形態においても、先の第1の実施形態の場合と同様に、図25Aおよび図25Bに示す半導体装置40、あるいは図26Aおよび図26Bに示す半導体装置40A上に、先に図15A〜図15Cに示す工程を施すことにより、封止部材38および半田バンプ21cを形成することができる。

【0145】

また本実施形態においても、先の実施形態と同様な様々な変形が可能である。

【0146】

[第3の実施形態]

前記各実施形態に於ける半導体装置の構成は、配線基板上におけるアンダーフィル樹脂の濡れ拡がりを抑制できるため、単一の配線基板上に多数の半導体素子を近接してフリップチップ実装するマルチチップモジュールに適用した場合に有効である。

【0147】

この様な第3の実施形態による半導体装置60の構成を、図27に示す。

【0148】

図27を参照するに、配線基板21上には、各々が、先の第1の実施形態による半導体装置20〜20F、あるいは第2の実施形態による半導体装置40,40Aのいずれかよりなり、単一の半導体素子22を含む複数の半導体装置要素61A〜61Dが、行列状に配置されている。

【0149】

図27に示される構成によれば、上下方向あるいは左右方向に隣接する一対の半導体チップ22の間にもチップ型容量素子24などの受動素子を配置することができ、マルチチップモジュール構成の半導体装置60に対し、優れた電気特性を保証することができる。

【0150】

これに対し、各々の半導体装置要素61A〜61Dが先に説明した導電パタ―ン25,26を有さない場合には、図28あるいは図29に示すようにアンダーフィル樹脂23が各々の半導体素子22から拡がってしまい、チップ型容量素子24などの受動素子は、前記配線基板21上に、前記複数の半導体素子を囲んで配置する外はなく、十分な個数のチップ型容量素子24を配置できないため、電気特性が不安定となり易い。

【0151】

なお図28,29では便宜上、図27に示す構成と同じ参照符号を使ってはいるが、これらの図面は本実施形態の半導体装置あるいはその変形例を示すものではない。

【0152】

図20は、図28に示す半導体装置60の一変形例によるマルチチップ構成の半導体装置60Aを示す平面図である。

【0153】

図60Aを参照するに、本変形例では外側の導電パタ―ン26が、上下および左右に隣接する半導体装置要素61A〜61Dの間で共用されており、これにより、配線基板21上における半導体装置要素61A〜61Dの占有面積を低減することができる。

【0154】

[第4の実施形態]

先の各実施形態で説明した半導体装置の構成は、複数の異なった電源電圧を使う場合に拡張することができる。

【0155】

このような第4の実施形態による半導体装置80を、図31に示す。

【0156】

図31に於いて、先に説明した部分に対応する部分には同一の参照符号を付し、説明を省略する。

【0157】

図31を参照するに、前記配線基板21上には、前記導電パタ―ン25を囲繞して、前記導電パタ―ン26に対応して導電パタ―ン261が形成されており、さらに前記導電パタ―ン261を囲繞してその外側に次の導電パタ―ン262が形成されており、前記導電パタ―ン262の外側にはこれを囲繞してさらに次の導電パタ―ン263が形成されており、前記導電パタ―ン263の外側にはこれを囲繞してさらに次の導電パタ―ン264が形成されている。

【0158】

このように、半導体装置80にあっては、導電パタ―ン261〜264が前記導電パタ―ン25を囲繞して同心的に形成されている。

【0159】

本第4の実施形態では、例えば前記導電パタ―ン25に第1の電源電圧(電源1)を供給する場合、導電パタ―ン261には接地電圧(グランド)が供給され、導電パタ―ン262には第2の電源電圧(電源2)が供給され、導電パタ―ン263には接地電圧(グランド)が供給され、導電パタ―ン264には第2の電源電圧(電源2)が供給されるように構成される。

【0160】

このような各導電パタ―ン25,261,262,263、264への電源電圧1,電源電圧2,電源電圧3および接地電圧の供給は、前記配線基板21中の配線パタ―ン21V(図4A,図4Bを参照)により行うことができる。

【0161】

あるいは前記導電パタ―ン25に接地電圧(グランド)を供給する場合には、導電パタ―ン261に第1の電源電圧(電源1)を供給し、導電パタ―ン262に接地電圧(グランド)を供給し、導電パタ―ン263に第2の電源電圧(電源2)を供給し、導電パタ―ン264に第接地電圧(グランド)を供給するように構成してもよい。

【0162】

この場合には、2種類の電源電圧を供給することになる。

【0163】

本実施形態でも前記チップ型容量素子24などの受動素子は、前記導電パタ―ン25と導電パタ―ン261の間、導電パタ―ン261と導電パタ―ン262の間、導電パタ―ン262と導電パタ―ン263の間、および導電パタ―ン263と導電パタ―ン264の間を架橋して設けられる。

【0164】

[第5の実施形態]

複数の電源電圧を使った第5の実施形態による半導体装置100を、図32に示す。

【0165】

半導体装置100は、前記半導体装置20の拡張に相当し、前記導電パタ―ン26の外側に、図14Bに示すと同様に、複数の多端子構成のセラミックキャパシタ34が、半導体素子22を挟んで図面上で左右に合対向して配置されている。

【0166】

本第5の実施形態では、先の半導体装置20の場合と同様に、前記導電パタ―ン25に電源電圧1(電源1)と接地電圧(グランド)の一方が供給され、前記パタ―ン26に前記電源電圧1(電源1)と接地電圧(グランド)の他方が供給されるが、前記セラミックキャパシタ34は、前記図14Bにおける端子34aおよび34bに電源電圧1(電源1)と接地電圧(グランド)をそれぞれ印加されるキャパシタ341と、前記端子34aおよび34bに電源電圧2(電源2)と接地電圧(グランド)をそれぞれ印加されるキャパシタ342と、前記端子34aおよび34bに電源電圧3(電源3)と接地電圧(グランド)をそれぞれ印加されるキャパシタ343と、を含み、これにより半導体装置100では、電源電圧1、電源電圧2、および電源電圧3のそれぞれに、デカップリングキャパシタが設けられ、安定化が図られることになる。

【0167】

また当該半導体装置100では、前記導電パタ―ン26の外側に、前記チップ型容量素子24と同様な二端子構成の複数のセラミックキャパシタ44が、半導体素子22を挟んで図面上で上下に合い対向して配置されている。前記複数のセラミックキャパシタ44はキャパシタ441,442,443を含み、キャパシタ441は電源電圧1(電源1)および接地電圧(グランド)を供給され、キャパシタ442は電源電圧1(電源2)および接地電圧(グランド)を供給され、キャパシタ443は電源電圧1(電源3)および接地電圧(グランド)を供給され、これにより半導体装置100では、電源電圧1、電源電圧2、および電源電圧3のさらなる安定化が図られることになる。

【0168】

[第6の実施形態]

複数の電源電圧(電源電圧1,電源電圧2)を適用した第6の実施形態による半導体装置の一部を図33A,図33Bに示す。

【0169】

図33Aは、チップ型容量素子が実装される前の状態を、図33Bはチップ型容量素子が実装された後の状態を示している。図中、先に説明した部分には同一の参照符号を付し、説明を省略する。

【0170】

図33Aを参照するに、本実施形態では、前記導体パターン25および導体パターン26のいずれもが接地電圧(グランド)に設定され、前記導体パターン25中には、前記配線基板21上に形成され電源電圧1(電源1)が供給される電極パッド45aを露出するカットアウト25a、および前記配線基板21上に形成され電源電圧2(電源2)が供給される電極パッド45bを露出するカットアウト25bが形成されている。同様に前記導体パターン26中には、前記配線基板21上に形成され電源電圧1(電源1)が供給される電極パッド46aを露出するカットアウト26a、および前記配線基板21上に形成され電源電圧2(電源2)が供給される電極パッド46bを露出するカットアウト26bが形成されている。なお本実施形態でも、図示はしないが、前記導体パターン25は半導体素子22下のアンダーフィル樹脂23の濡れ拡がりを阻止するダムを構成している。

【0171】

本実施形態では、前記導電パタ―ン25上のカットアウト25aと導電パタ―ン26上のカットアウト26aは、互い違いの関係に形成されており、これに伴い、電極パッド25aと電極パッド25bも、互い違いの関係に形成されている。また同様にカットアウト25bとカットアウト26bも互い違いの関係に形成されており、これに伴い電極パッド45bと電極パッド46bも互い違いの関係に形成されている。

【0172】

図33Bでは、前記配線基板21上に端子1〜8を有する多端子構成のセラミックキャパシタが、チップ型容量素子53A,53Bとして実装されている。より具体的には前記チップ型容量素子53Aが、その端子1と3をそれぞれ前記電極パッド45aに、端子6と8をそれぞれ前記電極パッド46aに、端子2,4を前記導体パターン25に、さらに端子5,7を前記導体パタ―ン26に、コンタクトさせて実装されている。また図33では前記キャパシタ53Bが、その端子1と3がそれぞれ前記電極パッド45aに、端子6と8がそれぞれ前記電極パッド46aに、端子2,4が前記導体パターン25に、さらに端子5,7が前記導体パタ―ン26にコンタクトするように実装されている。

【0173】

換言すると、図33A,図33Bに示す構成では、電極パッド45a,46aが、実装される多端子セラミックキャパシタ53Aの端子に対応した位置に形成されており、電極パッド45b,46bが、実装される多端子セラミックキャパシタ53Bの端子に対応した位置に形成されている。

【0174】

このような多端子チップ型容量素子53A,53Bとしては、例えば株式会社村田製作所からLLAシリーズとして市販のセラミックキャパシタを使うことができる。

【0175】

かかる構成により、電源電圧1の電源ラインにキャパシタ53Aが、また電源電圧2の電源ラインにキャパシタ53Bが挿入され、それぞれの電圧変動が、これらのキャパシタにより、独立に、かつ効果的に吸収される。

【0176】

なお、図33A,図33Bに示す構成において、電源電圧1と電源電圧2を一致させることにより、単一の電源電圧を用いた半導体装置を構成できる。

【0177】

図33A,図33Bに示す実施形態の一変形例を、図34A,図34Bに示す。

【0178】

図34Aを参照するに、前記電極パッド45a,45b,46a,46bに加えて、前記配線基板21上の導体パターン25と導体パターン26との間に、接地電圧が供給される電極パッド47aおよび前記電源電圧1(電源1)が供給される電極パッド47bが形成されている。また前記配線基板21上の導体パターン25と導体パターン26との間に、接地電圧が供給される電極パッド47cおよび前記電源電圧2(電源2)が供給される電極パッド47dが形成されている。

【0179】

なお本実施形態では、導電パタ―ン25上のカットアウト25aと導電パタ―ン26上のカットアウト26aは、互いに対称的な関係に形成されており、これに伴い、電極パッド45aと電極パッド46aも、互いに対称的な関係に形成されている。

同様に、導電パタ―ン25上のカットアウト25bと導電パタ―ン26上のカットアウト26bも、互いに対称的な関係に形成されており、これに伴い、電極パッド45bと電極パッド46bも、互いに対称的な関係に形成されている。

【0180】

図34Bは、前記図34Aに示す電源パッド45a,46a,45b,46b,47a,47b上に、端子1〜10を有する多端子セラミックキャパシタ53C,53Dがチップ型容量素子として実装された状態を示す。

【0181】

図34Bを参照するに、本変形例では前記チップ型容量素子53Cは、その端子1および3をそれぞれ前記電極パッド45aに、端子5および7をそれぞれ前記電極パッド46aに、端子2および4を前記導電パタ―ン25に、端子6および8を導電パタ―ン26に、端子9および10をそれぞれ電極パッド47aおよび47bにコンタクトさせて実装されている。また本変形例では前記チップ型容量素子53Dは、その端子1および3をそれぞれ前記電極パッド45bに、端子5および7をそれぞれ前記電極パッド46bに、端子2および4を前記導電パタ―ン25に、端子6および8を導電パタ―ン26に、端子9および10をそれぞれ電極パッド47cおよび47dにコンタクトさせて実装されている。換言すると、図34A,図34Bに示す構成では、電極パッド45a,46a,47a,47bが、実装される多端子セラミックキャパシタ53Cの端子に対応した位置に形成されており、電極パッド45b,46b,47c,47dが、実装される多端子セラミックキャパシタ53Dの端子に対応した位置に形成されている。

【0182】

かかる構成によっても、電源電圧1の電源ラインにチップ型容量素子53Cが、また電源電圧2の電源ラインにチップ型容量素子53Dが挿入され、それぞれの電圧変動が、これらのキャパシタにより、独立に、かつ効果的に吸収される。

【0183】

このようなチップ型容量素子55,56としては、例えば株式会社村田製作所よりLLMシリーズとして市販されているセラミックキャパシタを適用することができる。

【0184】

前記図33A,図33Bに示す実施形態の更なる変形例を図35A,図35Bに示す。

【0185】

図35Aを参照するに、本変形例では、前記電極パッド46a,46bの数が、それぞれ3個に増やされており、さらに前記配線基板21上の導体パターン25と導体パターン26との間に、チップ型容量素子53Eに対応して、接地電圧が供給される電極パッド48aおよび前記電源電圧1(電源1)が供給される電極パッド48bが、図面上で左右に並んで形成されている。同様に本変形例では、前記配線基板21上の導体パターン25と導体パターン26との間に、前記チップ型容量素子53Eに対応して、電源電圧1(電源1)が供給される電極パッド48cおよび接地電圧(グランド)が供給される電極パッド48dが、図面上で左右に並んで形成されている。

【0186】

さらに本変形例では、前記配線基板21上の導体パターン25と導体パターン26との間に、チップ型容量素子53Fに対応して、電源電圧2(電源2)が供給される電極パッド48eおよび接地電圧(グランド)が供給される電極パッド48fが、図面上で左右に並んで形成されており、また前記配線基板21上の導体パターン25と導体パターン26との間に、前記チップ型容量素子53Fに対応して、電源電圧2(電源2)が供給される電極パッド48gおよび前記接地電圧(グランド)が供給される電極パッド48hが、図面上で左右に並んで形成されている。

【0187】

本変形例では、図33Aおよび図33Bに示す実施形態と同様に、導体パターン25中に形成されるカットアウト25aと導体パターン26中に形成されるカットアウト26aが互い違いの関係に形成され、これに伴って電極パターン45aと電極パターン46aも、互い違いの関係に形成される。またカットアウト25bとカットアウト26bも互い違いの関係に形成され、これに伴って電極パターン45bと電極パターン46bも互い違いの関係に形成される。

【0188】

図35Bを参照するに、本変形例では前記チップ型容量素子53Eは、その端子1,3,5を前記導体パターン25にコンタクトさせ、端子2,4をそれぞれ前記電極パッド45aにコンタクトさせ、端子6,8,10をそれぞれ前記電極パッド46aにコンタクトさせ、端子7および9を前記導電パタ―ン26にコンタクトさせ、端子11および12をそれぞれ端子48a,48bにコンタクトさせ、端子13,14をそれぞれ端子48c、48dにコンタクトさせて実装されている。また本変形例では前記チップ型容量素子53Fは、その端子1,3,5を前記導体パターン25にコンタクトさせ、端子2,4をそれぞれ前記電極パッド45bにコンタクトさせ、端子6,8,10をそれぞれ前記電極パッド46bにコンタクトさせ、端子7および9を前記導電パタ―ン26にコンタクトさせ、端子11および12をそれぞれ端子48e,48fにコンタクトさせ、端子13,14をそれぞれ端子48g,48hにコンタクトさせて実装されている。

【0189】

換言すると、図35A,図35Bに示す構成では、電極パッド45a,46a,48a〜48dが、実装される多端子セラミックキャパシタ53Eの端子に対応した位置に形成されており、電極パッド45b,46b,48e〜48hが、実装される多端子セラミックキャパシタ53Fの端子に対応した位置に形成されている。

【0190】

かかる構成によれば、電源電圧1の電源ラインにチップ型容量素子53Eが、また電源電圧2の電源ラインにチップ型容量素子53Fが挿入され、それぞれの電圧変動が、これらのキャパシタにより、独立に、かつ効果的に吸収される。

【0191】

このようなチップ型容量素子53E,53Fとしては、前記村田製作所製のセラミックキャパシタを適用することができる。

【0192】

前記図33A,図33Bに示す実施形態の更なる変形例を、図36A,図36Bに示す。

【0193】

図36Aを参照するに、本変形例では、前記電極パッド45a,45a,46a,46bの数が、それぞれ3個に増やされており、さらに前記配線基板21上の導体パターン25と導体パターン26との間に、チップ型容量素子53Eに対応して、接地電圧が供給される電極パッド48aおよび前記電源電圧1(電源1)が供給される電極パッド48bが、図面上で左右に並んで形成されている。同様に本変形例では、前記配線基板21上の導体パターン25と導体パターン26との間に、前記チップ型容量素子53Eに対応して、電源電圧1(電源1)が供給される電極パッド48cおよび接地電圧(グランド)が供給される電極パッド48dが、図面上で左右に並んで形成されている。

【0194】

さらに本変形例では、前記配線基板21上の導体パターン25と導体パターン26との間に、チップ型容量素子53Fに対応して、電源電圧2(電源2)が供給される電極パッド48eおよび接地電圧(グランド)が供給される電極パッド48fが、図面上で左右に並んで形成されており、また前記配線基板21上の導体パターン25と導体パターン26との間に、前記チップ型容量素子53Fに対応して、電源電圧2(電源2)が供給される電極パッド48gおよび前記接地電圧(グランド)が供給される電極パッド48hが、図面上で左右に並んで形成されている。

【0195】

本変形例では、図33Aおよび図33Bに示す実施形態と同様に、導体パターン25中に形成されるカットアウト25aと導体パターン26中に形成されるカットアウト26aが互い違いの関係に形成され、これに伴って電極パターン45aと電極パターン46aも、互い違いの関係に形成される。またカットアウト25bとカットアウト26bも互い違いの関係に形成され、これに伴って電極パターン45bと電極パターン46bも互い違いの関係に形成される。

【0196】

図35Bを参照するに、本変形例では前記チップ型容量素子53Gは、その端子1,3,5を前記導体パターン25にコンタクトさせ、端子2,4,6をそれぞれ前記電極パッド45aにコンタクトさせ、端子7,9,11をそれぞれ前記電極パッド46aにコンタクトさせ、端子8,10,12を前記導電パタ―ン26にコンタクトさせ、端子13および14をそれぞれ端子48a,48bにコンタクトさせ、端子15,16をそれぞれ端子48c、48dにコンタクトさせて実装されている。また本変形例では前記チップ型容量素子53Hは、その端子1,3,5を前記導体パターン25にコンタクトさせ、端子2,4,6をそれぞれ前記電極パッド45bにコンタクトさせ、端子7,9,11をそれぞれ前記電極パッド46bにコンタクトさせ、端子8,10,12前記導電パタ―ン26にコンタクトさせ、端子13および14をそれぞれ端子48e,48fにコンタクトさせ、端子15,16をそれぞれ端子48g,48hにコンタクトさせて実装されている。換言すると、図36A,図36Bに示す構成では、電極パッド45a,46a,48a〜48dが、実装される多端子セラミックキャパシタ53Gの端子に対応した位置に形成されており、電極パッド45b,46b,48e〜48hが、実装される多端子セラミックキャパシタ53Hの端子に対応した位置に形成されている。

【0197】

かかる構成によれば、電源電圧1の電源ラインにチップ型容量素子53Gが、また電源電圧2の電源ラインにチップ型容量素子53Hが挿入され、それぞれの電圧変動が、これらのキャパシタにより、独立に、かつ効果的に吸収される。このようなチップ型容量素子53G,53Hとしては、例えば株式会社村田製作所よりLLKシリーズとして市販のセラミックキャパシタを使うことができる。

【0198】

図37Aは、前記図36Bの半導体装置を、半導体素子22およびアンダーフィル樹脂23の一部まで含めて示し、図37B〜図37Eは、それぞれ図37Aに示す線M−M’,線N−N’,線O−O’および線P−P’に沿った断面を示す。

【0199】

ただし図中、先に説明した部分に対応する部分には同一の参照符号を付し、説明を省略する。

【0200】

図37B〜図37Dを参照するに、本実施形態では前記配線基板21中に形成される内部配線21Vが、接地電圧(グランド)を供給される電源パタ―ン21V1と電源電圧1を供給される電源パタ―ン21V2の外に、前記電源パタ―ン21V2の下に、電源電圧2(電源2)を供給される電源パタ―ン21V3を含んでおり、前記電源パタ―ン21V3は、図37Dに示すビアプラグ21v3を介して、前記半導体素子22の電極パッド21aの一つに接続される。

【0201】

図37Bでは、前記キャパシタ53Gの端子4に対応する半田パタ―ンS4が電極パタ―ン45a上に形成されており、前記電極パタ―ン45aは前記電源パタ―ン21V2に接続されている。また先の各実施形態と同様に、本実施形態でも、導電パタ―ン25を構成する半田パタ―ンが電極パッド25A上に形成され、アンダーフィル樹脂23の濡れ拡がりを阻止するダムを構成している。また前記キャパシタ53Gの端子10に対応する半田パタ―ンS10が、前記導体パターン26を構成する半田パタ―ンに接続され融合している。

【0202】

一方、図37Cでは、導電パタ―ン25,26が先の各実施形態と同様に形成されており、導電パタ―ン25が前記アンダーフィル樹脂23の濡れ拡がりを阻止するダムを構成している。

【0203】

また図37Cでは、前記導電パタ―ン25,26の間に、前記キャパシタ53Gの端子15,16に対応する半田パタ―ンS15,S16が形成されており、前記半田パタ―ンS15は対応する電極パターン48cを介して電源パタ―ン21V1に接続されており、半田パタ―ンS16は、対応する電極パターン48dを介して電源パタ―ン21V2に接続されている。

【0204】

さらに図37Dに示す構成にあっては、導電パタ―ン25,26が先の各実施形態と同様に形成されており、導電パタ―ン25が、やはり前記アンダーフィル樹脂23の濡れ拡がりを阻止するダムを構成している。

【0205】

図37Dに示す構成にあっては、更に、前記導電パタ―ン25,26の間に、前記キャパシタ53Hの端子3および9に対応する半田パタ―ンS3,S9が形成されており、前記半田パタ―ンS3は、前記導電パタ―ン25を構成する半田パタ―ンに接続され融合しており、一方、前記半田パタ―ンS9は、対応する電極パターン46bを介して電源パタ―ン21V3に接続されている。

【0206】

図37Eに示す構成にあっては、導電パタ―ン25,26は見えないが、前記キャパシタ53Gの端子13に対応する半田パタ―ンS13が、電源電圧1(電源1)が供給される電源パタ―ン21V2に接続され、前記キャパシタ53Gの端子15に対応する半田パタ―ンS15が、接地電圧1(グランド)が供給される電源パタ―ン21V1に接続され、前記キャパシタ53Hの端子13に対応する半田パタ―ンS13が、電源電圧2(電源2)が供給される電源パタ―ン21V3に接続され、前記キャパシタ53Hの端子15に対応する半田パタ―ンS15が、接地電圧1(グランド)が供給される電源パタ―ン21V1に接続されている。

【0207】

以上、様々な実施形態について説明してきたが、本発明は更なる変形が可能である。

【0208】

例えば使用するアンダーフィル樹脂23の種類により、図38に示すように導体パタ―ン25,26を、それぞれ複数の、相互に分離した部材251〜254および261〜264より構成することができる。濡れ拡がり性の低い樹脂を前記アンダーフィル樹脂23として使う場合、あるいは導体パタ―ン25を構成する半田との濡れ性が低い樹脂を前記アンダーフィル樹脂23として使い場合には、図38に示す構成であっても、アンダーフィル樹脂の濡れ拡がりを抑制することが可能である。

【0209】

また半導体装置が、チップ型容量素子24が半導体素子22の一方の側、あるいは特定の側にのみ形成される場合には、図39に示すように導体パターン25,26を、チップ型容量素子24が形成される側のみに形成してもよい。

【0210】

さらに本発明は、前記シングルチップ構成あるいはマルチチップ構成の半導体装置、あるいはシステムインパッケージのみならず、図40Aおよび図40Bに示すように、前記配線基板21の代わりに別の半導体素子111を使い、その上に例えば図3A,図3Bの構成、あるいは図27の構成を形成し、チップオンチップ構成の半導体装置を形成することも可能である。

【0211】

更に前記各実施形態で説明した半導体装置を用い、図40Cに示すように、先の実施形態のいずれかの半導体装置上に、さらに別の半導体パッケージを実装したパッケージオンパッケージ構造の半導体装置を形成することも可能である。

【0212】

図40Cに示す例では、前記別の半導体パッケージは配線基板501とその上に実装され樹脂503で封止された半導体素子502を含み、前記半導体素子502は前記配線基板501にボンディングワイヤ504にて配線されている。図示の例では、別の半導体パッケージは、前記配線基板21上に、半田バンプ505により実装されている。

【0213】

さらに図40Dに示すように、先の各実施形態で説明した半導体装置において、配線基板21の代わりに実装基板(マザーボード)601を使い、ベアチップ実装の電子装置を構成することも可能である。

【0214】

以上、本発明を好ましい実施形態について説明したが、本発明はかかる特定の実施形態に限定されるものではなく、特許請求の範囲に記載した要旨内において様々な変形・変更が可能である。

(付記1)

基板と、

前記基板の主面上にフリップチップ状態で搭載された半導体素子と、

前記基板の主面のうち、前記半導体素子の少なくとも一の縁部に沿って配設された第1の導電パタ―ンと、

前記基板の主面上に於いて、前記第1の導電パタ―ンから離間し、かつ前記第1の導電パタ―ンに沿って配設された第2の導電パタ―ンと、

前記基板の主面上に於いて、前記第1の導電パタ―ンと第2の導電パタ―ンとの間の橋絡状態をもって配置された受動素子と、

前記基板と前記半導体チップとの間の空間を充填する樹脂層と、

を含み、

前記樹脂層は、前記基板の主面に於いて、前記半導体素子と前記第1の導電パタ―ンとの間に延在することを特徴とする半導体装置。

(付記2)

前記第1の導電パタ―ンは、前記半導体素子を囲繞していることを特徴とする付記1記載の半導体装置。

(付記3)

前記第2の導電パタ―ンは、前記第1の導電パタ―ンを囲繞していることを特徴とする付記1または2記載の半導体装置。

(付記4)

前記第2の導電パタ―ンは、前記第1の導電パタ―ンを全体として囲繞する複数の部材より構成されることを特徴とする付記1または2記載の半導体装置。

(付記5)

前記第1の導電パタ―ンは、前記半導体素子の外縁に一致して延在することを特徴とする付記1〜4のうち、いずれか一項記載の半導体装置。

(付記6)

前記第1の導電パタ―ンは、前記半導体素子に近接して延在する第1の部分と、前記半導体素子から離間して延在する第2の部分と、前記第1の部分と前記第2の部分を接続する屈曲部とを有し、前記第2の導体パターンは前記第1の導体パターンに平行して延在し、前記受動素子は、前記第1の導電パタ―ンの第1の部分に形成されることを特徴とする付記1〜4のうち、いずれか一項記載の半導体装置。

(付記7)

前記屈曲部では前記第1の導電パタ―ンは直角に屈曲することを特徴とする付記6記載の半導体装置。

(付記8)

前記屈曲部では前記第1の導電パタ―ンは、前記第1の部分から前記第2の部分へと漸移することを特徴とする付記6記載の半導体装置。

(付記9)

前記第1の導電パタ―ンは、前記半導体チップを全体として囲繞する複数の部材より構成されることを特徴とする付記1記載の半導体装置。

(付記10)

前記第1の導電パタ―ンと前記第2の導電パタ―ンの一方には電源電圧が供給され、他方には接地電圧が供給されることを特徴とする付記1〜9のうち、いずれか一項記載の半導体装置。

(付記11)

前記受動素子は、第1の端子と第2の端子を有する二端子素子であり、前記受動素子は、前記第1の端子が前記第1の導電パタ―ンに、前記第2の端子が前記第2の導電パタ―ンに接続された状態で実装されていることを特徴とする付記10記載の半導体装置。

(付記12)

前記第1の導電部材および前記第2の導電部材は、それぞれ前記第1の導電部材の他の部分および前記第2の導電部材の他の部分よりも幅広の第1の接続部および第2の接続部を含み、前記受動素子は、前記第1の端子を前記第1の接続部に、前記第2の端子を前記第2の接続部に接続して実装されていることを特徴とする付記11記載の半導体装置。

(付記13)

前記第1の導電パタ―ンと前記第2の導電パタ―ンの一方には第1の電源電圧が供給され、他方には接地電圧が供給され、さらに前記第2の導電部材の外側には、第3の電源電圧が供給される別の受動素子が配置されていることを特徴とする付記1〜9のうち、いずれか一項記載の半導体装置。

(付記14)

前記第1の導電パタ―ンと前記第2の導電パタ―ンのいずれにも接地電圧が供給され、前記第1の導電パタ―ンには、前記基板表面を露出する複数のカットアウトが、それぞれ、前記基板表面上に形成され電源電圧を供給される第1の電極パッドを露出するように形成されており、前記第2の導電パタ―ンには、前記基板表面を露出する複数のカットアウトが、それぞれ、前記基板表面上に形成され前記電源電圧を供給される第2の電極パッドを露出するように形成されており、前記基板上には、前記受動素子として、第1の側縁部に前記第1の導電パタ―ンに接続される複数の第1の接地端子と、前記第1の電極パッドに接続される複数の第1の電源端子とが交互に配列され、前記第1の側縁部に対向する第2の側縁部に、前記第2の導電パタ―ンに接続される複数の第2の接地端子と、前記第2の電極パッドに接続される複数の第2の電源端子が交互に配列された多端子キャパシタが、前記複数の第1の接地端子が前記第1の導電パタ―ンに接続され、前記複数の第1の電源端子が、対応する複数の前記第1の電極パッドに接続され、前記複数の第2の接地端子が前記第2の導電パタ―ンに接続され、前記複数の第2の電源端子が、対応する複数の前記第2の電極パッドに接続された状態で、実装されていることを特徴とする付記1〜9のうち、いずれか一項記載の半導体装置。

(付記15)

前記第1の導電パタ―ンと前記第2の導電パタ―ンのいずれにも接地電圧が供給され、前記第1の導電パタ―ンには、前記基板表面を露出する複数の第1のカットアウトが、それぞれ、前記基板表面上に形成され第1の電源電圧を供給される第1の電極パッドを露出するように形成されており、前記第2の導電パタ―ンには、前記基板表面を露出する複数の第2のカットアウトが、それぞれ、前記基板表面上に形成され前記第1の電源電圧を供給される第2の電極パッドを露出するように形成されており、

前記第1の導電パタ―ンには、前記基板表面を露出する複数の第3のカットアウトが、それぞれ、前記基板表面上に形成され第2の電源電圧を供給される第3の電極パッドを露出するように形成されており、前記第2の導電パタ―ンには、前記基板表面を露出する複数の第4のカットアウトが、それぞれ、前記基板表面上に形成され前記第2の電源電圧を供給される第4の電極パッドを露出するように形成されており、