半導体装置とその製造方法

【課題】 寄生ダイオードを介したリーク電流を抑えること。

【解決手段】 半導体装置1は、c面を表面とする窒化物半導体の半導体層13と、厚みが減少する厚み減少部14aを有する窒化物半導体のp型の埋込み層14と、を備える。埋込み層14では、厚み減少部14aの内部に酸素濃度がピークとなる部分が存在しており、そのピーク部分と厚み減少部14aの傾斜面の間のp型不純物の濃度が酸素濃度よりも高い部分が存在する。

【解決手段】 半導体装置1は、c面を表面とする窒化物半導体の半導体層13と、厚みが減少する厚み減少部14aを有する窒化物半導体のp型の埋込み層14と、を備える。埋込み層14では、厚み減少部14aの内部に酸素濃度がピークとなる部分が存在しており、そのピーク部分と厚み減少部14aの傾斜面の間のp型不純物の濃度が酸素濃度よりも高い部分が存在する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、p型の埋込み層を備えた半導体装置及びその製造方法に関する。

【背景技術】

【0002】

窒化物半導体を利用した半導体装置の開発が進められており、その一例が特許文献1に開示されている。特許文献1に開示される半導体装置の概要を図11に示す。半導体装置4は、基板311、窒化ガリウムのバッファ層312、窒化ガリウムの半導体層313、p型の窒化ガリウムの埋込み層314、ヘテロ接合層317、ドレイン電極322、ゲート部325、ソース電極326、ベース電極327を備えている。ヘテロ接合層317は、窒化ガリウムの電子走行層315と窒化アルミニウムガリウムの電子供給層316を有しており、電子走行層315と電子供給層316のヘテロ接合面に2次元電子ガス層が形成されている。ゲート部325は、ゲート電極323とゲート絶縁膜324を有している。

【0003】

半導体装置4では、2次元電子ガス層を電子が走行することで、ドレイン電極322とソース電極326の間が導通する。半導体装置4では、ゲート部325のゲート電極323に印加する電圧に応じて、オンとオフが切換えられる。

【0004】

p型の埋込み層314は、2次元電子ガス層を走行する電子が周囲の原子に衝突したときに生じる正孔を排出するために設けられている。半導体装置4では、埋め込み層314が半導体層313の表面の一部に選択的に設けられていることを特徴としている。例えば、埋込み層314が半導体層313の表面全体に設けられていると、ドレイン電極322の下方において、埋込み層314とヘテロ接合層317の接合面における電界集中が問題となる。一方、埋込み層314が選択的に設けられていると、そのような電界集中を回避しながら、正孔の排出能を維持することができる。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2004−260140号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

半導体装置4は、有機金属気相成長法等を利用して、シリコン基板311上に、バッファ層312、半導体層313、埋込み層314、ヘテロ接合層317を結晶成長して作成される。埋込み層314は、半導体層313上に成膜された後に、一部をエッチングすることで選択的に形成される。ヘテロ接合層317は、埋込み層314の一部をエッチングした後に、半導体層313と埋込み層314の表面から結晶成長される。

【0007】

通常、窒化物半導体を利用する半導体装置は、c面を成長面として採用されることが多い。このため、埋込み層314の一部をエッチングしたときに現れる埋込み層314の側面314Sは、c面以外の面であり、例えばa面、又はm面である。

【0008】

本発明者らの検討の結果、ヘテロ接合層317を結晶成長する際に、埋込み層314の側面314Sに多量の酸素が導入されることが分かってきた。窒化物半導体では、c面から酸素がほとんど導入されないが、c面以外の面から酸素が導入され易い。半導体装置4では、埋込み層314の側面314Sがc面以外の面であり、このことが原因であると考えられる。

【0009】

酸素は、窒化物半導体においてn型の不純物として機能する。このため、p型の埋め込み層314の端部に多量の酸素が導入されると、その部分がn型化する。この結果、埋め込み層314の側面314Sの近傍に、寄生のpnダイオードが形成される。

【0010】

半導体装置4がオフすると、この寄生のpnダイオードには逆バイアスが印加される。この逆バイアス電圧が寄生のpnダイオードの降伏電圧を超えると、寄生のpnダイオードを介してリーク電流が流れてしまう。

【0011】

なお、上記では、半導体装置4を例にしてp型の埋込み層の課題を説明したが、他の種類の半導体装置にもp型の埋込み層を選択的に形成したいことがあり、そのような場合も同様の課題が存在する。

【0012】

本明細書で開示される技術は、p型の埋め込み層を有する半導体装置において、寄生のpnダイオードを介したリーク電流を抑制することを目的としている。

【課題を解決するための手段】

【0013】

本明細書で開示される技術では、p型の埋込み層の一部をエッチングした後に、側面が露出する埋込み層の端部にマストランスポートを生じさせる。これにより、埋込み層の端部は、徐々に厚みが減少する厚み減少部となる。厚み減少部の傾斜面がc面に近づくことから、酸素の導入が抑えられる。これにより、寄生pnダイオードの動作が抑えられ、リーク電流が抑えられる。

【0014】

本明細書で開示する半導体装置は、半導体層とp型の埋込み層を備えている。半導体層は、c面を表面とする窒化物半導体である。埋込み層は、半導体層の表面の一部に設けられており、厚みが減少する厚み減少部を有する窒化物半導体である。埋込み層では、厚み減少部の内部に酸素濃度がピークとなる部分が存在しており、そのピーク部分と厚み減少部の傾斜面の間にp型不純物の濃度が酸素濃度よりも高い部分が存在する。この態様によると、酸素濃度がピークとなる部分がn型化していても、そのピーク部分と厚み減少部の傾斜面の間がp型化しており、n型部分が孤立した状態となっている。これにより、寄生pnダイオードの動作が抑えられ、リーク電流が抑えられる。

【0015】

本明細書で開示する半導体装置は、高電子移動度トランジスタに適用してもよい。この場合、半導体装置は、ヘテロ接合層とソース電極とドレイン電極とゲート部をさらに備えている。ヘテロ接合層は、半導体層及び埋込み層上に設けられており、ヘテロ接合が構成されている窒化物半導体である。ソース電極は、へテロ接合層上の一部に設けられている。ドレイン電極も、へテロ接合層上の一部に設けられている。ゲート部は、へテロ接合層上の一部に設けられており、ソース電極とドレイン電極の間に配置されている。ここで、ゲート部は、ショットキー型であってもよく、絶縁ゲート型であってもよい。

【0016】

高電子移動度トランジスタに設けられているへテロ接合層は、電子走行層と、電子走行層よりもバンドギャップが広い電子供給層を有していてもよい。この場合、ゲート部の下方には、埋込み層と電子走行層と電子供給層がこの順で並んでいるのが好ましい。この半導体装置は、p型埋込み層によってヘテロ接合面に形成される2次元電子ガス層が空乏化され、ノーマリオフで動作することができる。

【0017】

本明細書で開示される半導体装置の製造方法は、熱処理によるマストランスポートによって、埋込み層の厚み減少部を形成する工程を備えていてもよい。簡単な製造方法を利用して、寄生のpnダイオードの動作が抑制された半導体装置を製造することができる。

【発明の効果】

【0018】

本明細書で開示される技術によると、p型の埋め込み層に形成される寄生のpnダイオードの動作が抑えられ、リーク電流を抑えることができる。

【図面の簡単な説明】

【0019】

【図1】実施例1の半導体装置の製造工程を示す(1)。

【図2】実施例1の半導体装置の製造工程を示す(2)。

【図3】マストランスフェーズと気相成長フェーズの基板温度の変化を示す。

【図4】実施例1の半導体装置の製造工程を示す(3)。

【図5】実施例1の半導体装置の埋込み層の要部拡大図を示す。

【図6】実施例1の半導体装置の埋込み層の不純物分布を示す。

【図7】実施例1の半導体装置の製造工程を示す(4)。

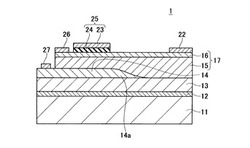

【図8】実施例1の半導体装置の製造工程を示す(5)。

【図9】実施例2の半導体装置の断面図を示す。

【図10】実施例3の半導体装置の断面図を示す。

【図11】従来の半導体装置の断面図を示す。

【発明を実施するための形態】

【0020】

実施例で開示される技術的特徴の幾つかを以下に整理して記す。

(特徴1)へテロ接合層は、窒化ガリウムを材料とする電子走行層と、電子走行層上に設けられている窒化アルミニウムガリウムを材料とする電子供給層を備えているのが望ましい。電子走行層の半導体材料は、InXaGaYaAl1−Xa−YaN(0≦Xa≦1、0≦Ya≦1、0≦Xa+Ya≦1)であるのが望ましい。電子供給層の半導体材料は、InXbGaYbAl1−Xb−YbN(0≦Xb≦1、0≦Yb≦1、0≦Xb+Yb≦1)であるのが望ましい。ここで、(1−Xa−Ya)<(1−Xb−Yb)である。

(特徴2)p型の埋込み層は、ソース電極側からドレイン電極側に向けて厚みが減少する厚み減少部を有しているのが望ましい。

(特徴3)半導体装置の製造方法は、p型の埋込み層の一部を除去する除去工程と、除去工程の後に埋込み層を熱処理する熱処理工程を備える。熱処理工程により、埋込み層の端部をマストランスポートさせ、埋込み層に厚み減少部が形成される。

(特徴4)特徴3において、半導体装置の製造方法は、埋込み層上に半導体を結晶成長させる工程をさらに備える。前記熱処理工程は、基板温度を前記結晶成長工程よりも高い温度にすることを特徴としている。

【実施例1】

【0021】

図1〜6を参照し、高電子移動度トランジスタを製造する方法を説明する。まず、図1に示されるように、有機金属気相成長法を利用して、基板11上に、窒化ガリウムのバッファ層12と、窒化ガリウムのノンドープの半導体層13と、窒化ガリウムのp型の埋込み層14を結晶成長する。基板11の材料には、シリコン、サファイア、又は炭化珪素が用いられる。バッファ層12は、低温成長されており、基板11と半導体層13の間で歪みが伝播するのを抑制する。半導体層13と埋込み層14は、連続成長されており、所定の厚みにまで結晶成長した後に、原料ガスにp型の不純物を加えることで形成される。p型の不純物には、マグネシウムが用いられている。なお、これらの結晶成長の成長面には、c面が採用されている。

【0022】

次に、図2に示されるように、ドライエッチング技術を利用して、埋込み層14の一部を除去し、半導体層13の一部を露出させる。このとき、埋込み層14の端部では、c面以外の面方位である側面14Sが露出する。なお、この例では、埋込み層14のみを除去しているが、必要に応じて、半導体層13の表面部の一部を除去してもよい。

【0023】

次に、有機金属気相成長法を利用して、半導体層13と埋込み層14の表面から結晶成長を行う。図3に、この段階の基板温度の一例を示す。本実施例では、気相成長フェーズに先立って、マストランスポートフェーズが実施されることを特徴としている。時間t1において、アンモニア雰囲気下で基板温度を上昇させる。基板温度がA1に達すると、その基板温度A1を所定期間(時間t2から時間t3)維持する。基板温度A1は、気相成長フェーズの基板温度A2よりも高く、具体的には1050℃以上が好ましい。また、基板温度A1を維持する所定期間(時間t2から時間t3)は、約5分以上が好ましい。マストランスフェーズが終了すると、図4に示されるように、埋込み層14の端部においてマストランスポートが発生し、厚み減少部14aが形成される。

【0024】

図5に、埋込み層14の厚み減少部14aの拡大断面図を示す。図中の破線で囲まれる領域14Oxyは、酸素が導入されている領域を示す。厚み減少部14aは、厚み減少開始点14bから厚み減少終了点14dまで、その厚みが徐々に減少しており、傾斜面14cが形成されている。マストランスポートが開始する前は、図2に示されるように、埋込み層14の端部において側面14Sが露出している。この側面14Sは、c面に対して略垂直な面であり、例えば、a面又はm面である。このような面方位は、酸素が多量に導入され易い。このため、マストランスポートが進行する初期段階では、埋込み層14の端部に多量の酸素が導入される。マストランスポートが進行し、厚み減少部14aの傾斜面14cが徐々にc面に近づくように平坦化すると、埋込み層14の端部に導入される酸素量が減少する。

【0025】

図6に、図5のA−A’線に沿った不純物濃度分布を示す。なお、この不純物濃度分布は、SIMS分析等を利用して観測することができる。埋込み層14のp型不純物にはマグネシウムが用いられている。図6に示されるように、導入される酸素濃度は、ピークを有する。このピーク部分は、マストランスポートが進行する初期段階で埋込み層14の端部に導入された酸素である。このピーク部分の酸素濃度は、マグネシウム濃度よりも高い。このため、埋込み層14の一部はn型化している。埋込み層14の厚み減少部14aでは、酸素濃度が急激に減少している。これは、マストランスポートが進行した後期段階では、埋込み層14の端部に導入される酸素量が減少したことを示している。この結果、n型化部分と傾斜面14cの間では、酸素濃度よりもマグネシウム濃度の方が高く、この部分がp型化している。このため、埋込み層14の厚み減少部14aでは、n型化部分が傾斜面14cにおいて露出していない。このように、マストランスフェーズは、厚み減少部14aの傾斜面がp型になるまで続けられる。

【0026】

図3に戻る。マストランスポートフェーズが終了すると、基板温度を低下させる。基板温度がA2に達すると(時間t4)、気相成長に必要な原料ガスが供給され、結晶成長が開始する。基板温度A2は、約1000〜1050℃が好ましい。

【0027】

図7に示されるように、気相成長フェーズでは、半導体層13と埋込み層14の表面にヘテロ接合層17が結晶成長される。ヘテロ接合層17は、電子走行層15と電子供給層16を有する。電子走行層15は、ノンドープの窒化ガリウムである。電子供給層16は、ノンドープの窒化アルミニウムガリウムである。電子供給層16に含まれるアルミニウム(Al)の組成比は、約0.1〜0.3に調整されていることが好ましい。

【0028】

次に、図8に示されるように、埋込み層14上のヘテロ接合層17の一部をエッチングし、埋込み層14の一部を露出させる。露出した埋込み層14の表面にベース電極27を形成し、ヘテロ接合層17の表面にドレイン電極22,ゲート部25,ソース電極22を形成する。ベース電極27は、埋込み層14にオーミック接触している。ドレイン電極22は、ヘテロ接合層17の表面の一部に設けられており、ヘテロ接合面に形成されている2次元電子ガス層に電気的に接続されている。ソース電極26も、ヘテロ接合層17の表面の一部に設けられており、ヘテロ接合面に形成されている2次元電子ガス層に電気的に接続されている。ゲート部25は、ヘテロ接合層の表面の一部に設けられており、ドレイン電極22とソース電極26の間に配置されている。ゲート部25は、ゲート電極23とゲート絶縁膜24を有している。ゲート電極23がゲート絶縁膜24を介してヘテロ接合面に形成されている2次元電子ガス層に対向している。

【0029】

以上の工程により、高電子移動度トランジスタである半導体装置1が完成する。以下、半導体装置1の動作を説明する。

【0030】

半導体装置1では、ドレイン電極22が負荷を介して電源の正極性に接続されており、ソース電極26とベース電極27が短絡して基準電位(この例では接地電位)に固定されている。半導体装置1では、ゲート部25の下方に、埋込み層14の膜厚部分、電子走行層15、電子供給層16がこの順で並んでいる。p型の埋込み層14は、ゲート部25のゲート電極23にゲートオン電圧が印加されていないときに、電子走行層15を空乏化している。このため、半導体装置1はノーマリオフ型である。

【0031】

ゲート電極23に閾値電圧よりも高い電圧が印加されると、半導体装置1はオン状態となる。このとき、電子走行層15と電子供給層16のヘテロ接合面に形成される2次元電子ガス層を介して、ドレイン電極22とソース電極26の間を電流が流れる。このとき、2次元電子ガス層を走行する電子が周囲の原子に衝突したときに生じる正孔は、埋込み層14を介してベース電極27に排出される。

【0032】

ゲート電極23に閾値電圧よりも低い電圧が印加されると、ゲート電極23の下方の2次元電子ガス層の電子密度が減少し、電流の流れが遮断され、半導体装置1がオフ状態となる。半導体装置1がオフすると、ドレイン電極22の電位が上昇する。図5を用いて説明したように、埋込み層14の厚み減少部14aに形成されているn型化部分は、傾斜面14cから露出しておらず、埋込み層14で覆われたように構成されている。n型化部分と傾斜面14cとの間に存在するp型化部分は、ベース電極27に電気的に接続されており、基準電位に固定されている。このため、n型化部分の電位は、埋込み層14の電位に追随して変動する。この結果、このn型化部分によって構成される寄生ダイオードにはバイアスが実質的に印加されないので、寄生ダイオードの動作が抑制されており、リーク電流が増大することが抑制されている。

【0033】

半導体装置1の他の特徴を列記する。

(1)埋込み層14の厚み減少部14aは、従来に比べ角部が平滑化されており、その部分での電界集中が緩和されており、より高耐圧化されていると評価できる。

(2)埋込み層14の材料は、アルミニウムを含む窒化ガリウムでもよい。この場合、埋込み層14に含まれるアルミニウムの濃度は、1×1020cm−3以下であることが好ましい。換言すれば、埋込み層14に含まれるアルミニウムのモル比は、窒化ガリウムに対して0.00001〜0.01に調整されていることが好ましい。窒化ガリウムにアルミニウムを含ませることにより、マストランスポートの進行速度を遅くすることができる。この場合、マストランスポートフェーズに要する時間は長くなるが、制御性が大幅に向上し、所望の形態の厚み減少部14aを形成することができる。

(3)上記半導体装置1はノーマリオフ型であったが、ノーマリオン型であってもよい。

【実施例2】

【0034】

図9に、縦型の高電子移動度トランジスタである半導体装置2を示す。半導体装置2は、n型の窒化ガリウムの基板111と、n−型の窒化ガリウムの半導体層113と、p型の窒化ガリウムの埋込み層114と、ヘテロ接合層117を備えている。ヘテロ接合層117は、n−型の窒化ガリウムの電子走行層115と、ノンドープの窒化ガリウムアルミニウムの電子供給層116を備えている。

【0035】

半導体装置2はさらに、基板111の裏面に接続されているドレイン電極122と、埋込み層114の表面に接続されているベース電極127と、ヘテロ接合層117の表面に接続されているソース電極126と、ヘテロ接合層117の表面に接続されているゲート部125を備えている。ゲート部125は、ゲート電極123とゲート絶縁膜124を有している。

【0036】

半導体装置2においても、埋込み層114の端部に厚み減少部114aが形成されている。この厚み減少部114aも熱処理によるマストランスポートによって作成されており、酸素が高濃度に導入された部分がn型化している。しかしながら、そのn型化部分がp型化部分で覆われており、寄生ダイオードの動作が抑制されている。

【実施例3】

【0037】

図10に、JFET型の半導体装置3を示す。なお、実施例2と共通する構成要素には共通する符号を付し、その説明を省略する。図10に示されるように、半導体装置3は、その表面構造が図9の半導体装置2と相違する。

【0038】

半導体装置3は、半導体層113と埋込み層114上に設けられているn−型の高抵抗層215と、その高抵抗層215上に設けられているn+型の低抵抗層216を備えている。半導体装置3はさらに、埋込み層3に接続するゲート電極225と、低抵抗層216に接続するソース電極226を備えている。

【0039】

半導体装置3においても、埋込み層114の端部に厚み減少部114aが形成されている。この厚み減少部114aも熱処理によるマストランスポートによって作成されており、酸素が高濃度に導入された部分がn型化している。しかしながら、そのn型化部分がp型化部分で覆われており、寄生ダイオードの動作が抑制されている。

【0040】

以上、本発明の具体例を詳細に説明したが、これらは例示に過ぎず、特許請求の範囲を限定するものではない。特許請求の範囲に記載の技術には、以上に例示した具体例を様々に変形、変更したものが含まれる。また、本明細書または図面に説明した技術要素は、単独であるいは各種の組合せによって技術的有用性を発揮するものであり、出願時の請求項に記載の組合せに限定されるものではない。また、本明細書または図面に例示した技術は複数の目的を同時に達成し得るものであり、そのうちの一つの目的を達成すること自体で技術的有用性を持つものである。

【符号の説明】

【0041】

13,113:半導体層

14,114:埋込み層

14a,114a:厚み減少部

15,115:電子走行層

16,116:電子供給層

17,117:ヘテロ接合層

【技術分野】

【0001】

本発明は、p型の埋込み層を備えた半導体装置及びその製造方法に関する。

【背景技術】

【0002】

窒化物半導体を利用した半導体装置の開発が進められており、その一例が特許文献1に開示されている。特許文献1に開示される半導体装置の概要を図11に示す。半導体装置4は、基板311、窒化ガリウムのバッファ層312、窒化ガリウムの半導体層313、p型の窒化ガリウムの埋込み層314、ヘテロ接合層317、ドレイン電極322、ゲート部325、ソース電極326、ベース電極327を備えている。ヘテロ接合層317は、窒化ガリウムの電子走行層315と窒化アルミニウムガリウムの電子供給層316を有しており、電子走行層315と電子供給層316のヘテロ接合面に2次元電子ガス層が形成されている。ゲート部325は、ゲート電極323とゲート絶縁膜324を有している。

【0003】

半導体装置4では、2次元電子ガス層を電子が走行することで、ドレイン電極322とソース電極326の間が導通する。半導体装置4では、ゲート部325のゲート電極323に印加する電圧に応じて、オンとオフが切換えられる。

【0004】

p型の埋込み層314は、2次元電子ガス層を走行する電子が周囲の原子に衝突したときに生じる正孔を排出するために設けられている。半導体装置4では、埋め込み層314が半導体層313の表面の一部に選択的に設けられていることを特徴としている。例えば、埋込み層314が半導体層313の表面全体に設けられていると、ドレイン電極322の下方において、埋込み層314とヘテロ接合層317の接合面における電界集中が問題となる。一方、埋込み層314が選択的に設けられていると、そのような電界集中を回避しながら、正孔の排出能を維持することができる。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2004−260140号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

半導体装置4は、有機金属気相成長法等を利用して、シリコン基板311上に、バッファ層312、半導体層313、埋込み層314、ヘテロ接合層317を結晶成長して作成される。埋込み層314は、半導体層313上に成膜された後に、一部をエッチングすることで選択的に形成される。ヘテロ接合層317は、埋込み層314の一部をエッチングした後に、半導体層313と埋込み層314の表面から結晶成長される。

【0007】

通常、窒化物半導体を利用する半導体装置は、c面を成長面として採用されることが多い。このため、埋込み層314の一部をエッチングしたときに現れる埋込み層314の側面314Sは、c面以外の面であり、例えばa面、又はm面である。

【0008】

本発明者らの検討の結果、ヘテロ接合層317を結晶成長する際に、埋込み層314の側面314Sに多量の酸素が導入されることが分かってきた。窒化物半導体では、c面から酸素がほとんど導入されないが、c面以外の面から酸素が導入され易い。半導体装置4では、埋込み層314の側面314Sがc面以外の面であり、このことが原因であると考えられる。

【0009】

酸素は、窒化物半導体においてn型の不純物として機能する。このため、p型の埋め込み層314の端部に多量の酸素が導入されると、その部分がn型化する。この結果、埋め込み層314の側面314Sの近傍に、寄生のpnダイオードが形成される。

【0010】

半導体装置4がオフすると、この寄生のpnダイオードには逆バイアスが印加される。この逆バイアス電圧が寄生のpnダイオードの降伏電圧を超えると、寄生のpnダイオードを介してリーク電流が流れてしまう。

【0011】

なお、上記では、半導体装置4を例にしてp型の埋込み層の課題を説明したが、他の種類の半導体装置にもp型の埋込み層を選択的に形成したいことがあり、そのような場合も同様の課題が存在する。

【0012】

本明細書で開示される技術は、p型の埋め込み層を有する半導体装置において、寄生のpnダイオードを介したリーク電流を抑制することを目的としている。

【課題を解決するための手段】

【0013】

本明細書で開示される技術では、p型の埋込み層の一部をエッチングした後に、側面が露出する埋込み層の端部にマストランスポートを生じさせる。これにより、埋込み層の端部は、徐々に厚みが減少する厚み減少部となる。厚み減少部の傾斜面がc面に近づくことから、酸素の導入が抑えられる。これにより、寄生pnダイオードの動作が抑えられ、リーク電流が抑えられる。

【0014】

本明細書で開示する半導体装置は、半導体層とp型の埋込み層を備えている。半導体層は、c面を表面とする窒化物半導体である。埋込み層は、半導体層の表面の一部に設けられており、厚みが減少する厚み減少部を有する窒化物半導体である。埋込み層では、厚み減少部の内部に酸素濃度がピークとなる部分が存在しており、そのピーク部分と厚み減少部の傾斜面の間にp型不純物の濃度が酸素濃度よりも高い部分が存在する。この態様によると、酸素濃度がピークとなる部分がn型化していても、そのピーク部分と厚み減少部の傾斜面の間がp型化しており、n型部分が孤立した状態となっている。これにより、寄生pnダイオードの動作が抑えられ、リーク電流が抑えられる。

【0015】

本明細書で開示する半導体装置は、高電子移動度トランジスタに適用してもよい。この場合、半導体装置は、ヘテロ接合層とソース電極とドレイン電極とゲート部をさらに備えている。ヘテロ接合層は、半導体層及び埋込み層上に設けられており、ヘテロ接合が構成されている窒化物半導体である。ソース電極は、へテロ接合層上の一部に設けられている。ドレイン電極も、へテロ接合層上の一部に設けられている。ゲート部は、へテロ接合層上の一部に設けられており、ソース電極とドレイン電極の間に配置されている。ここで、ゲート部は、ショットキー型であってもよく、絶縁ゲート型であってもよい。

【0016】

高電子移動度トランジスタに設けられているへテロ接合層は、電子走行層と、電子走行層よりもバンドギャップが広い電子供給層を有していてもよい。この場合、ゲート部の下方には、埋込み層と電子走行層と電子供給層がこの順で並んでいるのが好ましい。この半導体装置は、p型埋込み層によってヘテロ接合面に形成される2次元電子ガス層が空乏化され、ノーマリオフで動作することができる。

【0017】

本明細書で開示される半導体装置の製造方法は、熱処理によるマストランスポートによって、埋込み層の厚み減少部を形成する工程を備えていてもよい。簡単な製造方法を利用して、寄生のpnダイオードの動作が抑制された半導体装置を製造することができる。

【発明の効果】

【0018】

本明細書で開示される技術によると、p型の埋め込み層に形成される寄生のpnダイオードの動作が抑えられ、リーク電流を抑えることができる。

【図面の簡単な説明】

【0019】

【図1】実施例1の半導体装置の製造工程を示す(1)。

【図2】実施例1の半導体装置の製造工程を示す(2)。

【図3】マストランスフェーズと気相成長フェーズの基板温度の変化を示す。

【図4】実施例1の半導体装置の製造工程を示す(3)。

【図5】実施例1の半導体装置の埋込み層の要部拡大図を示す。

【図6】実施例1の半導体装置の埋込み層の不純物分布を示す。

【図7】実施例1の半導体装置の製造工程を示す(4)。

【図8】実施例1の半導体装置の製造工程を示す(5)。

【図9】実施例2の半導体装置の断面図を示す。

【図10】実施例3の半導体装置の断面図を示す。

【図11】従来の半導体装置の断面図を示す。

【発明を実施するための形態】

【0020】

実施例で開示される技術的特徴の幾つかを以下に整理して記す。

(特徴1)へテロ接合層は、窒化ガリウムを材料とする電子走行層と、電子走行層上に設けられている窒化アルミニウムガリウムを材料とする電子供給層を備えているのが望ましい。電子走行層の半導体材料は、InXaGaYaAl1−Xa−YaN(0≦Xa≦1、0≦Ya≦1、0≦Xa+Ya≦1)であるのが望ましい。電子供給層の半導体材料は、InXbGaYbAl1−Xb−YbN(0≦Xb≦1、0≦Yb≦1、0≦Xb+Yb≦1)であるのが望ましい。ここで、(1−Xa−Ya)<(1−Xb−Yb)である。

(特徴2)p型の埋込み層は、ソース電極側からドレイン電極側に向けて厚みが減少する厚み減少部を有しているのが望ましい。

(特徴3)半導体装置の製造方法は、p型の埋込み層の一部を除去する除去工程と、除去工程の後に埋込み層を熱処理する熱処理工程を備える。熱処理工程により、埋込み層の端部をマストランスポートさせ、埋込み層に厚み減少部が形成される。

(特徴4)特徴3において、半導体装置の製造方法は、埋込み層上に半導体を結晶成長させる工程をさらに備える。前記熱処理工程は、基板温度を前記結晶成長工程よりも高い温度にすることを特徴としている。

【実施例1】

【0021】

図1〜6を参照し、高電子移動度トランジスタを製造する方法を説明する。まず、図1に示されるように、有機金属気相成長法を利用して、基板11上に、窒化ガリウムのバッファ層12と、窒化ガリウムのノンドープの半導体層13と、窒化ガリウムのp型の埋込み層14を結晶成長する。基板11の材料には、シリコン、サファイア、又は炭化珪素が用いられる。バッファ層12は、低温成長されており、基板11と半導体層13の間で歪みが伝播するのを抑制する。半導体層13と埋込み層14は、連続成長されており、所定の厚みにまで結晶成長した後に、原料ガスにp型の不純物を加えることで形成される。p型の不純物には、マグネシウムが用いられている。なお、これらの結晶成長の成長面には、c面が採用されている。

【0022】

次に、図2に示されるように、ドライエッチング技術を利用して、埋込み層14の一部を除去し、半導体層13の一部を露出させる。このとき、埋込み層14の端部では、c面以外の面方位である側面14Sが露出する。なお、この例では、埋込み層14のみを除去しているが、必要に応じて、半導体層13の表面部の一部を除去してもよい。

【0023】

次に、有機金属気相成長法を利用して、半導体層13と埋込み層14の表面から結晶成長を行う。図3に、この段階の基板温度の一例を示す。本実施例では、気相成長フェーズに先立って、マストランスポートフェーズが実施されることを特徴としている。時間t1において、アンモニア雰囲気下で基板温度を上昇させる。基板温度がA1に達すると、その基板温度A1を所定期間(時間t2から時間t3)維持する。基板温度A1は、気相成長フェーズの基板温度A2よりも高く、具体的には1050℃以上が好ましい。また、基板温度A1を維持する所定期間(時間t2から時間t3)は、約5分以上が好ましい。マストランスフェーズが終了すると、図4に示されるように、埋込み層14の端部においてマストランスポートが発生し、厚み減少部14aが形成される。

【0024】

図5に、埋込み層14の厚み減少部14aの拡大断面図を示す。図中の破線で囲まれる領域14Oxyは、酸素が導入されている領域を示す。厚み減少部14aは、厚み減少開始点14bから厚み減少終了点14dまで、その厚みが徐々に減少しており、傾斜面14cが形成されている。マストランスポートが開始する前は、図2に示されるように、埋込み層14の端部において側面14Sが露出している。この側面14Sは、c面に対して略垂直な面であり、例えば、a面又はm面である。このような面方位は、酸素が多量に導入され易い。このため、マストランスポートが進行する初期段階では、埋込み層14の端部に多量の酸素が導入される。マストランスポートが進行し、厚み減少部14aの傾斜面14cが徐々にc面に近づくように平坦化すると、埋込み層14の端部に導入される酸素量が減少する。

【0025】

図6に、図5のA−A’線に沿った不純物濃度分布を示す。なお、この不純物濃度分布は、SIMS分析等を利用して観測することができる。埋込み層14のp型不純物にはマグネシウムが用いられている。図6に示されるように、導入される酸素濃度は、ピークを有する。このピーク部分は、マストランスポートが進行する初期段階で埋込み層14の端部に導入された酸素である。このピーク部分の酸素濃度は、マグネシウム濃度よりも高い。このため、埋込み層14の一部はn型化している。埋込み層14の厚み減少部14aでは、酸素濃度が急激に減少している。これは、マストランスポートが進行した後期段階では、埋込み層14の端部に導入される酸素量が減少したことを示している。この結果、n型化部分と傾斜面14cの間では、酸素濃度よりもマグネシウム濃度の方が高く、この部分がp型化している。このため、埋込み層14の厚み減少部14aでは、n型化部分が傾斜面14cにおいて露出していない。このように、マストランスフェーズは、厚み減少部14aの傾斜面がp型になるまで続けられる。

【0026】

図3に戻る。マストランスポートフェーズが終了すると、基板温度を低下させる。基板温度がA2に達すると(時間t4)、気相成長に必要な原料ガスが供給され、結晶成長が開始する。基板温度A2は、約1000〜1050℃が好ましい。

【0027】

図7に示されるように、気相成長フェーズでは、半導体層13と埋込み層14の表面にヘテロ接合層17が結晶成長される。ヘテロ接合層17は、電子走行層15と電子供給層16を有する。電子走行層15は、ノンドープの窒化ガリウムである。電子供給層16は、ノンドープの窒化アルミニウムガリウムである。電子供給層16に含まれるアルミニウム(Al)の組成比は、約0.1〜0.3に調整されていることが好ましい。

【0028】

次に、図8に示されるように、埋込み層14上のヘテロ接合層17の一部をエッチングし、埋込み層14の一部を露出させる。露出した埋込み層14の表面にベース電極27を形成し、ヘテロ接合層17の表面にドレイン電極22,ゲート部25,ソース電極22を形成する。ベース電極27は、埋込み層14にオーミック接触している。ドレイン電極22は、ヘテロ接合層17の表面の一部に設けられており、ヘテロ接合面に形成されている2次元電子ガス層に電気的に接続されている。ソース電極26も、ヘテロ接合層17の表面の一部に設けられており、ヘテロ接合面に形成されている2次元電子ガス層に電気的に接続されている。ゲート部25は、ヘテロ接合層の表面の一部に設けられており、ドレイン電極22とソース電極26の間に配置されている。ゲート部25は、ゲート電極23とゲート絶縁膜24を有している。ゲート電極23がゲート絶縁膜24を介してヘテロ接合面に形成されている2次元電子ガス層に対向している。

【0029】

以上の工程により、高電子移動度トランジスタである半導体装置1が完成する。以下、半導体装置1の動作を説明する。

【0030】

半導体装置1では、ドレイン電極22が負荷を介して電源の正極性に接続されており、ソース電極26とベース電極27が短絡して基準電位(この例では接地電位)に固定されている。半導体装置1では、ゲート部25の下方に、埋込み層14の膜厚部分、電子走行層15、電子供給層16がこの順で並んでいる。p型の埋込み層14は、ゲート部25のゲート電極23にゲートオン電圧が印加されていないときに、電子走行層15を空乏化している。このため、半導体装置1はノーマリオフ型である。

【0031】

ゲート電極23に閾値電圧よりも高い電圧が印加されると、半導体装置1はオン状態となる。このとき、電子走行層15と電子供給層16のヘテロ接合面に形成される2次元電子ガス層を介して、ドレイン電極22とソース電極26の間を電流が流れる。このとき、2次元電子ガス層を走行する電子が周囲の原子に衝突したときに生じる正孔は、埋込み層14を介してベース電極27に排出される。

【0032】

ゲート電極23に閾値電圧よりも低い電圧が印加されると、ゲート電極23の下方の2次元電子ガス層の電子密度が減少し、電流の流れが遮断され、半導体装置1がオフ状態となる。半導体装置1がオフすると、ドレイン電極22の電位が上昇する。図5を用いて説明したように、埋込み層14の厚み減少部14aに形成されているn型化部分は、傾斜面14cから露出しておらず、埋込み層14で覆われたように構成されている。n型化部分と傾斜面14cとの間に存在するp型化部分は、ベース電極27に電気的に接続されており、基準電位に固定されている。このため、n型化部分の電位は、埋込み層14の電位に追随して変動する。この結果、このn型化部分によって構成される寄生ダイオードにはバイアスが実質的に印加されないので、寄生ダイオードの動作が抑制されており、リーク電流が増大することが抑制されている。

【0033】

半導体装置1の他の特徴を列記する。

(1)埋込み層14の厚み減少部14aは、従来に比べ角部が平滑化されており、その部分での電界集中が緩和されており、より高耐圧化されていると評価できる。

(2)埋込み層14の材料は、アルミニウムを含む窒化ガリウムでもよい。この場合、埋込み層14に含まれるアルミニウムの濃度は、1×1020cm−3以下であることが好ましい。換言すれば、埋込み層14に含まれるアルミニウムのモル比は、窒化ガリウムに対して0.00001〜0.01に調整されていることが好ましい。窒化ガリウムにアルミニウムを含ませることにより、マストランスポートの進行速度を遅くすることができる。この場合、マストランスポートフェーズに要する時間は長くなるが、制御性が大幅に向上し、所望の形態の厚み減少部14aを形成することができる。

(3)上記半導体装置1はノーマリオフ型であったが、ノーマリオン型であってもよい。

【実施例2】

【0034】

図9に、縦型の高電子移動度トランジスタである半導体装置2を示す。半導体装置2は、n型の窒化ガリウムの基板111と、n−型の窒化ガリウムの半導体層113と、p型の窒化ガリウムの埋込み層114と、ヘテロ接合層117を備えている。ヘテロ接合層117は、n−型の窒化ガリウムの電子走行層115と、ノンドープの窒化ガリウムアルミニウムの電子供給層116を備えている。

【0035】

半導体装置2はさらに、基板111の裏面に接続されているドレイン電極122と、埋込み層114の表面に接続されているベース電極127と、ヘテロ接合層117の表面に接続されているソース電極126と、ヘテロ接合層117の表面に接続されているゲート部125を備えている。ゲート部125は、ゲート電極123とゲート絶縁膜124を有している。

【0036】

半導体装置2においても、埋込み層114の端部に厚み減少部114aが形成されている。この厚み減少部114aも熱処理によるマストランスポートによって作成されており、酸素が高濃度に導入された部分がn型化している。しかしながら、そのn型化部分がp型化部分で覆われており、寄生ダイオードの動作が抑制されている。

【実施例3】

【0037】

図10に、JFET型の半導体装置3を示す。なお、実施例2と共通する構成要素には共通する符号を付し、その説明を省略する。図10に示されるように、半導体装置3は、その表面構造が図9の半導体装置2と相違する。

【0038】

半導体装置3は、半導体層113と埋込み層114上に設けられているn−型の高抵抗層215と、その高抵抗層215上に設けられているn+型の低抵抗層216を備えている。半導体装置3はさらに、埋込み層3に接続するゲート電極225と、低抵抗層216に接続するソース電極226を備えている。

【0039】

半導体装置3においても、埋込み層114の端部に厚み減少部114aが形成されている。この厚み減少部114aも熱処理によるマストランスポートによって作成されており、酸素が高濃度に導入された部分がn型化している。しかしながら、そのn型化部分がp型化部分で覆われており、寄生ダイオードの動作が抑制されている。

【0040】

以上、本発明の具体例を詳細に説明したが、これらは例示に過ぎず、特許請求の範囲を限定するものではない。特許請求の範囲に記載の技術には、以上に例示した具体例を様々に変形、変更したものが含まれる。また、本明細書または図面に説明した技術要素は、単独であるいは各種の組合せによって技術的有用性を発揮するものであり、出願時の請求項に記載の組合せに限定されるものではない。また、本明細書または図面に例示した技術は複数の目的を同時に達成し得るものであり、そのうちの一つの目的を達成すること自体で技術的有用性を持つものである。

【符号の説明】

【0041】

13,113:半導体層

14,114:埋込み層

14a,114a:厚み減少部

15,115:電子走行層

16,116:電子供給層

17,117:ヘテロ接合層

【特許請求の範囲】

【請求項1】

c面を表面とする窒化物半導体の半導体層と、

前記半導体層の前記表面の一部に設けられており、厚みが減少する厚み減少部を有する窒化物半導体のp型の埋込み層と、を備えており、

前記埋込み層では、前記厚み減少部の内部に酸素濃度がピークとなる部分が存在しており、そのピーク部分と前記厚み減少部の傾斜面の間にp型不純物の濃度が酸素濃度よりも高い部分が存在する半導体装置。

【請求項2】

前記半導体層及び前記埋込み層上に設けられており、ヘテロ接合が構成されている窒化物半導体のヘテロ接合層と、

前記へテロ接合層上の一部に設けられているソース電極と、

前記へテロ接合層上の一部に設けられておりドレイン電極と、

前記へテロ接合層上の一部に設けられており、前記ソース電極と前記ドレイン電極の間に配置されているゲート部と、をさらに備えている請求項1に記載の半導体装置。

【請求項3】

前記へテロ接合層は、電子走行層と、前記電子走行層よりもバンドギャップが広い電子供給層を有しており、

前記ゲート部の下方には、前記埋込み層と前記電子走行層と前記電子供給層がこの順で並んでいる請求項1又は2に記載の半導体装置。

【請求項4】

請求項1〜3のいずれか一項に記載の半導体装置を製造する方法であって、

熱処理によるマストランスポートによって、前記埋込み層の前記厚み減少部を形成する工程を備える製造方法。

【請求項1】

c面を表面とする窒化物半導体の半導体層と、

前記半導体層の前記表面の一部に設けられており、厚みが減少する厚み減少部を有する窒化物半導体のp型の埋込み層と、を備えており、

前記埋込み層では、前記厚み減少部の内部に酸素濃度がピークとなる部分が存在しており、そのピーク部分と前記厚み減少部の傾斜面の間にp型不純物の濃度が酸素濃度よりも高い部分が存在する半導体装置。

【請求項2】

前記半導体層及び前記埋込み層上に設けられており、ヘテロ接合が構成されている窒化物半導体のヘテロ接合層と、

前記へテロ接合層上の一部に設けられているソース電極と、

前記へテロ接合層上の一部に設けられておりドレイン電極と、

前記へテロ接合層上の一部に設けられており、前記ソース電極と前記ドレイン電極の間に配置されているゲート部と、をさらに備えている請求項1に記載の半導体装置。

【請求項3】

前記へテロ接合層は、電子走行層と、前記電子走行層よりもバンドギャップが広い電子供給層を有しており、

前記ゲート部の下方には、前記埋込み層と前記電子走行層と前記電子供給層がこの順で並んでいる請求項1又は2に記載の半導体装置。

【請求項4】

請求項1〜3のいずれか一項に記載の半導体装置を製造する方法であって、

熱処理によるマストランスポートによって、前記埋込み層の前記厚み減少部を形成する工程を備える製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【公開番号】特開2013−106022(P2013−106022A)

【公開日】平成25年5月30日(2013.5.30)

【国際特許分類】

【出願番号】特願2011−251281(P2011−251281)

【出願日】平成23年11月17日(2011.11.17)

【出願人】(000003609)株式会社豊田中央研究所 (4,200)

【出願人】(000003207)トヨタ自動車株式会社 (59,920)

【Fターム(参考)】

【公開日】平成25年5月30日(2013.5.30)

【国際特許分類】

【出願日】平成23年11月17日(2011.11.17)

【出願人】(000003609)株式会社豊田中央研究所 (4,200)

【出願人】(000003207)トヨタ自動車株式会社 (59,920)

【Fターム(参考)】

[ Back to top ]