半導体装置とその製造方法

【課題】 単純で容易な実装手段によりMOSFETの閾値電圧を制御することが可能な半導体装置とその製造方法を提供する。

【解決手段】 一実施形態によれば、電界効果トランジスタは、STI(浅いトレンチ分離)を含んでいる半導体基板402と、p−FET401及びn−FET403と、p−FET401が形成される基板の窪み内のシリコン・ゲルマニウム層800と、n−FET部上とシリコン・ゲルマニウム層上に設けられた、ハフニウム化合物とレアアース化合物を含むゲート誘電体414, 432と、ゲート誘電体414, 432上にそれぞれ配置された互いに同じ材料を含むゲート電極416, 434とを具備している。

【解決手段】 一実施形態によれば、電界効果トランジスタは、STI(浅いトレンチ分離)を含んでいる半導体基板402と、p−FET401及びn−FET403と、p−FET401が形成される基板の窪み内のシリコン・ゲルマニウム層800と、n−FET部上とシリコン・ゲルマニウム層上に設けられた、ハフニウム化合物とレアアース化合物を含むゲート誘電体414, 432と、ゲート誘電体414, 432上にそれぞれ配置された互いに同じ材料を含むゲート電極416, 434とを具備している。

【発明の詳細な説明】

【技術分野】

【0001】

本発明の実施形態は、半導体装置、例えばチャネル・シリコン・ゲルマニウム層を有する電界効果トランジスタとその製造方法に関する。

【背景技術】

【0002】

多くのデバイス技術のうちでシリコンの大規模集積回路は、高度な情報社会を支えるために使用されている。高機能の集積回路を製造するため、MOSFETやCMOSFET(相補的なMOSFET)のような高性能の半導体装置が利用される。

【0003】

MOSFETやCMOSFETのようなデバイスの設計において、デバイス構造、導電型、動作電圧などの要因によってそれぞれ最適な閾値電圧を有するゲート電極の形成は、このようなデバイスの製造工程を複雑にする。そのため、デバイスの製造コストを増加させたり、デバイスの信頼性を低下させたり、効率或いはその他の有効な物の損失を招くことになる。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2009−253003号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

本実施形態は、単純で容易な実装手段によりMOSFETの閾値電圧を制御することが可能な半導体装置とその製造方法を提供する。

【課題を解決するための手段】

【0006】

本実施形態の半導体装置によれば、基板と、前記基板上に設けられたp型電界効果トランジスタと、前記基板上に設けられたn型電界効果トランジスタと、を具備し、前記p型電界効果トランジスタは、前記基板上に形成されたシリコン・ゲルマニウム層と、前記シリコン・ゲルマニウム層上に形成され、ハフニウム化合物とレアアース化合物を含む第1の材料としてのhigh-k誘電体を有する第1のゲート誘電体層と、前記第1のゲート誘電体層上に形成された第2の材料を有する第1のゲート電極と、を具備し、前記n型電界効果トランジスタは、前記基板層上に形成された前記high-k誘電体を有する第2のゲート誘電体層と、前記第2のゲート誘電体層上に形成された前記第2の材料を有する第2のゲート電極とを具備することを特徴とする。

【図面の簡単な説明】

【0007】

【図1】一実施形態に係るMOSFETを示す断面図である。

【図2】種々の実施形態に係る各々の半導体装置の電圧変化を示す図である。

【図3】種々の実施形態に係る各々の半導体装置の価電子帯の変調を示す図である。

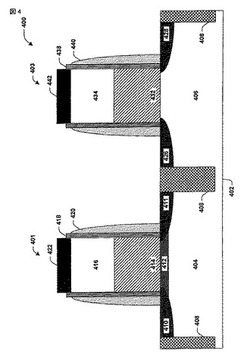

【図4】一実施形態に係る半導体装置例の一部を示す断面図である。

【図5】一実施形態に係る半導体装置製造の方法の例を示す図である。

【図6】一実施形態に係る半導体装置製造の方法の例を示す図である。

【図7】一実施形態に係る半導体装置製造の方法の例を示す図である。

【図8】一実施形態に係る半導体装置製造の方法の例を示す図である。

【図9】一実施形態に係る半導体装置製造の方法の例を示す図である。

【図10】一実施形態に係る半導体装置製造の方法の例を示す図である。

【図11】一実施形態に係る半導体装置製造の方法の例を示す図である。

【図12】一実施形態に係る半導体装置製造の方法の例を示す図である。

【図13】一実施例に係る半導体装置の製造の方法の例を示すフローダイヤグラムである。

【発明を実施するための形態】

【0008】

本実施形態は電界効果トランジスタとその製造方法を提供する。特に、本実施形態は、チャネル・シリコン・ゲルマニウム層と、ハフニウム化合物及びレアアース化合物を含むゲート誘電体を有する電界効果トランジスタを提供する。電界効果トランジスタは、半導体基板とゲート誘電体との間にシリコン・ゲルマニウム層を含んでいる。

【0009】

シリコン・ゲルマニウム層は、(100)面を有する上面と底面ならびに、2つ以上の面を有する側面とを有している。シリコン・ゲルマニウム層は電界効果トランジスタのチャネル領域の上方にほぼ一定の高さを有している。一実施形態において、シリコン・ゲルマニウム層は、ゲート構造に覆われた半導体基板の一部でチャネル長方向に側面を持たない。別の実施形態において、シリコン・ゲルマニウム層は、ゲート構造で覆われない半導体基板部分で全て側面を有している。電界効果トランジスタは、オン電流(Ion)特性、線形ドレイン電流(Idlin)特性、及び閾値電圧(Vt)特性のうちの1つ以上をチャネル・シリコン・ゲルマニウム層により改善することができる。

【0010】

電界効果トランジスタは、半導体基板内にソース/ドレイン領域、及び浅いトレンチ分離(以下、STIと称す)を含んでいる。電界効果トランジスタは、さらにSTI間に位置する半導体基板の上面の溝内にシリコン・ゲルマニウム層と、誘電体、ゲート電極、及び側面スペーサを含むシリコン・ゲルマニウム層上のゲート構造と、ゲート構造により覆われていないシリコン・ゲルマニウム層と半導体基板の上部上の金属シリサイドを含んでいる。

【0011】

別の実施形態において、電界効果トランジスタは、STI間のソース/ドレイン領域を含む半導体基板と、STI間の半導体基板のほぼ全上面における溝内のシリコン・ゲルマニウム層と、ハフニウム化合物及びレアアース化合物を含むゲート誘電体を含んでいるシリコン・ゲルマニウム層上のゲート構造、及びゲート電極を含んでいる。

【0012】

電界効果トランジスタは、さらに、ゲート構造によって覆われていない半導体基板とシリコン・ゲルマニウム層の上部上に側面スペーサ及び金属シリサイドを含んでいる。シリコン・ゲルマニウム層は(100)面を有する上面と底面、及び2面以上の側面を有している。シリコン・ゲルマニウム層は、ゲート構造の下のチャネル長方向に側面を有していない。

【0013】

図1は、一実施形態に係る半導体装置100の断面図を示している。図1に示すように、半導体装置100は、金属酸化膜半導体(MOS)トランジスタ或いはMOSFET102を含んでいる。半導体装置100はシリコン基板104と分離構造106をさらに含んでいる。MOSFET102は、例えばp型のトランジスタである(以下、pMOS又はpFETと称す)。分離構造106は、例えばSTIである。さらに、基板104は例えばシリコン基板である。

【0014】

一実施形態によれば、MOSFET102は、基板104上に形成された例えば活性領域108を含んでいる。さらに、MOSFET102は活性領域108内に形成されたソース領域110とドレイン領域112を含んでおり、ソース領域110とドレイン領域112は互いに離間されている。活性領域108に形成されたチャネル領域114は、ソース領域110とドレイン領域112との間に形成されている。チャネル領域114は、例えばシリコン・ゲルマニウム(SiGe)のような材料を用いて、ゲルマニウム(Ge)を組み込み構成されている。

【0015】

MOSFET102は例えば誘電体層116を含んでいる。誘電体層116は高誘電率、k(或いはhigh-k誘電体)により構成される。例えば、high-k誘電体は、レアアース(RE)化合物と様々なハフニウム(Hf)化合物との組み合わせから構成される。例えば、high-k誘電体はHf酸化物及びランタン(HfO2+La)を含ことができる。さらに、例えば、Hf化合物は、ジルコニウム(Zr)酸化物、HfZr酸化物、Hfケイ酸塩、Zrケイ酸塩、あるいはHfZrケイ酸塩を含むことができ、さらに、RE化合物は、イットリウム(Y)、ジスプロシウム(Dy)、ストロンチウム(Sr)、バリウム(Ba)、イッテルビウム(Yb)、ルテチウム(Lu)、マグネシウム(Mg)、ベリリウム(Be)、スカンジウム(Sc)、セリウム(Ce)、プラセオジム(Pr)、ネオジム(Nd)、ユウロピウム(Eu)、ガドリニウム(Gd)、テルビウム(Tb)、或いはエルビウム(Er)のような、RE金属(REM)、及び(又は)RE酸化物(REO)を含むことができる。しかしながら、前記材料のリストは単なる例であり、他の材料を使用することも可能である。

【0016】

MOSFET102は、誘電体層116上に設けられたゲート電極118をさらに含んでいる。図示するように、ゲート電極118は単一の導電層ゲートを含んでいる。しかしながら、ゲート電極118はさらに多様な導電層ゲートを含むことが可能である。さらに、例えばゲート電極118は金属又は金属合金を用いて形成することも可能である。ゲート電極118に利用し得る材料の例としては、Ti、Hf、Ta、W、Al、Ru、Pt、Re、Cu、Ni、Pd、Ir及び/又はMoのような金属と、TiN、TaN、TiC、TaC、WN、WC及び/又はHfNのような窒化物及び炭化物と、RuOx及び/又はReOxのような伝導性の酸化物と、Ti−Al、Hf−Al、Ta−Al及び/又はTaAlNのような金属−金属合金と、TiN/W、TiN/Ti−Al、Ta/TiN/Ti−Alなどの前記材料の多重積層構造を含む。しかしながら、前記材料のリストは一例であり、ゲート電極に他の材料を使用することも可能である。

【0017】

さらに別の実施形態において、MOSFET102は、例えば第1のスペーサ120、第2のスペーサ122及びシリサイド層124を含んでいる。シリサイド層124はゲート電極118上、及び/又はソース領域110とドレイン領域112上に積層されている。シリサイド層124は、例えばNiSix、PtSix、PdSix、CoSix、TiSix、WSixなどのようなSi及び金属シリサイドで構成される。しかし、前記材料のリストは一例であり、シリサイド層124に他の材料を使用することが可能である。

【0018】

MOSFET102は任意の適切なチャネル幅を有している。チャネル幅は、一般に、活性領域108の紙面と垂直方向における活性領域108の長さである。チャネル幅は例えば約100nm以上、約2000nm以下である。MOSFETは任意の適切なチャネル長を有している。チャネル長は、一般に、対応するソース110とドレイン112領域間と定義される。チャネル長は、例えば約10nm以上、約100nm以下である。MOSFET102は任意の適切なチャネル高さを有している。チャネル高さは、一般に、チャネル底面とチャネル上面との間で定義される。一実施形態において、チャネル高さは約2nm以上、約25nm以下である。別の実施形態において、チャネル高さは約5nm以上、約15nm以下である。さらに、MOSFET102は、任意の適切な誘電体の高さを有している。一実施形態において、誘電体の高さは約1nm以上、約10nm以下である。別の実施形態において、誘電体の高さは約2nm以上、約5nm以下である。

【0019】

簡単化のため、図1に示していないが、MOSFET102は電界効果トランジスタ構造で通常使用することができるあらゆる特徴を含むことができる。例えば、ゲートコンタクトプラグ、ソース−ドレインコンタクト、ゲート構造間の絶縁層などが、さらにMOSFET102へ含まれる。

【0020】

チャネル114は底面及び側面を有する。底面は(100)面(例えば面方位或いは面オリエンテーション)或いは、これに準ずる面(例えば、(100)、(010)或いは(001)面)(以下、総称して「(100)面」と呼ぶ)を有する。トレンチの側面は、(111)面、或いはこれに準ずる面(以下、総称して「面(111)」と呼ぶ)と他の面を含むことができる。側面は実質的に(111)面のみを含むのではない。換言すれば、トレンチの側面は2つ以上の異なる面を有する。

【0021】

シリコン・ゲルマニウム層は底面及び上面を有する。底面と上面は(100)面を有する。シリコン・ゲルマニウム層はさらに側面を有する。シリコン・ゲルマニウム層の側面は(111)面及び他の面を含むことができる。シリコン・ゲルマニウム層の側面は本質的に(111)面だけを含むのではない。換言すれば、シリコン・ゲルマニウム層の側面は2つ以上の異なる面を有する。

【0022】

ゲルマニウム量がチャネル領域の正孔移動度を増加させる限り、シリコン・ゲルマニウム層は任意の適切なゲルマニウム量を有する。一実施形態において、シリコン・ゲルマニウム層は、約0重量%以上、約80重量%以下のシリコン及び約20重量%以上約100重量%以下のゲルマニウムを含む。別の実施形態において、シリコン・ゲルマニウム層は、約30重量%以上、約75重量%以下のシリコン及び約25重量%以上、約70重量%以下のゲルマニウムを含む。さらに別の実施形態において、シリコン・ゲルマニウム層は約60重量%以上、約70重量%以下のシリコン及び約30重量%以上、約40重量%以下のゲルマニウムを含む。

【0023】

ここに例示されるような、MOSFT102の構造に関しても、種々の他の半導体装置に関しても同様に、デバイス構造、導電型、オペレーション電圧などにより各々の最適な閾値電圧を有するゲート電極の構造の形成が複雑化し、否定的な効果を導くことを認識すべきである。従って、安定かつ信頼できる処理を通した半導体装置の閾値電圧の制御が望ましいと認識すべきである。このため、一実施形態によれば、半導体装置における基板の主成分ではない付加的要素をチャネル層114に加えることができる。一例として、チャネル層114に導入された付加的要素の量に、少なくとも一部分基づいて、閾値電圧を変化させることができる。このように半導体装置を構成することにより、従来方式と比較して、より少ない変数で尚且つ信頼できる処理によって仕事関数を容易に調整し、結果的にデバイス性能の改良をもたらすと認識できる。

【0024】

図1及びここに提供される各々の他の例証が、実施形態としての半導体装置の例を示しているが、ここに記述された実施形態は、新しいチャネルデバイス(例えばSiC、SiGeC、III−V材料など)、新しいデバイス構造(例えば絶縁体(SOI)、3−次元のトランジスタ(例えばfinFET、verticalFET、ナノワイヤー、ナノチューブ、...)上のSiなど)、及び(又は)任意の他の適切なデバイス構造へ適用可能である。

【0025】

一実施形態によれば、半導体装置100に対して強化された閾値電圧制御は、チャネル層114へ付加的要素を導入することと、誘電体層116へ付加的要素を導入することにより達成できる。例として、図1に示すように、Geがチャネル層114へ組み入れられ、p型又はp−FETの半導体装置100に対して正の閾値電圧シフトをもたらす。さらに、誘電体層116はRE化合物を含んでいる。この手法は、LaのようなRE化合物がn−FETデバイスの誘電体層中へ排他的に使用される従来の半導体製造方法と対照的である、なぜならRE化合物は、一般的に、p−FETデバイスへ負の閾値電圧シフトをもたらすからである。

【0026】

例えば、図2に示すように、グラフ200はチャネル・シリコン・ゲルマニウム(c−SiGe)上のチャネル層シリコン(Si)キャップ(ナノメーター(nm))に対する線形の閾値電圧(Vtlin)のシフトあるいは差分(ミリボルト(mV))を表している。Siキャップの増加に従い、線形の閾値電圧は減少する。グラフ200は、Hf化合物とRE化合物との組み合わせを用いて構成された誘電体を有するp−FETのチャネル層中のc−Siの代わりにc−SiGeを用いることに起因した負の静電荷の生成により、Vtlinが(110)面に対して約500mV以下正方向へシフトすること、及び(100)面に対して約400mV以下正方向へシフトすることを示している。

【0027】

補足例として、図3に示すように、グラフ300は、チャネル・シリコン(c−Si)及びチャネル・シリコン・ゲルマニウム(c−SiGe)のキャパシタンス(pF)に対するゲート電圧(V)(閾値電圧(Vt)に依存する)を表している。グラフ300は、価電子帯の変調の効果を示しており、Hf化合物とRE化合物との組み合わせを用いて構成された誘電体層を有するp−FETのチャネル層中のc−Siの代わりにc−SiGeを用いることで、(110)面に対して約900mV以下のVtシフトと、(100)面に対して約750mV以下のVtシフトをもたらすことを示している。

【0028】

図4は、実施形態に係る半導体装置400の断面図を示している。図4に示すように、半導体装置400は第1のトランジスタ或いは金属酸化膜半導体(MOS)トランジスタ(又はMOSFETと呼ばれる)401、及び第2のトランジスタ或いはMOSFT403を含みうる。半導体装置400はまた、分離構造408で区切られた第1の活性領域404と第2の活性領域406とを含むシリコン基板402を含んでいる。MOSFET401は、基板402の第1の活性領域404上に構成され、MOSFET403は第2の活性領域406上に構成される。分離構造は、浅いトレンチ分離(STIs)である。さらに、基板402はシリコン基板である。

【0029】

一実施形態によれば、MOSFET401及びMOSFET403は異なる導電型である。例えば、MOSFET401はp型トランジスタ(又はpMOS又はp-FETと呼ぶ)であり、MOSFET403はn型トランジスタ(又はnMOS又はn-FETと呼ぶ)である。この実施形態において、半導体装置400は相補型MOSFETデバイス(又はCMOSデバイスと呼ぶ)であり、p−FET401とn−FET403は相補であり、かつ同じ基板402に構築される。MOSFT401は、ほぼ図1のMOSFET102と同じである。

【0030】

活性領域404内に形成され、互いに分離されているソース領域410とドレイン領域411を、p−FET401はさらに含んでいる。アクティブ領域404内に形成されたチャネル領域412は、ソース領域410とドレイン領域411を分離し得る。非限定的な例において、チャネル領域412はチャネル・シリコンゲル・マニウム(c−SiGe)のようなチャネル材を含むことができる。

【0031】

さらに、p−FET401は、誘電体層414を含んでいる。誘電体層414は、high-k誘電体を有する。例えば、high-k誘電体は様々なハフニウム化合物とレアアース(RE)化合物との組み合わせで構成される。非限定的な例において、high-k誘電体は、Hf酸化物及びランタン(Hf02+La)を含むことができる。さらに非限定的な例において、Hf化合物は、Zr酸化物、HfZr酸化物、Hfケイ酸塩、Zrケイ酸塩、あるいはHfZrケイ酸塩を含み、さらにRE化合物はY、Dy、Sr、Ba、Yb、Lu、Mg、Be、Sc、Ce、Pr、Nd、Eu、Gd、Tb、或いはErのようなRE金属(REM)及び/又はRE酸化物(REO)を含むことができる。しかし、前のリストは単なる例であり、他の構成を利用し得ることは勿論である。

【0032】

p−FET401は、誘電体層414上に設けられたゲート電極416をさらに含んでいる。一実施形態において、ゲート電極416は単一の導電層ゲートを含んでいる。しかし、ゲート電極416が様々な導電層ゲートを含み得ることは勿論である。さらに非限定的な例において、ゲート電極416は金属又は金属合金を用いて形成することも可能である。ゲート電極416へ適用し得る構成の具体例は、Ti、Hf、Ta、W、Al、Ru、Pt、Re、Cu、Ni、Pd、Ir及び(又は)Moのような金属と、TiN、TaN、TiC、TaC、WN、WC及び(又は)HfNのような窒化物、及び炭化物と、RuOx及び(又は)ReOxのような伝導性酸化物と、Ti−Al、Hf−Al、Ta−Al及び(又は)TaAINのような金属−金属合金と、TiN/W、TiN/Ti−Al、Ta/TiN/Ti−Alなどのような前述の構成の多重積層構造を含む。しかし、前のリストは単なる例であり、他の構成を利用し得ることは勿論である。

【0033】

さらに、p−FET401は第1のスペーサ418と、第2のスペーサ420と、シリサイド層422を含んでいる。シリサイド層422は、ゲート電極416上、及び(又は)ソース領域410ならびにドレイン領域411上に積層される。シリサイド層422は、NiSix、PtSix、PdSix、CoSix、TiSix、WSixなどのようなSi及び金属シリサイドで構成される。しかし、前のリストは例示であり、シリサイド層422へ他の構成を適用かなことは言うまでもない。

【0034】

p−FET401と同様に、n−FET403は互いに分離された活性領域406内に形成されたソース領域426及びドレイン領域428を含んでいる。活性領域406内に形成された図示せぬチャネル領域は、ソース領域426とドレイン領域428とを分離し得る。

【0035】

さらに、n−FET403は、誘電体層432を含んでいる。誘電体層432は、誘電体層414中のhigh-k誘電体と実質的に同一又は類似したhigh-k誘電体を有する。例えば、誘電体層414と誘電体層432は、HfO2ゲート+LaのようなRE化合物とハフニウム化合物とを同一の組み合わせで用いて構成される。n-FET403は、誘電体層432上に設けられたゲート電極434をさらに含んでいる。一実施形態において、ゲート電極434は、単一の導電層ゲートを含んでいる。しかし、ゲート電極434は種々の導電層を含むことが可能である。さらに、非限定的な例において、ゲート電極434は、ゲート電極416と同一の金属あるいは金属合金を用いて形成することも可能である。

【0036】

さらに、n−FET403は、第1のスペーサ438と、第2のスペーサ440と、シリサイド層442を含んでいる。シリサイド層422と同様に、シリサイド層442はゲート電極434上、及び(又は)ソース領域426とドレイン領域428上に積層され、Si及び金属シリサイドで構成される。

【0037】

図4に示すように、基板402の最表面におけるシリコン(Si)に対するゲルマニウム(Ge)の濃度は、n-FET403に比べてp-FET401の方が高い。チャネル412中のSiGeは、誘電体層414におけるハフニウム化合物とRE化合物の組み合わせの使用を可能にする。例えば、LaのようなRE化合物は、一般的にn-FET中でのみ用いられる。なぜなら、Laは一般的にp-FETのVtを負の方向へシフトする。このため、p-FETのhigh-k誘電体中では使用できない。しかし、p−FET401のVtは、チャネル412中でSiGeをSiに置換することにより、正方向(例えばプラス)へシフトできる(図2−3参照)。

【0038】

チャネルSiGe上に設けられる誘電体層414として、Hf化合物とRE化合物との組み合わせからなるhigh-k誘電体を用いることで、p-FET401のVtが正方向へシフトし、誘電体層414と誘電体層432へ、例えばHfO2+Laのような、単一のhigh-k誘電体を用いることを可能とする。さらに、ゲート電極416とゲート電極434は、前述した同一のゲート電極材料を用いることができる。したがって、上記は、異なる金属ゲート材料と異なるhigh-k誘電体材をp-FETとn-FETへ典型的に用いるCMOSデバイスに関して、単純な構造を提供できる。

【0039】

半導体装置400の構造に関して、ここで例示した他の半導体装置と同様に、デバイス構造、導電型、動作電圧などに従う各々の適切な閾値電圧を有するゲート電極の構造が複雑化し、否定的な効果を導くことを認識できる。したがって、安定性と信頼性の高い処理を通じて半導体装置の閾値電圧を制御するためのメカニズムが望まれると認識できる。

【0040】

図5乃至図12は、電界効果トランジスタの形成に関する多くの実施形態の一つを具体的に示している。図5は、典型的な電界効果トランジスタ500の中間状態の断面を示している。

【0041】

電界効果トランジスタ500は、基板、例えばシリコン基板502と、半導体基板中の複数のSTI508により分離された、第1の活性領域504と第2の活性領域506とを含んでいる。STIは、化学気相成長(CVD)と、リソグラフィと、エッチング技術により形成される。半導体基板上にパターニングされたハードマスクが形成される。パターニングされたハードマスクに覆われていない半導体基板の一部は、半導体基板中に開口部を形成するため、例えばエッチングにより除去される。STIは、STI材料で開口部を満たすことにより形成される。

【0042】

図5には図示していないが、ウェルとチャネルは、STI間の半導体基板間の活性領域504及び506内に形成される。例えば電界効果トランジスタがp型のトランジスタである場合、ウェルは1つ以上のN型ドーパント(例えばリン)の注入によって形成され、さらにチャネルは1つ以上のN型ドーパント(例えばヒ素)の注入によって形成される。一実施形態において、p型トランジスタ(又はpMOSかp−FET)は、活性領域504に形成され、さらにn型トランジスタ(又はnMOSかn−FET)は、活性領域506に形成される。

【0043】

図6は、複数のSTI508間の半導体基板502の一部分を除去することにより、活性領域504の最上部で、半導体基板502の上部のほぼ全面で窪み600が形成されることを示している。この窪みは異方性化学ウェットエッチングにより形成される。異方性化学ウェットエッチングの前に、酸化物が半導体基板上に形成される場合、酸化物は希釈された沸化水素酸(HF)により除去することができる。半導体基板は希釈HFに少しの間、浸される。

【0044】

(100)面を有し底面602を有する窪みをエッチングにより形成する間、窪みは任意の適切な異方性化学ウェットエッチングにより形成できる。異方性化学ウェットエッチングは、一般に(100)の底面及び(111)面を有する側面604(又は、サイドファセット)を形成する。

【0045】

異方性化学ウェットエッチングのエッチャントの例は、水酸化テトラアルキルアンモニウム(例えば水酸化テトラメチルアンモニウム(TMAH))及び水酸化アンモニウム(NH4OH)のような基礎液を含んでいる。一例として、TMAH溶液を用いた窪みの形成を下記に述べる。TMAH溶液を用いた窪みの形成は、TMAH溶液中へ半導体構造500を浸すか、半導体構造500の上部にTMAH溶液を霧散又は散布することにより一般的に処理される。

【0046】

TMAH溶液は、他の構成要素を実質的に破損あるいはエッチングすることなく、半導体構造500の一部を除去するために十分な量のTMAHを含んでいる。一実施形態において、TMAH溶液は、TMAHの約0.5重量%以上、約40重量%以下を含んでいる。別の実施形態において、TMAH溶液は、TMAHの約1重量%以上、約25重量%以下を含んでいる。所望のTMAHの濃度を生成するため、TMAHは脱イオン水のような水で希釈される。

【0047】

半導体基板502は、窪みの形成を促進するために適切な温度でTMAH溶液と接触される。一実施形態において、半導体基板は、摂氏約20度以上、摂氏約100度以下の温度でTMAH溶液と接触される。別の実施形態において、半導体基板は、摂氏約30度以上、摂氏約60度以下の温度でTMAH溶液と接触される。半導体基板は、窪みの形成を促進するのに適切な時間でTMAH溶液と接触される。一実施形態において、半導体基板は、約5秒以上、約20分以下の間、TMAH溶液と接触される。また、一実施形態において、半導体基板は、約10秒以上、約15分以下の間、TMAH溶液と接触される。例えば、半導体基板は、2.5分の間、摂氏約45度の温度で、TMAHの約2.5重量%を含むTMAH溶液と接触される。

【0048】

別の実施形態において、腐食液はNH4OH溶液である。NH4OHの所望の濃度(例えば、NH4OH: H2O=1: 3,000(wt/wt))を生成するため、NH4OHは脱イオン水のような水で希釈される。半導体基板は、約100秒間、摂氏約45度の温度でNH4OH溶液と接触される。

【0049】

窪み600は任意の適切な深さを有する。この窪みはほぼ一定の深さを有している。深さは変化するかもしれないし、本実施形態に重要ではないかもしれない。深さは、例えば製造した電界効果トランジスタの希望する実施形態に依存し得る。一実施形態において、溝の深さは約5nm以上、約15nm以下である。別の実施形態において、深さは約2nm以上、25nm以下である。さらに別の実施形態において、深さは約10nmである。

【0050】

図7は、窪み600の側面の面方位を変えるために半導体基板を熱することを示している。側面が単一の面方位を有している場合、熱処理は単一の面方位を2つ以上の面方位へ変える。側面が単一の(111)面を有する場合、熱処理は、単一の(111)面を2つ以上の面、例えば、(111)面、(112)面、(200)面、(101)面、(011)面などへ変える。熱処理により、窪み600は側面704に関して2つ以上の面を含む。(100)面の底面は変化せずに残存する。半導体基板は熱処理によって再結晶化される。

【0051】

窪みの側面に二つ以上の面を形成することを促進するため、及び(又は)半導体基板の再結晶化のため、任意の適切な条件の下で、半導体基板502は加熱される。一実施形態において、半導体基板は、約1分以上、約10分以下の間、摂氏約700度以上、摂氏約900度以下の温度で水素中にて加熱される。別の実施例において、半導体基板は、約10秒以上、約30分以下の間、摂氏約500度以上、摂氏約900度以下の温度で水素中にて加熱される。

【0052】

図8は窪み中へシリコン・ゲルマニウム層800を形成することを示している。シリコン・ゲルマニウム層はエピタキシャル技術によって形成される。シリコン・ゲルマニウム・エピタキシャル成長は、任意の適切な条件、例えば、シリコン原料ガス(例えばSiH4、Si2H6、SiH8、SiF4など)、ゲルマニウム原料ガス(例えばGeH4、GeF4など)及び任意のキャリアガスを使用して、高温(例えば摂氏1100度)の下で進められる。シリコン・ゲルマニウムの上部が半導体基板及び(又は)STIの上部とほぼ同一面である時、シリコン・ゲルマニウム・エピタキシャル成長は終了する。

【0053】

一実施形態において、溝が(100)面の底面を有する場合、シリコン・ゲルマニウム層は(100)面の底面602を有する。シリコン・ゲルマニウム層は、(100)面の上面802を有している。別の実施形態において、溝が2つ以上の異なる面を有する側面を有する場合、シリコン・ゲルマニウム層は側面704に2つ以上の異なる面を有する。さらに別の実施形態において、溝がほぼ一定の深さを有する場合、シリコン・ゲルマニウム層はほぼ一定の高さを有する。

【0054】

図9は、シリコン・ゲルマニウム層800上の第1のゲート誘電体層902と、第2の活性領域506の最上部上の第2のゲート誘電体層904を含んでいるゲート形状900の形成を示している。さらに、第1のゲート電極906は第1のゲート誘電体層902上に配置され、また、第2のゲート電極908は第2のゲート誘電体層904上に配置される。ゲート構造は、半導体装置500上のゲート誘電体層と、ゲート誘電体層上のゲート電極層の形成と、ゲート誘電体層とゲート電極層のパターンニングにより形成される。

【0055】

ゲート誘電体層902及び904はhigh-k誘電体を有する。例えば、high-k誘電体はレアアース(RE)化合物と様々なハフニウム(Hf)化合物との組み合わせを含むことができる。非限定的な例において、high-k誘電体はHf酸化物及びランタン(HfO2+La)を含むことができる。さらに非限定的な例において、Hf化合物は、Zr酸化物、HfZr酸化物、Hfケイ酸塩、Zrケイ酸塩、あるいはHfZrケイ酸塩を含み、さらにRE化合物は、Y、Dy、Sr、Ba、Yb、Lu、Mg、Be、Sc、Ce、Pr、Nd、Eu、Gd、Tb、或いはErのようなRE金属(REM)及び/又はRE酸化物(REO)を含むことができる。しかし、前記リストは単なる例示であり、他の構成をとり得ることは言うまでもない。

【0056】

ゲート誘電体層902と904、及びゲート電極906と908は、任意の適切な技術により形成できる。例えば、ゲート誘電体層902と904、及びゲート電極906と908は、堆積(例えばCVD、スピン・オン技術など)、リソグラフィ、そしてエッチング技術により形成できる。さらに、ゲート誘電体層902と904はエピタキシャル成長技術(例えばシリコン・エピタキシャル成長)及び酸化技術(例えば熱酸化、プラズマ支援酸化など)によって形成できる。さらに、RE化合物は注入、ドーピング或いは任意の適切な技術によって、誘電体層中のHf化合物と結合するか、加えられるか、別の方法で連結できる。

【0057】

誘電体層902と904及びゲート電極906と908は、ほぼ一定の高さを有している。この高さは、変わる可能性があり、本実施形態において、重要ではない。高さは、例えば製造される電界効果トランジスタの希望の実施形態に依存する可能性がある。一実施形態において、誘電体層902と904の高さは約1nm以上、約10nm以下である。別の実施形態において、高さは約2nm以上、約5nm以下である。さらに別の実施形態において、高さは約2nmである。

【0058】

図10は、ゲート誘電体層902と904及びゲート電極906と908の隣接側面と、シリコン・ゲルマニウム層800の上面或いは活性領域506の最上面上へ側面スペーサ(例えば側壁層)1002を形成することを示している。側面スペーサは、酸化物のような任意の適切な絶縁材料を含んでいる。酸化物の例は、シリコン酸化物、テトラエチルオルトシリケート(TEOS)酸化物、高アスペクト比プラズマ(HARP)酸化物、高温酸化物(HTO)、高密度プラズマ(HDP)酸化物、原子層堆積(ALD)プロセスによって形成された酸化物など(例えばシリコン酸化物)を含んでいる。側面スペーサ材料の他の例は、窒化物(例えば窒化シリコン、シリコンオキシナイトライド及びシリコンリッチ窒化シリコン)、ケイ酸塩、ダイヤモンド−ライクカーボン、炭化物などを含む。

【0059】

側面スペーサは、任意の適切な技術、例えば半導体基板を覆うスペーサ材を含む層の形成と、次に、ゲート構造の側面近くでないスペーサ材層の一部を除去することで形成される。スペーサ材層は堆積技術(例えばCVD、スピン・オン技術など)により、少なくともゲート構造の側面を覆って形成される。

【0060】

スペーサ材層を形成した後、スペーサ材層の一部は例えばエッチングにより除去される。エッチングがシリコン・ゲルマニウム層上のゲート絶縁層及びゲート電極の側面に隣接するスペーサを除去する間、任意の適切なエッチングが使用される。ウェットエッチング及び(又は)ドライエッチングが適用可能である。エッチングの例は、反応性イオン・エッチング(RIE)、化学プラズマ・エッチング、或いは適切な化学的性質を用いた適切な異方性エッチングを含む。

【0061】

図示されていないが、ソース/ドレイン拡張領域、及び(又は)ポケット領域は側面スペーサ1002及び1004の形成の前後に形成される。任意の適切な注入構成及び濃度は、ソース/ドレイン拡張領域に適用される。ソース/ドレイン拡張領域は任意の適切な技術によって形成することができる。ソース/ドレイン拡張領域は、1つ以上のドーパントの注入により形成される。ドーパントは、ゲート構造によってカバーされない半導体基板の部分へ注入される。ゲート構造は注入スクリーンとして機能する。ソース/ドレイン拡張領域は、比較的低いエネルギー準位、及び(又は)比較的低いドーパント量を備えた注入によって形成される。一実施形態において、ソース/ドレイン拡張領域は、約0.1KeV以上、約1KeV以下のエネルギー準位、及び1E14 atoms/cm2以上、3E15 atoms/cm2以下の量で形成される。別の実施形態において、ソース/ドレイン拡張領域は、約1KeV以上、約5KeV以下のエネルギー準位、ならびに5E13 atoms/cm2以上、3E15 atoms/cm2以下の量で形成される。

【0062】

同様に、任意の適切な注入構成及び濃度は、ポケット領域へ適用される。ポケット注入は、電界効果トランジスタのVt特性を改善する。ポケット領域が、メモリ装置のコンタクトパンチスルー特性を改善するという条件で、ポケット領域は、任意の適切なサイズ、形、注入構成と濃度を有する。一実施形態において、ポケット領域は半導体基板の表面に垂直な軸から半導体基板の方向に、約0度以上、約40度以下の傾斜注入角度を有している。ポケット領域は、任意の適切な注入角度において、1つ以上のドーパントの注入によって形成される。

【0063】

一実施形態において、ポケット領域は、約25KeV以上、約60KeV以下のエネルギー準位で形成される。別の実施形態において、ポケット領域は、約30KeV以上、約70KeV以下のエネルギー準位で形成される。一実施形態において、ポケット領域は約5E12 atoms/cm2以上、8E13 atoms/cm2以下の量で形成される。別の実施形態において、ポケット領域は5E12 atoms/cm2以上、1E14 atoms/cm2以下の量で形成される。

【0064】

図11は、半導体基板502中において、ゲート構造に隣接するソース/ドレイン領域1100及び1102の形成と、ソース/ドレイン領域1102間の半導体基板の活性領域506中における、図示せぬ第2のチャネル領域を示している。任意の適切な注入構成及び濃度は、ソース/ドレイン領域へ適用される。例えば、ソース/ドレイン領域1100は1つ以上のn−typeドーパント(例えばヒ素)を含む。図示されていないが、注入されたドーパントは、半導体基板をアニールすることで活性化される。

【0065】

ソース/ドレイン領域1100及び1102は、任意の適切な技術によって形成される。ソース/ドレイン領域1100及び1102は、1つ以上のドーパントの注入によって形成することができる。ドーパントは、ゲート構造及び側面スペーサによってカバーされない、半導体基板の部分へ注入される。ゲート構造及び側面のスペーサは注入スクリーンとして機能する。ソース/ドレイン領域1100及び1102は、比較的高いエネルギー準位、及び(又は)比較的高いドーパント量を備えた注入により形成される。一実施形態において、ソース/ドレイン領域は約5KeV以上、20KeV以下のエネルギー準位、及び8E14 atoms/cm2以上、1E16 atoms/cm2以下の量で形成される。別の実施形態において、ソース/ドレイン領域は、約2KeV以上、約8KeV以下のエネルギー準位、及び1E14 atoms/cm2以上、1E16 atoms/cm2以下の量で形成される。さらに別の実施形態において、ソース/ドレイン領域は、埋め込まれたエピタキシャルSiGeにより形成される。ドーパントはイン−サイト(in-situ)・ドープド・エピタキシャルにより形成される。

【0066】

図12は、ゲート構造(例えばゲート構造及び側面スペーサ)によってカバーされないシリコン・ゲルマニウム層800及び半導体基板502の部分上の図示せぬ金属シリサイドの形成を示している。ゲート電極がシリコンを含んでいる場合、金属シリサイド1200及び1202はゲート電極上に形成される。金属シリサイドは、ゲート構造によってカバーされない電界効果トランジスタの部分を備えた電界効果トランジスタ上に形成された金属層の化学反応によって形成される。金属シリサイドは、金属層が電界効果トランジスタのシリコンを含む層又は構成要素と接触しない所では形成されない。

【0067】

図12に示していないが、金属層は電界効果トランジスタ上に形成される。金属層は、後のプロセスで金属シリサイドへ変換される任意の適切な金属化合物を含んでいる。金属の例は、タングステン、タンタル、モリブデンなどの超硬合金、及びプラチナ、パラジウム、コバルト・ニッケルなどのような周期表のグループVIIIの金属を含む。金属層は、後の熱処理において、シリコン基板、及び(又は)ゲート電極中に潜んだシリコンと金属シリサイド化合物を生ずるために変換される。金属層は任意の適切な技術、例えばCVD、物理気相蒸着法(PVD)などにより形成される。金属層は、例えば後のプロセスで形成された金属シリサイドの所望の厚さに依存する任意の適切な厚さを有する。

【0068】

電界効果トランジスタの層/構成要素に含まれているシリコンと金属層との間の化学反応を起こすため、金属層を加熱することにより、金属層は金属シリサイドへ変換される。一実施形態において、金属シリサイドは、金属層とシリコン基板に潜在しているシリコン及び(又は)ゲート電極のポリシリコンとの化学反応により形成される。シリサイド化プロセス中、金属層の金属は、層/構成要素に含まれている潜在シリコンへ拡散し、金属シリサイドを形成する。この結果、金属シリサイドは、選択的に電界効果トランジスタ上に形成される。

【0069】

金属シリサイドは、例えば、所望の実装及び(又は)製造した電界効果トランジスタに依存する任意の適切な高さを有している。一実施形態において、金属シリサイドは約5nm以上、約30nm以下の高さを有する。別の実施形態において、金属シリサイドは約10nm以上、約25nm以下の高さを有する。

【0070】

シリサイド化プロセスの適切な条件やパラメーター(例えば、温度、熱処理の継続時間など)の選択は、例えば、金属シリサイドの望ましい次元(例えば高さ)や、要素/層に含まれている潜在シリコン及び(又は)金属層の配置及び(又は)要素と、希望の実装、及び(又は)製造した電界効果トランジスタなどに依存する。例えば、金属シリサイドはラッピド・サーマル・アニール(RTA)により形成される。

【0071】

金属層の一部は、例えば側面スペーサ及びSTI上に反応せずに残り、例えばエッチングによって除去される。金属層の未反応部分は、金属層の未反応部分と任意の適切な金属エッチャントを接触することにより除去される。金属シリサイドのような電界効果トランジスタのその他の層/構成要素の全てにほぼ影響あるいは損傷を与えない。

【0072】

金属エッチャントの例は、酸化エッチャント液を含む。酸化エッチャント液の例は、例えば、H2SO4/H2O2、HNO3/H2O2、HCI/H2O2、H2O2/NH4OH/H2O、H3PO4、HNO3、CH3COOHなどを含んだ酸性溶液を含む。他の金属エッチャント液が、電界効果トランジスタのその他の構成要素/層に対して金属層の未反応部分を選択的に除去することが可能な限り、他の金属エッチャント液も使用可能である。

【0073】

金属シリサイドは、シリコンとポリシリコンよりも著しく低いシート抵抗を有している。ポリシリコンを含むゲート上に形成された金属シリサイドは、一般にポリサイドゲートと呼ばれ、ポリシリコン・ゲートと比較してゲート構造の抵抗を著しく低下する。その結果、ゲート電極の全体的な伝導性が増加される。

【0074】

図13は、半導体装置を形成する例示的な方法1300を示している。1302において、窪みはSTI間の半導体基板上において、p−FETのほぼ全上部に形成される。前述したように、CMOSデバイスを含む半導体基板上に、n−FETも存在する。一実施形態において、窪みは底面の(100)面及び側面の(111)面を有する。別の実施形態において、半導体基板は窪みの側面の(111)面を、2つ以上の異なる面に変更するために加熱される。1304において、シリコン・ゲルマニウム層は窪みの中に形成される。一実施形態において、シリコン・ゲルマニウム層は底面及び上面の(100)面と、側面の2つ以上の面を有する。

【0075】

1306において、ゲート誘電体及びゲート電極を含むゲート構造が、シリコン・ゲルマニウム層上に形成される。ゲート誘電体は、high-k誘電体を有する。例えば、high-k誘電体は、様々なハフニウム(Hf)化合物とレアアース(RE)化合物との組み合わせを含むことができる。非限定的な例において、high-k誘電体はHf酸化物及びランタン(HfO2+La)を含んでいる。さらに非限定的な例において、Hf化合物は、Zr酸化物、HfZr酸化物、Hfケイ酸塩、Zrケイ酸塩、あるいはHfZrケイ酸塩を含み、さらにRE化合物は、Y、Dy、Sr、Ba、Yb、Lu、Mg、Be、Sc、Ce、Pr、Nd、Eu、Gd、Tb或いはErのようなRE金属(REM)及び(又は)RE酸化物(REO)を含むことができる。しかし、前記リストは単なる例示であり、他の構成を利用可能なことは勿論である。

【0076】

さらに、ゲート電極118に利用される構成の非限定的な例は、Ti、Hf、Ta、W、Al、Ru、Pt、Re、Cu、Ni、Pd、Ir及び(又は)Moのような金属と、TiN、TaN、TiC、TaC、WN、WC及び(又は)HfNのような窒化物及び炭化物と、RuOx及び(又は)ReOxのような伝導性の酸化物と、Ti−Al、Hf−Al、Ta−Al及び(又は)TaAINのような金属−金属−合金と、TiN/W、TiN/Ti−Al、Ta/TiN/Ti−Alなどのような前述の構成の多層構造を含む。しかし、前記リストは例示であり、他の構成もゲート電極へ適用できることを認識すべきである。

【0077】

1308において、ソース/ドレイン領域が半導体基板の中に形成される。一実施形態において、ソース/ドレイン拡張領域及びソース/ドレインポケットも半導体基板中で形成される。1310において、金属シリサイドがシリコン・ゲルマニウム層の上部及びゲート構造によってカバーされない半導体基板に形成される。

【0078】

図13には示していないが、窪みは異方性化学ウェットエッチングにより形成される。別の実施形態において、溝は、水酸化テトラメチルアンモニウム溶液、或いは水酸化アンモニウム溶液を用いて形成される。さらに別の実施形態において、シリコン・ゲルマニウムはシリコン・ゲルマニウム・エピタキシャル・プロセスにより形成される。さらに別の実施形態において、窪みの側面の(111)面は、約5分以上、約100分以下の間摂氏約700度以上、摂氏約1,300度以下の温度で水素中の半導体基板を熱することにより、2つ以上の異なる面に変更される。

【0079】

図13には示していないが、コンタクトホール、導電線及び他の適切な要素は、任意の適切な半導体装置製造プロセスにより形成される。半導体装置製造プロセスの一般的な例は、半導体装置を形成するために通常使用される、マスキング、パターンニング、エッチング、クリーニング、平坦化、熱酸化、注入、アニール、熱処理、及び堆積技術を含んでいる。

【0080】

図13には示していないが、1306中のゲート構造に類似のゲート構造は、半導体基板上のn−FET上に形成される。n−FET上に形成されたゲート構造は、p−FET上に形成したゲート構造と同じhigh-k誘電率及び同じゲート電極材料を有する。さらに、1308に類似のソース/ドレイン領域はn−FET上で形成され、1310に類似の金属シリサイドは、ゲート構造によってカバーされないn−FET上部に形成される。前述したように、p−FETの溝中のシリコン・ゲルマニウム層に関する実施例は、適切な閾値電圧を得るために、p−FET及びn−FETの両方へ単一のhigh-k誘電体及び金属ゲートの使用を可能にすると認識すべきである。

【0081】

その他、本発明は上記各実施形態そのままに限定されるものではなく、実施段階ではその要旨を逸脱しない範囲で構成要素を変形して具体化できる。また、上記各実施形態に開示されている複数の構成要素の適宜な組み合わせにより、種々の発明を形成できる。例えば、実施形態に示される全構成要素から幾つかの構成要素を削除してもよい。さらに、異なる実施形態にわたる構成要素を適宜組み合わせてもよい。

【0082】

(付記)

(4) 前記レアアース化合物は、Y、Dy、Sr、Ba、Yb、Lu、又はMgのうちの少なくとも1つを含むことを特徴とする3記載の半導体装置。

【0083】

(5) 前記レアアース化合物は、Be、Sc、Ce、Pr、Nd、Eu、Gd、Tb、又はErのうちの少なくとも1つを含むことを特徴とする請求項1記載の半導体装置。

【0084】

(6) 前記シリコン・ゲルマニウム層上に形成された前記high-k誘電体を有する前記第1のゲート誘電体層は、p型電界効果トランジスタ中に負の静電荷を生成することを特徴とする5記載の半導体装置。

【0085】

(7) 前記シリコン・ゲルマニウム層上に形成された前記high-k誘電体を有する前記第1のゲート誘電体層は、前記p型の電界効果トランジスタの閾値電圧を正の方向にシフトすることを特徴とする6記載の半導体装置。

【0086】

(8) 前記閾値電圧の前記シフトは前記シリコン・ゲルマニウム層におけるシリコンに対するゲルマニウムの割合に少なくとも一部分基づくことを特徴とする7記載の半導体装置。

【0087】

(9) 前記基板の前記p型電界効果トランジスタ形成領域の表面は窪みを有し、前記窪み内に前記シリコン・ゲルマニウム層が形成され、前記窪みは、約2nm以上約25nm以下の深さを有することを特徴とする8記載半導体装置。

【0088】

(13) 前記シリコン・ゲルマニウムと、ハフニウム化合物及びレアアースを含む前記第1の材料との組み合わせは、p型電界効果トランジスタ中に負の静電荷を生成することを特徴とする12記載の半導体装置。

【0089】

(14) 前記シリコン・ゲルマニウムと、ハフニウム化合物とレアアースを含む前記第1の材料との組み合わせは、p型電界効果トランジスタの閾値電圧をシフトすることを特徴とする13記載の半導体装置。

【0090】

(15) 前記閾値電圧に関する前記シフトは、正の方向に約500mV以下であることを特徴とする14記載の半導体装置。

【0091】

(16) 前記基板は、第1の材料により構成された第2のゲート誘電体と、前記第2のゲート誘電体上に設けられた第2の材料により構成された第2のゲート電極とを有するn型電界効果トランジスタをさらに含むことを特徴とする15記載の半導体装置。

【0092】

(19) 前記シリコン・ゲルマニウム層中のゲルマニウム濃度を制御することにより前記p型電界効果トランジスタの閾値電圧が正の方向へ移動することを特徴とする18記載の半導体装置の製造方法。

【0093】

(20) 前記半導体基板上のn型電界効果トランジスタ領域に、第1のゲート誘電体層と同じハフニウム化合物及びレアアース化合物を用い第2のゲート誘電体を形成することと、

前記n型電界効果トランジスタ領域において、前記第2のゲート誘電体上に第2のゲート電極を形成することをさらに含むことを特徴とする19記載の半導体装置の製造方法。

【符号の説明】

【0094】

104、402…シリコン基板、102…MOSFET、p−FET…401、n−FET…403、110、410、426…ソース領域、112、411、428…ドレイン領域、116、414、432…誘電体層、118、416、434…ゲート電極、124、422、442…シリサイド層、412…チャネル、602…窪み。

【技術分野】

【0001】

本発明の実施形態は、半導体装置、例えばチャネル・シリコン・ゲルマニウム層を有する電界効果トランジスタとその製造方法に関する。

【背景技術】

【0002】

多くのデバイス技術のうちでシリコンの大規模集積回路は、高度な情報社会を支えるために使用されている。高機能の集積回路を製造するため、MOSFETやCMOSFET(相補的なMOSFET)のような高性能の半導体装置が利用される。

【0003】

MOSFETやCMOSFETのようなデバイスの設計において、デバイス構造、導電型、動作電圧などの要因によってそれぞれ最適な閾値電圧を有するゲート電極の形成は、このようなデバイスの製造工程を複雑にする。そのため、デバイスの製造コストを増加させたり、デバイスの信頼性を低下させたり、効率或いはその他の有効な物の損失を招くことになる。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2009−253003号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

本実施形態は、単純で容易な実装手段によりMOSFETの閾値電圧を制御することが可能な半導体装置とその製造方法を提供する。

【課題を解決するための手段】

【0006】

本実施形態の半導体装置によれば、基板と、前記基板上に設けられたp型電界効果トランジスタと、前記基板上に設けられたn型電界効果トランジスタと、を具備し、前記p型電界効果トランジスタは、前記基板上に形成されたシリコン・ゲルマニウム層と、前記シリコン・ゲルマニウム層上に形成され、ハフニウム化合物とレアアース化合物を含む第1の材料としてのhigh-k誘電体を有する第1のゲート誘電体層と、前記第1のゲート誘電体層上に形成された第2の材料を有する第1のゲート電極と、を具備し、前記n型電界効果トランジスタは、前記基板層上に形成された前記high-k誘電体を有する第2のゲート誘電体層と、前記第2のゲート誘電体層上に形成された前記第2の材料を有する第2のゲート電極とを具備することを特徴とする。

【図面の簡単な説明】

【0007】

【図1】一実施形態に係るMOSFETを示す断面図である。

【図2】種々の実施形態に係る各々の半導体装置の電圧変化を示す図である。

【図3】種々の実施形態に係る各々の半導体装置の価電子帯の変調を示す図である。

【図4】一実施形態に係る半導体装置例の一部を示す断面図である。

【図5】一実施形態に係る半導体装置製造の方法の例を示す図である。

【図6】一実施形態に係る半導体装置製造の方法の例を示す図である。

【図7】一実施形態に係る半導体装置製造の方法の例を示す図である。

【図8】一実施形態に係る半導体装置製造の方法の例を示す図である。

【図9】一実施形態に係る半導体装置製造の方法の例を示す図である。

【図10】一実施形態に係る半導体装置製造の方法の例を示す図である。

【図11】一実施形態に係る半導体装置製造の方法の例を示す図である。

【図12】一実施形態に係る半導体装置製造の方法の例を示す図である。

【図13】一実施例に係る半導体装置の製造の方法の例を示すフローダイヤグラムである。

【発明を実施するための形態】

【0008】

本実施形態は電界効果トランジスタとその製造方法を提供する。特に、本実施形態は、チャネル・シリコン・ゲルマニウム層と、ハフニウム化合物及びレアアース化合物を含むゲート誘電体を有する電界効果トランジスタを提供する。電界効果トランジスタは、半導体基板とゲート誘電体との間にシリコン・ゲルマニウム層を含んでいる。

【0009】

シリコン・ゲルマニウム層は、(100)面を有する上面と底面ならびに、2つ以上の面を有する側面とを有している。シリコン・ゲルマニウム層は電界効果トランジスタのチャネル領域の上方にほぼ一定の高さを有している。一実施形態において、シリコン・ゲルマニウム層は、ゲート構造に覆われた半導体基板の一部でチャネル長方向に側面を持たない。別の実施形態において、シリコン・ゲルマニウム層は、ゲート構造で覆われない半導体基板部分で全て側面を有している。電界効果トランジスタは、オン電流(Ion)特性、線形ドレイン電流(Idlin)特性、及び閾値電圧(Vt)特性のうちの1つ以上をチャネル・シリコン・ゲルマニウム層により改善することができる。

【0010】

電界効果トランジスタは、半導体基板内にソース/ドレイン領域、及び浅いトレンチ分離(以下、STIと称す)を含んでいる。電界効果トランジスタは、さらにSTI間に位置する半導体基板の上面の溝内にシリコン・ゲルマニウム層と、誘電体、ゲート電極、及び側面スペーサを含むシリコン・ゲルマニウム層上のゲート構造と、ゲート構造により覆われていないシリコン・ゲルマニウム層と半導体基板の上部上の金属シリサイドを含んでいる。

【0011】

別の実施形態において、電界効果トランジスタは、STI間のソース/ドレイン領域を含む半導体基板と、STI間の半導体基板のほぼ全上面における溝内のシリコン・ゲルマニウム層と、ハフニウム化合物及びレアアース化合物を含むゲート誘電体を含んでいるシリコン・ゲルマニウム層上のゲート構造、及びゲート電極を含んでいる。

【0012】

電界効果トランジスタは、さらに、ゲート構造によって覆われていない半導体基板とシリコン・ゲルマニウム層の上部上に側面スペーサ及び金属シリサイドを含んでいる。シリコン・ゲルマニウム層は(100)面を有する上面と底面、及び2面以上の側面を有している。シリコン・ゲルマニウム層は、ゲート構造の下のチャネル長方向に側面を有していない。

【0013】

図1は、一実施形態に係る半導体装置100の断面図を示している。図1に示すように、半導体装置100は、金属酸化膜半導体(MOS)トランジスタ或いはMOSFET102を含んでいる。半導体装置100はシリコン基板104と分離構造106をさらに含んでいる。MOSFET102は、例えばp型のトランジスタである(以下、pMOS又はpFETと称す)。分離構造106は、例えばSTIである。さらに、基板104は例えばシリコン基板である。

【0014】

一実施形態によれば、MOSFET102は、基板104上に形成された例えば活性領域108を含んでいる。さらに、MOSFET102は活性領域108内に形成されたソース領域110とドレイン領域112を含んでおり、ソース領域110とドレイン領域112は互いに離間されている。活性領域108に形成されたチャネル領域114は、ソース領域110とドレイン領域112との間に形成されている。チャネル領域114は、例えばシリコン・ゲルマニウム(SiGe)のような材料を用いて、ゲルマニウム(Ge)を組み込み構成されている。

【0015】

MOSFET102は例えば誘電体層116を含んでいる。誘電体層116は高誘電率、k(或いはhigh-k誘電体)により構成される。例えば、high-k誘電体は、レアアース(RE)化合物と様々なハフニウム(Hf)化合物との組み合わせから構成される。例えば、high-k誘電体はHf酸化物及びランタン(HfO2+La)を含ことができる。さらに、例えば、Hf化合物は、ジルコニウム(Zr)酸化物、HfZr酸化物、Hfケイ酸塩、Zrケイ酸塩、あるいはHfZrケイ酸塩を含むことができ、さらに、RE化合物は、イットリウム(Y)、ジスプロシウム(Dy)、ストロンチウム(Sr)、バリウム(Ba)、イッテルビウム(Yb)、ルテチウム(Lu)、マグネシウム(Mg)、ベリリウム(Be)、スカンジウム(Sc)、セリウム(Ce)、プラセオジム(Pr)、ネオジム(Nd)、ユウロピウム(Eu)、ガドリニウム(Gd)、テルビウム(Tb)、或いはエルビウム(Er)のような、RE金属(REM)、及び(又は)RE酸化物(REO)を含むことができる。しかしながら、前記材料のリストは単なる例であり、他の材料を使用することも可能である。

【0016】

MOSFET102は、誘電体層116上に設けられたゲート電極118をさらに含んでいる。図示するように、ゲート電極118は単一の導電層ゲートを含んでいる。しかしながら、ゲート電極118はさらに多様な導電層ゲートを含むことが可能である。さらに、例えばゲート電極118は金属又は金属合金を用いて形成することも可能である。ゲート電極118に利用し得る材料の例としては、Ti、Hf、Ta、W、Al、Ru、Pt、Re、Cu、Ni、Pd、Ir及び/又はMoのような金属と、TiN、TaN、TiC、TaC、WN、WC及び/又はHfNのような窒化物及び炭化物と、RuOx及び/又はReOxのような伝導性の酸化物と、Ti−Al、Hf−Al、Ta−Al及び/又はTaAlNのような金属−金属合金と、TiN/W、TiN/Ti−Al、Ta/TiN/Ti−Alなどの前記材料の多重積層構造を含む。しかしながら、前記材料のリストは一例であり、ゲート電極に他の材料を使用することも可能である。

【0017】

さらに別の実施形態において、MOSFET102は、例えば第1のスペーサ120、第2のスペーサ122及びシリサイド層124を含んでいる。シリサイド層124はゲート電極118上、及び/又はソース領域110とドレイン領域112上に積層されている。シリサイド層124は、例えばNiSix、PtSix、PdSix、CoSix、TiSix、WSixなどのようなSi及び金属シリサイドで構成される。しかし、前記材料のリストは一例であり、シリサイド層124に他の材料を使用することが可能である。

【0018】

MOSFET102は任意の適切なチャネル幅を有している。チャネル幅は、一般に、活性領域108の紙面と垂直方向における活性領域108の長さである。チャネル幅は例えば約100nm以上、約2000nm以下である。MOSFETは任意の適切なチャネル長を有している。チャネル長は、一般に、対応するソース110とドレイン112領域間と定義される。チャネル長は、例えば約10nm以上、約100nm以下である。MOSFET102は任意の適切なチャネル高さを有している。チャネル高さは、一般に、チャネル底面とチャネル上面との間で定義される。一実施形態において、チャネル高さは約2nm以上、約25nm以下である。別の実施形態において、チャネル高さは約5nm以上、約15nm以下である。さらに、MOSFET102は、任意の適切な誘電体の高さを有している。一実施形態において、誘電体の高さは約1nm以上、約10nm以下である。別の実施形態において、誘電体の高さは約2nm以上、約5nm以下である。

【0019】

簡単化のため、図1に示していないが、MOSFET102は電界効果トランジスタ構造で通常使用することができるあらゆる特徴を含むことができる。例えば、ゲートコンタクトプラグ、ソース−ドレインコンタクト、ゲート構造間の絶縁層などが、さらにMOSFET102へ含まれる。

【0020】

チャネル114は底面及び側面を有する。底面は(100)面(例えば面方位或いは面オリエンテーション)或いは、これに準ずる面(例えば、(100)、(010)或いは(001)面)(以下、総称して「(100)面」と呼ぶ)を有する。トレンチの側面は、(111)面、或いはこれに準ずる面(以下、総称して「面(111)」と呼ぶ)と他の面を含むことができる。側面は実質的に(111)面のみを含むのではない。換言すれば、トレンチの側面は2つ以上の異なる面を有する。

【0021】

シリコン・ゲルマニウム層は底面及び上面を有する。底面と上面は(100)面を有する。シリコン・ゲルマニウム層はさらに側面を有する。シリコン・ゲルマニウム層の側面は(111)面及び他の面を含むことができる。シリコン・ゲルマニウム層の側面は本質的に(111)面だけを含むのではない。換言すれば、シリコン・ゲルマニウム層の側面は2つ以上の異なる面を有する。

【0022】

ゲルマニウム量がチャネル領域の正孔移動度を増加させる限り、シリコン・ゲルマニウム層は任意の適切なゲルマニウム量を有する。一実施形態において、シリコン・ゲルマニウム層は、約0重量%以上、約80重量%以下のシリコン及び約20重量%以上約100重量%以下のゲルマニウムを含む。別の実施形態において、シリコン・ゲルマニウム層は、約30重量%以上、約75重量%以下のシリコン及び約25重量%以上、約70重量%以下のゲルマニウムを含む。さらに別の実施形態において、シリコン・ゲルマニウム層は約60重量%以上、約70重量%以下のシリコン及び約30重量%以上、約40重量%以下のゲルマニウムを含む。

【0023】

ここに例示されるような、MOSFT102の構造に関しても、種々の他の半導体装置に関しても同様に、デバイス構造、導電型、オペレーション電圧などにより各々の最適な閾値電圧を有するゲート電極の構造の形成が複雑化し、否定的な効果を導くことを認識すべきである。従って、安定かつ信頼できる処理を通した半導体装置の閾値電圧の制御が望ましいと認識すべきである。このため、一実施形態によれば、半導体装置における基板の主成分ではない付加的要素をチャネル層114に加えることができる。一例として、チャネル層114に導入された付加的要素の量に、少なくとも一部分基づいて、閾値電圧を変化させることができる。このように半導体装置を構成することにより、従来方式と比較して、より少ない変数で尚且つ信頼できる処理によって仕事関数を容易に調整し、結果的にデバイス性能の改良をもたらすと認識できる。

【0024】

図1及びここに提供される各々の他の例証が、実施形態としての半導体装置の例を示しているが、ここに記述された実施形態は、新しいチャネルデバイス(例えばSiC、SiGeC、III−V材料など)、新しいデバイス構造(例えば絶縁体(SOI)、3−次元のトランジスタ(例えばfinFET、verticalFET、ナノワイヤー、ナノチューブ、...)上のSiなど)、及び(又は)任意の他の適切なデバイス構造へ適用可能である。

【0025】

一実施形態によれば、半導体装置100に対して強化された閾値電圧制御は、チャネル層114へ付加的要素を導入することと、誘電体層116へ付加的要素を導入することにより達成できる。例として、図1に示すように、Geがチャネル層114へ組み入れられ、p型又はp−FETの半導体装置100に対して正の閾値電圧シフトをもたらす。さらに、誘電体層116はRE化合物を含んでいる。この手法は、LaのようなRE化合物がn−FETデバイスの誘電体層中へ排他的に使用される従来の半導体製造方法と対照的である、なぜならRE化合物は、一般的に、p−FETデバイスへ負の閾値電圧シフトをもたらすからである。

【0026】

例えば、図2に示すように、グラフ200はチャネル・シリコン・ゲルマニウム(c−SiGe)上のチャネル層シリコン(Si)キャップ(ナノメーター(nm))に対する線形の閾値電圧(Vtlin)のシフトあるいは差分(ミリボルト(mV))を表している。Siキャップの増加に従い、線形の閾値電圧は減少する。グラフ200は、Hf化合物とRE化合物との組み合わせを用いて構成された誘電体を有するp−FETのチャネル層中のc−Siの代わりにc−SiGeを用いることに起因した負の静電荷の生成により、Vtlinが(110)面に対して約500mV以下正方向へシフトすること、及び(100)面に対して約400mV以下正方向へシフトすることを示している。

【0027】

補足例として、図3に示すように、グラフ300は、チャネル・シリコン(c−Si)及びチャネル・シリコン・ゲルマニウム(c−SiGe)のキャパシタンス(pF)に対するゲート電圧(V)(閾値電圧(Vt)に依存する)を表している。グラフ300は、価電子帯の変調の効果を示しており、Hf化合物とRE化合物との組み合わせを用いて構成された誘電体層を有するp−FETのチャネル層中のc−Siの代わりにc−SiGeを用いることで、(110)面に対して約900mV以下のVtシフトと、(100)面に対して約750mV以下のVtシフトをもたらすことを示している。

【0028】

図4は、実施形態に係る半導体装置400の断面図を示している。図4に示すように、半導体装置400は第1のトランジスタ或いは金属酸化膜半導体(MOS)トランジスタ(又はMOSFETと呼ばれる)401、及び第2のトランジスタ或いはMOSFT403を含みうる。半導体装置400はまた、分離構造408で区切られた第1の活性領域404と第2の活性領域406とを含むシリコン基板402を含んでいる。MOSFET401は、基板402の第1の活性領域404上に構成され、MOSFET403は第2の活性領域406上に構成される。分離構造は、浅いトレンチ分離(STIs)である。さらに、基板402はシリコン基板である。

【0029】

一実施形態によれば、MOSFET401及びMOSFET403は異なる導電型である。例えば、MOSFET401はp型トランジスタ(又はpMOS又はp-FETと呼ぶ)であり、MOSFET403はn型トランジスタ(又はnMOS又はn-FETと呼ぶ)である。この実施形態において、半導体装置400は相補型MOSFETデバイス(又はCMOSデバイスと呼ぶ)であり、p−FET401とn−FET403は相補であり、かつ同じ基板402に構築される。MOSFT401は、ほぼ図1のMOSFET102と同じである。

【0030】

活性領域404内に形成され、互いに分離されているソース領域410とドレイン領域411を、p−FET401はさらに含んでいる。アクティブ領域404内に形成されたチャネル領域412は、ソース領域410とドレイン領域411を分離し得る。非限定的な例において、チャネル領域412はチャネル・シリコンゲル・マニウム(c−SiGe)のようなチャネル材を含むことができる。

【0031】

さらに、p−FET401は、誘電体層414を含んでいる。誘電体層414は、high-k誘電体を有する。例えば、high-k誘電体は様々なハフニウム化合物とレアアース(RE)化合物との組み合わせで構成される。非限定的な例において、high-k誘電体は、Hf酸化物及びランタン(Hf02+La)を含むことができる。さらに非限定的な例において、Hf化合物は、Zr酸化物、HfZr酸化物、Hfケイ酸塩、Zrケイ酸塩、あるいはHfZrケイ酸塩を含み、さらにRE化合物はY、Dy、Sr、Ba、Yb、Lu、Mg、Be、Sc、Ce、Pr、Nd、Eu、Gd、Tb、或いはErのようなRE金属(REM)及び/又はRE酸化物(REO)を含むことができる。しかし、前のリストは単なる例であり、他の構成を利用し得ることは勿論である。

【0032】

p−FET401は、誘電体層414上に設けられたゲート電極416をさらに含んでいる。一実施形態において、ゲート電極416は単一の導電層ゲートを含んでいる。しかし、ゲート電極416が様々な導電層ゲートを含み得ることは勿論である。さらに非限定的な例において、ゲート電極416は金属又は金属合金を用いて形成することも可能である。ゲート電極416へ適用し得る構成の具体例は、Ti、Hf、Ta、W、Al、Ru、Pt、Re、Cu、Ni、Pd、Ir及び(又は)Moのような金属と、TiN、TaN、TiC、TaC、WN、WC及び(又は)HfNのような窒化物、及び炭化物と、RuOx及び(又は)ReOxのような伝導性酸化物と、Ti−Al、Hf−Al、Ta−Al及び(又は)TaAINのような金属−金属合金と、TiN/W、TiN/Ti−Al、Ta/TiN/Ti−Alなどのような前述の構成の多重積層構造を含む。しかし、前のリストは単なる例であり、他の構成を利用し得ることは勿論である。

【0033】

さらに、p−FET401は第1のスペーサ418と、第2のスペーサ420と、シリサイド層422を含んでいる。シリサイド層422は、ゲート電極416上、及び(又は)ソース領域410ならびにドレイン領域411上に積層される。シリサイド層422は、NiSix、PtSix、PdSix、CoSix、TiSix、WSixなどのようなSi及び金属シリサイドで構成される。しかし、前のリストは例示であり、シリサイド層422へ他の構成を適用かなことは言うまでもない。

【0034】

p−FET401と同様に、n−FET403は互いに分離された活性領域406内に形成されたソース領域426及びドレイン領域428を含んでいる。活性領域406内に形成された図示せぬチャネル領域は、ソース領域426とドレイン領域428とを分離し得る。

【0035】

さらに、n−FET403は、誘電体層432を含んでいる。誘電体層432は、誘電体層414中のhigh-k誘電体と実質的に同一又は類似したhigh-k誘電体を有する。例えば、誘電体層414と誘電体層432は、HfO2ゲート+LaのようなRE化合物とハフニウム化合物とを同一の組み合わせで用いて構成される。n-FET403は、誘電体層432上に設けられたゲート電極434をさらに含んでいる。一実施形態において、ゲート電極434は、単一の導電層ゲートを含んでいる。しかし、ゲート電極434は種々の導電層を含むことが可能である。さらに、非限定的な例において、ゲート電極434は、ゲート電極416と同一の金属あるいは金属合金を用いて形成することも可能である。

【0036】

さらに、n−FET403は、第1のスペーサ438と、第2のスペーサ440と、シリサイド層442を含んでいる。シリサイド層422と同様に、シリサイド層442はゲート電極434上、及び(又は)ソース領域426とドレイン領域428上に積層され、Si及び金属シリサイドで構成される。

【0037】

図4に示すように、基板402の最表面におけるシリコン(Si)に対するゲルマニウム(Ge)の濃度は、n-FET403に比べてp-FET401の方が高い。チャネル412中のSiGeは、誘電体層414におけるハフニウム化合物とRE化合物の組み合わせの使用を可能にする。例えば、LaのようなRE化合物は、一般的にn-FET中でのみ用いられる。なぜなら、Laは一般的にp-FETのVtを負の方向へシフトする。このため、p-FETのhigh-k誘電体中では使用できない。しかし、p−FET401のVtは、チャネル412中でSiGeをSiに置換することにより、正方向(例えばプラス)へシフトできる(図2−3参照)。

【0038】

チャネルSiGe上に設けられる誘電体層414として、Hf化合物とRE化合物との組み合わせからなるhigh-k誘電体を用いることで、p-FET401のVtが正方向へシフトし、誘電体層414と誘電体層432へ、例えばHfO2+Laのような、単一のhigh-k誘電体を用いることを可能とする。さらに、ゲート電極416とゲート電極434は、前述した同一のゲート電極材料を用いることができる。したがって、上記は、異なる金属ゲート材料と異なるhigh-k誘電体材をp-FETとn-FETへ典型的に用いるCMOSデバイスに関して、単純な構造を提供できる。

【0039】

半導体装置400の構造に関して、ここで例示した他の半導体装置と同様に、デバイス構造、導電型、動作電圧などに従う各々の適切な閾値電圧を有するゲート電極の構造が複雑化し、否定的な効果を導くことを認識できる。したがって、安定性と信頼性の高い処理を通じて半導体装置の閾値電圧を制御するためのメカニズムが望まれると認識できる。

【0040】

図5乃至図12は、電界効果トランジスタの形成に関する多くの実施形態の一つを具体的に示している。図5は、典型的な電界効果トランジスタ500の中間状態の断面を示している。

【0041】

電界効果トランジスタ500は、基板、例えばシリコン基板502と、半導体基板中の複数のSTI508により分離された、第1の活性領域504と第2の活性領域506とを含んでいる。STIは、化学気相成長(CVD)と、リソグラフィと、エッチング技術により形成される。半導体基板上にパターニングされたハードマスクが形成される。パターニングされたハードマスクに覆われていない半導体基板の一部は、半導体基板中に開口部を形成するため、例えばエッチングにより除去される。STIは、STI材料で開口部を満たすことにより形成される。

【0042】

図5には図示していないが、ウェルとチャネルは、STI間の半導体基板間の活性領域504及び506内に形成される。例えば電界効果トランジスタがp型のトランジスタである場合、ウェルは1つ以上のN型ドーパント(例えばリン)の注入によって形成され、さらにチャネルは1つ以上のN型ドーパント(例えばヒ素)の注入によって形成される。一実施形態において、p型トランジスタ(又はpMOSかp−FET)は、活性領域504に形成され、さらにn型トランジスタ(又はnMOSかn−FET)は、活性領域506に形成される。

【0043】

図6は、複数のSTI508間の半導体基板502の一部分を除去することにより、活性領域504の最上部で、半導体基板502の上部のほぼ全面で窪み600が形成されることを示している。この窪みは異方性化学ウェットエッチングにより形成される。異方性化学ウェットエッチングの前に、酸化物が半導体基板上に形成される場合、酸化物は希釈された沸化水素酸(HF)により除去することができる。半導体基板は希釈HFに少しの間、浸される。

【0044】

(100)面を有し底面602を有する窪みをエッチングにより形成する間、窪みは任意の適切な異方性化学ウェットエッチングにより形成できる。異方性化学ウェットエッチングは、一般に(100)の底面及び(111)面を有する側面604(又は、サイドファセット)を形成する。

【0045】

異方性化学ウェットエッチングのエッチャントの例は、水酸化テトラアルキルアンモニウム(例えば水酸化テトラメチルアンモニウム(TMAH))及び水酸化アンモニウム(NH4OH)のような基礎液を含んでいる。一例として、TMAH溶液を用いた窪みの形成を下記に述べる。TMAH溶液を用いた窪みの形成は、TMAH溶液中へ半導体構造500を浸すか、半導体構造500の上部にTMAH溶液を霧散又は散布することにより一般的に処理される。

【0046】

TMAH溶液は、他の構成要素を実質的に破損あるいはエッチングすることなく、半導体構造500の一部を除去するために十分な量のTMAHを含んでいる。一実施形態において、TMAH溶液は、TMAHの約0.5重量%以上、約40重量%以下を含んでいる。別の実施形態において、TMAH溶液は、TMAHの約1重量%以上、約25重量%以下を含んでいる。所望のTMAHの濃度を生成するため、TMAHは脱イオン水のような水で希釈される。

【0047】

半導体基板502は、窪みの形成を促進するために適切な温度でTMAH溶液と接触される。一実施形態において、半導体基板は、摂氏約20度以上、摂氏約100度以下の温度でTMAH溶液と接触される。別の実施形態において、半導体基板は、摂氏約30度以上、摂氏約60度以下の温度でTMAH溶液と接触される。半導体基板は、窪みの形成を促進するのに適切な時間でTMAH溶液と接触される。一実施形態において、半導体基板は、約5秒以上、約20分以下の間、TMAH溶液と接触される。また、一実施形態において、半導体基板は、約10秒以上、約15分以下の間、TMAH溶液と接触される。例えば、半導体基板は、2.5分の間、摂氏約45度の温度で、TMAHの約2.5重量%を含むTMAH溶液と接触される。

【0048】

別の実施形態において、腐食液はNH4OH溶液である。NH4OHの所望の濃度(例えば、NH4OH: H2O=1: 3,000(wt/wt))を生成するため、NH4OHは脱イオン水のような水で希釈される。半導体基板は、約100秒間、摂氏約45度の温度でNH4OH溶液と接触される。

【0049】

窪み600は任意の適切な深さを有する。この窪みはほぼ一定の深さを有している。深さは変化するかもしれないし、本実施形態に重要ではないかもしれない。深さは、例えば製造した電界効果トランジスタの希望する実施形態に依存し得る。一実施形態において、溝の深さは約5nm以上、約15nm以下である。別の実施形態において、深さは約2nm以上、25nm以下である。さらに別の実施形態において、深さは約10nmである。

【0050】

図7は、窪み600の側面の面方位を変えるために半導体基板を熱することを示している。側面が単一の面方位を有している場合、熱処理は単一の面方位を2つ以上の面方位へ変える。側面が単一の(111)面を有する場合、熱処理は、単一の(111)面を2つ以上の面、例えば、(111)面、(112)面、(200)面、(101)面、(011)面などへ変える。熱処理により、窪み600は側面704に関して2つ以上の面を含む。(100)面の底面は変化せずに残存する。半導体基板は熱処理によって再結晶化される。

【0051】

窪みの側面に二つ以上の面を形成することを促進するため、及び(又は)半導体基板の再結晶化のため、任意の適切な条件の下で、半導体基板502は加熱される。一実施形態において、半導体基板は、約1分以上、約10分以下の間、摂氏約700度以上、摂氏約900度以下の温度で水素中にて加熱される。別の実施例において、半導体基板は、約10秒以上、約30分以下の間、摂氏約500度以上、摂氏約900度以下の温度で水素中にて加熱される。

【0052】

図8は窪み中へシリコン・ゲルマニウム層800を形成することを示している。シリコン・ゲルマニウム層はエピタキシャル技術によって形成される。シリコン・ゲルマニウム・エピタキシャル成長は、任意の適切な条件、例えば、シリコン原料ガス(例えばSiH4、Si2H6、SiH8、SiF4など)、ゲルマニウム原料ガス(例えばGeH4、GeF4など)及び任意のキャリアガスを使用して、高温(例えば摂氏1100度)の下で進められる。シリコン・ゲルマニウムの上部が半導体基板及び(又は)STIの上部とほぼ同一面である時、シリコン・ゲルマニウム・エピタキシャル成長は終了する。

【0053】

一実施形態において、溝が(100)面の底面を有する場合、シリコン・ゲルマニウム層は(100)面の底面602を有する。シリコン・ゲルマニウム層は、(100)面の上面802を有している。別の実施形態において、溝が2つ以上の異なる面を有する側面を有する場合、シリコン・ゲルマニウム層は側面704に2つ以上の異なる面を有する。さらに別の実施形態において、溝がほぼ一定の深さを有する場合、シリコン・ゲルマニウム層はほぼ一定の高さを有する。

【0054】

図9は、シリコン・ゲルマニウム層800上の第1のゲート誘電体層902と、第2の活性領域506の最上部上の第2のゲート誘電体層904を含んでいるゲート形状900の形成を示している。さらに、第1のゲート電極906は第1のゲート誘電体層902上に配置され、また、第2のゲート電極908は第2のゲート誘電体層904上に配置される。ゲート構造は、半導体装置500上のゲート誘電体層と、ゲート誘電体層上のゲート電極層の形成と、ゲート誘電体層とゲート電極層のパターンニングにより形成される。

【0055】

ゲート誘電体層902及び904はhigh-k誘電体を有する。例えば、high-k誘電体はレアアース(RE)化合物と様々なハフニウム(Hf)化合物との組み合わせを含むことができる。非限定的な例において、high-k誘電体はHf酸化物及びランタン(HfO2+La)を含むことができる。さらに非限定的な例において、Hf化合物は、Zr酸化物、HfZr酸化物、Hfケイ酸塩、Zrケイ酸塩、あるいはHfZrケイ酸塩を含み、さらにRE化合物は、Y、Dy、Sr、Ba、Yb、Lu、Mg、Be、Sc、Ce、Pr、Nd、Eu、Gd、Tb、或いはErのようなRE金属(REM)及び/又はRE酸化物(REO)を含むことができる。しかし、前記リストは単なる例示であり、他の構成をとり得ることは言うまでもない。

【0056】

ゲート誘電体層902と904、及びゲート電極906と908は、任意の適切な技術により形成できる。例えば、ゲート誘電体層902と904、及びゲート電極906と908は、堆積(例えばCVD、スピン・オン技術など)、リソグラフィ、そしてエッチング技術により形成できる。さらに、ゲート誘電体層902と904はエピタキシャル成長技術(例えばシリコン・エピタキシャル成長)及び酸化技術(例えば熱酸化、プラズマ支援酸化など)によって形成できる。さらに、RE化合物は注入、ドーピング或いは任意の適切な技術によって、誘電体層中のHf化合物と結合するか、加えられるか、別の方法で連結できる。

【0057】

誘電体層902と904及びゲート電極906と908は、ほぼ一定の高さを有している。この高さは、変わる可能性があり、本実施形態において、重要ではない。高さは、例えば製造される電界効果トランジスタの希望の実施形態に依存する可能性がある。一実施形態において、誘電体層902と904の高さは約1nm以上、約10nm以下である。別の実施形態において、高さは約2nm以上、約5nm以下である。さらに別の実施形態において、高さは約2nmである。

【0058】

図10は、ゲート誘電体層902と904及びゲート電極906と908の隣接側面と、シリコン・ゲルマニウム層800の上面或いは活性領域506の最上面上へ側面スペーサ(例えば側壁層)1002を形成することを示している。側面スペーサは、酸化物のような任意の適切な絶縁材料を含んでいる。酸化物の例は、シリコン酸化物、テトラエチルオルトシリケート(TEOS)酸化物、高アスペクト比プラズマ(HARP)酸化物、高温酸化物(HTO)、高密度プラズマ(HDP)酸化物、原子層堆積(ALD)プロセスによって形成された酸化物など(例えばシリコン酸化物)を含んでいる。側面スペーサ材料の他の例は、窒化物(例えば窒化シリコン、シリコンオキシナイトライド及びシリコンリッチ窒化シリコン)、ケイ酸塩、ダイヤモンド−ライクカーボン、炭化物などを含む。

【0059】

側面スペーサは、任意の適切な技術、例えば半導体基板を覆うスペーサ材を含む層の形成と、次に、ゲート構造の側面近くでないスペーサ材層の一部を除去することで形成される。スペーサ材層は堆積技術(例えばCVD、スピン・オン技術など)により、少なくともゲート構造の側面を覆って形成される。

【0060】

スペーサ材層を形成した後、スペーサ材層の一部は例えばエッチングにより除去される。エッチングがシリコン・ゲルマニウム層上のゲート絶縁層及びゲート電極の側面に隣接するスペーサを除去する間、任意の適切なエッチングが使用される。ウェットエッチング及び(又は)ドライエッチングが適用可能である。エッチングの例は、反応性イオン・エッチング(RIE)、化学プラズマ・エッチング、或いは適切な化学的性質を用いた適切な異方性エッチングを含む。

【0061】

図示されていないが、ソース/ドレイン拡張領域、及び(又は)ポケット領域は側面スペーサ1002及び1004の形成の前後に形成される。任意の適切な注入構成及び濃度は、ソース/ドレイン拡張領域に適用される。ソース/ドレイン拡張領域は任意の適切な技術によって形成することができる。ソース/ドレイン拡張領域は、1つ以上のドーパントの注入により形成される。ドーパントは、ゲート構造によってカバーされない半導体基板の部分へ注入される。ゲート構造は注入スクリーンとして機能する。ソース/ドレイン拡張領域は、比較的低いエネルギー準位、及び(又は)比較的低いドーパント量を備えた注入によって形成される。一実施形態において、ソース/ドレイン拡張領域は、約0.1KeV以上、約1KeV以下のエネルギー準位、及び1E14 atoms/cm2以上、3E15 atoms/cm2以下の量で形成される。別の実施形態において、ソース/ドレイン拡張領域は、約1KeV以上、約5KeV以下のエネルギー準位、ならびに5E13 atoms/cm2以上、3E15 atoms/cm2以下の量で形成される。

【0062】

同様に、任意の適切な注入構成及び濃度は、ポケット領域へ適用される。ポケット注入は、電界効果トランジスタのVt特性を改善する。ポケット領域が、メモリ装置のコンタクトパンチスルー特性を改善するという条件で、ポケット領域は、任意の適切なサイズ、形、注入構成と濃度を有する。一実施形態において、ポケット領域は半導体基板の表面に垂直な軸から半導体基板の方向に、約0度以上、約40度以下の傾斜注入角度を有している。ポケット領域は、任意の適切な注入角度において、1つ以上のドーパントの注入によって形成される。

【0063】

一実施形態において、ポケット領域は、約25KeV以上、約60KeV以下のエネルギー準位で形成される。別の実施形態において、ポケット領域は、約30KeV以上、約70KeV以下のエネルギー準位で形成される。一実施形態において、ポケット領域は約5E12 atoms/cm2以上、8E13 atoms/cm2以下の量で形成される。別の実施形態において、ポケット領域は5E12 atoms/cm2以上、1E14 atoms/cm2以下の量で形成される。

【0064】

図11は、半導体基板502中において、ゲート構造に隣接するソース/ドレイン領域1100及び1102の形成と、ソース/ドレイン領域1102間の半導体基板の活性領域506中における、図示せぬ第2のチャネル領域を示している。任意の適切な注入構成及び濃度は、ソース/ドレイン領域へ適用される。例えば、ソース/ドレイン領域1100は1つ以上のn−typeドーパント(例えばヒ素)を含む。図示されていないが、注入されたドーパントは、半導体基板をアニールすることで活性化される。

【0065】

ソース/ドレイン領域1100及び1102は、任意の適切な技術によって形成される。ソース/ドレイン領域1100及び1102は、1つ以上のドーパントの注入によって形成することができる。ドーパントは、ゲート構造及び側面スペーサによってカバーされない、半導体基板の部分へ注入される。ゲート構造及び側面のスペーサは注入スクリーンとして機能する。ソース/ドレイン領域1100及び1102は、比較的高いエネルギー準位、及び(又は)比較的高いドーパント量を備えた注入により形成される。一実施形態において、ソース/ドレイン領域は約5KeV以上、20KeV以下のエネルギー準位、及び8E14 atoms/cm2以上、1E16 atoms/cm2以下の量で形成される。別の実施形態において、ソース/ドレイン領域は、約2KeV以上、約8KeV以下のエネルギー準位、及び1E14 atoms/cm2以上、1E16 atoms/cm2以下の量で形成される。さらに別の実施形態において、ソース/ドレイン領域は、埋め込まれたエピタキシャルSiGeにより形成される。ドーパントはイン−サイト(in-situ)・ドープド・エピタキシャルにより形成される。

【0066】

図12は、ゲート構造(例えばゲート構造及び側面スペーサ)によってカバーされないシリコン・ゲルマニウム層800及び半導体基板502の部分上の図示せぬ金属シリサイドの形成を示している。ゲート電極がシリコンを含んでいる場合、金属シリサイド1200及び1202はゲート電極上に形成される。金属シリサイドは、ゲート構造によってカバーされない電界効果トランジスタの部分を備えた電界効果トランジスタ上に形成された金属層の化学反応によって形成される。金属シリサイドは、金属層が電界効果トランジスタのシリコンを含む層又は構成要素と接触しない所では形成されない。

【0067】

図12に示していないが、金属層は電界効果トランジスタ上に形成される。金属層は、後のプロセスで金属シリサイドへ変換される任意の適切な金属化合物を含んでいる。金属の例は、タングステン、タンタル、モリブデンなどの超硬合金、及びプラチナ、パラジウム、コバルト・ニッケルなどのような周期表のグループVIIIの金属を含む。金属層は、後の熱処理において、シリコン基板、及び(又は)ゲート電極中に潜んだシリコンと金属シリサイド化合物を生ずるために変換される。金属層は任意の適切な技術、例えばCVD、物理気相蒸着法(PVD)などにより形成される。金属層は、例えば後のプロセスで形成された金属シリサイドの所望の厚さに依存する任意の適切な厚さを有する。

【0068】

電界効果トランジスタの層/構成要素に含まれているシリコンと金属層との間の化学反応を起こすため、金属層を加熱することにより、金属層は金属シリサイドへ変換される。一実施形態において、金属シリサイドは、金属層とシリコン基板に潜在しているシリコン及び(又は)ゲート電極のポリシリコンとの化学反応により形成される。シリサイド化プロセス中、金属層の金属は、層/構成要素に含まれている潜在シリコンへ拡散し、金属シリサイドを形成する。この結果、金属シリサイドは、選択的に電界効果トランジスタ上に形成される。

【0069】

金属シリサイドは、例えば、所望の実装及び(又は)製造した電界効果トランジスタに依存する任意の適切な高さを有している。一実施形態において、金属シリサイドは約5nm以上、約30nm以下の高さを有する。別の実施形態において、金属シリサイドは約10nm以上、約25nm以下の高さを有する。

【0070】

シリサイド化プロセスの適切な条件やパラメーター(例えば、温度、熱処理の継続時間など)の選択は、例えば、金属シリサイドの望ましい次元(例えば高さ)や、要素/層に含まれている潜在シリコン及び(又は)金属層の配置及び(又は)要素と、希望の実装、及び(又は)製造した電界効果トランジスタなどに依存する。例えば、金属シリサイドはラッピド・サーマル・アニール(RTA)により形成される。

【0071】

金属層の一部は、例えば側面スペーサ及びSTI上に反応せずに残り、例えばエッチングによって除去される。金属層の未反応部分は、金属層の未反応部分と任意の適切な金属エッチャントを接触することにより除去される。金属シリサイドのような電界効果トランジスタのその他の層/構成要素の全てにほぼ影響あるいは損傷を与えない。

【0072】

金属エッチャントの例は、酸化エッチャント液を含む。酸化エッチャント液の例は、例えば、H2SO4/H2O2、HNO3/H2O2、HCI/H2O2、H2O2/NH4OH/H2O、H3PO4、HNO3、CH3COOHなどを含んだ酸性溶液を含む。他の金属エッチャント液が、電界効果トランジスタのその他の構成要素/層に対して金属層の未反応部分を選択的に除去することが可能な限り、他の金属エッチャント液も使用可能である。

【0073】

金属シリサイドは、シリコンとポリシリコンよりも著しく低いシート抵抗を有している。ポリシリコンを含むゲート上に形成された金属シリサイドは、一般にポリサイドゲートと呼ばれ、ポリシリコン・ゲートと比較してゲート構造の抵抗を著しく低下する。その結果、ゲート電極の全体的な伝導性が増加される。

【0074】

図13は、半導体装置を形成する例示的な方法1300を示している。1302において、窪みはSTI間の半導体基板上において、p−FETのほぼ全上部に形成される。前述したように、CMOSデバイスを含む半導体基板上に、n−FETも存在する。一実施形態において、窪みは底面の(100)面及び側面の(111)面を有する。別の実施形態において、半導体基板は窪みの側面の(111)面を、2つ以上の異なる面に変更するために加熱される。1304において、シリコン・ゲルマニウム層は窪みの中に形成される。一実施形態において、シリコン・ゲルマニウム層は底面及び上面の(100)面と、側面の2つ以上の面を有する。

【0075】

1306において、ゲート誘電体及びゲート電極を含むゲート構造が、シリコン・ゲルマニウム層上に形成される。ゲート誘電体は、high-k誘電体を有する。例えば、high-k誘電体は、様々なハフニウム(Hf)化合物とレアアース(RE)化合物との組み合わせを含むことができる。非限定的な例において、high-k誘電体はHf酸化物及びランタン(HfO2+La)を含んでいる。さらに非限定的な例において、Hf化合物は、Zr酸化物、HfZr酸化物、Hfケイ酸塩、Zrケイ酸塩、あるいはHfZrケイ酸塩を含み、さらにRE化合物は、Y、Dy、Sr、Ba、Yb、Lu、Mg、Be、Sc、Ce、Pr、Nd、Eu、Gd、Tb或いはErのようなRE金属(REM)及び(又は)RE酸化物(REO)を含むことができる。しかし、前記リストは単なる例示であり、他の構成を利用可能なことは勿論である。

【0076】

さらに、ゲート電極118に利用される構成の非限定的な例は、Ti、Hf、Ta、W、Al、Ru、Pt、Re、Cu、Ni、Pd、Ir及び(又は)Moのような金属と、TiN、TaN、TiC、TaC、WN、WC及び(又は)HfNのような窒化物及び炭化物と、RuOx及び(又は)ReOxのような伝導性の酸化物と、Ti−Al、Hf−Al、Ta−Al及び(又は)TaAINのような金属−金属−合金と、TiN/W、TiN/Ti−Al、Ta/TiN/Ti−Alなどのような前述の構成の多層構造を含む。しかし、前記リストは例示であり、他の構成もゲート電極へ適用できることを認識すべきである。

【0077】

1308において、ソース/ドレイン領域が半導体基板の中に形成される。一実施形態において、ソース/ドレイン拡張領域及びソース/ドレインポケットも半導体基板中で形成される。1310において、金属シリサイドがシリコン・ゲルマニウム層の上部及びゲート構造によってカバーされない半導体基板に形成される。

【0078】

図13には示していないが、窪みは異方性化学ウェットエッチングにより形成される。別の実施形態において、溝は、水酸化テトラメチルアンモニウム溶液、或いは水酸化アンモニウム溶液を用いて形成される。さらに別の実施形態において、シリコン・ゲルマニウムはシリコン・ゲルマニウム・エピタキシャル・プロセスにより形成される。さらに別の実施形態において、窪みの側面の(111)面は、約5分以上、約100分以下の間摂氏約700度以上、摂氏約1,300度以下の温度で水素中の半導体基板を熱することにより、2つ以上の異なる面に変更される。

【0079】

図13には示していないが、コンタクトホール、導電線及び他の適切な要素は、任意の適切な半導体装置製造プロセスにより形成される。半導体装置製造プロセスの一般的な例は、半導体装置を形成するために通常使用される、マスキング、パターンニング、エッチング、クリーニング、平坦化、熱酸化、注入、アニール、熱処理、及び堆積技術を含んでいる。

【0080】

図13には示していないが、1306中のゲート構造に類似のゲート構造は、半導体基板上のn−FET上に形成される。n−FET上に形成されたゲート構造は、p−FET上に形成したゲート構造と同じhigh-k誘電率及び同じゲート電極材料を有する。さらに、1308に類似のソース/ドレイン領域はn−FET上で形成され、1310に類似の金属シリサイドは、ゲート構造によってカバーされないn−FET上部に形成される。前述したように、p−FETの溝中のシリコン・ゲルマニウム層に関する実施例は、適切な閾値電圧を得るために、p−FET及びn−FETの両方へ単一のhigh-k誘電体及び金属ゲートの使用を可能にすると認識すべきである。

【0081】

その他、本発明は上記各実施形態そのままに限定されるものではなく、実施段階ではその要旨を逸脱しない範囲で構成要素を変形して具体化できる。また、上記各実施形態に開示されている複数の構成要素の適宜な組み合わせにより、種々の発明を形成できる。例えば、実施形態に示される全構成要素から幾つかの構成要素を削除してもよい。さらに、異なる実施形態にわたる構成要素を適宜組み合わせてもよい。

【0082】

(付記)

(4) 前記レアアース化合物は、Y、Dy、Sr、Ba、Yb、Lu、又はMgのうちの少なくとも1つを含むことを特徴とする3記載の半導体装置。

【0083】

(5) 前記レアアース化合物は、Be、Sc、Ce、Pr、Nd、Eu、Gd、Tb、又はErのうちの少なくとも1つを含むことを特徴とする請求項1記載の半導体装置。

【0084】

(6) 前記シリコン・ゲルマニウム層上に形成された前記high-k誘電体を有する前記第1のゲート誘電体層は、p型電界効果トランジスタ中に負の静電荷を生成することを特徴とする5記載の半導体装置。

【0085】

(7) 前記シリコン・ゲルマニウム層上に形成された前記high-k誘電体を有する前記第1のゲート誘電体層は、前記p型の電界効果トランジスタの閾値電圧を正の方向にシフトすることを特徴とする6記載の半導体装置。

【0086】

(8) 前記閾値電圧の前記シフトは前記シリコン・ゲルマニウム層におけるシリコンに対するゲルマニウムの割合に少なくとも一部分基づくことを特徴とする7記載の半導体装置。

【0087】

(9) 前記基板の前記p型電界効果トランジスタ形成領域の表面は窪みを有し、前記窪み内に前記シリコン・ゲルマニウム層が形成され、前記窪みは、約2nm以上約25nm以下の深さを有することを特徴とする8記載半導体装置。

【0088】

(13) 前記シリコン・ゲルマニウムと、ハフニウム化合物及びレアアースを含む前記第1の材料との組み合わせは、p型電界効果トランジスタ中に負の静電荷を生成することを特徴とする12記載の半導体装置。

【0089】

(14) 前記シリコン・ゲルマニウムと、ハフニウム化合物とレアアースを含む前記第1の材料との組み合わせは、p型電界効果トランジスタの閾値電圧をシフトすることを特徴とする13記載の半導体装置。

【0090】

(15) 前記閾値電圧に関する前記シフトは、正の方向に約500mV以下であることを特徴とする14記載の半導体装置。

【0091】

(16) 前記基板は、第1の材料により構成された第2のゲート誘電体と、前記第2のゲート誘電体上に設けられた第2の材料により構成された第2のゲート電極とを有するn型電界効果トランジスタをさらに含むことを特徴とする15記載の半導体装置。

【0092】

(19) 前記シリコン・ゲルマニウム層中のゲルマニウム濃度を制御することにより前記p型電界効果トランジスタの閾値電圧が正の方向へ移動することを特徴とする18記載の半導体装置の製造方法。

【0093】

(20) 前記半導体基板上のn型電界効果トランジスタ領域に、第1のゲート誘電体層と同じハフニウム化合物及びレアアース化合物を用い第2のゲート誘電体を形成することと、

前記n型電界効果トランジスタ領域において、前記第2のゲート誘電体上に第2のゲート電極を形成することをさらに含むことを特徴とする19記載の半導体装置の製造方法。

【符号の説明】

【0094】

104、402…シリコン基板、102…MOSFET、p−FET…401、n−FET…403、110、410、426…ソース領域、112、411、428…ドレイン領域、116、414、432…誘電体層、118、416、434…ゲート電極、124、422、442…シリサイド層、412…チャネル、602…窪み。

【特許請求の範囲】

【請求項1】

基板と、

前記基板上に設けられたp型電界効果トランジスタと、

前記基板上に設けられたn型電界効果トランジスタと、

を具備し、

前記p型電界効果トランジスタは、

前記基板上に形成されたシリコン・ゲルマニウム層と、

前記シリコン・ゲルマニウム層上に形成され、ハフニウム化合物とレアアース化合物を含む第1の材料としてのhigh-k誘電体を有する第1のゲート誘電体層と、

前記第1のゲート誘電体層上に形成された第2の材料を有する第1のゲート電極と、を具備し、

前記n型電界効果トランジスタは、

前記基板層上に形成された前記high-k誘電体を有する第2のゲート誘電体層と、

前記第2のゲート誘電体層上に形成された前記第2の材料を有する第2のゲート電極と

を具備することを特徴とする半導体装置。

【請求項2】

前記第1の材料に含まれる前記ハフニウム化合物は、Hf酸化物、Zr酸化物、HfZr酸化物、Hfケイ酸塩、Zrケイ酸塩或いはHfZrケイ酸塩のうち、少なくとも1つを含むことを特徴とする請求項1記載の半導体装置。

【請求項3】

前記レアアース化合物は、Laであることを特徴とする請求項2記載の半導体装置。

【請求項4】

基板と

前記基板上に設けられたp型電界効果トランジスタと、を具備し、

前記p型電界効果トランジスタは、

前記基板上に形成されたシリコン・ゲルマニウム層と、

前記シリコン・ゲルマニウム層上に形成され、ハフニウム化合物とレアアースとを含む高誘電率を有する第1の材料から形成されたゲート誘電体と、

前記ゲート誘電体上に第2の材料から形成されたゲート電極と

を具備する半導体装置。

【請求項5】

前記第1の材料に含まれる前記ハフニウム化合物は、Hf酸化物、Zr酸化物、HfZr酸化物、Hfケイ酸塩、Zrケイ酸塩或いはHfZrケイ酸塩のうち少なくとも1つを含むことを特徴とする請求項4記載の半導体装置。

【請求項6】

前記第1の材料に含まれる前記レアアース化合物は、La、Y、Dy、Sr、Ba、Yb、Lu、Mg、Be、Sc、Ce、Pr、Nd、Eu、Gd、Tb、又はErのうち少なくとも1つを含むことを特徴とする請求項5記載の半導体装置。

【請求項7】

浅いトレンチ分離間の半導体基板上でp型電界効果トランジスタ領域のほぼ全上部に窪みを形成し、

前記窪み内にシリコン・ゲルマニウム層を形成し、

前記p型電界効果トランジスタ領域中の前記シリコン・ゲルマニウム層上へハフニウム化合物とレアアース化合物により構成された高誘電率を有するゲート誘電体を形成し、

前記p型電界効果トランジスタ領域中に前記ゲート誘電体上にゲート電極を形成すること

を具備した半導体装置の製造方法。

【請求項8】

前記ハフニウム化合物と前記レアアース化合物から高誘電率kを有するゲート誘電体を形成することは、Hf酸化物、Zr酸化物、HfZr酸化物、Hfケイ酸塩、Zrケイ酸塩、又はHfZrケイ酸塩のうち少なくとも1つを含む前記ハフニウム化合物の形成と、La、Y、Dy、Sr、Ba、Yb、Lu、Mg、Be、Sc、Ce、Pr、Nd、Eu、Gd、Tb、又はErのうち少なくとも1つを含む前記レアアース化合物の形成を含むことを特徴とする請求項7記載の半導体装置の製造方法。

【請求項1】

基板と、

前記基板上に設けられたp型電界効果トランジスタと、

前記基板上に設けられたn型電界効果トランジスタと、

を具備し、

前記p型電界効果トランジスタは、

前記基板上に形成されたシリコン・ゲルマニウム層と、

前記シリコン・ゲルマニウム層上に形成され、ハフニウム化合物とレアアース化合物を含む第1の材料としてのhigh-k誘電体を有する第1のゲート誘電体層と、

前記第1のゲート誘電体層上に形成された第2の材料を有する第1のゲート電極と、を具備し、

前記n型電界効果トランジスタは、

前記基板層上に形成された前記high-k誘電体を有する第2のゲート誘電体層と、

前記第2のゲート誘電体層上に形成された前記第2の材料を有する第2のゲート電極と

を具備することを特徴とする半導体装置。

【請求項2】

前記第1の材料に含まれる前記ハフニウム化合物は、Hf酸化物、Zr酸化物、HfZr酸化物、Hfケイ酸塩、Zrケイ酸塩或いはHfZrケイ酸塩のうち、少なくとも1つを含むことを特徴とする請求項1記載の半導体装置。

【請求項3】

前記レアアース化合物は、Laであることを特徴とする請求項2記載の半導体装置。

【請求項4】

基板と

前記基板上に設けられたp型電界効果トランジスタと、を具備し、

前記p型電界効果トランジスタは、

前記基板上に形成されたシリコン・ゲルマニウム層と、

前記シリコン・ゲルマニウム層上に形成され、ハフニウム化合物とレアアースとを含む高誘電率を有する第1の材料から形成されたゲート誘電体と、

前記ゲート誘電体上に第2の材料から形成されたゲート電極と

を具備する半導体装置。

【請求項5】

前記第1の材料に含まれる前記ハフニウム化合物は、Hf酸化物、Zr酸化物、HfZr酸化物、Hfケイ酸塩、Zrケイ酸塩或いはHfZrケイ酸塩のうち少なくとも1つを含むことを特徴とする請求項4記載の半導体装置。

【請求項6】

前記第1の材料に含まれる前記レアアース化合物は、La、Y、Dy、Sr、Ba、Yb、Lu、Mg、Be、Sc、Ce、Pr、Nd、Eu、Gd、Tb、又はErのうち少なくとも1つを含むことを特徴とする請求項5記載の半導体装置。

【請求項7】

浅いトレンチ分離間の半導体基板上でp型電界効果トランジスタ領域のほぼ全上部に窪みを形成し、

前記窪み内にシリコン・ゲルマニウム層を形成し、

前記p型電界効果トランジスタ領域中の前記シリコン・ゲルマニウム層上へハフニウム化合物とレアアース化合物により構成された高誘電率を有するゲート誘電体を形成し、

前記p型電界効果トランジスタ領域中に前記ゲート誘電体上にゲート電極を形成すること

を具備した半導体装置の製造方法。

【請求項8】

前記ハフニウム化合物と前記レアアース化合物から高誘電率kを有するゲート誘電体を形成することは、Hf酸化物、Zr酸化物、HfZr酸化物、Hfケイ酸塩、Zrケイ酸塩、又はHfZrケイ酸塩のうち少なくとも1つを含む前記ハフニウム化合物の形成と、La、Y、Dy、Sr、Ba、Yb、Lu、Mg、Be、Sc、Ce、Pr、Nd、Eu、Gd、Tb、又はErのうち少なくとも1つを含む前記レアアース化合物の形成を含むことを特徴とする請求項7記載の半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【公開番号】特開2013−4968(P2013−4968A)

【公開日】平成25年1月7日(2013.1.7)

【国際特許分類】

【出願番号】特願2012−124497(P2012−124497)

【出願日】平成24年5月31日(2012.5.31)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

【公開日】平成25年1月7日(2013.1.7)

【国際特許分類】

【出願日】平成24年5月31日(2012.5.31)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

[ Back to top ]