半導体装置とその製造方法

【課題】上下の半導体チップ間の隙間を維持しつつ、アンダーフィル樹脂の充填前における半導体チップ間の接続強度を高めることを可能にした積層型半導体装置を提供する。

【解決手段】実施形態の半導体装置1は、第1の半導体チップ2と、第1の半導体チップ2上に積層された第2の半導体チップ3とを具備する。第1および第2の半導体チップ2、3は、バンプ接続体6を介して電気的に接続されている。第1および第2の半導体チップ2、3の少なくとも一方には、ストッパ用突起7と接着用突起8とが設けられている。ストッパ用突起7は、第1および第2の半導体チップ2、3の他方に非接着状態で接触している。接着用突起8は、第1および第2の半導体チップ2、3に接着されている。

【解決手段】実施形態の半導体装置1は、第1の半導体チップ2と、第1の半導体チップ2上に積層された第2の半導体チップ3とを具備する。第1および第2の半導体チップ2、3は、バンプ接続体6を介して電気的に接続されている。第1および第2の半導体チップ2、3の少なくとも一方には、ストッパ用突起7と接着用突起8とが設けられている。ストッパ用突起7は、第1および第2の半導体チップ2、3の他方に非接着状態で接触している。接着用突起8は、第1および第2の半導体チップ2、3に接着されている。

【発明の詳細な説明】

【技術分野】

【0001】

本発明の実施形態は、半導体装置とその製造方法に関する。

【背景技術】

【0002】

半導体装置の小型化や高機能化を実現するために、1つのパッケージ内に複数の半導体チップを積層して封止したSiP(System in Package)構造の半導体装置が実用化されている。SiP構造の半導体装置では、半導体チップ間の電気信号を高速に送受信することが求められる。このような場合、半導体チップ間の電気的な接続にはマイクロバンプが用いられる。マイクロバンプは、例えば5〜50μm程度の直径を有し、10〜100μm程度のピッチで半導体チップの表面に形成される。

【0003】

マイクロバンプを用いて半導体チップ間を接続する場合、上下の半導体チップに設けられたバンプ同士を位置合わせした後、熱を加えながら上下の半導体チップを圧着してバンプ同士を接続する。上下の半導体チップ間の隙間には、接続信頼性等を高めるためにアンダーフィル樹脂が充填される。バンプ接続の際に、チップ間の隙間が減少しすぎるとバンプの過度の潰れやそれに伴うショートが発生する。このため、上下の半導体チップ間の隙間を維持することが求められている。さらに、バンプ接続後に半導体チップに反りが生じると、バンプ間の接続部に破断が生じて接続不良(オープン不良)が発生するおそれがある。このため、アンダーフィル樹脂を充填する前の半導体チップ間の接続強度を高めることが求められている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2003−197853号公報

【特許文献2】特開2005−268594号公報

【特許文献3】特開2008−192815号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

本発明が解決しようとする課題は、積層された半導体チップ間をバンプ電極で接続するにあたって、上下の半導体チップ間の隙間を維持しつつ、アンダーフィル樹脂を充填する前の半導体チップ間の接続強度を高めることを可能にした半導体装置とその製造方法を提供することにある。

【課題を解決するための手段】

【0006】

実施形態の半導体装置は、第1の接続領域と、前記第1の接続領域を除く第1の非接続領域とを備える第1の表面を有する第1の半導体チップと、前記第1の接続領域と対向する第2の接続領域と、前記第2の接続領域を除く第2の非接続領域とを備える第2の表面を有し、前記第1の半導体チップ上に積層された第2の半導体チップと、前記第1の半導体チップと前記第2の半導体チップとを電気的に接続するように、前記第1の表面の前記第1の接続領域と前記第2の表面の前記第2の接続領域との間に設けられたバンプ接続部と、前記第1の表面の前記第1の非接続領域および前記第2の表面の前記第2の非接続領域の少なくとも一方の領域に局所的に設けられ、かつ前記第1の非接続領域および前記第2の非接続領域の他方の領域と非接着状態で接触する第1のストッパ用突起と、前記第1の表面の前記第1の非接続領域と前記第2の表面の前記第2の非接続領域との間に局所的に設けられ、前記第1および第2の表面に接着された第1の接着用突起と、前記第1の半導体チップの前記第1の表面と前記第2の半導体チップの前記第2の表面との間の隙間に充填された樹脂とを具備する。

【図面の簡単な説明】

【0007】

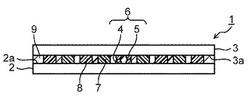

【図1】第1の実施形態による半導体装置を示す断面図である。

【図2】第1の実施形態による半導体装置の第1の製造工程を示す断面図である。

【図3】第1の実施形態の製造工程で用いる第1および第2の半導体チップのバンプ電極形成面の第1の例を示す平面図である。

【図4】図3に示す第1の半導体チップと第2の半導体チップとを組合せた状態を示す平面透視図である。

【図5】半導体チップの厚さと半導体チップ単体の反り量との関係を示す図である。

【図6】第1の実施形態の製造工程で用いる第1および第2の半導体チップのバンプ電極形成面の第2の例を示す平面図である。

【図7】図6に示す第1の半導体チップと第2の半導体チップとを組合せた状態を示す平面透視図である。

【図8】第1の実施形態による半導体装置の第2の製造工程を示す断面図である。

【図9】第2の実施形態による半導体装置を示す断面図である。

【図10】図9に示す半導体装置を用いた半導体パッケージを示す断面図である。

【図11】図10に示す半導体パッケージの第1の変形例を示す断面図である。

【図12】図10に示す半導体パッケージの第2の変形例を示す断面図である。

【図13】図10に示す半導体パッケージの第3の変形例を示す断面図である。

【図14】第2の実施形態による半導体装置の製造工程を示す断面図である。

【図15】第3の実施形態による半導体装置を示す断面図である。

【図16】第3の実施形態による半導体装置の製造工程を示す断面図である。

【図17】第3の実施形態の製造工程で用いる第1および第2の半導体チップのバンプ電極形成面を示す平面図である。

【図18】図17に示す第1の半導体チップと第2の半導体チップとを組合せた状態を示す平面透視図である。

【図19】第3の実施形態による半導体装置の他の例を示す断面図である。

【図20】第4の実施形態の製造工程で用いる第1および第2の半導体チップのバンプ電極形成面の第1の例を示す平面図である。

【図21】図20に示す第1の半導体チップと第2の半導体チップとを組合せた状態を示す平面透視図である。

【図22】第4の実施形態の製造工程で用いる第1および第2の半導体チップのバンプ電極形成面の第2の例を示す平面図である。

【図23】図22に示す第1の半導体チップと第2の半導体チップとを組合せた状態を示す平面透視図である。

【図24】第5の実施形態による半導体装置を示す断面図である。

【図25】第5の実施形態による半導体装置の製造工程を示す断面図である。

【図26】第5の実施形態の製造工程で用いる第1および第2の半導体チップのバンプ電極形成面を示す平面図である。

【発明を実施するための形態】

【0008】

以下、実施形態の半導体装置とその製造方法について、図面を参照して説明する。

【0009】

(第1の実施形態)

第1の実施形態による半導体装置とその製造方法について、図面を参照して説明する。図1は第1の実施形態による半導体装置を示す図、図2、図3および図4は第1の実施形態による半導体装置の製造工程を示す図である。半導体装置1は第1の半導体チップ2と第2の半導体チップ3とを具備している。第1の半導体チップ2の上面(第1の表面)2aは第1の接続領域を有し、第1の接続領域内に第1のバンプ電極4が形成されている。

【0010】

第2の半導体チップ3の下面(第2の表面)3aは、第1の接続領域と対向する第2の接続領域を有し、第2の接続領域内に第2のバンプ電極5が形成されている。第2の半導体チップ3は、第2のバンプ電極5を第1のバンプ電極4と接続しつつ、第1の半導体チップ2上に積層されている。すなわち、第1の半導体チップ2と第2の半導体チップ3とは、第1のバンプ電極4と第2のバンプ電極5との接続体(バンプ接続部)6を介して、電気的および機械的に接続されている。接続領域とは、半導体チップ2、3の表面2a、3aにおけるバンプ電極4、5の形成領域を意味するものである。バンプ電極4、5とは、第1の半導体チップ2と第2の半導体チップ3とを電気的および機械的に接続するバンプ接続部を形成する電極を意味するものである。

【0011】

第1および第2の半導体チップ2、3の両方にバンプ電極4、5を形成する場合、バンプ電極4、5の構成としては半田/半田、Au/半田、半田/Au、Au/Au等の組合せが例示される。バンプ電極4、5を形成する半田としては、SnにCu、Ag、Bi、In等を添加したSn合金を用いたPbフリー半田が例示される。Pbフリー半田の具体例としては、Sn−Cu合金、Sn−Ag合金、Sn−Ag−Cu合金等が挙げられる。バンプ電極4、5を形成する金属はAuに代えて、Cu、Ni、Sn、Pd、Ag等を用いてもよい。これらの金属は単層膜に限らず、複数の金属の積層膜を用いてもよい。バンプ電極4、5の形状としては、半球状や柱状等の突起形状が挙げられるが、パッドのような平坦形状であってもよい。バンプ電極4、5の組合せとしては、突起体同士の組合せ、突起体と平坦体との組合せ等が挙げられる。

【0012】

第1の半導体チップ2の上面2aにおける第1の接続領域を除く領域(第1の非接続領域)、および第2の半導体チップ3の下面3aにおける第2の接続領域を除く領域(第2の非接続領域)の少なくとも一方の領域には、第1の半導体チップ2と第2の半導体チップ3との間の隙間(ギャップ)が、設定したバンプ電極4、5の接続高さ(バンプ接続部6の設定高さ)となるように、ストッパ用突起7が局所的に設けられている。第1の半導体チップ2と第2の半導体チップ3とを圧着した際、それらの隙間(ギャップ)はストッパ用突起7で規定されるため、バンプ接続部6の過度の潰れやバンプ電極4、5間の接続不良(オープン不良)等の発生を抑制することができる。ストッパ用突起7の先端は、第1の非接続領域および第2の非接続領域の他方の領域と非接着状態で接触している。

【0013】

さらに、第1の半導体チップ2の上面2aにおける第1の非接続領域、および第2の半導体チップ3の下面3aにおける第2の非接続領域の少なくとも一方の領域には、第1のバンプ電極4と第2のバンプ電極5とを接続した際に、第1の半導体チップ2と第2の半導体チップ3との接続状態を強化する接着用突起8が局所的に設けられている。第1および第2の非接続領域の少なくとも一方の領域に設けられた接着用突起8は、第1および第2の非接続領域の他方の領域に接着されている。接着用突起8は第1の非接続領域と第2の非接続領域との間に局所的に設けられ、第1の半導体チップ2の上面2aと第2の半導体チップ3の下面3aにそれぞれ接着されている。

【0014】

バンプ接続部6を介して接続された第1の半導体チップ2と第2の半導体チップ3との間の隙間には、アンダーフィル樹脂(樹脂)9が充填されている。第1の半導体チップ2の第1の非接続領域と第2の半導体チップ3の第2の非接続領域との間に接着用突起8を設けることによって、アンダーフィル樹脂9を充填する前の第1の半導体チップ2と第2の半導体チップ3との接続強度を高めることができる。すなわち、第1の半導体チップ2と第2の半導体チップ3とは、アンダーフィル樹脂9を充填する以前に、第1のバンプ電極4と第2のバンプ電極5との接続部6に加えて、接着用突起8により接続されている。従って、アンダーフィル樹脂9を充填する前の接続強度を高めることができる。

【0015】

第1の半導体チップ2に設けられたバンプ電極4と第2の半導体チップ3に設けられたバンプ電極5とは、例えば加熱しながら圧着することにより接続される。半導体チップ2、3の表面には、通常保護膜としてポリイミド樹脂膜のような有機絶縁膜(絶縁膜)が設けられている。半導体チップ2、3を構成するシリコン基板の熱膨張係数は3ppm程度であるのに対し、ポリイミド樹脂の熱膨張係数は35ppm程度と大きい。このため、半導体チップ2、3に反りが生じやすく、特に半導体チップ2、3の厚さが薄くなるほど反り量が大きくなる傾向がある。従って、接着用突起がない場合には、バンプ電極4、5を接続する際に、あるいは接続した後に、半導体チップ2、3の反りでバンプ電極4、5の接続部6が破断することがある。

【0016】

図5に半導体チップの厚さと常温での半導体チップの反り量との関係の一例を示す。ここでは1辺の長さが12mmの半導体チップの単体でのシミュレーションによる反り量を示す。図5に示すように、半導体チップ2、3の厚さが薄くなるほど反り量が大きくなる。半導体チップ2、3に大きな反りが生じると、第1のバンプ電極4と第2のバンプ電極5とを接続したバンプ接続部6が破断するおそれがある。半導体チップ2、3の厚さが100μmの場合の不良発生率は0%、90μmの場合の不良発生率は10%、80μmの場合の不良発生率は30%である。これらに対して、半導体チップ2、3の厚さが70μmになると不良発生率が約100%となる。

【0017】

このような点に対して、第1の半導体チップ2と第2の半導体チップ3とをバンプ接続部6に加えて接着用突起8により接続することによって、第1の半導体チップ2と第2の半導体チップ3との接続強度が向上する。このため、熱圧着あるいはリフロー等によるバンプ接続後(アンダーフィル樹脂9の充填前)の半導体チップ2、3の反りを抑制することができる。従って、半導体チップ2、3の反りによりアンダーフィル樹脂9の充填前に第1のバンプ電極4と第2のバンプ電極5とのバンプ接続部6が破断することを抑制することができる。接続不良(オープン不良)の発生を抑制することが可能となる。

【0018】

半導体チップ2、3の厚さが薄くなるほど、半導体チップ2、3の反りによるバンプ接続部6の破断が発生しやすくなる。実施形態の半導体装置1は、厚さが100μm以下の半導体チップ2、3を用いる場合に有効であり、さらには厚さが70μm以下の半導体チップ2、3を用いる場合により効果的である。さらに、バンプ電極4、5の形成面積が小さい場合に効果的である。従って、半導体装置1は半導体チップ2、3の表面2a、3aに対するバンプ電極4、5の形成面積の比率が5%以下の場合に有効であり、さらに1%以下の場合により効果的である。

【0019】

半導体装置1は、直径が60μm以下のバンプ電極4、5を用いる場合に有効であり、さらに直径が40μm以下のバンプ電極4、5を用いる場合により効果的である。バンプ電極4、5の直径は、接続安定性等を考慮して5μm以上とすることが好ましい。後述する他の実施形態による半導体装置も同様である。第1のバンプ電極4の直径と第2のバンプ電極5の直径とは、ほぼ同一でもよいし、また異なっていてもよい。例えば、第2のバンプ電極5を突起形状とし、第1のバンプ電極4をパッド形状とする場合、第1のバンプ電極4の直径を第2のバンプ電極5のそれより大きくすることによって、第2のバンプ電極5の第1のバンプ電極4に対する接続性を高めることができる。

【0020】

さらに、接着用突起8は半導体チップ2、3間に局所的に設けられているため、第1の半導体チップ2と第2の半導体チップ3との位置合わせ精度や第1のバンプ電極4と第2のバンプ電極5との接続性を高めることができる。例えばNCF(Non Conductive Film)のような接着機能と封止機能とを併せ持つ熱硬化性絶縁樹脂層を半導体チップ間の隙間全体に配置する方法では、第1の半導体チップと第2の半導体チップとを位置合わせする際に、アライメントマークの検出精度が低下する。マイクロバンプの形成ピッチが狭くなるほど、位置合わせ精度をより一層高めることが求められる。半導体装置1では、接着用突起8がアライメントマークを覆わずに局所的に設けられているため、アライメントマークの検出精度を高めることができ、それにより位置合わせ精度を向上させることが可能となる。

【0021】

半導体チップ間の隙間全体に配置された熱硬化性絶縁樹脂層は、第1のバンプ電極と第2のバンプ電極との間に噛み込まれて接続性が低下するおそれがあるのに対し、局所的に設けられた接着用突起8はバンプ電極4、5間に噛み込まれないため、バンプ電極4、5間の接続性を低下させるおそれがない。従って、第1のバンプ電極4と第2のバンプ電極5との接続性を向上させることができる。さらに、半導体チップの隙間全体に配置される熱硬化性絶縁樹脂層がある場合には、半導体チップ間の接続時や接着時に巻き込みボイドを発生しやすい。接続領域に発生したボイドは、バンプ接続部が樹脂で覆われていない状態を生じさせることがあるため、電極間でショートが発生するおそれがある。半導体装置1では、接着用突起8を用いて半導体チップ2、3間の接続強度を高めつつ、バンプ電極4、5間を接続し、その上でアンダーフィル樹脂9を充填している。このため、バンプ接続部6を確実に覆った状態で封止することができる。従って、半導体装置1の信頼性を高めることが可能となる。

【0022】

上述した半導体装置1は、例えば以下のようにして作製される。半導体装置1の製造工程について、図2、図3および図4を参照して説明する。図2(a)に示すように、第1のバンプ電極4を有する第1の半導体チップ2と第2のバンプ電極5を有する第2の半導体チップ3とを用意する。図2(a)において、ストッパ用突起7は第2の半導体チップ3の下面3aにおける第2の非接続領域に形成されている。接着用突起8は第1の半導体チップ2の上面2aにおける第1の非接続領域に形成されている。ストッパ用突起7および接着用突起8は第1および第2の非接続領域の少なくとも一方に形成されていればよく、例えば両方の領域に形成されていてもよい。

【0023】

ストッパ用突起7は、例えばポリイミド樹脂、フェノール樹脂、エポキシ樹脂、ベンゾシクロブテン樹脂を用いることが好ましい。接着用突起8は、例えばエポキシ樹脂、ポリイミド樹脂、アクリル樹脂、フェノール樹脂等を用いた熱硬化性樹脂で形成することが好ましい。ストッパ用突起7や接着用突起8は、リソグラフィ技術やディスペンサによる塗布技術を適用して形成したり、フィルムの接着により形成することができる。液状の熱硬化性樹脂組成物を塗布して接着用突起8を形成する場合、半導体チップ2、3を接着する前に半硬化状態としておくことが好ましい。あるいは、速硬化型の材料を用いて、半導体チップ2、3の接着、接続時の時間を短縮することが好ましい。

【0024】

図3にストッパ用突起7および接着用突起8の配置例を示す。図3(a)は第1の半導体チップ2の上面(バンプ電極形成面)2aを示している。図3(b)は第2の半導体チップ3の下面(バンプ電極形成面)3aを示している。バンプ電極4、5はそれぞれ半導体チップ2、3の表面2a、3aの中央付近に配置されており、ストッパ用突起7はその周囲を含めて第2の半導体チップ3の表面全体に配置されている。接着用突起8はストッパ用突起7の間等に配置されている。図4に第1の半導体チップ2と第2の半導体チップ3とを組合せた状態におけるストッパ用突起7と接着用突起8の配置を示す。

【0025】

図3は直径が20〜1000μm程度のストッパ用突起7と同様な形状を有する接着用突起8を示しているが、ストッパ用突起7および接着用突起8のサイズと形状はこれに限られるものではない。接着用突起8を液状樹脂の塗布やフィルムの接着等により形成する場合、ある程度の面積を有していることが好ましい。図6(b)に示すように、ストッパ用突起7を配置する際に、第2の半導体チップ3の表面全体に配置するのではなく、一部に空白領域(ストッパ用突起7の未配置領域)を形成する。図6(a)に示すように、ストッパ用突起7の未配置領域に対応させた領域に接着用突起8を配置する。図7にストッパ用突起7と接着用突起8とを組合せた配置を示す。このような配置を適用することで、液状樹脂の塗布やフィルムの接着等による接着用突起8の形成性が向上する。図6および図7はバンプ電極4、5を半導体チップ2、3の四隅にも配置した構造を示している。

【0026】

第1の半導体チップ2と第2の半導体チップ3との第1の接続方法について述べる。図2(a)に示すように、ステージ11上に載置され、かつ吸着保持された第1の半導体チップ2上に、ボンディングヘッド12に吸着保持された第2の半導体チップ3を配置する。図示を省略したカメラ等で第1および第2の半導体チップ2、3のアライメントマークを検出して、第2の半導体チップ3を第1の半導体チップ2上に対して位置合わせする。次いで、図2(b)に示すように、ストッパ用突起7で半導体チップ2、3間の隙間を維持しつつ、第1の半導体チップ2と第2の半導体チップ3とを、バンプ電極4、5の接続温度以上で、かつ接着用突起8を構成する熱硬化性樹脂が硬化する温度以上の温度で圧着する。

【0027】

このような熱圧着工程によって、第1のバンプ電極4と第2のバンプ電極5とを接続すると共に、接着用突起8を第1および第2の半導体チップ2、3の表面2a、3aに接着させる。バンプ電極4、5の接続温度とは、バンプ電極4、5の少なくとも一方を半田で形成した場合、半田の融点以上の温度である。第1の接続方法において、接着用突起8を構成する熱硬化性樹脂が硬化する温度と時間以上で接着用突起8をキュアする工程や、バンプ電極4、5の接続温度以上の温度でバンプ電極4、5を圧着またはリフローする工程を補助的に実施してもよい。

【0028】

第1の半導体チップ2と第2の半導体チップ3との第2の接続方法について述べる。第1の方法と同様に、第1の半導体チップ2と第2の半導体チップ3とを位置合わせする。第1の半導体チップ2と第2の半導体チップ3とを、バンプ電極4、5の接続温度未満で、かつ接着用突起8を構成する熱硬化性樹脂が接着性を発現して硬化し始める温度および時間以上で圧着して、第1のバンプ電極4と第2のバンプ電極5とを仮固定する。接着用突起8を構成する熱硬化性樹脂が硬化する温度と時間以上で接着用突起8を熱処理することによって、接着用突起8をキュアする。バンプ電極4、5の接続温度以上の温度で圧着またはリフローすることで、第1のバンプ電極4と第2のバンプ電極5とを接続する。

【0029】

第2の接続方法において、第1のバンプ電極4と第2のバンプ電極5との仮固定を、接着用突起8を構成する熱硬化性樹脂が硬化する温度と時間以上で実施することによって、バンプ電極4、5の仮固定と同時に接着用突起8を硬化させてもよい。あるいは、第1のバンプ電極4と第2のバンプ電極5との接続を、接着用突起8を構成する熱硬化性樹脂が硬化する温度と時間以上で実施することで、バンプ電極4、5の接続と同時に接着用突起8を硬化させてもよい。これらの場合、接着用突起8のキュア工程を省略してもよい。

【0030】

第1の接続方法または第2の接続方法で第1の半導体チップ2と第2の半導体チップ3とを接続した後、図2(c)に示すように、第1の半導体チップ2と第2の半導体チップ3との間の隙間にアンダーフィル樹脂9を充填して硬化させることによって、半導体装置1が製造される。ここでは図示を省略したが、半導体装置1は外部接続端子を有する配線基板やリードフレーム等の回路基材上に搭載されてSiP構造の半導体装置等として使用される。半導体装置1と回路基材との接続は、フリップチップボンディングやワイヤボンディング等により実施される。

【0031】

上述したように、アンダーフィル樹脂9を充填する前の段階において、第1の半導体チップ2と第2の半導体チップ3とがバンプ接続部6に加えて接着用突起8により接続されているため、熱圧着もしくはリフロー後の半導体チップ2、3の反りを抑制することができる。従って、半導体チップ2、3の反りによって、アンダーフィル樹脂9の充填前に第1のバンプ電極4と第2のバンプ電極5との接続部が破断することを抑制することができる。よって、バンプ電極4、5間の接続不良(オープン不良)の発生が抑制される。

【0032】

図8は半導体装置1の第2の製造工程を示している。図8(a)に示すように、ストッパ用突起7の高さhは第1のバンプ電極4の高さH1と第2のバンプ電極5の高さH2との合計高さ(H1+H2)より低いことが好ましい。このような条件(h<H1+H2)を満足させることによって、第1のバンプ電極4と第2のバンプ電極5とをより確実に接続することができる。図8(b)に示すように、第2のバンプ電極5を第1のバンプ電極4に接触させる。この段階では、ストッパ用突起7は第1の半導体チップ2の表面に接触していない。さらに、図8(c)に示すように、ストッパ用突起7が第1の半導体チップ2の表面に接触するまで、例えば第2のバンプ電極5を変形させる。

【0033】

第2のバンプ電極5を変形させる工程は、第1のバンプ電極4と第2のバンプ電極5とが接続する温度で圧着する工程であってもよいし、あるいは接着用突起8を構成する熱硬化性樹脂が接着性を発現して硬化し始める温度および時間以上で第1のバンプ電極4と第2のバンプ電極5とを仮固定する工程であってもよい。他の工程は第1の製造工程と同様に実施される。上述した条件(h<H1+H2)を満足させることで、ストッパ用突起7により維持される間隔が広くなりすぎて、第1のバンプ電極4と第2のバンプ電極5との接続が不十分になる(バンプ電極4、5の接触状態が不十分になる)ことが防止される。

【0034】

(第2の実施形態)

第2の実施形態による半導体装置について説明する。図9は第2の実施形態の半導体装置を示す図である。第1の実施形態と同一部分については、同一符号を付して一部説明を省略する場合がある。図9に示す半導体装置20は、第1の半導体チップ21と第2の半導体チップ22と第3の半導体チップ23とを積層した構造を有している。ここでは第1ないし第3の半導体チップ21、22、23を積層した半導体装置20について述べるが、半導体チップの積層数は4層以上であってもよい。第3の半導体チップ23の積層工程を繰り返すことで、必要数の半導体チップを積層した半導体装置を得ることができる。

【0035】

第1の半導体チップ21の上面(第1の表面)は第1の接続領域を有し、第1の接続領域内に第1のバンプ電極4が形成されている。第2の半導体チップ22の下面(第2の表面)は第2の接続領域を有し、第2の接続領域内に第2のバンプ電極5が形成されている。第2の半導体チップ22は、第2のバンプ電極5を第1のバンプ電極4と接続しつつ、第1の半導体チップ21上に積層されている。第1の半導体チップ21と第2の半導体チップ22とは、第1の実施形態と同様に、第1のバンプ接続部6Aを介して電気的および機械的に接続されている。

【0036】

第2の半導体チップ22上に第3の半導体チップ23が積層されるため、第2の半導体チップ22の上面(第3の表面)は第3の接続領域を有し、第3の接続領域内に第3のバンプ電極24が設けられている。第2のバンプ電極5と第3のバンプ電極24とは、第2の半導体チップ22内に設けられた貫通電極(Through Silicon Via:TSV)25Aを介して電気的に接続されている。第3の半導体チップ23の下面(第4の表面)は第4の接続領域を有し、第4の接続領域内に第4のバンプ電極26が形成されている。第2の半導体チップ22と第3の半導体チップ23とは、第2のバンプ接続部6Bを介して電気的および機械的に接続されている。第4のバンプ電極26は、第3の半導体チップ23の上面に設けられた電極27と貫通電極(TSV)25Bを介して電気的に接続されている。

【0037】

第1の半導体チップ21の上面における第1の非接続領域、および第2の半導体チップ22の下面における第2の非接続領域の少なくとも一方の領域には、第1のストッパ用突起7Aおよび第1の接着用突起8Aがそれぞれ局所的に設けられている。ストッパ用突起7Aの先端は、第1および第2の非接続領域の他方の領域と非接着状態で接触している。第1および第2の非接続領域の少なくとも一方の領域に局所的に設けられた接着用突起8Aは、第1および第2の非接続領域の他方の領域に接着されており、第1の半導体チップ21の上面と第2の半導体チップ22の下面とを接着している。

【0038】

同様に、第2の半導体チップ22の上面における第3の非接続領域、および第3の半導体チップ23の下面における第4の非接続領域の少なくとも一方の領域には、第2のストッパ用突起7Bおよび第2の接着用突起8Bがそれぞれ局所的に設けられている。ストッパ用突起7Bの先端は、第3および第4の非接続領域の他方の領域と非接着状態で接触している。第3および第4の非接続領域の少なくとも一方の領域に設けられた接着用突起8Bは、第3および第4の非接続領域の他方の領域に接着されている。接着用突起8Bは第3の非接続領域と第4の非接続領域との間に局所的に設けられ、第2の半導体チップ22の上面と第3の半導体チップ23の下面にそれぞれ接着されている。

【0039】

上述したように、3個の半導体チップ21、22、23、もしくはそれ以上の半導体チップを積層する場合においても、アンダーフィル樹脂9の充填前の半導体チップ間の接続強度を接着用突起8A、8Bで高めることによって、熱圧着もしくはリフロー後における半導体チップの反りを抑制することができる。従って、第1および第2のバンプ電極4、5間と第3および第4のバンプ電極24、26間の接続不良(オープン不良)を抑制することが可能となる。ストッパ用突起7A、7Bおよび接着用突起8A、8Bの形成材料、形成箇所、配置形状等については、第1の実施形態と同様である。

【0040】

第2の実施形態の半導体装置20は、例えば図10に示すような半導体パッケージ30として使用される。図10に示す半導体パッケージ30において、半導体装置20は外部接続端子31と内部接続端子32とを有する配線基板33上に搭載されている。配線基板33の内部接続端子32は、半導体装置20の最上段の半導体チップ23の上面に形成された再配線層34とボンディングワイヤ35とを介して、半導体装置20と電気的に接続されている。配線基板33上には、半導体装置20をボンディングワイヤ35等と共に封止する樹脂封止層36が形成されている。

【0041】

半導体装置20と配線基板33と電気的な接続は、フリップチップボンディングにより実施してもよい。図11は半導体装置20と配線基板32とをフリップチップボンディングした状態を示している。半導体装置20をフリップチップボンディングするため、第1の半導体チップ21の下面には第5のバンプ電極28が設けられている。第5のバンプ電極28と第1のバンプ電極4とは、第1の半導体チップ21内に設けられた貫通電極(TSV)25Cを介して電気的に接続されている。第1の半導体チップ21は、基板33上に実装されている。基板33と第1の半導体チップ21とは、基板33の内部接続端子32上に設けられた第6のバンプ電極29と第5のバンプ電極28との接続体(バンプ接続部)6Cを介して電気的および機械的に接続されている。

【0042】

第1の半導体チップ21の下面における非接続領域、および基板33の表面の少なくとも一方の領域には、第3のストッパ用突起7Cおよび第3の接着用突起8Cがそれぞれ局所的に設けられている。ストッパ用突起7Cの先端は、第1の半導体チップ21の下面における非接続領域および基板33の表面の他方の領域と非接着状態で接触している。第1の半導体チップ21の下面における非接続領域および基板33の表面の少なくとも一方の領域に設けられた接着用突起8Cは、第1の半導体チップ21の下面における非接続領域および基板33の表面の他方の領域に接着されている。

【0043】

図12は図10に示す半導体パッケージ30の変形例を示している。半導体装置20を構成する半導体チップ21〜23がNAND型フラッシュメモリのようなメモリチップである場合、半導体装置20上にはコントローラチップやインタフェースチップのような外部デバイスとの間でデータ通信を行う半導体チップ37が搭載されていてもよい。半導体チップ37は半田バンプ38を介して半導体装置20と接続されている。半導体装置20は、半導体チップ37やボンディングワイヤ35等を介して配線基板33と電気的に接続されている。図13に示すように、半導体装置20は積層順の最上段(紙面最下段)に位置する半導体チップ37に設けられた半田バンプ39を介して、配線基板33と電気的および機械的に接続されていてもよい。

【0044】

第2の実施形態による半導体装置20の製造工程について、図14を参照して説明する。図14はステージ11とボンディングヘッド12の図示を省略したが、基本的には第1の実施形態と同様にして積層工程が実施される。

【0045】

第1の半導体チップ21と第2の半導体チップ22と第3の半導体チップ23との第1の接続方法について述べる。図14(a)に示すように、第1のバンプ電極4と第1の接着用突起8Aとを有する第1の半導体チップ21と、第2のバンプ電極5と第1のストッパ用突起7Aとを有する第2の半導体チップ22とを位置合わせする。図14(b)に示すように、第1の半導体チップ21と第2の半導体チップ22とを、バンプ電極4、5の接続温度以上で、かつ接着用突起8Aを構成する熱硬化性樹脂が硬化する温度以上の温度で圧着することによって、第1および第2のバンプ電極4、5を接続する。

【0046】

図14(c)に示すように、第2の半導体チップ22の上面における第3の非接続領域に第2の接着用突起8Bを形成する。第2の接着用突起8Bは、ディスペンサによる塗布やフィルムの接着等により形成することが好ましい。図14(d)に示すように、第4のバンプ電極26と第2のストッパ用突起7Bとを有する第3の半導体チップ23を、第2の半導体チップ22に対して位置合わせする。図14(e)に示すように、第2の半導体チップ22と第3の半導体チップ23とを、バンプ電極24、26の接続温度以上で、かつ接着用突起8Bを構成する熱硬化性樹脂が硬化する温度以上の温度で圧着することによって、第3および第4のバンプ電極24、26を接続する。

【0047】

第1の接続方法において、接着用突起を構成する熱硬化性樹脂が硬化する温度と時間以上で接着用突起をキュアする工程や、バンプ電極の接続温度以上の温度でバンプ電極を圧着またはリフローする工程を補助的に実施してもよい。

【0048】

第1の半導体チップ21と第2の半導体チップ22と第3の半導体チップ23との第2の接続方法について述べる。第1のバンプ電極4と第1の接着用突起8Aとを有する第1の半導体チップ21と、第2のバンプ電極5と第1のストッパ用突起7Aとを有する第2の半導体チップ22とを位置合わせする。接着用突起8Aを構成する熱硬化性樹脂が接着性を発現して硬化し始める温度および時間以上で、第1のバンプ電極4と第2のバンプ電極5とを仮固定する。

【0049】

第2の半導体チップ22の上面における第3の非接続領域に第2の接着用突起8Bを形成する。第4のバンプ電極26と第2のストッパ用突起7Bとを有する第3の半導体チップ23を、第2の半導体チップ22に対して位置合わせする。接着用突起8Bを構成する熱硬化性樹脂が接着性を発現して硬化し始める温度および時間以上で、第3のバンプ電極24と第4のバンプ電極26とを仮固定する。

【0050】

第1ないし第3の半導体チップ21、22、23の積層体をオーブン内に配置し、接着用突起8A、8Bを構成する熱硬化性樹脂が硬化する温度と時間以上で加熱する。接着用突起8A、8Bを硬化させることで、第1の半導体チップ21と第2の半導体チップ22との間を接着用突起8Aで接着し、かつ第2の半導体チップ22と第3の半導体チップ23との間を接着用突起8Bで接着する。半導体チップ間を接着用突起8A、8Bで接着したチップ積層体を、バンプ電極の接続温度以上の温度で圧着またはリフローする。

【0051】

圧着工程は、接着用突起8A、8Bを硬化させたチップ積層体を加熱しつつ圧着することにより実施される。リフロー工程を適用する場合には、半導体チップ間を接着用突起8A、8Bで接着したチップ積層体をリフロー炉内に配置する。リフロー炉内を還元雰囲気とした状態で、バンプ電極の接続温度以上の温度に加熱することによって、第1のバンプ電極4と第2のバンプ電極5とを接続すると共に、第3のバンプ電極24と第4のバンプ電極26とを接続する。リフロー工程は還元雰囲気中で実施することが好ましい。これによって、バンプ電極の表面酸化膜を除去しつつ、バンプ接続部を得ることができる。

【0052】

第2の接続方法において、接着用突起8A、8Bのキュア処理は、バンプ電極の仮固定と同時に実施してもよい。この場合には、バンプ電極の仮固定を接着用突起8A、8Bを構成する熱硬化性樹脂が硬化する温度と時間以上で実施する。あるいは、接着用突起8A、8Bのキュア処理は、バンプ電極の接続と同時に実施してもよい。この場合には、バンプ電極の接続を接着用突起8A、8Bを構成する熱硬化性樹脂が硬化する温度と時間以上で実施する。接着用突起8A、8Bの硬化反応が不十分であると、接着用突起8A、8Bと半導体チップ21、22、23との接着が不十分であるために剥がれが生じ、バンプ接続部6が破断して接続不良が発生するおそれがある。従って、接着性が維持される範囲で、接着用突起8A、8Bを十分に硬化させることが好ましい。

【0053】

第1の半導体チップ21と第2の半導体チップ22と第3の半導体チップ23との第3の接続方法について述べる。第2の接続方法と同様に、第1のバンプ電極4と第2のバンプ電極5とを仮固定する。第2の半導体チップ22の上面における第3の非接続領域に第2の接着用突起8Bを形成する。第4のバンプ電極26と第2のストッパ用突起7Bとを有する第3の半導体チップ23を、第2の半導体チップ22に対して位置合わせする。第2の半導体チップ22と第3の半導体チップ23とを、バンプ電極24、26の接続温度以上で、かつ接着用突起8Bを構成する熱硬化性樹脂が硬化する温度と時間以上で圧着することによって、第3および第4のバンプ電極24、26を接続する。

【0054】

このように、最上段の半導体チップ23はバンプ電極の接続温度以上の温度に加熱しつつ圧着することが好ましい。それ以外の半導体チップ21、22はバンプ電極の接続温度未満の温度に加熱しつつ圧着する。これによって、チップ積層体の強度が向上する。全ての半導体チップ21、22、23をバンプ電極の接続温度以上の温度で圧着すると、半導体チップ21、22、23に対する熱負荷が増大する。最上段の半導体チップ23のみをバンプ電極の接続温度以上の温度に加熱しつつ圧着することで、半導体チップ21、22、23に対する熱負荷を低減しつつ、チップ積層体の強度を高めることができる。

【0055】

最上段の半導体チップ23をバンプ電極の接続温度以上の温度で熱圧着することによって、第1のバンプ電極4と第2のバンプ電極5、および第3のバンプ電極24と第4のバンプ電極26間とが接続される。第3の接続方法において、接着用突起8A、8Bをキュア処理する工程や、チップ積層体の圧着またはリフローする工程を、補助的に実施してもよい。図12に示す半導体パッケージのように、第1ないし第3の半導体チップ21、22、23と最上段の半導体チップ37とのサイズが異なる場合や、バンプ電極の配列が異なる場合には、第3の半導体チップ23および最上段の半導体チップ37を、それぞれバンプ電極の接続温度以上の温度に加熱しつつ圧着することが好ましい。それ以外の半導体チップ21、22はバンプ電極の接続温度未満の温度に加熱しつつ圧着する。

【0056】

第1、第2、または第3の接続方法で第1ないし第3の半導体チップ21、22、23を接続した後、図14(f)に示すように、第1の半導体チップ21と第2の半導体チップ22との隙間、および第2の半導体チップ22と第3の半導体チップ23との隙間に、それぞれアンダーフィル樹脂9を充填して硬化させる。このようにして、第2の実施形態による半導体装置20が製造される。3個もしくはそれ以上の半導体チップを積層する場合においても、アンダーフィル樹脂9の充填前の半導体チップ間の接続強度を接着用突起8A、8Bで高めることで、熱圧着もしくはリフロー後における半導体チップの反りを抑制することができる。従って、第1および第2のバンプ電極4、5間、第3および第4のバンプ電極24、26間の接続不良(オープン不良)を抑制することが可能となる。

【0057】

(第3の実施形態)

第3の実施形態による半導体装置の構成と製造工程について、図15および図16を参照して説明する。第3の実施形態による半導体装置40は、第1および第2の実施形態におけるストッパ用突起7および接着用突起8に代えて、ストッパ兼接着用突起41を有している。第1および第2の実施形態と同一部分については、同一符号を付して一部説明を省略する場合がある

【0058】

図15に示す半導体装置40は、ストッパ兼接着用突起41と第1のバンプ電極4とを有する第1の半導体チップ2と、第2のバンプ電極5を有する第2の半導体チップ3とを備えている。第1の半導体チップ2と第2の半導体チップ3とは、第1のバンプ電極4と第2のバンプ電極5との接続体(バンプ接続部6)を介して、電気的および機械的に接続されている。ストッパ兼接着用突起41は、第1の半導体チップ2の上面(第1の表面)2aにおける非接続領域に局所的に設けられており、第1の半導体チップ2の上面2aと第2の半導体チップ3の下面3aにそれぞれ接着されている。第1の半導体チップ2と第2の半導体チップ3との間の隙間には、アンダーフィル樹脂9が充填されている。

【0059】

第1の半導体チップ2の上面2aに設けられたストッパ兼接着用突起41は、第1の半導体チップ2と第2の半導体チップ3とを圧着した際に、それらの隙間(ギャップ)を保持し、かつ加熱した際に第2の半導体チップ3の下面3aに接着されるものである。従って、ストッパ用突起7と接着用突起8とを用いた第1の実施形態と同様に、圧着時における第1の半導体チップ2と第2の半導体チップ3との間の隙間(ギャップ)を維持しつつ、アンダーフィル樹脂9を充填する前の第1の半導体チップ2と第2の半導体チップ3との接続強度を高めることができる。これらによって、バンプ電極4、5間の接続信頼性を向上させることが可能となる。

【0060】

ストッパ兼接着用突起41は、例えば感光性および熱硬化性を有する樹脂を用いて形成される。感光性および熱硬化性樹脂の具体例としては、感光性接着剤樹脂のような感光剤を含有する熱硬化性樹脂が挙げられる。感光性および熱硬化性樹脂によれば、突起41の形成段階においては、紫外線等の照射により硬化するため、ストッパとして機能させることができる。さらに、加熱時には熱硬化するため、第1および第2の半導体チップ2、3の表面と強固に接着し、接着剤(接着用突起)として機能する。ストッパ兼接着用突起41は、感光性および熱硬化性を有する樹脂で形成したものに限らす、例えば耐熱樹脂製突起の先端に接着剤層を形成したものであってもよい。これによっても、同様なストッパ機能と接着機能とを得ることができる。ストッパ兼接着用突起41は、第2の半導体チップ3の下面3aに設けてもよい。

【0061】

第3の実施形態の半導体装置40は、例えば以下のようにして作製される。図16(a)に示すように、第1のバンプ電極4とストッパ兼接着用突起41とを有する第1の半導体チップ2と、第2のバンプ電極5を有する第2の半導体チップ3とを用意する。図17および図18にストッパ兼接着用突起41の配置例を示す。図17(a)は第1の半導体チップ2の上面(バンプ電極形成面)2aを示している。図17(b)は第2の半導体チップ3の下面(バンプ電極形成面)3aを示している。図18は第1の半導体チップ2と第2の半導体チップ3とを組合せた状態を示している。ストッパ兼接着用突起41は、半導体チップ2の中央付近に存在するバンプ電極4の周囲を含めて、第1の半導体チップ2の表面全体に配置されている。

【0062】

次に、第1の実施形態と同様に、第1の半導体チップ2と第2の半導体チップ3とを位置合わせする。図16(b)に示すように、ストッパ兼接着用突起41で隙間を維持しつつ、第1の半導体チップ2と第2の半導体チップ3とを熱圧着する。このような熱圧着工程によって、第1のバンプ電極4と第2のバンプ電極5とを接続すると共に、ストッパ兼接着用突起41を第1および第2の半導体チップ2、3の表面2a、3aに接着する。第1の半導体チップ2と第2の半導体チップ3との接続工程は、第1の実施形態における第1または第2の接続方法と同様に実施される。

【0063】

この後、図16(c)に示すように、第1の半導体チップ2と第2の半導体チップ3との間の隙間にアンダーフィル樹脂9を充填して硬化させることによって、半導体装置40が製造される。アンダーフィル樹脂9を充填する前の段階において、第1の半導体チップ2と第2の半導体チップ3とがバンプ接続部6に加えて、ストッパ兼接着用突起41により接続されているため、熱圧着もしくはリフロー後における半導体チップ2、3の反りを抑制することができる。従って、半導体チップ2、3の反りによって、アンダーフィル樹脂9の充填前に第1のバンプ電極4と第2のバンプ電極5との接続部が破断することによる接続不良(オープン不良)の発生を抑制することが可能となる。

【0064】

3個以上の半導体チップを積層する場合には、半導体チップの積層工程を繰り返し実施すればよい。図19は3個の半導体チップ21、22、23を積層して構成した半導体装置42を示している。半導体装置42は、第2の実施形態における第1、第2、または第3の接続方法と同様な方法を適用することにより作製される。半導体チップ21、22、23を、第2の実施形態における第1、第2、または第3の接続方法と同様にして接続する。ストッパ兼接着用突起41は、積層する際に上側に位置する半導体チップ(22、23)の下面に形成されていることが好ましい。この後、第1の半導体チップ21と第2の半導体チップ22との隙間、および第2の半導体チップ22と第3の半導体チップ23との隙間に、それぞれアンダーフィル樹脂9を充填して硬化させる。

【0065】

(第4の実施形態)

第4の実施形態による半導体装置の構成について、図20、図21、図22および図23を参照して説明する。第4の実施形態による半導体装置は、第1および第2の実施形態における接着用突起8、または第3の実施形態におけるストッパ兼接着用突起41に、アンダーフィル樹脂のはみ出し抑制機能を持たせたものである。なお、それら以外の構成については、第1ないし第3の実施形態と同一であるため、ここでは説明を省略する。

【0066】

図20はアンダーフィル樹脂のはみ出し抑制機能を有する接着用突起8の配置例を示している。図20(a)は第1の半導体チップ2の上面2aを示している。図20(b)は第2の半導体チップ3の下面3aを示している。図21は第1の半導体チップ2と第2の半導体チップ3とを組合せた状態を示している。接着用突起8は、半導体チップ2の対向する2つの外形辺に沿って、半導体チップ2の外周領域に設けられている。このような接着用突起8によれば、アンダーフィル樹脂の注入辺とそれと対向する辺以外からのアンダーフィル樹脂のはみ出しを抑制することができる。

【0067】

図22はアンダーフィル樹脂のはみ出し抑制機能を有するストッパ兼接着用突起41の配置例を示している。図22(a)は第1の半導体チップ2の上面2aを示している。図22(b)は第2の半導体チップ3の下面3aを示している。図23は第1の半導体チップ2と第2の半導体チップ3とを組合せた状態を示している。ストッパ兼接着用突起41は、半導体チップ2の外周領域とバンプ電極4の周囲に設けられている。半導体チップ2の外周領域において、ストッパ兼接着用突起41はアンダーフィル樹脂の注入辺を除く外形辺に沿って配置されている。このようなストッパ兼接着用突起41によれば、アンダーフィル樹脂の注入辺以外からのアンダーフィル樹脂のはみ出しが抑制される。

【0068】

半導体チップ2の3つの外形辺に沿ってストッパ兼接着用突起41を配置する場合、アンダーフィル樹脂の充填は、例えば減圧下で充填した後に大気圧に開放する方法、樹脂を充填した後に加圧下でキュアする方法により実施することが有効である。これらの方法は充填時に発生したボイドを差圧で押し潰す方法である。特に、ストッパ兼接着用突起41を図22(a)に示すように配置する場合に、圧力が効率よく加わり、ボイドを効果的に押し潰すことができる。図20および図21に示す接着用突起8の配置をストッパ兼接着用突起41に適用してもよい。図22および図23に示すストッパ兼接着用突起41の配置を接着用突起8に適用してもよい。

【0069】

(第5の実施形態)

第5の実施形態による半導体装置の構成と製造工程について、図24、図25および図26を参照して説明する。第5の実施形態による半導体装置50は、ストッパ用突起7および接着用突起8の接触面、もしくはストッパ兼接着用突起41の接触面に設けられた有機絶縁膜(絶縁膜)51を備えている。それ以外の構成は、基本的には第1ないし第3の実施形態と同一である。第1ないし第3の実施形態と同一部分については、同一符号を付して一部説明を省略する場合がある。ここではストッパ兼接着用突起41を用いた半導体装置50について主として説明するが、ストッパ用突起7および接着用突起8を適用する場合も同様である。

【0070】

図24に示す半導体装置50は、第1のバンプ電極4を有する第1の半導体チップ2と、第2のバンプ電極5とストッパ兼接着用突起41とを有する第2の半導体チップ3とを備えている。第1の半導体チップ2と第2の半導体チップ3とは、第1のバンプ電極4と第2のバンプ電極5とのバンプ接続部6を介して、電気的および機械的に接続されている。ストッパ兼接着用突起41は、第2の半導体チップ3の下面3aにおける非接続領域に局所的に設けられており、第1の半導体チップ2に接着されている。第1の半導体チップ2と第2の半導体チップ3との間にはアンダーフィル樹脂9が充填されている。

【0071】

第1の半導体チップ2の上面2aには第1のバンプ電極4に加えて、Al配線膜等を用いた表面配線52が形成されている場合がある。表面配線52は所望のパターンに応じて形成されているため、表面配線52が存在する部分と存在しない部分とがある。表面配線52の有無によって、第1の半導体チップ2の上面2aには1〜2μm程度の凹凸が生じている。表面配線52が存在していない部分に配置されたストッパ兼接着用突起41と第1の半導体チップ2の上面2aと間には隙間が生じ、ストッパや接着剤として機能させることができない。そこで、第5の実施形態の半導体装置50においては、第1の半導体チップ2の上面2aにおける非接続領域を有機絶縁膜51で覆っている。

【0072】

第1の半導体チップ2の上面2aにおける非接続領域を有機絶縁膜51で覆うことによって、ストッパ兼接着用突起41の接触高さが均一になり、全てのストッパ兼接着用突起41をストッパおよび接着剤として良好に機能させることができる。有機絶縁膜51には、ポリイミド系樹脂やフェノール系樹脂等の熱硬化性樹脂が適用される。有機絶縁膜51は、さらにキュア温度が250℃以下の熱硬化性樹脂、例えば低温キュアのポリイミド系樹脂やフェノール系樹脂が好ましい。有機絶縁膜51は、例えばスピンコートによる塗布工程とリソグラフィ工程と現像工程とにより形成される。

【0073】

有機絶縁膜51はストッパ兼接着用突起41の接着面に形成される。図24に示す半導体装置50において、ストッパ兼接着用突起41は予め第2の半導体チップ3の下面3aに設けられているため、有機絶縁膜51は第1の半導体チップ2の上面2aの非接続領域に設けられる。ストッパ兼接着用突起41を第1の半導体チップ2の上面2aに設ける場合、有機絶縁膜51は第2の半導体チップ3の下面3aの非接続領域に設けられる。ストッパ兼接着用突起41に代えて、ストッパ用突起7および接着用突起8を適用する場合も同様である。有機絶縁膜51は、ストッパ用突起7や接着用突起8が形成されたチップ面と対向する半導体チップの面の非接続領域に設けられる。

【0074】

有機絶縁膜51は、ストッパ兼接着用突起41の接触面の高さを均一にする、言い換えると接触面を平坦化する効果に加えて、ストッパ兼接着用突起41の接着信頼性を向上させる効果を有する。ストッパ兼接着用突起41は、例えば80〜200ppm/℃程度の線膨張係数を有するのに対し、半導体チップ2の表面に設けられた無機絶縁膜の線膨張係数は、例えば0.1〜10ppm/℃程度である。このため、有機絶縁膜51を形成しない場合には、ストッパ兼接着用突起41と無機絶縁膜との熱膨張差により剥離が生じやすくなる。これに対して、有機絶縁膜51の線膨張係数は、例えば40〜70ppm/℃程度であるため、ストッパ兼接着用突起41との熱膨張差が低減される。従って、ストッパ兼接着用突起41の剥離を抑制することができる。

【0075】

上記したように有機絶縁膜51を設けると、その膜厚の分だけストッパ兼接着用突起41の高さを減少させることできる。周囲の環境等により熱変化が生じた場合に、ストッパ兼接着用突起41の高さ方向の変動が減少するため、ストッパ兼接着用突起41の接着信頼性が向上する。ストッパ兼接着用突起41の高さを低減するために、有機絶縁膜51はストッパ兼接着用突起41の接着面(第1の半導体チップ2の上面2a)に加えて、ストッパ兼接着用突起41の形成面(第2の半導体チップ3の下面3a)に形成することも有効である。ストッパ兼接着用突起41に代えて、ストッパ用突起7および接着用突起8を適用する場合も同様である。

【0076】

第5の実施形態の半導体装置50は、例えば以下のようにして作製される。図25(a)に示すように、第1のバンプ電極4を有する第1の半導体チップ2と、第2のバンプ電極5とストッパ兼接着用突起41とを有する第2の半導体チップ3とを用意する。図26にストッパ兼接着用突起41および有機絶縁膜51の形成例を示す。図26(a)は第1の半導体チップ2の上面2aを示している。図26(b)は第2の半導体チップ3の下面3aを示している。有機絶縁膜51は、第1の半導体チップ2の上面2aの非接続領域、すなわちバンプ電極4の形成位置を除く領域全体に形成されている。

【0077】

第1の半導体チップ2と第2の半導体チップ3とを位置合わせした後、図25(b)に示すように、第1のバンプ電極4と第2のバンプ電極5とを接触させ、さらにストッパ兼接着用突起41Aが有機絶縁膜51に接触するまでバンプ電極4、5を変形させる。第1の実施形態における第1または第2の接続方法と同様にして、第1の半導体チップ2と第2の半導体チップ3とを接続する。この後、前述した第3の実施形態と同様に、第1の半導体チップ2と第2の半導体チップ3との間の隙間にアンダーフィル樹脂9を充填して硬化させることによって、半導体装置50が製造される。

【0078】

ここでは2個の半導体チップ2、3を積層する場合について説明したが、3個またはそれ以上の半導体チップを積層する場合も同様である。3個またはそれ以上の半導体チップを積層する場合の構成は、第2および第3の実施形態に示した通りである。ストッパ兼接着用突起41に代えて、ストッパ用突起7および接着用突起8を適用する場合の構成は、第1および第2の実施形態に示した通りである。

【0079】

なお、第1ないし第5の実施形態の構成は、それぞれ組合せて適用することができ、また一部置き換えることも可能である。本発明のいくつかの実施形態を説明したが、これらの実施形態は例として提示したものであり、発明の範囲を限定することは意図していない。これら実施形態は、その他の様々な形態で実施し得るものであり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれると同時に、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

【技術分野】

【0001】

本発明の実施形態は、半導体装置とその製造方法に関する。

【背景技術】

【0002】

半導体装置の小型化や高機能化を実現するために、1つのパッケージ内に複数の半導体チップを積層して封止したSiP(System in Package)構造の半導体装置が実用化されている。SiP構造の半導体装置では、半導体チップ間の電気信号を高速に送受信することが求められる。このような場合、半導体チップ間の電気的な接続にはマイクロバンプが用いられる。マイクロバンプは、例えば5〜50μm程度の直径を有し、10〜100μm程度のピッチで半導体チップの表面に形成される。

【0003】

マイクロバンプを用いて半導体チップ間を接続する場合、上下の半導体チップに設けられたバンプ同士を位置合わせした後、熱を加えながら上下の半導体チップを圧着してバンプ同士を接続する。上下の半導体チップ間の隙間には、接続信頼性等を高めるためにアンダーフィル樹脂が充填される。バンプ接続の際に、チップ間の隙間が減少しすぎるとバンプの過度の潰れやそれに伴うショートが発生する。このため、上下の半導体チップ間の隙間を維持することが求められている。さらに、バンプ接続後に半導体チップに反りが生じると、バンプ間の接続部に破断が生じて接続不良(オープン不良)が発生するおそれがある。このため、アンダーフィル樹脂を充填する前の半導体チップ間の接続強度を高めることが求められている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2003−197853号公報

【特許文献2】特開2005−268594号公報

【特許文献3】特開2008−192815号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

本発明が解決しようとする課題は、積層された半導体チップ間をバンプ電極で接続するにあたって、上下の半導体チップ間の隙間を維持しつつ、アンダーフィル樹脂を充填する前の半導体チップ間の接続強度を高めることを可能にした半導体装置とその製造方法を提供することにある。

【課題を解決するための手段】

【0006】

実施形態の半導体装置は、第1の接続領域と、前記第1の接続領域を除く第1の非接続領域とを備える第1の表面を有する第1の半導体チップと、前記第1の接続領域と対向する第2の接続領域と、前記第2の接続領域を除く第2の非接続領域とを備える第2の表面を有し、前記第1の半導体チップ上に積層された第2の半導体チップと、前記第1の半導体チップと前記第2の半導体チップとを電気的に接続するように、前記第1の表面の前記第1の接続領域と前記第2の表面の前記第2の接続領域との間に設けられたバンプ接続部と、前記第1の表面の前記第1の非接続領域および前記第2の表面の前記第2の非接続領域の少なくとも一方の領域に局所的に設けられ、かつ前記第1の非接続領域および前記第2の非接続領域の他方の領域と非接着状態で接触する第1のストッパ用突起と、前記第1の表面の前記第1の非接続領域と前記第2の表面の前記第2の非接続領域との間に局所的に設けられ、前記第1および第2の表面に接着された第1の接着用突起と、前記第1の半導体チップの前記第1の表面と前記第2の半導体チップの前記第2の表面との間の隙間に充填された樹脂とを具備する。

【図面の簡単な説明】

【0007】

【図1】第1の実施形態による半導体装置を示す断面図である。

【図2】第1の実施形態による半導体装置の第1の製造工程を示す断面図である。

【図3】第1の実施形態の製造工程で用いる第1および第2の半導体チップのバンプ電極形成面の第1の例を示す平面図である。

【図4】図3に示す第1の半導体チップと第2の半導体チップとを組合せた状態を示す平面透視図である。

【図5】半導体チップの厚さと半導体チップ単体の反り量との関係を示す図である。

【図6】第1の実施形態の製造工程で用いる第1および第2の半導体チップのバンプ電極形成面の第2の例を示す平面図である。

【図7】図6に示す第1の半導体チップと第2の半導体チップとを組合せた状態を示す平面透視図である。

【図8】第1の実施形態による半導体装置の第2の製造工程を示す断面図である。

【図9】第2の実施形態による半導体装置を示す断面図である。

【図10】図9に示す半導体装置を用いた半導体パッケージを示す断面図である。

【図11】図10に示す半導体パッケージの第1の変形例を示す断面図である。

【図12】図10に示す半導体パッケージの第2の変形例を示す断面図である。

【図13】図10に示す半導体パッケージの第3の変形例を示す断面図である。

【図14】第2の実施形態による半導体装置の製造工程を示す断面図である。

【図15】第3の実施形態による半導体装置を示す断面図である。

【図16】第3の実施形態による半導体装置の製造工程を示す断面図である。

【図17】第3の実施形態の製造工程で用いる第1および第2の半導体チップのバンプ電極形成面を示す平面図である。

【図18】図17に示す第1の半導体チップと第2の半導体チップとを組合せた状態を示す平面透視図である。

【図19】第3の実施形態による半導体装置の他の例を示す断面図である。

【図20】第4の実施形態の製造工程で用いる第1および第2の半導体チップのバンプ電極形成面の第1の例を示す平面図である。

【図21】図20に示す第1の半導体チップと第2の半導体チップとを組合せた状態を示す平面透視図である。

【図22】第4の実施形態の製造工程で用いる第1および第2の半導体チップのバンプ電極形成面の第2の例を示す平面図である。

【図23】図22に示す第1の半導体チップと第2の半導体チップとを組合せた状態を示す平面透視図である。

【図24】第5の実施形態による半導体装置を示す断面図である。

【図25】第5の実施形態による半導体装置の製造工程を示す断面図である。

【図26】第5の実施形態の製造工程で用いる第1および第2の半導体チップのバンプ電極形成面を示す平面図である。

【発明を実施するための形態】

【0008】

以下、実施形態の半導体装置とその製造方法について、図面を参照して説明する。

【0009】

(第1の実施形態)

第1の実施形態による半導体装置とその製造方法について、図面を参照して説明する。図1は第1の実施形態による半導体装置を示す図、図2、図3および図4は第1の実施形態による半導体装置の製造工程を示す図である。半導体装置1は第1の半導体チップ2と第2の半導体チップ3とを具備している。第1の半導体チップ2の上面(第1の表面)2aは第1の接続領域を有し、第1の接続領域内に第1のバンプ電極4が形成されている。

【0010】

第2の半導体チップ3の下面(第2の表面)3aは、第1の接続領域と対向する第2の接続領域を有し、第2の接続領域内に第2のバンプ電極5が形成されている。第2の半導体チップ3は、第2のバンプ電極5を第1のバンプ電極4と接続しつつ、第1の半導体チップ2上に積層されている。すなわち、第1の半導体チップ2と第2の半導体チップ3とは、第1のバンプ電極4と第2のバンプ電極5との接続体(バンプ接続部)6を介して、電気的および機械的に接続されている。接続領域とは、半導体チップ2、3の表面2a、3aにおけるバンプ電極4、5の形成領域を意味するものである。バンプ電極4、5とは、第1の半導体チップ2と第2の半導体チップ3とを電気的および機械的に接続するバンプ接続部を形成する電極を意味するものである。

【0011】

第1および第2の半導体チップ2、3の両方にバンプ電極4、5を形成する場合、バンプ電極4、5の構成としては半田/半田、Au/半田、半田/Au、Au/Au等の組合せが例示される。バンプ電極4、5を形成する半田としては、SnにCu、Ag、Bi、In等を添加したSn合金を用いたPbフリー半田が例示される。Pbフリー半田の具体例としては、Sn−Cu合金、Sn−Ag合金、Sn−Ag−Cu合金等が挙げられる。バンプ電極4、5を形成する金属はAuに代えて、Cu、Ni、Sn、Pd、Ag等を用いてもよい。これらの金属は単層膜に限らず、複数の金属の積層膜を用いてもよい。バンプ電極4、5の形状としては、半球状や柱状等の突起形状が挙げられるが、パッドのような平坦形状であってもよい。バンプ電極4、5の組合せとしては、突起体同士の組合せ、突起体と平坦体との組合せ等が挙げられる。

【0012】

第1の半導体チップ2の上面2aにおける第1の接続領域を除く領域(第1の非接続領域)、および第2の半導体チップ3の下面3aにおける第2の接続領域を除く領域(第2の非接続領域)の少なくとも一方の領域には、第1の半導体チップ2と第2の半導体チップ3との間の隙間(ギャップ)が、設定したバンプ電極4、5の接続高さ(バンプ接続部6の設定高さ)となるように、ストッパ用突起7が局所的に設けられている。第1の半導体チップ2と第2の半導体チップ3とを圧着した際、それらの隙間(ギャップ)はストッパ用突起7で規定されるため、バンプ接続部6の過度の潰れやバンプ電極4、5間の接続不良(オープン不良)等の発生を抑制することができる。ストッパ用突起7の先端は、第1の非接続領域および第2の非接続領域の他方の領域と非接着状態で接触している。

【0013】

さらに、第1の半導体チップ2の上面2aにおける第1の非接続領域、および第2の半導体チップ3の下面3aにおける第2の非接続領域の少なくとも一方の領域には、第1のバンプ電極4と第2のバンプ電極5とを接続した際に、第1の半導体チップ2と第2の半導体チップ3との接続状態を強化する接着用突起8が局所的に設けられている。第1および第2の非接続領域の少なくとも一方の領域に設けられた接着用突起8は、第1および第2の非接続領域の他方の領域に接着されている。接着用突起8は第1の非接続領域と第2の非接続領域との間に局所的に設けられ、第1の半導体チップ2の上面2aと第2の半導体チップ3の下面3aにそれぞれ接着されている。

【0014】

バンプ接続部6を介して接続された第1の半導体チップ2と第2の半導体チップ3との間の隙間には、アンダーフィル樹脂(樹脂)9が充填されている。第1の半導体チップ2の第1の非接続領域と第2の半導体チップ3の第2の非接続領域との間に接着用突起8を設けることによって、アンダーフィル樹脂9を充填する前の第1の半導体チップ2と第2の半導体チップ3との接続強度を高めることができる。すなわち、第1の半導体チップ2と第2の半導体チップ3とは、アンダーフィル樹脂9を充填する以前に、第1のバンプ電極4と第2のバンプ電極5との接続部6に加えて、接着用突起8により接続されている。従って、アンダーフィル樹脂9を充填する前の接続強度を高めることができる。

【0015】

第1の半導体チップ2に設けられたバンプ電極4と第2の半導体チップ3に設けられたバンプ電極5とは、例えば加熱しながら圧着することにより接続される。半導体チップ2、3の表面には、通常保護膜としてポリイミド樹脂膜のような有機絶縁膜(絶縁膜)が設けられている。半導体チップ2、3を構成するシリコン基板の熱膨張係数は3ppm程度であるのに対し、ポリイミド樹脂の熱膨張係数は35ppm程度と大きい。このため、半導体チップ2、3に反りが生じやすく、特に半導体チップ2、3の厚さが薄くなるほど反り量が大きくなる傾向がある。従って、接着用突起がない場合には、バンプ電極4、5を接続する際に、あるいは接続した後に、半導体チップ2、3の反りでバンプ電極4、5の接続部6が破断することがある。

【0016】

図5に半導体チップの厚さと常温での半導体チップの反り量との関係の一例を示す。ここでは1辺の長さが12mmの半導体チップの単体でのシミュレーションによる反り量を示す。図5に示すように、半導体チップ2、3の厚さが薄くなるほど反り量が大きくなる。半導体チップ2、3に大きな反りが生じると、第1のバンプ電極4と第2のバンプ電極5とを接続したバンプ接続部6が破断するおそれがある。半導体チップ2、3の厚さが100μmの場合の不良発生率は0%、90μmの場合の不良発生率は10%、80μmの場合の不良発生率は30%である。これらに対して、半導体チップ2、3の厚さが70μmになると不良発生率が約100%となる。

【0017】

このような点に対して、第1の半導体チップ2と第2の半導体チップ3とをバンプ接続部6に加えて接着用突起8により接続することによって、第1の半導体チップ2と第2の半導体チップ3との接続強度が向上する。このため、熱圧着あるいはリフロー等によるバンプ接続後(アンダーフィル樹脂9の充填前)の半導体チップ2、3の反りを抑制することができる。従って、半導体チップ2、3の反りによりアンダーフィル樹脂9の充填前に第1のバンプ電極4と第2のバンプ電極5とのバンプ接続部6が破断することを抑制することができる。接続不良(オープン不良)の発生を抑制することが可能となる。

【0018】

半導体チップ2、3の厚さが薄くなるほど、半導体チップ2、3の反りによるバンプ接続部6の破断が発生しやすくなる。実施形態の半導体装置1は、厚さが100μm以下の半導体チップ2、3を用いる場合に有効であり、さらには厚さが70μm以下の半導体チップ2、3を用いる場合により効果的である。さらに、バンプ電極4、5の形成面積が小さい場合に効果的である。従って、半導体装置1は半導体チップ2、3の表面2a、3aに対するバンプ電極4、5の形成面積の比率が5%以下の場合に有効であり、さらに1%以下の場合により効果的である。

【0019】

半導体装置1は、直径が60μm以下のバンプ電極4、5を用いる場合に有効であり、さらに直径が40μm以下のバンプ電極4、5を用いる場合により効果的である。バンプ電極4、5の直径は、接続安定性等を考慮して5μm以上とすることが好ましい。後述する他の実施形態による半導体装置も同様である。第1のバンプ電極4の直径と第2のバンプ電極5の直径とは、ほぼ同一でもよいし、また異なっていてもよい。例えば、第2のバンプ電極5を突起形状とし、第1のバンプ電極4をパッド形状とする場合、第1のバンプ電極4の直径を第2のバンプ電極5のそれより大きくすることによって、第2のバンプ電極5の第1のバンプ電極4に対する接続性を高めることができる。

【0020】

さらに、接着用突起8は半導体チップ2、3間に局所的に設けられているため、第1の半導体チップ2と第2の半導体チップ3との位置合わせ精度や第1のバンプ電極4と第2のバンプ電極5との接続性を高めることができる。例えばNCF(Non Conductive Film)のような接着機能と封止機能とを併せ持つ熱硬化性絶縁樹脂層を半導体チップ間の隙間全体に配置する方法では、第1の半導体チップと第2の半導体チップとを位置合わせする際に、アライメントマークの検出精度が低下する。マイクロバンプの形成ピッチが狭くなるほど、位置合わせ精度をより一層高めることが求められる。半導体装置1では、接着用突起8がアライメントマークを覆わずに局所的に設けられているため、アライメントマークの検出精度を高めることができ、それにより位置合わせ精度を向上させることが可能となる。

【0021】

半導体チップ間の隙間全体に配置された熱硬化性絶縁樹脂層は、第1のバンプ電極と第2のバンプ電極との間に噛み込まれて接続性が低下するおそれがあるのに対し、局所的に設けられた接着用突起8はバンプ電極4、5間に噛み込まれないため、バンプ電極4、5間の接続性を低下させるおそれがない。従って、第1のバンプ電極4と第2のバンプ電極5との接続性を向上させることができる。さらに、半導体チップの隙間全体に配置される熱硬化性絶縁樹脂層がある場合には、半導体チップ間の接続時や接着時に巻き込みボイドを発生しやすい。接続領域に発生したボイドは、バンプ接続部が樹脂で覆われていない状態を生じさせることがあるため、電極間でショートが発生するおそれがある。半導体装置1では、接着用突起8を用いて半導体チップ2、3間の接続強度を高めつつ、バンプ電極4、5間を接続し、その上でアンダーフィル樹脂9を充填している。このため、バンプ接続部6を確実に覆った状態で封止することができる。従って、半導体装置1の信頼性を高めることが可能となる。

【0022】

上述した半導体装置1は、例えば以下のようにして作製される。半導体装置1の製造工程について、図2、図3および図4を参照して説明する。図2(a)に示すように、第1のバンプ電極4を有する第1の半導体チップ2と第2のバンプ電極5を有する第2の半導体チップ3とを用意する。図2(a)において、ストッパ用突起7は第2の半導体チップ3の下面3aにおける第2の非接続領域に形成されている。接着用突起8は第1の半導体チップ2の上面2aにおける第1の非接続領域に形成されている。ストッパ用突起7および接着用突起8は第1および第2の非接続領域の少なくとも一方に形成されていればよく、例えば両方の領域に形成されていてもよい。

【0023】

ストッパ用突起7は、例えばポリイミド樹脂、フェノール樹脂、エポキシ樹脂、ベンゾシクロブテン樹脂を用いることが好ましい。接着用突起8は、例えばエポキシ樹脂、ポリイミド樹脂、アクリル樹脂、フェノール樹脂等を用いた熱硬化性樹脂で形成することが好ましい。ストッパ用突起7や接着用突起8は、リソグラフィ技術やディスペンサによる塗布技術を適用して形成したり、フィルムの接着により形成することができる。液状の熱硬化性樹脂組成物を塗布して接着用突起8を形成する場合、半導体チップ2、3を接着する前に半硬化状態としておくことが好ましい。あるいは、速硬化型の材料を用いて、半導体チップ2、3の接着、接続時の時間を短縮することが好ましい。

【0024】

図3にストッパ用突起7および接着用突起8の配置例を示す。図3(a)は第1の半導体チップ2の上面(バンプ電極形成面)2aを示している。図3(b)は第2の半導体チップ3の下面(バンプ電極形成面)3aを示している。バンプ電極4、5はそれぞれ半導体チップ2、3の表面2a、3aの中央付近に配置されており、ストッパ用突起7はその周囲を含めて第2の半導体チップ3の表面全体に配置されている。接着用突起8はストッパ用突起7の間等に配置されている。図4に第1の半導体チップ2と第2の半導体チップ3とを組合せた状態におけるストッパ用突起7と接着用突起8の配置を示す。

【0025】

図3は直径が20〜1000μm程度のストッパ用突起7と同様な形状を有する接着用突起8を示しているが、ストッパ用突起7および接着用突起8のサイズと形状はこれに限られるものではない。接着用突起8を液状樹脂の塗布やフィルムの接着等により形成する場合、ある程度の面積を有していることが好ましい。図6(b)に示すように、ストッパ用突起7を配置する際に、第2の半導体チップ3の表面全体に配置するのではなく、一部に空白領域(ストッパ用突起7の未配置領域)を形成する。図6(a)に示すように、ストッパ用突起7の未配置領域に対応させた領域に接着用突起8を配置する。図7にストッパ用突起7と接着用突起8とを組合せた配置を示す。このような配置を適用することで、液状樹脂の塗布やフィルムの接着等による接着用突起8の形成性が向上する。図6および図7はバンプ電極4、5を半導体チップ2、3の四隅にも配置した構造を示している。

【0026】

第1の半導体チップ2と第2の半導体チップ3との第1の接続方法について述べる。図2(a)に示すように、ステージ11上に載置され、かつ吸着保持された第1の半導体チップ2上に、ボンディングヘッド12に吸着保持された第2の半導体チップ3を配置する。図示を省略したカメラ等で第1および第2の半導体チップ2、3のアライメントマークを検出して、第2の半導体チップ3を第1の半導体チップ2上に対して位置合わせする。次いで、図2(b)に示すように、ストッパ用突起7で半導体チップ2、3間の隙間を維持しつつ、第1の半導体チップ2と第2の半導体チップ3とを、バンプ電極4、5の接続温度以上で、かつ接着用突起8を構成する熱硬化性樹脂が硬化する温度以上の温度で圧着する。

【0027】

このような熱圧着工程によって、第1のバンプ電極4と第2のバンプ電極5とを接続すると共に、接着用突起8を第1および第2の半導体チップ2、3の表面2a、3aに接着させる。バンプ電極4、5の接続温度とは、バンプ電極4、5の少なくとも一方を半田で形成した場合、半田の融点以上の温度である。第1の接続方法において、接着用突起8を構成する熱硬化性樹脂が硬化する温度と時間以上で接着用突起8をキュアする工程や、バンプ電極4、5の接続温度以上の温度でバンプ電極4、5を圧着またはリフローする工程を補助的に実施してもよい。

【0028】

第1の半導体チップ2と第2の半導体チップ3との第2の接続方法について述べる。第1の方法と同様に、第1の半導体チップ2と第2の半導体チップ3とを位置合わせする。第1の半導体チップ2と第2の半導体チップ3とを、バンプ電極4、5の接続温度未満で、かつ接着用突起8を構成する熱硬化性樹脂が接着性を発現して硬化し始める温度および時間以上で圧着して、第1のバンプ電極4と第2のバンプ電極5とを仮固定する。接着用突起8を構成する熱硬化性樹脂が硬化する温度と時間以上で接着用突起8を熱処理することによって、接着用突起8をキュアする。バンプ電極4、5の接続温度以上の温度で圧着またはリフローすることで、第1のバンプ電極4と第2のバンプ電極5とを接続する。

【0029】

第2の接続方法において、第1のバンプ電極4と第2のバンプ電極5との仮固定を、接着用突起8を構成する熱硬化性樹脂が硬化する温度と時間以上で実施することによって、バンプ電極4、5の仮固定と同時に接着用突起8を硬化させてもよい。あるいは、第1のバンプ電極4と第2のバンプ電極5との接続を、接着用突起8を構成する熱硬化性樹脂が硬化する温度と時間以上で実施することで、バンプ電極4、5の接続と同時に接着用突起8を硬化させてもよい。これらの場合、接着用突起8のキュア工程を省略してもよい。

【0030】

第1の接続方法または第2の接続方法で第1の半導体チップ2と第2の半導体チップ3とを接続した後、図2(c)に示すように、第1の半導体チップ2と第2の半導体チップ3との間の隙間にアンダーフィル樹脂9を充填して硬化させることによって、半導体装置1が製造される。ここでは図示を省略したが、半導体装置1は外部接続端子を有する配線基板やリードフレーム等の回路基材上に搭載されてSiP構造の半導体装置等として使用される。半導体装置1と回路基材との接続は、フリップチップボンディングやワイヤボンディング等により実施される。

【0031】

上述したように、アンダーフィル樹脂9を充填する前の段階において、第1の半導体チップ2と第2の半導体チップ3とがバンプ接続部6に加えて接着用突起8により接続されているため、熱圧着もしくはリフロー後の半導体チップ2、3の反りを抑制することができる。従って、半導体チップ2、3の反りによって、アンダーフィル樹脂9の充填前に第1のバンプ電極4と第2のバンプ電極5との接続部が破断することを抑制することができる。よって、バンプ電極4、5間の接続不良(オープン不良)の発生が抑制される。

【0032】

図8は半導体装置1の第2の製造工程を示している。図8(a)に示すように、ストッパ用突起7の高さhは第1のバンプ電極4の高さH1と第2のバンプ電極5の高さH2との合計高さ(H1+H2)より低いことが好ましい。このような条件(h<H1+H2)を満足させることによって、第1のバンプ電極4と第2のバンプ電極5とをより確実に接続することができる。図8(b)に示すように、第2のバンプ電極5を第1のバンプ電極4に接触させる。この段階では、ストッパ用突起7は第1の半導体チップ2の表面に接触していない。さらに、図8(c)に示すように、ストッパ用突起7が第1の半導体チップ2の表面に接触するまで、例えば第2のバンプ電極5を変形させる。

【0033】

第2のバンプ電極5を変形させる工程は、第1のバンプ電極4と第2のバンプ電極5とが接続する温度で圧着する工程であってもよいし、あるいは接着用突起8を構成する熱硬化性樹脂が接着性を発現して硬化し始める温度および時間以上で第1のバンプ電極4と第2のバンプ電極5とを仮固定する工程であってもよい。他の工程は第1の製造工程と同様に実施される。上述した条件(h<H1+H2)を満足させることで、ストッパ用突起7により維持される間隔が広くなりすぎて、第1のバンプ電極4と第2のバンプ電極5との接続が不十分になる(バンプ電極4、5の接触状態が不十分になる)ことが防止される。

【0034】

(第2の実施形態)

第2の実施形態による半導体装置について説明する。図9は第2の実施形態の半導体装置を示す図である。第1の実施形態と同一部分については、同一符号を付して一部説明を省略する場合がある。図9に示す半導体装置20は、第1の半導体チップ21と第2の半導体チップ22と第3の半導体チップ23とを積層した構造を有している。ここでは第1ないし第3の半導体チップ21、22、23を積層した半導体装置20について述べるが、半導体チップの積層数は4層以上であってもよい。第3の半導体チップ23の積層工程を繰り返すことで、必要数の半導体チップを積層した半導体装置を得ることができる。

【0035】

第1の半導体チップ21の上面(第1の表面)は第1の接続領域を有し、第1の接続領域内に第1のバンプ電極4が形成されている。第2の半導体チップ22の下面(第2の表面)は第2の接続領域を有し、第2の接続領域内に第2のバンプ電極5が形成されている。第2の半導体チップ22は、第2のバンプ電極5を第1のバンプ電極4と接続しつつ、第1の半導体チップ21上に積層されている。第1の半導体チップ21と第2の半導体チップ22とは、第1の実施形態と同様に、第1のバンプ接続部6Aを介して電気的および機械的に接続されている。

【0036】

第2の半導体チップ22上に第3の半導体チップ23が積層されるため、第2の半導体チップ22の上面(第3の表面)は第3の接続領域を有し、第3の接続領域内に第3のバンプ電極24が設けられている。第2のバンプ電極5と第3のバンプ電極24とは、第2の半導体チップ22内に設けられた貫通電極(Through Silicon Via:TSV)25Aを介して電気的に接続されている。第3の半導体チップ23の下面(第4の表面)は第4の接続領域を有し、第4の接続領域内に第4のバンプ電極26が形成されている。第2の半導体チップ22と第3の半導体チップ23とは、第2のバンプ接続部6Bを介して電気的および機械的に接続されている。第4のバンプ電極26は、第3の半導体チップ23の上面に設けられた電極27と貫通電極(TSV)25Bを介して電気的に接続されている。

【0037】

第1の半導体チップ21の上面における第1の非接続領域、および第2の半導体チップ22の下面における第2の非接続領域の少なくとも一方の領域には、第1のストッパ用突起7Aおよび第1の接着用突起8Aがそれぞれ局所的に設けられている。ストッパ用突起7Aの先端は、第1および第2の非接続領域の他方の領域と非接着状態で接触している。第1および第2の非接続領域の少なくとも一方の領域に局所的に設けられた接着用突起8Aは、第1および第2の非接続領域の他方の領域に接着されており、第1の半導体チップ21の上面と第2の半導体チップ22の下面とを接着している。

【0038】

同様に、第2の半導体チップ22の上面における第3の非接続領域、および第3の半導体チップ23の下面における第4の非接続領域の少なくとも一方の領域には、第2のストッパ用突起7Bおよび第2の接着用突起8Bがそれぞれ局所的に設けられている。ストッパ用突起7Bの先端は、第3および第4の非接続領域の他方の領域と非接着状態で接触している。第3および第4の非接続領域の少なくとも一方の領域に設けられた接着用突起8Bは、第3および第4の非接続領域の他方の領域に接着されている。接着用突起8Bは第3の非接続領域と第4の非接続領域との間に局所的に設けられ、第2の半導体チップ22の上面と第3の半導体チップ23の下面にそれぞれ接着されている。

【0039】

上述したように、3個の半導体チップ21、22、23、もしくはそれ以上の半導体チップを積層する場合においても、アンダーフィル樹脂9の充填前の半導体チップ間の接続強度を接着用突起8A、8Bで高めることによって、熱圧着もしくはリフロー後における半導体チップの反りを抑制することができる。従って、第1および第2のバンプ電極4、5間と第3および第4のバンプ電極24、26間の接続不良(オープン不良)を抑制することが可能となる。ストッパ用突起7A、7Bおよび接着用突起8A、8Bの形成材料、形成箇所、配置形状等については、第1の実施形態と同様である。

【0040】

第2の実施形態の半導体装置20は、例えば図10に示すような半導体パッケージ30として使用される。図10に示す半導体パッケージ30において、半導体装置20は外部接続端子31と内部接続端子32とを有する配線基板33上に搭載されている。配線基板33の内部接続端子32は、半導体装置20の最上段の半導体チップ23の上面に形成された再配線層34とボンディングワイヤ35とを介して、半導体装置20と電気的に接続されている。配線基板33上には、半導体装置20をボンディングワイヤ35等と共に封止する樹脂封止層36が形成されている。

【0041】

半導体装置20と配線基板33と電気的な接続は、フリップチップボンディングにより実施してもよい。図11は半導体装置20と配線基板32とをフリップチップボンディングした状態を示している。半導体装置20をフリップチップボンディングするため、第1の半導体チップ21の下面には第5のバンプ電極28が設けられている。第5のバンプ電極28と第1のバンプ電極4とは、第1の半導体チップ21内に設けられた貫通電極(TSV)25Cを介して電気的に接続されている。第1の半導体チップ21は、基板33上に実装されている。基板33と第1の半導体チップ21とは、基板33の内部接続端子32上に設けられた第6のバンプ電極29と第5のバンプ電極28との接続体(バンプ接続部)6Cを介して電気的および機械的に接続されている。

【0042】

第1の半導体チップ21の下面における非接続領域、および基板33の表面の少なくとも一方の領域には、第3のストッパ用突起7Cおよび第3の接着用突起8Cがそれぞれ局所的に設けられている。ストッパ用突起7Cの先端は、第1の半導体チップ21の下面における非接続領域および基板33の表面の他方の領域と非接着状態で接触している。第1の半導体チップ21の下面における非接続領域および基板33の表面の少なくとも一方の領域に設けられた接着用突起8Cは、第1の半導体チップ21の下面における非接続領域および基板33の表面の他方の領域に接着されている。

【0043】

図12は図10に示す半導体パッケージ30の変形例を示している。半導体装置20を構成する半導体チップ21〜23がNAND型フラッシュメモリのようなメモリチップである場合、半導体装置20上にはコントローラチップやインタフェースチップのような外部デバイスとの間でデータ通信を行う半導体チップ37が搭載されていてもよい。半導体チップ37は半田バンプ38を介して半導体装置20と接続されている。半導体装置20は、半導体チップ37やボンディングワイヤ35等を介して配線基板33と電気的に接続されている。図13に示すように、半導体装置20は積層順の最上段(紙面最下段)に位置する半導体チップ37に設けられた半田バンプ39を介して、配線基板33と電気的および機械的に接続されていてもよい。

【0044】

第2の実施形態による半導体装置20の製造工程について、図14を参照して説明する。図14はステージ11とボンディングヘッド12の図示を省略したが、基本的には第1の実施形態と同様にして積層工程が実施される。

【0045】

第1の半導体チップ21と第2の半導体チップ22と第3の半導体チップ23との第1の接続方法について述べる。図14(a)に示すように、第1のバンプ電極4と第1の接着用突起8Aとを有する第1の半導体チップ21と、第2のバンプ電極5と第1のストッパ用突起7Aとを有する第2の半導体チップ22とを位置合わせする。図14(b)に示すように、第1の半導体チップ21と第2の半導体チップ22とを、バンプ電極4、5の接続温度以上で、かつ接着用突起8Aを構成する熱硬化性樹脂が硬化する温度以上の温度で圧着することによって、第1および第2のバンプ電極4、5を接続する。

【0046】

図14(c)に示すように、第2の半導体チップ22の上面における第3の非接続領域に第2の接着用突起8Bを形成する。第2の接着用突起8Bは、ディスペンサによる塗布やフィルムの接着等により形成することが好ましい。図14(d)に示すように、第4のバンプ電極26と第2のストッパ用突起7Bとを有する第3の半導体チップ23を、第2の半導体チップ22に対して位置合わせする。図14(e)に示すように、第2の半導体チップ22と第3の半導体チップ23とを、バンプ電極24、26の接続温度以上で、かつ接着用突起8Bを構成する熱硬化性樹脂が硬化する温度以上の温度で圧着することによって、第3および第4のバンプ電極24、26を接続する。

【0047】

第1の接続方法において、接着用突起を構成する熱硬化性樹脂が硬化する温度と時間以上で接着用突起をキュアする工程や、バンプ電極の接続温度以上の温度でバンプ電極を圧着またはリフローする工程を補助的に実施してもよい。

【0048】

第1の半導体チップ21と第2の半導体チップ22と第3の半導体チップ23との第2の接続方法について述べる。第1のバンプ電極4と第1の接着用突起8Aとを有する第1の半導体チップ21と、第2のバンプ電極5と第1のストッパ用突起7Aとを有する第2の半導体チップ22とを位置合わせする。接着用突起8Aを構成する熱硬化性樹脂が接着性を発現して硬化し始める温度および時間以上で、第1のバンプ電極4と第2のバンプ電極5とを仮固定する。

【0049】

第2の半導体チップ22の上面における第3の非接続領域に第2の接着用突起8Bを形成する。第4のバンプ電極26と第2のストッパ用突起7Bとを有する第3の半導体チップ23を、第2の半導体チップ22に対して位置合わせする。接着用突起8Bを構成する熱硬化性樹脂が接着性を発現して硬化し始める温度および時間以上で、第3のバンプ電極24と第4のバンプ電極26とを仮固定する。

【0050】

第1ないし第3の半導体チップ21、22、23の積層体をオーブン内に配置し、接着用突起8A、8Bを構成する熱硬化性樹脂が硬化する温度と時間以上で加熱する。接着用突起8A、8Bを硬化させることで、第1の半導体チップ21と第2の半導体チップ22との間を接着用突起8Aで接着し、かつ第2の半導体チップ22と第3の半導体チップ23との間を接着用突起8Bで接着する。半導体チップ間を接着用突起8A、8Bで接着したチップ積層体を、バンプ電極の接続温度以上の温度で圧着またはリフローする。

【0051】

圧着工程は、接着用突起8A、8Bを硬化させたチップ積層体を加熱しつつ圧着することにより実施される。リフロー工程を適用する場合には、半導体チップ間を接着用突起8A、8Bで接着したチップ積層体をリフロー炉内に配置する。リフロー炉内を還元雰囲気とした状態で、バンプ電極の接続温度以上の温度に加熱することによって、第1のバンプ電極4と第2のバンプ電極5とを接続すると共に、第3のバンプ電極24と第4のバンプ電極26とを接続する。リフロー工程は還元雰囲気中で実施することが好ましい。これによって、バンプ電極の表面酸化膜を除去しつつ、バンプ接続部を得ることができる。

【0052】

第2の接続方法において、接着用突起8A、8Bのキュア処理は、バンプ電極の仮固定と同時に実施してもよい。この場合には、バンプ電極の仮固定を接着用突起8A、8Bを構成する熱硬化性樹脂が硬化する温度と時間以上で実施する。あるいは、接着用突起8A、8Bのキュア処理は、バンプ電極の接続と同時に実施してもよい。この場合には、バンプ電極の接続を接着用突起8A、8Bを構成する熱硬化性樹脂が硬化する温度と時間以上で実施する。接着用突起8A、8Bの硬化反応が不十分であると、接着用突起8A、8Bと半導体チップ21、22、23との接着が不十分であるために剥がれが生じ、バンプ接続部6が破断して接続不良が発生するおそれがある。従って、接着性が維持される範囲で、接着用突起8A、8Bを十分に硬化させることが好ましい。

【0053】

第1の半導体チップ21と第2の半導体チップ22と第3の半導体チップ23との第3の接続方法について述べる。第2の接続方法と同様に、第1のバンプ電極4と第2のバンプ電極5とを仮固定する。第2の半導体チップ22の上面における第3の非接続領域に第2の接着用突起8Bを形成する。第4のバンプ電極26と第2のストッパ用突起7Bとを有する第3の半導体チップ23を、第2の半導体チップ22に対して位置合わせする。第2の半導体チップ22と第3の半導体チップ23とを、バンプ電極24、26の接続温度以上で、かつ接着用突起8Bを構成する熱硬化性樹脂が硬化する温度と時間以上で圧着することによって、第3および第4のバンプ電極24、26を接続する。

【0054】

このように、最上段の半導体チップ23はバンプ電極の接続温度以上の温度に加熱しつつ圧着することが好ましい。それ以外の半導体チップ21、22はバンプ電極の接続温度未満の温度に加熱しつつ圧着する。これによって、チップ積層体の強度が向上する。全ての半導体チップ21、22、23をバンプ電極の接続温度以上の温度で圧着すると、半導体チップ21、22、23に対する熱負荷が増大する。最上段の半導体チップ23のみをバンプ電極の接続温度以上の温度に加熱しつつ圧着することで、半導体チップ21、22、23に対する熱負荷を低減しつつ、チップ積層体の強度を高めることができる。

【0055】

最上段の半導体チップ23をバンプ電極の接続温度以上の温度で熱圧着することによって、第1のバンプ電極4と第2のバンプ電極5、および第3のバンプ電極24と第4のバンプ電極26間とが接続される。第3の接続方法において、接着用突起8A、8Bをキュア処理する工程や、チップ積層体の圧着またはリフローする工程を、補助的に実施してもよい。図12に示す半導体パッケージのように、第1ないし第3の半導体チップ21、22、23と最上段の半導体チップ37とのサイズが異なる場合や、バンプ電極の配列が異なる場合には、第3の半導体チップ23および最上段の半導体チップ37を、それぞれバンプ電極の接続温度以上の温度に加熱しつつ圧着することが好ましい。それ以外の半導体チップ21、22はバンプ電極の接続温度未満の温度に加熱しつつ圧着する。

【0056】

第1、第2、または第3の接続方法で第1ないし第3の半導体チップ21、22、23を接続した後、図14(f)に示すように、第1の半導体チップ21と第2の半導体チップ22との隙間、および第2の半導体チップ22と第3の半導体チップ23との隙間に、それぞれアンダーフィル樹脂9を充填して硬化させる。このようにして、第2の実施形態による半導体装置20が製造される。3個もしくはそれ以上の半導体チップを積層する場合においても、アンダーフィル樹脂9の充填前の半導体チップ間の接続強度を接着用突起8A、8Bで高めることで、熱圧着もしくはリフロー後における半導体チップの反りを抑制することができる。従って、第1および第2のバンプ電極4、5間、第3および第4のバンプ電極24、26間の接続不良(オープン不良)を抑制することが可能となる。

【0057】

(第3の実施形態)

第3の実施形態による半導体装置の構成と製造工程について、図15および図16を参照して説明する。第3の実施形態による半導体装置40は、第1および第2の実施形態におけるストッパ用突起7および接着用突起8に代えて、ストッパ兼接着用突起41を有している。第1および第2の実施形態と同一部分については、同一符号を付して一部説明を省略する場合がある

【0058】

図15に示す半導体装置40は、ストッパ兼接着用突起41と第1のバンプ電極4とを有する第1の半導体チップ2と、第2のバンプ電極5を有する第2の半導体チップ3とを備えている。第1の半導体チップ2と第2の半導体チップ3とは、第1のバンプ電極4と第2のバンプ電極5との接続体(バンプ接続部6)を介して、電気的および機械的に接続されている。ストッパ兼接着用突起41は、第1の半導体チップ2の上面(第1の表面)2aにおける非接続領域に局所的に設けられており、第1の半導体チップ2の上面2aと第2の半導体チップ3の下面3aにそれぞれ接着されている。第1の半導体チップ2と第2の半導体チップ3との間の隙間には、アンダーフィル樹脂9が充填されている。

【0059】

第1の半導体チップ2の上面2aに設けられたストッパ兼接着用突起41は、第1の半導体チップ2と第2の半導体チップ3とを圧着した際に、それらの隙間(ギャップ)を保持し、かつ加熱した際に第2の半導体チップ3の下面3aに接着されるものである。従って、ストッパ用突起7と接着用突起8とを用いた第1の実施形態と同様に、圧着時における第1の半導体チップ2と第2の半導体チップ3との間の隙間(ギャップ)を維持しつつ、アンダーフィル樹脂9を充填する前の第1の半導体チップ2と第2の半導体チップ3との接続強度を高めることができる。これらによって、バンプ電極4、5間の接続信頼性を向上させることが可能となる。

【0060】

ストッパ兼接着用突起41は、例えば感光性および熱硬化性を有する樹脂を用いて形成される。感光性および熱硬化性樹脂の具体例としては、感光性接着剤樹脂のような感光剤を含有する熱硬化性樹脂が挙げられる。感光性および熱硬化性樹脂によれば、突起41の形成段階においては、紫外線等の照射により硬化するため、ストッパとして機能させることができる。さらに、加熱時には熱硬化するため、第1および第2の半導体チップ2、3の表面と強固に接着し、接着剤(接着用突起)として機能する。ストッパ兼接着用突起41は、感光性および熱硬化性を有する樹脂で形成したものに限らす、例えば耐熱樹脂製突起の先端に接着剤層を形成したものであってもよい。これによっても、同様なストッパ機能と接着機能とを得ることができる。ストッパ兼接着用突起41は、第2の半導体チップ3の下面3aに設けてもよい。

【0061】

第3の実施形態の半導体装置40は、例えば以下のようにして作製される。図16(a)に示すように、第1のバンプ電極4とストッパ兼接着用突起41とを有する第1の半導体チップ2と、第2のバンプ電極5を有する第2の半導体チップ3とを用意する。図17および図18にストッパ兼接着用突起41の配置例を示す。図17(a)は第1の半導体チップ2の上面(バンプ電極形成面)2aを示している。図17(b)は第2の半導体チップ3の下面(バンプ電極形成面)3aを示している。図18は第1の半導体チップ2と第2の半導体チップ3とを組合せた状態を示している。ストッパ兼接着用突起41は、半導体チップ2の中央付近に存在するバンプ電極4の周囲を含めて、第1の半導体チップ2の表面全体に配置されている。

【0062】

次に、第1の実施形態と同様に、第1の半導体チップ2と第2の半導体チップ3とを位置合わせする。図16(b)に示すように、ストッパ兼接着用突起41で隙間を維持しつつ、第1の半導体チップ2と第2の半導体チップ3とを熱圧着する。このような熱圧着工程によって、第1のバンプ電極4と第2のバンプ電極5とを接続すると共に、ストッパ兼接着用突起41を第1および第2の半導体チップ2、3の表面2a、3aに接着する。第1の半導体チップ2と第2の半導体チップ3との接続工程は、第1の実施形態における第1または第2の接続方法と同様に実施される。

【0063】

この後、図16(c)に示すように、第1の半導体チップ2と第2の半導体チップ3との間の隙間にアンダーフィル樹脂9を充填して硬化させることによって、半導体装置40が製造される。アンダーフィル樹脂9を充填する前の段階において、第1の半導体チップ2と第2の半導体チップ3とがバンプ接続部6に加えて、ストッパ兼接着用突起41により接続されているため、熱圧着もしくはリフロー後における半導体チップ2、3の反りを抑制することができる。従って、半導体チップ2、3の反りによって、アンダーフィル樹脂9の充填前に第1のバンプ電極4と第2のバンプ電極5との接続部が破断することによる接続不良(オープン不良)の発生を抑制することが可能となる。

【0064】

3個以上の半導体チップを積層する場合には、半導体チップの積層工程を繰り返し実施すればよい。図19は3個の半導体チップ21、22、23を積層して構成した半導体装置42を示している。半導体装置42は、第2の実施形態における第1、第2、または第3の接続方法と同様な方法を適用することにより作製される。半導体チップ21、22、23を、第2の実施形態における第1、第2、または第3の接続方法と同様にして接続する。ストッパ兼接着用突起41は、積層する際に上側に位置する半導体チップ(22、23)の下面に形成されていることが好ましい。この後、第1の半導体チップ21と第2の半導体チップ22との隙間、および第2の半導体チップ22と第3の半導体チップ23との隙間に、それぞれアンダーフィル樹脂9を充填して硬化させる。

【0065】

(第4の実施形態)

第4の実施形態による半導体装置の構成について、図20、図21、図22および図23を参照して説明する。第4の実施形態による半導体装置は、第1および第2の実施形態における接着用突起8、または第3の実施形態におけるストッパ兼接着用突起41に、アンダーフィル樹脂のはみ出し抑制機能を持たせたものである。なお、それら以外の構成については、第1ないし第3の実施形態と同一であるため、ここでは説明を省略する。

【0066】

図20はアンダーフィル樹脂のはみ出し抑制機能を有する接着用突起8の配置例を示している。図20(a)は第1の半導体チップ2の上面2aを示している。図20(b)は第2の半導体チップ3の下面3aを示している。図21は第1の半導体チップ2と第2の半導体チップ3とを組合せた状態を示している。接着用突起8は、半導体チップ2の対向する2つの外形辺に沿って、半導体チップ2の外周領域に設けられている。このような接着用突起8によれば、アンダーフィル樹脂の注入辺とそれと対向する辺以外からのアンダーフィル樹脂のはみ出しを抑制することができる。

【0067】

図22はアンダーフィル樹脂のはみ出し抑制機能を有するストッパ兼接着用突起41の配置例を示している。図22(a)は第1の半導体チップ2の上面2aを示している。図22(b)は第2の半導体チップ3の下面3aを示している。図23は第1の半導体チップ2と第2の半導体チップ3とを組合せた状態を示している。ストッパ兼接着用突起41は、半導体チップ2の外周領域とバンプ電極4の周囲に設けられている。半導体チップ2の外周領域において、ストッパ兼接着用突起41はアンダーフィル樹脂の注入辺を除く外形辺に沿って配置されている。このようなストッパ兼接着用突起41によれば、アンダーフィル樹脂の注入辺以外からのアンダーフィル樹脂のはみ出しが抑制される。

【0068】

半導体チップ2の3つの外形辺に沿ってストッパ兼接着用突起41を配置する場合、アンダーフィル樹脂の充填は、例えば減圧下で充填した後に大気圧に開放する方法、樹脂を充填した後に加圧下でキュアする方法により実施することが有効である。これらの方法は充填時に発生したボイドを差圧で押し潰す方法である。特に、ストッパ兼接着用突起41を図22(a)に示すように配置する場合に、圧力が効率よく加わり、ボイドを効果的に押し潰すことができる。図20および図21に示す接着用突起8の配置をストッパ兼接着用突起41に適用してもよい。図22および図23に示すストッパ兼接着用突起41の配置を接着用突起8に適用してもよい。

【0069】

(第5の実施形態)

第5の実施形態による半導体装置の構成と製造工程について、図24、図25および図26を参照して説明する。第5の実施形態による半導体装置50は、ストッパ用突起7および接着用突起8の接触面、もしくはストッパ兼接着用突起41の接触面に設けられた有機絶縁膜(絶縁膜)51を備えている。それ以外の構成は、基本的には第1ないし第3の実施形態と同一である。第1ないし第3の実施形態と同一部分については、同一符号を付して一部説明を省略する場合がある。ここではストッパ兼接着用突起41を用いた半導体装置50について主として説明するが、ストッパ用突起7および接着用突起8を適用する場合も同様である。

【0070】

図24に示す半導体装置50は、第1のバンプ電極4を有する第1の半導体チップ2と、第2のバンプ電極5とストッパ兼接着用突起41とを有する第2の半導体チップ3とを備えている。第1の半導体チップ2と第2の半導体チップ3とは、第1のバンプ電極4と第2のバンプ電極5とのバンプ接続部6を介して、電気的および機械的に接続されている。ストッパ兼接着用突起41は、第2の半導体チップ3の下面3aにおける非接続領域に局所的に設けられており、第1の半導体チップ2に接着されている。第1の半導体チップ2と第2の半導体チップ3との間にはアンダーフィル樹脂9が充填されている。

【0071】

第1の半導体チップ2の上面2aには第1のバンプ電極4に加えて、Al配線膜等を用いた表面配線52が形成されている場合がある。表面配線52は所望のパターンに応じて形成されているため、表面配線52が存在する部分と存在しない部分とがある。表面配線52の有無によって、第1の半導体チップ2の上面2aには1〜2μm程度の凹凸が生じている。表面配線52が存在していない部分に配置されたストッパ兼接着用突起41と第1の半導体チップ2の上面2aと間には隙間が生じ、ストッパや接着剤として機能させることができない。そこで、第5の実施形態の半導体装置50においては、第1の半導体チップ2の上面2aにおける非接続領域を有機絶縁膜51で覆っている。

【0072】

第1の半導体チップ2の上面2aにおける非接続領域を有機絶縁膜51で覆うことによって、ストッパ兼接着用突起41の接触高さが均一になり、全てのストッパ兼接着用突起41をストッパおよび接着剤として良好に機能させることができる。有機絶縁膜51には、ポリイミド系樹脂やフェノール系樹脂等の熱硬化性樹脂が適用される。有機絶縁膜51は、さらにキュア温度が250℃以下の熱硬化性樹脂、例えば低温キュアのポリイミド系樹脂やフェノール系樹脂が好ましい。有機絶縁膜51は、例えばスピンコートによる塗布工程とリソグラフィ工程と現像工程とにより形成される。

【0073】

有機絶縁膜51はストッパ兼接着用突起41の接着面に形成される。図24に示す半導体装置50において、ストッパ兼接着用突起41は予め第2の半導体チップ3の下面3aに設けられているため、有機絶縁膜51は第1の半導体チップ2の上面2aの非接続領域に設けられる。ストッパ兼接着用突起41を第1の半導体チップ2の上面2aに設ける場合、有機絶縁膜51は第2の半導体チップ3の下面3aの非接続領域に設けられる。ストッパ兼接着用突起41に代えて、ストッパ用突起7および接着用突起8を適用する場合も同様である。有機絶縁膜51は、ストッパ用突起7や接着用突起8が形成されたチップ面と対向する半導体チップの面の非接続領域に設けられる。

【0074】

有機絶縁膜51は、ストッパ兼接着用突起41の接触面の高さを均一にする、言い換えると接触面を平坦化する効果に加えて、ストッパ兼接着用突起41の接着信頼性を向上させる効果を有する。ストッパ兼接着用突起41は、例えば80〜200ppm/℃程度の線膨張係数を有するのに対し、半導体チップ2の表面に設けられた無機絶縁膜の線膨張係数は、例えば0.1〜10ppm/℃程度である。このため、有機絶縁膜51を形成しない場合には、ストッパ兼接着用突起41と無機絶縁膜との熱膨張差により剥離が生じやすくなる。これに対して、有機絶縁膜51の線膨張係数は、例えば40〜70ppm/℃程度であるため、ストッパ兼接着用突起41との熱膨張差が低減される。従って、ストッパ兼接着用突起41の剥離を抑制することができる。

【0075】

上記したように有機絶縁膜51を設けると、その膜厚の分だけストッパ兼接着用突起41の高さを減少させることできる。周囲の環境等により熱変化が生じた場合に、ストッパ兼接着用突起41の高さ方向の変動が減少するため、ストッパ兼接着用突起41の接着信頼性が向上する。ストッパ兼接着用突起41の高さを低減するために、有機絶縁膜51はストッパ兼接着用突起41の接着面(第1の半導体チップ2の上面2a)に加えて、ストッパ兼接着用突起41の形成面(第2の半導体チップ3の下面3a)に形成することも有効である。ストッパ兼接着用突起41に代えて、ストッパ用突起7および接着用突起8を適用する場合も同様である。

【0076】

第5の実施形態の半導体装置50は、例えば以下のようにして作製される。図25(a)に示すように、第1のバンプ電極4を有する第1の半導体チップ2と、第2のバンプ電極5とストッパ兼接着用突起41とを有する第2の半導体チップ3とを用意する。図26にストッパ兼接着用突起41および有機絶縁膜51の形成例を示す。図26(a)は第1の半導体チップ2の上面2aを示している。図26(b)は第2の半導体チップ3の下面3aを示している。有機絶縁膜51は、第1の半導体チップ2の上面2aの非接続領域、すなわちバンプ電極4の形成位置を除く領域全体に形成されている。

【0077】

第1の半導体チップ2と第2の半導体チップ3とを位置合わせした後、図25(b)に示すように、第1のバンプ電極4と第2のバンプ電極5とを接触させ、さらにストッパ兼接着用突起41Aが有機絶縁膜51に接触するまでバンプ電極4、5を変形させる。第1の実施形態における第1または第2の接続方法と同様にして、第1の半導体チップ2と第2の半導体チップ3とを接続する。この後、前述した第3の実施形態と同様に、第1の半導体チップ2と第2の半導体チップ3との間の隙間にアンダーフィル樹脂9を充填して硬化させることによって、半導体装置50が製造される。

【0078】

ここでは2個の半導体チップ2、3を積層する場合について説明したが、3個またはそれ以上の半導体チップを積層する場合も同様である。3個またはそれ以上の半導体チップを積層する場合の構成は、第2および第3の実施形態に示した通りである。ストッパ兼接着用突起41に代えて、ストッパ用突起7および接着用突起8を適用する場合の構成は、第1および第2の実施形態に示した通りである。

【0079】

なお、第1ないし第5の実施形態の構成は、それぞれ組合せて適用することができ、また一部置き換えることも可能である。本発明のいくつかの実施形態を説明したが、これらの実施形態は例として提示したものであり、発明の範囲を限定することは意図していない。これら実施形態は、その他の様々な形態で実施し得るものであり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれると同時に、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

【特許請求の範囲】

【請求項1】

第1の接続領域と、前記第1の接続領域を除く第1の非接続領域とを備える第1の表面を有する第1の半導体チップと、

前記第1の接続領域と対向する第2の接続領域と、前記第2の接続領域を除く第2の非接続領域とを備える第2の表面と、第3の接続領域と、前記第3の接続領域を除く第3の非接続領域とを備え、前記第2の表面とは反対側の第3の表面とを有し、前記第1の半導体チップ上に積層された第2の半導体チップと、

前記第3の接続領域と対向する第4の接続領域と、前記第4の接続領域を除く第4の非接続領域とを備える第4の表面を有し、前記第2の半導体チップ上に積層された第3の半導体チップと、

前記第1の半導体チップと前記第2の半導体チップとを電気的に接続するように、前記第1の表面の前記第1の接続領域と前記第2の表面の前記第2の接続領域との間に設けられた第1のバンプ接続部と、

前記第1の表面の前記第1の非接続領域および前記第2の表面の前記第2の非接続領域の少なくとも一方の領域に局所的に設けられ、かつ前記第1の非接続領域および前記第2の非接続領域の他方の領域と非接着状態で接触する第1のストッパ用突起と、

前記第1の表面の前記第1の非接続領域と前記第2の表面の前記第2の非接続領域との間に局所的に設けられ、前記第1および第2の表面に接着された第1の接着用突起と、

前記第2の半導体チップと前記第3の半導体チップとを電気的に接続するように、前記第3の表面の前記第3の接続領域と前記第4の表面の前記第4の接続領域との間に設けられた第2のバンプ接続部と、

前記第3の表面の前記第3の非接続領域および前記第4の表面の前記第4の非接続領域の少なくとも一方の領域に局所的に設けられ、かつ前記第3の非接続領域および前記第4の非接続領域の他方の領域と非接着状態で接触する第2のストッパ用突起と、

前記第3の表面の前記第3の非接続領域と前記第4の表面の前記第4の非接続領域との間に局所的に設けられ、前記第3および第4の表面に接着された第2の接着用突起と、

前記第1の半導体チップの前記第1の表面と前記第2の半導体チップの前記第2の表面との間の隙間、および前記第2の半導体チップの前記第3の表面と前記第3の半導体チップの前記第4の表面との間の隙間に充填された樹脂とを具備し、

前記第2のバンプ接続部は、前記第2の半導体チップ内に設けられた貫通電極を介して、前記第1のバンプ接続部と電気的に接続されており、

前記第1の接着用突起は、前記第1の表面の前記第1の非接続領域および前記第2の表面の前記第2の非接続領域の少なくとも一方の領域に設けられ、前記第1の非接続領域および前記第2の非接続領域の少なくとも他方の領域には、絶縁膜が設けられており、

前記第2の接着用突起は、前記第3の表面の前記第3の非接続領域および前記第4の表面の前記第4の非接続領域の少なくとも一方の領域に設けられ、前記第3の非接続領域および前記第4の非接続領域の少なくとも他方の領域には、絶縁膜が設けられていることを特徴とする半導体装置。

【請求項2】

第1の接続領域と、前記第1の接続領域を除く第1の非接続領域とを備える第1の表面を有する第1の半導体チップと、

前記第1の接続領域と対向する第2の接続領域と、前記第2の接続領域を除く第2の非接続領域とを備える第2の表面を有し、前記第1の半導体チップ上に積層された第2の半導体チップと、

前記第1の半導体チップと前記第2の半導体チップとを電気的に接続するように、前記第1の表面の前記第1の接続領域と前記第2の表面の前記第2の接続領域との間に設けられた第1のバンプ接続部と、

前記第1の表面の前記第1の非接続領域および前記第2の表面の前記第2の非接続領域の少なくとも一方の領域に局所的に設けられ、かつ前記第1の非接続領域および前記第2の非接続領域の他方の領域と非接着状態で接触する第1のストッパ用突起と、

前記第1の表面の前記第1の非接続領域と前記第2の表面の前記第2の非接続領域との間に局所的に設けられ、前記第1および第2の表面に接着された第1の接着用突起と、

前記第1の半導体チップの前記第1の表面と前記第2の半導体チップの前記第2の表面との間の隙間に充填された第1の樹脂と

を具備することを特徴とする半導体装置。

【請求項3】

さらに、前記第2の半導体チップ上に積層された第3の半導体チップを具備し、

前記第2の半導体チップは、第3の接続領域と、前記第3の接続領域を除く第3の非接続領域とを備え、前記第2の表面とは反対側の第3の表面を有し、

前記第3の半導体チップは、前記第3の接続領域と対向する第4の接続領域と、前記第4の接続領域を除く第4の非接続領域とを備える第4の表面を有し、かつ前記第2の半導体チップ上に積層されており、

前記第2の半導体チップと前記第3の半導体チップとは、前記第3の表面の前記第3の接続領域と前記第4の表面の前記第4の接続領域との間に設けられた第2のバンプ接続部により電気的に接続されており、

前記第2の半導体チップの前記第3の表面と前記第3の半導体チップの前記第4の表面との間には、前記第3の表面の前記第3の非接続領域および前記第4の表面の前記第4の非接続領域の少なくとも一方の領域に局所的に設けられ、かつ前記第3の非接続領域および前記第4の非接続領域の他方の領域と非接着状態で接触する第2のストッパ用突起が配置されており、

前記第3の表面の前記第3の非接続領域と前記第4の表面の前記第4の非接続領域との間には、前記第3および第4の表面に接着された第2の接着用突起が局所的に配置されており、

前記第2の半導体チップの前記第3の表面と前記第3の半導体チップの前記第4の表面との間の隙間には第2の樹脂が充填されている、請求項2に記載の半導体装置。

【請求項4】

第1の接続領域と、前記第1の接続領域を除く第1の非接続領域とを備える第1の表面を有する第1の半導体チップと、

前記第1の接続領域と対向する第2の接続領域と、前記第2の接続領域を除く第2の非接続領域とを備える第2の表面を有し、前記第1の半導体チップ上に積層された第2の半導体チップと、

前記第1の半導体チップと前記第2の半導体チップとを電気的に接続するように、前記第1の表面の前記第1の接続領域と前記第2の表面の前記第2の接続領域との間に設けられた第1のバンプ接続部と、

前記第1の表面の前記第1の非接続領域および前記第2の表面の前記第2の非接続領域の少なくとも一方の領域に局所的に設けられ、かつ前記第1の非接続領域および前記第2の非接続領域の他方の領域に接着された第1のストッパ兼接着用突起と、

前記第1の半導体チップの前記第1の表面と前記第2の半導体チップの前記第2の表面との間の隙間に充填された第1の樹脂と

を具備することを特徴とする半導体装置。

【請求項5】

さらに、前記第2の半導体チップ上に積層された第3の半導体チップを具備し、

前記第2の半導体チップは、第3の接続領域と、前記第3の接続領域を除く第3の非接続領域とを備え、前記第2の表面とは反対側の第3の表面を有し、

前記第3の半導体チップは、前記第3の接続領域と対向する第4の接続領域と、前記第4の接続領域を除く第4の非接続領域とを備える第4の表面を有し、かつ前記第2の半導体チップ上に積層されており、

前記第2の半導体チップと前記第3の半導体チップとは、前記第3の表面の前記第3の接続領域と前記第4の表面の前記第4の接続領域との間に設けられた第2のバンプ接続部により電気的に接続されており、

前記第2の半導体チップの前記第3の表面と前記第3の半導体チップの前記第4の表面との間には、前記第3の表面の前記第3の非接続領域および前記第4の表面の前記第4の非接続領域の少なくとも一方の領域に局所的に設けられ、かつ前記第3の非接続領域および前記第4の非接続領域の他方の領域に接着された第2のストッパ兼接着用突起が配置されており、

前記第2の半導体チップの前記第3の表面と前記第3の半導体チップの前記第4の表面との間の隙間には第2の樹脂が充填されている、請求項4に記載の半導体装置。

【請求項6】

第1の接続領域と、前記第1の接続領域を除く第1の非接続領域と、前記第1の接続領域に設けられた第1のバンプ電極とを備える第1の表面を有する第1の半導体チップを用意する工程と、

前記第1の接続領域に対応する第2の接続領域と、前記第2の接続領域を除く第2の非接続領域と、前記第2の接続領域に設けられた第2のバンプ電極とを備える第2の表面を有する第2の半導体チップを用意する工程と、

前記第1の表面の前記第1の非接続領域および前記第2の表面の前記第2の非接続領域の少なくとも一方の領域に、第1のストッパ用突起および第1の接着用突起、あるいは第1のストッパ兼接着用突起を局所的に形成する工程と、

前記第1のバンプ電極と前記第2のバンプ電極とを位置合わせしつつ、前記第1の半導体チップ上に前記第2の半導体チップを積層する工程と、

前記第1のストッパ用突起または前記第1のストッパ兼接着用突起で前記第1の半導体チップの前記第1の表面と前記第2の半導体チップの前記第2の表面との間の隙間を維持しつつ、前記第1のバンプ電極と前記第2のバンプ電極とを接触させて加熱し、前記第1のバンプ電極と前記第2のバンプ電極とを接続すると共に、前記第1の接着用突起または前記第1のストッパ兼接着用突起を前記第1の非接続領域および前記第2の非接続領域の他方の領域に接着する工程と、

前記第1の半導体チップの前記第1の表面と前記第2の半導体チップの前記第2の表面との間の隙間に第1の樹脂を充填する工程と

を具備することを特徴とする半導体装置の製造方法。

【請求項1】

第1の接続領域と、前記第1の接続領域を除く第1の非接続領域とを備える第1の表面を有する第1の半導体チップと、

前記第1の接続領域と対向する第2の接続領域と、前記第2の接続領域を除く第2の非接続領域とを備える第2の表面と、第3の接続領域と、前記第3の接続領域を除く第3の非接続領域とを備え、前記第2の表面とは反対側の第3の表面とを有し、前記第1の半導体チップ上に積層された第2の半導体チップと、

前記第3の接続領域と対向する第4の接続領域と、前記第4の接続領域を除く第4の非接続領域とを備える第4の表面を有し、前記第2の半導体チップ上に積層された第3の半導体チップと、

前記第1の半導体チップと前記第2の半導体チップとを電気的に接続するように、前記第1の表面の前記第1の接続領域と前記第2の表面の前記第2の接続領域との間に設けられた第1のバンプ接続部と、

前記第1の表面の前記第1の非接続領域および前記第2の表面の前記第2の非接続領域の少なくとも一方の領域に局所的に設けられ、かつ前記第1の非接続領域および前記第2の非接続領域の他方の領域と非接着状態で接触する第1のストッパ用突起と、

前記第1の表面の前記第1の非接続領域と前記第2の表面の前記第2の非接続領域との間に局所的に設けられ、前記第1および第2の表面に接着された第1の接着用突起と、

前記第2の半導体チップと前記第3の半導体チップとを電気的に接続するように、前記第3の表面の前記第3の接続領域と前記第4の表面の前記第4の接続領域との間に設けられた第2のバンプ接続部と、

前記第3の表面の前記第3の非接続領域および前記第4の表面の前記第4の非接続領域の少なくとも一方の領域に局所的に設けられ、かつ前記第3の非接続領域および前記第4の非接続領域の他方の領域と非接着状態で接触する第2のストッパ用突起と、

前記第3の表面の前記第3の非接続領域と前記第4の表面の前記第4の非接続領域との間に局所的に設けられ、前記第3および第4の表面に接着された第2の接着用突起と、

前記第1の半導体チップの前記第1の表面と前記第2の半導体チップの前記第2の表面との間の隙間、および前記第2の半導体チップの前記第3の表面と前記第3の半導体チップの前記第4の表面との間の隙間に充填された樹脂とを具備し、

前記第2のバンプ接続部は、前記第2の半導体チップ内に設けられた貫通電極を介して、前記第1のバンプ接続部と電気的に接続されており、

前記第1の接着用突起は、前記第1の表面の前記第1の非接続領域および前記第2の表面の前記第2の非接続領域の少なくとも一方の領域に設けられ、前記第1の非接続領域および前記第2の非接続領域の少なくとも他方の領域には、絶縁膜が設けられており、

前記第2の接着用突起は、前記第3の表面の前記第3の非接続領域および前記第4の表面の前記第4の非接続領域の少なくとも一方の領域に設けられ、前記第3の非接続領域および前記第4の非接続領域の少なくとも他方の領域には、絶縁膜が設けられていることを特徴とする半導体装置。

【請求項2】

第1の接続領域と、前記第1の接続領域を除く第1の非接続領域とを備える第1の表面を有する第1の半導体チップと、

前記第1の接続領域と対向する第2の接続領域と、前記第2の接続領域を除く第2の非接続領域とを備える第2の表面を有し、前記第1の半導体チップ上に積層された第2の半導体チップと、

前記第1の半導体チップと前記第2の半導体チップとを電気的に接続するように、前記第1の表面の前記第1の接続領域と前記第2の表面の前記第2の接続領域との間に設けられた第1のバンプ接続部と、

前記第1の表面の前記第1の非接続領域および前記第2の表面の前記第2の非接続領域の少なくとも一方の領域に局所的に設けられ、かつ前記第1の非接続領域および前記第2の非接続領域の他方の領域と非接着状態で接触する第1のストッパ用突起と、

前記第1の表面の前記第1の非接続領域と前記第2の表面の前記第2の非接続領域との間に局所的に設けられ、前記第1および第2の表面に接着された第1の接着用突起と、

前記第1の半導体チップの前記第1の表面と前記第2の半導体チップの前記第2の表面との間の隙間に充填された第1の樹脂と

を具備することを特徴とする半導体装置。

【請求項3】

さらに、前記第2の半導体チップ上に積層された第3の半導体チップを具備し、

前記第2の半導体チップは、第3の接続領域と、前記第3の接続領域を除く第3の非接続領域とを備え、前記第2の表面とは反対側の第3の表面を有し、

前記第3の半導体チップは、前記第3の接続領域と対向する第4の接続領域と、前記第4の接続領域を除く第4の非接続領域とを備える第4の表面を有し、かつ前記第2の半導体チップ上に積層されており、

前記第2の半導体チップと前記第3の半導体チップとは、前記第3の表面の前記第3の接続領域と前記第4の表面の前記第4の接続領域との間に設けられた第2のバンプ接続部により電気的に接続されており、

前記第2の半導体チップの前記第3の表面と前記第3の半導体チップの前記第4の表面との間には、前記第3の表面の前記第3の非接続領域および前記第4の表面の前記第4の非接続領域の少なくとも一方の領域に局所的に設けられ、かつ前記第3の非接続領域および前記第4の非接続領域の他方の領域と非接着状態で接触する第2のストッパ用突起が配置されており、

前記第3の表面の前記第3の非接続領域と前記第4の表面の前記第4の非接続領域との間には、前記第3および第4の表面に接着された第2の接着用突起が局所的に配置されており、

前記第2の半導体チップの前記第3の表面と前記第3の半導体チップの前記第4の表面との間の隙間には第2の樹脂が充填されている、請求項2に記載の半導体装置。

【請求項4】

第1の接続領域と、前記第1の接続領域を除く第1の非接続領域とを備える第1の表面を有する第1の半導体チップと、

前記第1の接続領域と対向する第2の接続領域と、前記第2の接続領域を除く第2の非接続領域とを備える第2の表面を有し、前記第1の半導体チップ上に積層された第2の半導体チップと、

前記第1の半導体チップと前記第2の半導体チップとを電気的に接続するように、前記第1の表面の前記第1の接続領域と前記第2の表面の前記第2の接続領域との間に設けられた第1のバンプ接続部と、

前記第1の表面の前記第1の非接続領域および前記第2の表面の前記第2の非接続領域の少なくとも一方の領域に局所的に設けられ、かつ前記第1の非接続領域および前記第2の非接続領域の他方の領域に接着された第1のストッパ兼接着用突起と、

前記第1の半導体チップの前記第1の表面と前記第2の半導体チップの前記第2の表面との間の隙間に充填された第1の樹脂と

を具備することを特徴とする半導体装置。

【請求項5】

さらに、前記第2の半導体チップ上に積層された第3の半導体チップを具備し、

前記第2の半導体チップは、第3の接続領域と、前記第3の接続領域を除く第3の非接続領域とを備え、前記第2の表面とは反対側の第3の表面を有し、

前記第3の半導体チップは、前記第3の接続領域と対向する第4の接続領域と、前記第4の接続領域を除く第4の非接続領域とを備える第4の表面を有し、かつ前記第2の半導体チップ上に積層されており、

前記第2の半導体チップと前記第3の半導体チップとは、前記第3の表面の前記第3の接続領域と前記第4の表面の前記第4の接続領域との間に設けられた第2のバンプ接続部により電気的に接続されており、

前記第2の半導体チップの前記第3の表面と前記第3の半導体チップの前記第4の表面との間には、前記第3の表面の前記第3の非接続領域および前記第4の表面の前記第4の非接続領域の少なくとも一方の領域に局所的に設けられ、かつ前記第3の非接続領域および前記第4の非接続領域の他方の領域に接着された第2のストッパ兼接着用突起が配置されており、

前記第2の半導体チップの前記第3の表面と前記第3の半導体チップの前記第4の表面との間の隙間には第2の樹脂が充填されている、請求項4に記載の半導体装置。

【請求項6】

第1の接続領域と、前記第1の接続領域を除く第1の非接続領域と、前記第1の接続領域に設けられた第1のバンプ電極とを備える第1の表面を有する第1の半導体チップを用意する工程と、

前記第1の接続領域に対応する第2の接続領域と、前記第2の接続領域を除く第2の非接続領域と、前記第2の接続領域に設けられた第2のバンプ電極とを備える第2の表面を有する第2の半導体チップを用意する工程と、

前記第1の表面の前記第1の非接続領域および前記第2の表面の前記第2の非接続領域の少なくとも一方の領域に、第1のストッパ用突起および第1の接着用突起、あるいは第1のストッパ兼接着用突起を局所的に形成する工程と、

前記第1のバンプ電極と前記第2のバンプ電極とを位置合わせしつつ、前記第1の半導体チップ上に前記第2の半導体チップを積層する工程と、

前記第1のストッパ用突起または前記第1のストッパ兼接着用突起で前記第1の半導体チップの前記第1の表面と前記第2の半導体チップの前記第2の表面との間の隙間を維持しつつ、前記第1のバンプ電極と前記第2のバンプ電極とを接触させて加熱し、前記第1のバンプ電極と前記第2のバンプ電極とを接続すると共に、前記第1の接着用突起または前記第1のストッパ兼接着用突起を前記第1の非接続領域および前記第2の非接続領域の他方の領域に接着する工程と、

前記第1の半導体チップの前記第1の表面と前記第2の半導体チップの前記第2の表面との間の隙間に第1の樹脂を充填する工程と

を具備することを特徴とする半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【公開番号】特開2013−8963(P2013−8963A)

【公開日】平成25年1月10日(2013.1.10)

【国際特許分類】

【出願番号】特願2012−119530(P2012−119530)

【出願日】平成24年5月25日(2012.5.25)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

【公開日】平成25年1月10日(2013.1.10)

【国際特許分類】

【出願日】平成24年5月25日(2012.5.25)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

[ Back to top ]