半導体装置の作製方法

【課題】簡単な工程で絶縁膜、半導体膜、導電膜等の膜パターンを有する基板を作製する方法を提供する。また、層間絶縁膜、平坦化膜、ゲート絶縁膜等の絶縁膜、配線、電極、端子等の導電膜、半導体膜等の半導体素子の各部位の膜を形成する方法を提供する。また、低コストで、スループットや歩留まりの高い半導体装置の作製方法を提供する。

【解決手段】ガリウムと亜鉛を含む液滴を吐出して、基板上に膜パターンを形成する。または、印刷法により、基板上にガリウムと亜鉛を含む材料を用いて膜パターンを形成する。

【解決手段】ガリウムと亜鉛を含む液滴を吐出して、基板上に膜パターンを形成する。または、印刷法により、基板上にガリウムと亜鉛を含む材料を用いて膜パターンを形成する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、インクジェット法に代表される液滴吐出法を用いて形成した半導体素子を有

する半導体装置の作製方法、また半導体素子の各部位の膜、マスクパターン及びコンタク

トホールを形成する技術に関するものである。

【背景技術】

【0002】

半導体装置の作製において、設備の低コスト化、工程の簡略化を目的として、半導体素

子に用いられる薄膜や配線のパターン形成に、液滴吐出装置を用いることが検討されてい

る。

【0003】

その際、半導体素子におけるコンタクトホールを形成するにあたっては、レジストを基

板全面に塗布形成しプリベークを行った後、マスクパターンを介して紫外線等を照射し、

現像によってレジストパターンを形成するというフォトリソグラフィー工程を経た後、該

レジストパターンをマスクパターンとしてコンタクトホールとなるべき部分に存在する絶

縁膜をエッチング除去することにより、コンタクトホールを形成する方法が用いられてい

る。

【0004】

また、レジストパターンを用いて、半導体膜、絶縁膜、金属膜等をエッチングして所望

の形状の膜パターンを形成している。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2000−89213号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

しかしながら、従来のコンタクトホールを有する絶縁膜、膜パターン等の形成工程にお

いて、膜パターン及びレジストの材料の大部分が無駄になると共に、マスクパターン形成

するための工程数が多く、スループットが低下するという問題がある。

【0007】

また、コンタクトホールを開孔する際に、レジストの塗布量及び下地の表面状態の制御

が不十分だと、コンタクトホール部分にもレジストが広がってしまい、コンタクト不良が

発生してしまう可能性がある。

【0008】

本発明は、このような問題点に鑑みてなされたものであり、簡単な工程で絶縁膜、半導

体膜、導電膜等の膜パターンを有する基板を作製する方法、さらには、低コストで、スル

ープットや歩留まりの高い半導体装置の作製方法を提供することを目的とする。

【課題を解決するための手段】

【0009】

本発明の一は、基板上に塗れ性の低い第1の保護膜(以下、マスクパターンと示す。)

を形成した後、前記第1のマスクパターンの外縁に塗れ性の高い材料を塗布又は吐出して

膜パターン、及び該膜パターンを有する基板を形成することを特徴とする。

【0010】

また、本発明の一は、基板上に塗れ性の低い第1のマスクパターンを形成した後、前記

第1のマスクパターンを除く領域に塗れ性の高い材料を塗布又は吐出して膜パターン、及

び該膜パターンを有する基板を形成することを特徴とする。

【0011】

また、本発明の一は、基板上に塗れ性の低い第1のマスクパターンを形成した後、前記

第1のマスクパターンが形成されない領域に塗れ性の高い材料を塗布又は吐出して膜パタ

ーン、及び該膜パターンを有する基板を形成することを特徴とする。

【0012】

また、本発明の一は、薄膜又は部材上に塗れ性の低い第1のマスクパターンを形成した

後、塗れ性の高い第2のマスクパターンを形成し、第1のマスクパターン及び該第1のマ

スクパターンで覆われた薄膜又は部材を除去し、膜パターン又はコンタクトホールを有す

る絶縁膜を形成することを特徴とする。なお、この後、第2のマスクパターンを除去する

ことも可能である。

【0013】

塗れ性の低い第1のマスクパターンは液体を弾きやすい。一方、塗れ性の高い第2の

マスクパターンは液体が塗れ広がる。第1のマスクパターンの表面では第2のマスクパタ

ーンの材料となる溶液が半球状にはじかれるため、自己整合的に第2のマスクパターンを

形成することができる。

【0014】

塗れ性の低い第1のマスクパターンとしては、絶縁膜にフッ素プラズマを照射して形成

することができる。フッ素プラズマは、フッ素又はフッ化物の雰囲気内でプラズマを発生

させる方法、又はフッ素樹脂を有する誘電体を有する電極を用いてプラズマを発生させる

方法等がある。

【0015】

また、塗れ性の低い第1のマスクパターンを形成する方法としては、塗れ性の低い材料

を所定の場所吐出又は塗布して形成することができる。塗れ性の低い材料としては、フッ

化炭素鎖を有する化合物が挙げられる。

【0016】

塗れ性の低い第1のマスクパターンと塗れ性の高い第2のマスクパターンの接触角の差

は、30度、望ましくは40度以上であることが好ましい。この結果、第1のマスクパタ

ーンの表面で第2のマスクパターンの材料が半球状にはじかれ、自己整合的に各マスクパ

ターンを形成することが可能である。

【0017】

また、第2のマスクパターンは、膜パターンを形成するマスクとして用いることが好ま

しい。

【0018】

膜パターンとしては、所望の形状を有する絶縁膜、半導体膜、及び導電膜、並びにコン

タクトホールを有する絶縁膜である。代表的には、ゲート絶縁膜、層間絶縁膜、保護膜、

コンタクトホールを有する絶縁膜等の絶縁膜、チャネル形成領域、ソース領域、ドレイン

領域等の半導体膜、及びソース電極、ドレイン電極、配線、ゲート電極、画素電極、アン

テナ等の導電膜が挙げられる。なお、マスクパターンを除去した後、該膜パターンの周辺

(マスクパターンが形成されていた領域)には、マスクパターンの組成物が残存している

。

【0019】

塗れ性の低い第1のマスクパターンは、液相法又は印刷法を用いて形成する。液相法の

代表例としては、液滴吐出法、インクジェット法等が挙げられる。

【0020】

また、塗れ性の高い第2のマスクパターンは、液相法を用いて形成する。液相法の代表

例としては、液滴吐出法、インクジェット法、スピンコート法、ロールコート法、スロッ

トコート法等が挙げられる。

【0021】

また、本発明の一は、塗れ性の低い第1のマスクパターン及び塗れ性の高い第2のマス

クパターンを用いて形成される膜パターン、又は部材を用いて半導体素子を形成すること

を特徴とする。半導体素子としては、TFT、電界効果トランジスタ(FET)、MOS

トランジスタ、バイポーラトランジスタ、有機半導体トランジスタ、MIM素子、記憶素

子、ダイオード、光電変換素子、容量素子、抵抗素子等が挙げられる。

【0022】

また、本発明の一は、塗れ性の低い第1のマスクパターン及び塗れ性の高い第2のマス

クパターンを用いて形成される膜パターン、該膜パターン付基板、又は半導体素子を有す

る半導体装置、及びその作製方法を特徴とする。半導体装置としては、半導体素子で構成

された集積回路、表示装置、無線タグ、ICタグ、ICカード等が挙げられる。表示装置

としては、代表的には液晶表示装置、発光表示装置、DMD(Digital Micromirror Devi

ce;デジタルマイクロミラーデバイス)、PDP(Plasma Display Panel;プラズマディ

スプレイパネル)、FED(Field Emission Display;フィールドエミッションディスプ

レイ)、電気泳動表示装置(電子ペーパー)等の表示装置があげられる。なお、TFTは

、順スタガ型TFT、逆スタガ型TFT(チャネルエッチ型TFT又はチャネル保護型T

FT)、トップゲートのコプレナー型TFT、ボトムゲートのコプレナー型TFT等であ

る。

【0023】

なお、本発明において、表示装置とは、表示素子を用いたデバイス、即ち画像表示デバ

イスを指す。また、表示パネルにコネクター、例えばフレキシブルプリント配線(FPC

:Flexible Printed Circuit)もしくはTAB(Tape A

utomated Bonding)テープもしくはTCP(Tape Carrier

Package)が取り付けられたモジュール、TABテープやTCPの先にプリント

配線板が設けられたモジュール、または表示素子にCOG(Chip On Glass

)方式によりIC(集積回路)やCPUが直接実装されたモジュールも全て表示装置に含

むものとする。

【0024】

また、本発明の一は、上記膜パターン、それを有する基板、半導体素子、又は半導体装

置を有する液晶テレビジョン、若しくはELテレビジョンである。

【0025】

また、本発明の一は、親液表面上に撥液表面を形成する材料を用いてマスクパターンを

形成した後、マスクパターンの外縁に親液性を示す材料を用いて膜パターン、及び該膜パ

ターンを有する基板を形成することを特徴とする。

【0026】

また、本発明の一は、親液表面上に撥液表面を形成する材料を用いてマスクパターンを

形成した後、マスクパターンを除く領域に親液性を示す材料を用いて膜パターン、及び膜

パターンを有する基板を形成することを特徴とする。

【0027】

また、本発明の一は、親液表面上に撥液表面を形成する材料を用いてマスクパターンを

形成した後、マスクパターンを除く領域に親液性を示す材料を用いて膜パターン、及び膜

パターンを有する基板を形成することを特徴とする。

【0028】

また、本発明の一は、親液表面を有する膜又は部材上に撥液表面を形成する材料を用い

て第1のマスクパターンを形成した後、親液性を示す材料を用いて第2のマスクパターン

を形成し、第1のマスクパターン及び該第1のマスクパターンで覆われた親液表面を有す

る膜又は部材を除去して、膜パターン又はコンタクトホールを形成することを特徴とする

。なお、この後、第2のマスクパターンを除去することも可能である。

【0029】

膜パターンとしては、所望の形状を有する絶縁膜、半導体膜、及び導電膜、並びにコン

タクトホールを有する絶縁膜である。代表的には、ゲート絶縁膜、層間絶縁膜、保護膜、

コンタクトホールを有する絶縁膜等の絶縁膜、チャネル形成領域、ソース領域、ドレイン

領域等の半導体膜、及びソース電極、ドレイン電極、配線、ゲート電極、画素電極、アン

テナ等の導電膜が挙げられる。なお、マスクパターンを除去した後、該膜パターンの周辺

(マスクパターンが形成されていた領域)には、マスクパターンの組成物が残存している

。

【0030】

撥液表面を形成する材料の代表例としては、Rn−Si−X(4-n)(n=1、2、3)の

化学式で表されるシランカップリング剤があげられる。ここで、Rは、アルキル基などの

比較的不活性な基を含む物である。また、Xはハロゲン、メトキシ基、エトキシ基又はア

セトキシ基など、基質表面の水酸基あるいは吸着水との縮合により結合可能な加水分解基

からなる。

【0031】

また、シランカップリング剤として、Rにフルオロアルキル基を有するフッ素系シラン

カップリング剤(フルオロアルキルシラン(FAS))は、より撥液性が高い撥液表面を

形成する。

【0032】

また、撥液表面を形成する材料の代表例として、フッ素炭素鎖を有する材料(代表的に

は、フッ素系樹脂)があげられる。

【0033】

また、撥液表面を形成する溶媒としては、nーペンタン、n−ヘキサン、n−ヘプタン

、n−オクタン、n−デカン、ジシクロペンタン、ベンゼン、トルエン、キシレン、デュ

レン、インデン、テトラヒドロナフタレン、デカヒドロナフタレン、スクワランなどの炭

化水素系溶媒又はテトラヒドロフランなどである。

【0034】

また、撥液表面形成する材料に、プラズマ、レーザ又は電子ビーム等の処理を施すこと

によって、撥液性をより向上させることができる。

【0035】

親液性を示す材料としては、親液表面と加水分解により結合することが可能な置換基(

水酸基、水素基)、又は水素結合をすることが可能な置換基(水酸基、水素基、カルボニ

ル基、アミノ基、スルホニル基、エーテル基等)を有する材料である。代表的には、アク

リル樹脂、ポリイミド樹脂、メラミン樹脂、ポリエステル樹脂、ポリカーボネート樹脂、

フェノール樹脂、エポキシ樹脂、ポリアセタール、ポリエーテル、ポリウレタン、ポリア

ミド(ナイロン)、フラン樹脂、ジアリルフタレート樹脂等の有機樹脂、シロキサン、ポ

リシラザンを用いることができる。シロキサンとは、珪素(Si)と酸素(O)との結合

で骨格構造が構成され、置換基に少なくとも水素を含む、又は置換基にフッ素、アルキル

基、又は芳香族炭化水素のうち少なくとも1種を有するポリマー材料である。またポリシ

ラザンとは、珪素(Si)と窒素(N)の結合を有するポリマー材料である。

【0036】

親液表面とは、極性を示す反応基を表面に有するものであり、代表的には加水分解によ

り結合することが可能な置換基(水酸基、水素基)、又は水素結合することが可能な置換

基(水酸基、水素基、カルボニル基、アミノ基、スルホニル基、エーテル基等)を有する

。

【0037】

撥液表面を形成する材料で形成されるマスクパターンは、液相法を用いて形成する。液

相法の代表例としては、液滴吐出法、インクジェット法等が挙げられる。

【0038】

また、親液性を示す溶液で形成されるマスクパターン又は膜パターンは、液相法を用い

て形成する。液相法の代表例としては、液滴吐出法、インクジェット法、スピンコート法

、ロールコート法、スロットコート法等が挙げられる。

【0039】

また、本発明は、撥液表面を形成する材料で形成されるマスクパターンを用いて形成さ

れる膜パターン、又は部材を用いて半導体素子を形成することを特徴とする。半導体素子

としては、TFT、電界効果トランジスタ(FET)、MOSトランジスタ、バイポーラ

トランジスタ、有機半導体トランジスタ、MIM素子、記憶素子、ダイオード、光電変換

素子、容量素子、抵抗素子等が挙げられる。

【0040】

また、本発明は、撥液表面を有するマスクパターンを用いて形成される膜パターン、該

膜パターン付基板、又は半導体素子を有する半導体装置、及びその作製方法を特徴とする

。半導体装置としては、半導体素子で構成された集積回路、表示装置、無線タグ、ICタ

グ等が挙げられる。表示装置としては、代表的には液晶表示装置、発光表示装置、DMD

(Digital Micromirror Device;デジタルマイクロミラーデバイス)、PDP(Plasma D

isplay Panel;プラズマディスプレイパネル)、FED(Field Emission Display;フィ

ールドエミッションディスプレイ)、電気泳動表示装置(電子ペーパー)等の表示装置が

あげられる。なお、TFTは、順スタガ型TFT、逆スタガ型TFT(チャネルエッチ型

TFT又はチャネル保護型TFT)である。

【0041】

なお、本発明において、表示装置とは、表示素子を用いたデバイス、即ち画像表示デバ

イスを指す。また、表示パネルにコネクター、例えばフレキシブルプリント配線(FPC

:Flexible Printed Circuit)もしくはTAB(Tape A

utomated Bonding)テープもしくはTCP(Tape Carrier

Package)が取り付けられたモジュール、TABテープやTCPの先にプリント

配線板が設けられたモジュール、または表示素子にCOG(Chip On Glass

)方式によりIC(集積回路)やCPU(中央演算装置:Central Proces

sing Unit)が直接実装されたモジュールも全て表示装置に含むものとする。

【0042】

また、本発明は、上記膜パターン、それを有する基板、半導体素子、又は半導体装置を

有する液晶テレビジョン、ELテレビジョンである。

【発明の効果】

【0043】

本発明のごとく、塗れ性の低い第1のマスクパターン及び塗れ性の高い第2のマスクパ

ターンを用いることにより、所望の形状を有する膜パターンを所望の箇所に形成すること

ができる。層間絶縁膜、平坦化膜、ゲート絶縁膜等として機能する膜を、所望の箇所に選

択的に形成することができる。しかも、レジストマスクパターンを用いた露光・現像プロ

セス等を経ることなく膜パターン、コンタクトホールを有する絶縁膜を形成できるため、

従来と比較して、工程を大幅に簡略化することができる。

【0044】

また、塗れ性の低いマスクパターンに対してプラズマ、レーザ又は電子ビーム等の処理

を施すことによって、塗れ性をより低下させることができる。

【0045】

また、撥液表面を形成する材料で形成されるマスクパターンを用いることにより、所望

の形状を有する膜パターンを所望の箇所に形成することができる。層間絶縁膜、平坦化膜

、ゲート絶縁膜等として機能する膜を、所望の箇所に選択的に形成することができる。し

かも、レジストマスクパターンを用いた露光・現像プロセス等を経ることなく膜パターン

、コンタクトホールを有する絶縁膜を形成できるため、従来と比較して、工程を大幅に簡

略化することができる。また、マスクパターンは撥液表面を有するため、親液性の材料で

形成される膜は形成されないため、該マスクパターンの除去を容易にし、良好なコンタク

トホールを簡略なプロセスで形成することができる。

【0046】

また、撥液表面を形成する材料で形成されるマスクパターンに対してプラズマ、レーザ

又は電子ビーム等の処理を施すことによって、撥液性をより向上させることができる。

【0047】

また、塗れ性の低いマスクパターンや、撥液表面を形成する材料で形成されるマスクパ

ターン、導電膜等を形成する際に、液滴吐出法を用いることによって、それらの膜の材料

を含む液滴の吐出口であるノズルと基板との相対的な位置を変化させることで任意の場所

に液滴を吐出でき、ノズル径、液滴の吐出量及びノズルと吐出物が形成される基板との移

動速度の相対的な関係によって、形成するパターンの厚さや太さを調整できるため、それ

らの膜を所望の箇所に精度良く吐出形成することができる。また、パターニング工程、す

なわちマスクパターンを用いた露光・現像プロセスを省略することができるため、工程の

大幅な簡略化及びコストの低減を図ることが可能となる。また、液滴吐出法を用いること

により、任意の場所にパターンを形成でき、形成するパターンの厚さや太さを調整できる

ので、一辺が1〜2mを越えるような大面積の半導体素子基板も、低コストで歩留まり良

く製造することができる。

【0048】

このように、本発明を用いることによって、膜パターン、膜パターンを有する基板、コ

ンタクトホールを有する絶縁膜、さらには、それらを有する半導体素子、及び半導体装置

を、簡単な工程で精度良く形成することができ、さらには、低コストで、スループットや

歩留まりの高い半導体素子、半導体装置の作製方法を提供することができる。

【図面の簡単な説明】

【0049】

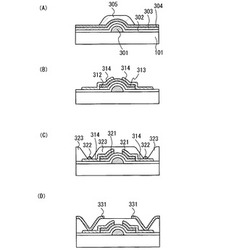

【図1】本発明に係る膜パターンを形成する工程を説明する断面図。

【図2】本発明に係る膜パターンを形成する工程を説明する断面図。

【図3】本発明に係る半導体装置の作製工程を説明する断面図。

【図4】本発明に係る半導体装置の作製工程を説明する断面図。

【図5】本発明に係る半導体装置の作製工程を説明する断面図。

【図6】本発明に係る半導体装置の作製工程を説明する断面図。

【図7】本発明に係る膜パターンを形成する工程を説明する断面図。

【図8】本発明に係る半導体装置の作製工程を説明する断面図。

【図9】本発明に係る半導体装置の作製工程を説明する断面図。

【図10】本発明に係る半導体装置の作製工程を説明する断面図。

【図11】本発明に係る半導体装置の作製工程を説明する上面図。

【図12】本発明に係る半導体装置の作製工程を説明する上面図。

【図13】本発明に係る半導体装置の作製工程を説明する上面図。

【図14】本発明に係る表示装置の駆動回路の実装方法を説明する上面図。

【図15】本発明に係る表示装置の駆動回路の実装方法を説明する断面図。

【図16】本発明に係る液晶表示モジュールの構成を説明する図。

【図17】電子機器の構成を説明するブロック図。

【図18】電子機器の一例を説明する図。

【図19】電子機器の一例を説明する図。

【図20】本発明に適用することのできる液滴吐出装置の構成を説明する図。

【図21】本発明に係る液晶表示パネルにおいて走査線側駆動回路をTFTで形成する場合の回路構成を示す図。

【図22】本発明に係る液晶表示パネルにおいて走査線側駆動回路をTFTで形成する場合の回路構成を示す図(シフトレジスタ回路)。

【図23】本発明に係る液晶表示パネルにおいて走査線側駆動回路をTFTで形成する場合の回路構成を示す図(バッファ回路)。

【図24】本発明に係る膜パターンを形成する工程を説明する断面図。

【図25】本発明に係る半導体装置の作製工程を説明する断面図。

【図26】本発明に係る半導体装置の作製工程を説明する断面図。

【図27】本発明に係る半導体装置の作製工程を説明する断面図。

【図28】本発明に適用することのできる液晶滴下方法を説明する図。

【図29】塗れ性の低い領域及び塗れ性の高い領域の接触角を説明する図。

【図30】本発明に係る発光表示モジュールの構成を説明する図。

【図31】本発明に適用可能な発光素子の形態を説明する図。

【図32】本発明に係る膜パターンを形成する工程を説明する断面図。

【図33】本発明に係る膜パターンを形成する工程を説明する断面図。

【図34】本発明に係る膜パターンを形成する工程を説明する断面図。

【発明を実施するための形態】

【0050】

以下、発明を実施するための最良の形態について図面を参照しながら説明する。但し、

本発明は多くの異なる態様で実施することが可能であり、本発明の趣旨及びその範囲から

逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解

される。従って、本発明は本実施の形態の記載内容に限定して解釈されるものではない。

また、各図面において共通の部分は同じ符号を付して詳しい説明を省略する。

【0051】

(第1実施形態)

本実施形態においては、塗れ性の低いマスクパターンを用いて所望の形状を有する膜パタ

ーンを形成する工程を、図1を用いて示す。なお、本実施形態で示すマスクパターンは、

膜パターンを形成するために用いるマスクパターンである。

【0052】

図1(A)に示すように、基板101上に、第1の膜102を成膜する。この上に、液

滴吐出法、インクジェット法等により塗れ性の低い第1のマスクパターン103を形成す

る。ここでは、マスクパターンの形成方法として液滴吐出法を用いる。

【0053】

基板101としては、ガラス基板、石英基板、アルミナなど絶縁物質で形成される基板

、後工程の処理温度に耐え得る耐熱性を有するプラスチック基板、シリコンウェハ、金属

板等を用いることができる。この場合、酸化シリコン(SiOx)、窒化シリコン(Si

Nx)、酸化窒化シリコン(SiOxNy)(x>y)、窒化酸化シリコン(SiNxO

y)(x>y)など、基板側から不純物などの拡散を防止するための絶縁膜を形成してお

くことが望ましい。また、ステンレスなどの金属または半導体基板などの表面に酸化シリ

コンや窒化シリコンなどの絶縁膜を形成した基板なども用いることができる。また、基板

101として、320mm×400mm、370mm×470mm、550mm×650

mm、600mm×720mm、680mm×880mm、1000mm×1200mm

、1100mm×1250mm、1150mm×1300mmのような大面積基板を用い

ることができる。ここでは、基板101としてガラス基板を用いる。

【0054】

なお、基板101にプラスチック基板を用いる場合、PC(ポリカーボネート)、PE

S(ポリエチレンスルホン)、PET(ポリエチレンテレフタレート)もしくはPEN(

ポリエチレンナフタレート)等のガラス転移点が比較的高いものを用いることが好ましい

。

【0055】

第1の膜102としては、スパッタリング法、蒸着法、CVD法、塗布法等により形成

された絶縁膜、導電膜、半導体膜のいずれをも用いることができる。絶縁膜で形成される

第1の膜102は、公知の無機絶縁材料、又は有機絶縁材料を適宜用いる。代表例として

は、ポリイミド、ポリアミド、ポリエステル、アクリル、PSG(リンガラス)、BPS

G(リンボロンガラス)、ポリシラザン系SOGや、シリケート系SOG(Spin on Glas

s)、アルコキシシリケート系SOG、シロキサンポリマーに代表されるSi−CH3結合

を有するSiO2等を、液滴吐出法、塗布法、印刷法により形成することができる。また

、窒化珪素、窒化酸化珪素、酸化珪素等をPVD法(Physical Vapor Deposition)、C

VD法(Chemical Vapor Deposition)、熱酸化法により形成することができる。また、

Ag、Cu、Ni、Pt、Pd、Ir、Rh、W、Al、Ta、Mo、Cd、Zn、Fe

、Ti、Si、Ge、Zr、Ba等の金属酸化物を、蒸着法、陽極酸化法等により形成す

ることができる。ここでは、スパッタリング法により酸化珪素膜を成膜する。

【0056】

導電膜で形成される第1の膜102の材料としては、Ag、Au、Cu、Ni、Pt、

Pd、Ir、Rh、W、Al、Ta、Mo、Cd、Zn、Fe、Ti、Si、Ge、Zr

、Ba等の金属又はその合金、若しくはその金属窒化物、さらには透明導電膜として用い

られる酸化インジウムスズ(ITO)、酸化亜鉛(ZnO)、酸化インジウム亜鉛(IZ

O)、ガリウムを添加した酸化亜鉛(GZO)、酸化珪素を含む酸化インジウムスズ、有

機インジウム、有機スズ等の材料を適宜用いて形成することができる。また、1〜20%

のニッケルを含むアルミニウムを用いることができる。ここでは、第1の導電膜をアルミ

ニウムで形成する。

【0057】

半導体膜で形成される第1の膜102の材料としては、シリコン、シリコン・ゲルマニ

ウム(SiGe)等を用いた非晶質半導体、非晶質状態と結晶状態とが混在したセミアモ

ルファス半導体、非晶質半導体中に0.5nm〜20nmの結晶粒を観察することができ

る微結晶半導体、及び結晶性半導体から選ばれたいずれの状態を有する膜を形成すること

ができる。また、ポリチエニレンビニレン、ポリ(2,5−チエニレンビニレン)、ポリ

アセチレン、ポリアセチレン誘導体、ポリアリレンビニレンなどの有機半導体材料を用い

て形成しても良い。

【0058】

ここでは、第1の膜として、酸化珪素膜をCVD法により形成する。

【0059】

第1のマスクパターンは、後に形成する膜パターンを形成するためのマスクとして機能

する。このため、塗れ性が低いことが好ましい。

【0060】

第1のマスクパターン103の形成方法としては、所定の場所に塗れ性の高い絶縁膜を

形成し、該表面にフッ素プラズマを照射して形成する。また、誘電体が設けられた電極を

用意し、誘電体が空気、酸素又は窒素を用いたプラズマに曝されるようにプラズマを発生

させてプラズマ処理を行うことができる。この場合、誘電体が電極表面全体を覆う必要は

ない。誘電体としては、フッ素系樹脂を用いることができる。フッ素系樹脂を用いる場合

、絶縁膜表面にCF2結合が形成されることにより表面改質が行われ、塗れ性が低下する

。

【0061】

絶縁膜の材料として、ポリビニルアルコール(PVA)のような水溶性樹脂を、H2O

等の溶媒に混合した材料を用いることができる。また、PVAと他の水溶性樹脂を組み合

わせて使用してもよい。また、アクリル樹脂、ポリイミド樹脂、メラミン樹脂、ポリエス

テル樹脂、ポリカーボネート樹脂、フェノール樹脂、エポキシ樹脂、ポリアセタール、ポ

リエーテル、ポリウレタン、ポリアミド(ナイロン)、フラン樹脂、ジアリルフタレート

樹脂、レジスト等の有機樹脂などを用いることができる。

【0062】

絶縁膜の作製方法としては、液滴吐出法、スクリーン(孔版)印刷、オフセット(平版

)印刷、凸版印刷やグラビア(凹版)印刷等が挙げられ、これらにより所定の領域に形成

することができる。

【0063】

また、第1のマスクパターン103は、塗れ性の低い材料を塗布又は吐出して形成する

ことができる。塗れ性の低い材料の代表例としては、フッ化炭素鎖を有する化合物が挙げ

られる。フッ化炭素鎖を有する化合物の組成物の一例としては、Rn−Si−X(4-n)(

n=1、2、3)の化学式で表されるシランカップリング剤が挙げられる。ここで、Rは

、アルキル基などの比較的不活性な基を含む物である。また、Xはハロゲン、メトキシ基

、エトキシ基又はアセトキシ基など、基質表面の水酸基あるいは吸着水との縮合により結

合可能な加水分解基からなる。

【0064】

また、シランカップリング剤の代表例として、Rにフルオロアルキル基を有するフッ素

系シランカップリング剤(フルオロアルキルシラン(FAS))を用いることにより、塗

れ性を低下させることができる。FASのRは、(CF3)(CF2)x(CH2)y(x:

0以上10以下の整数、y:0以上4以下の整数)で表される構造を持ち、複数個のR又

はXがSiに結合している場合には、R又はXはそれぞれすべて同じでも良いし、異なっ

ていてもよい。代表的なFASとしては、ヘプタデカフルオロテトラヒドロデシルトリエ

トキシシラン、ヘプタデカフルオロテトラヒドロデシルトリクロロシラン、トリデカフル

オロテトラヒドロオクチルトリクロロシラン、トリフルオロプロピルトリメトキシシラン

等のフルオロアルキルシラン(以下、FASという。)が挙げられる。

【0065】

塗れ性の低い溶媒としては、nーペンタン、n−ヘキサン、n−ヘプタン、n−オクタ

ン、n−デカン、ジシクロペンタン、ベンゼン、トルエン、キシレン、デュレン、インデ

ン、テトラヒドロナフタレン、デカヒドロナフタレン、スクワランなどの炭化水素系溶媒

又はテトラヒドロフランなどを用いる。

【0066】

また、塗れ性の低い材料の組成物の一例として、フッ化炭素鎖を有する材料(フッ素系

樹脂)を用いることができる。フッ素系樹脂として、ポリテトラフルオロエチレン(PT

FE;四フッ化エチレン樹脂)、パーフルオロアルコキシアルカン(PFA;四フッ化エ

チレンパーフルオロアルキルビニルエーテル共重合樹脂)、パーフルオロエチレンプロピ

レンコーポリマー(PFEP;四フッ化エチレン−六フッ化プロピレン共重合樹脂)、エ

チレン−テトラフルオロエチレンコポリマー(ETFE;四フッ化エチレン−エチレン共

重合樹脂)、ポリビニリデンフルオライド(PVDF;フッ化ビニリデン樹脂)、ポリク

ロロトリフルオロエチレン(PCTFE;三フッ化塩化エチレン樹脂)、エチレン−クロ

ロトリフルオロエチレンコポリマー(ECTFE;三フッ化塩化エチレン−エチレン共重

合樹脂)、ポリテトラフルオロエチレン−パーフルオロジオキソールコポリマー(TFE

/PDD)、ポリビニルフルオライド(PVF;フッ化ビニル樹脂)等を用いることがで

きる。

【0067】

続いて、塗れ性の低い材料が付着した表面をエタノール洗浄すると、極めて膜厚が薄く

塗れ性の低い第1のマスクパターンを形成することができる。

【0068】

微細な形状を有する膜パターンを形成する場合、図7(A)に示すように、第1の膜1

02上に形成する第1のマスクパターン103の形状は、閉曲線状のものが好ましい。こ

の場合、図7(B)に示すように閉曲線状のマスクパターンの内側に、塗れ性の高い材料

111を吐出し、乾燥または焼成を行う。この結果、図7(C)に示すように、任意の形

状で塗れ性の高い膜パターン121を形成することができる。図7(C)において、マス

クパターンは除去され、薄膜表面上にマスクパターンの組成物122が残存している。

【0069】

液滴吐出手段に用いるノズルの径は、0.1〜50μm(好適には0.6〜26μm)

に設定し、ノズルから吐出される組成物の吐出量は0.00001pl〜50pl(好適

には0.0001〜10pl)に設定する。この吐出量は、ノズルの径の大きさに比例し

て増加する。また、被処理物とノズル吐出口との距離は、所望の箇所に滴下するために、

できる限り近づけておくことが好ましく、好適には0.1〜2mm程度に設定する。

【0070】

なお、液滴吐出法に用いる組成物の粘度は300mPa・s以下が好適であり、これは

、乾燥が起こることを防止し、吐出口から組成物を円滑に吐出できるようにするためであ

る。なお、用いる溶媒や用途に合わせて、組成物の粘度、表面張力等は適宜調整するとよ

い。

【0071】

次に、図1(B)に示すように、第1の膜102上であって、且つ第1のマスクパター

ン103の間に、第1のマスクパターンと比較して塗れ性の高い材料111を塗布する。

【0072】

ここで、図29を用いて塗れ性の低い領域と塗れ性の高い領域の関係について示す。塗

れ性の低い領域103とは、図29に示すように、第1の膜102表面において液体の接

触角θ1が大きい領域である。この表面上では液体は、半球状にはじかれる。一方、塗れ

性の高い領域104(図1(B)では、塗れ性の高い材料111で形成される領域)は、

第1の膜102表面において液体の接触角θ2が小さい領域である。この表面上では、液

体は塗れ広がる。

【0073】

このため、接触角の異なる二つの領域が接している場合、相対的に接触角の小さい領域

が塗れ性が高い領域となり、接触角の大きい方の領域が塗れ性が低い領域となる。この二

つの領域上に溶液を塗布又は吐出した場合、溶液は、塗れ性が高い領域表面に塗れ広がり

、塗れ性が低い領域との界面で半球状にはじかれる。

【0074】

塗れ性の低い領域の接触角θ1と塗れ性の高い領域の接触角θ2の差は、30度、望ま

しくは40度以上であることが好ましい。この結果、塗れ性の低い領域の表面で塗れ性の

高い領域の材料が半球状にはじかれ、自己整合的に各マスクパターンを形成することが可

能である。このため、第1のマスクパターン103の形成方法及び材料で列挙されたもの

の中で、互いの接触角の差が30度、望ましくは40度以上の場合、接触角の小さい材料

で形成された領域は塗れ性の高い領域となり、接触角の大きい材料で形成された領域は塗

れ性の低い領域となりうる。同様に、後に塗れ性の高い材料111として列挙されるもの

の中で、互いの接触角の差が30度、望ましくは40度以上の場合、接触角の小さい材料

で形成された領域は塗れ性の高い領域となり、接触角の大きい材料で形成された領域は塗

れ性の低い領域となりうる。

【0075】

なお、表面が凹凸を有する場合、塗れ性が低い領域ではさらに接触角が増大する。即ち

、塗れ性がより低下する。一方、塗れ性が高い領域では、さらに接触角が低下する。即ち

、塗れ性がより向上する。このため、凹凸を有する各表面上に塗れ性の低い材料と塗れ性

の高い材料を塗布又は吐出し、焼成することにより、端部が均一な膜を形成することがで

きる。

【0076】

塗れ性の高い材料111としては、第1のマスクパターンと比較して塗れ性の高い絶縁

材料、導電材料、及び半導体材料を適宜用いることができる。絶縁材料の代表例として、

アクリル樹脂、ポリイミド樹脂、メラミン樹脂、ポリエステル樹脂、ポリカーボネート樹

脂、フェノール樹脂、エポキシ樹脂、ポリアセタール、ポリエーテル、ポリウレタン、ポ

リアミド(ナイロン)、フラン樹脂、ジアリルフタレート樹脂等の有機樹脂、シロキサン

ポリマー、ポリシラザン、PSG(リンガラス)、BPSG(リンボロンガラス)、を用

いることができる。

【0077】

また、水、アルコール系、エーテル系、ジメチルホルムアミド、ジメチルアセトアミド

、ジメチルスルホキシド、N−メチルピロリドン、ヘキサメチルホスファミド、クロロホ

ルム、塩化メチレン等の極性溶媒を用いた溶液を用いることもできる。

【0078】

また、導電材料の代表例として、導電体を溶媒に溶解又は分散させたものを用いること

ができる。導電体としては、Ag、Au、Cu、Ni、Pt、Pd、Ir、Rh、W、A

l、Ta、Mo、Cd、Zn、Fe、Ti、Si、Ge、Zr、Ba等の金属、又はハロ

ゲン化銀の微粒子や分散性ナノ粒子を用いることができる。または、透明導電膜として用

いられるITO、酸化珪素を含むITO、有機インジウム、有機スズ、酸化亜鉛(ZnO

)、窒化チタン(TiN:Titanium Nitride)等を用いることができる。

【0079】

さらには、上記導電体の複数が溶解又は分散された導電体を用いることもできる。

【0080】

また、半導体材料の代表例として、有機半導体材料を用いることができる。有機半導体

材料としては、その骨格が共役二重結合から構成されるπ電子共役系の高分子材料が望ま

しい。代表的には、ポリチオフェン、ポリ(3−アルキルチオフェン)、ポリチオフェン

誘導体、ペンタセン等の可溶性の高分子材料を用いることができる。

【0081】

第1のマスクパターンと比較して塗れ性の高い材料を塗布する方法としては、液滴吐出

法、インクジェット法、スピンコート法、ロールコート法、スロットコート法等を適用す

ることができる。

【0082】

次に、図1(C)に示すように、第1のマスクパターンと比較して塗れ性の高い材料を

乾燥、焼成して膜パターン121を形成する。この結果、塗れ性の高い材料が絶縁材料の

場合、膜パターンは所望の形状を有する絶縁膜となる。また、塗れ性の高い材料が導電材

料の場合、膜パターンは所望の形状を有する導電膜となる。また、塗れ性の高い材料が半

導体材料の場合、膜パターンは所望の形状を有する半導体膜となる。なお、該工程におい

て、第1のマスクパターンの溶媒は蒸発し、組成物は第1の膜102の表面に残存又は膜

中に浸透する。なお、第1の膜表面に残存した組成物は、酸素を用いたアッシング、ウエ

ットエッチング、ドライエッチング等の公知のエッチング方法により除去することができ

る。図1(C)においては、122は、第1の膜中に浸透したマスクパターンの組成物を

示す。この工程において、乾燥及び焼成は適宜塗れ性の高い材料にあわせて行えばよい。

【0083】

なお、上記の工程に代えて、第1のマスクパターンの溶媒を乾燥した後、適宜塗れ性の

高い材料を塗布してもよい。すなわち、図24(A)に示すように、第1の膜102上に

塗れ性の低い材料を用いて第1のマスクパターン103を形成した後、図24(B)に示

すように、第1のマスクパターンを乾燥する。このとき、第1のマスクパターンの組成物

は第1の膜102の表面に残存又は膜中に浸透する。図24(B)において、122は、

第1の膜にマスクパターンの組成物が浸透した領域である。次に、図24(C)に示すよ

うに、第1のマスクパターンと比較して塗れ性の高い材料121を塗布する。この場合は

、第1のマスクパターンが形成されていた領域には、第1のマスクパターンの組成物62

2が残存しているため、図24(C)に示すように、第1のマスクパターンと比較して塗

れ性の高い材料は弾かれ、選択的に塗布される。この後、第1のマスクパターンと比較し

て塗れ性の高い材料を、適宜乾燥又は焼成することで膜パターン121が形成される。

【0084】

以上の工程により、公知のフォトリソグラフィー工程を用いずとも、所望の形状を有す

る膜パターンを形成することができる。このため、作製工程数を大幅に削減することが可

能である。

【0085】

(第2実施形態)

本実施形態においては、撥液表面を形成する材料で形成されるマスクパターンを用いて所

望の形状を有する膜パターンを形成する工程を、図32を用いて示す。なお、本実施形態

で示すマスクパターンは、膜パターンを形成するために用いるマスクパターンである。

【0086】

図32(A)に示すように、基板1001上に、第1の膜1002を成膜する。この上

に、液滴吐出法、インクジェット法等により保護膜(第1のマスクパターン)1003を

形成する。ここでは、マスクパターンの形成方法として液滴吐出法を用いる。第1の膜1

002としては、親液表面を有する膜であることが好ましい。なお、基板1001表面が

親液性を示す場合、第1の膜は成膜する必要はない。

【0087】

基板1001としては、ガラス基板、石英基板、アルミナなど絶縁物質で形成される基

板、後工程の処理温度に耐え得る耐熱性を有するプラスチック基板、シリコンウェハ、金

属板等を用いることができる。この場合、酸化シリコン(SiOx)、窒化シリコン(S

iNx)、酸化窒化シリコン(SiOxNy)(x>y)、窒化酸化シリコン(SiNx

Oy)(x>y)など、基板側から不純物などの拡散を防止するための絶縁膜を形成して

おくことが望ましい。また、ステンレスなどの金属または半導体基板などの表面に酸化シ

リコンや窒化シリコンなどの絶縁膜を形成した基板なども用いることができる。

【0088】

第1のマスクパターン1003としては、撥液表面を形成する溶液を用いて形成する。撥

液表面を形成する溶液の組成物の一例としては、Rn−Si−X(4-n)(n=1、2、3)

の化学式で表されるシランカップリング剤を用いる。ここで、Rは、アルキル基などの比

較的不活性な基を含む物である。また、Xはハロゲン、メトキシ基、エトキシ基又はアセ

トキシ基など、基質表面の水酸基あるいは吸着水との縮合により結合可能な加水分解基か

らなる。

【0089】

また、シランカップリング剤の代表例として、Rにフルオロアルキル基を有するフッ素

系シランカップリング剤(フルオロアルキルシラン(FAS))を用いることにより、よ

り撥液性を高めることができる。FASのRは、(CF3)(CF2)x(CH2)y(x:

0以上10以下の整数、y:0以上4以下の整数)で表される構造を持ち、複数個のR又

はXがSiに結合している場合には、R又はXはそれぞれすべて同じでも良いし、異なっ

ていてもよい。代表的なFASとしては、ヘプタデカフルオロテトラヒドロデシルトリエ

トキシシラン、ヘプタデカフルオロテトラヒドロデシルトリクロロシラン、トリデカフル

オロテトラヒドロオクチルトリクロロシラン、トリフルオロプロピルトリメトキシシラン

等のフルオロアルキルシラン(以下、FASという。)が挙げられる。

【0090】

撥液表面を形成する溶液の溶媒としては、nーペンタン、n−ヘキサン、n−ヘプタン

、n−オクタン、n−デカン、ジシクロペンタン、ベンゼン、トルエン、キシレン、デュ

レン、インデン、テトラヒドロナフタレン、デカヒドロナフタレン、スクワランなどの炭

化水素系溶媒又はテトラヒドロフランなど、撥液表面を形成する溶媒を用いる。

【0091】

また、撥液表面を形成する溶液の組成物の一例として、フッ素炭素鎖を有する材料(フ

ッ素系樹脂)を用いることができる。フッ素系樹脂として、ポリテトラフルオロエチレン

(PTFE;四フッ化エチレン樹脂)、パーフルオロアルコキシアルカン(PFA;四フ

ッ化エチレンパーフルオロアルキルビニルエーテル共重合樹脂)、パーフルオロエチレン

プロピレンコーポリマー(PFEP;四フッ化エチレン−六フッ化プロピレン共重合樹脂

)、エチレン−テトラフルオロエチレンコポリマー(ETFE;四フッ化エチレン−エチ

レン共重合樹脂)、ポリビニリデンフルオライド(PVDF;フッ化ビニリデン樹脂)、

ポリクロロトリフルオロエチレン(PCTFE;三フッ化塩化エチレン樹脂)、エチレン

−クロロトリフルオロエチレンコポリマー(ECTFE;三フッ化塩化エチレン−エチレ

ン共重合樹脂)、ポリテトラフルオロエチレン−パーフルオロジオキソールコポリマー(

TFE/PDD)、ポリビニルフルオライド(PVF;フッ化ビニル樹脂)等を用いるこ

とができる。

【0092】

また、マスクパターンとして撥液表面を形成しない(即ち、親液表面を形成する)有機

物を用い、後にCF4プラズマ等による処理を行って、撥液表面を形成してもよい。例え

ば、ポリビニルアルコール(PVA)のような水溶性樹脂を、H2O等の溶媒に混合した

材料を用いることができる。また、PVAと他の水溶性樹脂を組み合わせて使用してもよ

い。さらには、マスクパターンが撥液表面を有する場合であっても、該プラズマ処理等を

行うことによって、撥液性をより向上させることができる。

【0093】

微細な形状を有する膜を形成する場合、図33(A)に示すように、親液表面を有する

第1の膜1002上に形成する第1のマスクパターン1003の形状は、閉曲線状のもの

が好ましい。この場合、図33(B)に示すように閉曲線状のマスクパターンの内側に、

後に示す第2の溶液1011を吐出し、乾燥または焼成を行う。この結果、図33(C)

に示すように、任意の形状の膜パターン1021を形成することができる。図33(C)

において、マスクパターンは除去され、親液性を有する表面上にマスクパターンの組成物

1022が残存している。

【0094】

液滴吐出手段に用いるノズルの径は、0.1〜50μm(好適には0.6〜26μm)

に設定し、ノズルから吐出される組成物の吐出量は0.00001pl〜50pl(好適

には0.0001〜10pl)に設定する。この吐出量は、ノズルの径の大きさに比例し

て増加する。また、被処理物とノズル吐出口との距離は、所望の箇所に滴下するために、

できる限り近づけておくことが好ましく、好適には0.1〜2mm程度に設定する。

【0095】

なお、液滴吐出法に用いる組成物の粘度は300mPa・s以下が好適であり、これは

、乾燥が起こることを防止し、吐出口から組成物を円滑に吐出できるようにするためであ

る。なお、用いる溶媒や用途に合わせて、組成物の粘度、表面張力等は適宜調整するとよ

い。

【0096】

次に、図32(B)に示すように、第1のマスクパターン1003の間に、第2の溶液

1011を塗布する。第2の溶液としては、親液性を有する溶液が挙げられる。親液性を

有する溶液の代表例としては、アクリル樹脂、ポリイミド樹脂、メラミン樹脂、ポリエス

テル樹脂、ポリカーボネート樹脂、フェノール樹脂、エポキシ樹脂、ポリアセタール、ポ

リエーテル、ポリウレタン、ポリアミド(ナイロン)、フラン樹脂、ジアリルフタレート

樹脂等の有機樹脂、シロキサン、ポリシラザンを用いることができる。また、水、アルコ

ール系、エーテル系、ジメチルホルムアミド、ジメチルアセトアミド、ジメチルスルホキ

シド、N−メチルピロリドン、ヘキサメチルホスファミド、クロロホルム、塩化メチレン

等の極性溶媒を用いた溶液を用いることもできる。第2の溶液を塗布する方法としては、

液滴吐出法、インクジェット法、スピンコート法、ロールコート法、スロットコート法等

を適用することができる。

【0097】

次に、図32(C)に示すように、第2の溶液111を乾燥、焼成して膜パターン10

21を形成する。なお、該工程において、マスクパターンの溶媒は蒸発し、組成物は第1

の膜1002の表面に残存又は膜中に浸透する。なお、第1の膜表面に残存した組成物は

、酸素を用いたアッシング、ウエットエッチング、ドライエッチング等の公知のエッチン

グ方法により除去することができる。図32(C)においては、1022は、第1の膜中

に浸透したマスクパターンの組成物を示す。この工程において、乾燥及び焼成は適宜第2

の溶液の材料にあわせて行えばよい。

【0098】

なお、上記の工程に代えて、第1のマスクパターンの溶媒を乾燥した後、第2の溶液を

塗布してもよい。すなわち、図34(A)に示すように、第1の膜1002上に撥液表面

を形成する溶液を用いて第1のマスクパターン103を形成した後、図34(B)に示す

ように、第1のマスクパターンを乾燥する。このとき、マスクパターンの組成物は第1の

膜102の表面に残存又は膜中に浸透する。図34(B)において、1022は、第1の

膜にマスクパターンの組成物が浸透した領域である。次に、図34(C)に示すように、

親液性の第2の溶液1011を塗布する。この場合は、マスクパターンが形成されていた

領域には、第1のマスクパターンの組成物1022が残存しているため、図34(C)に

示すように、第2の溶液は、弾かれ選択的に塗布される。この後、第2の溶液1011を

、適宜乾燥、焼成して第2の膜パターン1021を形成する。

【0099】

以上の工程により、公知のフォトリソグラフィー工程を用いずとも、所望の形状を有す

る膜パターンを形成することができる。このため、作製工程数を大幅に削減することが可

能である。

【0100】

(第3実施形態)

以下の実施形態及び実施例においては、第1実施形態を用いて説明する。しかしながら、

適宜第2実施形態を適用することが可能である。

【0101】

本実施形態においては、塗れ性の低い第1のマスクパターン及び塗れ性の高い第2のマ

スクパターンを用いて所望の形状を有する膜パターンを形成する工程を、図2を用いて示

す。なお、本実施形態で示す第1のマスクパターンは、第2のマスクパターンを形成する

ために用いるマスクパターンであり、第2のマスクパターンはエッチング用マスクパター

ンである。

【0102】

図2(A)に示すように、第1の基板101上に第1の膜201を形成し、第1の膜2

01上に第2の膜202を形成する。第1の膜の材料としては、適宜用いることができる

。また、第2の膜としては、第1実施形態の第1の膜102と同様の材料を用いることが

できる。

【0103】

次に、第2の膜202上に、液滴吐出法により塗れ性の低い材料を塗布して塗れ性の低

い第1のマスクパターン103を形成する。このとき、塗れ性の低い材料に適宜あわせて

、塗れ性の低い材料を乾燥及び焼成する。

【0104】

次に、図2(B)に示すように、塗れ性の高い材料を塗布して、塗れ性の高い第2のマ

スクパターン212を形成する。塗れ性の高い材料は、塗れ性の低い材料と比較して塗れ

性が高いため、第1のマスクパターン103と接触した部分が弾かれ、図2(B)に示す

ように、第1のマスクパターンが形成されていない領域に塗れ性の高い材料が塗布される

。塗れ性の高い材料を塗布する方法としては、液滴吐出法、インクジェット法、スピンコ

ート法、ロールコート法、スロットコート法等を適用することができる。この後、必要に

応^じて塗れ性の高い材料を乾燥し焼成する。この結果、エッチング用マスクパターンで

ある第2のマスクパターン212を形成することができる。

【0105】

次に、図2(C)に示すように、第1のマスクパターン103を除去する。本実施形態

では、アッシングにより第1のマスクパターン103を除去する。この後、第2の膜の露

出した領域をドライエッチング、ウエットエッチング等の公知の手法によりエッチングし

て、所望の形状を有する膜パターン221を形成することができる。なお、第1のマスク

パターンが柱状又は円柱状である場合、膜パターンは、コンタクトホールを有する膜とな

る。

【0106】

なお、図2(D)に示すように、第2のマスクパターン212を除去し、所望の形状を

有する膜パターン221を露出してもよい。

【0107】

以上の工程により、公知のフォトリソグラフィー工程を用いずとも、マスクパターンを

形成することができる。このため、従来より少ない工程数で膜を所望の形状にエッチング

することが可能である。また、従来より少ない工程数で、膜パターン又は良好なコンタク

トホールを形成することも可能である。

【0108】

(第4実施形態)

以下、半導体素子の作製方法について示す。なお、以下の実施形態では、半導体素子と

してTFTを用いて説明するが、これに限定されるものではなく、有機半導体トランジス

タ、ダイオード、MIM素子、記憶素子、ダイオード、光電変換素子、容量素子、抵抗素

子等を用いることができる。

【0109】

本実施形態では、本発明を用いて半導体素子として逆スタガ型TFTの代表例としてチ

ャネルエッチ型TFTを形成する工程を、図3を用いて説明する。

【0110】

図3(A)に示すように、基板101上にゲート電極301を形成する。ゲート電極の

形成方法としては、液滴吐出法、印刷法、電界メッキ法、PVD法、CVD法を用いて導

電膜を形成する。なお、PVD法またはCVD法を用いて導電膜を形成する場合、第3実

施形態の手法またはフォトリソグラフィー工程によって、導電膜上にマスクパターンを形

成し、所望の形状にエッチングしてゲート電極を形成する。本実施形態においては、液滴

吐出法を用いて、基板101上に導電材料を含む組成物を選択的に吐出する。この場合、

マスクパターンを用いたエッチング工程が不要となるので、作製工程を大幅に簡略化する

ことができる。

【0111】

液滴吐出法でゲート電極を形成する場合、吐出口から吐出する組成物は、第1実施形態

で塗れ性の低い材料に列挙した導電体を溶媒に溶解又は分散させたものを用いることがで

きる。また、導電膜を積層してゲート電極301を形成することができる。

【0112】

なお、吐出口から吐出する組成物は、比抵抗値を考慮して、金、銀、銅のいずれかの材

料を溶媒に溶解又は分散させたものを用いることが好ましい。より好ましくは、低抵抗且

つ安価な銀又は銅を用いるとよい。但し、銅を用いる場合には、不純物対策のため、合わ

せてバリア膜を設けるとよい。溶媒は、酢酸ブチル、酢酸エチル等のエステル類、イソプ

ロピルアルコール、エチルアルコール等のアルコール類、メチルエチルケトン、アセトン

等の有機溶剤等を用いればよい。

【0113】

ここで、銅を配線として用いる場合のバリア膜としては、窒化シリコン、酸化窒化シリ

コン、窒化アルミニウム、窒化チタン、窒化タンタル(TaN:Tantalum Nitride)など

窒素を含む絶縁性又は導電性の物質を用いると良く、これらを液滴吐出法で形成しても良

い。

【0114】

なお、液滴吐出法に用いる組成物の粘度は5〜20mPa・sが好適であり、これは、

乾燥が起こることを防止し、吐出口から組成物を円滑に吐出できるようにするためである

。また、表面張力は40mN/m以下が好ましい。なお、用いる溶媒や用途に合わせて、

組成物の粘度等は適宜調整するとよい。一例として、酸化インジウムスズ(ITO)、酸

化亜鉛(ZnO)、酸化インジウム亜鉛(IZO)、ガリウムを添加した酸化亜鉛(GZ

O)、酸化珪素を含む酸化インジウムスズ、有機スズを溶媒に溶解又は分散させた組成物

の粘度は5〜20mPa・s、銀を溶媒に溶解又は分散させた組成物の粘度は5〜20m

Pa・s、金を溶媒に溶解又は分散させた組成物の粘度は10〜20mPa・sである。

【0115】

各ノズルの径や所望のパターン形状などに依存するが、ノズルの目詰まり防止や高精細

なパターンの作製のため、導電体の粒子の径はなるべく小さい方が好ましく、好適には粒

径0.1μm以下が好ましい。組成物は、電解法、アトマイズ法又は湿式還元法等の公知

の方法で形成されるものであり、その粒子サイズは、一般的に約0.5〜10μmである

。ただし、ガス中蒸発法で形成すると、分散剤で保護されたナノ分子は約7nmと微細で

あり、またこのナノ粒子は、被覆剤を用いて各粒子の表面を覆うと、溶剤中に凝集がなく

、室温で安定に分散し、液体とほぼ同じ挙動を示す。したがって、被覆剤を用いることが

好ましい。

【0116】

組成物を吐出する工程は、減圧下で行っても良い。これは、組成物を吐出して被処理物

に着弾するまでの間に、該組成物の溶媒が揮発し、後の乾燥と焼成の工程を省略又は短く

することができるためである。溶液の吐出後は、溶液の材料により、常圧下又は減圧下で

、レーザ光の照射や瞬間熱アニール、加熱炉等により、乾燥と焼成の一方又は両方の工程

を行う。乾燥と焼成の工程は、両工程とも加熱処理の工程であるが、例えば、乾燥は10

0度で3分間、焼成は200〜350度で15分間〜120分間で行うもので、その目的

、温度と時間が異なるものである。乾燥と焼成の工程を良好に行うためには、基板を加熱

しておいてもよく、そのときの温度は、基板等の材質に依存するが、100〜800度(

好ましくは200〜350度)とする。本工程により、溶液中の溶媒の揮発又は化学的に

分散剤を除去し、周囲の樹脂が硬化収縮することで、融合と融着を加速する。雰囲気は、

酸素雰囲気、窒素雰囲気又は空気で行う。但し、金属元素を分解又は分散している溶媒が

除去されやすい酸素雰囲気下で行うことが好適である。

【0117】

なお、液滴吐出法により形成した導電膜は、導電体である微粒子が3次元に不規則に重

なり合って形成されている。即ち、3次元凝集体粒子で構成されている。このため、表面

は微細な凹凸を有する。また、導電膜の温度及びその加熱時間により、微粒子が溶融し微

粒子の集合体となる。このときの集合体の大きさは、導電膜の温度及びその加熱時間によ

り増大するため、表面の高低差が大きい膜となる。なお、微粒子が溶融した領域は、多結

晶構造となる場合もある。

【0118】

また、加熱温度、雰囲気、時間により導電膜には、有機物で形成されるバインダーが残存

する。

【0119】

レーザ光の照射は、連続発振またはパルス発振の気体レーザ又は固体レーザを用いれば

良い。前者の気体レーザとしては、エキシマレーザ、YAGレーザ等が挙げられ、後者の

固体レーザとしては、Cr、Nd等がドーピングされたYAG、YVO4等の結晶を使っ

たレーザ等が挙げられる。なお、レーザ光の吸収率の関係から、連続発振のレーザを用い

ることが好ましい。また、パルス発振と連続発振を組み合わせた所謂ハイブリッドのレー

ザ照射方法を用いてもよい。但し、基板の耐熱性に依っては、レーザ光の照射による加熱

処理は、数マイクロ秒から数十秒の間で瞬間に行うとよい。瞬間熱アニール(RTA)は

、不活性ガスの雰囲気下で、紫外光乃至赤外光を照射する赤外ランプやハロゲンランプな

どを用いて、急激に温度を上昇させ、数マイクロ秒から数分の間で瞬間的に熱を加えて行

う。この処理は瞬間的に行うために、実質的に最表面の薄膜のみを加熱することができ、

下層の膜には影響を与えないという利点がある。

【0120】

次に、ゲート電極301にゲート絶縁膜302を形成する。ゲート絶縁膜302はプラ

ズマCVD法またはスパッタリング法などの薄膜形成法を用い、窒化シリコン、酸化シリ

コン、その他の珪素を含む絶縁膜の単層又は積層構造で形成する。また、ゲート絶縁膜を

ゲート電極に接する側から、窒化珪素膜(窒化酸化珪素膜)、酸化珪素膜、及び窒化珪素

膜(窒化酸化珪素膜)の積層構造とすることが好ましい。この構造では、ゲート電極が、

窒化珪素膜と接しているため、酸化による劣化を防止することができる。

【0121】

次に、ゲート絶縁膜302上に、第1の半導体膜303を形成する。第1の半導体膜3

03としては、非晶質半導体、非晶質状態と結晶状態とが混在したセミアモルファス半導

体(SASとも表記する)、非晶質半導体中に0.5nm〜20nmの結晶粒を観察する

ことができる微結晶半導体、及び結晶性半導体から選ばれたいずれの状態を有する膜で形

成する。特に、0.5nm〜20nmの結晶を粒観察することができる微結晶状態はいわ

ゆるマイクロクリスタル(μc)と呼ばれている。いずれも、シリコン、シリコン・ゲル

マニウム(SiGe)等を主成分とする膜厚は、10〜60nmの半導体膜を用いること

ができる。

【0122】

SASは、非晶質構造と結晶構造(単結晶、多結晶を含む)との中間的な構造を有し、自

由エネルギー的に安定な第3の状態を有する半導体である。また短距離秩序を持ち格子歪

みを有する結晶質な領域を含んでいる。そして少なくとも膜中の一部の領域には、0.5

〜20nmの結晶領域を観測することができ、珪素を主成分とする場合にはラマンスペク

トルが520cm-1よりも低波数側にシフトしている。X線回折では珪素結晶格子に由来

するとされる(111)、(220)の回折ピークが観測される。また未結合手(ダング

リングボンド)の中和剤として、SASは水素或いはハロゲンを1原子%、又はそれ以上

含んでいる。

【0123】

SASは、珪化物気体をグロー放電分解することにより得ることができる。代表的な珪化

物気体としては、SiH4であり、その他にもSi2H6、SiH2Cl2、SiHCl3、S

iCl4、SiF4などを用いることができる。珪化物気体を水素、水素とヘリウム、アル

ゴン、クリプトン、ネオンから選ばれた一種又は複数種の希ガス元素で希釈して用いるこ

とによりSASの形成を容易なものとすることができる。このとき希釈率が10倍〜10

00倍の範囲となるように、珪化物気体を希釈すると好ましい。またSi2H6及びGeF

4を用い、ヘリウムガスで希釈する方法を用いてSASを形成することができる。グロー

放電分解による被膜の反応生成は減圧下で行うと好ましく、圧力は概略0.1Pa〜13

3Paの範囲で行えばよい。グロー放電を形成するための電力は1MHz〜120MHz

、好ましくは13MHz〜60MHzの高周波電力を供給すればよい。基板加熱温度は3

00度以下が好ましく、100〜250度の基板加熱温度が推奨される。

【0124】

また結晶性半導体膜は、非晶質半導体膜を加熱又はレーザ照射により結晶化して形成する

ことができる。また、直接、結晶性半導体膜を形成してもよい。この場合、GeF4、又

はF2等のフッ素系ガスと、SiH4、又はSi2H6等のシラン系ガスとを用い、熱又はプ

ラズマを利用して直接、結晶性半導体膜を形成することができる。

【0125】

次に、導電性を有する第2の半導体膜304を成膜する。導電性を有する第2の半導体

膜304はnチャネル型のTFTを形成する場合には、15属の元素、代表的にはリンま

たはヒ素を添加する。また、pチャネルTFTを形成する場合には、13属の元素、代表

的にはボロンを添加する。第2の半導体膜は、珪化物気体にボロン、リン、ヒ素のような

13属又は15属の元素を有する気体を加えたプラズマCVD法で成膜する。また、半導

体膜を成膜したのち、13属または15属の元素を有する溶液を半導体膜上に塗布しレー

ザ光を照射して導電性を有する第2の半導体膜を形成することができる。レーザ光として

は、公知のパルス発振のレーザ又は連続発振のレーザから照射されるレーザ光を適宜用い

る。

【0126】

次に、導電性を有する第2の半導体膜304の上に、第1のマスクパターン305を液

滴吐出法により形成する。この第1のマスクパターン305は、耐熱性高分子材料を用い

て形成することが好ましく、芳香環、複素環を主鎖にもち、脂肪族部分が少なく高極性の

ヘテロ原子基を含む高分子を用いることが好ましい。そのような高分子物質の代表例とし

てはポリイミド又はポリベンゾイミダゾールなどが挙げられる。ポリイミドを用いる場合

には、ポリイミドを含む組成物を、ノズルから第2の半導体膜304上に吐出し、200

℃で30分焼成して形成することができる。

【0127】

次に、図3(B)に示すように、第1のマスクパターン305を用いて、第1の半導体

膜303及び第2の半導体膜304をエッチングし、所望の形状を有する第1の半導体領

域312及び第2の半導体領域313を形成する。エッチング用ガスとしては、Cl2、

BCl3、SiCl4もしくはCCl4などを代表とする塩素系ガス、CF4、SF6、NF3

、CHF3などを代表とするフッ素系ガス、あるいはO2を用いることができる。第1のマ

スクパターン305は、エッチング後に除去する。

【0128】

次に、第2の半導体領域313上に、ソース電極及びドレイン電極314を、導電材

料を液滴吐出法によって吐出することにより形成する。導電材料としては、ゲート電極3

01に用いた材料と同様の材料を、溶媒に溶解又は分散させたものを用いることができる

。ここでは、Agを含む組成物(以下「Agペースト」という。)を選択的に吐出し、上

記に示すようなレーザ光照射又は熱処理による乾燥及び焼成を適宜行い膜厚600〜80

0nmの各電極を形成する。

【0129】

なお、この焼成をO2雰囲気中で行うと、Agペースト内に含まれているバインダー(

熱硬化性樹脂)などの有機物が分解され、有機物をほとんど含まないAg膜を得ることが

できる。また、膜表面を平滑にすることができる。さらに、Agペーストを減圧下で吐出

することにより、ペースト中の溶媒が揮発するため、後の加熱処理を省略、又は加熱処理

時間を短縮することができる。

【0130】

なお、ソース電極及びドレイン電極314は、導電膜を予めスパッタ法等によって成膜

しておき、マスクパターンを液滴吐出法によって形成した後に、エッチングにより形成し

てもよい。このマスクパターンも、上述した材料を用いて形成することができる。

【0131】

次に、図3(C)に示すように、ソース電極及びドレイン電極314をマスクとして、

第2の半導体領域をエッチングして第1の半導体領域312を露出する。ここでは、エッ

チングして分断された第2の半導体領域を第3の半導体領域321と示す。なお、エッチ

ング条件は、上で述べた条件を適宜適用する。また、本実施形態では、ソース電極及びド

レイン電極を用いて第2の半導体領域をエッチングしたが、この工程に限定されるもので

はなく、上記に示したマスクパターンを形成して該半導体膜をエッチングしてもよい。

【0132】

なお、第1の半導体領域312を、有機半導体材料を用い、印刷法、スプレー法、スピ

ン塗布法、液滴吐出法などで形成することができる。この場合、上記エッチング工程が必

要ないため、工程数を削減することが可能である。本発明に用いる有機半導体材料として

は、その骨格が共役二重結合から構成されるπ電子共役系の高分子材料が望ましい。代表

的には、ポリチオフェン、ポリ(3−アルキルチオフェン)、ポリチオフェン誘導体、ペ

ンタセン等の可溶性の高分子材料を用いることができる。

【0133】

その他にも本発明に用いることができる有機半導体材料としては、可溶性の前駆体を成

膜した後で処理することにより第2の半導体領域を形成することができる材料がある。な

お、このような前駆体を経由する有機半導体材料としては、ポリチエニレンビニレン、ポ

リ(2,5−チエニレンビニレン)、ポリアセチレン、ポリアセチレン誘導体、ポリアリ

レンビニレンなどがある。

【0134】

前駆体を有機半導体に変換する際には、加熱処理だけではなく塩化水素ガスなどの反応

触媒を添加することがなされる。また、これらの可溶性有機半導体材料を溶解させる代表

的な溶媒としては、トルエン、キシレン、クロロベンゼン、ジクロロベンゼン、アニソー

ル、クロロホルム、ジクロロメタン、γブチルラクトン、ブチルセルソルブ、シクロヘキ

サン、NMP(N−メチル−2−ピロリドン)、シクロヘキサノン、2−ブタノン、ジオ

キサン、ジメチルホルムアミド(DMF)または、THF(テトラヒドロフラン)などを

適用することができる。

【0135】

なお、第1の半導体領域312に有機半導体を用いた場合、第3の半導体領域321の

代わりに、ポリアセチレン、ポリアニリン、PEDOT(poly-ethlyenedioxythiophen)、

PSS(poly-styrenesulphonate)のような有機導電性材料で形成される導電膜を形成す

ることができる。導電膜は、コンタクト層、又はソース電極及びドレイン電極として機能

する。

【0136】

また、第3の半導体領域321の代わりに、金属元素で形成される導電膜を用いること

ができる。この場合、多くの有機半導体材料が電荷を輸送する材料がキャリアとして正孔

を輸送するp型半導体であることからその半導体膜とオーミック接触を取るために仕事関

数の大きい金属を用いることが望ましい。

【0137】

具体的には、金や白金、クロム、パラジウム、アルミニウム、インジウム、モリブデン

、ニッケル等の金属又は合金等が望ましい。これらの金属又は合金材料を用いた導電性ペ

ーストを用いて印刷法やロールコーター法、液滴吐出法で形成することができる。

【0138】

さらには、有機半導体材料で形成される第1の半導体領域、有機導電性材料で形成され

る導電膜、及び金属元素で形成される導電膜を積層してもよい。

【0139】

なお、第1の半導体領域312がSASで形成されている場合、本実施形態のように、

ソース領域及びドレイン領域がゲート電極を覆っている構造のほかに、ソース領域及びド

レイン領域の端部とゲート電極の端部が一致しているいわゆるセルフアライン構造とする

ことができる。さらには、ソース領域及びドレイン領域がゲート電極を覆わず、一定の距

離を隔てて形成されている構造とすることができる。この構造の場合、オフ電流を低減す

ることができるため、該TFTを表示装置のスイッチング素子として用いた場合、コント

ラストを向上させることができる。さらに、第2の半導体領が域複数のゲート電極を覆う

いわゆるマルチゲート構造のTFTとしても良い。この場合も、オフ電流を低減すること

ができる。

【0140】

次に、ソース電極及びドレイン電極314上に、パッシベーション膜を成膜することが

好ましい。パッシベーション膜は、プラズマCVD法又はスパッタリング法などの薄膜形

成法を用い、窒化珪素、酸化珪素、窒化酸化珪素、酸化窒化珪素、酸化窒化アルミニウム

、または酸化アルミニウム、ダイアモンドライクカーボン(DLC)、窒素含有炭素(C

N)、その他の絶縁性材料を用いて形成することができる。

【0141】

次に、塗れ性の低い第2のマスクパターン322を形成する。第2のマスクパターンは

、後に形成される層間絶縁膜を形成するためのマスクパターンである。第2のマスクパタ

ーンは、第1実施形態に示される第1のマスクパターン103と同様の材料を用いて形成

する。

【0142】

次に、第2のマスクパターン以外の領域に、絶縁性材料を塗布して塗れ性の高い層間絶

縁膜323を形成する。第2のマスクパターン322は層間絶縁膜323と比較して塗れ

性が低く、所望の形状を有する層間絶縁膜が形成される。層間絶縁膜323の材料として

は、アクリル樹脂、ポリイミド樹脂、ポリエステル樹脂、エポキシ樹脂、ポリエーテル、

ポリウレタン,シロキサンポリマー、ポリシラザンを適宜用いることができる。

【0143】

次に、図3(D)に示すように、酸素を用いたアッシングにより第2のマスクパターン

322を除去し、ソース電極及びドレイン電極313、314を露出する。なお、ソース

電極及びドレイン電極上にパッシベーション膜を成膜した場合は、該パッシベーション膜

も除去する。次に、ソース電極及びドレイン電極それぞれに接続する導電膜331を形成

する。ここでは、液滴吐出法により導電材料を溶媒に溶解又は分散したペーストを吐出し

、焼成して導電膜を形成する。導電膜の導電材料としては、ソース電極及びドレイン電極

と同様の材料を用いるこことができる。なお、導電膜331は、接続配線又は画素電極と

して機能する。

【0144】

以上の工程により、チャネルエッチ型TFTを作製することができる。

(第5実施形態)

本実施形態においては、チャネル保護型(チャネルストッパ型)TFTの作製工程につ

いて図4を用いて示す。

【0145】

図4(A)に示すように、第4実施形態と同様に基板101上にゲート電極301、ゲ

ート絶縁膜302、及び第1の半導体膜303を形成する。

【0146】

次に、第1の半導体膜303上であって、且つゲート電極301に重畳する領域に保護

膜401を形成する。形成方法及び材料は、第4実施形態に示す第1のマスクパターン3

05と同様のものを用いることができる。

【0147】

次に、第4実施形態と同様に第2の半導体膜(導電性を有する半導体膜)304を成膜

する。次に、第1のマスクパターン305を第4実施形態と同様に形成する。

【0148】

次に、図4(B)に示すように、第1のマスクパターンを用いて、第1の半導体膜をエ

ッチングして第1の半導体領域312を形成し、第2の半導体膜をエッチングして、第2

の半導体領域313を形成する。次に、第2の半導体領域313上にソース電極及びドレ

イン電極314を形成する。

【0149】

次に、図4(C)に示すように、ソース電極及びドレイン電極314をマスクとして、

第2の半導体領域をエッチングして保護膜401を露出させると共に、第2の半導体膜を

分断し、ソース領域及びドレイン領域321を形成する。なお、本実施形態では、ソース

電極及びドレイン電極を用いて第2の半導体膜をエッチングしたが、この工程に限定され

るものではなく、上記に示した第1のマスクパターンと同様にマスクを形成して該半導体

膜を選択的にエッチングしてもよい。

【0150】

次に、図4(D)に示すように、ソース電極及びドレイン電極314上にパッシベーシ

ョン膜を成膜する。次に、塗れ性の低い第2のマスクパターン322を形成した後、塗れ

性の高い絶縁材料を用いて層間絶縁膜323を形成する。

【0151】

次に、図4(E)に示すように、第2のマスクパターン322を除去した後、第4実施

形態と同様にソース電極及びドレイン電極314に接続する導電膜331を形成する。

【0152】

以上の工程により、チャネル保護型TFTを形成することができる。保護膜401はチ

ャネル保護膜として機能するため、不純物が添加された半導体膜をエッチングする際、チ

ャネル領域となる第1の半導体領域のオーバーエッチング等による損傷を防止することが

できる。これによって、安定した特性で高移動度化が可能なTFTを得ることができる。

【0153】

(第6実施形態)

本実施形態においては、順スタガ型TFTの作製工程について図5を用いて示す。

【0154】

図5(A)に示すように、基板101上にソース電極及びドレイン電極501を形成する

。ソース電極及びドレイン電極501の材料は、第4実施形態に示したソース電極及びド

レイン電極314と同様のものを適宜用いる。形成方法としては、液滴吐出法、印刷法、

電界メッキ法、PVD法、CVD法を用いる。なお、PVD法またはCVD法を用いた場

合、第3実施形態の手法またはフォトリソグラフィー工程によって、マスクパターンを形

成し、所望の形状にエッチングする。

【0155】

次に、13属又は15属の不純物を有する導電性を有する第1の半導体膜502を成膜す

る。第1の半導体膜502は、第4実施形態の第2の半導体膜303と同様の形成方法を

適宜適用する。次に、ソース電極及びドレイン電極501の間及びソース電極及びドレイ

ン電極上の第1の半導体膜502の一部をエッチングするための第1のマスクパターン5

03を形成する。第1のマスクパターンは、第4実施形態の第1のマスクパターン305

と同様の材料及び作製方法を適宜用いて形成する。

【0156】

次に、図5(B)に示すように、第1のマスクパターン503により第1の半導体膜を公

知の手法によりエッチングしてソース領域及びドレイン領域511を形成する。次に、第

2の半導体膜512及びゲート絶縁膜513を順次成膜する。第2の半導体膜512及び

ゲート絶縁膜513はそれぞれ、第4実施形態に示した第1の半導体膜303及びゲート

絶縁膜302の材料及び作製方法を適宜用いる。

【0157】

次に、ソース領域及びドレイン領域511の間にゲート電極514を形成する。次に、第

2のマスクパターン515を形成する。ゲート電極514及び第2のマスクパターン51

5はそれぞれ、第4実施形態に示すゲート電極301及び第1のマスクパターン305の

材料及び形成方法を適宜適用する。

【0158】

次に、図5(C)に示すように、第2のマスクパターン515を用いて、ゲート絶縁膜5

13をエッチングしゲート絶縁膜521を形成し、第2の半導体膜512をエッチングし

て半導体領域522を形成すると共にソース電極及びドレイン電極501の一部を露出す

る。

【0159】

次に、図5(D)に示すように、露出されたソース電極及びドレイン電極501表面に、

塗れ性の低い第3のマスクパターン531を形成した後、塗れ性の高い材料を用いて層間

絶縁膜323を形成する。第3のマスクパターン531は、第4実施形態に示す第2のマ

スクパターン322の材料及び形成方法を適宜用いる。

【0160】

次に、図5(E)に示すように、第3のマスクパターン531を除去した後、導電膜33

1を形成する。

【0161】

以上の工程により、順スタガ型TFTを形成することができる。

【0162】

(第7実施形態)

本実施形態においては、トップゲートのコプレナー構造のTFTの作製工程について図6

を用いて示す。

【0163】

図6(A)に示すように、基板上100に第1の絶縁膜602を成膜する。第1の絶縁

膜としては、基板101からの不純物が後に形成されるTFTに侵入するのを防止するた

めのものであり、酸化珪素膜、窒化珪素膜、酸化窒化珪素膜、窒化酸化珪素膜等の膜を、

PVD法、CVD法等の公知の手法により成膜する。なお、基板101から不純物がTF

Tに侵入しない材料、代表的には石英等で形成されている場合には、第1の絶縁膜602

を成膜する必要はない。

【0164】

次に、第1の絶縁膜602上に半導体領域603を形成する。半導体領域603は、第

4実施形態で示される第1の半導体膜303を、第3実施形態、若しくは公知のエッチン

グ法により所望の形状にエッチングして形成する。

【0165】

次に、半導体領域603上に13属又は15属の不純物を有する溶液604を液滴吐出

法に吐出した後、レーザ光605を照射する。この工程により、図6(B)に示されるよ

うに、導電性を有する半導体領域(ソース領域及びドレイン領域)611を形成すること

ができる。このため、13属又は15属の不純物を有する溶液は、後のソース領域及びド

レイン領域となる半導体領域上に吐出することが好ましい。

【0166】

次に、図6(B)に示すように、ソース領域及びドレイン領域611上に塗れ性の低い

第1のマスクパターン612を形成する。第1のマスクパターン612は、後に形成され

るゲート絶縁膜及び層間絶縁膜の形成を妨げるためのものであるので、後のコンタクトホ

ール及び接続配線を形成する領域に吐出することが好ましい。第1のマスクパターン61

2は、第4実施形態で示される第2のマスクパターン322と同様の材料及び形成方法を

適宜用いる。

【0167】

次に、シロキサンポリマー、ポリシラザン等の有機SOG、無機SOG等の塗れ性の高

い材料を液滴吐出法又は塗布法により形成し、乾燥及び焼成を行ってゲート絶縁膜613

を形成する。なお、有機SOG、無機SOG等は塗れ性が高いため、第1のマスクパター

ン612で弾かれる。また、該工程において、第1のマスクパターン612は乾燥され、

図6(C)に示すように、半導体領域603中又は表面に第1のマスクパターンの組成物

622が残存する。

【0168】

次に、図6(C)に示すように、半導体領域603上において、ソース領域及びドレイ

ン領域611の間であって、ゲート絶縁膜613上にゲート電極621を形成する。ゲー

ト電極621は、第4実施形態に示されるゲート電極301と同様の材料及び作製方法を

適宜用いる。

【0169】

次に、塗れ性の高い絶縁材料を塗布して層間絶縁膜323を形成する。第1のマスクパ

ターンの組成物622は塗れ性が低いため、塗れ性の高い絶縁材料は弾かれる。このため

、選択的に層間絶縁膜323を形成することができる。

【0170】

次に、導電膜331を形成する。

【0171】

以上の工程により、トップゲートのコプレナー構造のTFTを形成することができる。

【0172】

(第8実施形態)

本実施形態においては、トップゲートのコプレナー構造のTFTの作製工程について、

第7実施形態と異なる作製工程を、図25を用いて説明する。第7実施形態では、塗布法

又は液滴吐出法によりゲート絶縁膜を形成したTFTについて述べたが、本実施形態では

、CVD法又はPVD法でゲート絶縁膜を成膜したTFTについて示す。

【0173】

図25(A)に示すように、第7実施形態と同様に半導体領域603を形成し、半導体

領域603上に13属又は15属の不純物を有する溶液604を液滴吐出法に吐出した後

、レーザ光605を照射し、図25(B)に示すように、導電性を有する半導体領域(ソ

ース領域及びドレイン領域)611を形成する。

【0174】

次に、半導体領域及び第1の絶縁膜602上に、CVD法又はPVD法によってゲート

絶縁膜713を成膜する。この場合は、基板表面上全面にゲート絶縁膜が成膜される。次

に、半導体領域603上において、ソース領域及びドレイン領域611の間であって、ゲ

ート絶縁膜713上にゲート電極621を形成する。

【0175】

次に、図25(C)に示すように、ソース領域及びドレイン領域611とゲート絶縁膜

713が重畳する領域に、塗れ性の低い第1のマスクパターン612を形成する。第1の

マスクパターン612は、後に形成される層間絶縁膜の形成を妨げるためのものであるの

で、後のコンタクトホール及び接続配線を形成する領域に吐出することが好ましい。次に

、塗れ性の高い絶縁材料を塗布して層間絶縁膜323を形成する。第1のマスクパターン

は塗れ性が低いため、塗れ性の高い絶縁材料は第1のマスクパターン612に弾かれる。

【0176】

次に、図25(D)に示すように、層間絶縁膜323をマスクとして、酸素を用いたア

ッシングにより第1のマスクパターン612を除去し、ゲート絶縁膜713の一部を露出

する。次に、ゲート絶縁膜の露出された領域をエッチングして、ソース領域及びドレイン

領域を露出する。次に、ソース領域及びドレイン領域それぞれに接続する導電膜331を

形成する。

【0177】

以上の工程により、トップゲートのコプレナー構造のTFTを形成することができる。

また、同様のコンタクトホールを形成する工程及び公知の手法により、ボトムゲートのコ

プレナー構造のTFTを形成することができる。

【0178】

(第9実施形態)

本実施形態では、上記実施形態におけるマスクパターン形成に用いることができる液滴吐

出装置の一態様について説明する。図20において、基板1900上において、1つのパ

ネル1930が形成される領域を点線で示す。

【0179】

液滴吐出手段1905は、ヘッドを有し、ヘッドは複数のノズルを有する。本実施の形

態では、十個のノズルが設けられたヘッドを三つ(1903a、1903b、1903c

)有する場合で説明するが、ノズルの数や、ヘッドの数は処理面積や工程等により設定す

ることができる。

【0180】

ヘッドは、制御手段1907に接続され、制御手段がコンピュータ1910により制御

することにより、予め設定されたパターンを描画することができる。描画するタイミング

は、例えば、ステージ1931上に固定された基板1900等に形成されたマーカー19

11を基準点として行えばよい。また、基板1900の縁を基準点として行ってもよい。

これら基準点をCCDなどの撮像手段1904で検出し、画像処理手段1909にてデジ

タル信号に変換させる。デジタル変化された信号をコンピュータ1910で認識して、制

御信号を発生させて制御手段1907に送る。このようにパターンを描画するとき、パタ

ーン形成面と、ノズルの先端との間隔は、0.1cm〜5cm、好ましくは0.1cm〜

2cm、さらに好ましくは0.1cm前後とするとよい。このように間隔を短くすること

により、液滴の着弾精度が向上する。

【0181】

このとき、基板1900上に形成されるパターンの情報は記憶媒体1908に格納され

ており、この情報を基にして制御手段1907に制御信号を送り、各ヘッド1903a、

1903b、1903cを個別に制御することができる。すなわち、ヘッド1903a、

1903b、1903cが有する各ノズルから異なる組成物を吐出することができる。例

えばヘッド1903a、1903bが有するノズルは絶縁膜材料を有する組成物を吐出し

、ヘッド1903cが有するノズルは導電膜材料を有する組成物を吐出することができる

。

【0182】

さらに、ヘッドが有する各ノズルを個別に制御することもできる。ノズルを個別に制御

することができるため、特定のノズルから異なる材料を有する組成物を吐出することがで

きる。例えば同一ヘッド1903aに、導電膜材料を有する組成物を吐出するノズルと、

絶縁膜材料を有する組成物を吐出するノズルとを設けることができる。

【0183】

なお、ノズルは組成物が充填されたタンクと接続されている。

【0184】

また、層間絶縁膜の形成工程のように大面積に対して液滴吐出処理を行う場合、層間絶

縁膜材料を有する組成物を全ノズルから吐出させるとよい。さらに、複数のヘッドが有す

る全ノズルから、層間絶縁膜材料を有する組成物を吐出するとよい。その結果、スループ

ットを向上させることができる。もちろん、層間絶縁膜形成工程において、一つのノズル

から層間絶縁膜材料を有する組成物を吐出し、複数走査することにより大面積に対して液

滴吐出処理を行ってもよい。

【0185】

そしてヘッドをジグザグ又は往復させ、大型マザーガラスに対するパターン形成を行う

ことができる。このとき、ヘッドと基板を相対的に複数回走査させればよい。ヘッドを基

板に対して走査するとき、進行方向に対してヘッドを斜めに傾けるとよい。

【0186】

ヘッドの幅は、大型マザーガラスから複数のパネルを形成する場合、ヘッドの幅は1つ

のパネルの幅と同程度とすると好ましい。1つのパネル1930が形成される領域に対し

て一回の走査でパターン形成することができ、高いスループットが期待できるからである

。

【0187】

また、ヘッドの幅は、パネルの幅より小さくしてもよい。このとき、複数の幅の小さな

ヘッドを直列に配置し、1つのパネルの幅と同程度としてもよい。複数の幅の小さなヘッ

ドを直列に配置することにより、ヘッドの幅が大きくなるにつれて懸念されるヘッドのた

わみの発生を防止することができる。もちろん、幅の小さなヘッドを複数回走査すること

により、パターン形成を行ってもよい。

【0188】

このような液滴吐出法により溶液の液滴を吐出する工程は、減圧下で行うと好ましい。

溶液を吐出して被処理物に着弾するまでの間に、該溶液の溶媒が蒸発し、溶液の乾燥と焼

成の工程を省略することができるからである。また、減圧下で行うと、導電体の表面に酸

化膜などが形成されないため好ましい。また溶液を滴下する工程は、窒素雰囲気中や有機

ガス雰囲気中で行ってもよい。

【0189】

また、液滴吐出法として、ピエゾ方式を用いることができる。ピエゾ方式は、液滴の制

御性に優れインク選択の自由度の高いことからインクジェットプリンターでも利用されて

いる。なお、ピエゾ方式には、ベンダー型、(代表的にはMLP(Multi Layer Piezo)

タイプ)とピストン型(代表的にはMLChip(Multi Layer Ceramic Hyper Integrat

ed Piezo Segments)タイプ)、サイドウォール型、ルーフウォール型がある。また溶液

の溶媒によっては、発熱体を発熱させ気泡を生じさせ溶液を押し出す、いわゆるサーマル

方式を用いた液滴吐出法でもよい。

【実施例1】

【0190】

次に、アクティブマトリクス基板及びそれを有する表示パネルの作製方法について図8

〜図13を用いて説明する。本実施例では、表示パネルとして液晶表示パネルを用いて説

明する。図8〜10は、画素部及び接続端子部の縦断面構造を模式的に示したものであり

、A−B及びC−Dに対応する平面構造を図11〜13に示す。

【0191】

図8(A)に示すように、基板800表面を400度で酸化して膜厚100nmの絶縁

膜801を形成する。この絶縁膜は、後に形成する導電膜のエッチングストッパー膜の機

能を果たす。次に、絶縁膜801上に第1の導電膜802を成膜し、第1の導電膜上に液

滴吐出法により第1のマスクパターン803〜805を形成する。基板800には、旭硝

子社製AN100ガラス基板を用い、第1の導電膜802には、タングステンターゲット

及びアルゴンガスを用いてスパッタリング法により膜厚100nmのタングステン膜を成

膜する。第1のマスクパターンには、ポリイミドを液滴吐出法により吐出し、200度3

0分加熱して焼成する。第1のマスクパターンは、後に形成されるゲート配線、ゲート電

極及び接続導電膜上に吐出する。

【0192】

次に、図8(B)に示すように、第1のマスクパターン803〜805を用いて第1の

導電膜の一部をエッチングして、ゲート配線811、ゲート電極812、及び接続導電膜

813を形成する。この後、第1のマスクパターン803〜805を、剥離液を用いて剥

離する。

【0193】

次に、プラズマCVD法によりゲート絶縁膜814を成膜する。ゲート絶縁膜814と

しては、400度で加熱したチャンバーでSiH4とN2O(流量比SiH4:N2O=1:

200)を用いたプラズマCVD法により、膜厚110nmの酸化窒化珪素膜(H:1.8

%, N:2.6%, O:63.9%, Si:31.7%)を成膜する。

【0194】

次に、第1の半導体膜815及びn型を呈する第2の半導体膜816を成膜する。第1の

半導体膜815としては、プラズマCVD法により膜厚150nmのアモルファスシリコ

ン膜を成膜する。次に、アモルファスシリコン膜の表面の酸化膜を除去した後、シランガ

スとフォスフィンガスを用いて膜厚50nmのセミアモルファスシリコン膜を成膜する。

【0195】

次に、第2の半導体膜上に第2のマスクパターン817、818を形成する。第2のマ

スクパターンは、ポリイミドを液滴吐出法により第2の半導体膜816上に吐出し、20

0度30分加熱して形成する。第2のマスクパターン817は、後の半導体領域が形成さ

れる領域上に吐出する。

【0196】

次に、図8(C)に示すように、第2のマスクパターンを用いて第2の半導体膜816

をエッチングして、第1の半導体領域821、822(ソース及びドレイン領域)を形成

する。第2の半導体膜816は、流量比がCF4:O2=10:9の混合ガスを用いてエッ

チングする。この後、第2のマスクパターン817、818を、剥離液を用いて剥離する

。

【0197】

次に、第3のマスクパターン823を形成する。第3のマスクパターンは、ポリイミド

を液滴吐出法により第1の半導体領域821、822及び第1の半導体膜815の一部の

上に吐出し、200度30分加熱して形成する。

【0198】

次に、図8(D)に示すように、第3のマスクパターン823を用いて第1の半導体膜

815をエッチングして、第2の半導体領域831を形成する。なお、図8(D)は縦断

面構造を模式的に示し、A−B及びC−Dに対応する平面構造を図11に示すので同時に

参照する。この後、第3のマスクパターン823を、剥離液を用いて剥離する。

【0199】

次に、図8(E)に示すように、塗れ性の低い第4のマスクパターン832を形成する

。塗れ性の低い第4のマスクパターンは、液滴吐出法によりゲート絶縁膜814と接続導

電膜813とが重畳する領域に、フッ素系シランカップリング剤を溶媒に溶解した溶液を

吐出して形成する。なお、第4のマスクパターン832は、後のドレイン電極と接続導電

膜813とが接続する領域にコンタクトホールを形成するための第5のマスクパターンを

形成するための保護膜である。

【0200】

次に、塗れ性の高い材料を用いて第5のマスクパターン833を形成する。第5のマス

クパターンは、第1のコンタクトホールを形成するためのマスクであり、ポリイミドを液

滴吐出法により吐出し、200度で30分加熱して形成する。このとき、第4のマスクパ

ターン832は塗れ性が低く、第5のマスクパターン833は塗れ性が高いため、第4の

マスクパターンが形成される領域には、第5のマスクパターン833は形成されない。

【0201】

次に、図9(A)に示すように、酸素アッシングにより第4のマスクパターン832を

除去してゲート絶縁膜の一部を露出する。次に、第5のマスクパターン833を用いて、

露出されたゲート絶縁膜をエッチングする。ゲート絶縁膜は、CHF3を用いてエッチン

グする。この後、酸素アッシング及び剥離液を用いたエッチングにより第5のマスクパタ

ーンを剥離する。

【0202】

次に、ソース配線841及びドレイン配線842を液滴吐出法で形成する。このとき、

ドレイン配線842は、第2の半導体領域822及び接続導電膜813に接続されるよう

に形成する。ソース配線841、及びドレイン配線842は、Ag(銀)粒子が分散された

溶液を吐出し、100度30分加熱して乾燥した後、酸素濃度10%の雰囲気中で230

度1時間加熱して焼成する。次に、保護膜843を成膜する。保護膜は、シリコンターゲ

ット、及びスパッタリングガスとしてアルゴン並びに窒素(流量比Ar:N2=1:1)

を用いたスパッタリング法により、膜厚100nmの窒化珪素膜を成膜する。

【0203】

なお、図9(A)のA−B及びC−Dに対応する平面図を図12に示す。

【0204】

次に、図9(B)に示すように、保護膜843と接続導電膜813とが重畳する領域、

及びゲート配線並びにソース配線が接続端子と接続する領域に、塗れ性の低い第6のマス

クパターン851、852を形成した後、層間絶縁膜853を形成する。第6のマスクパ

ターンは、後に形成する層間絶縁膜のマスクである。第6のマスクパターンとして、液滴

吐出法によりフッ素系シランカップリング剤を溶媒に溶解した溶液を吐出し、層間絶縁膜

853として、液滴吐出法により塗れ性の高い絶縁材料であるポリイミドを吐出した後、

200度30分の加熱及び300℃1時間の加熱により、両方を焼成する。

【0205】

次に、図9(C)に示すように、CF4、O2、及びHeの混合ガス(流量比CF4:O2

:He=8:12:7)を用いて第6のマスクパターン851をエッチングした後、保護

膜843及びゲート絶縁膜814の一部をエッチングして、第2のコンタクトホールを形

成する。このエッチング工程において、ゲート配線並びにソース配線が接続端子と接続す

る領域の保護膜843及びゲート絶縁膜814をエッチングする。

【0206】

次に、第2の導電膜861を成膜した後、第7のマスクパターンを形成する。第2の導

電膜は、スパッタリング法により膜厚110nmの酸化珪素を含むインジウム錫酸化物(

ITO)を成膜し、後に画素電極を形成する領域にポリイミドを液滴吐出法により滴下し

、200度で30分加熱する。

【0207】

本実施例では、透過型の液晶表示パネルを作製するため、画素電極を、酸化珪素を含む

ITOで形成したが、これに代わってインジウム錫酸化物(ITO)、酸化亜鉛(ZnO

)、酸化スズ(SnO2)などを含む組成物により所定のパターンを形成し、焼成によっ

て画素電極を形成しても良い。また、反射型の液晶表示パネルを作製する場合には、Ag

(銀)、Au(金)、Cu(銅))、W(タングステン)、Al(アルミニウム)等の金

属の粒子を主成分とした組成物を用いることができる。

【0208】

次に、図9(D)に示すように、第7のマスクパターンを用いて第2の導電膜をエッチ

ングして画素電極871を形成する。このエッチング工程において、ゲート配線並びにソ

ース配線が接続端子と接続する領域に形成された第2の導電膜もエッチングする。この後

、第7のマスクパターンを、剥離液を用いて剥離する。なお、図9(D)のA−B及びC

−Dに対応する平面図を図13に示す。

【0209】

画素電極871は、第2のコンタクトホールにおいて、接続導電膜813と接続してい

る。接続導電膜813は、ドレイン配線842と接続しているため、画素電極871とド

レイン配線842とは、電気的に接続している。本実施例においては、ドレイン配線84

2は銀(Ag)で形成されており、画素電極871は酸化珪素を含むITOで形成されて

いるが、これらが直接接続していないため、銀が酸化されず、コンタクト抵抗を高めずと

も、ドレイン配線と画素電極とを電気的に接続することができる。

【0210】

また、画素電極を形成する他の方法としては、選択的に導電材料を含む溶液を液滴吐出法

で滴下して、エッチング工程無しに画素電極を形成することができる。さらには、後に画

素電極が形成されない領域に塗れ性の低いマスクパターンを形成した後、導電性を有する

溶液を吐出して、画素電極を形成することができる。この場合、マスクパターンは、酸素

を用いたアッシングで除去することができる。また、マスクパターンを除去せず、残存さ

せておいてもよい。

【0211】

以上の工程により、アクティブマトリクス基板を形成することができる。

【0212】

次に、図10(A)に示すように、画素電極871を覆うように印刷法やスピンコート法

により、絶縁膜を成膜し、ラビングを行って配向膜872を形成する。なお、配向膜87

2は、斜方蒸着法により形成することもできる。次に、画素を形成した周辺の領域に液滴

吐出法によりシール材873を形成する。

【0213】

次に、図10(B)に示すように、ディスペンサ式(滴下式)により、シール材873で

形成された閉ループ内側に、液晶材料を滴下する。

【0214】

ここで、図28を用いてアクティブマトリクス基板に液晶滴下法により液晶材料を滴下す

る工程を示す。図28(A)は、ディスペンサ2701によって液晶材料を滴下する工程

の斜視図であり、図28(B)は、図28(A)のA―Bにおける断面図である。

【0215】

シール材2702で囲まれた画素部2703を覆うように液晶材料2704を液晶ディス

ペンサ2701から滴下、または、吐出させている。液晶ディスペンサ2701を移動さ

せてもよいし、液晶ディスペンサ2701を固定し、基板2700を移動させることによ

って液晶層を形成することができる。また、複数の液晶ディスペンサ2701を設置して

一度に液晶を滴下してもよい。

【0216】

図28(B)に示すように、シール材2702で囲まれた領域のみに選択的に液晶材料

2704を滴下、または吐出させている。

【0217】

次に、真空中で、配向膜883及び対向電極882が設けられた対向基板881と貼り合

わせ、紫外線硬化を行って、液晶材料を充填して液晶層884を形成する。

【0218】

シール材873には、フィラーが混入されていてもよく、さらに、対向基板にはカラー

フィルタや遮蔽膜(ブラックマトリクス)などが形成されていても良い。また、液晶層8

84を形成する方法として、ディスペンサ式(滴下式)の代わりに、対向基板を貼り合わ

せてから毛細管現象を用いて液晶材料を注入するディップ式(汲み上げ式)を用いることが

できる。

【0219】

また、ここでは画素部に液晶材料を滴下したが、対向基板側に液晶材料を滴下した後、

画素部を有する基板を張り合わせても良い。

【0220】

次に、図10(C)に示すように、ゲート配線811、ソース配線(図示しない)それ

ぞれに、異方性導電膜885を介して接続端子(ゲート配線に接続される接続端子886

、ソース配線に接続される接続端子は図示せず。)を貼り付けて液晶表示パネルを形成す

ることができる。

【0221】

なお、層間絶縁膜853及び配向膜872を、基板全面に形成することができる。この

場合、シール材を形成する前に、液滴吐出法によりマスクを形成した後、公知のエッチン

グ法により、これらの絶縁膜を除去して、ソース配線及びゲート配線を露出する。

【0222】

以上の工程により液晶表示パネルを作製することができる。なお、静電破壊防止のため

の保護回路、代表的にはダイオードなどを、接続端子とソース配線(ゲート配線)の間、

または画素部に設けてもよい。この場合、上記したTFTと同様の工程で作製し、画素部

のゲート配線とダイオードのドレイン又はソース配線とを接続することにより、静電破壊

を防止することができる。

【0223】

なお、第1実施形態乃至第9実施形態のいずれをも本実施例に適用することができる。

また、本実施例では、表示パネルとして液晶表示パネルの作製方法を示したが、これに限

られるものではなく、有機材料又は無機材料で形成された発光物質を発光層として有する

発光表示装置、DMD(Digital Micromirror Device;デジタルマイクロミラーデバイス

)、PDP(Plasma Display Panel;プラズマディスプレイパネル)、FED(Field Em

ission Display;フィールドエミッションディスプレイ)、電気泳動表示装置(電子ペー

パー)等のアクティブ型表示パネルに適宜適用することができる。

【実施例2】

【0224】

本実施例では、パッシブマトリクス基板を用いる表示パネルについて、図26を用いて

説明する。本実施例では、表示パネルとして、EL(Electro Luminesc

ence)表示パネル(発光表示パネル)を用いて説明する。

【0225】

図26(A)に示すように、透光性を有する基板2601上に、透光性導電膜で形成され

る第1の画素電極2602を形成する。第1の電極は、複数の第1の電極が平行に配置さ

れている。本実施例では、第1の電極として、ITO、ZnO2を組成物として有する溶

液を平行に描画しながら吐出し焼成して、第1の画素電極を形成する。

【0226】

次に、第1の画素電極2602上に、等間隔で第1の電極と直交した複数の第1の絶縁膜

2603を形成する。第1の絶縁膜としては、SiO2、SiN等の絶縁膜を成膜し、平

行にエッチングして形成する。

【0227】

次に、図26(B)に示すように、後に有機EL材料層が形成される領域、即ち隣り合う

第1の絶縁膜2603の一部及びその間の領域に、塗れ性の低いマスクパターン2611

を形成する。塗れ性の低いマスクパターンとして、FASを有する溶液を液滴吐出法によ

り吐出して形成する。

【0228】

なお、有機EL材料層には、無機材料で形成される材料を含む場合もある。

【0229】

次に、塗れ性の低いマスクパターンが形成されていない領域、即ちマスクパターンの外縁

に、塗れ性の高い溶液吐出し、乾燥及び焼成をして第2の絶縁膜2612を形成する。本

実施例では、ポリイミドを吐出する。

【0230】

なお、塗れ性の高い溶液の組成、粘度、表面張力等により図26(B)に示すような、断

面が逆テーパー形状の第2の絶縁膜2612を形成することができる。

【0231】

また、塗れ性の高い溶液の組成、粘度、表面張力等により図27に示すように、断面が順

テーパ形状の第2の絶縁膜2631を形成することができる。

【0232】

次に、図26(C)に示すように、酸素を用いたアッシングにより、マスクパターン26

11を除去する。次に、有機EL材料を蒸着して、即ち隣り合う第1の絶縁膜2603及

びその間の領域に、有機EL材料層2621を形成する。この工程において、第2の絶縁

膜2612上にも、有機EL材料層2622が形成される。

【0233】

次に、図26(D)に示すように、導電材料を蒸着し、第2の画素電極2623を形成す

る。なお、この工程において、第2の絶縁膜2612上に形成された有機EL材料262

2上に、第2の導電材料2624が蒸着される。本実施例では、第2の画素電極はAl、

Al-Li合金、Ag-Mg合金等で形成されている。

【0234】

なお、第2の絶縁膜2612の断面が逆テーパー形状の場合、有機EL材料層2621及

び第2の画素電極2623は、第2の絶縁膜2612の頭部によって蒸着が妨げられる。

このため、公知のフォトリソグラフィー工程を用いずとも、第2の絶縁膜2612ごとに

分断することができる。

【0235】

また、第2の絶縁膜2631が順テーパー形状の場合、液滴吐出法により、図27(B)

に示すように、各第2の絶縁膜2631の間に、有機EL材料及び導電材料を有する溶液

をそれぞれ吐出して、有機EL材料2622及び第2の画素電極2623を形成すること

ができる。

【0236】

この後、保護膜を成膜して有機EL表示パネルを作製することができる。

【0237】

なお、第1実施形態乃至第9実施形態のいずれをも本実施例に適用することができる。

また、本実施例では、表示パネルとして有機EL表示パネルの作製方法を示したが、これ

に限られるものではなく、液晶表示装置、DMD(Digital Micromirror Device;デジタ

ルマイクロミラーデバイス)、PDP(Plasma Display Panel;プラズマディスプレイパ

ネル)、FED(Field Emission Display;フィールドエミッションディスプレイ)、電

気泳動表示装置(電子ペーパー)等のパッシブ型表示パネルに適宜適用することができる

。

【0238】

本実施例において、公知のフォトリソグラフィーを用いずとも、有機EL材料層を絶縁す

る絶縁膜を形成することができる。

【実施例3】

【0239】

本実施例では、上記実施例に示した表示パネルへの駆動回路(信号線駆動回路1402及

び走査線駆動回路1403a、1403b)の実装について、図14を用いて説明する。

【0240】

図14(A)に示すように、画素部1401の周辺に信号線駆動回路1402、及び走査

線駆動回路1403a、1403bを実装する。図14(A)では、信号線駆動回路14

02、及び走査線駆動回路1403a、1403b等として、COG方式により、基板1

400上にICチップ1405を実装する。そして、FPC(フレキシブルプリントサー

キット)1406を介して、ICチップと外部回路とを接続する。

【0241】

また、図14(B)に示すように、SASや結晶性半導体でTFTを形成する場合、画素

部1401と走査線駆動回路1403a、1403b等を基板上に一体形成し、信号線駆

動回路1402等を別途ICチップとして実装する場合がある。図14(B)において、

信号線駆動回路1402として、COG方式により、基板1400上にICチップ140

5を実装する。そして、FPC1406を介して、ICチップと外部回路とを接続する。

【0242】

またさらに図14(C)に示すように、COG方式に代えて、TAB方式により信号線駆

動回路1402等を実装する場合がある。そして、FPC1406を介して、ICチップ

と外部回路とを接続する。図14(C)において、信号線駆動回路をTAB方式により実

装しているが、走査線駆動回路をTAB方式により実装してもよい。

【0243】

ICチップをTAB方式により実装すると、基板に対して画素部を大きく設けることがで

き、狭額縁化を達成することができる。

【0244】

ICチップは、シリコンウェハを用いて形成するが、ICチップの代わりにガラス基板上

にICを形成したIC(以下、ドライバICと表記する)を設けてもよい。ICチップは

、円形のシリコンウェハからICチップを取り出すため、母体基板形状に制約がある。一

方ドライバICは、母体基板がガラスであり、形状に制約がないため、生産性を高めるこ

とができる。そのため、ドライバICの形状寸法は自由に設定することができる。例えば

、ドライバICの長辺の長さを15〜80mmとして形成すると、ICチップを実装する

場合と比較し、必要な数を減らすことができる。その結果、接続端子数を低減することが

でき、製造上の歩留まりを向上させることができる。

【0245】

ドライバICは、基板上に形成された結晶質半導体を用いて形成することができ、結晶

質半導体は連続発振型のレーザ光を照射することで形成するとよい。連続発振型のレーザ

光を照射して得られる半導体膜は、結晶欠陥が少なく、大粒径の結晶粒を有する。その結

果、このような半導体膜を有するトランジスタは、移動度や応答速度が良好となり、高速

駆動が可能となり、ドライバICに好適である。

【実施例4】

【0246】

本実施例では、上記実施例に示した表示パネルへの駆動回路(信号線駆動回路1402及

び走査線駆動回路1403a、1403b)の実装方法について、図15を用いて説明す

る。この実装方法としては、異方性導電材を用いた接続方法やワイヤボンディング方式等

を採用すればよく、その一例について図15を用いて説明する。なお、本実施例では、信

号線駆動回路1402及び走査線駆動回路1403a、1403bにドライバICを用い

た例を示す。ドライバICの代わりに、適宜ICチップを用いることができる。

【0247】

図15(A)はアクティブマトリクス基板1701に、ICドライバ1703が異方性

導電材を用いて実装された例を示す。アクティブマトリクス基板1701上には、ソース

配線又はゲート配線等の各配線(図示しない。)と該配線の取り出し電極である電極パッ

ト1702a、1702bが形成されている。

【0248】

ドライバIC1703表面には、接続端子1704a、1704bが設けられ、その周

辺部には保護絶縁膜1705が形成される。

【0249】

アクティブマトリクス基板1701上には、ドライバIC1703が異方性導電接着剤1

706で固定されており、接続端子1704a、1704bと電極パット1702a、1

702bはそれぞれ、異方性導電接着剤中に含まれる導電性粒子1707で電気的に接続

されている。異方性導電接着剤は、導電性粒子(粒径3〜7μm程度)を分散、含有する

接着性樹脂であり、エポキシ樹脂、フェノール樹脂等が挙げられる。また、導電性粒子(

粒径が数〜数百μm程度)は、金、銀、銅、パラジウム、又は白金から選ばれた一元素、

若しくは複数の元素の合金粒子で形成される。また、これらの元素の多層構造を有する粒

子でも良い。さらには、樹脂粒子に金、銀、銅、パラジウム、又は白金から選ばれた一元

素、若しくは複数の元素の合金がコーティングされた粒子でもよい。

【0250】

また、異方性導電接着剤の代わりに、ベースフィルム上にフィルム状に形成された異方

性導電フィルムを転写して用いても良い。異方性導電フィルムも、異方性導電接着剤と同

様の導電性粒子が分散されている。異方性導電接着剤1706中に混入された導電性粒子

1707の大きさと密度を適したものとすることにより、このような形態でドライバIC

をアクティブマトリクス基板に実装することができる。本実装方法は、図14(A)及び

図14(B)のドライバICの実装方法に適している。

【0251】

図15(B)は有機樹脂の収縮力を用いた実装方法の例であり、ドライバICの接続端

子表面にTaやTiなどでバッファ層1711a、1711bを形成し、その上に無電解

メッキ法などによりAuを約20μm形成しバンプ1712a、1712bとする。ドラ

イバICとアクティブマトリクス基板との間に光硬化性絶縁樹脂1713を介在させ、光

硬化して固まる樹脂の収縮力を利用して電極間を圧接して実装することができる。本実装

方法は、図14(A)及び図14(B)のドライバICの実装方法に適している。

【0252】

また、図15(C)で示すように、アクティブマトリクス基板1701にドライバIC

1703を接着剤1721で固定して、ワイヤ1722a、1722bによりドライバI

Cの接続端子と配線基板上の電極パット1702a、1702bとを接続しても良い。そ

して有機樹脂1723で封止する。本実装方法は、図14(A)及び図14(B)のドラ

イバICの実装方法に適している。

【0253】

また、図15(D)で示すように、FPC(Flexible printed circuit)1731上の

配線1732と、導電性粒子1708を含有する異方性導電接着剤1706を介してドラ

イバIC1703を設けてもよい。この構成は、携帯端末等の筐体の大きさが限られた電

子機器に用いる場合に大変有効である。本実装方法は、図14(C)のドライバICの実

装方法に適している。

【0254】

なお、ドライバICの実装方法は、特に限定されるものではなく、公知のCOG方法やワ

イヤボンディング方法、或いはTAB方法、半田バンプを用いたリフロー処理を用いるこ

とができる。なお、リフロー処理を行う場合は、ドライバIC又はアクティブマトリクス

基板に用いられる基板が耐熱性の高いプラスチック、代表的にはポリイミド基板、HT基

板(新日鐵化学社製)、極性基のついたノルボルネン樹脂からなるARTON(JSR製

)等を用いることが好ましい。

【実施例5】

【0255】

実施例4に示される液晶表示パネルにおいて、半導体膜をSASで形成することによっ

て、図14(B)及び図14(C)に示すように、走査線側の駆動回路を基板1400上

に形成した場合の、駆動回路について説明する。

【0256】

図21は、1〜15cm2/V・secの電界効果移動度が得られるSASを使ったn

チャネル型のTFTで構成する走査線側駆動回路のブロック図を示している。

【0257】

図21において1500で示すブロックが1段分のサンプリングパルスを出力するパル

ス出力回路に相当し、シフトレジスタはn個のパルス出力回路により構成される。バッフ

ァ回路1501の先に画素が接続さる。

【0258】

図22は、パルス出力回路1500の具体的な構成を示したものであり、nチャネル型

のTFT3601〜3612で回路が構成されている。このとき、SASを使ったnチャ

ネル型のTFTの動作特性を考慮して、TFTのサイズを決定すれば良い。例えば、チャ

ネル長を8μmとすると、チャネル幅は10〜80μmの範囲で設定することができる。

【0259】

また、バッファ回路1501の具体的な構成を図23に示す。バッファ回路も同様にn

チャネル型のTFT3621〜3636で構成されている。このとき、SASを使ったn

チャネル型のTFTの動作特性を考慮して、TFTのサイズを決定すれば良い。例えば、

チャネル長を10μmとすると、チャネル幅は10〜1800μmの範囲で設定すること

となる。

【実施例6】

【0260】

本実施例では、表示モジュールについて説明する。ここでは、表示モジュールの一例と

して、液晶モジュールを、図16を用いて示す。

【0261】

図16に示す液晶モジュールにおいて、アクティブマトリクス基板1601と対向基板

1602とが、シール材1600により固着され、それらの間には画素部1603と液晶

層1604とが設けられ表示領域を形成している。

【0262】

着色層1605は、カラー表示を行う場合に必要であり、RGB方式の場合は、赤、緑

、青の各色に対応した着色層が書く画素に対応して設けられている。アクティブマトリク

ス基板1601と対向基板1602との外側には、偏光板1606、1607が配設され

ている。また、偏光板1606の表面には、保護膜1616が形成されており、外部から

の衝撃を緩和している。

【0263】

アクティブマトリクス基板1601に設けられた接続端子1608には、FPC160

9を介して配線基板1610が接続されている。FPC又は接続配線には画素駆動回路(

ICチップ、ドライバIC等)1611が設けられ、配線基板1610には、コントロー

ル回路や電源回路などの外部回路1612が組み込まれている。

【0264】

冷陰極管1613、反射板1614、及び光学フィルム1615はバックライトユニッ

トであり、これらが光源となって液晶表示パネルへ光を投射する。液晶パネル、光源、配

線基板、FPC等は、ベゼル1617で保持及び保護されている。

【実施例7】

【0265】

本実施例では、表示モジュールの一例として、発光表示モジュールの外観について、図

30を用いて説明する。図30(A)は、第1の基板と、第2の基板との間を第1のシー

ル材1205及び第2のシール材1206によって封止されたパネルの上面図であり、図

30(B)は、図30(A)のA−A’における断面図に相当する。

【0266】

図30(A)において、点線で示された1201は信号線(ソース線)駆動回路、12

02は画素部、1203は走査線(ゲート線)駆動回路である。本実施例において、信号

線駆動回路1201、画素部1202、及び走査線駆動回路1203は第1のシール材及

び第2のシール材で封止されている領域内にある。第1のシール材としては、フィラーを

含む粘性の高いエポキシ系樹脂を用いるのが好ましい。また、第2のシール材としては、

粘性の低いエポキシ系樹脂を用いるのが好ましい。また、第1のシール材1205及び第

2のシール材はできるだけ水分や酸素を透過しない材料であることが望ましい。

【0267】

また、画素部1202とシール材1205との間に、乾燥剤を設けてもよい。さらには

、画素部において、走査線又は信号線上に乾燥剤を設けてもよい。乾燥剤としては、酸化

カルシウム(CaO)や酸化バリウム(BaO)等のようなアルカリ土類金属の酸化物の

ような化学吸着によって水(H2O)を吸着する物質を用いるのが好ましい。但し、これ

に限らずゼオライトやシリカゲル等の物理吸着によって水を吸着する物質を用いても構わ

ない。

【0268】

また、透湿性の高い樹脂に乾燥剤の粒状の物質を含ませた状態で第2の基板1204に

固定することができる。ここで、透湿性の高い樹脂としては、例えば、エステルアクリレ

ート、エーテルアクリレート、エステルウレタンアクリレート、エーテルウレタンアクリ

レート、ブタジエンウレタンアクリレート、特殊ウレタンアクリレート、エポキシアクリ

レート、アミノ樹脂アクリレート、アクリル樹脂アクリレート等のアクリル樹脂を用いる

ことができる。この他、ビスフェノールA型液状樹脂、ビスフェノールA型固形樹脂、含

ブロムエポキシ樹脂、ビスフェノールF型樹脂、ビスフェノールAD型樹脂、フェノール

型樹脂、クレゾール型樹脂、ノボラック型樹脂、環状脂肪族エポキシ樹脂、エピビス型エ

ポキシ樹脂、グリシジルエステル樹脂、グリシジルアミン系樹脂、複素環式エポキシ樹脂

、変性エポキシ樹脂等のエポキシ樹脂を用いることができる。また、この他の物質を用い

ても構わない。また、例えばシロキサンポリマー、ポリイミド、PSG(リンガラス)、

BPSG(リンボロンガラス)、等の無機物等を用いてもよい。

【0269】

乾燥剤を走査線と重畳する領域に設けることで、また、透湿性の高い樹脂に乾燥剤の粒

状の物質を含ませた状態で第2の基板に固定することで、開口率を低下せずに表示素子へ

の水分の侵入及びそれに起因する劣化を抑制することができる。

【0270】

なお、1210は、信号線駆動回路1201及び走査線駆動回路1203に入力される

信号を伝送するための接続配線であり、外部入力端子となるFPC(フレキシブルプリン

ト配線)1209から、接続配線1208を介してビデオ信号やクロック信号を受け取る

。

【0271】

次に、断面構造について図30(B)を用いて説明する。第1の基板1200上には駆

動回路及び画素部が形成されており、TFTを代表とする半導体素子を複数有している。

駆動回路として信号線駆動回路1201と画素部1202とを示す。なお、信号線駆動回

路1201はnチャネル型TFT1221とpチャネル型TFT1222とを組み合わせ

たCMOS回路が形成される。

【0272】

本実施例においては、同一基板上に信号線駆動回路、走査線駆動回路、及び画素部のT

FTが形成されている。このため、発光表示装置の容積を縮小することができる。

【0273】

また、画素部1202はスイッチング用TFT1211と、駆動用TFT1212とそ

のドレインに電気的に接続された反射性を有する導電膜からなる第1の画素電極(陽極)

1213を含む複数の画素により形成される。

【0274】

また、これらのTFT1211、1212、1221、1222の層間絶縁膜1220

としては、無機材料(酸化シリコン、窒化シリコン、酸化窒化シリコンなど)、有機材料

(ポリイミド、ポリアミド、ポリイミドアミド、ベンゾシクロブテン、またはシロキサン

ポリマー)を主成分とする材料を用いて形成することができる。また、層間絶縁膜の原料

としてシロキサンポリマーを用いると、シリコンと酸素を骨格構造に有し、側鎖に水素又

は/及びアルキル基を有する構造の絶縁膜となる。

【0275】

また、第1の画素電極(陽極)1213の両端には絶縁物(バンク、隔壁、障壁、土手

などと呼ばれる)1214が形成される。絶縁物1214に形成する膜の被覆率(カバレ

ッジ)を良好なものとするため、絶縁物1214の上端部または下端部に曲率を有する曲

面が形成されるようにする。絶縁物1214の材料としては、無機材料(酸化シリコン、

窒化シリコン、酸化窒化シリコンなど)、有機材料(ポリイミド、ポリアミド、ポリイミ

ドアミド、ベンゾシクロブテン、またはシロキサンポリマー)を主成分とする材料を用い

て形成することができる。また、絶縁物の原料としてシロキサンポリマーを用いると、シ

リコンと酸素を骨格構造に有し、側鎖に水素又は/及びアルキル基を有する構造の絶縁膜

となる。また、絶縁物1214を窒化アルミニウム膜、窒化酸化アルミニウム膜、炭素を

主成分とする薄膜、または窒化珪素膜からなる保護膜(平坦化膜)で覆ってもよい。また

、絶縁物1214として、黒色顔料、色素などの可視光を吸収する材料を溶解又は分散さ

せてなる有機材料を用いることで、後に形成される発光素子からの迷光を吸収することが

できる。この結果、各素のコントラストが向上する。また、層間絶縁膜1220も遮光性

を有する絶縁物で設けることによって、絶縁物1214とのトータルで遮光の効果を得る

ことができる。

【0276】

また、第1の画素電極(陽極)1213上には、有機化合物材料の蒸着を行い、発光物

質を含む層1215を選択的に形成する。

【0277】

発光物質を含む層1215は公知の構造を適宜用いることができる。ここで、発光物質

を含む層の構造を、図31を用いて示す。

【0278】

図31(A)は第1の画素電極11を透光性の酸化物導電性材料で形成した例であり、

酸化珪素を1〜15原子%の濃度で含む酸化物導電性材料で形成している。その上に正孔

注入層若しくは正孔輸送層41、発光層42、電子輸送層若しくは電子注入層43を積層

した発光物質を含む層16を設けている。第2の画素電極17は、LiFやMgAgなど

アルカリ金属又はアルカリ土類金属を含む第1の電極33とアルミニウムなどの金属材料

で形成する第2の電極34で形成している。この構造の画素は、図中に矢印で示したよう

に第1の画素電極11側から光を放射することが可能となる。

【0279】

図31(B)は第2の画素電極17から光を放射する例を示し、第1の画素電極11は

アルミニウム、チタンなどの金属、又は該金属と化学量論的組成比以下の濃度で窒素を含

む金属材料で形成する第1の電極35と、酸化珪素を1〜15原子%の濃度で含む酸化物

導電性材料で形成する第2の電極32で形成している。その上に正孔注入層若しくは正孔

輸送層41、発光層42、電子輸送層若しくは電子注入層43を積層した発光物質を含む

層16を設けている。第2の画素電極17は、LiFやCaFなどのアルカリ金属又はア

ルカリ土類金属を含む第3の電極33とアルミニウムなどの金属材料で形成する第4の電

極34で形成するが、いずれの層も100nm以下の厚さとして光を透過可能な状態とし

ておくことで、第2の電極17から光を放射することが可能となる。

【0280】

図31(E)は、両方向、即ち第1の電極及び第2の電極から光を放射する例を示し、

第1の画素電極11に、透光性を有し且つ仕事関数の大きい導電膜を用い、第2の画素電

極17に、透光性を有し且つ仕事関数の小さい導電膜を用いる。代表的には、第1の画素

電極11を、酸化珪素を1〜15原子%の濃度で含む酸化物導電性材料で形成し、第2の

画素電極17を、それぞれ100nm以下の厚さのLiFやCaFなどのアルカリ金属又

はアルカリ土類金属を含む第3の電極33とアルミニウムなどの金属材料で形成する第4

の電極34で形成すればよい。

【0281】

図31(C)は第1の画素電極11から光を放射する例を示し、かつ、発光物質を含む

層を電子輸送層若しくは電子注入層43、発光層42、正孔注入層若しくは正孔輸送層4

1の順に積層した構成を示している。第2の画素電極17は、発光物質を含む層16側か

ら酸化珪素を1〜15原子%の濃度で含む酸化物導電性材料で形成する第2の電極32、

アルミニウム、チタンなどの金属、又は該金属と化学量論的組成比以下の濃度で窒素を含

む金属材料で形成する第1の電極35で形成している。第1の画素電極11は、LiFや

CaFなどのアルカリ金属又はアルカリ土類金属を含む第3の電極33とアルミニウムな

どの金属材料で形成する第4の電極34で形成するが、いずれの層も100nm以下の厚

さとして光を透過可能な状態としておくことで、第1の画素電極11から光を放射するこ

とが可能となる。

【0282】

図31(D)は第2の画素電極17から光を放射する例を示し、かつ、発光物質を含む

層を電子輸送層若しくは電子注入層43、発光層42、正孔注入層若しくは正孔輸送層4

1の順に積層した構成を示している。第1の画素電極11は図31(A)の第2の画素電

極と同様な構成とし、膜厚は発光物質を含む層で発光した光を反射可能な程度に厚く形成

している。第2の画素電極17は、酸化珪素を1〜15原子%の濃度で含む酸化物導電性

材料で構成している。この構造において、正孔注入層若しくは正孔輸送層41を無機物で

ある金属酸化物(代表的には酸化モリブデン若しくは酸化バナジウム)で形成することに

より、第2の画素電極17を形成する際に導入される酸素が供給されて正孔注入性が向上

し、駆動電圧を低下させることができる。

【0283】

図31(F)は、両方向、即ち第1の画素電極及び第2の画素電極から光を放射する例

を示し、第1の画素電極11に、透光性を有し且つ仕事関数の小さい導電膜を用い、第2

の画素電極17に、透光性を有し且つ仕事関数の大きい導電膜を用いる。代表的には、第

1の画素電極11を、それぞれ100nm以下の厚さのLiFやCaFなどのアルカリ金

属又はアルカリ土類金属を含む第3の電極33とアルミニウムなどの金属材料で形成する

第4の電極34で形成し、第2の画素電極17を、酸化珪素を1〜15原子%の濃度で含

む酸化物導電性材料で形成すればよい。

【0284】

こうして、図30(B)に示すように、第1の画素電極(陽極)1213、発光物質を

含む層1215、及び第2の画素電極(陰極)1216からなる発光素子1217が形成

される。発光素子1217は、第2の基板1204側に発光する。

【0285】

また、発光素子1217を封止するために保護積層1218を形成する。保護積層は、

第1の無機絶縁膜と、応力緩和膜と、第2の無機絶縁膜との積層からなっている。次に、

保護積層1218と第2の基板1204とを、第1のシール材1205及び第2のシール

材1206で接着する。なお、第2のシール剤を実施例1の図28に示す液晶を滴下する

装置のように、シール剤を滴下する装置を用いて滴下することが好ましい。シール剤をデ

ィスペンサから滴下、又は吐出させてシール剤をアクティブマトリクス基板上に塗布した

後、真空中で、第2の基板とアクティブマトリクス基板とを貼り合わせ、紫外線硬化を行

って封止することができる。

【0286】

なお、第2の基板1204表面には、偏光板1225が固定され、偏光板1225表面

には、1/2λ又は1/4λの位相差板1229及び反射防止膜1226が設けられてい

る。また、第2の基板1204から順に、1/4λ板の位相差板及び1/2λ板の位相差

板1229、偏光板1225を順次設けてもよい。位相差板及び偏光板を設けることによ

り、外光が画素電極で反射することを防止することが可能である。なお、第1の画素電極

1213及び第2の画素電極1216を透光性又は半透光性を有する導電膜で形成し、層

間絶縁膜1220を可視光を吸収する材料、又は可視光を吸収する材料を溶解又は分散さ

せてなる有機材料を用いて形成すると、各画素電極で外光が反射しないため、位相差板及

び偏光板を用いなくとも良い。

【0287】

接続配線1208とFPC1209とは、異方性導電膜又は異方性導電樹脂1227で

電気的に接続されている。さらに、各配線と接続端子との接続部を封止樹脂で封止するこ

とが好ましい。この構造により、断面部からの水分が発光素子に侵入し、劣化することを

防ぐことができる。

【0288】

なお、第2の基板1204と、保護積層1218との間には、不活性ガス、例えば窒素

ガスを充填した空間を有してもよい。水分や酸素の侵入の防止を高めることができる。

【0289】

画素部1202と偏光板1225の間に着色層を設けることができる。この場合、画素

部に白色発光が可能な発光素子を設け、RGBを示す着色層を別途設けることでフルカラ

ー表示することができる。また、画素部に青色発光が可能な発光素子を設け、色変換層な

どを別途設けることによってフルカラー表示することができる。さらには、各画素部、赤

色、緑色、青色の発光を示す発光素子を形成し、且つ着色層を用いることもできる。この

ような表示モジュールは、各RBGの色純度が高く、高精細な表示が可能となる。

【0290】

また、第1の基板1200又は第2の基板1204の一方、若しくは両方にフィルム又

は樹脂等の基板を用いて発光表示モジュールを形成してもよい。このように対向基板を用

いず封止すると、表示装置の軽量化、小型化、薄膜化を向上させることができる。

【0291】

なお、第1実施形態乃至第9実施形態のいずれをも本実施例に適用することができる。

また、本実施例では、表示モジュールとして発光表示モジュールを示したが、これに限ら

れるものではなく、発光表示装置、DMD(Digital Micromirror Device;デジタルマイ

クロミラーデバイス)、PDP(Plasma Display Panel;プラズマディスプレイパネル)

、FED(Field Emission Display;フィールドエミッションディスプレイ)、電気泳動

表示装置(電子ペーパー)等の表示モジュールに適宜適用することができる。

【実施例8】

【0292】

実施例6又は実施例7に示される表示モジュールを筺体に組み込むことによって様々な電

子機器を作製することができる。電子機器としては、テレビジョン装置、ビデオカメラ、

デジタルカメラ、ゴーグル型ディスプレイ(ヘッドマウントディスプレイ)、ナビゲーシ

ョンシステム、音響再生装置(カーオーディオ、オーディオコンポ等)、ノート型パーソ

ナルコンピュータ、ゲーム機器、携帯情報端末(モバイルコンピュータ、携帯電話、携帯

型ゲーム機または電子書籍等)、記録媒体を備えた画像再生装置(具体的にはDigital Ve

rsatile Disc(DVD)等の記録媒体を再生し、その画像を表示しうるディスプレイを備

えた装置)などが挙げられる。ここでは、これらの電子機器の代表例としてテレビジョン

装置を及びそのブロック図をそれぞれ図17及び図18に、デジタルカメラを図19に示

す。

【0293】

図17は、アナログのテレビジョン放送を受信するテレビジョン装置の一般的な構成を

示す図である。図17において、アンテナ1101で受信されたテレビ放送用の電波は、

チューナ1102に入力される。チューナ1102は、アンテナ1101より入力された

高周波テレビ信号を希望受信周波数に応じて制御された局部発振周波数の信号と混合する

ことにより、中間周波数(IF)信号を生成して出力する。

【0294】

チューナ1102により取り出されたIF信号は、中間周波数増幅器(IFアンプ)1

103により必要な電圧まで増幅された後、映像検波回路1104によって映像検波され

ると共に、音声検波回路1105によって音声検波される。映像検波回路1104により

出力された映像信号は、映像系処理回路1106により、輝度信号と色信号とに分離され

、さらに所定の映像信号処理が施されて映像信号となり、本発明の一つである液晶表示装

置、発光表示装置、DMD(Digital Micromirror Device;デジタルマイクロミラーデバ

イス)、PDP(Plasma Display Panel;プラズマディスプレイパネル)、FED(Fiel

d Emission Display;フィールドエミッションディスプレイ)、電気泳動表示装置(電子

ペーパー)等の映像系出力部1108に出力される。

【0295】

また、音声検波回路1105により出力された信号は、音声系処理回路1107により

、FM復調などの処理が施されて音声信号となり、適宜増幅されてスピーカ等の音声系出

力部1109に出力される。

【0296】

なお、本発明を用いたテレビジョン装置は、VHF帯やUHF帯などの地上波放送、ケ

ーブル放送、又はBS放送などのアナログ放送に対応するものに限らず、地上波デジタル

放送、ケーブルデジタル放送、又はBSデジタル放送に対応するものであっても良い。

【0297】

図18はテレビジョン装置を前面方向から見た斜視図であり、筐体1151、表示部1

152、スピーカ部1153、操作部1154、ビデオ入力端子1155等を含む。また

、図17に示すような構成となっている。

【0298】

表示部1152は、図17の映像系出力部1108の一例であり、ここで映像を表示す

る。

【0299】

スピーカ部1153は、図17の音声系出力部の一例であり、ここで音声を出力する。

【0300】

操作部1154は、電源スイッチ、ボリュームスイッチ、選局スイッチ、チューナース

イッチ、選択スイッチ等が設けられており、該ボタンの押下によりテレビジョン装置の電

源のON/OFF、映像の選択、音声の調整、及びチューナの選択等を行う。なお、図示

していないが、リモートコントローラ型操作部によって、上記の選択を行うことも可能で

ある。

【0301】

ビデオ入力端子1155は、VTR、DVD、ゲーム機等の外部からの映像信号をテレ

ビジョン装置に入力する端子である。

【0302】

本実施例で示されるテレビジョン装置を壁掛け用テレビジョン装置の場合、本体背面に壁

掛け用の部位が設けられている。

【0303】

テレビジョン装置の表示部に本発明の半導体装置の一例である表示装置を用いることによ

り、低コストで、スループットや歩留まり高くテレビジョン装置を作製することができる

。また、テレビジョン装置の映像検波回路、映像処理回路、音声検波回路、音声処理回路

を制御するCPUに本発明の半導体装置を用いることにより、低コストで、スループット

や歩留まり高くテレビジョン装置を作製することができる。このため、壁掛けテレビジョ

ン装置、鉄道の駅や空港などにおける情報表示板や、街頭における広告表示板など特に大

面積の表示媒体として様々な用途に適用することができる。

【0304】

図19(A)及び図19(B)は、デジタルカメラの一例を示す図である。図19(A)

は、デジタルカメラの前面方向から見た斜視図、図19(B)は、後面方向から見た斜視

図である。図19(A)において、デジタルカメラには、レリーズボタン1301、メイ

ンスイッチ1302、ファインダー窓1303、フラッシュ1304、レンズ1305、

鏡胴1306、筺体1307が備えられている。

【0305】

また、図19(B)において、ファインダー接眼窓1311、モニター1312、操作

ボタン1313が備えられている。

【0306】

レリーズボタン1301は、半分の位置まで押下されると、焦点調整機構および露出調

整機構が作動し、最下部まで押下されるとシャッターが開く。

【0307】

メインスイッチ1302は、押下又は回転によりデジタルカメラの電源のON/OFF

を切り替える。

【0308】

ファインダー窓1303は、デジタルカメラ前面のレンズ1305の上部に配置されて

おり、図19(B)に示すファインダー接眼窓1311から撮影する範囲やピントの位置

を確認するための装置である。

【0309】

フラッシュ1304は、デジタルカメラの前面上部に配置され、被写体輝度が低いとき

に、レリーズボタンが押下されてシャッターが開くと同時に補助光を照射する。

【0310】

レンズ1305は、デジタルカメラの正面に配置されている。レンズは、フォーカシン

グレンズ、ズームレンズ等により構成され、図示しないシャッター及び絞りと共に撮影光

学系を構成する。また、レンズの後方には、CCD(Charge Coupled Device)等の撮像

素子が設けられている。

【0311】

鏡胴1306は、フォーカシングレンズ、ズームレンズ等のピントを合わせるためにレン

ズの位置を移動するものであり、撮影時には、鏡胴を繰り出すことにより、レンズ130

5を手前に移動させる。また、携帯時は、レンズ1305を沈胴させてコンパクトにする

。なお、本実施例においては、鏡胴を繰り出すことにより被写体をズーム撮影することが

できる構造としているが、この構造に限定されるものではなく、筺体1307内での撮影

光学系の構成により鏡胴を繰り出さずともズーム撮影が可能なデジタルカメラでもよい。

【0312】

ファインダー接眼窓1311は、デジタルカメラの後面上部に設けられており、撮影す

る範囲やピントの位置を確認する際に接眼するために設けられた窓である。

【0313】

操作ボタン1313は、デジタルカメラの後面に設けられた各種機能ボタンであり、セ

ットアップボタン、メニューボタン、ディスプレイボタン、機能ボタン、選択ボタン等に

より構成されている。

【0314】

本発明の半導体装置の一実施例である表示装置をモニターに用いことにより、低コストで

、スループットや歩留まり高くデジタルカメラを作製することが可能である。また、各種

機能ボタン、メインスイッチ、レリーズボタン等の操作入力を受けて関連した処理を行う

CPU、自動焦点動作及び自動焦点調整動作を行う回路、ストロボ発光の駆動制御、CC

D(charge coupled device)の駆動を制御するタイミング制御回路、CCD等の撮像素

子によって光電変換された信号から画像信号を生成する撮像回路、撮像回路で生成された

画像信号をデジタル信号に変換するA/D変換回路、メモリへの画像データの書き込み及

び画像データの読み出しを行うメモリインターフェース等の各回路を制御するCPU等に

本発明の半導体装置の一例であるCPUを用いることにより、低コストで、スループット

や歩留まり高くデジタルカメラを作製することが可能である。

【技術分野】

【0001】

本発明は、インクジェット法に代表される液滴吐出法を用いて形成した半導体素子を有

する半導体装置の作製方法、また半導体素子の各部位の膜、マスクパターン及びコンタク

トホールを形成する技術に関するものである。

【背景技術】

【0002】

半導体装置の作製において、設備の低コスト化、工程の簡略化を目的として、半導体素

子に用いられる薄膜や配線のパターン形成に、液滴吐出装置を用いることが検討されてい

る。

【0003】

その際、半導体素子におけるコンタクトホールを形成するにあたっては、レジストを基

板全面に塗布形成しプリベークを行った後、マスクパターンを介して紫外線等を照射し、

現像によってレジストパターンを形成するというフォトリソグラフィー工程を経た後、該

レジストパターンをマスクパターンとしてコンタクトホールとなるべき部分に存在する絶

縁膜をエッチング除去することにより、コンタクトホールを形成する方法が用いられてい

る。

【0004】

また、レジストパターンを用いて、半導体膜、絶縁膜、金属膜等をエッチングして所望

の形状の膜パターンを形成している。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2000−89213号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

しかしながら、従来のコンタクトホールを有する絶縁膜、膜パターン等の形成工程にお

いて、膜パターン及びレジストの材料の大部分が無駄になると共に、マスクパターン形成

するための工程数が多く、スループットが低下するという問題がある。

【0007】

また、コンタクトホールを開孔する際に、レジストの塗布量及び下地の表面状態の制御

が不十分だと、コンタクトホール部分にもレジストが広がってしまい、コンタクト不良が

発生してしまう可能性がある。

【0008】

本発明は、このような問題点に鑑みてなされたものであり、簡単な工程で絶縁膜、半導

体膜、導電膜等の膜パターンを有する基板を作製する方法、さらには、低コストで、スル

ープットや歩留まりの高い半導体装置の作製方法を提供することを目的とする。

【課題を解決するための手段】

【0009】

本発明の一は、基板上に塗れ性の低い第1の保護膜(以下、マスクパターンと示す。)

を形成した後、前記第1のマスクパターンの外縁に塗れ性の高い材料を塗布又は吐出して

膜パターン、及び該膜パターンを有する基板を形成することを特徴とする。

【0010】

また、本発明の一は、基板上に塗れ性の低い第1のマスクパターンを形成した後、前記

第1のマスクパターンを除く領域に塗れ性の高い材料を塗布又は吐出して膜パターン、及

び該膜パターンを有する基板を形成することを特徴とする。

【0011】

また、本発明の一は、基板上に塗れ性の低い第1のマスクパターンを形成した後、前記

第1のマスクパターンが形成されない領域に塗れ性の高い材料を塗布又は吐出して膜パタ

ーン、及び該膜パターンを有する基板を形成することを特徴とする。

【0012】

また、本発明の一は、薄膜又は部材上に塗れ性の低い第1のマスクパターンを形成した

後、塗れ性の高い第2のマスクパターンを形成し、第1のマスクパターン及び該第1のマ

スクパターンで覆われた薄膜又は部材を除去し、膜パターン又はコンタクトホールを有す

る絶縁膜を形成することを特徴とする。なお、この後、第2のマスクパターンを除去する

ことも可能である。

【0013】

塗れ性の低い第1のマスクパターンは液体を弾きやすい。一方、塗れ性の高い第2の

マスクパターンは液体が塗れ広がる。第1のマスクパターンの表面では第2のマスクパタ

ーンの材料となる溶液が半球状にはじかれるため、自己整合的に第2のマスクパターンを

形成することができる。

【0014】

塗れ性の低い第1のマスクパターンとしては、絶縁膜にフッ素プラズマを照射して形成

することができる。フッ素プラズマは、フッ素又はフッ化物の雰囲気内でプラズマを発生

させる方法、又はフッ素樹脂を有する誘電体を有する電極を用いてプラズマを発生させる

方法等がある。

【0015】

また、塗れ性の低い第1のマスクパターンを形成する方法としては、塗れ性の低い材料

を所定の場所吐出又は塗布して形成することができる。塗れ性の低い材料としては、フッ

化炭素鎖を有する化合物が挙げられる。

【0016】

塗れ性の低い第1のマスクパターンと塗れ性の高い第2のマスクパターンの接触角の差

は、30度、望ましくは40度以上であることが好ましい。この結果、第1のマスクパタ

ーンの表面で第2のマスクパターンの材料が半球状にはじかれ、自己整合的に各マスクパ

ターンを形成することが可能である。

【0017】

また、第2のマスクパターンは、膜パターンを形成するマスクとして用いることが好ま

しい。

【0018】

膜パターンとしては、所望の形状を有する絶縁膜、半導体膜、及び導電膜、並びにコン

タクトホールを有する絶縁膜である。代表的には、ゲート絶縁膜、層間絶縁膜、保護膜、

コンタクトホールを有する絶縁膜等の絶縁膜、チャネル形成領域、ソース領域、ドレイン

領域等の半導体膜、及びソース電極、ドレイン電極、配線、ゲート電極、画素電極、アン

テナ等の導電膜が挙げられる。なお、マスクパターンを除去した後、該膜パターンの周辺

(マスクパターンが形成されていた領域)には、マスクパターンの組成物が残存している

。

【0019】

塗れ性の低い第1のマスクパターンは、液相法又は印刷法を用いて形成する。液相法の

代表例としては、液滴吐出法、インクジェット法等が挙げられる。

【0020】

また、塗れ性の高い第2のマスクパターンは、液相法を用いて形成する。液相法の代表

例としては、液滴吐出法、インクジェット法、スピンコート法、ロールコート法、スロッ

トコート法等が挙げられる。

【0021】

また、本発明の一は、塗れ性の低い第1のマスクパターン及び塗れ性の高い第2のマス

クパターンを用いて形成される膜パターン、又は部材を用いて半導体素子を形成すること

を特徴とする。半導体素子としては、TFT、電界効果トランジスタ(FET)、MOS

トランジスタ、バイポーラトランジスタ、有機半導体トランジスタ、MIM素子、記憶素

子、ダイオード、光電変換素子、容量素子、抵抗素子等が挙げられる。

【0022】

また、本発明の一は、塗れ性の低い第1のマスクパターン及び塗れ性の高い第2のマス

クパターンを用いて形成される膜パターン、該膜パターン付基板、又は半導体素子を有す

る半導体装置、及びその作製方法を特徴とする。半導体装置としては、半導体素子で構成

された集積回路、表示装置、無線タグ、ICタグ、ICカード等が挙げられる。表示装置

としては、代表的には液晶表示装置、発光表示装置、DMD(Digital Micromirror Devi

ce;デジタルマイクロミラーデバイス)、PDP(Plasma Display Panel;プラズマディ

スプレイパネル)、FED(Field Emission Display;フィールドエミッションディスプ

レイ)、電気泳動表示装置(電子ペーパー)等の表示装置があげられる。なお、TFTは

、順スタガ型TFT、逆スタガ型TFT(チャネルエッチ型TFT又はチャネル保護型T

FT)、トップゲートのコプレナー型TFT、ボトムゲートのコプレナー型TFT等であ

る。

【0023】

なお、本発明において、表示装置とは、表示素子を用いたデバイス、即ち画像表示デバ

イスを指す。また、表示パネルにコネクター、例えばフレキシブルプリント配線(FPC

:Flexible Printed Circuit)もしくはTAB(Tape A

utomated Bonding)テープもしくはTCP(Tape Carrier

Package)が取り付けられたモジュール、TABテープやTCPの先にプリント

配線板が設けられたモジュール、または表示素子にCOG(Chip On Glass

)方式によりIC(集積回路)やCPUが直接実装されたモジュールも全て表示装置に含

むものとする。

【0024】

また、本発明の一は、上記膜パターン、それを有する基板、半導体素子、又は半導体装

置を有する液晶テレビジョン、若しくはELテレビジョンである。

【0025】

また、本発明の一は、親液表面上に撥液表面を形成する材料を用いてマスクパターンを

形成した後、マスクパターンの外縁に親液性を示す材料を用いて膜パターン、及び該膜パ

ターンを有する基板を形成することを特徴とする。

【0026】

また、本発明の一は、親液表面上に撥液表面を形成する材料を用いてマスクパターンを

形成した後、マスクパターンを除く領域に親液性を示す材料を用いて膜パターン、及び膜

パターンを有する基板を形成することを特徴とする。

【0027】

また、本発明の一は、親液表面上に撥液表面を形成する材料を用いてマスクパターンを

形成した後、マスクパターンを除く領域に親液性を示す材料を用いて膜パターン、及び膜

パターンを有する基板を形成することを特徴とする。

【0028】

また、本発明の一は、親液表面を有する膜又は部材上に撥液表面を形成する材料を用い

て第1のマスクパターンを形成した後、親液性を示す材料を用いて第2のマスクパターン

を形成し、第1のマスクパターン及び該第1のマスクパターンで覆われた親液表面を有す

る膜又は部材を除去して、膜パターン又はコンタクトホールを形成することを特徴とする

。なお、この後、第2のマスクパターンを除去することも可能である。

【0029】

膜パターンとしては、所望の形状を有する絶縁膜、半導体膜、及び導電膜、並びにコン

タクトホールを有する絶縁膜である。代表的には、ゲート絶縁膜、層間絶縁膜、保護膜、

コンタクトホールを有する絶縁膜等の絶縁膜、チャネル形成領域、ソース領域、ドレイン

領域等の半導体膜、及びソース電極、ドレイン電極、配線、ゲート電極、画素電極、アン

テナ等の導電膜が挙げられる。なお、マスクパターンを除去した後、該膜パターンの周辺

(マスクパターンが形成されていた領域)には、マスクパターンの組成物が残存している

。

【0030】

撥液表面を形成する材料の代表例としては、Rn−Si−X(4-n)(n=1、2、3)の

化学式で表されるシランカップリング剤があげられる。ここで、Rは、アルキル基などの

比較的不活性な基を含む物である。また、Xはハロゲン、メトキシ基、エトキシ基又はア

セトキシ基など、基質表面の水酸基あるいは吸着水との縮合により結合可能な加水分解基

からなる。

【0031】

また、シランカップリング剤として、Rにフルオロアルキル基を有するフッ素系シラン

カップリング剤(フルオロアルキルシラン(FAS))は、より撥液性が高い撥液表面を

形成する。

【0032】

また、撥液表面を形成する材料の代表例として、フッ素炭素鎖を有する材料(代表的に

は、フッ素系樹脂)があげられる。

【0033】

また、撥液表面を形成する溶媒としては、nーペンタン、n−ヘキサン、n−ヘプタン

、n−オクタン、n−デカン、ジシクロペンタン、ベンゼン、トルエン、キシレン、デュ

レン、インデン、テトラヒドロナフタレン、デカヒドロナフタレン、スクワランなどの炭

化水素系溶媒又はテトラヒドロフランなどである。

【0034】

また、撥液表面形成する材料に、プラズマ、レーザ又は電子ビーム等の処理を施すこと

によって、撥液性をより向上させることができる。

【0035】

親液性を示す材料としては、親液表面と加水分解により結合することが可能な置換基(

水酸基、水素基)、又は水素結合をすることが可能な置換基(水酸基、水素基、カルボニ

ル基、アミノ基、スルホニル基、エーテル基等)を有する材料である。代表的には、アク

リル樹脂、ポリイミド樹脂、メラミン樹脂、ポリエステル樹脂、ポリカーボネート樹脂、

フェノール樹脂、エポキシ樹脂、ポリアセタール、ポリエーテル、ポリウレタン、ポリア

ミド(ナイロン)、フラン樹脂、ジアリルフタレート樹脂等の有機樹脂、シロキサン、ポ

リシラザンを用いることができる。シロキサンとは、珪素(Si)と酸素(O)との結合

で骨格構造が構成され、置換基に少なくとも水素を含む、又は置換基にフッ素、アルキル

基、又は芳香族炭化水素のうち少なくとも1種を有するポリマー材料である。またポリシ

ラザンとは、珪素(Si)と窒素(N)の結合を有するポリマー材料である。

【0036】

親液表面とは、極性を示す反応基を表面に有するものであり、代表的には加水分解によ

り結合することが可能な置換基(水酸基、水素基)、又は水素結合することが可能な置換

基(水酸基、水素基、カルボニル基、アミノ基、スルホニル基、エーテル基等)を有する

。

【0037】

撥液表面を形成する材料で形成されるマスクパターンは、液相法を用いて形成する。液

相法の代表例としては、液滴吐出法、インクジェット法等が挙げられる。

【0038】

また、親液性を示す溶液で形成されるマスクパターン又は膜パターンは、液相法を用い

て形成する。液相法の代表例としては、液滴吐出法、インクジェット法、スピンコート法

、ロールコート法、スロットコート法等が挙げられる。

【0039】

また、本発明は、撥液表面を形成する材料で形成されるマスクパターンを用いて形成さ

れる膜パターン、又は部材を用いて半導体素子を形成することを特徴とする。半導体素子

としては、TFT、電界効果トランジスタ(FET)、MOSトランジスタ、バイポーラ

トランジスタ、有機半導体トランジスタ、MIM素子、記憶素子、ダイオード、光電変換

素子、容量素子、抵抗素子等が挙げられる。

【0040】

また、本発明は、撥液表面を有するマスクパターンを用いて形成される膜パターン、該

膜パターン付基板、又は半導体素子を有する半導体装置、及びその作製方法を特徴とする

。半導体装置としては、半導体素子で構成された集積回路、表示装置、無線タグ、ICタ

グ等が挙げられる。表示装置としては、代表的には液晶表示装置、発光表示装置、DMD

(Digital Micromirror Device;デジタルマイクロミラーデバイス)、PDP(Plasma D

isplay Panel;プラズマディスプレイパネル)、FED(Field Emission Display;フィ

ールドエミッションディスプレイ)、電気泳動表示装置(電子ペーパー)等の表示装置が

あげられる。なお、TFTは、順スタガ型TFT、逆スタガ型TFT(チャネルエッチ型

TFT又はチャネル保護型TFT)である。

【0041】

なお、本発明において、表示装置とは、表示素子を用いたデバイス、即ち画像表示デバ

イスを指す。また、表示パネルにコネクター、例えばフレキシブルプリント配線(FPC

:Flexible Printed Circuit)もしくはTAB(Tape A

utomated Bonding)テープもしくはTCP(Tape Carrier

Package)が取り付けられたモジュール、TABテープやTCPの先にプリント

配線板が設けられたモジュール、または表示素子にCOG(Chip On Glass

)方式によりIC(集積回路)やCPU(中央演算装置:Central Proces

sing Unit)が直接実装されたモジュールも全て表示装置に含むものとする。

【0042】

また、本発明は、上記膜パターン、それを有する基板、半導体素子、又は半導体装置を

有する液晶テレビジョン、ELテレビジョンである。

【発明の効果】

【0043】

本発明のごとく、塗れ性の低い第1のマスクパターン及び塗れ性の高い第2のマスクパ

ターンを用いることにより、所望の形状を有する膜パターンを所望の箇所に形成すること

ができる。層間絶縁膜、平坦化膜、ゲート絶縁膜等として機能する膜を、所望の箇所に選

択的に形成することができる。しかも、レジストマスクパターンを用いた露光・現像プロ