半導体装置の製造方法、スパッタ装置及びコリメート板

【課題】ターゲットの利用率を十分に向上させ、且つ、プラズマダメージを十分に抑制する。

【解決手段】複数の貫通孔が形成されているコリメート板を介してスパッタを行うことにより、ゲート絶縁膜及びゲート電極を有する半導体素子上に金属膜を形成する金属膜形成工程(ステップS1)を備える。この金属膜形成工程では、貫通孔のアスペクト比(貫通孔の深さ/貫通孔の開口径)が1/6以上2/3以下であるコリメート板を用いる。金属膜形成工程を、半導体装置のシリサイド形成工程で行う。半導体素子のアンテナ比を45000以下とする。アスペクト比をコリメート板の中央部から外周部に向けて徐々に小さくし、コリメート板の最外周部ではアスペクト比を1/2以下とする。

【解決手段】複数の貫通孔が形成されているコリメート板を介してスパッタを行うことにより、ゲート絶縁膜及びゲート電極を有する半導体素子上に金属膜を形成する金属膜形成工程(ステップS1)を備える。この金属膜形成工程では、貫通孔のアスペクト比(貫通孔の深さ/貫通孔の開口径)が1/6以上2/3以下であるコリメート板を用いる。金属膜形成工程を、半導体装置のシリサイド形成工程で行う。半導体素子のアンテナ比を45000以下とする。アスペクト比をコリメート板の中央部から外周部に向けて徐々に小さくし、コリメート板の最外周部ではアスペクト比を1/2以下とする。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置の製造方法、スパッタ装置及びコリメート板に関する。

【背景技術】

【0002】

例えば、半導体装置のシリサイド形成工程(サイリサイドプロセス)でのTi、Co、Niのスパッタ成膜は、スパッタによるプラズマダメージを低減することを主な目的として、ターゲットとウェハとの間にコリメート板を配置して行うことが好ましい。このようにコリメート板を用いて行うスパッタを、コリメートスパッタという。

【0003】

コリメート板は、荷電粒子(主に電子)を捕捉することにより、半導体素子に加わるプラズマダメージを低減する。しかし、コリメート板は、ターゲットから打ち出されたスパッタ粒子の一部も捕捉するため、ウェハに到達するスパッタ粒子の割合を下げ、ターゲットの利用率を低下させる。なお、ターゲットの利用率は、スパッタによるターゲットの重量の減少量のうち、スパッタによりウェハ上に成膜される金属膜の総重量の割合で表される。

【0004】

このため、コリメートスパッタにおいては、プラズマダメージを十分に抑制し、なおかつ、ターゲットの利用率を十分に高めることが好ましい。

【0005】

コリメートスパッタを用いて半導体装置を製造する方法については、例えば、特許文献1、2に開示されている。

【0006】

特許文献1には、コリメート板の貫通孔のアスペクト比を0.7以上1.3以下とする点が記載されている。

【0007】

特許文献2には、膜厚均一性を改善する目的で、コリメート板の貫通孔のアスペクト比を中央から外側にかけて徐々に小さくする技術が開示されている。なお、特許文献2では、最も小さいアスペクト比を1とすると、最も大きいアスペクト比を1.05から1.5とする点が記載されている。すなわち、特許文献2では、複数の貫通孔どうしでの相対値によってアスペクト比を定義しており、1つの貫通孔における開口径に対する深さの割合については記載がない。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特開2004−263305号公報

【特許文献2】特開2007−273490号公報

【発明の概要】

【発明が解決しようとする課題】

【0009】

特許文献1のようにアスペクト比が0.7以上1.3以下のコリメート板を用いる場合、プラズマダメージは十分に抑制できるが、コリメート板によるスパッタ粒子の捕捉割合が高いため、ターゲットの利用率が低下してしまう。

【0010】

ターゲットは高価なものであるため、できるだけその利用率を向上させることが好ましいが、例えば、アスペクト比が1のコリメート板を用いてスパッタを行った場合、ターゲットの利用率が僅か20%程度となってしまい、残り80%程度はコリメート板もしくはシールドに付着して無駄になる。

【0011】

このように、ターゲットの利用率を十分に向上させ、且つ、プラズマダメージを十分に抑制することは困難だった。

【課題を解決するための手段】

【0012】

本発明は、複数の貫通孔が形成されているコリメート板を介してスパッタを行うことにより、ゲート絶縁膜及びゲート電極を有する半導体素子上に金属膜を形成する金属膜形成工程を備え、前記金属膜形成工程では、前記貫通孔のアスペクト比(前記貫通孔の深さ/前記貫通孔の開口径)が1/6以上2/3以下である前記コリメート板を用いることを特徴とする半導体装置の製造方法を提供する。

【0013】

この半導体装置の製造方法によれば、貫通孔のアスペクト比が2/3以下であるコリメート板を用いてスパッタを行うので、コリメート板によるスパッタ粒子の捕捉割合を低下させることにより、ターゲットの利用率を十分に向上させることができる。しかも、貫通孔のアスペクト比が1/6以上であるコリメート板を用いてスパッタを行うので、半導体素子に加わるプラズマダメージを十分に抑制することができる。

【0014】

また、本発明は、スパッタ室と、前記スパッタ室内において相互に対向するように配置されているバッキングプレート及び成膜対象物ホルダと、前記バッキングプレートと前記成膜対象物ホルダとの間に配置されているコリメート板と、前記バッキングプレートと前記成膜対象物ホルダとの間の空間の周囲に配置され、前記コリメート板と電気的に接続されるシールドと、を備え、前記バッキングプレートにはターゲットを、前記成膜対象物ホルダには成膜対象物を、前記成膜対象物と前記ターゲットとが前記コリメート板を挟んで相互に対向するようにそれぞれ配置した状態で、前記バッキングプレートと前記シールドとの間に電圧を印加することにより、プラズマを形成して、前記ターゲットから飛び出すスパッタ粒子を前記コリメート板を介して前記成膜対象物に付着させるように構成され、前記コリメート板には複数の貫通孔が形成され、前記貫通孔のアスペクト比(前記貫通孔の深さ/前記貫通孔の開口径)が1/6以上2/3以下であることを特徴とするスパッタ装置を提供する。

【0015】

また、本発明は、複数の貫通孔が形成され、前記貫通孔のアスペクト比(前記貫通孔の深さ/前記貫通孔の開口径)が1/6以上2/3以下であることを特徴とするコリメート板を提供する。

【発明の効果】

【0016】

本発明によれば、ターゲットの利用率を十分に向上させることができるとともに、プラズマダメージを十分に抑制することができる。

【図面の簡単な説明】

【0017】

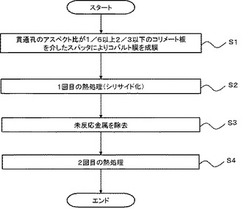

【図1】第1の実施形態に係る半導体装置の製造方法の一連の工程を示すフローチャートである。

【図2】第1の実施形態に係るスパッタ装置の正面断面図である。

【図3】第1の実施形態に係るコリメート板を示す図であり、このうち(a)は平面図、(b)は正面断面図である。

【図4】第1の実施形態に係る半導体装置の製造方法を説明するための一連の工程図である。

【図5】第1の実施形態に係る半導体装置の製造方法を説明するための一連の工程図である。

【図6】第1の実施形態に係る半導体装置の製造方法を説明するための一連の工程図である。

【図7】第1の実施形態に係る半導体装置の製造方法を説明するための一連の工程図である。

【図8】ウェハの面内における成膜速度及び膜厚均一性と、コリメート板の貫通孔のアスペクト比と、の関係を示す図である。

【図9】ウェハの面内における成膜速度及び膜厚均一性と、コリメート板の貫通孔のアスペクト比と、の関係をプロットしたグラフを示す図である。

【図10】ウェハの面内における成膜速度及び膜厚均一性と、コリメート板の貫通孔のアスペクト比と、の関係をプロットしたグラフを示す図である。

【図11】半導体装置のアンテナ比とゲート絶縁膜へのプラズマダメージとの関係を示す図である。

【発明を実施するための形態】

【0018】

以下、本発明の実施形態について、図面を用いて説明する。なお、すべての図面において、同様の構成要素には同一の符号を付し、適宜に説明を省略する。

【0019】

〔第1の実施形態〕

図1は第1の実施形態に係る半導体装置の製造方法の一連の工程を示すフローチャートであり、特に、半導体装置のシリサイド形成工程に含まれる一連の工程を示す。図2は第1の実施形態に係るスパッタ装置100の正面断面図である。図3は第1の実施形態に係るコリメート板1を示す図であり、このうち(a)は平面図、(b)は正面断面図である。図4乃至図7は第1の実施形態に係る半導体装置の製造方法を説明するための一連の工程図である。図8はウェハの面内における成膜速度及び膜厚均一性と、コリメート板1の貫通孔2のアスペクト比と、の関係を示す図であり、図9及び図10はウェハの面内における成膜速度及び膜厚均一性と、コリメート板1の貫通孔のアスペクト比と、の関係をプロットしたグラフを示す図である。図11は半導体装置のアンテナ比とゲート絶縁膜38へのプラズマダメージとの関係を示す図である。

【0020】

本実施形態に係る半導体装置の製造方法では、複数の貫通孔2が形成されているコリメート板1を介してスパッタを行うことにより、ゲート絶縁膜38及びゲート電極33を有する半導体素子上に金属膜(例えば、Co膜37)を形成する金属膜形成工程(ステップS1)を備え、金属膜形成工程では、貫通孔2のアスペクト比(貫通孔2の深さD/貫通孔2の開口径W)が1/6以上2/3以下であるコリメート板1を用いる。また、本実施形態に係るスパッタ装置100は、スパッタ室10と、スパッタ室10内において相互に対向するように配置されているバッキングプレート12及び成膜対象物ホルダ(例えば、基板ホルダ13)と、バッキングプレート12と成膜対象物ホルダ(例えば、基板ホルダ13)との間に配置されているコリメート板1と、バッキングプレート12と成膜対象物ホルダ(例えば、基板ホルダ13)との間の空間の周囲に配置され、コリメート板1と電気的に接続されるシールド4と、を備え、バッキングプレート12にはターゲット11を、成膜対象物ホルダ(例えば、基板ホルダ13)には成膜対象物(例えば、ウェハ20)を、成膜対象物(例えば、ウェハ20)とターゲット11とがコリメート板1を挟んで相互に対向するようにそれぞれ配置した状態で、バッキングプレート12とシールド4との間に電圧を印加することにより、プラズマを形成して、ターゲット11から飛び出すスパッタ粒子をコリメート板1を介して成膜対象物(例えば、ウェハ20)に付着させるように構成され、コリメート板1には複数の貫通孔2が形成され、貫通孔2のアスペクト比(貫通孔2の深さD/貫通孔2の開口径W)が1/6以上2/3以下である。また、本実施形態に係るコリメート板1は、複数の貫通孔2が形成され、貫通孔2のアスペクト比(貫通孔2の深さD/貫通孔2の開口径W)が1/6以上2/3以下である。以下、詳細に説明する。

【0021】

先ず、本実施形態に係るスパッタ装置100の構成を説明する。

【0022】

図2に示すように、スパッタ装置100は、スパッタ室10と、スパッタ室10内において相互に対向するように配置されているバッキングプレート12及び基板ホルダ13と、これらバッキングプレート12と基板ホルダ13との間に配置されているコリメート板1と、を備える。更に、スパッタ装置100は、コリメート板保持部3と、シールド4と、ウェハ保持部5と、をスパッタ室10内に備え、カソードマグネット7をスパッタ室10の上側に備えている。さらに図示していないが、シールド4の内側には、シールド4の内側にスパッタガスを導入するガス導入口が設けられている。また、スパッタ室10は真空ポンプに接続されている。スパッタ室10内は、スパッタを行っていない時は真空ポンプによって高真空に保たれ、スパッタ時は真空ポンプによって排気を行いながら、ガス導入口より所定流量の不活性ガス(例えばAr)をシールド4の内側に流し、シールド4の内側のガス圧力を0.1mTorr〜50mTorrの間の一定圧力とする。このスパッタ装置100により、コリメートスパッタを行うことが可能である。

【0023】

シールド4、コリメート板保持部3及びバッキングプレート12は、それぞれ導電性の材質(例えば金属)からなる。シールド4は、図2に示すように、バッキングプレート12と基板ホルダ13との間の空間の周囲に配置されている。このシールド4は、コリメート板1と電気的に接続される。具体的には、例えば、以下に説明するように、シールド4は、コリメート板保持部3を介してコリメート板1と電気的に接続されている。コリメート板保持部3は、例えば、シールド4に固定されている。なお、シールド4の一部によりコリメート板保持部3が構成されていても良い。このコリメート板保持部3は、例えば、コリメート板1の外周部の被保持部9(図3:後述)を上下から挟み持つようにして保持する。これにより、シールド4は、コリメート板保持部3を介してコリメート板1と電気的に接続される。ターゲット11は、メタルボンディングもしくは拡散接合により、バッキングプレート12における基板ホルダ13側の面上に取り付けられている。成膜対象物としての半導体ウェハ(以下、単にウェハ)20は、基板ホルダ13におけるバッキングプレート12側の面上に配置される。ウェハ保持部5は、基板ホルダ13上においてウェハ20を所定位置に位置決めする。こうして、ウェハ20とターゲット11とがコリメート板1を挟んで相互に対向するように配置される。なお、基板ホルダ13は、接地(アース接続)されていても良いし、どこにも接地されていなくても良い。この状態で、所定流量の不活性ガス(例えばAr)を、ガス導入口よりシールド4の内側に流し、シールド4の内側のガス圧力を0.1mTorr〜50mTorrの間の一定圧力に設定し、バッキングプレート12とシールド4との間に電圧を印加することにより、不活性ガスのプラズマが発生する。これにより、ターゲット11から飛び出すスパッタ粒子をコリメート板1を介してウェハ20に付着させて、ウェハ20上に金属膜を成膜させることができる。

【0024】

なお、本実施形態に係るスパッタ装置100は、コリメート板1以外の構成については、周知のコリメートスパッタ用のスパッタ装置と同様であるため詳細な説明を省略する。

【0025】

このスパッタ装置100は、例えば、半導体装置のシリサイド形成工程で用いられるシリサイド形成用スパッタ装置である。

【0026】

次に、図3を参照してコリメート板1の構成を説明する。

【0027】

図3に示すように、コリメート板1は、扁平な板状の本体部8を備えている。この本体部8には、該本体部8の表裏を貫通するように複数の貫通孔2が形成されている。

【0028】

貫通孔2の深さ(縦方向長さ)をD(図3(b))、貫通孔2の開口径(横方向長さ:例えば、対向する2つの角の間の距離)をW(図3(a)、(b))とすると、貫通孔2のアスペクト比は、D/Wで表される。貫通孔2のアスペクト比は1/6以上2/3以下に設定されている。アスペクト比を2/3以下とするのは、コリメート板1により捕捉されるスパッタ粒子を減らしターゲット11の利用率を高くするためである。アスペクト比を1/6以上とするのは、コリメート板1により荷電粒子を十分に捕捉し、プラズマダメージの低減効果を十分に得るためである。

【0029】

更に、このアスペクト比は、コリメート板1の中央部から外周部に向けて徐々に小さくなっていることがより好ましい。具体的には、例えば、図3(b)に示すように、貫通孔2の深さD(本体部8の厚さに等しい)をコリメート板1の中央部から外周部に向けて徐々に薄くすることにより、アスペクト比をコリメート板1の中央部から外周部に向けて徐々に小さくしている。

【0030】

このように貫通孔2のアスペクト比がコリメート板1の中央部から外周部に向けて徐々に小さくなっている場合に、コリメート板1の最外周部ではこのアスペクト比が1/2以下であることが好ましい。このようなコリメート板1を用いることにより、ターゲット11の利用率、プラズマダメージ低減効果、及び膜厚均一性をそれぞれ良好にすることができる。なお、コリメート板1の中央部の貫通孔2のアスペクト比は2/3程度とすることが好ましい。

【0031】

ターゲット11の利用率を更に向上させる方法として、ターゲット11からスパッタされる粒子の方向分布を調整する方法がある。スパッタ面に対して垂直方向にスパッタされる粒子の割合を増やせば、コリメート板1により捕捉される粒子の割合が減り、ウェハ20に到達する割合が増加してターゲット11の利用率が上がる。スパッタ面に対して垂直方向にスパッタされる粒子の割合を増やす方法としては、スパッタ面を金属結晶の最稠密面に垂直な面とする方法、或いは、スパッタの放電電圧を高くする方法がある。

【0032】

また、本体部8の外周部には、コリメート板保持部3により保持される被保持部9が形成されている。

【0033】

図3に示すように、貫通孔2の平面形状は、例えば、正六角形であり、コリメート板1の平面形状は、六方最密格子形状となっている。各貫通孔2の平面寸法及び形状は、コリメート板1のほぼ全面で均一とされている。ただし、コリメート板1の最外周部では、例えば、コリメート板1の外周形状に合わせて、正六角形とは異なる異形形状(正六角形の一部分を切り取ったような形状)の貫通孔2aが形成されており、正六角形の貫通孔2bと比べて平面寸法も小さくされている。なお、貫通孔2bの平面寸法(開口径W)は、10mm以上30mm以下であることが好ましく、貫通孔2bの深さは、3mm以上20mm以下であることが好ましい。

【0034】

なお、貫通孔2の平面形状及びコリメート板1の平面形状は、この例に限らない。例えば、貫通孔2は、四角形、長方形、正方形、ひし形、円形などであっても良い。また、図3では平面視におけるコリメート板1の外周形状が円形である例を示しているが、コリメート板1の外周形状はその他の形状であっても良い。

【0035】

また、隣り合う貫通孔2を相互に仕切る隔壁2cの厚さは、0.5mm以上2mm以下であることが好ましい。

【0036】

また、コリメート板1の材質としては、例えば、チタン、SUSが挙げられる。

【0037】

次に、本実施形態に係る半導体装置の製造方法を説明する。

【0038】

図1に示すように、本実施形態に係る半導体装置の製造方法では、金属膜(例えばCo膜37)を成膜する金属膜成膜工程(ステップS1)と、1回目の熱処理によりシリサイド化を行う第1熱処理工程と(ステップS2)と、未反応金属を除去する除去工程(ステップS3)と、2回目の熱処理を行う第2熱処理工程(ステップS4)と、をこの順に行うことにより、半導体素子上にシリサイド層39を形成する。

【0039】

本実施形態に係る半導体装置の製造方法では、先ず、図4に示すように、一般的なCMOS(Complementary Metal Oxide Semiconductor)の製造方法によって半導体素子を作成する。すなわち、シリコン基板31上に、素子分離膜としてのSTI(Shallow Trench Isolation)32、ゲート絶縁膜38、ゲート電極33、エクステンション34、サイドウォール35及びソース・ドレイン拡散領域36を形成することにより、半導体素子を作成する。

【0040】

ここで、この半導体素子としては、アンテナ比が45000以下となるように作成された半導体素子を用いることが好ましい。ここで、アンテナ比は、ゲート電極33の面積をS1、ゲート絶縁膜38の面積をS2とすると、S1/S2で表される。

【0041】

なお、ゲート絶縁膜38の膜厚は、例えば、18Å(1.8nm)以上70Å(7nm)とすることができる。

【0042】

次に、図4に示すように、この半導体素子上にコバルト膜37(以下、Co膜37)を成膜する。すなわち、半導体素子のシリコン層(例えば、ソース・ドレイン拡散領域36、及び、ポリシリコンからなるゲート電極33)上及び絶縁層(例えば、STI32及びサイドウォール35)上に、コバルト膜37を成膜する(図1のステップS1)。なお、この成膜前には、例えば、フッ酸系のエッチング液によりウェハ20の表面の自然酸化膜を除去しておくことが好ましい。

【0043】

ステップS1の成膜は、スパッタ装置100を用いたコリメートスパッタにより行う。

【0044】

ここで、ターゲット11としては、Co(コバルト)ターゲットを用いる。ターゲット11は、例えば、そのスパッタ面(コリメート板1及びウェハ20の方を向く面)が面方位(002)が主配向となるように構成されている。すなわち、ターゲット11がスパッタ装置100のバッキングプレート12に上述したように取り付けられた状態で、多結晶Coからなるターゲット11の結晶配向において、主として(002)の面がコリメート板1及びウェハ20の方を向くように、ターゲット11は構成されている。これは、コバルトの場合(002)面に垂直な方向で透磁率が最も低く、カソードマグネット7によりターゲット11の表面部付近に形成される磁場の強さの低下を小さくするためである。

【0045】

また、コリメート板1とターゲット11との距離は、20mm以上40mm以下であることが好ましい。また、コリメート板1とウェハ20との距離は20mm以上50mm以下であることが好ましい。また、ゲート電極33に到達する電荷量が0.1C/cm2以下となるような条件でスパッタを行うことが好ましい。

【0046】

このスパッタは、放電電圧を400V以上600V以下、スパッタ電力を1kw以上5kw以下、スパッタ温度(例えば、ウェハ20の温度)を300℃以上400℃以下として行うことが好ましい。

【0047】

このようにCo膜37を成膜した後は、1回目の熱処理(アニール)を行う(図1のステップS2)。この熱処理により、Co膜37はその下層に位置するシリコン層(例えば、ソース・ドレイン拡散領域36、及び、ポリシリコンなどからなるゲート電極33)と反応してシリサイド化する。これにより、図5に示すように、ソース・ドレイン拡散領域36上、及び、ゲート電極33上にシリサイド層(コバルトシリサイド層)39を形成することができる。

【0048】

次に、このような1回目の熱処理後のウェハ20を例えばHPM(hydrochloic acid/hydrogen Peroxide Mixture)などの薬液に浸すことによって、未反応金属(図5の段階で残留しているCo膜37)を除去する除去処理を行う(図1のステップS3)。これにより、図6に示すように、未反応金属を除去することができる。

【0049】

このように未反応金属を除去した後は、2回目の熱処理(図1のステップS4)を行う。これにより、半導体装置50(図7)を得ることができる。

【0050】

次に、図8乃至図10を参照して、実施例及び比較例について説明する。

【0051】

なお、各実施例及び各比較例のデータは、図1のステップS1の金属膜形成工程の直後にCo膜37の膜厚を測定することにより得たデータである。また、各実施例及び比較例は、スパッタに用いたコリメート板1が互いに異なる他は、全てのスパッタ条件(スパッタ時間、スパッタ電力及びスパッタ室10内のArの流量等)を同一条件とした。このため、ターゲット11の利用率は膜厚(または成膜速度)に比例する。なお、図8及び図9の膜厚均一性は、ウェハ20上のCo膜37の膜厚の平均値をX、最も厚い部分の膜厚をY1、最も薄い部分の膜厚をY2とすると、{(Y1−Y2)/2X}×100(%)で表される。

【0052】

先ず、実施例1として、コリメート板1の全面に亘って貫通孔2のアスペクト比(図中のA/R)を2/3とした場合には、図8乃至図10に示すように、ウェハ20上のCo膜37の膜厚均一性が3.0%となり、成膜速度は6Å/秒程度となった。

【0053】

この比較例1として、コリメート板(図示略)の全面に亘って貫通孔のアスペクト比を1とした場合には、図8乃至図10に示すように、ウェハ20上のCo膜の膜厚均一性が1.2%となり、成膜速度は4Å/秒前後となった。比較例1では、実施例1よりも成膜速度が遅い、つまり、ターゲット11の利用率が悪いことが分かる。

【0054】

次に、実施例2として、コリメート板1の全面に亘って貫通孔2のアスペクト比を1/3とした場合には、図8乃至図10に示すように、ウェハ20上のCo膜37の膜厚均一性が6.5%となり、成膜速度は10Å/秒〜11Å/秒程度となった。つまり、アスペクト比を小さくすることにより、ターゲット11の利用率を更に向上させることができる。

【0055】

次に、実施例3として、コリメート板1の中央部では貫通孔2のアスペクト比が2/3、コリメート板1の最外周部では貫通孔2のアスペクト比が1/2であり、中央部から外周部にかけて徐々にアスペクト比を小さくしたコリメート板1を用いた場合を説明する。この場合、図8及び図10に示すように、ウェハ20上のCo膜37の膜厚均一性が1.2%となり、成膜速度は8Å/秒前後となった。つまり、実施例3のコリメート板1を用いることにより、ターゲット11の利用率を高い水準(約8Å/秒)にでき、且つ、膜厚均一性も高い水準(約1.2%)にすることができる。

【0056】

更に、実施例4として、コリメート板1の中央部では貫通孔2のアスペクト比が2/3、コリメート板1の最外周部では貫通孔2のアスペクト比が0.6(3/5)であり、中央部から外周部にかけて徐々にアスペクト比を小さくしたコリメート板1を用いた場合を説明する。この場合、図10に示すように、ウェハ20上のCo膜37の膜厚均一性が1.3%程度となり、成膜速度は7Å/秒前後となった。

【0057】

同様に、実施例5として、コリメート板1の中央部では貫通孔2のアスペクト比が2/3、コリメート板1の最外周部では貫通孔2のアスペクト比が0.4(2/5)であり、中央部から外周部にかけて徐々にアスペクト比を小さくしたコリメート板1を用いた場合を説明する。この場合、図10に示すように、ウェハ20上のCo膜37の膜厚均一性が1.1%程度となり、成膜速度は9Å/秒程度となった。

【0058】

同様に、実施例6として、コリメート板1の中央部では貫通孔2のアスペクト比が2/3、コリメート板1の最外周部では貫通孔2のアスペクト比が0.3(3/10)であり、中央部から外周部にかけて徐々にアスペクト比を小さくしたコリメート板1を用いた場合を説明する。この場合、図10に示すように、ウェハ20上のCo膜37の膜厚均一性が1.4%程度となり、成膜速度は10Å/秒前後となった。

【0059】

同様に、実施例7として、コリメート板1の中央部では貫通孔2のアスペクト比が2/3、コリメート板1の最外周部では貫通孔2のアスペクト比が1/6であり、中央部から外周部にかけて徐々にアスペクト比を小さくしたコリメート板1を用いた場合を説明する。この場合、図10に示すように、ウェハ20上のCo膜37の膜厚均一性が1.8%程度となり、成膜速度は11Å/秒前後となった。

【0060】

つまり、実施例4乃至7のコリメート板1を用いることによっても、ターゲット11の利用率を高い水準(約7Å/秒〜11Å/秒程度)にでき、且つ、膜厚均一性も高い水準(約1.1〜1.8%)にすることができる。

【0061】

なお、比較例2として、コリメート板を用いずにスパッタを行った場合(図中のアスペクト比=0)には、図9に示すように、成膜速度が約16Å/秒となった。ただし、この場合、背景技術で説明したように、プラズマダメージを低減することができない。

【0062】

次に、図11を参照して、図1のステップS1の金属膜形成工程で用いる半導体素子(半導体装置)のアンテナ比とゲート絶縁膜へのプラズマダメージとの関係について説明する。

【0063】

図11に示すように、上述の比較例1のコリメート板(アスペクト比が1)を用いた場合には、アンテナ比が800以上45000以下の範囲では、プラズマダメージが観察されず、アンテナ比が125000の場合にはプラズマダメージが観察されたゲート絶縁膜が存在した。

【0064】

一方、実施例8として、コリメート板1の中央部では貫通孔2のアスペクト比が2/3、コリメート板1の最外周部では貫通孔2のアスペクト比が1/3であり、中央部から外周部にかけて徐々にアスペクト比を小さくしたコリメート板1を用いた場合を説明する。この場合にも、アンテナ比が800以上45000以下の範囲では、プラズマダメージが観察されず、アンテナ比が125000の場合にはプラズマダメージが観察されたゲート絶縁膜38が存在した。このように、実施例8のコリメート板1を用いた場合のプラズマダメージの程度は、比較例1のコリメート板を用いた場合と同程度に抑制できた。このように、図1のステップS1の金属膜形成工程では、アンテナ比が45000以下の半導体素子を用いることにより、プラズマダメージの影響を十分に抑制することができる。

【0065】

以上のような第1の実施形態によれば、複数の貫通孔2が形成されているコリメート板1を介してスパッタを行うことにより、ゲート絶縁膜38及びゲート電極33を有する半導体素子上に金属膜(例えば、Co膜37)を形成する金属膜形成工程(ステップS1)を備え、金属膜形成工程では、貫通孔2のアスペクト比が1/6以上2/3以下であるコリメート板1を用いるので、コリメート板1によるスパッタ粒子の捕捉割合を低下させることにより、ターゲット11の利用率を十分に向上させることができる。しかも、貫通孔2のアスペクト比が1/6以上であるので、ゲート絶縁膜38へのプラズマダメージも十分に抑制することができる。

【0066】

また、ターゲット11の利用率を向上させることにより、ターゲット11の消費量を抑制できるため、ターゲット11の交換頻度を低減し、スパッタ装置100の稼働率を向上させることができる。また、コリメート板1を用いたスパッタを繰り返し行うと、貫通孔2内には次第にスパッタ粒子が堆積し、貫通孔2が詰まってくる。すると、金属膜の成膜速度が低下する。しかも、膜厚均一性も悪化する。具体的には、ウェハ20の外周部で膜厚が厚くなり、中央部では膜厚が薄くなる。このため、スパッタ装置100には、コリメート板1を取り外して薬液で洗浄する等のメンテナンスが必要である。このような事情に対し、貫通孔2のアスペクト比が2/3以下のコリメート板1を用いることにより、アスペクト比が2/3を超えるコリメート板を用いる場合と比べて、貫通孔2を詰まりにくくすることができるので、コリメート板1のメンテナンス頻度も低減することができる。

【0067】

また、金属膜形成工程(ステップS1)を、半導体装置50のシリサイド形成工程で行うので、半導体装置50のシリサイド層39を均一な膜厚で形成することができる。

【0068】

また、金属膜形成工程(ステップS1)に用いられる半導体素子(半導体装置)のアンテナ比を45000以下とすることにより、ゲート絶縁膜38へのプラズマダメージを抑制することができる。

【0069】

また、Co(コバルト)は強磁性体であるため、コバルトからなるターゲット11を用いる場合、カソードマグネット7によりターゲット11の表面付近に形成される磁場が弱くなり、放電もし難い。コバルトの透磁率は結晶格子の方向によって異なり、(002)面に垂直な方向で最も小さくなる事が知られている。本実施形態では、コバルトからなるターゲット11のスパッタ面を(002)面を主配向とする面として金属膜形成工程(ステップS1)を行うことにより、ターゲット11の表面付近に形成されるカソードマグネット7による磁場の強度低下を抑制し、スパッタを好適に行うことができる。

【0070】

また、貫通孔2のアスペクト比が、コリメート板1の中央部から外周部に向けて徐々に小さくなっているので、金属膜形成工程(ステップS1)で形成される金属膜の膜厚の面内均一性を高めることができる。具体的には、コリメート板1の中央部での貫通孔2のアスペクト比を2/3程度とし、最外周部での貫通孔2のアスペクト比を1/2以下とすることにより、金属膜形成工程(ステップS1)で形成される金属膜の膜厚の面内均一性を高めることができる。

【0071】

上記の実施形態では、金属膜形成工程で成膜する金属膜としてCo膜37を例示したが、この金属膜はCo膜37に限らず、例えば、Ni(ニッケル)膜、或いはTi(チタン)膜であっても良い。従って、ターゲット11としては、Niターゲット、或いはTiターゲットを用いることができる。

【0072】

また、上記の金属膜形成工程は、シリサイド形成工程以外の半導体製造工程で用いても良いし、或いは、半導体製造工程以外に上記の金属膜形成工程を適用しても良い。また、スパッタ装置100がシリサイド形成用スパッタ装置である例を説明したが、スパッタ装置100はシリサイド形成用以外のスパッタ装置であっても良い。

【符号の説明】

【0073】

1 コリメート板

2 貫通孔

2a 貫通孔

2b 貫通孔

2c 隔壁

3 コリメート板保持部

4 シールド

5 ウェハ保持部

7 カソードマグネット

8 本体部

9 被保持部

10 スパッタ室

11 ターゲット

12 バッキングプレート

13 基板ホルダ(成膜対象物ホルダ)

20 半導体ウェハ

31 シリコン基板

32 STI

33 ゲート電極

34 エクステンション

35 サイドウォール

36 ソース・ドレイン拡散領域

37 コバルト膜

38 ゲート絶縁膜

39 シリサイド層

50 半導体装置

100 スパッタ装置

【技術分野】

【0001】

本発明は、半導体装置の製造方法、スパッタ装置及びコリメート板に関する。

【背景技術】

【0002】

例えば、半導体装置のシリサイド形成工程(サイリサイドプロセス)でのTi、Co、Niのスパッタ成膜は、スパッタによるプラズマダメージを低減することを主な目的として、ターゲットとウェハとの間にコリメート板を配置して行うことが好ましい。このようにコリメート板を用いて行うスパッタを、コリメートスパッタという。

【0003】

コリメート板は、荷電粒子(主に電子)を捕捉することにより、半導体素子に加わるプラズマダメージを低減する。しかし、コリメート板は、ターゲットから打ち出されたスパッタ粒子の一部も捕捉するため、ウェハに到達するスパッタ粒子の割合を下げ、ターゲットの利用率を低下させる。なお、ターゲットの利用率は、スパッタによるターゲットの重量の減少量のうち、スパッタによりウェハ上に成膜される金属膜の総重量の割合で表される。

【0004】

このため、コリメートスパッタにおいては、プラズマダメージを十分に抑制し、なおかつ、ターゲットの利用率を十分に高めることが好ましい。

【0005】

コリメートスパッタを用いて半導体装置を製造する方法については、例えば、特許文献1、2に開示されている。

【0006】

特許文献1には、コリメート板の貫通孔のアスペクト比を0.7以上1.3以下とする点が記載されている。

【0007】

特許文献2には、膜厚均一性を改善する目的で、コリメート板の貫通孔のアスペクト比を中央から外側にかけて徐々に小さくする技術が開示されている。なお、特許文献2では、最も小さいアスペクト比を1とすると、最も大きいアスペクト比を1.05から1.5とする点が記載されている。すなわち、特許文献2では、複数の貫通孔どうしでの相対値によってアスペクト比を定義しており、1つの貫通孔における開口径に対する深さの割合については記載がない。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特開2004−263305号公報

【特許文献2】特開2007−273490号公報

【発明の概要】

【発明が解決しようとする課題】

【0009】

特許文献1のようにアスペクト比が0.7以上1.3以下のコリメート板を用いる場合、プラズマダメージは十分に抑制できるが、コリメート板によるスパッタ粒子の捕捉割合が高いため、ターゲットの利用率が低下してしまう。

【0010】

ターゲットは高価なものであるため、できるだけその利用率を向上させることが好ましいが、例えば、アスペクト比が1のコリメート板を用いてスパッタを行った場合、ターゲットの利用率が僅か20%程度となってしまい、残り80%程度はコリメート板もしくはシールドに付着して無駄になる。

【0011】

このように、ターゲットの利用率を十分に向上させ、且つ、プラズマダメージを十分に抑制することは困難だった。

【課題を解決するための手段】

【0012】

本発明は、複数の貫通孔が形成されているコリメート板を介してスパッタを行うことにより、ゲート絶縁膜及びゲート電極を有する半導体素子上に金属膜を形成する金属膜形成工程を備え、前記金属膜形成工程では、前記貫通孔のアスペクト比(前記貫通孔の深さ/前記貫通孔の開口径)が1/6以上2/3以下である前記コリメート板を用いることを特徴とする半導体装置の製造方法を提供する。

【0013】

この半導体装置の製造方法によれば、貫通孔のアスペクト比が2/3以下であるコリメート板を用いてスパッタを行うので、コリメート板によるスパッタ粒子の捕捉割合を低下させることにより、ターゲットの利用率を十分に向上させることができる。しかも、貫通孔のアスペクト比が1/6以上であるコリメート板を用いてスパッタを行うので、半導体素子に加わるプラズマダメージを十分に抑制することができる。

【0014】

また、本発明は、スパッタ室と、前記スパッタ室内において相互に対向するように配置されているバッキングプレート及び成膜対象物ホルダと、前記バッキングプレートと前記成膜対象物ホルダとの間に配置されているコリメート板と、前記バッキングプレートと前記成膜対象物ホルダとの間の空間の周囲に配置され、前記コリメート板と電気的に接続されるシールドと、を備え、前記バッキングプレートにはターゲットを、前記成膜対象物ホルダには成膜対象物を、前記成膜対象物と前記ターゲットとが前記コリメート板を挟んで相互に対向するようにそれぞれ配置した状態で、前記バッキングプレートと前記シールドとの間に電圧を印加することにより、プラズマを形成して、前記ターゲットから飛び出すスパッタ粒子を前記コリメート板を介して前記成膜対象物に付着させるように構成され、前記コリメート板には複数の貫通孔が形成され、前記貫通孔のアスペクト比(前記貫通孔の深さ/前記貫通孔の開口径)が1/6以上2/3以下であることを特徴とするスパッタ装置を提供する。

【0015】

また、本発明は、複数の貫通孔が形成され、前記貫通孔のアスペクト比(前記貫通孔の深さ/前記貫通孔の開口径)が1/6以上2/3以下であることを特徴とするコリメート板を提供する。

【発明の効果】

【0016】

本発明によれば、ターゲットの利用率を十分に向上させることができるとともに、プラズマダメージを十分に抑制することができる。

【図面の簡単な説明】

【0017】

【図1】第1の実施形態に係る半導体装置の製造方法の一連の工程を示すフローチャートである。

【図2】第1の実施形態に係るスパッタ装置の正面断面図である。

【図3】第1の実施形態に係るコリメート板を示す図であり、このうち(a)は平面図、(b)は正面断面図である。

【図4】第1の実施形態に係る半導体装置の製造方法を説明するための一連の工程図である。

【図5】第1の実施形態に係る半導体装置の製造方法を説明するための一連の工程図である。

【図6】第1の実施形態に係る半導体装置の製造方法を説明するための一連の工程図である。

【図7】第1の実施形態に係る半導体装置の製造方法を説明するための一連の工程図である。

【図8】ウェハの面内における成膜速度及び膜厚均一性と、コリメート板の貫通孔のアスペクト比と、の関係を示す図である。

【図9】ウェハの面内における成膜速度及び膜厚均一性と、コリメート板の貫通孔のアスペクト比と、の関係をプロットしたグラフを示す図である。

【図10】ウェハの面内における成膜速度及び膜厚均一性と、コリメート板の貫通孔のアスペクト比と、の関係をプロットしたグラフを示す図である。

【図11】半導体装置のアンテナ比とゲート絶縁膜へのプラズマダメージとの関係を示す図である。

【発明を実施するための形態】

【0018】

以下、本発明の実施形態について、図面を用いて説明する。なお、すべての図面において、同様の構成要素には同一の符号を付し、適宜に説明を省略する。

【0019】

〔第1の実施形態〕

図1は第1の実施形態に係る半導体装置の製造方法の一連の工程を示すフローチャートであり、特に、半導体装置のシリサイド形成工程に含まれる一連の工程を示す。図2は第1の実施形態に係るスパッタ装置100の正面断面図である。図3は第1の実施形態に係るコリメート板1を示す図であり、このうち(a)は平面図、(b)は正面断面図である。図4乃至図7は第1の実施形態に係る半導体装置の製造方法を説明するための一連の工程図である。図8はウェハの面内における成膜速度及び膜厚均一性と、コリメート板1の貫通孔2のアスペクト比と、の関係を示す図であり、図9及び図10はウェハの面内における成膜速度及び膜厚均一性と、コリメート板1の貫通孔のアスペクト比と、の関係をプロットしたグラフを示す図である。図11は半導体装置のアンテナ比とゲート絶縁膜38へのプラズマダメージとの関係を示す図である。

【0020】

本実施形態に係る半導体装置の製造方法では、複数の貫通孔2が形成されているコリメート板1を介してスパッタを行うことにより、ゲート絶縁膜38及びゲート電極33を有する半導体素子上に金属膜(例えば、Co膜37)を形成する金属膜形成工程(ステップS1)を備え、金属膜形成工程では、貫通孔2のアスペクト比(貫通孔2の深さD/貫通孔2の開口径W)が1/6以上2/3以下であるコリメート板1を用いる。また、本実施形態に係るスパッタ装置100は、スパッタ室10と、スパッタ室10内において相互に対向するように配置されているバッキングプレート12及び成膜対象物ホルダ(例えば、基板ホルダ13)と、バッキングプレート12と成膜対象物ホルダ(例えば、基板ホルダ13)との間に配置されているコリメート板1と、バッキングプレート12と成膜対象物ホルダ(例えば、基板ホルダ13)との間の空間の周囲に配置され、コリメート板1と電気的に接続されるシールド4と、を備え、バッキングプレート12にはターゲット11を、成膜対象物ホルダ(例えば、基板ホルダ13)には成膜対象物(例えば、ウェハ20)を、成膜対象物(例えば、ウェハ20)とターゲット11とがコリメート板1を挟んで相互に対向するようにそれぞれ配置した状態で、バッキングプレート12とシールド4との間に電圧を印加することにより、プラズマを形成して、ターゲット11から飛び出すスパッタ粒子をコリメート板1を介して成膜対象物(例えば、ウェハ20)に付着させるように構成され、コリメート板1には複数の貫通孔2が形成され、貫通孔2のアスペクト比(貫通孔2の深さD/貫通孔2の開口径W)が1/6以上2/3以下である。また、本実施形態に係るコリメート板1は、複数の貫通孔2が形成され、貫通孔2のアスペクト比(貫通孔2の深さD/貫通孔2の開口径W)が1/6以上2/3以下である。以下、詳細に説明する。

【0021】

先ず、本実施形態に係るスパッタ装置100の構成を説明する。

【0022】

図2に示すように、スパッタ装置100は、スパッタ室10と、スパッタ室10内において相互に対向するように配置されているバッキングプレート12及び基板ホルダ13と、これらバッキングプレート12と基板ホルダ13との間に配置されているコリメート板1と、を備える。更に、スパッタ装置100は、コリメート板保持部3と、シールド4と、ウェハ保持部5と、をスパッタ室10内に備え、カソードマグネット7をスパッタ室10の上側に備えている。さらに図示していないが、シールド4の内側には、シールド4の内側にスパッタガスを導入するガス導入口が設けられている。また、スパッタ室10は真空ポンプに接続されている。スパッタ室10内は、スパッタを行っていない時は真空ポンプによって高真空に保たれ、スパッタ時は真空ポンプによって排気を行いながら、ガス導入口より所定流量の不活性ガス(例えばAr)をシールド4の内側に流し、シールド4の内側のガス圧力を0.1mTorr〜50mTorrの間の一定圧力とする。このスパッタ装置100により、コリメートスパッタを行うことが可能である。

【0023】

シールド4、コリメート板保持部3及びバッキングプレート12は、それぞれ導電性の材質(例えば金属)からなる。シールド4は、図2に示すように、バッキングプレート12と基板ホルダ13との間の空間の周囲に配置されている。このシールド4は、コリメート板1と電気的に接続される。具体的には、例えば、以下に説明するように、シールド4は、コリメート板保持部3を介してコリメート板1と電気的に接続されている。コリメート板保持部3は、例えば、シールド4に固定されている。なお、シールド4の一部によりコリメート板保持部3が構成されていても良い。このコリメート板保持部3は、例えば、コリメート板1の外周部の被保持部9(図3:後述)を上下から挟み持つようにして保持する。これにより、シールド4は、コリメート板保持部3を介してコリメート板1と電気的に接続される。ターゲット11は、メタルボンディングもしくは拡散接合により、バッキングプレート12における基板ホルダ13側の面上に取り付けられている。成膜対象物としての半導体ウェハ(以下、単にウェハ)20は、基板ホルダ13におけるバッキングプレート12側の面上に配置される。ウェハ保持部5は、基板ホルダ13上においてウェハ20を所定位置に位置決めする。こうして、ウェハ20とターゲット11とがコリメート板1を挟んで相互に対向するように配置される。なお、基板ホルダ13は、接地(アース接続)されていても良いし、どこにも接地されていなくても良い。この状態で、所定流量の不活性ガス(例えばAr)を、ガス導入口よりシールド4の内側に流し、シールド4の内側のガス圧力を0.1mTorr〜50mTorrの間の一定圧力に設定し、バッキングプレート12とシールド4との間に電圧を印加することにより、不活性ガスのプラズマが発生する。これにより、ターゲット11から飛び出すスパッタ粒子をコリメート板1を介してウェハ20に付着させて、ウェハ20上に金属膜を成膜させることができる。

【0024】

なお、本実施形態に係るスパッタ装置100は、コリメート板1以外の構成については、周知のコリメートスパッタ用のスパッタ装置と同様であるため詳細な説明を省略する。

【0025】

このスパッタ装置100は、例えば、半導体装置のシリサイド形成工程で用いられるシリサイド形成用スパッタ装置である。

【0026】

次に、図3を参照してコリメート板1の構成を説明する。

【0027】

図3に示すように、コリメート板1は、扁平な板状の本体部8を備えている。この本体部8には、該本体部8の表裏を貫通するように複数の貫通孔2が形成されている。

【0028】

貫通孔2の深さ(縦方向長さ)をD(図3(b))、貫通孔2の開口径(横方向長さ:例えば、対向する2つの角の間の距離)をW(図3(a)、(b))とすると、貫通孔2のアスペクト比は、D/Wで表される。貫通孔2のアスペクト比は1/6以上2/3以下に設定されている。アスペクト比を2/3以下とするのは、コリメート板1により捕捉されるスパッタ粒子を減らしターゲット11の利用率を高くするためである。アスペクト比を1/6以上とするのは、コリメート板1により荷電粒子を十分に捕捉し、プラズマダメージの低減効果を十分に得るためである。

【0029】

更に、このアスペクト比は、コリメート板1の中央部から外周部に向けて徐々に小さくなっていることがより好ましい。具体的には、例えば、図3(b)に示すように、貫通孔2の深さD(本体部8の厚さに等しい)をコリメート板1の中央部から外周部に向けて徐々に薄くすることにより、アスペクト比をコリメート板1の中央部から外周部に向けて徐々に小さくしている。

【0030】

このように貫通孔2のアスペクト比がコリメート板1の中央部から外周部に向けて徐々に小さくなっている場合に、コリメート板1の最外周部ではこのアスペクト比が1/2以下であることが好ましい。このようなコリメート板1を用いることにより、ターゲット11の利用率、プラズマダメージ低減効果、及び膜厚均一性をそれぞれ良好にすることができる。なお、コリメート板1の中央部の貫通孔2のアスペクト比は2/3程度とすることが好ましい。

【0031】

ターゲット11の利用率を更に向上させる方法として、ターゲット11からスパッタされる粒子の方向分布を調整する方法がある。スパッタ面に対して垂直方向にスパッタされる粒子の割合を増やせば、コリメート板1により捕捉される粒子の割合が減り、ウェハ20に到達する割合が増加してターゲット11の利用率が上がる。スパッタ面に対して垂直方向にスパッタされる粒子の割合を増やす方法としては、スパッタ面を金属結晶の最稠密面に垂直な面とする方法、或いは、スパッタの放電電圧を高くする方法がある。

【0032】

また、本体部8の外周部には、コリメート板保持部3により保持される被保持部9が形成されている。

【0033】

図3に示すように、貫通孔2の平面形状は、例えば、正六角形であり、コリメート板1の平面形状は、六方最密格子形状となっている。各貫通孔2の平面寸法及び形状は、コリメート板1のほぼ全面で均一とされている。ただし、コリメート板1の最外周部では、例えば、コリメート板1の外周形状に合わせて、正六角形とは異なる異形形状(正六角形の一部分を切り取ったような形状)の貫通孔2aが形成されており、正六角形の貫通孔2bと比べて平面寸法も小さくされている。なお、貫通孔2bの平面寸法(開口径W)は、10mm以上30mm以下であることが好ましく、貫通孔2bの深さは、3mm以上20mm以下であることが好ましい。

【0034】

なお、貫通孔2の平面形状及びコリメート板1の平面形状は、この例に限らない。例えば、貫通孔2は、四角形、長方形、正方形、ひし形、円形などであっても良い。また、図3では平面視におけるコリメート板1の外周形状が円形である例を示しているが、コリメート板1の外周形状はその他の形状であっても良い。

【0035】

また、隣り合う貫通孔2を相互に仕切る隔壁2cの厚さは、0.5mm以上2mm以下であることが好ましい。

【0036】

また、コリメート板1の材質としては、例えば、チタン、SUSが挙げられる。

【0037】

次に、本実施形態に係る半導体装置の製造方法を説明する。

【0038】

図1に示すように、本実施形態に係る半導体装置の製造方法では、金属膜(例えばCo膜37)を成膜する金属膜成膜工程(ステップS1)と、1回目の熱処理によりシリサイド化を行う第1熱処理工程と(ステップS2)と、未反応金属を除去する除去工程(ステップS3)と、2回目の熱処理を行う第2熱処理工程(ステップS4)と、をこの順に行うことにより、半導体素子上にシリサイド層39を形成する。

【0039】

本実施形態に係る半導体装置の製造方法では、先ず、図4に示すように、一般的なCMOS(Complementary Metal Oxide Semiconductor)の製造方法によって半導体素子を作成する。すなわち、シリコン基板31上に、素子分離膜としてのSTI(Shallow Trench Isolation)32、ゲート絶縁膜38、ゲート電極33、エクステンション34、サイドウォール35及びソース・ドレイン拡散領域36を形成することにより、半導体素子を作成する。

【0040】

ここで、この半導体素子としては、アンテナ比が45000以下となるように作成された半導体素子を用いることが好ましい。ここで、アンテナ比は、ゲート電極33の面積をS1、ゲート絶縁膜38の面積をS2とすると、S1/S2で表される。

【0041】

なお、ゲート絶縁膜38の膜厚は、例えば、18Å(1.8nm)以上70Å(7nm)とすることができる。

【0042】

次に、図4に示すように、この半導体素子上にコバルト膜37(以下、Co膜37)を成膜する。すなわち、半導体素子のシリコン層(例えば、ソース・ドレイン拡散領域36、及び、ポリシリコンからなるゲート電極33)上及び絶縁層(例えば、STI32及びサイドウォール35)上に、コバルト膜37を成膜する(図1のステップS1)。なお、この成膜前には、例えば、フッ酸系のエッチング液によりウェハ20の表面の自然酸化膜を除去しておくことが好ましい。

【0043】

ステップS1の成膜は、スパッタ装置100を用いたコリメートスパッタにより行う。

【0044】

ここで、ターゲット11としては、Co(コバルト)ターゲットを用いる。ターゲット11は、例えば、そのスパッタ面(コリメート板1及びウェハ20の方を向く面)が面方位(002)が主配向となるように構成されている。すなわち、ターゲット11がスパッタ装置100のバッキングプレート12に上述したように取り付けられた状態で、多結晶Coからなるターゲット11の結晶配向において、主として(002)の面がコリメート板1及びウェハ20の方を向くように、ターゲット11は構成されている。これは、コバルトの場合(002)面に垂直な方向で透磁率が最も低く、カソードマグネット7によりターゲット11の表面部付近に形成される磁場の強さの低下を小さくするためである。

【0045】

また、コリメート板1とターゲット11との距離は、20mm以上40mm以下であることが好ましい。また、コリメート板1とウェハ20との距離は20mm以上50mm以下であることが好ましい。また、ゲート電極33に到達する電荷量が0.1C/cm2以下となるような条件でスパッタを行うことが好ましい。

【0046】

このスパッタは、放電電圧を400V以上600V以下、スパッタ電力を1kw以上5kw以下、スパッタ温度(例えば、ウェハ20の温度)を300℃以上400℃以下として行うことが好ましい。

【0047】

このようにCo膜37を成膜した後は、1回目の熱処理(アニール)を行う(図1のステップS2)。この熱処理により、Co膜37はその下層に位置するシリコン層(例えば、ソース・ドレイン拡散領域36、及び、ポリシリコンなどからなるゲート電極33)と反応してシリサイド化する。これにより、図5に示すように、ソース・ドレイン拡散領域36上、及び、ゲート電極33上にシリサイド層(コバルトシリサイド層)39を形成することができる。

【0048】

次に、このような1回目の熱処理後のウェハ20を例えばHPM(hydrochloic acid/hydrogen Peroxide Mixture)などの薬液に浸すことによって、未反応金属(図5の段階で残留しているCo膜37)を除去する除去処理を行う(図1のステップS3)。これにより、図6に示すように、未反応金属を除去することができる。

【0049】

このように未反応金属を除去した後は、2回目の熱処理(図1のステップS4)を行う。これにより、半導体装置50(図7)を得ることができる。

【0050】

次に、図8乃至図10を参照して、実施例及び比較例について説明する。

【0051】

なお、各実施例及び各比較例のデータは、図1のステップS1の金属膜形成工程の直後にCo膜37の膜厚を測定することにより得たデータである。また、各実施例及び比較例は、スパッタに用いたコリメート板1が互いに異なる他は、全てのスパッタ条件(スパッタ時間、スパッタ電力及びスパッタ室10内のArの流量等)を同一条件とした。このため、ターゲット11の利用率は膜厚(または成膜速度)に比例する。なお、図8及び図9の膜厚均一性は、ウェハ20上のCo膜37の膜厚の平均値をX、最も厚い部分の膜厚をY1、最も薄い部分の膜厚をY2とすると、{(Y1−Y2)/2X}×100(%)で表される。

【0052】

先ず、実施例1として、コリメート板1の全面に亘って貫通孔2のアスペクト比(図中のA/R)を2/3とした場合には、図8乃至図10に示すように、ウェハ20上のCo膜37の膜厚均一性が3.0%となり、成膜速度は6Å/秒程度となった。

【0053】

この比較例1として、コリメート板(図示略)の全面に亘って貫通孔のアスペクト比を1とした場合には、図8乃至図10に示すように、ウェハ20上のCo膜の膜厚均一性が1.2%となり、成膜速度は4Å/秒前後となった。比較例1では、実施例1よりも成膜速度が遅い、つまり、ターゲット11の利用率が悪いことが分かる。

【0054】

次に、実施例2として、コリメート板1の全面に亘って貫通孔2のアスペクト比を1/3とした場合には、図8乃至図10に示すように、ウェハ20上のCo膜37の膜厚均一性が6.5%となり、成膜速度は10Å/秒〜11Å/秒程度となった。つまり、アスペクト比を小さくすることにより、ターゲット11の利用率を更に向上させることができる。

【0055】

次に、実施例3として、コリメート板1の中央部では貫通孔2のアスペクト比が2/3、コリメート板1の最外周部では貫通孔2のアスペクト比が1/2であり、中央部から外周部にかけて徐々にアスペクト比を小さくしたコリメート板1を用いた場合を説明する。この場合、図8及び図10に示すように、ウェハ20上のCo膜37の膜厚均一性が1.2%となり、成膜速度は8Å/秒前後となった。つまり、実施例3のコリメート板1を用いることにより、ターゲット11の利用率を高い水準(約8Å/秒)にでき、且つ、膜厚均一性も高い水準(約1.2%)にすることができる。

【0056】

更に、実施例4として、コリメート板1の中央部では貫通孔2のアスペクト比が2/3、コリメート板1の最外周部では貫通孔2のアスペクト比が0.6(3/5)であり、中央部から外周部にかけて徐々にアスペクト比を小さくしたコリメート板1を用いた場合を説明する。この場合、図10に示すように、ウェハ20上のCo膜37の膜厚均一性が1.3%程度となり、成膜速度は7Å/秒前後となった。

【0057】

同様に、実施例5として、コリメート板1の中央部では貫通孔2のアスペクト比が2/3、コリメート板1の最外周部では貫通孔2のアスペクト比が0.4(2/5)であり、中央部から外周部にかけて徐々にアスペクト比を小さくしたコリメート板1を用いた場合を説明する。この場合、図10に示すように、ウェハ20上のCo膜37の膜厚均一性が1.1%程度となり、成膜速度は9Å/秒程度となった。

【0058】

同様に、実施例6として、コリメート板1の中央部では貫通孔2のアスペクト比が2/3、コリメート板1の最外周部では貫通孔2のアスペクト比が0.3(3/10)であり、中央部から外周部にかけて徐々にアスペクト比を小さくしたコリメート板1を用いた場合を説明する。この場合、図10に示すように、ウェハ20上のCo膜37の膜厚均一性が1.4%程度となり、成膜速度は10Å/秒前後となった。

【0059】

同様に、実施例7として、コリメート板1の中央部では貫通孔2のアスペクト比が2/3、コリメート板1の最外周部では貫通孔2のアスペクト比が1/6であり、中央部から外周部にかけて徐々にアスペクト比を小さくしたコリメート板1を用いた場合を説明する。この場合、図10に示すように、ウェハ20上のCo膜37の膜厚均一性が1.8%程度となり、成膜速度は11Å/秒前後となった。

【0060】

つまり、実施例4乃至7のコリメート板1を用いることによっても、ターゲット11の利用率を高い水準(約7Å/秒〜11Å/秒程度)にでき、且つ、膜厚均一性も高い水準(約1.1〜1.8%)にすることができる。

【0061】

なお、比較例2として、コリメート板を用いずにスパッタを行った場合(図中のアスペクト比=0)には、図9に示すように、成膜速度が約16Å/秒となった。ただし、この場合、背景技術で説明したように、プラズマダメージを低減することができない。

【0062】

次に、図11を参照して、図1のステップS1の金属膜形成工程で用いる半導体素子(半導体装置)のアンテナ比とゲート絶縁膜へのプラズマダメージとの関係について説明する。

【0063】

図11に示すように、上述の比較例1のコリメート板(アスペクト比が1)を用いた場合には、アンテナ比が800以上45000以下の範囲では、プラズマダメージが観察されず、アンテナ比が125000の場合にはプラズマダメージが観察されたゲート絶縁膜が存在した。

【0064】

一方、実施例8として、コリメート板1の中央部では貫通孔2のアスペクト比が2/3、コリメート板1の最外周部では貫通孔2のアスペクト比が1/3であり、中央部から外周部にかけて徐々にアスペクト比を小さくしたコリメート板1を用いた場合を説明する。この場合にも、アンテナ比が800以上45000以下の範囲では、プラズマダメージが観察されず、アンテナ比が125000の場合にはプラズマダメージが観察されたゲート絶縁膜38が存在した。このように、実施例8のコリメート板1を用いた場合のプラズマダメージの程度は、比較例1のコリメート板を用いた場合と同程度に抑制できた。このように、図1のステップS1の金属膜形成工程では、アンテナ比が45000以下の半導体素子を用いることにより、プラズマダメージの影響を十分に抑制することができる。

【0065】

以上のような第1の実施形態によれば、複数の貫通孔2が形成されているコリメート板1を介してスパッタを行うことにより、ゲート絶縁膜38及びゲート電極33を有する半導体素子上に金属膜(例えば、Co膜37)を形成する金属膜形成工程(ステップS1)を備え、金属膜形成工程では、貫通孔2のアスペクト比が1/6以上2/3以下であるコリメート板1を用いるので、コリメート板1によるスパッタ粒子の捕捉割合を低下させることにより、ターゲット11の利用率を十分に向上させることができる。しかも、貫通孔2のアスペクト比が1/6以上であるので、ゲート絶縁膜38へのプラズマダメージも十分に抑制することができる。

【0066】

また、ターゲット11の利用率を向上させることにより、ターゲット11の消費量を抑制できるため、ターゲット11の交換頻度を低減し、スパッタ装置100の稼働率を向上させることができる。また、コリメート板1を用いたスパッタを繰り返し行うと、貫通孔2内には次第にスパッタ粒子が堆積し、貫通孔2が詰まってくる。すると、金属膜の成膜速度が低下する。しかも、膜厚均一性も悪化する。具体的には、ウェハ20の外周部で膜厚が厚くなり、中央部では膜厚が薄くなる。このため、スパッタ装置100には、コリメート板1を取り外して薬液で洗浄する等のメンテナンスが必要である。このような事情に対し、貫通孔2のアスペクト比が2/3以下のコリメート板1を用いることにより、アスペクト比が2/3を超えるコリメート板を用いる場合と比べて、貫通孔2を詰まりにくくすることができるので、コリメート板1のメンテナンス頻度も低減することができる。

【0067】

また、金属膜形成工程(ステップS1)を、半導体装置50のシリサイド形成工程で行うので、半導体装置50のシリサイド層39を均一な膜厚で形成することができる。

【0068】

また、金属膜形成工程(ステップS1)に用いられる半導体素子(半導体装置)のアンテナ比を45000以下とすることにより、ゲート絶縁膜38へのプラズマダメージを抑制することができる。

【0069】

また、Co(コバルト)は強磁性体であるため、コバルトからなるターゲット11を用いる場合、カソードマグネット7によりターゲット11の表面付近に形成される磁場が弱くなり、放電もし難い。コバルトの透磁率は結晶格子の方向によって異なり、(002)面に垂直な方向で最も小さくなる事が知られている。本実施形態では、コバルトからなるターゲット11のスパッタ面を(002)面を主配向とする面として金属膜形成工程(ステップS1)を行うことにより、ターゲット11の表面付近に形成されるカソードマグネット7による磁場の強度低下を抑制し、スパッタを好適に行うことができる。

【0070】

また、貫通孔2のアスペクト比が、コリメート板1の中央部から外周部に向けて徐々に小さくなっているので、金属膜形成工程(ステップS1)で形成される金属膜の膜厚の面内均一性を高めることができる。具体的には、コリメート板1の中央部での貫通孔2のアスペクト比を2/3程度とし、最外周部での貫通孔2のアスペクト比を1/2以下とすることにより、金属膜形成工程(ステップS1)で形成される金属膜の膜厚の面内均一性を高めることができる。

【0071】

上記の実施形態では、金属膜形成工程で成膜する金属膜としてCo膜37を例示したが、この金属膜はCo膜37に限らず、例えば、Ni(ニッケル)膜、或いはTi(チタン)膜であっても良い。従って、ターゲット11としては、Niターゲット、或いはTiターゲットを用いることができる。

【0072】

また、上記の金属膜形成工程は、シリサイド形成工程以外の半導体製造工程で用いても良いし、或いは、半導体製造工程以外に上記の金属膜形成工程を適用しても良い。また、スパッタ装置100がシリサイド形成用スパッタ装置である例を説明したが、スパッタ装置100はシリサイド形成用以外のスパッタ装置であっても良い。

【符号の説明】

【0073】

1 コリメート板

2 貫通孔

2a 貫通孔

2b 貫通孔

2c 隔壁

3 コリメート板保持部

4 シールド

5 ウェハ保持部

7 カソードマグネット

8 本体部

9 被保持部

10 スパッタ室

11 ターゲット

12 バッキングプレート

13 基板ホルダ(成膜対象物ホルダ)

20 半導体ウェハ

31 シリコン基板

32 STI

33 ゲート電極

34 エクステンション

35 サイドウォール

36 ソース・ドレイン拡散領域

37 コバルト膜

38 ゲート絶縁膜

39 シリサイド層

50 半導体装置

100 スパッタ装置

【特許請求の範囲】

【請求項1】

複数の貫通孔が形成されているコリメート板を介してスパッタを行うことにより、ゲート絶縁膜及びゲート電極を有する半導体素子上に金属膜を形成する金属膜形成工程を備え、

前記金属膜形成工程では、前記貫通孔のアスペクト比(前記貫通孔の深さ/前記貫通孔の開口径)が1/6以上2/3以下である前記コリメート板を用いることを特徴とする半導体装置の製造方法。

【請求項2】

前記金属膜形成工程をシリサイド形成工程で行うことを特徴とする請求項1に記載の半導体装置の製造方法。

【請求項3】

前記半導体素子のアンテナ比(前記ゲート電極の面積/前記ゲート絶縁膜の面積)が45000以下であることを特徴とする請求項1又は2に記載の半導体装置の製造方法。

【請求項4】

前記金属膜形成工程では、前記スパッタのターゲットとしてCoターゲットを用いて、前記金属膜としてCo膜を形成することを特徴とする請求項1乃至3の何れか一項に記載の半導体装置の製造方法。

【請求項5】

前記ターゲットのスパッタ面は、(002)面が主配向の面であることを特徴とする請求項4に記載の半導体装置の製造方法。

【請求項6】

前記アスペクト比が前記コリメート板の中央部から外周部に向けて徐々に小さくなっていることを特徴とする請求項1乃至5の何れか一項に記載の半導体装置の製造方法。

【請求項7】

前記コリメート板の最外周部では前記アスペクト比が1/2以下であることを特徴とする請求項6に記載の半導体装置の製造方法。

【請求項8】

スパッタ室と、

前記スパッタ室内において相互に対向するように配置されているバッキングプレート及び成膜対象物ホルダと、

前記バッキングプレートと前記成膜対象物ホルダとの間に配置されているコリメート板と、

前記バッキングプレートと前記成膜対象物ホルダとの間の空間の周囲に配置され、前記コリメート板と電気的に接続されるシールドと、

を備え、

前記バッキングプレートにはターゲットを、前記成膜対象物ホルダには成膜対象物を、前記成膜対象物と前記ターゲットとが前記コリメート板を挟んで相互に対向するようにそれぞれ配置した状態で、前記バッキングプレートと前記シールドとの間に電圧を印加することにより、プラズマを形成して、前記ターゲットから飛び出すスパッタ粒子を前記コリメート板を介して前記成膜対象物に付着させるように構成され、

前記コリメート板には複数の貫通孔が形成され、前記貫通孔のアスペクト比(前記貫通孔の深さ/前記貫通孔の開口径)が1/6以上2/3以下であることを特徴とするスパッタ装置。

【請求項9】

当該スパッタ装置は、半導体装置のシリサイド形成工程で用いられるシリサイド形成用スパッタ装置であることを特徴とする請求項8に記載のスパッタ装置。

【請求項10】

前記アスペクト比が前記コリメート板の中央部から外周部に向けて徐々に小さくなっていることを特徴とする請求項8又は9に記載のスパッタ装置。

【請求項11】

前記コリメート板の最外周部では前記アスペクト比が1/2以下であることを特徴とする請求項10に記載のスパッタ装置。

【請求項12】

複数の貫通孔が形成され、前記貫通孔のアスペクト比(前記貫通孔の深さ/前記貫通孔の開口径)が1/6以上2/3以下であることを特徴とするコリメート板。

【請求項13】

前記アスペクト比が当該コリメート板の中央部から外周部に向けて徐々に小さくなっていることを特徴とする請求項12に記載のコリメート板。

【請求項14】

当該コリメート板の最外周部では前記アスペクト比が1/2以下であることを特徴とする請求項13に記載のコリメート板。

【請求項1】

複数の貫通孔が形成されているコリメート板を介してスパッタを行うことにより、ゲート絶縁膜及びゲート電極を有する半導体素子上に金属膜を形成する金属膜形成工程を備え、

前記金属膜形成工程では、前記貫通孔のアスペクト比(前記貫通孔の深さ/前記貫通孔の開口径)が1/6以上2/3以下である前記コリメート板を用いることを特徴とする半導体装置の製造方法。

【請求項2】

前記金属膜形成工程をシリサイド形成工程で行うことを特徴とする請求項1に記載の半導体装置の製造方法。

【請求項3】

前記半導体素子のアンテナ比(前記ゲート電極の面積/前記ゲート絶縁膜の面積)が45000以下であることを特徴とする請求項1又は2に記載の半導体装置の製造方法。

【請求項4】

前記金属膜形成工程では、前記スパッタのターゲットとしてCoターゲットを用いて、前記金属膜としてCo膜を形成することを特徴とする請求項1乃至3の何れか一項に記載の半導体装置の製造方法。

【請求項5】

前記ターゲットのスパッタ面は、(002)面が主配向の面であることを特徴とする請求項4に記載の半導体装置の製造方法。

【請求項6】

前記アスペクト比が前記コリメート板の中央部から外周部に向けて徐々に小さくなっていることを特徴とする請求項1乃至5の何れか一項に記載の半導体装置の製造方法。

【請求項7】

前記コリメート板の最外周部では前記アスペクト比が1/2以下であることを特徴とする請求項6に記載の半導体装置の製造方法。

【請求項8】

スパッタ室と、

前記スパッタ室内において相互に対向するように配置されているバッキングプレート及び成膜対象物ホルダと、

前記バッキングプレートと前記成膜対象物ホルダとの間に配置されているコリメート板と、

前記バッキングプレートと前記成膜対象物ホルダとの間の空間の周囲に配置され、前記コリメート板と電気的に接続されるシールドと、

を備え、

前記バッキングプレートにはターゲットを、前記成膜対象物ホルダには成膜対象物を、前記成膜対象物と前記ターゲットとが前記コリメート板を挟んで相互に対向するようにそれぞれ配置した状態で、前記バッキングプレートと前記シールドとの間に電圧を印加することにより、プラズマを形成して、前記ターゲットから飛び出すスパッタ粒子を前記コリメート板を介して前記成膜対象物に付着させるように構成され、

前記コリメート板には複数の貫通孔が形成され、前記貫通孔のアスペクト比(前記貫通孔の深さ/前記貫通孔の開口径)が1/6以上2/3以下であることを特徴とするスパッタ装置。

【請求項9】

当該スパッタ装置は、半導体装置のシリサイド形成工程で用いられるシリサイド形成用スパッタ装置であることを特徴とする請求項8に記載のスパッタ装置。

【請求項10】

前記アスペクト比が前記コリメート板の中央部から外周部に向けて徐々に小さくなっていることを特徴とする請求項8又は9に記載のスパッタ装置。

【請求項11】

前記コリメート板の最外周部では前記アスペクト比が1/2以下であることを特徴とする請求項10に記載のスパッタ装置。

【請求項12】

複数の貫通孔が形成され、前記貫通孔のアスペクト比(前記貫通孔の深さ/前記貫通孔の開口径)が1/6以上2/3以下であることを特徴とするコリメート板。

【請求項13】

前記アスペクト比が当該コリメート板の中央部から外周部に向けて徐々に小さくなっていることを特徴とする請求項12に記載のコリメート板。

【請求項14】

当該コリメート板の最外周部では前記アスペクト比が1/2以下であることを特徴とする請求項13に記載のコリメート板。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【公開番号】特開2010−255048(P2010−255048A)

【公開日】平成22年11月11日(2010.11.11)

【国際特許分類】

【出願番号】特願2009−106490(P2009−106490)

【出願日】平成21年4月24日(2009.4.24)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

【公開日】平成22年11月11日(2010.11.11)

【国際特許分類】

【出願日】平成21年4月24日(2009.4.24)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

[ Back to top ]